### Development of FETs based on ultra-wide band gap materials for high voltage power electronics

Jash Mehta

#### ▶ To cite this version:

Jash Mehta. Development of FETs based on ultra-wide band gap materials for high voltage power electronics. Micro and nanotechnologies/Microelectronics. Université de Lille, 2024. English. NNT: 2024ULILN018. tel-04666870

## $\begin{array}{c} {\rm HAL~Id:~tel\text{-}04666870} \\ {\rm https://hal.science/tel\text{-}04666870v1} \end{array}$

Submitted on 28 Nov 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Development of FETs based on ultra-wide band gap materials for high voltage power electronics

# Développement de FET basés sur des matériaux à bande interdite ultra-large pour l'électronique de puissance haute tension

#### Thèse

présentée à l'Université de Lille, faculté des Sciences et Technologies Institut d'Electronique, de Microélectronique et de Nanotechnologies (IEMN) UMR CNRS 8520 par

### Jash Rinku MEHTA

pour obtenir le titre de

#### **DOCTEUR DE L'UNIVERSITE**

Spécialité : Electronique, microélectronique, nanoélectronique et micro-ondes, Ecole Soutenue le **25 Juin 2024** devant le jury composé de :

M. Frédéric MORANCHO Rapporteur

Professeur (Université de Toulouse)

M. Jérôme BILLOUE Rapporteur

Professeur (Université de Tours)

Mme. Marie-Paule BESLAND Examinatrice

Directrice de Recherche CNRS (IMN, Nantes)

M. Gaudenzio MENEGHESSO Examinateur

Professeur (Università di Padova)

M. Yvon CORDIER Invité

Directeur de recherche CNRS (CRHEA)

M. Tuami LASRI Examinateur

Professeur (Université de Lille) (President of Jury)

M. Farid MEDIDOUB Directeur de Thèse

Chercheur CNRS (IEMN)

### Acknowledgements

Completing this PhD has been a long, rewarding, and often challenging journey, and so many people made this possible, to whom I owe my deepest gratitude.

First, to my supervisor, Dr. Farid MEDJDOUB, I cannot thank you enough for your guidance, patience, and wisdom throughout this process. You pushed me to think deeper, work harder, and always aim higher. Your support has been invaluable, and I'm truly grateful for everything you've done. I'm also thankful to the reporters of my committee, Prof. Morancho, and Prof. Billoue, for their time, insights, and constructive feedback. Your suggestions helped shape this research into something I am truly proud of.

Special thanks to my project partners from various CNRS institutes throughout France who have been crucial to this journey. The stimulating discussions, collaboration, and shared challenges have been a source of inspiration. A huge thanks to IEMN engineers for their continuous support in clean room and characterization platforms.

To all my colleagues of team WIND and friends in IEMN and Lille, thank you for the countless conversations, brainstorming sessions, and much-needed coffee breaks. You've made the tough times easier and the good times even better. I'll cherish all the friendships we've built over the years.

I am forever grateful to my family for their endless support. To my parents, thank you for always believing in me, even when I doubted myself. Your love and encouragement have been my foundation. And to my partner, I couldn't have done this without your understanding and unwavering support. You have been my rock.

This PhD journey has been a collective effort, and I dedicate this work to all of you who stood by me and lifted me when I needed it most.

# Table of Contents

| List of Figures                                        |                       |

|--------------------------------------------------------|-----------------------|

| List of Table                                          | 1                     |

| General Introduction                                   | Introduction          |

| Chapter-01 Introduction                                |                       |

| 1.1 Introduction to Power Electronics                  |                       |

| 1.2 Gallium Nitride (GaN)                              |                       |

| 1.2.1 Crystal properties                               | 2                     |

| 1.2.2 Epitaxy techniques                               | 2                     |

| 1.3 GaN HEMTs                                          |                       |

| 1.3.1 History of HEMTs                                 | 2                     |

| 1.3.2 Formation of 2-DEG                               | 3                     |

| 1.3.3 GaN HEMT Structure                               | 3                     |

|                                                        |                       |

|                                                        |                       |

|                                                        |                       |

|                                                        |                       |

| •                                                      |                       |

|                                                        |                       |

| 1.3.10 Limitations of GaN-on-Si HEMTs for high voltag  | ge power electronics5 |

| 1.4 Power Device Figure of Merit                       |                       |

| 1.5 UWBG semiconductor – Aluminum Gallium Nitride (A   | NGaN)6                |

| 1.6 Towards State-of-the-Art AlGaN channel HFETs       | 6                     |

| Chapter-02 Bulk AlN Substrate for High Voltage Power E | lectronics6           |

| 2.1 Bulk Aluminum Nitride substrate for power electron | nics6                 |

| 2.2 Fabrication of GaN channel MIS-HEMTs on bulk AlN   | ا substrate           |

|                                                        |                       |

| 2.2.2 Device fabrication                               |                       |

|                                                        |                       |

| 2.3.1 Impact of GaN channel thickness on 2DEG          |                       |

|                                                        |                       |

| 2.3.3 Output Characteristics                           |                       |

| 2.3.4 Buffer breakdown measurements                    |                       |

| 2.3.5 Transistor breakdown measurements                |                       |

| 2.4 Electric Field Imaging in GaN-on-AlN MISHEMTs      |                       |

| 2.5 Conclusion                                           | 80  |

|----------------------------------------------------------|-----|

| Chapter-03 AlGaN channel HFETS on Si and bulk AlN        | 82  |

| 3.1 AlGaN channel HFETs on Si                            | 83  |

| 3.1.1 Device Fabrication and structural characterization | 84  |

| 3.1.2 DC characterization                                | 85  |

| 3.1.3 Buffer Breakdown Characteristics                   | 87  |

| 3.1.4 Transistor Breakdown Characteristics               | 87  |

| 3.1.5 High-Temperature DC Characterization               | 88  |

| 3.1.6 Electron Transport in AlGaN channel HFETs on Si    | 91  |

| 3.2 AlGaN channel HFETs on bulk AIN                      | 94  |

| 3.2.1 Device fabrication and structural characterization | 94  |

| 3.2.2 DC Characterization                                | 97  |

| 3.2.3 AIN breakdown characteristics                      | 98  |

| 3.2.4 Transistor breakdown characteristics               | 99  |

| 3.2.5 High voltage robustness test                       | 100 |

| 3.2.6 Impact of SiN and High-Temperature Operation       | 103 |

| 3.2.7 Self-Heating Temperature Measurements              | 106 |

| 3.2.8 State-of-the-Art                                   | 110 |

| 3.3 Ohmic contact to Al-rich AlGaN                       | 111 |

| 3.3.1 Device Fabrication                                 | 111 |

| 3.3.2 DC Characterization                                | 113 |

| 3.3.3 Buffer breakdown characteristics                   | 114 |

| 3.3.4 Transistor breakdown characteristics               | 115 |

| 3.4 Conclusion                                           | 117 |

| General Conclusion                                       | 119 |

| Prospects                                                | 123 |

| Ohmic contact to AlGaN channel                           | 123 |

| Local Substrate Removal                                  | 124 |

| Normally-Off Operation                                   | 124 |

| References                                               | 126 |

| Scientific Contributions                                 | 137 |

### Abstract

Wide Bandgap Semiconductors (WBG) such as Silicon Carbide (SiC) and Gallium Nitride (GaN) show superior material properties to Silicon. However, the even wider bandgap material or dielectric such as Aluminium Gallium Nitride (AlGaN) or Aluminium Nitride (AlN) material system gives the flexibility of creating heterojunctions while dramatically broadening the device design space for medium/high power conversion systems. This thesis will focus on the demonstration of Ultrawide Bandgap (UWBG) semiconductors for developing high-voltage Field-Effect Transistors (FETs). In this context, an approach based on downsizing GaN channel thickness grown on bulk AlN substrates has been developed. The evolution of on-state current density and breakdown voltage has been realized with different GaN channel thicknesses. A high AlN lateral breakdown field of up to 10 MV/cm has been experimentally demonstrated. On the other hand, the integration of bulk AlN substrates to current Silicon foundries is challenging. Thus, it can be said that "What can be done on Silicon, will be done on Silicon." Addressing this challenge, we took an approach toward the demonstration of novel AlGaN channel-based Heterostructure FETs (HFETs) on Silicon for high-voltage applications. The impact of Al composition in the barrier and channel layers on the electrical and thermal performance of various AlGaN/AlGaN HFETs has been studied. Later, we demonstrate robust AlGaN channel HFETs on bulk AlN suitable for extreme power electronics with more than 2 kV breakdown voltage. The major challenge for AlGaN-based HFETs is to develop ohmic contact to the channel addressing which we demonstrated high current density (> 0.2 A/mm) Al-rich AlGaN channel HFETs on Silicon with more than 4 MV/cm average transistor breakdown electric field. This ongoing development in AlGaN HFETs highlights a promising direction that potentially leads to more sustainable and efficient power electronic solutions with smaller device dimensions along with better high voltage/high-temperature operation capabilities.

### Résumé

Les semi-conducteurs à large bande interdite (WBG) tels que le carbure de silicium (SiC) et le nitrure de gallium (GaN) présentent des propriétés physiques supérieures à celles du silicium. Cependant, les matériaux ou diélectriques à bande interdite encore plus large, tels que le nitrure d'aluminium et de gallium (AlGaN) ou le nitrure d'aluminium (AlN), permettent de créer des hétérojonctions tout en élargissant considérablement les possibilités de conception des dispositifs pour les systèmes de conversion d'énergie à moyenne/haute puissance. Cette thèse se concentrera sur la démonstration de semi-conducteurs à bande passante ultra-large (UWBG) pour le développement de transistors à effet de champ (FET) à haute tension. Dans ce contexte, une approche basée sur la réduction de l'épaisseur du canal GaN a été développée sur des substrats d'AlN. L'évolution de la densité de courant à l'état passant et de la tension de claquage a été réalisée avec différentes épaisseurs de canaux GaN. Un champ de claquage latéral élevé de l'AlN allant jusqu'à 10 MV/cm a été démontré expérimentalement. D'autre part, l'intégration de substrats d'AlN dans les fonderies de silicium actuelles est un défi. On peut donc dire que "ce qui peut être fait sur le silicium sera fait sur le silicium". Pour relever ce défi, nous avons adopté une approche visant à démontrer de nouveaux HFET à base de canaux AlGaN sur substrat de silicium pour des applications à haute tension. L'impact de la composition en Al des couches de barrière et du canal sur les performances électriques et thermiques de divers HFET AlGaN/AlGaN a été étudié. Par la suite, nous avons démontré la robustesse des HFET à canal AlGaN sur AlN massif, appropriés à l'électronique de puissance en conditions extremes et une tension d'operation supérieure à 2 kV. Le principal défi pour les HFET à base d'AlGaN est de minimiser les résistances de contacts de source et de drain. Nous avons pu démontrer une densité de courant élevée (> 0,2 A/mm) ainsi que des transistors à canal AlGaN riche en Al sur substrat de silicium avec un champ électrique de claquage moyen supérieur à 4 MV/cm. Ces résultats mettent en evidence une approche prometteuse qui pourrait potentiellement conduire à des solutions pour une électronique de puissance plus durable et plus efficace avec des dimensions de dispositifs réduites ainsi que des capacités de fonctionnement à haute tension/haute temperature accrues.

# List of Figures

| Fig. 1. 1 Power semiconductor devices applications according to the voltage range and            |      |

|--------------------------------------------------------------------------------------------------|------|

| rated power                                                                                      | 23   |

| Fig. 1. 2 Radar chart showing material properties of Si, GaN and SiC                             | 25   |

| Fig. 1. 3 Schematic view of GaN (a.) crystal structure (b.) crystal planes and direction in      |      |

| hexagonal symmetry                                                                               | 26   |

| Fig. 1. 4 Charge distribution profile along with conduction band diagram of an AlGaN/Ga          | aΝ   |

| heterostructureheterostructure                                                                   | 30   |

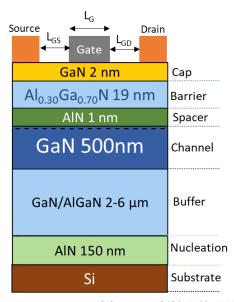

| Fig. 1. 5 Schematic cross-sectional diagram of AlGaN/GaN HEMTs                                   | 32   |

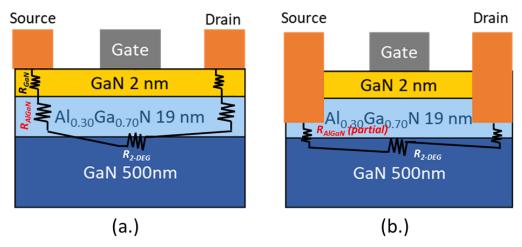

| Fig. 1. 6 Schematic of AlGaN/GaN HEMTs source/drain contacts with (a.) contacts                  |      |

| deposited on top of barrier and (b.) barrier etched contacts along with their contact            |      |

| resistances                                                                                      | 35   |

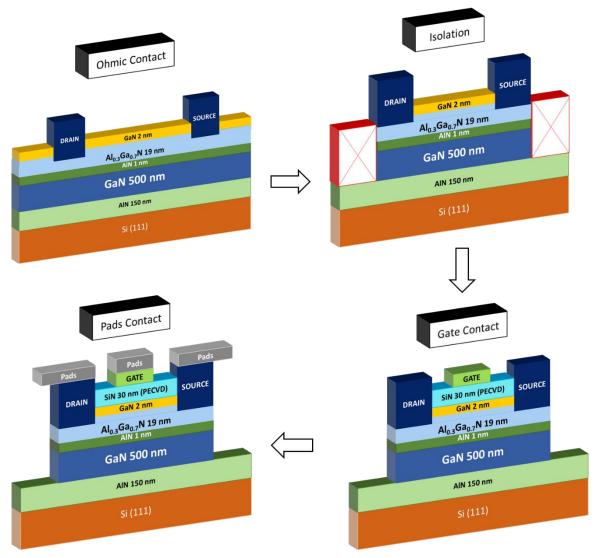

| Fig. 1. 7 Schematic fabrication flow diagram of GaN HEMTs                                        | 36   |

| Fig. 1. 8 Schematic of ohmic contact fabrication                                                 |      |

| Fig. 1. 9 SEM images of ohmic contacts after RTA                                                 | 38   |

| Fig. 1. 10 Schematic of TLM bar pattern with various contact spacing (left) and Graphica         | ıl   |

| description of TLM (right)                                                                       | 39   |

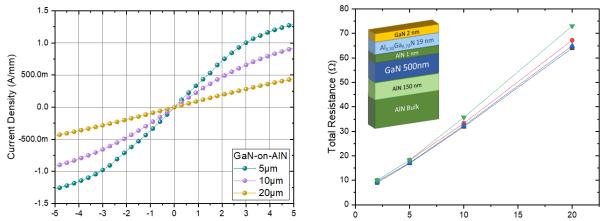

| Fig. 1. 11 I-V characteristics (left) and Total resistance vs TLM spacing (right) for GaN-or     | n-   |

| AlN with the inset showing the cross-sectional schematic of structure                            | 40   |

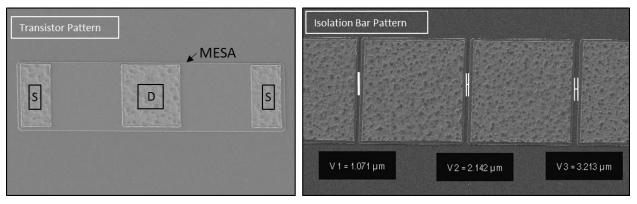

| Fig. 1. 12 images of MESA isolated transistor pattern (Left) and Isolation bar pattern           |      |

| (Right)                                                                                          | 41   |

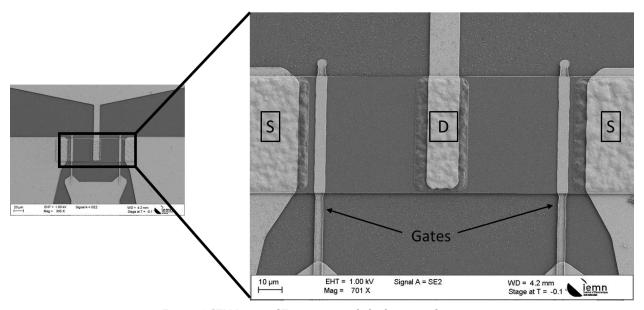

| Fig. 1. 13 SEM Image of Transistors with dual gate configuration                                 | 42   |

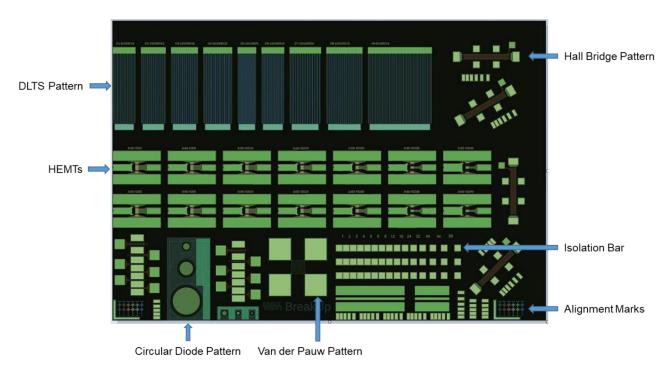

| Fig. 1. 14 Schematic of device Fabrication mask                                                  | 43   |

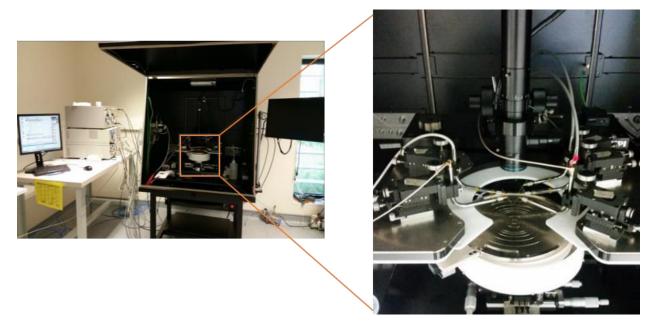

| Fig. 1. 15 High voltage characterization bench setup                                             | 44   |

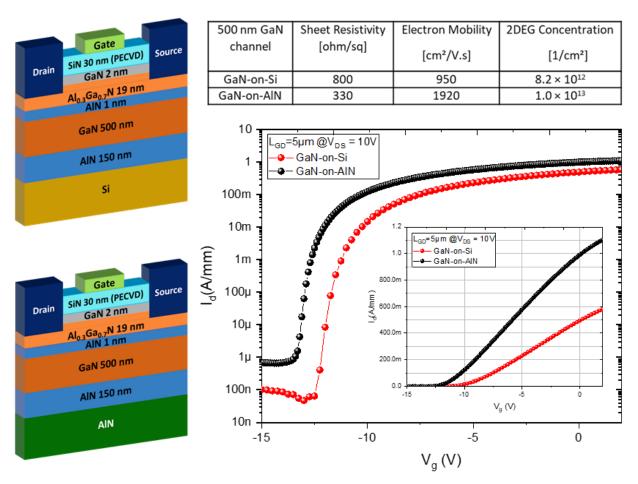

| Fig. 1. 16 Schematic of GaN-on-Si and GaN-on-AlN MISHEMTs (left) with their transfer             |      |

| characteristics and 2DEG properties                                                              | 45   |

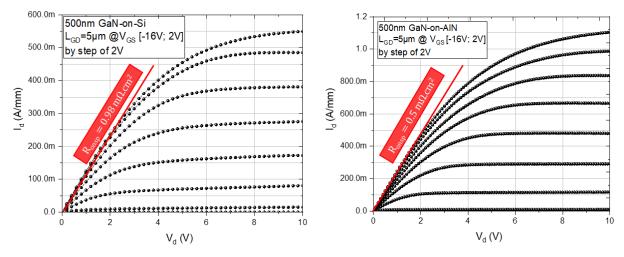

| Fig. 1. 17 Output characteristics of GaN-on-Si (left) and GaN-on-AlN (Right) MISHEMTS.           | 46   |

| Fig. 1. 18 Lateral breakdown characteristics for GaN-on-Si and GAN-on-ALN for 96μm               |      |

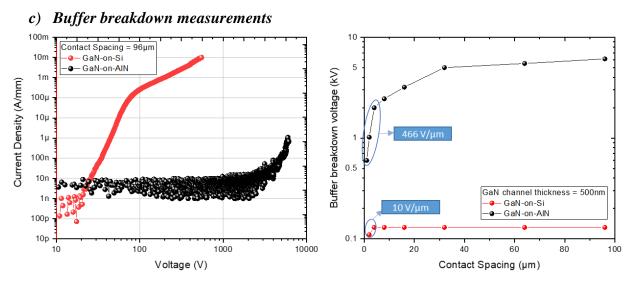

| contact spacing (left) and evolution of buffer breakdown voltage with increasing contact         | t    |

| spacing                                                                                          | 47   |

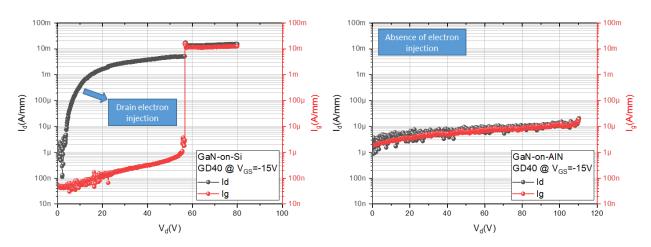

| Fig. 1. 19 Transistor breakdown characteristics for GaN-on-Si (left) and GaN-on-AlN (rig         | ght) |

| for devices with $L_{\text{GD}}$ = 40 $\mu m$                                                    |      |

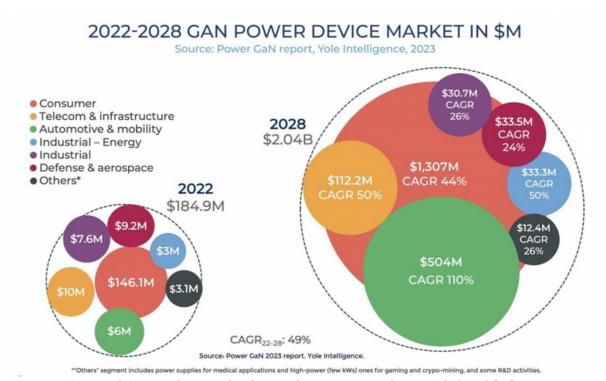

| Fig. 1. 20 GaN power device market share prediction 2022-2028 (source: Yole Group) [6            | 53]  |

|                                                                                                  |      |

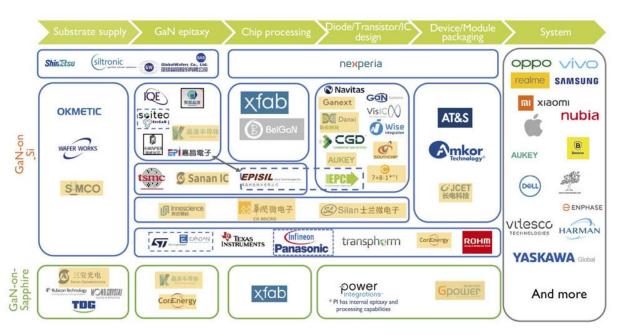

| Fig. 1. 21 Global power GaN supply chain (source: Yole Group)                                    |      |

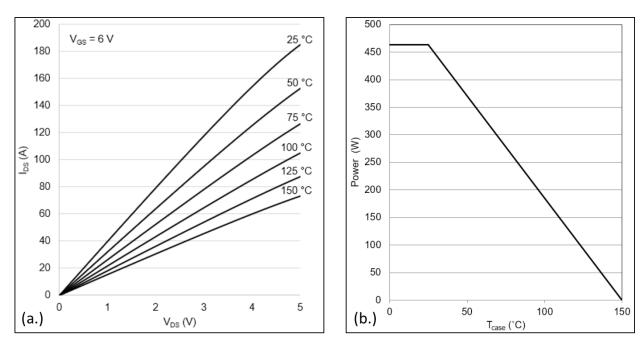

| Fig. 1. 22 GaN systems top-side cooled 650V E-mode GaN transistor (a.) $T_{\rm j}$ dependence of | )f   |

| $I_{DS}$ - $V_{DS}$ at $V_{GS}$ =6V and (b.) power dissipation temperature derating [67]         | 54   |

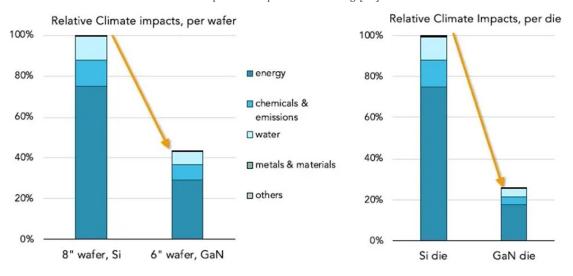

| Fig. 1. 23 Comparison of Fab energy/material usage for GaN and Si (source:                       |      |

| www.powerelectronicsnews.com)                                                                    | 54   |

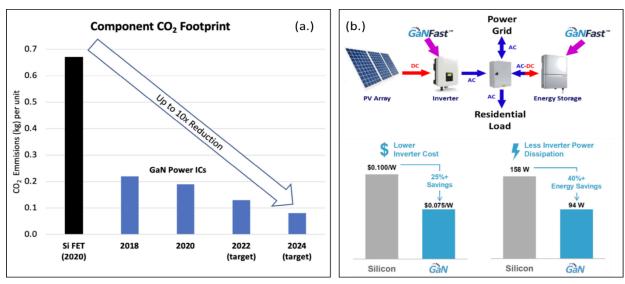

| Fig. 1. 24 (a.) CO <sub>2</sub> footprint comparison between GaN and Si device production (b.) Cost estimation of GaN replacing Si based power electronics in a solar PV system (source: |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Navitas Semiconductors)                                                                                                                                                                  |

| Fig. 1. 25 (a.) Conventional isolated charger circuit diagram (b.) Experimental efficiency of                                                                                            |

| GaN and SiC based charger at V <sub>out</sub> =400V, Power=0.5~7.2kW [71]                                                                                                                |

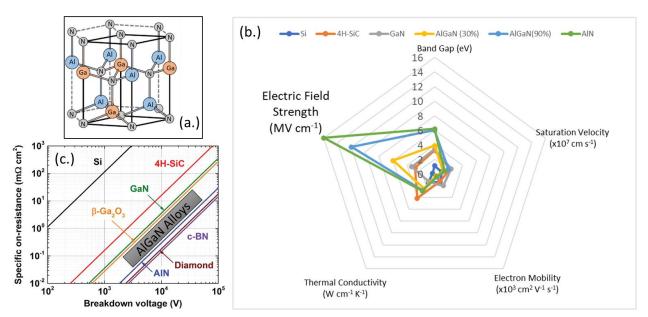

| Fig. 1. 26 (a.) Schematic of crystal structure for AlGaN with 60% Al content, (b.) Radar chars showing material properties of WBG semiconductors and AlGaN alloys and (c.) BFOM          |

| evolution for various WBG and UWBG semiconductors                                                                                                                                        |

| Fig. 1. 27 Simulated AlGaN/AlGaN Matrix showing the 2-DEG concentration per cm <sup>2</sup> for                                                                                          |

| various Al content in the barrier and channel                                                                                                                                            |

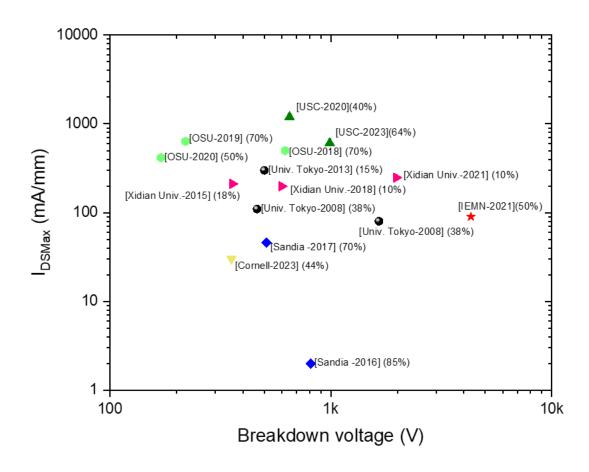

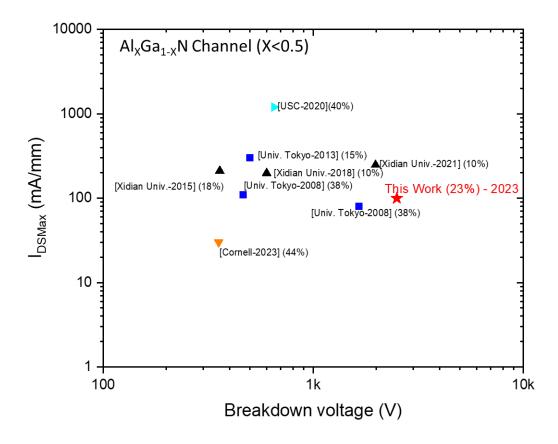

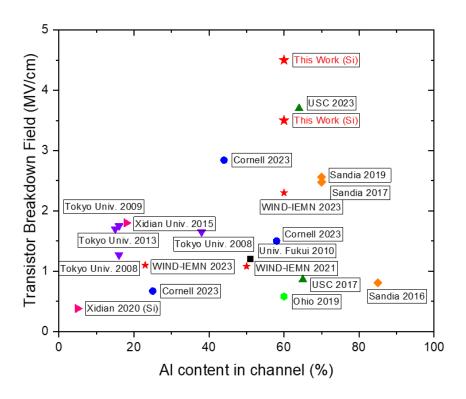

| Fig. 1. 28 State-of-the-art AlGaN channel devices                                                                                                                                        |

| rig. 1. 20 State-of-the-art Ardaiv channel devices                                                                                                                                       |

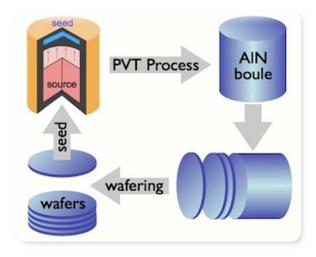

| Fig. 2. 1 Bulk AlN wafer processing flow diagram                                                                                                                                         |

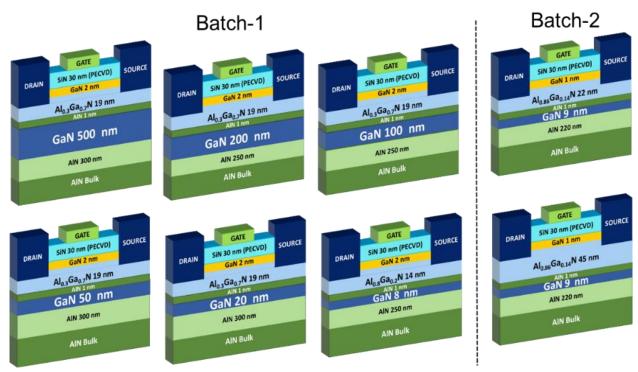

| Fig. 2. 2 Cross-sectional schematic structures of fabricated GaN channel MISHEMTs on AlN                                                                                                 |

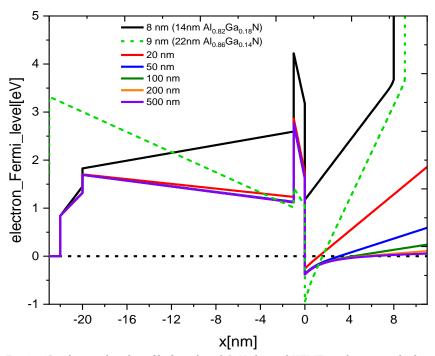

| Fig. 2. 3 Conduction band profile for relaxed GaN channel HEMTs with various thickness. 68                                                                                               |

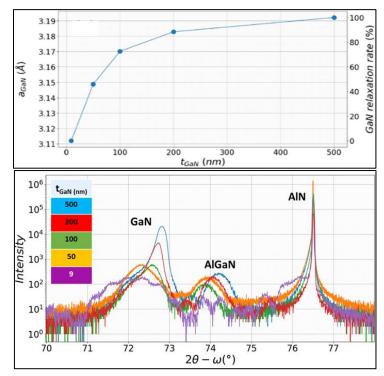

| Fig. 2. 4 Evolution of strain relaxation rate with GaN channel thickness [Top], XRD 2theta-                                                                                              |

| omega scans performed around (004) reflections for various GaN channel HEMTs [Bottom]                                                                                                    |

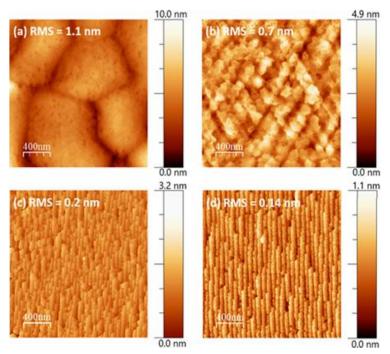

| Fig. 2. 5 AFM images of the surface of HEMTs with (a) 500nm, (b) 50nm, (c) 20nm and (d) 8nm GaN channel thickness                                                                        |

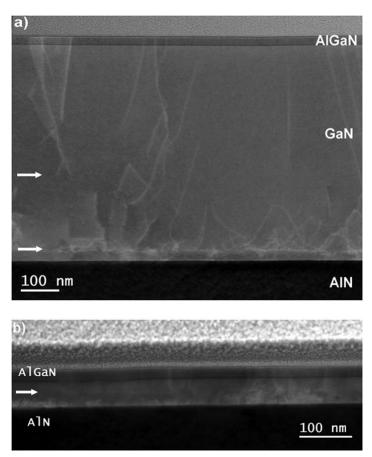

| Fig. 2. 6 Cross-sectional high angle annular dark field (HAADF)-STEM images of HEMT                                                                                                      |

| structures grown on the AlN substrate with GaN channel thicknesses of 500 (a) and 50 $\mbox{nm}$                                                                                         |

| (b). The white arrow close to the GaN/AlN interface shows the upper limit of the first                                                                                                   |

| transition region in (a) and (b). The second arrow in (a) is located at about 200 nm above the first transition region and corresponds to an additional decrease in the defect density.  |

|                                                                                                                                                                                          |

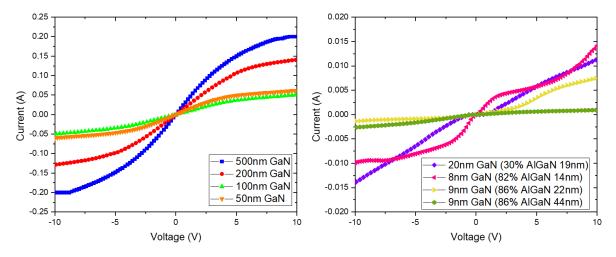

| Fig. 2. 7 Current-Voltage characteristics of various GaN channel HEMTs for 5μm TLM                                                                                                       |

| contact spacing                                                                                                                                                                          |

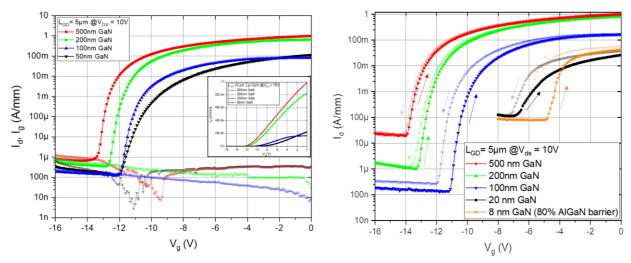

| Fig. 2. 8 [Left] Transfer characteristics of GaN HEMTs with 500nm, 200nm, 100nm and                                                                                                      |

| 50nm channel thickness in semi-log and linear scale and [Right] Forward-Reverse Id-Vg                                                                                                    |

| sweeps for various GaN channel HEMTs                                                                                                                                                     |

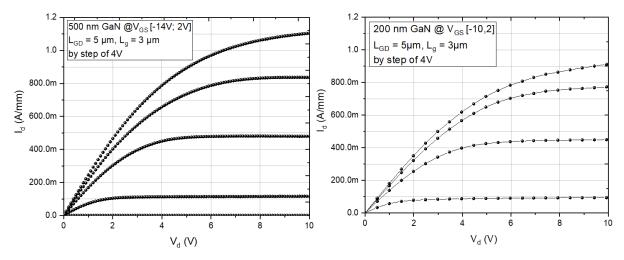

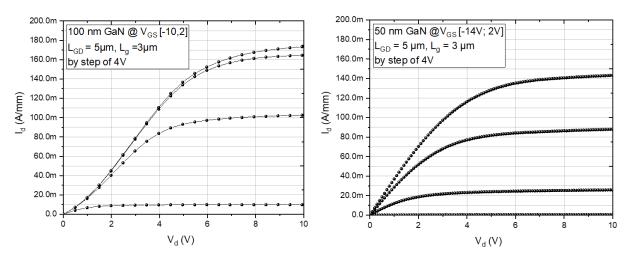

| Fig. 2. 9 Output characteristics for 500nm and 200nm thick GaN channel MISHEMTs 74                                                                                                       |

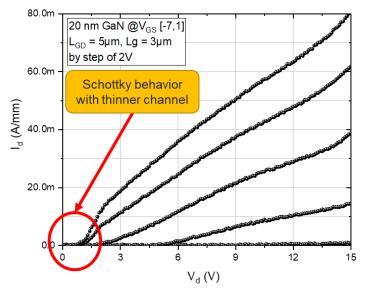

| Fig. 2. 10 Output characteristics 20nm thin GaN channel HEMTs                                                                                                                            |

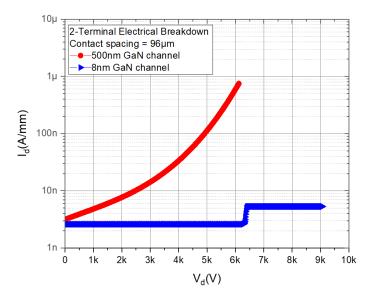

| Fig. 2. 12 Buffer leakage current characteristics for 500nm and 8nm GaN channel devices                                                                                                  |

| with 96µm contact spacing                                                                                                                                                                |

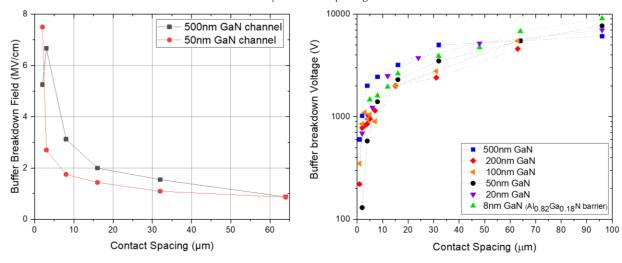

| Fig. 2. 13 [Left] Evolution of buffer breakdown electric field with two terminal contact                                                                                                 |

| spacing and [Right] Summary of AlN breakdown voltage with various contact spacing 76                                                                                                     |

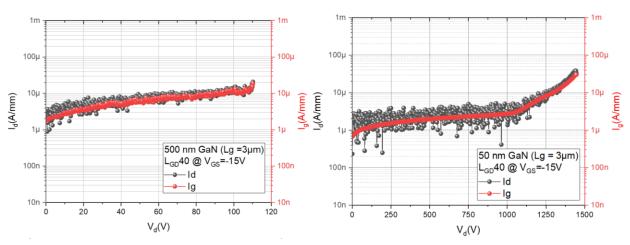

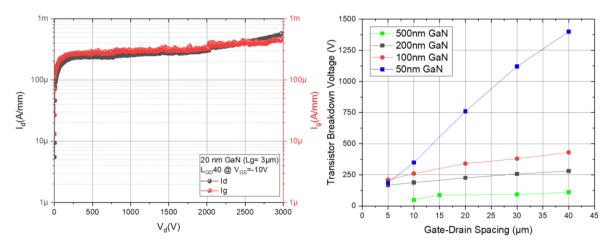

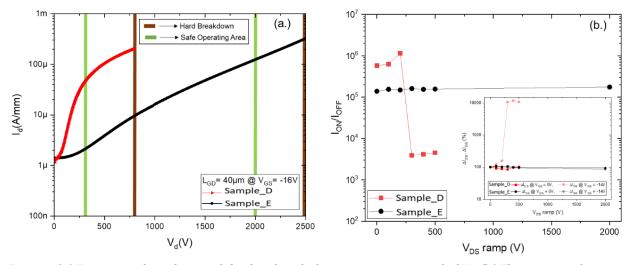

| Fig. 2. 14 [Left] Transistor breakdown characteristics for MISHEMTs with L <sub>GD</sub> =40μm and                                                                                       |

| L <sub>G</sub> =3µm for 200nm thick GaN channel and [Right] Summary of transistor breakdown                                                                                              |

|                                                                                                                                                                                          |

| voltage with various gate-drain spacing for different GaN channel MISHEMTs with gate                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| leakage below $100\mu A/mm$                                                                                                                                                                                 |

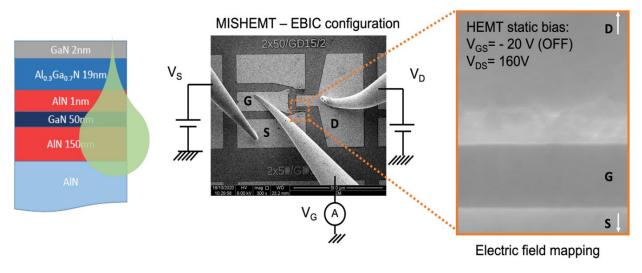

| peer of electron beam irradiation (green), [Middle] configuration of the electron beam induced current measurement used on the MISHEMT and [Right] Mapping of the space charge region nearby gate electrode |

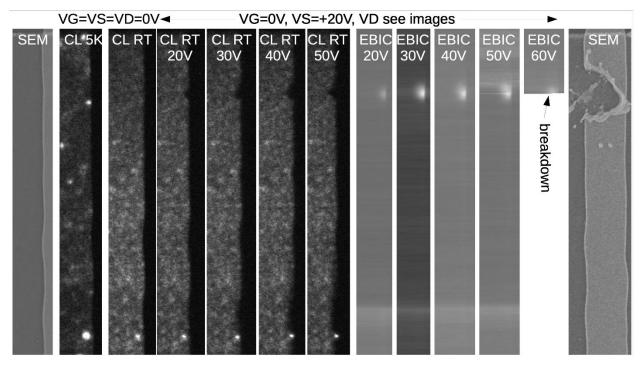

| Fig. 2. 17 Cathodoluminescence mapping at 360 nm at 5 K and RT under different bias.  EBIC measurements using the same bias polarization and SEM images before [Left] and after breakdown [Right]           |

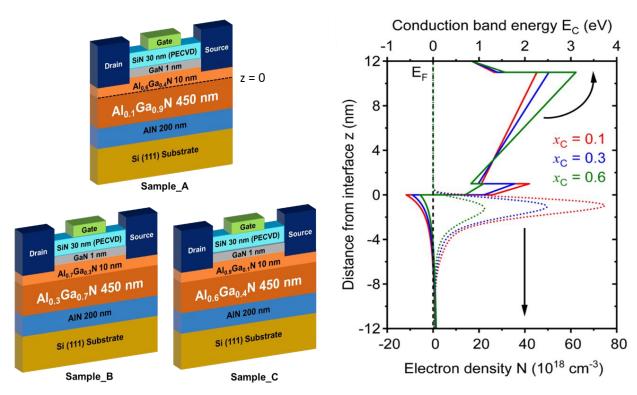

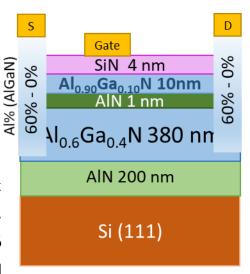

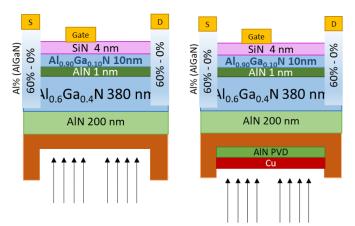

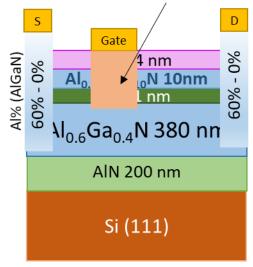

| Fig. 3. 1 Cross-sectional schematic structure (Left) and conduction band profile with                                                                                                                       |

| simulated channel electron density (Right) for the AlGaN channel HEMTs with various Al compositions                                                                                                         |

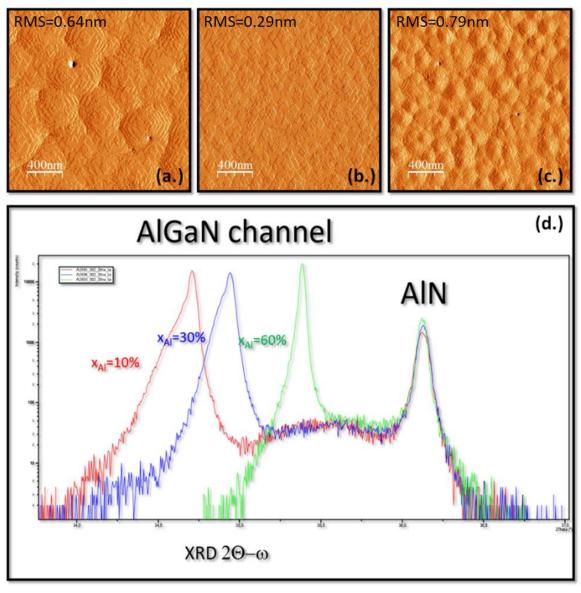

| Fig. 3. 2 AFM scans for heterostructures with (a.) 10%, (b.) 30% and (c.) 60% AlGaN channel. (d.) XRD $2\theta$ - $\omega$ scans for AlGaN channel HFETs                                                    |

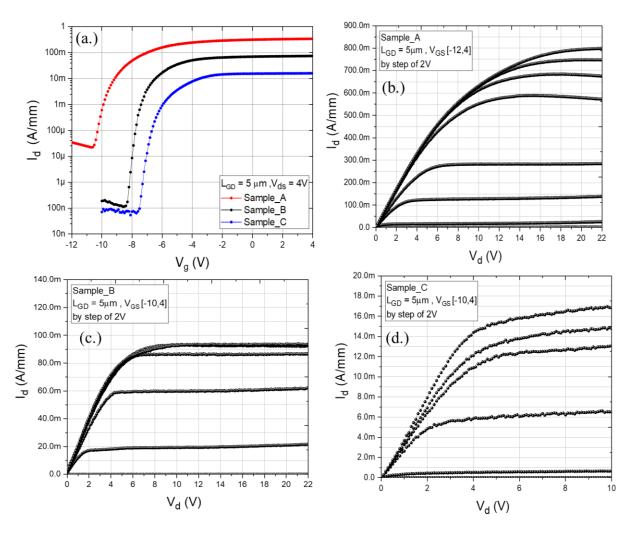

| Fig. 3. 3 (a.) Transfer characteristics and Output characteristics of (b.)10%, (c.)30%, and (d.)60% AlGaN channel HFETs                                                                                     |

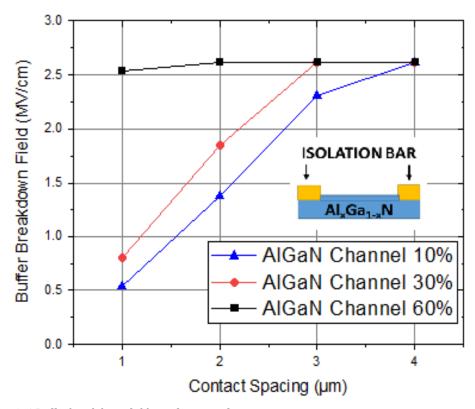

| Fig. 3. 4 Buffer breakdown field as a function of contact spacing                                                                                                                                           |

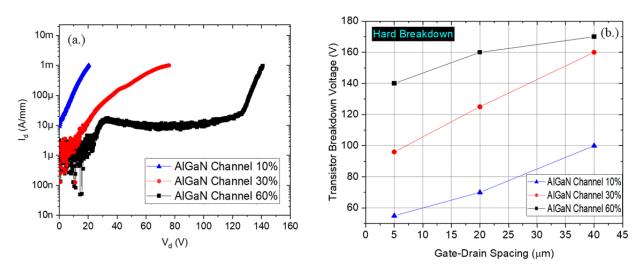

| Fig. 3. 5 (a.) Off-state 3-terminal breakdown voltage for transistors at VGS = $-$ 12 V for 10% AlGaN channel HFETs and VGS = $-$ 10 V for 30% and 60% AlGaN channel HFETs with a                           |

| gate-drain spacing of 5 $\mu$ m, (b.) for various gate-drain spacing                                                                                                                                        |

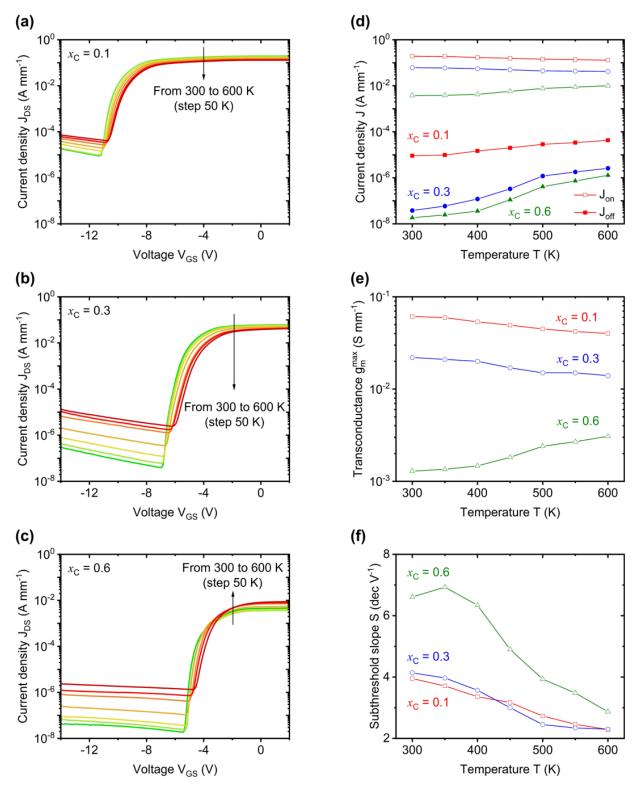

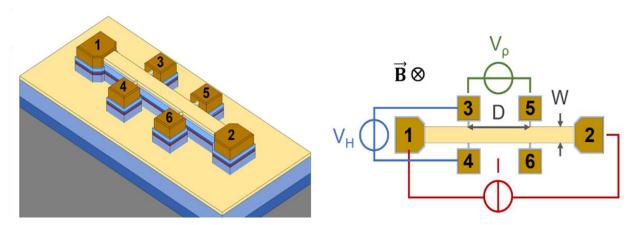

| current densities, (e) the maximum transconductance and (f) the subthreshold slope 90 Fig. 3. 7 3D schematic view of the Hall bridge (Left) and Electrical characterization setup of                        |

| Hall measurements in Hall bridge configuration (Right)91                                                                                                                                                    |

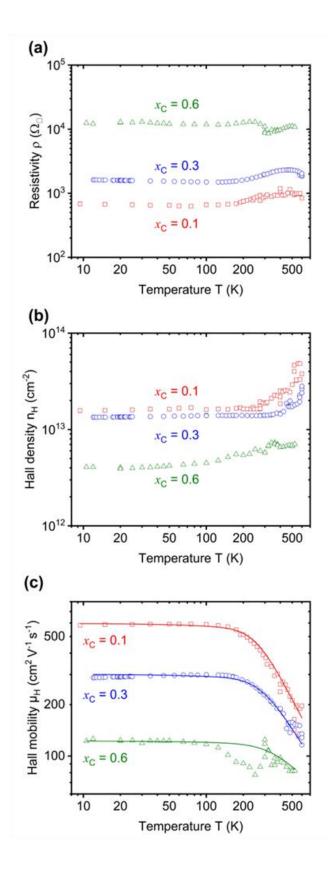

| Fig. 3. 8 Temperature Hall Effect results for various AlGaN channel HFETs. Evolution of (a.) Sheet Resistance (b.) 2DEG concentration and (c.) Electron mobility (symbol) with                              |

| calculated low field mobility (line)                                                                                                                                                                        |

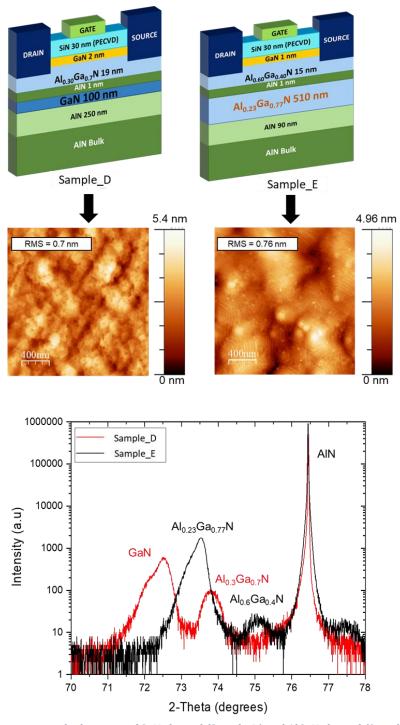

| (Sample_E) heterostructures on bulk AlN along with their AFM scans and XRD scans 96                                                                                                                         |

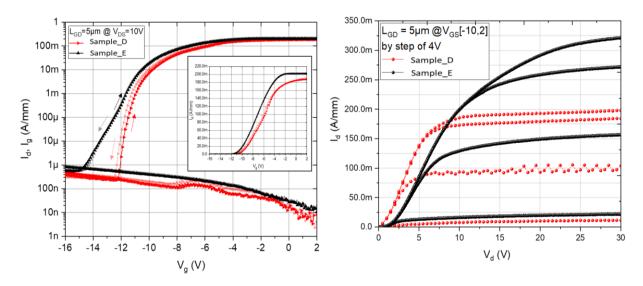

| Fig. 3. 10 Transfer characteristics (left) and Output characteristics (right) of fabricated GaN and AlGaN channel MISHFETs on AlN                                                                           |

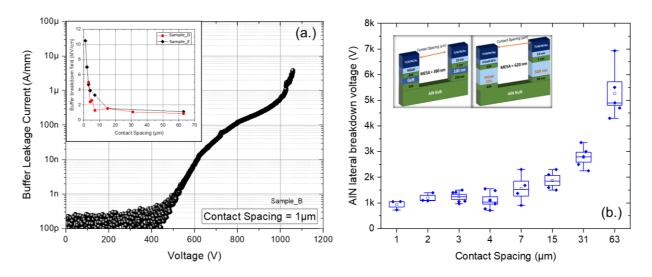

| Fig. 3. 11 Buffer leakage current characteristics for 1µm contact spacing (Left) and Mean                                                                                                                   |

| values of AlN lateral breakdown voltage for various contact spacing of GaN and AlGaN channel MISHFETs99                                                                                                     |

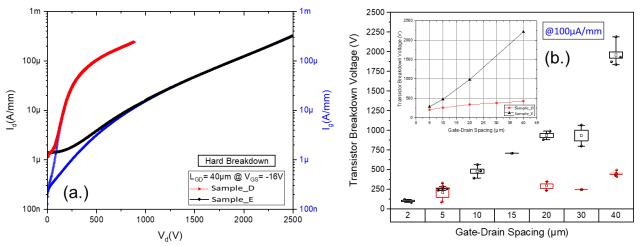

| Fig. 3. 12 (a.) Hard electrical breakdown characteristics for transistors with a gate-drain                                                                                                                 |

| spacing of 40 μm at VGS = -16V and (b.) Mean value of transistor blocking voltage for various LGD of GaN and AlGaN channel MISHFETs99                                                                       |

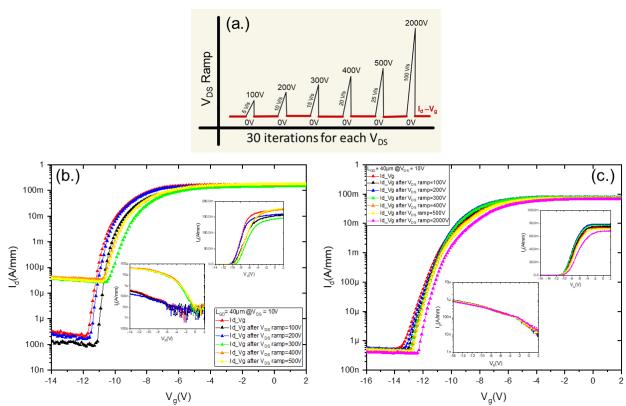

| Fig. 3. 13 (a.) Robustness test schematic for various VDS stress voltages, Transfer                                   |

|-----------------------------------------------------------------------------------------------------------------------|

| characteristics measured after each V <sub>DS</sub> ramp for (b.) GaN channel MISHFETs and (c.)                       |

| AlGaN channel MISHFETs with their insets showing gate leakage current density and linear                              |

| transfer characteristics100                                                                                           |

| Fig. 3. 14 (a.) (a.) Transistor voltage derating defined on drain leakage current against                             |

| applied $V_{DS}$ (b.) The maximum change in gate leakage current density (inset - $I_{ON}/I_{OFF}$ ratio)             |

| for GaN and Al <sub>0.23</sub> Ga <sub>0.77</sub> N channel HFETs for various V <sub>DS</sub> ramp iterations101      |

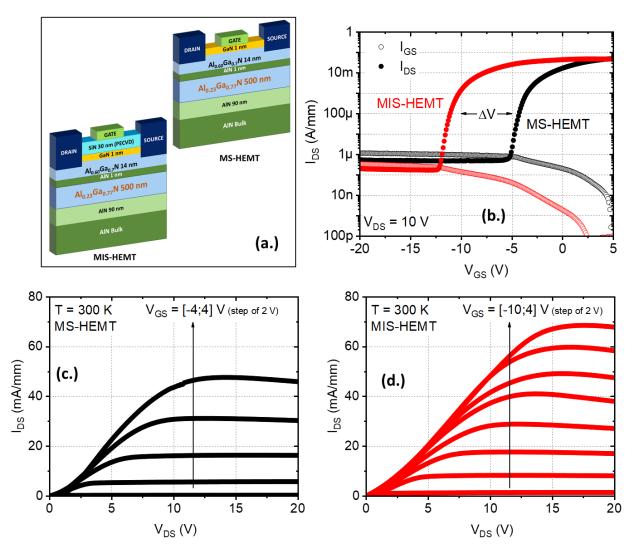

| Fig. 3. 15 (a.) Schematic of structures with and without SiN passivation, (b.) transfer                               |

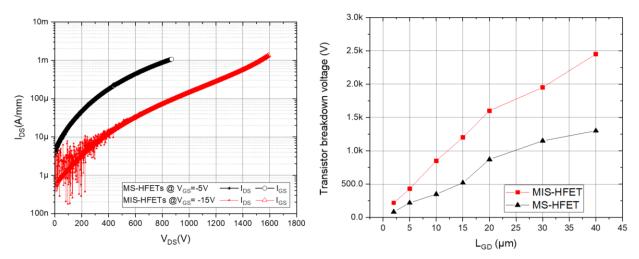

| characteristics measured at V <sub>DS</sub> =10V, output characteristics of (c.) MS-HEMT (without SiN)                |

| and (d.) MI SHEMT (with SiN)103                                                                                       |

| Fig. 3. 16 Transistor breakdown voltage for devices with L <sub>GD</sub> =20 μm (left) and Evolution of               |

| transistor breakdown voltage with various LGD (right) for MIS-HFETs and MS-HFETs104                                   |

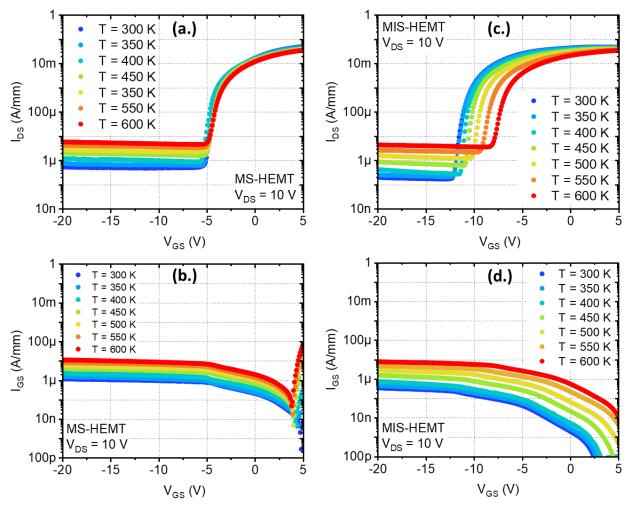

| Fig. 3. 17 Transfer characteristics along with gate current leakage evolution with applied                            |

| $V_{DS}$ = 10V for AlGaN channel (a.), (b.) MS-HEMT and (c.), (d.) MIS-HEMT measured over 300                         |

| K – 600 K temperature range105                                                                                        |

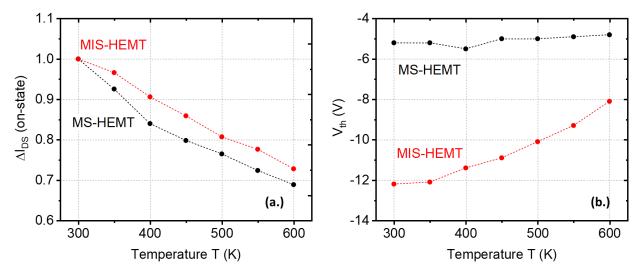

| Fig. 3. 18 (a.) Change in on-state drain current density normalized at 300 K and (b.)                                 |

| threshold voltage evolution measured over 300 K - 600 K temperature range                                             |

| Fig. 3. 19 Schematic of GaN and AlGaN channel MIS-HFETs with surface deposited CeO <sub>2</sub>                       |

| microparticles107                                                                                                     |

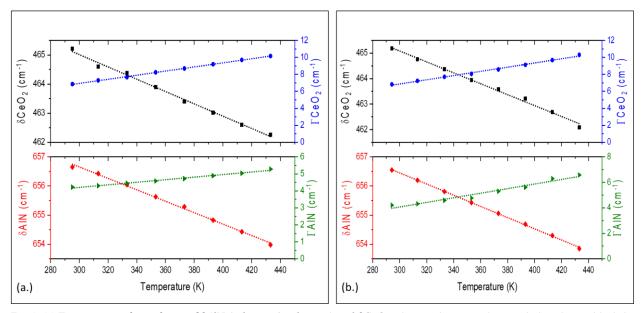

| Fig. 3. 20 Temperature dependence of $\delta$ AlN (substrate/nucleation) and $\delta$ CeO <sub>2</sub> (close to the  |

| gate) along with their linewidth shift for (a.) 500nm GaN channel HEMT and (b.) 500nm                                 |

| AlGaN channel HFET108                                                                                                 |

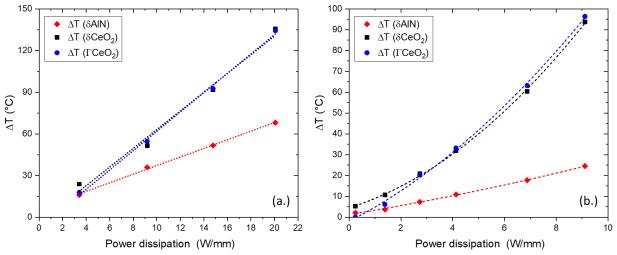

| Fig. 3. 21 Impact of power dissipation on the self-heating temperatures ( $\Delta T$ ) measured                       |

| from $\delta CeO_2$ , $\Gamma$ $CeO_2$ , and $\delta$ AlN components for (a.) GaN channel HEMTs (linear fit) and (b.) |

| AlGaN channel HFETs (quadratic fit)109                                                                                |

| Fig. 3. 22 State-of-the art AlGaN channel HFETs with <50% Al content in the channel110                                |

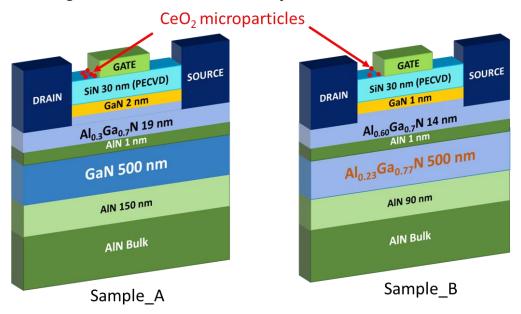

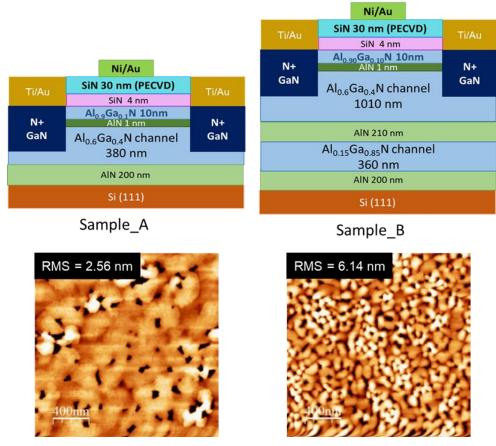

| Fig. 3. 23 Schematic diagram of sample_A (thin AlGaN channel) and sample_B(thick AlGaN                                |

| channel) HFETs along with the AFM scans of GaN n+ contacts after regrowth111                                          |

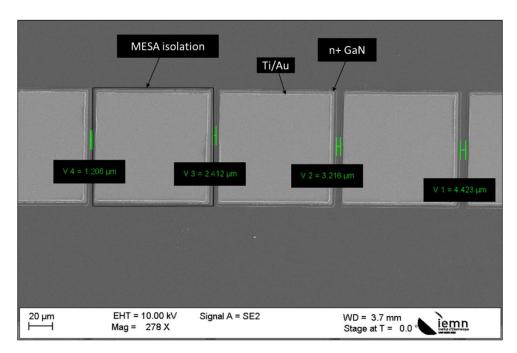

| Fig. 3. 24 SEM image of isolated bar pattern showing various regions of contacts along with                           |

| their spacing112                                                                                                      |

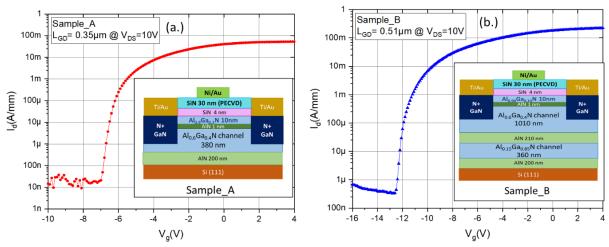

| Fig. 3. 25 Transfer characteristics of Al-rich AlGaN channel HFETs with (a.) thin AlGaN                               |

| channel and (b.) thick AlGaN channel measured at $V_{DS} = 10V$ 113                                                   |

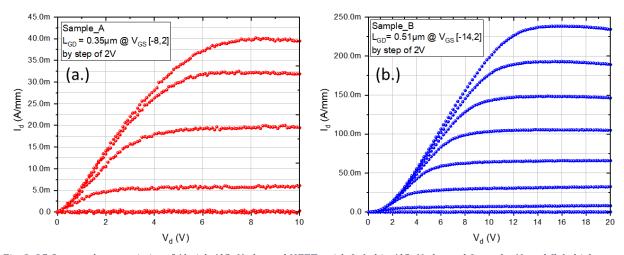

| Fig. 3. 26 Output characteristics of Al-rich AlGaN channel HFETs with (a.) thin AlGaN                                 |

| channel (sample_A) and (b.) thick AlGaN channel (sample_B) measured at $V_{DS} = 10V113$                              |

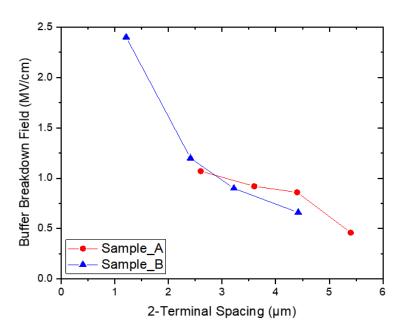

| Fig. 3. 27 Buffer breakdown electric field evolution with contact spacing114                                          |

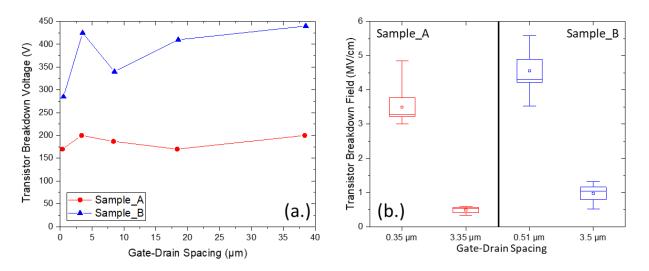

| Fig. 3. 28 Summary of (a.) transistor breakdown voltage with gate-drain spacing and (b.)                              |

| evolution of transistor breakdown field with gate-drain spacing115                                                    |

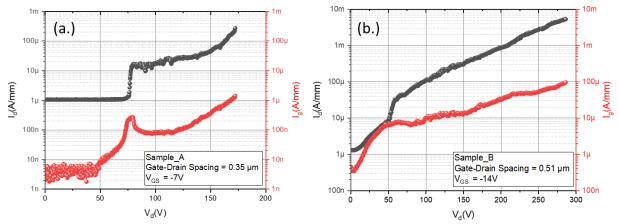

| Fig. 3. 29 Transistor breakdown characteristics of (a.) thin AlGaN channel and (b.) thick                             |

| AlGaN channel MISHFETs115                                                                                             |

| Fig. 3. 30 State-of-the-art AlGaN devices with the transistor breakdown field evolution with                          |

| Al content in the AlGaN channel116                                                                                    |

# List of Tables

| Table 1. 1 Comparison of material properties, cost and availability for various substrates                                                                                              | 21       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 1. 2 Commercial WBG power devices along with their technical specifications and switching FOM                                                                                     |          |

| Table 1. 3 Comparison of WBG and UWBG material properties along with their FOM 6                                                                                                        |          |

| Table 2. 1 Hall Effect Measurements, Contact Resist,ance and channel relaxation rate for various GaN channel HEMTs7                                                                     | '2       |

| Table 3. 1 Hall Effect measurements of AlGaN channel HEMTs                                                                                                                              | (        |

| Table 3. 3 Hall Effect measurements extracted 2DEG properties for GaN and AlGaN channe MISHFETs9 Table 3. 4 Hall Effect measurements extracted 2DEG properties for thin and thick AlGaN | el<br>97 |

| channel MISHFETs11                                                                                                                                                                      | .2       |

### General Introduction

Worldwide electricity consumption is predicted to surpass 50 petawatt hours by 2050. The gradual decline in fossil fuel reserves and increase in CO emissions will eventually lead to the development of renewable and sustainable power generation. In this frame, the need for power conversion, transmission, and distribution will be essential, which can be achieved by developing efficient power electronics. Si-based MOSFETs and IGBTs were major electronic devices that initiated the development of power conversion systems. However, these devices' electrical losses and material-specific limitations will not meet future conversion efficiency demands.

Wide band gap (WBG) semiconductors with their superior material properties over conventional silicon devices offer even faster, powerful, and compact devices. In the last decade, GaN and SiC gained significant attention in the semiconductor industry for the development of commercial devices capable of withstanding high voltage (up to 1200 V), high current (up to 150 A), and high temperature with up to 99% efficiency. Despite the given advantages, these WBG semiconductors are limited by their critical breakdown field, which is less than 3 MV/cm. Moreover, SiC MOSFETs and IGBTs are almost 3 times more costly than their counterpart Si-IGBTs. As the WBG technology evolves, the scope for dramatic improvements lessens, leading to a plateau in high-voltage performance enhancements. This scenario has led to the exploration of ultra-wide-bandgap (UWBG) materials defined by a bandgap larger than 3.4 eV. The UWBG semiconductors AlGaN alloys can push the critical electric field up to 10-12 MV/cm by varying Al content and the polarization fields enable the development of heterostructures consisting of a two-dimensional electron gas (2DEG) at the AlGaN/AlGaN interface. Thus, AlGaN alloys might offer higher breakdown voltages surpassing the WBG semiconductor limitations enabling multiple kilo-volt device operation. This thesis aims to demonstrate the fabrication and characterization of novel AlGaN-channel based transistors for high-voltage applications.

This work has been carried out within several French National projects listed below:

- BREAkuP (n°ANR-17-CE05-00131) ultra-wide Bandgaps for futuRE high-power electronic ApPlications. Within this project, we demonstrated the first series of GaN HEMTs fabricated on bulk AlN. This project was completed in collaboration with CNRS laboratories IEMN, CRHEA, and Institut Néel.

- HBV (n°IA-11-LABX-0014) High Breakdown Voltage This project aimed for the development of transistors delivering superior breakdown voltage by using UWBG semiconductors. A part of this project was performed in collaboration with IEMN, CRHEA, L2C, GREYC, and Néel.

- ACTION (n°ANR-22-CE05-0028) novel AlGaN Channel Transistors for hIgh vOltage applicatioNs - targets the development of AlGaN channel transistors on large diameter Si substrates. This project is ongoing with collaborative partners IEMN, Néel, CRHEA, and industrial partner EasyGaN.

The organization of the thesis is divided into 3 chapters:

Chapter 1: This chapter starts with an introduction to power electronics and wide band gap semiconductors along with a brief history of power devices. Then, the material properties of GaN along with a detailed device fabrication process are explained including their associated challenges. A study based on GaN HEMTs is shown covered by an experiment based on silicon and AlN substrate to understand their impact on device electrical characteristics. Furthermore, we delve into the challenges, industrial prospects, and environmental impacts of GaN-based devices. Finally, with the introduction of AlGaN material properties, the state-of-the-art AlGaN channel devices are presented.

Chapter 2: We will demonstrate the benefits of bulk AlN for high-voltage power electronics with the introduction of a series of GaN HEMTs fabricated on bulk AlN substrates. This chapter will detail a study showing the impact of GaN channel thickness downscaling on the device performance and 2-DEG properties. Moreover, electric field imaging of GaN channel MISHEMTs is discussed to evaluate the electrical breakdown phenomena.

Chapter 3: This chapter focuses on the novel AlGaN channel HFETs and has been divided into several studies. Firstly, AlGaN-on-Si transistors with various Al compositions in the channel are explored along with their high-temperature operation to understand the

impact of Al in the channel. Then, extreme AlGaN-on-AlN power transistors have been fabricated resulting in high-voltage and high-temperature performance. Moreover, self-heating temperature measurements were also carried out by Raman spectroscopy to understand the evolution of channel temperatures. Finally, a study based on the development of ohmic contacts to the AlGaN channel has been demonstrated yielding in state-of-the-art device performance.

### Chapter-01 Introduction

With the advancements in the technological era and the rising energy consumption, the use of power semiconductors leads towards efficient power generation, conversion, transmission, and distribution. The power semiconductor industry has been dominated by silicon for decades but recent advancements in compound semiconductors are clearly changing the scenario. The discovery of III-Nitride compound semiconductors such as GaN and SiC due to their unique and superior material properties has revolutionized the recent power electronics industry. These WBG semiconductors offer the advantage of high-power efficiency along with reduced size and weight while delivering high power density.

This chapter will begin with an introduction to power electronics and their applications followed by an introduction to WBG semiconductor materials. Next, the aspects of energy consumption and the need for efficient power electronics will be presented followed by a glimpse of current semiconductor market trends. Furthermore, the III-Nitride materials will be discussed briefly along with their use in developing heterostructures field effect transistor (HFET) technology along with their merits and demerits. Finally, current state-of-the-art technology based on UWBG AlGaN will be shown concluding the aim of this thesis work.

### 1.1 Introduction to Power Electronics

Power electronics play a vital role in the efficient control, conversion, and conditioning of electricity in modern society influencing a wide range of applications. It all began with the idea of a simple switch to control the flow of current that aspired to become modern-day FETs. Power electronics involves semiconductor devices such as diodes, transistors (such as MOSFETs and IGBTs), and thyristors that can handle high voltages, and high currents along with faster switching. The development of any electronic system starts with the design and conception of a circuit followed by material growth and device nanomicro fabrication. The micro/nano devices are then assembled into application-specific integrated circuits to realize efficient transfer and control of power in various systems.

Until the early 20th century, bulky vacuum tubes controlled electrical signals with high power consumption. In 1925, physicist Julius E. Lilienfeld introduced the concept of field effect in semiconductors patented with a fascinating experiment to control the electric current based on a three-electrode structure. However, his attempts to develop a functional semiconductor device were not fruitful because of the limited resources. The foremost devices for solid-state power semiconductors were rectifiers made of copper oxide, which found use in the early versions of battery chargers and radio equipment power supplies. L.O. Grundahl and P. H. Geiger introduced these devices in 1927. In 1945, German physicist Heinrich Welker patented the junction field effect transistors (JFET) working on the principle of charge flow control in the depletion region. On December 27, 1947, John Bardeen and Walter Brattain successfully demonstrated the first bipolar point-contact transistor at Bell Laboratories in New Jersey. However, the first transistor was not ready for commercial applications. During this period, germanium was the desirable choice of material for semiconductor applications due to its low bandgap and high carrier mobility [1]. After several attempts to develop a functional FET, a bipolar junction transistor (BJT) was invented by Shockley in 1948. Simultaneously, in August 1948, German physicists Herbert Mataré and Heinrich Welker applied for a patent on an amplifier based on the minority carrier injection, which they called "Transistron" in Aulnay-sous-Bois, France [2]. The Transistron was developed independently of Bell laboratories in France and was later commercially developed for French telecommunication and military applications.

In 1948, based on his research on surface physics Bardeen secured a patent for an insulate-gate field effect transistor (IGFET) featuring an inversion layer crucial in confining the minority carriers, thus enhancing modulation and conductivity. Bardeen's patent and concept of the inversion layer are fundamental to the current complementary metal-oxidesemiconductor (CMOS) technology. In 1950, W. Shockley proposed a three terminal solidstate semiconductor device with alternating P-N-P-N layers called silicon-controlled rectifier (SCR) or thyristor. The three terminals are namely anode, cathode and gate. In 1952, R.N. Hall demonstrated first germanium power diode with impressive reverse blocking voltage of 200V and current rating of 35 A. The transistor applications began in many electronic devices replacing vacuum tubes by the early 1950s [3]. Later in 1956, the trio Bardeen, Brattain, and Shockley were honored with the Nobel Prize in Physics for their work on semiconductors and the discovery of the transistor effect. In the same year, General Electric commercially released the first thyristor devices. Silicon rectifiers, with their larger band gap, provided greater reverse voltage capacity and could operate at higher temperatures. By the late 1950s, alloy junctions had been developed that could handle up to 500 volts. The late 1950s also saw the combination of diffused junctions and mesa technology, a crucial step that later enabled reverse blocking capabilities of several kilovolts. By 1958, Jack Kilby at Texas Instruments showed the working example of an integrated circuit (IC) for which, he was awarded jointly the Nobel Prize in Physics in 2000.

In 1959, Mohamed Atalla and Dawon Kahng invented the highly scalable metal-oxide-semiconductor field effect transistor (MOSFET) which superseded the principle of both the BJT and JFET fabricated by growing an insulating silicon-oxide layer on semiconducting silicon. The first MOSFET was almost 100 times slower than contemporary BJTs but it was worthy for the ease of fabrication and its applications in IC. In 1961, the Gate Turn-Off Thyristor (GTO) marked a significant advancement in power electronics by combination of the fast-switching capabilities of a transistor with the low conduction losses characteristic of a SCR. In 1963, Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor Inc., California, developed CMOS Technology. Combining the logic of NMOS and PMOS processes and demonstrating its application as an inverter and ring oscillator, they demonstrated low standby power density and high switching power density that can be

realized in a circuit with a very high packing density enabling the integration of over 10,000 transistors into a single IC [3].

Following the introduction of the GTO, another major development occurred in 1964 with the creation of the TRIAC, or bidirectional AC switch, by General Electric. The TRIAC was primarily designed for 60 Hz applications, particularly in consumer lighting and motor speed control. Its bidirectional current flow capability made it an ideal component for controlling AC power where both positive and negative current flow needed to be managed. By the mid-1960s, mesa junctions had been optimized to theoretically allow for avalanche breakdown voltages up to 9000 V [4], [5]. Additionally, improvements in device packaging minimized thermal and mechanical stress on the chip, led to increased current handling capacities. Today, thyristors with a diameter of 77 mm are available, capable of sustaining continuous currents of 5000 A and reverse voltages of 3000 V with a maximum junction temperature of 125°C weighing almost up to 2 kg. However, the SCR needs an additional circuitry to reduce the anode-cathode current below the holding current to change the SCR from the conducting state to the blocking state. By 1970, power MOSFETs emerged featuring vertical structure. When compared with the BJT, MOSFET had the advantageous features of a high-input impedance, high switching speed, ease of paralleling, and a much superior safe operating area (SOA) making it attractive for computer and automotive electronics. Power MOSFETs were limited to 200V due to the drastic increase in on-resistance with the increasing blocking voltage; this hindered the progress of developing high current devices. To overcome this limitation and target higher voltage systems, a new class of power devices based upon the combination of BJT and MOS concept were developed called insulated-gate bipolar transistor (IGBT). By 1979, Jayant Baliga successfully developed the first IGBT at General Electric.

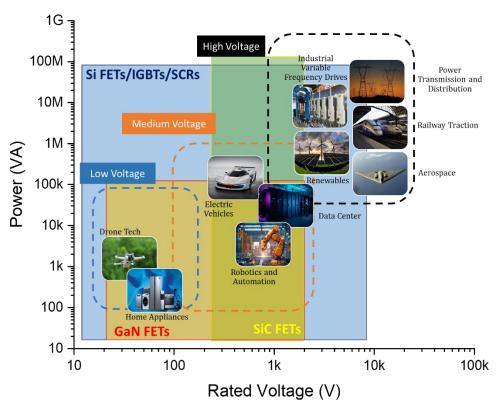

Fig. 1. 1 Power semiconductor devices applications according to the voltage range and rated power

The development of high-speed and compact computers began with the emergence of efficient microprocessors in the 1980's and the implementation of deep sub-micron CMOS technology. In 1983, Baliga et al. presented the results of insulated gate rectifier (IGR) suggesting suppression of a parasitic thyristors action and the rectifier was a clear representation of MOS gated bipolar transistor [6]. However, their switching speed was slow and the reverse biased SOA were small to replace BJT. To resolve this issue, Nakagawa et al. presented concept of non-latch-up 1200 V 75 A Bipolar MOSFET with large SOA [7]. Over the decades, MOSFETs and IGBTs emerged to be key component in power electronic systems with the development of innovative structures which evolved to produce high power density and lower die footprint sizes [8]–[10].

The applications of power electronic devices can be differentiated based on their rated voltage such as low voltage, medium voltage, and high voltage with their corresponding maximum voltage limited by 200 V, 1.2 kV, and more than 1.2 kV respectively. The various domains of applications are highlighted according to the rated voltage with their required

power rating as shown in *Fig. 1.1*. The various applications of power electronics can be described as follows:

- 1.) Renewable Energy Systems

- DC-DC boost converter

- Inverter

- 2.) Electric Vehicles (EVs)

- Motor control unit

- Inverter

- Bidirectional AC-DC converter

- LiDAR

- 3.) Consumer Electronics

- Wireless chargers

- Power adapters

- 4.) Power system

- Flexible AC Transmission System (FACTS)

- Power factor correction (PFC)

- High Voltage Direct Current (HVDC) Transmission

- Smart grid

- 5.) Aerospace and Defense

- Satellite and aircraft systems

- Radar systems

- 6.) Medical applications

- X-Ray machines

- MRI machines

- CT scan

- 7.) Industrial applications

- Variable frequency drive (VFD)

- Automation systems

- Uninterruptible power supply (UPS)

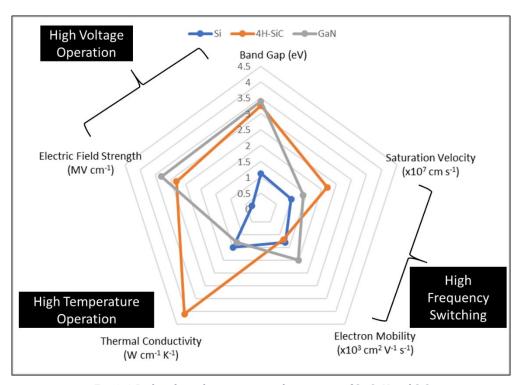

Silicon power devices cover the majority of power electronics applications from small ICs to bulky high-voltage converters. However, the evolution of modern-day power electronics has been significantly driven by advancements in material science with the introduction of WBG materials, such as GaN and SiC. Their high band gap (> 3 eV) and almost 10× higher electric field strength allows them to operate at much higher voltages with low on-resistances compared to Si devices. Moreover, the high electron mobility and saturation velocity allow the WBG FETs to operate at higher switching frequencies. Additionally, their high thermal conductivity enables high-temperature operation beyond the limits of Si. The material parameters for Si, GaN and SiC has been shown in *Fig. 1.2*

Fig. 1. 2 Radar chart showing material properties of Si, GaN and SiC

### 1.2 Gallium Nitride (GaN)

### 1.2.1 Crystal properties

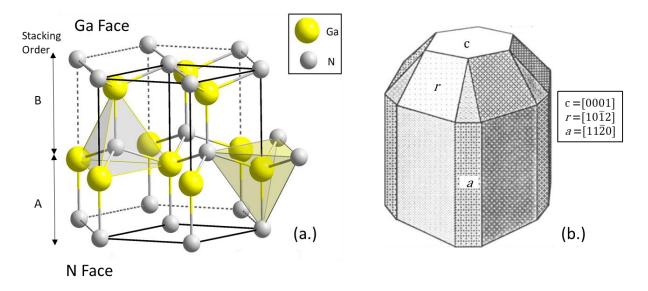

The III-Nitride group shares three crystal structures: the wurtzite, zincblende, and rocksalt structures. Under ambient conditions, GaN shows a wurtzite structure (P63mc – space group) defined by a hexagonal unit cell, resulting in two lattice constants, c and a. It consists of six atoms of each type. The structure is formed from two interlocking Hexagonal Close Packed (HCP) sublattices, with each lattice featuring a single type of atom offset along

the c-axis by 5/8 of the cell height. The wurtzite structure shows ABABAB type stacking sequence of closely packed diatomic planes in the {0001} direction. The structure consists of two interpenetrating face-centered cubic sublattices, offset by one-quarter of the distance along a body diagonal. Each atom in the structure may be viewed as positioned at the center of a tetrahedron, with its four nearest neighbors defining the four corners of the tetrahedron. Fig. 1.3 shows the crystal structure of GaN along with the crystal planes and their directions. The rocksalt (NaCl) structure can be induced in GaN under very high-pressure conditions around 50 GPa. The zinc blend structure has a cubic unit cell (F43m – space group) with the position of the atoms in the unit cell identical to the diamond crystal structure. However, the bandgap of cubic GaN is lower than wurtzite GaN despite of high electron mobility and can only be grown on (011) crystal planes of cubic Si [11]. The cubic GaN is a metastable phase whereas the wurtzite GaN is a stable phase [12]. Hence, wurtzite is the most commonly used GaN crystal structure suitable for power device fabrication. As shown in the figure, depending on the growth techniques, wurtzite GaN can be grown on a substrate starting from the N-face and ending at the Ga-face known as N-polar GaN. The GaN crystal starting from Ga-face and N-face on the surface is known to be Ga-polar or metal polar GaN. The latter is most widely used in the fabrication of HEMTs and HFETs since N-polar GaN deals with material growth and reliability related challenges.

Fig. 1.3 Schematic view of GaN (a.) crystal structure (b.) crystal planes and direction in hexagonal symmetry

The lattice parameters of GaN depends on the stoichiometry, defects and carrier concentration. The dependence of lattice parameter on temperature can be quantified by thermal expansion coefficient, defined by  $\Delta a/a$ . Measurements made over the temperature range of 300-900 K indicate the mean coefficient of thermal expansion of GaN in the c plane to be  $\Delta a/a = 5.8 \times 10^{-6}$  K<sup>-1</sup> [13]. GaN along the c-axis shows thermal conductivity up to 253 W/m. K as demonstrated by Shibata *et. al* verifying GaN as one of the promising materials for high-power switching [14].

GaN is an exceedingly stable compound and exhibits significant hardness. The room temperature hardness of bulk single-crystal GaN is 10.2 GPa and it shows a decrease in hardness at  $1200^{\circ}$  C temperature [15]. In the hexagonal wurtzite structure, GaN has a molecular weight of 83.727 gm/mol. At room temperature, the lattice parameters are  $a_0 = 3.1892 \pm 0.0009$  Å and  $c_0 = 5.1850 \pm 0.0005$  Å. The variability of the lattice constant in early versions of GaN can indeed be attributed to several factors including growth conditions, impurity concentrations, and film stoichiometry. The incorporation of impurities can lead to either contraction or expansion of lattice depending on their type. Different growth temperatures, pressures, and substrate materials can lead to variations in the lattice structure.

### 1.2.2 Epitaxy techniques

The first synthesis of GaN was made in the early 1930s however, due to limited material understanding it remained unexplored for several decades [16]. A major drawback of GaN is that native substrates are not yet available in large quantities and dimensions. This is, in part, due to the low solubility of nitrogen in Ga and the high vapor pressure of nitrogen on GaN. As a result, the bulk growth must resort to high temperatures and high pressures. Incorporating stoichiometric quantities of nitrogen into the film is indeed a major challenge in the growth of Group-III nitrides like GaN, AlN, etc. Achieving the right stoichiometry is crucial for the formation of high-quality nitride films, which directly affects the performance of GaN HEMTs. Substrate surface preparation is the foundation of achieving a high-quality epitaxy. The commonly used growth techniques include Hydride Vapor Phase Epitaxy (HVPE), Metal Organic Chemical Vapor Deposition (MOCVD), and Molecular Beam Epitaxy (MBE).

HVPE is a prominent growth technique used for the production of GaN crystals. HVPE involves the reaction of gaseous hydrogen chloride with liquid or solid gallium to form gallium chloride, which then reacts with ammonia to produce GaN. In this procedure, chloride gas undergoes a reaction with a source of gallium within a temperature range of 800-900°C, resulting in the formation of a gaseous phase within the source zone. Following this initial reaction, the gaseous product is then conveyed to a nitrogen-rich area within the deposition zone, where temperatures are elevated to 1000-1100°C [17]. It is in this environment that the product reacts further with nitrogen, leading to the crystallization of gallium nitride (GaN). HVPE is valued for its efficiency in producing large-area GaN substrates with good crystalline quality. The most significant advantages of HVPE growth include the atmospheric pressure condition and a high growth rate on the order of several hundreds of micrometers per hour [18].

In MOCVD, Trimethylgallium (TMGa) or Trimethylaluminum (TMAl) reacts with NH<sub>3</sub> on a 1000°C heated substrate. MOCVD is favored for its ability to precisely control the composition and thickness of the thin films, making it ideal for fabricating complex semiconductor structures with high purity and uniformity essential for HEMT devices. A typical range of growth temperatures involved in the MOCVD process is  $\sim 500$  to 1200 °C. MOCVD growth can also be carried at either atmospheric pressure or low pressure ( $10^{-2}$ - $10^{-3}$  Torr) which eventually reduces the cost of maintenance. Additionally, growth rates up to 5  $\mu$ m/h can be achieved [19]. However, the need for toxic gases and compounds increases the overall cost with the need for proper protection and exhaust systems.

In MBE, the thin films are grown by firing off metal atoms onto a heated substrate for reaction. MBE usually works in the ultra-high vacuum around  $10^{-9}$  –  $10^{-11}$  Torr pressures, due to which it is compatible with in-situ diagnostics such as Reflection High-Energy Electron Diffraction (RHEED), Auger electron spectrometry, etc. RHEED gun can keep track of the thickness on an atomic scale by employing various patterns on the surface of the substrate. Typically,  $0.3-1~\mu\text{m/h}$  growth rates are employed along with variations in the nucleation and growth temperature to obtain high-quality thin films [20]. The typical growth temperatures in MBE are much lower as compared with MOCVD. All the heterostructures used in this thesis work are grown using the ammonia source MBE technique.

### 1.3 GaN HEMTs

### 1.3.1 History of HEMTs

The high electron mobility transistors (HEMTs) are field effect transistors having lateral architecture containing a 2-DEG at the interface of barrier and channel generated by a combination of polarization effects including spontaneous and piezoelectric polarization in the materials. In 1979, physicist Takashi Mimura, while working at Fujitsu, Japan, invented the HEMTs that use the field effect to control electrons at the interface of a single heterojunction. GaAs MOSFETs that could offer high-speed performance compared to Si MOSFETs motivated his research. Independently, in the same year Daniel Delagebeaudeuf and Tranc Nuyen filed a patent for a heterojunction field effect transistor (HFET) developed using GaAs/AlGaAs doped heterojunctions while working at Thomson-CSF in Paris, France [21]. In 1986, Fujitsu, Japan demonstrated GaAs/AlGaAs HEMT for high-performance very large-scale integration (VLSI) technology along with the self-alignment device fabrication [22]. By 1990, HEMTs based on GaAs/AlGaAs and AlInAs/GaInAs grown on InP substrates demonstrated high performances with their operation up to 95GHz showing great potential for developing millimeter-wave low-noise amplifiers, exhibiting world-record performances for three-terminal semiconductor devices [23]-[25]. However, the high performance of these devices is accompanied by challenges such as low breakdown voltage, issues of thermal dissipation, kink effects, surface degradation, contact degradation, device burnout, etc. [26]. In 1992, Asif Khan et. al observed and confirmed the presence of a 2-DEG in GaN/AlGaN heterojunction demonstrating its high electron mobility [27], [28]. A year later, they demonstrated the first operation of AlGaN/GaN HEMT grown on sapphire substrates, benchmarking the wide-bandgap material for power electronics [29].

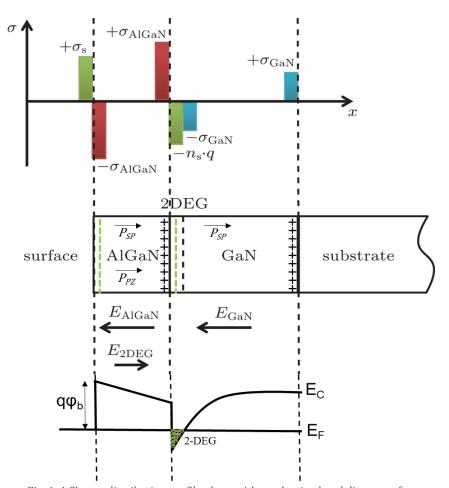

#### 1.3.2 Formation of 2-DEG

GaN HEMTs or heterojunction field effect transistors (HFETs) are derived from the formation of highly mobile 2-DEG at the heterojunction of AlGaN/GaN without any external doping. Firstly, there is a conduction band bending phenomenon in the AlGaN due to the internal polarization fields resulting in the accumulation of electrons at the interface. Secondly, due to fermi level alignment at the heterojunction, the electrons at the interface will form a 2-DEG [30]. The 2-DEG formation can be explained by the existing donor states on the surface of the AlGaN barrier [31]. The spontaneous ( $P_{SP}$ ) polarization and piezoelectric ( $P_{PZ}$ ) polarization generated in the heterostructure can be simplified with the total polarization ( $P_{TOT}$ ) =  $P_{SP}$  (AlGaN) -  $P_{SP}$  (GaN) +  $P_{PZ}$  (AlGaN), considering relaxed GaN channel. The total sheet charge density of 2-DEG can be given by:

Fig. 1. 4 Charge distribution profile along with conduction band diagram of an AlGaN/GaN heterostructure

$$n_{s} = \frac{\sigma_{AlGaN}}{q} - \frac{\varepsilon}{q^{2}d} (q\varphi_{b} + E_{f} - \Delta E_{c})$$

(1.1)

where  $\sigma_{AlGaN}$  is the net polarization-induced charge density in the AlGaN layer, d is the thickness of the AlGaN layer,  $n_s$  is the sheet density of 2-DEG, q is the electron charge, and  $\varepsilon$ is the dielectric constant of AlGaN,  $\phi_b$  is the surface barrier height,  $E_f$  is the Fermi level position with respect to the GaN conduction-band edge at the AlGaN/GaN interface, and  $\Delta E_c$  is the conduction band discontinuity between GaN and AlGaN as shown in Fig. 1.4. The 2-DEG thickness is estimated to be around 2-5 nm. As the thickness of the AlGaN layer is further increased, the 2-DEG density will tend to saturate approaching the value of total polarization-induced charge until the critical thickness after which the barrier tends towards relaxation. This total polarization-induced charge density can be controlled by varying the Al composition in the barrier [32]. The optimal range for the mole fraction in AlGaN/GaN structures is typically between 0.2 and 0.4 [33]. These values are ideal because they generate a substantial polarization charge, which is crucial for creating electrons in the 2-DEG. Moreover, they provide sufficient conduction band discontinuity at the AlGaN/GaN heterojunction, ensuring effective electron confinement. However, higher molar fractions can exacerbate thermal and lattice mismatches between AlGaN and GaN, leading to increased defect density and rougher interfaces affecting the overall performance of the device.

#### 1.3.3 GaN HEMT Structure

The GaN HEMTs are usually fabricated with source/drain ohmic contacts to channel the flow of electrons in 2-DEG and Schottky gate contact to modulate the 2-DEG channel as shown in Fig. 1.5. The detailed explanation of GaN HEMT fabrication process and characterization techniques are described in the next section. The typical GaN HEMT structure can be exploited into various epi-layers described as follows from top to bottom:

I. <u>Cap</u>: The cap layer in HEMTs serves two critical functions that enhance the device's overall performance. Firstly, it reduces the remote Coulomb scattering of electrons in 2-DEG, which effectively enhances the channel mobility. This improvement in mobility is crucial for achieving faster electron transport and better device efficiency. Secondly, the cap plays a role in reducing the peak electric field at the drain-side gate edge, which contributes

to improved device breakdown voltage. This enhancement in breakdown voltage is vital for the robustness and reliability of the device, especially under high-voltage operations. Usually, the cap layer is made up of GaN or SiN.

II. <u>Barrier</u>: The barrier layer enables the formation of a 2-DEG channel at the AlGaN/GaN heterojunction. The thickness and Al content of the barrier will directly affect the 2-DEG properties and hence the transistor threshold voltage, which is tunable. Moreover, it improves the electron confinement in the channel and minimizes the leakage current. The barrier layer for the GaN channel is usually composed of compound semiconductors such as AlGaN, AlN, AlInN, InP, or InAlGaN [34]–[37].

Fig. 1. 5 Schematic cross-sectional diagram of AlGaN/GaN HEMTs

- **III. Channel:** The channel layer facilitates the control of 2-DEG charges by applying a voltage across source-drain contacts. The source-drain contact resistances and drift velocity of electrons flowing from source to drain (channel resistance) will largely determine the output performance of transistors. The thermal stability of the GaN channel allows the devices to operate at much higher temperatures compared to Si FETs.

- **IV. Spacer:** The spacer layer enhances the 2-DEG properties and maintains high electron concentration. It reduces the scattering and electron trapping effects

- at the AlGaN/GaN interface, reducing the current collapse and eventually improving the device's performance.

- V. Buffer: The buffer layer is typically located between the substrate and active layers used to improve the quality of the GaN channel. It prevents the threading dislocations and defects propagating from the substrate towards the channel by burying the defects and bending the dislocations in its vicinity, preserving the quality of the channel. It also provides the electrical isolation of the active area of HEMTs from the substrate and prevents leakage currents. The buffer layer helps with strain management providing the lattice transition from substrate to channel and helps in improving the channel electron confinement. The controlled doping of buffer highly positively influences the device operation under high-stress conditions and improves device reliability and breakdown voltage. The buffer can be made up of various epitaxial configurations such as:

- a. <u>Superlattice buffer</u>: The typical superlattice configuration consists of alternating GaN/AlN layers of less than 20 nm thickness grown for around 4-6µm thickness eventually improving the strain relaxation in layers while providing high insulation and better 2-DEG confinement. They also reduces the dispersion and highly improves the device reliability [38], [39].

- **b. Step graded buffer:** The step-graded buffer layer is usually made up of multiple AlGaN layers stacked in decreasing Al content from the substrate. This allows the mitigation of defects and dislocations originating from the substrate [40].

- VI. <u>Nucleation</u>: The nucleation layer is key to successful GaN epitaxy over variety of substrates. It acts as an intermediate layer to compensate for the lattice mismatch and thermal expansion coefficient difference between GaN channel and various substrates and facilitates the crack free growth of GaN. It acts as seed layer of buffer layers.

| Material | Cost per   | Thermal      | Thermal                    | Maximum   | Critical  |

|----------|------------|--------------|----------------------------|-----------|-----------|

|          | wafer (\$) | Conductivity | expansion                  | Size      | Breakdown |

|          |            | (W/m. K)     | coefficient                | Available | Field     |

|          |            |              | $(10^{-6} \text{ K}^{-1})$ | (mm)      | (MV/cm)   |

| Si       | 20-80      | 150          | 2.5                        | 300       | 0.3       |

| Sapphire | 100-200    | 20-30        | 5-6                        | 300       | 0.4       |

| SiC      | 1300-      | 370          | 3 - 5                      | 200       | 2-3       |

|          | 1800       |              |                            |           |           |

| Bulk     | 3000       | 230          | 3-4                        | 100       | 2-3       |

| GaN      |            |              |                            |           |           |

| Bulk AlN | 5000       | 320          | 4.5                        | 50        | 16        |

Table 1.1 Comparison of material properties, cost and availability for various substrates

VII. Substrate: The choice of substrate material involves a trade-off between the performance, cost and manufacturing capability. The various substrates include Si, sapphire, SiC, bulk GaN and bulk AlN. SiC is widely used for RF applications due to its high thermal conductivity, enabling efficient high frequency switching. Moreover, bulk GaN and AlN are one the most suitable substrates for GaN HEMT epitaxy due to their low lattice mismatch with GaN combined with high thermal conductivity and exceptionally high breakdown field (up to 15 MV/cm) compared to Si (see table 1.1). Silicon remains the prior choice of substrate for industry in order to develop cost-effective electronics. However, it comes with challenges in thermal management and defect control. In this thesis work, HFETs have been fabricated based on an approach to create extreme BV device on AlN and on the contrary a cheaper counterpart based on silicon substrates aiming to overcome GaN-on-Si lateral device operating voltage limitations.

VIII. Source/Drain Contacts: The Source/Drain contacts are fabricated in order to obtain ohmic contacts to the 2-DEG and control the flow of electrons from source to drain. The schematic of typical contacts and the associated resistances are shown in Fig. 1.6. The contacts directly deposited on top of the barrier give a higher resistance path to the 2-DEG. This increases the onstate resistance that indeed lowers the performance of device and induces higher conduction losses. To overcome this issue, partial barrier etched contacts are performed under the source/drain region reducing the overall

contact resistance. Generally, Ti/Al/Ni/Au metal stack is used to fabricate source/drain ohmic contacts to GaN HEMTs.

Fig. 1. 6 Schematic of AlGaN/GaN HEMTs source/drain contacts with (a.) contacts deposited on top of barrier and (b.) barrier etched contacts along with their contact resistances.

IX. Gate Contact: Ni/Au gate contact is often used to achieve Schottky contacts to deplete the 2-DEG. Ni/Au forms a thermally stable Schottky barrier with sufficient barrier height and has high structural integrity necessary for high power applications. For HEMTs or HFETs, usually gate dielectric is used in order to avoid gate leakage current under high electric field with improved field distribution and it acts as a passivation to 2-DEG improving the sheet resistance. The gate dielectric material such as oxide and nitride are commonly used as gate dielectric to constitute metal oxide semiconductor (MOS) and metal insulator semiconductor (MIS) - HEMTs respectively. MISHEMTs or MISHFETs are the choice of devices fabricated throughout this thesis work and used as a test vehicle. Moreover, the impact of SiN on the HFET performance is shown later in section 3.2.6.

#### 1.3.4 Device Fabrication Process

The device fabrication has been developed in the central micro-nano fabrication (CMNF) 1600 m² ISO6 clean room at the Institute of Electronics, Microelectronics and Nanotechnology (IEMN) laboratory. The on-wafer high voltage characterization up to 10 kV has been realized at the Microwave, Optics, and Photonics characterization center (CHOP) facility of IEMN. The HEMT fabrication begins with the dicing of samples using various equipment such as a saw cutter, laser dicing, or diamond point cutter. Since these are novel heterostructures, the wafers are diced into small pieces of approximately 2 cm × 2 cm or quarter pieces depending on the size and type of the substrate. Multiple samples are derived from each wafer necessary for the process optimization at each step and to conclude the

Fig. 1. 7 Schematic fabrication flow diagram of GaN HEMTs

design of experiments. After dicing, the samples are cleaned by standard cleaning process first with acetone and then with isopropyl alcohol (IPA) to get rid of surface contaminants and wafer dust [41]. Finally, the samples are dried using nitrogen gas.

The device processing begins with the formation of source/drain ohmic contacts followed by isolation of the device's active area. Afterward, on-wafer measurements are carried out inside the clean room to verify the 2DEG properties of heterostructures and the quality of ohmic contacts. The surface is passivated after the isolation followed by the deposition of gate and pad contacts as shown in Fig 1.7.

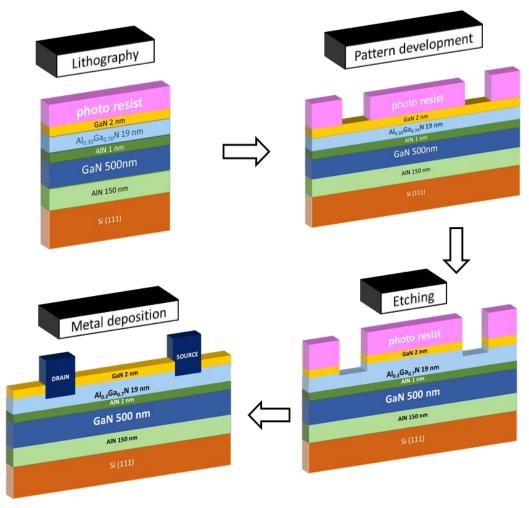

Fig. 1. 8 Schematic of ohmic contact fabrication

#### a) Ohmic contact development

#### i. Source/Drain Contact Fabrication Process

Typically, a 2-3 µm thick bilayer photoresist stack consisting of LOR10A and S1818 are used for contact development. However, during the fabrication of heterostructures grown on bulk AlN substrates, the bilayer lift-off technique showed retention and redeposition of metal particles. The lift-off profile was not clean as well, which might be caused to partial barrier etching prior to metallization or due to the thin undercut of S1818 photo resist. Hence, a new lift-off recipe was developed using a single-layer ARP5320 photoresist. The new recipe uses a 2 µm layer of diluted ARP5320 photoresist reducing the lithography processing time by almost 60% as compared to the bilayer photoresist with a notable improvement of the lift-off profile and excellent contact edge acuity (see Fig. 1.9). The ohmic contact fabrication can be realized into photolithography and development of mask pattern followed by barrier etching and metal deposition as shown in Fig. 1.8. The development of source/drain contact starts with the deposition of hexamethyldisilazane (HMDS), which acts as an adhesion promoter for the resist. Then, ARP5320 photoresist is deposited followed by a 4 min post-bake at 100°C. The devices are then aligned with photo mask using Suss Microtech MA6 aligner and exposed to a UV lamp (365 nm) at around 360-370 watts lamp power. Finally, the patterns are revealed on the sample using the AR 300-26 developer solution.

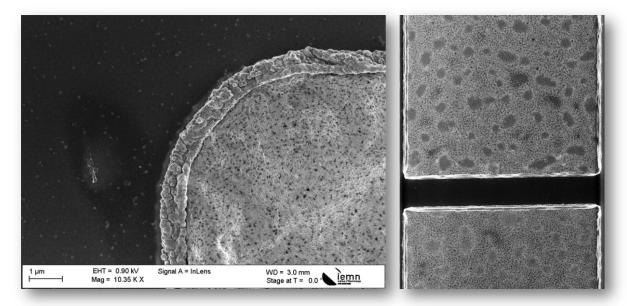

Fig. 1. 9 SEM images of ohmic contacts after RTA

To achieve ohmic behavior, the contact must be in close proximity to the 2DEG. Hence, a recessed barrier etching technique is applied, where approximately 2/3<sup>rd</sup> of the barrier thickness is etched. The devices are moved to inductively coupled plasma-reactive ion etching (ICP-RIE) tool for the GaN/AlGaN etching using low-power Cl<sub>2</sub>/Ar or high-power BCl<sub>3</sub>/SF<sub>6</sub> plasma chemistry [42]–[44]. After dry etching, the contact surface is treated in a HF-incorporated buffered oxide etch (BOE) solution for 30s to remove the native oxide from the surface prior to metallization [45]. The metallization was realized in Plassys MEB550S ebeam evaporator system. The samples are mounted on the holder and kept in the load lock, which is then transferred to the main chamber for required metal stack deposition. The deposition of Ti (12nm)/ Al (200nm)/ Ni (40nm)/ Au (100nm) metal stack is performed using e-beam evaporation under a high vacuum [34]. After metallization, the samples are immersed in the SVC-14 solution heated at 70°C for 1-2 hours for the metal lift-off followed by standard cleaning. The samples undergo rapid thermal annealing (RTA) at 825°C for 30 seconds optimized for GaN channel HEMTs under constant 250 SCCM nitrogen flow concluding the fabrication of source/drain contacts. It can be pointed out that RTA at CMNF using Annealsys AS-one can be ramped up to 1300°C at a maximum rate of 200°C/s.

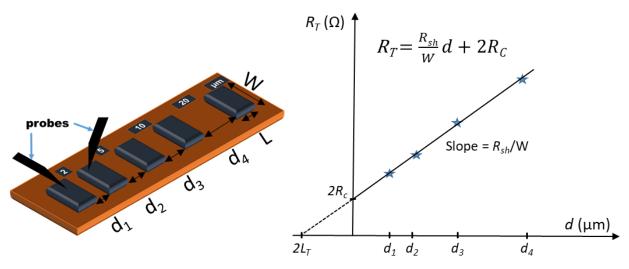

Fig. 1. 10 Schematic of TLM bar pattern with various contact spacing (left) and Graphical description of TLM (right)

#### ii. Contact resistance measurement