# Throughput Optimization Techniques for Heterogeneous Architectures

Nicolas Derumigny

## ► To cite this version:

Nicolas Derumigny. Throughput Optimization Techniques for Heterogeneous Architectures. Computer Science [cs]. Université Grenoble-Alpes; Colorado State University, 2023. English. NNT: 2023GRALM082. tel-04561954v4

## HAL Id: tel-04561954 https://hal.science/tel-04561954v4

Submitted on 25 Nov 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial - NoDerivatives 4.0 International License

COLORADO STATE UNIVERSITY

THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES et de la COLORADO STATE UNIVERSITY

École doctorale : MSTII - Mathématiques, Sciences et Technologies de l'Information, Informatique Spécialité : Informatique

Unité de recherche : Laboratoire d'Informatique de Grenoble

# Techniques d'Optimisation du Débit pour Architectures Hétérogènes

# **Throughput Optimization Techniques for Heterogeneous Architectures**

Présentée par :

# Nicolas DERUMIGNY

## Direction de thèse :

**Fabrice RASTELLO** Directeur de recherche, Inria centre Grenoble-alpes Louis-Noël POUCHET Co-Directeur de thèse Associate Professor, Colorado State University

Directeur de thèse

## Rapporteurs :

Sebastian HACK Full Professor, Saarland University **Erven ROHOU** Directeur de recherche, Inria centre Rennes

Thèse soutenue publiquement le 13 décembre 2023, devant le jury composé de :

## Frédéric DÉTROT

| Professeur des universités, Grenoble INP                                  | Président             |

|---------------------------------------------------------------------------|-----------------------|

| Fabrice RASTELLO                                                          | Directeur de thèse    |

| Directeur de recherche, Inria centre Grenoble-alpes<br>Louis-Noël POUCHET |                       |

| Associate Professor, Colorado State University                            | Co-Directeur de thèse |

| Sebastian HACK                                                            | Rapporteur            |

| Full Professor, Saarland University Erven ROHOU                           |                       |

| Directeur de recherche, Inria centre Rennes                               | Rapporteur            |

| Ayal ZACKS                                                                | Examinateur           |

| Ingénieur, Mobileye                                                       |                       |

## Invités :

Francisco ORTEGA Assistant Professor, Colorado State University James WILSON Full Professor, Colorado State University Yashwant MALAIYA Full Professor, Colorado State University

Titre : Techniques d'Optimisation du Débit pour Architectures Hétérogènes

Mots clés : CPU, architecture, FPGA, synthèse haut-niveau, débit

#### Résumé :

Alors que les processeurs deviennent de plus en plus complexes et nombreux, leur optimisation manuelle est un processus coûteux et propice à l'erreur. Ce manuscrit vise à guider les programmeurs et designers d'accélérateurs via une étude parallèle des impératifs logiciels et matériels qui y sont liés.

Dans la première partie, nous présentons un programme capable de déterminer automatiquement un modèle de performances décrivant le comportement d'un processeur. Dans la seconde partie, nous couvrons l'optimisation de design d'accélérateurs dédiés dans le cadre de la synthèse hautniveau, sous l'aspect du partage de resources.

Title: Throughput Optimization Techniques for Heterogeneous Architectures

Keywords: CPU, architecture, FPGA, HLS, throughput

#### Abstract:

While processors are becoming more and more complex, their manual optimization is a costly and tedious process. This manuscript aims at guiding programmers and hardware designers by proposing a two-sided study of both the software and hardware constraints associated with high-performance accelerator usage.

In the first part, we present a framework able to automatically built a performance model describing the behavior of a CPU. In the second part, we cover the optimization process of dedicated hardware accelerator in the context of high-level synthesis under the angle of resource sharing.

#### ABSTRACT

## THROUGHPUT OPTIMIZATION TECHNIQUES FOR HETEROGENEOUS ARCHITECTURES

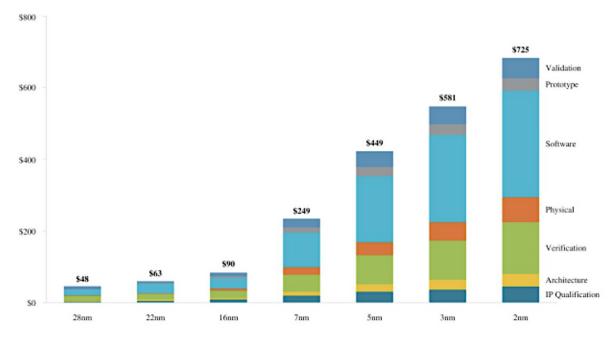

Moore's Law has allowed during the past 40 years to exponentially increase transistor density of integrated circuits. As a result, computing devices ranging from generalpurpose processors to dedicated accelerators have become more and more complex due to the specialization and the multiplication of their compute units. Therefore, both low-level program optimization (e.g. assembly-level programming and generation) and accelerator design must solve the issue of efficiently mapping the input program computations to the various chip capabilities. However, real-world chip blueprints are not openly accessible in practice, and their documentation is often incomplete. Given the diversity of CPUs available (Intel's / AMD's / Arm's microarchitectures), we tackle in this manuscript the problem of automatically inferring a performance model applicable to fine-grain throughput optimization of regular programs. Furthermore, when order of magnitude of performance gain over generic accelerators are needed, domain-specific accelerators must be considered; which raises the same question of the number of dedicated units as well as their functionality. To remedy this issue, we present two complementary approaches: on one hand, the study of single-application specialized accelerators with an emphasis on hardware reuse, and, on the other hand, the generation of semi-specialized designs suited for a user-defined set of applications.

Tout au long des 40 dernières années, la loi de Moore a permis d'augmenter de façon exponentielle la densité des transistors des circuits intégrés. En conséquence, les appareils informatiques – allant des processeurs centraux aux accélérateurs dédiés, sont devenus de plus en plus complexes du fait de la multiplicité croissante de leurs unités de calcul. Par conséquent, à la fois le design de puces et l'optimisation logicielle (qu'elle soit manuelle, en assembleur, ou effectuée par un compilateur) doivent résoudre le problème de l'association efficace des calculs variés du programmes aux unités présentes sur le matériel. Or, les caractéristiques de ces unités ne sont pas toujours disponibles. Devant la diversité des CPU du commerce (Intel, AMD, Arm ayant chacun leurs microarchitectures), nous nous attaquons ici au problème de la génération automatique de modèles de performance, applicables lors de l'optimisation à grain fin de programmes réguliers. De plus, dans les cas où des gains de multiples ordre de grandeur sont désirés, des accélérateurs spécifiques doivent être utilisés, ce qui pose une question similaire au niveau de l'organisation de la puce. Pour faire face à ces questions, nous proposons deux approches complémentaires : d'une part, l'étude d'accélérateurs de calcul haute performance dédiés à une unique application et, d'autre part, la génération automatique d'architectures semi-spécialisées à une famille d'applications.

#### ACKNOWLEDGEMENTS

Thought I would lie by telling that I have not been warned, the process of writing this manuscript revealed to be harder that anticipated. First, the initial goal of compiling the work realized in two radically different universities was completed by a worldwide pandemic and my inclination to launch myself in too many projects; which already made the task challenging – but I was still not expecting *that*.

Studying, researching is a never-ending quest of discoveries and knowledge, but also of disappointments and "walls" that sometimes cannot be overcome. In this path, I was helped by many fabulous people whom I dedicated this manuscript to. First, my two advisors Louis-Noël Pouchet and Fabrice Rastello. Louis-Noël, you taught me what to expect as a researcher, the challenges that come with it but also the will to do *good science*. Thank you for your never-ending goal of letting people do what makes them feel happy when they go to sleep, and sorry not to have baked more brioche while you were in Fort Collins – I am sure other occasions will come. Fabrice, you taught me to trust my ideas, to collaborate with other students, to stay impartial writing my work, and what a good coffee taste like. Thanks for your guidance and your patience, both of which should have been put quite to the test with me. Sorry again for the lack of *numbers*! Without both of you, I would not have the same understanding of academia.

I would also not have done this work without Corentin, whom I thank from the heart. I owe you a lot, and I apologies to have relied too much on you during deadlines – you are one of the kindest person I know for that. Thank also to my colleagues Chistophe, Stéphane, Théophile, Nicolas and Théo whose discussions where always very insightful.

However, academic work is not the only reflection of one's activities, and part of the work on CPU would have not been possible without the support of my colleagues at *Hardware & Co.* Thank you Eric for your experience, Thibaut for your character and your common sense, Matthieu for your model of regularity and organization, and all the others I forget: Thomas, David, Adrien, Kéta, and of course Guillaume H., whose timing was more than perfect.

A special thank is also more than deserved by you, Guillaume L. for your support, your passion and you time for both professional and personal matters. I owe you probably more than you think. One thing leading to another, I also want to reluctantly thank Pascal. You introduced me to fantastic people and taught me the hard way how to have the courage to stand up and change everything. For better or worse, this manuscript would been deeply modified if I had not met you.

Thanks also to my family for leaving me enough independence and letting me trace my own path while still being there when needed: mom, dad, and my sister Heloïse who is always so glad to see me coming back. Alexis, I know that I should have called you more often. You were of precious advice, thank you to let me catch glimpses of a professor's life, and for all the laughs we shared! I also do not forget my colleague at AMD, Benoit Pradelle, Florian, Stefan and Thibault, who make me realize that a dynamic team is sufficient to go to work with a smile on one's lips.

Last but not least, I want to thank you Marie for your support, you presence, your frankness and your constant reminder that life is not just about work and side projects. You made me travel all around the world for you... literally! Thanks for the constant connection to France – and India. I once again apologize for the 2 years spent so far away from you. This is now over.

## TABLE OF CONTENTS

| ACKNOWL<br>LIST OF TA | Γ<br>EDGEMENTS<br>ABLES<br>IGURES                             | ii<br>iv<br>x<br>xii |

|-----------------------|---------------------------------------------------------------|----------------------|

| Chapter 1             | Introduction                                                  | 1                    |

| Chapter 2             | Background                                                    | 6                    |

| 2.1                   | Abstract Resource Model                                       | 7                    |

| 2.1.1                 | Resources                                                     | 7                    |

| 2.1.2                 | Pipelining and Resource Sharing                               | 8                    |

| 2.1.3                 | Scheduling                                                    | 10                   |

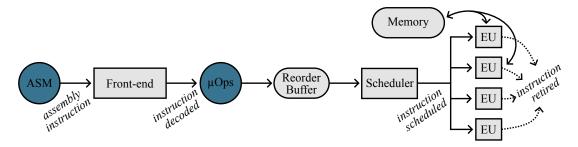

| 2.2                   | General CPU Architecture                                      | 13                   |

| 2.2.1                 | Out-of-order Execution                                        | 13                   |

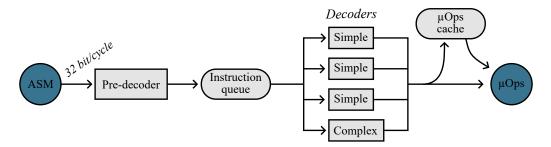

| 2.2.2                 | Front-end                                                     | 14                   |

| 2.2.3                 | Instruction Set Extensions                                    | 15                   |

| I Throu               | ghput Optimization for Superscalar Architectures              | 16                   |

| Chapter 3             | Throughput Performance Models for Superscalar Architectures   | 17                   |

| 3.1                   | State of the Art                                              | 18                   |

| 3.1.1                 | Performance Counters Derived Models                           | 18                   |

| 3.1.2                 | Proprietary and Ad-Hoc Tools                                  | 19                   |

| 3.1.3                 | Comparison with the Abstract Resource Model                   | 19                   |

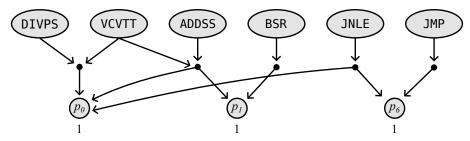

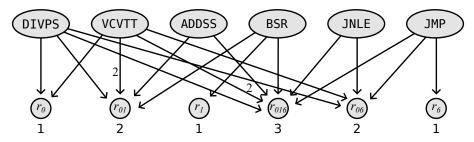

| 3.2                   | Conjunctive and Disjunctive Resource Mapping                  | 21                   |

| 3.2.1                 | Tripartite and Bipartite Port Mapping                         | 21                   |

| 3.2.2                 | Dual Representation of a Disjunctive Mapping                  | 22                   |

| 3.3                   | Code Generation for Accurate Throughput Measurements          | 25                   |

| 3.3.1                 | Padding Microkernels of Multiple Instructions                 | 25                   |

| 3.3.2                 | Generation of Basic Blocks with no Dependencies               | 26                   |

| 3.3.3                 | Limitations of the Code Generator                             | 28                   |

| Chapter 4             | PALMED: Efficient Automated Characterisation of Throughput in |                      |

|                       | Superscalar Architetures                                      | 30                   |

| 4.1                   | Complete Flow of PALMED                                       | 31                   |

| 4.2                   | Selection Heuristics                                          | 33                   |

| 4.2.1                 | How not to Benchmark the Whole ISA                            | 33                   |

| 4.2.2                 | Max Clique: Very Basic Instructions                           | 34                   |

| 4.2.3                 | Min Order: Most Greedier Instructions                         | 35                   |

| 4.3                   | Finding the Exact Core Mapping                                | 37                   |

| 4.3.1                 | Determine Hazardous Instructions                              | 37                   |

| 4.3.2                 | Bipartite Weight Problem (BWP)                                | 38                   |

| 4.3.3                 | Characterize Resources $(LP_1)$                               | 38                   |

| 4.3.4                 | Find Saturating Kernels $(LP_2)$                              | 39                   |

| $ \begin{array}{r} 4.4 \\ 4.4.1 \\ 4.4.2 \\ 4.5 \\ 4.6 \\ \end{array} $                                                                                                                    | Faster approximation of the Complete Resource Mapping ProblemFinding the Shape of the Mapping: $(ILP_1)$ Find Saturating Kernels $(LP_2)$ Complete Mapping $(LP_{AUX})$ Evaluation: Basic Blocks Throughput Prediction without Depen-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41<br>41<br>42<br>44                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $4.6.1 \\ 4.6.2$                                                                                                                                                                           | dencies          Exact Port Mapping Recovery          Real-world CPU Throughput Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>45<br>46                                                                                                                                                                                                                                                         |

| Chapter 5<br>5.1                                                                                                                                                                           | Formal Proofs of Convergence of PALMED<br>Equivalence of the Abstract Resource Model and the Port Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                                                                                                                                                                                                                     |

| $5.1.1 \\ 5.1.2$                                                                                                                                                                           | Model       Primary Definitions         Primary Definitions       Primary Definitions         Equivalence between Disjunctive and Conjunctive formulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53<br>53<br>55                                                                                                                                                                                                                                                         |

| $5.2 \\ 5.2.1$                                                                                                                                                                             | Selection of Basic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58<br>58                                                                                                                                                                                                                                                               |

| $5.2.2 \\ 5.2.3$                                                                                                                                                                           | Max Clique: Selection of Independent Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60<br>60                                                                                                                                                                                                                                                               |

| 5.3                                                                                                                                                                                        | Convergence to the Complete Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60<br>62                                                                                                                                                                                                                                                               |

| II Gene                                                                                                                                                                                    | ration of Throughput-Efficient Accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66                                                                                                                                                                                                                                                                     |

| Chapter 6                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>0-</b>                                                                                                                                                                                                                                                              |

| - · T. · · ·                                                                                                                                                                               | High-Level Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                                                                                                                                                                                                                     |

| 6.1                                                                                                                                                                                        | High-Level Synthesis    Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67<br>68                                                                                                                                                                                                                                                               |

| -                                                                                                                                                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                        |

| 6.1                                                                                                                                                                                        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68                                                                                                                                                                                                                                                                     |

| $6.1 \\ 6.1.1$                                                                                                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68<br>68                                                                                                                                                                                                                                                               |

| $ \begin{array}{r} 6.1 \\ 6.1.1 \\ 6.1.2 \end{array} $                                                                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68<br>68<br>71                                                                                                                                                                                                                                                         |

| $ \begin{array}{r} 6.1 \\ 6.1.1 \\ 6.1.2 \\ 6.1.3 \end{array} $                                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68<br>68<br>71<br>77                                                                                                                                                                                                                                                   |

| $ \begin{array}{r} 6.1 \\ 6.1.1 \\ 6.1.2 \\ 6.1.3 \\ 6.1.4 \end{array} $                                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68<br>68<br>71<br>77<br>78                                                                                                                                                                                                                                             |

| $ \begin{array}{r} 6.1\\ 6.1.1\\ 6.1.2\\ 6.1.3\\ 6.1.4\\ 6.1.5 \end{array} $                                                                                                               | Introduction       Overview         Overview       Overview         Annotation of the Source Code with pragma       Overview         Controlling Resource Usage       Overview         Handling Off-chip Communications       Overview         Selection of the Design Frequency       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68<br>68<br>71<br>77<br>78<br>79                                                                                                                                                                                                                                       |

| $\begin{array}{c} 6.1 \\ & 6.1.1 \\ & 6.1.2 \\ & 6.1.3 \\ & 6.1.4 \\ & 6.1.5 \\ & 6.2 \end{array}$                                                                                         | Introduction       Overview         Overview       Overview         Annotation of the Source Code with pragma       Overview         Controlling Resource Usage       Overview         Handling Off-chip Communications       Overview         Selection of the Design Frequency       Overview         Generic Toolchain's Limitations       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68<br>68<br>71<br>77<br>78<br>79<br>81                                                                                                                                                                                                                                 |

| $ \begin{array}{r} 6.1\\ 6.1.1\\ 6.1.2\\ 6.1.3\\ 6.1.4\\ 6.1.5\\ 6.2\\ 6.2.1 \end{array} $                                                                                                 | Introduction       Overview         Overview       Overview         Annotation of the Source Code with pragma       Overview         Controlling Resource Usage       Overview         Handling Off-chip Communications       Overview         Selection of the Design Frequency       Overview         Generic Toolchain's Limitations       Overview         Parallel Operations       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>68<br>71<br>77<br>78<br>79<br>81<br>81                                                                                                                                                                                                                           |

| $\begin{array}{c} 6.1 \\ & 6.1.1 \\ & 6.1.2 \\ & 6.1.3 \\ & 6.1.4 \\ & 6.1.5 \\ & 6.2 \\ & 6.2.1 \\ & 6.2.2 \end{array}$                                                                   | Introduction       Overview         Overview       Annotation of the Source Code with pragma         Annotation of the Source Usage       Handling Resource Usage         Controlling Resource Usage       Handling Off-chip Communications         Selection of the Design Frequency       Handling         Generic Toolchain's Limitations       Handle Operations         Frequency Domains       Handle Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68<br>68<br>71<br>77<br>78<br>79<br>81<br>81<br>81                                                                                                                                                                                                                     |

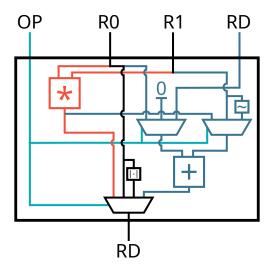

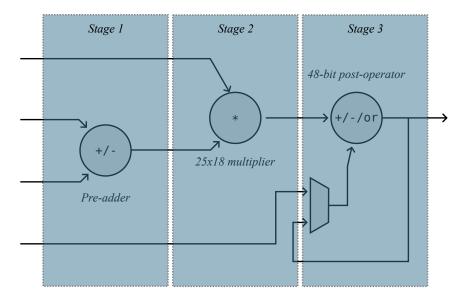

| $\begin{array}{c} 6.1 \\ & 6.1.1 \\ & 6.1.2 \\ & 6.1.3 \\ & 6.1.4 \\ & 6.1.5 \\ & 6.2 \\ & 6.2.1 \\ & 6.2.2 \\ & 6.2.3 \end{array}$                                                        | Introduction       Overview         Overview       Annotation of the Source Code with pragma         Annotation of the Source Usage       Handling Resource Usage         Controlling Resource Usage       Handling Off-chip Communications         Belection of the Design Frequency       Handling         Generic Toolchain's Limitations       Handle Operations         Frequency Domains       Handle Operations         DSP Primitives       Handle Operations                                                                                                                                                                                                                                                                                                                                                                                                                     | 68<br>68<br>71<br>77<br>78<br>79<br>81<br>81<br>81<br>82                                                                                                                                                                                                               |

| $\begin{array}{c} 6.1 \\ & 6.1.1 \\ & 6.1.2 \\ & 6.1.3 \\ & 6.1.4 \\ & 6.1.5 \\ & 6.2 \\ & 6.2.1 \\ & 6.2.2 \\ & 6.2.3 \\ & 6.3 \end{array}$                                               | IntroductionOverviewAnnotation of the Source Code with pragmaAnnotation of the Source UsageControlling Resource UsageHandling Off-chip CommunicationsSelection of the Design FrequencyGeneric Toolchain's LimitationsParallel OperationsFrequency DomainsDSP PrimitivesToolchain's Limitations for Resource-Shared Design Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68<br>68<br>71<br>77<br>78<br>79<br>81<br>81<br>81<br>82<br>83                                                                                                                                                                                                         |

| $\begin{array}{c} 6.1 \\ & 6.1.1 \\ & 6.1.2 \\ & 6.1.3 \\ & 6.1.4 \\ & 6.1.5 \\ & 6.2 \\ & 6.2.1 \\ & 6.2.2 \\ & 6.2.3 \\ & 6.3.1 \end{array}$                                             | Introduction       Overview         Overview       Annotation of the Source Code with pragma         Annotation of the Source Usage       Annotation         Controlling Resource Usage       Handling Off-chip Communications         Handling Off-chip Communications       Selection of the Design Frequency         Generic Toolchain's Limitations       Parallel Operations         Parallel Operations       Frequency Domains         DSP Primitives       DSP Primitives         Toolchain's Limitations for Resource-Shared Design Generation         Expressing Shared Modules       Overhead of Operation Clustering                                                                                                                                                                                                                                                          | <ol> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> </ol>                                                                                                                         |

| $\begin{array}{c} 6.1\\ & 6.1.1\\ & 6.1.2\\ & 6.1.3\\ & 6.1.4\\ & 6.1.5\\ & 6.2\\ & 6.2.1\\ & 6.2.2\\ & 6.2.3\\ & 6.3.1\\ & 6.3.2\end{array}$                                              | Introduction       Overview         Overview       Annotation of the Source Code with pragma         Annotation of the Source Usage       Annotation         Controlling Resource Usage       Handling Off-chip Communications         Handling Off-chip Communications       Handling Off-chip Communications         Selection of the Design Frequency       Handling Off-chip Communications         Generic Toolchain's Limitations       Handling Off-chip Communications         Parallel Operations       Handling Communications         Frequency Domains       Handling Communications         DSP Primitives       Handling Communications         Toolchain's Limitations for Resource-Shared Design Generation       Handling Communications         Expressing Shared Modules       Handling Communications                                                                 | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> </ul>                                                                                                             |

| $\begin{array}{c} 6.1\\ & 6.1.1\\ & 6.1.2\\ & 6.1.3\\ & 6.1.4\\ & 6.1.5\\ & 6.2\\ & 6.2.1\\ & 6.2.2\\ & 6.2.3\\ & 6.3.3\\ & 6.3.1\\ & 6.3.2\\ & 6.3.3\\ & 6.3.4\\ \end{array}$             | Introduction       Overview         Overview       Annotation of the Source Code with pragma         Annotation of the Source Usage       Generic Controlling Resource Usage         Handling Off-chip Communications       Handling Off-chip Communications         Selection of the Design Frequency       Generic Toolchain's Limitations         Generic Toolchain's Limitations       Parallel Operations         Frequency Domains       DSP Primitives         Toolchain's Limitations for Resource-Shared Design Generation       Expressing Shared Modules         Overhead of Operation Clustering       Fine-grain Execution Pipeline Generation         Fine-grain Execution Pipeline Generation       Accurate Measuring of the Execution Time         Towards a General Formulation of the Resource Sharing Problem       .                                                 | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> <li>85</li> <li>85</li> <li>85</li> <li>87</li> </ul>                                                 |

| $\begin{array}{c} 6.1 \\ & 6.1.1 \\ & 6.1.2 \\ & 6.1.3 \\ & 6.1.4 \\ & 6.1.5 \\ & 6.2 \\ & 6.2.1 \\ & 6.2.2 \\ & 6.2.3 \\ & 6.3.3 \\ & 6.3.1 \\ & 6.3.2 \\ & 6.3.3 \\ & 6.3.4 \end{array}$ | Introduction       Overview         Annotation of the Source Code with pragma       Annotation of the Source Code with pragma         Controlling Resource Usage       Handling Off-chip Communications         Handling Off-chip Communications       Selection of the Design Frequency         Generic Toolchain's Limitations       Parallel Operations         Parallel Operations       Parallel Operations         DSP Primitives       DSP Primitives         Toolchain's Limitations for Resource-Shared Design Generation       Expressing Shared Modules         Overhead of Operation Clustering       Fine-grain Execution Pipeline Generation         Fine-grain Execution Pipeline Generation       Accurate Measuring of the Execution Time         Towards a General Formulation of the Resource Sharing Problem       Existing Resource Sharing Techniques               | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> <li>85</li> <li>85</li> <li>85</li> <li>87</li> <li>88</li> </ul>                                                 |

| $\begin{array}{c} 6.1\\ & 6.1.1\\ & 6.1.2\\ & 6.1.3\\ & 6.1.4\\ & 6.1.5\\ & 6.2\\ & 6.2.1\\ & 6.2.2\\ & 6.2.3\\ & 6.3\\ & 6.3.1\\ & 6.3.2\\ & 6.3.3\\ & 6.3.4\\ \end{array}$               | Introduction       Overview         Annotation of the Source Code with pragma       Overview         Annotation of the Source Usage       Overview         Handling Off-chip Communications       Handling Off-chip Communications         Selection of the Design Frequency       Generic Toolchain's Limitations         Parallel Operations       Parallel Operations         Prequency Domains       Poperations         DSP Primitives       Overhead of Operation Clustering         Fine-grain Execution Pipeline Generation       Fine-grain Execution Pipeline Generation         Accurate Measuring of the Execution Time       Accurate Measuring Techniques         Basic Blocks-Level Resource Sharing       Sharing                                                                                                                                                         | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> <li>85</li> <li>85</li> <li>85</li> <li>87</li> <li>88</li> <li>88</li> </ul>                                     |

| $\begin{array}{c} 6.1\\ & 6.1.1\\ & 6.1.2\\ & 6.1.3\\ & 6.1.4\\ & 6.1.5\\ & 6.2\\ & 6.2.1\\ & 6.2.2\\ & 6.2.3\\ & 6.3.3\\ & 6.3.1\\ & 6.3.2\\ & 6.3.3\\ & 6.3.4\\ \end{array}$             | Introduction       Overview         Annotation of the Source Code with pragma       Annotation of the Source Usage         Controlling Resource Usage       Handling Off-chip Communications         Selection of the Design Frequency       Generic Toolchain's Limitations         Parallel Operations       Parallel Operations         Frequency Domains       Frequency Domains         DSP Primitives       Toolchain's Limitations for Resource-Shared Design Generation         Expressing Shared Modules       Overhead of Operation Clustering         Fine-grain Execution Pipeline Generation       Accurate Measuring of the Execution Time         Towards a General Formulation of the Resource Sharing Problem       Existing Resource Sharing Techniques         Basic Blocks-Level Resource Sharing       Loop-based Resource Sharing for Throughput-based Optimization | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> <li>85</li> <li>85</li> <li>85</li> <li>87</li> <li>88</li> <li>88</li> </ul>                                     |

| $\begin{array}{c} 6.1\\ & 6.1.1\\ & 6.1.2\\ & 6.1.3\\ & 6.1.4\\ & 6.1.5\\ & 6.2\\ & 6.2.1\\ & 6.2.2\\ & 6.2.3\\ & 6.3\\ & 6.3.1\\ & 6.3.2\\ & 6.3.3\\ & 6.3.4\\ \end{array}$               | Introduction       Overview         Annotation of the Source Code with pragma       Overview         Annotation of the Source Usage       Overview         Handling Off-chip Communications       Handling Off-chip Communications         Selection of the Design Frequency       Generic Toolchain's Limitations         Parallel Operations       Parallel Operations         Prequency Domains       Poperations         DSP Primitives       Overhead of Operation Clustering         Fine-grain Execution Pipeline Generation       Fine-grain Execution Pipeline Generation         Accurate Measuring of the Execution Time       Accurate Measuring Techniques         Basic Blocks-Level Resource Sharing       Sharing                                                                                                                                                         | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> <li>85</li> <li>85</li> <li>85</li> <li>87</li> <li>88</li> <li>88</li> </ul>                                     |

| $\begin{array}{c} 6.1\\ & 6.1.1\\ & 6.1.2\\ & 6.1.3\\ & 6.1.4\\ & 6.1.5\\ & 6.2\\ & 6.2.1\\ & 6.2.2\\ & 6.2.3\\ & 6.3.3\\ & 6.3.1\\ & 6.3.2\\ & 6.3.3\\ & 6.3.4\\ \end{array}$             | Introduction       Overview         Annotation of the Source Code with pragma       Annotation of the Source Usage         Controlling Resource Usage       Handling Off-chip Communications         Selection of the Design Frequency       Generic Toolchain's Limitations         Parallel Operations       Parallel Operations         Frequency Domains       Frequency Domains         DSP Primitives       Toolchain's Limitations for Resource-Shared Design Generation         Expressing Shared Modules       Overhead of Operation Clustering         Fine-grain Execution Pipeline Generation       Accurate Measuring of the Execution Time         Towards a General Formulation of the Resource Sharing Problem       Existing Resource Sharing Techniques         Basic Blocks-Level Resource Sharing       Loop-based Resource Sharing for Throughput-based Optimization | <ul> <li>68</li> <li>68</li> <li>71</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>81</li> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>83</li> <li>85</li> <li>85</li> <li>85</li> <li>85</li> <li>87</li> <li>88</li> <li>88</li> <li>90</li> </ul> |

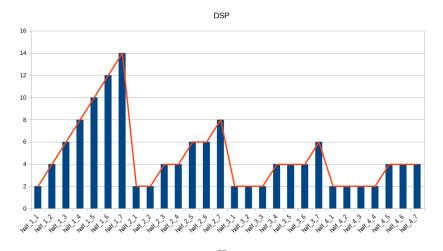

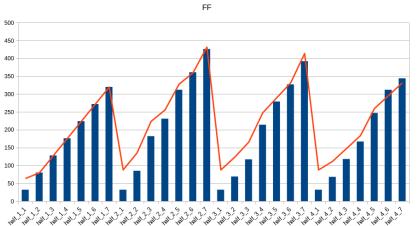

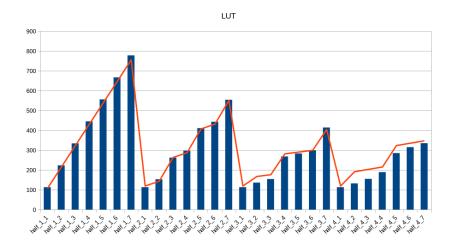

96

7.3.1

| 7.3.2     | LUT Estimation                                                  | 96  |  |  |

|-----------|-----------------------------------------------------------------|-----|--|--|

| 7.3.3     | Storage Units Estimation                                        | 97  |  |  |

| 7.3.4     | Microbenchmarking CDAGs                                         | 98  |  |  |

| 7.3.5     | Combination of Sequential and Parallel Models                   | 98  |  |  |

| 7.3.6     | Evaluation                                                      | 100 |  |  |

| 7.4       | Latency Estimation of Compute Units                             | 103 |  |  |

| 7.4.1     | Formula and Micro-benchmarking                                  |     |  |  |

| 7.4.2     | Evaluation                                                      | 103 |  |  |

| 7.5       | Naive Convex Encoding of the Resource Sharing Problem           | 105 |  |  |

| 7.5.1     | Variables                                                       | 105 |  |  |

| 7.5.2     | Objective Function                                              | 106 |  |  |

| 7.5.3     | Constraints                                                     | 106 |  |  |

| 7.6       | Real-life Implementation, Heuristics                            | 110 |  |  |

| 7.6.1     | Exact Implementation: Scaling                                   | 110 |  |  |

| 7.6.2     | A Faster Greedy Approximation                                   | 111 |  |  |

| Chapter 8 | Automated Generation of Semi-generic Throughput-oriented Accel- |     |  |  |

|           | erators                                                         | 116 |  |  |

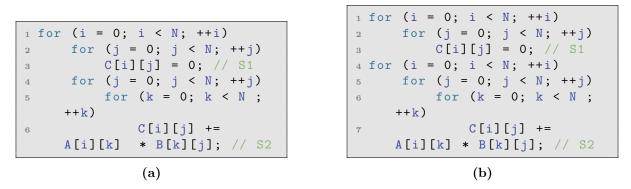

| 8.1       | Illustrative Examples                                           | 117 |  |  |

| 8.1.1     | Data Centering                                                  | 117 |  |  |

| 8.1.2     | Center, Correlation and Multi-purpose Acceleration              | 118 |  |  |

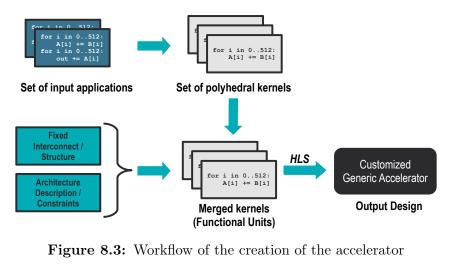

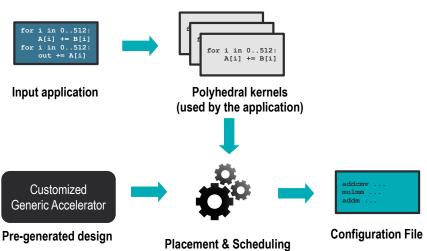

| 8.1.3     | Accelerator Creation and Usage Workflow                         | 120 |  |  |

| 8.2       | Kernel Merging for Multi-Functionalities                        | 122 |  |  |

| 8.2.1     | Polyhedral Kernel Representation                                | 122 |  |  |

| 8.2.2     | Decomposition of Applications into Kernels                      | 123 |  |  |

| 8.2.3     | Kernel Set and Workloads                                        | 125 |  |  |

| 8.2.4     | Kernel Merging                                                  | 128 |  |  |

| 8.2.5     | Profitability Criteria                                          | 129 |  |  |

| 8.3       | Accelerator Implementation                                      | 132 |  |  |

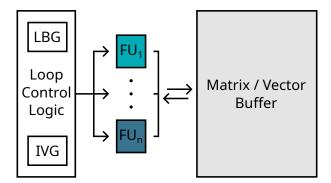

| 8.3.1     | Structure of the Accelerator                                    | 132 |  |  |

| 8.3.2     | Iteration Vector Generator (IVG)                                | 132 |  |  |

| 8.3.3     | Functional Units                                                | 132 |  |  |

| 8.3.4     | Loop Bound Generator (LBG)                                      | 134 |  |  |

| 8.3.5     | Loop Control Logic                                              | 134 |  |  |

| 8.3.6     | Off-Chip Communications                                         | 134 |  |  |

| 8.3.7     | Access to the Local Buffer                                      | 134 |  |  |

| 8.4       | Experimental Results                                            | 135 |  |  |

| 8.4.1     | Linear Algebra                                                  | 136 |  |  |

| 8.4.2     | Correlation                                                     | 139 |  |  |

| 8.4.3     | Scaling and Comparison                                          | 140 |  |  |

| 8.5       | Limitations                                                     | 143 |  |  |

| 8.5.1     | Routing between FUs and Buffers                                 | 143 |  |  |

| 8.5.2     | Merging of Kernels with Different Iteration Space               | 143 |  |  |

| 8.5.3     | Data Reuse: Optimizing Buffer Communication                     | 143 |  |  |

| 8.5.4     | No Control Flow Instructions                                    | 143 |  |  |

| 8.5.5     | Vectorization of the FUs                                        | 144 |  |  |

| 8.6       | Related Work                                                    | 145 |  |  |

| 8.6.1     | Generic Resource-shared Designs                                 | 145 |  |  |

| 8.6.2     | DSP-dedicated Resource Sharing on Overlay Architectures | 147 |

|-----------|---------------------------------------------------------|-----|

| Chapter 9 | Conclusion and Future Research Directions               | 150 |

## LIST OF TABLES

| 2.1          | Example of resource for different hardware targets                                                                                                                                                                       | 8                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| $4.1 \\ 4.2$ | Summary of key features of PALMED vs. related work                                                                                                                                                                       | 30                                      |

| 4.3          | lated from uops.info's mappingMain features of the obtained mappings                                                                                                                                                     | $\begin{array}{c} 46 \\ 49 \end{array}$ |

| 7.1          | Resource, latency and throughput estimates of two architectures for an accelerator executing 10 successive instances of the program from Fig. 7.3c                                                                       | 95                                      |

| 7.2          | Resource predictor accuracy                                                                                                                                                                                              | 100                                     |

| 7.3          | Resource predictor coefficients for sequential composition of additions (a) and multiplications (b)                                                                                                                      | 101                                     |

| 7.4          | Resource predictor coefficients for parallel composition of additions (a) and multiplications (b)                                                                                                                        | 101                                     |

| 7.5          | Resource predictor accuracy on FP16 multipliers and adders                                                                                                                                                               | 101                                     |

| 7.6          | Latency predictor coefficients on FP16 multipliers and adders                                                                                                                                                            | 103                                     |

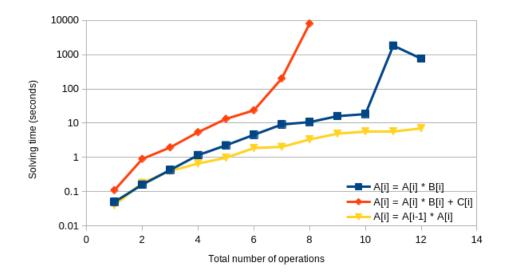

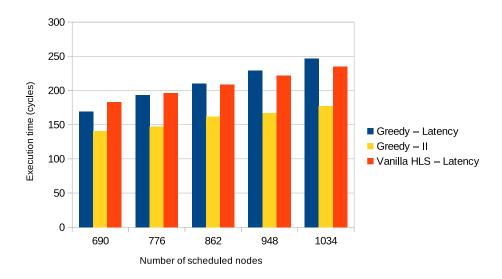

| 7.7          | Greedy scheduling-placement solving time and number of operations for one $Nx16$ DWT iteration.                                                                                                                          | 113                                     |

| 8.1          | Performance and area metric for coarse-grained pipeline (CGP) vs coarse                                                                                                                                                  |                                         |

|              | grained replication (CGR) of CENTER accelerator (matrices of size $64 \times 64$ ,                                                                                                                                       | 110                                     |

| 8.2          | FP16 data type)                                                                                                                                                                                                          | 119                                     |

|              | celerator and dedicated accelerator $\ldots \ldots \ldots$                                                                                                | 120                                     |

| 8.3          | Performance per area metric for coarse-grain pipelined correlation, sum accel-                                                                                                                                           |                                         |

|              | erator and dedicated accelerator                                                                                                                                                                                         | 120                                     |

| 8.4<br>8.5   | Configuration of the LA-GA accelerator and the Correlation accelerator<br>Supported kernels list, by either the Correlation or the Linear Algebra accel-                                                                 | 135                                     |

| 0.0          | erator                                                                                                                                                                                                                   | 136                                     |

| 8.6          | Execution time (a) and performance-per-area (b) of a custom IP optimized<br>for Max Sharing (MS) and Max Throughput (MT) and the Generic Accelera-<br>ter hath with www IUS FUS (LA CA IUS) and were IUS FUS (LA CA) for |                                         |

|              | tor, both with pure HLS FUs (LA-GA-HLS) and non-HLS FUs (LA-GA) for several linear algebra benchmarks                                                                                                                    | 137                                     |

| 8.7          | Execution time (a) and performance-per-area (b) of a custom IP optimized                                                                                                                                                 | 101                                     |

| 0.1          | for Max Sharing (MS) and Max Throughput (MT) and the Generic Accelera-                                                                                                                                                   |                                         |

|              | tor, both with pure HLS FUs (LA-GA-HLS) and non-HLS FUs (LA-GA) for                                                                                                                                                      |                                         |

|              | batched linear algebra benchmarks                                                                                                                                                                                        | 138                                     |

| 8.8          | Execution time (a) and performance-per-area (b) of a custom IP optimized for                                                                                                                                             |                                         |

|              | Max Sharing (MS) and Max Throughput (MT) and the Generic Accelerator,                                                                                                                                                    |                                         |

|              | both with pure HLS FUs (CORR-GA-HLS) and non-HLS FUs (CORR-GA)                                                                                                                                                           |                                         |

|              | for correlation subexpressions                                                                                                                                                                                           | 138                                     |

| 8.9          | Execution time (a) and performance-per-area (b) of a custom IP optimized for                                                                                                                                             |                                         |

|              | Max Sharing (MS) and Max Throughput (MT) and the Generic Accelerator,                                                                                                                                                    |                                         |

|              | both with pure HLS FUs (CORR-GA-HLS) and non-HLS FUs (CORR-GA)                                                                                                                                                           |                                         |

|              | for batched correlation subexpressions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                           | 139                                     |

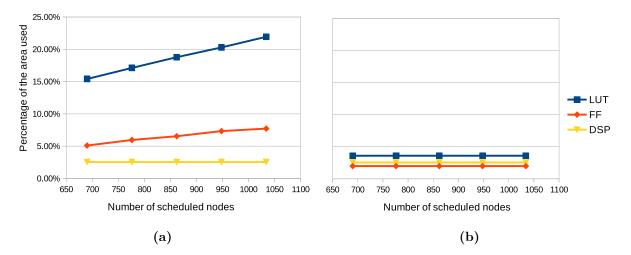

| 8.10 | Scaling properties of the LA-GA accelerator                              | 141 |

|------|--------------------------------------------------------------------------|-----|

| 8.11 | Maximum frequency achieved for each design                               | 141 |

| 8.12 | Performance per area comparison with data extracted from other published |     |

|      | accelerators                                                             | 142 |

## LIST OF FIGURES

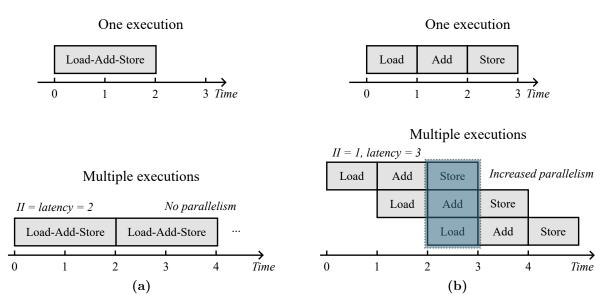

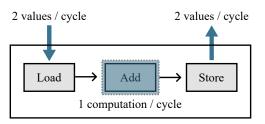

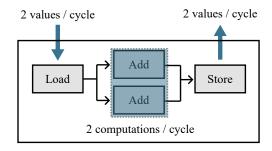

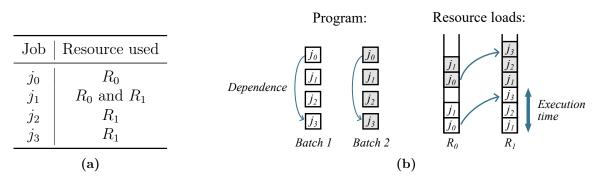

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>  | Non-pipelined (a) versus pipelined (b) designs                                                                                                                                                                                                                                                                                                                                                                   | 9<br>10<br>10<br>13<br>14        |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

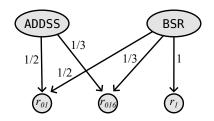

| 3.1<br>3.2<br>3.3                                                            | Mappings computed for a few SKL-SP instructions                                                                                                                                                                                                                                                                                                                                                                  | 22<br>23                         |

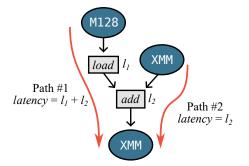

| 3.4                                                                          | one ORQ (register rotation left of a constant factor 1) $\dots \dots \mu$ OPs generated for SSE vector add (VADDPD) with one operand from memory (M128) and two register operands (XMM) and associated latency $\dots \dots \dots$ | 27<br>28                         |

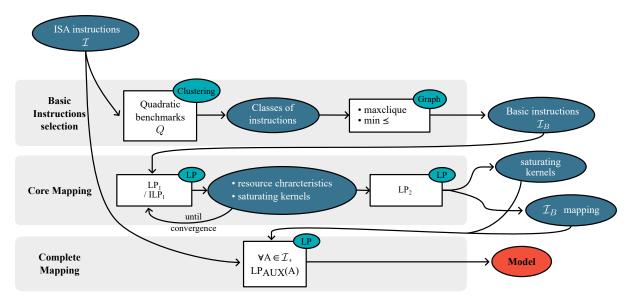

| $4.1 \\ 4.2$                                                                 | High-level view of the algorithms of PALMED                                                                                                                                                                                                                                                                                                                                                                      | 31                               |

| 4.3                                                                          | tions, edges symbolize instructions with additive IPC                                                                                                                                                                                                                                                                                                                                                            | 35                               |

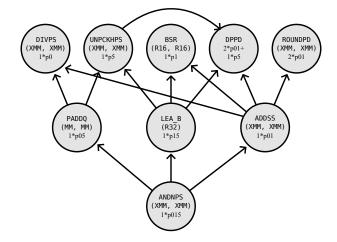

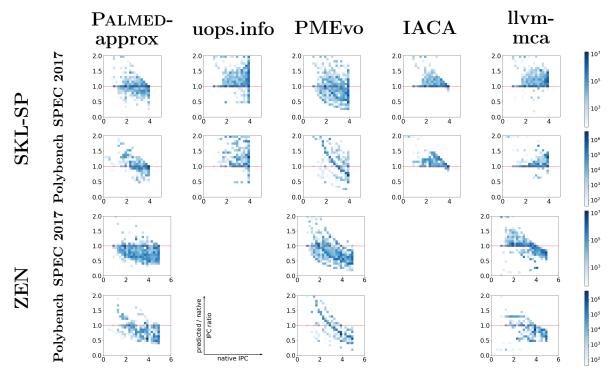

| 4.4                                                                          | between instructions                                                                                                                                                                                                                                                                                                                                                                                             | 36<br>50                         |

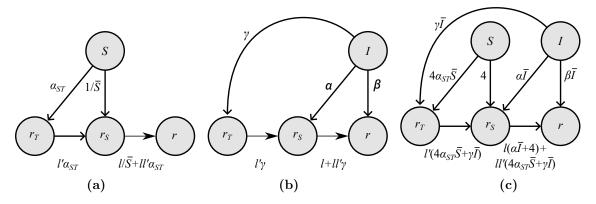

| $5.1 \\ 5.2$                                                                 | Conjunctive resource mapping (a) and its extended form (b); both normalized Saturating benchmarks $S$ and instructions to analyse $I$ : individual uses (5.2b and 5.2a), and benchmark $S^{4\cdot\overline{S}}I^{\overline{I}}$ (5.2c)                                                                                                                                                                           | 59<br>62                         |

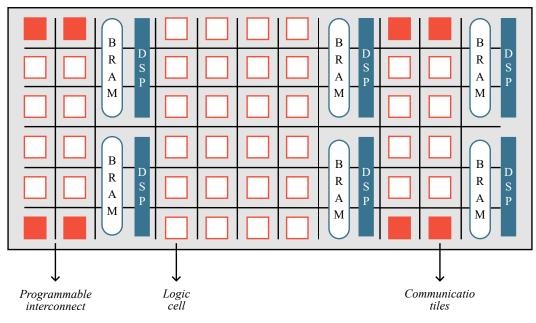

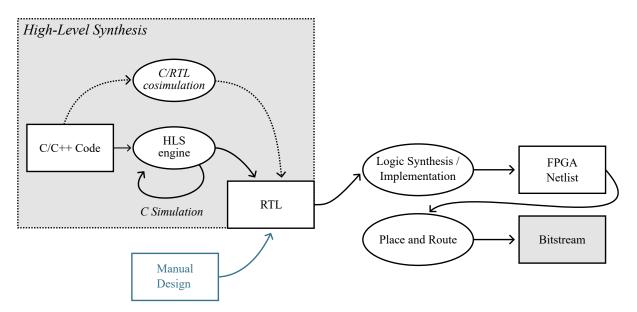

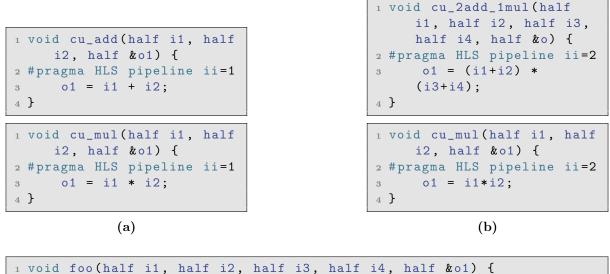

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \end{array}$ | Generic architecture of an FPGA                                                                                                                                                                                                                                                                                                                                                                                  | 68<br>70<br>72<br>73<br>74<br>75 |

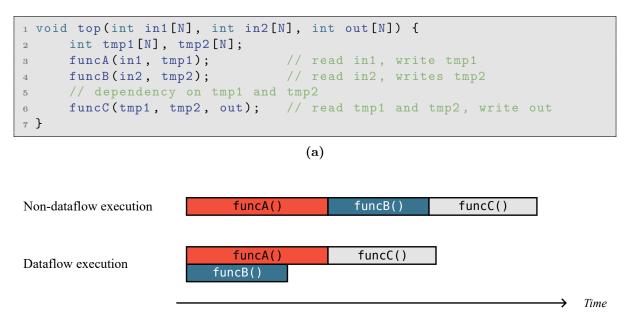

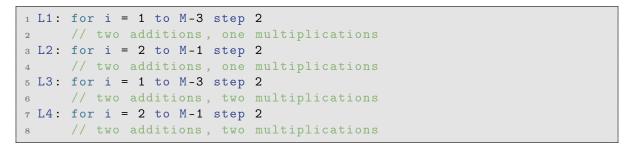

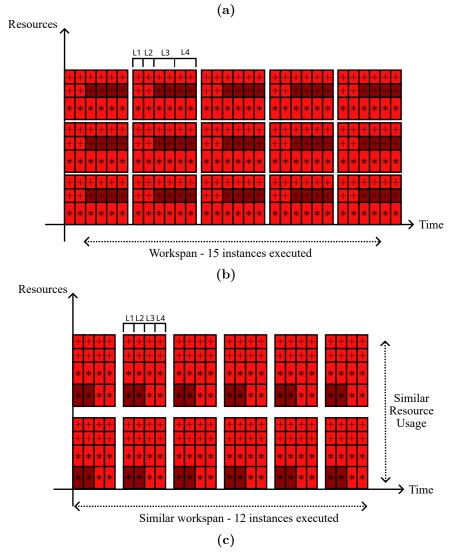

| 6.7<br>6.8                                                                   | Loops, dataflow and concurrent execution: code (a) and corresponding execu-<br>tion times with /without dataflow (b)                                                                                                                                                                                                                                                                                             | 76<br>78                         |

| 6.9                                                                          | ASAP scheduling in Vitis: operators (a) and functions (b)                                                                                                                                                                                                                                                                                                                                                        | 81                               |

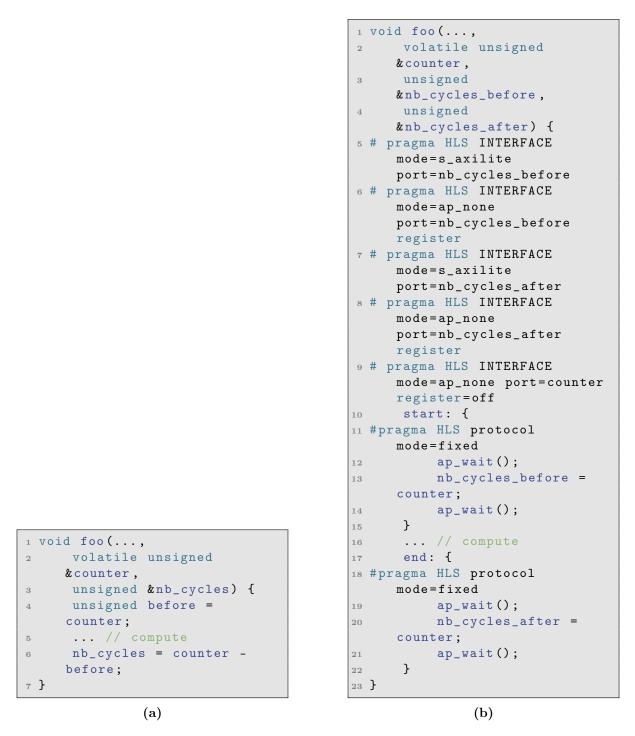

| $6.10 \\ 6.11 \\ 6.12$                                                       | Erroneous (a) and correct (b) HLS execution time measurement using an on-                                                                                                                                                                                                                                                                                                                                        | 83<br>84                         |

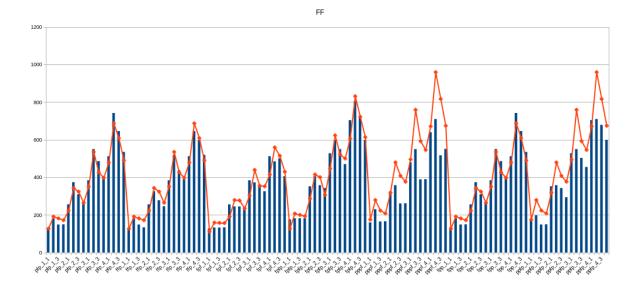

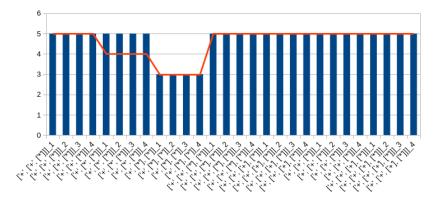

| 7.1                                                                          | chip counter                                                                                                                                                                                                                                                                                                                                                                                                     | 86<br>89                         |