## Nanocomposants émergents pour l'ingénierie neuromorphique

Fabien Alibart

#### ▶ To cite this version:

Fabien Alibart. Nanocomposants émergents pour l'ingénierie neuromorphique. Physique [physics]. Université de Lille, 2022. tel-04527992

## $\begin{array}{c} {\rm HAL~Id:~tel\text{-}04527992} \\ {\rm https://hal.science/tel\text{-}04527992v1} \end{array}$

Submitted on 31 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

UNIVERSITE DE LILLE – Ecole doctorale ENGSYS – Institut d'électronique, de microélectronique et de Nanotechnologies

# Nanocomposants émergents pour l'ingénierie neuromorphique

Mémoire présenté pour obtenir l'Habilitation à Diriger des Recherches

Spécialité: Sciences de l'information et des systemes

## Fabien Alibart 21/10/2022

#### Composition du Jury:

Pr. Kamal LMIMOUNI, Professeur des Universités, IEMN-Université de Lille

Dr. Julie GROLLIER, Directrice de Recherche, CNRS-Thales

Dr. Marie-Paule BESLAND, Directrice de Recherche, IMN-CNRS

Pr. Sylvain SAIGHI, Professeur des Universités, IMS-Université de Bordeaux

Dr. Yannick COFFINIER, Directeur de Recherche, IEMN-CNRS

Dr. Damien QUERLIOZ, Chargé de Recherche, C2N-CNRS

Dr. Dominique VUILLAUME, Directeur de Recherche, IEMN-CNRS

Président

Rapporteure Rapporteure

Rapporteur

Examinateur

Examinateur

Garant

### Table des matières

| 1.     | CHAPTER 16                                                                     |

|--------|--------------------------------------------------------------------------------|

| Neuro  | morphic computing and engineering overview6                                    |

| 1.1.   | INTRODUCTION6                                                                  |

| 1.2.   | DATA REPRESENTATION IN SNNs                                                    |

| 1.3.   | LEARNING RULES IN SNNS                                                         |

| 1.4.   | ENERGY CONSUMPTION CHALLENGES                                                  |

| 1.5.   | THE INTEGRATION CHALLENGE                                                      |

| 1.6.   | CONCLUSION: TOWARD A TRUE ARTIFICIAL INTELLIGENCE?                             |

| 2.     | CHAPTER 2                                                                      |

| 2.1.   | INTRODUCTION                                                                   |

| 2.2.   | PHYSICAL IMPLEMENTATION OF IN-MEMORY COMPUTING WITH RRAM                       |

| 2.2.1. | Background16                                                                   |

| 2.2.2. | Dot-product Precision18                                                        |

| 2.2.3. | Integration                                                                    |

| 2.2.4. | Scalability21                                                                  |

| 2.3.   | CIRCUIT DESIGN CHALLENGES FOR VMM IMPLEMENTATION25                             |

| 2.3.1. | Background                                                                     |

| 2.3.2. | Input circuits26                                                               |

| 2.3.3. | Output circuits                                                                |

| 2.3.4. | Recent chips demonstration on integrating CMOS circuits and RS devices 31      |

| 2.4.   | SYSTEM LEVEL DEVELOPMENT OF RS-BASED VMM ENGINES35                             |

| 2.4.1. | Leveraging the cost of mixed analog/digital approaches and data trafficking 35 |

| 2.4.2. | Current system-level propositions for RS-based VMM engines37                   |

| 2.5.   | CONCLUSIONS AND PERSPECTIVES41                                                 |

| 3.     | CHAPTER 3                                                                      |

| Filam  | entary switching: Synaptic plasticity through device volatility47              |

| 3.1.   | INTRODUCTION                                                                   |

| 3.2.   | RESULTS AND DISCUSSION                                                         |

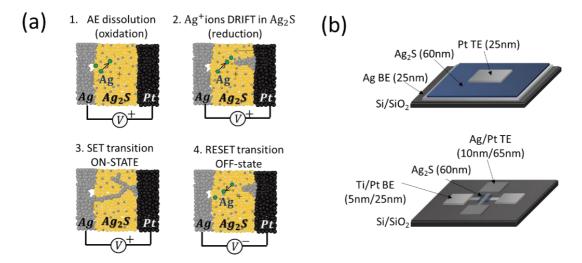

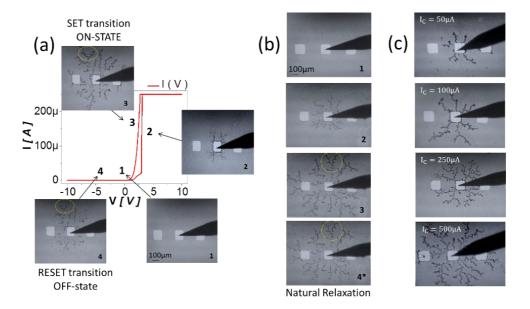

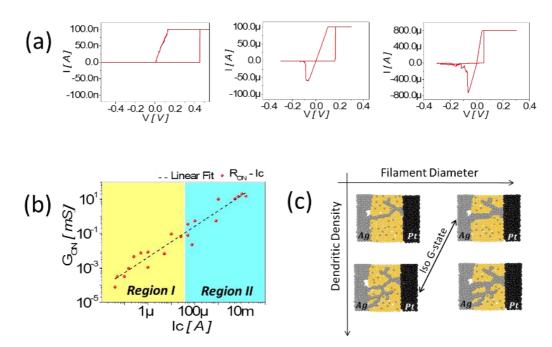

| 3.2.1. | Ag2S filamentary switching48                                                   |

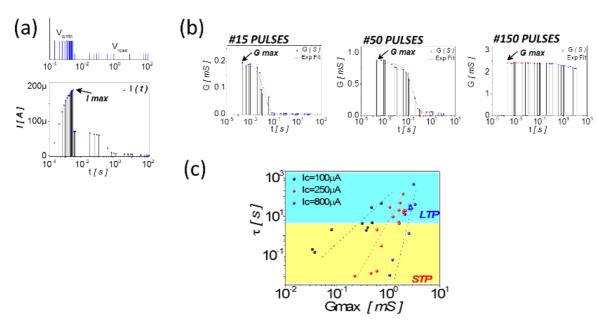

| 3.2.2. | Synaptic plasticity implementation51                                           |

| 3.2.             | DISCUSSION     | 54                                                                                  |    |

|------------------|----------------|-------------------------------------------------------------------------------------|----|

| 3.3.             | Conclusion     | JS55                                                                                |    |

| 4.               | CHAPTER 4      |                                                                                     |    |

|                  |                | e-Dependent Pattern Classification with Organic Electrochemical Transistor Array    | ys |

| 4.1.             | Introduction   | ON57                                                                                |    |

| 4.2.             | RESULTS        | 58                                                                                  |    |

| 4.2.1.           | Transie        | ent dynamics of OECTs as implicit time representation58                             |    |

| 4.2.2.           | Reservo        | oir computing: dynamical signal processing with network of OECTs 60                 |    |

| 4.2.3.           | Influenc       | ce of the number of OECT in the reservoir63                                         |    |

| 4.2.4.           | Influenc       | ce of the variability in the reservoir63                                            |    |

| 4.3.             | Conclusion     |                                                                                     |    |

| 5.               | CHAPTER 5      |                                                                                     |    |

| An ior           | o-electronic n | euromorphic interface for communication with living systems 66                      |    |

| 5.1.             | Introduction   | ON66                                                                                |    |

| 5.2.             | OBJECTIVES:    | BRINGING NEUROMORPHIC ENGINEERING AT THE INTERFACE WITH BIOLOGY                     | 68 |

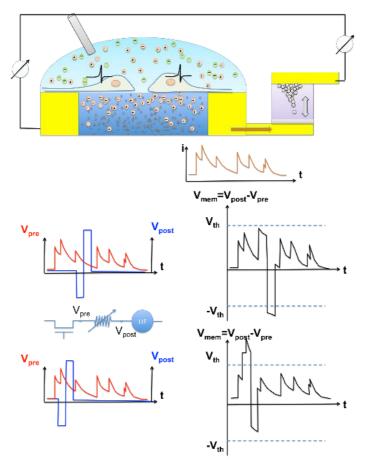

| 5.2.1.           | Objectiv       | ve 1: in-situ synaptic learning on biological signals with resistive memory devices | 68 |

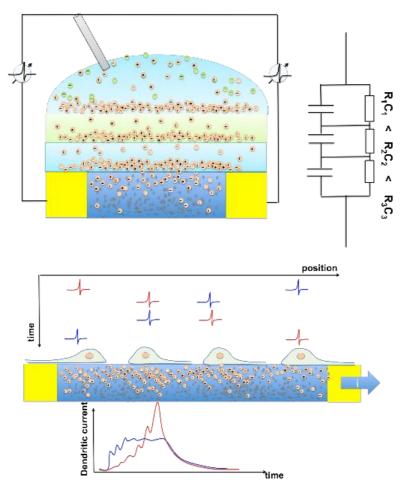

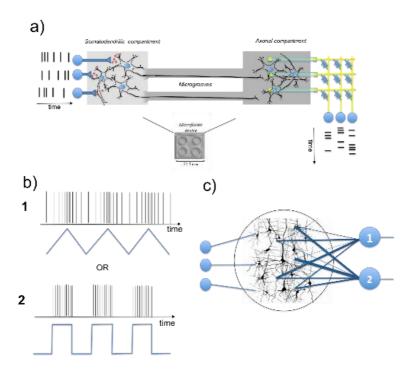

| 5.2.2.<br>actuat |                | we 2: Spatio temporal integration of the signal with dendritic sensors and synaptic |    |

| 5.2.3.           | Objectiv       | ve 3: demonstration of efficient communication on a classification task.70          |    |

| 5.3.             | BREAKTHROU     | UGH, IMPACT AND COMPLEMENTARITY WITH OTHER APPROACHES 71                            |    |

| ANNE             | XE: scientific | resume                                                                              |    |

#### Note introductive du document :

Ce manuscrit propose de présenter un résumé de mes activités de recherche couvrant la période de 2012 à 2022. Ces travaux ont été réalisés au CNRS à l'Institut d'Électronique, de Microélectronique et de Nanotechnologies depuis 2012 et au Laboratoire Nanotechnologies et Nanosystèmes de 2017 à 2020. A travers ce manuscrit, je propose d'illustrer mes travaux centrés sur l'électronique neuromorphique et ayant cherchés à étudier comment différentes technologies pouvaient être utilisées dans ce contexte. Notamment, les composants de type memristor à base de TiO2 m'ont permis une approche classique en microélectronique visant à travailler sur la montée en maturité d'un composant et son intégration au niveau circuit et systèmes pour la réalisation de puces neuromorphiques. Un deuxième volet de mes travaux s'est intéressé à utiliser des mécanismes non-conventionnels observés dans les nanotechnologies pour réaliser des fonctions innovantes en électronique neuromorphique. Ces travaux sont restés à un niveau très amont visant principalement les preuves de principe et se sont attachés à diversifier les matériaux et composants, depuis les conducteurs ioniques aux matériaux organiques et des composants mémoires aux transistors électrochimiques. Enfin, le dernier volet de mes travaux concerne une approche largement interdisciplinaire combinant plusieurs thématiques autour de l'électronique neuromorphique. Je m'intéresse à l'utilisation de concepts de traitement de l'information issus de l'électronique neuromorphique (ou bio-inspirée) pour le fonctionnement de réseaux de capteurs organiques couplés aux réseaux de neurones biologiques. Ces travaux ont été initiés depuis 2015 dans le cadre d'une collaboration avec le laboratoire JPArc (LilleNeuroCog) et sont au cœur de mon projet de recherche actuel et futur.

Le premier chapitre se présente comme un article de perspective sur l'électronique neuromorphique. Il présente un état de l'art superficiel du domaine et s'attache à identifier les grands enjeux et objectifs sous différents angles. Ce chapitre propose une analyse suivant trois axes principaux : (i) une comparaison aux réseaux de neurones artificiels, (ii) les enjeux de l'implémentation matérielle et (iii) les perspectives offertes par la biologie.

Le deuxième chapitre est un article de revue publié en 2020 qui propose une synthèse des différents enjeux liés a l'intégration des memristors sur CMOS. Au niveau applicatif, les memristors sont ici considérés pour des applications de type réseaux de neurones statiques mais les défis identifiés pour les systèmes hybrides CMOS/memristors restent valides pour l'électronique neuromorphique. Ce chapitre propose une structure classique depuis les composants, l'intégration au niveau circuit, jusqu'aux défis au niveau système. Il permet notamment de montrer que l'innovation attendue pour les systèmes de type calcul en mémoire à partir de composants memristors nécessite un travail largement interdisciplinaire allant du matériau au système de traitement de l'information. Ce travail a été réalisé principalement en collaboration avec Amirali Amirsoleimani.

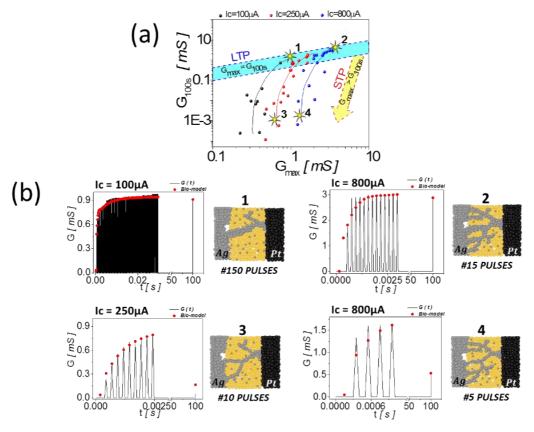

Le chapitre 3 a été publié en 2015 et couvre les travaux de thèse de Selina La Barbera. L'idée maitresse de ces travaux était d'exploiter la physique des composants mémoires filamentaires pour réaliser différentes formes de plasticité synaptique. Notamment, utiliser la volatilité de ces cellules mémoires liée à l'instabilité du filament conducteur a permis de mimer les mécanismes de plasticité court terme (STP) et long terme (LTP). Ces travaux ont été poursuivis ensuite pour étudier comment ces mécanismes pouvaient être utilisés pour réaliser des apprentissages non-supervisés.

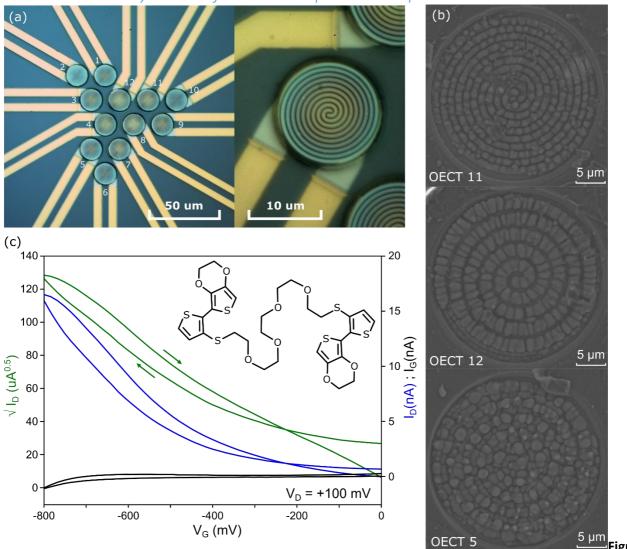

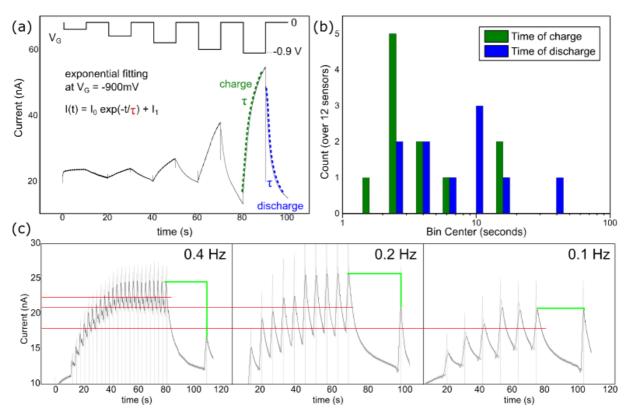

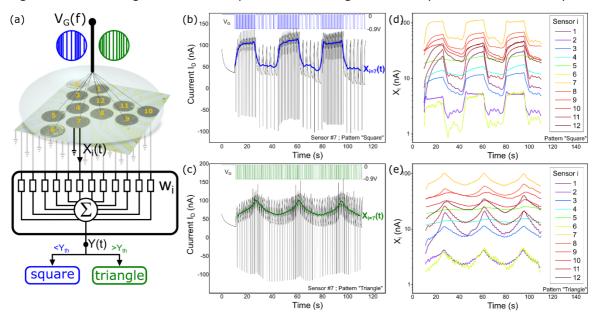

Le chapitre 4 est un article publié en 2018 montrant comment les concepts issus de l'électronique neuromorphique peuvent être utilisés dans le contexte d'un réseau de capteurs ioniques de type transistors électrochimiques. Ces travaux montrent comment la dynamique des capteurs et leur variabilité permettent d'implémenter des fonctions non-triviales de classification de signaux dynamiques. Ces travaux ont été réalisés en collaboration principalement avec Sebastien Pecqueur.

Enfin, le chapitre 5 présente mon projet de recherche qui s'intéresse à utiliser le traitement de l'information neuromorphique et bio-inspiré pour développer des interfaces innovantes aux réseaux de neurones biologiques. L'idée directrice de ces travaux et d'utiliser un paradigme de traitement de l'information le plus proche des systèmes biologiques et d'intégrer des fonctions de traitement des signaux directement au niveau de l'interface des réseaux de neurones biologiques.

### 1.CHAPTER 1

# Neuromorphic computing and engineering overview

#### 1.1. INTRODUCTION

What is really intelligence? This simple question is today stimulating multiple answers, which depend strongly on the angle used to analyze it. From a human-centered approach, intelligence is associated to the ability of human to formulate complex ideas, understand non-trivial mechanisms or planned elaborated strategies to anticipate future events. From a biological viewpoint, intelligence can appear through multiple forms such as collective behaviors in animals and vegetals, or ability to optimized resources for survival of all living species. But todays, this question is not restricted anymore to living organisms and we start to believe that intelligence could be embedded in artificial objects. The Artificial Intelligence revolution (AI), started decades ago with the first computers, offers a new substrate for researchers to tackle this question: in addition to the philosophical or biological angles, engineering is now a new domain in which intelligence could be considered. Indeed, these past years have seen impressive progresses in this direction with computers solving complex problems such as the Go game played by AlphaGo, image recognition surpassing human capacity in the ImageNet challenge or autonomous vehicles and robots evolving in real-life environment. However, this story is not only an engineering question. It is the result of the integration of multiple discoveries, from biological and computational neurosciences, computer sciences and mathematics, to material and physical sciences. Consequently, any attempt to expose how engineering is today progressing toward the development of intelligent systems should consider an interdisciplinary approach and could not be limited to the development of hardware materials.

In this chapter, we will present an overview of a specific domain that is intimately linked to Al. Neuromorphic computing and engineering (NCE), a term coined by Carver Mead in the 70s, is indeed emerging as a central aspect of AI and is bridging together multiple scientific domains. Progresses in AI have been deeply marked by machine learning in general, and Artificial Neural Networks (ANNs) in particular. ANNs, and their more recent development toward deep networks were at the origin of the second AI revolution that occurs in the 2010's. Inspired by the computing principles of the brain, ANNs rely on neurons (activation functions) and synapses (weighted connections) to compute data. They are also integrating the key ingredient of learning through mathematical models to define the synaptic weights. Neuromorphic computing is based on the same key ingredients but is using some very distinctive elements. Section 2 will present how NCE is capitalizing on spike encoding to represent information and what is the impact of this choice on data processing. Notably, spike encoding implies deep modification on the activation function of neurons, which represents a significant difference in between Spiking Neural Networks (SNNs) and ANNs. We will present in section 3 the incidences of spike coding on learning rules used in SNNs. In particular, we will expose the main learning rules used in SNNs and what are the most promising strategies. Another important distinction of NCE with machine learning is its profound connection to the hardware used to compute information. This aspect was already present in the pioneering work of Carver Mead, which considered the analogy between an ionic channel and a transistor as a foundation for NCE. This leads today to strongly hardware-oriented strategies for NCE that will be presented through two main point of view. Section 4 will put the emphasis on the energy consumption challenge that NCE is trying to solve. This energy consumption is directly linked to the hardware substrates used to implement SNNs. Section 5 will present

the challenges of integration to reach the density of components (i.e. neurons and synapses) comparable to what biology can do.

#### 1.2. DATA REPRESENTATION IN SNNs.

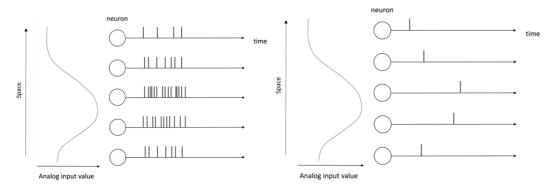

One of the major difference that we can recognize today in between ANNs and SNNs is based on the data encoding used in both approaches. In the one hand, ANNs are computing data with analog values through their layered structures. Input data can be considered as vectors  $\{x_i\} \in \mathbb{R}^n$  presented at the input layer. The synaptic conductances in between two layers corresponds to matrices  $W = (w_{ij})$ . The vector matrix operation is the essential operation realized to compute the output vector that is passed through the neurons activation function to generate the input vector of the next layer. In this sense, ANNs can be considered as frame-based operator where data are organized into series of vectors. Consequently, ANNs are clocked systems where the notion of throughput (number of operations per second) is a relevant metric. In the other hand, SNNs are encoding continuous analog information through spikes. The simplest data representation corresponds to a rate-coding scheme, i.e. the analog value of the signal carrying information (or strength of a stimuli) is associated to the average frequency of the train of pulses. The neuron can then transmit some analog signals through its mean firing rate (figure 1a). A second coding scheme is known as temporal-coding in which each individual neuron is using the timing of the spike with respect to others neurons in order to encode the signal. The first spike is carrying a strong analog value while the later ones are associated to smaller analog values (figure 1b). Both coding schemes are used to encode continuous signals, at the opposite to "frame-based" ANNs. It is to note that spike coding raises an important issues for data representation. Both rate-based and time-based are somehow ubiquitous in real spiking signals, but moving from one representation to the other is not straightforward. It turns out that an alternative description of the spike encoding that could describe both strategies would be to consider a probability of spikes. Quantum physics theory, where both the time and localization of a particle cannot be known at the same time, but only its probability of presence, is an interesting analogy.

Figure 1: (a) Rate-based representation of analog signals. (b) Time-based representation of analog signals

In SNNs, spikes are discrete events, which could be associated to a digital value (i.e. "0" or "1"). Their temporal organization is carrying the analog features of the signal. In order to decode this analog information, neurons rely on the integration of the spikes. Various neurons models are used for NCE, with Leaky Integrate and Fire (LIF) being the most popular [2]. Each incoming spike contributes to increase the membrane potential of the neuron ( $V_{mem}$ ).  $V_{mem}$  tends to leak with a given time constant. When the potential  $V_{mem}$  exceeds a threshold, the neuron fires an output spike and the membrane potential is reset to its resting state. This mechanism means that the neuron in itself is responsible for holding in its membrane potential part of the analog information (at least until  $V_{mem}$  leaks completely or a spike is emitted). This mechanism is often associated to a memory effect of the neuron. To some extends, an additionnal memory effect, which we describe here as the trace of the information in the network, can be identified through the recurrent connections and the delay of propagation. When propagating in the network and finally coming back to the

same place, a spike can "live" in a local point (i.e. a specific neuron) for a given duration. These considerations are used here to highlight a major difference in between ANNs and SNNs operation, which is intimately linked to the data representation. ANNs are data-driven system where static neurons and synapses compute the analog signals, only data are modified (this holds for inference only, not learning obviously). At the opposite, in SNNs, data are represented *in* the network through the combination of various dynamics of the elements that compose the SNNs. This representation of data (i.e. data are *in* the computing elements) is a major departure from the traditional way of considering data processing.

The spike encoding is an essential aspect that is limiting the development of SNNs. The conservative way of dealing with data processing is to consider data from sensors separately from the computing elements. However, as pointed out by H. Barlow 60 years ago [3]: "it is foolish to investigate sensory mechanisms blindly—one must also look at the ways in which animals make use of their senses". In other words, the way data are encoded at the sensory level cannot be separated from the higher computing levels. Along this line, developing SNNs for processing requires converting analog sensory signals into spikes. This analog-to-spike conversion is often under considered but is in fact a critical element of the processing itself. During the spike conversion, either the totality of the signal is converted or features from the signal can be enhanced or suppressed in order to convey only the meaningful part of information. For example, the simplest data conversion is to convert an analog signal into a train of spikes following the rate-coding strategy. In this technic, the limitation is mostly on the sampling of the analog signal since a minimal interval is required to define a mean frequency, but all information is transmitted without discrimination. More elaborated spike conversion are considering a more event-driven conversion by associating a spike to an apriori important aspect of the signal such as a change in intensity (see for example BSA technic [4]). The latest progresses in this direction are now trying to develop finer features extraction such as in sparse coding strategies where filters of features need to be learn from the signal based on relevant criterion such as performances and sparsity.

Ultimately, NCE needs to consider not only SNN for processing but also the sensory elements of the circuit [5]. In this direction, the most significant achievements have been done with event-based camera that are emulating vision. The same bio-inspired approach has been applied to artificial cochlea implementation for sound processing. There is still lots of room for innovation in this domain if we think about the different sensory modalities used by living species to interact with their environment or to the large amount of sensors that are currently deployed on various Edge Computing applications.

Nevertheless, NCE is maybe somehow overestimating the importance of spikes. Analysis of electrophysiological signals reveals that signals in the brain present complex components such as subthreshold membrane potentials changes, collective Local Field Potential (LFP) resulting from the synchrony of populations of cells, or low frequency oscillations that are carrying an important part of the information (at least for some specific tasks). These different data representation are not integrated in current SNNs that are considering the spikes as the quantum of information. More recent progresses in biological neurosciences are now putting the emphasis on the role of additional elements to neurons to process / transmit information. The example of the tri-partite synapse where the astrocyte supervised the synaptic activity is a striking example of this issue. This could be extended further to the role of multiple chemical such as hormones in the way information is represented and processed in biological networks. The question that needs to be answered is: "is the spike enough to reproduce the complexity and performances of biological brains?"

#### 1.3. LEARNING RULES IN SNNs

One of the keys of success of ANNs, and deep network in particular, is the backpropagation of error algorithm (backprop). Nevertheless, backprop required to be able to differentiate the activation function of neurons to compute the synaptic weights modification. Since spiking neurons are non-differentiable functions, backprop cannot be directly transposed to SNNs. Until recently, this made deep SNNs (i.e. multilayer) and recurrent SNNs hard to train and was preventing SNNs to reach equivalent performances as

deep networks. Several strategies have started to emerge and were proposing alternative to make SNNs compatible with backprop algorithms. The key idea here is to find some equivalent technic to compute the gradient descent, which involves differentiating the neuron activation function. Smoothing of the activation functions or surrogate functions to the gradient are very attracting options that have demonstrated equivalent performances of multi-layer SNNs with their equivalent ANNs. Nevertheless, these technics are approximation of gradient descent technics and are unlikely to bring SNNs above ANNs performances [6].

A very distinctive aspect of NCE with ANNs for learning is to consider more bio-inspired learning rules. A very famous example is the proposition of Spike Timing Dependent Plasticity (STDP). STDP is a variation around the seminal Hebb's idea of "who fire together, wire together" and was identified in biology. Spike timing is used to define correlation in between a pre and post-neuron (pre fires before post) and anticorrelation (post fires before pre). The correlation (anti-correlation) of activity is used to define weight potentiation (depression) during learning. A key aspect of STDP, which is not present in ANNs, is to propose a local learning rule (i.e. weight modification depends only on pre and post-neuron activity). This is highly desirable from a hardware perspective since it could enable the development of massively parallel hardware substrates where information doesn't need to travel extensively in between computing nodes. At the opposite, backprop suffers from the spatial credit assignement issue, which consists in the problem of calculating the weight modification based on some loss function calculated at the output of the network and to retro-propagate this error across it. Nevertheless, STDP was limited until recently to single layers SNNs and was not adapted to deep SNNs. A direct consequence was a poor level of performances with respect to ANNs. There has been recently some breakthroughs along this line with the proposition of neo-hebbian learning rules [7]. In these extensions of Hebb's rule, a third factor is added to the standard two factors (e.g. pre-neuron activity and post-neuron activity in STDP) and result in three-factor learning rules. For example, an additional learning signal to the STDP can be used to indicate how much the local learning is useful with respect to an objective function describing the network performances. This strategy, even if trading-off the locality of learning, was able to demonstrate high performances of multi-layer SNNs and could be a game changer in the development of deep SNNs.

From a different angle, important progresses has been realized recently toward high performances SNNs. In these approaches, the key idea is to find a way to calculate the error of the network based on local information only. In other words, the the idea is to calculate locally the backprop signal. Equilibrium propagation (eq-prop) corresponds to an energy-based model of the network and was used to derive a learning rule, which was able to backpropagate the error [8]. In eq-prop, error retro-propagation is based on two main ingredients. Weights modification is associated to a local term that depends on the local activity of the pre and post neuron, and on a global term describing the network performances. This approach is again promoting locality with respect to standard backprop algorithm. The local learning term was also demonstrated to be equivalent to some extend to STDP. Note that this proposition belongs to a broader stream that tends to bring ideas from ANNs to SNNs [9]. A second promising direction was also proposed for recurrent SNNs. Eligibility propagation (e-prop) is proposing to define learning based on a local learning term and some eligibility traces that are indicating to the network "when to learn" based on the global objective function to implement [10]. E-prop have shown equivalent performances to LSTM ANNs, which are one of the most widely used recurrent ANNs network. While important differences exist in between eg-prop and eprop, both are offering new perspective for deep SNNs deployment since locality of learning is preserved to some extend and could be deployed on massively parallel hardware substrates.

Biology is also pointing toward a combination of local / global learning in neural network [11]. An example of this idea is the tri-partite synapse. In this synaptic model, learning depends in addition to pre and post-synaptic factors (e.g. spike activity, membrane potential,...) on the astrocyte signal that is supervising the actual learning. Astrocytes are non-spiking cells that are known to regulate calcium ions concentration (among other functions) across multiple neuronal cells. Through this calcium regulation, learning can be strengthened or weakened. Other evidence coming from biology are also strengthening the combination of local and global effects. For instance, dopamine release during learning has been demonstrated to be a

reward signal triggering synaptic plasticity. All these elements can find analogy to some extend to the previously mentioned learning rules. But it is to note that these mechanisms are involving complex spatial and temporal dynamics during learning that are making bio-realist learning algorithms hard to define.

#### 1.4. ENERGY CONSUMPTION CHALLENGES

Energy consumption remains a major challenge for the development of AI. If ANNs algorithms have demonstrated attractive performances for various tasks, their deployment on edge applications that requires strong constraints on the hardware energy budget is still limited. ANNs are indeed data intensive systems that require massive exchange of information in between the computing nodes and the off-chip memory (these signals could be either input data or models parameters such as synaptic weights). Conventionnal hardware are mostly using DRAM memory to store data and parameters and most of the energy is dissipated through data movement in between the different element of the system. Note that this statement applies for both conventional CPU and GPU, even if the later is allowing for higher throughput (throughput being the number of operations per second, TOPS). To this end, in-memory computing (IMC) has attracted a deep interest to reduce energy consumption associated to data movement [12]. IMC is intimately linked to the hardware concept of embedded memory where the physical devices for memory are integrated along with the CMOS computing elements, thus limiting the physical distance of data movements. If IMC could be realized with various technologies (embedded DRAM, SRAM, for instance), a very attractive option is to used resistive memory technologies (RRAM or memristors). In this approach, memristors are used to implement synaptic weights and the Kirchoff's laws are used to realize the key operation of dot product (note that dot products, vector matrix multiplication and Multiply And ACcumulate are essentially the same basic operation). Benefits of this approach are two sides: (i) IMC of dot product allows for reduce latency since the operation could be realized in principle in a single time step and, (ii) data movement is limited thanks to onchip synaptic weight. This later aspect is of first interest for implementation of on-chip learning strategies. Note that the dot product operation in itself doesn't present a significant interest in term of energy with todays technologies since memristors require to sink a significant current during writing and reading. But if IMC with memristor is still a very active research direction for ANNs implementation that could enable high throughput with low energy (TOPS/W), challenges still exisits regarding the variability of memristors, which makes them good candidates for low accuracy computing, but less attractive for conventional backprop algorithms requiring high accuracy weight updates during gradient descent.

Innovative hardware (i.e. IMC) are partially solving the energy consumption issue of ANNs but power consumption of biological systems seems still out of reach. Note that this applies for both ANNs and SNNs. Nevertheless, SNNs are pointing toward the possibility of better energy performances with respect to ANNs thanks to their distinctive data representation. Spike encoding of information is pointing toward a very efficient way of computing information if spatial and temporal sparsity is obtained. Spatial sparsity corresponds to a good distribution of the information along the different nodes of the network. Temporal sparsity corresponds to a representation of signals with as few spikes as possible. Both spatial and temporal sparsity are also favored by encoding only the essential part of the signal. For instance, when computing ANNs models involves dense vector matrix operation at each "frame" of the signal, SNNs are distributing over time the same operation, thus limiting instantaneous power consumption. A second aspect that spike computing seems to offer is the ability to compute with low accuracy and large noise, while preserving efficient performances. Indeed, biological networks are using 2-3 bits resolution for synapses and their signal to noise ratio are well behind the requirements of digital technologies. In term of energy, this have a direct impact since accuracy in electronic systems comes at the price of higher energy consumption and higher latencies.

From a hardware perspective, biology is also pointing toward key differences with current approaches. An interesting example is to compare the subthreshold voltage slope used by ionic channels in comparison to transistors channel in the seminal work of Carver Mead [13]. This important difference could be explain to some extend by multiple aspects. (i) Biology is using various carriers of information, and in particular ions, for computing. For instance, divalent ions are reducing by a factor of two the energy required to overcome the thermal barrier used for charge separation in a physical systems (this Boltzmann limit in transistor corresponds directly to the subthreshold voltage slope of about 60 mV in transitors). (ii) Electronic systems are relying on fast moving and confined electrons through drift and diffusion, which implies important Joule effects. At the opposite, biology is based on slow motion of ions in a dilute conductor (i.e. the electrolyte) mostly driven by diffusion. (iii) Separation of charges in biology doesn't rely solely on electrostatic effects but also employs mechanical components such as ionic pumps. These elements suggests that reaching the energy performances of biology with current approaches would require rethinking profoundly the choice of substrate used for computing.

#### 1.5. THE INTEGRATION CHALLENGE

In 2010, the Synapse project proposed a roadmap for the development of brain-inspired hardware. The most critical metric was the synaptic connection since density of synapses is around 10000 times larger than neurons. They estimated the footprint of an electronic synapse to be 100 nm². Such ultimate footprint would ensure ultra-high integration of synaptic elements to match what is observed in the brain. Memristors have been strongly considered to fill this requirement since sub-5 nm devices has been demonstrated (note that flash technology scaling has been stopped at the 28 nm node). In addition to ultra-small footprint, memristor in its simplest version is also compatible with crossbar integration scheme, which could allow for high-density integration. Nevertheless, passive crossbar (i.e. memristor are integrated at the crosspoint of two metal wires without selector) have faced several challenges that still need to be answered. The most critical ones are crosstalk effects (i.e. undesired programming of adjacent memristors during writing of a specific one) and mismatch of the crossbar wires impedance with the memristors. This later effect worsen when scaling the crossbar dimensions and would require important effort at the technological level to decrease wire resistance and increase memristor resistance.

Another important limitation to high-density integration of memristor appears to be the complexity of the overhead circuitry required to drive the memristor elements. This overhead increase when writing scheme of the memristors becomes more complex, in particular during learning of the synaptic weights. It appears today that 1T1R integration is favored to solve the crosstalk issue. But integrating complex writing schemes to implement synaptic plasticity are requiring 2T1R for STDP implementation, and up to 6T2R1C for backpropagation [14]. A very attractive option to limit this increased footprint associated to the writing circuitry is to rely on the physics of memristor technologies to implement locally various plasticity rules and synaptic mechanisms. For instance, various drawbacks of conventional memories such as retention or stochastic switching could be turn into advantages to reproduce synaptic effects during learning and operation.

An additional difficulty associated with integration density in ANNs and SNNs is the interconnection of the different nodes in a parallel manner. Since conventional CMOS technologies are bounded to a 2D integration of the transistors, important interconnects in the middle-end of line are required. This constraint is pointing toward the necessity of 3D integration of computing elements, and in particular of the synaptic connections. There is a true potential to integrate memristors in 3D but this objective will require important technological efforts.

A more fundamental limitation in the development of computing substrates that could match the requirements of high density of neurons and synapses in ANNs and SNNs is the top-down approach imposed by conventional technologies. If general-purpose computers are offering a large abstraction between the

algorithms and the physical substrates, the development of neuromorphic circuits is creating a strong link in between both. It means that the complexity of the algorithm (number of nodes and parameters) is directly mapped on the physical substrate used for computing and need to be known before fabrication. Even if sparse networks are obtained after learning by using pruning technics for example, the initial network topology needs to be over-estimated in order to enable learning. Definition of the optimal topologies that could be used without trading too much on the flexibility is a very important question that is only partially answered today. At the opposite, biological networks are using relaxed device dimensions (i.e. neurons are about 30 um and synapses are 100-200 nm). However, they evolved following a bottom-up strategy, which implies that material resources are created when required and are used very efficiently. This aspect, in addition to the truly 3D integration of the brain could be a key ingredient that technology would need to reproduce in order to reach the level of performances of its biological counterparts.

#### 1.6. CONCLUSION: TOWARD A TRUE ARTIFICIAL INTELLIGENCE?

NCE appears as a promising solution to bring current AI toward its next generation. The first practical aspect of bringing AI to the next level is to unlock the energy consumption challenge. This could result in the deployment of AI on a variety of embedded applications near sensors, which are regrouped into the class of edge computing applications. Having intelligent computing embedded on portable devices will reduce the bottleneck of data exchange to / from the cloud and its (often not displayed) related energy consumption. This aspect is two sides since it will reduce the energy sink of large data centers and reduce the pressure on the battery lifetime of portable devices. From the previous elements describe above, we see that the main vector for this "AI revolution" is based on hardware innovation that NCE is promoting thanks to its strong roots with hardware physics and on how moving from bio-inspired observations to hardware implementations. Nevertheless, reaching this goal needs to approach the problem globaly and to consider both data encoding (section 1.2), learning (section 1.3), energy consumption at the device (section 1.4) and system level (section 1.5).

But there is also a more profound impact of NCE on the future of AI. Today, ANNs are currently surpassing all other approaches in terms of performances for a large variety of AI tasks. This is suggesting that there is not a real need in innovation in computing, but continuous scaling of ANNs could be enough to sustain the deployment of AI. Nevertheless, ANNs are still not convincing on their ability to promote a "real" intelligence. It seems that some ingredients to engineer intelligence on hardware systems are still missing. This requires of course to define what can be considered an intelligent behavior, and to have some metrics to compare the performances of a deep network with the one of a sea cucumber or a fly. NCE is holding some promises to this end since it could promote a truly interdisciplinary research at the frontiers in between biology, neurosciences, computer science, and electrical engineering. This interdisciplinary approach could help us progressing toward the understanding of data representation in the brain (section 1.2), learning (section 1.3) and biological wetware principles (sections 1.4 and 1.5). If it is hard to identify a safe methodology toward this goal, an engineering approach would certainly benefit from material integration of the different NCE concepts toward embodiment of AI on hardware that could integrate every levels from sensing to computing. This should require sustained efforts on neuromorphic sensors development, online (even continual) learning circuits and autonomous computing systems deployment.

<sup>[1]</sup> LA BARBERA, Selina, ALIBART, Fabien. Synaptic plasticity with memristive nanodevices. In: *Advances in Neuromorphic Hardware Exploiting Emerging Nanoscale Devices*. Springer, New Delhi, 2017. p. 17-43.

[2] BRUNEL, Nicolas. Modeling point neurons: From Hodgkin-Huxley to integrate-and-fire. *Computational modeling methods for neuroscientists*, 2010, p. 161-185.

- [3] BARLOW, Horace B., et al. Possible principles underlying the transformation of sensory messages. *Sensory communication*, 1961, vol. 1, no 01.

- [4] SCHRAUWEN, Benjamin et VAN CAMPENHOUT, Jan. BSA, a fast and accurate spike train encoding scheme. In: *Proceedings of the International Joint Conference on Neural Networks, 2003.* IEEE, 2003. p. 2825-2830.

- [5] LIU, Shih-Chii et DELBRUCK, Tobi. Neuromorphic sensory systems. *Current opinion in neurobiology*, vol. 20, no 3, p. 288-295 (2010)

- [6] NEFTCI, Emre O., MOSTAFA, Hesham, et ZENKE, Friedemann. Surrogate gradient learning in spiking neural networks: Bringing the power of gradient-based optimization to spiking neural networks. *IEEE Signal Processing Magazine*, 2019, vol. 36, no 6, p. 51-63.

- [7] GERSTNER, Wulfram, LEHMANN, Marco, LIAKONI, Vasiliki, et al. Eligibility traces and plasticity on behavioral time scales: experimental support of neohebbian three-factor learning rules. Frontiers in neural circuits, 2018, vol. 12, p. 53.

- [8] SCELLIER, Benjamin et BENGIO, Yoshua. Equilibrium propagation: Bridging the gap between energy-based models and backpropagation. *Frontiers in computational neuroscience*, 2017, vol. 11, p. 24.

- [9] LILLICRAP, Timothy P., SANTORO, Adam, MARRIS, Luke, et al. Backpropagation and the brain. Nature Reviews Neuroscience, 2020, vol. 21, no 6, p. 335-346.

- [10] BELLEC, Guillaume, SCHERR, Franz, SUBRAMONEY, Anand, et al. A solution to the learning dilemma for recurrent networks of spiking neurons. *Nature communications*, 2020, vol. 11, no 1, p. 1-15.

- [11] ROELFSEMA, Pieter R. et HOLTMAAT, Anthony. Control of synaptic plasticity in deep cortical networks. *Nature Reviews Neuroscience*, 2018, vol. 19, no 3, p. 166-180.

- [12] Sze, V., Chen, Y.-H., Emer, J., Suleiman, A. & Zhang, Z. Hardware for machine learning: Challenges and opportunities. In 2017 IEEE Custom Integrated Circuits Conference (CICC), 1–8 (IEEE, 2017).

- [13] MEAD, Carver. Neuromorphic electronic systems. Proceedings of the IEEE, vol. 78, no 10, p. 1629-1636 (1990)

- [14] IELMINI, Daniele et AMBROGIO, Stefano. Emerging neuromorphic devices. *Nanotechnology*, 2019, vol. 31, no 9, p. 092001.

### 2.CHAPTER 2

In-Memory Vector-Matrix Multiplication in Monolithic CMOS-Memristor Integrated Circuits: Design Choices, Challenges, and Perspectives

#### 2.1. Introduction

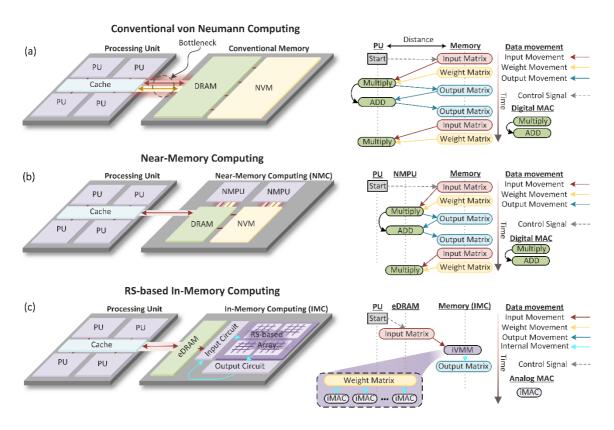

The semiconductor technology sector, and particularly its research core, are currently undergoing fundamental changes. After decades of predictable evolution based on the strategy relying on CMOS scaling<sup>1</sup> yielding incremental processor performance improvements, new solutions are required<sup>2</sup>. The first driving force for this revolution is energy consumption, which remains a major challenge for the ubiquitous deployment of electronic chips on an ever-increasing number of devices<sup>3</sup>. Solving this challenge would enable both: the integration of more computing functions on a variety of portable miniaturized devices with demanding energy/form-factor constraints, and more generally, conserving the total energy required to power billions of electronic devices. The second driving force is the massive deployment of artificial intelligence (AI) in our everyday life, which is redefining the basic principles of the hardware architecture required for computing. In particular, von Neumann computing architecture<sup>4</sup> is not well adapted to machine learning (ML) implementation, which is a main vector for the widespread adoption of Al. Indeed, implementations of ML algorithms on standard CPUs are typically inefficient in term of speed due to the constant dataflow between arithmetic units (AUs) and the memory, limited by the von Neumann bottleneck. There is consequently an important need to improve computing efficiency from both an energy consumption and throughput perspective. To this end, hardware innovation is expected to play a major role by offering viable solutions to sustain the deployment of electronics.

Specialized hardware such as GPUs<sup>5</sup>, which are highly parallelized versions of classical von Neumann CPUs, have been game changers in the acceleration of ML. However, they are offering only a partial solution to the speed and energy challenges. More precisely, GPUs are a first step toward hardware specialization where the key operation of Multiply and Accumulate (MAC) has been parallelized in order to offer important speed improvements. Since MAC operation represents the most intensive calculation required for ML algorithm implementation, it explains why GPUs have led to important breakthroughs in acceleration of ML by enabling training and operation of deep neural networks<sup>6</sup> in a reasonable amount of time. But parallelization solely cannot solve the energy challenge for two reasons: (i) intensive data movement between the different physical elements of the hardware results in important energy consumption (i.e. data movement between on-chip memory and AU, but also data movement in between the different on-chip and off-chip memory level) <sup>7</sup>; (ii) as in

CPU, the fundamental algorithmic operation is still realized with the same elementary logical operations, which require the same energy budget.

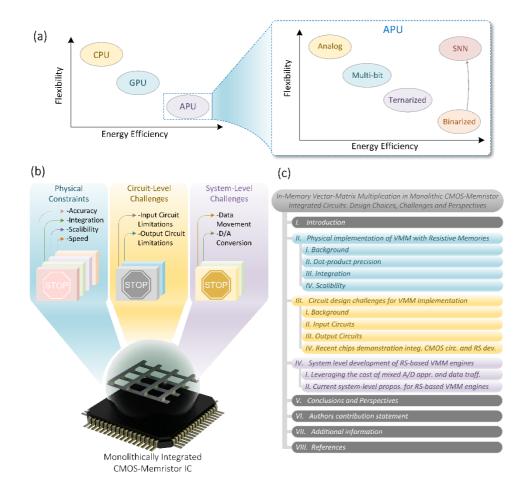

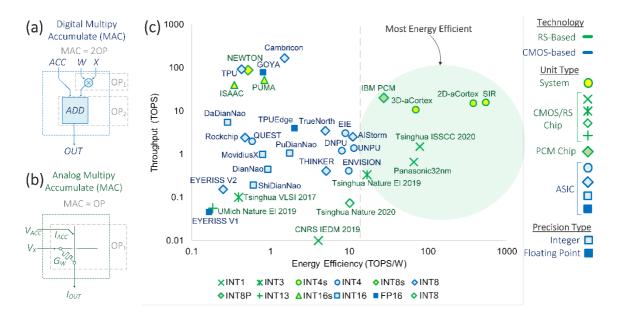

Improving both energy and speed requires to rethink more deeply hardware design principles and prudently explore emerging computing technologies. Along this line, more advanced solutions exploit hardware specialization even further and propose to design application processing units (APUs), which optimize the throughput and energy requirement for a specific application (Figure 1(a)). In these approaches, innovation is more supported by hardware diversification and specialization, rather than by software innovation to make a balance between their functional flexibility and performance <sup>2</sup>. By deploying hardware specialization, there have been several low power research chips, data center chips and cards proposed in addition to recent advancements in CPUs and GPU-based neural engines. However, it should be noted that reaching an end-to-end solution for an efficient hardware will require scrutinizing other computing paradigms and technologies. In this context, in-memory computing architectures enable efficient computing with negligible data movement by co-locating memory and processing unit. This path has been explored with various technological solutions, from mainstream SRAM and DRAM to more emerging ones such as eDRAM 8. Beyond charge-based digital memory technologies, in-memory computing based on non-volatile resistive switching devices (RS) monolithically integrated on CMOS is opening new perspectives for ultra-efficient MAC operation engine development <sup>9</sup>. Firstly, monolithic integration of memory in close vicinity of logical units reduces significantly the distance for data trafficking, and thus should reduce energy consumption and throughput limitation<sup>9-11</sup>. Secondly, in-memory computing represents a new physical implementation of the basic MAC operation with potential for important improvements with respect to the same criterions.

In this paper, we aim to review the main limitations and opportunities of in-memory computing with resistive memories for MAC operation engine, also known as Vector Matrix Multiplication engine (VMM engine). On this basis, as shown in Figure 1(b), the challenges hindering toward the path of monolithically integrated resistive memory and CMOS VMM engines to become a mainstream hardware have been categorized into three different levels: physical constraints, circuit-level challenges and system-level challenges. Initially, we define the main issues corresponding to physical limitations of this specific class of hardware e.g. accuracy, integration, scalability and speed. Subsequently, we assess the circuit-level challenges and analysed the input and output circuit design costs and opportunities. Finally, system-level obstacles such as data movement and data conversion issue have been discussed. Also, we propose a rational analysis of such APUs performance and their trade-offs in the context of ML applications, but the same reasoning could be applied to a wider range of applications <sup>12</sup> such as image processing <sup>13,14</sup>, combinatorial optimization <sup>15-19</sup>, sparse coding <sup>20,21</sup>, associative memory <sup>22-26</sup>, deep learning inference/training <sup>27-30</sup>, unclonable functions <sup>31-34</sup>, principle component analysis 35,36, spiking neural networks 37-41, solving linear 42, and partial differential equations <sup>43</sup> and reservoir computing <sup>44-46</sup>. Our intent is to provide a comprehensive analysis to assess the novelty of the reviewed examples and discuss different design choices to better understand this emerging class of hardware and to rationalize performances evaluation.

Figure 1: Different computing hardware performance overview and challenges and limitations hindering the path toward of monolithic <u>CMOS-memristor VMM</u> integrated circuits to become mainstream AI hardware. (a) Here, a simple view of <u>APU platform's</u> energy efficiency performance and its flexibility in terms of application range is compared with conventional platforms like <u>CPUs</u> and <u>GPUs</u>. Different RS-based <u>APU</u> classes with low to high resolution weight networks are displayed in terms of energy efficiency and application spectrum flexibility. At the opposite to the trade-off between flexibility and energy that current hardware are experiencing, Spiking Neural Networks (<u>SNN</u>) observed in biology combine both flexibility and low energy consumption. Finding the keys for this implementation seems a disruptive direction for future hardware design. (b) The challenge has been divided into three different categories: physical constraints, circuit-level challenges and system-level challenges. (c) Manuscript's tree structure.

#### 2.2. Physical implementation of In-Memory computing with RRAM

#### 2.2.1. Background

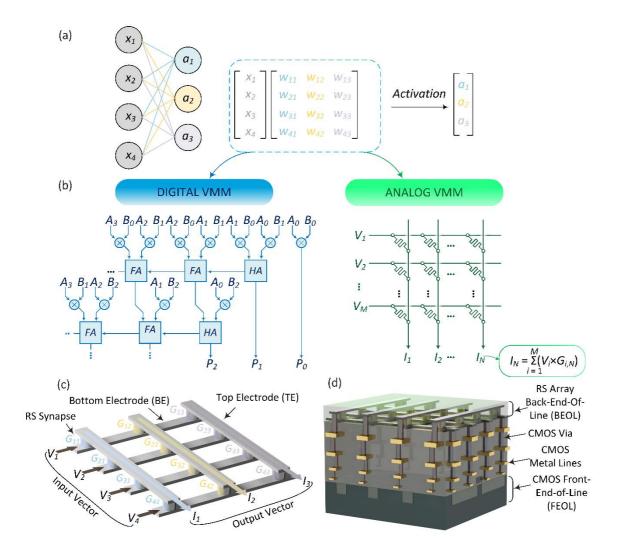

VMM is the main operation module required to implement neural network structure (Figure 2(a)). The first basic function required for VMM physical implementation is the multiplication between two real numbers a and b ( $a \times b = c$ ). In digital logic, multiplication is realized by pipelining multiple full-adders (Figure 2(b)). The precision of the multiplication is defined by the digital representation of the real numbers (number of bits, floating/fixed point). Resistive memory on the other hand offers a new concept for implementing multiplication leveraging Ohm's law where the current I is equal to voltage V multiplied by conductance G ( $V \times G = I$ ) (Figure 2(b-c)). The advantages of this approach are two-fold: (i) only a single time step is required to compute the multiplication versus multiple time steps in digital implementation and (ii) energy consumption is considerably lower.

Projected resistive memories performance for an average resistance of R=1 MOhm, read voltage of 0.1 V with pulse duration of 1 ns, the energy consumption equals  $E_1=0.1\times 10^{-7}\times 10^{-9}=10^{-17}$  J. Note that with todays performances, the energy calculation should consider R=10-100 kOhms, V=0.1 V and t=1 µs leading to  $E_2=0.1\times 10^{-5/-6}\times 10^{-6}=10^{-12/-13}$  J. These energy consumption should be compared with 8-bit digital multiplication of  $E_3=0.2$  pJ with 45 nm CMOS technology node~\cite{horowitz20141} pointing out the important gain attainable only if resistive memory improvement is sustained.

The second basic operation required by VMM is the addition. While this operation is carried out by adders in digital electronics, this can also be implemented physically in the analog domain by summing all currents resulting from each multiplicative element in a shared metal line (Kirchoff's law). This strategy shows a clear advantage for speed improvement due to its highly parallel manner as the Add operations are carried out within multiple parallel channels of the crossbar simultaneously in a single clock cycle with the multiplications. For the sake of comparison, one 8-bit full-adder uses approximately 200 gates in conventional CMOS design and requires number of computing cycles proportional to the Add operation precision. These two basic multiplication and addition operations correspond to the fundamental MAC operation or dot-product, which constitutes the core of VMM.

While this qualitative analysis highlights the advantages in terms of speed and energy consumption of in-memory computing for VMM engine implementation, a fair comparison with digital CMOS technology is more complex and limitations start to appear due to non-ideal parameters such as physical constraints, overhead circuit design and system level operation.

Figure 2: (a) A basic neural network structure is shown including input vector, weight matrix and output vector. (b) Schematic of the digital and analog vector matrix multiplication and their implementations. VMM digital implementation is realized by pipelining multiple adder and multiplier digital blocks. Analog VMM on  $M \times N$  RS-based crossbar is realized by summing currents from M lines in N columns. (c) The physical implementation of RS-based VMM engine shows input vector is applied as a voltage vector into the world-line of the array (bottom electrode), weight matrix is stored on RS device conductance and output is sensed as accumulated current in the bit-line (top electrode). (d) 3D illustration of RS-based crossbar monolithically integrated on top of the CMOS using back-end-of-line (BEOL).

#### 2.2.2. Dot-product Precision

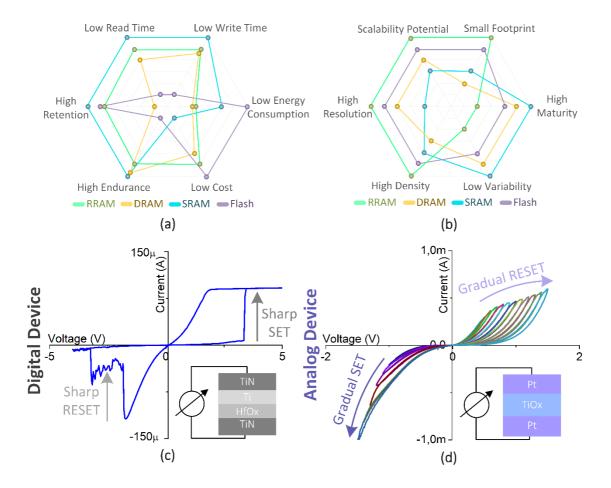

Resistive switching (RS) devices have been developed following two main research directions. On the one hand, resistive switching mechanism has been investigated as a potential solution for the development of a universal memory. This kind of binary memory, called Resistive Random Access Memory (RRAM), could combine high switching speed (sub-ns), low energy (pJ range) and high endurance (10<sup>12</sup> cycles) of DRAM and SRAM with non-volatility (>10 years retention) and scalability (<10 nm) (Figure 3(a-b)). Various RRAM cell candidates, among which HfOx and TaOx RRAM are the best representatives (figure 3c), are already integrated in fabrication lines of industry and integrated with CMOS technology<sup>47</sup>. They take advantage from CMOS technological maturity and reliability and have been exploited mostly in digital applications such as storage class memories (i.e. Flash). Some recent works have investigated the possibility to store few discrete conductance levels in a single memory cell resulting in up to 3-bit multi-level cells. This kind of device can either implement a 1-bit dot-product or a low resolution, e.g. < 3-bit dot-product <sup>48</sup>.

On the other hand, many research groups have focused on resistive switching mechanism for memristor or memristive device implementation (Figure 3d). The association between the theoretical concept proposed by Chua <sup>49</sup> and a possible physical implementation of this new circuit element <sup>50</sup> has open new perspectives for circuit design, and specially for VMM. In the ideal memristor framework, resistive switching is used to implement a variable resistor where continuous resistive states can be reached by controlling the voltage (or current) applied to (through) the switching material. In that scope, the number of conductance states that can be stored in the memristive element directly defines the precision of the in-memory dot-product computation. In recent years, optimization of memristive device has focused on the resolution and controllability of the analog switching using various switching mechanisms and materials such as transition metal oxides, ferroelectric tunnel junctions or more exotic materials (See <sup>51</sup> for a review of the different options). Memristive devices have demonstrated analog switching controlled by analog pulses of voltage equivalent to 8-bit accuracy, paving the way for 8-bit dot-product <sup>52</sup>. The 8-bit accuracy has been demonstrated on discrete devices and only 4- to 5-bit resolution has been reported for integrated devices due to parasitic effects induced from other circuit elements<sup>53</sup>.

The maturity of memristive technologies is not as developed as the RRAM technology, which results in inferior performance regarding endurance, retention and speed. There are still several research opportunities in this area and efforts need to be pursued to improve memristive devices overall performance. However, there is currently no strategy nor materials allowing to reach the 32-bit dot-product precision offered by digital approaches. This imposes limitations in terms of VMM applications, such as deep neural networks that relies deeply on high accuracy calculation of the synaptic weights during training <sup>54</sup>. In that scope, innovations in integration schemes could greatly improve the accuracy of the memristor-based VMM. For instance, while RRAMs differ from analog memristive devices by the difficulty to access to intermediate resistance states, there is, in principle, no physical limitation to have multi-level analog states in RRAM. HfOx-based RRAM, usually exhibiting sharp SET and semi-gradual RESET<sup>55</sup>, can be better controlled by using analog current limitation mechanism through an access transistor to implement analog switching close to 5-bit precision<sup>56</sup>. The trade-off here is between a more complex cell design and a higher precision of programming. Along this line, one interesting approach proposed by 57 consists in a hybrid architecture, where two Phase Change Memories (PCM)resistive cells are coupled with six transistors and one capacitor (1C6T2R). Small weight increments, or decrements, are accumulated on a capacitor and stored back in the non-volatile resistive element once accumulated changes fall within the resolution range. Such integration widens the range of VMM applications like in-situ training while decreasing energy consumption compared to contemporary von Neumann architectures. This resolution improvement comes at the cost of more complex resistive cells design and additional shared control circuitry. Short- and mid-term efforts should be dedicated to more complex resistive cells design that would leverage design complexity with controllability and precision for analog VMM implementation.

Fig. 3. (a) In this spider diagram, RRAM, DRAM, SRAM, and Flash memories are compared in terms of the cost, read time, write time, energy consumption, endurance and retention. (b) In this diagram, RRAM, DRAM, SRAM and Flash memories are compared in terms of other criteria: flexibility, footprint size, maturity, density, variability and potential of the scalability. (c) The *i-v* curve of the prototypical RRAM digital HfOx and its sharp switching behavior in SET and RESET regions are depicted. (d) The switching behaviour for the prototypical memristive TiOx analog device is displayed <sup>58</sup>. Both RRAM and memristive devices belongs to resistive memories family and are used to construct the spider diagrams.

#### 2.2.3. Integration

One of the substantial advantages of RS devices is their advanced integration potential thanks to their excellent scalability. Sub-10 nm switching crosspoints have been reported in  $^{59}$  and  $^{60}$ , paving the way to surpass the scaling limitations of Flash and DRAM. In addition, the two-terminal structure of RS devices enables ultra-dense integration in crossbar arrays, in which a memory device is located at each intersection between two metallic wires resulting in a matrix-like organization. Finally, RS devices and crossbar arrays can be fabricated with CMOS high-volume manufacturing processes and materials allowing monolithic 3D integration in CMOS BEOL. This ideal approach (see Figure 2(d)) results in a  $^{4}F^{2}$  footprint for a single memory crosspoint,  $^{F}F$  being the critical dimension of the metal line interconnect). Monolithic 3D BEOL integration of resistive memories presents a major advantage compared to other on-chip memory technologies such as SRAM, which requires a footprint of  $^{2}F^{2}$  in the front-end-of-line (FEOL). This very attractive approach could relax CMOS scaling requirements by providing additional integration opportunities in the vertical dimension. In addition to BEOL attractiveness, the possibility to stack multiple crossbars on top of each other has been demonstrated experimentally and could be conveniently integrated with CMOS for ultra-high-

density memory circuit design<sup>33,61</sup>. There are still important engineering challenges to address in order to bring these concepts to their full potential: (i) compatibility of advanced lithography steps with BEOL metal layout, (ii) impact of monolithic 3D fabrication processes on the performance of previously fabricated devices, (iii) process homogeneity and yield ensuring high-quality fabrication for each layer and (iv) high-conductivity interconnects even for ultra-fine pitch. While crossbar architecture offers a truly parallel organization that could map directly the VMM operation, the main limitation comes from the difficulty to access individual memory cell accurately. Parasitic sneak path, currents coming from other resistive cells in the array, are preventing an accurate reading of each resistive element individually.

RRAM and memristive devices can be addressed with or without the use of a selector. On the one hand, RRAM requirements have favored optimizations towards accessibility and controllability of individual memory cell by adding a selector, usually a FEOL transistor, in series with the two-terminal element leading to 1T1R cells. This solution requires a transistor per memory cell with the allocation of additional silicon area and interconnects for memory management, decreasing the attractiveness of two terminal resistive memory. The resulting integration scheme is then only considered as a pseudo-crossbar array. Two-terminal selectors, such as threshold switching elements or non-linear diodes, are today attracting lots of attention toward 1S1R cells. Those passive elements can prevent sneak path currents and preserve two-terminal interconnection of each memory cell <sup>62</sup>. Still, 1S1R integration is facing important challenges such as (i) large variability coming from the selector itself and (ii) shorter endurance in the case of switching selectors that needs to be switched for each read operation. Detailed review in this topic can be found in <sup>63</sup>.

On the other hand, memristor-based approaches for physical VMM have favored the concept of selector-less passive crossbar integration. While RAM operations require precise access to individual memory cell, memristor-based dot-product is different since this operation is not affected by sneak paths (e.g. all lines and columns are polarized at the same time and all resistive cells are read at the same time). More exploratory in-memory computing paradigms such as neuromorphic computing, or bio-inspired spiking neural networks, can also take advantage of a similar principle. The trade-off being to favor parallelism and aggressive integration at the cost of less accurate access to individual crosspoints sequentially. It should be noted that practical integration of crossbar on chip still requires access transistors at the N input lines and M output columns of the crossbar thus leading to  $(N+M)T(N\times M)R$  actual footprint on silicon. There is consequently a strong interest in improving passive crossbar dimensions above the  $64 \times 64$  size report so far<sup>53</sup>.

#### 2.2.4. Scalability

In digital approaches, computational scalability of the Add operation is ensured by pipelining simple logical operations of single bits, thus allowing for very large vector-matrix manipulation (adding multiple dot-product, for instance). The digital approach is based on a trade-off between scalability of the operation, and computing time (e.g. how many clock cycles and basic operation are required). In RS-based Add operation, adding multiple dot-products is realized in a single time step. This advantage comes at the price of higher instantaneous power requirements. Adding currents from multiple dot-products results in a large current summation that could become a bottleneck for the VMM operation (Figure 4(a,c)). Adding infinite size of dot-products results in infinite time in digital scheme while it results in infinite power for Kirchoff's law-based approach. Practically, memristor-based VMM has been reported for matrix size of up to 128×64 <sup>14</sup>. While this was demonstrated with pseudo-crossbar having micron size electrodes, such limitations in matrix size should become a

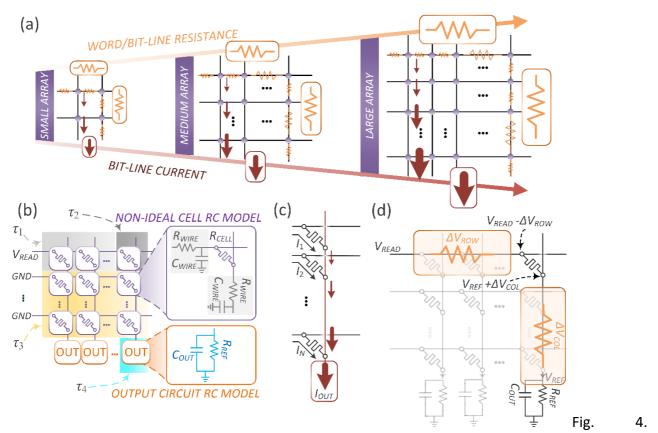

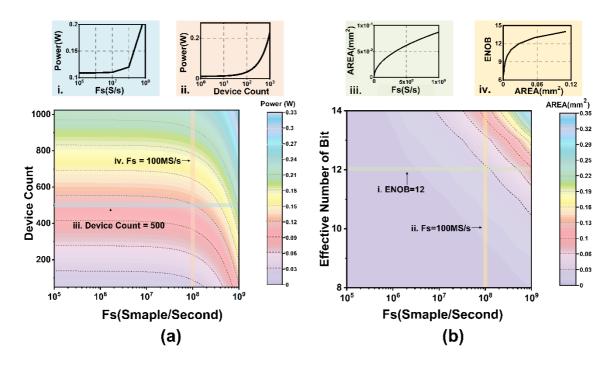

serious computational scalability challenge with electrodes in the tenth of nanometer range that would prevent sinking large currents through them. 64×64 VMM operation was demonstrated in<sup>53</sup> using purely passive crossbar with a more advanced patterning process (<200 nm). Dot-product demonstration with other integrated approaches<sup>76,77</sup> are today limited to small vectors dimensions, with vector dimension below 25, and impose restrictions on the VMM application. There is a concern that this limitation will get worse by decreasing the metal linewidth and will require high aspect-ratio lines to achieve a high conductivity interconnect<sup>60</sup>. Alternatively, increasing the mean resistance of RS devices would increase scalability significantly by reducing power consumption at the cost of lower VMM operation speed. The inference operation speed is determined based on the delay induced from the input circuits, RS-based crossbar array and output circuits. In very large RS arrays, there are several parameters which should be considered to determine the delay such as interconnect resistance, interconnect capacitance, RS cell resistance, overhead circuit's impedance and capacitance. The inference delay is calculated based on the Elmore delay model as follow,

$$t_{inf} = t_{settling} + 2.2 \times \sum_{\tau=1}^{4} \tau_{i}$$

Where t<sub>settling</sub> is the settling time of the output circuit. As it can be seen in Figure 4(b), the parameters  $\tau_1$ ,  $\tau_2$ ,  $\tau_3$  and  $\tau_4$  are the delays from row, RS cell, column and output circuit, respectively <sup>78</sup>. By considering the LRS resistance of the device much larger than the interconnect resistance between each two adjacent cells, the delays  $\tau_3$  and  $\tau_4$  are dominant in very large arrays. By increasing the LRS of the RS cell, the inference time delay increases as it is impacting both  $\tau_3$  and  $\tau_4$ . Therefore, the throughput of the system will be reduced accordingly. However, increasing the size of the array would also impact the inference delay e.g. increasing the number of rows will make  $\tau_3$  the dominant term to impact the total delay and it will reduce the delay. On the other hand, increasing the number of columns will increase the latency. Crossbar and pseudo-crossbar scalability challenges can also be related to computing performance (e.g. accuracy). Unlike digital approaches where input digital signals margins allow to cope with noise and parasitic, analog VMM implementation accuracy is negatively impacted in the case of large vector operations. The resulting mismatch between the resistance of the memory cells and the one of metal interconnects becomes critical in large crossbar arrays (figure 4(d)). The same bias applied on the word-line is seen differently by each cell in the crossbar due to linear voltage drops which leads to a decrease of accuracy for the VMM operation. A straightforward physical solution to these constraints is to limit the size of the crossbar array and thus the VMM performed in one step. Note that small VMM dimensions are largely used for convolutions in Convolutional Neural Networks (CNN). In conclusion, scalability of memristor-based VMM operation represents a future research direction that requires innovative solutions at both technological and system levels.

Scalability challenges and RC tree Elmore delays model for RS crossbar array is displayed. (a) The scalability challenges including large bit-line current and word/bit-line resistance has been shown to get worse by increasing the size of the RS crossbar array. (b) RS crossbar RC Elmore delay model is displayed by dividing the array delay into four regions corresponding to  $\tau_1$ ,  $\tau_2$ ,  $\tau_3$  and  $\tau_4$  are the delays from row, RS cell, column and output circuit, respectively. (c) Increasing the number of rows increase the accumulated current in the column and could become a major bottleneck for output circuits design. Same limitation applies for large number of columns requiring to inject large current into the row and affecting input circuits design (d) The line resistance is another challenge for scalability of RS-based array due to the voltage degradation in the rows ( $\Delta V_{\text{ROW}}$ ) and columns ( $\Delta V_{\text{COL}}$ ) that can be leveraged by engineering optimization and/or compensated from input/output circuits strategies.

#### Addressing non-ideal parameters of RS-based system which impacts neural network accuracy

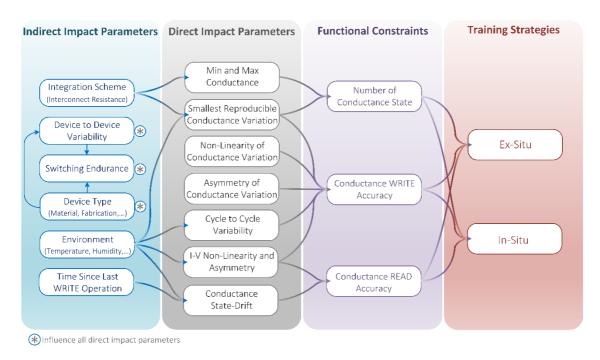

Fig. 5. Schematic classification of memristor-based system's non-idealities according to the way they influence Artificial Neural Network (ANN) accuracy. Each arrow connection should be read as "could have a significant influence on" but with no consideration for their relative impact level. The first column "Indirect Impact" can be considered as hyper-parameters that only impact the ANN accuracy through their influence on other parameters. The second column "Direct Impact" represents the fundamental parameters that directly influence the ANN accuracy. The third column "Functional constraints" lists some measurements that are often used as reference to quantify a memristive device performance.

Designing a RS-based system compatible with established microelectronic industrial technologies and large-scale production is only one part of the challenge. Since RS devices have inherent physical imperfections "\cite{wang2019cross,adam2018challenges,Sung2018}, it is necessary to find efficient ways to deal with them. The impact level of such non-ideal parameters can be varied on different applications and here we focus on how they influence VMM-based ML applications, specifically, the accuracy of physically implemented Artificial Neural Network (ANN).

The accuracy of an ANN denotes the output success rate for a task for which it has been trained. For example, the accuracy of digit recognition using the MNIST database corresponds to the proportion of correctly classified image from a test dataset. In the context of RS-based ANN, we can distinguish two training strategies: *in-situ* and *ex-situ* ~\cite{alibart2013pattern}. In the *in-situ* scheme, the training is performed directly on the hardware by updating weights (i.e. the conductance of all devices) after each training epoch. This approach is notably impacted by all device non-ideal parameters that affect the conductance writing accuracy ~\cite{pan2020strategies,chen2015mitigating,hu2018memristor} (Figure 5) because this operation is repeated several times during *in-situ* training. In the case of *ex-situ*, the weight matrix is initially calculated in software ANN before to be transferred to the device array by encoding the determined

weights into the conductance for each cell. In that scope, the conductance programming process occurs only one time per device, which make it viable to apply advanced methods to mitigate non-ideal parameters related to writing ~\cite{pan2020strategies,alibart2012high}. Finally, a hybrid strategy showed some interesting results by fine tuning the network weights after the transfer ~\cite{yao2020fully}.

To better understand the different impacts of RS-based system non-ideal parameters on training strategies, it is interesting to not only consider their impact on functional constraints (write/read accuracy, latency, energy consumption...) but also the inter-dependence between the different parameters. For example, the *switching endurance*, which represents the average number of cycles before losing resistive switching behavior, directly impacts *minimum and maximum conductance* values over cycles ~\cite{lee2010evidence}, which in turn contribute to determine the total *number of conductance state*. Therefore, poor *switching endurance* could indirectly lead to low number of conductance state, or even failure such as stuck-at-fault where only one conductance state exists ~\cite{xia2018fault}. The impossibility to update the conductance decreases the ANN accuracy ~\cite{li2018efficient}, even more so for *ex-situ* training where weights are supposed to be mapped on working devices. The same analyse can be made with the *device to device variability* parameter, which become a problem only if this variability concerns critical device characteristics like *cycle to cycle variability* ~\cite{adam2018challenges} or the overall *asymmetry of the conductance variation* ~\cite{pan2020strategies}.

Further work should be conducted on the interactions between all non-ideal parameters in order to clarify their direct and indirect impact on the accuracy of physically implemented ANN, which could help the design and demonstration of mitigation strategies.

#### 2.3. CIRCUIT DESIGN CHALLENGES FOR VMM IMPLEMENTATION

#### 2.3.1. Background

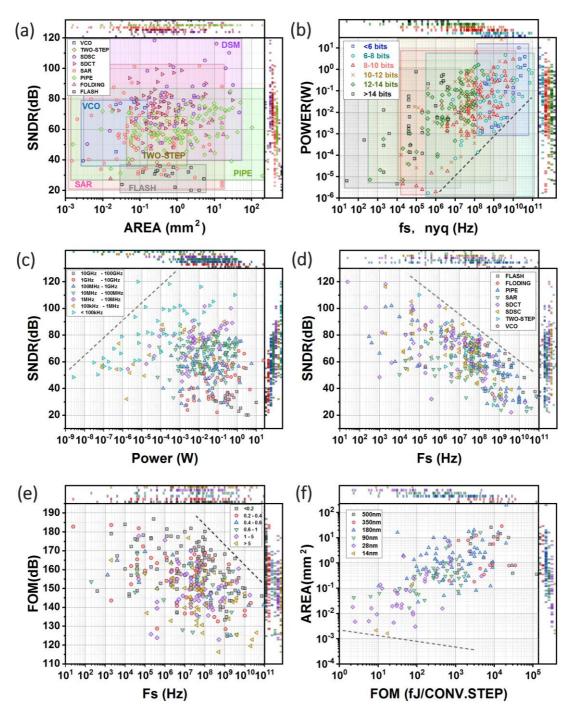

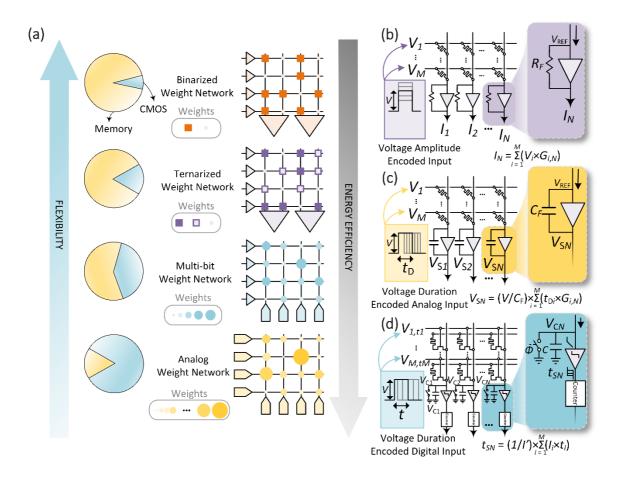

As mentioned previously, projected energy consumption for a single dot-product operation can indeed be as small as 0.01 fJ, while 0.2 pJ are consumed with 8-bit digital VMM based on 45 nm CMOS technology node~\cite{horowitz20141}. However, this comparison is not a complete picture since it does not consider energy consumption for input/output signals generation. A more rigorous evaluation of memristor-based dot-product energy consumption should be done by considering 8bit digital-to-analog converter (DAC) at the input and 8-bit analog-to-digital converter (ADC) at the output where both components consume approximately 0.1 mW and can be run at the frequency of 1 GHz (1 ns clock cycle). The total energy required to compute the 8-bit dot-product with RS devices becomes largely dominated by these DAC/ADC-based overhead circuits since  $E_{DAC} + E_{ADC} =$  $2\times0.1\times10^{-3}\times10^{-9}$  = 0.2 pJ. This simple example therefore highlights the importance of the overhead circuitry in the assessment of VMM engine performance. While most of the approaches so far have been using software-emulated or custom printed circuit boards (PCB), there are recently only a few fully integrated chip demonstrations. These demonstrations benefits are two sides: (i) exploring CMOS design overhead circuits and their compatibility with RS devices and (ii) exploring various strategies at the system level for building a fully operational chip. These choices are defining the application field of the VMM engine and impacting both the energy and accuracy performances.

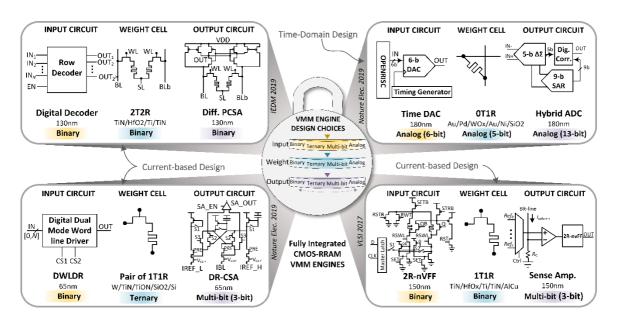

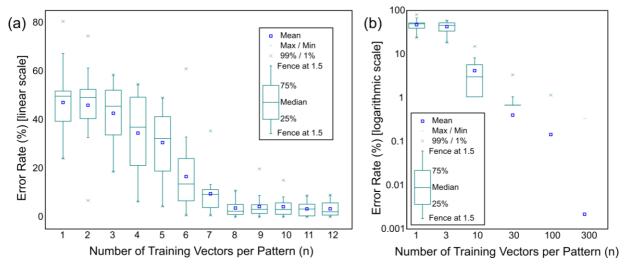

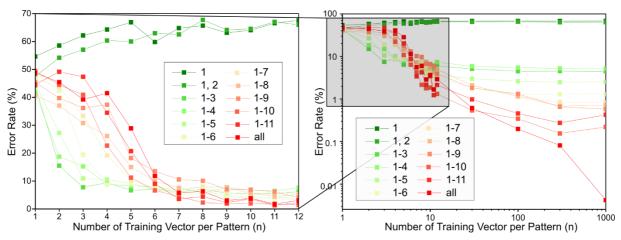

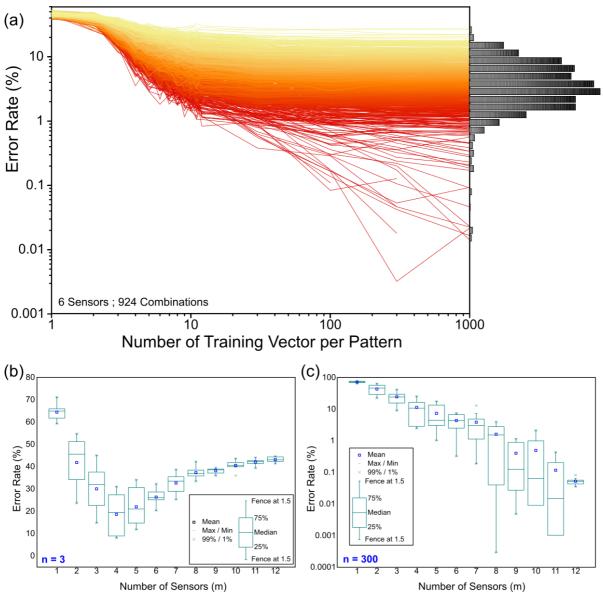

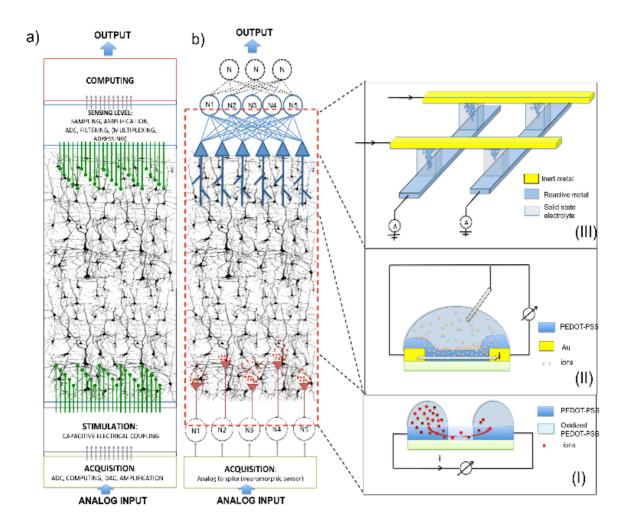

#### 2.3.2. Input circuits