# Evolutions of the Software Flow for Automated Testing Michele Portolan

#### ▶ To cite this version:

Michele Portolan. Evolutions of the Software Flow for Automated Testing. Automatic. Université Grenoble Alpes, 2024. tel-04526188

## HAL Id: tel-04526188 https://hal.science/tel-04526188

Submitted on 29 Mar 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

Pour obtenir l'Habilitation à Diriger des Recherches (HDR) de

### L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS) Spécialité : Nano électronique et Nano technologies

Unité de recherche : Laboratoire TIMA (Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés)

## Évolutions du flux logiciel pour les tests automatisés

## **Evolutions of the Software Flow for Automated Testing**

Présentée par :

## **Michele PORTOLAN**

Thèse soutenue publiquement le 19/03/2024, devant le jury composé de :

| Alberto BOSIO<br>Professeur, Ecole Centrale de Lyon, INL (France)           | Président du jury |

|-----------------------------------------------------------------------------|-------------------|

| <b>Olivier SENTIEYS</b><br>Professeur, Université de Rennes (France)        | Rapporteur        |

| Henri-Pierre CHARLES<br>Directeur de Recherches, CEA LIST Grenoble (France) | Rapporteur        |

| Arnaud VIRAZEL<br>Professeur, LIRMM Montpellier (France)                    | Rapporteur        |

| Matteo SONZA REORDA<br>Professeur, Politecnico di Torino (Italie)           | Examinateur       |

| <b>Régis LEVEUGLE</b><br>Professeur, Laboratoire TIMA Grenoble (France)     | Examinateur       |

| Jeff REARICK<br>Senior Fellow, AMD (USA)                                    | Invité            |

# Acknowledgments

First of all, I would like to thank the Reviewers and all the members of this HdR jury for their participation.

Thanks to Régis, Suresh and Brad: without your help, guidance and tutoring, I would never have become the professional I am now.

To my wife Nadia, thank you from the bottom of my heart for all your love and support and for helping me being myself.

A special thanks to my sons, Clovis and Cléante, for always keeping me on my toes with their questions and for showing me the world with new, enthusiastic eyes.

"The Road goes ever on and on, Down from the door where it began. Now far ahead the Road has gone, And I must follow, if I can, Pursuing it with eager feet, Until it joins some larger way Where many paths and errands meet. And whither then? I cannot say" Bilbo Baggins, The Lord of the Rings

# Table of Contents

| Ir | ntrod   | uction           |                                                                                     | 1  |

|----|---------|------------------|-------------------------------------------------------------------------------------|----|

| 1  | C       | urricul          | um Vitae                                                                            | 3  |

|    | 1.1     | Curric           | ulum Vitae                                                                          | 3  |

|    | 1.2     | Teach            | ing Activities                                                                      | 6  |

|    | 1.3     |                  | r Synthesis                                                                         |    |

|    | 1.      |                  | Project Participation:                                                              |    |

|    |         |                  | upervisions and Management                                                          |    |

|    |         | 1.3.2.           |                                                                                     |    |

|    |         | 1.3.2.2          |                                                                                     |    |

|    |         | 1.3.2.3          |                                                                                     |    |

|    |         | 1.3.2.4          | 4 Short Term Contracts                                                              |    |

|    |         | 1.3.2.5          | 5                                                                                   |    |

|    |         | 1.3.2.0          | J                                                                                   |    |

|    |         |                  | ific Themes                                                                         |    |

|    | 1.4     |                  | oftware Methods for Next-Generation Test Standards                                  | 12 |

|    |         | 1.4.1.           | I J J                                                                               |    |

|    |         |                  | gement in automotive and IoT Application"                                           |    |

|    |         | 1.4.1.2<br>Mixed | 2 Jules Quentin KOUAMO: Software Methods and Architectures for the<br>I-Signal SoCs |    |

|    | 1.      |                  | arly Reliability and Security Analysis                                              |    |

|    | 1.      |                  | Kais Chibani "Robustness analysis of Integrated Digital Systems"                    |    |

|    | 1.      |                  | Design Exploration for Approximate Computing                                        |    |

|    |         |                  | Autonomous deployment of Small Cells                                                |    |

|    | 1.5     |                  | rations                                                                             |    |

|    | 1.6     |                  | s and Software Filings                                                              |    |

| -  |         |                  |                                                                                     |    |

| 2  |         |                  | ons and State of the Art                                                            |    |

|    | 2.1     |                  | utomated Test Flow                                                                  |    |

|    | 2.2     |                  | ole of Standards and Patents                                                        |    |

|    | 2.      | -                | TAG                                                                                 |    |

|    |         | 2.2.1.1          |                                                                                     |    |

|    |         | 2.2.1.2          | 1                                                                                   |    |

|    |         | 2.2.1.3          |                                                                                     |    |

|    | 2.      |                  | Domain Specific Languages                                                           |    |

|    |         |                  | Evolutions, limitations and new usages of JTAG                                      |    |

|    |         |                  | Core Testing : 1500                                                                 |    |

|    |         |                  | EEE 1687 or IJTAG                                                                   |    |

|    | <i></i> | 2.2.5.           |                                                                                     |    |

|    |         | 2.2.5.2          |                                                                                     |    |

|    | 2.      |                  | Putting it all together: retargeting                                                |    |

|    | 2.3     |                  | Standards                                                                           |    |

|    | 2.4     | -                | ty Issues                                                                           |    |

|    | 2.4     | 4.1 S            | can Authentication                                                                  | 55 |

| 2.4.2 Scan Encryption                                                                   | 58     |

|-----------------------------------------------------------------------------------------|--------|

| 3 The need for a New Test Flow                                                          | 60     |

| 3.1 Limitations of the Legacy Automated Test Flow                                       |        |

| 3.1.1 Topology resolution (vertical retargeting) limitations                            |        |

| 3.1.2 Concurrency (horizontal retargeting) limitation                                   |        |

| 3.1.3 Interactive behavior                                                              | 63     |

| 3.1.4 Interface Domains                                                                 | 64     |

| 4 A New Automated Test Flow: Specification                                              | 66     |

| 4.1 High Level Requirements                                                             | 66     |

| 4.2 Relocatable Test Executable                                                         | 69     |

| 4.3 Circuit Model                                                                       | 70     |

| 4.3.1 Retargeting                                                                       | 70     |

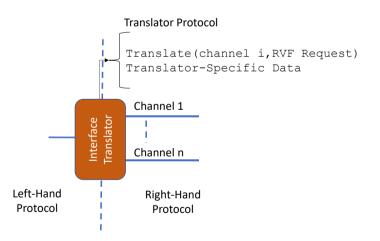

| 4.3.2 Interfaces                                                                        | 72     |

| 4.3.3 Conclusions                                                                       | 75     |

| 4.4 Test Manager                                                                        | 76     |

| 4.4.1 Vertical Retargeting                                                              | 76     |

| 4.4.2 Concurrency (Horizontal Retargeting)                                              |        |

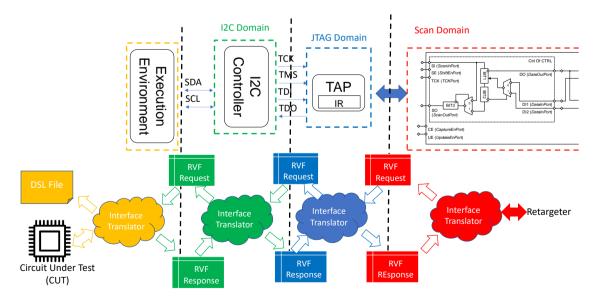

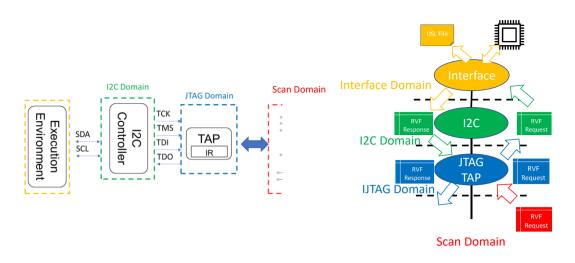

| 4.5 Domain Crossing and RVF propagation                                                 | 81     |

| 5 A New Automated Test Flow: Implementation                                             |        |

| 5.1 Early Developments : Test Instruction Set Architecture and NSDL: 2007 $\rightarrow$ | 201383 |

| 5.2 First Abstractions: New System-Level Test (NeSLT : 2013 $\rightarrow$ 2015)         |        |

| 5.3 A General Solution: MAnager for Soc Test (MAST: $2015 \rightarrow 2017$ )           |        |

| 5.4 New Perspectives with MAST: $2018 \rightarrow$ Present                              | 97     |

| 5.4.1 Interface Independence and P1687.1                                                |        |

| 5.4.2 Interactive IJTAG                                                                 |        |

| 5.4.3 Unified Test Middleware: "Test Operating System"                                  |        |

| 5.4.4 Security as part of the Test Flow                                                 |        |

| 5.4.5 Analog Interfaces                                                                 |        |

| 6 Short-to-Mid Term Perspectives                                                        | 110    |

| 6.1 Silicon Lifetime Management                                                         | 110    |

| 6.2 Security                                                                            | 110    |

| 6.3 Scaling up : FPGAs                                                                  | 111    |

| 6.4 Mixed Signal Testing                                                                | 112    |

| 7 Conclusions and Long-Term Directions                                                  | 113    |

| 8 Bibliographie                                                                         | 116    |

| 9 Glossary                                                                              | 122    |

V

# **Figure Index**

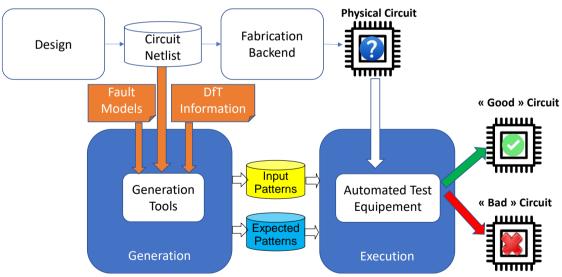

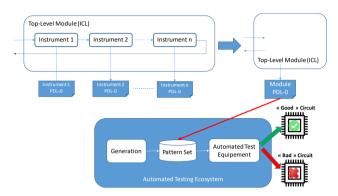

| Figure 1: The Ecosystem of Automated Testing                                                  | 25 |

|-----------------------------------------------------------------------------------------------|----|

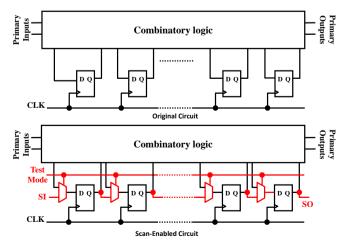

| Figure 2 Example of Scan Insertion                                                            | 26 |

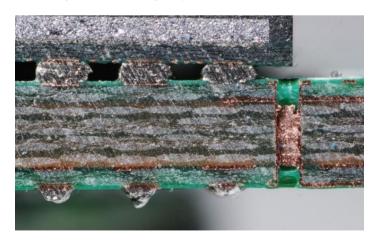

| Figure 3 Cross-cut section of BGA mounted circuit (from Wikipedia)                            | 30 |

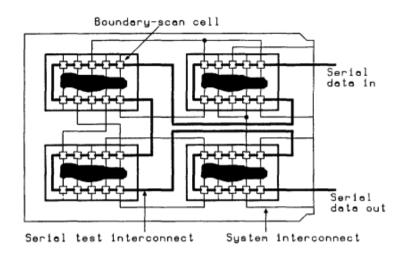

| Figure 4 A boundary-scannable board design", from [1149]                                      | 31 |

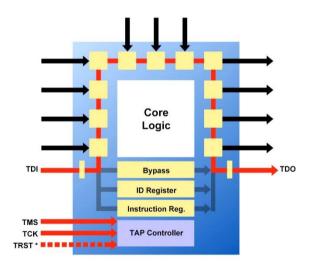

| Figure 5 JTAG standard architecture (source JTAG Technologies)                                | 31 |

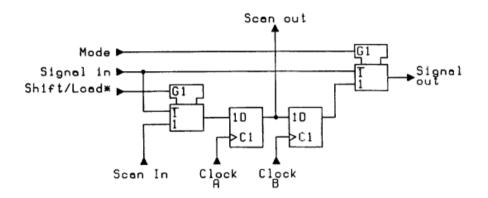

| Figure 6 An example of boundary-scan register cell, from [1149]                               | 32 |

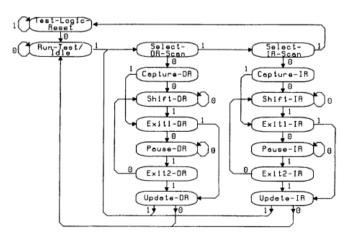

| Figure 7 The JTAG Finite State Machine, from [1149.1]                                         | 32 |

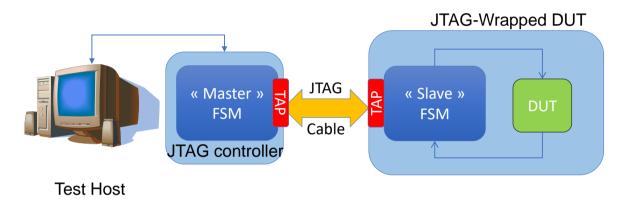

| Figure 8 JTAG Usage Setup                                                                     |    |

| Figure 9 Example of a BSR description from [1149]                                             |    |

| Figure 10 Example of TAP Instruction Mapping in BSDL, from [1149]                             | 35 |

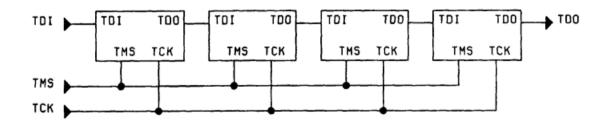

| Figure 11 Daisy-Chain JTAG Topology, from [1149]                                              | 35 |

| Figure 12 JTAG Star topology, from [1149]                                                     | 36 |

| Figure 13 JTAG Retargeting                                                                    | 36 |

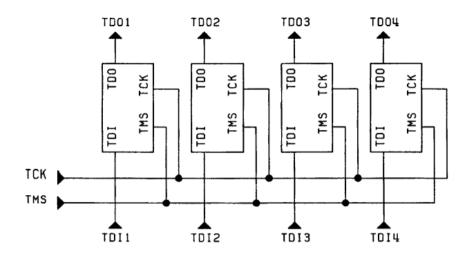

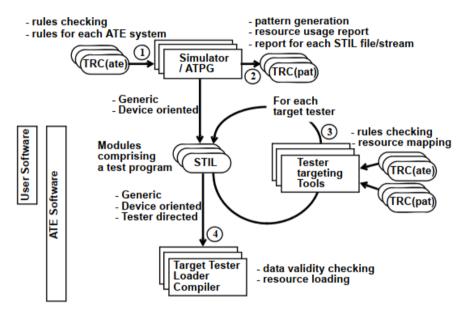

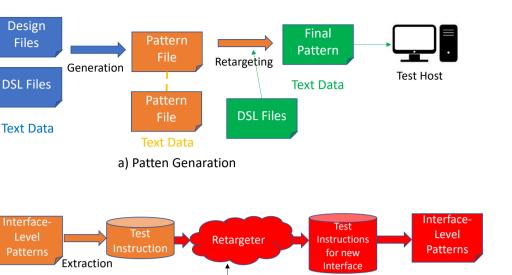

| Figure 14 STIL Usage model, from [1450]                                                       |    |

| Figure 15 Example of an SVF program from [SVF99]                                              | 38 |

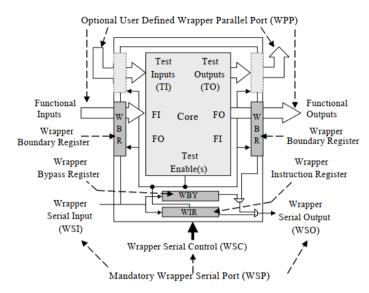

| Figure 16 Standard IEEE 1500 Wrapper components, from [1500]                                  | 40 |

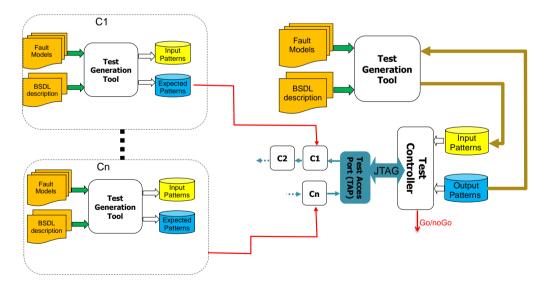

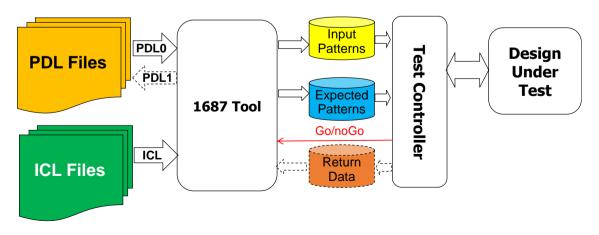

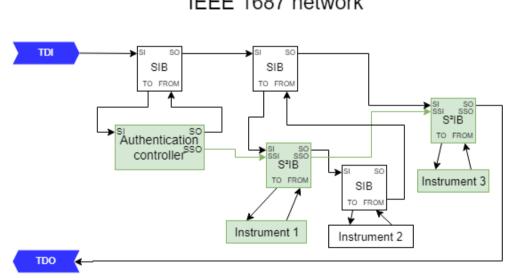

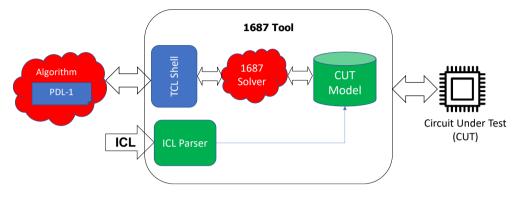

| Figure 17 IEEE 1687 (IJTAG) Use Model                                                         | 41 |

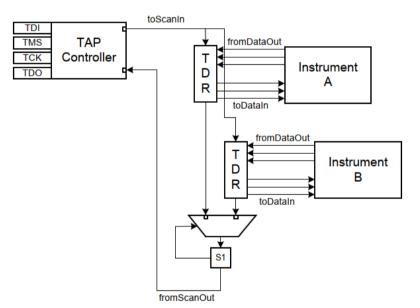

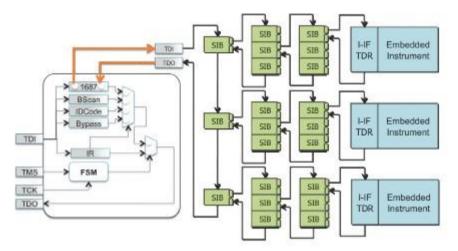

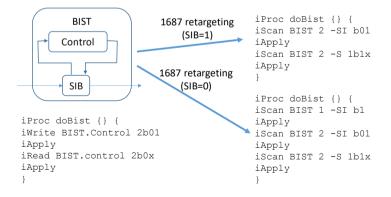

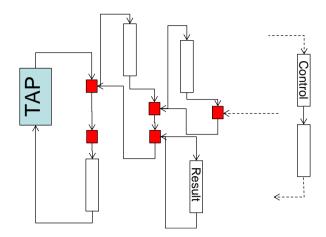

| Figure 18 Example of an IJTAG Reconfigurable Scan Network, from [1687]                        | 42 |

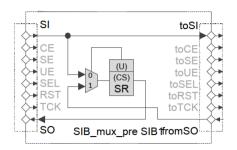

| Figure 19 Example of a SIB, from [1687]                                                       |    |

| Figure 20 Example of a SIB-enabled hierarchy [DWO13]                                          |    |

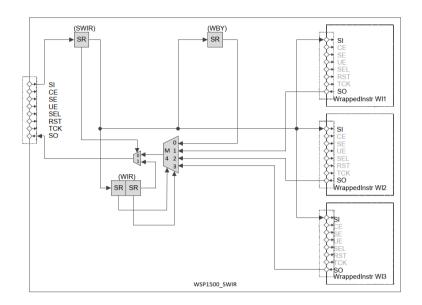

| Figure 21 Example of a 1500 Wrapper from section E.20 of [1687]                               | 44 |

| Figure 22 ICL Description of Figure 21, from [1687]                                           | 44 |

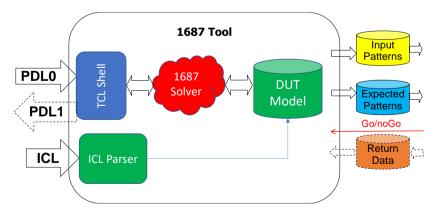

| Figure 23 Internal Setup of the 1687 Tool of Figure 17                                        |    |

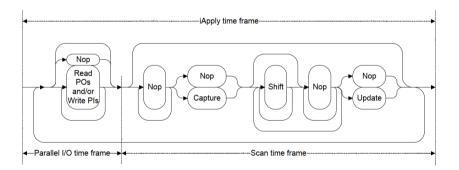

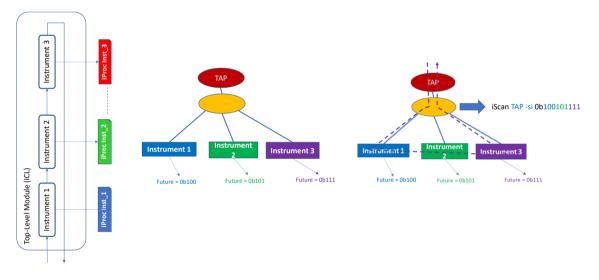

| Figure 24 Sequence of Operations during an iApply, from [1687]                                |    |

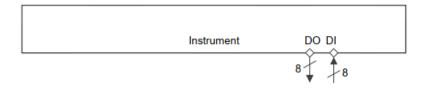

| Figure 25 Example generic Instrument from Annex E.2 of [1687]                                 | 49 |

| Figure 26 Raw Instrument connected to a Scan Register                                         | 50 |

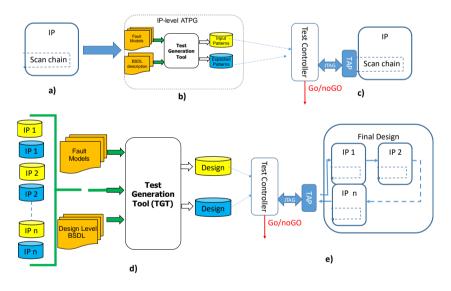

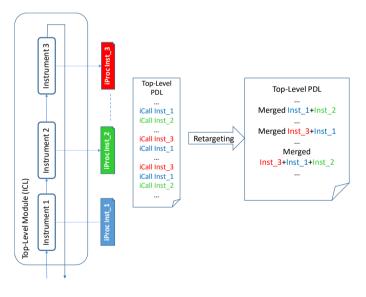

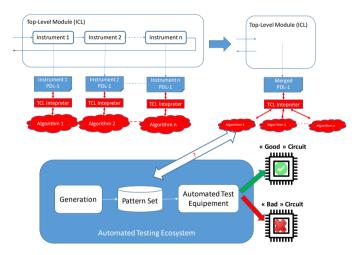

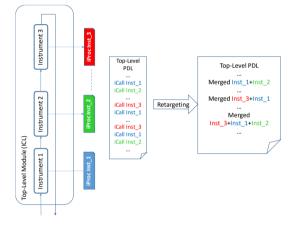

| Figure 27 Partitioned Retargeting [J.4]                                                       |    |

| Figure 28 Horizontal Retargeting Merging for a 3-instrument 1687 system [J.4]                 |    |

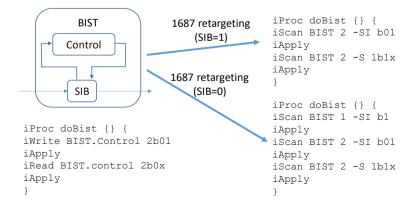

| Figure 29 Vertical Retargeting of a SIB, from [J.4]                                           |    |

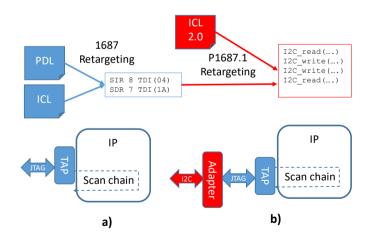

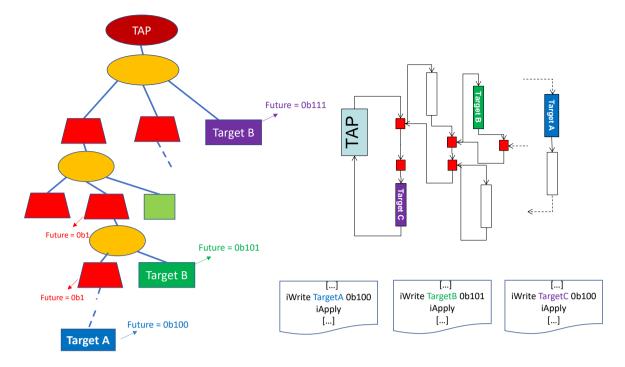

| Figure 30 Hypothetical P1687.1 Retargeting Flow, from [J.4]                                   |    |

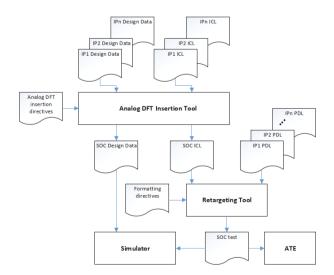

| Figure 31 Envisioned EDA ecosystem to support structured analog DFT and testing, from [SAR17] |    |

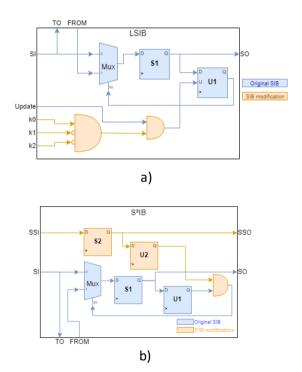

| Figure 32 Locking SIB and Secure SIB Implementations                                          |    |

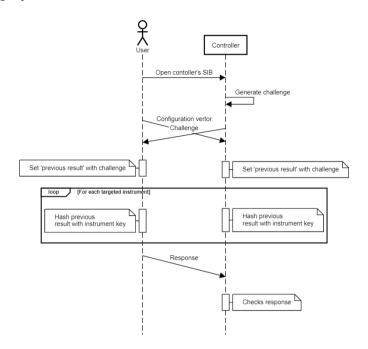

| Figure 33: FGA Challenge response protocol, from [7]                                          |    |

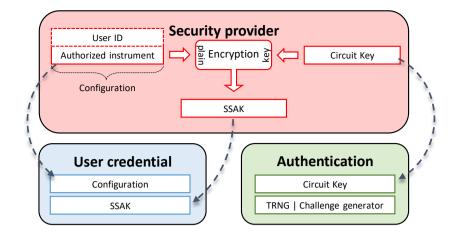

| Figure 34 SSAK's procedural key generation and distribution, from [7]                         |    |

| Figure 35: SSAK Authentication architecture, from [7]                                         |    |

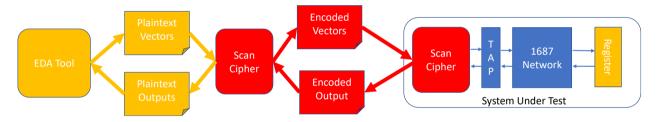

| Figure 36 Principles of Scan Encryption                                                       |    |

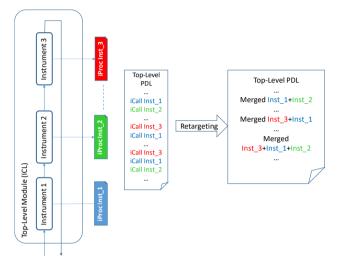

| Figure 37 Example of a deeply hierarchical system                                             |    |

| Figure 38 IJTAG Legacy Top-Down Retargeting Backend for PDL-0, from [J.4]                     |    |

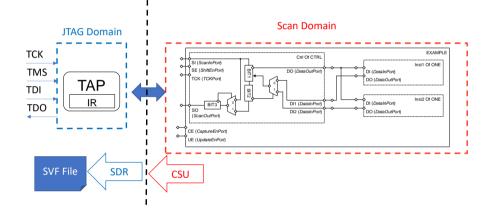

| Figure 39 Interactive IEEE 1687 Tool Setup                                                    |    |

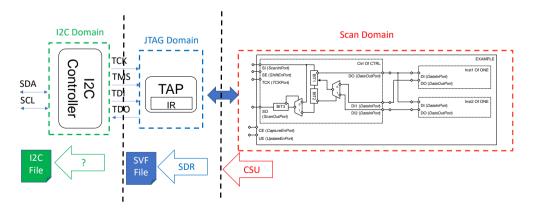

| Figure 40 IJTAG Legacy Retargeting Backend for PDL-0, from [J.4]                              |    |

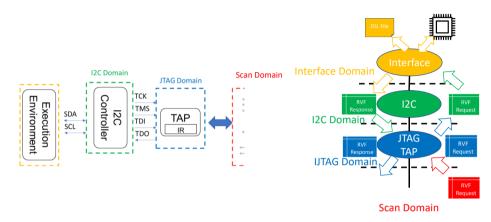

| Figure 41 Domain Translation between Scan and JTAG                                            |    |

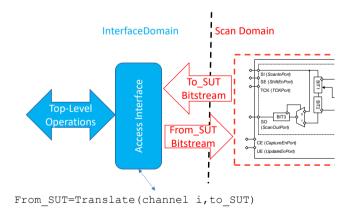

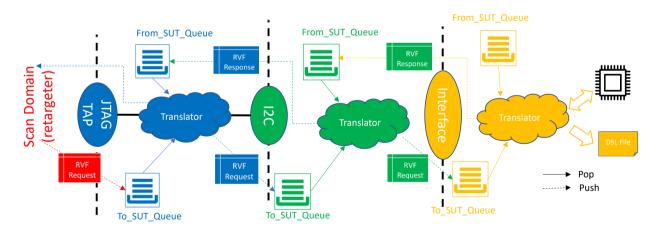

| Figure 42 Domain Translation between multiple interfaces                                      |    |

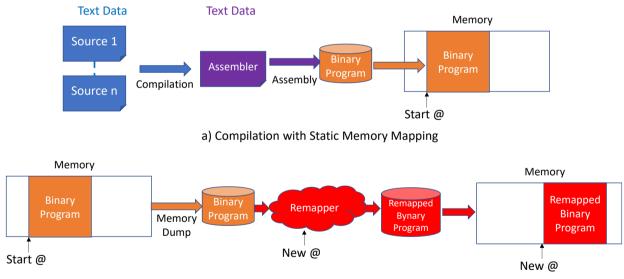

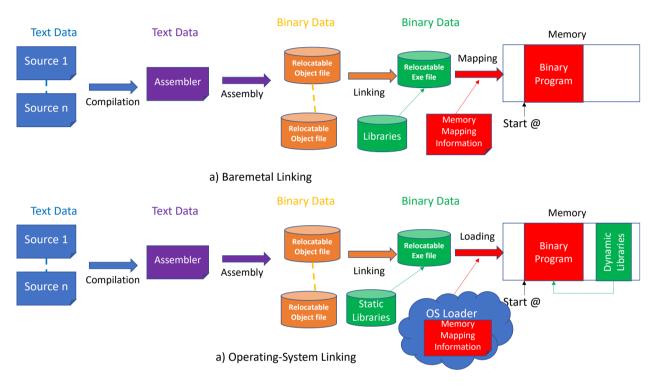

| Figure 43 Software Compilation with Static Memory Mapping                                     |    |

| Figure 44 Principles of the Software Relocation Flow                                          |    |

| Figure 45 Information flow in the Automated Test Flow                                         | 68 |

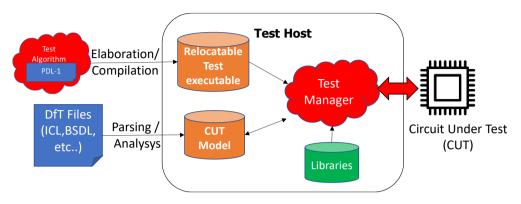

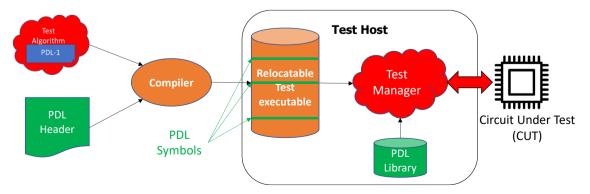

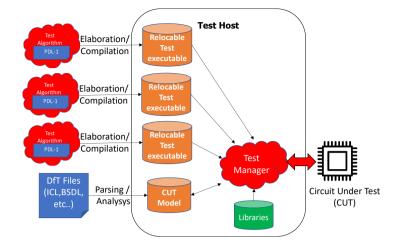

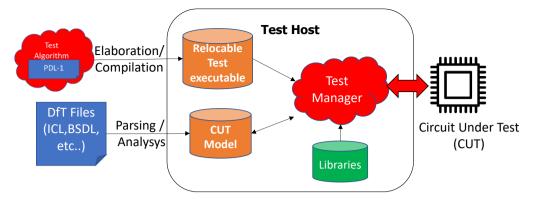

| Figure 46 New Automated Test Flow                                                          | 69  |

|--------------------------------------------------------------------------------------------|-----|

| Figure 47 Details of the Compilation Step                                                  | 69  |

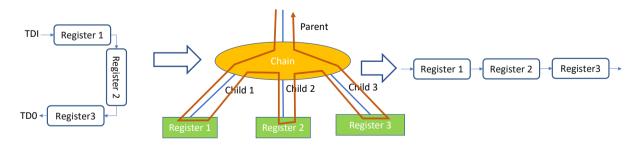

| Figure 48 Tree Representation of a Scan Chain                                              | 70  |

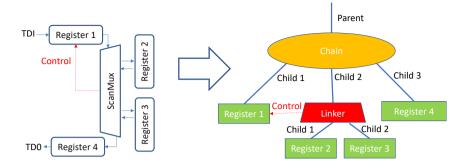

| Figure 49 Tree Representation of a ScanMux                                                 | 71  |

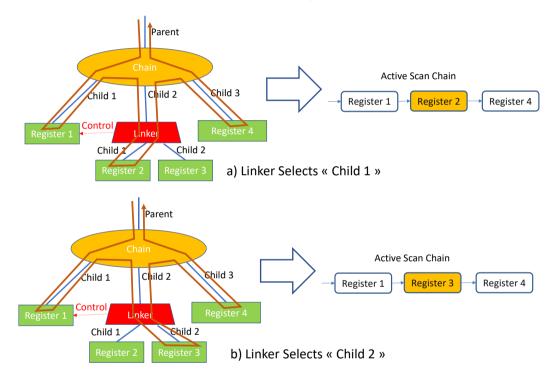

| Figure 50 Extraction of Active Scan Path through depth-first tree transversal              | 71  |

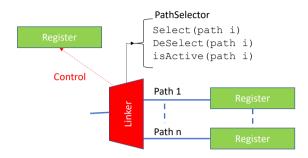

| Figure 51 Complete Specification of a Linker Node, from [1]                                | 72  |

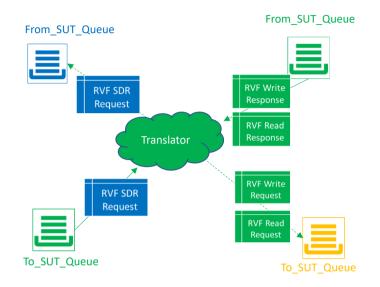

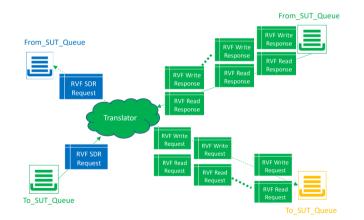

| Figure 52 Domain Crossing through the Relocatable Vector Format                            | 72  |

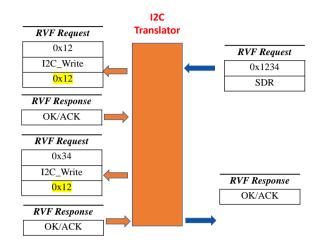

| Figure 53 RVF Translation for a JTAG - to - I2C Translator                                 | 74  |

| Figure 54 Complete Specification of the Interface Translator Node                          | 74  |

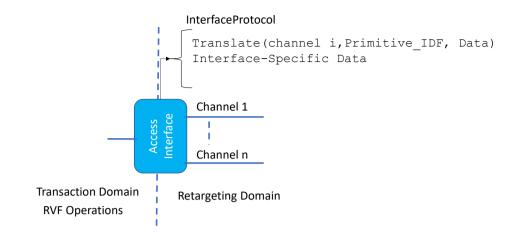

| Figure 55 Specification of the Access Interface Node                                       | 75  |

| Figure 56 Complete Circuit Model Abstraction                                               | 75  |

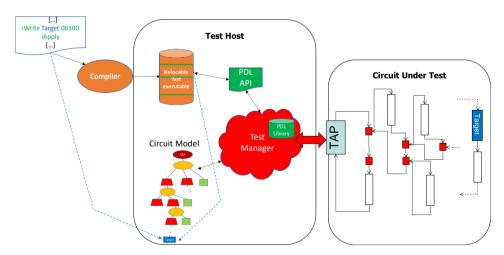

| Figure 57 Complete Setup for Vertical Retargeting                                          |     |

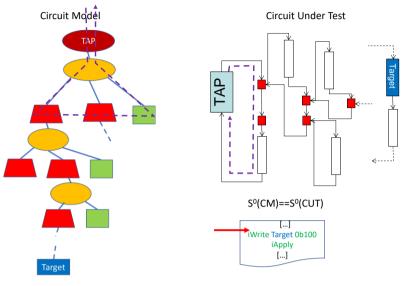

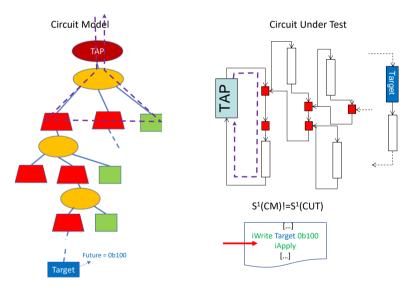

| Figure 58 Circuit Model and CUT status at time 0                                           | 77  |

| Figure 59 Status mismatch caused by a PDL instruction                                      | 77  |

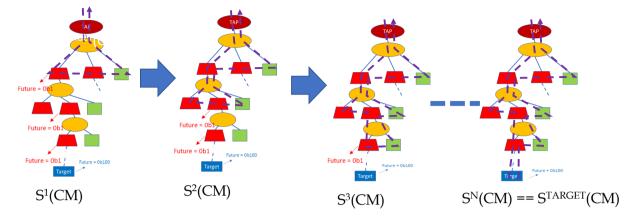

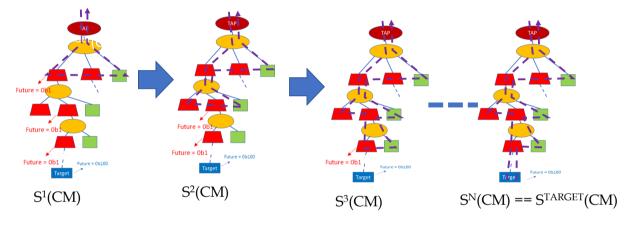

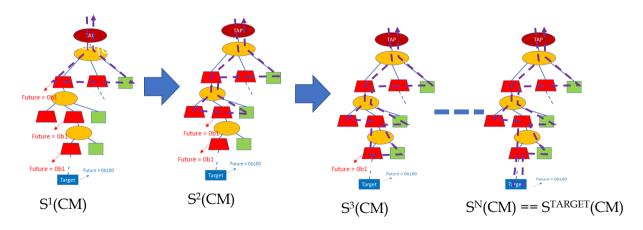

| Figure 60 Sequence of n CM state reaching STARGET(CM) from S <sup>0</sup> (CM)             | 78  |

| Figure 61 Horizontal Retargeting in the new Test Flow                                      | 80  |

| Figure 62 Circuit Model Abstraction for Horizontal Retargeting                             | 80  |

| Figure 63 Circuit Model Abstraction for Horizontal and Vertical Retargeting                | 81  |

| Figure 64 RVF Packet Propagation on the Circuit Model                                      | 82  |

| Figure 65 P1687 Demonstrator (2007-2008)                                                   | 84  |

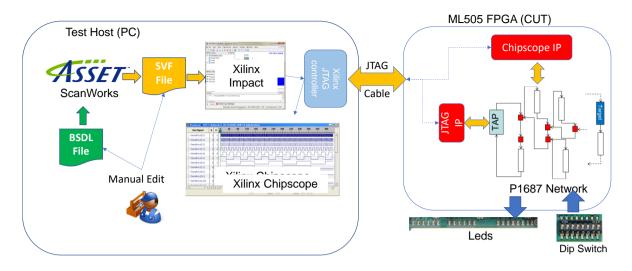

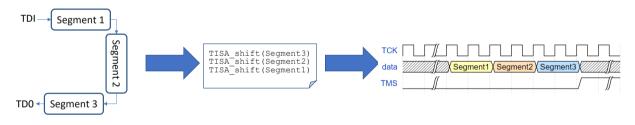

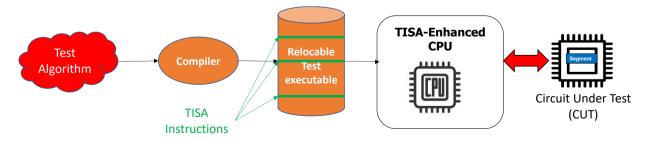

| Figure 66 TISA Principles                                                                  | 85  |

| Figure 67 TISA Single-Algorithm Use Model                                                  | 85  |

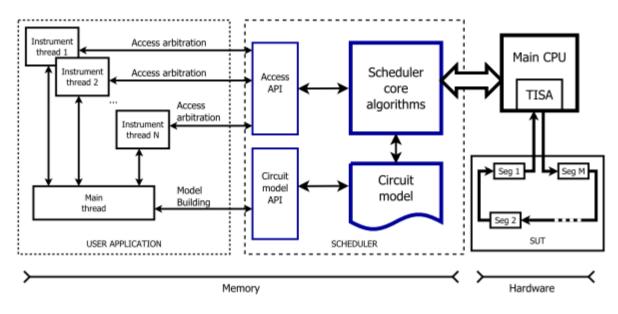

| Figure 68 Complete TISA Setup, from [J.5]                                                  | 86  |

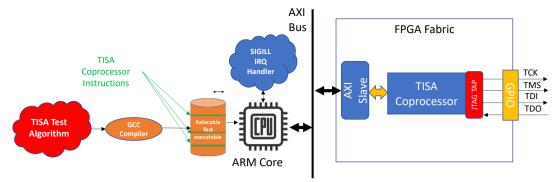

| Figure 69 TISA Scheduler protocol, from [J.5]                                              |     |

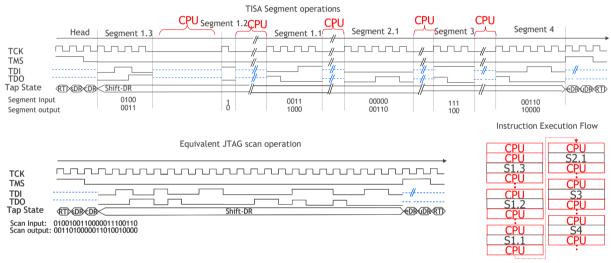

| Figure 70 TISA Hardware demonstrator on Zynq                                               |     |

| Figure 71 Execution of the TISA Hardware demonstrator, from [J.5]                          |     |

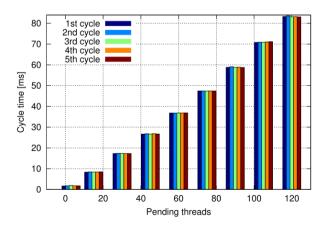

| Figure 72 TISA Scheduling Performances, from [J.5]                                         |     |

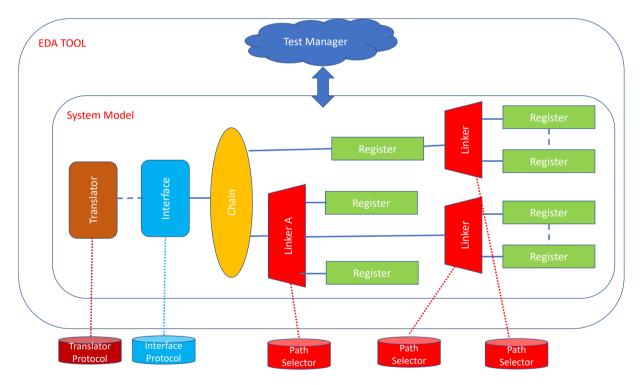

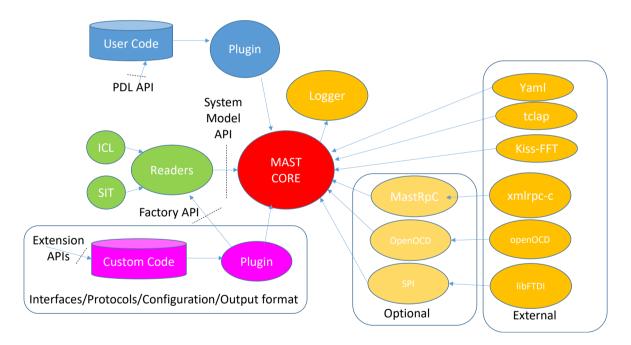

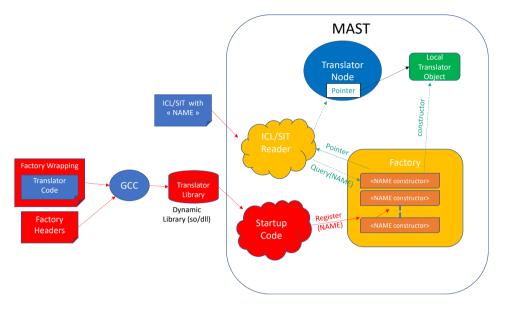

| Figure 73 Final MAST Software Architecture                                                 |     |

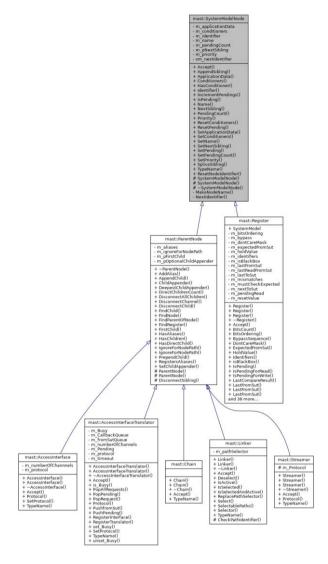

| Figure 74 Doxygen-Generated UML Class Diagram for MAST System Model                        | 93  |

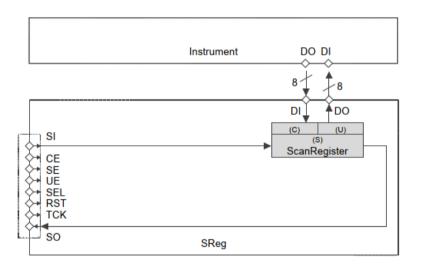

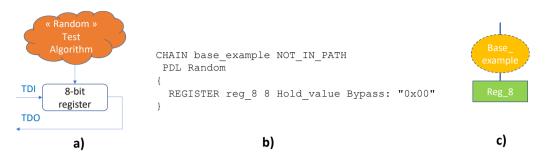

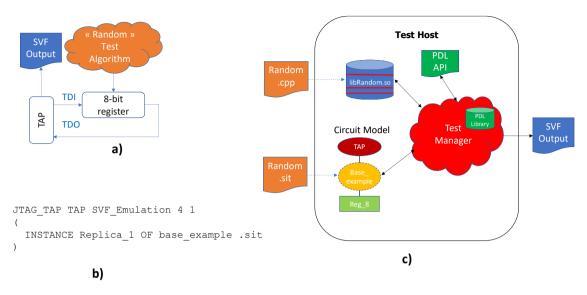

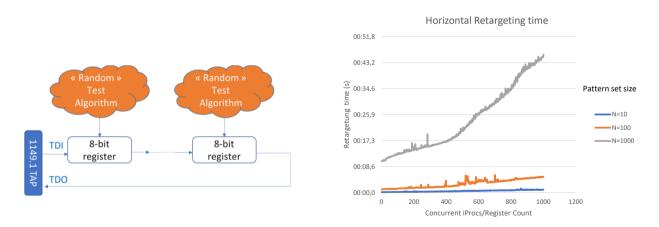

| Figure 75 Benchmark Module a), its SIT Description b) and the corresponding abstraction c) | 94  |

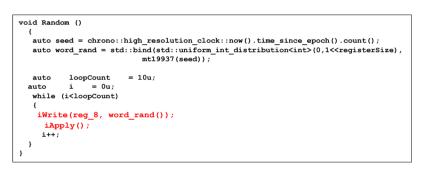

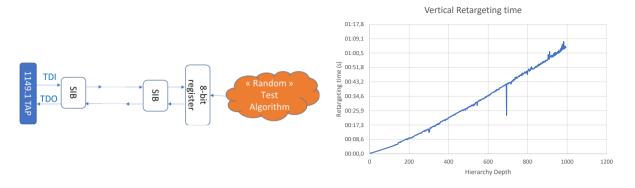

| Figure 76 "Random" Testbench algorithm                                                     | 94  |

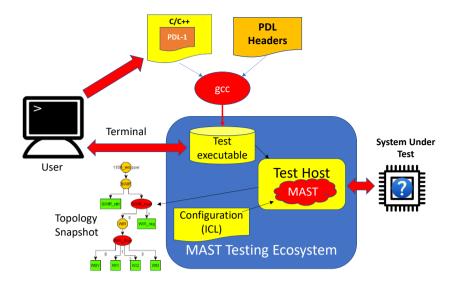

| Figure 77 Details of the MAST Compilation flow for the Testbench                           | 94  |

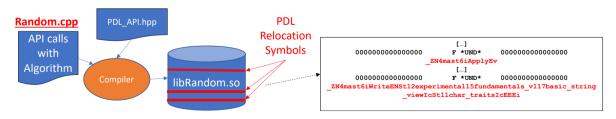

| Figure 78 Execution of the Random testbench                                                | 95  |

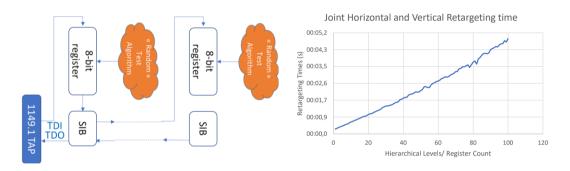

| Figure 79 MAST performances for Horizontal Retargeting [J.4]                               | 95  |

| Figure 80 MAST performances for Vertical Retargeting [J.4]                                 | 96  |

| Figure 81 MAST performances for joint Horizontal and Vertical Retargeting [J.4]            |     |

| Figure 82 First Domain Crossing Abstraction                                                | 97  |

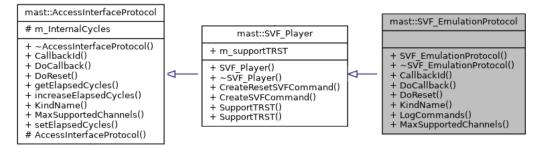

| Figure 83 UML Class Diagram for the SVF Emulation Protocol                                 | 98  |

| Figure 84 Propagation and synchronization of RVF packets inside MAST                       |     |

| Figure 85 RVF Packet flow for a T-2-T I2C-to-JTAG Translator                               | 99  |

| Figure 86 RVF Packet flow for a Bit-Banging I2C-to-JTAG Translator                         | 99  |

| Figure 87 Factory Pattern applied to Translators                                           |     |

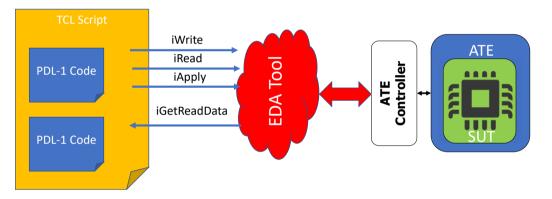

| Figure 88 Implicit PDL-1 Execution Model                                                   |     |

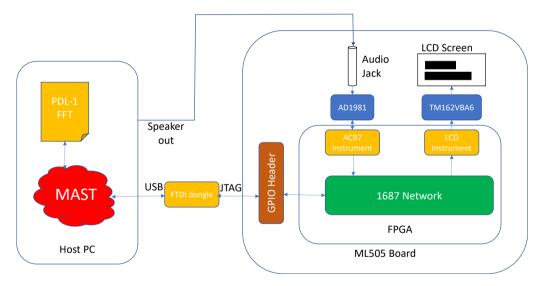

| Figure 89 Fully Interactive Flow with MAST                                                 | 102 |

| Figure 90 Top-Level Specification of the Interactive Demo                                  |     |

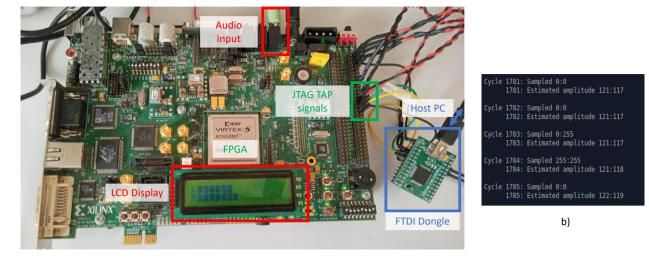

| Figure 91 Experimental setup for the Interactive Demo.                                     | 103 |

#### viii

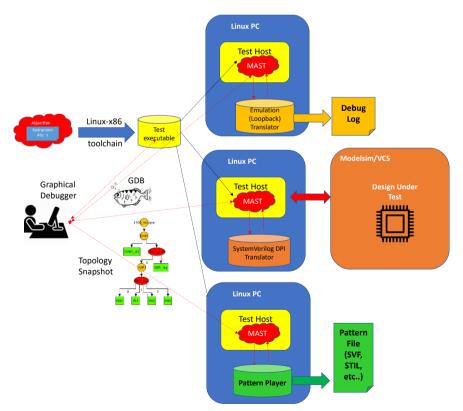

| Figure 92 MAST Portability through the Design Cycle                            |     |

|--------------------------------------------------------------------------------|-----|

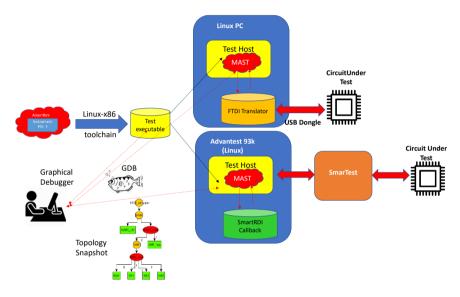

| Figure 93 Circuit Prototyping and ATE Bring-Up with MAST                       |     |

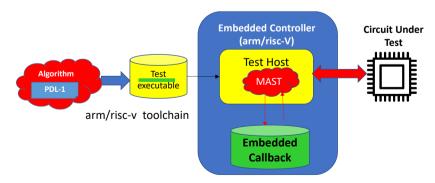

| Figure 94 Embedded Test Controller with MAST                                   |     |

| Figure 95 SSAK-Secured Scan Chain and its Abstraction                          |     |

| Figure 96 SIT Description of the SSAK example                                  |     |

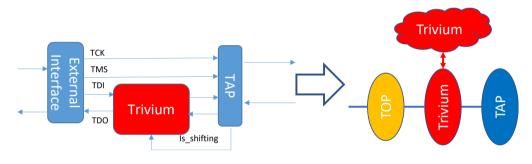

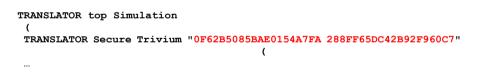

| Figure 97 Trivium Stream Cypher and its Abstraction                            |     |

| Figure 98 SIT Description of the Trivium Example                               |     |

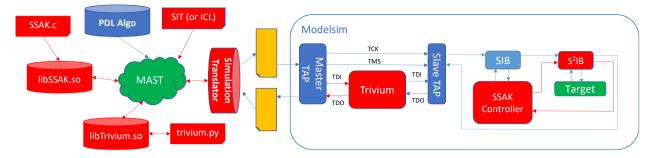

| Figure 99 Experimental Setup for Secure Scan Chain Access                      |     |

| Figure 100 Example of a P1687.2 system, from [VSTA20]                          |     |

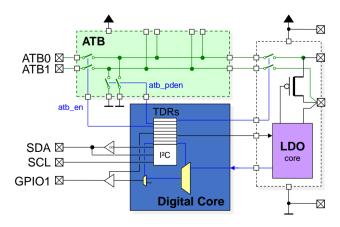

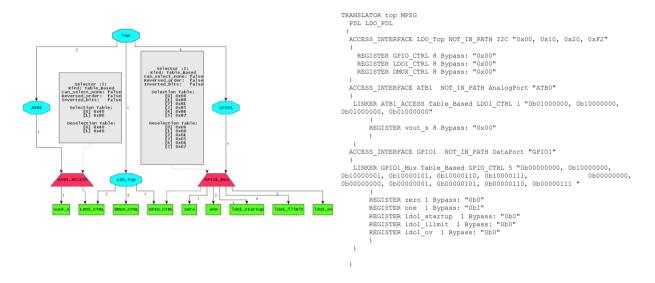

| Figure 101 PMIC Abstraction and its SIT representation                         | 109 |

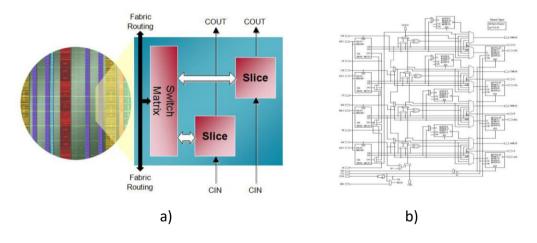

| Figure 102 Xilinx/AMD 7-Series High-Level architecture a) and Slice details b) | 111 |

|                                                                                |     |

# **Table Index**

| Table 1 First part of PDL Commands list, from [1687]                  | .47 |

|-----------------------------------------------------------------------|-----|

| Table 2 Second part of PDL Commands list, from [1687]                 |     |

| Table 3 PDL Level-1 commands, from [1687]                             | .48 |

| Table 4 Specification of the Relocatable Vector Format (RVF)          |     |

| Table 5 Technology Readiness Level definition, adapted from Wikipedia |     |

# Introduction

During his career, a Researcher naturally follows different directions and topics. There are many reasons: for personal interests, to exploit collaboration opportunities, to learn new skills, etc.. There is no need, and neither strictly speaking any value, in enforcing coherence between the different topics as long as it is possible to correctly apply and expand one own's competences and be able to contribute to the field. And, why not, taking pleasure in it.

The way a Scientific Theme is addressed is well-known: first, it must be studied to understand its current State of the Art and, more importantly, its Open Questions and Evolution Potential. Second, a Theoretical analysis must be applied to find the common elements, the missing ones and elaborate a strategy to introduce new ideas. Last, the Abstraction must be Implemented to demonstrate its feasibility and its real contribution. Once some results are reached, the cycle starts from the beginning: well-known does not mean easy.

In this document, after giving a through description of my career in Chapter 1 "Curriculum Vitae", I decided to focus on one of my Research Themes, which I had the opportunity to build from the ground up over a period of almost 15 years, from my first Role after my PhD to the current time through different positions and employers : the Evolutions of the Software Flow for Automated Testing.

As its name states, Chapter 2 gives the "Motivations and State of the Art" of the topic, while Chapter 3 "The need for a New Test Flow" tackles the issue by providing an in-depth Theoretical Analysis of the current shortcomings. Chapter 4 "A New Automated Test Flow: Specification" provides and justifies the final Abstraction to improve the filed. Chapter 5 "A New Automated Test Flow: Implementation" provides a description of the different iterations done over the years to refine the Abstraction, Implement it and use to provide innovative solutions. Based on these results, Chapters 6 provides the "Short-to-Mid Term Perspectives" of these topics. Lastly, Chapter 7 draws "Conclusions and Long-Term Directions" from a more general point of view.

# **1** Curriculum Vitae

#### 1.1 Curriculum Vitae

Name: Michele Portolan Birth Date: 9/7/1979 in Trento (Italy) Married Nationality: Italian Professional Address: ⊠ : TIMA Laboratory 46 Av. Felix Viallet 38031 Grenoble France Trance Sefection 2000 and 20000 and 2000 a

#### **Current Position**

Senior Associate Professor at Grenoble-INP Phelma, working at TIMA lab

#### Phelma Co-Head for the Major « Embedded Systems and Connected Objects »

#### **Professional Experience**

| Oct 2021-Today     | Senior Associate Professor at Grenoble-INP Phelma                       |

|--------------------|-------------------------------------------------------------------------|

| Sep 2018- Sep 2019 | Invited Professor at the Politecnico of Torino, Italy                   |

| Sep 2013- Sep 2021 | Associate Professor at Grenoble-INP Phelma                              |

| 2007 -August 2013  | Member of Techical Staff at Alcatel-Lucent Bell Labs Ireland and France |

| 2006-2007          | Lecturer at Institut National Polytechnique de Grenoble                 |

#### Academic Experience

| 2006           | PhD in Microelectronics, defended on December 6th 2006                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------|

| 2003 September | <b>Italian Master Degree in Electronics Engineering</b> , awarded by the Politecnico di Torino, grade 110/110 Cum Laude.  |

|                | Master of Advanced Studies (DEA) in Microelectronics, with honors, delivered by Université Joseph Fourier, Grenoble       |

| 2003 June      | <b>French Master Degree in Telecommunication Engineering</b> , with honors, delivered by the Département Télécoms of INPG |

#### Language Skills

| Italian  | Mother Tongue      |

|----------|--------------------|

| French   | Bilingual          |

| English  | Bilingual          |

| Japanese | Lower Intermediate |

#### Competences

Test Standards, Hardware Design Flow, Automated Test Flow, Software Design, C/C++, Operating Systems, Compilation and Languages, FPGA Prototyping, Embedded Systems, Reliability and Dependability, Hardware Safety and Security, Hardware/Software mixed systems, Modeling and Simulation, Fixed Networks and 3G/4G.

#### Internantional Scientific Experience

- Secretary of the IEEE 1687 Renewal Working Group.

- Signing member of the IEEE 1687-2014 Standard.

- Valorization Liaison for the TIMA Laboratory

- Member of the standardization working groups IEEE P1687.1, IEEE P2654

- 30+ publications at International Conference, 7 Journal Papers

- 17 US and European Patents, 100% grant rate.

- APP (Agence pour la Protection des Programmes) filings for protection of original software

- Coordinator of several internal projects in Bell Labs.

- « Development of a safe and secure Embedded System», PhD Thesis

#### **Teaching Experience**

- Responsible for Industrial Liaisons for the SEOC Major of Phelma

- Supervisor for several Master Degree internship

- Joint Supervisor of two PhDs

- Development of teaching support materials

- Head of the SLE (Embedded Systems and Software) from 2014 to 2017

- Co founder of the SEOC Major in 2017 as the fusion of SLE and ISSC (Signals, Internet, Services and Connected Systems)

#### Awards and Promotions

- Promotion to Senior Associate Professor, October 2021. Reserved to the top ~10/20% of Associate Professors

- Prime d'Encadrement et De Recherche (PEDR) (French Research and Supervision Bonus, awarded following an evaluation over 5 years of activity, awarded to the top 20%) 2020-2024

#### **International Experience**

- Global Coordinator of TTTC's « E.J. McCluskey Best Doctoral Thesis Award » 2013 → present

- Program Chair for the "1st Test Access, Automation and Adoption Workshop", 2021

- Chair of « 3rdTest Standards Application Workshop (TESTA) », 2018

- Vice General Chair of « 2ndTest Standards Application Workshop (TESTA) », 2017

- Organiser of « 1st International Test Standards Application Workshop (TESTA) », 2016

- Program Committee Member of the Latin-American Test symposium (LATS) since 2016

- « Awards co-Chair » for the « Test Technology Technical Council» (TTTC) since 2012

- « Industrial Liaison co-Chair » for the « 2012 European Testing Symposium » (ETS12), Annecy, France, Mai 2012

- « Peer Reviewer » International Conferences (ITC, ETS, DDECS, etc...) and journals (IEEE Design and Test, Journal of Electronic Testing : Theory and Applications » )

- « Publication Chair » for the « 12th International On-Line Testing Symposium » (IOLTS06), Como, Italy, July 2006

- « Audio-visual Chair » for the « 11th International On-Line Testing Symposium » (IOLTS05), Saint Raphael, France, July 2005

#### **Personal Interest and Hobbies**

- Classical, Medieval and Contemporary Literature (English, French and Italian)

- Road Cycling, Mountain Hiking, Golf

- Analog Film Photography

# **1.2** Teaching Activities

Classes taught as PhD candidate and Lecturer (2004 à 2007)

| Title                  | University          | Level | Year           | Hours  | Туре    |

|------------------------|---------------------|-------|----------------|--------|---------|

| Computer Architecture  | Département Télécom | BAC+4 | 2007           | 13,5h  | TD      |

| Operating Systems      | ENSERG              | BAC+4 | 2007           | 32h    | TD      |

| SoC Project            | ENSERG              | BAC+5 | 2006           | 24h    | Project |

| Computer Architecture  | Département Télécom | BAC+4 | 2006           | 10,5h  | TD      |

| Digital Circuit Design | Département Télécom | BAC+3 | 2006           | 15h    | TD      |

| VHDL                   | ENSERG              | BAC+4 | 2006           | 21h    | TD      |

| C Project              | ENSERG              | BAC+4 | 2004 à<br>2006 | 116h   | Project |

| Computer Architecture  | Département Télécom | BAC+3 | 2005           | 18h TP | Project |

| Computer Architecture  | Département Télécom | BAC+3 | 2006           | 32h    | Project |

| VLSI Design and Test   | Département Télécom | BAC+4 | 2004           | 6h     | TD      |

#### Classes taught as Associate Professor

| Digital Design                                          | University     | Level | Year                                 | Hours  | Туре   |

|---------------------------------------------------------|----------------|-------|--------------------------------------|--------|--------|

| System Integration                                      | Ensimag        | BAC+4 | 2013-14-15-16                        | ~15/an | СМ     |

| System Integration                                      | Ensimag        | BAC+4 | 2013                                 | ~18/an | TPTD   |

| Design of Integrated Digital Systems                    | Ensimag        | BAC+4 | 2017-19-20-21-22-<br>23              | ~20/an | TPTD   |

| Design of Integrated Digital Systems                    | Ensimag        | BAC+4 | 2017-19-20-21-22-<br>23              | ~15/an | СМ     |

| Implementation of a Embedded System U<br>Case           | Ensimag/Phelma | BAC+5 | 2013-14-15-16- 17-<br>19-20-21-22-23 | ~40/an | Projet |

| Design of mixed integrated functions                    | Phelma         | BAC+4 | 2014-15-16- 17-19<br>20-21-22-23*    | ~50/an | Projet |

| VLSI - ASIC + FPGA                                      | Phelma         | BAC+4 | 2014                                 | 12     | TPTD   |

| Analysis and integration of a complex integrated system | Phelma         | BAC+5 | 2016-17-19-20-21-<br>22              | ~30/an | Projet |

\* class scheduled in the second semester

| Reliability and Test | University | Level | Year             | Hours  | Туре |

|----------------------|------------|-------|------------------|--------|------|

| Fault Tolenance      | Ensimag    | BAC+5 | 2013-14-15-16-17 | ~27/an | СМ   |

| Test of circuits                  | Phelma         | BAC+5 | 2015-16-17-19-20-<br>21-22-23* | ~8/an  | TPTD |

|-----------------------------------|----------------|-------|--------------------------------|--------|------|

| Hardware Reliability and Security | Ensimag/Phelma | BAC+5 | 2019-20-21-22-23               | ~13/an | СМ   |

| Hardware Reliability and Security | Ensimag/Phelma | BAC+5 | 2019-20-21-22-23               | ~16/an | TP   |

\* class scheduled in the second semester

| Computer Science                              | University | Level | Year                           | Hours | Туре  |

|-----------------------------------------------|------------|-------|--------------------------------|-------|-------|

| Computers and Microprocessors                 | Phelma     | BAC+3 | 2014                           | 16    | TD    |

| Computer Science Project in C                 | Phelma     | BAC+4 | BAC+4 2014-15-16-17-19 - 20-21 |       | TPTD  |

| Computer Science Projet (SEI)                 | Phelma     | BAC+4 | 2014                           | 35    | TD+TP |

| Operating Systems and Parallel<br>Programming | Phelma     | BAC+4 | 2022                           | 6     | СМ    |

| Operating Systems and Parallel<br>Programming | Phelma     | BAC+4 | 2022                           | 22    | TD    |

| Operating Systems and Parallel<br>Programming | Phelma     | BAC+4 | 2022                           | 6     | TP    |

| Miscellanous                                                  | University | Level | Year                        | Hours  | Туре   |

|---------------------------------------------------------------|------------|-------|-----------------------------|--------|--------|

| Préorientation - SEI : Conception analogiq<br>et numérique    | Phelma     | BAC+3 | 2013                        | 8      | TD     |

| Préorientation - SLE : Circuits numériques                    | Phelma     | BAC+3 | 2013-14-14                  | ~20/an | TD     |

| Préorientation - SEOC - Systèm<br>Embarqués et Obj. Connectés | Phelma     | BAC+3 | 2016-17-19-20-21-<br>22-23* | ~9/an  | СМ     |

| Group Projects                                                | Phelma     | BAC+3 | 2014-15-16                  | ~16/an | Projet |

| Group Projects                                                | Phelma     | BAC+3 | 2015                        | 17     | Projet |

\* : heures prévues pour le deuxième semestre

| Tutoring and Oral Defenses                    | University | Level | Year                         | Hours  | Туре    |

|-----------------------------------------------|------------|-------|------------------------------|--------|---------|

| Retour d'Expérience (REX)                     | PHELMA     | BAC+4 | 2013                         | 1      | TD      |

| 2 <sup>nd</sup> Year Internship Tutor         | Phelma     | BAC+2 | 2013-14                      | 6      | Tutorat |

| 3 <sup>rd</sup> Year Internship Tutor         | ENSIMAG    | BAC+5 | 2013-2017-19-20-<br>21-22-23 | ~6/an  | PFE     |

| 3 <sup>rd</sup> Year Internship Oral Defenses | ENSIMAG    | BAC+5 | 2014-16-17-19-<br>2021-22-23 | ~25/an | PFE     |

| Tutoring for Apprentices | PHELMA | BAC+3 | 2013-14-15-16-17-<br>18-19-20 | ~10/an | Tutorat |

|--------------------------|--------|-------|-------------------------------|--------|---------|

| Industrial Projects      | Phelma | BAC+4 | 2016                          | 48     | PFE     |

\* : heures prévues pour le deuxième semestre

| Pedagogic Responsibilities                                         | University | Year                   | Hours  | Туре |  |

|--------------------------------------------------------------------|------------|------------------------|--------|------|--|

| Responsibility for SLE Major                                       | PHELMA     | 2013-14-15-16-17-19-20 | 24/an  | Resp |  |

| Responsibility for SEOC Major                                      | PHELMA     | 2021-22-23             | ~40/an | Resp |  |

| External Relationships with the "Grenoble University Space Center" | PHELMA     | 2015                   | 12     | Resp |  |

| Jury Pré sélection AP-CSI                                          | PHELMA     | 2016                   | 3      | Jury |  |

| Jury Pré sélection AP-CSI                                          | PHELMA     | 2017                   | 6      | Jury |  |

| Dossiers Admis Sur Titre (AST)                                     | PHELMA     | 2016-17-19             | 6/an   | Jury |  |

Doctoral Level Classes

|                                                  | University               | Level    | Year                    | Hours | Туре |

|--------------------------------------------------|--------------------------|----------|-------------------------|-------|------|

| Test and Design for Test for Integrated Circuits | Ecole doctorale<br>EEATS | Doctorat | 2014,16                 | 6     | СМ   |

| Advanced Techniques for Digital Testing          | Politecnico di<br>Torino | Doctorat | 2020,2021,2022,<br>2023 | ~8/an | СМ   |

#### Summary of hours taught per year:

| 2013- | 2014-  | 2015-  | 2016-  | 2017-   | 2018- | 2019- | 2020-  | 2021-  | 2022- |

|-------|--------|--------|--------|---------|-------|-------|--------|--------|-------|

| 2014  | 2015   | 2016   | 2017   | 2018    | 2019  | 2020  | 2021   | 2022   | 2023  |

| 200   | 410,75 | 346,25 | 373,75 | 295,75* | 192*  | 355*  | 344,75 | 372,75 | 348,5 |

\*years taking part of a MOISE inter-annual modulation

#### **1.3** Career Synthesis

When I arrived at the TIMA laboratory in 2013, my Research group was in a "down" phase: several big projects were coming to an end, and classic themes were looking for a new ideas and directions. In this context, I immediately took the 50% supervision of Kais Chibani's thesis, and I committed myself to both integrate the group's open themes and develop my own topics. In the theme of Reliability, we have unsuccessfully submitted several ANR subjects over the years, regularly reaching Phase 2, which prevented us from launching any PhD theses in this subject. At the same time, my Test theme was gaining strength and allowed me to obtain my own funding. Unfortunately, the durations of these Projects were too short to finance PhD, and I had to fall back on short-term contracts to have the subject mature and develop. Thanks to these results, in 2017 I was able to participate in the European HADES Project, which allowed me to start the 50% supervision of Kalpana Senthamarai Kannan's thesis. The withdrawal of the German partners forced a budget reduction, which prevented me from supervising a second Phd student. During the Project, I also actively participated in the supervision of the second doctoral student in our group, Vincent Reynaud, even though this was not planned in advance and therefore I was not officially registered as a supervisor. My participation allowed Vincent to broaden the scope of his thesis towards my own themes (Standards and EDA for Test), which resulted in several high-end joint publications. The results of Kalpana Senthamarai Kannan's work allowed us to begin a collaboration with the DAUIN laboratory at the Politecnico di Torino: in this context we were able to launch an ERAMUS + exchange to welcome a doctoral student, Sandro Sartoni, which I supervised during his stay in Grenoble and resulted in a joint publication.

In 2023, I started a new collaboration with Emmanuel Simeu from the "Reliable RF and Mixedsignal Systems" (RMS) group to explore the synergies between Digital and Mixed Signal testing; through the PhD Thesis of Jules Quentin Kouamo, started in November through a "Thèse flechée" of the EEATS Doctoral School.

#### **1.3.1 Project Participation:**

- ICT Standardisation Observatory and Support facility in Europe 6th Call (StandICT.eu 2023, part de H2020), "Advance Design-for-Test standards for complex electronics systems", Budget ~10k€ over 6 Moth, Project Owner

- Eramus + Project EMNESS (European Master Network On Embedded System Security 394.5 K€) - Work Package Leader et Phelma Referent.

- Europen Project HADES (Hierarchy-Aware and secure embedded test infrastructure for Dependability and performance Enhancement of integrated Systems 15 M€), 2017-2020, Task Leader, PhD Co-Supervisor

- Technology Maturation project MAST financed by Linksium, 2015-2016, (138,7 k€), Project Owner, Supervision of two Short-Term Contracts

- Technology Incubation project MAST financed by Linksium, 2017, (57,7 K€), Sceintific Advisor, Supersion of a Short-Term Contract

- IRS Project (Initiatives de Recherche Stratégiques) CADI, « Calcul Approché et Distribué dans les systèmes Intégrés », 2019, 10% research time, Supervision of two Master Degree Thesis

- IRS Project (Initiatives de Recherche Stratégiques) AVOCAM, « Analyse de durée de Vie pour l'Optimisation de Calcul Approché Matériel », 2020/2021, 20% research time, Supervision of three Master Degree Thesis

- IRT40 Cybersécurité, Development of lab classes dedicated to Hardware Security UGA/G-INP, années 2020-2021 (21k) 20% research time, Supervision of one Master Degree Thesis

#### 1.3.2 Supervisions and Management

#### 1.3.2.1 PhD:

- Jules Quention Kouamo, PhD with the Université de Grenoble, started in November 2023, 50% supervision with Emmanuel Simeu, Professor at UGA

- Senthamarai Kannan Kalpana, PhD with the Université de Grenoble, Defended on July 2015, 50% supervision with Lorena Anghel, Professor at G-INP → now FPGA Firmware Engineer at ASML, Netherlands

- 3. Chibani Kais, PhD with the Université de Grenoble, Defended in 2016, 50% supervision with Régis Leveugle, Professor at G-INP → now Sr. Digital Verification Engineer at ST Microelectronics, Grenoble

#### 1.3.2.2 Erasmus + :

Sandro Sartoni, Doctorant au Politecnico di Torino, Italie, April 2022 -July 2022. Subject: Aging Prediction for a RISC-V processor in FDSOI 28nm

#### 1.3.2.3 Master Thesis

- 1. Mert Arisoy, Politecnico di Torino, Italy;

- 2. Pierpaolo Iannicelli, Politecnico di Torino, Italy ;

- 3. Xavier Gros, Master 2 MISTRE, UGA, Grenoble

- 4. Atoine Cerf, Master 2 MISTRE, UGA, Grenoble

- 5. Provent Thomas, M2 Université Claude Bernard Lyon 1;

- 6. Muller Meireles Assumpçao Joao Pedro, ENSIMAG ;

- 7. Josef Ahmad, Politecnico di Torino, Italy;

#### 1.3.2.4 Short Term Contracts

- 1. Coulon Jean-Francois, 15 month over three contracts between 2016 and 2017;

- 2. Niels Grateloup, 3 months in 2016

#### 1.3.2.5 PhD Jurys

I participated to several PhD Jurys, being also a Reviewer in Italy where the rules allowed me to. I have been proposed to be reviewer for Elshamy, but I had to decline because of my lack of HdR.

- 2021 : Jury Member for Mohamed Elshamy, Université de la Sorbonne, Laboratoire LIP6, France, July 2021

- 2021 : Reviewer for Davide Piumatti, Politecnico di Torino Doctorate School, Italy, February 2020

- 2020 : Reviewer for Marco Restifo, Politecnico di Torino Doctorate School, Italy, February 2020

- 2017 : Reviewer for Alejandro Velasco, Politecnico di Torino Doctorate School, Italy, February 2020

- 2017 : Jury Member for Riccardo Cantoro, Politecnico di Torino Doctorate School, Italy, February 2020

- 2015 : Jury President for the XXVII cycle of the « Phd in Computer Science and Information Systems "of the Politecnico di Torino Doctorate School, Italy

#### 1.3.2.6 Recruitment Jurys

Member of the Recruitment jury for an Associate Professor (Maitre de Conférences Section 63) at the INP Toulouse, May 2019

#### 1.4 Scientific Themes

Since my PhD, I worked on several scientific themes, of which I will give a brief summary in this section. However, in the rest of the document, I decided to develop in details my main Scientific Theme: Software Methods for Next-Generation Test Standards. It is a line of Research that I have been developing on my own since my arrival in Bell Labs Ireland in 2007 over a span of more than 15 years.

#### 1.4.1 Software Methods for Next-Generation Test Standards

The complexity of today's electronic systems, the production volumes and the quality imposed by critical applications such as the automobile are putting traditional testing approaches under great pressure. To overcome this problem, the testing field is going through a period of profound evolution, dominated by new "Design for Test" techniques that push automation to the very heart of systems. This field has always been dominated by the simple and extremely effective "Scan Test" for structural testing, where the integrity of a circuit is checked by seeing it as a network of nodes. These approaches have difficulty following system scaling because of their combinatorial complexity. Moreover, they are not at all adapted to new design paradigms such as "IP-based Design" or to new issues such as security. Often seen by Academics as mere collections of already existing solutions, Standards are on the contrary very powerful tools for pushing new approaches towards manufacturers, who see in standardization a guarantee of quality and support. My direct experience in the development of the P1687 standard between 2007 and 2014 allowed me to foresee its impact on current practices and development flows. In particular, I identified a series of criticalities in the associated EDA tools, caused by the axioms and paradigms which are at their heart, and which cannot be resolved through simple incremental corrections. This research theme is therefore based on the analysis and theoretical abstraction of current practices to formalize new needs and develop the corresponding software suites. This line of research generated several publications, as well a Technology Transfer project, with several APP (Software Protection) filings and a Patent. It should be noted that this Patent is an integral part of the current proposal to the IEEE P1687.1 Standard Working Group and it was therefore the subject of a "Letter of Assurance for Essential Patent Claims" to the IEEE, which guarantees its possible commercial exploitation. future.

The PhDs of Kalapana Senthamarai Kannan and Jules Quention Kouamo, are part of this line of research as explorations of long-term impact and applications.

#### 1.4.1.1 Kalapana Senthamarai Kannan: "Performance and Safety/Security Management in automotive and IoT Application"

Due to technology scaling and transistor size getting smaller and closer to atomic size, the last generation of CMOS technologies such as FDSOI presents important variability of several physical parameters. As a consequence, it becomes more and more difficult to guarantee circuit functionality for all Process, Voltage, Temperature (PVT) corners and in turn, to compensate for different sources of variability. Moreover, circuit wear-out degradation leads to additional temporal variations, potentially resulting in timing and functional failures. Under normal operation conditions, a transistor can be affected by various aging effects such as Hot Carrier Injection (HCI), Negative/Positive Bias Temperature Instability (NBTI,PBTI), and TimeDependent Dielectric Breakdown (TDDB). In advanced technologies, such as FDSOI, local and global variability, NBTI and HCI phenomena are considered as critical reliability issues. Hence, considering these phenomena as early as possible in the design steps (i.e. during the standard cells characterization step, or at the circuit and system design) are mandatory, especially for high reliable application such as automotive applications, or mixed critical applications.

Indeed, the above-mentioned reliability threats can severely degrade performances, and in the worst case, provoke system failures, affecting safety goals of critical reliable systems. Accurate simulations with physical degradation models of aging phenomena combined with actual silicon measures are, de facto, necessary to better understand and assess the reliability impact on complex digital designs. To handle such problems, one conventional method consists in providing bigger safety margins (also called guard bands) at design-time. Adding pessimistic timing margins (or their equivalent voltage margins) to guarantee all Operating Points under worse case conditions is not possible anymore due to the huge impact on design costs, with an upward trend as technology moves further. Therefore, the usage of delay violation monitors, usually placed at the end of potential critical paths, becomes necessary. Placing the monitors in a given design is a critical task: the designer has to select the endpoints that will age the most, as it may become a potential point of failure. Monitor warnings signals can trigger adaptive techniques, such as Adaptive Voltage Scaling (AVS) or Dynamic Voltage Frequency Scaling (DVFS). They are then used to adapt dynamically the frequency and the voltage according to the operating conditions and the application needs. In addition to the reduction of design margin, monitors also help compensate performance and power degradation. Sometimes, the circuit's lifetime can be extended. It is worth noticing that the area overhead induced by the monitor placement should be carefully considered and should remain reasonable. The number of selected endpoints for monitor insertion should be as small as possible, but still cover the most important critical endpoints of the design. However, endpoint selection is an extremely complex task which requires a deep knowledge of both the target technology and the final workload.

To alleviate these restrictions, in this PhD we explored Machine Learning approaches to find methods that starting from a limited set of technological parameters are able to efficiently predict the delay degradation of paths depending on a given workload and available Operating Performance Points (OPP) expressed in terms of Voltage and Frequency. The aim was to obtain a lightweight, embeddable solution that can be used in conjunction with delay violation monitors in order to alleviate monitor insertion complex task, but also and to identify the best OPPs following different optimization strategies. The ML framework obtained during this PhD has been validated and compared with the State-of-the-Art data with excellent results, and used as the base of innovative System-level applications to identify Aging-aware Path Slack Ranking and proposes an adaptative OPP strategy optimizing both performance and lifetime.

# 1.4.1.2 Jules Quentin KOUAMO: Software Methods and Architectures for the test of Mixed-Signal SoCs

The complexity of current electronic systems, the production volumes and the quality level required in critical applications, like for instance in automotive, challenge traditional approaches

to testing integrated systems. To overcome these difficulties, the field of testing is currently undergoing a period of profound evolution, dominated by new "Design for Test" techniques which push automation to the very heart of systems. This field has long been dominated by "Scan Test", which is simple and very effective for structural testing, which consists of verifying the integrity of the circuit as a network of nodes. However, these approaches have difficulty in keeping up with the scaling of systems due to their combinatorial complexity. In addition, they are not at all adapted to new design paradigms such as "Design by IP" or to systems that integrate analog modules, the tests of which are often functional and interactive. Often seen by Academics as collections of already existing solutions, Standards are on the contrary very powerful tools for transferring new approaches to industry, where standardization is seen as a guarantee of quality and support. This is particularly true for the IEEE 1687-2014 standard, also known as "Internal JTAG", which for the first time integrates functional testing and dynamic architectures at the very heart of its proposal. Unfortunately, the most innovative and disruptive elements of the standard are not integrated into current CAD flows, which are rather focused on incremental developments with high ROI (Return Of Investment). The importance and weight of Analog in modern System-on-Chip (SoC) continues to grow, but its complex interaction with Digital has not yet been fully explored. Several initiatives are underway, including an attempt to extend IJTAG to analog testing thanks to the IEEE P1687.2 standardization committee. While custom solutions to specific problems exist, the systematic consideration of the peculiar constraints of these areas for a unified and coherent solution has never been addressed. For example, analog testing is dominated by Built-In-Self-Test (BIST), where a hardware component is developed adhoc and integrated into the chip, with almost no interaction with the outside. This is of course efficient, but takes a long time to develop and is very resource-intensive.

The work proposed in this thesis aims to develop an infrastructure that will allow for hybrid software and hardware approaches optimized according to the needs of designers. Particular attention will be paid to the life cycle: a Mixed-Signal System must pass through multiple phases of Design, Validation and Test, and each has its own tools and constraints which make information sharing and solution porting almost impossible. An objective of the thesis work is to fill the technological "gap" between these stages and to evaluate the feasibility of a unified approach.

#### 1.4.2 Early Reliability and Security Analysis

Today's computing is a true continuum that runs from IoT devices or smartphones to large, mission-critical data center servers, often performing crucial tasks. In this context, the security and reliability of microprocessor-based computer systems are therefore major challenges. The concepts are closely related: while reliability defines the probability that a system will not be subject to failures, safety guarantees that even in the presence of such failures, the system will not generate any dangerous results. While the first describes a characteristic of the system itself, the second is more focused on the interaction with the environment, and therefore its usage. Faults

affecting hardware components (e.g., microprocessor, memory,) are then propagated through the software and can induce failures such as loss of information, incorrect behavior, up to complete unavailability of the system. All this can be described in terms of reliability or security. These qualities are now mainly quantified through costly and complex Fault Injection or Radiation campaigns. This means that a new campaign must be performed for each software or hardware change. Additionally, at an early stage of design, the final architecture of the microprocessor may not yet be defined. These campaigns can therefore be very long and impact Time-To-Market, especially if reliability levels are not achieved and a correction of part of the system is necessary. This research theme is therefore focused on the research and formalization of alternative approaches allowing early analysis: light from a computational point of view but still precise, it is capable of coherently identifying critical elements of hardware and software. The goal is to obtain a set of tools that can be used repeatedly during the design phase to ensure that the final system will meet the target reliability and security constraints. This is one of the driving themes of my TIMA research group that I have pursued since my thesis work, and which has enabled significant scientific advances and also an industrial impact, evidenced by the APP deposit of the EARS software resulting from this thematic and the thesis of Kais Chibani which I co-supervised with Régis Leveugle.

#### 1.4.2.1 Kais Chibani "Robustness analysis of Integrated Digital Systems"

Many applications are today concerned with soft errors, i.e. spurious bit modifications occurring in a circuit at runtime. Such errors can be provoked by environmental disturbances, without any physical defect induced in the circuit. In some cases, they can also result from malicious attacks. No matter their origin, a designer must consider the potential consequences of such errors. It is well known that not all soft errors lead to application failures; the probability of failure strongly depends not only on the target circuit's architecture, but also on the application characteristics, the induced usage of the hardware elements and the execution scenario. The real sensitivity of a circuit (defined here as the probability of failure, assuming a soft error occurred) must therefore be evaluated with respect to a given situation in order to avoid large over-estimations.

The first type of analysis required at design time is an evaluation of the intrinsic sensitivity. If the probability of failure is too large with respect to the application requirements, mitigation techniques can then be applied on the most critical parts. In this work, we focus on the intrinsic sensitivity evaluation, before any specific method is implemented for fault tolerance. However, the analysis must allow a designer to identify the most critical parts for selective hardening. The analysis must also be done early in the design flow in order to reduce the cost of rework or mitigation insertion, when necessary. Preliminary analyses can occur very early, based on the pure behavioral descriptions of the circuit, obtaining what is usually called an Architecture Vulnerability Factor. However, these analyses are usually extremely conservative and tend to over-estimate the sensibility of the system, resulting in high overheads which are not always acceptable. In order to obtain accurate quantifications, the registers actually implemented in the final circuit and potentially subject to soft errors must be known – a Register-Transfer Level (RTL) description is therefore often the earliest used in the studies. In this work, we will assume that

such a description is available, as well as a testbench defining an execution scenario representative of the use of the circuit in the final system. The precise sensitivity is usually evaluated by means of fault injection campaigns, which require a specific set-up, can be very long and expensive and can be performed only when the final circuit is available. As a result, if a major weakness is found, a redesign iteration can be extremely long and directly impact the whole project's timeline.

In this PhD, the focus is to avoid fault injections and the need for specific equipment or skills. The aim is to obtains tools and strategies that can be applied early in the design flow to obtain robustness estimations which can help the Designer's choices. The results are not meant to give a precise value of the system's robustness, but rather to identify the components which are more critical, so that they might be selectively hardened. This loop evaluation → hardening should be lightweight enough to be repeatable several times in the Design phase to obtain incremental gains and increase the confidence in the system's robustness. To estimate the "criticality" of an element, this work relied on the most classical metric, i.e. lifetime of data in the registers. At a given moment in time, not all flip-flops in a circuit contain useful data, while data re-used after a large number of clock cycles has a higher probability to be corrupted by random disturbances than some piece of information used only during a few cycles. So, the more often a register is "alive", i.e. it contains data that will be reused later, the more critical it will be.

The work started by making an architecture analysis of an existing open source processor, the Leon 3: we built a model of its Pipeline with a particular emphasis on the data transfer between registers (both visible to the User or hidden in the Architecture), and used traces from an execution to compute the Lifetime of each one of them. This proved the feasibility of the approach and its capability to provide estimate coherent with the State of the Art. We then moved to main part of the PhD, where we extended the approach to generic Digital Circuits expressed in RTL (VHDL). The resulting tool, called EARS, was able to give precise estimations of the criticality of each Register in the circuit with no a-priori information on its architecture by analyzing the simulation traces of a given payload against an internal model of the circuit. As opposed to simulation-based fault injections, only one simulation has to be run, with an important performance gain. The approach was run on the Leon 3 VHDL description for several workloads and consistently provided result coherent with emulation-based fault injections, but at a fraction of the computational effort. The EARS tool has been the subject of an APP depot, and has been reused several times in the context of TIMA's research in this subject.

#### 1.4.3 Design Exploration for Approximate Computing

Approximate computing is a design methodology aimed at increasing the efficiency of electronics systems. As its name suggests, it involves accepting a result which is not necessarily exact, on condition of gaining in terms of energy consumption, calculation speed and/or complexity of the implemented system. Of course, an exact calculation must not be essential for correct operation. The loss of precision must then remain within a "reasonable" margin of error. To situate some of the areas of application, it is of course possible to mention image processing for which, for example, the exact value of a certain percentage of pixels might no impact on the finale result (ex: "light green" or "dark green" in a traffic light recognition). Major application areas currently include classification problems, artificial intelligence, etc. In addition to the relative novelty of

this type of approach (it is still considered "a new calculation paradigm"), the main obstacle to its application comes from the difficulty for a designer to be able to evaluate early enough and effectively which part of the system can be approximated without unacceptably degrading the service provided to the user. This new theme, coming directly from my Visiting Professor period of 2018-2019, is a synergy between TIMA's own themes (most notably, the EARS tool developed by Kais Chibani) and the research of the Politecnico di Torino focused on the statistical study of the effects of local approximations on the overall result. In the literature, the choice of elements to be approximated is always left to the expertise of the developer through qualitative and adhoc analyses: if the error measured is unacceptable, the only choice is to start from scratch, with a considerable cost. In this theme, possible thanks to the complementary skills of TIMA and Politecnico, we reverse the problem and aim at the formalization and development of automated methods and tools capable of analyzing a system and identifying the circuit areas that can be approximated with the least impact on the final result, with considerable savings in time and resources during specification and design.

#### 1.4.4 Autonomous deployment of Small Cells

When deploying dense cellular networks, Quality of Service (QoS) depends not only by the Area Coverage, but from a multiplicity of dynamic parameters, such as for instance the user density, their usage behavior or their movement patterns. These conditions are extremely difficult to estimate through a priori models. Moreover, in the early 2000's a new deployment paradigm started being developed by actors such as Alcatel-Lucent: Small Cells. The correct term would rather we "a base station inside a small box": a PC-sized cabinet able to support a small number of users (usually a few dozens) in a restricted area. The concept has been pushed even further with the introduction of "femto cells", small boxes able to provide 3G coverage in a really small area (usually no more than 20-30 meters) to half a dozen users, and using the ADSL Box as backhaul. These have been commercially distributed under the name of either "femto cells" or "range extenders". As they are supposed to be plug-and-play into unknown environments (usually in close spaces) their centralized management and optimization is close to impossible. Upon me joining Bell Labs Ireland, a lot of work had been done in developing autonomous QoS genetic optimization algorithms, but all were based on centralized Matlab simulations. In this topic, I focused on the porting of these approaches to real-world scenarios by providing an abstraction from the Matlab simulation based on measurable distributed values, and ported a demonstrator on an actual Alcatel-Lucent product: a femto cell based on a Montavista Linux and IBM Rational Rose, commercialized by Vodaphone. Even though the results were promising, I was forced to interrupt this line of research when I moved to TIMA and lost access to the Alcatel-Lucent Intellectual Property.

### 1.5 Publications

#### ORCID profile: https://orcid.org/0000-0002-8284-3823

- Journal Publications

- [J.1] L. Anghel, R. Cantoro, R. Masante, M. Portolan, S. Sartoni and M. S. Reorda, "Self-Test Library Generation for In-field Test of Path Delay faults," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, doi: 10.1109/TCAD.2023.3268210.

- [J.2] M. Portolan, E. Valea, P. Maistri, G. Di Natale, "Flexible and Portable Management of Secure Scan Implementations Exploiting P1687.1 Extensions", IEEE Design & Test on 30/9.2021, DOI : 10.1109/MDAT.2021.3117875

- [J.3] K. Kannan, M. Portolan, L. Anghel, "Activity-aware prediction of Critical Paths Aging in FDSOI technologies", Microelectronics Reliability Volume 124, September 2021, 114261, https://doi.org/10.1016/j.microrel.2021. 114261

- [J.4] **Portolan M.**, "Automated Test Flow: the Present and the Future", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (IEEE-TCAD), December 2019, DOI:10.1109/TCAD.2019.2961328

- [J.5] **Portolan M.**, Goyal S., Van Treuren B.,, «Executing IJTAG: Are Vectors Enough? » IEEE Design & Test, vol.30, no.5, pp.15,25, Oct. 2013

- [J.6] Portolan M., Goyal S., Van Treuren B., Chiang C\_H., Chakraborty T. and Cook T.B., « A Common Language Framework for Next-Generation Embedded Testing » IEEE Design & Test of Computers Volume: 27, Issue: 5 , Pp: 36 – 49, 2010

- [J.7] Portolan M., Leveugle R., « A Highly Flexible Hardened RTL Processor Core Based on LEON », IEEE Transactions on Nuclear Science (IEEE-TNS), Volume 53, Issue 4, Part 1, Aug. 2006 Page(s):2069 - 2075

- <u>Standards:</u>

- 1687-2014 IEEE Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device, Electronic ISBN: 978-0-7381-9416-5, DOI: 10.1109/IEEESTD.2014.6974961, 5 Dec. 2014

- <u>Proceedings in International Conferences</u>

- [1] M. Portolan, V. Reynaud, P.Maistri, R. Leveugle, G. Di Natale "Security EDA Extension through P1687.1 and 1687 Callbacks", 2021 International Test Conference (ITC21), November 2021, ISBN: 978-1-6654-1695-5, ISSN: 2378-2250

- [2] Maistri P., Reynaud V., Portolan M., Leveugle R. " Secure Test with RSNs: Seamless Authenticated Extended Confidentiality ", 19th IEEE International New Circuits and Systems Conference (NEWCAS), June 2021

- [3] H. -M. von Staudt, B. Van Treuren, J. Rearick, M. Portolan and M. Keim, "Exploring and Comparing IEEE P1687.1 and IEEE 1687 Modeling of Non-TAP Interfaces," 2021 IEEE European Test Symposium (ETS), 2021, pp. 1-10, doi: 10.1109/ETS50041.2021.9465438.

- [4] M. Laisne, A. Crouch, M. Portolan,; M. Keim, H.M. Von Staudt, M. Abdalwahab, B. Van Treuren, J. Rearick,, "Modeling Novel Non-JTAG IEEE 1687-Like Architectures", 2020 International Test Conference (ITC20), November 2020, Washington DC, US

- [5] L. Anghel, R. Cantoro, D. Foti, M. Portolan, S. Santoni. M. Sonza Reorda, "New Perspectives on Core In-Field Path-Delay Test", 2020 International Test Conference (ITC20), November 2020, Washington DC, US

- [6] Portolan M. et al., "A Comprehensive End-to-end Solution for a Secure and Dynamic Mixed-signal 1687 System", 2020 International Symposium on On-Line Testing and Robust System Design (IOLTS 2020), Naples, Italy

- [7] Portolan M., Reynaud V., Maistri P., Leveugle R., "Dynamic Authentication-Based Secure Access to Test Infrastructure", 2020 European Test Symposium (ETS 2020), Tallin, ESTONIA, 25 mai au 1 juin 2020

- [8] Portolan M., Rearick J., Keim M., Linking Chip, Board, and System Test via Standards", 2020 European Test Symposium (ETS 2020), Tallinn, ESTONIA, 25 mai au 1 juin 2020

- [9] A. Damljanovic, A. Jutman, M. Portolan, E. Sanchez, G. Squillero, A. Tsertov, "Simulation-based Equivalence Checking between IEEE 1687 ICL and RTL", 2019 International Test Conference, November 2019

- [10] M. Portolan, R. Cantoro, E. Sanchez, "A Functional Approach to Test and Debug of IEEE 1687 Reconfigurable Networks", 2019 European Test Symposium, May 2019

- [11] A. Savino, M. Portolan, S. Di Carlo and R. Leveugle, "Approximate computing design exploration through data lifetime metrics", 2019 European Test Symposium, May 2019

- [12] R. Leveugle, M. Portolan, S. Di Carlo, A. Savino, G. Di Natale and A. Bosio,

"Alternatives to Fault Injections for Early Safety/Security Evaluations", Embedded Tutorial at the 2019 European Test Symposium, May 2019

- [13] M. Portolan, M. J. Barragan, R.Alhakim, S. Mir, "Mixed-signal BIST computation offloading using IEEE 1687", 2017 22nd IEEE European Test Symposium (ETS), Year: 2017, Pages: 1 - 2, DOI: 10.1109/ETS.2017.7968222

- [14] G. Di Natale, M. Kooli ; A. Bosio, M. Portolan, R.Leveugle, "Reliability of computing systems: From flip flops to variables", 2017 IEEE 23rd International Symposium on On-Line Testing and Robust System Design (IOLTS), 2017

- [15] Portolan M., "Accessing 1687 systems using arbitrary protocols", 2016 IEEE International Test Conference (ITC), Year: 2016, Pages: 1 - 9, DOI: 10.1109/TEST.2016.7805839

- [16] <u>K. Chibani</u>; M. Portolan; R. Leveugle, "Evaluating application-aware soft error effects in digital circuits without fault injections or probabilistic computations", 2016 IEEE 22nd International Symposium on On-Line Testing and Robust System Design (IOLTS), Year: 2016, Pages: 54 - 59, DOI: 10.1109/IOLTS.2016.7604672

- [17] M. Portolan, R. Rolland, "Student-driven development of a digital tester", 2016

11th European Workshop on Microelectronics Education (EWME), Year: 2016,

Pages: 1 3, DOI: 10.1109/EWME.2016.7496479

- [18] <u>K Chibani</u>, **M Portolan**, R Leveugle, "Application-aware soft error sensitivity evaluation without fault injections-Application to Leon3", European Conference on Radiation and its Effects on Components and Systems (RADECS'16), 2016

- [19] Portolan M., "A novel test generation and application flow for functional access to IEEE 1687 instruments", 21th IEEE European Test Symposium (ETS), Year: 2016, Pages: 1 - 6, DOI: 10.1109/ETS.2016.7519302

- [20] <u>K Chibani</u>, M Ben-Jrad, **M Portolan**, R Leveugle, "Fast accurate evaluation of register lifetime and criticality in a pipelined microprocessor", Very Large Scale Integration (VLSI-SoC), 2014 22nd International Conference on, October

- [21] <u>K. Chibani</u>, **M Portolan**, R Leveugle, "Fast register criticality evaluation in a SPARC microprocessor", Microelectronics and Electronics (PRIME), 2014 10th Conference on Ph. D. Research in, June 2014

- [22] <u>K. Chibani</u>; S. Bergaoui; M. Portolan; R. Leveugle, "Criticality evaluation of embedded software running on a pipelined microprocessor and impact of compilation options", 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2014

- [23] Cherubini D., Portolan M., "Automatic Equivalent Model Generation and Evolution for Small Cell Networks", Fourth International Workshop on Indoor and Outdoor Small Cells 2013 (WiOPT), Tsukuba, Japan, Mai 2013

- [24] **Portolan M.**, « Packet-based JTAG for remote testing », 2012 International Test Conference (ITC12), Anaheim CA, 4-9 November 2012

- [25] Portolan M., Goyal S. and Van Treuren B., « Scan chain Securization through Open-circuit Deadlocks », Poster for the 2010 International Test Conference (ITC10), Austin TX, November 2010

- [26] Portolan M., Goyal S. and Van Treuren B., « Scalable and efficient integrated test architecture », 2009 International Test Conference (ITC09), Austin TX, November 2009

- [27] Vanhauwaert, P.; Portolan, M.; Leveugle, R.; Roche, P., « Usefulness and effectiveness of HW and SW protection mechanisms in a processor-based system», 15th IEEE International Conference on Electronics, Circuits and Systems (ICECS 2008), 2008

- [28] Portolan M., Goyal S., Van Treuren B., Chiang C\_H., Chakraborty T. and Cook T.B., « A New Language Approach for IJTAG», 2008 International Test Conference (ITC08), San Francisco CA, October 26-30 2008

- [29] Portolan M., Leveugle R., « A Highly Flexible Hardened RTL Processor Core Based on LEON », 8th European Conference on Radiation and Its Effects on Components and Systems (RADECS 05) – 2005

- [30] Portolan M., Leveugle R., « Towards a Secure and Reliable System » 2005 IFIP International Conference on Embedded and Ubiquitous Computing (EUC'2005) – 2005

- [31] Portolan M., Leveugle R., « On The Need for Common Evaluation Methods for Fault Tolerance Costs in Microprocessors » 11th International On-Line Testing Symposyum (IOLTS05) – 2005

- [32] Portolan M., Leveugle R., « Operating systems function Reuse to achieve Low-Cost Fault-Tolerance », 10th International On-Line Testing Symposyum (IOLTS04) – 2004

- [33] Portolan M., Leveugle R., « A Context-Switch Based checkpoint And Rollback Scheme » –XIX Conference on Design of Circuits and Integrated Systems (DCIS 04) – 2004

- Workshops et Posters

- [W1] "Targeting Approximation through Data Lifetime: A Quest for Optimization Metrics", A. Savino, M. Portolan, S. Di Carlo and R. Leveugle, AxC 2019 : Fourth Workshop on Approximate Computing, May 2019

- [W2] M.Portolan, R.Cantoro, E.Sanchez, M. Reorda, "A Functional Approach to Test and Debug of IEEE 1687 Reconfigurable Networks", 2018 International Test Conference, October 2018

- [W3] <u>K. Kannan</u>, **M. Portolan**, L. Anghel ,"Run-Time Aging Prediction Through Machine-Learning", ", 2018 International Test Conference, October 2018

- [W4] M. Portolan, M. J. Barragan, H. Malloug, S. Mir, "Interactive Mixed-Signal Testing Through 1687", First International Test Standards Application Workshop (TESTA'16)

- [W5] Portolan M., Goyal S., Van Treuren B. « A New Execution Model for Interactive JTAG Applications », 2013 European Test Symposium (ETS13), Avignon, France, May 2013

- [W6] Portolan M., Goyal S., Van Treuren B., Chiang C\_H., Chakraborty T. and Cook T.B., « A new description language for SoC testing », 2008 European Test Symposium (ETS08), Verbania, Italy, May 25-29, 2008

- [W7] Portolan M., Goyal S., Van Treuren B., Chiang C\_H., Chakraborty T. and Cook T.B., « A Novel Hardware Description language for efficient debug and diagnosis of digital circuits », 2008 IEEE International Workshop on Silicon Debug and Diagnosis (SDD2008), San Diego, CA, April 27- May 1st, 2008

- <u>National conferences</u>

Portolan M., Leveugle R., « Réalisation d'une Tolérance aux Fautes à Bas Coût dans les SoCs en Utilisant le Système d'Exploitation » – Actes des Journées Nationales du Réseau Doctoral de Microélectronique – 2004

- Invited Presentations