## Machine learning for timing estimation

Abderaouf Nassim Amalou

#### ▶ To cite this version:

Abderaouf Nassim Amalou. Machine learning for timing estimation. Computer Science [cs]. Université de Rennes, 2023. English. NNT: . tel-04406029

### HAL Id: tel-04406029

https://hal.science/tel-04406029

Submitted on 19 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

#### L'Université de Rennes

ÉCOLE DOCTORALE Nº 601 Mathématiques, Télécommunications, Informatique, Signal, Systèmes, Électronique

Spécialité : Informatique

Par

# « Abderaouf Nassim AMALOU »

## « Machine Learning for timing estimation »

Thèse présentée et soutenue à « Rennes », le « 12 décembre 2023» (date préliminaire) Unité de recherche : « Univ. Rennes, INRIA, CNRS, IRISA»

#### Rapporteurs avant soutenance:

Claire PAGETTI Ingénieure de Recherche (HDR), ONERA Toulouse

Jalil BOUKHOBZA Professeur, ENSTA Bretagne

#### **Composition du Jury:**

Président :

Examinateurs : Olivier SENTIEYS Professeur, Université de Rennes

Smail NIAR Professeur, Université Polytechnique Hauts-de-France

Claire PAGETTI Ingénieure de Recherche, ONERA Toulouse

Jalil BOUKHOBZA Professeur, ENSTA Bretagne

Dir. de thèse : Isabelle PUAUT Professeure, Université de Rennes Co-dir. de thèse : Elisa FROMONT Professeure, Université de Rennes

# **ACKNOWLEDGEMENT**

En préambule de ce manuscrit de thèse, je souhaiterais adresser mes remerciements les plus sincères aux personnes qui m'ont apporté leur aide et ont ainsi contribué à l'élaboration de ce modeste travail.

Je tiens à exprimer ma profonde gratitude envers mes encadrantes de thèse Pr. Isabelle PUAUT et Pr. Elisa FROMONT, enseignantes-chercheuses à l'université de Rennes, qui m'ont marqué au cours de ces trois années par leurs précieux conseils, leur écoute, leur réactivité et leur disponibilité. La confiance qu'elles m'ont accordée et leur sens de la pédagogie ont affirmé ma détermination et m'ont permis de mener à terme ce travail.

Je souhaiterais adresser mes profonds remerciements aux membres du jury qui m'ont fait l'honneur d'accepter de juger ce travail.

Je suis particulièrement reconnaissant envers les membres de l'équipe PACAP : Erven, Pierre, Damien, Caroline, Anis, Camille, Pierre, Nicolas, Hugo, Antoine, Sara, Nicolas, Aurore, Hector, ainsi que les membres de l'équipe LACADOM : Alexandre, Tassadit, Sébastien, Luis, Louis, Christine, Laurance, Véronique, Peggy, Romaric, Julien, Camille, Lénaïgue, pour tous les bons moments que nous avons passés ensemble.

J'aimerais adresser un remerciement particulier à Virginie Desroches et Gaelle Tworkowski pour leur disponibilité, leur amabilité et leur gentillesse.

Je ne saurais terminer sans exprimer mes remerciements les plus chaleureux à toute ma famille, en particulier à ma mère et mon père, à ma sœur, à mon grand frère ainsi qu'à ma belle-sœur, pour le soutien et les encouragements qu'ils m'ont apportés avec un dévouement total.

Pour finir, je remercie tous mes amis et en particulier ma femme Manele, dont la bienveillance et l'encouragement ininterrompus m'ont permis de mener à bien ce travail.

# **TABLE OF CONTENTS**

| In | trod | uction |                                                       | 19 |

|----|------|--------|-------------------------------------------------------|----|

| 1  | Bac  | kgroui | nd on Timing Estimation Using Machine Learning        | 25 |

|    | 1.1  | Execu  | tion time estimation: a bird's-eye view               | 25 |

|    |      | 1.1.1  | Levels of execution time estimation                   | 25 |

|    |      | 1.1.2  | Execution time usages                                 | 26 |

|    |      | 1.1.3  | Factors behind the variability of execution times     | 27 |

|    |      | 1.1.4  | Execution time estimation techniques                  | 30 |

|    | 1.2  | WCE    | $\Gamma$ estimation techniques                        | 32 |

|    |      | 1.2.1  | Static techniques                                     | 33 |

|    |      | 1.2.2  | End-to-end measurements techniques                    | 35 |

|    |      | 1.2.3  | Hybrid techniques                                     | 36 |

|    | 1.3  | Machi  | ine learning                                          | 38 |

|    |      | 1.3.1  | Regression-based machine learning algorithms          | 39 |

|    |      | 1.3.2  | Deep learning techniques                              | 45 |

|    |      | 1.3.3  | Inputs used for ML-based timing models                | 52 |

|    | 1.4  | Machi  | ine learning for execution time estimation            | 56 |

|    |      | 1.4.1  | ACET estimation using ML                              | 59 |

|    |      | 1.4.2  | BCET estimation using ML                              | 59 |

|    |      | 1.4.3  | WCET estimation using ML                              | 60 |

|    | 1.5  | Concl  | usion                                                 | 61 |

| 2  | WC   | CET Es | stimation Using Classical Machine Learning Techniques | 63 |

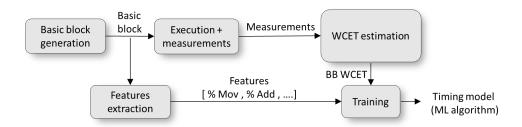

|    | 2.1  | The V  | VE-HML approach                                       | 64 |

|    |      | 2.1.1  | Learning the processor timing model (training)        | 64 |

|    |      | 2.1.2  | Estimating the WCET of a target program               | 66 |

|    |      | 2.1.3  | Automatic generation of training data                 | 66 |

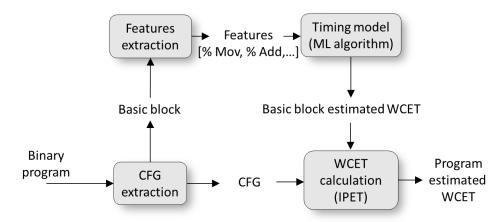

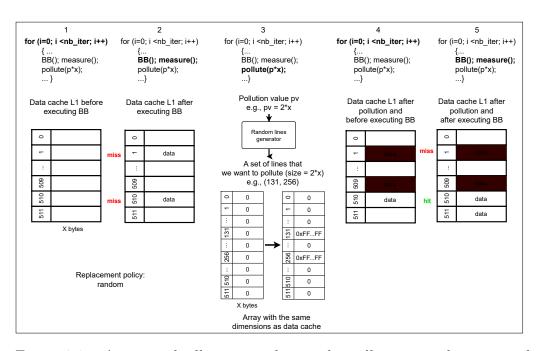

|    |      | 2.1.4  | Supporting processors with data caches                | 67 |

|    | 2.2  | Exper  | imental setup                                         | 71 |

|    |      | 2.2.1  | Hardware and software environments                    | 71 |

|    |      | 2.2.2  | Benchmarks                                            | 72 |

|    |      | 2.2.3  | Implementation of the training phase                  | 73 |

#### TABLE OF CONTENTS

|   |     | 2.2.4   | Implementation of the WCET estimation phase                          | 75  |

|---|-----|---------|----------------------------------------------------------------------|-----|

|   | 2.3 | Exper   | imental results                                                      | 76  |

|   |     | 2.3.1   | Prediction of WCETs of programs                                      | 76  |

|   |     | 2.3.2   | Benefits of cache modeling                                           | 78  |

|   |     | 2.3.3   | Comparison with a hybrid WCET estimation technique                   | 79  |

|   |     | 2.3.4   | Prediction of WCETs of basic blocks                                  | 80  |

|   | 2.4 | Concl   | usion                                                                | 81  |

| 3 | AC  | ET Es   | timation: A Dive into LSTM and Transformers                          | 83  |

|   | 3.1 | New n   | machine learning architectures for timing estimation                 | 84  |

|   |     | 3.1.1   | Motivation for context awerness                                      | 84  |

|   |     | 3.1.2   | ACET estimation using LSTMs, CATREEN                                 | 86  |

|   |     | 3.1.3   | ACET estimation using Transformers, ORXESTRA                         | 89  |

|   | 3.2 | Exper   | imental setup                                                        | 92  |

|   |     | 3.2.1   | Datasets and benchmarks                                              | 92  |

|   |     | 3.2.2   | Baselines                                                            | 95  |

|   |     | 3.2.3   | Hardware and software setups                                         | 96  |

|   |     | 3.2.4   | Setup for the learning phase                                         | 97  |

|   | 3.3 | Exper   | imental results                                                      | 97  |

|   |     | 3.3.1   | Evaluation of the pretraining (for ORXESTRA and Transformers         |     |

|   |     |         | $vanilla\ only)\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$                       | 98  |

|   |     | 3.3.2   | Hyperparameters tuning                                               | 99  |

|   |     | 3.3.3   | Prediction results on the test dataset                               | 100 |

|   |     | 3.3.4   | Impact of the context size                                           | 102 |

|   |     | 3.3.5   | Impact of the basic block size                                       | 103 |

|   |     | 3.3.6   | Optimization effect on prediction                                    | 104 |

|   |     | 3.3.7   | Inference throughput                                                 | 105 |

|   | 3.4 | Concl   | usion                                                                | 106 |

| 4 | Tow | vards F | Refined WCET Estimation: The Potential of Transformers $\mathbf{XL}$ | 107 |

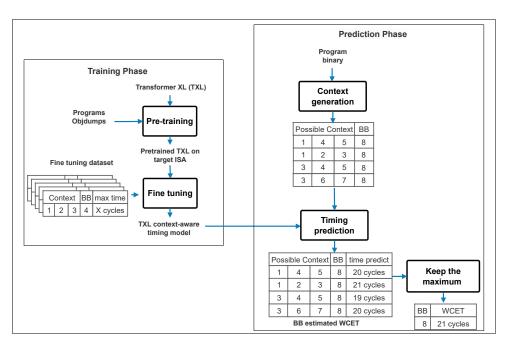

|   | 4.1 | The C   | CAWET approach                                                       | 108 |

|   |     | 4.1.1   | Overview of CAWET                                                    | 109 |

|   |     | 4.1.2   | Training phase using Transformers XL                                 | 110 |

|   |     | 4.1.3   | Prediction phase                                                     | 111 |

|   | 4.2 | Exper   | imental setup                                                        |     |

|   |     | 4.2.1   | Dataset and benchmarks                                               |     |

|   |     | 4.2.2   | Context-agnostic baselines                                           |     |

|   |     | 4.2.3   | <u> </u>                                                             | 117 |

|                           |        | 4.2.4   | Setup for the learning phase                                    | 118   |

|---------------------------|--------|---------|-----------------------------------------------------------------|-------|

|                           |        |         |                                                                 |       |

|                           |        | 4.2.5   | Setup for the prediction phase                                  | . 119 |

|                           | 4.3    | Exper   | rimental results                                                | . 119 |

|                           |        | 4.3.1   | Quality of WCET predictions for the Cortex M4                   | . 119 |

|                           |        | 4.3.2   | Quality of WCET predictions for the Cortex M7                   | . 121 |

|                           |        | 4.3.3   | Impact of CAWET features (Cortex M4 and M7) $\dots \dots \dots$ | . 122 |

|                           |        | 4.3.4   | Quality of WCET predictions for the Cortex A53                  | . 123 |

|                           | 4.4    | Concl   | usion                                                           | . 124 |

| 5                         | Cor    | nclusio | n and future works                                              | 125   |

| •                         |        |         |                                                                 |       |

|                           | 5.1    | Key c   | ontributions                                                    | . 125 |

|                           | 5.2    | Open    | issues and future perspectives                                  | . 126 |

| $\mathbf{B}_{\mathbf{i}}$ | ibliog | graphy  | ,                                                               | 131   |

# **LIST OF FIGURES**

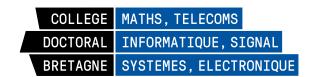

| 1.1  | Static timing analysis workflow                                             |    |  |

|------|-----------------------------------------------------------------------------|----|--|

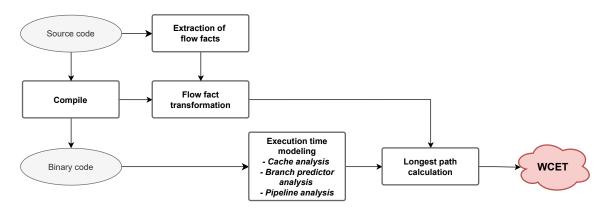

| 1.2  | Control flow graph for the code depicted in Listing 1.1                     | 34 |  |

| 1.3  | IPET formulas for the CFG of Figure 1.2                                     | 34 |  |

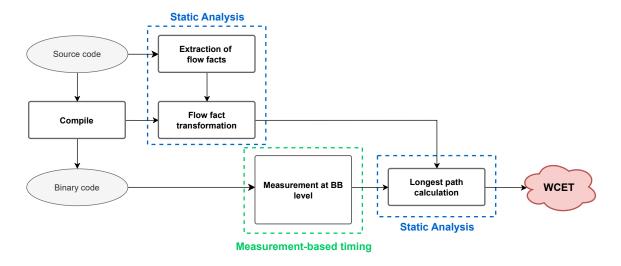

| 1.4  | Hybrid timing analysis workflow                                             | 36 |  |

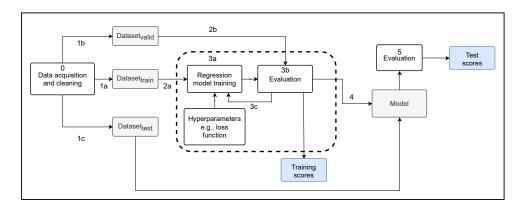

| 1.5  | Regression learning workflow                                                | 40 |  |

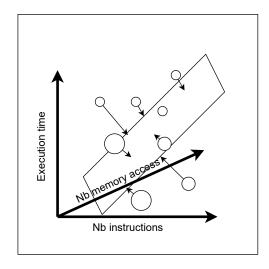

| 1.6  | Linear regression for execution time estimation example                     | 41 |  |

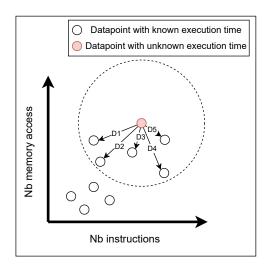

| 1.7  | KNN example for execution time estimation                                   | 43 |  |

| 1.8  | Example of a random forest model for execution time estimation              | 44 |  |

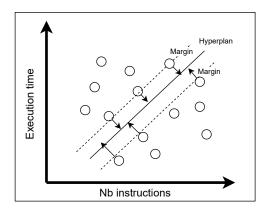

| 1.9  | SVR example for execution time estimation                                   | 44 |  |

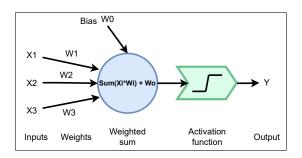

| 1.10 | An example of an artificial neuron                                          | 45 |  |

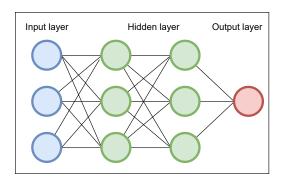

| 1.11 | An example of a deep neural network consisting of an input layer, hidden    |    |  |

|      | layers, and an output layer                                                 | 46 |  |

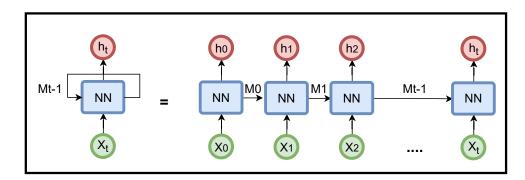

| 1.12 | An RNN unfolds through time                                                 | 47 |  |

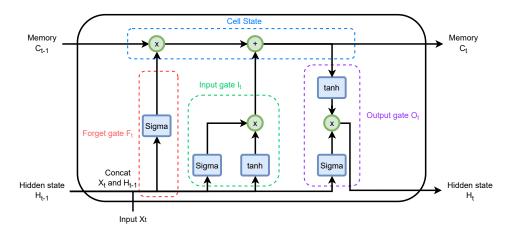

| 1.13 | An LSTM cell, represented by the different gates that compose it: Forget    |    |  |

|      | gate, Input gate, and Output gate.                                          | 48 |  |

| 1.14 | The Transformers architecture, as described in the original paper           | 49 |  |

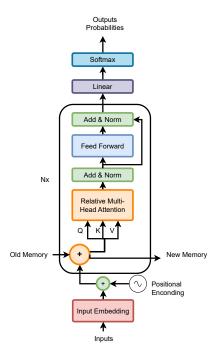

| 1.15 | The Transformers XL architecture                                            | 51 |  |

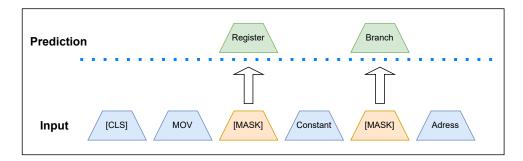

| 1.16 | Masked language modeling on a simple example                                | 52 |  |

| 1.17 | Basic block representation using one-hot-encoding example                   | 54 |  |

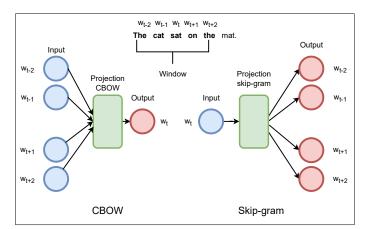

| 1.18 | Word2vec architecture (CBOW and Skip-gram)                                  | 55 |  |

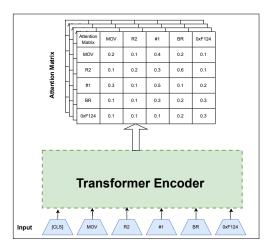

| 1.19 | Assembly code embedding using Transformers's attention matrix               | 56 |  |

| 1.20 | ITHEMAL architecture                                                        | 60 |  |

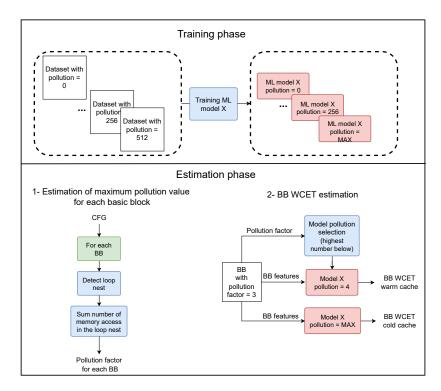

| 2.1  | WE-HML training phase                                                       | 65 |  |

| 2.2  | WE-HML WCET estimation phase                                                | 66 |  |

| 2.3  | An example illustrating data cache pollution simulation on a basic block in |    |  |

|      | 5 steps. The process targets a data cache that employs a random replace-    |    |  |

|      | ment policy                                                                 | 69 |  |

| 2.4  | The introduction of cache pollution during both the training and estimation |    |  |

|      | (prediction) phases                                                         | 71 |  |

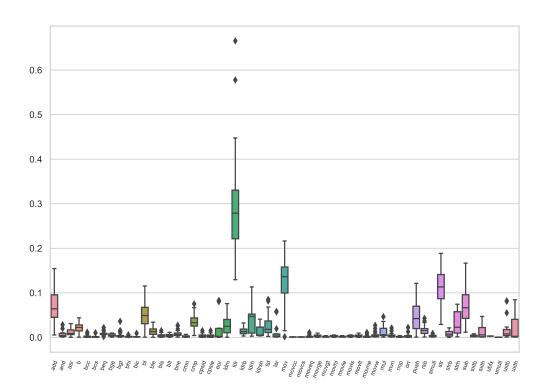

| 2.5  | Statistics about instruction proportion in basic blocks used for training   |    |  |

|      | (top), in our synthetic data and TACLeBench benchmarks (bottom)             | 74 |  |

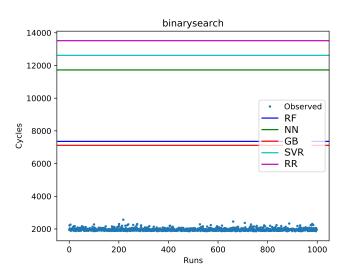

| 2.6     | ML-predicted WCETs versus observed execution times for $\it binary search.$                                                                                                                                                                                                                                                                                                                                                                       | 77  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

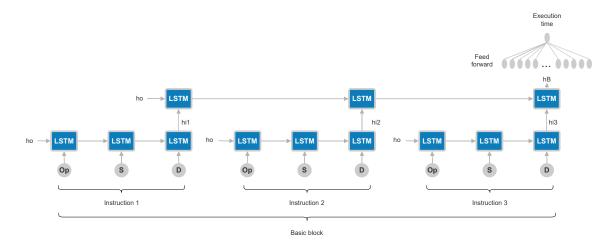

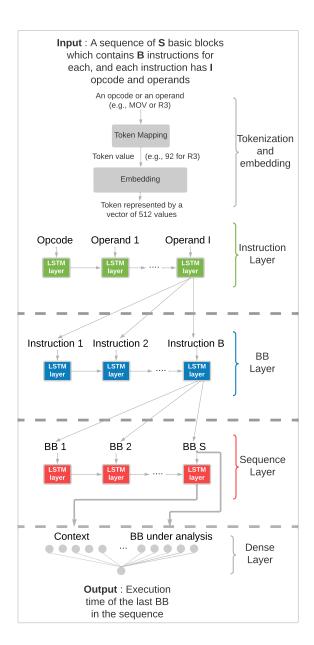

| 3.1 3.2 | Inter Basic Blocks hardware dependencies                                                                                                                                                                                                                                                                                                                                                                                                          | 86  |

|         | of one such operand/opcode. CATREEN calculates (lower part) a timing                                                                                                                                                                                                                                                                                                                                                                              | 88  |

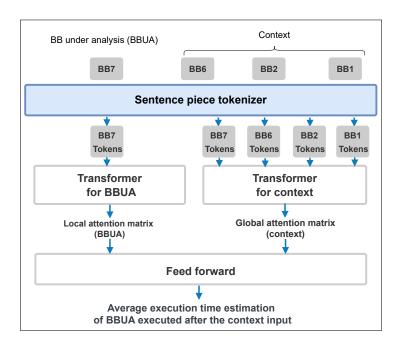

| 3.3     | estimation for the last basic block in the input sequence                                                                                                                                                                                                                                                                                                                                                                                         | 90  |

| 3.4     | Example of an execution trace, extracted from OZONE tool [72]                                                                                                                                                                                                                                                                                                                                                                                     |     |

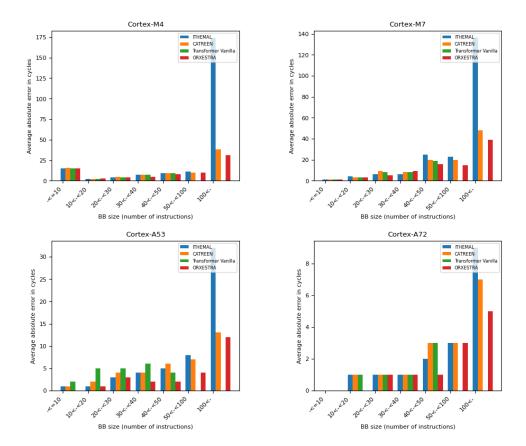

| 3.5     | Mean absolute cycle error (average number of cycle error) boxplot comparison of ITHEMAL (blue), CATREEN (orange), Transformers vanilla (green), and ORXESTRA (red) for different processors (M4, M7, A53, A72) and six Categories of basic blocks. The most left category represents basic blocks with a size of 10 or less instructions (-<=10), while the most right category includes basic blocks with a number of instructions exceeding 100 |     |

|         | instructions (100<). Each subfigure represents a processor                                                                                                                                                                                                                                                                                                                                                                                        | 104 |

| 4.1     | Overview of CAWET                                                                                                                                                                                                                                                                                                                                                                                                                                 | 109 |

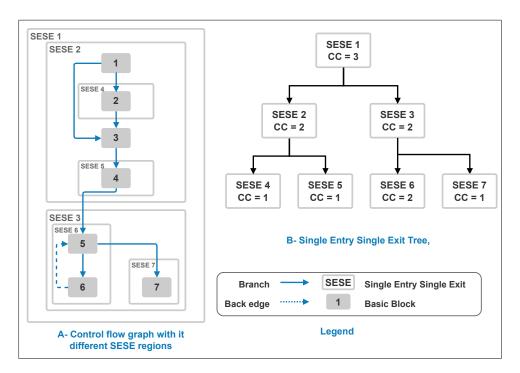

| 4.2     | A CFG example transformed into a SESE tree and annotated with cyclomatic complexity                                                                                                                                                                                                                                                                                                                                                               | 112 |

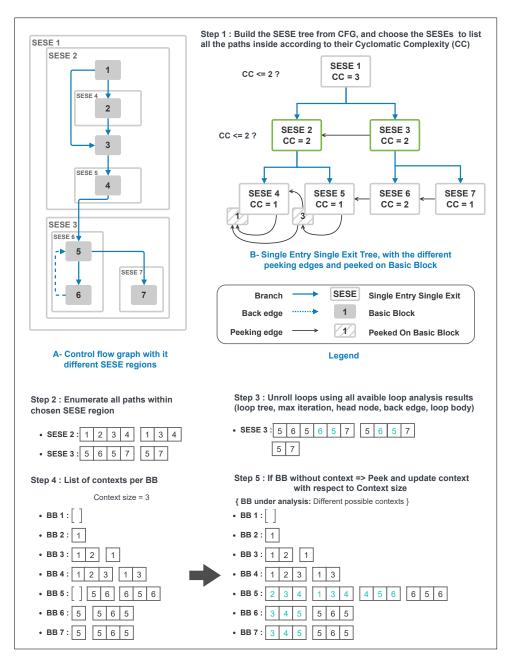

| 4.3     | Example of the different steps for context generation, where the cyclomatic complexity limit is set to 2 and the context size is set to 3 BBs                                                                                                                                                                                                                                                                                                     | 113 |

| 5.1     | Plot showing feature impacts on timing prediction for a basic block on MSP430                                                                                                                                                                                                                                                                                                                                                                     | 127 |

# LIST OF TABLES

| 1.1 | Comparative analysis of execution time estimation solutions                                                                                          | 32  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Comparing static, measurement-based, and hybrid WCET solutions                                                                                       | 37  |

| 1.3 | Representing a code snippet with static features [138]                                                                                               | 53  |

| 1.4 | List of some PAPI performance counters [135]                                                                                                         | 53  |

| 1.5 | Summary of works conducted for estimating the execution time                                                                                         | 58  |

| 2.1 | Experimented machine learning algorithms                                                                                                             | 65  |

| 2.2 | Properties of benchmarks                                                                                                                             | 72  |

| 2.3 | Estimated WCET obtained by WE-HML versus MOET                                                                                                        | 76  |

| 2.4 | Improvement (decrease) of estimated WCET resulting from cache manage-                                                                                |     |

|     | ment                                                                                                                                                 | 78  |

| 2.5 | Comparison with hybrid method                                                                                                                        | 79  |

| 2.6 | Pearson correlation score of Scikit-learn ML algorithms on basic blocks, depending on the technique used for estimating the WCET of basic blocks     |     |

|     | and pollution value                                                                                                                                  | 80  |

| 3.1 | Composition of the dataset for the finetuning phase, showing benchmarks, each accompanied by a brief description, the number of programs, and the    |     |

|     | total count of basic blocks retrieved per program. This dataset serves as                                                                            |     |

|     | the training and testing of all competitors also                                                                                                     | 95  |

| 3.2 | Hyperparameters for deep learning architectures, including ITHEMAL, <i>CATREEN</i> , Transformers vanilla, and <i>ORXESTRA</i> , are presented. (NA: |     |

|     | Not Applicable)                                                                                                                                      | 96  |

| 3.3 | Summary of the processors used and their micro-architectural features. $$ . $$ .                                                                     | 97  |

| 3.4 | Perplexity scores obtained by ORXESTRA and the Transformers vanilla                                                                                  |     |

|     | in the pretraining phase                                                                                                                             | 99  |

| 3.5 | MAPE performance of ITHELAM, CATREEN, Transformers vanilla, and                                                                                      |     |

|     | ORXESTRA, for different learning hyperparameters (loss function, opti-                                                                               |     |

|     | mizer, learning rate) for Cortex-M7. The lower, the better                                                                                           | 100 |

| 3.6 | loss function, optimizer, and learning rate used for ITHEMAL CATREEN,                                                                                |     |

|     | the Transformers vanilla, and ORXESTRA                                                                                                               | 100 |

| 3.7  | Test results of Neural Networks (NN), ITHEMAL [130], CATREEN [8],                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|      | and ORXESTRA on various ARM Cortex targets: M4, M7, A53, and A72.                                                                         |

|      | The results are based on the first test dataset, which includes a balance                                                                 |

|      | between the number of small and large-sized BBs. Evaluation metrics: mean                                                                 |

|      | absolute percentage error and Pearson correlation (Corr.)                                                                                 |

| 3.8  | Test Results: Mean Absolute Percentage Error (MAPE) on Different Tar-                                                                     |

|      | gets (M4, M7, A53, and A72) using the second test set. The Test Set is                                                                    |

|      | specifically chosen to be within the prediction capabilities of Transformers                                                              |

|      | vanilla, ensuring a fairer comparison among models                                                                                        |

| 3.9  | Impact of the context size (number of BB considered as context) on the                                                                    |

|      | Mean Absolute Percentage Error of CATREEN                                                                                                 |

| 3.10 | Impact of the context size (number of BB considered as context) on the                                                                    |

|      | Mean Absolute Percentage Error of ORXESTRA                                                                                                |

| 3.11 | MAPE performance of ORXESTRA, CATREEN, ITHEMAL and Neural                                                                                 |

|      | Networks across various GCC optimization levels (O0, O1, O2 and O3) and                                                                   |

|      | architectural targets $\dots \dots \dots$ |

| 3.12 | The mean throughput over all processors, when treating 1000 BB for each                                                                   |

|      | technique (with a batch size of 1 and batch size of 32)                                                                                   |

| 4.1  | The benchmarks used for training CAWET                                                                                                    |

| 4.2  | Selected TacleBench codes used to evaluate the quality of the predictions 116                                                             |

| 4.3  | Summary of the processors used and their micro-architectural features 118                                                                 |

| 4.4  | Comparison of WCET predictions for CAWET and a Neural Network (NN)                                                                        |

|      | baseline on TacleBench programs for Cortex-M4                                                                                             |

| 4.5  | Impact of the context size on the Mean Absolute Error (MAE) on TacleBench                                                                 |

|      | programs for Cortex-M4                                                                                                                    |

| 4.6  | Comparison of WCET predictions for CAWET (vanilla) and a Neural Net-                                                                      |

|      | work (NN) baseline for Cortex-M7                                                                                                          |

| 4.7  | Comparison of WCET predictions for CAWET and a Neural Network (NN)                                                                        |

|      | baseline for Cortex-M7 when accounting for the static cache analysis results $122$                                                        |

| 4.8  | RPE measures of CAWET predictions for Cortex-M4 and Cortex-M7 when                                                                        |

|      | adding different features of CAWET: context accounting (A), peek-on mech-                                                                 |

|      | anism (B), loop unrolling (C), and cache analysis (D)                                                                                     |

| 4.9  | Comparison of WCET predictions on Cortex A53 for: CAWET, a prob-                                                                          |

|      | abilistic WCET solution, WE-HML, CAWET (vanilla), and a modified                                                                          |

|      | CAWET to account for static cache analysis results                                                                                        |

# RÉSUMÉ

Les systèmes embarqués sont des dispositifs électroniques contrôlés par un logiciel pour effectuer des tâches spécifiques. Ces tâches vont de l'exploitation d'appareils programmables à la maison à la gestion des systèmes dans les voitures et les avions. La prévalence de ces systèmes a considérablement augmenté, comme en témoignent les projections suggérant que le nombre de dispositifs Internet des objets (IoT) atteindra 50 milliards d'ici 2030 [4]. Au fur et à mesure que les nouvelles technologies évoluent, elles présenteront inévitablement de nouveaux défis liés à la taille, au coût et aux performances de ces systèmes embarqués. Par conséquent, les concepteurs de systèmes doivent comprendre le comportement du logiciel embarqué en ce qui concerne ces contraintes. Cependant, la complexité croissante des architectures matérielles, associée à une documentation insuffisante, complique la tâche d'estimer les performances des logiciels. Les performances peuvent être des performances de pire en pire (WCETs) dans les systèmes en temps réel ou les performances moyennes de cas dans ceux à usage général.

Dans les systèmes à usage général, l'utilisation efficace des ressources est essentielle. L'une des façons d'améliorer les mesures de rendement, comme le temps d'exécution moyen, est par le biais de transformations ou d'optimisations au niveau du code. Toutefois, l'évaluation précise de ces optimisations nécessite la compréhension de divers facteurs, y compris l'interaction entre les instructions du programme. Pour faciliter ce processus d'évaluation complexe, des outils spécialisés ont été conçus pour quantifier le temps d'exécution, en se concentrant spécifiquement sur l'impact des optimisations. Selon les ressources disponibles, ces outils utilisent généralement soit des techniques de profilage [135, 49] lorsque le matériel cible est accessible, soit des simulateurs de processeurs [19, 13, 3, 120], qui sont des outils logiciels qui émulent le comportement d'un processeur, permettant ainsi l'analyse des performances et les tests de logiciel sans avoir besoin du matériel réel.

Dans les systèmes en temps réel, les tâches viennent avec des délais spécifiques qui doivent être respectés pour considérer le système comme fonctionnant correctement. S'assurer que les tâches sont terminées à temps nécessite l'évaluation du WCET pour chaque tâche. Cette évaluation aide l'algorithme de planification à allouer des ressources afin que chaque tâche atteigne sa date limite, même dans les scénarios les plus exigeants. Pour une estimation précise de WCET, différentes méthodes peuvent être employées, qui impliquent généralement une considération simultanée du code de la tâche et de l'architecture du

processeur qui l'exécute.

Les méthodes d'estimation WCET sont divisées en méthodes static, méthodes basées sur la mesure de l'end-to-end et méthodes hybrides hybrid [170]. Static methods évalue le WCET sans exécuter le programme. Dans la première phase, le programme est divisé en blocs de base. Un bloc de base (BB) est une séquence d'instructions avec un point d'entrée unique et un point de sortie unique. Le WCET de chaque BB est estimé grâce à la connaissance de l'architecture du processeur. Dans la deuxième phase, les techniques statiques calculent l'estimation WCET pour l'ensemble du programme en fonction de la WCET de chaque BB dans le code. Pour cette deuxième phase, Implicit Path Enumeration Technique (IPET) [170, 117] est la classe de techniques la plus couramment utilisée. IPET s'appuie sur la résolution d'un problème d'optimisation linéaire généré à partir du graphique de flux de contrôle du programme (CFG). Les méthodes statiques fournissent une estimation safe WCET, qui est une limite supérieure de tout temps d'exécution possible, à condition que l'estimation WCET de chaque bloc de base soit elle-même sûre.

End-to-end measurement-based méthodes sont des techniques empiriques qui ne nécessitent pas de connaissances détaillées du matériel. Ils lancent le programme sur une série d'entrées, et les temps d'exécution résultants sont mesurés et recueillis. Le WCET est ensuite estimé, soit en considérant le WCET comme la mesure la plus élevée, soit par extrapolation en utilisant des techniques statistiques [30]. Par construction, lorsque l'on utilise la mesure la plus élevée comme estimation WCET, ces techniques ne peuvent que sous-estimer la WCET à moins que l'entrée et l'état matériel résultant du chemin d'exécution le plus long ne soient utilisés lors des tests [51]. Par conséquent, une marge de sécurité est souvent ajoutée à l'estimation WCET pour atténuer le manque de confiance dans les mesures.

Les méthodes *Hybrid* mélangent des approches statiques et basées sur la mesure. Dans une grande majorité de ces techniques (par exemple, [**BETT:06 a**, 30, 157, 59]), *mesures* sont utilisées pour estimer le WCET des blocs de base. Le WCET de l'ensemble du programme est ensuite estimé en utilisant des méthodes de calcul telles que l'IPET. L'avantage des techniques hybrides est qu'elles ne nécessitent pas de connaissance de l'architecture tout en étant en mesure de trouver le chemin le plus long.

Néanmoins, les outils actuels pour l'estimation WCET, qu'ils soient statiques, endto-end ou hybrides, présentent chacun leur propre ensemble de défis. Les outils d'analyse statique nécessitent une compréhension approfondie de la microarchitecture du processeur, y compris des aspects tels que les caches [67], les pipelines [113] et les prédicteurs de branches citeCOLI:00a. L'acquisition d'une telle connaissance détaillée des microarchitectures devient de plus en plus difficile, soit en raison de restrictions de propriété intellectuelle, soit parce que la complexité des architectures modernes complique l'élaboration de modèles de timing fiables et sûrs. Les méthodes de bout en bout utilisent soit des outils de profilage, soit des simulateurs de cycle précis. Alors que les outils de profilage peuvent perturber la mesure des performances pendant leur fonctionnement, les simulateurs cycle précis, bien que précis, sont intrinsèquement riches en ressources et peuvent être lents. Les deux approches dans le cadre des méthodes end-to-end peuvent également manquer de caractéristiques de sécurité cruciales. Pendant ce temps, les techniques hybrides souffrent de problèmes tels que la couverture complète du code <sup>1</sup> [111]. Compte tenu de ces défis, il y a un besoin urgent de méthodes plus simples et plus efficaces pour la modélisation du temps complexe des processeurs.

Au cours de la dernière décennie, le Machine Learning (ML) est rapidement devenu un outil révolutionnaire dans de nombreux domaines, du secteur des véhicules autonomes aux diagnostics améliorés dans les soins de santé. De même, le rôle de ML dans l'architecture informatique a évolué d'un concept théorique à une technologie fondamentale, influençant la conception, le contrôle et la simulation de divers composants du système. Historiquement, l'interaction entre ML et l'architecture informatique s'est largement concentrée sur l'adaptation d'éléments architecturaux pour mieux servir les algorithmes ML tels que les accélérateurs de réseaux neuronaux [36]. Cependant, la dernière décennie a marqué un changement significatif vers une relation plus réciproque, car de plus en plus de travaux appliquent avec succès ML à l'architecture de processeur et à la résolution de problèmes de conception de compilateur [mlsYS\_survey2018, 32].

Compte tenu des défis croissants associés à la complexité du matériel et à la documentation limitée, cette thèse vise à automatiser la création de modèles de timing matériel. En tirant parti des techniques d'apprentissage automatique, l'objectif est de prédire les performances des cas moyens et des cas les plus mauvais sans nécessiter une documentation approfondie du processeur ciblé. Les solutions proposées fonctionnent toutes en deux phases distinctes. Au cours de la phase d'apprentissage learning phase, le timing des fragments de code est établi sur la base des mesures dans leurs divers "contexts d'exécution", y compris les boucles et les dépendances entre les instructions. Dans la phase inferring ultérieure, le modèle de timing développé est appliqué pour calculer le temps d'exécution de nouveaux fragments de code. Ces calculs sont censés être informés par le contexte d'exécution de chaque fragment de code, déterminé par exemple par une analyse statique. Cette méthodologie offre trois avantages clés :

- Il fournit des estimations de temps raisonnablement précises et rapides.

- Il élimine la nécessité d'analyses statiques coûteuses ou de simulations cycle-exactes.

- Il ne nécessite aucune connaissance détaillée de la microarchitecture du processeur.

<sup>1.</sup> Assurer une couverture complète du code signifie vérifier que chaque partie du code du logiciel a été exécutée et analysée, ne laissant aucune section non testée ou non vérifiée.

Bien que l'information de timing obtenue ne soit pas sûre, elle a une valeur significative pour l'estimation du timing dans les premiers stades du développement du système, des systèmes en temps réel à faibles niveaux de critique, des logiciels à usage général, ou des optimisations de compilateur de guidage.

Alors que des recherches antérieures ont été menées sur la dérivation automatique de modèles de timing en utilisant l'apprentissage automatique [21, 87], elle s'est concentrée principalement sur le matériel simple avec un timing d'instruction constant et indépendant du contexte. Cette thèse vise à ouvrir un nouveau terrain en introduisant la prise de conscience du contexte dans ces techniques d'apprentissage automatique, étendant ainsi leur applicabilité à des conceptions de matériel plus complexes. Spécifiquement, les traces d'exécution d'un programme serviront de représentations contextuelles pour les séquences d'instructions pour lesquelles il faudra estimer les temps de l'execution. En tirant une analogie du domaine du traitement automatique du langage naturel (TAL), ces traces d'exécution peuvent être considérées comme des textes dans lesquels des instructions individuelles peuvent être vues comme des mots. En traitant ces traces, nous pouvons acquérir des connaissances précieuses sur les facteurs contextuels qui influent sur le temps d'exécution des instructions (effets de pipeline, effets de cache et effets prédicteurs de branches), en tirant parti des progrès en TAL pour guider nos modèles. Cette nouvelle approche promet d'améliorer l'exactitude des estimations des délais d'exécution des programmes, ce qui peut à son tour conduire au développement de systèmes intégrés plus efficaces et fiables.

#### Contribution

Cette thèse introduit de nouvelles méthodologies à l'intersection entre l'apprentissage automatique et l'estimation du temps d'exécution. Les trois contributions de cette thèse sont les suivantes :

estimation WCET hybride à l'aide de l'apprentissage automatique pour les architectures avec caches [7]. Notre proposition initiale est une nouvelle approche hybride, WE-HML [7], conçue pour améliorer l'estimation WCET. Cette méthode intègre de manière distincte les considérations de la mémoire cache de données lors de la formation d'une gamme de modèles d'apprentissage automatique fondamentaux. La formation utilise des ensembles de données synthétiquement générés et est complétée par une technique statique pour estimer le WCET global d'un programme.

Utilisation de la TAL dans l'estimation ACET. En nous tournant vers ACET, nous explorons l'intégration des techniques de TAL pour capturer les dépendances entre les séquences d'instruction. Nous enquêtons sur diverses architectures d'apprentissage

profond, y compris la mémoire à court terme [82] (comme publié dans le journal [8]) et Transformers [56, 43]. Nous avons constaté que Transformers XL [43] était le mieux adapté pour contextualiser et estimer avec précision les temps d'exécution de blocs de base.

Évaluation WCET en connaissance de contexte à l'aide de Transformers [6]. Sur la base du succès de l'application TAL dans l'estimation ACET, nous prenons le défi d'identifier le contexte du pire des cas pour les blocs de base, conduisant à la conception de CAWET [6]. Cette nouvelle solution identifie non seulement chaque contexte d'exécution court pour un bloc de base donné, mais elle exploite également Transformers XL [43] pour améliorer la précision de l'estimation WCET. En outre, nous avons intégré ces améliorations dans un outil d'analyse statique, créant une méthodologie hybride qui atténue considérablement les surestimations observées dans notre modèle initial WE-HML.

#### Outline

Le reste de ce document est organisé comme suit :

Chapitre 1. Nous mettons les bases en présentant les concepts clés nécessaires à la compréhension de ce document. Nous examinons les méthodes courantes pour estimer les délais d'exécution dans les scénarios généraux et examinons des techniques spécialisées pour l'estimation WCET. Ce chapitre sert également d'introduction à certaines techniques de régression et d'apprentissage profond. Le chapitre se termine par un aperçu des applications de pointe de l'apprentissage automatique pour l'estimation du temps d'exécution.

Chapitre 2. Ce chapitre a été le premier travail achevé au cours de cette thèse. Il présente une nouvelle méthodologie hybride pour l'analyse WCET en utilisant des techniques de base d'apprentissage automatique. Dans ce chapitre, nous accordons une attention particulière aux effets de mémoire, plus spécifiquement, aux comportements de cache qui peuvent se produire dans des boucles ancrées lors de l'exécution de code.

Chapitre 3. Dans ce chapitre, nous nous aventurons dans le domaine du traitement automatique du langage naturel (TAL), en explorant des techniques avancées d'apprentissage automatique telles que LSTM et Transformers [165] pour estimer les temps d'exécution moyens de cas de fragments de code. Nous accordons ici une attention particulière au rôle du contexte d'exécution dans ces estimations.

Chapitre 4. Nous revenons à l'estimation WCET, où nous nous appuyons sur les conclusions des chapitres précédents en améliorant le modèle hybride du Chapitre 2 en utilisant les modèles les plus efficaces identifiés dans le Chapitres refch3. Le défi de ce chapitre est d'identifier le contexte d'exécution dans le pire des cas, ce qui est crucial pour

appliquer efficacement ces modèles d'apprentissage automatique dans l'estimation WCET hybride.

**Chapitre 5.** Enfin, nous terminons la thèse avec un regard vers l'avenir, en discutant des travaux futurs et des voies d'amélioration.

# INTRODUCTION

Embedded systems are electronic devices controlled by software to perform specific tasks. These tasks range from operating programmable appliances at home to managing systems in cars and airplanes. The prevalence of these systems has increased significantly, as evidenced by projections suggesting that the number of Internet of Things (IoT) devices will reach 50 billion by 2030 [4]. As new technologies evolve, they will inevitably introduce further challenges related to the size, cost, and performance of these embedded systems. Therefore, system designers need to understand the embedded software's behavior with respect to these constraints. However, the increasing complexity of hardware architectures, coupled with insufficient documentation, complicates the task of estimating software performance. Performance may be a worst-case performance (Worst-Case Execution Times - WCETs) in real-time systems or average-case performance in general-purpose ones.

In general-purpose systems, efficient utilization of resources is crucial. One way to enhance performance metrics, like average execution time, is through code-level transformations or optimizations. However, accurately evaluating these optimizations requires understanding various factors, including the interplay among program instructions. To facilitate this complex evaluation process, specialized tools have been designed to quantify execution time, specifically focusing on the impact of optimizations. Depending on the available resources, these tools typically employ either profiling techniques [135, 49] when the target hardware is accessible, or processor simulators [19, 13, 3, 120], which are software tools that emulate the behavior of a processor, thereby enabling performance analysis and software testing without the need for the actual hardware.

In real-time systems, tasks come with specific deadlines that need to be met to consider the system as functioning correctly. Ensuring tasks are completed on time requires evaluating the WCET for each task. This evaluation helps the scheduling algorithm allocate resources so that every task meets its deadline, even in the most demanding scenarios. For accurate WCET estimation, various methods can be employed, which typically involve a simultaneous consideration of both the task's code and the architecture of the processor executing it.

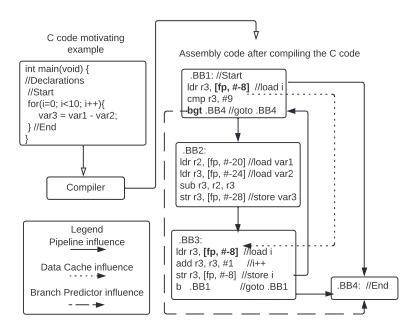

WCET estimation methods are divided into static methods, end-to-end measurement-based methods, and hybrid methods [170]. Static methods estimate the WCET without executing the program. In the first phase, the program is divided into basic blocks. A Basic Block (BB) is a sequence of instructions with a single entry point and a single exit

point. The WCET of each BB is estimated thanks to the knowledge of the processor architecture. In the second phase, static techniques calculate the WCET estimate for the whole program based on the WCET of each BB within the code. For this second phase, Implicit Path Enumeration Technique (IPET) [170, 117] is the most commonly used class of techniques. IPET relies on solving a linear optimization problem generated from the program's Control Flow Graph (CFG). Static methods provide a safe WCET estimate, which is an upper bound of any possible execution time, provided that the WCET estimate of each basic block is itself safe.

End-to-end measurement-based methods are empirical techniques that do not require detailed knowledge of the hardware. They launch the program on a series of inputs, and the resulting execution times are measured and gathered. The WCET is then estimated, either by considering the WCET as the highest measurement or by extrapolating using statistical techniques [30]. By construction, when using the highest measurement as WCET estimate, these techniques can only underestimate the WCET, unless the input and the hardware state resulting in the longest execution path are used during the tests [51]. Therefore, a safety margin is often added to the WCET estimate to mitigate the lack of confidence in the measurements.

Hybrid methods mix static and measurement-based approaches. In a vast majority of these techniques (e.g., [100, 30, 17, 157, 59]), measurements are used to estimate the WCET of basic blocks. The WCET of the whole program is then estimated using calculation methods such as IPET. The advantage of hybrid techniques is that they do not require knowledge of the architecture while being able to find the longest path.

Nevertheless, current tools for WCET estimation, whether they are static, end-to-end, or hybrid, each come with their own set of challenges. Static analysis tools demand an in-depth understanding of the processor's microarchitecture, including aspects like caches [67], pipelines [113], and branch predictors [40]. Acquiring such detailed knowledge of microarchitectures is becoming more difficult, either due to intellectual property restrictions or because the complexity of modern architectures complicates the development of reliable and safe timing models. End-to-end methods utilize either profiling tools or cycle-accurate simulators. While profiling tools can disrupt performance measurement during their operation, cycle-accurate simulators, though precise, are inherently resource-intensive and can be slow. Both approaches within end-to-end methods may also lack crucial safety features. Meanwhile, hybrid techniques suffer from issues like ensuring complete code coverage <sup>2</sup> [111]. Given these challenges, there is a pressing need for more straightforward and efficient methods for complex processor timing modeling.

<sup>2.</sup> Ensuring complete code coverage means verifying that every part of the software code has been executed and analyzed, leaving no section untested or unchecked.

During the past decade, Machine Learning (ML) has quickly become a revolutionary tool in many fields, from the autonomous vehicles sector to enhanced diagnostics in healthcare [137, 106]. Similarly, ML's role in computer architecture has evolved from a theoretical concept to a foundational technology, influencing design, control, and simulation across various system components [163]. Historically, the interplay between ML and computer architecture largely focused on adapting architectural elements to better serve ML algorithms like neural network accelerators [36]. However, the last decade has marked a significant shift toward a more reciprocal relationship, as more and more works successfully apply ML to processor architecture and compiler design problem-solving [124, 169, 32].

Given the growing challenges associated with hardware complexity and limited documentation, this thesis aims at automating the creation of hardware timing models. By leveraging machine learning techniques, the objective is to predict both average-case and worst-case performance without requiring extensive documentation of the targeted processor. The proposed solutions all operate in two distinct phases. During the *learning phase*, the timing for code snippets is established based on measurements in their various "execution contexts", including loops and dependencies between instructions. In the subsequent *inferring phase*, the developed timing model is applied to calculate the execution time of new code snippets. These calculations are supposed to be informed by the execution context of each code snippet, as determined through, for example, static analysis. This methodology offers three key advantages:

- It provides reasonably accurate and fast timing estimations.

- It eliminates the need for costly static analyses or cycle-accurate simulation.

- It does not require detailed knowledge of the processor's microarchitecture.

Although the obtained timing information is not provably safe, it holds significant value for estimating timing in the early stages of system development, real-time systems at low criticality levels (for example, DAL B and C in the aeronautic industry [20]), general-purpose software, or guiding compiler optimizations.

While previous research has been conducted on the automatic derivation of timing models using machine learning [21, 87], it predominantly focused on simple hardware with constant and context-independent instruction timing. This thesis aims to break new ground by introducing context awareness into these machine learning techniques, thereby extending their applicability to more complex hardware designs. Specifically, execution traces of a program will serve as contextual representations for the instruction sequences for which execution times need to be estimated. Drawing an analogy from the field of Natural Language Processing (NLP), these execution traces can be thought of as texts in which individual instructions can be seen as words. By processing these traces, we can

gain valuable insights into the contextual factors that influence instruction execution time (pipeline effects, cache effects, and branch predictor effects), leveraging advancements in NLP to guide our models. This new approach promises to enhance the accuracy of program execution time estimates, which in turn can drive the development of more efficient and reliable embedded systems.

#### Contributions

This thesis introduces new methodologies at the crossroads of machine learning and execution time estimation. The three contributions of this thesis are as follows:

Hybrid WCET estimation using machine learning for architectures with caches [7]. Our initial proposition is a novel hybrid approach, WE-HML [7], designed for improved WCET estimation. This method distinctively incorporates data cache memory considerations when training a range of foundational machine learning models. The training utilizes synthetically generated datasets and is complemented with a static technique to estimate the overall WCET of a program.

Employment of NLP in ACET estimation. Shifting our focus toward ACET, we explore the integration of NLP techniques to capture the dependencies between instruction sequences. We investigate various deep learning architectures, including Long-Short Term Memory [82] (as published in the paper [8]) and Transformers [56, 43]. We found that Transformers XL [43] was the best suited for accurately contextualizing and estimating basic block execution times.

Context-aware WCET estimation using Transformers [6]. Building on the success of NLP application in ACET estimation, we take on the challenge of identifying "worst-case context" for basic blocks, leading to the conception of CAWET [6]. This novel solution not only identifies every short execution context for a given basic block, but it also leverages Transformers XL [43] to enhance WCET estimation accuracy. Moreover, we integrated these enhancements into a static analysis tool, creating a hybrid methodology that significantly mitigates the overestimations observed in our initial WE-HML model.

#### Outline

The rest of this document is organized as follows:

Chapter 1. We lay the groundwork by introducing the key concepts necessary for understanding this document. We review the prevalent methods for estimating execution times in general scenarios and delve into specialized techniques for WCET estimation. This chapter also serves as a short introduction to some regression and deep learning techniques. The chapter concludes with an overview of cutting-edge applications of machine learning for execution time estimation.

Chapter 2. This chapter was the first work completed in the course of this thesis. It presents a novel hybrid methodology for WCET analysis using basic machine learning techniques. In this chapter, we pay close attention to memory effects, more specifically, to cache behaviors that may arise within nested loops during code execution.

Chapter 3. In this chapter, we venture into the realm of Natural Language Processing (NLP), exploring advanced machine learning techniques like LSTM and Transformers [165] to estimate average-case execution times of code snippets. Here, we give special emphasis to the role of execution context in these estimations.

Chapter 4. We return to WCET estimation, where we build upon the findings of the previous chapters by enhancing the hybrid model from Chapter 2 using the most effective models identified in Chapter 3. The challenge in this chapter is to pinpoint the worst-case execution context, which is crucial for applying these machine learning models effectively in hybrid WCET estimation.

Chapter 5. Finally, we conclude the thesis with a look ahead, discussing future work and avenues for further improvement.

#### **Publications**

Please note that for the following publications, the authors are arranged in order of their contribution, with the principal contributor listed first.

**Abderaouf N., AMALOU**, Isabelle PUAUT, and Gilles MULLER. "WE-HML: Hybrid WCET Estimation Using Machine Learning for Architectures with Caches." The 27th International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA). IEEE, 2021.

**Abderaouf N., AMALOU**, Elisa FROMONT, and Isabelle PUAUT. "CATREEN: Context-Aware Code Timing Estimation with Stacked Recurrent Networks." The 34th IEEE International Conference on Tools with Artificial Intelligence (ICTAI) IEEE, 2022.

**Abderaouf N., AMALOU**, Elisa FROMONT, and Isabelle PUAUT. "CAWET: Context-Aware Worst-Case Execution Time Estimation Using Transformers." The 35th Euromicro Conference on Real-Time Systems, (ECRTS 2023). Schloss Dagstuhl-Leibniz-Zentrum für Informatik, 2023.

#### In progress

Hugo REYMOND, **Abderaouf N., AMALOU**, Hector CHABOT and Isabelle PUAUT. "Worst-Case Execution Time and Energy Estimation in Low-Power Microprocessors using Explainable ML."

**Abderaouf N., AMALOU**, Elisa FROMONT, and Isabelle PUAUT. "Interpretable, Fast, and Accurate Context-Aware Basic Block Timing Prediction using Transformers."

# BACKGROUND ON TIMING ESTIMATION USING MACHINE LEARNING

Over the past decade, the application of machine learning techniques to estimate the execution time of programs has gained interest among researchers, yielding several solutions. Each method stands out for its distinct features, including its domain of use, the code level utilized to estimate its execution time, and the way timing is obtained. In this chapter, we dive into various classifications of these techniques, providing a comprehensive overview of their advantages and disadvantages. We conclude the chapter with an analysis of the current state-of-the-art in timing estimation using machine learning and outline potential future directions for research.

This chapter is organized as follows: first, a comprehensive overview of the context surrounding execution time estimation, in general, is provided in Section 1.1, encompassing different uses of execution time, factors that influence it, and the various techniques for its calculation or estimation. Subsequently, a focused investigation into Worst-Case Execution Time (WCET) estimation is conducted in Section 1.2. The utilization of machine learning techniques is introduced and further detailed in Section 1.3. The synergy between machine learning and the estimation of execution time is evaluated through a review of the existing literature in Section 1.4. Finally, Section 1.5 assesses the limitations in current state-of-the-art methods, setting the stage for the specific challenges and contributions addressed in this thesis.

## 1.1 Execution time estimation: a bird's-eye view

#### 1.1.1 Levels of execution time estimation

Execution time is a usual metric for assessing the performance of a program or a system, and it can be understood at different levels.

**Execution time of an instruction.** At the lowest level, the execution time can refer to the time taken to execute a single instruction in a program. This could be a simple operation, such as an addition or a multiplication in a CPU. Microbenchmark tools can

be used for this purpose [2].

Execution time of a basic block (BB). A basic block is a code sequence with no branch *in*, except at the entry, and no branch *out*, except at the exit. In other words, if a single instruction is executed in the basic block, all the instructions are executed in sequence. Therefore, the execution time of a basic block would be the total time taken to execute all the instructions in the block. The basic block code level is widely used in realtime systems for worst-case execution time estimation and compiler design, where considering BB-level timing is a useful approach for understanding the performance characteristics of a program and guiding optimization efforts.

Execution time of a workload, function, program, or application. These terms are often used interchangeably to refer to larger units of execution. In each of these terms, the execution time would refer to the total time taken to complete all the operations, whether it is processing a workload, running a function, executing a program, or operating an application. This is typically a more complex measure, as it must account for various factors, such as function calls, control flow, resource usage, presence of multiple tasks, and interactions between software and hardware components.

This thesis's primary focus revolves around exploring program execution time. Specifically, the time analysis of the basic block, which not only serves to determine the worst-case execution time of programs in case of realtime applications, but also provides valuable insights that can be leveraged for compiler optimization techniques.

#### 1.1.2 Execution time usages

Execution time estimation can be approached from different perspectives and categorized into average, best, and worst-case scenarios.

Average-case execution time (ACET). The average execution time is crucial for assessing the typical (mean or average) duration required to complete a task. It considers different inputs or different repeated execution scenarios to calculate the average. This metric is important for compiler optimization and microarchitecture design [149].

Best-case execution time (BCET). The best-case execution time serves as a reference point in performance analysis, defined as the minimum time necessary for a task to execute under optimal conditions. This metric is important for throughput analysis, aiding in the identification of potential system bottlenecks. A thorough understanding of the constraints and capabilities of the microarchitecture, obtained through BCET analysis, enables more precise finetuning of optimization strategies. Consequently, this enhances system throughput and overall efficiency [129].

Worst-case execution time (WCET). The worst-case execution time represents the maximum time required for a task or module to complete. It indicates the worst-case scenario and is crucial for determining timing constraints and ensuring system stability under extreme conditions. In safety-critical systems and realtime applications, it is essential to guarantee that the system meets its deadlines, even in worst-case scenarios. Consider the collision avoidance system of an autonomous vehicle. Estimating the worst execution time of the collision detection algorithm is vital to ensure that the system can respond within the required time frame to avoid accidents. By accounting for the worst-case execution time, designers can allocate sufficient processing resources and validate the system's ability to operate safely under all conditions (including the worst-case).

#### 1.1.3 Factors behind the variability of execution times

Obtaining an accurate estimate of execution times is challenging due to interactions between hardware and software components. Understanding these interactions and how they affect the execution time variability is essential to improve the reliability and precision of timing estimation solutions. This Section focuses on explaining the key factors that contribute to timing variability that are divided into two categories: hardware-related factors [81] and software-related factors [128].

#### Hardware-related factors

Within a singular microarchitecture, execution time is subject to inherent variability arising from numerous intrinsic factors. In the following, we explore the potential factors contributing to this variability:

Memory hierarchy. Processors use various levels of cache memories to store frequently accessed data and instructions. When a code is executed multiple times, the cache may contain the required data/instruction, resulting in faster execution. However, if the needed data/instructions are not found in the cache (cache miss), the program will run slower (if there are no time anomalies [145]) because it has to rely on other types of memory, which are usually slower. The size and organization of the memories (cache and main memory), along with the code's memory access patterns, influence the cache hit and miss rates.

**Pipeline dependencies.** One source of the execution time variation is the pipeline, which refers to the sequence of stages or operations through which an instruction is divided, with each stage dependent on the completion of the previous one. The dependencies within the pipeline can be summarized into three types:

Read-after-write (RAW). One operation needs to read data produced by a previous operation before it can start.

Write-after-write (WAW). Multiple operations want to write in the same memory location, so they must be executed in a specific order.

Write-after-read (WAR). An operation needs to write data to a memory location that a subsequent operation wants to read from, so it must wait until the read is finished.

Branch prediction. Processors utilize branch prediction techniques to minimize the impact of conditional branches on program execution. If the processor's branch prediction mechanism accurately predicts the outcome of branches, it can maintain a high instruction throughput. However, if the predictions are incorrect, the processor may waste cycles fetching and executing instructions that are ultimately discarded, leading to longer execution times. The effectiveness of branch prediction depends on the specific patterns of conditional branches in the program.

Superscalar processors. A superscalar processor is a type of microprocessor that can execute multiple instructions in parallel. It achieves this by having multiple execution units, allowing it to process more than one instruction during a single clock cycle. Regarding pipeline dependencies, superscalar processors face similar issues as other pipelined architectures. The dependencies described above (RAW, WAW, and WAR) can cause stalls and inefficiencies in instruction executions, affecting the execution time. To mitigate these issues, superscalar processors use sophisticated techniques such as instruction reordering and dynamic instruction scheduling.

Out-of-order processors. Out-of-order processors are an advanced type of microprocessor that can execute instructions out of their original order as long as the data

dependencies are maintained. In out-of-order processors, a large instruction window and

a complex hardware structure are employed to detect and handle dependencies efficiently.

The processor maintains a buffer called the reorder buffer to keep track of the order of

the instructions in the original program sequence, ensuring that the instructions are committed to memory in the correct order (order of program instructions execution). When

it comes to pipeline dependencies, this kind of processor can effectively reduce stalls and

increase instruction throughput. By dynamically reordering instructions based on data

availability, they can maximize the utilization of execution units, leading to improved

performance and better overall efficiency.

**CPU frequency scaling.** Many modern processors employ dynamic frequency scaling [158] (DVFS), where the CPU clock speed can be adjusted according to the workload. If the processor detects a high demand for computational resources, it may increase its clock speed to provide better performance. On the contrary, if the workload is low, it may reduce the clock speed to save power. This variation in clock speed can affect the

execution time of a program, as a higher clock speed globally leads to faster execution.

Resource sharing. Improving system performance is critical, and sharing resources is the key to achieving this. Multicore processors, which allow multiple tasks to run simultaneously, are a significant advancement. This not only boosts system performance but also necessitates effective distribution of computing elements such as CPU cycles and memory bandwidth across running programs. However, this also presents challenges, especially when running resource-intensive tasks simultaneously. This scenario can lead to a shortage of available resources for each program, causing variations in execution times. Additionally, interference during memory hierarchy access and cache coherence issues [23, 153] can also lead to inconsistent execution times.

Other factors. Other factors can also influence execution time, such as **speculative** fetching [47], variable latency instructions [52] (e.g., square root, division), multithreading [14], and timing anomalies [145]. Additionally, the initial hardware state can set off a domino effect [14], further affecting performance.

#### Software-related factors

Factors not related to the processor microarchitecture can influence the execution time of programs. These software-related factors are:

**Program inputs.** Modifying the input of a program can affect its execution time. Different inputs may lead to different control flows, data access patterns, and, therefore, utilization of resources. For example, larger input sizes may require more memory or lead to more loop iterations, resulting in longer execution times, even when the hardware and software environment remains the same.

Compiler optimizations. The choice of compiler and its optimization settings can impact the execution time of a program. A compiler can apply various optimizations and changes to the program, such as loop unrolling, instruction scheduling, and constant folding, to generate more efficient code. Different compiler versions or optimization levels can result in different performance characteristics, affecting the execution times of the program.

Operating system interferences. The way the operating system schedules processes and assigns CPU time to processes can impact the execution time of a program. The scheduling algorithm, priority levels, and interruptions can influence how much CPU time is allocated to a specific program. If a program has lower priority or is competing with other high-priority processes (such as I/O interruption), its execution time may be longer.

These factors are crucial in determining the execution time of a task in different

scenarios. In an average case, it is essential to understand the common hardware state (for example, since cache hits occur more frequently than cache misses [81], a situation where the data is available in the cache can be considered as the average hardware state) and the typical software state (considering the most commonly used program inputs). Conversely, for the worst-case scenarios, it is necessary to identify the most unfavorable conditions that the hardware and software can encounter while running a program.

#### 1.1.4 Execution time estimation techniques

Techniques used for execution time estimation can be classified in general into four categories: static analysis, measurement-based, simulation-based, and data-driven techniques.

#### Static analysis techniques

Static analysis techniques rely mainly on assumptions about the code's behavior complemented by the expert's knowledge to time a program. This approach involves an automatic and detailed inspection of a program's code without actually executing it. The aim is to make time complexity estimates based on the number and types of operations, data size, and control flow. A simple example would be to count the number of instructions and match this to an execution time. More complex solutions use more advanced cost functions for estimating the execution time of instructions as those provided by: Low-Level Virtual Machine Microprocessor Code Analyzer (LLVM MCA) [12], Open Simple Analytic Compiler Architecture (OSACA) [109], Portable inference of port Mappings for out-of-order processors by EVolutionary Optimization (PMEvo) [146], and Intel Architecture Code Analyzer (IACA) [92]. These tools analyze the execution of input assembly code using a static model of the processor and provide various statistics, such as throughput and latency.

#### Measurement-based techniques

These techniques are centered on collecting data derived directly from an observation of the system.

**Profiling.** Profiling is the practice of capturing various metrics during the execution of a program to analyze its performance and behavior. These metrics range from CPU usage and memory consumption to the frequency of specific operations. The insights gathered not only help in optimizing the program itself but also serve as a foundation for predicting the execution time of similar applications. Tools like the Performance Application Programming Interface (PAPI) [135] and Perf [49] are widely used for this purpose,

offering a comprehensive suite of functionalities to monitor performance attributes. Alternatively, hardware-based approaches, such as FPGA synthesis [136], can be employed to gather precise performance data.

Hardware solutions (e.g., Joint Test Action Group JTAG). These solutions involve dedicated hardware, such as JTAG interfaces, to capture hardware-level timing information. They offer accurate estimates but often necessitate additional hardware support. An example is the J-Trace Pro trace solution from Segger [151], which is used to connect to the JTAG interface of the target processor, alongside Ozone [71], a crossplat-form debugger and performance analyzer. Ozone generates execution traces with a format of one line per machine instruction, including other information such as the cycle counter.

#### Simulation-based techniques

Simulations construct a replica of the processor microarchitecture behavior and estimate the execution time by running the simulated model under various scenarios. These simulators, such as GEM5 [19], ARM cycle accurate [120], uops info Code Analyzer (uiCA) [3], and simplescalar [13], can integrate heuristic simplifications (e.g., assuming some parts of the processor microarchitecture functioning and incorporate real world data, such as memory latency).

#### Data-driven techniques

Machine learning [126] presents a new paradigm for estimating execution time by leveraging historical data. Unlike traditional methods that depend on static models or broad approximations, machine learning algorithms, particularly regression models, delve into past code execution time records to predict future ones. These models excel in discerning the intricate relationships between code attributes and their corresponding execution times. For a comprehensive examination of related examples, refer to Section 1.3. It is worth noting that this approach forms the central focus of this thesis.

Each technique offers its own advantages and limits. The appropriate choice depends on a number of factors, including the available resources and the required precision of the timing estimate. The summary of the advantages and limits of the four categories of execution time estimation techniques is presented in Table 1.1.

| Technique       | Advantages                          | Limits                               |

|-----------------|-------------------------------------|--------------------------------------|

| Static analysis |                                     |                                      |

|                 | No need to execute code.            | Inaccuracies due to simplification.  |

|                 | Portable across different hardware. | Resource-intensive for complex       |

|                 |                                     | cases.                               |

|                 |                                     |                                      |

| Measurement-    |                                     |                                      |

| based           | Uses real system data.              | Can be invasive.                     |

|                 | Captures complex behaviors.         | Limited by measurement scope.        |

|                 |                                     |                                      |

| Simulation-     |                                     |                                      |

| based           | Emulates before implementation.     | Needs accurate models.               |

|                 | Controlled environment for scenar-  | Simulations are slower than real ex- |

|                 | ios.                                | ecution.                             |