# Implementation of embedded artificial intelligence algorithms in the readout system of the ATLAS liquid argon calorimeter

Nemer Chiedde

#### ► To cite this version:

Nemer Chiedde. Implementation of embedded artificial intelligence algorithms in the readout system of the ATLAS liquid argon calorimeter. Physics [physics]. Aix-Marseile Université; CNRS, 2023. English. NNT: 2023AIXM0399. tel-04404776

### HAL Id: tel-04404776 https://hal.science/tel-04404776

Submitted on 19 Jan2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial - NoDerivatives 4.0 International License

NNT: 2023AIXM0399

## **THÈSE DE DOCTORAT**

Soutenue à Aix-Marseille Université le 21 novembre 2023 par

# **Nemer CHIEDDE**

Implementation of embedded artificial intelligence algorithms in the readout system of the ATLAS liquid argon calorimeter

| Discipline                                                                                                                                                                | Composition du jury                                                |                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|

| Physique et Sciences de la Matière<br><b>Spécialité</b>                                                                                                                   | Tetiana HRYN'OVA<br>Laboratoire d'Annecy de                        | Rapporteuse           |

| Instrumentation                                                                                                                                                           | Physique des Particules                                            |                       |

| <b>École doctorale</b><br>ED 352 Physique et Sciences de la Matière                                                                                                       | Philippe SCHWEMLING<br>Université Paris Cité et<br>Irfu/CEA-Saclay | Rapporteur            |

| <ul> <li>Laboratoire/Partenaires de recherche</li> <li>Centre National de la Recherche Scien-<br/>tifique (CNRS)</li> <li>Centre de Physique des Particules de</li> </ul> | Jean-Baptiste SAUVAN<br>Laboratoire Louis<br>Leprince-Ringuet      | Examinateur           |

| Marseille (CPPM)                                                                                                                                                          | Emmanuel MONNIER<br>CPPM                                           | Directeur de thèse    |

|                                                                                                                                                                           | Georges AAD<br>CPPM                                                | Co-directeur de thèse |

| •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                               | Cristinel DIACONU<br>CPPM                                          | Président du jury     |

I, undersigned, Nemer CHIEDDE, hereby declare that the work presented in this manuscript is my own work, carried out under the scientific direction of Emmanuel MONNIER and Georges AAD, in accordance with the principles of honesty, integrity and responsibility inherent to the research mission. The research work and the writing of this manuscript have been carried out in compliance with both the french national charter for Research Integrity and the Aix-Marseille University charter on the fight against plagiarism.

This work has not been submitted previously either in this country or in another country in the same or in a similar version to any other examination body.

Marseille, 21 novembre 2023

Cette œuvre est mise à disposition selon les termes de la Licence Creative Commons Attribution - Pas d'Utilisation Commerciale - Pas de Modification 4.0 International.

#### List of publications done as part of this thesis project:

- AAD, G.; BERTHOLD, A.-S.; CALVET, T. P.; CHIEDDE, N.; FORTIN, E.; FRITZSCHE, N.; HENTGES, R. G.; LAATU, L. A. O.; MONNIER, E.; STRAESSNER, A.; VOIGT, J. C. for Artificial Neural Networks on FPGAs for Real-Time Energy Reconstruction of the ATLAS LAr Calorimeters. Geneva, 2021. Available: https://cds.cern.ch/record/2775033

- 2. CHIEDDE, N. for Machine Learning for Real-Time Processing of ATLAS Liquid Argon Calorimeter Signals with FPGAs. Geneva, 2021. Available: https://cds.cern.ch/record/2789016

- CHAMBERY, P.; DE BONU DE LAVERGNE, M.; PRACCHIA, M.; VERNET, K.; CHICHE, S; et.al for JRJC 2021- Journ'ees de Rencontres Jeunes Chercheurs. La Rochelle, 2021. Available: https://hal.science/hal-03832762v2/file/JRJC2021\_Proceedings.pdf

- 4. AAD, G.; CALVET, T.; CHIEDDE, N.; FAURE, R.; FORTIN, E. M.; LAATU, L.; MONNIER, M; SUR, N. for *Firmware implementation of a recurrent neural network for the computation of the energy deposited in the liquid argon calorimeter of the ATLAS experiment*. Marseille, 2023. Available:https://arxiv.org/pdf/2302.07555.pdf

#### Conferences and summer schools attended during this thesis period:

- 1. TWEPP 2021 Topical Workshop on Electronics for Particle Physics; On-line, September 2021

- Journées de Rencontre des Jeunes Chercheurs 2021: Village La Fayette; La Rochelle France, October 2021

- ANF d'électronique numérique IN2P3 "Raw2Smart DATA": IJCLab; Orsay France, November 2021

- DIS2023: XXX International Workshop on Deep-Inelastic Scattering and Related Subjects; East Lansing - USA, march 2023

# ABSTRACT

The Large Hadron Collider (LHC) is currently the world's leading particle accelerator. In 2012, it allowed the discovery of the Higgs boson, the last unobserved particle in the Standard Model of particle physics. The High Luminosity phase of the LHC (HL-LHC), starting in 2029, will allow further study of the Higgs boson properties and improve new particle discovery potential. Up to 200 simultaneous proton-proton collisions are expected at the HL-LHC, which puts stringent requirements on the ATLAS detector electronic. To prepare for these conditions, the readout electronics of the Liquid Argon (LAr) calorimeter of the ATLAS detector will be replaced. The new electronics will contain high-end Field-Programable Gate Arrays (FPGAs) capable of computing the energy deposited in the calorimeter in real time at 40 MHz. The performance optimal filtering algorithms, currently used to compute the energy, will significantly degrade due to the increased rate of overlapping pulses in high luminosity conditions. Neural networks (NNs) were shown to perfectly recover this performance loss. This thesis presents the implementation of neural network firmware embedded in FPGAs. The development is carried out first in High Level Synthesis (HLS), which offers a convenient solution for adapting and optimizing the firmware parameters to facilitate its implementation on FPGA platforms in the prototyping phase. The resource usage and the performance of the firmware are carefully analyzed. The developed tools are implemented in the HLS4ML library, which is open-source software designed to automatically translate a trained NN to a firmware. A test firmware was also developed to be able to validate the neural network implementation on the hardware. This test firmware allows to inject input values into the neural network and extract the computed energies to be compared with simulation. The computed energies in the FPGA were shown to perfectly match the expected values from simulation.

**Keywords :** LHC, ATLAS, liquid argon calorimeter, FPGA, digital signal processing, energy reconstruction.

# RÉSUMÉ

Le Grand Collisionneur de Hadrons (LHC) est actuellement le plus grand accélérateur de particules au monde. En 2012, il a permis la découverte du boson de Higgs, la dernière particule non observée dans le Modèle Standard de la physique des particules. La phase de Haute Luminosité du LHC (HL-LHC), qui débutera en 2029, permettra d'étudier davantage les propriétés du boson de Higgs et d'améliorer le potentiel de découverte de nouvelles particules. Jusqu'à 200 collisions proton-proton simultanées sont prévues au HL-LHC, ce qui impose des exigences strictes sur l'électronique du detecteur ATLAS. Pour se préparer à ces conditions, l'électronique de lecture du calorimètre à argon liquide (LAr) du détecteur ATLAS sera remplacée. La nouvelle électronique contiendra des réseaux de portes programmables sur site ou Field Programmable gate arrays (FPGAs) haut de gamme capables de calculer en temps réel l'énergie déposée dans le calorimètre à une fréquence de 40 MHz. Les performances des algorithmes de filtrage optimal, actuellement utilisés pour calculer l'énergie, se dégraderont significativement en raison de l'augmentation du taux d'empilement des impulsions dans des conditions de haute luminosité. Il a été démontré que les réseaux neuronaux (NNs) peuvent compenser cette perte de performance. Cette thèse présente la mise en œuvre de firmware de réseaux neuronaux intégrés dans des FPGA. Le développement est d'abord réalisé en High-Level Synthesis (HLS), ce qui offre une solution pratique pour adapter et optimiser les paramètres du firmware afin de faciliter leur mise en œuvre sur les plateformes FPGA en phase de prototypage. L'utilisation des ressources et les performances du firmware sont soigneusement analysées. Les outils développés sont intégrés dans la bibliothèque HLS4ML, qui est un logiciel open-source conçu pour traduire automatiquement un réseau neuronal entraîné en firmware. Un firmware de test a également été développé pour valider la mise en œuvre du réseau neuronal sur le matériel. Ce firmware de test permet d'injecter des valeurs d'entrée dans le réseau neuronal et d'extraire les énergies calculées pour les comparer à la simulation. Il a ensuite ete demontre que les energies calculees dans le FPGA correspondent parfaitement aux valeurs obtenues en simulation.

**Mots-clés :** LHC, ATLAS, calorimètre à argon liquide, FPGA, traitement numérique du signal, reconstruction de l'énergie.

# ACKNOWLEDGEMENTS

When I started my postgraduate academic degree back in 2020, I could not imagine how much I would grow personally and professionally. As a Brazilian in France, I want to express my gratitude to God for having the opportunity of be in contact with wonderful people throughout my graduation period. I am glad that I have this moment and space to thank many people who helped me in some way. I am grateful to my supervisor Emmanuel Monnier and Georges Aad, not only for the ongoing support but also for having accepted to guide me. I deeply thank them for believing in me during this time and for the opportunities they provided for my growth.

It was a pleasure to be part of the CPPM team and meet people who I will remember forever with a lot of nostalgia and affection. In particular, I thank Neelam Kumari, Peter Matta, Frederic Hachon and Franck Salomon for the deep discussions and sharing of valuable knowledge and experiences. To Lauri Laatu and Nairit Sur, thank you for your technical insights and feedback, which helped me greatly in my professional growth. Special thanks to Brigitte Pantat and Véronique Roux for the support and assistance provided with administrative matters. They went above and beyond their duties and always helped me with all the difficulties I faced. I appreciate you making my life easier and more peaceful and for making me feel at home even when I was far away. I want to convey my appreciation to the reviewers of this manuscript, as well as the other jury members, Tetiana Hryn'ova, Philippe Schwemling and Jean-Baptiste Sauvan. Thank you for taking the time to read my work and attend my defense. I would like to extend a special thank you to the laboratory director, Cristinel Diaconu, as well as to the CPPM services to have accompanied me throughout my thesis. Your commitment to academic excellence and professionalism helped me work in a professional and international environment.

I want to say how much I appreciate my friends Angela Ayobi and Diego Arias. Thank you for all the support you have given me over the years. Your kind words, encouragement, and emotional support were essential for me to face the challenges that arose in my path. Your constant support allowed me to move forward, even in the toughest times.

I want to conclude by thanking my mother, Magda Macera Gomes. She has always been by my side and encouraged me to pursue my dreams and goals, even when they seemed impossible. She is a warrior, a constant source of inspiration, and an example of unconditional love and dedication. I also thank my sister, Marcela Chiedde, for the love, support, and encouragement she has always offered me. Your presence in my life has been a blessing. To my grandmother Joana Roldana Macera for the support, care, and love. I thank you for being part of my journey and for always being there when I needed you. May we continue to journey together with joy and gratitude in this life. This accomplishment would not have been possible without you.

| Figure 1 | _ | Formes de l'impulsion actuelle du calorimètre LAr dans le détecteur et de         |    |

|----------|---|-----------------------------------------------------------------------------------|----|

|          |   | la sortie du signal après le façonnage bipolaire. Les points représentent les     |    |

|          |   | échantillons séparés de 25 ns.                                                    | 22 |

| Figure 2 | _ | Représentation d'une séquence d'échantillons (en noir) simulée par le logiciel    |    |

|          |   | AREUS. Le rectangle vert indique les impulsions d'une cellule dans les            |    |

|          |   | conditions du HL-LHC, tandis que le rectangle bleu met en évidence la             |    |

|          |   | présence d'impulsions crées à différents moments et se superposant. Pour          |    |

|          |   | améliorer la lisibilité, les vrais dépôts d'énergie transversale sont décalés de  |    |

|          |   | cinq cycles de croisement vers la droite et sont affichés en rouge                | 23 |

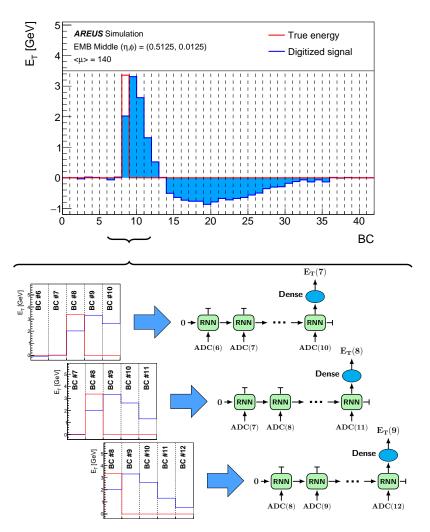

| Figure 3 | _ | Application de la fenêtre glissante des réseaux récurrents basés sur LSTM.        |    |

|          |   | À chaque instant, l'amplitude du signal des quatre BC passés et présents est      |    |

|          |   | entrée dans une couche LSTM. La dernière sortie de cellule est concaténée         |    |

|          |   | avec une opération dense comprenant un seul neurone et fournissant la             |    |

|          |   | prédiction de l'énergie transverse.                                               | 24 |

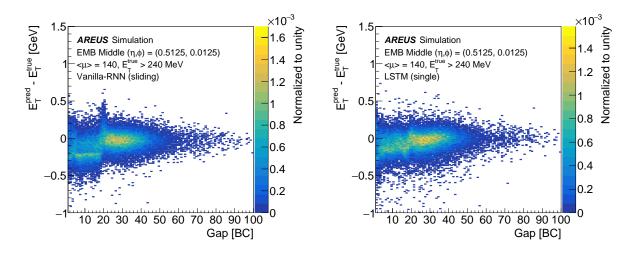

| Figure 4 | _ | Résolution de l'énergie transversale pour un filtre optimal et les différents     |    |

|          |   | algorithmes RNN. Les performances sont mesurées en comparant l'énergie            |    |

|          |   | transverse réelle déposée dans une cellule LAr du milieu du calorimètre           |    |

|          |   | électromagnétique tonneaux (EMB) ( $\eta = 0,5125$ et $\phi = 0,0125$ ) à la pré- |    |

|          |   | diction faite par le RNN après avoir simulé l'impulsion échantillonnée avec       |    |

|          |   | le logiciel AREUS et en supposant $\mu = 140$ . Seules les énergies supérieures   |    |

|          |   | à $3\sigma$ du niveau de bruit sont prises en compte. La moyenne, la médiane,     |    |

|          |   | l'écart-type et la plus petite plage qui inclut 98% des événements sont affichés. | 25 |

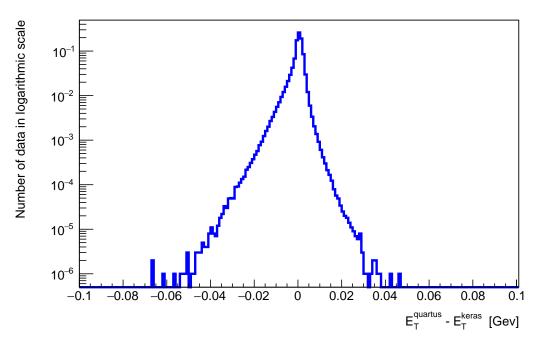

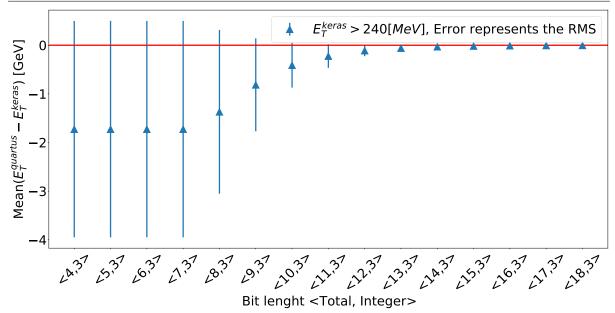

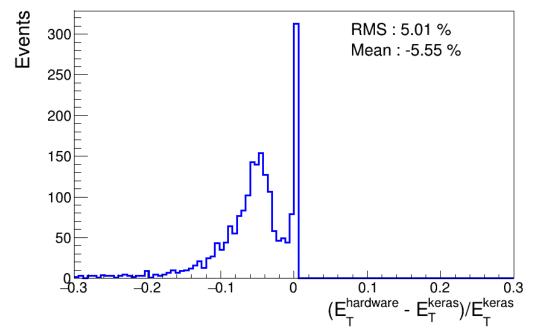

| Figure 5 | _ | Différence entre l'énergie transverse calculée avec Quartus et celle calculée     |    |

|          |   | avec Keras. Les valeurs de Quartus sont obtenues en utilisant l'implémentation    |    |

|          |   | LSTM dans HLS4ML.                                                                 | 26 |

| Figure 6 | _ | Différence entre l'énergie transverse calculée avec Quartus et celle calculée     |    |

|          |   | avec Keras. Les valeurs de Quartus sont obtenues en utilisant l'implémentation    |    |

|          |   | Vanilla-RNN dans HLS4ML.                                                          | 26 |

| Figure 7 | _ | Schéma simplifié des connexions entre le RNN et le firmware de test               | 27 |

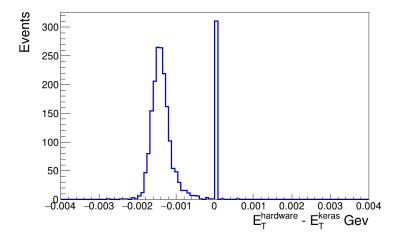

| Figure 8 | _ | Différence entre l'énergie transverse calculée avec le firmware et celle cal-     |    |

|          |   | culée avec Keras.                                                                 | 28 |

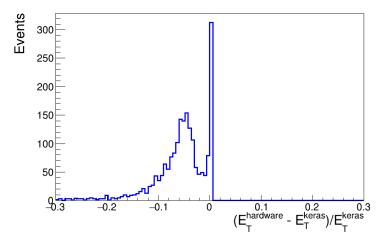

| Figure 9 | _ | SDifférence relative entre l'énergie transverse calculée avec le firmware et      |    |

|          |   | celle calculée avec Keras.                                                        | 28 |

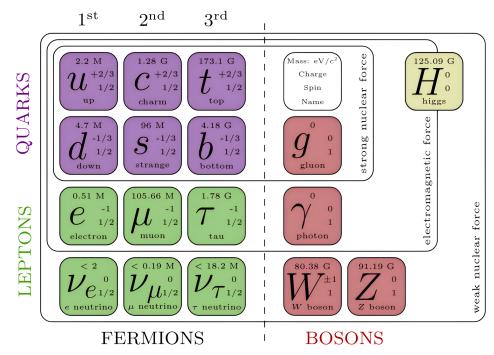

| Figure 10 – Summary of SM elementary particles and their properties, including theo-                      |    |

|-----------------------------------------------------------------------------------------------------------|----|

| rized graviton as a force carrier for the gravitational force.                                            | 34 |

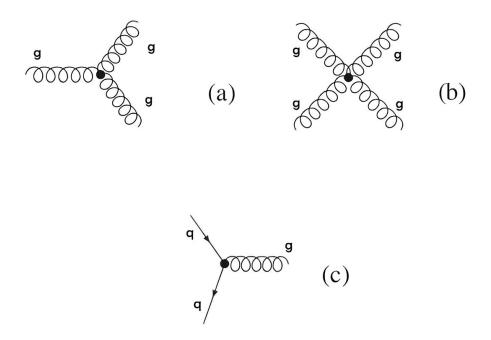

| Figure 11 – Representation of the potential interaction vertices within QCD are depicted                  |    |

| as follows: (a) represents a three-gluon vertex , (b) represents a four-gluon                             |    |

| vertex, and (c) represents a quark-gluon interaction.                                                     | 37 |

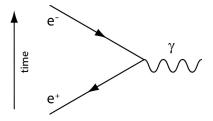

| Figure 12 – Feynman diagram representing any charged particles scattering process                         | 38 |

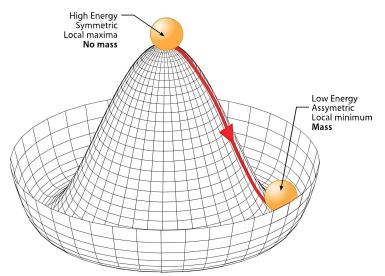

| Figure 13 – Illustration of the Higgs potential configuration in relation to the component                |    |

| of the Higgs field $\phi$                                                                                 | 39 |

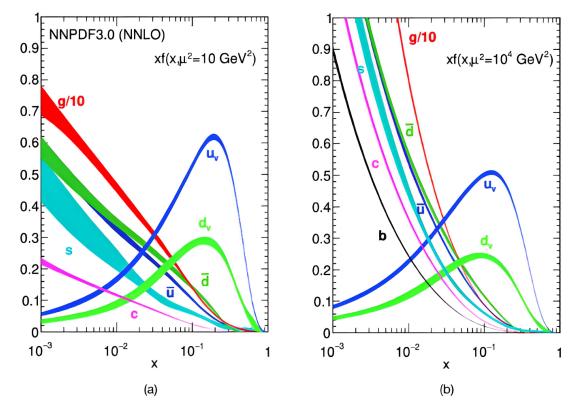

| Figure 14 – Graph of the longitudinal momentum fraction $(x)$ multiplied by the PDF as                    |    |

| a function of x, for two momentum transfer scales: $Q^2 = 10$ , GeV <sup>2</sup> (a) and                  |    |

| $Q^2 = 10^4$ , GeV <sup>2</sup> (b)                                                                       | 40 |

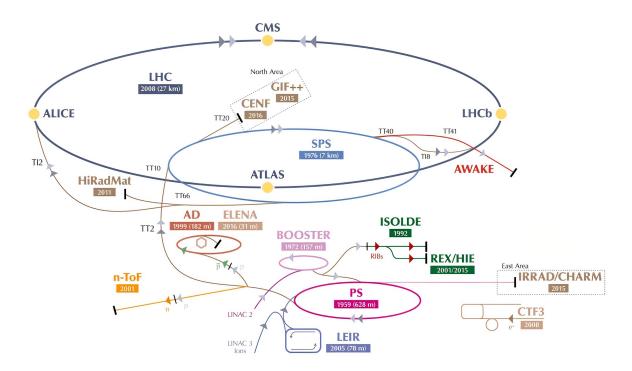

| Figure 15 – Schematic view of CERN accelerator complex and locations of experiments                       |    |

| at LHC.                                                                                                   | 43 |

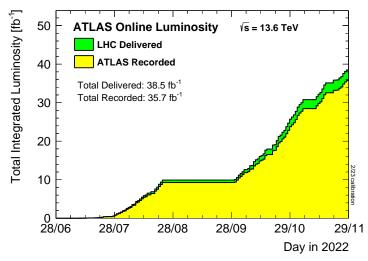

| Figure 16 – Comparison between the cumulative luminosity delivered to (green) and the                     |    |

| one recorded by ATLAS (yellow) during stable beams for $p - p$ collisions at                              |    |

| 13.6 TeV centre-of-mass energy in 2022.                                                                   | 45 |

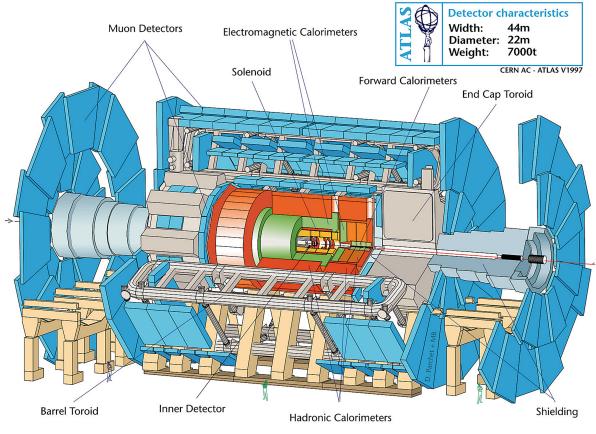

| Figure 17 – Distribution of the average pileup $\langle \mu \rangle$ . The average pileup during the full |    |

| Run 3 amounts to $\langle \mu \rangle = 42.5$ .                                                           | 45 |

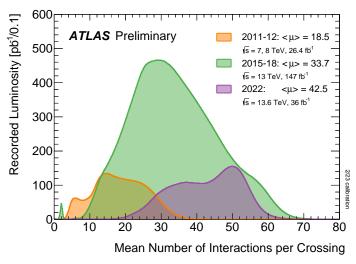

|                                                                                                           | 47 |

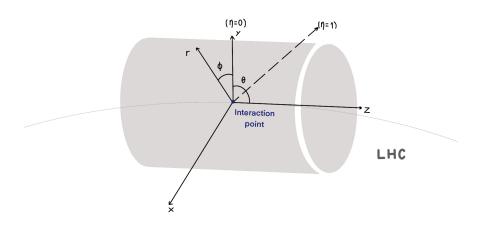

| Figure 19 – The ATLAS detector's system of coordinates.                                                   | 48 |

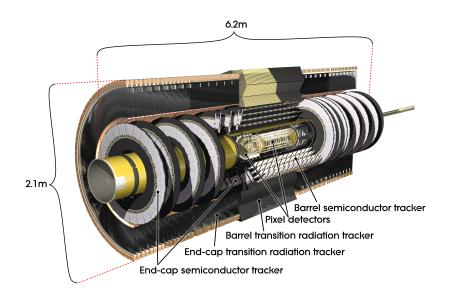

| Figure 20 – Cut view of the ATLAS Inner Detector.                                                         | 49 |

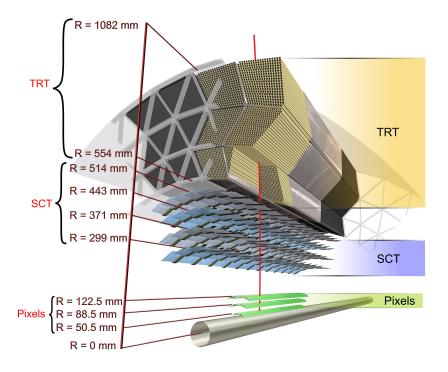

| Figure 21 – Transverse section and structural elements of the ATLAS Inner Detector                        | 49 |

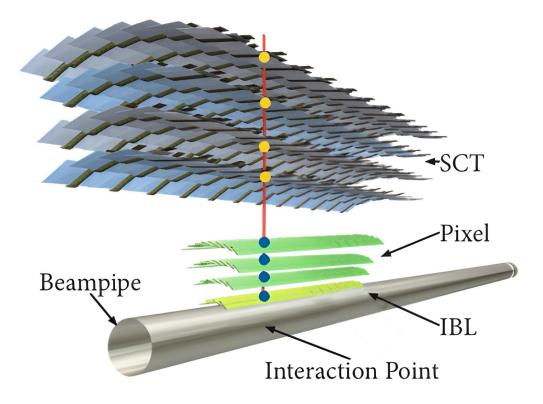

| Figure 22 – The ATLAS Silicon system including the Insertable B-Layer.                                    | 51 |

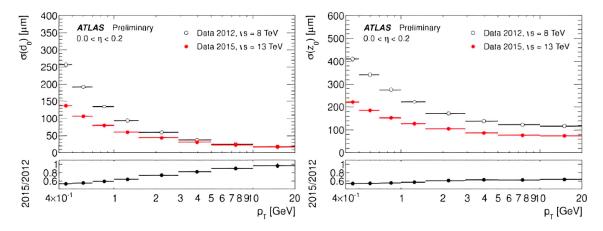

| Figure 23 – The resolution of d0 (left) and z0 (right) depends on the value of $p_T$ and it               |    |

| differs between ATLAS Run-1 (without IBL) and Run-2 (with IBL).                                           | 52 |

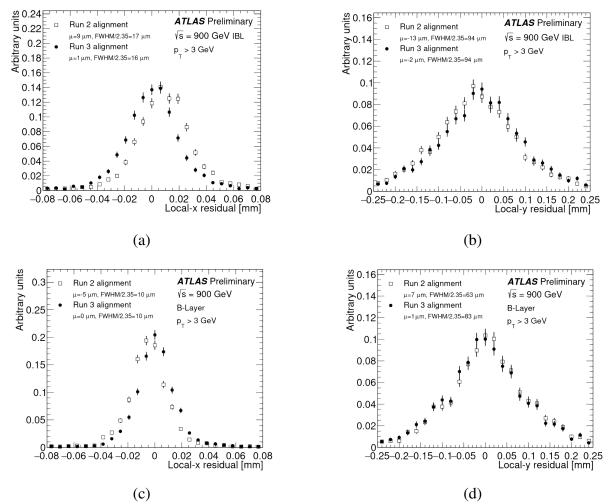

| Figure 24 – Difference between ATLAS Run-2 and Run-3 alignment. Track-hit residuals                       |    |

| in the IBL in the local X (a) and Y (b) coordinates and in the B-Layer in the                             |    |

| local X (c) and Y (d) coordinates.                                                                        | 52 |

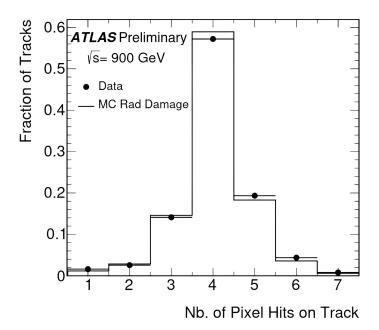

| Figure 25 – Distributions of the average number of SCT hits associated to selected                        |    |

| particle tracks as a function of the pseudo-rapidity, $\eta$ , of the tracks in data                      |    |

| (filled points with error bars) and simulation (continuous line).                                         | 53 |

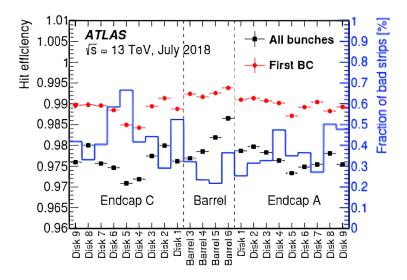

| Figure 26 – The hit efficiency of the SCT detector was measured during a standard p-p                     |    |

| collision run in July 2018. The black squares and red dots represent the                                  |    |

| values measured using all bunches and only the first BC, respectively. The                                |    |

| first bunches were used to avoid any pileup effect from past BC. The hit                                  |    |

| efficiency was averaged over each SCT barrel layer and endcap disk. The                                   |    |

| fraction of bad strips was also superimposed.                                                             | 54 |

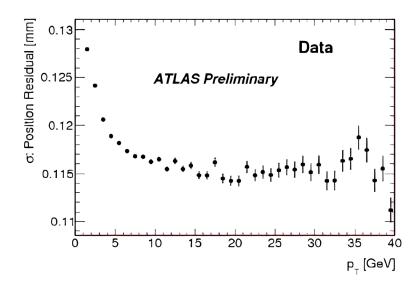

| Figure 27 – | The width of position residuals in the TRT barrel can be expressed as a              |    |

|-------------|--------------------------------------------------------------------------------------|----|

|             | function of track $P_T$ . As track $P_T$ decreases, the scattering of the track      |    |

|             | increases and results in a rise in residuals.                                        | 55 |

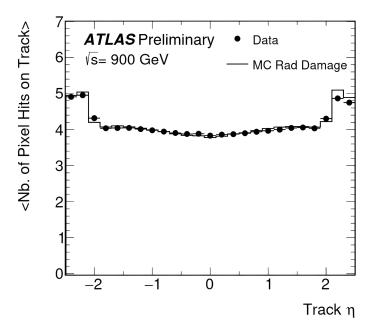

| Figure 28 – | Distributions of the average number of TRT hits associated to selected               |    |

|             | particle tracks as a function of the pseudo-rapidity, $\eta$ , of the tracks in data |    |

|             | (filled points with error bars) and simulation (continuous line).                    | 55 |

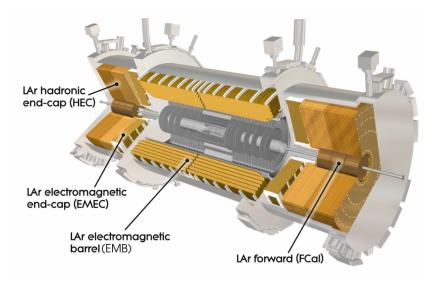

| Figure 29 – | Schematic view of the ATLAS calorimeters.                                            | 56 |

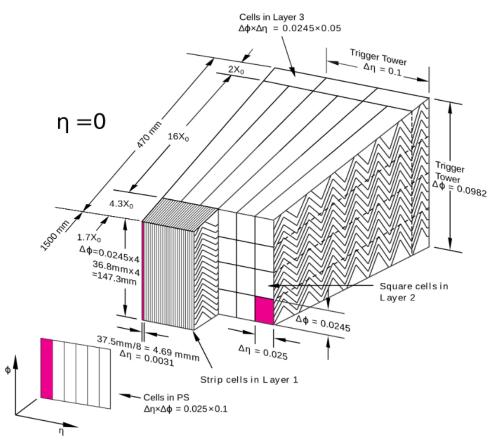

| Figure 30 – | Schematic view of the LAr calorimeter barrel showing the arrangement of              |    |

|             | single cells in different layers.                                                    | 57 |

| Figure 31 – | Schematic of a cell of electromagnetic calorimeter.                                  | 58 |

| Figure 32 – | Tile calorimeter module with its various optical read-out components, includ-        |    |

|             | ing the tiles, fibers, and photomultipliers.                                         | 59 |

| Figure 33 – | The ATLAS Muons subsystem.                                                           | 60 |

| Figure 34 – | The ATLAS TDAQ system in Run 3 with emphasis on the components                       |    |

|             | relevant for triggering as well as the detector read-out and data flow.              | 62 |

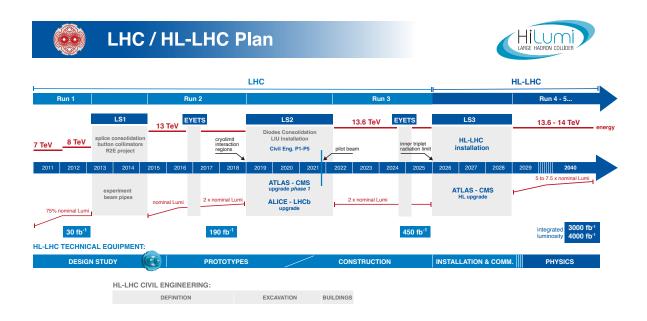

| Figure 35 – | The LHC to HL-LHC plan.                                                              | 63 |

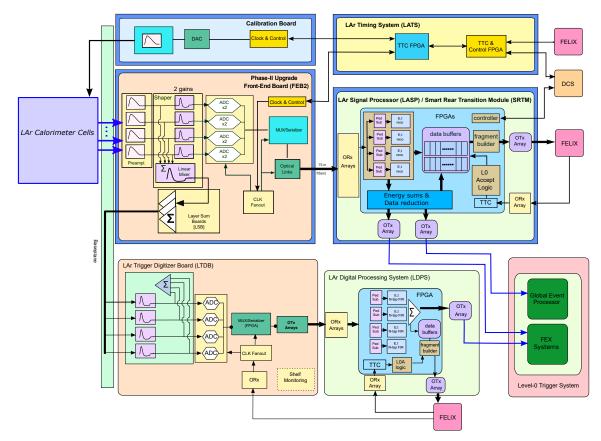

| Figure 36 – | Schematic block diagram of the LAr calorimeter readout architecture for the          |    |

|             | Phase-II upgrade.                                                                    | 64 |

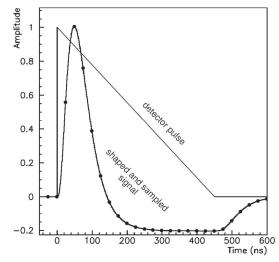

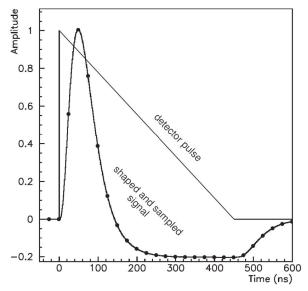

| Figure 37 – | Shapes of the LAr calorimeter current pulse in the detector and of the signal        |    |

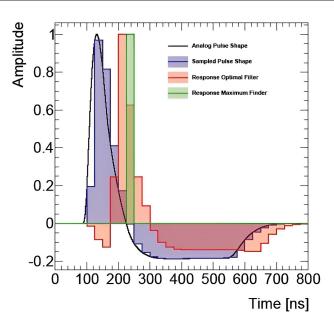

|             | output after bipolar shaping. The dots represent the samples seperated by 25 ns.     | 66 |

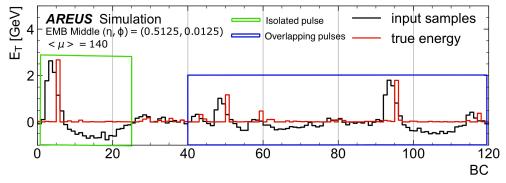

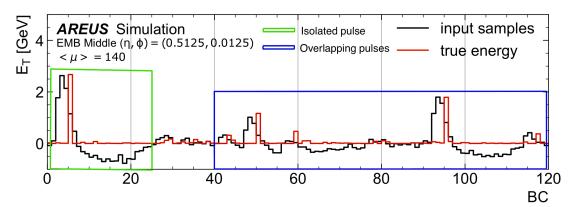

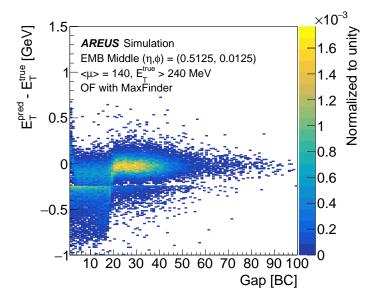

| Figure 38 – | Representation of a sample sequence (black) simulated by AREUS. The                  |    |

|             | green box indicates the pulses of a cell under HL-LHC pileup conditions,             |    |

|             | whereas the blue box highlights the presence of overlapping pulses. The true         |    |

|             | transverse energy deposits is shifted by five BC to the right and is shown in red.   | 67 |

| Figure 39 – | The shape bipolar shaping of the LAr calorimeter's pulse in the detector is          |    |

|             | depicted in black, while the signal following digitizing is displayed in purple.     |    |

|             | The red line shows the reconstruction done by the Optimal Filtering (OF)             |    |

|             | on the sampled pulse shape shifted by 5, and the green line displays the OF          |    |

|             | with the maximun value shifted by 6                                                  | 69 |

| Figure 40 – | The resolution of the OF with maximum finder as a function of the gap                |    |

|             | between two energy deposits for higher energies than 240 MeV                         | 69 |

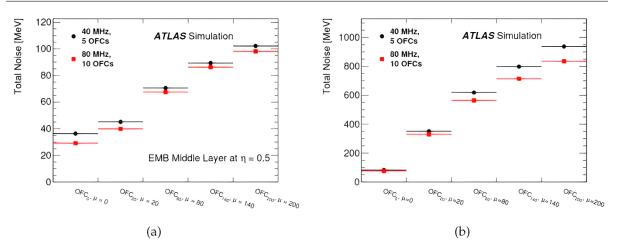

| Figure 41 – | The amount of noise, given optimal filtering with either 5 samples at a 40           |    |

|             | MHz sampling rate or 10 samples at an 80 MHz sampling rate, is determined            |    |

|             | by the level of pileup for a cell in the EM middle layer at $\eta = 0.5$ (a) and a   |    |

|             | HEC cell in the first layer at $\eta = 2.35$ (b)                                     | 70 |

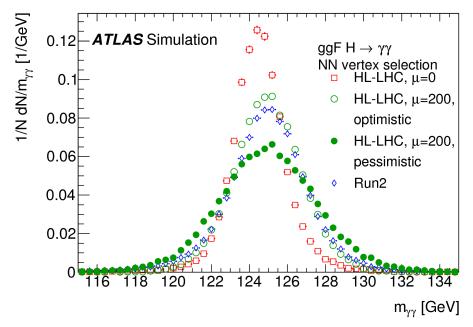

| Figure 42 – | Diphoton invariant mass obtained using data in Run 2, $\langle \mu \rangle = 0$ simulation<br>and $\langle \mu \rangle = 200$ simulation at HL-LHC using the optimistic (reduction of<br>pileup noise and more unconverted photons) and pessimistic (no improve-<br>ment) photon resolution scenarios. High pileup decrease significantly the $\gamma\gamma$                                                                                                                 |                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Figure 43 – | resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                              |

| Figure 44 – | Schematic of a Vanilla-RNN cell, a fundamental processing unit in recurrent neural networks. The cell takes two inputs: $x^{}$ , representing the current input, and $a^{}$ , representing the previous hidden state which contains information from past inputs. The cell computes a new hidden state, $a^{}$ ,                                                                                                                                                             | 73                              |

| Figure 45 – | Schematic of a LSTM cell. At each time-step, the cell tracks and updates a memory variable (the cell state) $c^{}$ , which is different from the hidden                                                                                                                                                                                                                                                                                                                      | /4                              |

| Figure 46 – | state, $a^{}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76                              |

| Figure 47 – | the deposited transverse energy with a delay of six BCs                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |

| Figure 48 – | Transverse energy resolution for optimal filtering and the different RNN algorithms. The performance is measured by comparing the real transverse energy deposited in an EMB middle LAr cell ( $\eta = 0.5125$ and $\phi = 0.0125$ ) to the prediction made by the RNN after simulating the sampled pulse with AREUS and assuming $\mu = 140$ . Only energies that are $3\sigma$ above the noise level are taken into account. The mean, the median, the standard deviation, | <ul><li>79</li><li>81</li></ul> |

| Figure 49 – | Resolution as function of the time gap between high energy deposit for                                                                                                                                                                                                                                                                                                                                                                                                       | 82                              |

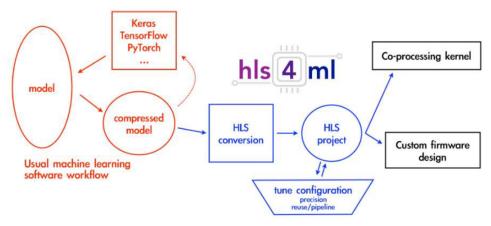

| Figure 50 – | Schematic view of the HLS4ML workflow division.                              | 84 |

|-------------|------------------------------------------------------------------------------|----|

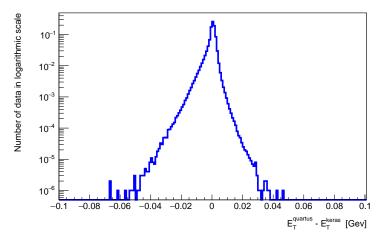

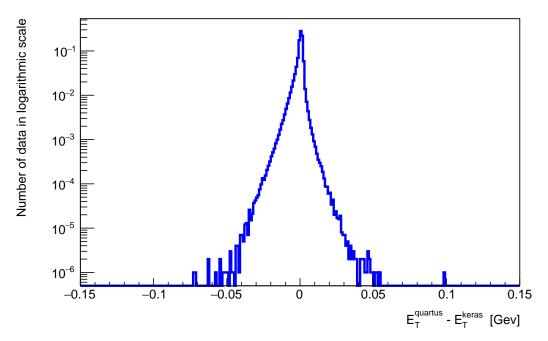

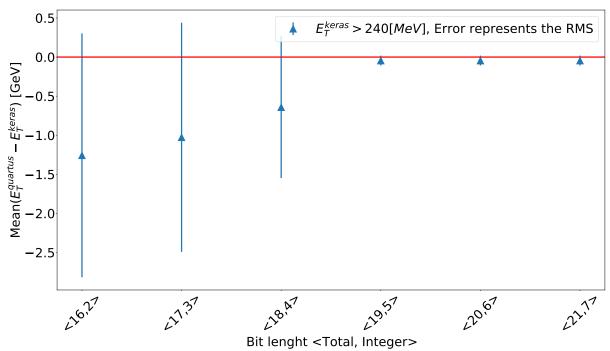

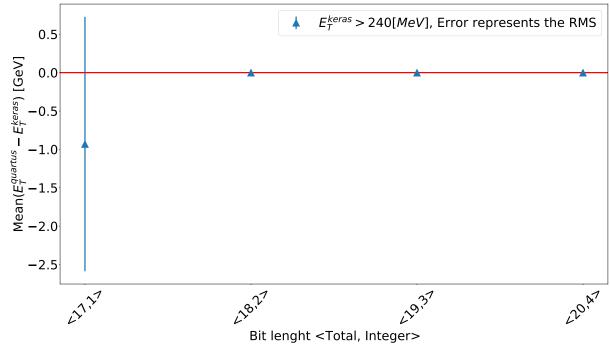

| Figure 51 – | Difference between the tranverse energy computed with Quartus and the        |    |

|             | one computed with Keras. The Quartus values are obtained using LSTM          |    |

|             | implementation in HLS4ML.                                                    | 87 |

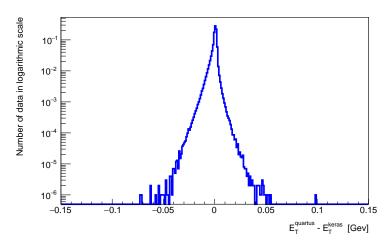

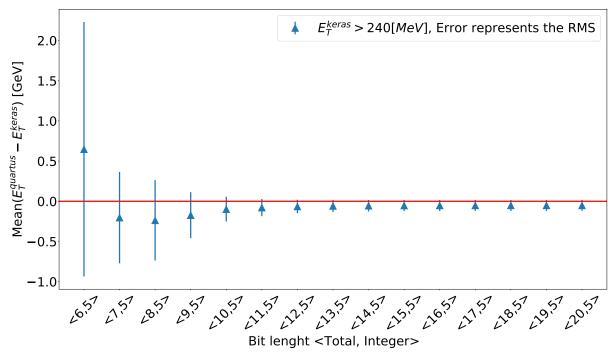

| Figure 52 – | Difference between the tranverse energy computed with Quartus and the one    |    |

|             | computed with Keras. The Quartus values are obtained using Vanilla-RNN       |    |

|             | implementation in HLS4ML.                                                    | 87 |

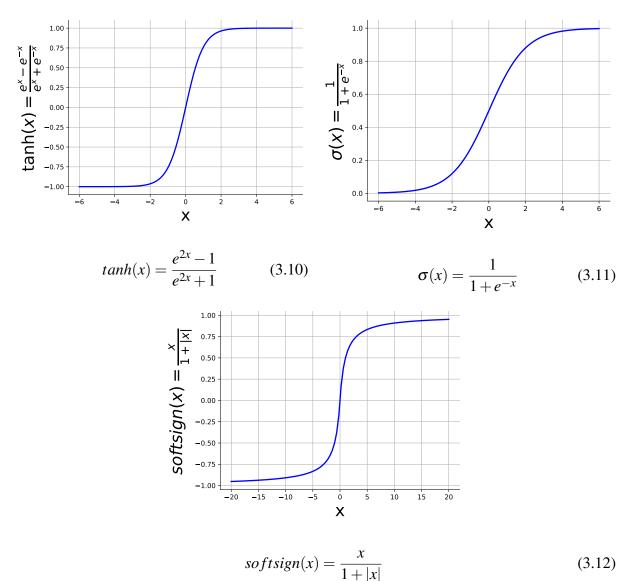

| Figure 53 – | Representation of various nonlinear functions that are used as activation    |    |

| -           | function for neural network.                                                 | 88 |

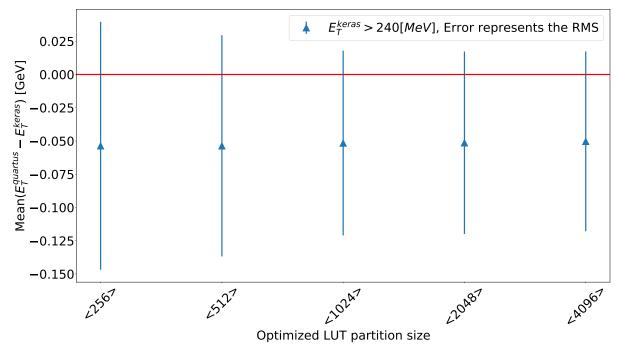

| Figure 54 – | Firmware energy resolution in a Stratix 10 FPGA as function of the LUT       |    |

| C           | size for an LSTM network at a target frequency of 400 MHz. The markers       |    |

|             | show the mean value while the error bars show the RMS                        | 89 |

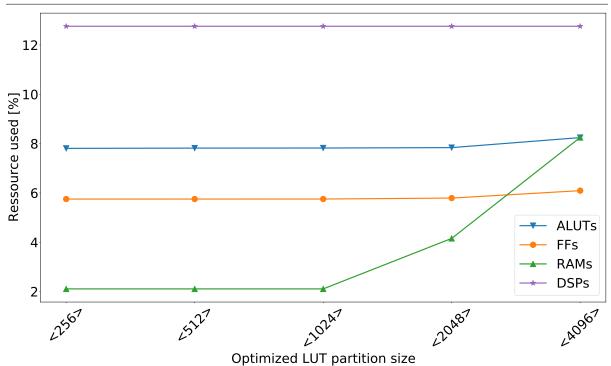

| Figure 55 – | Resource usage in a Stratix 10 FPGA as function of the LUT size for a LSTM   |    |

| -           | network at a target frequency of 400 MHz                                     | 90 |

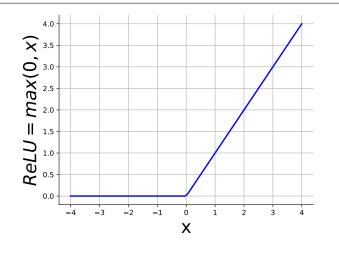

|             | Representation of the activation function ReLU.                              | 91 |

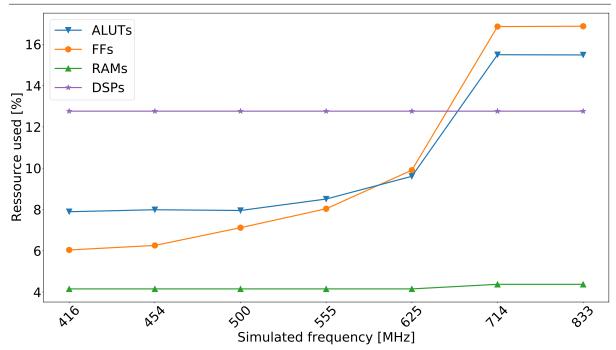

| e           | Resource usage in a Stratix 10 FPGA as function of the frequency for a       |    |

|             | LSTM network.                                                                | 92 |

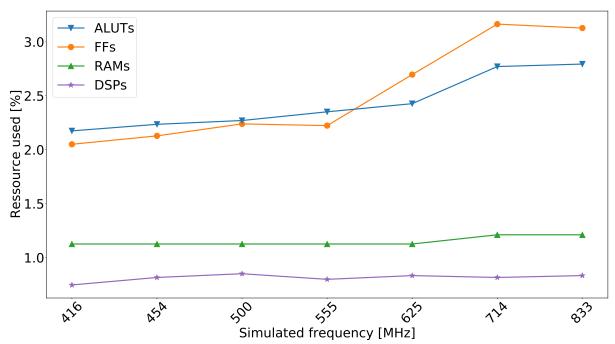

|             | Resource usage in a Stratix 10 FPGA as function of the frequency for a       |    |

| -           | Vanilla-RNN network.                                                         | 92 |

| Figure 59 – | Firmware energy resolution in a Stratix 10 FPGA as function of the Bit       |    |

|             | Width size for an LSTM network at a target frequency of 400 MHz. The         |    |

|             | markers show the mean value while the error bars show the RMS                | 93 |

| Figure 60 – | Firmware energy resolution in a Stratix 10 FPGA as function of the Bit       |    |

|             | Width size for a Vanilla-RNN network at a target frequency of 400 MHz.       |    |

|             | The markers show the mean value while the error bars show the RMS            | 94 |

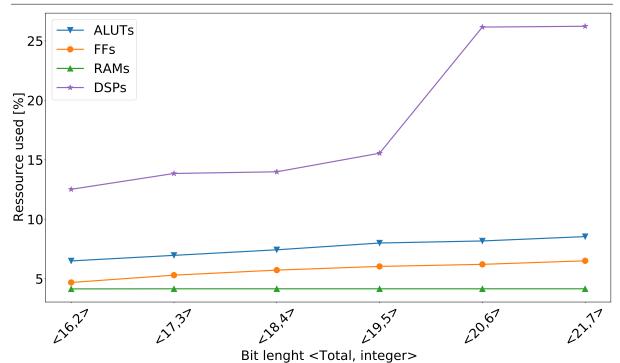

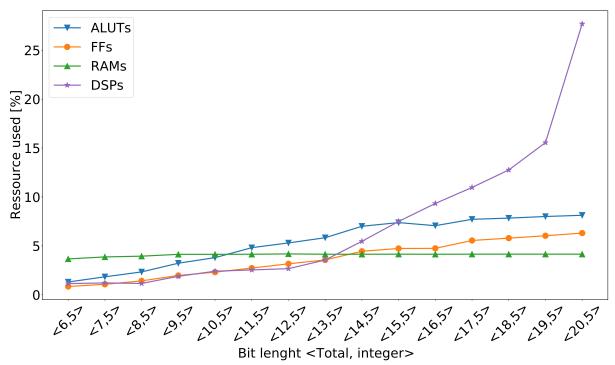

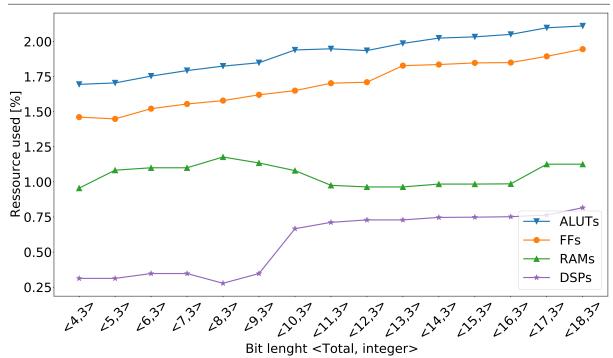

| Figure 61 – | Resource usage in a Stratix 10 FPGA as function of the Bit Width size for a  |    |

|             | LSTM network at a target frequency of 400 MHz                                | 95 |

| Figure 62 – | Resource usage in a Stratix 10 FPGA as function of the Bit Width size for a  |    |

|             | Vanilla-RNN network at a target frequency of 400 MHz                         | 95 |

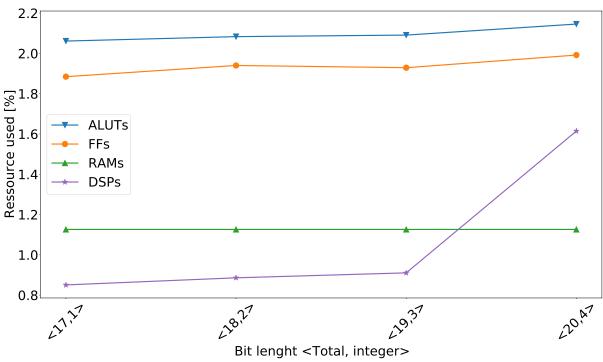

| Figure 63 – | Resource usage in a Stratix 10 FPGA as function of the Bit Width size for    |    |

|             | LSTM network at a target frequency of 400 MHz. The markers show the          |    |

|             | mean value while the error bars show the RMS                                 | 96 |

| Figure 64 – | Resource usage in a Stratix 10 FPGA as function of the Bit Width size for a  |    |

|             | Vanilla-RNN network at a target frequency of 400 MHz. The markers show       |    |

|             | the mean value while the error bars show the RMS                             | 97 |

| Figure 65 – | Resource usage in a Stratix 10 FPGA as function of the Bit Width size for an |    |

|             | LSTM network at a target frequency of 400 MHz                                | 97 |

| Figure 66 – | Resource usage in a Stratix 10 FPGA as function of the Bit Width size for a  |    |

|             | Vanilla-RNN network at a target frequency of 400 MHz                         | 98 |

|             |                                                                              |    |

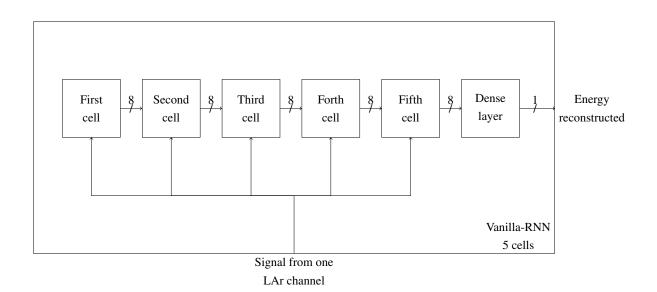

| Figure 67 –  | Diagram depicting a Vanilla-RNN which consists of 5 cells, each having<br>an internal dimension of 8 (representing the size of the state vector). These |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | cells are sequentially arranged and connected to each other. The RNN is                                                                                 |     |

|              | then followed by a dense layer. Each cell in the RNN takes input data and                                                                               |     |

|              | the state from the previous cell to compute a new state. The first cell solely                                                                          |     |

|              | relies on the input data since it lacks a preceding sample. The dense layer                                                                             |     |

|              | uses the state of the last cell to calculate the transverse energy 1                                                                                    | 100 |

| Figure 68 –  | • The Stratix 10 GX development kit employed for evaluating the firmware                                                                                | 100 |

| I Iguie 00   | comprising the neural networks                                                                                                                          | 101 |

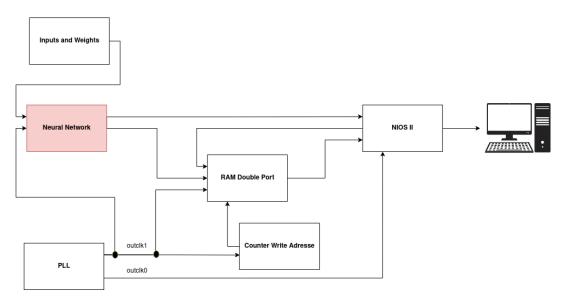

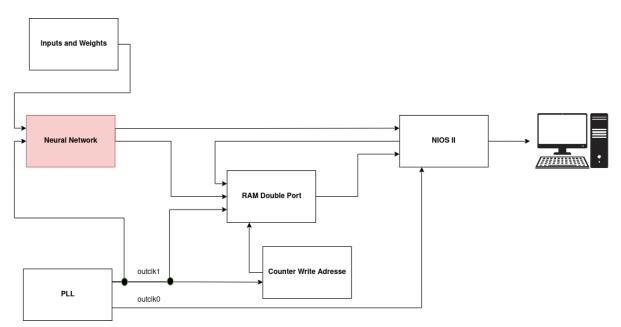

| Figure 69 –  | Simplified schematic depicting the connections between the RNN and the                                                                                  | 101 |

| I Iguie 09   | test firmware.                                                                                                                                          | 102 |

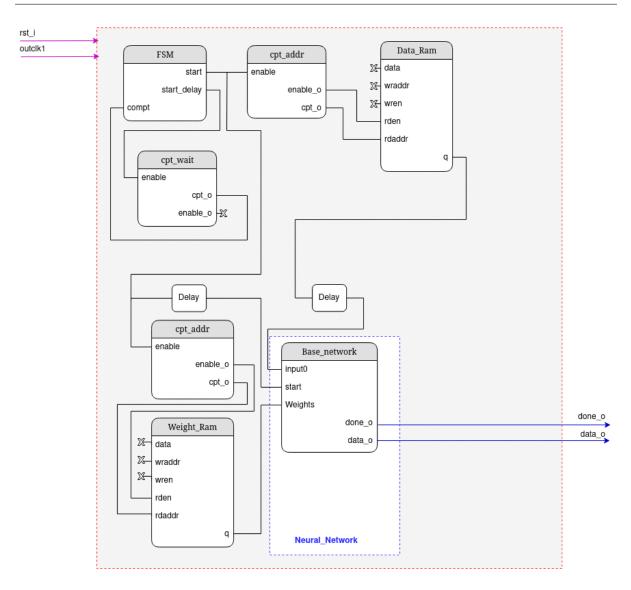

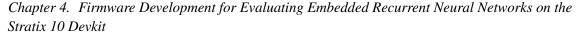

| Figure 70 –  | The schematic illustrates the components of the test firmware that are used                                                                             | 102 |

| 1.1801.0 1.0 | to input the data and the weights to the NN. It includes the core <b>base</b>                                                                           |     |

|              | <b>network</b> block with a 5-cell Vanilla-RNN having 8 internal dimensions.                                                                            |     |

|              | Two RAM segments, Weight_Ram and Data_Ram, store the data. The                                                                                          |     |

|              | <b>cpt_addr</b> counters manages RAM data transmission with precise timing.                                                                             |     |

|              | <b>Delays</b> ensure data synchronization, while <b>cpt_wait</b> briefly halts the <b>full</b>                                                          |     |

|              | state machine (FSM) for seamless initiation. The FSM coordinates the                                                                                    |     |

|              | system                                                                                                                                                  | 103 |

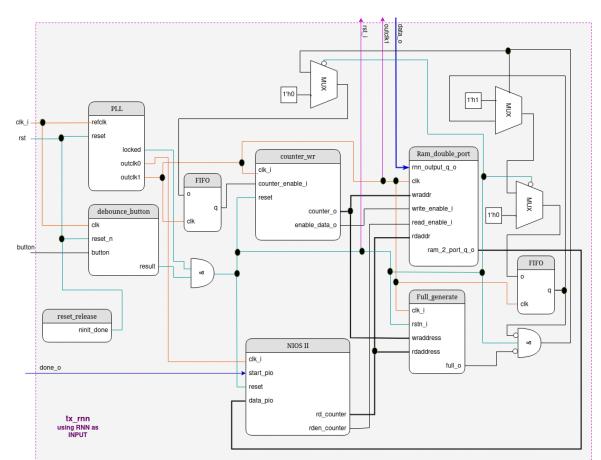

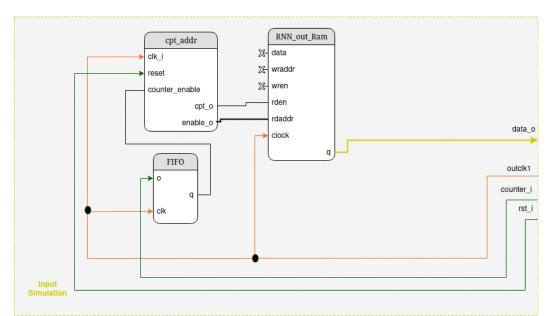

| Figure 71 –  | • The schematic illustrates the components of the test firmware that are used                                                                           |     |

| -            | to extract the computed RNN values. It includes the <b>Ram_double_port</b> that                                                                         |     |

|              | allows the reduction of the output value frequency rate. The <b>counter_wr</b>                                                                          |     |

|              | manages RAM write operations with precise timing. The FIFO ensures data                                                                                 |     |

|              | synchronization, while the Full_generate indicates if the RAM is full. The                                                                              |     |

|              | NIOS II controls the enable and read address of the RAM. The PLL creates                                                                                |     |

|              | two synchronous frequencies. The debounce_button and reset_release                                                                                      |     |

|              | enable proper system reset                                                                                                                              | 104 |

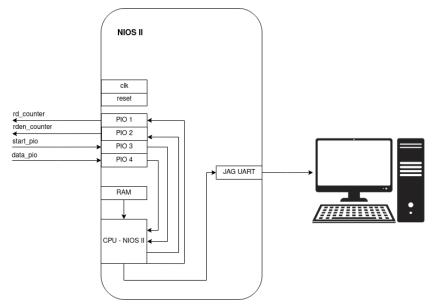

| Figure 72 –  | Components of the NIOS II Hardware Framework                                                                                                            | 106 |

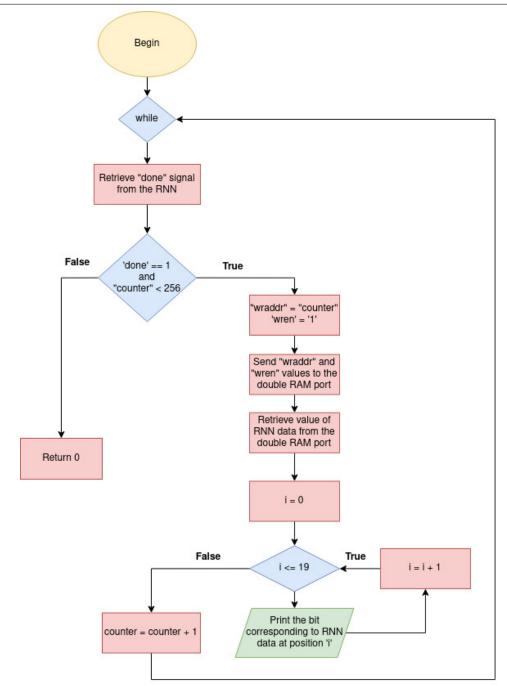

| Figure 73 –  | Representation of the code flow diagram of the C code used to retrieve data                                                                             |     |

|              | from the RNN as well as to control the read enable and read address of the                                                                              |     |

|              | double-port RAM                                                                                                                                         | 108 |

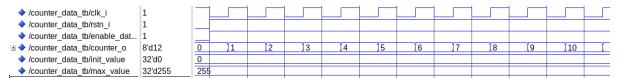

| Figure 74 –  | Simulation in ModelSim of the counter write address component. The                                                                                      |     |

|              | signal "clk_i" serves as the component clock, while "rstn_i" is an input                                                                                |     |

|              | signal for the component reset. The "enable_data_o" is an output signal                                                                                 |     |

|              | that enables writing to the RAM double-port. The signals "init_value" and                                                                               |     |

|              | "max_value" define the range (initial and final) of addresses for "counter                                                                              |     |

|              | o". The "counter_o" is responsible for handling write addresses within the                                                                              |     |

|              | double-port RAM and advances by one position during each clock cycle 1                                                                                  | 111 |

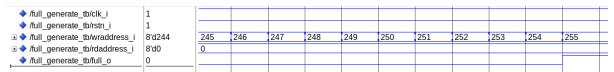

- Figure 76 Simulation in ModelSim of the full generator component. The signal "clk\_i" serves as the component clock, while "rstn\_i" is an input signal for the component reset. The signals "wraddress\_i" and "rdaddress\_i" are, respectively, the write and read address of the RAM double port. The signal "full\_o", indicates that the RAM double port is full.

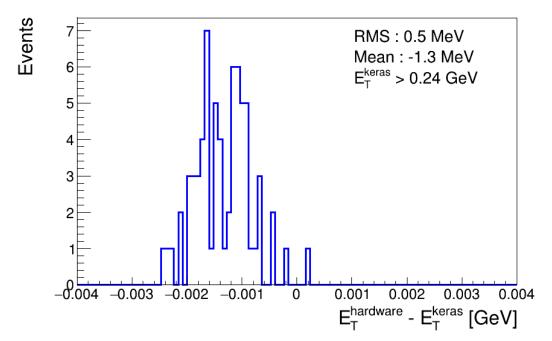

- Figure 78 The schematic depicts the components of the necessary test firmware implementation with a RAM replacing the RNN input. The arrangement closely resembles Figure 71, differing only in the origin of the "data\_o" from a RAM, and the replacement of the "done" signal with a FIFO in green. . . . 114

- Figure 79 Real-time validation of the test firmware using SignalTap with zoom in. The frequency utilized for this simulation was 560 MHz for signals "full\_o", "rstn\_i", "write\_enable\_i", "rnn\_output\_q\_o" signals and 70 MHz for signals "ram\_2\_port\_q\_o", "read\_enable\_i". The signal "write\_enable\_i" is enabling the writing while the "read\_enable\_i" maintaining deactivated the reading of the double-port RAM. The "rnn\_output\_q\_o" is the data come from the "RAM\_out\_Ram" (Figure 77). The "ram\_2\_port\_q\_o" sends the output values from the "RAM\_double\_port" (Figure 78) to the Nios II processor. The "full\_o" signal indicates the moment when this RAM is full, deactivating the "write\_enable\_i" signal. The "rsrn\_i" signal is used to reset the full system.115

| Figure 80 – | Real-time validation of the test firmware using SignalTap with zoom out.              |

|-------------|---------------------------------------------------------------------------------------|

|             | The frequency utilized for this simulation was 560 MHz for signals "full              |

|             | o", "rstn_i", "write_enable_i", "rnn_output_q_o" signals and 70 MHz for               |

|             | signals "ram_2_port_q_o", "read_enable_i". The signals "write_enable_i"               |

|             | and "read_enable_i" are enabling the writing and reading of the double-               |

|             | port RAM, respectively. The "rnn_output_q_o" is the data coming from                  |

|             | the "RAM_out_Ram" (Figure 77). The "ram_2_port_q_o" sends the output                  |

|             | values from the "RAM_double_port" (Figure 78) to the Nios II processor.               |

|             | The "full_o" signal indicates the moment when the RAM is full, deactivating           |

|             | the "write_enable_i" signal. The "rsrn_i" signal is used to reset the full system.115 |

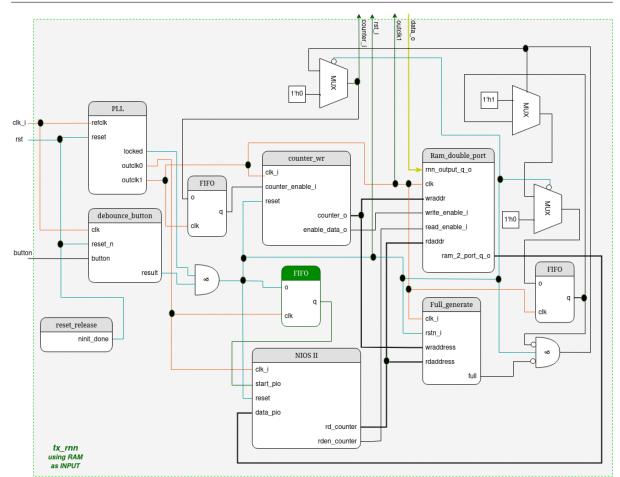

| Figure 81 – | Difference between the transverse energy computed with the firmware and               |

|             | the one computed with Keras                                                           |

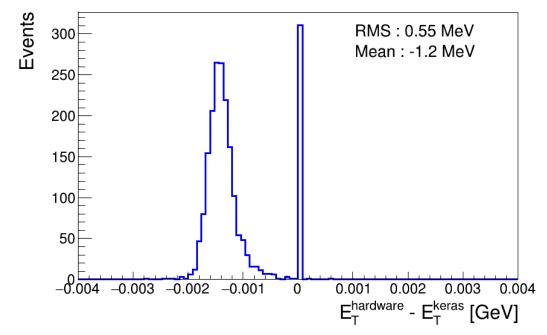

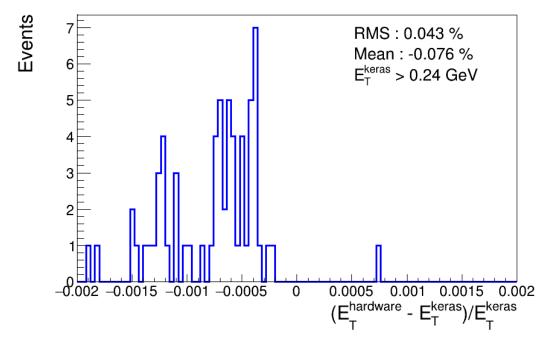

| Figure 82 – | Difference between the transverse energy computed with the firmware and               |

|             | the one computed with Keras. A cut on the Keras energy of 240 MeV is                  |

|             | performed to select values $3\sigma$ above the expected electronic noise level in     |

|             | the calorimeter                                                                       |

| Figure 83 – | Relative difference between the transverse energy computed with the firmware          |

|             | and the one computed with Keras                                                       |

| Figure 84 – | Relative difference between the transverse energy computed with the firmware          |

|             | and the one computed with Keras. A cut on the Keras energy of 240 MeV is              |

|             | performed to select values $3\sigma$ above the expected electronic noise level in     |

|             | the calorimeter                                                                       |

|             |                                                                                       |

| Table 1 | _ | Summary of helicity (right or left-handed) and different flavors. Right-handed  |    |

|---------|---|---------------------------------------------------------------------------------|----|

|         |   | helicity corresponds to a positive projection of the spin vector onto the mo-   |    |

|         |   | mentum vector, while left-handed helicity corresponds to a negative projection. | 35 |

| Table 2 | _ | Summary of the interactions, mass, and charge properties of the gauge bosons    |    |

|         |   | presented in the Standard Model                                                 | 35 |

| Table 3 | _ | Configurable key parameters of the single-cell and sliding-window algorithms.   | 80 |

| Table 4 | _ | Algorithm comparison in terms of number of parameters and MAC units             | 81 |

| Table 5 | _ | Intel Stratix 10 devices offer various combinations of operational modes and    |    |

|         |   | instances that are supported by the Variable Precision DSP Block.               | 93 |

| SYNTH   | ÈSE EN FRANÇAIS                                                     | 20        |

|---------|---------------------------------------------------------------------|-----------|

| 0.1     | Introduction                                                        | 20        |

| 0.2     | Les calorimètres LAr et la reconstruction d'énergie                 | 22        |

| 0.3     | La technique du filtre optimal                                      | 22        |

| 0.4     | Reconstruction de l'énergie avec des réseaux de neurones récurrents | 23        |

| 0.5     | RNN dans HLS4ML pour la reconstruction d'énergie                    | 25        |

| 0.6     | Évaluation des réseaux neuronaux récursifs embarqués sur le Stratix |           |

|         | 10 DevKit d'INTEL                                                   | 27        |

| 0.7     | Conclusion                                                          | 28        |

| INTROE  | DUCTION                                                             | 31        |

| 1       | STANDARD MODEL OF PARTICLE PHYSICS                                  | 33        |

| 1.1     | Fundamental Theory                                                  | 33        |

| 1.2     | Fundamental Interactions                                            | 36        |

| 1.2.1   | Strong Interaction                                                  | 36        |

| 1.2.2   | Electromagnetic Interaction                                         | 37        |

| 1.2.3   | Electroweak theory                                                  | 38        |

| 1.3     | Spontaneous Symmetry Breaking and the Higgs Mechanism               | 39        |

| 1.4     | Characteristics of proton–proton collisions                         | 40        |

| 1.5     | Beyond Standard Model Physics                                       | 41        |

| 2       | ATLAS EXPERIMENT                                                    | 42        |

| 2.1     | The Large Hadron Collider                                           | 42        |

| 2.1.1   | The accelerator design and injection chain                          | 43        |

| 2.1.2   | Experiments at the LHC                                              | <b>46</b> |

| 2.2     | The ATLAS detector                                                  | 47        |

| 2.2.1   | The ATLAS coordinate system                                         | <b>48</b> |

| 2.2.2   | The Inner Detector                                                  | <b>49</b> |

| 2.2.2.1 | The Pixel Detector                                                  | 50        |

| 2.2.2.2 | The Semiconductor Tracker Detector                                  | 53        |

| 2.2.2.3 | The Transition Radiation Tracker Detector                           | 54        |

| 2.2.3   | The Calorimeters                                                                               | 56        |

|---------|------------------------------------------------------------------------------------------------|-----------|

| 2.2.3.1 | Electromagnetic Calorimeter                                                                    | 57        |

| 2.2.3.2 | Tile Hadronic Calorimeter                                                                      | 59        |

| 2.2.3.3 | Forward Calorimeter                                                                            | 60        |

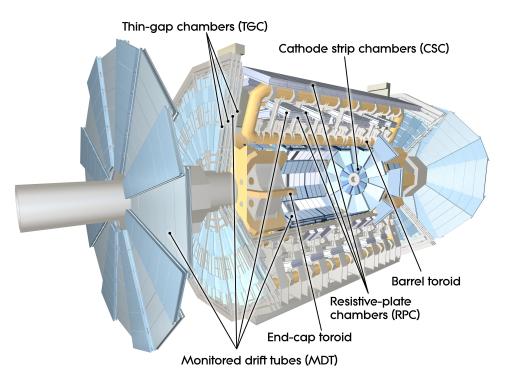

| 2.2.4   | Muon Spectrometer                                                                              | 60        |

| 2.2.4.1 | Monitored Drift Tube and Cathode Strip Chambers                                                | 61        |

| 2.2.4.2 | Resistive Plate Chambers and Thin Gap Chambers                                                 | 61        |

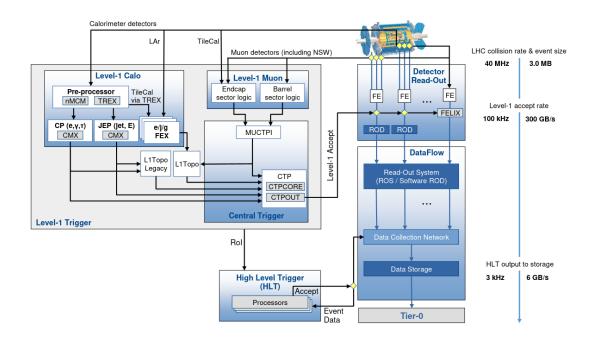

| 2.2.5   | Trigger and Data Acquisition                                                                   | 62        |

| 2.3     | High Luminosity-Large Hadron Collider                                                          | 63        |

| 3       | IMPLEMENTATION OF RECURRENT NEURAL NETWORK IN<br>HLS4ML TARGETING THE ENERGY RECONSTRUCTION IN |           |

|         | THE LAR CALORIMETER                                                                            | 65        |

| 3.1     | Introduction                                                                                   | 66        |

| 3.1.1   | Data Simulation                                                                                | 67        |

| 3.2     | The Optimal Filter Technique                                                                   | 68        |

| 3.3     | Neural Networks                                                                                | 70        |

| 3.3.1   | Artificial Neural Networks History                                                             | 70        |

| 3.3.2   | Fundamentals of Neural Networks                                                                | 71        |

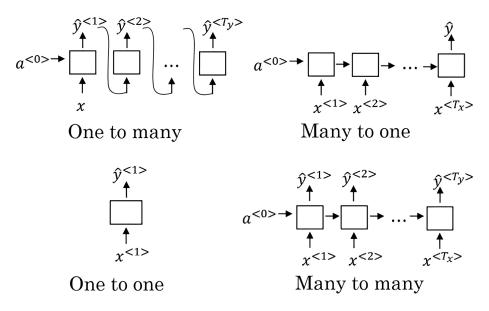

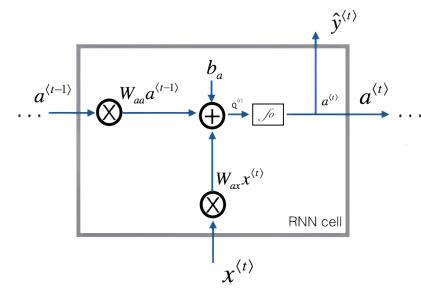

| 3.3.3   | Recurrent Neural Networks                                                                      | 72        |

| 3.3.3.1 | Vanilla Recurrent Neural Network                                                               | 74        |

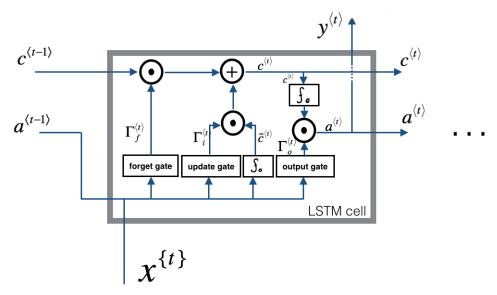

| 3.3.3.2 | Long Short-Term Memory                                                                         | 76        |

| 3.4     | Neural Network for Energy Reconstruction                                                       | 78        |

| 3.4.1   | Neural Networks results                                                                        | 80        |

| 3.5     | FPGAS                                                                                          | 82        |

| 3.5.1   | Hardware Platform Built with Intel FPGA                                                        | <i>82</i> |

| 3.5.2   | Intel High-Level Synthesis                                                                     | <i>83</i> |

| 3.6     | High Level Synthesis for Machine Learning                                                      | 83        |

| 3.7     | RNN Algorithms Implementation                                                                  | 85        |

| 3.7.1   | Implementation in HLS4ML                                                                       | 85        |

| 3.8     | RNN Optimization and Results                                                                   | 87        |

| 3.8.1   | Look-Up-Table Size                                                                             | 88        |

| 3.8.2   | Resource Usage as Function of the Frequency                                                    | <b>91</b> |

| 3.8.3   | Internal Fixed Point Size                                                                      | <i>92</i> |

| 3.8.3.1 | Integer Fixed Point                                                                            | 93        |

| 3.8.3.2 | Decimal Fixed Point                                                                            | 95        |

| 3.9     | Conclusion                                                                                     | 98        |

| 4       | FIRMWARE DEVELOPMENT FOR EVALUATING EMBEDDED                        |

|---------|---------------------------------------------------------------------|

|         | <b>RECURRENT NEURAL NETWORKS ON THE STRATIX 10 DEVKIT 99</b>        |

| 4.1     | NN firmware in VHSIC Hardware Description Language (VHDL) . 100     |

| 4.2     | Intel Development Kit                                               |

| 4.3     | General firmware test structure                                     |

| 4.3.1   | NIOS II                                                             |

| 4.3.1.1 | Structure of the NIOS II Hardware                                   |

| 4.3.1.2 | Structure of the NIOS II Software                                   |

| 4.3.2   | Double-port RAM                                                     |

| 4.3.3   | Counter for the write address of the double-port RAM                |

| 4.3.4   | Phase-Locked Loop                                                   |

| 4.3.5   | Reset release                                                       |

| 4.3.6   | Debounce button                                                     |

| 4.3.7   | Full generate                                                       |

| 4.4     | Validation with simulation                                          |

| 4.4.1   | Validation with ModelSim                                            |

| 4.5     | Validation of the energy extraction firmware on the hardware 112    |

| 4.5.1   | Design of the RAM                                                   |

| 4.5.2   | Validation with SignalTap                                           |

| 4.6     | Extraction of NN values                                             |

| 4.7     | Comparison between extracted values from hardware and simulation116 |

| 4.8     | Conclusion                                                          |

| 5       | CONCLUSION AND FUTURE PERSPECTIVES                                  |

| BIBLIO  | <b>GRAPHY</b>                                                       |

#### 0.1 Introduction

En 2012, un moment décisif en physique des particules a eu lieu lorsque les équipes ATLAS et CMS du Grand Collisionneur de Hadrons (LHC) ont révélé la découverte du boson de Higgs, la dernière pièce du puzzle du Modèle Standard (MS) de la physique des particules, enrichissant fondamentalement notre compréhension de la façon dont des particules telles que les bosons W et Z, les quarks et les leptons acquièrent leur masse grâce à leurs interactions avec le champ de Higgs. Le MS sert de tremplin vers une théorie plus complète capable d'élucider des énigmes telles que la matière noire, l'énergie sombre et l'asymétrie matière-antimatière. La prochaine étape de fonctionnement du Grand Collisionneur de Hadrons (LHC), appelée LHC à haute luminosité (HL-LHC), offrira une opportunité unique d'examiner de près le boson de Higgs mais aussi de découvrir des phénomènes rares qui vont au-delà du MS. Ceci est essentiel pour notre quête d'une compréhension plus profonde des particules fondamentales.

Le HL-LHC est prévu pour fonctionner jusqu'en 2040. Il représentera la phase finale de l'évolution du LHC, visant à augmenter considérablement sa luminosité par un facteur de 5 à 7 par rapport à sa conception initiale. Ceci se traduira par un taux de 140 à 200 collisions protonproton toutes les 25 ns. Cela impliquera également une augmentation considérable d'un ordre de grandeur de la quantité de données à enregistrer par rapport à toute les données combinées déjà recueillies lors des précédentes campagnes du LHC depuis 2011. Pour accommoder cette luminosité accrue, la deuxième phase de mise à niveau du détecteur ATLAS, dite Phase-II, prévue pour 2026-2028, est essentielle. Le détecteur ATLAS servira à la fois à scruter le Modèle Standard de la physique des particules et surtout à sonder les domaines au-delà.

Le calorimètre à argon liquide (LAr) d'ATLAS mesure principalement les énergies des particules interagissant de manière électromagnétique produites lors des collisions proton-proton au LHC. L'électronique de lecture du calorimètre LAr sera remplacée lors de la mise à niveau Phase-II du détecteur ATLAS pour préparer l'ère du HL-LHC. La nouvelle électronique de lecture comprendra des FPGA (Field Programmable Gate Array ou réseaux de portes programmables sur site) haut de gamme pour le traitement des données en temps réel. Cette mise à niveau vise à permettre des taux de déclenchement et de lecture plus élevés ainsi qu'une granularité et une efficacité améliorées au niveau du déclenchement. Un algorithme de filtrage optimal (OF) est appliqué sur le signal électronique en impulsion pour reconstruire l'énergie déposée dans chaque cellule du calorimètre LAr. Cependant, l'augmentation anticipée de la lumi-

nosité du LHC entraînera une augmentation de l'activité de « pileup », c'est-à-dire de collisions proton-proton multiples simultanées et hors temps. Cette activité de « pileup » peut dégrader significativement la résolution en énergie obtenue à partir de l'algorithme OF. Cette électronique Phase-II de traitement aura une capacité de calcul bien supérieure à la précédente. Cela permettra la mise en œuvre dans les FPGA d'algorithmes plus élaborés basés sur des réseaux neuronaux (NN) pour reconstruire les énergies déposées dans le calorimètre LAr. II a été démontré que les NN peuvent surpasser l'OF, notamment en présence de taux de « pileup » élevés. Les FPGA sont choisis pour leur capacité à traiter de grandes quantités de données avec une latence minimale, ce qui est une exigence cruciale pour le système de déclenchement d'ATLAS. L'implémentation du code en langage matériel, dit firmware, nécessite la conversion d'un modèle de réseau neuronal, écrit en langage informatique évolué, en un langage matériel spécifique pour les FPGA, tel que "High-Level Synthesis" (HLS) ou "VHSIC Hardware Description Language" (VHDL).

Cette thèse présente d'abord une description succincte du contexte scientifique théorique sous-tendant le programme HL-LHC. Le complexe d'accélérateur du CERN, le LHC, et le détecteur ATLAS sont ensuite présentés. Un accent particulier est mis sur le système de calorimétrie à argon liquide d'ATLAS qui produit les données traitées par un système électronique novateur s'appuyant sur des FPGA de dernière génération.

Cette thèse examine ensuite en profondeur le développement du firmware NN dans le langage HLS. Le HLS produit est incorporé dans la bibliothèque "High-Level Synthesis for Machine Learning" (HLS4ML), qui est une bibliothèque open source conçue pour automatiser le processus de production du firmware. Différents types de réseaux neuronaux pour les FPGA INTEL utilisés pour la reconstruction de l'énergie dans le calorimètre LAr ont été ajouté à HLS4ML. Ainsi, cette thèse introduit les réseaux neuronaux récurrents (RNN) utilisés pour la reconstruction de l'énergie, la bibliothèque HLS4ML et l'intégration des NN dans HLS4ML. L'utilisation des ressources des FPGA et les performances du firmware y sont également soigneusement analysées.

Cette thèse présente également un firmware de test conçu pour valider l'implémentation du NN dans le firmware du FPGA. Ce firmware de test permet l'injection de valeurs d'entrée dans le réseau neuronal embarqué sur le FPGA et la récupération des valeurs d'énergie calculées. Ces valeurs sont ensuite comparées aux résultats de simulation pour valider l'implémentation du NN. Le dispositif expérimental avec un kit de développement du FPGA INTEL Stratix 10, utilisé pour les tests en firmware, est décrit. Le firmware de test est également présenté, avec un aperçu de sa structure globale et une description des méthodologies et des techniques employées dans chaque composant de son architecture.

Les parties suivantes de cette synthèse vont maintenant décrire plus en détail le calorimètre, les méthodes de reconstruction en énergie et les développements et études effectués sur l'implémentation et les performances obtenues avec ces réseaux de neurones.

#### 0.2 Les calorimètres LAr et la reconstruction d'énergie

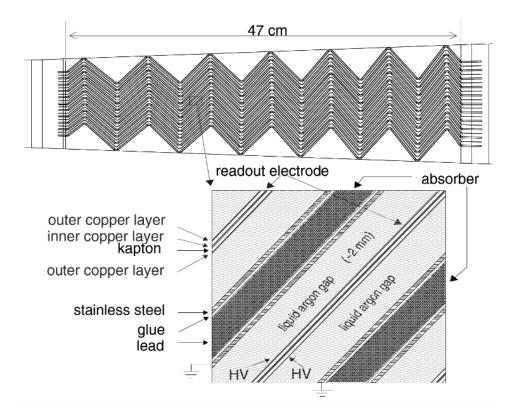

Le calorimètre à argon liquide est utilisé pour mesurer les énergies et éventuellement identifier les particules le traversant, ciblant spécifiquement les particules ionisant l'argon liquide qui sert d'environnement actif. La collecte des électrons d'ionisations par un circuit électrique d'amplification est obtenue par des électrodes soumises à une haute tension. Comme illustré dans la figure 1, le détecteur présente une réponse caractérisée par une impulsion de forme triangulaire induite par la création instantanée d'électrons d'ionisation et leur dérive dans le champs électrique produit entre les électrodes et les absorbeur en plomb/inox, cuivre ou tungstène. Cette réponse présente une montée rapide suivie d'une descente subséquente d'environ 500ns dépendant du temps de dérive dans l'argon liquide. Dans le contexte du traitement du signal, l'utilisation d'un filtre analogique est efficace pour accomplir la tâche de filtration du signal. Après la mise en place du filtre, la réponse résultante présente une impulsion bipolaire, permettant de déterminer l'amplitude du dépôt et le temps nécessaire à sa formation sur le premier lobe. La réponse présente un haut degré de cohérence, la seule variation étant l'amplitude de son pic, directement liée au dépôt d'énergie et à la durée du processus de dérive. Ce signal est ensuite numérisé à la fréquence de collision de 40 MHz. Le processus de reconstruction implique de partir de nombreux points échantillonnés sur le signal et d'utiliser un algorithme de OF pour obtenir l'énergie transverse reconstruite.

Figure 1 – Formes de l'impulsion actuelle du calorimètre LAr dans le détecteur et de la sortie du signal après le façonnage bipolaire. Les points représentent les échantillons séparés de 25 ns. [1]

#### 0.3 La technique du filtre optimal

Les dispositifs de lecture électronique actuels utilisent une technique connue sous le nom de Filtre Optimale pour calculer la quantité d'énergie dans chaque cellule. La reconstruction

d'énergie à partir de l'OF est représentée par la formule 1.

$$E(t) = \sum_{i=t}^{t+n} a_i \cdot s_i, \tag{1}$$

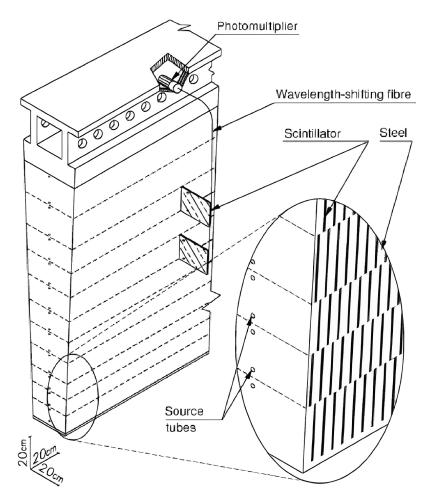

L'algorithme en question utilise un processus de filtrage sur les échantillons provenant d'un convertisseur analogique-numérique (A/D), ce qui résulte en la production d'une série temporelle d'énergie. Les coefficients du filtre sont optimisés en fonction des caractéristiques des signaux physique obtenues en faisceau test, du bruit et des signaux de calibration. La sélection de la taille de l'échantillon (N), pour tenir compte de la précision nécessaire et des ressources informatiques, impacte sur la précision de l'estimation de l'énergie. Actuellement, OF utilise trois échantillons au niveau du déclenchement et quatre échantillons au niveau de la lecture principale pour réduire le bruit et le l'empilement des signaux. Les dépôts d'énergie réels sont associés à un paquet de collision (BCID) et corrélés à des intervalles de temps spécifiques. Cependant, la résolution du OF diminue lorsque de courts intervalles de temps sont utilisés en raison de la distorsion des formes de pulse causées par les empilements successifs des impulsions, comme représenté dans la figure 2. Ceci est particulièrement pertinent dans le contexte de HL-HLC, où il y a une augmentation à la fois du taux d'empilement hors et en temps et du nombre d'impulsions.

Figure 2 – Représentation d'une séquence d'échantillons (en noir) simulée par le logiciel AREUS. Le rectangle vert indique les impulsions d'une cellule dans les conditions du HL-LHC, tandis que le rectangle bleu met en évidence la présence d'impulsions crées à différents moments et se superposant. Pour améliorer la lisibilité, les vrais dépôts d'énergie transversale sont décalés de cinq cycles de croisement vers la droite et sont affichés en rouge. [2]

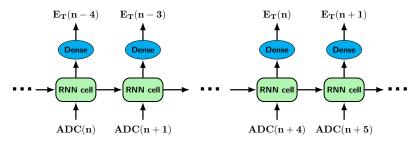

# 0.4 Reconstruction de l'énergie avec des réseaux de neurones récurrents

Afin de reconstruire les énergies, une architecture dite à fenêtres glissantes, représentée par la Figure 3, applique un Réseau de Neurones Récurrents (RNN) sur les échantillons. La séquence complète d'échantillons est divisée en séquences plus courtes qui se chevauchent, chaque séquence représentant un dépôt d'énergie. La point de calcul d'énergie pour chaque sous-séquence peut être choisie de manière à ce que la séquence contienne des informations

avant le dépôt considéré pour corriger les effets d'empilement et des échantillons après le dépôt pour reconstruire l'amplitude du signal. L'architecture de réseau choisie comporte une couche RNN et un neurone dans la couche de sortie. Quatre échantillons sont utilisés après le point de calcul de l'énergie, plus quelques autres dans le passé. Deux types de RNN ont été évalués, "Long Short-Term Memory" (LSTM) et Vanilla-RNN, qui sont respectivement une structure complexe et une simple. Les réseaux Vanilla-RNN et LSTM ont présenté des performances supérieures par rapport au réseau OF, tant en termes de biais moyen que de résolution, comme illustré dans la Figure 4. La plage contenant 98% des données a également été étudiée, et sa non symétrie indique la présence de caractéristiques non gaussiennes aux extrémités de la résolution, notamment pour des niveaux d'énergie faibles. La méthode OF a montré une tendance à mal récupérer les faibles énergies déposées, tandis que les réseaux neuronaux (NN) ont démontré une capacité plus efficace à reconstruire ces énergies.

Figure 3 – Application de la fenêtre glissante des réseaux récurrents basés sur LSTM. À chaque instant, l'amplitude du signal des quatre BC passés et présents est entrée dans une couche LSTM. La dernière sortie de cellule est concaténée avec une opération dense comprenant un seul neurone et fournissant la prédiction de l'énergie transverse. [3]

Le modèle LSTM, notamment sa variante à cellule unique, possède une quantité substantielle d'unités de multiplication-accumulation (MAC), ce qui le rend inapplicable pour une implémentation sur un FPGA. La raison de cette limitation est que les FPGAs ont une capacité limitée d'unités de multiplication-accumulation (MAC) par réseau, souvent de l'ordre de quelques centaines. Le Vanilla-RNN a présenté des performances comparables à celles du modèle LSTM, bien qu'il ait un nombre plus réduit de paramètres. En général, les performances des réseaux LSTM étaient quelque peu supérieures à celles du Vanilla-RNN. Cependant, l'implémentation LSTM (à cellule unique) nécessitait un nombre plus élevé de paramètres, environ cinq fois plus, par rapport au Vanilla-RNN.

Figure 4 – Résolution de l'énergie transversale pour un filtre optimal et les différents algorithmes RNN. Les performances sont mesurées en comparant l'énergie transverse réelle déposée dans une cellule LAr du milieu du calorimètre électromagnétique tonneaux (EMB) ( $\eta = 0,5125$  et  $\phi = 0,0125$ ) à la prédiction faite par le RNN après avoir simulé l'impulsion échantillonnée avec le logiciel AREUS et en supposant  $\mu = 140$ . Seules les énergies supérieures à  $3\sigma$  du niveau de bruit sont prises en compte. La moyenne, la médiane, l'écart-type et la plus petite plage qui inclut 98% des événements sont affichés. [3]

## 0.5 RNN dans HLS4ML pour la reconstruction d'énergie

Le HLS4ML est un outil puissant pour accélérer les applications d'apprentissage machine en transformant les modèles de haut niveau en implémentations matérielles ou firmware. Le logiciel est construit sous la forme d'une bibliothèque Python open-source qui peut traduire efficacement les modèles d'apprentissage machine, développés à l'aide de cadres populaires tels que TensorFlow, PyTorch ou Keras, en code HLS. Cette approche permet la génération automatique de circuits matériels optimisés qui peuvent être déployés sur des FPGA ou des ASIC pour obtenir de haute performance. La flexibilité de HLS4ML permet aux développeurs d'explorer facilement différentes options de conception et compromis, sans avoir besoin de modifier le code. Le HLS4ML ne prenait pas en charge les réseaux de neurones récurrents (RNN) pour les FPGA de la société INTEL. Dans le cadre de cette thèse, afin de prendre en charge les modèles RNN dans HLS4ML, un code C++ générique a été utilisé pour implémenter LSTM et Vanilla-RNN. De nouveaux paramètres ont également été ajoutés pour personnaliser la fonctionnalité du programme. Les modèles RNN dans HLS4ML ont été exécutés pour tester la flexibilité, les performances et la résolution du firmware implémenté. Un LSTM avec des fonctions non linéaires tanh et sigmoïde et un Vanilla-RNN avec des fonctions d'activation ReLU (Rectified Linear unit) ont été examinés. Les figures 5 et 6 montrent la disparité entre la valeur obtenu à partir de Keras et la simulation dans Quartus HLS4ML en utilisant le LSTM et le Vanilla-RNN. Le LSTM et le Vanilla-RNN ont des valeurs efficaces, ou racine de la moyenne des carrés (RMS), de 0,0033 et 0,0031 [GeV], respectivement, avec un pic maximum à zéro. Cela prouve que l'implémentation RNN a fonctionné.

Figure 5 – Différence entre l'énergie transverse calculée avec Quartus et celle calculée avec Keras. Les valeurs de Quartus sont obtenues en utilisant l'implémentation LSTM dans HLS4ML.

Figure 6 – Différence entre l'énergie transverse calculée avec Quartus et celle calculée avec Keras. Les valeurs de Quartus sont obtenues en utilisant l'implémentation Vanilla-RNN dans HLS4ML.

# 0.6 Évaluation des réseaux neuronaux récursifs embarqués sur le Stratix 10 DevKit d'INTEL

Le firmware dans HLS permet un prototypage rapide et une amélioration de l'architecture réseau. Mais cette thèse montre que l'implémentation HLS ne parvient pas à atteindre la fréquence nécessaire pour traiter dans un FPGA tous les 384 canaux, correspondant à trois cartes d'électronique de lecture du calorimètre électromagnétique, aux niveaux de latence requis. Le langage de description matériel VHDL associé au logiciel de conception QUARTUS, apportant beaucoup plus de fonctionnalités bas niveau et de flexibilité, a donc été utilisé pour améliorer les performance par rapport à l'implémentation HLS, répondant ainsi aux critères du firmware de la Phase II. Cette thèse décrit également comment tester le firmware NN in situ. Pour vérifier l'efficacité de l'implémentation NN sur la plateforme matérielle, un firmware de test a donc été développé.

Figure 7 – Schéma simplifié des connexions entre le RNN et le firmware de test.

Ce firmware de test est un cadre qui permet l'injection de données dans le NN et la récupération des énergies transverses reconstruites par l'implémentation FPGA du firmware RNN. Comme le montre le diagramme simplifié dans la Figure 7, la sortie du firmware RNN passera par plusieurs composants critiques avant d'atteindre la sortie vers l'ordinateur. Les données d'entrée et les poids sont transférés de la RAM vers le réseau neuronal, qui calcule ensuite l'énergie et la transfère vers une autre RAM. Le processeur logiciel embarqué, NIOS, lit cette deuxième RAM et envoie les données correspondantes à l'ordinateur. Le firmware de test est conçu avec la modularité à l'esprit afin de faciliter le test de diverses formes de firmware de réseau neuronal. Le firmware NN est validé, et la différence entre Keras et NN, representée sur les figures 8 et 9, s'est avérée être inférieure à 0,1% pour les énergies supérieures au seuil de bruit, ce qui est cohérent avec les valeurs prédites par simulation. Il convient de noter que la validation du firmware de test a été effectuée en utilisant un ensemble contraint de valeurs. Chaque exécution

est limitée à 256 extractions de valeurs. Pour valider la stabilité du firmware sur des périodes prolongées à 40 MHz, un test supplémentaire essentiel est requis. Cela peut être accompli en comparant les énergies calculées dans le FPGA aux valeurs attendues contenues dans la RAM. Avant de pouvoir être testés sur la carte LASP finale, le NN et le firmware de test doivent également être transférés sur les FPGA Agilex.

Figure 8 – Différence entre l'énergie transverse calculée avec le firmware et celle calculée avec Keras.

Figure 9 – SDifférence relative entre l'énergie transverse calculée avec le firmware et celle calculée avec Keras.

#### 0.7 Conclusion

La haute luminosité du HL-LHC entraînera des collisions avec un empilement élevé, ce qui se traduira par une réduction de la précision de la reconstruction des énergies déposées dans le calorimètre LAr de l'ATLAS avec l'utilisation de l'algorithme de filtrage optimal. Pour atteindre les objectifs de l'expérience ATLAS, le développement de méthodes innovantes de reconstruction de l'énergie est impératif. La mise à niveau de la phase II, prévue pour 2026-2028, implique le remplacement du système de lecture du calorimètre LAr.

Cette mise à niveau implique le remplacement de l'électronique de lecture et de traitement des données LAr par des cartes d'électronique à base de FPGA de pointe, offrant davantage de capacités de traitement et permettant la mise en œuvre de réseaux neuronaux pour la reconstruction de l'énergie. Ces algorithmes de reconstruction de l'énergie sont destinés à être intégrés, pour la phase-II, dans ces cartes, appelées LASP et contenant deux FPGAs.

Les architectures Vanilla-RNN et LSTM ont été développées pour reconstruire l'énergie déposée dans les cellules LAr et ont montré des performances améliorées par rapport à l'algorithme de filtrage optimal dans les circonstances exigeantes du HL-LHC. Les RNN ont été conçus pour reconstruire précisément l'énergie des impulsions superposées, ce qui permet de remédier aux vulnérabilités de l'algorithme de filtrage optimal en particulier pour de faibles énergies.

Cette thèse présente la mise en œuvre du réseau neuronal développé en firmware à l'aide du langage HLS, son implémentation dans la bibliothèque HLS4ML et les performances obtenues. De plus, elle décrit la conception d'un firmware de test, utilisé pour valider la mise en œuvre du réseau neuronal dans le matériel. La bibliothèque HLS4ML traduit les réseaux neuronaux développés avec des outils courants d'apprentissage automatique (tels que Keras) en langage HLS pouvant être utilisé pour générer du firmware. Elle rationalise l'étalonnage et l'optimisation des paramètres pour les réseaux neuronaux afin de les adapter aux structures FPGA, accélérant ainsi la phase de prototypage.

Cependant, le package HLS4ML ne prenait pas en charge les architectures RNN et les FPGA INTEL. J'ai implémenté les architectures Vanilla-RNN et LSTM dans HLS4ML de manière à réduire l'utilisation des ressources sur les FPGA tout en maintenant les performances. Cette implémentation ciblait les FPGA INTEL avec Quartus HLS. J'ai utilisé cette implémentation pour scanner les paramètres du réseau neuronal et trouver les réglages optimaux pouvant s'insérer dans les ressources du FPGA. Cependant, HLS, et donc HLS4ML, s'est révélé manquer de flexibilité pour générer un firmware conforme à la spécification LASP.

Aussi, un firmware en VHDL a été développé pour optimiser davantage le firmware HLS et répondre aux spécifications. Bien que le développement en HLS ait été très utile dans les phases de prototypage pour atteindre une optimisation rapide, pour valider le firmware RNN sur les FPGA, j'ai créé et déployé un firmware de test ciblant le kit de développement Intel Stratix 10. Ce firmware de test fournit les valeurs d'entrée et les poids au firmware RNN. Il permet également l'extraction de l'énergie reconstruite par le firmware RNN au moyen d'un système d'opération embarqué sur puce (NIOS II) et d'une connexion JTAG. Le firmware de test a été utilisé pour valider le firmware NN, et les valeurs extraites du FPGA se sont avérées correspondre aux valeurs attendues de la simulation.