# Co-design and implementation of a minimal kernel oriented by its proof, and evolution towards multicore architectures

Quentin Bergougnoux

#### ▶ To cite this version:

Quentin Bergougnoux. Co-design and implementation of a minimal kernel oriented by its proof, and evolution towards multicore architectures. Hardware Architecture [cs.AR]. Université de Lille, 2019. English. NNT: 2019LILUI029. tel-04398735

# HAL Id: tel-04398735 https://hal.science/tel-04398735v1

Submitted on 16 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Thèse

pour obtenir le grade de

#### DOCTEUR de l'Université de Lille

Domaine: Informatique

préparée au laboratoire CRIStAL

sous la supervision de École Doctorale des Sciences Pour l'Ingénieur

soutenue par

# Quentin Bergougnoux

le 19 juin 2019

#### Titre:

Co-design et implémentation d'un noyau minimal orienté par sa preuve, et évolution vers les architectures multi-cœur

> Directeur de thèse : Gilles Grimaud Co-directeur de thèse : Julien Cartigny

#### Jury

Pr. Noël De Palma,

Pr. Gaël Thomas,

Pr. Sébastien Monnet,

Mme. Fabienne Boyer,

Pr. Gilles Grimaud,

M.. Julien Cartigny,

President (Université Grenoble Alpes)

Rapporteur (Université Savoie Mont Blanc)

Examinateur (Université Grenoble Alpes)

Directeur de thèse (Université de Lille)

Co-directeur de thèse (Université de Lille)

## PhD Thesis

to obtain the grade of

#### DOCTEUR de l'Université de Lille

Domain: Computer Science

prepared in CRIStAL laboratory

under the supervision of École Doctorale des Sciences Pour l'Ingénieur

defended by

# Quentin Bergougnoux

on June 19, 2019

#### Title:

Co-design and implementation of a minimal kernel oriented by its proof, and evolution towards multicore architectures

> PhD. advisor: Gilles Grimaud PhD. co-advisor: Julien Cartigny

#### Jury

Pr. Noël De Palma, President (Université Grenoble Alpes) Pr. Gaël Thomas, Rapporteur (Telecom Sud Paris)

Pr. Sébastien Monnet, Rapporteur (Université Savoie Mont Blanc) Mme. Fabienne Boyer, Examiner (Université Grenoble Alpes)

Pr. Gilles Grimaud, Advisor (Université de Lille) M. Julien Cartigny, Co-advisor (Université de Lille)  $\ll$  Il est dur d'échouer, mais il est pire de n'avoir jamais tenté de réussir. »

— Franklin Delano Roosevelt

# Remerciements

Je tiens en premier lieu à remercier mes directeurs de thèse, Gilles Grimaud et Julien Cartigny. Comme tu l'as si bien exprimé Gilles, cette thèse fut une aventure pour nous tous, avec son lot d'embûches et d'aléas imprévus. Je peux aujourd'hui avoir la satisfaction et la fierté de l'avoir achevée, et vous dois énormément pour ça.

Je voudrais également remercier Gaël Thomas et Sébastien Monnet, pour avoir accepté de rapporter cette thèse et pour l'intérêt que vous avez porté à mon travail. Je remercie également Noël de Palma pour avoir accepté de présider le jury, ainsi que Fabienne Boyer pour avoir accepté d'en être examinatrice. J'ai énormément apprécié la richesse des échanges que nous avons pu avoir au cours de la soutenance et ce fut un honneur d'avoir votre présence au sein de ce jury.

J'adresse également de chaleureux remerciements à l'équipe 2XS et à tous ceux que j'ai pu côtoyer régulièrement au laboratoire. Je ne vais pas tous vous nommer ici car il y en aurait pour des pages et des pages, mais tous ces instants passés avec chacun d'entre vous ont égayé cette longue aventure. Je n'en serais probablement pas là si vous n'aviez pas fait parti, ne serait-ce que de façon éphémère, de ce quotidien. La personne que je suis devenue aujourd'hui, c'est aussi à vous que je la dois.

Sur un plan plus personnel, j'ai également des remerciements à adresser tout d'abord à ma famille: ma sœur Loraine, mes parents Philippe et Christine, mes grands-parents, et tous les autres. Vous qui m'avez porté et supporté pendant ces années, et qui m'avez poussé à continuer dans les moments de doute voire de détresse, je vous dois également énormément.

De même, je souhaiterais également adresser quelques mots à mes amis proches, qui m'ont également soutenu et porté quand il le fallait. Nous avons vécu beaucoup de choses ensemble, et j'espère que nous en vivrons encore beaucoup à l'avenir. Vous êtes une seconde famille pour moi - une famille un peu étrange, certes, mais une famille tout de même!

Enfin, j'adresse également plus particulièrement un énorme merci à ma compagne, Aurore, qui a eu le malheur de me subir au quotidien pendant cette dernière année. Je suis conscient que ça n'a pas dû être simple tous les jours, avec la montée de la pression et du stress à l'approche du jour fatidique. Tu n'as jamais cessé de me soutenir et de me pousser à aller au bout, et de croire en moi malgré mon pessimisme naturel. Du fond du cœur, un énorme merci.

Cette page de remerciements approche de la fin, aussi ai-je un dernier remerciement un peu spécial à adresser.

Merci à mon chat Neppy. En t'entendant miauler pendant une heure entière devant une porte fermée, et, par lassitude, cédant et t'ouvrant la porte, tu m'as fait comprendre qu'à force de persévérance, on arrivait toujours à ses fins... Il en est allé de même pour cette thèse. Cela peut paraître un peu ridicule, mais tes ronronnements et tes bêtises incessantes m'ont toujours redonné le sourire quand il le fallait, alors merci à toi, Little Nep.

# Résumé

Avec la croissance majeure de l'Internet des Objets et du Cloud Computing, la sécurité dans ces systèmes est devenue un problème majeur. Plusieurs attaques ont eu lieu dans les dernières années, mettant en avant la nécessité de garanties de sécurité fortes sur ces systèmes. La plupart du temps, une vulnérabilité dans le noyau ou un de ses modules est suffisante pour compromettre l'intégralité du système.

Établir et prouver des propriétés de sécurité par le biais d'assistants de preuve semble être un grand pas en avant vers l'apport de garanties de sécurité. Cela repose sur l'utilisation de modèles mathématiques dans le but de raisonner sur leur comportement, et d'assurer que ce dernier reste correct. Cependant, en raison de la base de code importante des logiciels s'exécutant dans ces systèmes, plus particulièrement le noyau, cela n'est pas une tâche aisée. La compréhension du fonctionnement interne de ces noyaux, et l'écriture de la preuve associée à une quelconque propriété de sécurité, est de plus en plus difficile à mesure que le noyau grandit en taille.

Dans cette thèse, je propose une nouvelle approche de conception de noyau, le proto-noyau. En réduisant les fonctionnalités offertes par le noyau jusqu'à leur plus minimal ensemble, ce modèle, en plus de réduire au maximum la surface d'attaque, réduit le coût de preuve au maximum. Il permet également à un vaste ensemble de systèmes d'être construits par-dessus, considérant que la minimalité des fonctionnalités comprises dans le noyau oblige les fonctionnalités restantes à être implémentées en espace utilisateur.

Je propose également dans cette thèse une implémentation complète de ce noyau, sous la forme du proto-noyau Pip. En ne fournissant que les appels systèmes les plus minimaux et indispensables, l'adaptation du noyau à des usages concrets et la faisabilité de la preuve sont assurées. Afin de réduire le coût de transition modèlevers-binaire, la majorité du noyau est écrite directement en Gallina, le langage de l'assistant de preuve Coq, et est automatiquement convertie en code C compilable pendant la phase de compilation. Pip ne repose alors que sur une fine couche d'abstraction matérielle écrite dans des langages de bas niveau, qui ne fournit que les primitives que le modèle requiert, telles que la configuration du matériel.

De plus, étant donné que l'Internet des Objets et le Cloud Computing nécessitent aujourd'hui ces architectures, je propose plusieurs extensions au modèle de Pip afin de supporter le matériel multi-cœur. Soutenus par des implémentations, ces modèles permettent d'apporter le proto-noyau Pip dans les architectures multi-cœur, apportant ainsi des garanties de sécurité fortes dans ces environnement.

Enfin, je valide mon approche et son implémentation par le biais d'évaluations de performances et d'une preuve de concept de portage de noyau Linux, démontrant ainsi la flexibilité du proto-noyau Pip dans des environnements réels.

# Abstract

Due to the major growth of the Internet of Things and Cloud Computing worlds, security in those systems has become a major issue. Many exploits and attacks happened in the last few years, highlighting the need of strong security guarantees on those systems. Most of the times, a vulnerability in the kernel or one of its modules is enough to compromise the whole system.

Etablishing and proving security properties through proof assistants seems to be a huge step towards bringing security guarantees. This relies on using mathematical models in order to reason on their behaviour, and prove the latter remains correct. Still, due to the huge and complex code base of the software running on those systems, especially the kernel, this is a tedious task. Understanding the internals of those kernels, and writing an associated proof on some security property, is more and more difficult as the kernel grows in size.

In this thesis, I propose a new approach of kernel design, the proto-kernel. By reducing the features provided by the kernel to their most minimal subset, this model, in addition to lowering the attack surface, reduces the cost of the proof effort. It also allows a wide range of systems to be built on top of it, as the minimality of the features embedded into the kernel causes the remaining features to be built at the userland level.

I also provide in this thesis a concrete implementation of this model, the Pip proto-kernel. By providing only the most minimal and mandatory system calls, both the usability of the kernel and the feasibility of the proof are ensured. In order to reduce the model-to-binary transition effort, most of the kernel is written directly in Gallina, the language of the Coq Proof Assistant, and is automatically converted to compilable C code during compilation phase. Pip only relies on a thin hardware abstraction layer written in low-level languages, which provides the operations the model requires, such as modifying the hardware configuration.

Moreover, as Internet of Things and Cloud Computing use cases would require, I propose some extensions of Pip's model, in order to support multicore hardware. Backed up by real implementations, those models bring the Pip proto-kernel to multicore architectures, bringing strong security guarantees in those modern environments.

Finally, I validate my approach and its implementation through benchmarks and a Linux kernel port proof-of-concept, displaying the flexibility of the Pip proto-kernel in real world environments.

# Contents

|          | Remerciements |          |                                     |     |  |  |  |  |  |

|----------|---------------|----------|-------------------------------------|-----|--|--|--|--|--|

|          | Résu          | ımé .    |                                     | V   |  |  |  |  |  |

| Abstract |               |          |                                     |     |  |  |  |  |  |

|          | Con           | tents.   |                                     | vii |  |  |  |  |  |

| In       | trodi         | uction   |                                     | 1   |  |  |  |  |  |

| 1        | Stat          | te of th | ne art                              | 5   |  |  |  |  |  |

|          | 1             | Opera    | ting system architecture            | 5   |  |  |  |  |  |

|          |               | 1.1      | Monolithic kernels                  |     |  |  |  |  |  |

|          |               | 1.2      | Micro kernels                       | 6   |  |  |  |  |  |

|          |               | 1.3      | Hybrid kernels                      | 8   |  |  |  |  |  |

|          |               | 1.4      | Exokernel                           | 8   |  |  |  |  |  |

|          |               | 1.5      | Trusted computing base and security | 9   |  |  |  |  |  |

|          |               | 1.6      | Managing hardware                   | 9   |  |  |  |  |  |

|          | 2             | Virtua   | d machines                          | 10  |  |  |  |  |  |

|          |               | 2.1      | Virtualization and abstraction      | 10  |  |  |  |  |  |

|          |               | 2.2      | Virtualization kinds                | 12  |  |  |  |  |  |

|          |               | 2.3      | Hypervision                         | 12  |  |  |  |  |  |

|          |               | 2.4      | Virtualization methods              | 13  |  |  |  |  |  |

|          | 3             | TCB a    | and formal proof                    | 16  |  |  |  |  |  |

|          |               | 3.1      | Minimizing the TCB                  | 16  |  |  |  |  |  |

|          |               | 3.2      | Proof and security                  | 16  |  |  |  |  |  |

|          |               | 3.3      | Goals of proving the TCB            | 16  |  |  |  |  |  |

|          |               | 3.4      | Hardware architecture               | 17  |  |  |  |  |  |

|          |               | 3.5      | Model-based proof                   | 18  |  |  |  |  |  |

|          |               | 3.6      | Implementation-based proof          | 18  |  |  |  |  |  |

|          |               | 3.7      | Combining both methodologies        | 19  |  |  |  |  |  |

|          |               | 3.8      | Common Criteria                     | 19  |  |  |  |  |  |

|          | 4             | Micro    | kernels and proofs                  | 21  |  |  |  |  |  |

|          |               | 4.1      | The seL4 micro kernel               | 21  |  |  |  |  |  |

|          |               | 4.2      | Access control and restrictions     | 22  |  |  |  |  |  |

|          |               | 4.3      | Refinement proof                    | 22  |  |  |  |  |  |

|          |               | 4.4      | Layered proof                       | 23  |  |  |  |  |  |

|          |               | 4.5      | Proof and language                  | 23  |  |  |  |  |  |

|          | 5             | Conclu   | asion                               | 23  |  |  |  |  |  |

| <b>2</b> | Pro | blem statement and model design 2        | 5 |

|----------|-----|------------------------------------------|---|

|          | 1   | Proof approach                           | 5 |

|          |     | 1.1 Proof-oriented design                | 5 |

|          |     | 1.2 Abstract model                       | 6 |

|          |     | 1.3 Security                             | 7 |

|          |     | 1.4 Performance                          | 8 |

|          | 2   | Hierarchical model                       | 9 |

|          |     | 2.1 Usual TCB model                      | 9 |

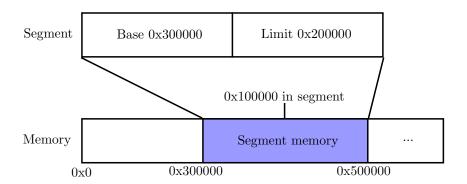

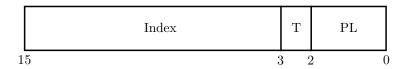

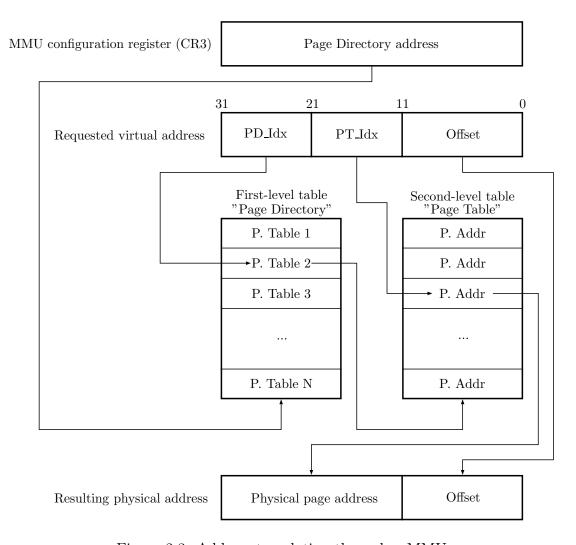

|          |     | 2.2 Segmentation vs. MMU                 | 0 |

|          |     | 2.3 Towards separation kernels           | 4 |

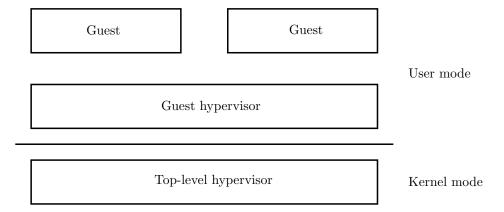

|          |     | 2.4 Recursive virtualization             | 4 |

|          |     | 2.5 Hierarchical TCB                     | 5 |

|          |     | 2.6 Access control management            | 6 |

|          | 3   | Interrupts and abstraction delegation    | 7 |

|          |     | 3.1 Execution flow                       |   |

|          |     | 3.2 Abstracting the interrupt controller |   |

|          |     | 3.3 Scheduling                           |   |

|          |     | 3.4 User mode implementation             |   |

|          | 4   | Conclusion                               |   |

|          | -   |                                          | _ |

| 3        | The | Pip proto-kernel 4                       | 1 |

|          | 1   | Proto-kernel                             | 1 |

|          |     | 1.1 Features                             | 1 |

|          |     | 1.2 Properties                           | 2 |

|          |     | 1.3 Managing virtual memory 4            | 3 |

|          |     | 1.4 Managing control flow                | 4 |

|          |     | 1.5 Managing the target architecture 4   | 5 |

|          | 2   | Proof integration                        | 6 |

|          |     | 2.1 Compiling the model                  | 6 |

|          |     | 2.2 Kernel architecture                  | 7 |

|          |     | 2.3 Kernel structures                    | 8 |

|          |     | 2.4 Memory model overhead                | 0 |

|          |     | 2.5 Initial state                        | 2 |

|          | 3   | Multicore                                | 3 |

|          |     | 3.1 Motivations                          | 3 |

|          |     | 3.2 Hardware architecture                | 4 |

|          |     | 3.3 Issues                               | 4 |

|          |     | 3.4 Multicore models                     | 6 |

|          |     | 3.5 Use cases                            |   |

|          | 4   | Conclusion                               |   |

|          |     |                                          |   |

| 4        |     | formances and return on experience 6     |   |

|          | 1   | Single core                              |   |

|          |     | 1.1 Micro benchmarks                     |   |

|          |     | 1.2 Introducing the macro-benchmarks 6   |   |

|          | _   | 1.3 Results                              |   |

|          | 2   | Feedback: the Linux kernel               |   |

|          |     | 2.1 Porting Linux                        | 6 |

| vii      | i   | CONTENT                                  | S |

|         | 2.2     | Minalro                            | 67  |

|---------|---------|------------------------------------|-----|

|         | 2.3     | Minako                             |     |

|         | 2.3     | Booting Linux                      |     |

|         | 2.4     | Isolating processes                |     |

| 3       | -       | Performances                       |     |

| 3       | Multico |                                    |     |

|         | 3.1     | Micro benchmarks                   |     |

| 4       | 3.2     | Macro-benchmarks                   |     |

| 4       | Conclu  | sion                               | 79  |

| Conclu  | sion    |                                    | 81  |

| Bibliog | raphy   |                                    | 85  |

|         |         |                                    |     |

| Append  |         |                                    | 93  |

| 1       | Expose  | ed API                             |     |

|         | 1.1     | Creating and removing partitions   |     |

|         | 1.2     | Managing the partition's internals | 96  |

|         | 1.3     | Managing pages                     | 96  |

|         | 1.4     | Managing control flow              | 97  |

|         | 1.5     | Managing hardware                  | 98  |

| 2       | Hardwa  | are abstraction layer              | 98  |

|         | 2.1     | Memory Abstraction Layer           | 98  |

|         | 2.2     | Interrupt Abstraction Layer        | 100 |

| List of | Figure  | es                                 | 101 |

CONTENTS

X CONTENTS

# Introduction

#### Overview

Everything begins with this simple observation: computer systems are everywhere. Although they used to be bound to mostly personal computers some years ago, today, the growth of technology and Internet brought computing in phones, tablets, sensors and even fridges. The Internet of Things, as it is called, is growing more and more, and is bringing Internet in your everyday life, up to the most insignificant object.

On the opposite side, this growth led to an evolution of users and enterprises' needs, in terms of data processing and storage. Cloud Computing was an answer to those issues, by putting servers anywhere around the world, and allowing users to rent the computing power and storage on those servers. A lot of customers can be using the same server at the same time, using virtualized systems.

Having connected objects and Cloud Computing almost everywhere, the overall security of these devices and systems remain questionable. What happens when a vulnerability is present in a device? Do my data remain truly confidential? Is there a possibility for a malicious user to steal my data?

There are many examples of nasty exploitations of vulnerabilities in Cloud or IoT devices. For instance, in 2016, hundreds of thoundands connected cameras were vulnerable to the same breach, and were exploited at the same time to perform a large-scale distributed denial of service attack [21]. As well, an exploitable vulnerability in Cloud servers could lead to huge data leaks [66].

The major problem is that a single vulnerable application can compromise a whole device. While Cloud and IoT hardware and software providers tend to provide more security to their devices, and claim to do so, the unending flow of discovered and exploited vulnerabilities tells us that it is just not enough.

### Context

My thesis was partially funded by the Celtic+ On Demand Secure Isolation project. This project involved many actors from different countries, such as Nextel in Spain, BEIA in Romania, Orange Labs in France among many others. Each actor had its defined task to perform, such as managing access control or designing the communication protocols. Mine was to design the lowest layer of the project's architecture, which is the memory isolation layer the remaining tasks were built onto.

Thus, the aim of my project is to provide a model and an implementation for a minimal kernel. It needs to provide strong guarantees about memory isolation between the applications running on top of it.

I have been doing my thesis in the 2XS (eXtra Small, eXtra Safe) team of the CRIStAL laboratory of the University of Lille. The research axis of the team mostly involves working on embedded devices with strong hardware constraints. Another research axis, which is directly related to my work, involves co-designing system software and the associated proof. Thus, a tight collaboration between the "formal proof" and the "embedded systems" parts of the team has been growing since the project began, and is still growing today.

#### Joint work

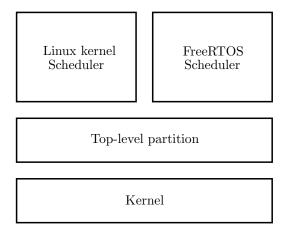

In addition to my thesis, two other thesis have been parts of this project. The first one, led by Narjes Jomaa, finished in December 2018 and was about verifying the API provided by our proto-kernel towards its isolation property [52]. The second one, led by Mahieddine Yaker, is still ongoing, and is about bringing strong security guarantees to the FreeRTOS real-time operating system, in order to build a secure, isolated operating system suitable for critical embedded systems [88].

#### Claim

This thesis presents a new kind of kernel model, the proto-kernel, suitable for high levels of certification. Its design is minimal, ensuring only memory isolation and, in a very simple fashion, control flow. The model of the API, which is under a proof process, is directly compiled into the binary and executed. Thus, any inconsistencies between the model and what is really executed are avoided. Moreover, it relies on no particular hardware mechanisms, except the presence of a Memory Management Unit.

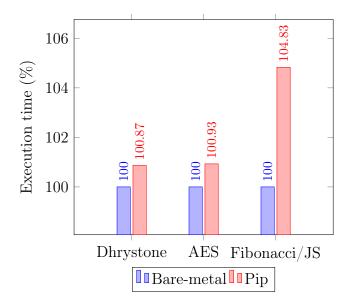

This thesis also presents a proof-of-concept of an implementation of this model and shows that its performances are acceptable. We claim that, through this model, we can achieve high levels of security at a minimal cost. This is demonstrated by a port of the Linux kernel on top of my proto-kernel, displaying less that 5% overhead.

#### Outline

This document is organized as follows:

Chapter 1 - State of the art presents a state of the art about operating system kernels, virtual machines, Trusted Computing base and formal proof on system software. The aim is to give a good overview of what already exists, and how my approach fits into it.

Chapter 2 - Problem statement and model design discusses the various issues my subject draws, and possible solutions to them. For each issue, I will discuss the possible solutions and drawbacks, and elaborate the proto-kernel model, which is my first contribution.

2 INTRODUCTION

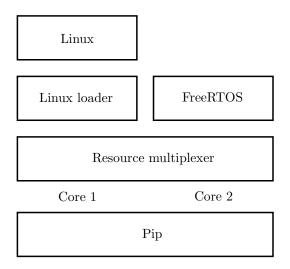

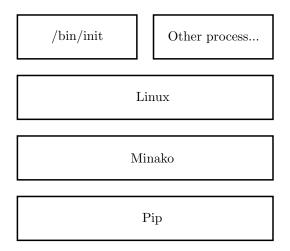

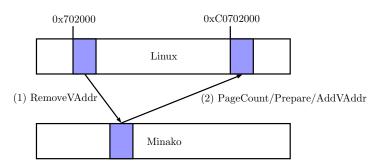

Chapter 3 - The Pip proto-kernel presents the implementation of my model, the Pip proto-kernel. I will explain the internals of the kernel, as well as how the proof is integrated into the development and build process. First, I present the single core implementation. Then, I propose several models to tackle issues that rise when considering multi-core harware, suitable for specific embedded devices and Cloud Computing.

Chapter 4 - Performances and return on experience evaluates the Pip proto-kernel through micro and macro benchmarks as well as its behaviour when porting Linux on top of it. The performances of the multi-core models are also discussed.

**Conclusion** concludes this document by suming up the previous chapters, and present some future possible work about Pip and my approach.

INTRODUCTION 3

4 INTRODUCTION

# Chapter 1

# State of the art

In this chapter, I will present many projects and concepts related to my work. I will begin by presenting the common kernel architectures often seen in general-purpose operating systems or in research kernels. Then, I will present virtualization-related concepts and projects, such as abstraction and hypervisor taxonomy. I will also introduce the concepts of Trusted Computing Base and how proving kernel code can lead into huge modifications of the TCB. Finally, I will focus a bit more on microkernel proofs, as there has already been lots of efforts around this.

# 1 Operating system architecture

In this section, we will take a look into many existing kernel architectures, and discuss the trust issues they induce.

#### 1.1 Monolithic kernels

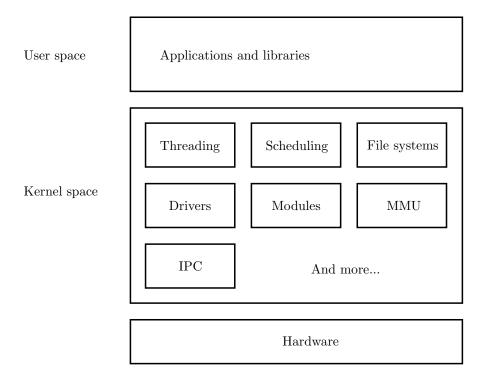

Monolithic kernels, usually bundled within general-purpose operating systems such as Windows, Linux or BSD-based distributions contain most, if not all, the function-nalities related to hardware management and kernel mechanisms within themselves. By doing so, there only remains applications and user interface in user mode, as seen in figure 1.1.

These kernels are most suitable for an everyday computing usage due to their efficient performance: by doing everything directly within the kernel, no privilege changes are required when a service is required, such as reading from a device or writing to a file.

Consequently, these kernels expose a huge API containing several hundreds of system calls fullfilling various purposes. As well, the code base for these is huge. For instance, there is more than 20 million source lines of code (SLOC) in the latest release of the Linux kernel.

An extension of the monolithic kernel model is the modular kernel. By allowing the loading of kernel modules coming from outside the kernel (most modules are stored on the filesystem as independent binaries) and linking them with the kernel, the latter becomes more and more extensible at run-time [31]. Still, this also brings up more security issues: what happens when a malicious module is loaded? Most of the times, modules are loaded at the kernel level, with the same rights. When doing

Figure 1.1: Monolithic kernel architecture

so, a malicious module can read and write data in the kernel, while a "bad-written" module can crash the overall system.

Nevertheless, several efforts were done to bring more security into modular kernels, such as the Barrier exo-kernel [46], which brought memory isolation between the Linux kernel and its modules, ensuring a malicious module won't compromise the kernel.

#### 1.2 Micro kernels

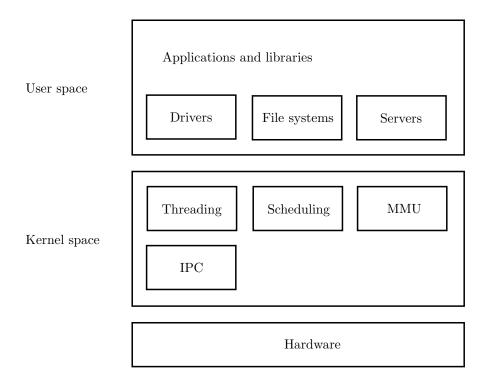

Micro kernels reduce the size of the kernel's code base, exposing only a nearminimum subset of functionnalities required to build a full operating system stack on top of it.

The features which used to be exposed in kernel space in monolithic kernels are now exposed as *servers* in user space instead, as described in figure 1.2. The code base for these kernels is then a lot reduced, being around 10.000 SLOC for most of them<sup>1</sup>.

Still, the first micro kernels, notably Mach, displayed bad performance. This was mostly due to the server-based architecture, which exposed many features as independent processes in different privilege levels than the kernel. Thus, it required a lot of inter-process communications and privilege changes for a simple request. Because of that, monolithic kernels were still overly used in comparison to microkernels, despite the high reliability of the latter [80].

As well, the minimal subset of functionnalities strictly required within the kernel was not clearly identified.

<sup>&</sup>lt;sup>1</sup>Around 4.000 SLOC for Minix 3

Figure 1.2: Micro kernel architecture

To solve both of these issues, the german scientist Jochen Liedtke [63] defined the L4 micro kernel family. Mostly, Liedtke stated:

"A concept is tolerated inside the microkernel only if moving it outside the kernel, i.e., permitting competing implementations, would prevent the implementation of the system's required functionality."

(Jochen Liedtke)

Therefore, a L4 microkernel would contain only 4 major features:

- virtual memory management,

- threading,

- scheduling,

- inter-process communication.

Several micro kernels were born from this concept, one on the most popular being OKL4, which is bundled today in tons of mobile devices. This kernel model is often known to be suitable for mobile and embedded devices, due to its low amount of SLOC, its proof-suitable design [43] and its better performance [48].

Meanwhile, other micro kernels, not belonging to the L4 family, are still popular. These include Minix, developed by Andrew Tannenbaum, or Mach, which is bundled today as the core component of XNU, the kernel of Apple's macOS, which belongs to the *hybrid kernel* family<sup>2</sup>.

Figure 1.3: XNU kernel architecture

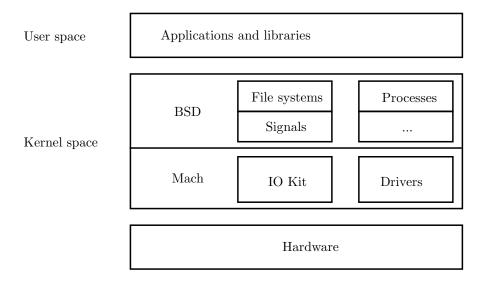

#### 1.3 Hybrid kernels

Hybrid kernels are designed to combine the good aspects of both monolithic and micro kernels.

They mostly consist of a core, base component being a micro kernel, with another monolithic kernel layer running on top of it. The most notable example of this is the XNU kernel, the core of Apple's macOS (see figure 1.3).

In XNU's model, the micro kernel layer is responsible for message passing, memory protection and threading<sup>3</sup>, while the BSD layer handles the POSIX API, UNIX processes, file systems and so on. Thus, the performance of the system (most especially during system calls) remains acceptable and close to a monolithic kernel's performance. Still, the driver framework (IO-Kit), the drivers themselves and memory management remain handled by the OSFMK micro kernel layer.

Thus, a vulnerability in the BSD layer of the kernel would not compromise the full system as, for instance, the driver subsystem is separate from it. This allows a hybrid kernel to rely on the robust and efficient security provided by a micro-kernel architecture while keeping the functionnalities provided by a monolithic kernel.

#### 1.4 Exokernel

As a way of further minimizing the size of the kernel, the MIT developed the Exokernel model [62] [35]. The major idea behind Exokernel is to force applications to communicate directly with the hardware as much as possible, without relying on abstractions provided by the kernel.

The Exokernel, as defined by Engler, Kaashoek and O'Toole, provides a secure way of accessing the hardware from userland. Systems implemented in userland are called *Library Operating Systems* [20], and manage to achieve high performance by optimizing them for this particular architecture.

<sup>&</sup>lt;sup>2</sup>More specifically, OSFMK, which is a commercial version of Mach.

<sup>&</sup>lt;sup>3</sup>This list of features is not exhaustive.

An Exokernel provides only two functionnalities related to hardware management and access. First, it provides memory partitioning, which enables memory isolation between library operating systems. It also features resource multiplexing, which is tightly related to scheduling policies and enables a fair share of the system's resources.

The minimality of the exo-kernel architecture is seen as a strong basis of security for critical systems [68], and highlights the relationship between small kernel base and reliable security guarantees.

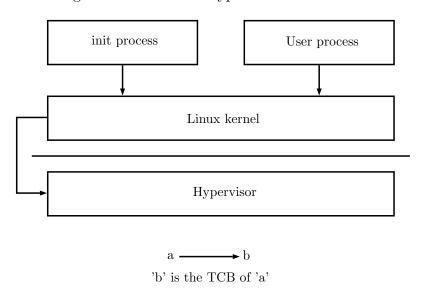

#### 1.5 Trusted computing base and security

The major common concept between all of these kernel families is the trust we can put in the kernel [45]. Indeed, we can consider that an application has to trust the kernel, and assume that the kernel is running properly. On the other hand, we cannot make any assumption on the execution of a user application if the kernel is compromised by a vulnerability or by a poor design. Indeed, a vulnerability into it might compromise the security properties of the whole system thus making any assumption onto the latter irrelevant.

As such, this introduces the concept of Trusted Computing Base, which is defined as following:

**Definition 1.** A Trusted Computing Base (TCB) the minimal set of hardware and software components that are critical and mandatory to the security of the system.

Any application or software component has then to trust the underlying software layer. In monolithic kernels, applications have to trust the whole kernel, while in micro kernels, for instance, an application has to trust the various servers it uses the latter putting their trust in the micro kernel as well.

Still, the software is not the only part of the TCB, as the previous definition states. Each software is run onto a specific hardware, which has to be taken into consideration as well when it comes to security assessments of a complete system.

# 1.6 Managing hardware

Being the most straightforward component of a TCB, the hardware the kernel is running onto represents a huge trust issue when trying to ensure security properties on a system. Many questions can be asked:

- does the hardware behave properly?

- what happens on a hardware failure?

- what happens when the hardware is incorrectly configured by the software?

- in summary, can we trust the hardware?

Recently, a huge vulnerability was found in Intel, AMD and ARM processors, exploiting speculative execution. These vulnerabilities, Spectre [58] and Meltdown [65], exploited an erroneous caching of data through speculative execution to leak, for instance, kernel data from userland. Being a hardware vulnerability, most systems

were affected, and the most straightforward software patch was to completly isolate the kernel and the userland's memory spaces, thus inducing a huge slowdown in terms of performances. Other vulnerabilities involving cache issues were also performed [38] [49], highlighting the major issue of hardware trust in secure software.

Ensuring security properties on the hardware can be done by either proving the hardware itself [50], or assuming that the hardware behaves properly and ensuring the software does not configure or use it in an inappropriate way. Many efforts were done to that end. Secure MMU has been developed as a hardware component designed to ensure memory isolation between a hypervisor and its guest [50]. The guest system is then fully isolated from the other guests and even with the hypervisor itself.

As well, many hardware today expose *Direct Memory Accesses* (*DMA*), which are designed for performance goals and consists of asking the hardware to read or write directly into physical memory, thus bypassing any memory virtualization or protection mechanism. DMAs would cause no problems when correctly configured. Still, when it comes to ensuring strong security properties, bypassing any memory protection or isolation is unacceptable.

To that end, IOMMUs were added, bringing memory virtualization between the hardware and physical memory. An IOMMU adds an address translation layer between the devices and the physical memory, in the same way the MMU does between the CPU and the memory. Using an IOMMU allows protecting the kernel from a bad configuration of third-party drivers, for instance.

By using IOMMUs, the hardware trust issues becomes a matter of ensuring proper configuration of the IOMMU chip, and handling the various vulnerabilities this new layer of hardware could involve. For instance, the IOMMU, like a MMU, works at a page granularity, whereas devices work at a thinner granularity, which could cause many issues [67]. Other projects, such as vIOMMU [19], involve a full virtualization of an IOMMU, bringing safety in guest virtual machines while keeping close-to-native performance.

#### 2 Virtual machines

The expression "virtual machine" nowadays covers a wide range of different kind of software, with different purposes. This sections aims at providing an overview of virtualization in general, as well as the softwares available to that end.

#### 2.1 Virtualization and abstraction

As virtualization and abstraction are two notions I will be relying on in the remaining of this document, I will present in this section the differences between these two terms.

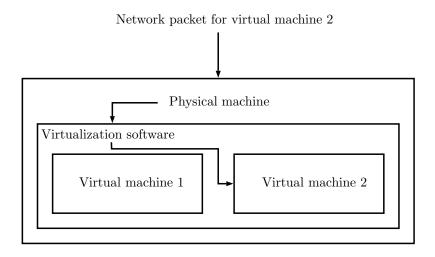

**Virtualization** In common sense, virtualization refers to the act of creating a virtual instance of an object, which does not have a physical existence. For instance, a virtual machine runs a virtualized hardware made to appear as a real hardware by the virtualization software, as depicted in figure 1.4. The virtualization software if usually called *Virtual machine Monitor (VMM)* or *Hypervisor*.

Figure 1.4: Example of virtualization

Figure 1.5: Example of abstraction

Today, virtualization is widely used in many different use cases, from personal to professionnal and industrial use cases. Cloud Computing servers make a heavy use of virtualization to allow multiple instances of operating systems to run on the same machine.

Abstraction Abstraction, on the opposite, refers to the act of using a common interface, feature or characteristic to interact with various objects, rather than using specific instances of the latter. For instance, a (simplified) file system layer, as described in figure 1.5 is an abstraction provided by an operating system to make complex operations, such as writing into a file, appear as a simple task to the user by using a common interface rather than specific implementations. Usually, operating systems heavily rely on abstractions to provide their functionnalities [81].

From now on, in this section, I will mainly focus on virtualization and virtualization software.

#### 2.2 Virtualization kinds

In computing, virtualization refers to the usage of a virtual machine, rather than a physical device, on which a software, for example an operating system, is run. The system on which the virtualization software is running is called the *host*, while the virtualized software is called the *guest*. There are two main kinds of virtualization, which are full virtualization and paravirtualization. Each has its advantages and drawbacks, making their use cases quite various.

**Full virtualization** In full virtualization, the software or operating system present in the virtual machine is running unmodified. The ability to run the software without any port or modification of the code is ensured by the VMM, which makes the virtual hardware appear as a physical hardware to the guest.

The main advantage of full virtualization resides in the ability to run any unmodified software, as soon as the virtualized hardware is coherent enough with the real hardware's behaviour. Nevertheless, full virtualization, when not using hardware optimizations, tend to provide poor performance due to the heavy usage of a virtualized hardware, including the CPU.

**Paravirtualization** In opposition to full virtualization, paravirtualization requires modifications to the guest software, in order to take the virtualization software into consideration. A full hardware environment is not provided. Rather, the guest uses directly the host's physical resources. Still, most of the times, the guest is aware of the VMM's existence, and can make many requests to it through *hypercalls*. As it uses directly the host's hardware, paravirtualization is often faster than full virtualization, but it also requires a modification of the guest software.

Thus, two major issues are drawn. First, not all software have an available paravirtualized version, making full virtualization mandatory in some cases. Secondly, each hypervisor has its own *hypercall* interface, making any modification or port of a paravirtualized guest bound to a specific hypervisor. There is a real issue of compatibility between hypervisors, which usually binds the choice of the hypervisor with the choice of the guest system.

# 2.3 Hypervision

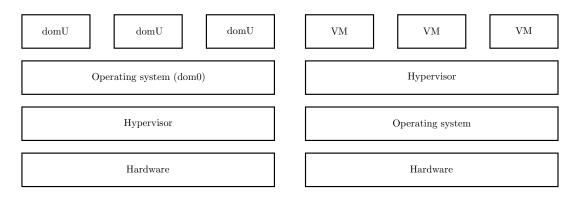

Hypervisors are often classified into two categories [37], depending on their way to provide an environment for their virtual machines.

**Type 1 hypervisors** Type 1 hypervisors provide a virtualized environment for guest software by making the hypervisor run directly on the host's hardware, and making it control every hardware access requested by guests. The task of initializing the system's base hardware is performed by the hypervisor itself, which acts as a kernel providing any mandatory feature a guest would need.

Usually, those hypervisors boot the primary operating system as a virtual machine guest (called  $dom\theta$ , using Xen terminology). The latter is then able to manage the hypervisor and boot other virtual machines, as depicted in figure 1.6. Most, if not all, Type 1 hypervisors provide paravirtualization or full virtualization, but are not able to virtualize another architecture.

Figure 1.6: Type 1 hypervisor

Figure 1.7: Type 2 hypervisor

Among Type 1 hypervisors, the most common ones are VMware ESX [85], Xen [22] and Microsoft Hyper-V [60].

**Type 2 hypervisors** Type 2 hypervisors rely on a running operating system. Implementing only the virtualization mechanisms, the host OS remains responsible for hardware initialization and resource access, as depicted in figure 1.7.

Among the wide range of Type 2 hypervisors, the most widely used are Oracle VirtualBox [14], bhyve [1] and its macOS counterpart xhyve [16], QEMU [23] and KVM [54]. Most of these hardware are able to virtualize another architecture than the hosts' through CPU virtualization.

#### 2.4 Virtualization methods

Type 2 hypervisors provide a virtual hardware the guest runs onto. Among this hardware, an interesting part is the virtual CPU provided.

Virtualizing a CPU Virtualizing a CPU can be done in several ways. The most straightforward way to do it is through a fetch-decode-execute loop, as the Bochs x86 Emulator does [2]. During the execution of the guest, each instruction is fetched, decoded and executed, as a simple, basical CPU would do. The performance provided is then far lower than an execution on real hardware. Still, this is a very portable way of virtualizing a CPU.

Some other CPU emulators perform a dynamic recompilation (or Just-In-Time/JIT recompilation) of the guest binary, as QEMU [13] does. This consists of taking the guest binary's instructions and convert them into the host system's instruction set, in order to make the host execute directly the guest's code. Although being highly dependant on the host's and guest's architectures, this is a much faster way to emulate a CPU as the host's hardware will execute it directly. Still, this approach has its limits. For instance, when the emulated software modifies its code on its own (as the older Windows NT kernels did), it forces the emulator software to throw away the previously recompiled code and recompile it again. Thus, code sections which would initially be optimized would become not efficient at all.

As well, JIT recompilation is challenged by dynamic code loading within the kernel (modules, iptables filters...).

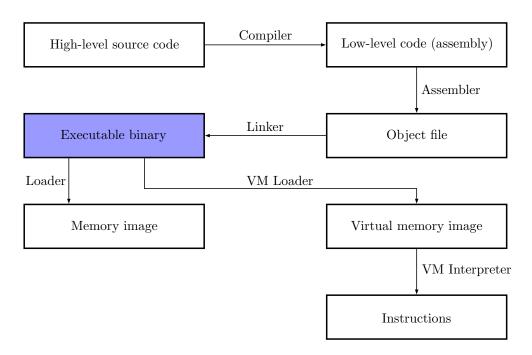

Figure 1.8: Binary compilation and execution

Figure 1.8 displays a flowchart of a binary's compilation and execution on real hardware and virtual machine, with the distributed/loaded binary being in the blue box.

Hardware-assisted virtualization When the host system and the guest system share the same hardware architecture, full virtualization can be enhanced by the usage of hardware facilities provided by the CPU, such as Intel VT-x or AMD-V [18] [36] [74].

Those extensions mostly provide a way for the guest to execute directly on the hardware while keeping the host safe from any unwanted tampering. These features include, but are not limited to, Nested Page Tables [69] [25] and virtual memory caches optimizations such as VPID [77].

For example, Intel's implementation of nested page tables, EPT, has been evaluated by VMware 2009 [17]. The comparison was done with shadow paging, which was a software way to virtualize MMU. The results have shown a 48% performance gain on MMU-intensive benchmarks, and up to 600% performance gain on MMU-intensive micro-benchmarks. Although, on some corner cases which can be avoided, EPT seem to cause some latency, it has become today widely used to reduce the overhead induced by MMU virtualization.

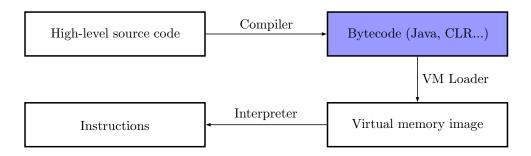

**Application virtualization** Finally, there is another interesting kind of virtual machine which is *Process Virtual Machines*.

These virtual machines, while not virtualizing a real hardware, virtualize an execution environment for applications written in high-level languages. The most popular virtual machine in this family is the Java Virtual Machine [73], which acts as a fully-featured execution environment for Java language binaries. Being a virtual machine exposing an abstract architecture [64], this kind of environments belong in

Figure 1.9: Process VM flowchart

virtual machines.

The same concept goes for Microsoft's CLR runtime, which serves as an execution for all the .Net-based languages (CSharp, FSharp, VB.Net...) [71].

Those virtual machines, as they rely on an internal, abstract architecture, contain their own instruction set. Moreover, they often define their own data types (which the hardware it is running onto may not be able to represent directly), and manipulate high-level objects and abstractions such as *objects*.

The main advantage, though, is that the code executed by those VMs can be distributed and run on any hardware. As the virtual machine runs its own instruction set, there is no need for various distributions of the same binary for different architectures, as depicted in figure 1.9.

As a comparison with figure 1.8, the end-to-end compilation of a binary and its loading on a Process VM is displayed in figure 1.9.

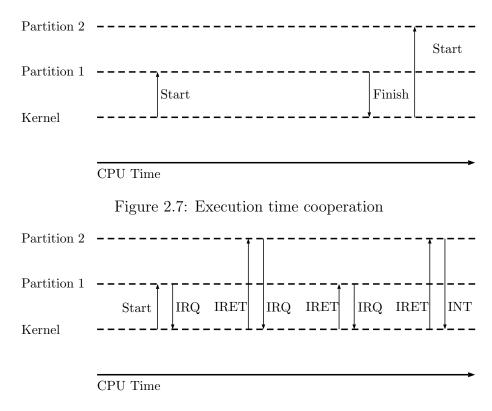

Real-time virtualization Most embedded systems today require real-time guarantees, especially for critical systems which can be found in avionics or automobile industries. Those systems, by essence, are very critical when it comes to the execution time of the various tasks running on the system. Thus, high guarantees are required and in virtualized environments, not only the guest system, but also the hypervisor need to provide real-time guarantees to ensure that the real-time constraints of the system are met.

Many hypervisors tend to fulfill those needs, such as Xtratum [28]. The latter provides spatial isolation through partitions, as well as strong temporal isolation with efficient real-time policies. Another one is RT-Xen [87], which aims to provide a real-time scheduling framework to the Xen hypervisor through four different algorithms (Deferrable, Sporadic, Periodic, Polling). This is mainly done through adding for each VCPU information such as a budget, a period and a priority.

As well, other projects allow the construction of real-time systems on top of it. An example is the OKL4 kernel [30], another L4-based microkernel, whose memory isolation is based on compartments (*Trusted Virtual Domains*). The latter are virtualized contexts with allocated sets of resources, allowing the implementation of a real-time operating system on top of it.

# 3 TCB and formal proof

In this section, we will discuss the various interests and issues caused by trying to bring strong security properties through formal proof on a system's TCB.

#### 3.1 Minimizing the TCB

When trying to bring strong security properties onto a system through formal proof, one on the major keypoints is to minimize the code base to be proved [26]. As such, minimizing the TCB to its strict minimal is essential. Indeed, the more function-nalities the kernel ensures, such as in monolithic kernels, the more difficult and fastidious it will be to bring security guarantees.

It is then essential to identify which functionnalities are mandatory to the kernel and the system, and which guarantees we want to bring onto it. Thus, bringing guarantees of a monolithic kernel is unreasonable due to the huge amount of functionnalities and code these kernels contain. Intuitively, it is more efficient and straightforward to work on micro kernels, or even smaller kernel models.

### 3.2 Proof and security

When talking about proof and security properties, it becomes important to define what exactly *security* means. Indeed, there is no universal security nor definition of it. Each proof effort on a kernel brings its own definition of security, and provides guarantees related this very definition. Some brings guarantees about memory isolation between applications while others ensure isolation between the kernel and the userland.

A proof then covers only the security properties defined, which brings up the question of what should be guaranteed, or what do we mean by security. Most security properties are built and defined on top of commonly recognized properties, such as memory isolation or partitioning, as defined by Rushby [51].

# 3.3 Goals of proving the TCB

As explained before, any application or software component running onto the system has to put its trust into the underlying layer. By bringing security properties onto this layer, and by proving them to be verified, we can ensure that this layer behaves properly, and that the behaviour of the application will not compromise the brought guarantees.

**Hoare triples** A common way to build a proof on a TCB is through Hoare triples, which works with states, properties and operations. It consists of ensuring that, given the system is in a state verifying the desired security property before an operation is performed, the resulting state of the system after the operation still verifies the property.

More precisely, given P and Q are assertions, or states, and C a command or operation, a Hoare triple is written as following:

$$\{P\}C\{Q\}\tag{1.1}$$

P and Q are respectively called the *precondition* and the *postcondition*. When the precondition is met, executing the operation C etablishes the postcondition. When aiming to prove a security property  $P_S$ , the Hoare triples consists of considering that if the precondition state verifies  $P_S$ , executing the operation C will result in a postcondition also verifying  $P_S$ .

TCB and proof relationship The Hoare triples gives a general representation of any reasoning on algorithms. Still, it does not define what the C command is. It might be a function provided by a library, a system call, an assembly mnemonic or even a logical block of hardware, such as a hardware device. In this context, any software proof relies on a succession of hypothesis exposed as Hoare triples, describing the "commands" we consider as trustable, i.e. which provides the expected postconditions from the initial preconditions.

A proof built this way then has, as a TCB, this set of hypothesis. Still, Hoare triples can be used to reason at different granularities (machine instruction, system call, library function...). Each reasoning then relies on a different TCB, some of them being part of other, like russian dolls.

Thus, ideally, each software hosted on a system should rely on a stack of TCBs. Each TCB element should be as small as possible, so that the proof and the amount of hypothesis it relies on could be the smallest possible too. In some way, this approach is similar to refinement proofs, but here, we conceive it in a bottom-up approach rather than a top-down approach, in order to enhance the reusability of the proven elements.

**Proof and code co-design** Moreover, proving security properties on the TCB (and most importantly, the kernel) is a major step towards an insurance of the security of the whole system. Still, proving a TCB brings major drawbacks, such as performances issues due to a lot of safety checks performed at each operation, and kernel structure modifications induced by the proof process. Mostly, when it comes to proving a TCB, the most flexible way is to develop the kernel while keeping the proof effort in mind. This has, for instance, been demonstrated by Popek et al. [75] [76] during their work on the UCLA secure operating system. Notably, they stated:

"The UCLA kernel operating system was still under construction during the proof effort, therefore permitting the desired verification changes at relatively low cost. That is, when code is encountered which is difficult to verify, alternate but equivalent methods of achieving the same effect are employed if they reduce the difficulty of verification."

(Gerald J. Popek, David A. Farber)

In summary, there is a huge link between the proof and the TCB. Modifying the TCB becomes impossible without modifying the proof, and in order to make a proof process possible, modifications would be required on the TCB's code base.

#### 3.4 Hardware architecture

As well, the hardware is a major issue when it comes to proving a TCB, and most of the times the software doesn't rely on a hardware which already brings formal

proof on security properties.

If we keep in mind that any software is designed to run on a *target architecture*, any kernel has to perform hardware-specific operations during its execution. Without modifying the kernel's structure here as well, it becomes mandatory to link the proof to the target hardware. The proof is then tied to a specific hardware, and becomes irrelevant when porting the kernel to another hardware.

The goal is then to get rid of the target architecture, by working on an abstraction of a hardware, which mostly consists of a minimal subset of features covered by hardware implementations. The features integrated into this abstract hardware then become the minimal hardware requirements to run the proved software. The latter are then expressed as proof hypothesis in the Hoare triples associated to the proof.

#### 3.5 Model-based proof

Considering the issues towards hardware integration into the proof, two different ways of proving the software are feasible.

The first one consists in building a model-based proof, reasoning with abstract models of both hardware and software algorithms. Once the proof process succeeds, these models are compiled into executable code for a specific, target architecture. The major drawback is that, even if the model is proved to verify the guarantees we want to ensure, there is no guarantee that the generated binary also verifies them. There is again a question of trust we can put into the compiler, resulting in the fact that even if we can in theory assume that the security properties are verified during the execution of the software, we no longer have strong guarantees [57].

To solve this, an additional step of verification towards the compiler is mandatory, for instance by using a verified compiler [61] such as CompCert [27], which allows proofs on code written in a subset of the C language, and ensures the generated binary is strictly equivalent to the source code.

# 3.6 Implementation-based proof

Another way of proving the software is to bring the proof directly at the binary level, verifying the generated binary instead of the source code. There is then strong guarantees on the executable binary, but requires a fastidious proof process which is, by essence, fully hardware-dependent as it relies on a binary for a specific architecture.

This relies mostly of a formalization of the target architecture's semantics (assembly mnemonics). It ensures that, given a known initial state, executing the sequence of instructions the program contains results into another known state, verifying the desired properties.

The major drawback is that the overall proof becomes irrelevant when the hardware changes or gets updated. As well, some architectures such as Intel x86 contain an insanely high amount of different mnemonics and instruction kinds<sup>4</sup>. This is also due to the high amount of upgrades and extensions to the architecture's instruction

<sup>&</sup>lt;sup>4</sup>Intel x86 today provides more that 3000 instructions and variants (https://stefanheule.com/blog/how-many-x86-64-instructions-are-there-anyway/)

set. Formalizing all the instruction set is very fastidious. Consequently, proving the binary often need to restrict the mnemonics used to a minimal, essential subset of the target architecture's possibilities.

#### 3.7 Combining both methodologies

When it comes to fully prove security properties from the model to the implementation, it becomes possible to combine both previous methodologies. Still, there are different ways to combine these, as there is a remaining gap between the abstract model and the implementation.

Two methodologies here are interesting:

#### Verifying the implementation towards the model

First, verifying a model and an implementation separately is fastidious. Still, by verifying an equivalence between a proved model and the resulting implementation, we can infer that the properties exposed and verified into the model are kept into the binary. Mostly, this consists of performing a proof process on the abstract model, and then checking that the binary is indeed equivalent to the model.

#### Compiling the model

Another way of combining those approaches is to compile directly the model into the binary. Thus, no equivalence check are needed, as the proved model is directly built into the resulting binary. Still, compiling a model into the binary is quite fastidious at first. Indeed, going from an abstract model written mostly in a functional language (suitable for the proof process) to compilable, hardware-dependent, freestanding code can be quite a challenge.

This also brings restrictions on the abstract model, which needs to be written in an imperative style. Again, two approaches exist:

- Embed a full runtime for the model's language into the binary, such as House [33], which embeds a minimal Haskell runtime into its binary,

- Compile the model code into C or assembly code, dropping all the dependencies and runtime issues in the process.

Bringing a runtime into the binary is the most straightforward way to compile the model directly into the binary, but also brings some issues. For instance, most of the languages used require a garbage collector, which also brings performance issues on its own. As well, not having full control on memory allocations and deallocations when it comes to bring strong properties on a kernel is not suitable.

#### 3.8 Common Criteria

As a way to provide a common and neutral basis for the evaluation of security properties on software, the ISO/IEC 15408, aka. Common Criteria (CC) was made.

The Common Criteria is a global standard used to evaluate the security level provided by the evaluated software (called the  $Target\ Of\ Evaluation\ /\ TOE$ ). It provides

an evaluation performed by an independent organism against security standards, and thus brings a more reliable evaluation of the product. Being recognized by 25 countries [7], an evaluation through Common Criteria is recognized in all these countries.

The Common Criteria specification is splitted into three parts, which are:

- introduction and general model [3], which contains the general concepts and base evaluation model,

- security functional requirements [5], which defines templates on which to base the functional requirements of the target of evaluation,

- security assurance requirements [4], which defines templates on which to base the assurance requirements of the target of evaluation.

Its main purpose is to evaluate systems through different levels of certification, called Evaluation Assurance Level, going from EAL1 to EAL7. Each EAL has its own requirements and prerequisites to certify a system. Notably, EAL6 and EAL7 require formal verification of the system.

#### **Evaluation Assurance Level**

Here is a quick description of EAL levels 1 to 7.

- **EAL1 Functionally tested** This level of certification if applicable to software with lower security threats. It basically provides evidence that the product works as expected regarding its documentation, and has good protection towards known threats.

- **EAL2 Structurally tested** In addition to EAL1, EAL2 brings tests at the design level of the product, as well as an additional vulnerability analysis.

- **EAL3 Methodically tested and checked** In addition to EAL2, EAL3 adds an investigation into the development process of the target, adding more tests and checks during the development phase, thus ensuring the target of evaluation's security properties are not corrupted during the development process.

- **EAL4 Methodically designed, tested and reviewed** EAL4 is the highest level at which it would be feasible to evaluate an already existing product. It requires more design specification and tests.

Lots of operating system went under a Common Criteria EAL4(+) certification process, such as Windows [15], Linux-based distributions [6] or even Solaris [10].

**EAL5 - Semiformally designed and tested** Most of the times, EAL5 requires the product to be designed and built with the idea of the certification in mind. It requires semiformal descriptions, structured architecture and more development procedures.

**EAL6 - Semiformally verified design and tested** This certification level brings high insurance againt significant risks. It requires a structured representation of the implementation of the product, as well as an even more structured architecture, additional vulnerability analysis and development process controls.

**EAL7 - Formally verified design and tested** Currently the highest level of certification available, EAL7 requires a formal specification and verification of the product, and an equivalence between the specification and the implementation.

Only a few products got an EAL7 certification, which is usually reserved to products with huge security requirements in high risk situations, or with high valued assets. A diode hardware, the Fox-It Data Diode got an EAL7+ certification level [11].

In summary, when designing a kernel, achieving high levels of certification brings higher restrictions and requirements. Achieving the EAL7 level is almost impossible for general-purpose operating systems, which barely achieve level EAL4. Mostly, this is due to the fact that formally designing a kernel, especially when it has already been developed without any formal design process in mind, is a tedious and insanely difficult task. Proving this design validates security properties is even more difficult.

Thus, when aiming for high certification levels, co-designing the kernel is the best approach, as the formal design of the kernel is already part of the development process since the early stages.

# 4 Micro kernels and proofs

In this section, I will go further into kernel security proofs by presenting some projects related to it, and explaining the whereabouts of their proof process.

#### 4.1 The seL4 micro kernel

One of the major recent projects related to kernel security is the seL4 micro kernel [44] [56], developed by the Australian laboratory Data61, formerly NICTA<sup>5</sup>. The aim of this project was to fully prove the memory protection model on a L4 micro kernel [55] [34] (see section 1.2) while keeping the performance expected from this kernel family.

The proof of seL4 is written using the Isabelle proof assistant, and it is verified during the proof process that the generated binary is equivalent to the verified source code. Thus, the developers of seL4 claim to be « running the manual » [32]. It is worth noticing that this was the first complete formal proof on an operating system kernel.

seL4 provides the features of a L4 kernel, which are virtual memory management, threading, scheduling and inter-process communication. As well, seL4 provides no memory allocation within the kernel. Any allocated memory has to be given directly from the caller application's own memory, which ensures that there is no possible Denial-of-Service through kernel memory overuse. This also ensures that an application could never use some memory out of its own boundaries.

<sup>&</sup>lt;sup>5</sup>https://www.data61.csiro.au/

Figure 1.10: Simplified capability-based access control

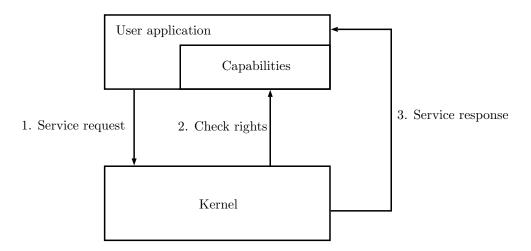

#### 4.2 Access control and restrictions

As a way to provide access control as well as a support for the proof, seL4 uses access tokens known as *Capabilities*. The latter handle rights for, for instance, specific hardware, memory or interrupt access to a given application running on top of it. Applications can give a subset of their capabilities to another application, thus allowing access delegation and revokation.

Another project, CapDL, was built to create static systems based on seL4 by using a Domain-Specific Language (DSL) to describe the capability architecture of a project [59].

Access control has been a basis for any proof-based effort of achieving verification of security properties. Indeed, it is an intuitive way to represent a user code's rights on the system, as well as a way to let user applications handle their rights without ever compromising the kernel. When a service is requested, the kernel checks the caller's rights to perform - or not - the operation accordingly (see figure 1.10). Therefore, any proof related to security properties on a system would rely on an access-control based mechanism, may it be capabilities or something else.

# 4.3 Refinement proof

seL4's proof is based on machine-checked refinement. It is a two-step verification process, which ensures that:

- the compilable C code (at least the one targetting ARM architectures) implements the Haskell model of the kernel,

- the Haskell model implements the high-level specification of the kernel.

By successfully verifying both of these steps, it is ensured that the compilable C code, which becomes later the executable binary, is equivalent to the high-level specification of the kernel. Still, this is fastidious: each modification on the C code or Haskell code involves a full reverification of the whole system. As well, again, there is no guarantee on the generated binary once the C code goes through the compilation and linking phase.

The CertiKOS hypervisor, developed by the University of Yale, whose memory manager, BabyVMM, was also verified [84] is composed of multiple thin layers of code. The overall verification is done through series of refinements.

#### 4.4 Layered proof

A complementary methodology of proof is layer-based proof, which has been also achieved by the CertiKOS project [40]

Instead of proving the whole system's code base, CertiKOS works on small layers of code which provide strong guarantees to the layers built on top of them.

This layer architecture is especially suitable for kernel developments. Most micro kernels and smaller-size kernels are built onto the same paradigm: multiple small layers of code, each one relying on a lower-level one. Thus, CertiKOS (and projects following the same concept) are kernel verification frameworks, most of their methodology being appliable to real-world kernels.

In 2018, the CertiKOS team also managed to build a certified, concurrent operating system on top of CertiKOS [41], through a programming toolkit called CCAL allowing specification, composition, compilation and linkage of certified layers.

#### 4.5 Proof and language

These projects highlighted a major fact: proof and language are highly dependent. Singularity [47], a project led by Microsoft Research, highlighted the tight link between proof, high-level language and system architecture. Written mostly in CSharp with a low-level CLR virtual machine, Singularity brings memory isolation directly through the language itself. Thus, it does not even use virtual memory, and instead ensures that the executed binary does not steps on another binary's memory at run-time.

#### 5 Conclusion

Considering this state of the art, many models and methodologies bring answers to the common issues related to security of proof development. The minimality of the kernel seems to be a major requirement, in order to make the proof feasible.

Moreover, the proof process itself draws many issues. Minimizing the mandatory effort to be provided in this process is a tedious task due to the complexity of the associated code base, even in smaller kernels. The proof process has a huge impact on the model, as the design of the model will be oriented by its proof. Thus, the triple Model — Proof — Code has to be seen as a unique entity in order to ease the verification process [79]. The question of the hardware architecture and portability of the resulting kernel is also a huge issue to solve.

In summary, despite the huge amount of models and methodologies already existing, none can provide a straightforward way to build a minimal, highly portable kernel requiring the lowest amount of proof effort. It is then needed to identify all the issues my thesis aims to solve, and to build a new model which answers every one of them.

5. CONCLUSION 23

5. CONCLUSION

# Chapter 2

# Problem statement and model design

In this chapter, I will go in more details into the problems tackled by my thesis. For each one, I will give some background and potential solutions, before choosing the most appropriate one and build the model of my work upon it. The resulting model will be the first contribution of my thesis, and will be designed to answer the issues developed in this chapter.

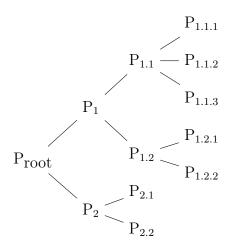

First, we want a security proof based on memory isolation. As it is known to be a difficult task, we choose instead to build the kernel around the proof effort, and not otherwise. In order to have the most robust but flexible design, we end up building a hierarchical memory isolation model.

First, I will present the proof-related problems, and how our security requirements revolves around them. Then, I will discuss the whereabouts of the hierarchical aspect of the model, and the benefits it brings. Finally, I will explain how memory isolation alone is not enough, and why interrupts and processor time should be managed by the model as well.

# 1 Proof approach

# 1.1 Proof-oriented design

**Kernel co-design** A major goal of my work is to provide a proof-oriented approach of designing the kernel. Mostly, this involves designing the kernel while taking the proof into consideration.

The most straightforward way to take the model into consideration while designing the kernel is to design the code which will be proved as a separate unit consisting of an abstract model. While the proof relies on this abstract model, the latter should also be compiled directly into the kernel. By keeping the same model for the kernel and the proof, it is ensured that the proof remains valid during the execution of the kernel.

Compiling an abstract model draws many issues related to the language used to design the model. As explained in section 1.3.4, formal languages are often used to those ends, such as Haskell or Coq. While being suitable for abstract reasonings and proof processes, those language are not appropriate when it comes to low-level programming. By relying on higher-level abstractions, such as lists, they involve many dependencies which, at a lower level, most of the times ties to the standard

C library and the functionnalities it provides. As this is used to design a kernel, we cannot rely on a standard library, thus requiring the model's code to avoid any usage of high-level abstractions.

**Proving the model** Here, two different issues have to be addressed. First, the model has to be proven against the memory isolation property. This process is mainly done by writing the model in functional languages, which allow reasoning on such properties much easier than in C or assembly code. In order to be able to do this in C, for instance, we need a precise, formal idea of the semantics of the source language. While functional languages provide appropriate environments to that end, this is not the case in C. An answer to this issue is provided by VeL-LVM [72] [90], which brings a formalization of LLVM IR's semantics. This allows reasoning on LLVM IR code in a formal way, ensuring that the code will bring the wanted behaviour.

By doing so, we ensure the model verifies our security properties. Consequently, it *should* be verified and remain correct during its execution.

But in this case, "should" is not enough. We aim to run the model directly on the hardware, and thus we need to compile it into executable code. We then need another guarantee, on the equivalence of the compiled binary code with the model's code. In other words, we have to ensure that there is an equivalence between the source code and the compiled binary. CompCert [27], for instance, brings this property by ensuring that the compiled code is equivalent to its source. CompCert also provides a formal specification of the C language, allowing reasoning on C code to provide the wanted properties.

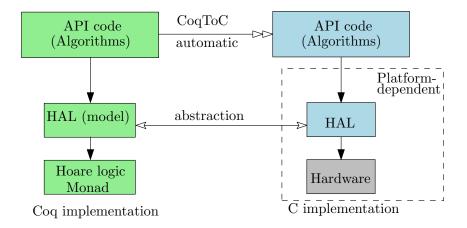

We finally chose to write the model through the Coq Proof Assistant [9], using the Gallina language. The model is then converted to C code using a Coq-To-C converter<sup>1</sup>, and rely on CompCert to compile into executable code. By doing so, the security properties ensured by the Gallina code remain verified in the executable binary.

What to prove? Finally, determining the frontier between the non-proved code and the proved code is mandatory. The latter mostly consists of the system call code. Indeed, all the critical operations performed by the kernel should be done mostly through system calls, thus making them the major part of the proved code. What remains is the architecture-dependent code, which is, as explained in section 1.3.4, both difficult to prove and, by essence, not usable for other architectures as it is tied to the very architecture it targets.

## 1.2 Abstract model

**Abstracting the model** As explained in the previous part, the totality of the proof process has to be done on the abstract model's code. The architecture dependant code is only designed to support the execution of the model by correctly configuring and interfacing with the hardware, but should not interfere with the proved code.

<sup>&</sup>lt;sup>1</sup>This converter, Digger, is not part of my work. Still, I will talk a bit more about it later in this document.

In order to allow the abstract model to know about the hardware possibilities while keeping the real hardware out of this, an interface is required. This interface provides enough knowledge to the abstract code about what the hardware can do, such as enabling or disabling virtual memory, or writing a value into a configuration table, and brings an abstract architecture into the model. Still, this is only an interface and brings no real code into the model.

Bringing the target architecture into the model We can bring the real architecture into the model during the compilation of the model into executable code, where it is linked with a hardware-dependent implementation of the provided interface. The portability of the kernel is then ensured, as only porting this code to another architecture provides a fully working port of the whole kernel. There is then no difference between the behaviour of the kernel's services on an architecture and another architecture, excepted the hardware-dependant operations.

By doing so, the proof is only written once for all architectures, and remains valid on any platform the kernel is running onto. The major drawback of this is that the proof then relies on an implementation of a hardware abstraction layer. A vulnerability in this HAL's behaviour might then, while not compromising the proof at an algorithmic level, cause issues during the execution of the real code. Having an accurate, efficient and secure implementation of the HAL then becomes a strong prerequisite for any proof-related reasoning.

# 1.3 Security

Bringing security to a model through formal proof requires having an accurate definition of the security we are trying to achieve. A lot of different visions of "security" are described in the state of the art and previous security-related kernel projects. In my work, we are going to focus on three major definitions, whose association builds our definition of security.

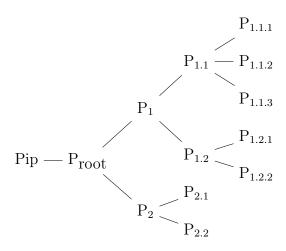

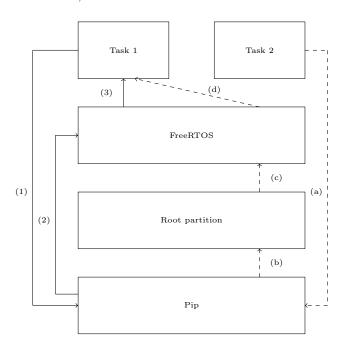

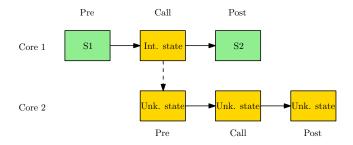

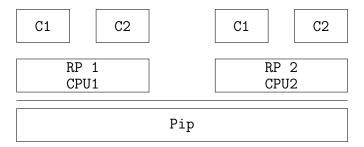

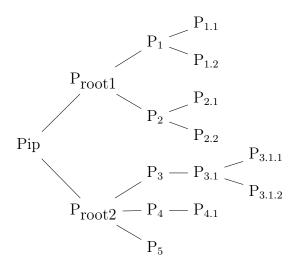

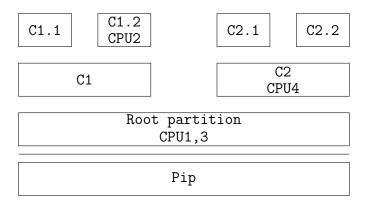

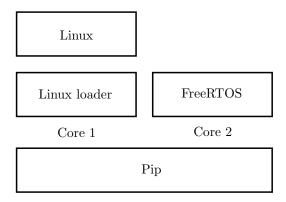

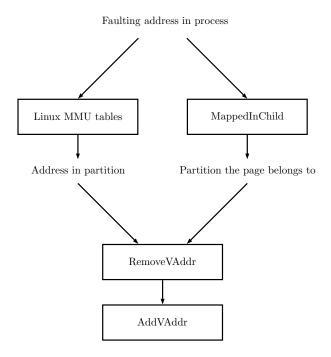

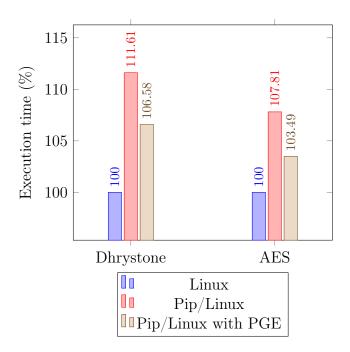

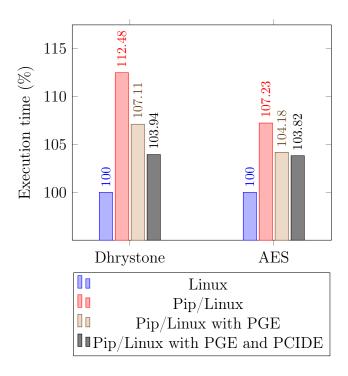

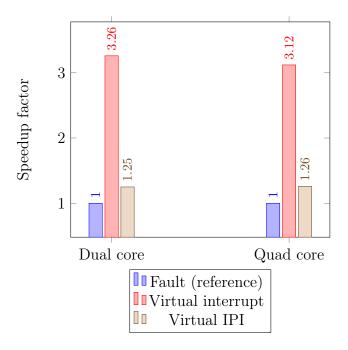

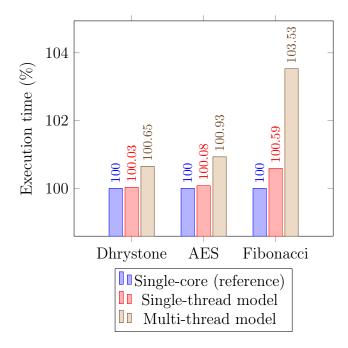

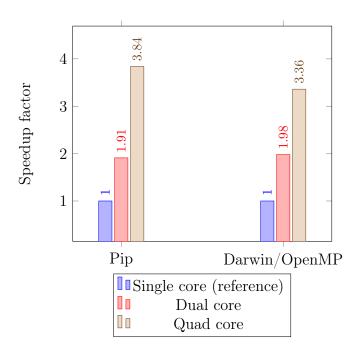

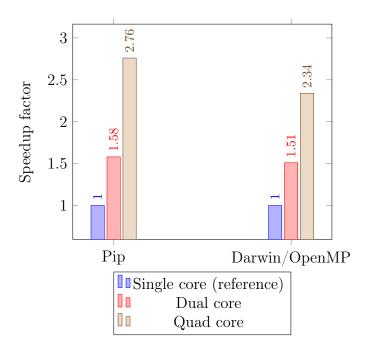

**Definition 2.** Confidentiality consists of ensuring that a running code unit cannot retrieve or read data that does not belong to it, such as from another code unit.