# Architecture Models Refinements for Software Development of Critical Real-time Embedded Systems

Etienne Borde

#### ▶ To cite this version:

Etienne Borde. Architecture Models Refinements for Software Development of Critical Real-time Embedded Systems. Computer Science [cs]. Sorbonne Universite, 2019. tel-04339297

### HAL Id: tel-04339297

https://hal.science/tel-04339297

Submitted on 13 Dec 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# HABILITATION À DIRIGER DES RECHERCHES DE SORBONNE UNIVERSITÉ

#### Spécialité

#### Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

#### Présentée par

Enseignant-Chercheur à TELECOM ParisTech / LTCI

### Architecture Models Refinements for Software Development of Critical Real-time Embedded Systems

Raffinements de Modèles d'Architectures pour le Développement Logiciel des Systèmes Temps-réels Embarqués Critiques

soutenue publiquement le 10 Mai 2019, devant le jury composé de :

| M. Fabrice KORDON   | Professeur à Sorbonne Université                | Président du jury |

|---------------------|-------------------------------------------------|-------------------|

| M. Xavier Blanc     | Professeur à Université de Bordeaux             | Rapporteur        |

| M. Ivica Crnkovic   | Professeur à Chalmers University of Technology  | Rapporteur        |

| M. Joel Goossens    | Professeur à Université Libre de Bruxelles      | Rapporteur        |

| M. Yamine Aït Ameur | Professeur à ENSEEIHT Toulouse                  | Examinateur       |

| M. Laurent George   | Professeur à ESIEE Paris                        | Examinateur       |

| M. Frank Singhoff   | Professeur à Université de Bretagne Occidentale | Examinateur       |

### Acknowledgements

I would like to sincerely thank Professors Xavier Blanc, Ivica Crnkovic, and Joël Goossens for giving me the great honor of reviewing my habilitation thesis. I greatly appreciated their feedback on my work and the accuracy of their assessment.

I would also like to thank Professors Yamine Ait Ameur, Laurent George, and Frank Singhoff for having accepted to serve on the jury, as well as Professor Fabrice Kordon for having accepted to be the president of the jury. I would especially like to thank Professor Fabrice Kordon for his help in preparing for this habilitation at Sorbonne Université.

The work presented in this document is the result of many and very rich interactions with colleagues from academia and industry.

First of all, I want to warmly thank Laurent Pautet who has been working with me since the very beginning of my career: from the PhD to this habilitation. It has been a pleasure to work with him, and learn from him. I also want to thank my colleagues from TELECOM ParisTech for the quality of their feedback on my work, and all the good times spent together: Thomas Robert, Florian Brandner, Rémi Sharrock, James Eagan, Ada Diaconescu, Elie Najm, Sylvie Vignes, and Petr Kuznetsov. Not to mention Sébastien Gardoll from CNRS.

This work is also the result of the work of brilliant PhD students that I would like to congratulate again for their achievements, and thank for their collaborations: Fabien Cadoret, Cuauhtémoc Castellanos, Elie Richa, Smail Rahmoun, and Roberto Medina.

Finally, this work is the result of numerous interactions with researchers and engineers from both academic and industrial insitutes: I would like to thank the Chaire ISC (in particular Eric Goubault from Polytechnique, and Alexandre Chapoutot from ENSTA), the IRT SystemX (along with Alstom, Renault, Thales, Safran), the AADL standardization committee (in particular Peter Feiler from the Software Engineering Institute, Jean-Pierre Talpin from INRIA, Pierre Dissaux from Ellidiss, and Brian Larson from Kansas State University) for their support, their contributions, and feedback.

Last but not least, I want to thank my wife Sara for her support in both my professional and personal achievements.

#### **Abstract**

Cyber Physical Systems are systems controlled or monitored by computer-based programs, tightly integrated networks, sensors, and actuators. Trains, aircrafts, cars, and some medical equipments are examples of complex CPS. Software development of complex CPS has become so difficult that it represents most of the cost of CPS production. According to domain experts, this trend is going to reach a point where software development would represent the main source of cost of a CPS production.

In addition, it is interesting to note that the integration, verification and validation of software in CPS require more efforts than the analysis, design, and implementation activities. The main reason is that these activities are conducted late in the development process and issues discovered at this stage of the process will require to rework artifacts produced in the previous activities (*i.e.* analysis, design and/or implementation).

In this document, we present our work aiming to improve the reliability of software development in the domain of CPS. In this context, we define the reliability of the development process as its capacity to deliver intermediate artifacts for which the rework effort would be as small as possible.

This problem is very difficult for general purpose software (*i.e.* used on desktop computers or servers), and even more difficult for software in CPS. The main reason is that software in CPS is often *critical*, *real-time and embedded on domain specific execution platforms*. As a consequence, non-functional properties (also called quality attributes) of software applications in CPS are often as important and difficult to satisfy as the logical correctness of these applications.

In order to the improve the reliability of software development in the domain of CPS, we propose a Model Driven Engineering (MDE) method based on step-wise refinements of software architecture descriptions (also called architectural models). An architecture description being an abstraction of the software being developed, the implementation of this software (*i.e.* source or binary code) is an **interpretation** of the architecture model. In the framework we propose, such interpretations are automated using **model refinements**, *i.e.* model to model transformations lowering the abstraction level of the architecture description.

However, models interpretation may introduce faults such as bugs or invalidation of non-functional requirements. It is hence necessary to control as much as possible the correctness, consistency, and optimality of artifacts produced along the model refinement steps. To reach this objective, we propose to

- define model transformations so as to interleave refinement steps with analysis of the resulting artifacts. We thus improve the consistency between the analysis results and the software implementation by analyzing models as close as possible to the implementation.

- 2. define timing analysis and real-time scheduling techniques to ensure the correctness of software architectures from a timing perspective.

- 3. formalize model transformations in order to ensure their correctness using formal verification techniques.

- 4. compose model transformations in order to automate the search for optimal (or near-optimal) architectures.

The work presented in this document is thus at the frontier among different research domains: MDE, real-time systems scheduling, formal verification, and operational research.

In this work, we chose to rely and extend the Architecture Analysis and Design Language (AADL) to model the cyber part of CPS. The reasons for this choice are simple: Firstly, AADL is a standard and a domain specific language for real-time embedded systems. Secondly, It allows to represent software architectures with different abstraction levels. Last but not least, AADL supports different types of models of computations communications, some of which being deterministic.

As a guideline for our work, we developed the methodology we propose in a MDE framework called RAMSES (Refinement of AADL Models for the Synthesis of Embedded Systems). This document presents both the methodology and some illustrations of its implementation in RAMSES.

# **Table of contents**

| Li | st of f | figures                                                          | 9  |

|----|---------|------------------------------------------------------------------|----|

| 1  | Intr    | oduction                                                         | 1  |

|    | 1.1     | Industrial Context and Scientific Challenges                     | 1  |

|    | 1.2     | Problem statement                                                | 4  |

|    | 1.3     | Organization of the document                                     | 7  |

| 2  | Ove     | rview of contributions                                           | 9  |

|    | 2.1     | Approach: Architecture refinement framework                      | 9  |

|    | 2.2     | Overview of the State-of-Art                                     | 11 |

|    | 2.3     | Supervised PhD students                                          | 16 |

| 3  | Arc     | hitecture Models Timing Analysis                                 | 19 |

|    | 3.1     | AADL Refinement Framework                                        | 21 |

|    | 3.2     | Code generation and fine-grain analysis of partitioned systems   | 22 |

|    | 3.3     | Periodic delayed communications                                  | 27 |

|    | 3.4     | Mixed-criticality DAGs analysis                                  | 30 |

|    | 3.5     | Concluding remarks                                               | 40 |

| 4  | Con     | nposition and formalization of model transformations             | 43 |

|    | 4.1     | Model transformation chains in RAMSES                            | 46 |

|    | 4.2     | Automatic construction of transformation chains                  | 48 |

|    | 4.3     | Precondition construction in algebraic graph transformations     | 52 |

|    | 4.4     | Design space exploration by composition of model transformations | 55 |

|    | 4.5     | Concluding remarks                                               | 61 |

8 Table of contents

| 5  | 5 Conclusion and Perspectives |        |                                                    |           |  |

|----|-------------------------------|--------|----------------------------------------------------|-----------|--|

|    | 5.1 Concluding remarks        |        |                                                    |           |  |

|    |                               | 5.1.1  | Overview of contributions                          | 64        |  |

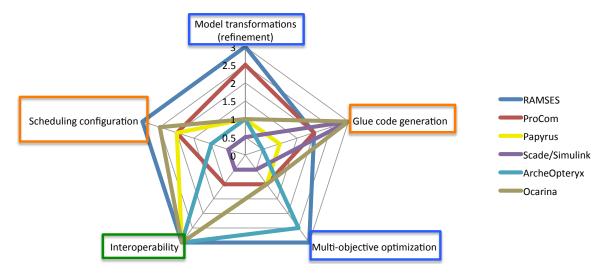

|    |                               | 5.1.2  | Comparison of RAMSES with existing frameworks      | 64        |  |

|    | 5.2                           | Future | Research Directions                                | 68        |  |

|    |                               | 5.2.1  | Software Security in Cyber-Physical Systems        | 68        |  |

|    |                               | 5.2.2  | Autonomy by Reconfiguration of CPS Applications    | 69        |  |

|    |                               | 5.2.3  | Uncertainty Management in Design Space Exploration | 70        |  |

|    |                               |        |                                                    |           |  |

| Bi | bliogı                        | raphy  |                                                    | <b>73</b> |  |

# List of figures

| 1.1  | Context: Critical CPSs Development Process                              | 2  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Problems in Critical CPSs Development Process                           | 4  |

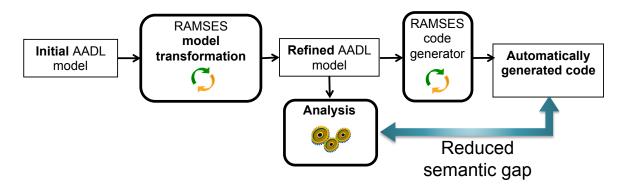

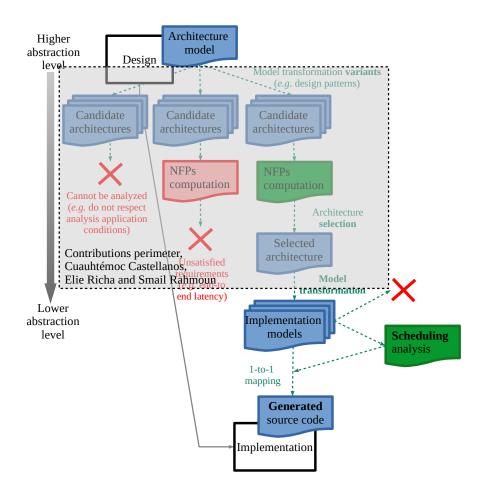

| 2.1  | Proposed refinement framework for CPS design models                     | 10 |

| 2.2  | Thematic distribution of co-supervised PhD students                     | 16 |

| 3.1  | Perimeter of research activities presented in this chapter              | 21 |

| 3.2  | Overview of RAMSES functionalities                                      | 22 |

| 3.3  | Model Refinement for Timing Analysis                                    | 24 |

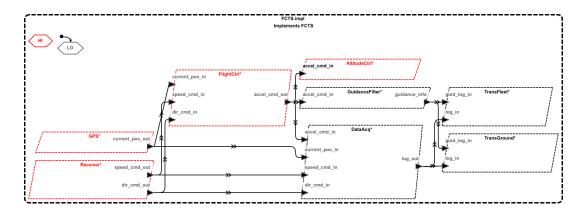

| 3.4  | AADL Model of our Case Study                                            | 27 |

| 3.5  | Illustrative Example of periodic-delayed communications                 | 29 |

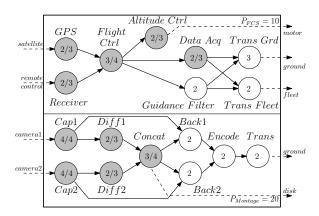

| 3.6  | UAV software architecture with two MC-DAGs                              | 32 |

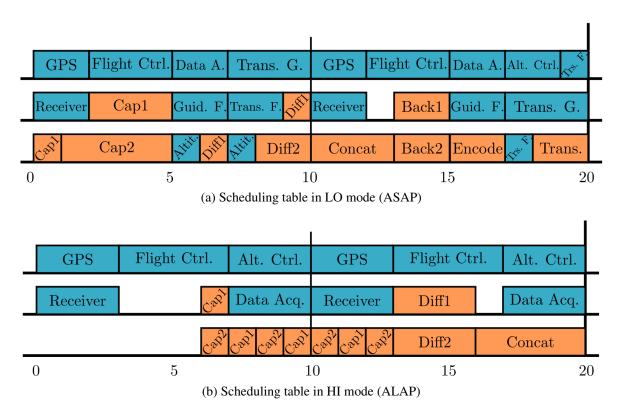

| 3.7  | Scheduling tables for the UAV, using G-LLF and <b>Safe Trans. Prop.</b> | 34 |

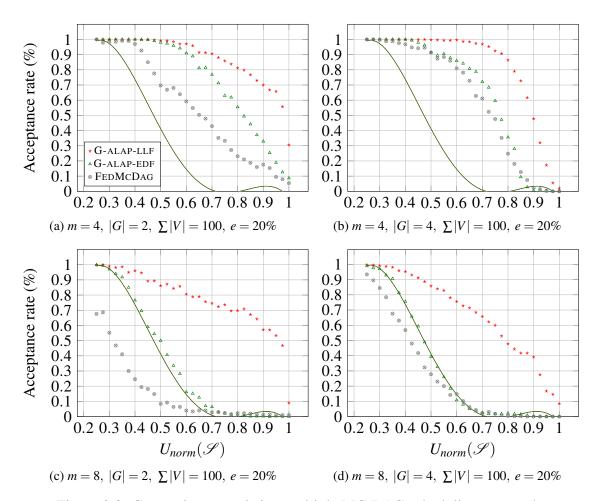

| 3.8  | Comparison to existing multiple MC-DAG scheduling approach              | 36 |

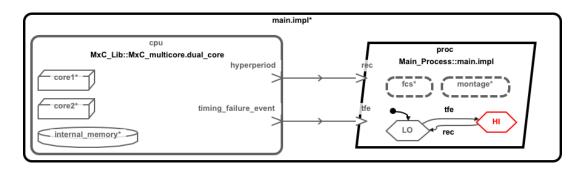

| 3.9  | UAV AADL architecture: system level                                     | 39 |

| 3.10 | UAV AADL architecture: FCS MC-DAG                                       | 39 |

| 4.1  | Perimeter of research activities presented in this chapter              | 45 |

| 4.2  | RAMSES refinements: chain of model transformations                      | 46 |

| 4.3  | Overview of the TMR (also called 2003) transformation                   | 47 |

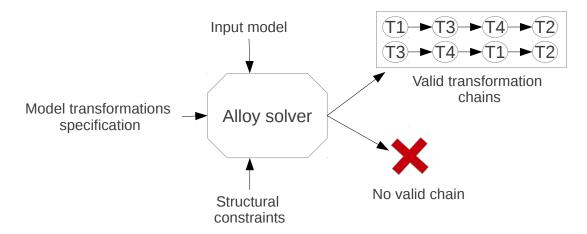

| 4.4  | Model transformation chains production with Alloy                       | 50 |

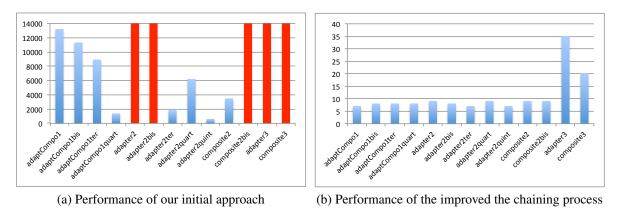

| 4.5  | Mean time to find transformation chains                                 | 51 |

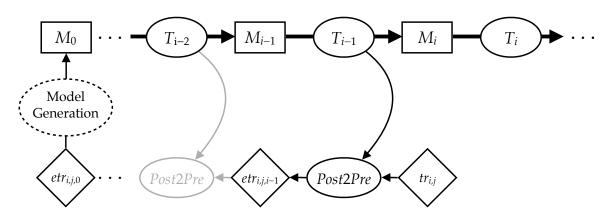

| 4.6  | Backward translation of test requirements                               | 54 |

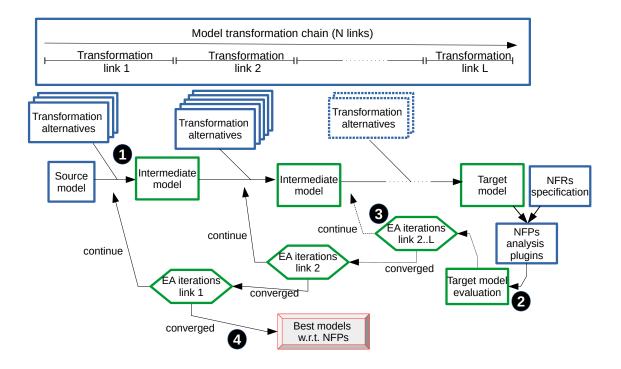

| 4.7  | Approach Overview                                                       | 56 |

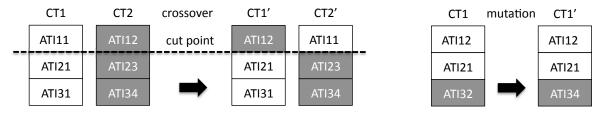

| 4.8  | Crossover and Mutation Operators                                        | 60 |

| 5 1  | Comparison between RAMSES and similar frameworks                        | 66 |

# Chapter 1

# Introduction

#### **Contents**

| 1.1 | Industrial Context and Scientific Challenges | 1 |

|-----|----------------------------------------------|---|

| 1.2 | Problem statement                            | 4 |

| 1.3 | Organization of the document                 | 7 |

### 1.1 Industrial Context and Scientific Challenges

A Cyber Physical System (CPS) is a system that is controlled or monitored by computer-based programs, tightly integrated networks, sensors, and actuators. "In cyber-physical systems, physical and software components are deeply intertwined, each operating on different spatial and temporal scales, exhibiting multiple and distinct behavioral modalities, and interacting with each other in a lot of ways that change with context." Robotic systems of course, but also transportation systems, medical devices or power plants are example of CPSs.

The evolution of software applications deployed in CPS shows a significant increase in their complexity. Measured in terms of lines of code (SLOC) embedded in different generations of aircraft systems, this complexity indicator shows the significance of their software evolution: Airbus A310: ~400 KSLOC, A320: ~800KSLOC, A330/340: ~2MSLOC, Boeing 777: ~4MSLOC, Airbus A380: ~8MSLOC, Boeing 787: ~10MSLOC. These impressive numbers are still below the numbers of estimated lines of code in military aircrafts or luxurious modern cars.

As a consequence, software development, takes an important role in the production of such systems. Our industrial partners in the avionics domain estimate that 70% of systems

<sup>&</sup>lt;sup>1</sup>https://www.nsf.gov/pubs/2010/nsf10515/nsf10515.htm

2 Introduction

production cost is due to software development, mainly because of very demanding validation, documentation, and integration activities. They estimate this ratio would grow up to about 90% in 2024.

The cost presented here above measures how difficult software development has become in the domain of CPS. This cost actually aggregates several sources of difficulties over the development life-cycle. In particular, our industrial partners (still in the avionics domain) estimate that 70% of software development cost is due to rework, validation, and verification activities, mostly because of faults introduced during the early phases of the development process. Counterintuitively, this estimation highlights that integration, verification, and validation activities represent more efforts than analysis, design, and implementation activities.

Verification and validation of software in CPS is particularly difficult because CPS are often mission or safety critical: failures of such systems could have catastrophic consequences. As a result, developers of CPS are often required to conform to certification processes aiming at ensuring these systems meet safety requirements.

On the other hand, software integration in CPS is also challenging because these systems have meet various requirements such as timing performance, energy consumption, weight, availability, maintainability, robustness, etc.

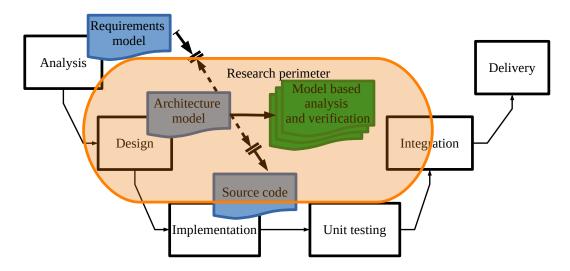

Figure 1.1: Context: Critical CPSs Development Process

Figure 1.1 gives an overview of a traditional development process, called V-cycle, generally used in the development of CPSs. The objective of the V-cycle development process is to anticipate validation activity by preparing verification and validation artifacts along with requirements, design, and implementation activities.

In addition, Model Driven Engineering (MDE) advocates for the use of models in order to improve the development process of software applications and in order to increase products quality. For example, models can be used to improve the development process by enabling early estimation of software applications performance. In addition, such estimation will help designers of software applications to compare different solutions and select the most appropriate one(s). As shown in figure 1.1, models can be the result of the requirements definition and design activities of the development process, while source code is produced during the implementation phase of the process.

In the work we present in this document, architecture models produced during the design activities play a major role: firstly, we combine them with verification and analysis techniques in order to detect design flaws as early as possible in the process. Secondly, as illustrated on the figure, we aim at using architecture models to bridge the gap between requirements models and source code. Therefore, the work presented in this document aims to improve methods dedicated to the design of software architecture(s) for embedded systems which are also critical, real-time, and distributed systems. Because the type of systems we consider are mission or safety critical, the methods we aim for must rely on rigorous models so as to guarantee safety related properties.

The targeted application domain is the domain of CPS, in which physical systems are controlled by a set of interconnected computation units (CUs) executing control and/or monitoring algorithms. More specifically, industrial partners involved in the definition of research problems presented in this document work on transportation systems (cars, planes, and/or trains). In next subsection, we present the general problems for which we proposed the scientific contributions presented in this document.

4 Introduction

#### 1.2 Problem statement

Given the increasing complexity and cost of software development in CPSs, a zoom on the research perimeter presented in previous section (see the orange part of figure 1.1) led us to raise the following research question: how to improve the reliability of CPS design activities? In the context of software development for CPS, we define the reliability of design activities as their capacity to deliver intermediate artifacts for which the rework effort would be as small as possible.

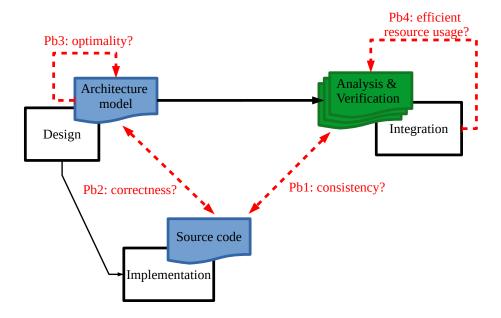

Figure 1.2: Problems in Critical CPSs Development Process

On figure 1.2, we provide a decomposition of this research question into different but connected research problems:

Problem 1: Are analysis results, obtained on an architecture model, consistent with the implementation of this architecture with source code?

By essence, architecture models are abstractions of the reality aiming to enable the analysis of a system under design. This analysis can evaluate quality of services or even safety properties of the system. On the other hand, the implementation of these models will require to interpret this abstract view and translate it into source code by introducing missing details. If these details had an impact on the analysis results, these results obtained with the model may no longer be

1.2 Problem statement 5

consistent with the properties exhibited by its implementation. The corresponding design would become obsolete, early design choices would be invalidated, leading to extra re-engineering efforts.

Problem 2: How to ensure the correctness of an architecture model implementation?

The activity transforming an architecture model into the implementation of a software application boils down to translate an abstract view of the system to provide an equivalent executable artifact. By essence, there exist several variants of such translation: an abstract model may have several possible implementations. In addition, this activity my rapidly become repetitive, thus error prone. It is therefore very important to ensure the correctness of the implementation by making sure the translation effort did not introduce flaws in the resulting source code. Such flaws may, again, invalidate analysis results, or even worse: introduce bugs in the source code of the application.

#### Problem 3: Is the input architecture optimal?

As explained in the presentation of Problem 1, the translation of abstract models into source code may invalidate early analysis results. One may conclude it would be sufficient to model systems with sufficient margins to ensure the preservation of analysis results along the development life-cycle. However, the values of such margins are difficult to anticipate, and it would be necessary to take very pessimistic estimations to make sure there would not be extra reengineering efforts eventually. In practice, this is infeasible since big margins also means poor quality: for instance, a computer loaded at 20% exhibits a big margin but is poorly exploited (which means more functions of more complex functions could have been deployed on it). In addition, quality attributes are often in conflict as improving one quality attribute requires to degrade another one. For instance, the deployment of replicated functions improves the availability of these functions to the price of extra weight, energy consumption, and data flow latency. It is thus important to deal with the problem of providing optimal (or near optimal) architecture models, otherwise the chance to face integration issues grows rapidly for complex systems.

6 Introduction

Problem 4: Are computation resources efficiently allocated to software applications?

In CPS, software architects have to pay extra attention to the allocation of computation resources to software applications. The main reason is that some of these applications will have a direct impact on the safety of the system. Such applications would be classified with a high level of criticality whereas others would be classified with a lower level of criticality. In most cyber physical systems, the provision of enough computation resource to high criticality functions is thus a safety requirement, whereas the provision of computation resources to lower criticality functions is a quality of service requirement. Note that quality of service, though not critical, is of prime importance as it has a direct impact on consumers satisfaction. In a CPS, an inefficient resource allocation may lead to a poor quality of services, and even worse, to safety requirements violation.

Problems 1 and 2 are obviously connected to our research question (*i.e.* how to improve the reliability of CPS design activities?) whereas the link with problems 3 and 4 may seems less direct. Yet, it is important to consider that software applications in CPS have to meet stringent requirements in terms of timing performance, memory footprint, safety, security, and/or energy consumption. These requirements, usually called Non-Functional Requirements (NFR), are often as important as functional requirements in CPSs. Thus, if errors are discovered late in the development process because of poor Non Functional Properties (NFPs) due to design flaws, a design rework is necessary and its cost will raise fast. It is thus important to ensure, as soon as possible in the design process, that considered architectures respect NFRs but also provide the best possible margin with respect to the limit imposed by these NFRs. This boils down to optimize these architectures, either during the modeling phase (problem 3) or during the deployment phase (problem 4).

Even though our work focuses on software architectures, specificities of CPSs require to take into consideration hardware platform characteristics as well. Indeed, the adequacy of a software architecture with respect to these requirements, called Non Functional Requirements (NFRs), cannot be assessed without a knowledge of the underlying hardware and/or network architecture.

This is the reason why we used in our work the Architecture Analysis and Design Language (AADL), an architecture description language offering the capabilities to model both the software and hardware architecture of a CPS, as well as the binding of software components onto hardware components.

In addition, Non Functional Properties (NFPs) evaluation requires dedicated models in which implementation details are abstracted away in order to focus on most relevant characteristics of the architecture for a given property. To extract such characteristics from a model, model transformations are often used: a model transformation is a software application that takes as input a model, and/or produce a model as output. Model transformations may be used to translate a given model from one formalism to another one with the same abstraction level. Such transformations are called horizontal transformations. Model transformations may also be used to change the level of abstraction of a model by adding or abstracting away modeling details. Such transformations are called vertical transformations. In this document, we call *refinement* a vertical model transformation adding modeling details.

Last but not least, CPS architects often consider design alternatives as decision variables in an optimization problem aiming at minimizing or maximizing NFPs. However, design alternatives often come into conflict with respect to their impacts on NFP: most of the time, a design alternative improves a NFP at the cost of degrading another NFP of a CPS. As a consequence, designers aim at providing the best possible trade-off among NFPs of a CPS.

### 1.3 Organization of the document

This document is organized as follows.

Chapter 2 contains an overview of the approach we propose to contribute to the resolution of the problems presented above. A brief presentation of related works helps to understand the originality of our approach.

In chapter 3, we present the core ideas our work relies on: model transformations of architecture models for the analysis, design, and optimisation of critical CPSs. Chapter 4 gives more details on the work we undertook on the composition and formalization of model transformations.

This work is integrated in RAMSES, which is to the best of our knowledge the only AADL to code generation framework implementing deterministic subsets of AADL. It is also the only AADL to code generation framework allowing fine-grained timing analysis of the non-deterministic subsets of AADL. Last but not least, model transformation compositions for design space exploration have been experimented in RAMSES on complex optimization problems with very satisfying results.

Finally, chapter 5 concludes this document and provides research perspectives for the work presented in this document.

# Chapter 2

# **Overview of contributions**

#### **Contents**

| 2.1 | Approach: Architecture refinement framework | 9  |

|-----|---------------------------------------------|----|

| 2.1 | Approach. Memeecure remement name work      |    |

| 2.2 | Overview of the State-of-Art                | 11 |

| 2.3 | Supervised PhD students                     | 16 |

In the previous chapter, we have defined ambitious and difficult research problems. We contributed to their resolution through the definition of an architecture models refinement framework we present in section 2.1. We then present in section 2.2 a brief overview of the state of the art in this domain, before to summarize this activity in terms of PhD students supervisions (section 2.3).

## 2.1 Approach: Architecture refinement framework

In order to answer the research problems introduced in previous chapter, we proposed a method based on model refinements, analysis, and optimization. The general idea behind this approach is to bridge the gap between requirements model and source code by defining model transformations that progressively lower the abstraction level of design models. Thus, from an abstract model provided by a CPS architect, we propose to define and compose model transformations which produce refined and optimal (or near optimal) architecture models. Such transformations would, for instance, integrate design patterns in the initial architecture model.

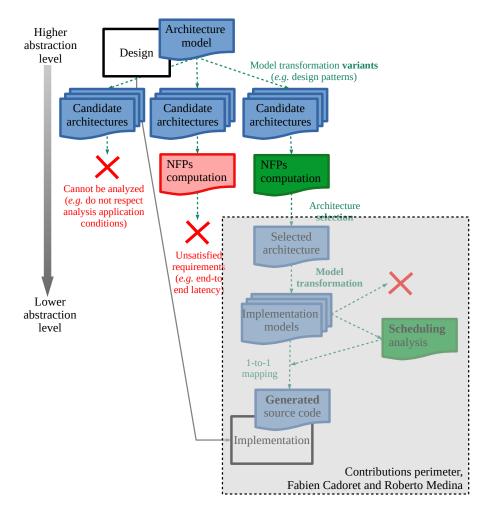

We then analyze the resulting models in order to evaluate the impact of the refinement on the system's NFPs and select architectures answering at best the trade-off among NFRs. We continue this process until we define implementation models, i.e. architecture models with a straightforward correspondence between model elements and source code (*e.g.* a one-to-one mapping between each modeling element and a construction in the underlying programming language and/or operating system configuration). Figure 2.1 illustrates this approach in a two stages refinement process: the input architecture model is refined into a set of architecture candidates. These candidates, are, when possible, analyzed to compute their NFPs and verified to check the design meets predefined NFR and structural constraints. Architecture candidates satisfying predefined NFRs and structural constraints are then selected and further refined into a set of implementation models. Again, these models are analyzed and the most appropriate model(s) is (are) used to automatically generate the corresponding source code.

Figure 2.1: Proposed refinement framework for CPS design models

By lowering the abstraction level of models used for both code generation and analysis, we improve consistency between analysis results and software implementation. More generally, we aim at applying model transformations and analyze output models to control the impact of these transformations on NFPs. This work contributes to the resolution of problem 1.

Because timing properties and in particular real-time tasks scheduling plays an important role in CPSs design, we first experimented these ideas so as to improve precision and/or reduce the pessimism of timing analysis based on architecture models. This work contributes to the resolution of problem 4.

We also worked on model transformations formalization as a mean to verify their correctness: we defined structural constraints on output models and proposed a method to define model transformation chains enforcing the respect of these constraints; we also defined a method to validate model transformation chains by producing integration test cases covering unit test requirements. This work contributes to the resolution of problem 2.

Last but not least, we proposed a design space exploration framework combining multiobjectives optimization techniques and model transformations composition in order to produce architecture models answering at best a trade-off among NFPs. This work contributes to the resolution of problem 3.

Pursuing the objective to provide *Refinement Techniques for Real-time Embedded Systems Architectures*, the work we present in this document covers different research domains:

- 1. Real-time scheduling analysis,

- 2. Model Driven Engineering,

- 3. Design Space exploration,

- 4. Safety and Security.

We give a rapid overview of the state of art of these domains in next section.

#### 2.2 Overview of the State-of-Art

Research areas mentioned at the end of the previous section cover a huge number of relevant research works. In this section, we do not seek for an exhaustive presentation of these areas. Instead, we aim at providing a minimal background information to have our readers understand the scientific context in which our research efforts were undertaken.

**Architectures description Languages.** Works in the domain of architecture description languages aim at defining modeling languages for software architectures, hardware architectures, or a combination of both. Historically, research works in this area have produced

formalisms, which may be Modeling Languages, Architecture Description Languages and/or Component-Based Modeling languages. In the domain of CPS, different languages have been proposed, such as SCADE <sup>1</sup>, MATLAB/SIMULINK <sup>2</sup>, LUSTRE [35], Giotto [36], Polychrony [33], the Synchronous Data Flows Graphs (SDFGs) [43], Wright [2], BIP [15], ProCom [17], the Palladio Component Model (PCM) [67], Fractal [16], UML/MARTE [56], and the Architecture Analysis and Design Language (AADL) [5]. These languages differ in many aspects, including the Model of Computation and Communication (MoCC) they define. For instance, SCADE relies on the synchronous model of computation in which computations and communications are assumed to take zero time. This hypothesis is satisfied if the underlying Computation Unit (CU) is fast enough to process input and produce results before the acquisition of the next input. Relaxing the synchronous hypothesis, Giotto defines a Logical Execution Time (LET) model of computation where components, modeled as tasks, take a predefined amount of time (the LET) to execute. Communications with a component (i.e. inputs reading, outputs writing) can only occur outside its LET interval (i.e. when the component is not executed). In SDFGs, the focus is more on communications among components than on their independent execution: applications are described as a set of communication channels connecting applications (also called actors, processes or tasks). These channels model communication FIFO queues, and the execution of an application is triggered by the content of its input queues. Last but not least, AADL is a standardized modeling language aiming at gathering both a representation of the software architecture, the hardware architecture, and the binding of software components onto hardware components. In our work, we consider source code generation as the final objective of an efficient MDE process. In some industry, and in particular in the transportation domain, several success stories show the added value of automated source code generation techniques. MATLAB/SIMULINK and SCADE SUITE provide source code generator widely used today. Note that these code generators produce the so-called functional code, i.e. software responsible to answer functional requirements. Another part of software applications for CPSs is called technical code, i.e. software responsible for interfacing functional code with the hardware platform of the CPS.

In this context, AADL is an interesting architecture description language since it allows to represent both the software architecture, the hardware architecture, and the allocation of software components on hardware components. In addition, as illustrated on figure 2.1, we aim at representing CPSs architecture at different abstraction level. This is also a facility offered by AADL, which was experimented during the PhD of Fabien Cadoret (2010 -

<sup>&</sup>lt;sup>1</sup>https://www.ansys.com/products/embedded-software/ansys-scade-suite

<sup>&</sup>lt;sup>2</sup>https://www.mathworks.com/products/simulink.html

2014). With respect to its usability in industrial applications, AADL is a standard with a high visibility. This is an important asset when it comes to experiment our work on industrial case studies. Last but not least, AADL defines a MoCC which is configurable thanks to standardized properties. For some subsets of AADL configurations, the MoCC is deterministic and matches existing formally defined languages (*e.g.* LET or SDFGs). In the PhD of Fabien Cadoret and Roberto Medina, we identified subsets of AADL with a deterministic and formally defined MoCC.

Being advanced users of the language, we have also contributed to its evolution by (i) providing regular feedback to the AADL standardization committee, and (ii) by leading the revision of its Behavior Annex: a sub-language of AADL dedicated to modeling components behavior with state machines.

**Scheduling and analysis of real-time systems.** Among NFRs of CPSs, timing requirements plays an important role. Indeed, one of the specificities of CPSs is that they control physical systems. This means CPSs implement control loops executed repeatedly with a frequency that is derived from an analysis of the system's physics. If the results of this control law are not produced in time, the physical system does not wait. This is why, in real-time systems, the outputs produced by a software function are valid if their computation is correct, *and* they are produced before a predefined *deadline*.

In order to ensure timing requirements are always satisfied, Liu and Layland [46] proposed to model software applications with a set of tasks  $\tau = {\tau_i}_{i=1..N}$  characterized by:

- a period  $T_i$ : the minimum delay between two consecutive executions of a task  $\tau_i$ .

- a capacity  $C_i$ : the time required for the CU to execute task  $\tau_i$ .  $C_i$  is usually set to the worst-case execution time (WCET) of  $\tau_i$ .

- a deadline  $D_i$ : time interval between the release of  $\tau_i$  and the date at which  $\tau_i$  must have finished its execution.

Since the definition of this very first task model, real-time systems have been intensively studied and this research field has significantly matured.

In particular, one important issue with the initial model introduced Liu and Layland is the induced pessimism on tasks response time which leads to a poor resource usage. Different sources of pessimism are indeed cumulated when verifying tasks always meet their deadlines, since the verification methods assume:

- tasks always execute all together for their worst case execution time;

- if tasks share data is a protected access, they execute all together spending the longest possible time in all their critical sections, causing significant blocking times.

In practice, the probability that one task executes for its WCET is low, so the probability they all together execute for their WCET is very low. To overcome this limitation, methods based on allowance [14] or mixed-criticality scheduling [19] have been proposed.

In the PhD of Fabien Cadoret, we first proposed to use AADL in order to implement fine-grain and less pessimistic response time analysis [13]. The objective was to reduce pessimism due to the presence of critical sections. We studied this problem in the context of avionics systems using the ARINC653 standard: in this context, blocking time induced by inter-partition communications is particularly significant. We also proposed a lock free implementation for a deterministic MoCC [21, 38]. More recently, in the PhD of Roberto Medina, we have considered a MoCC for which, by construction, data access protection is not needed: Directed Acyclic Graphs (DAGs) of tasks. Using this well-known MoCC, we have proposed new methods to schedule DAGs of mixed-criticality tasks.

In this research work, we showed the capacity of AADL to model such MoCCs. Even more significant, we used AADL to implement step-wise architecture refinements and proceed to timing analysis at different abstraction levels. This work has been integrated in the RAMSES platform<sup>3</sup>, an open source AADL to AADL model transformation and code generation platform.

Building on the knowledge gained designing model transformations in RAMSES, we developed new research activities dedicated to (i) compose and validate model transformations, and (ii) implement model-based design exploration techniques. We briefly introduce these methods in next subsection.

MDE and Model transformations for CPS. Model transformations are software applications taking model(s) as input and producing model(s) as output. Even though model transformations can be written in any programming language, they are by essence difficult to write. Indeed, a model transformation consists in transforming a typed graph into another typed graph. Writing and maintaining such applications rapidly becomes difficult [29]. For these reasons, dedicated model transformation methods [25, 55] and languages [39, 58, 4] and have been proposed. In RAMSES, we have initially decided to use ATL as a trade-off between the rigor of its semantics, and its simplicity of use. In addition, we decided to decompose model transformations as a chain of AADL to AADL transformations in order to enable verifications on intermediate AADL models.

However, we use model transformations in the context of critical CPSs, hence we have to pay extra attention to the validation of these transformations. This is why we proposed to formalize model transformations and more specifically model transformation chains.

In the PhD of Cuauhtémoc Castellanos, we proposed a formalization of model transforma-

<sup>&</sup>lt;sup>3</sup>https://mem4csd.telecom-paristech.fr/blog/

tions in Alloy [37]. From this formalization, and the specification of constraints on the output model (expressed with first order logic) we were able to automate the production of model transformation chains to produce output models satisfying the constraints [23, 22].

In the PhD of Elie Richa, we proposed a formalization of ATL as Algebraic Graph Transformations (AGT) [27]. An automated mapping to Henshin, as well as the automated construction of the weakest liberal precondition paved the way towards different kinds of ATL transformations verification [61, 60]. This work was defined as part of an integration test case generation, but it could also be used for proving model transformations.

In addition to our contributions on model transformations formalization, we proposed to use model transformations as a medium for design space exploration. We describe this work in next subsection.

**Design space exploration.** As CPS have to meet conflicting objectives with respect to their NFPs, lots of work have been conducted to automate design space exploration for CPSs. In particular, frameworks such as ArcheOpterix [1], PerOpteryx [40], and AQOSA [45] are model-based DSE frameworks in the sense that they rely on an input modeling language (*i.e.* AADL, PCM) and they provide interfaces for models analysis, optimization problems definition, and constraints validation.

As an extension to these principles, we proposed in the PhD of Smail Rahmoun to define design space exploration problems by composition of model transformation variants [63, 65]. The DSE framework we developed relies on genetic algorithms, and our method based on model transformations composition had the following advantages: first, by transferring structural validity constraints from the output model to the composition process, only valid architectures are considered during the exploration process. We expressed validity constraints with boolean formula and used SAT solving techniques to ensure explored architecture satisfy the validity constraints. Second, by defining model transformation composition techniques for DSE, we keep the optimization framework (based on genetic algorithm) completely generic: it only requires the definition of alternative model transformations as the definition of a new optimization problem. Following very similar ideas, the MOMoT framework was designed in parallel [30]. This work, as well as ours, fulfill the objective to make DSE generic. However, as opposed to our work, this work does not proceed to the validation of structural constraints during the composition of model transformation rules but after their application. As shown in [65], this would lead to a prohibitive loss of performance on complex optimization problems.

**Safety and Security.** When defining model driven methods for critical software applications, safety and security issues have to be considered. Safety related concerns have always been considered in our work, either by considering platforms (*e.g.* operating systems), standards

(e.g. for certification), or design patterns (e.g. triple modular redundancy) dedicated to improve systems safety. More recently, we have started a PhD with Jean Oudot aiming at defining quantitative evaluation methods for CPS security, as well as architecture optimization methods for CPS security. We also started another PhD with Maxime Ayrault aiming at defining design methods and runtime mechanisms to improving the resilience of CPSs to cyber attacks.

### 2.3 Supervised PhD students

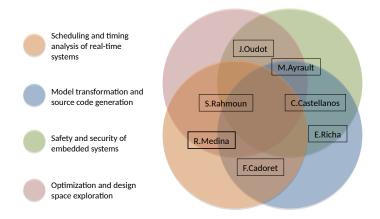

Fig. 2.2 provides a rapid overview of the PhDs undertaken with the aforementioned general objectives. In this figure, PhDs have been placed with respect to the research areas they contribute to.

Figure 2.2: Thematic distribution of co-supervised PhD students

These students have studied, with different viewpoints and objectives, the problems presented in section 2.3:

- Fabien Cadoret (02/2010 05/2014): initial proposal of the approach presented on figure 2.1, with a focus on consistency between models used for schedulability analysis and models used for code generation (thus contributing to solve problem 1). Fabien Cadoret also studied a deterministic MoCC of AADL, for which he proposed lock-free implementation variants (thus contributing to solve problem 4).

- Cuauhtémoc Castellanos (09/2011 12/2015) proposed to formalize model transformations into Alloy in order to ensure their composition always leads to analyzable models.

With respect to the approach presented in figure 2.1, this work aimed at chaining model

transformations in order to reduce the abstraction level of models used for analysis (contribution to solve problem 1) while making sure the model transformation is correct in the following sense: the model it produces respects the application condition of predefined analysis techniques (contribution to solve problem 2).

- Elie Richa (01/2012 12/2015) also studied the correctness of model transformations (problem 2) with another viewpoint: how to ease the verification and validation of their implementation? In this PhD, we defined a test framework for model transformation chains, allowing to enforce unit test coverage (where a unit is a single model transformation) using integration tests (*i.e.* tests on model transformation chains).

- Smail Rahmoun (11/2013 02/2017) extended the work of Fabien Cadoret and Cuauhtémoc Castellanos by considering design space exploration based on model transformations as a multi-objective optimization problem aiming to improve NFPs. This extension is presented in the upper part of figure 2.1, were candidate architecture are selected according to their NFPs. This work helped to automate the definition of near-optimal architectures, which is an important part of our initial goal: make the design process of CPSs more reliable by starting with the best possible design. In addition, the proposed approach was both applied on design patterns for safety (thus reusing and extending model transformations proposed by Cuauhtémoc Castellanos) and code generation (thus reusing and extending model transformations proposed by Fabien Cadoret).

- Roberto Medina (11/2015 01/2019) studied more specifically the problem of resource usage efficiency in real-time embedded systems (problem 4). This is an important topic in our context as improving the reliability of software development in real-time CPS often leads to consider margins on tasks execution time. As a consequence, computation resources are poorly used whereas system designers aim at deploying more and more complex applications in CPSs. As a contribution to solve this problem, Roberto Medina proposed new scheduling techniques on multi-core architectures based on the concepts of Mixed-Criticality, applied to directed acyclic graphs of tasks. In particular, we defined in this work new methods to (i) ensure schedulability of high criticality functions and (ii) evaluate the impact of sharing computation resource among functions of different criticality levels on the quality of service of low criticality functions.

- Jean Oudot (09/2017 ) is working on the definition of quantification methods for cyber-security of CPSs. Indeed, cyber security is becoming an important problem

in the design of CPS since these systems are becoming more and more connected to their environment. These interactions with their environment make CPSs subjects to cyber attacks with a more and more important surface attack. As opposed to traditional information systems or desktop computers, CPSs also have to meet stringent safety, performance, and/or energy consumption properties. For this reason, integrating security counter measures in CPS architectures raises important challenges in terms of multi-objective optimization problems. In particular, we aim at defining a methodology to select the set of sufficient counter measures to reach a level of acceptable risk while minimizing the impact of these counter measures on safety and performance properties. This work will contribute to the resolution of problem 3, with an emphasis on security counter measure selection and configuration.

• Maxime Ayrault (10/2018 - ) is also studying cyber security of CPS but with a different viewpoint: how to improve their resilience to attacks? Indeed, it is impossible to anticipate all the potential vulnerabilities of a complex CPS. In addition, once a CPS is deployed and used, attackers have time to study the system and discover new vulnerabilities. For this reason, it is important to deploy resilience mechanisms in CPSs to delay as much as possible the effectiveness of an attack and/or its propagation. This problem is obviously connected to the design of CPS architectures since resilience mechanisms have to be defined at design time. This work is going to contribute to the resolution of problem 3, with an emphasis on resilience to cyber attacks.

I have been the advisor of the first 6 PhD students listed above, and I am the supervisor of Maxime Ayrault's PhD.

In next chapters (3 and 4), we describe more precisely these research contributions and their link with the general approach presented on figure 2.1.

# Chapter 3

# **Architecture Models Timing Analysis**

| 3.1 | AADL Refinement Framework                                                          | 21 |

|-----|------------------------------------------------------------------------------------|----|

| 3.2 | Code generation and fine-grain analysis of partitioned systems $\ \ldots \ \ldots$ | 22 |

| 3.3 | Periodic delayed communications                                                    | 27 |

| 3.4 | Mixed-criticality DAGs analysis                                                    | 30 |

| 3.5 | Concluding remarks                                                                 | 40 |

|     |                                                                                    |    |

CPSs are subject to various non-functional requirements, and timing performance is an important class of such requirements when architecting software applications of a CPS. In addition, Model Driven Engineering (MDE) advocates for the use of models in order to improve the development process, as well as the quality, of these applications. In this chapter, we present a MDE framework aiming at automating the production of software applications of CPSs.

In particular, we consider source code generation as the final objective of an efficient MDE process. In some industry, and in particular in the transportation domain, several success stories show the added value of automated source code generation techniques. MATLAB/SIMULINK and SCADE SUITE provide source code generator widely used today. Note that these code generators produce the so-called functional code, *i.e.* software responsible to answer functional requirements. Another part of software applications for CPSs is called technical code, *i.e.* software responsible for interfacing functional code with the hardware platform of the CPS.

When it comes to the evaluation of timing performance in software architectures, both functional and technical concerns can have a great impact on the result. For instance, functional code is the main software artifact used to compute the execution time of tasks, i.e. their capacity  $C_i$  as defined in the previous chapter. On the other hand, technical code may implement complex communication mechanisms with a significant impact on timing performance. This is particularly true in avionics ARINC653 systems with inter partition communications. Nowadays, very few MDE frameworks are able to consider both the functional and technical code of a software application when evaluating their timing performances.

In this chapter, we present our contributions on the timing analysis of software architectures for CPSs. The remainder of this chapter is organized as follows. Section 3.1 gives an overview of the MDE framework we have designed to experiment our research activities. In the following sections, we present subsets of the AADL modeling language for which this framework was experimented: partitioned ARINC653 systems in section 3.2, periodic delayed queued communications in section 3.3, and DAGs of mixed-criticality tasks in section 3.4.

Results presented in sections 3.2 and 3.3 are results of Fabien Cadoret's PhD. Results presented in section 3.4 were obtained during Roberto Medina's PhD [52–54]. Figure 3.1 show how these contributions are positioned with respect to the approach we described in chapter 2.

Figure 3.1: Perimeter of research activities presented in this chapter

### 3.1 AADL Refinement Framework

In order to automate code generation for CPS while mastering the impact of generated code on timing performance, we proposed in 2011 a model transformation and code generation framework based on AADL, called RAMSES [13]. The basic principles of this framework are depicted on figure 3.2. The idea is to proceed to code generation in a step-wise model transformation process which would (i) exhibit the generated code into intermediate AADL models (*e.g.* refined AADL model on figure 3.2), (ii) analyze these intermediate models, until (iii) the AADL model reaches an abstraction level leading to a very simple mapping from AADL to source code constructions. One of the major benefit of this approach is to reduce the semantic gap between models used for analysis purpose, and models used for code generation per se.

Figure 3.2: Overview of RAMSES functionalities

This framework has been the playground of several ideas and experiments presented throughout this document. We describe those related to timing analysis in the remainder of this chapter.

# 3.2 Code generation and fine-grain analysis of partitioned systems

As mentioned in the introduction of this document, CPSs are often critical systems. However, among software components of a CPS, only a few are expected to have a high criticality level. As a consequence, CPS designers have to provide safe methods to share computation and storage resources among software components of different levels of criticality.

In the avionics domain, this problem has been solved by developing dedicated fault containment mechanisms in operating systems. These mechanisms are called time and space partitioning: applications are statically provisioned with dedicated memory and execution time slots and the operating system is in charge of enforcing the applications to remain within these predefined slots. Partitioned operating systems are known to ensure a good time and space isolation among software applications they execute, to the price of a timing overhead in communication mechanisms. This timing overhead is even more significant when considering communications among different partitions.

**Input models description.** Following the general principles described in section 3.1, we have proposed a method to precisely take into account this overhead when verifying timing requirements of a CPS. This method was first published at the International Conference on Complex Computer Systems [20] and specialized to a case study from the real-time systems domain in a publication at the international symposium on Rapid Systems Prototyping in 2014 [13]. The proposed method takes as input (i) the AADL model of applications

deployed on a partitioned system using the ARINC653 annex of AADL, and (ii) a behavioral description of the runtime services of an ARINC653 system provider, using the behavior annexe of AADL.

The AADL model of applications is composed of a set of interconnected processes, themeselves composed of interconnected tasks. In addition to these structural characteristics, models may come with a description of tasks internal behavior. The task set is expected to be described with the following information:

- timing consumption of each subprogram or thread component: either as a timing interval (bounded by best and worst case execution time) for subprograms or threads, or timed behavior actions (in the behavior annex), or a set of properties that enable to compute such timing consumptions from the control flow graph of the components (e.g. time of assignment actions, subprogram calls, expressions, etc.);

- accesses to shared data, in order to describe which component has access to a shared data, when does it access it, and what is the access policy to be considered for schedulability analysis;

- scheduling properties of the task set: scheduling protocol, periods, deadlines, and priorities (if needed, depending on the scheduling protocol).

AADL models of the runtime services are provided by RAMSES, with the support of operating systems provider. These models takes the form of a library of AADL subprograms and data components definition. Their behavior is described with the same elements as those described in previous paragraph for threads description. Their timing characteristics are supposed to be provided by operating systems vendors.

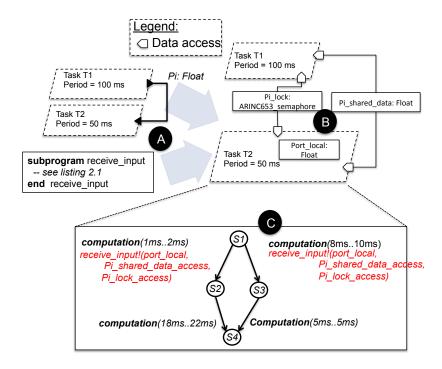

**Model refinements in RAMSES.** Figure 3.3 illustrates the principles of the architecture refinement implemented in RAMSES in order to provide fine-grain schedulability analysis. On the part **A** of the figure, we represented a summary of the input models: the architecture model on top, provided by an end-user of the framework, and the runtime services on the lower part, provided by an operating system vendor. As specified on the figure, the AADL code of the receive\_input runtime service is provided in listing 3.1. Part **B** of the figure represents the result of the refinement implemented as an automatic model transformation in RAMSES. This transformation expands abstract communication interfaces (*i.e.* AADL ports) into data accesses and subprogram calls. Data accesses enable threads to write or read the value of shared variable  $Pi\_shared\_data$ , which contains data exchanged between threads through these ports. Global variable  $Pi\_lock$  enables to protect accesses to  $Pi\_shared\_data$ . Subprogram calls are represented on part C of the figure (see  $receive\_input!(...)$ ).

Figure 3.3: Model Refinement for Timing Analysis

Listing 3.1 shows the AADL model of the *receive\_input* subprogram of the runtime services we use to implement communications between AADL threads. In addition, this listing provides the definition of a processor component which according to the AADL standard, is an abstract execution platform that represents both the hardware execution unit, and the operating system running on it. The reason for modeling the processor at this stage is that execution times of threads and subprograms obviously depend on the processor they are executed on.

From a timing analysis viewpoint, this model contains the following information:

- A computation statement describes that an execution time interval of one to two milliseconds is necessary at the beginning of the execution of this subprogram (see line 12 of listing 3.1). Note that these timing characteristics are only valid when the subprogram is executed on the *x86* processor (modeled in the same listing) as specified by the "in binding" statement line 12.

- Execution time of subprogram *receive\_input* can also be deduced from the assignment action line 14, combined with (i) the data size of operands of the assignment and (ii) the assignment time property given in line 22 of the listing.

- Data accesses are represented in lines 13 and 15, with respectively a locking and unlocking access to shared data that will be connected to interface *lock\_access* (line 5).

```

subprogram receive_input

2.

features

3

value_out: out parameter Float;

data_storage: requires data access Float;

4

5

lock_access: requires data access ARINC653_semaphore;

annex behavior_specification {**

6

7

states

s1: initial final state;

9

transitions

10

t1: s1 -[] -> s1

11

computation(1 ms ... 2 ms) in binding (x86);

12.

13

lock access!<;

14

value_out := data_storage;

15

lock_access!>;

16

}

**}:

17

18

end send_output;

19

processor x86

20

21

properties

22

Assign_Time => [Fixed => Ous; Per_Byte => 50 us];

23 | end x86;

```

Listing 3.1: AADL Runtime Services Component

In order to analyze the refined model illustrated on parts **B** and **C** of figure 3.3, at least three alternatives exist:

- 1. transform the intermediate model into a formal model to apply model checking techniques. Given its features, TIMES [3] would be a good candidate but to the best of our knowledge, it does not cover hierarchical scheduling (which is an important feature of ARINC653 systems). Another possibility could be to use more generic formal models such as timed automata or timed Petri nets. However, the translation of AADL to such models is a difficult task for which different research works were already undertaken [8, 66]. These works only cover a subset of AADL which is not he one considered in our work.

- 2. transform the intermediate model into a single task set with the following characteristics: each task is given for its capacity its WCET, and each critical section of each task is characterized by its WCET as well. The resulting model is simple to analyze with tools such as Cheddar [72] but it may cumulate pessimism (and thus waste of computation resources). Indeed, when a job executes for its task's WCET, it may spend little time in its critical section, and vice versa (when a job enters a critical section's WCET, it may spend little time in the task itself).

- 3. transform the intermediate model into a set of task sets: the control flow graph of each task of the intermediate model is transformed into an execution tree (going from one

suspended state of the task to another suspended state). Among the branches without accesses to locks, we only keep the one with the highest execution time. Branches with accesses to locks are kept as is in the tree. Task sets are then built from execution trees by applying a cartesian product of the set of execution branches of each task. Then, each task set is simple to analyze with tools such as Cheddar [72].

**Case study.** We experimented the latest alternative in [13]. The number of task sets to analyze grows rapidly with the number of branches in tasks execution trees. The number of task set configurations to analyze mainly depends on the characteristics of the input model: the number of configuration to analyze grows with the number of conditional branches in which shared data are acquired and released.

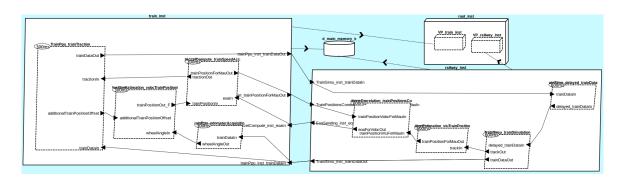

Figure 3.4 illustrates the AADL architecture of a case study from the train industry. In this domain, the main business objective is to reduce the time interval separating two consecutive trains while guaranteeing passengers safety. To reach this objective, the adaptation of powerful CU gives the opportunity to embed more computation power on-board trains. Functions traditionally deployed on the wayside infrastructure can then be embedded on-board in order to reduce response- time of functions. Trains may then be closer to one another by depending less on the wayside infrastructure. However, grouping functions on-board the train should not lead to hardware resources over-consumption otherwise the safety of the system may be put at risk.

Because train application are also made up of components of different criticality levels, partitioned operating systems are also studied for future architectures of these applications. Figure 3.4 illustrates the AADL architecture of a simplified application called Communications-Based Train Control (CBTC). This application is decomposed in two processes: the Automatic Train Operation (ATO) process, represented on the left of figure 3.4, is responsible for controlling the position, speed, and acceleration of the train. The other process, called Automatic Train Protection (ATP), is represented on the right of figure 3.4: it communicates with the ATO in order to check the validity of data computed by the ATO.

Our objective is to ensure CUs provide enough computation power to host both processes. The software architecture represented configure 3.4 is made up of two AADL processes, eight AADL threads (four threads in each process), and twelve connections among ports of these threads.

For the case study presented in figure 3.4, the timing analysis of our case study required the analysis of 64 tasks configurations (different values for the WCET of tasks and the WCET in critical sections). These configurations were analyzed using the Cheddar tool suite [72]. Experimentations were conducted on a 2.7 GHz Intel processor (Intel Core i7-3740QM; 4 cores) with 3.9 GiB memory and a SSD hard drive disk. The complete process, from the

Figure 3.4: AADL Model of our Case Study

beginning of the model refinement, until the compilation of generated code, passing by the analysis of 64 tasks configuration took 2 minutes and 17 seconds. Considering the complexity of the input architecture, this result seems to be very satisfactory: of course, the number of configuration to analyze can grow very fast by increasing the complexity of the input model, but the analysis of every single configuration is the price to pay for an exhaustive analysis. However, to limit the complexity of timing analysis, another strategy is to consider more deterministic MoCCs and to propose lock-fee implementations of these MoCCs. We present our work related to such techniques in the remainder of this chapter.

# 3.3 Periodic delayed communications

**MoCC presentation.** The MoCC we consider in this section is a variant of message passing communications among periodic tasks:

- Communication channels are modeled by directed ports and connections to enable various configurations regarding the number of sender and receiver.

- A task  $\tau_i$  can receive a set of messages on its input ports.

- A task  $\tau_i$  can send a message on its output ports to connected input ports.

- A message sent on an output port p, is eventually received on input ports connected to p.

We refined this model to ensure deterministic communications among tasks:

• During each job  $J_j$  of a task  $\tau_j$ , **exactly one message is sent** on each output port of a task.

- A message sent by a job is delivered to the receiving task at the **recipient release time following the sender job deadline**. More formally, a message sent to  $\tau_i$ , by the  $k^{th}$  job of  $\tau_j$  is considered delivered at  $\lceil \frac{k \cdot T_i + D_j}{T_i} \rceil \cdot T_i$  (remember that  $T_i$  and  $D_i$  are respectively the period and deadline of task  $\tau_i$ , as defined in notations used in chapter 2).

- Any message delivered to the  $k^{th}$  job of  $\tau_i$  should be removed from the receiving port at time  $k \cdot T_i + D_i$ . After this time, delivered messages to the  $k^{th}$  job of  $\tau_i$  are considered outdated.

- Messages delivered to a task are received in the order of sender jobs deadlines. When sender jobs deadlines are simultaneous, a predefined order noted ≺, e.g. task priorities, is used.

The model is said "periodic-delayed" as messages are periodically sent and their delivery is delayed until sender job deadlines. Such a communication model can be modeled in AADL with the following properties:

- The *Dispatch\_Protocol* property is set to *Periodic* for each thread component: tasks are periodic,

- The *Period*, and *Deadline* properties are set for each thread component (with *Deadline* ≤ *Period*),

- The *Timing* property is set to *Delayed* for output ports of tasks: messages are sent at deadline.

Note that the default value of the AADL *Output\_Rate* property already states that one message is produced per activation of the producer tasks. Similarly, we use *AllItems* as the default value for the property *Dequeue\_Protocol*, which means that all the messages available at release time of the recipient will be considered as consumed at the end of its job.

**Lock-free implementation.** In next paragraphs, we show how to compute message indexes for sent received messages order to implement these action without locks. The number of received messages at time t on a queue q of size Q can be computed as follows:

$$Received(q,t) = \sum_{j \in ST_q} \lfloor \frac{t - D_j}{T_j} \rfloor + 1$$

where  $ST_q$  is the set of tasks sending messages to q. The indexes of sent values can be computed as follows for queue q and the  $k^{th}$  job of a sender task  $\tau_i$ :

$$SendIndex(q, j, k) = Redeived(q, k \cdot T_i + D_i) - Followers(q, j, k)$$

where *Followers* is the number of successors of  $\tau_j$  (according to  $\prec$ ) in  $ST_q$  having their deadline at  $k \cdot T_j + D_j$ . More formally:

$$Follower(q, j, k) = \sum_{s \in ST_q, j \prec s} Collide(s, k \cdot T_j + D_j)$$

where Collide is defined as follows

$$Collide(s,t) = \begin{cases} 1 & \text{if } \frac{t-D_s}{T_s} \in \mathbb{N} \\ 0 & \text{otherwise} \end{cases}$$

Hence, the message sent in q by the  $k^{th}$  job of  $\tau_j$  ( $\tau_j$  is the task sending messages in q) is stored in slot SendIndex(q,i,k)  $modulo\ Q$  (Q is the size of q). Besides, received messages range from (ReadIndex(q,k-1)+1)  $modulo\ Q$  to ReadIndex(q,k)  $modulo\ Q$  where  $ReadIndex(q,k) = Received(q,k\cdot T_i)$  for the task  $\tau_i$  receiving messages from q. Note that SendIndex(q,j,k) and ReadIndex(q,k) can be computed independently without any internal state, reason why **lock free implementations** of these functions are possible. Finally, the size of q can be bound as follows (the proof of this result is available in [21]):

$$Q \le \sum_{j \in ST_q} \left( \left\lfloor \frac{2 \cdot T_q + D_{max}}{T_j} \right\rfloor + 1 \right)$$

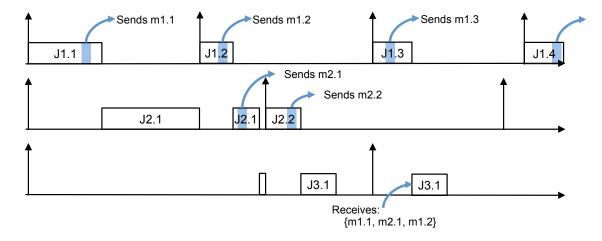

**Illustrative example** To illustrate this task and communication model, we consider the time-line depicted in Figure 3.5. This figure shows communications between three tasks:  $\tau_i$

Figure 3.5: Illustrative Example of periodic-delayed communications

with i = 1...3,  $T_i = D_i$ , and  $T_1 = 5$ ,  $T_2 = 7$ ,  $T_3 = 10$ .  $\tau_1$  and  $\tau_2$  send periodically messages

to  $\tau_3$  according to the communication model described above. As illustrated on this figure, exactly one message is sent during each task job for  $\tau_1$  and  $\tau_2$ . Note that messages m1.1, m2.1, and m1.2 are only delivered at time 10. Message m2.2 will not be delivered before 20 time units, even though job J2.2 (that produces m2.2) already finished its execution when J3.2 starts in this scenario. This model allows ensuring deterministic time for message reception independently of task interleaving and actual execution time. Notice also, that messages are ordered with respect to sender deadlines, reason why m2.1 is put before m1.2 in the queue even though J1.2 finishes before J2.1 sends message m2.2. This is done to enforce a deterministic order on message from the point of view of the receiver. Finally, m1.1, m2.1, and m2.2 are discarded at completion time of J3.2 even if these message were not used during this job.

**Discussion.** With respect to timing analysis of architecture models, periodic delayed communications bring the advantage of being deterministic and can therefore be implemented without locks. As a consequence, tasks with periodic delayed communications can be considered as independent tasks, which greatly simplifies timing analysis. For instance, it reduces the complexity of timing analysis induced by multiple critical sections (as presented in section 3.2). However, these lock free implementations require to store data structures and execute functions to retrieve and/or compute the indexes of sent or received messages. This is why the refined model produced by RAMSES is important: it allows to check platform resources are still sufficient even when taking into account the overhead due to the implementation of communication mechanisms. Last but not least, delayed communications tend to increase data flow latency, i.e. the time range separating the reception of inputs from sensors to the production of commands to actuators in a CPS. This is one of the reasons why we decided to consider task models made up of DAGs of tasks. Another reason was the necessity to provide solutions for scheduling mixed-criticality task sets on multi-core architectures. This work is presented in next section. Note however, that these two MoCCs (i.e. DAGs and periodic-delayed) are complementary: periodic delayed communications are often used to break cycles in tasks dependencies while preserving deterministic MoCC and lock free implementations. Last but not least, scheduling real-time DAGs is known to be a difficult problem and its adaptation to mixed criticality scheduling required a PhD thesis on its own.

## 3.4 Mixed-criticality DAGs analysis

The contributions presented in section 3.2 aim at automating the analysis of tasks sets with critical sections. On hypothesis of this work was that tasks are executed on monocore architectures. The results presented in section 3.3 show how to implement lock free

communications among periodic tasks. Given the communication model we considered, these results can be used when scheduling tasks on multi-core architecture. Tasks would then be considered as independent, which greatly ease the application of scheduling techniques. However, as stated at the end of previous section, this MoCC induces important latency on data flows.

**Context.** A MoCC frequently used to model critical embedded systems consists of data flow graphs. This model defines *actors* that communicate with each other in order to make the system run: the system is said to be *data-driven*. The actors defined by this model can be tasks, jobs or pieces of code. An actor can only execute if all its predecessors have produced the required amount of data. Therefore, actors have *data-dependencies* in their execution. Theory behind this model and its semantics provide interesting results in terms of logical correctness: deterministic execution, starvation freedom, bounded latency, are some examples of properties that can be formally proven thanks to data-flow graphs.

In this work we have considered a simple subclass of data-flow graphs in which data dependencies are directly captured into Directed Acyclic Graphs of tasks. In this MoCC, a software architecture is made up of DAGs in which vertices represents tasks, and edges represent precendence constraint, *i.e.* a task can only start executing when all its predecessors have finished their execution. In parallel, the adoption of multi-core architectures in the real-time scheduling theory led to the adaptation and development of new scheduling policies [26]. Processing capabilities offered by multi-core architectures are quite appealing for safety-critical systems since there are important constraints in terms of power consumption and weight. Nonetheless, this type of architecture was designed to optimize the average performance and not the worst case. Therefore, ensuring time correctness becomes harder when multi-core architectures are considered: in hard real-time systems the Worst Case Execution Time is used to determine if a system is schedulable.

This observation is one of the main reason for the popularity of the mixed-criticality scheduling (MCS), intensively studied these last years [19]. With MCS, tasks can be executed in different execution modes: in the nominal mode, high and low criticality tasks are both executed with an optimistic timing budget. When the system detects a timing failure event (TFE), *i.e.* a task did not complete its execution within its optimistic timing budget, the system switches to a degraded mode. In this mode, high criticality tasks are executed with their pessimistic timing budget, discarding [74] low criticality tasks or degrading them [73] (*i.e.* reducing their execution frequency).