# Functional safety and reliability of neuromorphic computing systems

Theofilos Spyrou

## ▶ To cite this version:

Theofilos Spyrou. Functional safety and reliability of neuromorphic computing systems. Artificial Intelligence [cs.AI]. Sorbonne Université, 2023. English. NNT: 2023SORUS118. tel-04133095v2

# HAL Id: tel-04133095 https://hal.science/tel-04133095v2

Submitted on 26 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT de sorbonne université

## FUNCTIONAL SAFETY & RELIABILITY OF NEUROMORPHIC COMPUTING SYSTEMS

présentée par THEOFILOS SPYROU

École Doctorale Informatique, Télécommunications et Électronique

réalisée au Laboratoire d'Informatique de Paris 6

#### soutenue le 7 juin 2023

devant le jury composé de :

| M.   | Bertrand GRANADO          | Prof., Sorbonne Univ., CNRS, LIP6, Paris          | Président          |

|------|---------------------------|---------------------------------------------------|--------------------|

| Mme. | Lorena ANGHEL             | Prof., Grenoble INP, Spintec, Grenoble            | Rapporteure        |

| M.   | Paolo RECH                | Assoc. Prof., Univ. Degli Studi di Trento, Italie | Rapporteur         |

| M.   | Said HAMDIOUI             | Prof., Univ. Technologique de Delft, Pays-Bas     | Examinateur        |

| M.   | Alkiviadis HATZOPOULOS    | Prof., Univ. Aristote de Thessalonique, Grèce     | Examinateur        |

| M.   | Haralampos STRATIGOPOULOS | DR, Sorbonne Univ., CNRS, LIP6, Paris             | Directeur de Thèse |

|      |                           |                                                   |                    |

Functional Safety & Reliability of Neuromorphic Computing Systems

Theofilos Spyrou Paris, 2023

SUPERVISOR: Haralampos Stratigopoulos To my parents who always supported and believed in me,

*my sister who is always there for me and stands by my side for life,*

> *my canine brother who taught me how to be a child again...*

## ABSTRACT

The recent rise of Artificial Intelligence (AI) has found a wide range of applications essentially integrating it. The goal is the improvement of the provided services and ultimately a more convenient life for everyone. Although AI has had some bad days in the past, it is now more mature than ever and it is gaining more and more ground in almost any field of our lives. However, there is a question that still persists and remains unanswered: how trustworthy AI really is?

The answer to this question is a combination of multiple factors such as the quality of the AI application, the ethics of the people who implemented it and those using it, etc. Among these factors, there is one standing out and needs to be thoroughly considered before the employment of AI in the field, especially in mission- and safety-critical applications like autonomous vehicles. This is no other than the dependability of the systems hosting the operation of AI applications, or the AI hardware accelerators.

At first sight, there might seem that there is no problem, as Artificial Neural Networks (ANNs), and particularly the biology-inspired Spiking Neural Networks (SNNs) are believed to be resilient structures just like their biological counterparts. The human brain for instance is known to be remarkably capable of tolerating faults that may occur in the neurons or synapses, retaining its functionality intact. However, although SNNs become heir of this property to some extent, an assumption of inherent fault tolerance is rather naive when considering that electronics do not operate the same way as biology. Hence, a defect of an electronic component or a fault occurring either during the fabrication of an Integrated Circuit (IC) or after its deployment in the field can have a disastrous effect on the performance of the executed AI application, threatening in this way the safety of the surrounding people and the environment.

Because of these, it is made evident that a methodological exploration of the dependability characteristics of AI hardware accelerators and neuromorphic platforms, i.e., accelerators hosting the training and/or inference of SNNs, is of utmost importance. First, a resilience analysis of the SNN and its neuromorphic chip against hardware-level faults helps in the study of the system's reliability by pinpointing the critical parts. Next, these parts need to be protected with a fault tolerance strategy that allows the network to tolerate some of the faults proactively and the rest reactively after testing and mitigating the effects of the detected faults.

This thesis tackles the subjects of testing and fault tolerance in SNNs and their neuromorphic implementations on hardware. It starts with a defect-oriented taxonomy of faulty behaviors of a spiking neuron at transistor level, which forms the basis of a behavioral-level fault model specific to SNNs, yet agnostic to the circuit design and architecture. Based on this, a series of large-scale fault injection experiments is conducted through a hardware-accelerated fault injection framework designed for SNNs, aiming at analyzing their resilience. Leveraging the results of these experiments, a cost-effective fault tolerance strategy for SNNs is proposed. Also, a neuromorphic hardware experimentation platform is presented, on which a reliability assessment of SNNs running on actual neuromorphic hardware is performed. After the assessment, the platform is equipped with an on-line on-chip testing mechanism that detects faults in real time. Finally, a compact functional test-set generation technique is demonstrated to address the problem of testing neuromorphic hardware in a generalized way.

# $\mathbf{R} \neq \mathbf{S} \mathbf{U} \mathbf{M} \neq$

L'essor récent de l'Intelligence Artificielle (IA) a trouvé un large éventail d'applications cibles. L'objectif est l'amélioration des services fournis au final une vie plus simple pour tous. Après avoir connu de mauvais jours, l'IA revient sur le devant de la scène, plus mature que jamais, et gagne de plus en plus de terrain dans presque tous les domaines de notre vie. Cependant, une question persiste et reste sans réponse : dans quelle mesure l'IA est-elle vraiment digne de confiance ?

La réponse à cette question est une combinaison de multiples facteurs tels que la qualité de l'IA, l'éthique des personnes qui l'ont mise en œuvre et de celles qui l'utilisent, etc. Parmi ces facteurs, il en est un qui se démarque et qui doit être examiné de manière approfondie, en particulier dans les applications critiques pour la mission et la sûreté telle que les véhicules autonomes. Il s'agit de la fiabilité des systèmes hébergeant l'IA, ou de leurs accélérateurs matériels.

On peut croire, à première vue, qu'il n'y a pas de problème, car les réseaux neuronaux artificiels (ANNs : Artificial Neural Networks en anglais), et en particulier les réseaux neuronaux à impulsions (SNNs : Spiking Neural Networks en anglais) d'inspiration biologique, sont considérés comme des structures résilientes, tout comme leurs homologues biologiques. Le cerveau humain, par exemple, est connu pour être remarquablement capable de tolérer les défauts qui peuvent se produire dans les neurones ou les synapses, en conservant sa fonctionnalité intacte. Cependant, bien que les SNNs héritent de cette propriété dans une certaine mesure, l'hypothèse d'une tolérance inhérente aux fautes est plutôt naïve si l'on considère que l'électronique ne fonctionne pas de la même manière que la biologie. Ainsi, le défaut d'un composant électronique ou une faute survenant pendant la fabrication d'un circuit intégré ou après son déploiement peut avoir un effet désastreux sur les performances de l'application exécutée, menaçant ainsi la sécurité des personnes environnantes et de l'environnement.

Pour ces raisons, il est évident qu'une exploration méthodologique des caractéristiques de fiabilité des accélérateurs matériels d'IA et des plateformes neuromorphiques, c'est-à-dire des accélérateurs hébergeant l'entraînement et/ou l'inférence de SNNs, est de la plus haute importance. Tout d'abord, une analyse de la résilience du SNN et de sa puce neuromorphique contre les fautes au niveau matériel aide à l'étude de la fiabilité du système en identifiant les parties critiques. Ensuite, ces parties doivent être protégées par une stratégie de tolérance aux fautes qui permet au réseau de tolérer certaines des fautes de manière proactive et le reste de manière réactive après avoir testé et atténué les effets des fautes détectées.

Cette thèse aborde les sujets du test et de la tolérance aux fautes dans les SNNs et leurs implémentations neuromorphiques matérielles. Elle commence par une taxonomie des comportements défectueux d'un neurone à impulsions au niveau des transistors, qui forme la base d'un modèle de fautes au niveau comportemental spécifique aux SNNs, mais agnostique à la conception et à l'architecture du circuit. Sur cette base, une série d'expériences d'injection de fautes à grande échelle est menée par le biais d'un *framework* d'injection de fautes accéléré matériellement conçu pour les SNNs, dans le but d'analyser leur résilience. En s'appuyant sur les résultats de ces expériences, une stratégie de tolérance aux fautes efficace pour les SNNs est proposée. Une plateforme d'expérimentation de matériel neuromorphique est également présentée, sur laquelle une évaluation de la fiabilité des SNNs fonctionnant sur du matériel neuromorphique réel est effectuée. Après l'évaluation, la plateforme est équipée d'un mécanisme de test sur puce et en ligne qui détecte les défauts en temps réel. Enfin, une technique compacte de génération de test-set fonctionnel est démontrée pour répondre au problème du test de matériel neuromorphique d'une manière généralisée.

## PUBLICATIONS

As a result of this thesis the following publications have appeared:

- [1] S. A. El-Sayed, T. Spyrou, E. Afacan, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Spiking neuron hardware-level fault modeling," in *Proc. 26th IEEE Int. Symp. On-Line Test. Robust Syst. Des.* (*IOLTS*), Jul. 2020.

- [2] T. Spyrou, S. A. El-Sayed, E. Afacan, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Neuron fault tolerance in spiking neural networks," in *Proc. Design Autom. Test Europe Conf. (DATE)*, Feb. 2021.

- [3] T. Spyrou, S. A. El-Sayed, E. Afacan, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Reliability analysis of a spiking neural network hardware accelerator," in *Proc. Design Autom. Test Europe Conf. (DATE)*, Mar. 2022.

- [4] S. A. El-Sayed, T. Spyrou, L. A. Camuñas-Mesa, and H.-G. Stratigopoulos, "Compact functional testing for neuromorphic computing circuits," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, 2022.

- [5] T. Spyrou and H.-G. Stratigopoulos, "On-line testing of neuromorphic hardware," in *Proc. IEEE Eur. Test Symp. (ETS)*, May 2023.

- [6] T. Spyrou, S. A. El-Sayed, and H.-G. Stratigopoulos, "SpikeFI: a fault injection framework for spiking neural networks," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, 2023 (submitted).

## ACKNOWLEDGMENTS

*"As you set out for Ithaka hope the voyage is a long one, full of adventure, full of discovery."*

— Konstantinos Kavafis

Pursuing a PhD degree is not only about research; it's a true voyage in the world of knowledge. And as in every journey, discovery is its basis and is essential in order to learn and understand the purpose. Besides, it is not the destination that matters but the journey itself, the adventure that is unrolled while heading toward the destination. During this, a lot of people come and go, each one contributing in their own way to the arrival at the final destination. Acknowledging these people's contribution and thanking them for that is the least act of appreciation someone can show in return. Before that though, let me start with how this wonderful philosophical voyage began.

It is June 2019 when a senior student at the Electrical and Computer Engineering department of the Polytechnic School of Aristotle University of Thessaloniki is finalizing his engineering thesis and preparing for the approaching exams of the final semester. And then, prof. Alkis Hatzopoulos, forwards to his students an email of prof. Haralampos Stratigopoulos, with the latter announcing the opening of a PhD position at Sorbonne University for which he was seeking a student. His proposal had just been accepted by Sorbonne Center for Artificial Intelligence (SCAI) and advanced to the final round before approval. So, the selected for the position student had to compete through a short interview with other 19 Artificial Intelligence (AI)-related topics and convince the jury that the topic was worth one of the ten granted fellowships.

Without spending a single moment, I directly replied to the email and a few days later I'm in prof. Hatzopoulos office discussing with prof. Stratigopoulos about the PhD. I remember the two first things I said: (i) I haven't got my diploma yet and (ii) I speak no French. Thankfully, none of these was a constraining factor and after a closer discussion with Haralampos, I was his choice for the position. Having no time to lose as the final interview was only two weeks ahead, we started preparing while in parallel the exams in Aristotle University were in progress. Eventually, everything goes fine with the exams and shortly after I find myself in Paris before the jury of SCAI. Let me mention at this point that the interview took place in the 20<sup>th</sup> + floor of Tour Zamansky, France's third highest building, which means that the view was better than any existing carte postale of the city of lights... Trying not to get distracted by the beauty of Paris, I turn my head the other way and start the presentation. Minutes passed like seconds and now we're waiting for the results. Of course, I had planned a few

days of vacation after the interview, since this was my first time in the city. After a lunch with Haralampos, I calmly head back to my hotel not expecting to have the results soon as it was a summer Friday afternoon at the end of June. But no! The results were ready a couple of hours later and before I make it back to the hotel, Haralampos calls me to announce the great news. I can't hide that this was the best day of my (professional) life and the weekend that followed the most relaxing and peaceful I ever had.

First and before all, I would like to warmly thank from the deepest of my heart **Haralampos Stratigopoulos** for trusting me and giving me this amazing opportunity. Honestly, having discussed with many other PhD students, it is not often the case to hear the best about student-supervisor relationships. Maybe my case was an outlier as I believe Haralampos was the best supervisor someone can have. He was always there during my PhD willing to help, explain, and teach. His guidance was essential and his involvement to the right extend: neither too much being intrusive, nor too little to feel abandoned. As his student, I learnt a lot of useful things by his side that I believe will shape my future career and contribute to my professional development. But beyond all lessons, Haralampos showed me what being a good professor is about, not only professionally but also humanly by respecting and treating everyone nicely, patiently, and selflessly. For all these, I am more than grateful to have had Haralampos as my mentor during this voyage.

A special thank you to prof. **Alkis Hatzopoulos** as well, who trusted me from the first moment and recommended me to Haralampos without any hesitations. It is more than fascinating the fact that the academic community can be so bonded with mutual cooperation and communication among universities worldwide. Prof. Hatzopoulos was my engineering thesis supervisor, so in a way, he prepared me for moving forward toward pursuing a higher academic degree with all the difficulties it may hide.

Another vital contribution to the realization of this PhD was the one of SCAI and the colleagues who work there. SCAI was founded right before my voyage started and as one of its very first ten students, I feel but proud if I have contributed the slightest at its scientific development and recognition through my work and effort. I would also like to thank Prof. **Gérard Biau** (director) and Dr **Xavier Fresquet** (deputy director) for all their help throughout these years and for their educational and scientific initiatives, which made the presence of SCAI strong in the scientific community. Also, the whole team of SCAI was very warm and I really enjoyed every meeting and every moment with my fellow students there, whose work is always admiring to hear about.

Luis A. Camuñas Mesa played a major role in the realization of this PhD with his essential contributions. Thank you Luis for the circuits you provided us with, which enabled the experiments performed as part of the work of this thesis; the multiple meetings to explain us the details of the various functionalities of the circuits; and your patience to answer all our questions. Once again, you proved the nice values of cooperation beyond the borders of a university or a country. I can also say that the Spanish comments in the designs taught some basics of the language and made me eager to actively start learning it!

When I started my voyage I saw it as something ordinary rather than a adventure full of surprises. Yet, there were many hidden surprises waiting to be unravelled in the way. The most important of them was when I met **Sarah A. ElSayed**, my twin sister albeit a few years older, as she used to say. Sarah was undeniably a source of inspiration for me, who literally made me view the world through a new pair of eyes. I will never forget the endless conversations, debates, cultural exchanges, etc., which could last until late at the office. It was my honor to work with you Sarah and definitely I hope that we will have this opportunity again at some point in time and space. Beyond all, I feel more than happy to have met such a great friend for life.

Sharing an office with other students and researchers is a nice experience. Either working on the same project, or on a similar research field, it is always interesting to learn about the work of colleagues and hear about their successes. The office 415 was one of these places where I made amazing friends and I am grateful to have shared it with them. **Antonis** the Grand Maître who turned chess into the sport of the lab and made us only dreaming a victory against him; **Julian** who was taking care to make our day with his endless positive energy; **Gabriel** who was the "serious" of the office and who helped me meet closer the French culture; **Spyros** who I know since high school and we had once again the opportunity to work together. Of course I cannot skip all these amazing colleagues that I worked with during these years: **Engin**, **Mohamed**, **Paul**, and **Shaima**. Thank you all for sharing the journey with me.

However, the borders of an office were not enough to keep me from making more friends. Ilias with whom we explored every corner of Paris and travelled in almost every place of France; Alan who was always in to every plan and showed me the amazing Mexican culture; Maxime who was the "teaser" of the lab (in a good way) and the most cheerful person I have ever met; Clara and Mathuran whose good vibes were brightening our days. Ning, Andrien, Rieul, Thomas, Nathan, Jonathan, Baptiste, Aymeric, and Abdelrahman were also some of the amazing friendships I built during my journey.

Outside the professional environment, the journey continued and actually was augmented as I lived for three years in the *Cité Internationale Universitaire de Paris* (CIUP); a multicultural campus with tens of residences of countries from all around the world, endless green spaces, and full of sport and cultural events. I had the opportunity to stay in the Portuguese and the Dutch houses where I learnt a lot not only about the cultures of these two countries but also for many more, since there was a huge variety in the nationalities of the residents. It was more than fascinating to meet so many people coming from different parts of the world and studying on various disciplines. Some of the greatest friendships that were born during my stay were these of **Tasos**, who is coming from a neighbor city of my hometown in Greece but we met so far away, **Dimitris**, and **Anastasia**, with all of whom I had an awesome time and enjoyed our endless conversations and adventures.

Nonetheless, the largest of my gratitude is reserved for my family. My parents **Anna** and **Dimitris** never stopped being by my side supporting each of my decisions and steps in life. They are the ones who helped me reach this point by teaching me how to dream and follow my ambitions. Thank you mom and dad for believing in me. My sister **Vasilina** is the only person in the world that was, is, and will be standing by my side for life. Although younger, I have to admit that I admire her for her willingness to achieve her goals being strong and independent, always ready to define her own paths. Thank you for helping me become a better person. Last but not least, I cannot leave aside the youngest member of the family, my brother **Faidon**. Despite the fact that he is a dog, the word "brother" describes our bond pretty accurately. He is the only one reminding me what is really important in life and what it means to be truly selfless. Thank you for being the most vivid example of life and the kindest creature I have ever met.

Theofilos

# CONTENTS

| 1   | Intro | ntroduction                            |                         |                                               |    |

|-----|-------|----------------------------------------|-------------------------|-----------------------------------------------|----|

|     | 1.1   | Artificial Intelligence: Industry v4.0 |                         |                                               | 2  |

|     |       | 1.1.1                                  | The Chr                 | onology of Thinking Machines                  | 2  |

|     |       | 1.1.2                                  | The AI V                | Winters & the Transition towards an AI Spring | 6  |

|     |       |                                        | 1.1.2.1                 | AI Winter I, 1973-1980                        | 6  |

|     |       |                                        | 1.1.2.2                 | AI Winter II, 1988-1993                       | 7  |

|     |       |                                        | 1.1.2.3                 | Post-AI Winter, 1994-2011                     | 7  |

|     |       |                                        | 1.1.2.4                 | AI Spring, 2012-now                           | 8  |

|     |       | 1.1.3                                  | Breathin                | ng New Life into AI                           | 8  |

|     |       |                                        | 1.1.3.1                 | AI Hardware Accelerators                      | 9  |

|     |       |                                        | 1.1.3.2                 | AI at the Edge                                | 10 |

|     |       |                                        | 1.1.3.3                 | Big Data                                      | 11 |

|     |       | 1.1.4                                  | Neurom                  | orphic Engineering: An Artificial Brain?      | 12 |

|     | 1.2   | Critica                                | ality of Al             | I Applications                                | 14 |

|     |       | 1.2.1                                  | AI Hard                 | lware in Safety-Critical Applications         | 14 |

|     |       | 1.2.2                                  | Reliabili               | ty Concerns over AI Hardware                  | 15 |

|     | 1.3   | Motiva                                 | ation                   | · · · · · · · · · · · · · · · · · · ·         | 16 |

|     | 1.4   | Towar                                  | d Trustwo               | orthy AI                                      | 17 |

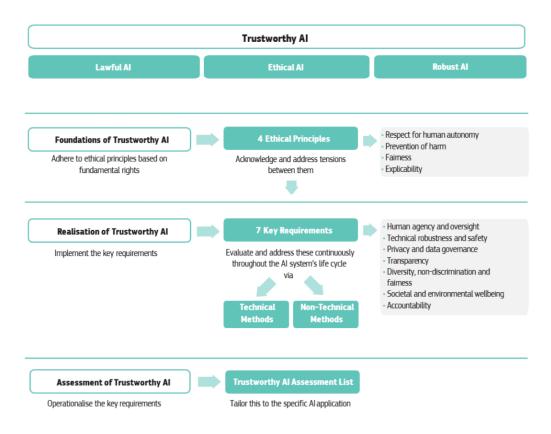

|     |       | 1.4.1                                  | A Multi-                | -Dimensional Problem                          | 17 |

|     |       |                                        | 1.4.1.1                 | Lawful AI                                     | 18 |

|     |       |                                        | 1.4.1.2                 | Ethical AI                                    | 19 |

|     |       |                                        | 1.4.1.3                 | Robust AI                                     | 20 |

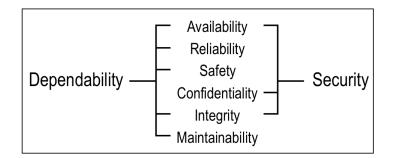

|     |       | 1.4.2                                  | Robustn                 | less through Dependability                    | 21 |

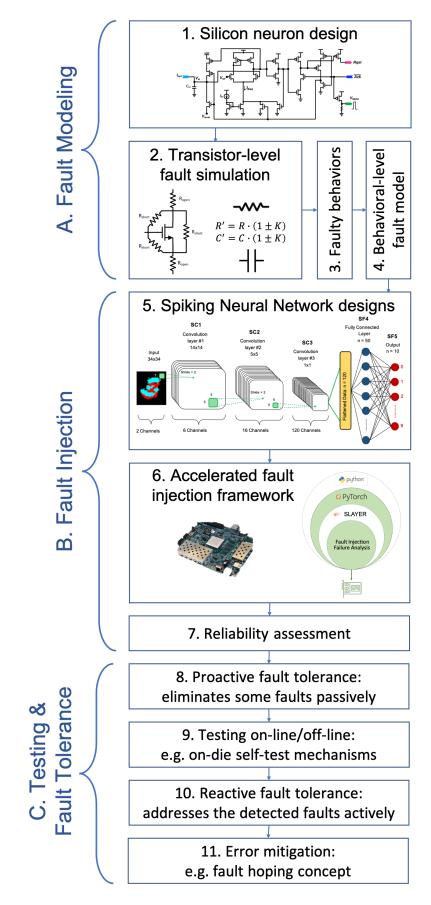

|     | 1.5   | Resear                                 | ch Methodology          |                                               | 25 |

|     |       | 1.5.1                                  |                         | Fault Modeling                                |    |

|     |       | 1.5.2                                  | Fault Injection         |                                               | 25 |

|     |       | 1.5.3                                  | Testing of              | & Fault Tolerance                             | 26 |

|     | 1.6   | Thesis                                 | Structur                | e                                             | 26 |

| 2   | A Bı  | rief Intr                              | oduction                | to Spiking Neural Networks                    | 29 |

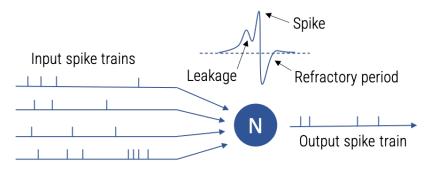

|     | 2.1   | Inform                                 | nation Pro              | ocessing                                      | 30 |

|     | 2.2   |                                        | ing                     |                                               |    |

|     | 2.3   | Neuro                                  | omorphic Implementation |                                               |    |

|     | 2.4   | Comparison with Conventional ANNs      |                         |                                               | 37 |

| 3   | Hare  | dware-I                                | Level Fau               | lt Modeling                                   | 39 |

| -   | 3.1   | The Sp                                 | oiking Ne               | euron                                         | 40 |

|     | -     | 3.1.1                                  | Behavio                 | ral Model                                     | 40 |

|     |       | 3.1.2                                  |                         | or-Level Design                               | 40 |

| - 0 |       |                                        | n Setup                 | 41                                            |    |

|     | 3.3   |                                        |                         | n Faulty Behaviors                            | 42 |

|     | -     | 3.3.1                                  | Catastro                | phic Faults                                   | 42 |

|     |       | -                                      |                         | -                                             |    |

|   |      | 3.3.2     | Paramet             | tric Faults                                   |  | 45         |

|---|------|-----------|---------------------|-----------------------------------------------|--|------------|

|   | 3.4  | Behav     | ioral-Lev           | el Fault Model                                |  | 47         |

| 4 | SNN  | J Fault   | Injection           | Framework                                     |  | 49         |

|   | 4.1  | Relate    | d Work c            | on Fault Injection Experiments and Frameworks |  | 50         |

|   | 4.2  | Descri    | iption of           | the Fault Injection Framework                 |  | 50         |

|   |      | 4.2.1     | The Spil            | ke Response Model                             |  | 52         |

|   |      | 4.2.2     | Fault M             | odeling                                       |  | 53         |

|   |      | -         | 4.2.2.1             | Neuron Faults                                 |  | 53         |

|   |      |           | 4.2.2.2             | Synapse Faults                                |  | 54         |

|   |      | 4.2.3     | Fault In            | jection Methodology                           |  | 54         |

|   | 4.3  | Case S    | Studies .           |                                               |  | 56         |

|   |      | 4.3.1     | N-MNIS              | ST SNN                                        |  | 56         |

|   |      | 4.3.2     | Gesture             | SNN                                           |  | 56         |

|   | 4.4  | Layer     | Criticalit          | у                                             |  | 57         |

|   | 4.5  | Faults    | Occurrir            | ng After Training                             |  | 57         |

|   |      | 4.5.1     |                     | Fault Injection Results                       |  | 58         |

|   |      |           | 4.5.1.1             | Dead Neurons                                  |  | 59         |

|   |      |           | 4.5.1.2             | Saturated Neurons                             |  | 59         |

|   |      |           | 4.5.1.3             | Neuron Timing Variations                      |  | 59         |

|   |      |           | 4.5.1.4             | Neuron Threshold Perturbation                 |  | 60         |

|   |      |           | 4.5.1.5             | Neuron Refractory Period Perturbation         |  | 61         |

|   |      | 4.5.2     | Synapse             | Fault Injection Results                       |  | 62         |

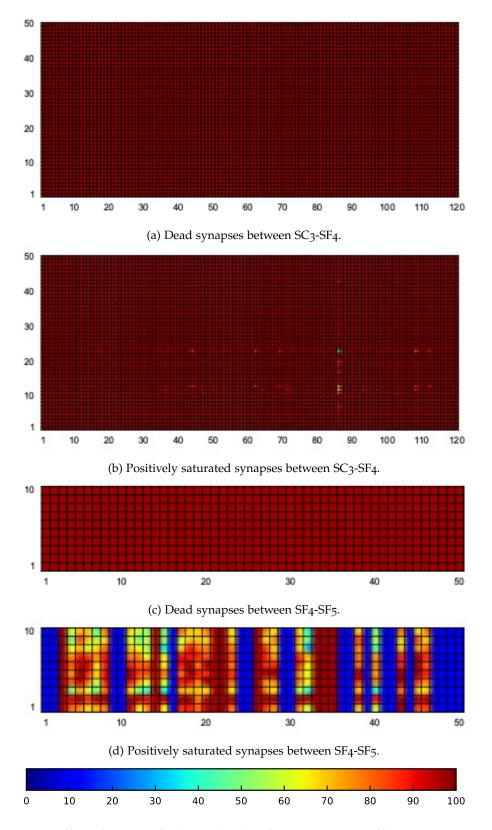

|   |      |           | 4.5.2.1             | Dead Synapses                                 |  | 62         |

|   |      |           | 4.5.2.2             | Positively Saturated Synapses                 |  | 62         |

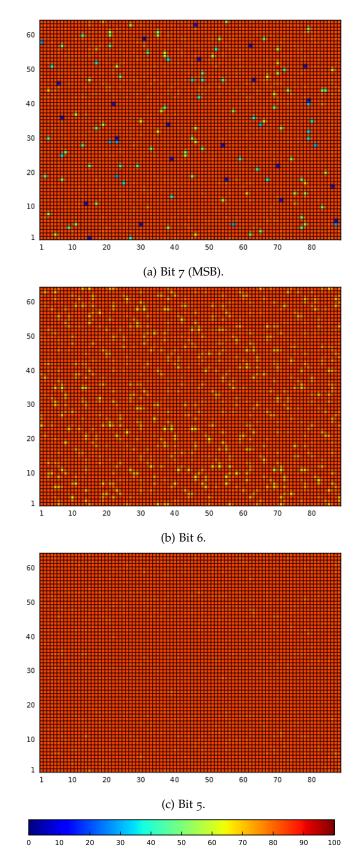

|   |      |           | 4.5.2.3             | Bit-Flipped Synapses                          |  | 62         |

|   | 4.6  | Faults    | Occurrir            | g Before Training                             |  | 65         |

| 5 | Neu  |           |                     | lware Experimentation Platform                |  | 67         |

| 5 | 5.1  | 1         |                     | Hardware Architecture                         |  | <i>6</i> 8 |

|   | 0    | 5.1.1     | -                   | volutional Node                               |  | 68         |

|   |      | 5         | 5.1.1.1             | The Convolutional Unit                        |  | 68         |

|   |      |           | 5.1.1.2             | The Router                                    |  | 69         |

|   |      |           | 5.1.1.3             | The Configuration Block                       |  | 70         |

|   |      | 5.1.2     | Memory              | / Hierarchy                                   |  | 70         |

|   | 5.2  | Embeo     | -                   | tem Design                                    |  | 71         |

|   |      | 5.2.1     | Control             | ling Processor                                |  | 72         |

|   |      | 5.2.2     |                     | Framework                                     |  | 73         |

| 6 | Reli | ability . |                     | ent of Neuromorphic Hardware                  |  | 75         |

|   | 6.1  | 2         |                     |                                               |  | 76         |

|   | 6.2  |           |                     |                                               |  | 77         |

|   | 6.3  |           | eliability Analysis |                                               |  |            |

|   | 5    | 6.3.1     | 2                   | Fault Injection Results                       |  | 78         |

|   |      | 6.3.2     |                     | d Fault Injection Results                     |  | ,<br>79    |

| 7 | Con  | 5         | 0                   | Testing for Neuromorphic Circuits             |  | 81         |

| ' | 7.1  |           |                     |                                               |  | 82         |

|   | 7.2  |           |                     | tional Test Generation Algorithm              |  | 83         |

|   |      | /         |                     |                                               |  |            |

|        | 7.3  | SNN Case Studies                                          |     |  |

|--------|------|-----------------------------------------------------------|-----|--|

|        | 7.4  | Fault Space Reduction                                     | 86  |  |

|        |      | 7.4.1 Behavioral-Level Fault Model                        | 86  |  |

|        |      | 7.4.2 Hardware-Level Fault Model                          | 88  |  |

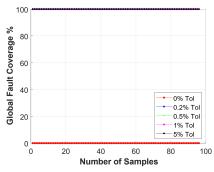

|        | 7.5  | Results                                                   | 88  |  |

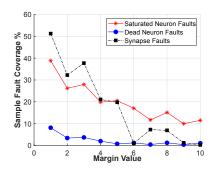

|        | 7.6  | Discussion                                                |     |  |

|        |      | 7.6.1 Generality                                          | 92  |  |

|        |      | 7.6.2 Test Generation Effort                              | 93  |  |

|        |      | 7.6.3 Other Metrics for Grading Functional Tests          | 94  |  |

|        | 7.7  | Related Work on Functional Test Generation and Comparison | 94  |  |

| 8      | Neu  | ron Fault Tolerance Strategy                              | 97  |  |

|        | 8.1  | Related Work on Fault Tolerance                           | 98  |  |

|        | 8.2  | Passive Fault Tolerance using Dropout                     | 99  |  |

|        | 8.3  | Active Fault Tolerance in Hidden Layers                   | 102 |  |

|        |      | 8.3.1 Offline Self-Test                                   | 102 |  |

|        |      | 8.3.2 Online Self-Test                                    | 103 |  |

|        |      | 8.3.3 Recovery Mechanism                                  | 103 |  |

|        | 8.4  | Active Fault Tolerance in the Output Layer                | 104 |  |

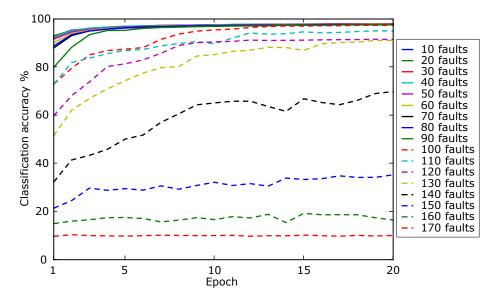

|        | 8.5  | Multiple Fault Scenario                                   | 105 |  |

| 9 On-L |      | Line Testing of Neuromorphic Hardware                     | 107 |  |

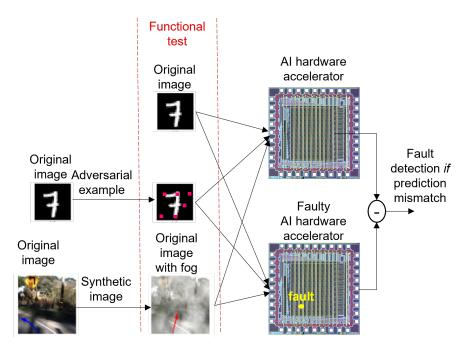

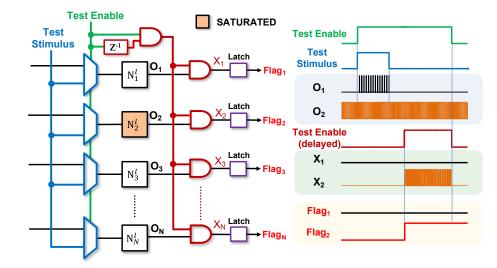

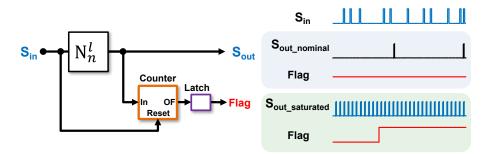

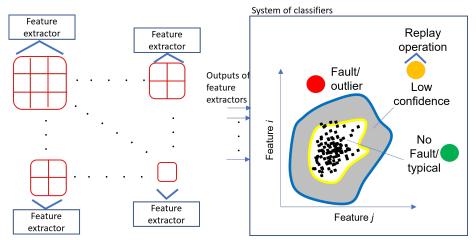

|        | 9.1  | Proposed Testing Approach                                 | 108 |  |

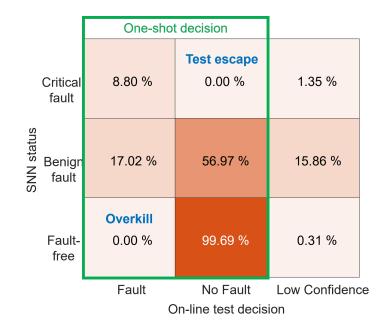

|        | 9.2  | Case Study                                                | 111 |  |

|        |      | 9.2.1 Classifiers                                         | 111 |  |

|        |      | 9.2.2 Dataset Categorization                              | 111 |  |

|        |      | 9.2.3 Fault Model                                         | 112 |  |

|        | 9.3  | Experimental Results                                      | 112 |  |

| 10     | Cond | clusions                                                  | 115 |  |

|        | 10.1 | Thesis Contributions                                      | 115 |  |

|        | 10.2 | Future Perspectives                                       | 117 |  |

|        |      |                                                           |     |  |

Bibliography

119

# LIST OF FIGURES

| Figure 1.1  | The Turing Test. Player C, the interrogator, is given the               |    |

|-------------|-------------------------------------------------------------------------|----|

|             | task of trying to determine which player – A or B – is a                |    |

|             | computer and which is a human [1]                                       | 3  |

| Figure 1.2  | The architecture of LeNet-5 [8]                                         | 4  |

| Figure 1.3  | The architecture of AlexNet [10]                                        | 4  |

| Figure 1.4  | The architecture of GoogLeNet, or Inception Network [11].               | 5  |

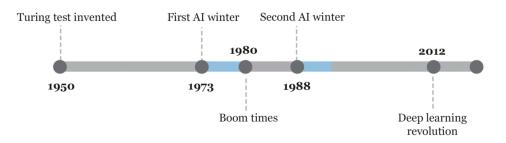

| Figure 1.5  | Timeline of AI winters                                                  | 6  |

| Figure 1.6  | AI hardware accelerators comparison                                     | 9  |

| Figure 1.7  | The edge computing infrastructure.                                      | 11 |

| Figure 1.8  | Comparison of power-area performance among biological                   |    |

|             | neurons, silicon neurons, and digital computers [29]                    | 13 |

| Figure 1.9  | The framework for trustworthy AI as proposed by the                     |    |

|             | EU [41]                                                                 | 18 |

| Figure 1.10 | Dependability and security attributes of a system [42]                  | 22 |

| Figure 1.11 | Proposed methodology to ensure the reliability of SNNs.                 | 24 |

| Figure 2.1  | Operation of the leaky I&F spiking neuron                               | 30 |

| Figure 2.2  | The Intel Loihi 2 die                                                   | 35 |

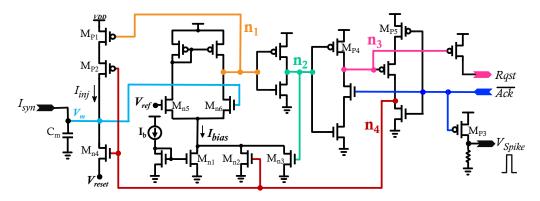

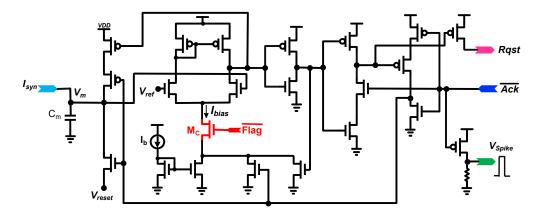

| Figure 3.1  | I&F neuron circuit.                                                     | 41 |

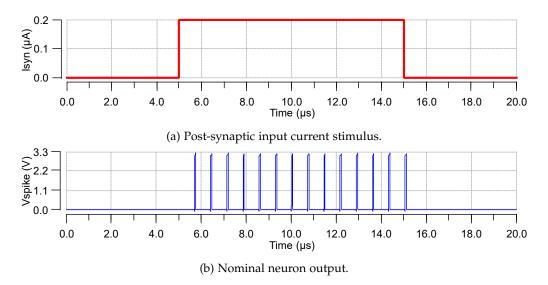

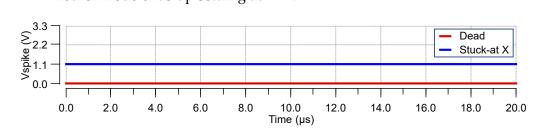

| Figure 3.2  | Nominal operation of I&F neuron                                         | 43 |

| Figure 3.3  | Saturated output caused by a stuck-on $M_{p1}$ transistor. $% M_{p1}$ . | 43 |

| Figure 3.4  | Dead (or stuck-at-o) output caused by a stuck-on $M_{n4}$               |    |

|             | transistor and stuck-at-X output caused by a stuck-off                  |    |

|             | $M_{p3}$ transistor                                                     | 44 |

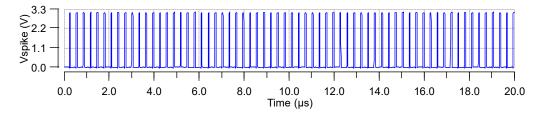

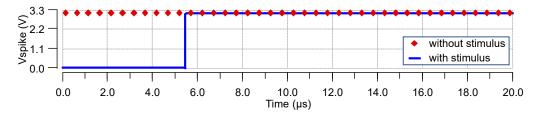

| Figure 3.5  | Stuck-at-1 output caused by a stuck-on $M_{n6}$ transistor              |    |

|             | (without requiring input stimulus) and by a stuck-off                   |    |

|             | $M_{n5}$ transistor (triggered with input stimulus)                     | 44 |

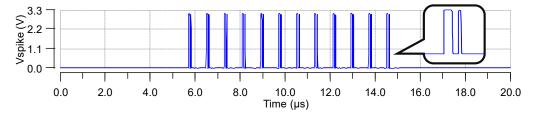

| Figure 3.6  | Output with ghost spikes caused by a stuck-off $M_{p4}$                 |    |

|             | transistor                                                              | 45 |

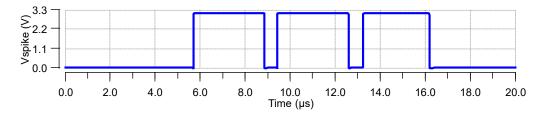

| Figure 3.7  | Long-duration spikes caused by a stuck-off $M_{p5}$ transistor.         | 45 |

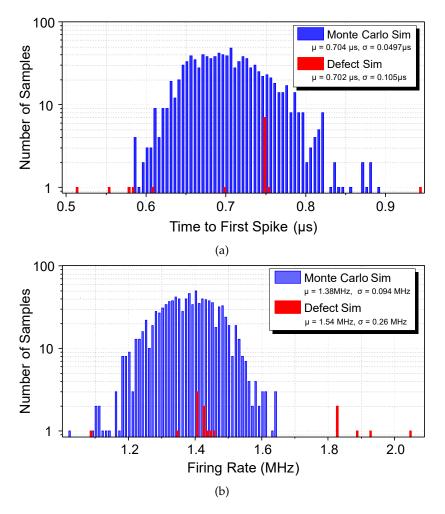

| Figure 3.8  | Histograms of timing variations.                                        | 47 |

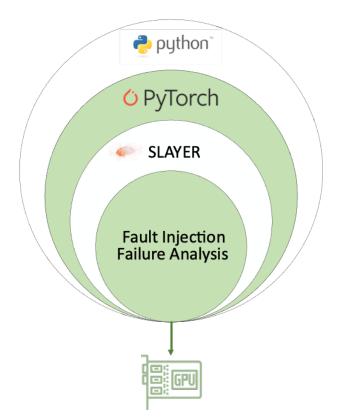

| Figure 4.1  | The fault injection framework built on top of the SLAYER                |    |

|             | and PyTorch frameworks accelerated on a GPU                             | 51 |

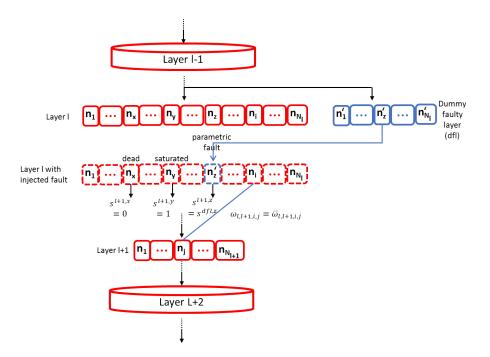

| Figure 4.2  | The fault injection methodology.                                        | 55 |

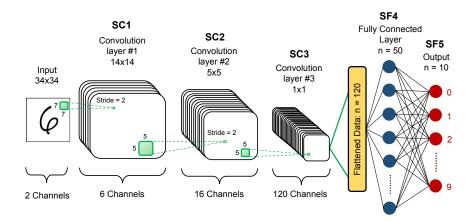

| Figure 4.3  | Architecture of the SNN for the N-MNIST dataset                         | 56 |

| Figure 4.4  | Architecture of the SNN for the IBM's DVS128 gesture                    |    |

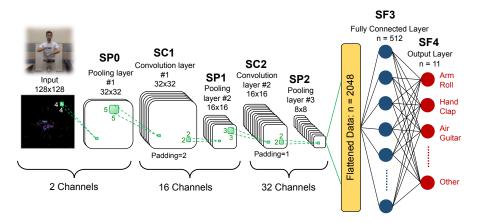

|             | dataset                                                                 | 57 |

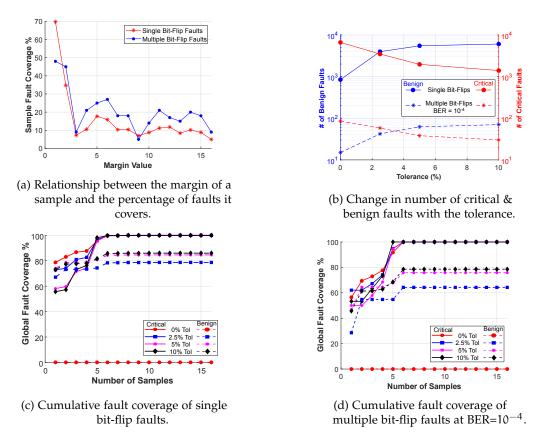

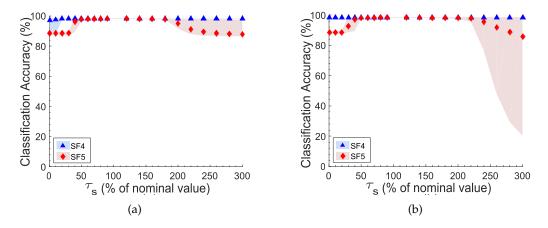

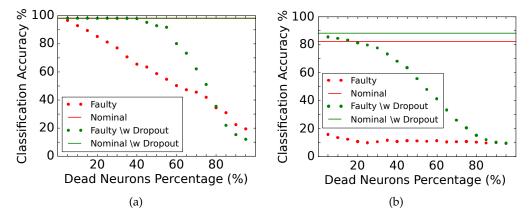

| Figure 4.5  | Effect of neuron faults on classification accuracy: (a) N-              |    |

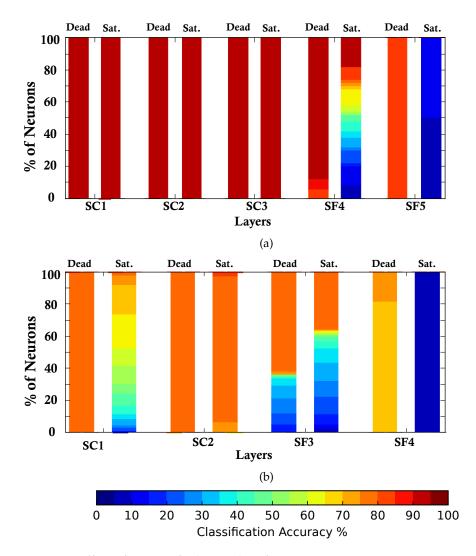

|             | MNIST SNN; (b) Gesture SNN                                              | 58 |

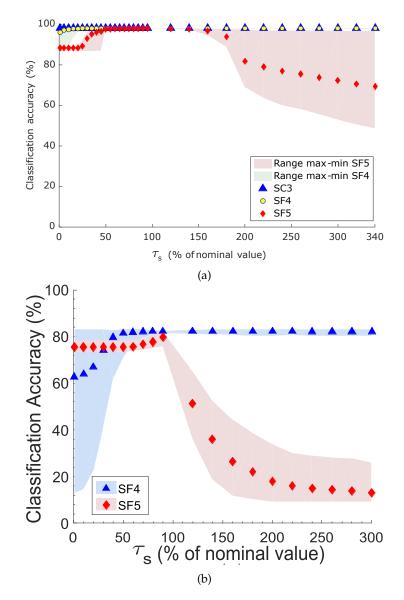

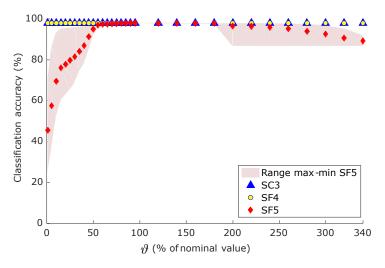

| Figure 4.6  | Effect of neuron timing variations: (a) N-MNIST SNN;                    |    |

|             | (b) Gesture SNN                                                         | 60 |

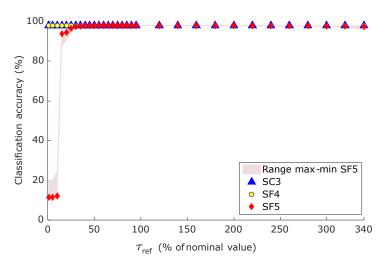

| Figure 4.7  | Effect of threshold perturbation faults on the N-MNIST SNN.                                                             | 61  |

|-------------|-------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.8  | Effect of refractory period faults on the N-MNIST SNN.                                                                  | 61  |

| Figure 4.9  | Effect of synapse faults on the classification accuracy of the N-MNIST SNN.                                             | 63  |

| Figure 4.10 | Effect of bit-flip synapse faults between SF3-SF4 for the gesture SNN                                                   | 64  |

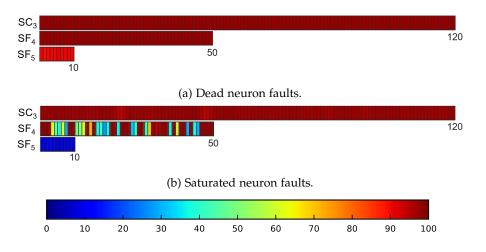

| Figure 4.11 | Classification accuracy drop as a function of fault density.<br>Only dead and saturated faults in layers SC3 and SF4 of | Ċ   |

|             | the N-MNIST SNN are considered                                                                                          | 66  |

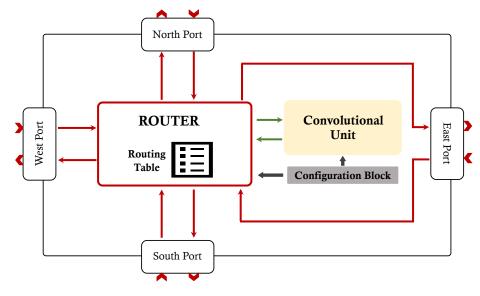

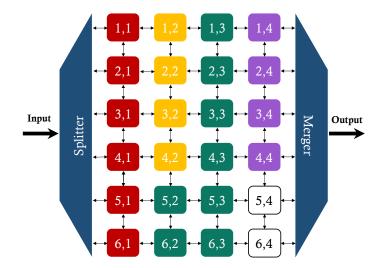

| Figure 5.1  | The convolutional node                                                                                                  | 68  |

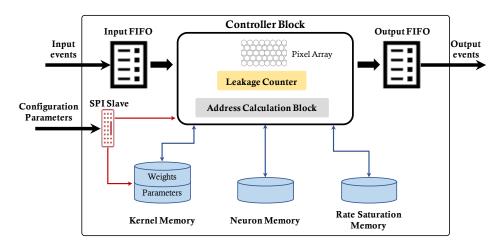

| Figure 5.2  | The convolutional unit                                                                                                  | 69  |

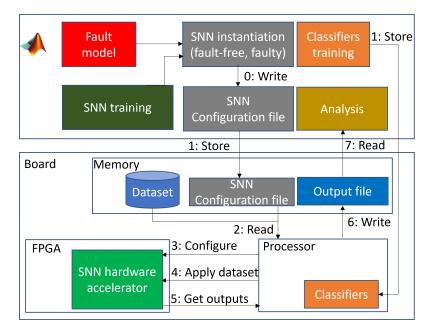

| Figure 5.3  | Embedded neuromorphic hardware accelerator platform.                                                                    | 71  |

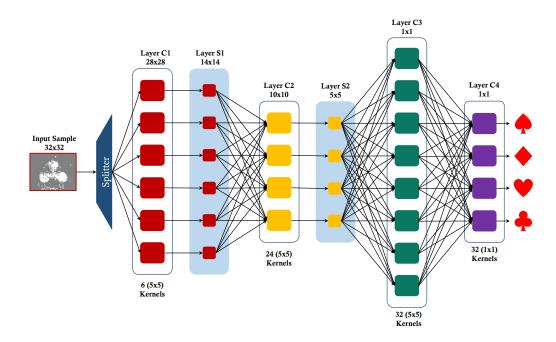

| Figure 6.1  | Convolutional SNN for poker card symbol recognition                                                                     | 76  |

| Figure 6.2  | 2-D mesh SNN implementation on the FPGA                                                                                 | 77  |

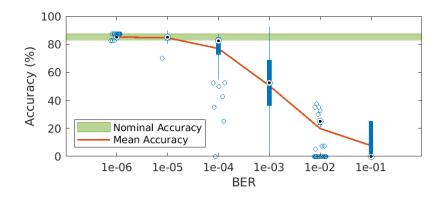

| Figure 6.3  | Network accuracy for different BER values                                                                               | 78  |

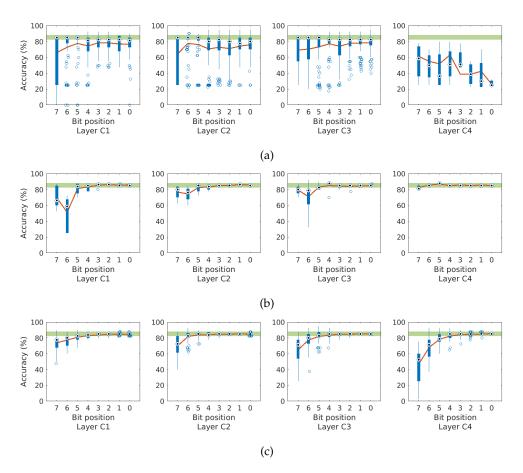

| Figure 6.4  | Single bit-flips layer-by-layer: (a) Router Parameters; (b)                                                             |     |

|             | Neuron Threshold; (c) Kernel Weights                                                                                    | 79  |

| Figure 6.5  | Multiple bit-flips for different BER values layer-by-layer:                                                             |     |

|             | (a) Neuron Parameters; (b) Kernel Weights                                                                               | 80  |

| Figure 7.1  | Functional test generation. The street images are from                                                                  |     |

|             | [136]. The chip image is from [113]                                                                                     | 84  |

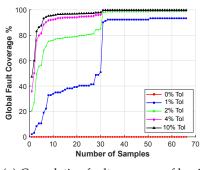

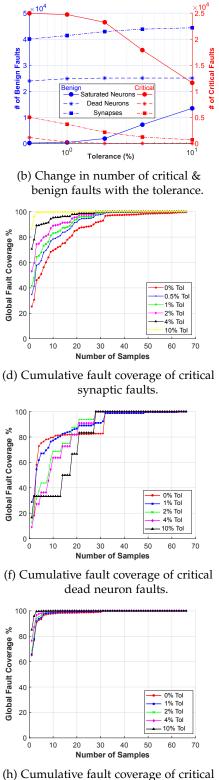

| Figure 7.2  | Effect of neuron faults on the classification accuracy of                                                               |     |

|             | the N-MNIST SNN                                                                                                         | 87  |

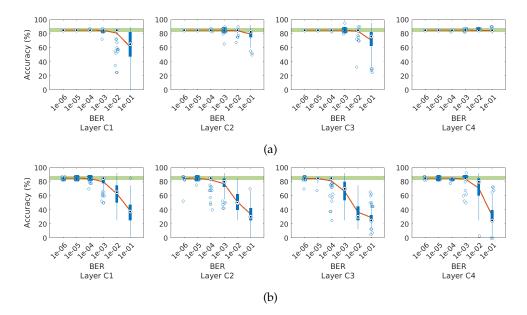

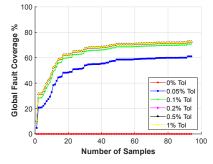

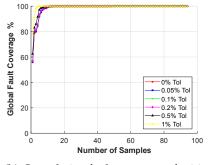

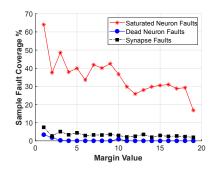

| Figure 7.3  | N-MNIST SNN                                                                                                             | 89  |

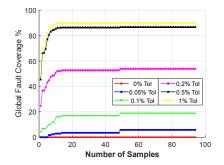

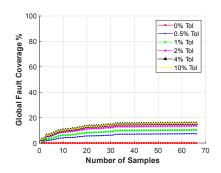

| Figure 7.4  | Gesture SNN                                                                                                             | 90  |

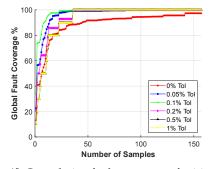

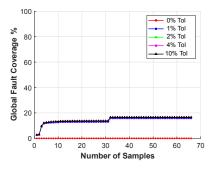

| Figure 7.5  | Poker card symbols SNN                                                                                                  | 91  |

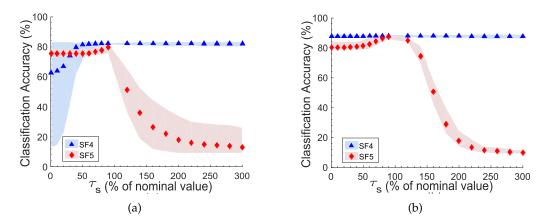

| Figure 8.1  | Effect of neuron faults on classification accuracy with and                                                             |     |

|             | without dropout: (a) N-MNIST SNN; (b) gesture SNN                                                                       | 100 |

| Figure 8.2  | Effect of neuron timing variations for the N-MNIST SNN:                                                                 |     |

|             | (a) without dropout; (b) with dropout                                                                                   | 101 |

| Figure 8.3  | Effect of neuron timing variations for the gesture SNN:                                                                 |     |

|             | (a) without dropout; (b) with dropout                                                                                   | 101 |

| Figure 8.4  | Offline self-test scheme.                                                                                               | 102 |

| Figure 8.5  | Online self-test scheme                                                                                                 | 103 |

| Figure 8.6  | I&F neuron design showing the recovery operation at                                                                     |     |

|             | neuron-level                                                                                                            | 104 |

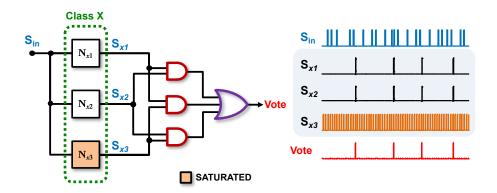

| Figure 8.7  | TMR at the output layer                                                                                                 | 105 |

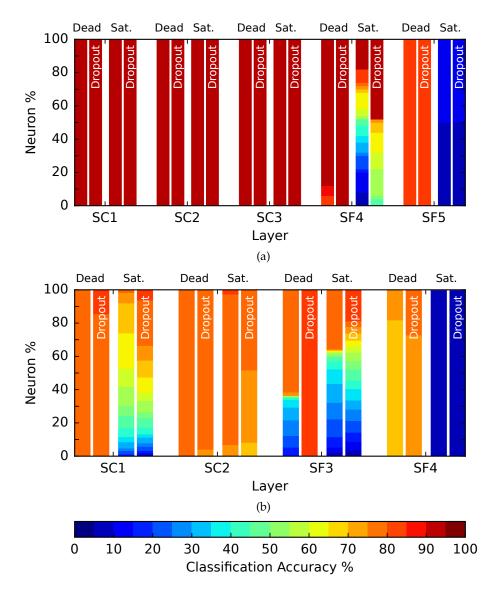

| Figure 8.8  | Fault tolerance for multiple fault scenarios: (a) N-MNIST                                                               |     |

|             | SNN; (b) gesture SNN                                                                                                    | 105 |

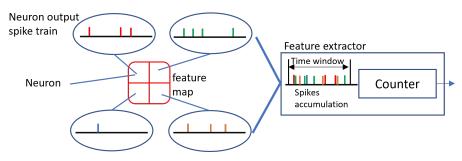

| Figure 9.1  | Principle of operation.                                                                                                 | 109 |

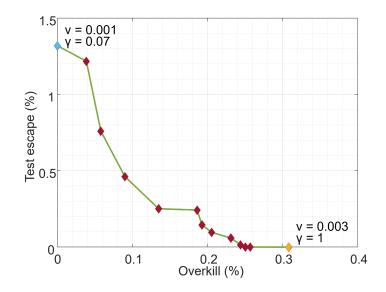

| Figure 9.2  | Pareto front curve test escape vs. overkill for SVM trained                                                             |     |

|             | with different pairs of hyper-parameter values $\nu$ and $\gamma.$ .                                                    | 112 |

| Figure 9.3  | Performance of system with two SVM                                                                                      | 113 |

# LIST OF TABLES

| Table 2.1 | Main characteristics of four large neuromorphic platforms |    |

|-----------|-----------------------------------------------------------|----|

|           | [27]                                                      | 34 |

| Table 2.2 | Comparison of features between conventional ANNs and      |    |

|           | SNNs [72]                                                 | 37 |

| Table 3.1 | Catastrophic faulty behaviors resulting from defect simu- |    |

|           | lation                                                    | 46 |

| Table 7.1 | Number of samples needed to reach the maximum fault       |    |

|           | coverage for different fault types at different tolerance |    |

|           | values.                                                   | 93 |

|           |                                                           |    |

## ACRONYMS

- AER Address Event Representation

- AI Artificial Intelligence

- ANN Artificial Neural Network

- ASIC Application Specific Integrated Circuit

- BER Bit-Error Rate

- BIST Built-In Self-Test

- CMOS Complementary Metal-Oxide-Semiconductor

- CNN Convolutional Neural Network

- CPU Central Processing Unit

- DfT Design-for-Test

- DNN Deep Neural Network

- DVS Dynamic Vision Sensor

- ECC Error Correction Code

- FAM Fault-Aware Mapping

- FATM Fault-Aware Training and Mapping

- FIFO First-In-First-Out

- FPGA Field Programmable Gate Array

- GPU Graphics Processing Unit

- I&F Integrate-and-Fire

- IC Integrated Circuit

- I/O Input/Output

- IoT Internet-of-Things

- IP Intellectual Property

- LSB Least Significant Bit

- MAC Multiply-and-Accumulate

- MBIST Memory Built-In Self-Test

- MC Monte Carlo

- ML Machine Learning

- MSB Most Significant Bit

- PDK Process Design Kit

- PE Process Element

- PPA Power-Performance-Area

- **RBF** Radial Basis Function

R-STDP Reward-modulated Spike-Timing-Dependent Plasticity

- SEU Single-Event Upset

- SLAYER Spike LAYer Error Reassignment

- SNN Spiking Neural Network

- SPI Serial Peripheral Interface

- SRM Spike Response Model

- STDP Spike-Timing-Dependent Plasticity

- STL Software Test Libraries

- SVM Support Vector Machine

- TMR Triple Modular Redundancy

- TPU Tensor Processing Unit

- VHDL Very High-Speed Integrated Circuit Hardware Description Language

- VLSI Very Large Scale Integration

# **1** INTRODUCTION

"Artificial Intelligence is the new electricity."

- Andrew Ng

The curiosity to explore, discover, and comprehend has been an integral part of human nature since the very beginning of its existence. It is nothing more than the desire deriving from deep within us to evolve; to go up; to reach further. And there is no better way to keep the hungriness of this unending desire fed than observation. Nature offers endless sources for inspiration, amongst which the most intriguing and challenging so far being the brain. That same thing defining our consciousness and logic, we use it in an effort to understand and replicate its own functionality in order to create a new form of intelligence, an artificial one.

And now that human evolution has eventually reached this point, new questions arise as we keep exploring the uncharted waters brought by Artificial Intelligence (AI) such as can we actually rely on it and trust it?

#### 2 INTRODUCTION

#### 1.1 ARTIFICIAL INTELLIGENCE: INDUSTRY V4.0

Human history has repeatedly shown that advancing is the cornerstone to a thriving society. Throughout evolution, humans have never seized to seek for improvements in all the aspects of their lives. A proof to this are the numerous breakthroughs whose outcome has contributed in redefining society in order for it to move forward.

Out of the plethora of technological advancements, there are three of them that left an enormous footprint on the shaping of the modern world. During less than three centuries, three revolutionary steps were taken and brought society into the future. Namely, the so-called *industrial revolutions* are composed of (i) the mechanization of production; (ii) the emergence of new sources of energy, i.e., electricity and fossil fuels; and (iii) nuclear energy.

What is arguably the forth component of the equation, is AI, although yet in its infant steps. With its full potential waiting to be unrolled, AI has met a rapid growth over the past years and can already find applications anywhere in almost any field, ranging from entertainment to medicine.

#### 1.1.1 The Chronology of Thinking Machines

Since the dawn of computers, a "thinking" machine has been many people's dream. Alan Turing was the first to substantially pioneer in the field of AI in the mid-20th century. During his public lecture in London in 1947, he referred to computer intelligence as a machine that can learn from experience and that the mechanism to achieve this is the possibility of letting the machine alter its own instructions. His later work was a source of inspiration to many researchers in the AI community.

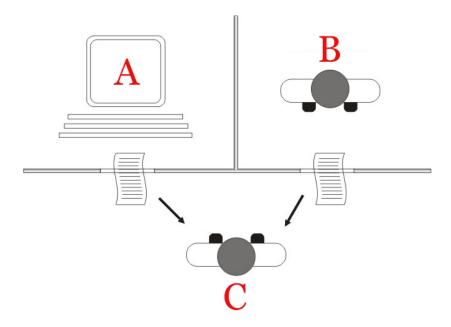

In 1950 Turing defined intelligence through his homonymous test [2], illustrated in Fig. 1.1. According to the Turing Test, or the Imitation Game as he named it, interrogators pose questions to a computer and a human and receive a written response. The goal is to determine which is the computer. The interrogators are free to ask anything as penetrating and wide-ranging as they like, while the computer is permitted to do anything possible to force a wrong identification. At the end of the experiment, if a sufficient proportion of the interrogators are not in position to differentiate the computer from the human being, then the computer is considered intelligent. Ever since there have been endless trials of AI algorithms to pass the Turing Test but none of them have yet actually succeeded.

The first successful AI programs were structured around mastering "mind sports", like chess and checkers, already from the 1950s [3]. Chess for example has always been a challenging game with clearly defined problems, allowing for reasoning and testing problem solving methods. A naive chess-playing computer would play by foreseeing all the available moves up to a depth that the game is over. However, this approach is practically impossible as this would involve examining an astronomically large number of moves. Therefore, developing a

Figure 1.1: The Turing Test. Player C, the interrogator, is given the task of trying to determine which player – A or B – is a computer and which is a human [1].

heuristic strategy for playing this kind of games would indeed require some intelligence to win. Having said that, chess does not make the best fit in the search of an intelligent system nowadays, since technology advanced and already in 1997 the reigning chess world champion, Garry Kasparov, was defeated by the Deep Blue computer of IBM, a massively parallel system with multiple levels of parallelism which could examine millions of possible moves per second and thus look ahead as many as 14 turns of play [4]. However, although fascinating, this cannot be considered an advancement in AI.

Another great milestone, which also shaped the modern form of AI, was in 1943 when the neurophysiologist Warren McCulloch and the mathematician Walter Pitts, published their work on *neural nets and automatons* [5]. According to it, each neuron in the brain is a simple digital processor and the brain as a whole is a form of computing machine. They proposed the "binary neuron" model, which, a decade later, was employed to bring the first Artificial Neural Network (ANN) to life by Belmont Farley and Wesley Clark [6]. Albeit limited by the early stage of the technology at the time, they managed to train a two-layer network consisting of 128 neurons to recognize simple patterns.

A few years later, Frank Rosenblatt's research on *percerptrons* [7], as he used to call neural networks, contributed to form the base of modern ANNs. More specifically, he aimed at generalizing the training procedure of neural networks, so that it could be applied to multi-layer networks, as well. The *back-propagating error correction*, or *back-propagation* as it is known today, is the most dominant training technique and is now in everyday use in the world of ANNs.

During the years that followed, the AI community never rested and contributions continued to arise in theoretical, philosophical, and applied levels. There was made progress on the domains of natural language processing and robotics,

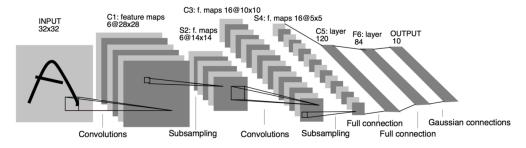

Figure 1.2: The architecture of LeNet-5 [8].

Figure 1.3: The architecture of AlexNet [10].

while also a lot of programming languages were designed and suited well the needs of AI applications, like LISP and PROLOG.

In the 1990s, a refreshing wind was blowing for AI that was about to drastically change it. Yann LeCun et al. created the LeNet network [9], one of the earliest Convolutional Neural Networks (CNNs), and promoted the development of deep learning. It was the first time that the back-propagation algorithm was applied on a practical application to recognize handwritten arithmetic digits. The final result of LeNet-5 was published in 1998 [8] and was shown to outperform all the other methods of handwritten character recognition in paper. Fig. 1.2 presents the architecture of LeNet-5. The success of this research was great making a big impact on the field of AI that initiated and inspired a wave of people to study neural networks.

LeNet was the starting point for a large number of neural network architectures that followed up. In 2012, AlexNet [10], a deep CNN shown in Fig. 1.3, was the winner of the ImageNet Large Scale Visual Recognition Challenge of that year with a clear difference over the runner-up. ImageNet is a huge dataset consisting of more than 14 million images containing objects of more than 20 thousand categories. The results showed that the depth of the model, i.e., the number of layers consisting it, was essential for its high performance, leading the way towards Deep Neural Networks (DNNs).

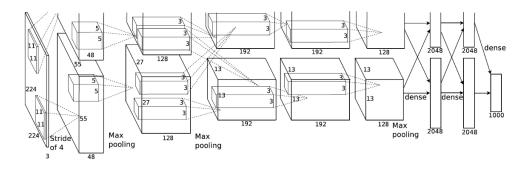

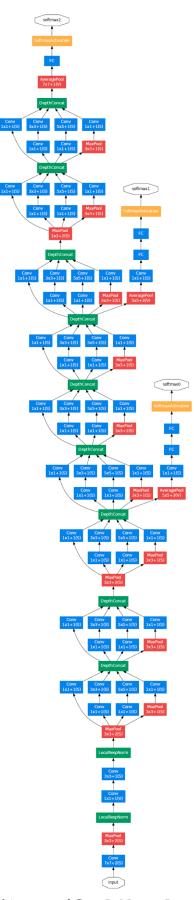

Nowadays, deep architectures have become the mainstream of neural networks with depths reaching hundreds of layers of various types, e.g., convolutional, dense, pooling, etc. Some examples of the most famous and widely-used DNN models include the VGGNet [12] and ResNet [13] variations, and the GoogLeNet,

Figure 1.4: The architecture of GoogLeNet, or Inception Network [11].

Figure 1.5: Timeline of AI winters.

or Inception Network [11], amongst many others just to name a few. However, deeper does not necessarily mean better. Thus, concurrently to the improvement of neural network architectures, machine learning techniques keep improving as well with more and more concepts being proposed constantly.

AI continues to emerge in very high speeds with more and more applications being adopted everywhere. A typical example is *ChatGPT*, an intelligent conversational agent that can answer followup questions, admit its mistakes, challenge incorrect premises, and reject inappropriate requests in a dialogue format. Since the application was released in November, 2022, and until the moment of writing this thesis, it has gained more than 100 million users in two months becoming the all-time fastest growing app.

It is evident that people rely more and more on AI which continues to grow and spreads in tremendous speed. The future of AI looks bright and we cannot but await to discover what lies within it. Just like every trend though, it must be treated with caution before it is ready to be used widely in a reliable way.

#### 1.1.2 The AI Winters & the Transition towards an AI Spring

It is common for emerging technologies to be surrounded by hype. Over-inflated promises by developers, unnaturally high expectations from end-users, and extensive promotion in the media [14] are the leading factors to cause a bubble. Soon the situation explodes and hype is replaced by pessimism in the community, which extends to the media, causing disappointment and criticism that result in funding cuts and people's interest moving away.

A similar situation happened with AI in the second half of the 20th century, which was described as the *AI winter* as an analogy to the nuclear winter. By taking a closer look at the timeline of AI (Fig. 1.5), we can distinguish two such major periods followed by a calmer post-AI winter that prepared the current *AI spring*.

#### 1.1.2.1 AI Winter I, 1973-1980

Already from the early 1970s, people have started questioning AI and its capabilities. The recent failure of AI research to effectively respond to community's expectations in domains such as robotics and natural language processing, led to a disappointment and abandonment of AI. Lighthill's report in 1973 [15] depicted these opinions in a rather pessimistic view of AI, causing funding cuts, the most severe of which being the British government's decision to end support for relevant research in most universities of the country. According to the report, AI researchers had failed to address the combinatorial explosion when solving problems within real-world domains. That is, the report states that AI techniques may work within the scope of small problem domains, but the techniques would not scale up well to solve more realistic problems.

#### 1.1.2.2 AI Winter II, 1988-1993

After the exaggeration of pessimism that caused the first AI winter, AI makes a come back with more enthusiasm in the community than ever. This is mainly attributed to the rise of *expert systems*, which were very rapidly adopted by corporations around the world in the early 1980s. In an effort to replace human experts, expert systems are computers emulating the human decision-making abilities [16]. They do so by reasoning through *knowledge bases* that represent facts and rules, mainly in an if–then structure, rather than through conventional procedural code.

Already by the first half of the decade, the use of expert systems was calculated to have saved tens of millions of dollars to the companies who employed them, causing more and more to start developing and deploying them. A new industry grew up to support expert systems, including both software and hardware companies, who built specialized computers optimized for the LISP programming language. Soon, the AI industry boomed from a few million dollars in 1980 to billions of dollars at the end of the decade [17].

Though, the extremely high cost and complicated architectures required by the expert systems led some companies to start seeking for alternative solutions. As a result, simpler and cheaper workstations appeared and LISP was soon adjusted in order to be portable to all UNIX systems allowing desktop computers to offer a simpler and more popular architecture to run LISP applications on. This in combination with the very expensive maintenance of expert systems made many companies to abandon the field, leading the billion-dollar AI industry to a new collapse. Once again, the hype of AI had taken over and was succeeded by disappointment.

#### 1.1.2.3 Post-AI Winter, 1994-2011

After the successive AI winters, the field kept moving forward with small but steady steps. AI found purpose as part of larger systems, assisting in sub-tasks necessary to carry out the overall operation. A lot of applications had silently embedded cutting edge - for the time - AI or other technologies that have developed from subdivisions of it, like fuzzy logic controllers that were used in automobiles.

The "cold" past of AI though is still haunting it and its reputation remains a midsummer night's dream. It is very often for the researchers in 1990s and

#### 8 INTRODUCTION

2000s to deliberately call their work by other names, such as cognitive systems, computational intelligence, etc., in order to avoid the stigma that was still present in the field. This was also an effort to emphasize that their work aimed at a particular sub-problem and not a global intelligent solution, as AI had already failed to reach these false promises of the past.

In general, during the post-winter period, AI did not stop to progress and was integrated in real-world applications, breaking down the myth that AI had failed. Computer scientists and companies may have avoided the term in an effort to seek for funding and not be viewed as dreamers but this let huge investments to take place at both state and private level, which by the end of the decade had reached again an amount of magnitude of billions in the USA and the European Union. People have also started to find again meaning in AI after the success of practical applications in fields like language translation and image recognition, which prove that AI can become a powerful tool.

#### 1.1.2.4 AI Spring, 2012-now

Already by the mid-2000s the scene of AI has started to heat up, getting ready for the upcoming "AI spring". Starting from 2012, the interest in the field of machine learning is substantially increased from both the research community and the corporate world, especially thanks to the revolution of deep learning. AI starts to develop more rapidly than ever establishing itself in general everyday-life applications, like language translation and search engines, as well as giving other sectors new aspects, like the car industry where the deployment of AI gave birth to the autonomous cars.

Although the advances occurred since the beginning of the AI spring seem to live the AI winter far behind in the past, concerns are still raised occasionally that a new winter could await due to overly ambitious or unrealistic promises given by scientists and commercial vendors. On the contrary, AI has strongly rooted in society and has found itself a purpose. Having said that, new hypes may arrive causing ups and downs in the interest to AI and its reputation, however, a collapse of the field seems now quite an impossible future for the technology. Of course, an "AI summer", where AI is deeply established in a way that people depend on it and is really intelligent, may still be very far away and the path towards it looks challenging and tough but at the same time it is more than fascinating to experience its true potentials being unfolded.

#### 1.1.3 Breathing New Life into AI

Reviewing the history of AI shows that its potential was understood very early. Besides, this is why it soon became a hype and over-enthusiasm was formed around it. But what were the reasons behind the failure of AI to fulfill people's expectations and in fact twice? There are many factors that played a major role and led to this but there are some that are attributed to the technology's immaturity and inefficacy to serve the needs of AI. Amongst them, the following two can be distinguished:

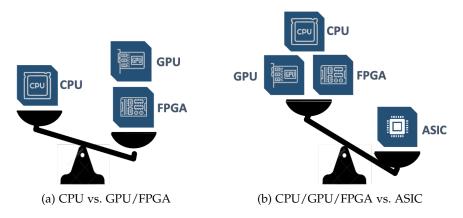

Figure 1.6: AI hardware accelerators comparison.

- insufficient computing capability;

- inadequately large data and wide access to it.

#### 1.1.3.1 AI Hardware Accelerators

The immense complexity that lies within the highly distributed processing of information required by AI algorithms, makes traditional computer hardware, such a Central Processing Unit (CPU), look totally powerless. It is true after all that fairly simple neural networks require significant computing capacity even by today's standards.

The AI community is forced to look for and employ other means that would allow for an effective realization of ANNs. In an effort to do so, a new purpose is given to an already used computer component, the Graphics Processing Unit (GPU). It is made obvious that if the parallelization characteristics of GPUs are exploited, then the processing of an ANN, and more particularly the training procedure, would be significantly accelerated.

AlexNet [10] proves this theory in practice and in great extend when the DNN utilizes a GPU to achieve the high performance that was a prerequisite because of the network's great depth. However, although AlexNet is considered the precursor of deep learning, it was not the first neural network to employ a GPU. Already since mid-2000s this technique has been applied [18]–[20] to speed up the calculations of ANNs, mainly CNNs, outperforming conventional processors.

There are many strong points of GPUs that make them are the perfect candidate for AI processing. One of them is their ability to access memory in a 2-D manner, i.e., row access and column access to memory take the same amount of time, even with very large matrices containing several thousand rows and columns [19]. Another advantage is that GPUs contain a huge amount of processing cores that allows for a very large scale of process distribution, which is also a common characteristic of ANNs where each neuron is a separate processing element and completely independent from the rest of the neurons in the same layer. In other words, the enormous matrix Multiply-and-Accumulate (MAC) operations needed for the calculation of a layer's activation, can be carried out in parallel if we exploit the full capabilities of GPUs. Despite their advantages, GPUs remain a general purpose processing unit. Therefore, a logical question that is raised in the effort to accelerate AI computations, is why not design a custom hardware architecture to perform the processing in the optimal way possible. The answer is simple and is no other than complexity of realization. As noted in [18] in 2005, using dedicated hardware to do machine learning typically ends up in disaster because of cost, obsolescence, and poor software.

A few years later this belief is reassessed as the maturation of Field Programmable Gate Arrays (FPGAs) during the 2010s transcends the aforementioned difficulties and makes dedicated AI hardware feasible in an elegant way. FPGAs soon begin to be used more and more often for AI acceleration until the problem of hosting the training and the inference of a DNN has become as simple as flushing a pre-designed hardware Intellectual Property (IP), many of which are offered as a publicly available open-source implementation.

FPGAs, as re-configurable devices, are by definition generic, so that their hardware components can be rearranged to implement a given circuit. This holds them back from fully leveraging the potentials of dedicated AI hardware. Considering also the advancements in Very Large Scale Integration (VLSI) Integrated Circuits (ICs), where integration has reached the scale of one-digit nanometer architectures, the way is paved for the implementation of Application Specific Integrated Circuit (ASIC) AI accelerators. The cost-energy-performance trade-off is increased over one magnitude with custom chip solutions, which is made evident by the relevant innovation proposed by leading companies and universities in the field in the late 2010s, such as Google's Tensor Processing Unit (TPU) [21], Apple's Neural Engine, and MIT's Eyeriss [22].

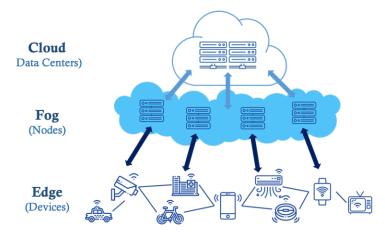

#### 1.1.3.2 AI at the Edge

Beyond speeding up training and inference on complex DNN models, there is also an incentive to design ASIC AI hardware accelerators that can fit inside the resource-constrained Internet-of-Things (IoT) edge devices. IoT is an example of edge computing, which is to push the computation, or specifically for AI the execution of AI algorithms, from the cloud closer to the user, i.e., to the edge.

AI at the edge holds so much promise because it can be applied to practically any electronic device, from self-driving cars that see pedestrians in the road to coffee makers that respond to voice commands. Motivated by concerns of availability, privacy, latency, network bandwidth, low power, and low cost, applications that require any combination of the above will eventually migrate to AI inference at the edge.

Opposed to the mainstream approach that wants AI to run in the cloud on giant server farms of GPUs and FPGAs, or clusters of them, the key point of AI at the edge is that all the processing is restricted locally to the hosting device, which allows for plenty of improvements. The most important of them are listed below:

Figure 1.7: The edge computing infrastructure.

- *Availability*: The system is continuously available since no external factor, such as an internet connection interruption, can affect it and therefore undermine its operation.

- *Privacy & Security*: Sensitive data are persisted at a local level and thus they do not have to be sent over the internet, ensuring the privacy and enhancing the security of the application.

- *Speed*: The overall application time is shorter as there is no need to wait for the data to be sent in the cloud and then receive back the results, resulting in low latency.

- *Bandwidth*: The off-line processing does not occupy any bandwidth, allowing this way for more devices to be simultaneously connected.

- *Energy consumption*: A significant amount of energy is saved after reducing the power-hungry data transfers that are needed.

The large and power-hungry GPUs and FPGAs are the worst match for the small battery-powered IoT devices. On the contrary, ASICs can become very small and achieve very low energy consumption, which makes them the ideal choice if the aforementioned advantages are to be achieved.

#### 1.1.3.3 Big Data

The bloom of the digital era, brought new perspectives for AI into light. The information storage switched from analog to digital, with the latter growing exponentially in capacity, which by the end of 2000s had almost completely dominated the global market. Not only this but the generated data met an exponential growth as well. As of 2012, 2.5 exabytes ( $2.5 \times 2^{60}$  bytes) of data were generated daily. This number continued only to grow, and as the International Data Group (IDC) reported, the global data volume grew from 4.4 zettabytes ( $4.4 \times 2^{70}$  bytes) to ten times higher between 2013 and 2020. By 2025, IDC predicts that there will be 163 zettabytes of data around the world. This explosion

is mainly a result of data collected by devices such as mobile phones and information-sensing devices, which already count tens of billions worldwide, far outnumbering the human population of the earth.

Of course the size of the data alone is of no importance. What differentiates the *big data* is a combination of characteristics, or the "5 Vs":

- *Volume*: The quantity of generated and stored data. It determines the value and potential insight.

- *Variety*: The type and nature of the data, i.e., structured, semi-structured, unstructured.

- Velocity: The speed at which the data is generated and processed.

- *Veracity*: The truthfulness or reliability of the data, which refers to the data quality and the data value [23].

- *Value*: The worth in information that can be achieved by the processing and analysis of large datasets.

Big data is comprised by data sets that are too large and complex to be dealt with traditional software tools within a tolerable elapsed time. The insights embedded in such data sets, that are diverse, complex, and of a massive scale, can become a source of knowledge if extracted properly. A technique that helped in this is machine learning.

It is no coincidence the fact that the first large data sets, like the ImageNet, begin to pop up from the late 2000s. It was not until then that the digital world was ready enough to qualitatively capture, widely distribute, and efficiently process big data. The great statistical power offered by the huge number of fields (rows) of big data sets, enabled DNN architectures to be trained efficiently, leaving behind problems caused by inadequate data sets, like *over-fitting*. In fact, it would never have been possible for deep architectures to work without setting their depth according to the size of data from which they extract information.

#### 1.1.4 Neuromorphic Engineering: An Artificial Brain?

It has always been a challenge for technology the way in which animal brains engage with their world effortlessly. Despite the technological advancements in computer science, electronics, machine learning, and other relevant fields, a system with skills comparable to those of the simplest intelligent being still seems unreachable. It is true that brains far outperform computers across a wide spectrum of tasks, particularly from the aspect of power consumption. A bee, for instance, demonstrates remarkable navigational and social capabilities at the same time that searches for nectar, and all this is the result of the power of less than a million neurons, burning less than a milliwatt. This performance is many orders of magnitude more task-competent and power-efficient than current neuronal simulations or autonomous robots [24].

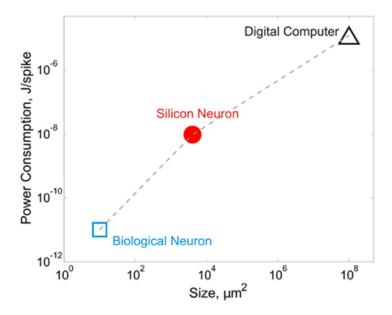

Figure 1.8: Comparison of power-area performance among biological neurons, silicon neurons, and digital computers [29].

In an attempt to mimic the operation of neural computing systems, neuromorphic engineering was introduced by Carver Mead in the late 1980s [25]. Neuromorphic engineering studies the use of electronic neural networks whose architectures and operations are based on those of biological nervous systems [26] and, unlike in the classic von Neumann architectures, the computational load is distributed among a multitude of artificial neurons.

Similar to biological cognitive systems, a real-time response is a fundamental requirement in neuromorphic engineering. Even with the current supercomputers though, simulating a large network of a neurobiological system is unrealistic in terms of time [27]. For example, a 2009 "cat-scale" neural simulation of 1 billion neurons and 10 trillion synaptic connections ran 700 times slower than real time, while burning about 2 megawatts [28]. Hence, the inefficiency of digital computers to compete with neurobiological systems, led to the advent of analog VLSI implementations of silicon neurons. As shown in Fig. 1.8, the power-area performance of silicon neurons lies between this of biological neurons and digital computers [29].

In his original contribution to the evolution of neuromorphic engineering, Mead emphasized that the physics of neural computation remain analog, rather than digital. Thus, instead of operating the transistors as on-off switches, he exploited their analog properties when operating in the sub-threshold region. This way, Complementary Metal-Oxide-Semiconductor (CMOS) transistors consume only a low level of power and also their output current vs. input voltage characteristic is similar to the sigmoid input-output characteristic of the neuronal ion channels [29].

Today's neuromorphic ICs include various digital and mixed-signal designs, too, rather than purely analog ones as in the beginning of neuromorphic engineering. Some of the most famous chips include IBM's TrueNorth [30], Intel's

Loihi [31], and ETH's ROLLS neuromorphic processor [32]. These chips offer compact designs that incorporate large numbers of neurons and synapses to implement Spiking Neural Networks (SNNs) with a very low power consumption. For example, TrueNorth offers up to 1 million neurons and 256 million synapses with a power density of  $20mW/cm^2$ . However, their user base still consists mostly of universities and industrial research groups [33]. It is also worth mentioning SpiNNaker [34], a massively parallel, multi-processor architecture for modeling and simulating large-scale SNNs.

Although many improvements are offered by neuromorphic engineering, it is not yet as mature as the AI hardware accelerators for conventional ANNs. Before industry is ready to adopt neuromorphic technology and employ it in the field, many obstacles would have to be overcome. That involves progress in the field of SNNs as well as the capture of data in neuromorphic, or spiking form. The specific advantages of SNNs, along with the challenges they face, will be further discussed in Chapter 2. The one thing that is for sure though is that the arrival of an *artificial brain* is not foreseen in the close future.

#### 1.2 CRITICALITY OF AI APPLICATIONS