## Optimization and Acceleration of HEVC and VVC Video Compression Standards Using Artificial Intelligence on Parallel Processing Platforms.

Soulef Bouaafia

### ► To cite this version:

Soulef Bouaafia. Optimization and Acceleration of HEVC and VVC Video Compression Standards Using Artificial Intelligence on Parallel Processing Platforms.. Computer Science [cs]. FSM, 2021. English. NNT: . tel-04098015

## HAL Id: tel-04098015 https://hal.science/tel-04098015v1

Submitted on 15 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

RÉPUBLIQUE TUNISIENNE MINISTÈRE DE L'ENSEIGNEMENT SUPÉERIEUR ET DE LA RECHERCHE SCIENTIFIQUE UNIVERSITÉ DE MONASTIR FACULTÉ DES SCIENCES DE MONASTIR

Ecole Doctorale : Matériaux, Dispositifs et Microsystèmes (EDMD)

## THÈSE

Présentée pour l'obtention du diplôme de

### DOCTORAT DE L'UNIVERSITÉ DE MONASTIR

Faculté des Sciences de Monastir

Spécialité : ÉLECTRONIQUE ET MICROÉLECTRONIQUE

Présentée par:

## Soulef BOUAAFIA

Sujet:

Optimisation et Accélération des Normes de Compression Vidéo HEVC et VVC utilisant l'Intelligence Artificielle sur des Plateformes de Traitement Parallèle.

Optimization and Acceleration of HEVC and VVC Video Compression Standards Using Artificial Intelligence on Parallel Processing Platforms.

Directeur de thèse : Fatma Ezahra SAYADI

Soutenue le 05/11/2021 devant la Commission d'Examen composée de :

| M. Nejib HASSEN          | Professeur, ISIMM              | Président          |

|--------------------------|--------------------------------|--------------------|

| M. Ali DOUIK             | Professeur, ENISO              | Rapporteur         |

| M. Khaled BEN KHALIFA    | Maître de conférences, ISSATSO | Rapporteur         |

| M. Chokri SOUANI         | Professeur, ISSATSO            | Examinateur        |

| Mme. Fatma Ezahra SAYADI | Maître de conférences, ENISO   | Directeur de Thèse |

Laboratoire d'Électronique et Microélectronique (Code: LR99ES30)

## Acknowledgments

First, I would like to witness my gratitude to Almighty God, who gave me the courage and strength to pursue this thesis and opened the gates of knowledge for me.

I have started my final internship project for my master's degree in Electronics and Microelectronics Lab Research  $E\mu E$ . It was March 2017. I never thought this training would be the reason for choosing me to pursue a long and fruitful Ph.D. journey full of fluctuations (The 1<sup>st</sup> registration was on January 23, 2019). What's for sure is that I will never forget this opportunity which was wonderful, overwhelming, and full of lessons and responsibilities. Thankfully, my Ph.D. was completed successfully in which we delivered many journals and international conferences. This wouldn't have happened without the help and support of countless people over the past three years.

First of all, I am deeply grateful to my supervisors Mrs. Fatma Ezahra SAYADI and Mrs. Randa KHEMIRI who gave me this opportunity and believed in me from the very beginning. Knowing that this Ph.D. experience wasn't always easy, it was always a pleasure, with a lot of excitement, to be up to the challenge and to beat paper deadlines. Working with you improved me a lot as a student, as a researcher, and as a person. It wasn't straightforward for me to understand how to think like a researcher. You have taught me, both consciously and unconsciously, how good work is done. I appreciate all your contributions of time and ideas to make my Ph.D. experience productive. You have always listened to my ideas and discussions with you frequently led to progress. Your ability to approach research problems and your high scientific standards set an example. I admire your ability to balance research interests and personal pursuits. I am thankful for the excellent example you have provided me as a successful and ambitious researcher.

I would first of all like to thank the members of the jury for their presence, for their careful reading of my thesis as well as for the remarks they will address to me during

this defense in order to improve my work. I thank Professors Ali DOUIK and Khaled BEN KHALIFA for finding the time to read my thesis and for their valuable feedback. I would like to thank Professor Chokri SOUANI for being examinator of this jury. And finally, I would like to thank Professor Nejib HASSEN for the honor he gave me when he agreed to chair this jury.

I would like to thank all  $E\mu E$  laboratory members, especially the Lab head **Pr**. Mohsen MACHHOUT and **Pr**. Mohamed ATRI for their advice and their human qualities of listening and understanding.

This work would never be completed without the support of my family. Words cannot describe my gratitude for my parents, my brothers, and my sisters. Without them, I could never have reached this current level of success. To all of you, thank you for your continuous encouragements and devotion.

I would like to give special thanks to my friend **Dr. Seifeddine MESSAOUD** who have always encouraged me.

Soulef BOUAAFIA

.....

## Abstract

ideo contents visualization has been revolutionized over the last decade with the advent of video-on-demand services, web-TV, video-sharing sites, live streaming service for individuals, and broadcast platforms offered by social networks. This led to an explosion of internet traffic. According to a recent Cisco study, video-driven internet traffic will quadruple between 2017 and 2022 and will represent 82% of overall internet traffic. The appearance of new video content, such as  $360^{\circ}$  video, Virtual Reality (VR), High Frame Rate (HFR) and the advent of very high spatial resolution 8K or even 16K leads to a significant increase in the amount of data to be transmitted. Consequently, efficient compression is essential to store or transmit this huge amount of data. Despite the considerable performance achieved by the video coding standards, the existing compression techniques showed their limitations and it is becoming increasingly difficult to meet the growing demands of data. Therefore, the adoption of new approaches such as machine learning based methods has great potential to address this challenge and can provide very promising results. The objective of this thesis is to introduce advanced techniques to significantly reduce the complexity of the High Efficiency Video Coding (HEVC) and the Versatile Video Coding (VVC) standards, while preserving the bitrate gain and ensuring a better video quality for users. These techniques, based on machine learning provide better performance in classification, in prediction and in efficient compression vs classical algorithms.

## Résumé

a visualisation de contenus vidéo a été révolutionnée au cours de la dernière décennie avec l'apparition des services de vidéo à la demande, de web-TV, de sites de partage de vidéos, de service de diffusion en direct pour les particuliers, et des plateformes de diffusion offertes par les reseaux sociaux. Ceci a conduit à une explosion du trafic internet. Selon une étude récente de Cisco, le trafic internet lié à la vidéo quadruplera entre 2017 et 2022 et représentera 82% du trafic internet global. L'apparition de nouveaux contenus vidéo, tels que la vidéo 360°, la Réalité Virtuelle (VR), le High Frame Rate (HFR) et l'avènement de très grandes résolutions spatiale 8K voire 16K conduit à une augmentation significative de la quantité de données à transmettre. Par conséquent, une compression efficace est essentielle pour stocker ou transmettre cette énorme quantité de données. Malgré les performances considérables obtenues par les normes de codage vidéo, les techniques de compression existantes ont montré leurs limites et il devient de plus en plus difficile de répondre aux demandes croissantes de données. Par conséquent, l'adoption de nouvelles approches telles que les méthodes d'apprentissage automatique représente un grand potentiel pour relever ce défi et peut fournir des résultats très prometteurs. L'objectif de cette thèse est d'introduire des techniques avancées pour réduire significativement la complexité des normes de codage vidéo High Efficiency Video Coding (HEVC) et Versatile Video Coding (VVC) tout en préservant le gain en débit et assurant une meilleure qualité de vidéo aux utilisateurs. Ces techniques basées sur l'apprentissage automatique offrent de meilleures performances en classification, en prédiction et en efficacité de compression par rapport aux algorithmes classiques.

# Table of Contents

| A                    | ckno  | wledgr       | nents                                        | i        |

|----------------------|-------|--------------|----------------------------------------------|----------|

| A                    | bstra | act          |                                              | v        |

| R                    | ésum  | ıé           | ×                                            | vi       |

| Ta                   | able  | of Con       | v v                                          | ii       |

| Li                   | st of | Figur        | es                                           | x        |

| Li                   | st of | <b>Table</b> | s x                                          | ii       |

| Li                   | st of | Abbr         | evations x                                   | ii       |

| General Introduction |       | oduction xv  | 7 <b>i</b>                                   |          |

| I                    | Vid   | leo Co       | ding and Artificial Intelligence Backgrounds | 1        |

|                      | I.1   | Introd       | luction                                      | 2        |

|                      | I.2   | Video        | Compression History                          | <b>2</b> |

|                      | I.3   | HEVO         | C Standard                                   | 4        |

|                      |       | I.3.1        | Sampled Representation of Pictures           | <b>5</b> |

|                      |       | I.3.2        | Block Partitioning in the HEVC Standard      | <b>5</b> |

|                      |       | I.3.3        | Intra Prediction                             | 6        |

|                      |       | I.3.4        | Inter Prediction                             | 7        |

|                      |       | I.3.5        | Transform and Quantization                   | 8        |

|                      |       | I.3.6        | Entropy Coding                               | 9        |

|                      |       | I.3.7        | In-Loop Filters                              | 9        |

|                      | I.4   | VVC          | Standard                                     | 9        |

|                      |       | I.4.1        | Block Partitioning in the VVC Standard       | 0        |

|                      |       | I.4.2        | Intra Prediction                             | 1        |

|                      |       | I.4.3        | Inter Prediction                             | 2        |

|                      |       | I.4.4        | Transform and Quantization                   | 3        |

|    |       | I.4.5   | Entropy Coding                                            | 13        |

|----|-------|---------|-----------------------------------------------------------|-----------|

|    |       | I.4.6   | In-Loop Filters                                           | 13        |

|    | I.5   | Video   | Coding Challenges                                         | 14        |

|    | I.6   | Artific | ial Intelligence: New Advancements and Innovations        | 15        |

|    |       | I.6.1   | Machine Learning                                          | 16        |

|    |       | I.6.2   | Deep Learning                                             | 18        |

|    |       |         | I.6.2.1 Convoluional Layer                                | 19        |

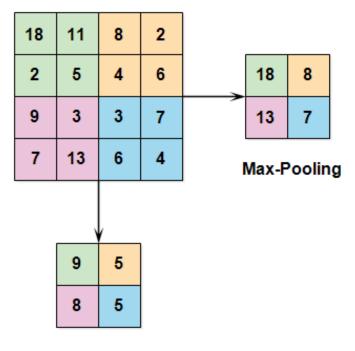

|    |       |         | I.6.2.2 Pooling Layer                                     | 20        |

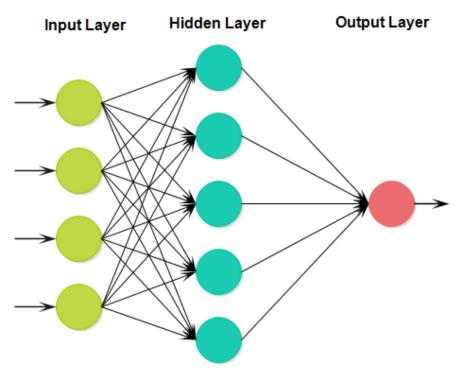

|    |       |         | I.6.2.3 Fully Connected Layer                             | 20        |

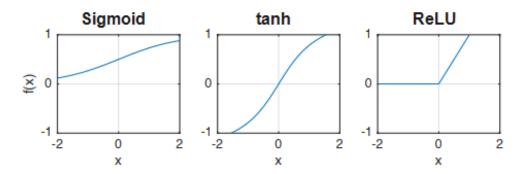

|    |       |         | I.6.2.4 Activation Functions                              | 21        |

|    |       |         | I.6.2.5 Backpropagation Algorithm                         | 22        |

|    | I.7   | Relate  | d Research                                                | 23        |

|    |       | I.7.1   | Heuristic Methods                                         | 23        |

|    |       | I.7.2   | Learning Methods                                          | 23        |

|    | I.8   | Conclu  | usion                                                     | 24        |

| п  | Mac   | hine l  | Learning Approach-based Fast CU Partition for Reducing    |           |

|    | HE    | VC Co   | mplexity                                                  | <b>26</b> |

|    | II.1  | Introd  | uction                                                    | 27        |

|    | II.2  | CU Pa   | rtition Structure                                         | 27        |

|    | II.3  | Propos  | sed CU Partition based on Machine Learning                | 29        |

|    |       | II.3.1  | CU Partition based on SVM                                 | 29        |

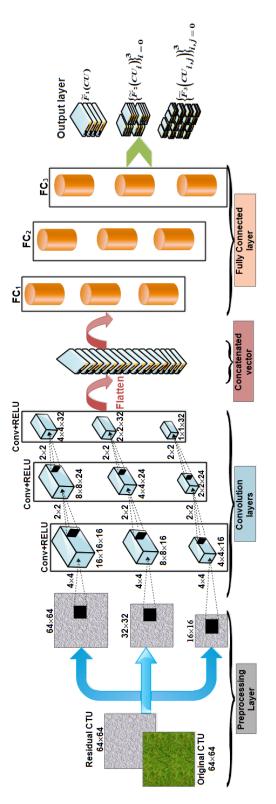

|    |       | II.3.2  | CU Partition based on Deep CNN                            | 32        |

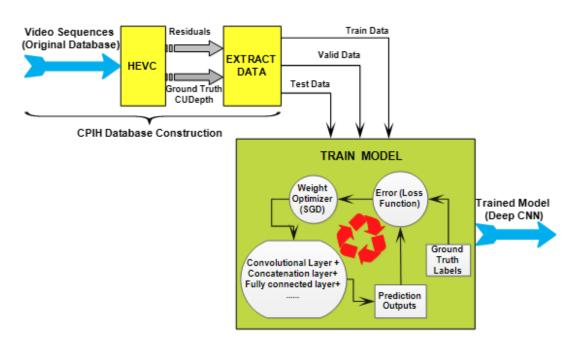

|    |       | II.3.3  | Training Phase                                            | 34        |

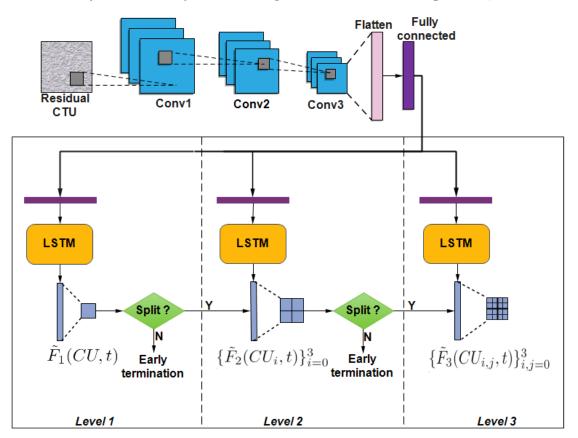

|    |       | II.3.4  | CU Partition based on Deep CNN-LSTM                       | 37        |

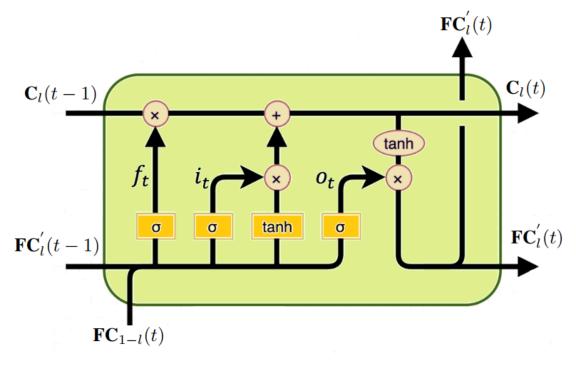

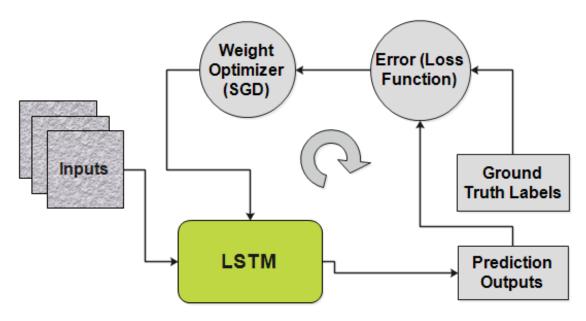

|    |       | II.3.5  | Training Phase                                            | 39        |

|    | II.4  | Experi  | imental Results                                           | 41        |

|    |       | II.4.1  | Experimental Settings                                     | 41        |

|    |       | II.4.2  | Performance Metrics                                       | 42        |

|    |       | II.4.3  | Performance Evaluation with Online SVM and Deep CNN       | 42        |

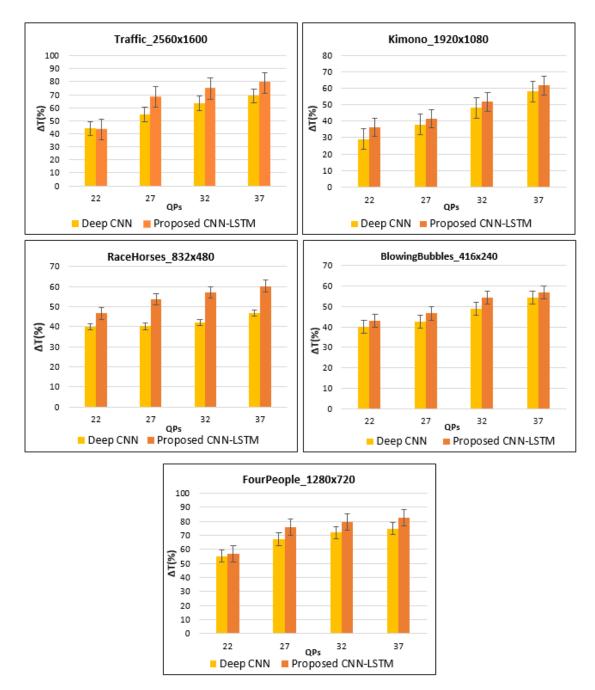

|    |       | II.4.4  | Performance Evaluation with Deep CNN and CNN-LSTM         | 44        |

|    |       | II.4.5  | Comparative Study                                         | 46        |

|    | II.5  | Conclu  | usion                                                     | 49        |

| II | [Dee  | p Lear  | ning based Video Quality Enhancement for the New Versa-   |           |

|    | tile  | Video   | Coding                                                    | <b>50</b> |

|    | III.1 | Introd  | uction                                                    | 51        |

|    | III.2 | Backg   | round                                                     | 51        |

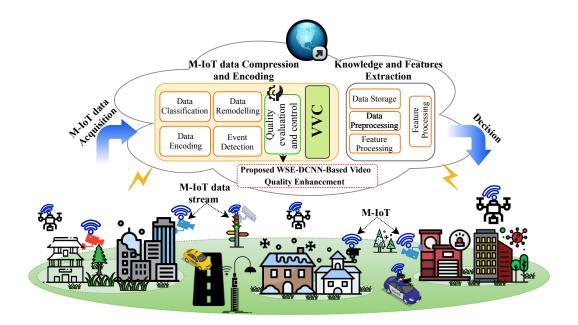

|    | III.3 | Propos  | sed M-IoT Scenario-based Architecture for Multimedia Data | 54        |

|    | III.4 | Propos  | sed Method                                                | 56        |

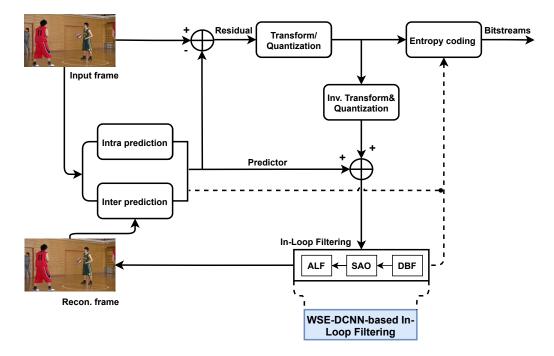

|    |       | III.4.1 | Proposed WSE-DCNN-based In-Loop Filtering For VVC         | 56        |

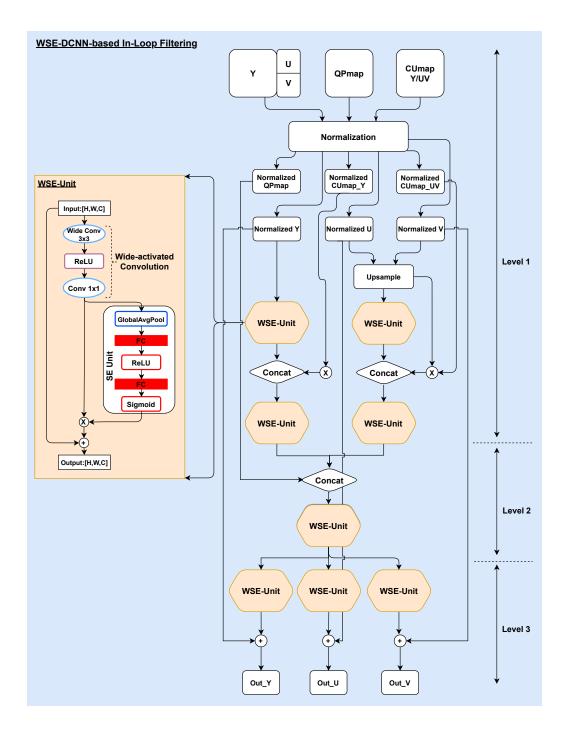

|         | III.4.2 WSE-DCNN Architecture                             | 57 |

|---------|-----------------------------------------------------------|----|

| III.5   | Experimental Results                                      |    |

|         |                                                           | 61 |

|         |                                                           | 63 |

|         |                                                           | 65 |

|         |                                                           | 69 |

| III.6   | Conclusion Conclusion                                     | 72 |

| IV Dee  | p CNN Co-Design for HEVC CU Partition Prediction on FPGA- |    |

| SoC     | •                                                         | 73 |

| IV.1    | Introduction                                              | 73 |

| IV.2    | Background                                                | 74 |

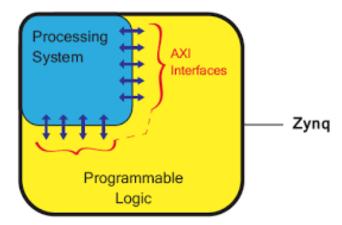

|         | IV.2.1 FPGA-SoC                                           | 74 |

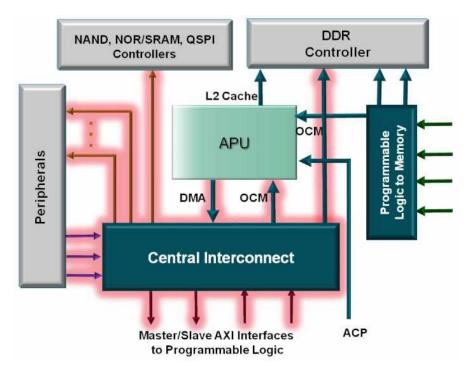

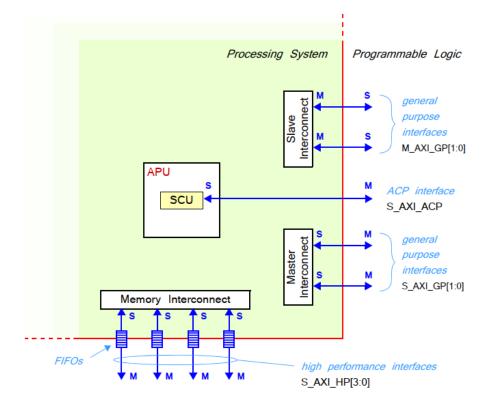

|         | IV.2.1.1 Processing System (PS)                           | 75 |

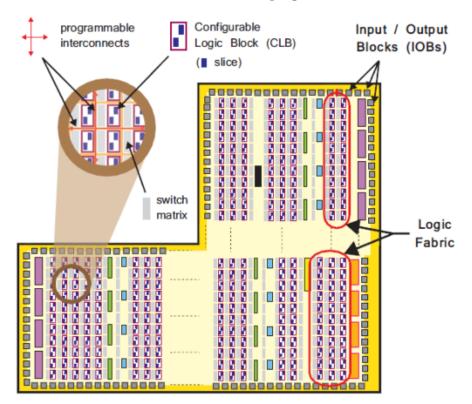

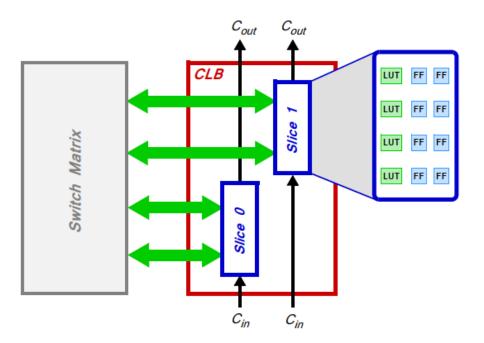

|         | IV.2.1.2 Programmable Logic (PL)                          | 76 |

|         | IV.2.1.3 PS—PL Interfaces                                 | 78 |

|         | IV.2.2 Direct Memory Access (AXI DMA)                     | 79 |

|         | IV.2.3 FPGA-SoC: PYNQ-Z1                                  | 80 |

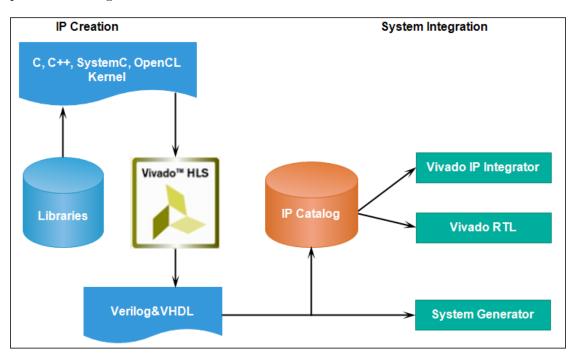

|         | IV.2.4 High Level Synthesis (HLS)                         | 80 |

| IV.3    | Proposed CNN Accelerator on FPGA-SoC                      | 80 |

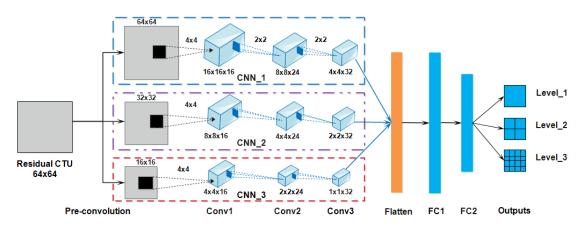

|         | IV.3.1 Proposed Deep CNN Architecture                     | 81 |

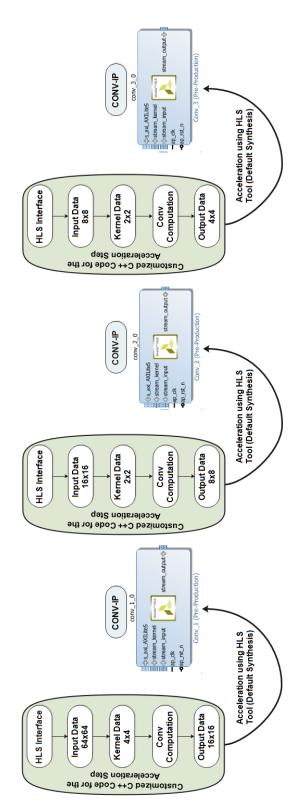

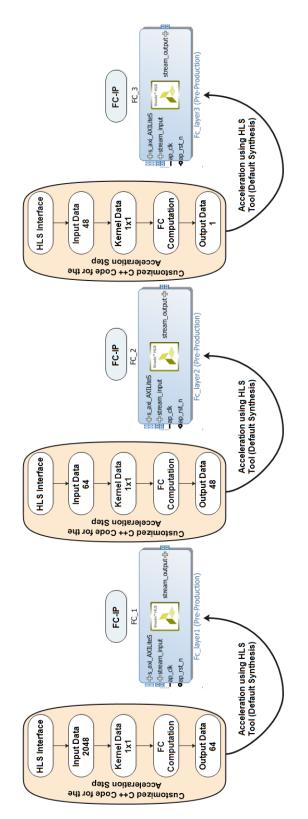

|         | IV.3.2 CNN Accelerator based on Vivado HLS                | 82 |

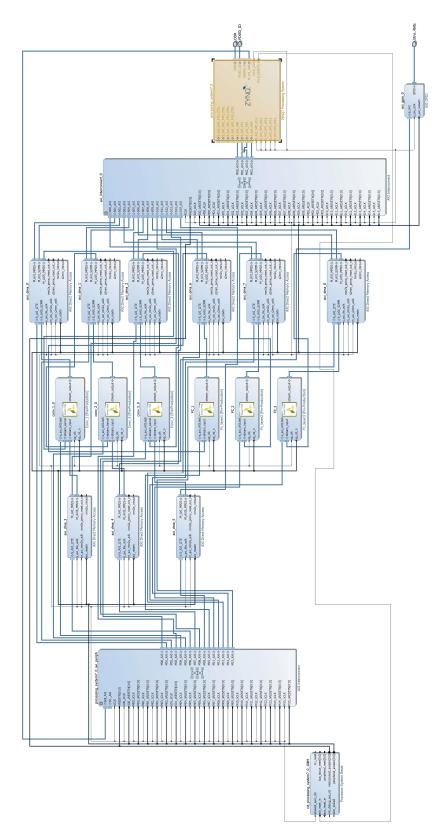

|         | IV.3.3 Hardware-Software Co-Design for CNN on FPGA-SoC    | 86 |

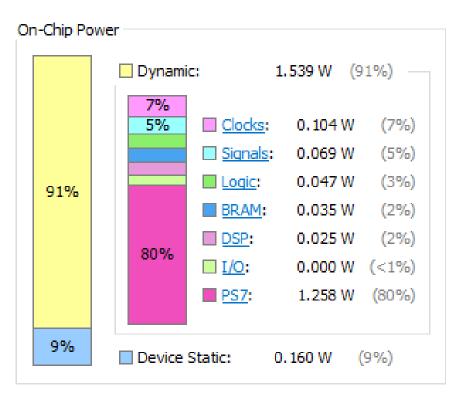

| IV.4    | Experimental Results                                      | 89 |

|         | IV.4.1 IP Cores Hardware Resource                         | 89 |

|         | IV.4.2 Hardware Cost of the Proposed Co-Design            | 90 |

|         | IV.4.3 Comparative Study                                  | 91 |

| IV.5    | Conclusion                                                | 93 |

| Genera  | al Conclusion and Perspectives                            | 94 |

| Bibliog | graphy                                                    | 97 |

| List of | Publications 1                                            | 09 |

| A Co    | nvolutional Neural Networks 1                             | 10 |

| A.1     | Convolutional Layer                                       | 10 |

| A.2     | Activation Functions                                      |    |

| A.3     | Pooling Layers                                            | 11 |

| A.4     | Fully Connected Layer                                     |    |

| A.5     | Backpropagation Algorithm                                 | 13 |

# List of Figures

| I.1   | History of Video Coding Standardization                                      | 3  |

|-------|------------------------------------------------------------------------------|----|

| I.2   | Block Diagram of the Hybrid Video Coding Layer for HEVC                      | 5  |

| I.3   | HEVC Quadtree Partitioning Structure, including CU, PU and TU (solid         |    |

|       | line for CU, dashed line for TU)                                             | 6  |

| I.4   | Intra Prediction Modes in the HEVC Standard                                  | 7  |

| I.5   | Example of Uni and Bi-directional Inter Prediction                           | 8  |

| I.6   | Example of Quadtree with Nested Multi-Type Tree Coding Block Struc-          |    |

|       | ture for VVC                                                                 | 11 |

| I.7   | Intra Directional Modes in VVC                                               | 12 |

| I.8   | Wide-Angular Intra-Picture Prediction                                        | 12 |

| I.9   | Example of HEVC Time Profile                                                 | 16 |

| I.10  | Example of SVM Classifier                                                    | 18 |

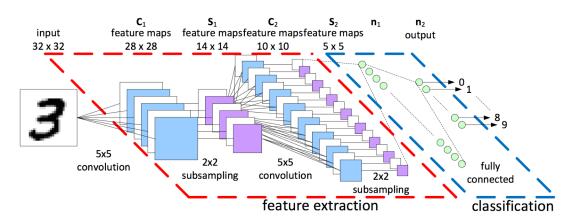

| I.11  | Overall Convolutional Neural Network Architecture                            | 20 |

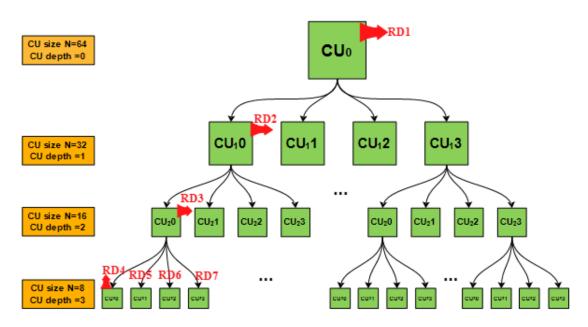

| II.1  | CU Partition Structure in HEVC                                               | 28 |

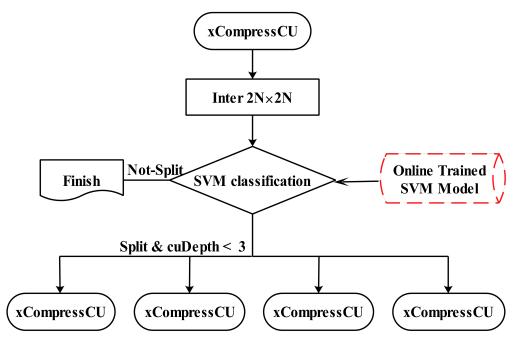

| II.2  | Flowchart of the Proposed Algorithm                                          | 31 |

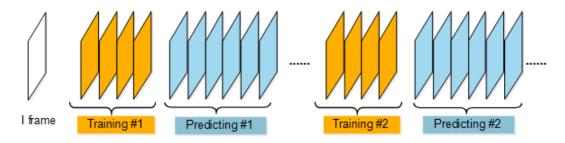

| II.3  | Online Training Mode                                                         | 31 |

| II.4  | Deep CNN Architecture                                                        | 33 |

| II.5  | Training Process                                                             | 35 |

| II.6  | Proposed Framework                                                           | 37 |

| II.7  | LSTM Cell                                                                    | 39 |

| II.8  | Learning Process                                                             | 40 |

| II.9  | Encoding Time of the Proposed CNN-LSTM and Deep CNN $\hfill \ldots \ldots$ . | 45 |

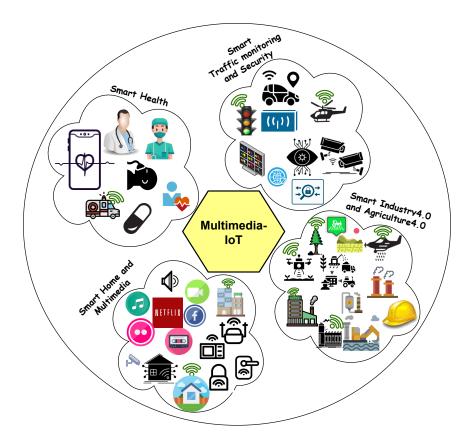

| III.1 | M-IoT Use Cases                                                              | 52 |

| III.2 | M-IoT Scenario-based Centralized Video Quality Enhancement                   | 55 |

| III.3 | Proposed VVC Standard Framework                                              | 56 |

| III.4 | WSE-DCNN Architecture                                                        | 58 |

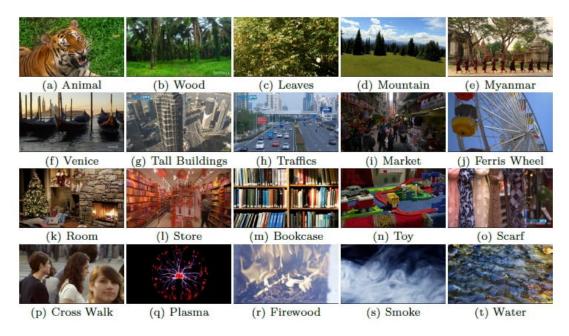

| III.5 | Sample Frames of Sequences from the BVI-DVC Database                         | 62 |

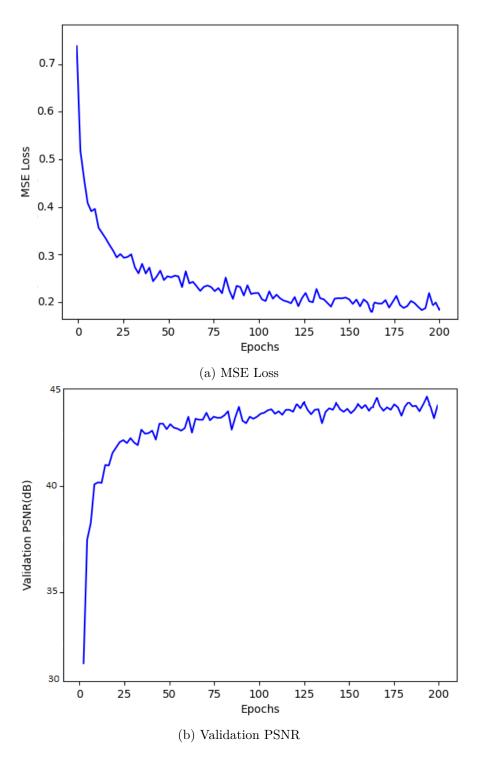

| III.6 | Training MSE Loss and Validation PSNR                                        | 64 |

### LIST OF FIGURES

| III.7 Ablation Study. Subjective Visual Quality Comparison (the 12th frame       |

|----------------------------------------------------------------------------------|

| of BQS<br>quare with $QP=37$ : (a) Original; (b) VVC without in-loop fil-        |

| tering $(PSNR=31.17\text{dB})$ ; (c) VVC $(PSNR=31.37\text{dB})$ ; (d) VVC-based |

| proposed model $(PSNR=31.68dB)$                                                  |

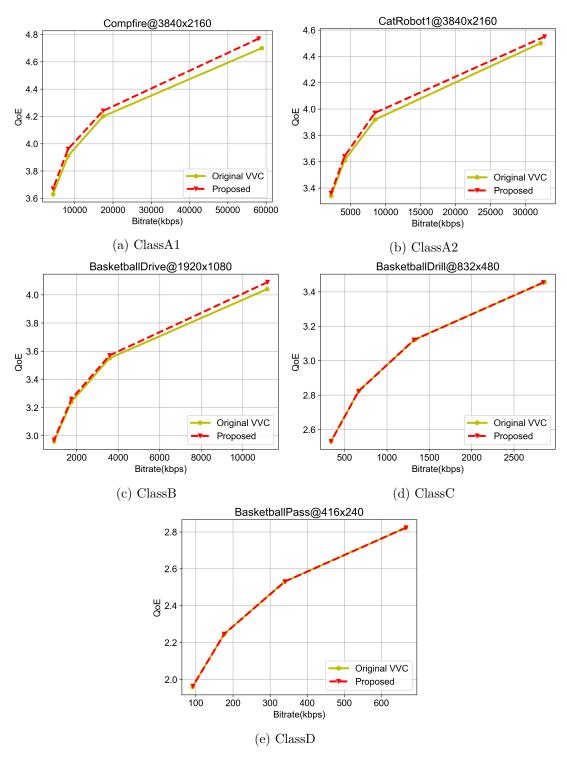

| III.8 Comparison of QoE Variation with Respect to bitrate                        |

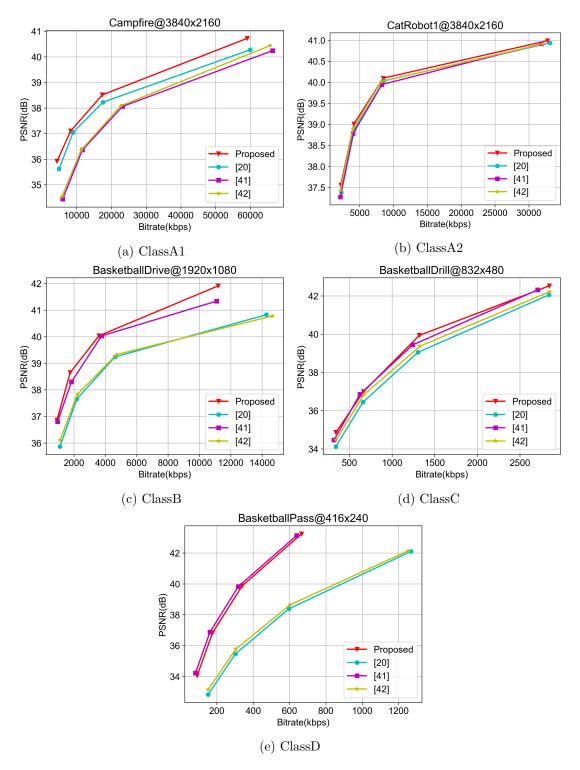

| III.9 RD-performance Curves of the Proposed Model Compared to other three        |

| Approaches                                                                       |

| IV.1 A simplified Model of the Zynq Architecture                                 |

| IV.2 Zynq Processing System                                                      |

| IV.3 Zynq Programmable Logic                                                     |

| IV.4 Block CLB                                                                   |

| IV.5 AXI Interconnects and Interfaces                                            |

| IV.6 Vivado HLS Design Flow                                                      |

| IV.7 Proposed Deep CNN-based CU Partition for HEVC 82                            |

| IV.8 CONV-IP Cores                                                               |

| IV.9 FC-IP Cores                                                                 |

| IV.10Hardware-Software Co-Design                                                 |

| IV.11Power Consumption                                                           |

| A.1 Convolution Operation                                                        |

| A.2 The Non-Linear Activation Functions                                          |

| A.3 Max vs Average pooling                                                       |

| A.4 Fully Connected Layer                                                        |

# List of Tables

| I.1         | Coding Tools of VVC vs HEVC                                           | 14 |

|-------------|-----------------------------------------------------------------------|----|

| II.1        | Sequences in CPIH Database                                            | 36 |

| II.2        | Test Sequences                                                        | 42 |

| II.3        | Performances Comparison between Deep CNN and Online SVM               | 43 |

| II.4        | Performances Comparison between Deep CNN and CNN-LSTM                 | 44 |

| II.5        | Comparative Study                                                     | 47 |

| III.1       | Key Features of BVI-DVC Video Training Database [MZB20]               | 62 |

| III.2       | Performance Evaluation of the Proposed model under RA Configuration . | 65 |

| III.3       | Coding Performance Comparison with other Approaches                   | 69 |

| IV.1        | CNN_1 Model Summary                                                   | 83 |

| IV.2        | Hardware Resource Occupation of the CONV-IP                           | 90 |

| IV.3        | Hardware Resource Occupation of the FC-IP                             | 91 |

| <b>IV.4</b> | Hardware Cost                                                         | 91 |

| IV.5        | Comparative Study                                                     | 93 |

# List of Abbreviations

| 5G :            | Fifth Generation $53$                        |

|-----------------|----------------------------------------------|

| <b>AI</b> :     | Artificial Intelligence 16, 50, 74           |

| ALF :           | Adaptive Loop Filter 14, 53                  |

| $\mathbf{AR}$ : | Augmented Reality xviii                      |

| ASIC :          | Application Specific Integrated Circuit 74   |

| AVC :           | Advenced Video Coding xix                    |

| AXI :           | Advanced eXtensible Interface 75             |

| BD-BR :         | Bjontegaard Delta bitrate 41, 42, 63, 66     |

| BD-PSNR :       | Bjontegaard Delta Peak Signal-to Noise Ratio |

|                 | 41                                           |

| CABAC :         | Context-Adaptive Binary Arithmetic Coding    |

|                 | 9                                            |

| CLBs :          | Configurable Logic Blocks 77                 |

| CNN :           | Convolutional Neural Network xx, 19, 32, 53, |

|                 | 95                                           |

| CPU :           | Central Processing Unit 80                   |

| CTC :           | Common Test Conditions 63                    |

| CTU :           | Coding Tree Unit 6, 56, 82                   |

| <b>CU</b> :     | Coding Unit xx, 6, 57, 95                    |

| DBF :           | De-Blocking Filter 9, 14, 53                 |

| DCT :           | Discrete Cosine Transform 9                  |

| DL :             | Deep Learning 18, 32                           |

|------------------|------------------------------------------------|

| DMA :            | Direct Memory Access 80, 87                    |

| DNNs :           | Deep Neural Networks 19                        |

| DST :            | Discrete Sine Transform 9                      |

| $\mathbf{FFs}$ : | Flip-Flops 77                                  |

| FPGAs :          | Field Programmable Gate Arrays 73, 74          |

| GoP :            | Group of Picture 31                            |

| GPU :            | Graphics Processing Unit $36$                  |

| HD :             | High Definition xviii, 50                      |

| HDR :            | High Dynamic Range 2, 95                       |

| HEVC :           | High Efficiency Video Coding v, vi, xix, 2, 95 |

| $\mathbf{HFR}$ : | High Frame Rate v, vi, xviii, 2                |

| HLS :            | High Level Synthesis 74, 96                    |

| IOBs :           | Input/Output Blocks 77                         |

| IoT :            | Internet of Things 50, 51                      |

| IP :             | Intellectual Property xxi, 74, 76              |

| ISO/IEC :        | International Organization for Standardiza-    |

|                  | tion and the International Electrotechnical    |

|                  | Commission 3                                   |

| ITUT :           | International Telecommunication Union,         |

|                  | Telecommunication 3                            |

| JCT-VC :         | Joint Collaboration Team on Video Coding $3$ , |

|                  | 4, 34                                          |

| JVET :           | Joint Video Exploration Team xix, 10           |

| JVT :            | Joint Video Team 3                             |

| LDP :            | Low Delay P 41, 42, 46                         |

| LSTM :           | Long-and Short-Term Memory $xx,95$             |

| LUTs :           | Look-Up-Tables 77                              |

| M-IoT :          | Multimedia-Internet of Things xx, 50, 51, 96   |

| <b>MB</b> :      | Macro-Block 6                                  |

|                  |                                                |

| ML :              | Machine Learning 16                                 |

|-------------------|-----------------------------------------------------|

| MOS :             | Mean Opinion Score 52                               |

| MPEG :            | Moving Picture Experts Group $\frac{3}{2}$          |

| MSE :             | Mean Square Error 63                                |

| $\mathbf{PL}$ :   | Programmable Logic 74, 87, 96                       |

| $\mathbf{PS}$ :   | Processing System 74, 87, 96                        |

| PSNR :            | Peak Signal-to-Noise Ratio 63                       |

| <b>PU</b> :       | Prediction Units 6                                  |

| $\mathbf{QoE}$ :  | Quality of Experience xx, $50$ , $52$ , $66$ , $95$ |

| $\mathbf{QoS}$ :  | Quality of Service 52                               |

| <b>QP</b> :       | Quantization Parameter 13, 41, 57, 61               |

| $\mathbf{QTMT}$ : | QuadTree plus Multi-type Tree 10, 97                |

| <b>RA</b> :       | Random Access xiv, $63$                             |

| RDO :             | Rate-Distortion Optimization 27, 46, 55, 82,        |

|                   | 95                                                  |

| ReLU :            | Rectified Linear Unit 22, 32                        |

| RTL :             | Register-Transfer-Level 80                          |

| SAO :             | Sample Adaptive Offset 9, 14, 53                    |

| SGD :             | Stochastic Gradient Descenth 35, 39                 |

| SoCs :            | System-on-Chips 74                                  |

| $\mathbf{SVM}$ :  | Support Vector Machines $xx$ , 95                   |

| TU :              | Transform Units 6                                   |

| UHD :             | Ultra-High Definition xviii, 10, 50, 95             |

| VCEG :            | Visual Coding Experts Group $3$                     |

| $\mathbf{VR}$ :   | Virtual Reality v, vi, xviii                        |

| $\mathbf{VVC}$ :  | Versatile Video Coding v, vi, xix, 2, 49, 55,       |

|                   | 95                                                  |

| WSE-DCNN :        | Wide-activated Squeeze-and-Excitation Deep          |

|                   | Convolutional Neural Network xx, $51, 55, 96$       |

|                   |                                                     |

## General Introduction

ith the development of multimedia computing, communication and display technologies, many video applications have emerged, such as TV broadcasting, video-on-demand, video conference, mobile video, video surveillance, 3D videos and Augmented Reality (AR), which can provide immersive telepresence and realistic visual perception experience. These video applications have been widely employed for multiple roles in human daily life, such as manufacturing, communication, national security, military, education, medicine, and entertainment. Nowadays, video data has been the majority data traffic over the internet and its volume grows explosively each year. The latest Cisco Visual Networking Index reports that Internet Protocol video traffic accounted for 75% of all Internet traffic in 2017, and they expect it to rise up to 82%by the year 2022 [CCH18]. On that occasion, million minutes of video contents will be delivered through the network in every second. To further enhance the immersive and realistic visual experiences, more high-end video applications emerge, such as High and Ultra-High Definition content (HD, UHD), Virtual Reality (VR), High Frame Rate (HFR) and 360° video and the advent of very high spatial resolution 8K or even 16K, which require larger data volume to represent higher fidelity and more details. Meanwhile, the number of video clients and cameras in use grows rapidly as the video demands keep boost in recent years, as HDTV, surveillance cameras, laptop and smart phones. The total amount of global video data doubles every two years, which is the bottleneck for data processing, storage and transmission.

Video coding is one of the basic technologies in video applications that allows video data to be structured and compressed more efficiently for computation, transmission and storage. It has been developed over three decades with four generations and the coding efficiency doubles every ten years. But there is a big gap as compared with the rapid growth of global video data doubling every two years. Achieving much higher compression efficiency and narrowing the gap in an effective way become urgent missions for video coding. Machine learning is a field of study that can learn from data, discover hidden patterns and make data-driven decisions. Due to its superior performance in learning from data, many emerging works have applied machine learning algorithms to video coding to further promote the coding performances, which becomes one of the most promising directions in both academic and industrial communities.

In this context, the advent of the video coding standard, High Efficiency Video Coding (HEVC), standardized in January 2013 [SOHW12] has made it possible to broadcast the UHD content on the communication network. The HEVC provides nearly 50% bitrate gain in comparison to the H.264/AVC standard for the same quality. However, HEVC is still not efficient enough to endure the burden of video transmission and storage for various large popular applications based on 8K and 360° videos. For this reason, Versatile Video Coding (VVC) appears the most recent video coding standard developed jointly by JVET, as known H.266 [BCO<sup>+</sup>21]. It is based on the same hybrid video coding block, as its predecessors from MPEG-2 to HEVC. VVC is designed to be both efficient and versatile to address today's media needs. This includes approximately 30% - 50%bitrate reduction over HEVC [WHB<sup>+</sup>20], as well as versatility by efficient coding of a wide range of video content and applications.

The main objective of this thesis is to significantly improve the coding efficiency of HEVC and VVC standards based on fast machine learning algorithms. This manuscript is structured in four chapters:

### Chapter I : Video Coding and Artificial Intelligence Backgrounds

The first chapter introduces the most emerging video technologies nowadays. For this purpose, the hybrid aspects of the video coding standards are discussed first and then some essential modules to build a codec with this structure are detailed. In order to emphasize on the similarity of general structure between different video coding standards, some sections also provide equivalent historical and descriptive information from HEVC along with VVC. Meanwhile, we summarize the most challenges in video coding standards. After that, we introduce the recent advancements in machine learning and deep learning models and their categories. Finally, some related research based on video coding techniques are reviewed.

### Chapter II : Machine Learning Approach-based Fast CU Partition for Reducing HEVC Complexity

The second chapter proposes a fast Coding Unit (CU) partition based on machine learning approaches to reduce the HEVC complexity of inter-mode. An online Support Vector Machines (SVM)-based fast CU partition method is proposed for reducing the encoding complexity of HEVC. Afterwards, to predict the CU partition of HEVC, a Deep Convolutional Neural Network (CNN) is proposed, which reduces the HEVC complexity at inter-mode. Unfortunately, these two machine learning algorithms do not explore the correlation of the CU partition across neighboring frames. A Long-and Short-Term Memory (LSTM) model was developed to learn the temporal dependency of the intermode CU partition. Therefore, a deep learning approach is proposed to predict the CU partition at inter-mode, which combines the CNN and LSTM structures. Finally, the obtained results are discussed in order to evaluate the performance of the proposed algorithms.

Chapter III : Deep Learning based Video Quality Enhancement for the New Versatile Video Coding The third chapter proposes a deep learning algorithm-based VVC standard to enhance visual video quality while improving the user's Quality of Experience (QoE). The proposed Wide-activated Squeeze-and-Excitation Deep Convolutional Neural Network (WSE-DCNN) model is integrated into VVC standard to replace in-loop filtering in order to alleviate the coding artifacts, such as ringing, blocking, and blurring. The proposed VVC filtering technique is used in the Multimedia-Internet of Things (M-IoT) scenario-based smart city context to help the centralized cloud meet the user's required video quality. Finally, all simulation results obtained are interpreted and compared to the related existing methods.

## Chapter IV : Deep CNN Co-Design for HEVC CU Partition Prediction on FPGA-SoC

The last chapter proposes a deep CNN based hardware-software design for HEVC CU prediction on FPGA-SoC. Our proposed work aims to accelerate the CNNs due to their computationally intensive. Hence, we create a hardware Intellectual Property (IP) core for each CNNs layer using the Vivado HLS tool. Then, we have designed a hardware-software architecture by importing the hardware IP cores based on the PYNQ-Z1 board. Finally, the achieved results are discussed and a comparative study is made.

Finally, the last part of this thesis will be reserved for a general conclusion that summarizes the results found and lists the different perspectives.

# Chapter I

# Video Coding and Artificial Intelligence Backgrounds

### Summary

| I.1 | Intr  | oduction                                | 2  |

|-----|-------|-----------------------------------------|----|

| I.2 | Vide  | eo Compression History                  | 3  |

| I.3 | HEV   | VC Standard                             | 4  |

|     | I.3.1 | Sampled Representation of Pictures      | 5  |

|     | I.3.2 | Block Partitioning in the HEVC Standard | 6  |

|     | I.3.3 | Intra Prediction                        | 7  |

|     | I.3.4 | Inter Prediction                        | 8  |

|     | I.3.5 | Transform and Quantization              | 9  |

|     | I.3.6 | Entropy Coding                          | 9  |

|     | I.3.7 | In-Loop Filters                         | 9  |

| I.4 | VVO   | C Standard                              | 10 |

|     | I.4.1 | Block Partitioning in the VVC Standard  | 10 |

|     | I.4.2 | Intra Prediction                        | 11 |

|     | I.4.3 | Inter Prediction                        | 12 |

|     | I.4.4 | Transform and Quantization              | 13 |

|     | I.4.5 | Entropy Coding                          | 13 |

### CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

| I.4.6 In-Loop Filters                                              |

|--------------------------------------------------------------------|

| I.5 Video Coding Challenges                                        |

| I.6 Artificial Intelligence: New Advancements and Innovations . 16 |

| I.6.1 Machine Learning 16                                          |

| I.6.2 Deep Learning 19                                             |

| I.7 Related Research                                               |

| I.7.1 Heuristic Methods                                            |

| I.7.2 Learning Methods                                             |

| I.8 Conclusion                                                     |

### I.1 Introduction

**I** n this chapter, a brief review of the video compression structure is presented. For this purpose, the hybrid video coding standards scheme is first discussed and then some essential modules to build a codec with this structure are detailed. In order to emphasize on the similarity of general structure between different video coding standards, some sections also provide equivalent historical information from High Efficiency Video Coding (HEVC) along with Versatile Video Coding (VVC). Meanwhile, we summarize the most challenges in video coding standards. After that, we introduce the recent advancements in machine learning and deep learning models and their categories. Finally, this chapter provides a detailed literature review on different advanced video coding approaches that have been proposed.

The remainder of this chapter is organized as follows. Section I.2 presents the video compression history. The HEVC standard structure is described in Section I.3. Section I.4 introduces the VVC coding tools. Then, Section I.5 provides the video coding challenges. Afterwards, a detailed overview of artificial intelligence technique is exposed in Section I.6. The related research of video coding approaches is presented in Section I.7. Finally, Section I.8 concludes this chapter.

### I.2 Video Compression History

Every second in year 2021, more than a million minutes of video content will cross the network. It would take a person more than 5 million years to watch all videos of one month [CCH18]. This forecast is convincing for video coding experts to think of more efficient compression tools and technologies. These technologies are expected to address various emerging video formats, namely High Dynamic Range (HDR), High Frame Rate (HFR), high resolution videos (e.g. 4K, 8K and beyond), immersive 360° videos, screeen content and more. Video coding standards aim at bringing format compatibility between devices. This enables the playback of any video file conforming the syntax of a given standard, with any device supporting it. From the industrial point of view, such unity facilitates the interaction between all components of the broadcast chain, including consumer electronics manufactures, broadcasters, content providers etc. This convenience in interaction, if achieved, can significantly accelerate the progress of the broadcast industry as a whole.

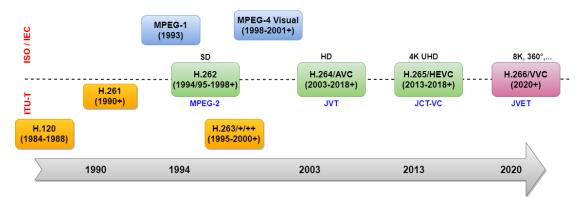

Historically, two major video coding standardization organizations have coexisted: Moving Picture Experts Group (MPEG), which belongs to the International Organization for Standardization and the International Electrotechnical Commission (ISO/IEC), and the Visual Coding Experts Group (VCEG), which belongs to the International Telecommunication Union, Telecommunication Standardization Sector (ITUT). The history of the different H.26x and MPEG-x families established by ITUT and ISO/IEC is shown in Figure I.1.

Figure. I.1: History of Video Coding Standardization

### CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

Most successful standardization acts of the MPEG were accomplished after its collaboration with the ITUT, in the late 90's. This joint collaboration, initially called Joint Video Team (JVT), then Joint Collaboration Team on Video Coding (JCT-VC), resulted in some of the most successful video coding standards in the family of "H.26x", notably H.264/Advanced Video Coding (AVC), developed in May 2003 [CKL06], and H.265/High Efficiency Video Coding (HEVC), finalized in January 2013 [SOHW12]. In October 2015, another collaboration between MPEG and VCEG formed the Joint Video Exploration Team (JVET) [MAS18] that was tasked with assessing the available compression technologies and exploring the requirements for a next-generation video compression standard. Hence, the new video coding standard called H.266/Versatile Video Coding (VVC) was standardized in July 2020 [BCO<sup>+</sup>21]. After the history presentation of the different video coding standards, the two latest HEVC and VVC will be detailed in next sections, since they will be used in this thesis.

### I.3 HEVC Standard

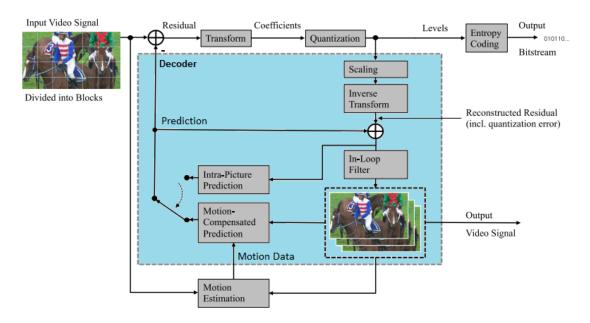

High Efficiency Video Coding (HEVC) is the sophisticated video coding standard, also known as H.265, standardized in 2013 by the JCT-VC [Ric13]. HEVC saves approximately 50% of bitrate for the same subjective video quality, with respect to its predecessor H.264/AVC standard. Thus, the HEVC codec is expected to ease the burden on global networks where High Definition (HD) and Ultra High Definition (UHD) video content is becoming more and more popular. HEVC is based on the basic hybrid structure as employed by previous standards since H.261. However, the standard contains series of incremental improvements [Ric13] over H.264/AVC in order to achieve better compression efficiency. The block diagram of a hybrid video coding layer conforming with the HEVC standard is illustrated in Figure I.2.

In accordance, a typical video encoder compliant with the HEVC standard would start by dividing each frame into block-shaped regions, with the exact block partitioning being conveyed to the decoder. The first picture of the video sequence is coded using only intra picture prediction, i.e., the prediction of the blocks in the picture is only

Figure. I.2: Block Diagram of the Hybrid Video Coding Layer for HEVC

based on the blocks from that same picture. For the remaining pictures of the video sequence, inter picture prediction is used. This type uses prediction information from other previously encoded pictures.

From Figure I.2, the result from the prediction is subtracted from the original block and the residual information is then transformed by a linear spatial transform. The transform coefficients are then scaled, quantized, compressed and transmitted in the receiver, together with the prediction information. The encoder also integrates the processing loop of the decoder in order to generate the same pictures as the output of the decoder. These pictures are then stored in a decoded picture buffer, and will be used for the prediction of the subsequent pictures. In the following, the general features of the hybrid video coding scheme used in HEVC will be described with more details.

### I.3.1 Sampled Representation of Pictures

Video sequence is typically captured using the RGB color space, which is not a particularity efficient representation for video coding. On the contrary, HEVC uses a more video coding friendly color space, the YCbCr, which divides the color space in 3 components: Y, known as luma, representing brightness; Cb and Cr, also known as chroma, which represent how much color deviates from gray towards blue and red, respectively.

## CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

As the human visual system is more sensitive to brightness, the typically used sampling scheme follows the 4:2:0 structure, meaning that four luma components are sampled for every chroma component. HEVC also supports each sample pixel value with 8 or 10 bits precision, with 8 bits being the most commonly used for HEVC standard  $[B^{+}13]$  and 10 bits used for VVC standard  $[FJK^{+}20]$ .

### I.3.2 Block Partitioning in the HEVC Standard

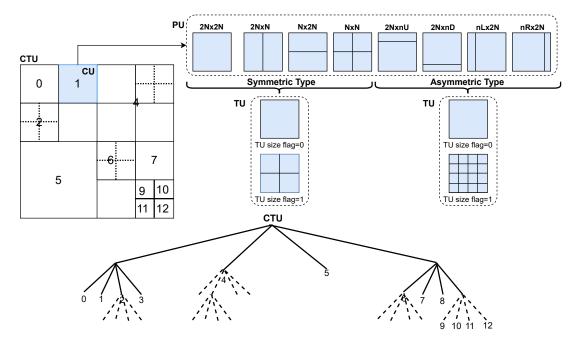

In the former video coding standard H.264/AVC, Variable Macro-Block (MB) sizes ranging from  $4 \times 4$  to  $16 \times 16$  are supported [CKL06]. Whereas larger block sizes, reached at  $64 \times 64$ , are used in HEVC standard to facilitate the high definition video compression. Additionally, more flexible partitioning of video frames is supported to improve the

Figure. I.3: HEVC Quadtree Partitioning Structure, including CU, PU and TU (solid line for CU, dashed line for TU)

coding efficiency, where available block size varies from  $4 \times 4$  up to  $64 \times 64$ , including symmetric partitioning, such as  $2N \times 2N$ ,  $2N \times N$ ,  $N \times 2N$  and  $N \times N$ , and also asymmetric motion partitioning (AMP) for instance  $2N \times nU$ ,  $2N \times nD$ ,  $nL \times 2N$  and  $nR \times 2N$ . In particular  $N \times N$  is only allowed for minimum coding unit (CU) and AMP is not applied to CUs smaller than  $16 \times 16$ . Figure I.3 introduces the partitioning and quadtree structure

## CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

used in the HEVC standard, in which the analogous structure, called Coding Tree Unit (CTU), is splitted into CUs using a quad-tree partitioning structure, and a CU can be further sub-divided into Prediction Units (PU) for inter-frame or intra-frame prediction and its transformation is performed using one or more Transform Units (TU).

### I.3.3 Intra Prediction

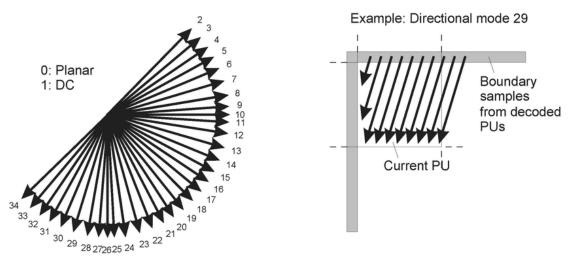

In intra picture prediction, the information of adjacent CTU from the same picture is used for spatial prediction, as shown in Figure I.4. There are a total of 35 intra picture prediction modes available in HEVC, corresponding to 33 different directional modes, a DC and a planar mode. For directional mode encoding, the spatially neighboring decoded blocks are used as reference for the prediction, using the selected angle to cover the current PU. This mode is the most used for regions with strong directional edges. Directional mode prediction is consistent across all block sizes and prediction directions. DC mode encoding simply uses a single value matching the mean value of boundary samples for the prediction. Finally, the planar mode assumes an amplitude surface with a horizontal and a vertical slope derived from the boundaries. This mode is supported for all block sizes in HEVC.

Figure. I.4: Intra Prediction Modes in the HEVC Standard

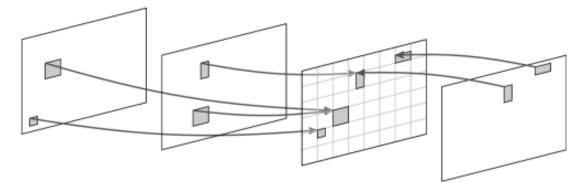

### I.3.4 Inter Prediction

In order to exploit the redundancies in the temporal adjacent images, inter-picture prediction based on previously coded pictures is an essential technique to obtain high compression rates. It consists of the application of the following two techniques: motion compensation and motion estimation. By using these techniques, pictures are predicted from previously encoded frames (uni-directional) or from previous and future frames (bi-directional), as shown in Figure I.5. The use of the bidirectional prediction is more complex, since it requires the video frames to be coded and stored out of order, so that future frames may be available.

Figure. I.5: Example of Uni and Bi-directional Inter Prediction

Before the application of motion compensation technique, the encoder has to find a block similar to the one it is encoding on a previous/future encoded frame, referred to as a reference frame. Such searching procedure is known as motion estimation, resulting in the identification of a motion vector, which points to the position of the best prediction block in the reference frame. However, since the identified block will most likely not be an exact match of the encoding block, the resulting difference (residue) has to be encoded and transmitted to the decoding end, so that it can be read by the decoder. These residuals, originated from the difference between the predicted block and the actual block, are known as prediction errors.

The actual position of the prediction in the neighboring frames may be out of the sampling grid (where the intensity is unknown), so the intensities of the positions in between the integer pixels must be interpolated and the resolution of the motion vector increased accordingly. For the interpolation in fractional luma sample positions, an 8-tap filter is used, while a 4-tap filter is used for chroma samples.

### I.3.5 Transform and Quantization

After the motion estimation, all the prediction error residuals are transformed into a set of coefficients for efficient transmission and storage. In the HEVC standard, as indicated in Figure I.3, TUs of size  $4\times4$ ,  $8\times8$ ,  $16\times16$  and  $32\times32$  are supported. The 2D transforms based on Discrete Cosine Transform (DCT) are designed for them and special efforts are particularly spent on selecting the value of the transfrom matrix for retaining the property of easy-to-implementation [SOHW12]. In addition, when transforming for  $4\times4$  block size in intra-frame prediction mode, another integer transformation based on Discrete Sine Transform (DST) is available for use. The resulting transform coefficients are then quantized, before being sent to the construction of the coded bitstream. Quantization is a compression technique which converts a range of values into a single quantum value. The maximum Quantization Parameter of HEVC standard is set to 51.

#### I.3.6 Entropy Coding

In the HEVC standard a bitstream is produced using motion parameters, prediction modes, quadtree partitioning information, quantized transform coefficients and some other control data through entropy coding. Only one entropy coding method, Context-Adaptive Binary Arithmetic Coding (CABAC), is specified in the standard. Although there is no change made on the core algorithm of CABAC, it is optimized on the aspects of context modeling, adaptive coefficient scanning, coefficient coding, sign data hiding and so on to improve its throughput.

### I.3.7 In-Loop Filters

Before writing the samples in the decoded picture buffer, they are processed first by a deblocking filter (DBF) and then by a sample adaptive offset filter (SAO). Block based coding schemes tend to produce blocking artifacts due to the fact that inner blocks are coded with more accuracy than outer blocks. To mitigate such artifacts, the decoded

samples are filtered by a DBF. After the deblocking has been processed, the samples are processed by SAO, a filter designed to allow for better reconstruction of the original signal amplitudes, reducing banding and ringing artifacts. SAO is performed on a per CTU basis and may or may not be applied, depending on the filtering type selected.

# I.4 VVC Standard

Versatile Video Coding (VVC) [BCO<sup>+</sup>21] [HBA<sup>+</sup>21] is the new generation video coding developed in July 2020, by the Joint Video Experts Team (JVET), as a successor of the HEVC [SOHW12]. As the next standard for sophisticated video coding technology, VVC allows up to 30% - 50% for bitrate savings while maintaining the same quality as HEVC. VVC has been designed to achieve improved compression capacity over previous standards such as HEVC, and at the same time to be highly versatile for effective use in a broadened range of applications. Some key application areas for the use of VVC particularly include UHD video (e.g. 4K or 8K resolution), video with a high dynamic range, and video for immersive media applications such as 360° omnidirectional video, in addition to the applications that have commonly been addressed by prior video coding standards.

Similar to its predecessor HEVC, VVC uses a block-based hybrid coding architecture with some coding tools that may be included or removed. The VVC architecture includes the inter-picture, intra-picture prediction, and transform coding with entropy coding.

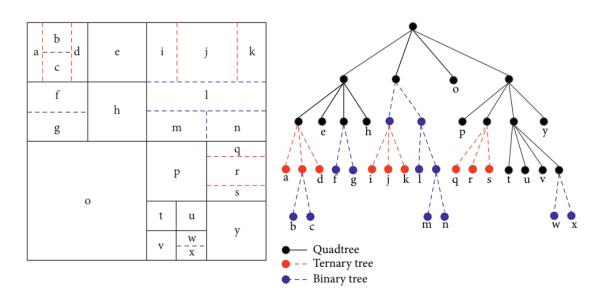

# I.4.1 Block Partitioning in the VVC Standard

In VVC, each picture is split into non-overlapping squares called CTUs. The largest CTU size allowed in VVC is  $128 \times 128$  pixels, larger than the maximum size allowed in HEVC,  $64 \times 64$ . Large blocks improve the efficiency of coding flat areas such as backgrounds, especially for high-resolution videos such as HD and 4K. In order to efficiently represent highly detailed areas such as textures and edges, VVC employs a flexible partitioning scheme that can CTUs partition sized of  $128 \times 128$  down CUs as small as  $4 \times 4$  pixels.

Figure I.6 shows one CTU divided into multiple CUs with a QuadTree plus Multi-

# CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

Figure. I.6: Example of Quadtree with Nested Multi-Type Tree Coding Block Structure for VVC

type Tree QTMT coding block structure, where the solid block edges represent quadtree partitioning and the dotted edges represent multitype tree partitioning with either binary or ternary splits. The first is the quadtree split that is also available in HEVC, which can recursively split CTU into squared CUs down to  $4 \times 4$  pixels, smaller than the  $8 \times 8$ minimum CU size in HEVC. The second part consists of binary-tree and ternary-tree splits that partition a block into two and three rectangles respectively. Both binary and ternary tree splits can operate in either horizontal or vertical directions, be recursively applied and mixed together in a nested multi-type tree.

The block partitioning in VVC is highly flexible and provides about 8 percent bitrate reduction over HEVC. However, this flexibility comes at a computational cost, especially on the encoder side, where many more permutations need to be evaluated to select the optimal partition.

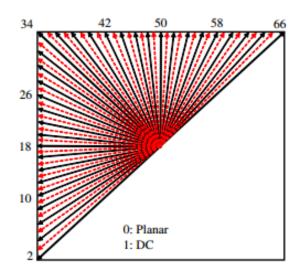

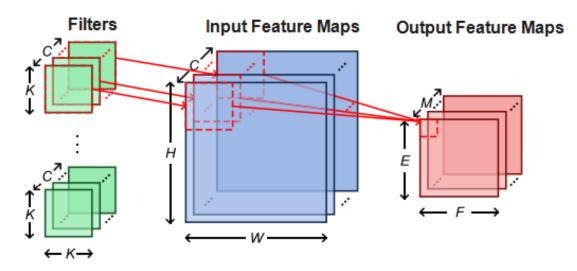

# I.4.2 Intra Prediction

The number of directional intra modes in VVC is extended from 33, as used in HEVC, to 65. The new directional modes, not used in HEVC, are depicted by red dotted arrows, as mentioned in Figure I.7, whereas the planar and DC modes are unchanged for both video encoder. These denser directional intra prediction modes apply for all block sizes and

# CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

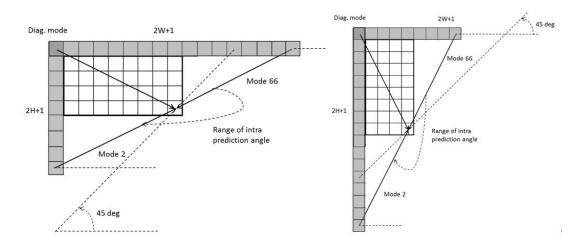

for both luma and chroma intra predictions. In HEVC, 33 angular prediction directions are defined from 45° to 135° in a clockwise direction. In VVC, the angular precision is basically doubled to produce 65 angles within that same range, and another 28 "wide-angle" prediction modes beyond this angular range can be used for non-square blocks, as illustrated in Figure I.8.

Figure. I.7: Intra Directional Modes in VVC

Figure. I.8: Wide-Angular Intra-Picture Prediction

# I.4.3 Inter Prediction

The basic concepts of uni-directional and bi-directional motion compensation from one or two reference pictures are mostly unchanged. However, there are some new tools

# CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

that have not been used in the last video coding standard. For each inter-predicted CU, motion parameters consisting of motion vectors, reference picture indices and reference picture list usage index, and additional information needed for the new coding feature of VVC to be used for inter-predicted sample generation. The motion parameter can be signalled in an explicit or implicit manner. When a CU is coded with skip mode, the CU is associated with one PU and has no significant residual coefficients, no coded motion vector delta or reference picture index. A merge mode is specified whereby the motion parameters for the current CU are obtained from neighbouring CUs, including spatial and temporal candidates, and additional schedules introduced in VVC. The merge mode can be applied to any inter-predicted CU, not only for skip mode. The alternative to merge mode is the explicit transmission of motion parameters, where motion vector, corresponding reference picture index for each reference picture list and reference picture list usage flag and other needed information are signalled explicitly per each CU.

Beyond the inter coding features in HEVC, VVC includes a number of new and refined inter prediction coding tools listed as follows; Extended merge prediction, 1/16th luma sample MV storage and  $8 \times 8$  motion field compression, Bi-prediction with CU-level weight (BCW), and Bi-directional optical flow (BDOF), etc.

#### I.4.4 Transform and Quantization

The size of transform block is increased from  $4 \times 4$  to  $64 \times 64$  in the VVC standard compared to the HEVC standard. In addition to the DCT-II used in HEVC, a multiple transformation selection (MTS) scheme is also used for residual coding of intra and inter coding blocks. The newly introduced transformation matrices are DST-VII and DCT-VIII. The change of the Quantization stage is the increase in the maximum Quantization Parameter (QP) from 51 to 63.

#### I.4.5 Entropy Coding

In VVC, the CABAC technique is improved in comparison to the HEVC design. The three main modifications are: modified context modeling for transform coefficients, multi-hypothesis probability estimation with context-dependent updating speed and

# CHAPTER I. VIDEO CODING AND ARTIFICIAL INTELLIGENCE BACKGROUNDS

adaptive initialization for context models (e.g. initial probability states of context models for inter coded slices can be initialized by copying states from previously coded pictures).

|                  | HEVC                                                                                | VVC                                                                                              |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

|                  | <ul> <li>Coding Tree Unit (CTU) quadtree (QT) structure</li> </ul>                  | • CTU quadtree structure with nested multi-type tree (QT+MTT)                                    |  |  |  |  |

| Block            | <ul> <li>From 64×64 to 8×8 Coding Unit (CU) size</li> </ul>                         | <ul> <li>From 128×128 to 4×4 CU size</li> </ul>                                                  |  |  |  |  |

| partitioning     |                                                                                     | Chroma separate tree (CST)                                                                       |  |  |  |  |

| partitioning     |                                                                                     | Local dual tree                                                                                  |  |  |  |  |

|                  |                                                                                     | Virtual pipeline data units (VPDUs)                                                              |  |  |  |  |

|                  | • DC, planar                                                                        | • DC, planar                                                                                     |  |  |  |  |

|                  | <ul> <li>33 directional prediction modes</li> </ul>                                 | <ul> <li>65 directional prediction modes</li> </ul>                                              |  |  |  |  |

|                  |                                                                                     | Wide-angle prediction modes                                                                      |  |  |  |  |

|                  | <ul> <li>Linear interpolation</li> </ul>                                            | <ul> <li>4-tap interpolation filters (IFs) using 2 sets of filters</li> </ul>                    |  |  |  |  |

| Intra prediction |                                                                                     | Position-dependent prediction combination (PDCP)                                                 |  |  |  |  |

|                  |                                                                                     | Multiple reference lines (MRL)                                                                   |  |  |  |  |

|                  |                                                                                     | Matrix-based intra-picture prediction (MIP)                                                      |  |  |  |  |

|                  |                                                                                     | Cross-component linear model (CCLM)                                                              |  |  |  |  |

|                  |                                                                                     | Intra sub-partitions (ISP)                                                                       |  |  |  |  |

|                  | Merge mode                                                                          | <ul> <li>Extended merge mode and MVP with</li> </ul>                                             |  |  |  |  |

|                  | <ul> <li>Advanced motion vector prediction (MVP)</li> </ul>                         | <ul> <li>History-based MVP (HMVP)</li> </ul>                                                     |  |  |  |  |

|                  |                                                                                     | <ul> <li>Pair-wise average MVP candidate</li> </ul>                                              |  |  |  |  |

|                  |                                                                                     | <ul> <li>Subblock-based temporal MVP (SBTMVP)</li> </ul>                                         |  |  |  |  |

|                  |                                                                                     | <ul> <li>Merge with motion vector difference (MMVD)</li> </ul>                                   |  |  |  |  |

|                  |                                                                                     | <ul> <li>Symmetric motion vector difference (SMVD)</li> </ul>                                    |  |  |  |  |

|                  |                                                                                     | Adaptive motion vector resolution (AMVR)                                                         |  |  |  |  |

| Inter prediction | 8-tap IFs for luma                                                                  | • 8-tap or 6-tap IFs for luma                                                                    |  |  |  |  |

|                  | <ul> <li>4-tap IFs for chroma</li> </ul>                                            | 4-tap IFs for chroma                                                                             |  |  |  |  |

|                  |                                                                                     | Geometric partitioning mode (GPM)                                                                |  |  |  |  |

|                  |                                                                                     | • Bi-prediction with CU-level weight (BCW)                                                       |  |  |  |  |

|                  |                                                                                     | Combined Intra/Inter prediction (CIIP)                                                           |  |  |  |  |

|                  |                                                                                     | Decoder-side motion vector refinement (DMVR)                                                     |  |  |  |  |

|                  |                                                                                     | Bi-directional optical flow (BDOF)                                                               |  |  |  |  |

|                  |                                                                                     | Affine motion                                                                                    |  |  |  |  |

|                  |                                                                                     | Prediction refinement with optical flow (PROF)                                                   |  |  |  |  |

|                  | • Square transform (up to 32×32)                                                    | • Square and rectangular transform (up to $64 \times 64$ )                                       |  |  |  |  |

|                  | Discrete cosine transform and discrete sine transform     Discrete cosine transform | Multiple transform selection (MTS)                                                               |  |  |  |  |

| F1/2             | <ul> <li>DCT-II and DST-VII</li> </ul>                                              | DCT-II, DST-VII, and DCT-VIII                                                                    |  |  |  |  |

| Forward/inverse  |                                                                                     | Non-separable secondary transform (LFNST)                                                        |  |  |  |  |

| transform and    |                                                                                     | Subblock transform (SBT)                                                                         |  |  |  |  |

| quantization     |                                                                                     | <ul> <li>Adaptive chroma QP offset</li> <li>SDH</li> </ul>                                       |  |  |  |  |

|                  | <ul> <li>Sign data hiding (SDH)</li> </ul>                                          |                                                                                                  |  |  |  |  |

|                  |                                                                                     | <ul> <li>Dependent quantization (DQ)</li> <li>Joint coding of chroma residuals (JCCR)</li> </ul> |  |  |  |  |

|                  | Context-adaptive binary arithmetic coding (CABAC)                                   | CABAC with multi-hypothesis probability estimates                                                |  |  |  |  |

|                  | Context-adaptive binary and infecte coding (CABAC)     Coefficient group            | Additional coefficient group size                                                                |  |  |  |  |

| Entropy coding   | Reverse diagonal, horizontal and vertical coefficient scan                          | Reverse diagonal coefficient scan only                                                           |  |  |  |  |

| Entropy coung    | • Reverse diagonal, nonzontal and vertical coefficient scan                         | Improved probability model sections for absolute transform                                       |  |  |  |  |

|                  |                                                                                     | coefficient levels                                                                               |  |  |  |  |

|                  |                                                                                     | Luma mapping with chroma scaling (LMCS)                                                          |  |  |  |  |

|                  | • Deblocking filter (DF)                                                            | <ul> <li>Deblocking boundary handling modifications</li> </ul>                                   |  |  |  |  |

|                  | · Beolocking mut (Dr)                                                               | Deblocking long filter                                                                           |  |  |  |  |

| T                |                                                                                     |                                                                                                  |  |  |  |  |

| Loop filtering   |                                                                                     | Luma-adaptive deblocking                                                                         |  |  |  |  |

|                  | <ul> <li>Sample adaptive offset (SAO)</li> </ul>                                    | • Sample adaptive offset (SAO)                                                                   |  |  |  |  |

|                  |                                                                                     | Adaptive loop filter (ALF)                                                                       |  |  |  |  |

|                  | au                                                                                  | Cross-Component ALF (CC-ALF)                                                                     |  |  |  |  |

|                  | Slices                                                                              | • Slices                                                                                         |  |  |  |  |

| Parallelization  | Tiles                                                                               | • Tiles                                                                                          |  |  |  |  |

|                  |                                                                                     | Subpictures                                                                                      |  |  |  |  |

|                  | <ul> <li>WPP with CTU row delay of two CTUs</li> </ul>                              | <ul> <li>WPP with CTU row delay of one CTU</li> </ul>                                            |  |  |  |  |

Table I.1: Coding Tools of VVC vs HEVC

# I.4.6 In-Loop Filters

In VVC, a remapping operation and three in-loop filters can be applied sequentially to the reconstructed picture to modify its representation domain and alleviate different types of artifacts. First, a new sample-based process called LMCS (Luma Mapping with Chroma Scaling) is performed. Then, a DBF is used to reduce blocking artifacts. SAO is then applied to the deblocked picture to attenuate ringing and banding artifacts. Finally, an Adaptive Loop Filter (ALF) reduces other potential distortion introduced by the quantization and transform processes. The deblocking filter design is based on the one in HEVC but is extended with longer deblocking filters and a luma-adaptive filtering mode designed specifically for HDR video. While SAO is the same as in HEVC, and the deblocking is very similar, LMCS and ALF are new compared with previous standards. The design of ALF in VVC consists of two operations: ALF with block-based filter adaption for both luma and chroma samples and a cross-component ALF (CC-ALF) for chroma samples.

Table I.1 summarizes the main coding tools of HEVC and VVC. VVC has adopted many new coding tools in each coding stage [MMS<sup>+</sup>21].

# I.5 Video Coding Challenges

During the last decade, multimedia services and video applications have significantly increased due to the huge progress in digital technologies. The emerging video applications and image representation offer an immersive and more natural viewing experience. However, these new services require both higher quality and resolution (4K, 8K) to satisfy the quality of service required by the end users. To meet the increasing demands for video content at better qualities and higher resolutions, video compression technology is being researched and developed, due to its higher performance. However, this unmatched performance is achieved by increasing the encoder computational complexity mainly due to its block partition structure. Indeed, the complexity reduction has always been a popular challenge in the video coding field. For example, Figure I.9 shows that the greatest complexity lies in the selection of the optimal prediction mode, especially in the inter-mode [CMMC19].

In this context, many researchers aim to reduce the complexity for each standard module through fast methods. The efficiency and versatility of recent Machine Learning based approaches paved the way for researching more extensive ways to integrate Machine Learning solutions into video coding schemes. In fact, they are able to achieve

Figure. I.9: Example of HEVC Time Profile

higher compression efficiency than older video compression technologies. In the next section, we will review the new technologies, such as Artificial Intelligence, Machine Learning and Deep Learning.

# I.6 Artificial Intelligence: New Advancements and Innovations

Artificial Intelligence (AI) is a branch of computer science that deals with simulation of human intelligence by machines processes and computational rationality. The term may also be applied to any machine that exhibits traits associated with a human mind such as learning and problem-solving. AI is a computer system able to perform tasks that normally require human intelligence, such as visual perception, speech recognition, decision making, and translation between languages. Machine learning and deep learning are subsets of AI, which are described in the following sections.

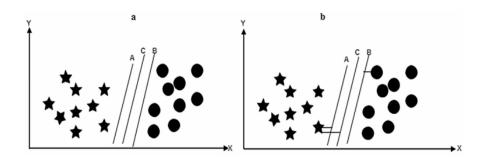

# I.6.1 Machine Learning