### Efficient Architectures for High-Performance Embedded Computing

Mostafa Rizk

#### ▶ To cite this version:

Mostafa Rizk. Efficient Architectures for High-Performance Embedded Computing. Hardware Architecture [cs.AR]. Université Bretagne Sud, 2022. tel-04063457

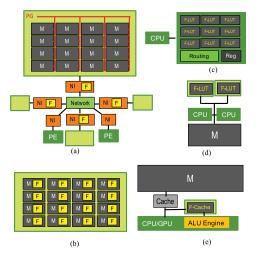

### HAL Id: tel-04063457 https://hal.science/tel-04063457

Submitted on 11 Apr 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# HABILITATION A DIRIGER DES RECHERCHES HDR

### L'UNIVERSITE BRETAGNE SUD

ECOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : STIC

### Par Mostafa RIZK

### Efficient Architectures for High-Performance Embedded Computing

Thèse présentée et soutenue à Brest, le 18/10/2022 Unité de recherche : Lab-STICC, UMR CNRS 6285 - 2AI team

#### Rapporteurs avant soutenance :

Ian O'CONNORProfesseur, Ecole Centrale de LyonMaurizio VALLEProfesseur, Université de GênesGuy GOGNIATProfesseur, Université Bretagne Sud

#### **Composition du Jury :**

| Rapporteurs :  | lan O'CONNOR         | Professeur, Ecole Centrale de Lyon                       |

|----------------|----------------------|----------------------------------------------------------|

|                | Maurizio VALLE       | Professeur, Université de Gênes                          |

|                | Guy GOGNIAT          | Professeur, Université Bretagne Sud                      |

| Examinateurs : | Amer BAGHDADI        | Professeur, IMT Atlantique                               |

|                | Adnan HARB           | Professeur, Lebanese International University            |

|                | Jean-Philippe DIGUET | Directeur de recherche CNRS, Head of CROSSING - IRL 2010 |

## Contents

| Co | ontent  | S                        | V |

|----|---------|--------------------------|---|

| Li | st of l | Rigures vi               | i |

| Li | st of [ | fables                   | X |

| De | edicat  | ion x                    | i |

| Gl | lossar  | y xii                    | i |

| Lo | ong A   | bstract xvi              | i |

| Ré | ésumé   | long xx                  | i |

| Pr | eface   | 1                        | 1 |

| I  | Det     | ailed Curriculum Vitae   | 3 |

| 1  | Rest    | ime                      | 5 |

|    | 1.1     | Summary                  | 5 |

|    | 1.2     | Professional Experiences | 7 |

|    | 1.3     | Educational Achievements | 8 |

|    | 1.4     | Training Courses         | 8 |

|    | 1.5     | Synergistic Activities   | 9 |

| 2  | Rese    | earch Experiences 11     | 1 |

|    | 2.1     | Research Topics          | 1 |

|    | 2.2     | Visiting Scholar         | 2 |

|    | 2.3     | Laboratory Membership    | 2 |

|    | 2.4   | Research Collaboration                                                     | 12 |

|----|-------|----------------------------------------------------------------------------|----|

|    | 2.5   | Involvement in Research Projects                                           | 13 |

|    | 2.6   | Publications                                                               | 14 |

|    | 2.7   | Supervision and Tutorship                                                  | 14 |

|    | 2.8   | Other Responsibilities and Activities                                      | 16 |

| 3  | Teac  | hing Experiences                                                           | 19 |

|    | 3.1   | Teaching and Administrative Responsibilities                               | 19 |

|    | 3.2   | Construction and Development of University Courses                         | 19 |

|    | 3.3   | Teaching University Courses                                                | 20 |

|    | 3.4   | Technical Training Courses                                                 | 23 |

| Ap | opend | ix A List of publications                                                  | 25 |

|    | A.1   | Book chapters                                                              | 25 |

|    | A.2   | Published journal papers                                                   | 25 |

|    | A.3   | Published international conferences                                        | 27 |

|    | A.4   | Published national conference papers                                       | 31 |

| Ap | opend | ix B Supervision Activities                                                | 33 |

| Ap | opend | ix C Contributions In Evaluation Committees                                | 37 |

| Ap | pend  | ix D Teaching Activities                                                   | 39 |

| II | 0     | verview of Past Research Activities                                        | 41 |

| In | trodu | ction to My Research Activities                                            | 43 |

| 4  | Flex  | ible and Efficient Architectures for Applications in Digital Communication | 45 |

|    | 4.1   | Preface                                                                    | 45 |

|    | 4.2   | Introduction                                                               | 45 |

|    | 4.3   | Context and Motivations                                                    | 46 |

|    | 4.4   | Contributions and Performed Work                                           | 50 |

|    | 4.5   | Findings                                                                   | 54 |

|    | 4.6   | Selected papers                                                            | 55 |

| 5  | Effic | cient Algorithms and Architectures for Dataflow Applications                       | 61    |

|----|-------|------------------------------------------------------------------------------------|-------|

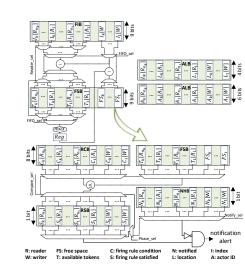

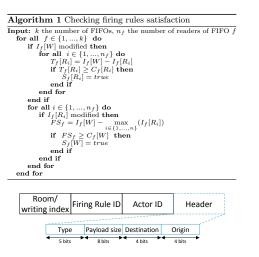

|    | 5.1   | Notifying Memories Concept                                                         | 61    |

|    | 5.2   | Run-Time Remapping of Dataflow Actors on NoC-based Heterogeneous MPSoCs            | 74    |

|    | 5.3   | Perspectives                                                                       | 83    |

| 6  | Flex  | ible and Efficient Architectures Based on Memristive Technologies                  | 103   |

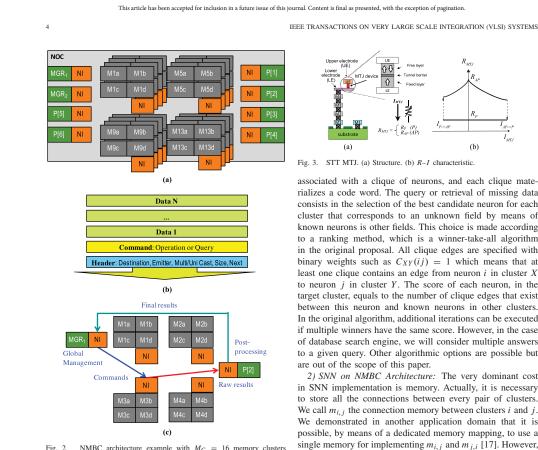

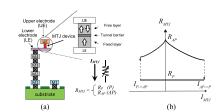

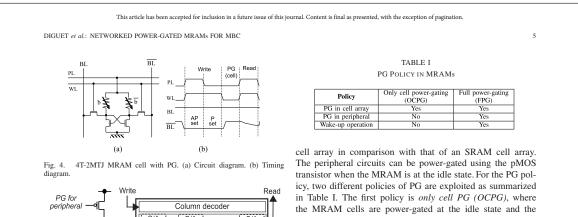

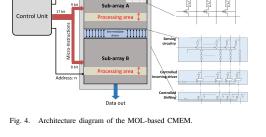

|    | 6.1   | Networked Power-Gated MRAMs for Memory-Based Computing                             | 103   |

|    | 6.2   | MRAM-based memorization system for NB-LDPC decoder                                 | 122   |

|    | 6.3   | Memristor Based Reconfigurable FFT Architecture                                    | 122   |

|    | 6.4   | Hybrid Memristor-CMOS Design for Logic Computation                                 | 127   |

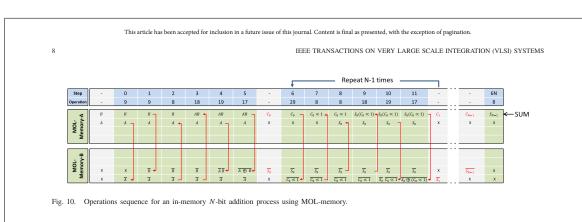

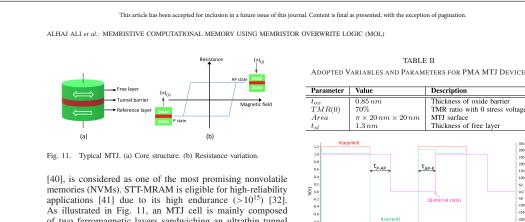

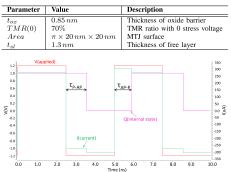

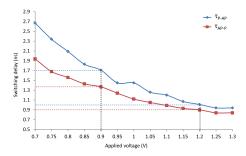

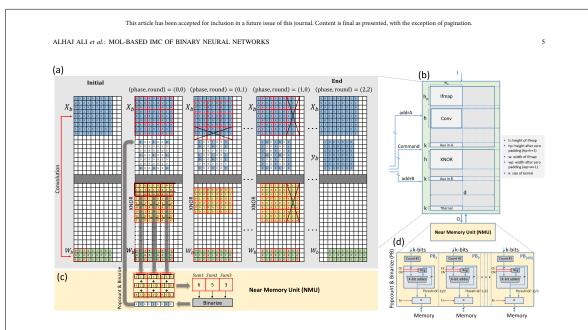

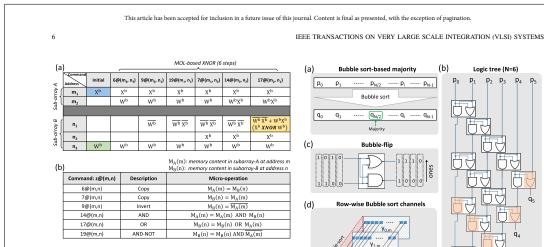

|    | 6.5   | Memristor Overwrite Logic (MOL) for In-Memory Computing                            | 148   |

| 7  | Effic | cient Implementations of Machine Learning Algorithms                               | 177   |

|    | 7.1   | Preface                                                                            | 177   |

|    | 7.2   | Introduction                                                                       | 177   |

|    | 7.3   | Context and Motivations                                                            | 178   |

|    | 7.4   | Contributions and Performed Work                                                   | 179   |

| II | I C   | Current Work and Future Directions                                                 | 223   |

| 8  | Ong   | oing Research Works                                                                | 225   |

|    | 8.1   | Preface                                                                            | 225   |

|    | 8.2   | Real-Time Visual SLAM Drone Navigation in GNSS-Denied Regions                      | 225   |

|    | 8.3   | Marine Objects Detection Using Deep Learning on Embedded Edge Devices              | 228   |

|    | 8.4   | Smart-Cameras Network for Multi-View AI-based Object Detection                     | 231   |

|    | 8.5   | Embedded AI to Assist Search and Rescue Missions                                   | 234   |

| 9  | Futi  | ire Research Directions                                                            | 239   |

|    | 9.1   | Design of Memory-centric Ultra-Low Power Processor                                 | 239   |

|    | 9.2   | Interactive Machine Learning on Edge Devices for Object Detection Appli-<br>cation | 239   |

|    |       |                                                                                    | • • • |

|    | 9.3   | Distributed Learning on Connected Devices                                          | 240   |

# **List of Figures**

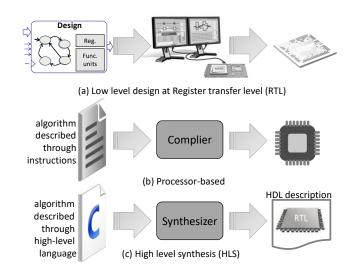

| 4.1 | Traditional available design approaches                                                           | 47  |

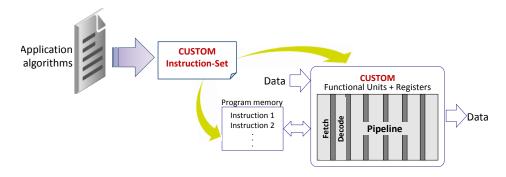

|-----|---------------------------------------------------------------------------------------------------|-----|

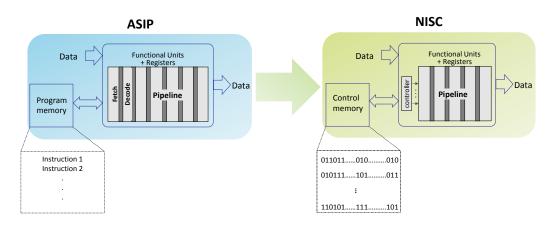

| 4.2 | ASIP design approach                                                                              | 47  |

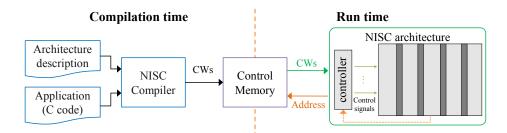

| 4.3 | Transition from ASIP to NISC design approach                                                      | 48  |

| 4.4 | NISC designing approach stages                                                                    | 49  |

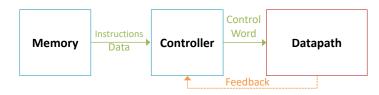

| 4.5 | General processor block diagram                                                                   | 49  |

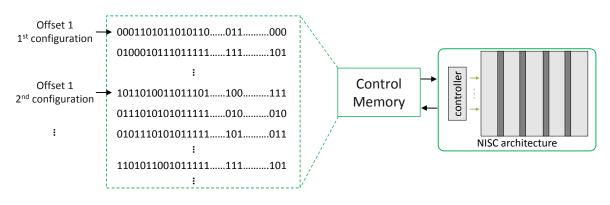

| 4.6 | Dynamic flexibility in NISC                                                                       | 50  |

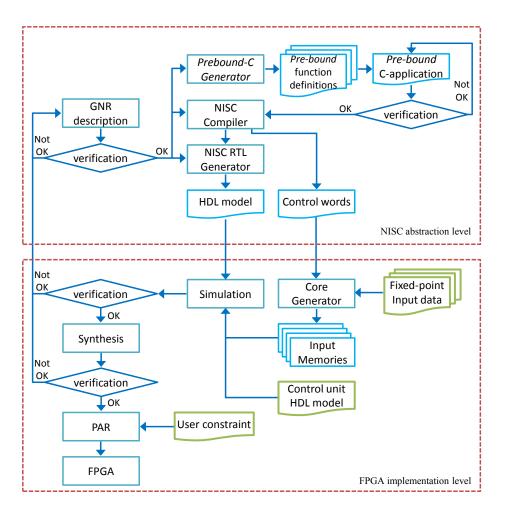

| 4.7 | Adopted design flow [1]                                                                           | 53  |

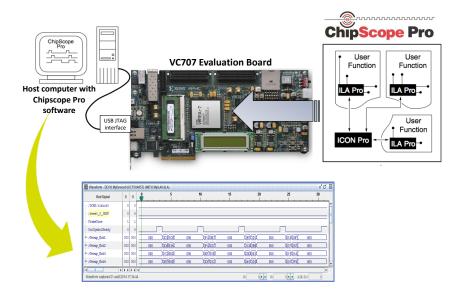

| 4.8 | On-board validation using Xilinx ChipScope Pro Analyzer                                           | 54  |

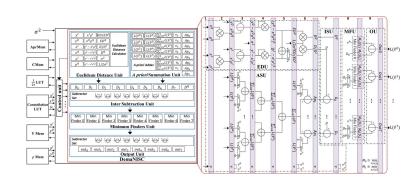

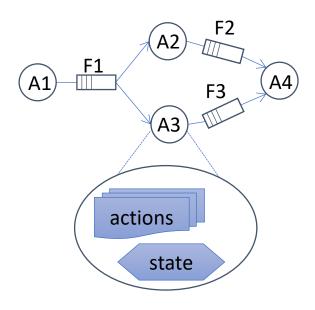

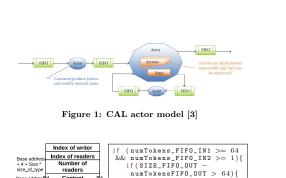

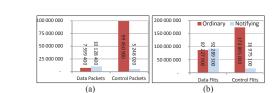

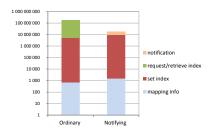

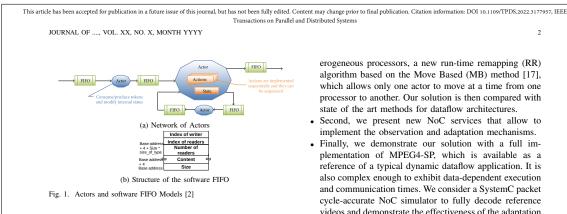

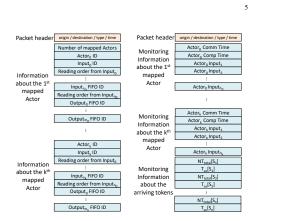

| 5.1 | Actor network model                                                                               | 63  |

| 5.2 | Structure of a software FIFO generated by Orcc tool                                               | 64  |

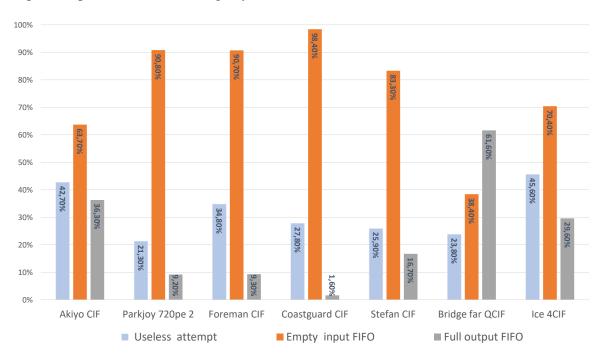

| 5.3 | Useless scheduling attempts by the MPEG4-SP decoder for different video .                         | 65  |

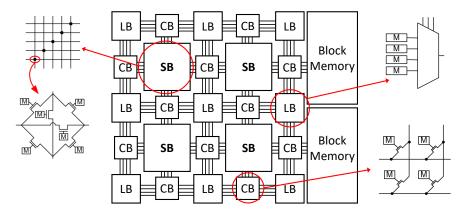

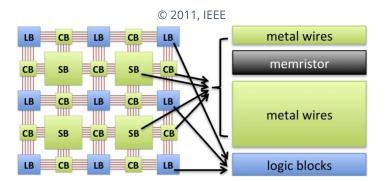

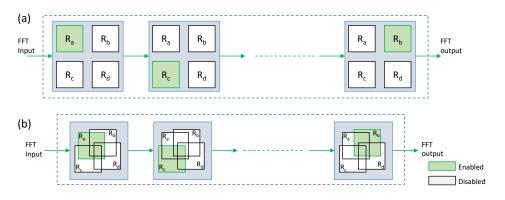

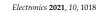

| 6.1 | Conventional FPGA architecture                                                                    | 124 |

| 6.2 | Memristor based-programmable routing structure for FPGA proposed in [2]                           | 124 |

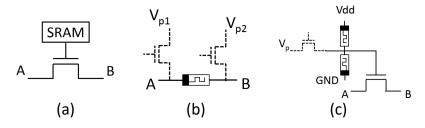

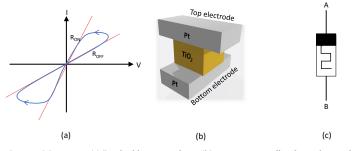

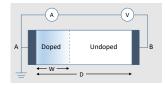

| 6.3 | Memristive switches: (a) 7T SRAM routing switch, (b) 2T1R routing switch, (c) 2T2R routing switch | 125 |

| 6.4 | The block diagram of the reconfigurable FFT                                                       | 125 |

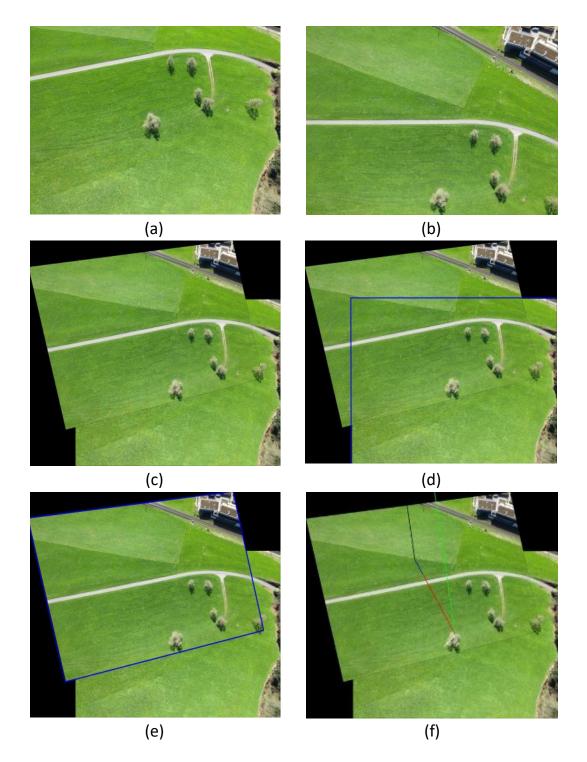

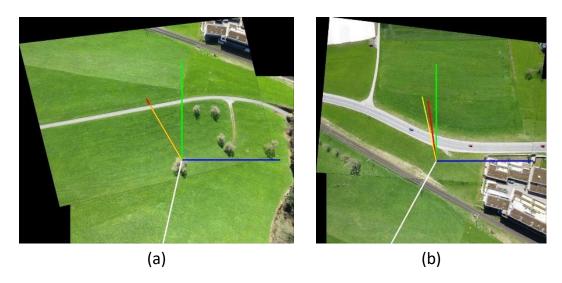

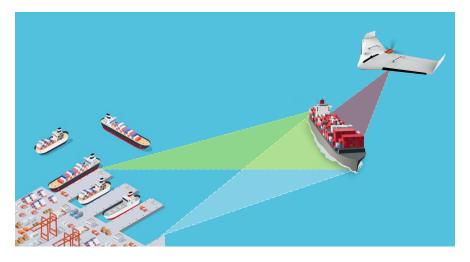

| 8.1 | Sample application of the proposed method                                                         | 227 |

| 8.2 | Bearing angle comparison results                                                                  | 228 |

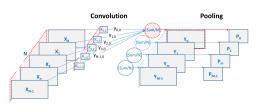

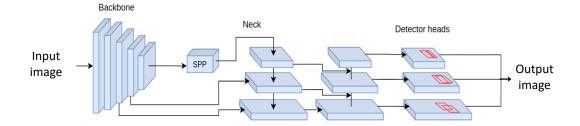

| 8.3 | Block diagram of YOLOv4 network                                                                   | 229 |

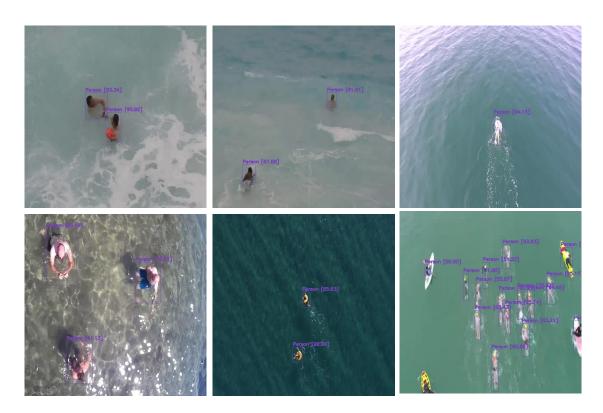

| 8.4 | Sample predictions of marine objects using the trained model                                      | 230 |

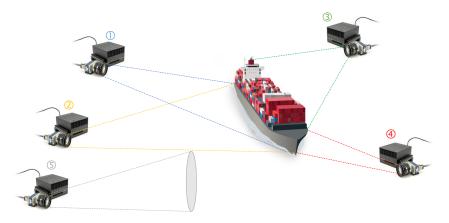

| 8.5 | Overview of the proposed multi-view smart-camera network                                          | 232 |

| 8.6 | Overview of the proposed top-view detection to assist multi-view marine object surveillance       | 233 |

| 8.7 | Sample detection results using the testing dataset images                                         | 236 |

| 8.8 | Samples of the obtained detection results using recorded video sequences .                        | 236 |

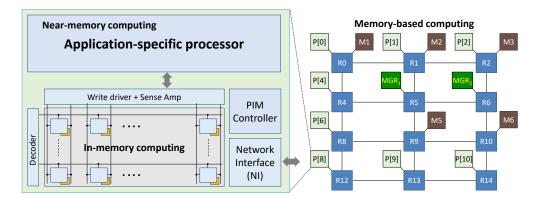

| 9.1 | Target architecture model combining PIM, MBC and NMC                                              | 240 |

# **List of Tables**

| <b>B</b> .1 | Supervised Master theses at Lab STICC and IMT Atlantique                  | 33 |

|-------------|---------------------------------------------------------------------------|----|

| B.2         | Supervised Master theses at Lebanese University                           | 34 |

| B.3         | Supervised Master theses at Lebanese International University             | 35 |

| B.4         | Supervised senior projects                                                | 36 |

|             |                                                                           |    |

| C.1         | Senior projects I have participated in their evaluation committees        | 37 |

| C.2         | Master theses I have participated in their evaluation committees          | 38 |

|             |                                                                           |    |

| D.1         | Taught courses at American University of Culture and Education, Lebanon . | 39 |

| D.2         | Taught courses at Lebanese University                                     | 39 |

| D.3         | Taught courses at Lebanese International University                       | 40 |

# Dedication

To my family

# Glossary

| 2D     | Two Dimensions                                  |

|--------|-------------------------------------------------|

| GPP    | $3^{rd}$ Generation Partnership Project         |

| 5G     | 5 <sup>th</sup> Generation Mobile Networks      |

| ACT    | Approximate Computing Technique                 |

| ADL    | Architectural Description Language              |

| AI     | Artificial Intelligence                         |

| AIS    | Automatic Identification System                 |

| ALU,   | Arithmetic Logic Unit                           |

| ALTD,  | Average-link Token Delay                        |

| APTD,  | Average-path Token Delay                        |

| ASIC   | Application-Specific Integrated Circuit         |

| ASIP   | Application-Specific Instruction-set Processor  |

| ASP    | Application Specific Processors                 |

| AWGN   | Additive White Gaussian Noise                   |

| BF     | Butterfly                                       |

| BNN    | Binary Neural Network                           |

| СВ     | Connection Block                                |

| СТР    | Code transferring packet                        |

| CNN    | Convolutional Neural Networks                   |

| CMEM   | Computational Memory                            |

| CMOS   | Complementary Metal–Oxide–Semiconductor         |

| COCO   | Common Object in Context                        |

| CPU    | Central Processing Unit                         |

| CV     | Computer Vision                                 |

| CW     | Control Word                                    |

| DF     | Dataflow                                        |

| DRP    | Data Reading Request Packets                    |

| DNN    | Deep Neural Network                             |

| DVB    | Digital Video Broadcasting                      |

| ECDIS  | Electronic Chart Display and Information System |

| e-skin | Electronic skin                                 |

| EU     | European Union                                  |

| FIP    | FIFO Index Packet                               |

| FIR    | Finite Impulse Response                         |

| FFT    | Fast Fourier Transform                          |

| FPG    | Full Power Gating                               |

|        |                                                 |

| FPGA                        | Field Programmable Gate Array                         |

|-----------------------------|-------------------------------------------------------|

| FLOPS                       | Floating Point Operations Per Second                  |

| FPS                         | Frames Per Second                                     |

| GNSS                        | Global Navigation Satellite System                    |

| GPGPU                       | General-Purpose Computing on Graphics Processing Unit |

| GPS                         | Global Positioning System                             |

| GPU                         | Graphics Processing Unit                              |

| H-BWN                       | Hybrid-precision Binary Weight Network                |

| HCNN                        | Hybrid Fixed-point Binary Convolution Neural Network  |

| HDL                         | Hardware Description Language                         |

| HLS                         | High-Level Synthesis                                  |

| HMA                         | Horizontal Microcoded Architectures                   |

| HP                          | Hewlett-Packard                                       |

| HRS                         | High Resistance State                                 |

| IMC                         | In-Memory Computing                                   |

| INS                         | Inertial Sensors                                      |

| ISA                         | Instruction Set Architecture                          |

| KPN                         | Kahn Process Network                                  |

| kNN                         | k-Nearest Neighbor                                    |

| LDPC                        | Low Density Parity Check Codes                        |

| LiDAR                       | Light Detection and Ranging                           |

| LLR                         | Log Likelihood Ratio                                  |

| LRS                         | Low Resistance State                                  |

| LTE                         | Long Term Evolution                                   |

| LTE-A                       | Long Term Evolution Advanced                          |

| MAGIC                       | Memristor Aided Logic                                 |

| mAP                         | Mean Average Precision                                |

| $\mathbf{M}_p \mathbf{IP}$  | Mapping Information Packet                            |

| MB                          | Move Based                                            |

| MBC                         | Memory-based Computing                                |

| MAJ                         | Memristor-based Majority                              |

| MCP                         | Mapping Confirmation Packet                           |

| MIMO                        | Multiple-Input Multiple-Output                        |

| $\mathbf{M}_{n}\mathbf{IP}$ | Monitoring Information Packet                         |

| ML                          | Machine Learning                                      |

| MMSE-IC                     | Minimum Mean Square Error-Interference Canceler       |

| MoC                         | Model of Computation                                  |

| MOL                         | Memristor Overwrite Logic                             |

| MPEG                        | Moving Picture Experts Group                          |

| MPSoC                       | Multi-processor System-on-Chip                        |

| MRAM                        | Magnetoresistive Random-Access Memory                 |

| mrFPGA                      | Memristor-based Reconfiguration mrFPGA                |

| MRL                         | Memristor Ratioed Logic                               |

| MTJ                         | Magnetic Tunnel Junction                              |

| <b>NB-LDPC</b>              | Binary-Low Density Parity Check                       |

| NI                          | Network Interface                                     |

|                             |                                                       |

| NISC            | No Instruction Sot Computer                                |

|-----------------|------------------------------------------------------------|

| NoC             | No-Instruction-Set-Computer<br>Network-on-Chip             |

| NMBC            | NoC-Memory Based Computing                                 |

| NP              | Notification Packet                                        |

| NM              | Notifying Memories                                         |

| NMC             | Near-Memory Computing                                      |

| NVM             | Nonvolatile Memory                                         |

| OCPG            | Only Cell Power Gating                                     |

| OFDM            | Orthogonal Frequency Division Multiplexing                 |

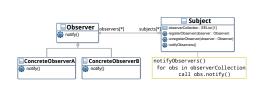

| OOP             | Object Oriented Programming                                |

| Orcc            | Open RVC-CAL Compiler                                      |

| РСВ             | Printed Circuit Board                                      |

| PE              | Processing Element                                         |

| PG              | Power Gating                                               |

| PIM             | Processing-In-Memory                                       |

| PLDs            | Programmable Logic Devices                                 |

| QoS             | Quality of Service                                         |

| RBF             | reconfigurable Butterfly                                   |

| <b>R-CNN</b>    | Region-Convolutional Neural Network                        |

| RTOS            | Real Time Operating System                                 |

| RR              | Run-time Remapping                                         |

| RTL             | Register Transfer Level                                    |

| RVC             | Reconfigurable Video Coding                                |

| SB              | Switch Block                                               |

| SIFT            | Scale Invariant Feature Transform                          |

| SISO            | Single-Input-Single-Output                                 |

| SLAM            | Simultaneous Localization and Mapping                      |

| SNN             | Sparse Neural Networks                                     |

| SoC             | System-on-Chip                                             |

| SoP             | Sum of Products                                            |

| SRAM            | Static Random-Access Memory                                |

| SSD<br>STT MDAM | Single Shot Detector                                       |

| STT-MRAM<br>STM | Spin-Transfer-Torque Magnetoresistive Random-Access Memory |

| SVD             | Scenario-based Run-time Task Mapping                       |

| SVD<br>SVM      | Singular Value Decomposition<br>Support Vector Machine     |

| TSVM            | Tensorial SVM                                              |

| UAV             | Unmanned Aerial Vehicle                                    |

| VIA             | Vertical Interconnect Access                               |

| WiMax           | Worldwide Interoperability for Microwave Access            |

| WiFi            | Wireless Fidelity                                          |

| X-MRL           | Crossbar Memristor Ratioed Logic                           |

| YOLO            | You Only Look Once                                         |

|                 | <b>,</b>                                                   |

### Long Abstract

This Habilitation to supervise research presents the numerous research activities performed since 20114 targeting the development of flexible and efficient architectures for high performance embedded computing.

The presented research activities aim at the realization of flexible and efficient architectures in multitude application domains such as digital communication, data-flow, neural networks, embedded machine learning and embedded vision. These research works have addressed the design and implementation of novel hardware architectures aiming to attain the emergent flexibility requirement, and the ever-increasing requirements of enhanced performance and reduced power consumption and implementation resources. The performed work has targeted the elaboration of new algorithms and hardware architectures using different design paradigms. Several approaches have been adopted including (1) the demonstration of design approaches that lead to better exploiting of resources; (2) making use of optimization techniques such as approximate computing, quantization, and building dedicated hardware architectures; (3) refinement of available algorithms or proposing new algorithms that enhance the performance; (4) exploiting the technological advancements especially related to memristive devices; (5) tackling emergent computing styles such as smart memory architectures, memory-based computing and in-memory computing and (6) benefiting from MPSoC design approaches.

In this context, several research works have been initiated through completed or ongoing research projects, two defended PhD theses and several Master theses. The most significant achievements are presented by grouping them in four sub-themes: (1) Flexible yet efficient architectures for applications in the digital communication domain; (2) Efficient algorithms and architectures for dataflow applications; (3) Efficient and flexible design paradigms based

on emergent memristive devices and (4) Efficient implementations of machine learning algorithms.

In the first theme, the No-Instruction-Set-Computer (NISC) design methodology is explored to design dedicated modules of turbo receiver. Two NISC-based architectures are demonstrated. The obtained results in terms of performance and implementation area confirm the feasibility of adopting NISC concept in designing flexible yet efficient applicationspecific processors in the domain of digital communications.

In the second theme, the novel Notifying Memories (NM) concept is introduced to eliminate useless accesses to memories. Memories are transferred into masters that notify processors when the data is ready to be processes. The use of the NM concept leads to significant reductions in latency, injection rate, transported flits and switch conflicts. Also, the throughput is highly enhanced while saving power. In addition, a novel remapping algorithm and network-on-chip (NoC)-based architecture design are proposed to cope with the dynamicity of dataflow actors.

In the third theme, memristive devices are adopted to enhance the computing performance. First, memory-based computing on NoC architecture is introduced by making use of emergent non-volatile memories with power-gating capabilities to enhance the performance and attain low power consumption. In addition, the use of memristors to design architectures which combine flexibility and efficiency, has been explored and introduced through the proposal of original architectures that break the limits of the existing ones. The exploration and study have been conducted in three main levels: (1) interconnect level, (2) processing level and (3) memory level.

The fourth theme focuses on the design and implementation of efficient machine learning algorithms targeting the tactile sensing application. In particular, approximate computing techniques and designing of custom hardware accelerators are adopted to reduce the computational complexity and achieve higher performance with low power consumption.

Current research activities focus on embedded computer vision (CV) and artificial intelligence (AI) with the goal of achieving efficient implementations on edge devices with low computational resources and low power budget. The application domains are real-time drone navigation, marine object detection using deep learning and multi-view object detection. Results achieved so far are novel and very encouraging.

Concerning the research perspectives, in the short and medium term, several perspectives are proposed: interactive machine learning on edge devices for object detection application, distributed learning on connected devices and tiny machine learning. In the longer term, it is planned to focus on building memory centric low-power processor.

## **Résumé long**

Ce mémoire d'habilitation à diriger des recherches présente mes nombreuses activités de recherche menées depuis 2014 visant le développement d'architectures flexibles et efficaces pour le calcul embarqué haute-performance.

Les activités de recherche présentées visent la proposition et la conception d'architectures flexibles et efficaces dans plusieurs domaines applicatifs tels que la communication numérique, les flots de données, les réseaux de neurones, l'apprentissage automatique et la vision embarquée. Ces travaux de recherche ont porté sur la conception et la mise en œuvre de nouvelles architectures matérielles visant à répondre aux exigences émergentes en matière de flexibilité, ainsi qu'aux exigences toujours plus grandes en termes de performances et de réduction de la consommation d'énergie et des ressources matérielles. Plusieurs approches ont été explorées, notamment : (1) la démonstration d'approches de conception permettant une meilleure exploitation des ressources, (2) l'utilisation de techniques d'optimisation telles que le calcul approximatif, la quantification et la construction d'architectures matérielles dédiées, (3) l'optimisation d'algorithmes existants ou la proposition de nouveaux algorithmes améliorant les performances, (4) l'exploitation des avancées technologiques, notamment en ce qui concerne les dispositifs memristifs, (5) la prise en compte des paradigmes de calcul émergents tels que le calcul en mémoire et les architectures de mémoire intelligente et (6) la mise à profit des approches de conception de MPSoC.

Dans ce contexte, plusieurs travaux de recherche ont été initiés à travers des projets de recherche terminés ou en cours, deux thèses de doctorat soutenues et plusieurs thèses de Master. Les réalisations les plus significatives sont présentées en les regroupant en quatre sous-thèmes : (1) Architectures flexibles et efficaces pour des applications dans le domaine des communications numériques, (2) Algorithmes et architectures efficaces pour des applica-

tions de flot de données, (3) Paradigmes de conception efficaces et flexibles basés sur des dispositifs memristifs émergents et (4) Implémentations efficaces d'algorithmes d'apprentissage automatique.

Dans le premier thème, la méthodologie de conception No-Instruction-Set-Computer (NISC) est explorée pour concevoir des accélérateurs dédiés aux récepteurs itératifs. Deux architectures basées sur NISC sont proposées et conçues. Les résultats obtenus en termes de performance et de surface confirment la pertinence de l'adoption du concept NISC dans la conception de processeurs flexibles et efficaces dans le domaine des communications numériques.

Dans le deuxième thème, le nouveau concept de Notifying Memories (NM) est introduit pour éliminer les accès inutiles aux mémoires. Les mémoires sont transposées dans des maîtres qui informent les processeurs lorsque les données sont prêtes à être traitées. L'utilisation du concept NM conduit à des réductions significatives de la latence, du taux d'injection, les flits transportés, des conflits de commutation. De plus, le débit est fortement amélioré tout en réduisant la consommation énergétique. En outre, un nouvel algorithme de remapping et une architecture basée sur un réseau-sur-puce (NoC) sont proposés pour faire face à la dynamicité des acteurs du flot de données.

Dans le troisième thème, les dispositifs memristifs sont explorés. Tout d'abord, une nouvelle architecture de NoC avec du calcul basé sur mémoire est introduite en utilisant des mémoires non-volatiles pour améliorer les performances et réduire la consommation énergétique. En outre, l'utilisation des memristors pour concevoir des architectures combinant flexibilité et efficacité a été explorée et introduite par la proposition d'architectures originales qui dépassent les limites des architectures existantes. L'exploration et l'étude ont été menées à trois niveaux : (1) au niveau des interconnexions, (2) au niveau du traitement et (3) au niveau de la mémoire.

Le quatrième thème porte sur la conception et la mise en œuvre d'algorithmes efficaces d'apprentissage automatique ciblant l'application de détection tactile. En particulier, des techniques de calcul approximatif et la conception d'accélérateurs matériels dédiés sont investiguées pour réduire la complexité du calcul et atteindre des performances plus élevées avec une faible consommation d'énergie. Mes activités de recherche actuelles se concentrent sur la vision par ordinateur et l'intelligence artificielle embarquées dans le but de réaliser des implémentations efficaces sur des dispositifs embarqués avec de faibles ressources de calcul et un faible budget énergétique. Les domaines d'application concernent la navigation de drones en temps réel, la détection d'objets marins par apprentissage profond et la détection d'objets avec multi-vues. Les résultats obtenus jusqu'à présent sont originaux et très encourageants.

En ce qui concerne les perspectives de recherche, à court et à moyen terme, plusieurs pistes sont proposées : l'apprentissage automatique interactif sur les dispositifs embarqués pour les applications de détection d'objets, l'apprentissage distribué sur dispositifs connectés et l'apprentissage machine embarqué (TinyML). À plus long terme, il est prévu d'explorer la construction de processeurs basse consommation centrés sur la mémoire.

## Preface

This document represents my Habilitation thesis manuscript. It summarizes my academic and professional career including recent and future research activities. It is organized as follows:

The first part includes my detailed Curriculum Vitae. It includes 3 chapters. Chapter 1 presents my personal resume. Chapter 2 and Chapter 3 provide my research and teaching experiences respectively.

The second part gives a high level view on my previous research activities. It includes 4 chapters:

- Chapter 4 presents the first research topic related to the proposal of flexible and efficient architectures for applications in digital communication.

- Chapter 5 presents the second research topic related to efficient algorithms and architectures for dataflow applications.

- Chapter 6 presents the third research topic that tackles the use of memristive devices in realizing efficient hardware architectures.

- Chapter 7 presents the fourth research topic about designing efficient hardware architectures for machine learning algorithms.

The third part provides a brief review of current research work (Chapter 8) and long-term future work (Chapter 9).

# Part I

## **Detailed Curriculum Vitae**

### **Chapter 1**

### Resume

#### **Current professional address**

Lab-STICC UMR CNRS 6285 IMT Atlantique – MEE Department Technopôle Brest-Iroise — CS 83818 29238 Brest Cedex 3 France Phone : +33 2 29 00 15 95 Fax : +33 2 29 00 11 84 Email : mostafa.rizk@imt-atlantique.fr Web : https://sites.google.com/liu.edu.lb/mostafa-rizk/

#### **1.1 Summary**

I received my Maitrise degree in Electronics, M.Sc in Biomedical Physics, and M.Sc in Signal, Telecom, Image, and Speech from the Lebanese University in 2007, 2008 and 2010 respectively. Then, I pursued my Ph.D. degree in Sciences and Technologies of Information and Communication from IMT Atlantique (former Telecom Bretagne) in France in 2014.

Then, I was a post-doctoral researcher at University of Bretagne Sud (UBS) and the Laboratory of Science and Technology of Information, communication, and Knowledge (Lab-STICC), CNRS, UMR 6285, in Lorient, France. Later in 2016, I joined the Lebanese International University in Lebanon as an assistant and then associate professor at the Computer and Communication Engineering Department. Currently, I am working at Lab-STICC UMR 6825 CNRS/IMT Atlantique in Brest, France where I am conducting my research in the domain of embedded deep learning and embedded computer vision.

My research activities have been conducted at Lab-STICC. In particular, I performed my research work with in three teams: the team specialized in the Interaction between Algorithm and Silicon (IAS), the team specialized in Methods, tOols, Circuits and Systems (MOCS),

and the team specialized in Algorithm Architecture Interactions (2AI) in collaboration with research laboratories in Lebanon.

The performed research work has focused on the hardware/software co-design for embedded architectures, circuits and systems. It stands at the crossing point between development and refinement of algorithms and designing digital embedded architectures. My conducted research has been supported in several projects and has been valorized through a number of publications in well reputable journals and through international and national conferences.

Since I defended my PhD in the end of 2014, which addressed the topic of designing novel flexible and efficient implementations for applications in the domain of digital communication, I have been doing research consistently in the domain of embedded systems targeting the realization of flexible and efficient architectures with reduced power implementations in multitude application domains. My research work has tackled emergent topics such as smart memory architectures, memory-based computing and in-memory computing. An important work has been done to investigate adopting novel non-volatile memory technologies and memristive devices to achieve flexible architectures with reduced power consumption. My research work has addressed the design and implementation of novel hardware architectures for applications in the fields of data-flow, embedded machine learning, embedded vision, and embedded intelligence aiming to attain the emergent flexibility requirement, and the ever increasing requirements of enhanced performance and reduced power consumption. The performed work has targeted the elaboration of new algorithms and hardware architectures in these fields.

During the last seven years, I have been involved in a number of research projects. I participated in the supervision of two successfully defended Ph.D theses. I was the direct tutor for several Master theses and undergraduate projects. Also, I served as member in several evaluation committees and participated in a number of theses juries.

My teaching activities lay in the domains of electronics, computer and communication engineering and informatics for undergraduate and graduate levels.

### **1.2 Professional Experiences**

| 2021-present | Contractual researcher at Lab-STICC, CNRS, UMR 6285, France                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2017–present | Instructor at the Lebanese University, Faculty of Sciences, Physics and Electronics Department, Hadat, Lebanon                                                         |

| 2016–present | Associate professor at the Lebanese International University (LIU),<br>School of Engineering, Department of Communication and Computer<br>Engineering, Beirut, Lebanon |

| 2017-2020    | Associate researcher at Institute Mines-Télécom, IMT Atlantique, Brest, France                                                                                         |

| 2015-2016    | Post-doctoral fellow at UBS, Lorient, France and Methods, tOols, Circuits and Systems (MOCS) research team at Lab-STICC                                                |

| 2014–2015    | Research Engineer at UBS, Lorient, France and MOCS research team at Lab-STICC                                                                                          |

| 2011–2012    | Instructor at the American University of Culture and Education (AUCE),<br>Lebanon, Faculty of Arts and Sciences, Department of Computer Sci-<br>ences                  |

| 2009–2010    | Six-month research internship at advanced data management company (ADM), Lebanon                                                                                       |

| 2007–2008    | Six-month professional internship at quality department and biomedical engineering department at RAH, Lebanon                                                          |

| 2008–2011    | Freelancing engineering projects (electronics, embedded systems and as-<br>sembly)                                                                                     |

|              |                                                                                                                                                                        |

#### **1.3 Educational Achievements**

| 2011–2014 | Doctorate's degree                                                                                                                    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

|           | <b>Organizations</b> : Institute Mines Télécom, IMT Atlantique (former Télécom Bretagne), France and Lebanese University              |

|           | <b>Laborartory</b> : Laboratory of Science and Technology of Information, Com-<br>munication and Knowledge (Lab-STICC) CNRS, UMR 6285 |

|           | <b>Major</b> : Information and Communication Sciences and Technologies and Electronics and Telecommunication                          |

|           | Distinction: Very honorable                                                                                                           |

| 2009–2010 | Research Master's degree                                                                                                              |

|           | <b>Organization</b> : Lebanese University, Doctoral School of Sciences and Technology, Lebanon                                        |

|           | Major: Signal, Telecoms, Image and Speech (STIP)                                                                                      |

| 2008–2009 | Professional Master's degree                                                                                                          |

|           | Organization: Lebanese University, Faculty of Sciences, Lebanon                                                                       |

|           | Major: Biomedical physics; Option: Quality control                                                                                    |

| 2006–2007 | Teaching diploma in sciences                                                                                                          |

|           | Organization: Lebanese University, Faculty of Sciences, Lebanon                                                                       |

|           | Major: Physics; Option: Electronics                                                                                                   |

| 2003-2006 | License degree of science                                                                                                             |

|           | Organization: Lebanese University, Faculty of Sciences, Lebanon                                                                       |

|           | Major: Physics; Option: Electronics                                                                                                   |

| 2002–2003 | Baccalaureate in sciences                                                                                                             |

### 1.4 Training Courses

- Scientific Computing Accelerated on FPGA: Three-day training on Vitis HLS (AMD-XilinX) and OneAPI (Intel) to accelerate scientific computing on FPGAs at Maison de la Simulation, Saclay, France.

- **Developing Accelerators using Vitis and PYNQ**: Full-day tutorial about Vitis development flow for compute acceleration on Xilinx FPGA; Xilinx University Program

- **Channel Coding**: Five-day training course about channel coding at Télécom Bretagne, Brest, France.

- Networks and Telecommunications: Twenty-hour training course about advanced architectures of stationary and mobile telecom at Doctoral School of Sciences and Technology, Lebanese University, Lebanon.

- Information Systems: Twenty-hour training course about information systems at Doctoral School of Sciences and Technology, Lebanese University

- Scientific English: Five-day training course about scientific English language at Télécom Bretagne, Brest, France.

- **Design Methodologies for Adaptive Circuits and Systems**: Full-day tutorial about designing adaptive circuits at IEEE Automation and Test in Europe Conference (DATE'13).

#### **1.5** Synergistic Activities

- 2016–2017 Member of the evaluation committee of SoC exhibition at LIU, Lebanon

- 2012–2014 Member of planning committee of IEEE student branch at Télécom Bretagne

- 2008–2009 Participation in organizing the PhD student day of ED-SICMA, Brest, France

## **Chapter 2**

## **Research Experiences**

### 2.1 Research Topics

My research topics are mainly focused on the hardware/software co-design. My main interests stand at the crossing point between algorithm development and digital architecture design for embedded systems including but not limited to:

- Digital design of flexible processing systems

- Intellectual Properties for wireless communication

- Hardware/software implementations

- Application Specific Processors (ASP)

- Network-on-Chip (NoC) design

- Embedded systems design in the fields of audio, video, and data-flow domains

- Embedded Multi-processor System-on-Chip (MPSoC) architectures

- Embedded systems based on emerging non-volatile memory technologies

- · Memory-based computing, near-memory computing and in-memory computing

- · Algorithm development and refinement for digital base-band components

- Algorithm development for task scheduling on MPSoC

- Embedded computer vision

- Embedded machine learning

## 2.2 Visiting Scholar

| December 2019  | visiting professor, UBS and Lab STICC, Lorient, France |

|----------------|--------------------------------------------------------|

| September 2018 | visiting professor, IMT-Atlantique, Brest, France      |

| September 2017 | visiting professor, Lab-STICC CNRS 6285, Brest, France |

## 2.3 Laboratory Membership

| 2010-2014    | member of TTS research group at Hasan Kamel Sabbah Lab at the<br>Lebanese University - Faculty of Sciences, Hadat, Lebanon                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 2011–2014    | member of the research team specialized in the Interaction between Algo-<br>rithm and Silicon (IAS) in Lab-STICC, CNRS, UMR 6285, Brest, France |

| 2014–2016    | member of the research team specialized in Methods, tOols, Circuits and Systems (MOCS) in Lab-STICC, CNRS, UMR 6285, Brest, France              |

| 2016-2017    | member of the research team specialized in Electronics in EEE depart-<br>ment at the Lebanese International University, Beirut, Lebanon         |

| 2017–present | member of the research team specialized in Algorithm Architecture In-<br>teractions (2AI) in Lab-STICC, CNRS, UMR 6285, Brest, France           |

## 2.4 Research Collaboration

The following list enumerates the institutes where I share research activities:

- CROSSING IRL 2010, Australia

- University of Genoa, Italy

- Université Bretagne Sud, France

- Tohoku University, Japan

- American University of Culture and Education, Lebanon

- American University of Beirut, Lebanon

- Lebanese University, Lebanon

- Lebanese International University, Lebanon

## 2.5 Involvement in Research Projects

I participated in the following research projects:

- 1. Mobile and wireless communications Enablers for Twenty-twenty Information Society (METIS):

- **Goal**: aims to lay the foundation of 5G, the next generation mobile and wireless communications system

- **Funding**: co-funded by the European Commission as an Integrated Project under the Seventh Framework Program for research and development (FP7)

- My Role: PhD student

- 2. Design Oriented Model of Computation for Embedded and Adaptive Multiprocessor (COMPA):

- Goal: aims to propose generic models for adaptive multi-processors embedded systems

- **Partners**: gathers three laboratories in Bretagne region (Lab-STICC, IETR, and IRISA)

- **Funding**: funded by the French National Research Agency (ANR, project ANR-11-INSE-0012)

- My Role: Research Engineer

- 3. Hierarchical Hardware Architectures Based on Associative-Memories and Network on Chips for Cyber-Attack Detection in Telecom Networks (CyAM):

- Goal: aims to exploit associative-memories and network on chips in Cyber-Attack detection

- **Partners**: conducted as collaboration between Lab-STICC and University of Tohoku in Japan

- Funding: funded by Bretagne region, France

- My Role: Post-doc Researcher

# 4. Optimization of Observation, Detection, Classification and Tracking of Seaships for Maritime Security by Mean of Embedded Deep Learning (ODESSA)

- **Goal**: aims to offer a new optoelectronic system that can detect a maritime security problem as early as possible while costing less than a radar tool

- **Partners**: conducted as collaboration between Lab STICC (IMT Atlantique and UBS) and two French Companies: Exavision and Inpixal

- Funding: funded by Bretagne region, France

- My Role: Post-doc Researcher

- 5. Deployment of electro-optical sensors and drones for living human detection and localization in search and rescue missions

- **Goal**: aims to demonstrate a novel low-cost solution that makes use of the availability and the affordability of drones to enhance detecting and locating wounded and lost individuals during and after disasters.

- Funding: funded by the Lebanese University

- My Role: Project technical leader

### 2.6 Publications

The results of my research activities led to the following publications:

- 1 Ph.D. thesis

- 2 Master theses

- 2 Book chapters

- 18 Journal papers

- 34 international conference papers

- 5 national conference papers

Further information about the publications is detailed in Appendix A.

### 2.7 Supervision and Tutorship

I have been involved in supervision and tutorship of 2 Ph.D. theses, 24 Master theses and 14 graduation projects.

#### 2.7.1 Supervision of Ph.D. Theses

- 1. **Supervision of the Ph.D. thesis of Dr. Hamoud Younes** Post doctoral fellow at IMT Atlantique, Brest, France

- **Title**: Embedded machine learning emphasis on hardware accelerators and approximate computing for tactile data processing

- Academic Years: 2018-2021

- University: University of Genoa, Italy

- 2. Supervision of the Ph.D. thesis of Dr. Khaled Alhaj Ali Post doctoral fellow at IMTAtlantique, France

- **Title**: New design approaches for flexible architectures and in-memory computing based on memristor technologies

- Academic Years: 2016-2020

- University: IMT Atlantique, Brest, France

### 2.7.2 Supervision of Master Theses

Since 2015, I have supervised the several Master theses in different universities. The following list presents these theses classified according to universities and the Master's programs.

- 1. Supervision of Master theses at Lebanese University, Lebanon:

- 4 Master theses in the program of the professional Master's degree of Sciences in Field Electro-Mechanical Engineering

- 1 Master thesis in the program of the professional Master's degree of Sciences in Medical Physics and Imaging Technologies

- 3 Master theses in the program of the research Master's degree of Sciences in Medical Physics and Life Imaging

- 1 Master thesis in the program of the research Master's degree of Sciences in Field Electro-Mechanical Engineering

- 1 Master thesis in the program of the research Master's degree of Sciences in Signal, Telecoms, Image, and Speech (STIP)

- 1 Master thesis in the program of the research Master's degree of Sciences in Information System and Big Data Intelligence

- 2. Supervision of Master theses at Lebanese International University, Lebanon:

- 11 Master theses in the program of the Master's degree of Sciences in Computer and Communication Engineering

- 2 Master theses in the program of the Master's degree of Sciences in Electrical and Electronics Engineering

#### 3. Supervision of Master theses at IMT Atlantique, Mathematical and Electrical Engineering Department, France:

- 2 internships in the program of Engineering in Embedded Systems

- 1 internship in the field of embedded artificial intelligence collaboration with the Lebanese University

#### 4. Supervision of Master theses at Lab STICC, Lorient, France:

• 1 internship in the field of Embedded Systems

### 2.7.3 Supervision of Graduation Projects

Since 2016, I have supervised several graduation projects in different universities. The following list presents these projects classified according to the universities and majors.

- 1. IMT Atlantique, Mathematical and Electrical Engineering Department, France

- 1 graduation project in the program of the Bachelor's degree of Engineering in Embedded systems

- 2. Lebanese International University (LIU), School of Engineering, Lebanon

- 1 graduation project in the program of the Bachelor's degree of Sciences in Electronics Engineering

- 10 graduation projects in the program of the Bachelor's degree of Sciences in Computer Engineering

#### 3. International University of Beirut (BIU), School of Engineering, Lebanon

• 2 graduation projects in the program of the Bachelor's degree of Engineering

Further information about my supervision experience is detailed in Appendix B.

## 2.8 Other Responsibilities and Activities

### 2.8.1 Reviewing Activities

- 1. Scientific journals:

- IEEE Transactions on Signal Processing

- IEEE Transactions on Circuits and Systems (TCAS-I)

- IEEE Transactions on Circuits and Systems-Part II (TCAS-II)

- IEEE Access

- IEEE Embedded Systems Letters

- Elsevier Embedded Hardware Design journal (Microprocessors and Microsystems)

- International Journal of Embedded Systems (IJES)

- Journal of Systems Architecture

- Journal of Aerospace Technology and Management

#### 2. International conferences:

- IEEE Design, Automation and Test in Europe (DATE)

- IEEE International New Circuits and Systems Conference (NewCas)

- IEEE International Conference on Communications and Information Technology (ICCIT)

- IEEE International Conference on Microelectronics (ICM)

- IEEE New Generation of Circuits and Systems Conference (NGCAS)

- IEEE International Conference on Computer and Applications (ICCA).

- IEEE International Conference on Electronics Circuits and Systems (ICECS).

- IEEE International Symposium on Rapid System Prototyping (RSP)

- IEEE Microwave Theory and Techniques in Wireless Communications (MTTW)

- International Conference on System-Integrated Intelligence (SysInt)

- IEEE International Conference on Innovation and Intelligence for Informatics, Computing and Technologies (3ICT)

- The International Conference on Smart Systems and Power Management (IC2SPM)

### 2.8.2 Technical Program Committee Member

I have served as technical program committee (TPC) member in the following international conferences and workshops:

- IEEE International Conference on Microelectronics (ICM 2013)

- IEEE International Conference on Electronics Circuits and Systems (ICECS 2019)

- IEEE International Conference on Innovation and Intelligence for Informatics, Computing and Technologies (3ICT 2020)

- IEEE International Symposium on Rapid System Prototyping (RSP 2021)

- IEEE Microwave Theory and Techniques in Wireless Communications (MTTW 2021)

- IEEE International Symposium on Rapid System Prototyping (RSP 2022)

- IEEE Microwave Theory and Techniques in Wireless Communications (MTTW 2022)

- Workshop on Maritime Computer Vision (WACV 2023)

### 2.8.3 Committee Membership

I have served as a committee member for evaluating Master theses and graduation projects in different majors at different universities. The following list shows my participation in evaluation committees classified according to university, level and major:

1. Lebanese University (LU), Faculty of Sciences (FS), Lebanon:

- 4 Master theses in the program of the professional Master's degree of Sciences in Field Electro-Mechanical Engineering (FEME)

- 2 Master theses in the program of the professional Master's degree of Sciences in Medical Physics and Imaging Technologies (MPIT)

- 5 Master theses in the program of the research Master's degree of Sciences in Medical Physics and Life Imaging (MPLI)

#### 2. Lebanese International University (LIU), School of Engineering (SoE), Lebanon:

- 9 Master theses in the program of the Master's degree of Sciences in Computer and Communication Engineering (MCCE)

- 10 graduation projects in the program of the Bachelor's degree of Sciences in Computer Engineering (CENG)

Further information about my teaching experience is detailed in Appendix C.

# **Chapter 3**

# **Teaching Experiences**

## **3.1 Teaching and Administrative Responsibilities**

I have worked as course coordinator for several courses at different universities. Course coordination involves following up the course progress and examination process in different branches and sections. The following list presents the courses that I have coordinated:

- Introduction to Mechatronics course in the program of the Master's degree of Science in Electrical and Electronics Engineering at School of Engineering at Lebanese International University

- Introduction to Computer course in the program of the Bachelor's degree in Computer at School of Arts and Sciences the American University of Culture and Education

- Microprocessors and Interfaces course in the program of the Bachelor's degree in Computer at School of Arts and Sciences the American University of Culture and Education

## **3.2** Construction and Development of University Courses

I have worked on remodeling and development of several courses at different universities. The reconstruction of a course includes the following duties: developing the syllabus, enhancing the course material, choosing the textbooks and updating the course assessment (exams and assignments).

- Microprocessors and Interfaces course in the program of the Bachelor's degree in Computer at School of Arts and Sciences the American University of Culture and Education

- Introduction to Computer course in the program of the Bachelor's degree in Computer at School of Arts and Sciences the American University of Culture and Education

- Introduction to Mechatronics course in the program of the Master's degree of Science in Electrical and Electronics Engineering at School of Engineering at Lebanese International University

- Contract Administration and Project Management course in the program of the Professional Master's degree of Science in Field Electromechanical Engineering at the Faculty of Sciences at Lebanese University

- Neural Network and Deep Learning course in the Image-Signal Module in the program of the Research Master's degree of Science in Medical Physics and Living Imaging at the Faculty of Sciences at Lebanese University

- Digital Electronics course in the program of the Master I degree of Science in Fundamental Physics (Biomedical Physics Course) at the Faculty of Sciences at Lebanese University

### **3.3 Teaching University Courses**

### **3.3.1** Teaching E Overview

Since 2011, I have taught several courses in the programs of various degrees in the following universities:

- 1. Lebanese University, Faculty of Sciences, Lebanon:

- Research Master's degree of Sciences in Signal, Telcom, Image and Speech

- Professional Master's degree of Sciences in Field Electro-Mechanical Engineering

- 2. Lebanese University, Institute of Social Sciences, Lebanon:

- Bachelor of Social Sciences

- 3. Lebanese International University (LIU), School of Engineering, Lebanon

- Bachelor's degree of Sciences in Computer Engineering

- Bachelor's degree of Sciences in Electrical Engineering

- Bachelor's degree of Sciences in Electronics Engineering

- Master's degree of Sciences in Computer and Communication Engineering

- 4. American University of Culture and Education (AUCE), Lebanon

- Bachelor's degree of Sciences in Computer Sciences

Further information about my teaching experience is detailed in Appendix D.

#### 3.3.2 Teaching Summary

#### 3.3.2.1 Common core courses

I have participated in teaching several courses and practical work related to electric circuits, electronics and fundamental logic circuits. During my academic career and for several academic years, I have taught "Electric Circuits", "Fundamentals of Digital Logic Design" and "Signals and Systems" courses, where I have applied the concepts in a fun and operational way using software simulators and basic hardware platforms.

Note that in my previous teaching work, I have participated in developing the plan of study to include the "Introduction to Engineering" which aims to teach engineering students how to solve a problem and implement the solution through building simple algorithms and implementing them on available hardware platforms, in particular Arduino toolset and its compatible sensors. Several teaching methods have been adopted especially project-based teaching in order to give the students the opportunity to develop knowledge and skills through engaging projects set around real-life challenges and problems.

#### 3.3.2.2 Courses in the field of embedded systems

I have a long experience in teaching courses about processors and microcontrollers, advanced digital logic systems, hardware description languages, computer architecture and embedded systems for under graduate and graduate levels.

I have taught "Advanced Logic Design" course that introduces designing of logic elements used in computations targeting Programmable Logic Devices (PLDs) and Field Programmable Gate Array (FPGA) devices. It aims to teach how to design, in VHDL, several modules such ad decoders, memories, ALU, multiplexers, registers, etc. Students are directed to use ModelSim in order to verify the designed modules. Also, I contributed in developing a practical course for graduate level about designing MIPS processors from scratch. The course aims to teach how to design, in VHDL, the sub-modules of the processor as well as the instruction set. Students are directed to use ModelSim in order to verify the designed processors.

I participated in teaching the technical work of the "Signals and Image Processors" course in the research Master program in Signals, Telecom, Image and Speech (STIP). This course focuses on implementing image processing techniques on FPGAs from algorithm till the hardware realization. In particular, the course introduces the design and implementation of Sobel filter on Spartan-6 FPGA.

I have taught the "Computer Architecture" course for graduate level. The course aims to introduce essential computer architecture design and analysis techniques. The course treats fundamental methods used to improve performance of microprocessors like pipelining, caches hierarchies, superscalar processors and out-of-order execution. This graduate course also considers parallel processing topics at different levels (instruction-level parallelism, data-level parallelism and thread-level parallelism). Scheduling and fault-tolerance strategies are also covered in this course. For several years, I have taught microprocessors and microcontrollers courses, which target the microchip PIC, ARM-based and Atmel microcontrollers. In general, these courses introduce the architectures of the targeted processors and their corresponding instruction sets. Moreover, these courses introduce programming of the microcontrollers including looping, branching, arithmetic and logical operations, timers, interrupts, communication protocols (UART, I2C, SPI, etc.) and controlling input-output pins. Students are directed to use the the associated software development tools (MPLab, CCS, STM32CubeMX, Arduino IDE, etc.) and software simulation tools - such as Proteus - to develop projects

Furthermore, I have taught the "Embedded Systems" course for graduate students which aims to provide the students with the basic information about embedded systems. The first part of this course introduces in details the ARM-based/AVR microcontrollers. The second part is devoted to the programming of embedded systems, where the students learn to design and develop a programmable embedded platform from scratch and interface a variety of sensors. In addition, the course cover multitasking by introducing real time operating system (RTOS) and using FreeRTOS to apply Queues, Semaphore and Mutex targeting Atmelbased processors (integrated in Arduino platforms) and ARM-based processors (integrated in STM32 platforms). Moreover, I have taught "Operating Systems" course and the "Linux" technical lab targeting Raspberry Pi platforms.

#### 3.3.2.3 Courses in the field of digital communication

Since 2016, I have taught the course of "Digital Communication" which is an introduction to modern digital communications at a graduate/senior undergraduate level. The coverage emphasizes a conceptual understanding of principles, techniques, and fundamental limits in digital communication systems. This course covers modulation for digital communications over additive white Gaussian noise (AWGN) channels; bandpass and low-pass signal representation; signal space representation of waveforms; modulation; demodulation; optimum receivers for AWGN channels; probability of error analysis; channel coding; synchronization; an introduction to digital communication through band-limited channels.

The course has been further developed in 2018 to include, in addition to theoretical concepts, direct applications of the theoretical concepts using MATLAB. It gives hands-on experience in translating digital communication concepts into software-defined radio technology using MATLAB coding of the different basic blocks of a digital communication system. Students can experiment a complete functional digital communication system by putting all the designed blocks together. Note that the Lab course of this work includes implementing the algorithms using USRPs from national instruments using LabView.

#### 3.3.2.4 Courses in the field of artificial intelligence and computer vision

I have taught the "Multimedia Networks" course for graduate level. The course aims to introduce different media types such as audio, image and video showing their characteristics and the techniques used in coding along with the corresponding available standards. Also, I have taught for graduate level the course of "Image Processing and Computer Vision" that includes the topics of filtering, transformation, edge detection, feature extraction and the use of neural networks and deep learning in computer vision.

I have initiated the teaching course "Neural Network and Deep Learning" in the Image-Signal Module in the program of the Research Master's degree of Science in "Medical Physics and Living Imaging" at the Faculty of Sciences at Lebanese University.

#### 3.3.2.5 Courses in the field of software engineering

I have taught practical course about software applications using object oriented programming (OOP). I teach an introductory course about relational database that includes a practical work that enables students to design an application embedding a database from scratch (SQL, phpmyadmin, Java, etc.).

#### 3.3.2.6 Courses in the field of mechatronics

I have developed a course to introduce mechatronics to electronics engineers. The course scope is to practically lead students to collect data from different sensors, analyze, and take decisions to control electromechanical actuators. The course introduces mechanical mechanisms (gears, pulleys, belts, pinions, screws, etc.); motion sensors (GPS, encoders, accelerometers, speed sensors, proximity sensors, etc.) and actuators (motors, servo motors, solenoids, etc.). I have organized practical tutorials for students that demonstrate the interaction between embedded systems and electromechanical system.

## **3.4 Technical Training Courses**

I provide technical training courses in the domain of basic and advanced programming, telecommunication and electronics (logic, digital systems, OOP programming, circuit design, and PCB assembly, FPGAs) to engineers, university and technical institutes students. These lectures are presented during private training sessions and workshops.

## Appendix A

## List of publications

### A.1 Book chapters

- [BC2] M. Rizk, F. Slim, A. Baghdadi, and J-Ph. Diguet "Towards Real-time Human Detection in Maritime Environment Using Deep Learning", in Advances in System-Integrated Intelligence. SYSINT 2022. Lecture Notes in Networks and Systems, vol 546. Springer, Cham, pp. 583-593. DOI: 10.1007/978-3-031-16281-7\_55

- [BC1] H. Younes, M. Alameh, A. Ibrahim, M. Rizk and M. Valle, "Efficient Algorithms for Embedded Tactile Data Processing", in Electronic Skin: Sensors and Systems, River Publishers, 2020, pp.113-138.

### A.2 Published journal papers

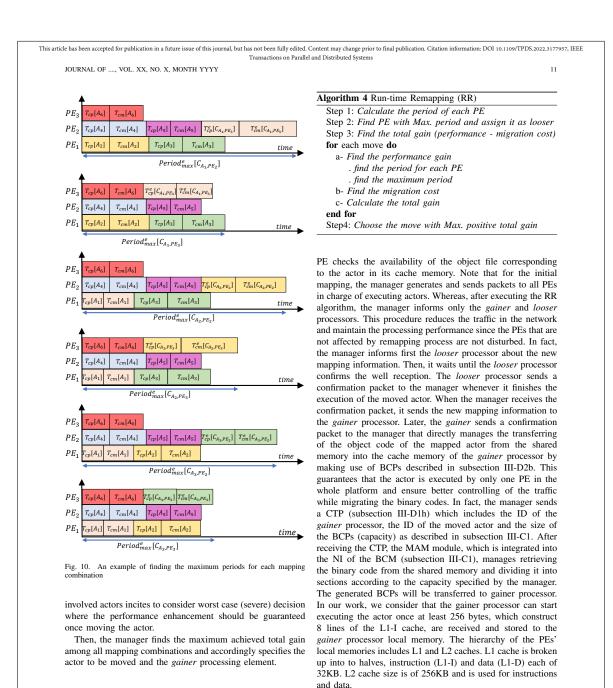

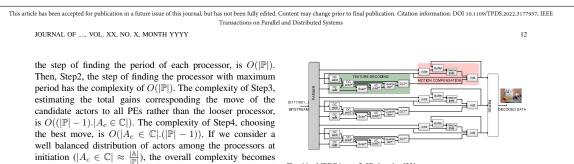

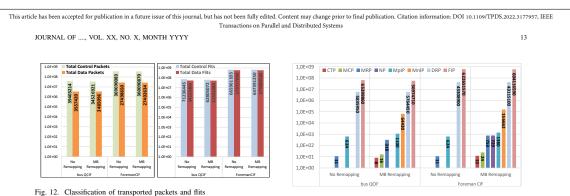

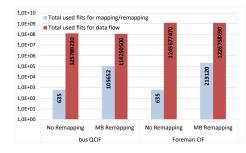

- [J18] M. Rizk, K. Martin and J-Ph. Diguet, "Run-time remapping algorithm of dataflow actors on NoC-based heterogeneous MPSoCs", in IEEE Transactions on Parallel Distributed Systems (TPDS), 2022. DOI: 10.1109/TPDS.2022.3177957

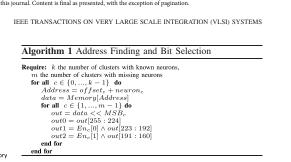

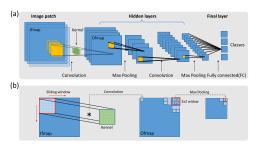

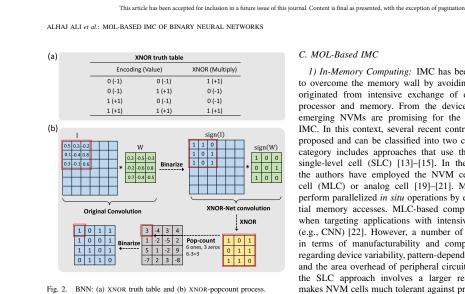

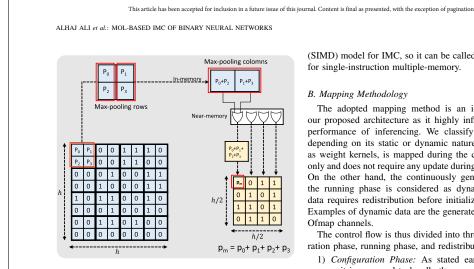

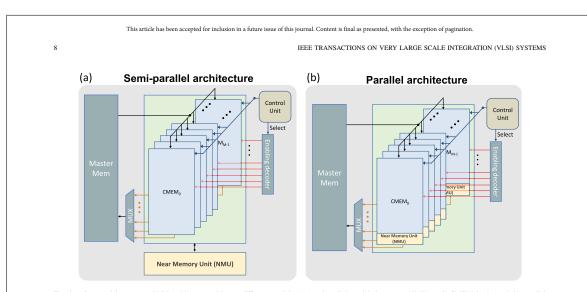

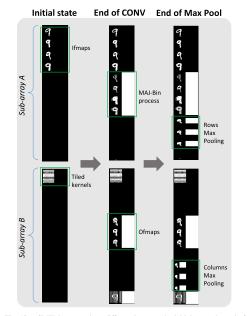

- [J17] K. Haj-Ali, A. Baghdadi, E. Dupraz, M. Léonardon, M. Rizk and J-Ph. Diguet, "MOL-based In-Memory Computing of Binary Neural Networks", in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, 2022. DOI: 10.1109/TVLSI.2022.3163233

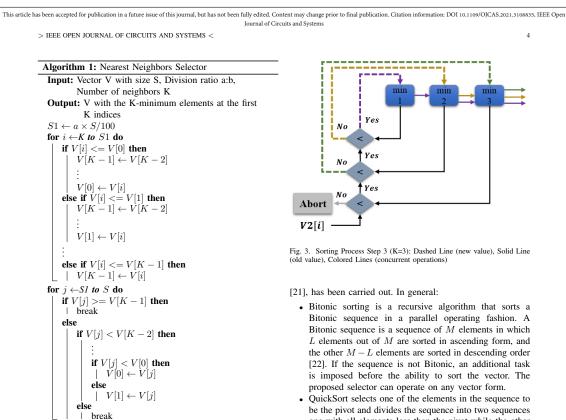

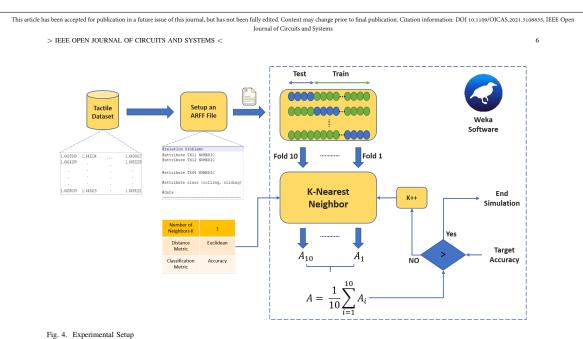

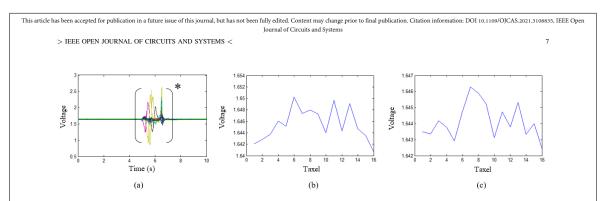

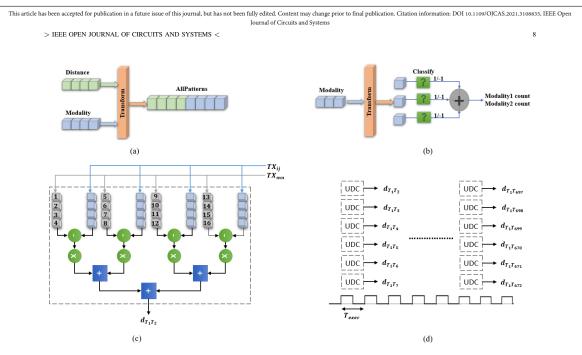

- [J16] H. Younes, A. Ibrahim, M. Rizk and M. Valle, "An Efficient Selection-Based kNN Architecture for Smart Embedded Hardware Accelerators," in IEEE Open Journal of Circuits and Systems (OJCAS), vol. 2, pp. 534-545, 2021. DOI: 10.1109/OJ-CAS.2021.3108835

- [J15] M. Rizk, A. Baghdadi and M. Jézéquel, "A literature survey on algorithms and hardware architectures of Max-Log-MAP demapping", Journal of Circuits, Systems, and Computers (JCSC), vol. 31, no. 3, p. 2230001, 2021. DOI: 10.1142/S021812662230001X

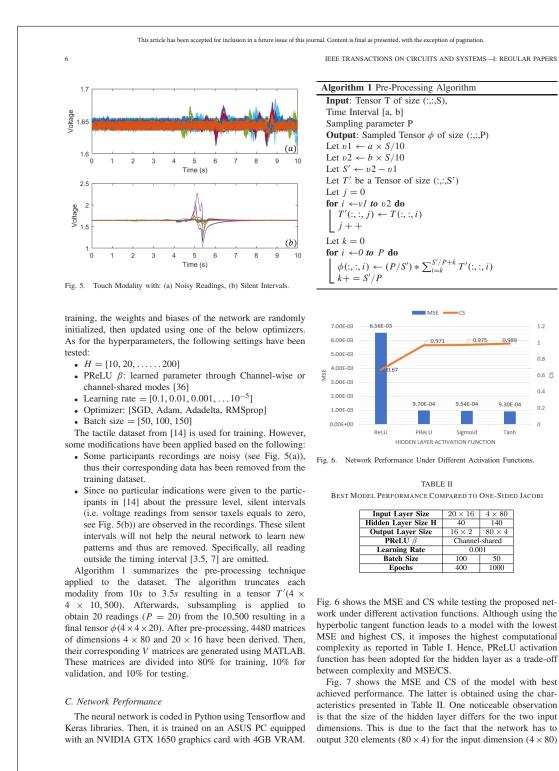

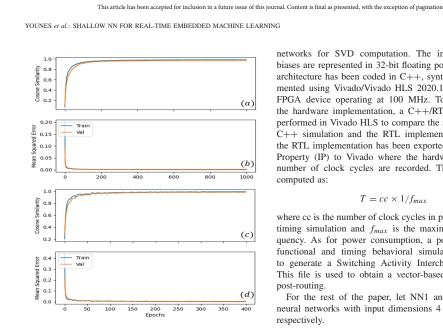

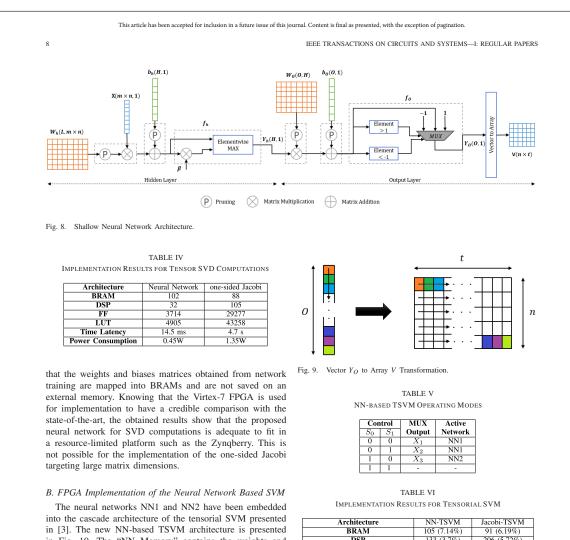

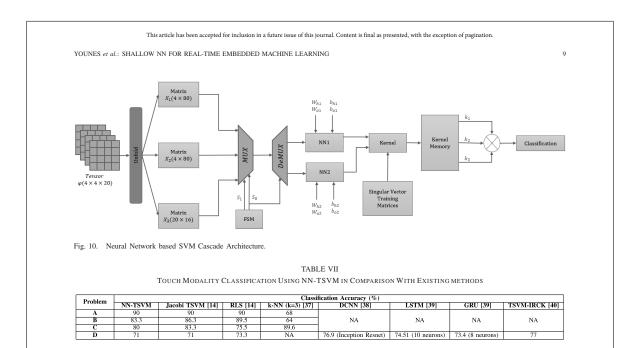

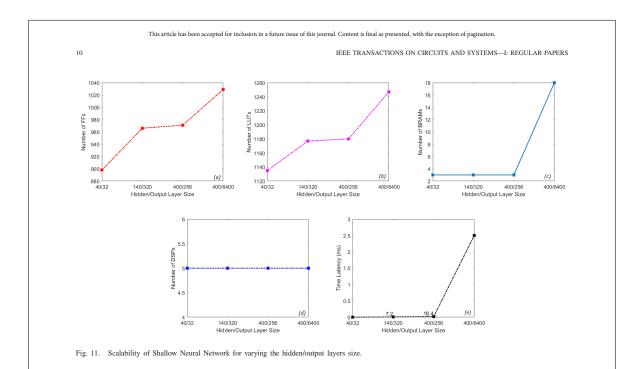

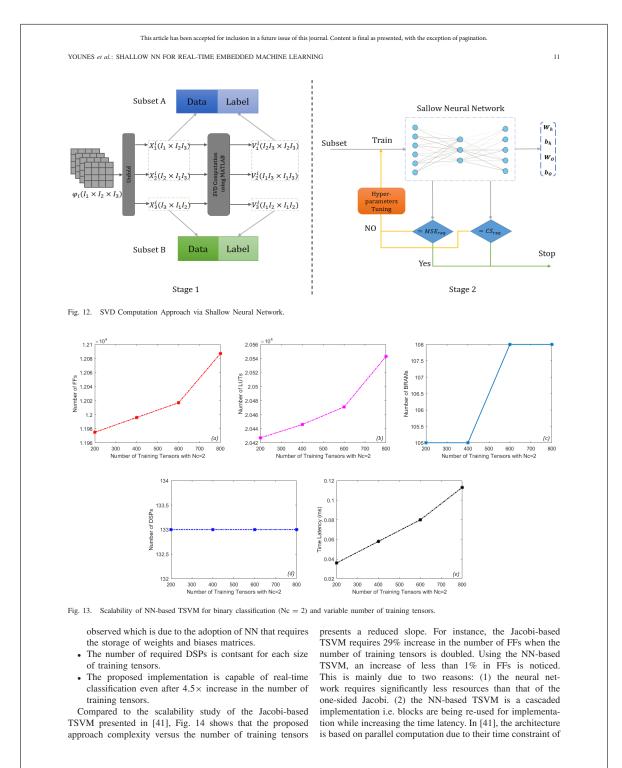

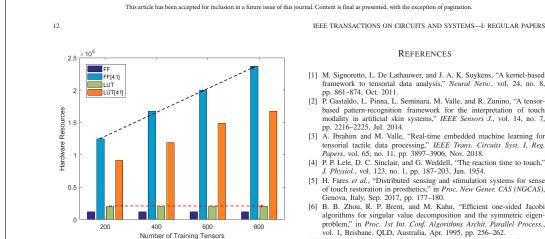

- [J14] H. Younes, A. Ibrahim, M. Rizk and M. Valle, "A Shallow Neural Network for Real-Time Embedded Machine Learning for Tensorial Tactile Data Processing," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 10, pp. 4232–4244, 2021. (DOI: 10.1109/TCSI.2021.3102303)

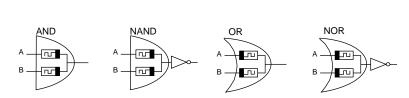

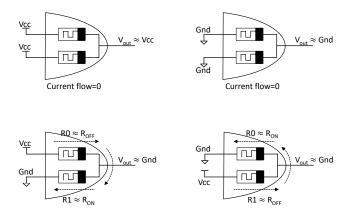

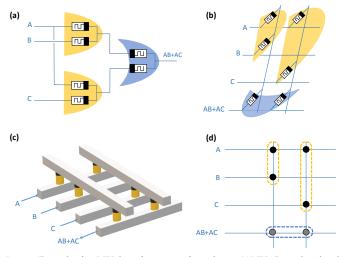

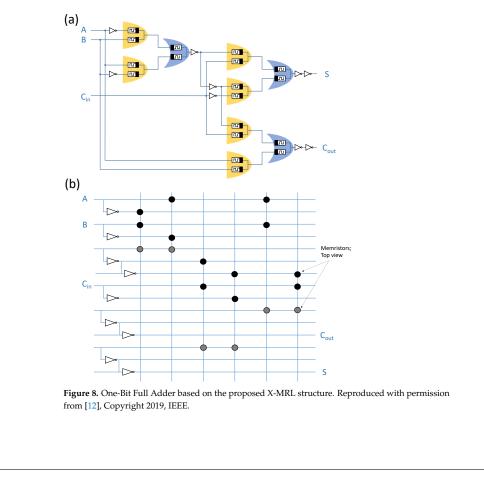

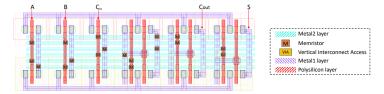

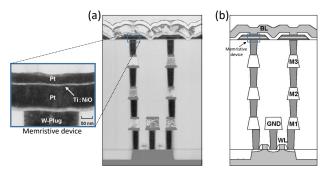

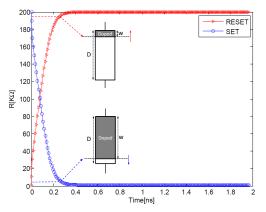

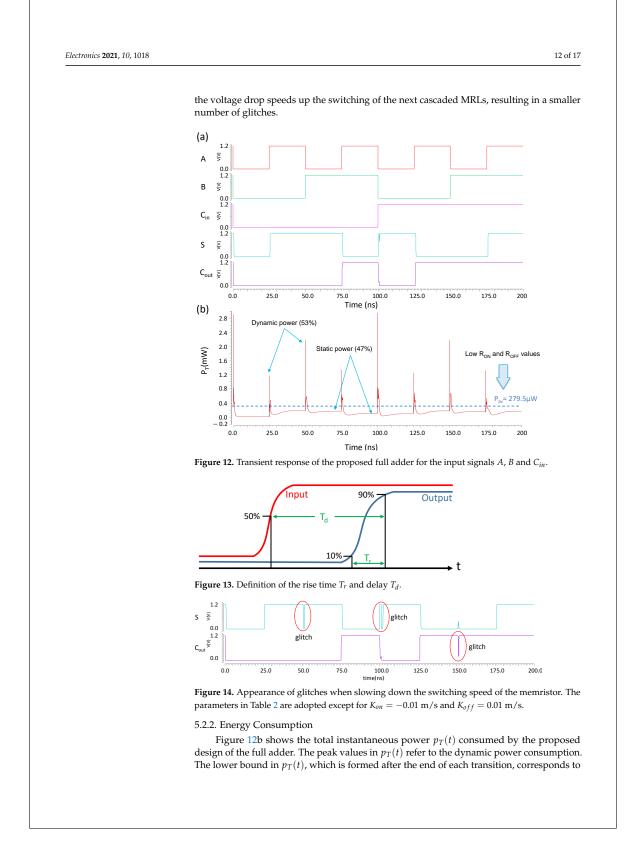

- [J13] K. Haj-Ali, M. Rizk, A. Baghdadi, J-Ph. Diguet and J. Joumaa, "Hybrid memristor-CMOS implementation of combinational logic based on X-MRL" in Electronics, vol. 10, no. 9, April 2021. DOI: 10.3390/electronics10091018

- [J12] M. Rizk, A. Baghdadi, M. Jézéquel, Y. Mohanna, and Y. Atat, "No-Instruction-Set-Computer Design Experience of Flexible and Efficient Architectures for Digital Communication Applications: two case studies on MIMO Turbo Detection and Universal Turbo Demapping", in Journal of Design Automation for Embedded Systems (DEAM), January, 2021. DOI: 10.1007/s10617-021-09245-x

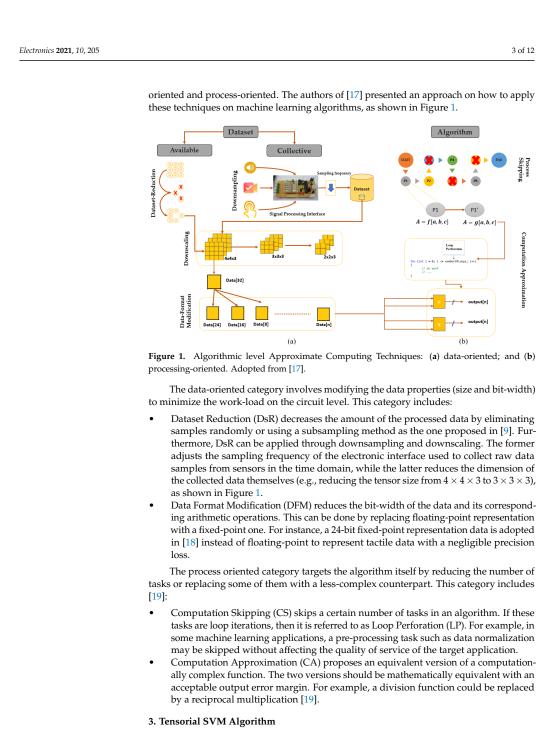

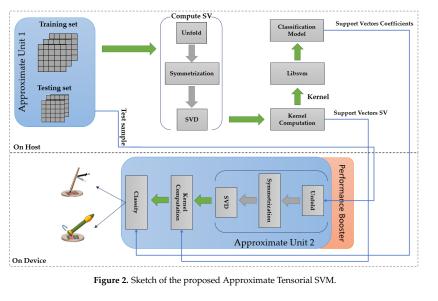

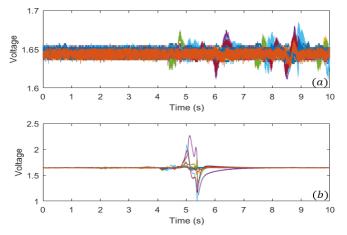

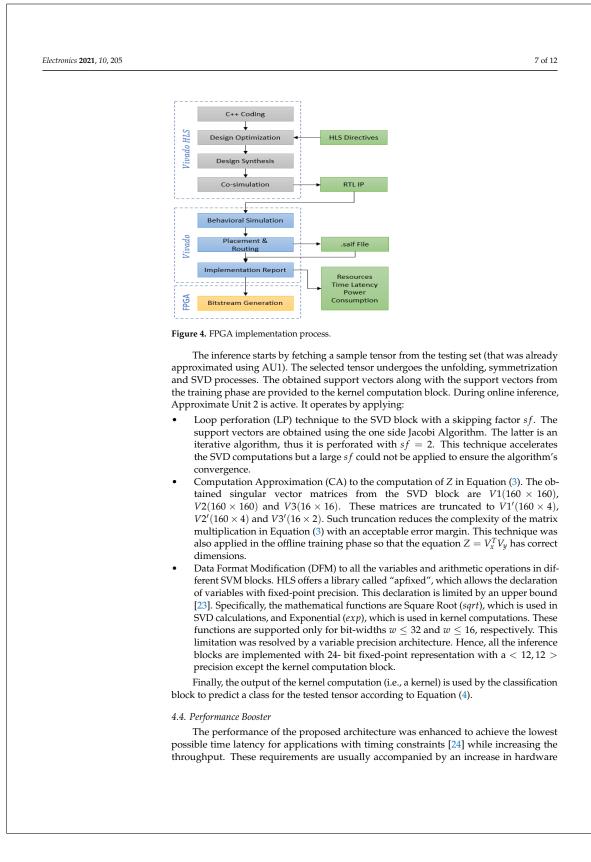

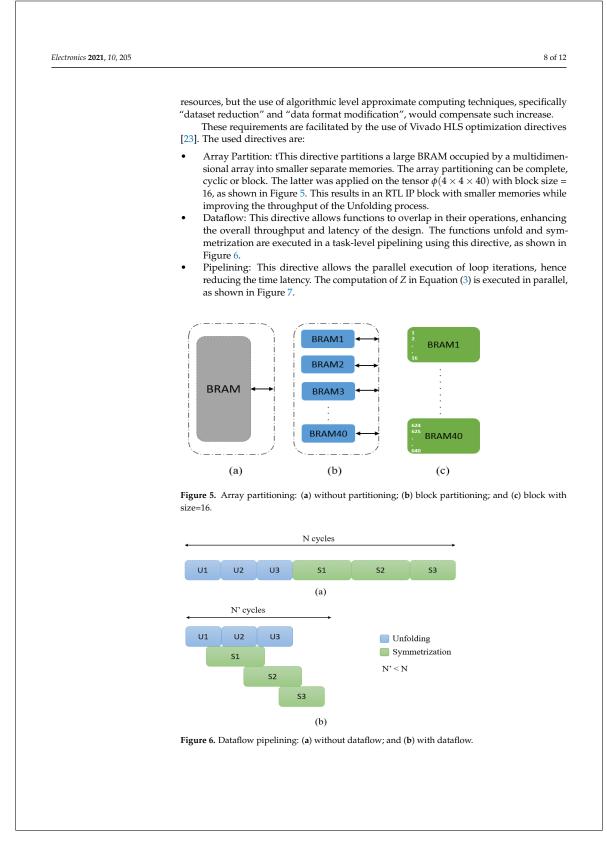

- [J11] H. Younes, A. Ibrahim, M. Rizk and M. Valle, "Algorithmic-Level Approximate Tensorial SVM Using High-Level Synthesis on FPGA," in Electronics, vol. 10, no. 2, January, 2021. DOI: 10.3390/electronics10020205

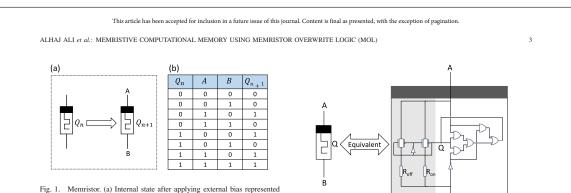

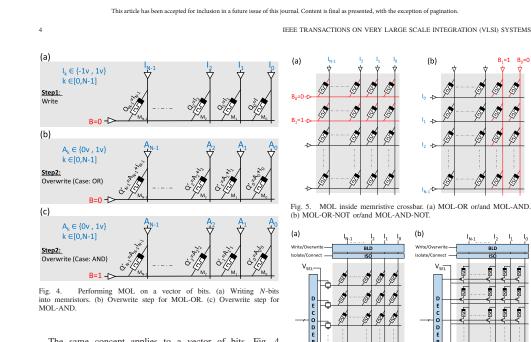

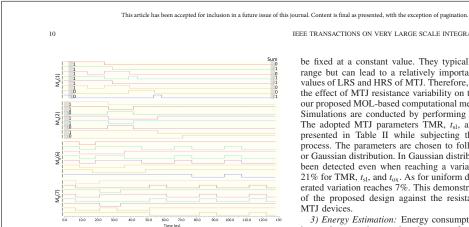

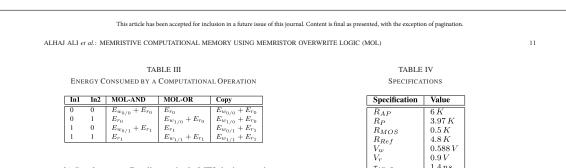

- [J10] K. Haj-Ali, M. Rizk, A. Baghdadi, J-Ph. Diguet and J. Joumaa, "Memristive Computational Memory Using Memristor Overwrite Logic (MOL)", in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, August, 2020. DOI: 10.1109/TVLSI.2020.3011522

- [J9] M. Rizk, A. Baghdadi, M. Jézéquel, Y. Mohanna, and Y. Atat, "NISC-Based MMSE-IC MIMO Turbo Detector", in Journal of Circuits, Systems, and Computers (JCSC), vol. 30, no.04, p. 2150069, September, 2020. DOI: 10.1142/S0218126621500699

- [J8] M. Rizk, A. Baghdadi, and M. Jézéquel, "Computational Complexity Reduction of MMSE-IC MIMO Turbo Detection", in Journal of Circuits, Systems, and Computers (JCSC), vol. 28, no. 13, March, 2019. DOI: 10.1142/S0218126619502281

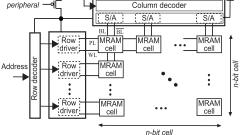

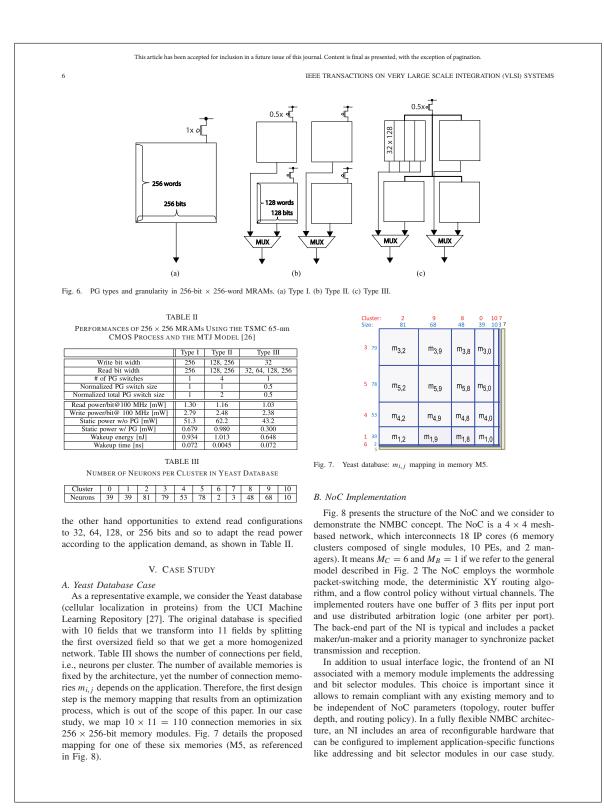

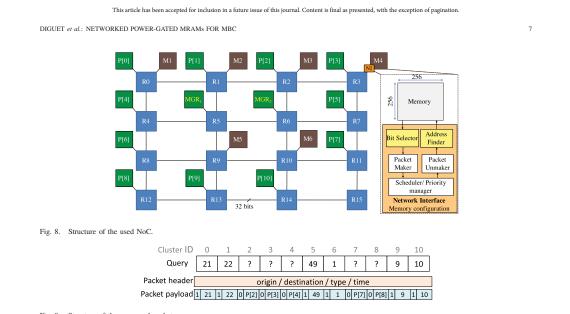

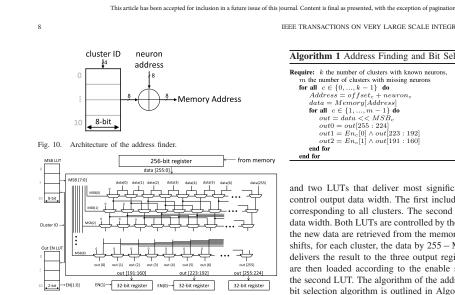

- [J7] J-Ph. Diguet, N. Onizawa, M. Rizk, M. J. Sepulveda, A. Baghdadi, and T. Hanyu, "Networked Power-gated MRAMs for Memory-Based Computing", in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 26, no. 12, pp. 2696-2708, December, 2018. DOI: 10.1109/TVLSI.2018.2856458

- [J6] M. Rizk, A. Baghdadi, M. Jézéquel, Y. Mohanna, and Y. Atat, "Efficient Quantization and Fixed-Point Representation for Turbo-Equalization and Turbo-Demapping", in EURASIP Journal on Embedded Systems, vol. 2017:33, December, 2017. DOI: 10.1186/s13639-017-0081-y

- [J5] Z. Bazzal, A. M. Ahmad, I. El-Bitar, M. Rizk and M. Raad, "Proposition of an Adaptive Retransmission Timeout for TCP in 802.11 Wireless Environments", in International Journal of Engineering Research and Application, vol. 7, Issue 2, (Part -4), February, 2017. DOI:10.9790/9622-0702046471

- [J4] M. Rizk, A. Baghdadi, M. Jézéquel, Y. Mohanna, and Y. Atat, "Design and Prototyping Flow of Flexible and Efficient NISC-Based Architectures for MIMO Turbo Equalization and Demapping", in Electronics, Special Issue "Rapid System Design with

Dedicated Architectures and Specific Software Tools", vol. 5, Issue 3, August, 2016. DOI:10.3390/electronics5030050

- [J3] M. Rizk, A. Baghdadi, M. Jézéquel, Y. Mohanna, and Y. Atat, "NISC-Based Soft-In Soft-Out Demapper", in IEEE Transactions on Circuits and Systems II (TCAS-II), vol. 62, Issue 11, November, 2015. DOI: 10.1109/TCSII.2015.2455991

- [J2] Y. Atat and M. Rizk, "Top Down Approach: SIMULINK Mixed Hardware / Software Design", International Journal of Computer Science Issues, vol. 9, Issue 3, No 3, May, 2012.

- [J1] M. Rizk, Y. Mohanna, H. Mougnieh, M. Hamad, F. Khalil, and A. Ghaddar, "Arabic Text to Speech Synthesizer : Arabic Letter to Sound Rules, in International Review on Computers and Software (IRECOS), vol. 6 n. 1, January, 2011.

### A.3 Published international conferences

- [C34] M. Yaacoub, H. Younes and M. Rizk, "Acoustic Drone Detection Based on Transfer Learning and Frequency Domain Features", in proc. of the IEEE International Conference on Smart Systems and Power Management (IC2SPM), November, 2022.

- [C33] J. Sharafaldeen, M. Rizk, D. Heller, A. Baghdadi and J-Ph. Diguet, "Marine Object Detection Based on Top-View Scenes Using Deep Learning on Edge Devices", in proc. of the the IEEE International Conference on Smart Systems and Power Management (IC2SPM), November, 2022.

- [C32] D. Heller, M. Rizk, R. Douguet, A. Baghdadi and J-Ph. Diguet, "Marine Objects Detection Using Deep Learning on Embedded Edge Devices", in proc. of the IEEE International Workshop on Rapid System Prototyping (RSP), part of Embedded Systems Week (ESWEEK), Shanghai, October 2022.

- [C31] Z. Ning, M. Rizk, A. Baghdadi and J-Ph. Diguet, "Enhancing Embedded AI-Based Object Detection Using Multi-View Approach", in proc. of the IEEE International Workshop on Rapid System Prototyping (RSP), part of Embedded Systems Week (ESWEEK), Shanghai, October 2022.

- [C30] M. Rizk, D. Heller, R. Douguet, A. Baghdadi and J-Ph. Diguet, "Optimization of Deep-Learning Detection of Humans in Marine Environment on Edge Device", in proc. of the IEEE International Conference on Electronics Circuits and Systems (ICECS), Glasgow UK, October 2022.

- [C30] M. Rizk, A. Baghdadi, and J-Ph. Diguet "Towards Real-time Human Detection in Maritime Environment Using Deep Learning" accepted to International Conference on System-Integrated Intelligence (SysInt 2022), Genova, Italy, September, 2022.

- [C29] M. Rizk, F. Slim and J. Charara, "Toward AI-Assisted UAV for human detection in search and rescue missions", in proc. of the IEEE International Conference on

Decision Aid Sciences and Applications (DASA), Bahrain, December, 2021. DOI: 10.1109/DASA53625.2021.9682412

- [C28] M. Rizk, A. Baghdadi and J-Ph. Diguet, "Rapid design and verification experience using flexible cycle-accurate NoC simulator", in proc. of the IEEE International Multidisciplinary Conference on Engineering Technology (IMCET), Beirut, Lebanon December 2021. DOI: 10.1109/IMCET53404.2021.9665518

- [C27] S. Hraybi and M. Rizk, "Examining YOLO for Real-Time Face-Mask Detection", in proc. of the IET Smart Cities Symposium (SCS), Bahrain, November, 2021. DOI: 10.1049/icp.2022.0402

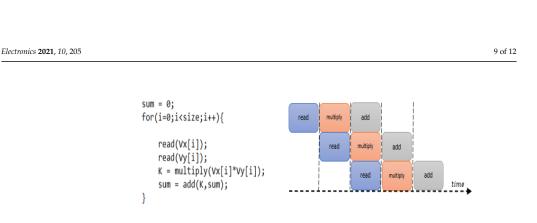

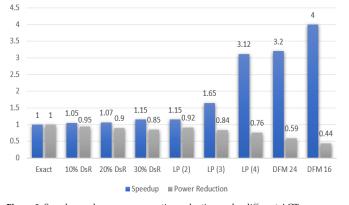

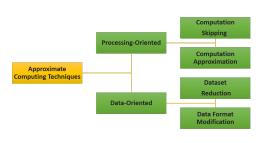

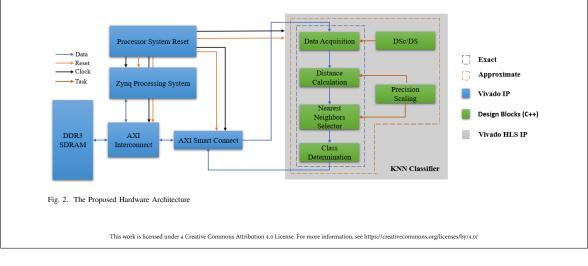

- [C26] M. Badran, S. Kareh and M. Rizk, "PharmServ: A digital platform to facilitate searching for pharmaceuticals in Lebanon", in proc. of the IET Smart Cities Symposium (SCS), Bahrain, November, 2021. DOI: 10.1049/icp.2022.0432