# Mapping parallel applications on parallel architectures Kevin J M Martin

### ▶ To cite this version:

Kevin J M Martin. Mapping parallel applications on parallel architectures. Hardware Architecture [cs.AR]. Université Bretagne Sud, 2023. tel-04054474v2

## HAL Id: tel-04054474 https://hal.science/tel-04054474v2

Submitted on 10 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial 4.0 International License

# HABILITATION À DIRIGER DES RECHERCHES

## UNIVERSITÉ DE BRETAGNE SUD

ÉCOLE DOCTORALE Nº 644 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique et Architectures numériques

Par

### Kevin J. M. MARTIN

# Mapping parallel applications on parallel architectures

## Granularity of parallelism and synchronisation

soutenue à Lorient, le 16 mars 2023 Unité de recherche : Lab-STICC

#### Composition du Jury :

| Président :<br>Rapporteurs : | Olivier Sentieys<br>Shuvra S. Bhattacharyya          | Professeur - Université de Rennes<br>Professeur - University of Maryland et<br>Chaire d'excellence - INSA/IETR Rennes |

|------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Examinateurs :               | Frédéric Pétrot<br>Claire Pagetti<br>Philippe Coussy | Professeur - Université Grenoble Alpes<br>Directrice de recherche - ONERA<br>Professeur - Université de Bretagne-Sud  |

Copyright © 2023 Kevin J. M. Martin

The template used for this document has been largely inspired from "The Legrand Orange Book", downloaded from http://www.LaTeXTemplates.com.

Licensed under the Creative Commons Attribution-NonCommercial 3.0 Unported License (the "License"). You may not use this file except in compliance with the License. You may obtain a copy of the License at http://creativecommons.org/licenses/by-nc/3.0. Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Some icons have been designed using resources from https://Flaticon.com or https://www.svgrepo.com/.

The images have been taken from https://Freepik.com, https://pixabay.com, https://www. shutterstock.com, or https://depositphotos.com.

This document is not for sale.

Made available online, 2023

If you think education is expensive, try ignorance.

$\label{eq:Robert Orben} Robert\ Orben \ (currently the leading candidate for crafter of this maxim)^1$

<sup>&</sup>lt;sup>1</sup>https://quoteinvestigator.com/2016/05/03/expense/

Les premiers remerciements vont naturellement vers les membres du jury. Mais au-delà des remerciements de convenance, je tiens à les remercier sincèrement d'avoir pris de leur temps pour lire ce (long) manuscrit et pour avoir assisté à ma soutenance. Je remercie en particulier Prof. Philippe Coussy d'avoir relu ce document avant l'envoi aux rapporteurs. Je remercie Prof. Frédéric Pétrot, qui, après avoir fait l'exercice de rapporter sur ma thèse, a accepté de rapporter sur mon HdR. Je remercie Prof. Olivier Sentieys d'avoir accepté de présider mon jury d'HdR. Il a été mon chef d'équipe pendant ma thèse, et ce n'est pas sans fierté que je lui ai exposé mon parcours depuis que j'ai quitté son équipe. Je remercie DR. Claire Pagetti d'avoir accepté de rapporter sur le document. Je resterai la première HDR sur laquelle elle a rapporté. Enfin, je remercie Prof. Shuvra Bhattacharyya de s'être prêté à cet exercice très français.

Ensuite je remercie les personnes qui ont contribué aux travaux qui sont présentés dans ce document. L'HDR, dans notre domaine, est paradoxalement un diplôme individuel, mais accessible à condition de travailler avec d'autres personnes. Ce document reflète donc un travail collectif, dans lequel j'ai pris ma part, mais dont je ne suis pas le contributeur unique.

Je tiens à remercier les personnes, qui, même si nous n'avons pas eu l'opportunité de travailler ensemble sur des projets de recherche ou l'encadrement de doctorante et doctorant, ont aussi participé à ce travail d'HDR. Par leurs conseils, discussions (pas nécessairement scientifiques), avis et commentaires.

Ce document met l'accent sur mes activités de recherche, mais je tiens à ne pas oublier de remercier mes collègues de l'IUT de Lorient, en particulier mes collègues du département GIM.

La vie d'enseignant-chercheur est un équilibre fragile, qui force à jongler entre enseignement, recherche, administration, et ce "travail-passion" s'invite volontiers dans la sphère privée et s'accapare sans scrupule du temps originellement dédié à d'autres activités personnelles. Sans repère solide, difficile d'avancer sereinement. Ma famille, mes amis et mes proches, ont donc aussi contribué à la réalisation de cette HDR. Lao n'nyarabi, na mansa muso.

Merci donc à toutes les personnes qui ont contribué de près ou loin.

Merci à toi Philippe, Matthieu, Gwenolé, Luca, Davide, Mickaël, Thomas, Satyajit, Rohit, Chilanka, Christie, Remi, Thomas, Jorgiano, Ghizlane, Anju, Chengcong, Ramesh, Baptiste, Majed.

Merci à toi Jean-Philippe, Thanh, Daniel, Yvan, Yaset, Emmanuel, Jean-Philippe, Mickaël, Paola, Mostafa, Johanna, Cataldo, Marcon, Alemeh, Marcelo, Navonil, Hemanta, Jérôme, Serge, Hajar, Hugo, Christina, Khadimou.

Merci à toi Florence, Virginie, Guy, Vianney, Arnaud, Mr Laurent, Marc, Cyrille, Philippe, Florent, Pierre, Dominique, Bertrand, Cédric, Cédric, les collègues du Lab-STICC.

Merci à toi Christophe, Tahar, Géraldine, Pao, Denis, Cédric, Didier, Philippe, Philippe, Philippe, Philippe<sup>2</sup>, Michel, Fred, Stéphane, Pascale, Cédric, Maud, Catherine, Morgane, Ludo, Valérie, Aziza, Serge, Yessine, Emilie, Yohan, Gaël, les collègues de l'IUT.

Merci aux communautés logiciels et matériels open-source : ORCC, PREESM, PULP, Gem5, Noxim, Linux, Sniper, QEMU, OVP, RISC-V, OpenPiton.

Merci à toi.

Merci aussi à Rantanplan.

<sup>&</sup>lt;sup>2</sup>oui, ça fait plein de "Philippe", ce n'est pas une erreur de copier/coller

|     | General introduction                                       | 1  |

|-----|------------------------------------------------------------|----|

| Т   | Synthèse                                                   |    |

| 1   | Curriculum Vitae                                           | 5  |

| 1.1 | État civil                                                 | 5  |

| 1.2 | Situation Professionnelle                                  | 5  |

| 1.3 | Parcours                                                   | 6  |

| 2   | Synthèse des activités d'enseignement                      | 9  |

| 2.1 | Description des thématiques enseignées depuis 2011         | 9  |

| 2.2 | Présentation synthétique des enseignements                 | 13 |

| 2.3 | Responsabilités et autres activités liées à l'enseignement | 14 |

| 2.4 | Synthèse et réflexions sur le métier d'enseignant          | 15 |

| 3   | Synthèse des activités de recherche                        | 19 |

| 3.1 | Présentation synthétique des thématiques de recherche      | 19 |

| 3.2 | Encadrement doctoral et scientifique                       | 24 |

| 3.3 | Diffusion et rayonnement                                   | 33 |

| 3.4 | Outils logiciels                                           | 36 |

| 3.5 | Responsabilités scientifiques                              | 36 |

| 3.6 | Synthèse et réflexions sur le métier de chercheur          | 37 |

| 3.7 | Liste des publications                                     | 38 |

| Ш   | Mapping parallel applications on parallel architectures                      |       |  |  |

|-----|------------------------------------------------------------------------------|-------|--|--|

|     | Introduction                                                                 | 45    |  |  |

| 4   | Exploiting ILP and DLP with CGRAs                                            | 49    |  |  |

| 4.1 | A warm-up on CGRAs                                                           | 49    |  |  |

| 4.2 | Contribution 1: From a fault-tolerant reconfigurable standalone architecture | ə57   |  |  |

| 4.3 | Contribution 2: to an ultra-low power programmable array                     | 61    |  |  |

| 4.4 | Contribution 3: Adding floating-point capabilities                           | 70    |  |  |

| 4.5 | Summary                                                                      | 73    |  |  |

| 5   | Exploiting DLP and TLP with multicore processors                             | 75    |  |  |

| 5.1 | A warm-up on multicore processors and dataflow model of computation          | 75    |  |  |

| 5.2 | The mapping problem                                                          | 81    |  |  |

| 5.3 | Model-based design and mapping of dataflow applications                      | 84    |  |  |

| 5.4 | Runtime mapping of dataflow applications on NoC-based MPSoC                  | 90    |  |  |

| 5.5 | Summary                                                                      | 96    |  |  |

| 6   | Exploiting DLP and TLP: scalability and synchronisation issues               | 99    |  |  |

| 6.1 | A warm-up on scalability and synchronisation                                 | 99    |  |  |

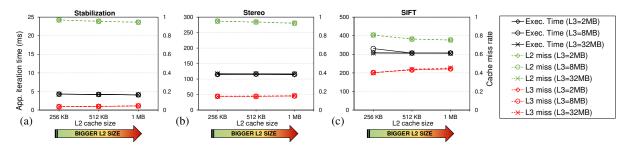

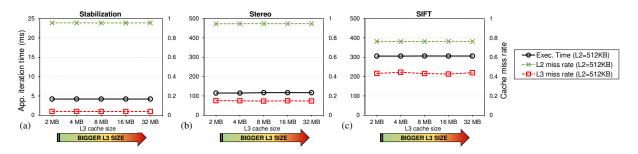

| 6.2 | On scalability of dataflow applications                                      | 104   |  |  |

| 6.3 | The notifying memories concept                                               | 106   |  |  |

| 6.4 | Subutai: synchronisation primitives spread throughout the NoC                | 115   |  |  |

| 6.5 | Summary                                                                      | 118   |  |  |

|     | Contributions wrap-up                                                        | . 121 |  |  |

| Perspectives and conclusion |

|-----------------------------|

|-----------------------------|

| 7   | Perspectives               | 125 |

|-----|----------------------------|-----|

| 7.1 | CGRAs for AI, AI for CGRAs | 125 |

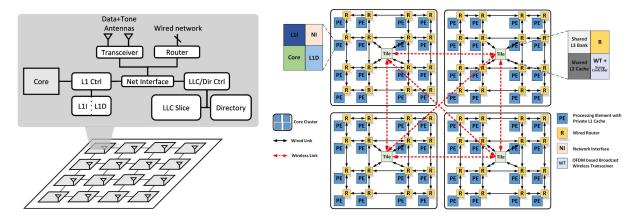

| 7.2 | Wireless Network-On-Chip   | 127 |

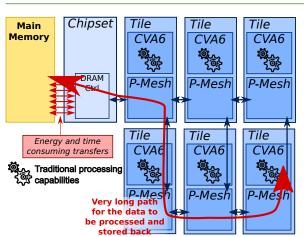

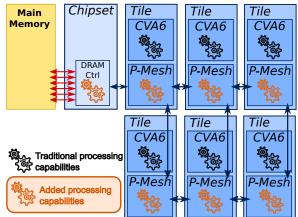

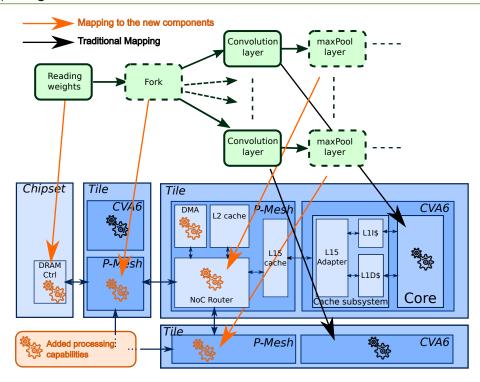

| 7.3 | Computing in network       | 128 |

| 8   | Closing chapter            | 133 |

|     | Acronymes                  | 135 |

Ш

| IV Bibliography and selected publications |                              |     |  |

|-------------------------------------------|------------------------------|-----|--|

|                                           | Bibliography                 | 139 |  |

| Α                                         | Selected publication on CGRA | 151 |  |

| B | Selected publication on mapping dataflow applications | 167 |

|---|-------------------------------------------------------|-----|

| С | Selected publication on synchronisation of tasks      | 187 |

T HIS document presents my teaching and research activities since September 2011, when I was hired as an associate professor at Université de Bretagne-Sud, to teach at IUT de Lorient and conduct my research in Lab-STICC laboratory, until August 2022. The document is organized in four main parts. The first part contains my curriculum vitae, and a synthesis of my teaching and research activities. The second part is the core of the document, presenting in more details my scientific contributions structured in three main research areas. The third part of the document opens up on research perspectives. Finally, the document ends with the bibliography and some selected publications. Each part is independent of each other.

This document is written in French for the first part (but some sections are likely to be understandable for a reader familiar with English). The second and third part of the document are written in English.

# **Synthèse**

#### 1 Curriculum Vitae ..... 5

- 1.1 État civil

- 1.2 Situation Professionnelle

- 1.3 Parcours

#### 2 Synthèse des activités d'enseignement 9

- 2.1 Description des thématiques enseignées depuis 2011

- 2.2 Présentation synthétique des enseignements

- 2.3 Responsabilités et autres activités liées à l'enseignement

- 2.4 Synthèse et réflexions sur le métier d'enseignant

#### 3 Synthèse des activités de recherche . 19

- 3.1 Présentation synthétique des thématiques de recherche

- 3.2 Encadrement doctoral et scientifique

- 3.3 Diffusion et rayonnement

- 3.4 Outils logiciels

- 3.5 Responsabilités scientifiques

- 3.6 Synthèse et réflexions sur le métier de chercheur

- 3.7 Liste des publications

# 1. Curriculum Vitae

## 1.1 État civil

| Nom         | MARTIN                                        |

|-------------|-----------------------------------------------|

| Prénoms     | Kevin John Michel                             |

| Né à        | removed for public version                    |

| Nationalité | removed for public version                    |

|             | personal situation removed for public version |

#### 1.2 Situation Professionnelle

| Poste                       | Maître de conférences                                     |

|-----------------------------|-----------------------------------------------------------|

| Établissement d'affectation | Université de Bretagne-Sud                                |

| Enseignement                | IUT Lorient - Département Génie Industriel et Maintenance |

| Recherche                   | Lab-STICC - équipe ARCAD                                  |

| Date de recrutement         | 01/09/2011                                                |

| Grade                       | MCF classe normale                                        |

| email                       | kevin.martin@univ-ubs.fr                                  |

| site web                    | http://www-labsticc.univ-ubs.fr/~kmartin/                 |

|                             | b https://orcid.org/0000-0002-8122-1192                   |

| téléphone                   | +33 2 97 87 46 36                                         |

#### ADRESSE PROFESSIONNELLE

Laboratoire Lab-STICC, UMR CNRS 6285 Centre de recherche, BP 92116 - 56321 LORIENT Cedex

#### 1.3 Parcours

| Septembre 2021 – Août 2022  | <b>Délégation CNRS.</b> Laboratoire Lab-STICC, équipe ARCAD (hardware architectures and computer-aided design tools)                                                                                                                                                          |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Septembre 2011 – Août 2021  | Maître de conférences à l'Université de Bretagne Sud, IUT Lo-<br>rient<br>Laboratoire Lab-STICC, équipe ARCAD depuis 2020, précédem-<br>ment MOCS (Méthodes, Outils, Circuits, Systèmes) 2011-2019                                                                            |

| Septembre 2010 – Août 2011  | ATER à Université Rennes 1, Irisa, équipe CAIRN                                                                                                                                                                                                                               |

| Avril 2007 – Septembre 2010 | Doctorat en informatique de l'Université de Rennes 1                                                                                                                                                                                                                          |

| Avril 2005 – Avril 2007     | Formation en <b>ingénierie logicielle</b> par voie d'apprentissage à<br>l'ETGL (École des Techniques du Génie Logiciel), CFA AFTI,<br>Saclay<br><b>Contrat d'apprentissage</b> en alternance (2 périodes de 6 mois) en<br>tant qu'ingénieur logiciel, à l'Irisa, INRIA Rennes |

| 2003-2004                   | <b>DEA STIR</b> (Signal, Télécoms, Image, Radar), Université de Rennes 1                                                                                                                                                                                                      |

#### 1.3.1 Synthèse de la carrière

Après l'obtention d'un DEA en Signal, Télécoms, Image, Radar, option Image de l'université de Rennes 1 en 2004, j'ai suivi une formation en ingénierie logicielle par voie d'apprentissage à partir d'avril 2005. Cette formation était en alternance entre le CFA AFTI (Association pour la Formation aux Techniques Industrielles)<sup>1</sup> à Saclay, et l'INRIA Rennes. À l'INRIA, j'étais intégré dans l'équipe R2D2 (qui est devenu CAIRN puis TARAN en 2021). L'alternance consistait en des périodes de 6 mois. Mon parcours académique m'a donné un bagage électronique quand la formation m'a apporté des connaissances en informatique et m'a initié au développement logiciel. C'est ce double parcours qui me permet aujourd'hui de me situer à l'interface entre le monde matériel et le monde logiciel.

À l'issue de la formation en avril 2007, j'ai directement poursuivi en thèse dans l'équipe CAIRN, thèse dirigée par Christophe Wolinski que j'ai soutenue en septembre 2010. J'ai ensuite effectué une année d'ATER à l'université de Rennes 1 entre septembre 2010 et août 2011. Depuis septembre 2011, je suis maître de conférences à l'université de Bretagne Sud, et affecté à l'IUT de Lorient au département Génie Industriel et Maintenance (GIM) pour l'enseignement. Mes travaux de recherche s'effectuent au laboratoire Lab-STICC, Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance. Le laboratoire est présent sur les villes de Brest, Quimper, Lorient et Vannes. Le Lab-STICC est une unité de recherche inter-établissements (CNRS, IMT Atlantique, ENIB, ENSTA Bretagne, UBO, UBS) comprenant plus de 600 personnes. Mon établissement est l'UBS, et je me trouve physiquement à Lorient.

À mon arrivée à Lorient, j'ai été intégré aux activités de l'équipe Méthodes et Outils pour les Circuits et Systèmes (MOCS) du Lab-STICC, et j'ai eu la chance d'être directement impliqué dans le projet ANR COMPA et l'encadrement de deux thèses (dont une liée au projet). J'ai progressivement développé trois axes de recherches: 1) Architectures de calcul spécialisées, 2) Déploiement de tâches sur architectures parallèles, 3) Synchronisation de tâches sur architectures parallèles.

La thèse qui m'a été proposée de co-encadrer dès mon arrivée est une thèse financée par le CEA à Saclay. Le doctorant a effectué de cours séjours dans notre laboratoire mais est resté majoritairement à Saclay. L'encadrement se présentait donc sous la forme de quelques déplacements à Saclay (6 au total) et

<sup>&</sup>lt;sup>1</sup>ce CFA n'existe plus aujourd'hui

de réunions par visio-conférences (3 par mois en moyenne). Cette thèse est devenue la première soutenue en tant qu'encadrant. Elle a débouchée sur deux publications en conférences internationales avec actes et comité de lecture (ASAP, GLS-VLSI) et deux dépôts de brevets. *Cette thèse a surtout lancé l'activité autour des CGRAs, le premier des axes de recherche développé dans ce document au chapitre 4, p. 49.*

Le projet COMPA est un projet ANR qui a débuté le 1<sup>er</sup> octobre 2011 et s'est terminé au 30 juin 2015. Le consortium initial incluait 3 partenaires académiques, l'IETR, l'Irisa (l'équipe dans laquelle j'ai effectué ma thèse), le Lab-STICC, et 3 partenaires industriels, Texas Instrument, CAPS Entreprise, et Modaë. Ce consortium a malheureusement beaucoup évolué car les trois partenaires industriels ont dû successivement se retirer du projet. Dans le cadre du projet, j'ai participé activement à la rédaction des différents livrables. Ce projet a permis de financer une thèse que j'ai co-encadrée. Elle a été soutenue le 19 juin 2015, et donnée lieu à une publication en conférence internationale avec comité de lecture (DASIP), et à un article dans une revue internationale (JSPS). Cette thèse s'est intéressée à la problématique du déploiement d'acteurs flot-de-données sur une architecture multi-processeurs hétérogène. *C'est le deuxième axe de recherche qui sera développé dans ce document au chapitre 5, p. 75*.

Lors de nos recherches pendant le projet COMPA, nous avons été exposé à la problématique de la synchronisation de tâches sur les architectures multi-processeurs. Dans le cas particulier des acteurs flot-de-données, nous pouvons tout simplement nous appuyer sur des techniques existantes, mais celles-ci s'avèrent peu efficaces alors qu'il est possible de s'appuyer sur les caractéristiques des applications flot-dedonnées pour améliorer la synchronisation entre les acteurs, en particulier par une meilleure gestion des accès mémoire. L'idée est de monitorer l'activité mémoire et déclencher des calculs en fonction de cette activité. Cette idée repose directement sur le patron de conception « Observer », bien connu dans le monde de l'ingénierie logiciel. Ma formation en génie logiciel et les nombreuses mises en œvre que j'ai faite de ce patron de conception ont été particulièrement utiles. Un premier prototype virtuel de l'application de ce patron de conception en matériel a été réalisé et fait l'objet d'une publication en conférence internationale (DAC2016). Les très bons résultats obtenus sur une seule application (un décodeur H264) méritaient des investigations plus poussées, c'est pourquoi j'ai déposé un projet ANR JCJC en automne 2016. Ce projet a été accepté et s'est étalé sur la période janvier 2018 - juin 2022. Cette activité de recherche sur les mécanismes de synchronisation de manière générale, et en particulier sur l'idée originale de la capacité de la mémoire à déclencher des calculs, que j'ai nommé « Notifying memories », fait l'objet du troisième axe de recherche développé dans ce document au chapitre 6, p. 99.

Depuis quelques années maintenant je m'intéresse particulièrement à la problématique mémoire et au lien entre architectures de calcul et mémoire, pour l'exploitation du parallélisme au niveau instructions ou de données avec les CGRAs, ou le parallélisme de tâche sur architectures multi-processeurs. Cette interaction calcul/mémoire est complexe, nécessite du temps, et couvre un large spectre de thématique. Pour pouvoir y consacrer plus de temps et développer ma propre activité sur ce sujet, j'ai sollicité une délégation CNRS d'un an à temps plein, que j'ai obtenue pour l'année universitaire 2021-2022. Cette délégation s'est effectué dans mon équipe de recherche.

#### Élément de contexte

Un élément de contexte important est la restructuration du Lab-STICC sur la période 2019-2020 au niveau de l'organisation des équipes de recherche, ce qui a conduit à scinder l'ancienne équipe MOCS (plus de 80 personnes), dans laquelle j'étais depuis 2011, en trois nouvelles équipes, dont ARCAD, mon équipe de recherche actuelle, pour une mise en place officielle à l'occasion de l'évaluation HCERES début 2021, en même temps que la mise en place de la nouvelle équipe de direction. À cette occasion, ma mission d'organisateur de séminaires de l'équipe MOCS a pris fin pour être reprise par les chefs d'équipe.

#

Ce chapitre décrit les enseignements réalisés sur la période 2011-2021. Dans un premier temps, les thématiques enseignées sont décrites. Dans un deuxième temps, une présentation synthétique chiffrée sur les volumes est réalisée. Ensuite, les responsabilités liées à l'enseignement sont présentées. Enfin, une réflexion sur le métier d'enseignant est proposée.

#### 2.1 Description des thématiques enseignées depuis 2011

#### 2.1.1 Automatisme et Informatique Industrielle

#### Niveau : 1ère année de DUT GIM, IUT Lorient, UBS

La thématique « automatisme et informatique industrielle » est organisée autour de trois modules dont l'objectif est de connaître le fonctionnement et la structures des systèmes numériques, en particulier les systèmes automatisés. Je suis en charge de l'enseignement de la partie numération, système binaire, algèbre de Boole, logique combinatoire et logique séquentielle. Cette partie est sanctionnée d'un examen de 2 heures dont je suis responsable de l'élaboration du sujet et de la correction. Au deuxième semestre, j'enseigne la partie acquisition de données, du capteur à l'ordinateur, incluant les capteurs, conditionneurs de signaux, numérisation, filtrage, conversion analogique-numérique et numérique-analogique. Cette partie est sanctionnée d'un examen de 1 heure dont je suis responsable de l'élaboration du sujet et de la correction. J'encadre les séries de TP couvrant l'ensemble du spectre de l'automatisme, avec également la partie automate, programmation ladder et graphcet. J'ai développé sept manipulations de quatre heures pour cette thématique. Le volume d'enseignement associé à cette thématique est d'environ 90 heures eq. TD.

#### 2.1.2 Électronique analogique

Niveau : 1ère année de DUT GIM, IUT Lorient, UBS

Le module d'électronique analogique consiste fournir les bases aux étudiants de premières années autour des notions de filtrage analogique, passif ou actif, d'amplificateur opérationnel, systèmes asservis. Lors des travaux pratiques, il s'agit d'abord de familiariser les étudiants avec les instruments d'observation et de mesures (multimètre, oscilloscopes), et le matériel électronique d'alimentation, GBF, etc. J'aide à

l'encadrement de TP mis en place par mon collègue responsable du module. Le volume d'enseignement associé à cette thématique est d'environ 48 heures eq. TD.

#### 2.1.3 Informatique

#### Niveau : 2ème année de DUT GIM, IUT Lorient, UBS

L'objectif du module intitulé « INFO2 » dans la spécialité GIM est d'utiliser les outils informatiques nécessaires au traitement de données générales et professionnelles. Les compétences visées incluent l'analyse et la création d'algorithmes, ainsi que la traduction d'un algorithme simple en langage de programmation en respectant une syntaxe imposée. L'outil choisi pour l'analyse et la création d'algorithme est Algobox. Le langage de programmation enseigné est le langage C. J'ai mis en place 6 manipulations de quatre heures pour ce module. Le volume d'enseignement associé est d'environ 30 heures eq. TD.

#### 2.1.4 Acquisition et sécurisation de données

#### Niveau : Licence professionnelle, IUT Lorient, UBS

Ce module reprend la partie enseignée au niveau DUT 1ère année autour de l'acquisition de données, du capteur à l'ordinateur, incluant les capteurs, conditionneurs de signaux, numérisation, filtrage, conversion analogique-numérique et numérique-analogique. Le module est agrémenté d'une partie sur la vision industrielle, incluant les capteurs (imageurs), l'éclairage, et l'ensemble du système d'acquisition, traitement, analyse, interprétation et communication. La notion de cybersécurité des systèmes industriels est également abordée. J'ai aidé au développement de quatre manipulations de quatre heures pour ce module, dont je suis aujourd'hui responsable. Le volume d'enseignement associé à cette thématique est d'environ 30 heures eq. TD.

#### 2.1.5 Microsystème

#### Niveau : 3ème année d'école d'ingénieur, filière mécatronique, ENSIBS, UBS

L'objectif du module de microsystème est d'être capable de concevoir un système sur-mesure, avec des composants matériels spécifiques, et d'identifier la relation matérielle-logicielle à travers la couche d'abstraction du matériel. Ces compétences sont développées lors de la conception d'un système numérique composé d'un processeur et de plusieurs périphériques, afin de piloter un base robotique. Les travaux pratiques pour ce module s'articulent autour d'un projet de seize heures, découpé en plusieurs parties avec une complexité graduelle. La plateforme utilisée est une carte DE0-nano, avec la suite d'outils Intel/Altera associée. Le volume d'enseignement associé est d'environ 30 heures eq. TD.

#### 2.1.6 Programmation parallèle

#### Niveau : Master 2, filières Systèmes Embarqués Systèmes Intégrés, et Cyber-Sécurité des Systèmes Embarqués, UBS

L'objectif du module est de découvrir la programmation parallèle à travers l'approche OpenMP. Les compétences visées sont la capacité d'analyser un code existant et d'y extraire le parallélisme, en utilisant les directives simples d'OpenMP. J'ai mis en place deux manipulations de quatre heures pour ce module. Le volume d'enseignement total est d'environ 18 heures eq. TD. Cette activité, en lien étroit avec mes activités de recherche, me permet d'identifier les étudiants présentant une appétence particulière pour ce sujet.

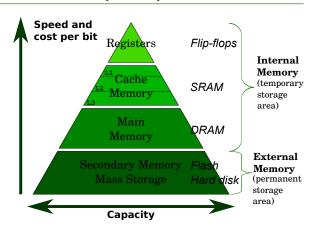

#### 2.1.7 Mémoires sur puce

Niveau : Master 2, filières Systèmes Embarqués Systèmes Intégrés, et Cyber-Sécurité des Systèmes Embarqués, UBS

10

L'aspect « mémoires sur puce » est une intervention spécifique dans le module « Système sur puce ». Cette intervention de quatre heures (6 heures eq. TD) permet d'identifier les problématiques de la mémoire sur puces, d'étudier les différentes technologies et organisations existantes, et comprendre la hiérarchie mémoire et son fonctionnement. Cette intervention est directement en lien avec mes activités de recherche.

#### 2.1.8 Algorithmes pour le VLSI

#### Niveau : Master 2, filières Systèmes Embarqués Systèmes Intégrés, UBS

Le module d'algorithmes pour le VLSI est un module dont j'ai assuré l'enseignement sur la période 2011-2016. L'objectif du module est dans un premier temps de faire connaître les différentes façons de concevoir des circuits, en se basant sur des cellules *full-custom, semi-custom, Gate Array*, ou FPGA. Le cycle de conception est présenté en identifiant les problèmes spécifiques rencontrées à chaque étape : synthèse, partitionnement, floorplanning, placement, routage, assignation des broches, compaction. Un focus est ensuite mis sur la notion de synthèse logique, avec l'utilisation des BDD (Binary Decision Diagram). Les algorithmes de partitionnement sont également regardés en détail, notamment l'incontournable Kernighan-Lin, et l'algorithme de Fiduccia et Mattheyses.

#### 2.1.9 Description des encadrements d'étudiants Projets tutorés

Sur la période 2012-2021, j'ai encadré les projets tutorés de première année de DUT. Cela représente quatre à six binômes tous les ans. Les sujets sont proposés par mes soins. Les étudiants peuvent aussi proposer leur sujet. Chaque binôme travaille sur un sujet différent. L'encadrement inclut un suivi régulier tout du long du deuxième semestre, une aide à la rédaction du rapport et l'élaboration de la soutenance, ainsi que la participation en tant que candide à autant de soutenances de projet (8 à 12 soutenances par an).

#### **O** Exemples de sujets

- Sujets donnés : Logiciels de simulation de circuits numériques, Matrice de LED sous Arduino, Système de déverrouillage d'un coffre par code (ou par badge), l'industrie à l'ère du numérique, ...

- Sujets proposés : arc électrique musical, cloche de protection mobile pour graveuse laser, ampli guitare à lampe, indicateurs lumineux pour motards, ...

La figure 2.1 montre le prototypage réalisé dans le cadre de la cloche de protection pour graveuse laser.

Projets GIM Période 2012-2021 41 binômes encadrés, 75 soutenances

Depuis 2017, j'encadre les projets tutorés de la licence professionnelle IMSA (Ingénierie et Maintenance des Systèmes Automatisés). Je propose un sujet tous les ans. J'encadre un seul binôme sur ce sujet. L'encadrement inclut un suivi régulier pendant la période de projet, une aide à la rédaction du rapport et l'élaboration de la soutenance, ainsi que la participation en tant que candide à une autre soutenance de projet.

#### **O** Exemples de sujets donnés

Maquette de monitoring, vision industrielle.

La figure 2.2 montre la maquette de monitoring réalisé dans le cadre des projets. L'ensemble matériel et logiciel a nécessité plusieurs binômes.

FIGURE 2.1 – Projet tutoré GIM1 - Réalisation d'une cloche de protection pour graveuse laser

FIGURE 2.2 – Projet tutoré IMSA - Maquette de monitoring

Projets LP IMSA *Période 2017-2021* 4 binômes encadrés, 8 soutenances

#### Encadrement de stages

L'encadrement des stages est équitablement réparti dans l'équipe pédagogique, ce qui représente trois à quatre stagiaires à encadrer tous les ans. L'encadrement inclut une visite en entreprise, une aide à la rédaction du rapport et l'élaboration de la soutenance, ainsi que la participation en tant que candide à autant de soutenances de stage (donc 6 à 8 soutenances par an). Il est à noter que la promotion 2020 était en pleine période de stage lors du confinement de mars 2020. Tous les stagiaires que j'encadrais ont eu la chance de pouvoir continuer leur stage, soit en présentiel (domaine de l'eau, activité essentielle), soit en distanciel. Seule la visite sur site n'a pas pu avoir lieu. Les soutenances ont eu lieu en distanciel.

#### Stages GIM2 Période 2011-2021

31 stagiaires encadrés, 62 soutenances

#### **Encadrement d'alternants**

Je participe à l'encadrement de deux types d'alternants : les apprentis du DUT GIM, ainsi que des contrats de professionnalisation de la licence pro IMSA. Bien que les niveaux soient différents, l'encadrement se concrétise par les mêmes actions : une à deux visites sur site par an, interactions avec le tuteur entreprise, point d'activité après chaque période en entreprise, aide à la rédaction du rapport et l'élaboration de la soutenance, participation en tant que candide à autant de soutenances que d'étudiants encadrés. Cela représente deux soutenances (une en tant que tuteur, une en tant que candide). Un étudiant en contrat de professionnalisation est amené à présenter deux fois : une fois début avril, et une autre fois fin août. Cela représente donc 4 soutenances par an. Lors du confinement de mars 2020, l'alternant GIM a continué son activité sur site (domaine agroalimentaire, activité essentielle). L'alternant IMSA a connu une période d'arrêt d'activité, sans possibilité de travailler à distance. L'encadrement a consisté également à rassurer l'étudiant sur la non remise en cause du diplôme.

2.2 Présentation synthétique des enseignements

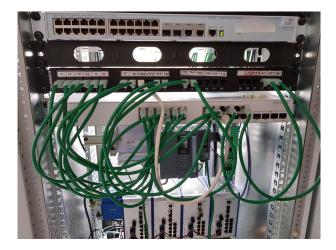

FIGURE 2.3 – Photo de l'armoire contenant une partie du matériel pour l'enseignement de la cybersécurité dans le département GIM.

Alternants Période 2011-2021

- 4 alternants GIM ( $4 \times 2$  ans), 32 soutenances

- 9 alternants IMSA ( $9 \times 1$  an), 36 soutenances

#### 2.1.10 Montée en compétence « cybersécurité des systèmes industriels »

Côté enseignement, le fait notoire des trois dernières années est une volonté de montée en compétence sur l'aspect « cybersécurité des systèmes industriels », insufflée à la fois par une décision politique de l'établissement, mais surtout par une préoccupation de nos partenaires industriels. Cette montée en compétence s'est traduite par le suivi de formations et l'intégration de la notion de cybersécurité des systèmes industriels pour la licence professionnelle IMSA (Ingénierie et Maintenance des Systèmes Automatisés) dans le cadre du module « acquisition et sécurisation de données ». L'IUT a investi récemment dans du matériel pour la mise en place de manipulations spécifiques sur cette thématique. Cet investissement important a permis au département GIM de s'équiper de plusieurs automates certifiés, d'un firewall, et de plusieurs switches ethernet industriels administrables et non administrables. Ce matériel était nécessaire pour la mise en place de nouvelles manipulations relatives à l'enseignement de la cybersécurité. Six maquettes sont en cours d'élaboration pour une série des six nouveaux TP. La figure 2.3 montre l'armoire qui accueille les automates, les switches administrables, et le firewall.

Par ailleurs, l'IUT de Lorient m'a nommé « référant cybersécurité ». Mes contacts quotidiens avec mes collègues de recherche de l'équipe ARCAD, dont certains sont spécialistes de cybersécurité, me confèrent une connaissance globale de cette problématique.

#### 2.2 Présentation synthétique des enseignements

Le tableau 2.1 présente l'enseignement effectué sur la période septembre 2011 - août 2021. Il est à noter que la somme des volumes de chaque enseignement n'est pas égale au service réalisé (heures payées), pour cause de proratisation des heures TP au delà du service dû, sauf pour la formation continue. Le volume pour chaque enseignement est donné en heure équivalent TD, avec 1h TP = 1h TD, et 1h CM = 1,5h TD.

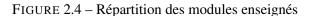

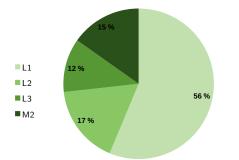

Le tableau 2.2 présente les modules enseignés sur la période 2011-2021, le niveau, le type de formation (initiale, continue), la nature (cours, TD, TP, encadrement), les effectifs moyens des promotions concernées, ainsi que le volume cumulé sur la période. La figure 2.4 propose une autre vue de ces enseignements et montre clairement que la partie automatisme et l'informatique industrielle est la plus importante.

| Année universitaire | Volume (service réalisé) |

|---------------------|--------------------------|

| 2011 - 2012         | 229                      |

| 2012 - 2013         | 247                      |

| 2013 - 2014         | 338                      |

| 2014 - 2015         | 282                      |

| 2015 - 2016         | 337                      |

| 2016 - 2017         | 340                      |

| 2017 - 2018         | 301                      |

| 2018 - 2019         | 288                      |

| 2019 - 2020         | 279                      |

| 2020 - 2021         | 292                      |

| Total               | 2 933                    |

TABLE 2.1 – Synthèse du volume d'enseignement réalisé sur la période septembre 2011 - août 2021

TABLE 2.2 - Synthèse des modules enseignés sur la période septembre 2011 - août 2021

| Enseignement                             | Niveau         | Type de formation    | Nature      | Effectif<br>moyen | Volume<br>cumulé |

|------------------------------------------|----------------|----------------------|-------------|-------------------|------------------|

| Automatisme et informatique industrielle | DUT1           | Initiale et continue | CM/TD/TP    | 80                | 1 081            |

| Électronique analogique                  | DUT1           | Initiale et continue | TD/TP       | 81                | 360              |

| Informatique                             | DUT2           | Initiale et continue | CM/TP       | 53                | 279              |

| Acquisition et sécurisation de données   | LP             | Continue             | TD/TP       | 25                | 154              |

| Microsystème                             | M2             | Initiale             | CM/TD/TP    | 35                | 248              |

| Programmation parallèle                  | M2             | Initiale             | CM/TD/TP    | 20                | 136              |

| Mémoires sur puce                        | M2             | Initiale             | СМ          | 20                | 12               |

| Algorithmes pour le VLSI                 | M2             | Initiale             | СМ          | 20                | 36               |

| Projets tutorés                          | DUT1, LP       | Initiale et continue | Encadrement | 12                | 108              |

| Encadrement de stages                    | DUT2           | Initiale             | Encadrement | 3                 | 152              |

| Encadrement d'alternants                 | DUT1, DUT2, LP | Continue             | Encadrement | 2                 | 264              |

La figure 2.5 montre la répartition des enseignements effectués par niveau. Étant affecté à l'IUT de Lorient, il est logique qu'une écrasante majorité de mes enseignements concerne les niveaux L1 (DUT1), L2 (DUT2), et L3 (LP), qui représentent près de 85% du volume. L'enseignement au niveau M2 (UFR, ENSIBS) occupe les 15% restants. On remarque que je n'ai effectué aucun enseignement au niveau M1 (BAC+4).

La figure 2.6 montre la répartition de mes enseignements par type. L'enseignement à l'IUT étant principalement axé sur l'apprentissage par la pratique, la majorité de mon activité (plus de 50%) concerne les travaux pratiques et l'encadrement de projets. L'encadrement lors de période en entreprise lors des alternances à l'occasion des stages représente 15%. Finalement, seulement 35% de mon activité se fait sous la forme de cours magistraux ou de travaux dirigés (et encore, les heures sont données en equivalent TD, les heures de cours en présentiel sont donc artificiellement gonflées de moitié).

#### 2.3 Responsabilités et autres activités liées à l'enseignement

#### 2.3.1 Programme pédagogique national

Le programme pédagogique enseigné à l'IUT est défini nationalement. J'ai participé à la mise en jour en 2015 du programme pédagogique qui concerne la partie automatisme et informatique industrielle. J'ai participé à la rédaction du nouveau programme lors du passage au BUT, notamment les modules (appelés « ressources ») informatique et certains liés à l'automatisme.

#### 2.3.2 Commission pédagogique

J'ai été membre de la commission pédagogique de l'IUT de Lorient sur la période 2017-2021. L'objectif principal de cette commission est d'organiser des « cafés pédagogiques », événements rassemblant

- Automatisme et Informatique Industrielle

- Électronique analogique

- Informatique

- Acquisition et sécurisation de données

- Microsystème

- Programmation parallèle

- Mémoires sur puce

- Algo VLSI

FIGURE 2.5 – Répartition des enseignements effectués par niveau (en heure eq. TD)

FIGURE 2.6 – Répartition des enseignements effectués par type (en heure eq. TD)

l'ensemble des enseignants de l'IUT de Lorient sur les thèmes des pratiques pédagogiques innovantes. Nous avons organisé des événements dédiés sur les sujets suivants : les quiz, les capsules vidéo, classe inversée, cours en ligne. Il faut noter que l'action « cours en ligne » s'est déroulée avant le confinement et s'est révélée très utile à cette occasion.

#### 2.3.3 Référant cybersécurité

Depuis 2019, je suis référant cybersécurité de l'IUT de Lorient, rôle qui consiste à :

- Être le référent de l'IUT de Lorient pour tout ce qui concerne la cybersécurité, et en particulier sur la cybersécurité des systèmes industriels.

- Être force de proposition pour introduire ou développer la cybersécurité au sein des formations de l'IUT de Lorient, et en particulier dans la licence « IMSA ».

- Conseiller la direction de l'IUT sur le thème de la cybersécurité et permettre à l'IUT de développer des compétences et donc des offres de formation en cyber (particulièrement dans le cadre de la cybersécurité des systèmes industriels) aussi bien en formation initiale qu'en formation continue.

- Représenter l'IUT de Lorient au bureau de l'institut cyber de l'UBS

- Suivre des formations pour monter en compétence dans le domaine de la cybersécurité et partager en retour avec les collègues des formations concernées.

- Assister aux différentes conférences organisées autour de la cybersécurité au sein de l'UBS

#### 2.4 Synthèse et réflexions sur le métier d'enseignant

Après 10 ans d'expérience en enseignement, je me pose encore les mêmes questions : comment transmettre la connaissance de manière efficace ? Comment améliorer mes enseignements ?

L'enjeu n'est pas le même selon le niveau enseigné. La maîtrise du contenu au niveau DUT n'est pas

une difficulté. Il s'agit d'enseigner les bases des différentes disciplines, qui par définition n'évoluent pas ou très peu. Le défi est au niveau pédagogique. Comment faire comprendre ces notions de base à des générations d'étudiants en constante évolution ? Les générations successives arrivent avec des bagages différents alors que le programme pédagogique reste le même. Dans le domaine technologique que j'enseigne, ces différences sont de manière intéressante liées à un certain contexte sociétal d'utilisation des outils numériques. Par exemple, il était quasiment acquis il y a quelques années que les étudiants connaissent une arborescence de fichiers dans un ordinateur. Avec l'utilisation massive des smartphones et la gestion transparente du stockage de l'information notamment dans le cloud, la notion d'arborescence de fichiers n'est plus acquise, et doit être revue.

L'enseignement au niveau master ou école d'ingénieur présente un autre défi. La maîtrise du contenu doit être consolidée, même au delà du périmètre défini dans le cadre du cours, pour mieux positionner le module dans un contexte plus général, et être capable de répondre aux éventuelles questions qui sortent du cadre.<sup>1</sup>

Du niveau BAC+1 à BAC+5, j'ai expérimenté différentes techniques, pour les CM, les TD, ou les TP, souvent après discussions et échanges avec les collègues. Pour les cours magistraux, au niveau DUT1 et DUT2, j'ai proposé des mini quiz, d'une dizaine de minutes, en fin de cours. Cela permet d'avoir un retour instantanée des notions comprises ou non en sortant du cours (mémoire court terme). J'ai même donné exactement le même quiz deux semaines après le premier (et après les TD sur ces notions, en prévenant les étudiants) pour évaluer la mémoire à long terme. Les résultats sur quelques promotions montrent que la moyenne du deuxième quiz est moins bonne que la moyenne du premier. Pour le niveau BAC+5, il m'arrive de proposer des cours très interactifs (lorsque le nombre d'étudiants le permet). Il s'agit d'échanger avec les étudiants, pour s'appuyer sur les bases déjà acquises pour faire connaître les nouvelles notions. Cette méthode marche généralement bien pour le premier cours d'un module.

Pour les TD, j'ai également utilisé la technique très classique d'envoyer une étudiante ou un étudiant au tableau, soit pour une correction interactive, soit pour écrire simplement la correction pour tout le monde pendant que j'explique individuellement. J'ai également essayé de faire travailler en petit groupe de 4/5 étudiants. Il n'y a finalement (sans surprise) pas de recette miracle. En fonction du contenu à transmettre, de l'autonomie des étudiants, et des acquis du cours magistral qui a précédé, le travail en groupe TD doit s'adapter.

Pour les TP, nous<sup>2</sup> avons proposé de constituer des binômes tournants. La constitution des binômes d'étudiants pour les séances de travaux pratiques est souvent laissée à la discrétion des étudiants euxmêmes. Par ailleurs, le binôme formé lors de la première séance est inchangé pour le reste de la série de TP. Ce schéma fonctionne généralement dans le cadre de TP parallèle, chaque binôme effectuant le même sujet de TP. Pour des raisons d'encombrement et de budget, les TP dans les ateliers mécaniques, ou les TP que j'encadre en automatisme, sont des TP « tournants », chaque binôme se trouvant sur une machine différente. Par ailleurs, pour des raisons pédagogiques, il est préférable que des binômes différents soient constitués à chaque séance. On pourrait même pousser la réflexion jusqu'à affirmer que ceci est une bonne reconstitution d'un contexte professionnel, puisqu'on ne choisit pas forcément les collègues avec lesquels on travaille. Différentes contraintes doivent être respectées, avec des possibilités de variation de taille de groupes, d'ordre à respecter pour certains TP, etc. Bien évidement, un étudiant ne doit pas faire le même TP plusieurs fois, et si possible, un binôme déjà créé ne doit pas être reformé, un monôme doit être unique pour la série de TP, etc. Il peut exister des cas où (et c'est généralement le cas), en cours de série de TP, la planification est changée (par l'enseignant). Ceci arrive typiquement lorsque plusieurs étudiants sont absents. Il est alors préférable de voir un même binôme reconstitué plusieurs fois que deux monômes (bien que cette affirmation ait fait l'objet de plusieurs débats : vaut-il mieux apprendre seul qu'à deux ? Qu'en est-il de la qualité de l'encadrement lorsqu'il y a trop de monômes?). Lorsque les classes sont grandes, l'affectation des binômes et des TP devient très vite un vrai casse-tête.

<sup>&</sup>lt;sup>1</sup>ceci dit, cela m'est arrivé plusieurs fois de dire simplement « *je ne sais pas* », et de revenir au cours suivant avec la réponse à la question.

<sup>&</sup>lt;sup>2</sup>sur l'idée originale de mon collègue Philippe Corfa

#### RÉFÉRENCES

Le problème d'affectation de binômes s'apparente à un problème de planification d'événements sportifs, les élèves étant alors les équipes, et les manipulations les terrains de sport. Le problème de planification d'événements sportifs (SSP pour *sport scheduling problem*) est un problème classique de la littérature. Il est intéressant de noter qu'au delà de la modélisation classique d'événements sportifs, le problème d'affectation de binômes requiert des contraintes particulières. J'ai mis à profit mes compétences en programmation par contraintes pour résoudre de manière automatique le problème d'affectation de binômes. Cette méthode a même fait l'objet d'une publication en conférence (ROADEF).

On parle aujourd'hui beaucoup de pédagogie innovante, avec des approches comme la pédagogie inversée, la pédagogie innovante collaborative, l'approche par projet, les CTF (Catch The Flag), les serious games, le travail de groupe. Les sciences de l'éducation évoluent aussi, et abondent régulièrement de nouvelles théories d'apprentissage. Personnellement, je les accueille avec beaucoup d'intérêt et de curiosité. On peut se questionner sur l'organisation classique CM/TD/TP, et notamment sur l'efficacité du cours magistral. Dans son article, Philippe Meirieu se pose même la question de le supprimer, sans préconiser de supprimer toute forme de magistralité [3]. En effet, le cours magistral s'est imposé dans un temps où l'accès à la connaissance n'était possible qu'à travers les livres, et l'explication n'était possible qu'en présentiel et de manière synchronisée. Aujourd'hui, la connaissance est disponible n'importe quand sur Internet, et les différentes plateformes de diffusion foisonnent d'explications sous forme de vidéos. Il est donc possible d'accéder à la connaissance à la demande depuis chez soi, en suivant son propre rythme d'apprentissage. Cela peut-il sonner le glas du métier d'enseignant? Au contraire. Je pense que cela renforce son utilité et sa responsabilité. En effet, Internet, c'est aussi « l'illusion de la connaissance » [1]. Internet, c'est l'information et la désinformation, la connaissance et la méconnaissance à la fois. Le rôle de l'enseignant dans ce contexte est non seulement d'alimenter le contenu (ce que beaucoup de collègues font déjà très bien par ailleurs), mais aussi, et surtout, d'être capable de diriger les étudiants vers les bonnes ressources, de trier l'information, et de maintenir l'intégrité du socle de connaissances pour les transmettre aux générations futures.

Pour améliorer la qualité de son enseignement, on peut demander un retour des étudiants. L'évaluation des enseignements est un sujet qui revient régulièrement sur la table et suscite souvent un débat dans notre communauté. Il est intéressant de regarder son impact dans les pays qui la pratique depuis plusieurs années. Ainsi, cette évaluation peut s'accompagner d'effets indésirables, comme en témoigne la mise en garde proposée dans [2]. Le risque est de se concentrer sur la satisfaction des étudiants, qui peut passer par de l'indulgence voire du laxisme vis à vis des efforts à fournir, au détriment de la transmission de la connaissance.

#### Références

- [1] Matthieu RICARD et Bruno PATINO. Internet, c'est l'illusion de la connaissance. fr. URL : https://www.parismatch.com/Actu/Societe/Matthieu-Ricard-et-Bruno-Patino-Internet-c-est-l-illusion-de-la-connaissance-1788572 (visité le 21/07/2022) (cf. page 17).

- [2] Nina Powell Rebekah WANIC. Student-centred education : a philosophy most unkind. en. Avr. 2022. URL : https://www.timeshighereducation.com/depth/student-centrededucation-philosophy-most-unkind (visité le 21/07/2022) (cf. page 17).

- [3] Philippe MEIRIEU. "Faut-il supprimer le cours magistral?" In : *Cahiers pédagogiques* 424 (mai 2004), p.7-9 (cf. page 17).

#

Ce chapitre présente une synthèse de mes activités de recherche réalisées sur la période septembre 2011 à juin 2022. La première section présente de manière synthétique trois axes de recherche qui seront ensuite développé en partie II. La suite du chapitre énumère l'ensemble de mes activités liées à la recherche : encadrement doctoral et scientifique, diffusion et rayonnement, outils logiciels, et responsabilités. Le chapitre se termine par une une réflexion sur le métier de chercheur et la liste de mes publications.

#### 3.1 Présentation synthétique des thématiques de recherche

Mes différentes activités et contributions en recherche peuvent se réunir sous une bannière « Méthodes, outils et supports matériels pour le déploiement d'applications parallèles sur architectures parallèles ». Trois grands axes de recherche peuvent ensuite se dégager et sont présentés de manière synthétique ici. Les trois axes de recherche sont :

- 1. Architectures de calcul spécialisées

- 2. Déploiement de tâches sur architectures parallèles

- 3. Synchronisation de tâches sur architectures parallèles

Ces trois axes de recherche sont ensuite présentés en détails dans trois chapitres différents qui constituent le cœur de ce document.

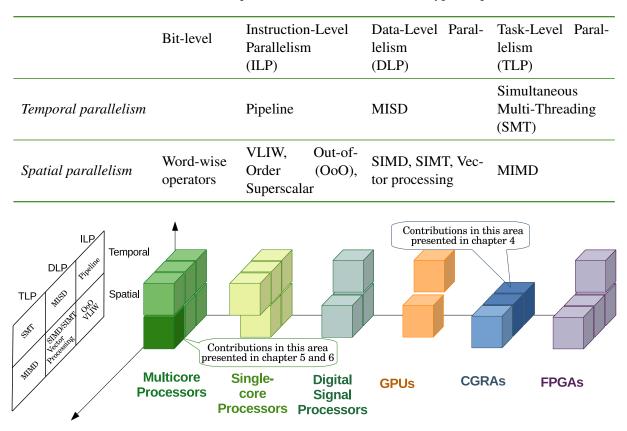

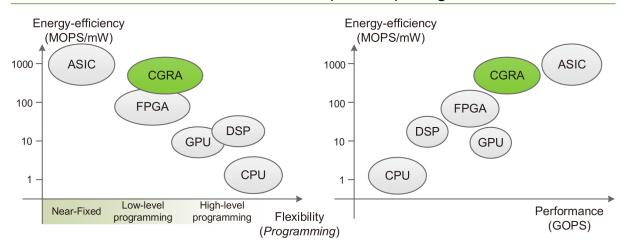

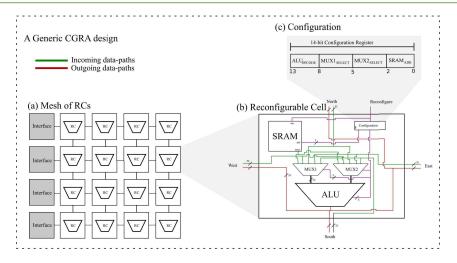

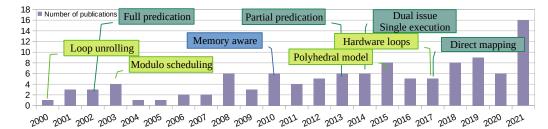

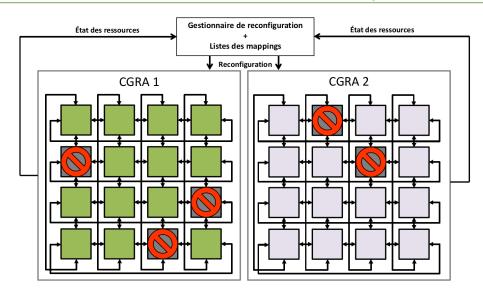

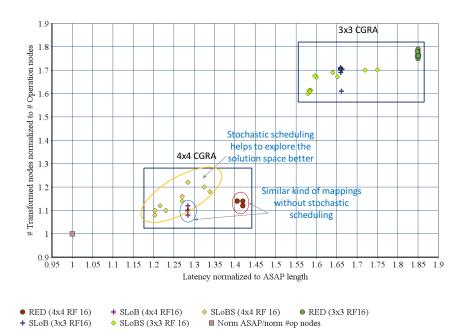

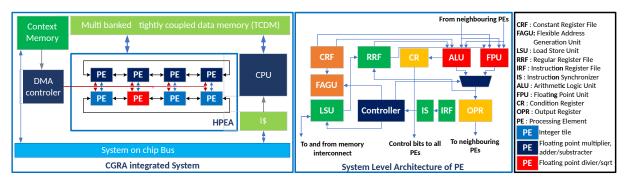

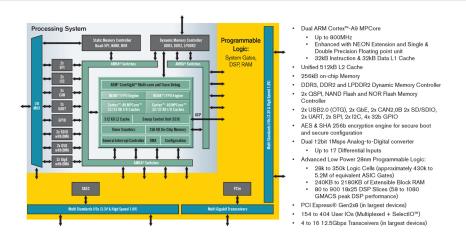

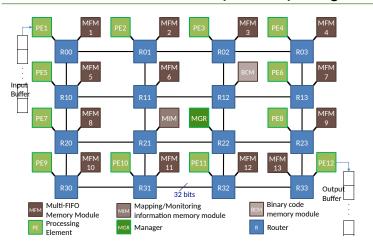

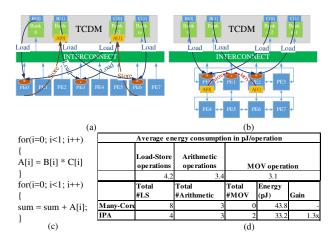

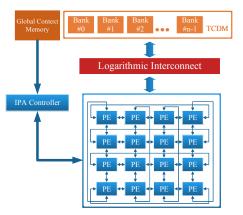

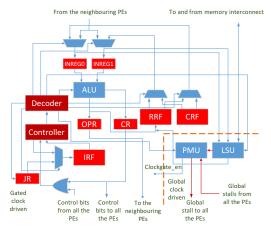

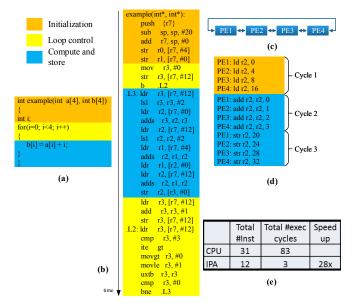

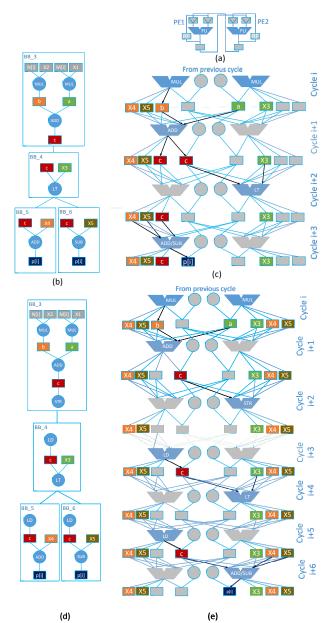

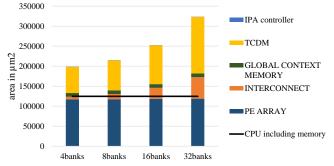

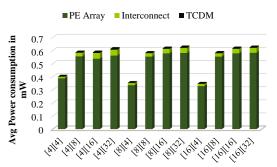

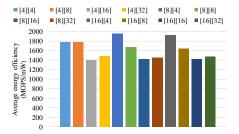

#### 3.1.1 Architectures de calcul spécialisées

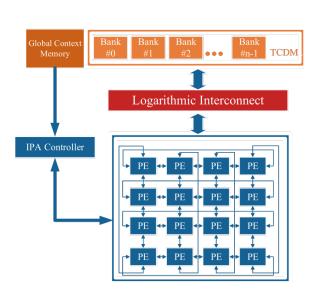

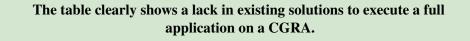

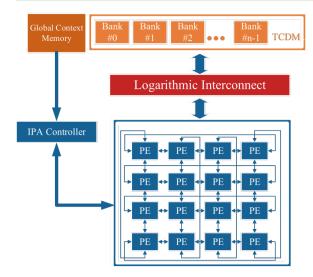

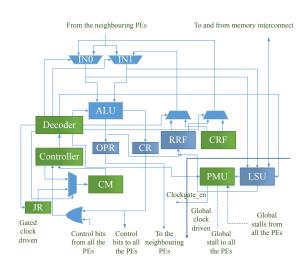

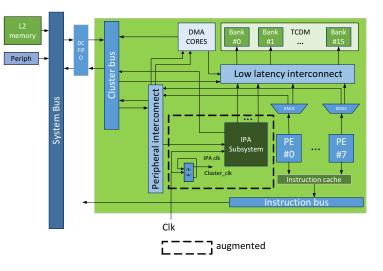

Les architectures de calcul spécialisées que j'étudie exploitent le parallélisme au niveau instructions et au niveau données, et s'inscrivent dans la catégorie des architectures reconfigurables à gros grain (CGRA pour Coarse Grained Reconfigurable Architecture). Dans le spectre des architectures de calcul, ces solutions proposent un compromis intéressant entre flexibilité et performance. Dans nos travaux, nous proposons des architectures très faible consommation qui respectent des budgets énergétiques très serrés de l'ordre de 3 mW, pour des systèmes embarqués ou des nœuds IoT. La figure 3.1 montre une vue schématique du CGRA que nous avons développé, appelé IPA pour *Integrated Programmable Array*. La flexibilité est apportée par le côté programmable de ces architectures. Elles doivent donc être accompagnées de méthodes et outils de projection d'application (compilation), incluant les structures de contrôle, conditionnelles et itératives, ce qui fait principalement l'objet de mes travaux. La question de la projection d'application peut se formuler ainsi : comment ordonnancer dans le temps et placer dans l'espace les opérations de l'application sur les

opérateurs de l'architecture, tout en respectant les dépendances de données et de contrôle, dans un temps raisonnable, de sorte que l'application soit la plus performante possible (temps d'exécution, efficacité énergétique)? Trouver la réponse consiste à résoudre plusieurs problèmes NP-complets, ce qui rend le sujet assez unique dans le domaine des architectures numériques de calcul.

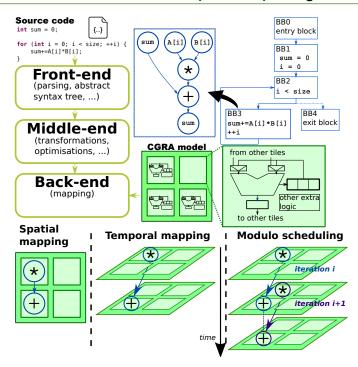

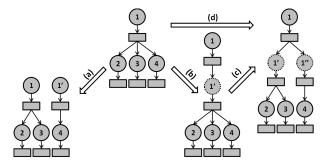

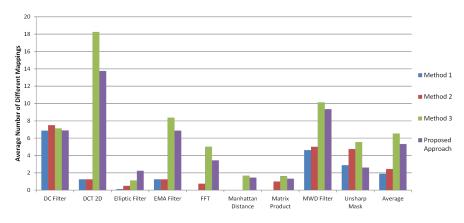

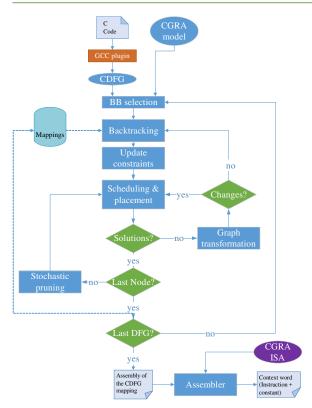

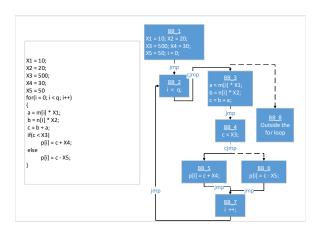

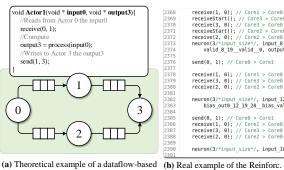

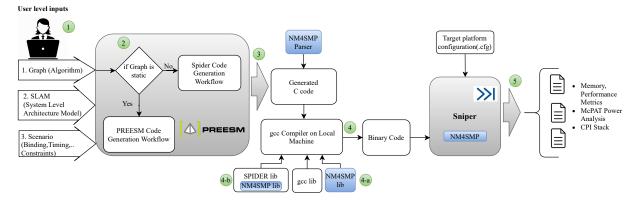

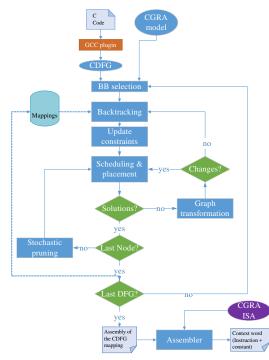

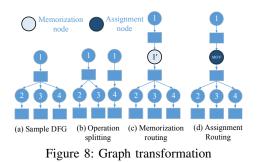

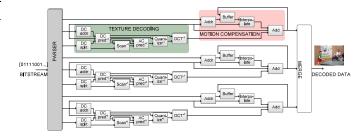

Nos principales contributions se situent autour de notre outil logiciel de projection d'application et de l'architecture du CGRA (conception des éléments de calcul, interconnexion, etc.). Un exemple de flot de compilation est donné figue 3.2, qui prend en entrée l'application spécifiée en langage C et un modèle de l'architecture CGRA cible. L'application est ensuite représentée sur forme de CDFG (*Control Data Flow Graph*), une représentation interne sous forme de graphe permettant de regrouper le flot de contrôle et le flot de données de l'application. La compilation sur CGRA consiste à « projeter » le CDFG sur un modèle du CGRA, également représenté sous forme de graphe. Il s'agit ensuite de résoudre un problème de placement et d'ordonnancement, que nous avons choisi de résoudre conjointement. Si ce problème n'a pas de solution, il est possible de transformer le graphe de l'application à la volée (par un jeu de mouvement ou de recalcul) pour tenter à nouveau de résoudre le problème [37].

CGRA model GCC plugin CDFG BB selection BB selection BB selection CDFG BB selection Constraints Scheduling & yes Changes? placement Solutions? no Graph Solutions? no Graph Solutions? no Graph Stochastic pruning Ves Stochastic pruning Ves Asembler Constraints Stochastic pruning Constraints Stochastic pruning Constraints Stochastic pruning Constraints Solutions? no Graph Constraints Stochastic pruning Constraints Solutions? no Graph Constraints Stochastic pruning Constraints Stochastic Sto

FIGURE 3.1 – IPA, *Integrated Programmable Array*, le CGRA que nous avons proposé

FIGURE 3.2 – Flot de projection d'une application spécifiée en langage C sur une architecture type CGRA

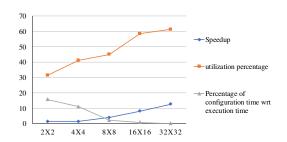

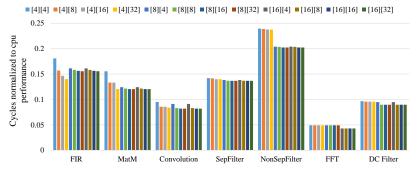

Une difficulté majeure est la prise en compte du flot de contrôle lors de la projection de l'application. Initialement étudié pour exécuter seulement le flot de données d'une application, aucun CGRA de l'état de l'art ne permettait de supporter le flot de contrôle (incluant le contrôle de boucles). Le support actuel du flot de contrôle (en plus du flot de données) permet d'obtenir une projection efficace. Nous avons proposé une solution pour le support de tout type de flot de contrôle (structures conditionnelles, alternatives, itératives) permettant de réduire les accès mémoire entre le CGRA et la mémoire partagée avec un processeur [25]. Nos résultats montrent un facteur d'accélération de 4 par rapport à un processeur généraliste pour un surcoût de 1.6 en surface, et un facteur de 1.8 par rapport aux techniques de l'état de l'art, sur les performances en nombre de cycles [7]. Cette projection efficace couplée à une faible consommation de l'architecture permettent un gain énergétique d'environ un ordre de grandeur par rapport à un processeur généraliste.

Dans notre approche, une projection complète est construite itérativement à partir de solutions partielles.

Mais toutes les solutions partielles n'aboutissent pas forcément à une solution complète. La principale difficulté lors du processus de projection est alors la maîtrise du nombre de solutions partielles permettant d'aboutir à une solution complète. Pour être sûr de trouver une solution, il faudrait conserver toutes les solutions partielles, ce qui en pratique n'est pas possible. En effet, il s'agit de résoudre conjointement un problème d'ordonnancement et un problème de placement qui sont tout deux des problèmes NP-complets. Le nombre de solutions partielles explose de manière exponentielle, et ce nombre devient très vite ingérable même pour de petites instances. Nous avons développé une technique de sélection intelligente pour conserver le bon nombre de solutions partielles [1, 28]. Ce nombre doit être suffisamment grand pour conserver une chance d'aboutir à une solution complète à partir d'une solution partielle, mais également suffisamment petit pour garder la maîtrise sur le nombre. Il s'agit également de s'assurer de conserver une certaine diversité dans les solutions partielles conservées. Notre technique permet de trouver des solutions pour des instances que d'autres approches de l'état de l'art ne permettent tout simplement pas d'obtenir.

Nous avons en complément proposé une approche permettant de répartir le plus uniformément possible les différents calculs sur les différentes tuiles, afin de diminuer la taille de la mémoire de configuration de chaque tuile [19]. Nous avons également proposé d'inclure les opérateurs permettant d'effectuer du calcul en virgule flottante [6], et des opérateurs pour la *transprécision* [18]. L'idée de la *transprécision* est de s'autoriser une perte de précision dans les calculs tout en gardant la dynamique des nombres, afin de réduire la consommation énergétique et d'établir un compromis précision/qualité du résultat. Nos résultats montrent un gain d'un ordre de grandeur en consommation énergétique pour un dégradation au pire de 9% de la qualité de résultats. Cet axe sera présenté dans le chapitre 4, p. 49.

Architectures de calcul spécialisées Période 2011-2022

Cette activité de recherche sur les CGRA et leur flot de compilation associé représente en tout :

- 3 thèses soutenues, 2 en cours

- 1 post-doc

- 4 articles de revue [1, 4, 6, 7]

- 2 brevets [10, 11]

- 10 publications en conférences [13, 16, 17, 18, 21, 25, 26, 28, 36, 37]

- plusieurs communications orales [48, 52, 27, 35]

#### 3.1.2 Déploiement de tâches sur architectures multi-processeurs

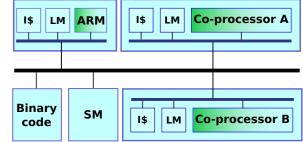

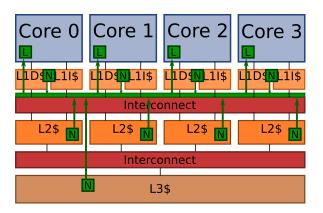

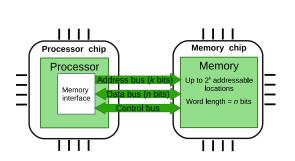

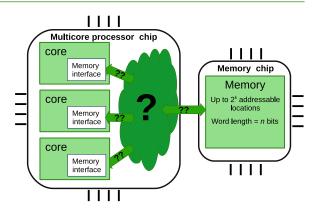

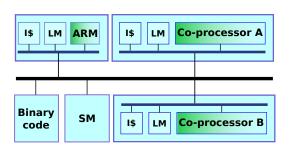

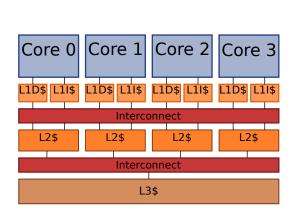

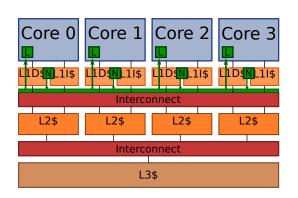

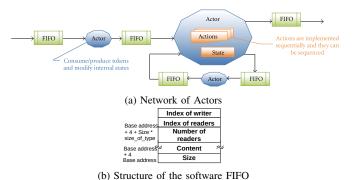

Le parallélisme niveau tâches est exploité par des architectures multi ou many-core. Nous nous intéressons aux architectures présentant quelques cœurs à plusieurs dizaines, et plus particulièrement à l'organisation du sous-système mémoire accompagnant ces architectures. Une exploitation efficace du parallélisme inhérent aux architectures multi-processeurs peut être particulièrement laborieuse d'un point de vu logiciel, surtout lorsque les particularités de la machine sont visibles du code applicatif. Une approche alors généralement adoptée consiste à considérer une seule mémoire partagée et cohérente, agrémentée de mécanismes de synchronisation adéquats, pour limiter l'adhérence du code applicatif à la machine cible. La mémoire est alors organisée autour d'une hiérarchie mémoire, constituée de la mémoire principale et de plusieurs niveaux de caches. Un ensemble de mécanismes matériels et logiciels complexes garantissent la consistance et la cohérence des données. Nous cherchons à répondre à une première question autour de ces architectures : comment déployer une application type flot-de-données ?

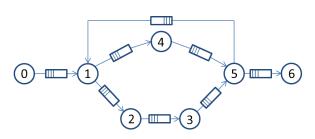

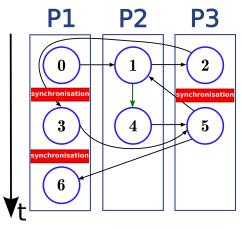

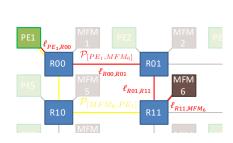

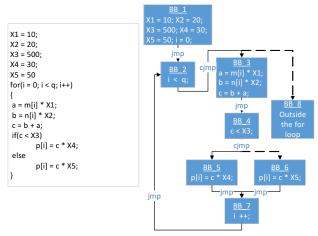

Le modèle de calcul flot-de-données possède des propriétés spécifiques qu'il est intéressant d'exploiter dans le cadre du parallélisme. Une application dite flot-de-données permet d'exprimer de manière explicite plusieurs niveaux de parallélisme : parallélisme de tâches, parallélisme de données, parallélisme temporel et parallélisme spatial. Un exemple de spécification d'une application sous cette forme est présenté figure 3.3. Si le déploiement d'applications flot-de-données sur une architecture multi-processeurs paraît alors évident, il n'en est pas de même pour le déploiement des données en mémoire. En réalité, de nombreuses complications viennent contre-carrer le déploiement, et en particulier, l'hétérogénéité du

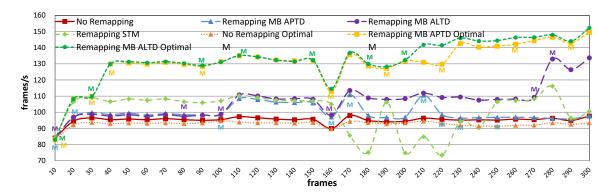

FIGURE 3.3 – Exemple d'application flot-dedonnées constituée de 7 tâches

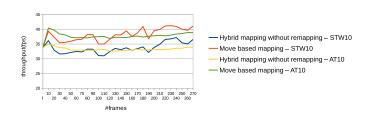

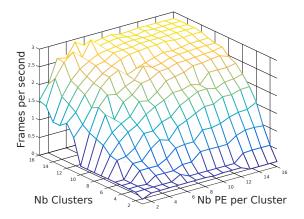

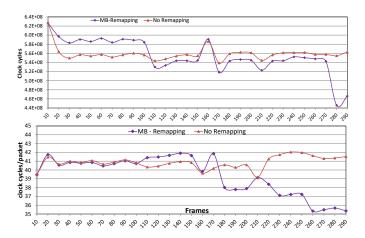

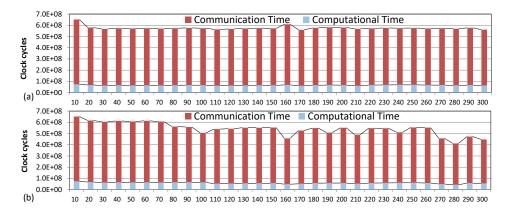

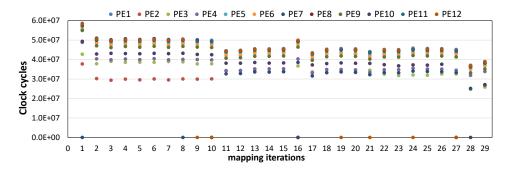

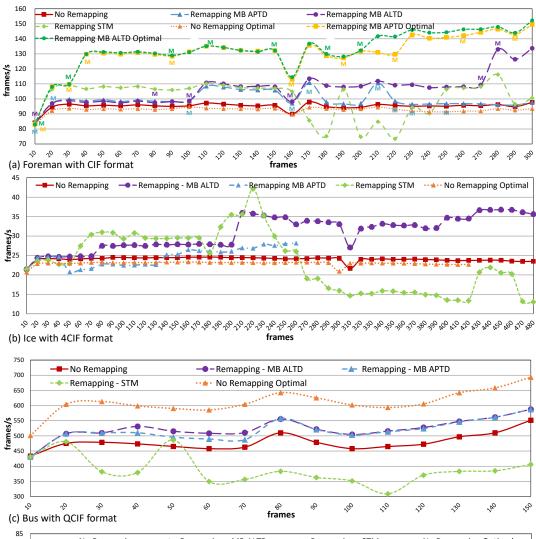

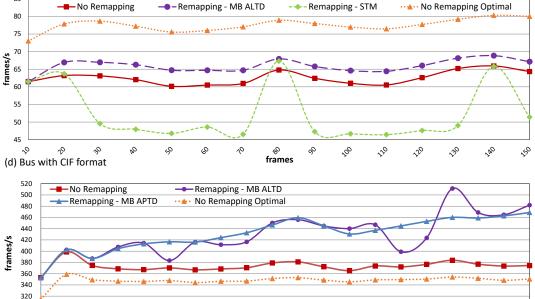

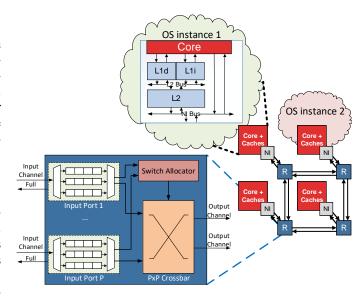

temps d'exécution des tâches et des temps d'accès à la mémoire, surtout dans le cadre d'applications flot-de-données dynamiques, et l'utilisation de buffers de données suivant un accès de type FIFO (First In First Out) qui n'exploitent pas favorablement les caractéristiques des caches présents aujourd'hui dans les machines. Le déploiement de tâches flot-de-données sur architectures multi-processeurs peut se modéliser sous la forme d'un problème de partitionnement de graphe. Ce problème peut ensuite être résolu à l'aide des méthodes bien connues du domaine, comme l'algorithme de Kernighan-Lin. Nous avons proposé un algorithme, basé sur l'algorithme de Fiduccia-Mattheyses, pour le déploiement à la volée d'applications flot-de-données dynamiques [8]. Le côté dynamique des applications étudiées impose de modifier à la volée le déploiement afin de répartir équitablement la charge de travail sur les processeurs à disposition. L'approche proposée, étudiée dans le cadre d'une application. L'idée défendue dans nos travaux est que le changement d'affectation s'accompagne d'un surcoût causé par les mouvements de données et d'instructions en mémoire. Nous avons montré qu'il n'est pas toujours rentable de changer complètement le placement, comme cela est proposé dans la littérature, dans un article accepté récemment [3], et fourni dans ce document en annexe B.

#### Déploiement de tâches sur architectures parallèles Période 2011-2022

Cette activité de recherche sur le déploiement d'applications flot-de-données sur architecture multi-processeurs représente en tout :

- 1 thèse

- 1 post-doc

- 1 projet ANR PRCI (COMPA)

- 1 projet Jeunes Chercheurs du GdR ISIS (MORDRED)

- 2 articles de revue [3, 8]

- 4 publications en conférences [23, 30, 33, 34]

- plusieurs communications orales ou demos [55, 56, 57, 58, 59]

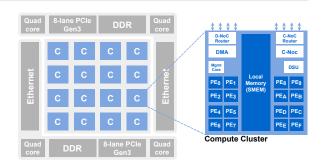

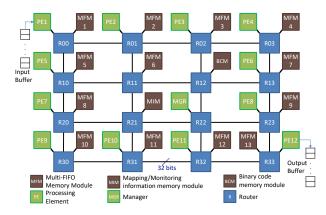

#### 3.1.3 Synchronisation de tâches sur architectures multiprocesseurs

Nous cherchons ici à répondre à une deuxième question autour des architectures multiprocesseurs : comment garantir la synchronisation ?

Deux verrous principaux sont identifiés aujourd'hui dans le déploiement des applications parallèles : 1) l'accès aux données, 2) la synchronisation entre les tâches. La figure 3.5 montre un exemple de déploiement du graphe de la figure 3.3 sur une architecture constituée de trois processeurs, selon un algorithme d'affectation élémentaire de type First-fit. Les traits noirs représentent les dépendances de données, telles qu'elles sont imposées par la structure du graphe. Le temps étant représenté en ordonné vers le bas, il paraît évident que les tâches 0 (T0) et 1 (T1) ne peuvent en réalité pas être ordonnancées en même temps, T1 ayant une dépendance de données sur T0. Même si dans le cadre d'une application flot-de-données, le parallélisme serait possible entre la deuxième itération de T0 et la première de T1 (parallélisme temporel), nous considérons pour plus de simplicité une unique itération du graphe. La synchronisation entre T0 et T1 est alors explicite, T1 doit attendre que T0 ait terminé (produit les données) pour pouvoir s'exécuter. L'autre type de synchronisation à observer est la synchronisation entre T0 et T3, qui sont affectés au même processeur. Même si T0 a terminé, T3 ne peut être exécutée qu'à condition que la tâche 2 (T2) ait terminée. Il faut donc ajouter de manière explicite dans le code applicatif un mécanisme de synchronisation. Dans cet exemple, finalement seul la dépendance entre T1 et T4 (symbolisée en vert) ne nécessite de synchronisation particulière. Dans tous les autres cas, une vérification préalable par un mécanisme de synchronisation est requise.

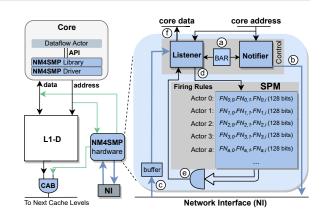

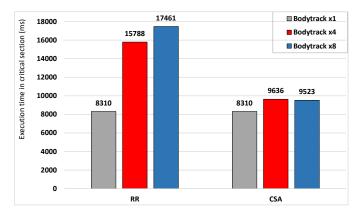

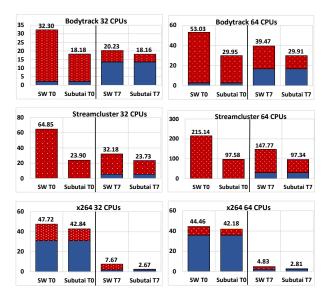

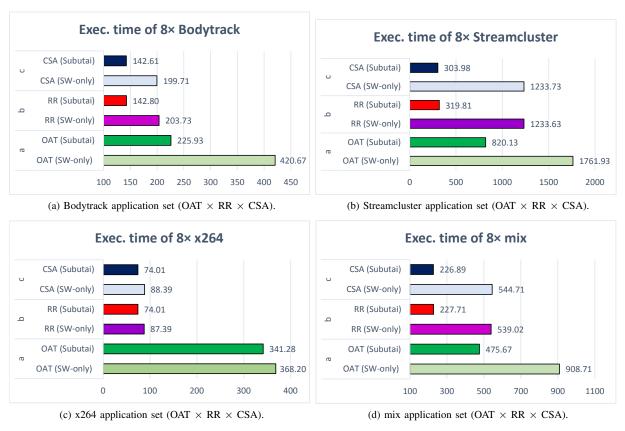

FIGURE 3.5 – Exemple d'ordonnancement des tâches de la figure 3.3 sur une architecture à 3 processeurs

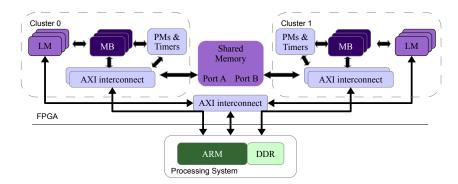

FIGURE 3.6 – Exemple de plateforme constituée de quatre processeurs avec une intégration des *no-tifying memories*

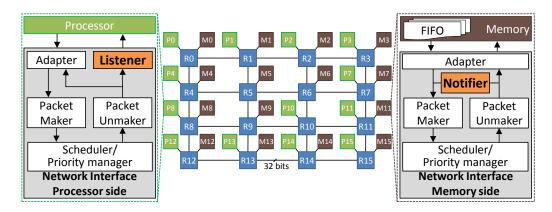

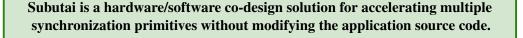

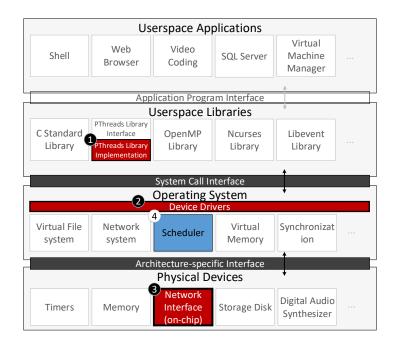

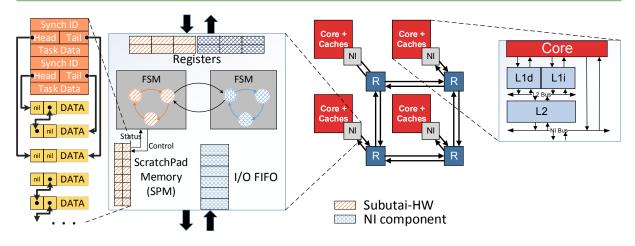

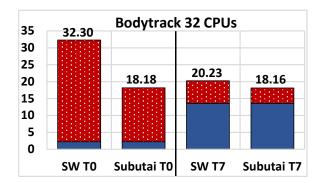

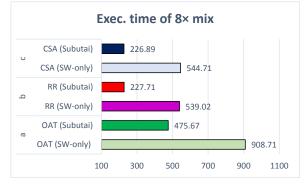

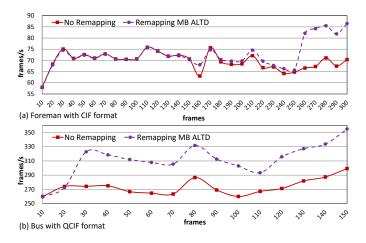

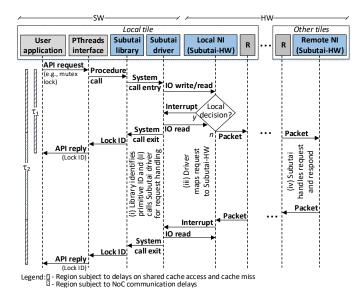

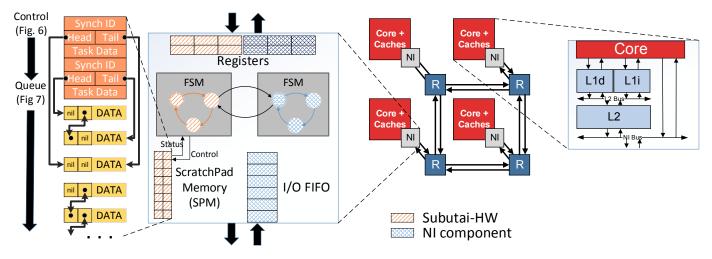

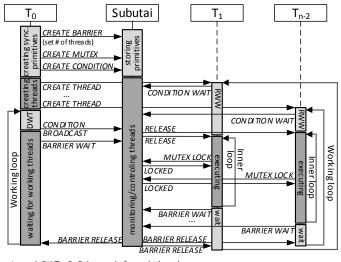

Nous proposons des supports matériels pour les mécanismes de synchronisation, en dehors du processeur, permettant de répondre aux problèmes d'accès aux données et de synchronisation. Premièrement, une solution logicielle/matérielle a été proposée pour distribuer les mécanismes de synchronisation dans le réseau sur puce, tout en restant compatible avec le code source originel [20]. Cette solution est composée d'un matériel spécialisé dans l'accélération des opérations de synchronisation, une mémoire privée, un pilote de système d'exploitation et une bibliothèque personnalisée. Nous ciblons la bibliothèque POSIX Threads (PThreads), largement utilisée comme bibliothèque de synchronisation native et en interne par d'autres bibliothèques telles que OpenMP ou TBB. Nous fournissons aussi des extensions destinées à accélérer encore davantage les applications dans deux cas: (i) plusieurs applications dans un contexte d'exécution fortement disputé; et (ii) sérialisation d'accès pour les variables condition dans Pthreads. Les résultats expérimentaux sur quatre applications du benchmark PARSEC fonctionnant sur un MPSoC à 64 cœurs montrent une accélération moyenne des applications de 1,57 par rapport à des solutions purement logicielles. Une accélération de 5% en plus est obtenue en utilisant notre politique d'ordonnancement *Critical Section-aware* comparée à un ordonnanceur *Round-Robin* de base.

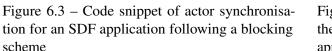

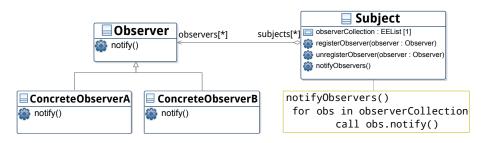

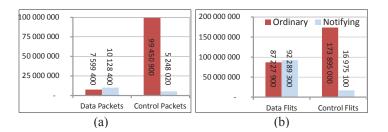

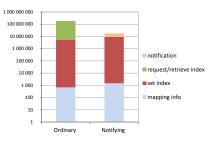

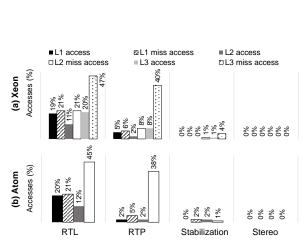

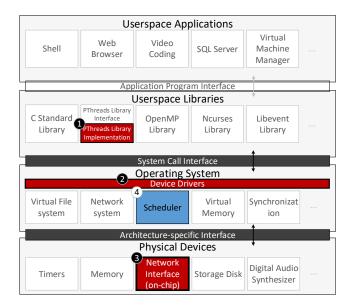

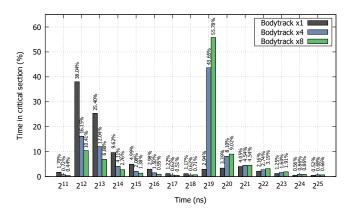

Deuxièmement, un concept complètement nouveau baptisé « notifying memories », a été proposé pour améliorer spécifiquement la synchronisation de tâche flot-de-données [29]. L'idée s'inspire du patron de conception *Observer*, dans lequel un observateur monitore une activité et informe le sujet de tout changement. Ce patron de conception est largement connu et utilisé dans la communauté du génie logiciel. Mes compétences doubles en architecture et génie logiciel m'ont permis d'en proposer une mise en œuvre matérielle. Cette approche permet de supprimer les accès inutiles à la mémoire. En effet, il existe deux principales approches pour la synchronisation : 1) les interruptions, 2) le *polling* (une scrutation continuelle). Les interruptions ne sont pas applicables dans notre cas car une caractéristique formelle du modèle flot-de-données impose la non préemption, c'est-à-dire qu'une tâche ne peut (ne doit) pas

être interrompue (pour exécuter une autre tâche de l'application). L'approche utilisée classiquement est donc basée sur une scrutation continuelle des valeurs en mémoire pour savoir si certaines données ont changé. J'ai mené une campagne expérimentale pour déterminer le coût en accès mémoire de ces scrutations et les résultats montrent que jusqu'à 45% des accès mémoires sont inutiles. L'utilisation de notre approche permet de supprimer ces accès inutiles pour garder la mémoire disponible pour des accès « utiles », c'est-à-dire ceux qui sont nécessaires pour effectuer un calcul. Nous avons mené une première étude en guise de preuve de concept pour une architecture à mémoires distribuées dénuées de cache. Les gains étaient attendus sur le débit ou le temps d'exécution de l'application mais les meilleurs résultats sont apparus au niveau de la consommation énergétique. En effet, un premier prototype matériel pire cas (en surface) du composant a été proposé et les résultats préliminaires affichent un gain en consommation énergétique de 50%.

Dans la foulée de ces bons résultats, nous avons étudié, dans le cadre du projet ANR JCJC Nooman dont je suis porteur, l'intérêt d'une telle approche pour des architectures à mémoire partagée centralisée avec une hiérarchie de caches, telle que présentée par la figure 3.6. Ce genre d'architecture supporte classiquement la cohérence de cache, et les mécanismes de synchronisation peuvent en tirer deux bénéfices : 1) le processus de scrutation continuelle s'opère localement au niveau du cache et ne requiert pas d'accès global à la mémoire, 2) la localité temporelle habituellement observée qui veut qu'un processeur ayant accédé au mécanisme de synchronisation récemment est amené à le ré-utiliser dans un futur proche, ce qui réduit grandement le coût d'accès à la prochaine tentative. Il n'en reste pas moins que ces accès continuels occupent inutilement des lignes du cache, et ramènent parfois des données « inutiles » dans le cache au détriment d'autres données « utiles ». La figure 3.6 montre également l'intégration des composants pour l'implémentation des *Notifying memories* : le *Notifier* (N) côté mémoire, et le *Listener* (L) côté processeur.

Les différents résultats obtenus me confortent dans ma direction scientifique : il existe une large place pour l'optimisation des transferts mémoire.

## Synchronisation de tâches sur architectures parallèles Période 2011-2022

Cette activité de recherche sur la synchronisation de tâches représente en tout :

- 2 thèses

- 2 post-doc

- 1 projet ANR JCJC

- 2 articles de revue [2, 5]

- 4 publications en conférences [15, 20, 24, 29]

- plusieurs communications orales [50, 53, 54]

#### 3.2 Encadrement doctoral et scientifique

# 3.2.1 Thèses soutenues entre 2011 et 2022

| Nom                | PEYRET Thomas                                                            |

|--------------------|--------------------------------------------------------------------------|

| Dates              | 01/11/2011 - 2/12/2014                                                   |

| Titre              | Architecture matérielle et flot de programmation associé pour la concep- |

|                    | tion de systèmes numériques tolérants aux fautes                         |

| Financement        | bourse CEA                                                               |

| Situation actuelle | System Architect at Alkalee                                              |

| Mon encadrement    | 30%                                                                      |

| Autres encadrants  | Coussy (20%), Thevenin (30%) Corre (20%)                                 |

| Publications       |                                                                          |

| • • • • • • •      | 117                                                                      |

- 2 brevets [10, 11]

- 2 conférences internationales avec actes et comité de lecture [36, 37]

- 1 conférence nationale avec comité de lecture et actes [35]

#### Résumé

Que ce soit dans l'automobile avec des contraintes thermiques ou dans l'aérospatial et le nucléaire soumis à des rayonnements ionisants, l'environnement entraîne l'apparition de fautes dans les systèmes électroniques. Ces fautes peuvent être transitoires ou permanentes et vont induire des résultats erronés inacceptables dans certains contextes applicatifs. L'utilisation de composants dits « rad-hard » est parfois compromise par leurs coûts élevés ou les difficultés d'approvisionnement liés aux règles d'exportation. Cette thèse propose une approche conjointe matérielle et logicielle indépendante de la technologie d'intégration permettant d'utiliser des composants numériques programmables dans des environnements susceptibles de générer des fautes. Notre proposition comporte la définition d'une Architecture Reconfigurable à Gros Grains (CGRA) capable d'exécuter des codes applicatifs complets mais aussi l'ensemble des mécanismes matériels et logiciels permettant de rendre cette architecture tolérante aux fautes. Ce résultat est obtenu par l'association de redondance et de reconfiguration dynamique du CGRA en s'appuyant sur une banque de configurations générée par une chaîne de programmation complète. Cette chaîne outillée repose sur un flot permettant de porter un code sous forme de Control and Data Flow Graph (CDFG) sur l'architecture en obtenant un grand nombre de configurations différentes et qui permet d'exploiter au mieux le potentiel de l'architecture. Les travaux, qui ont été validés aux travers d'expériences sur des applications du domaine du traitement du signal et de l'image, ont fait l'objet de publications en conférences internationales et de dépôts de brevets.

#### Abstract

Whether in automotive with heat stress or in aerospace and nuclear field subjected to cosmic, neutron and gamma radiation, the environment can lead to the development of faults in electronic systems. These faults, which can be transient or permanent, will lead to erroneous results that are unacceptable in some application contexts. The use of so-called rad-hard components is sometimes compromised due to their high costs and supply problems associated with export rules. This thesis proposes a joint hardware and software approach independent of integration technology for using digital programmable devices in environments that generate faults. Our approach includes the definition of a Coarse Grained Reconfigurable Architecture (CGRA) able to execute entire application code but also all the hardware and software mechanisms to make it tolerant to transient and permanent faults. This is achieved by the combination of redundancy and dynamic reconfiguration of the CGRA based on a library of configurations generated by a complete conception flow. This implemented flow relies on a flow to map a code represented as a Control and Data Flow Graph (CDFG) on the CGRA architecture by obtaining directly a large number of different configurations and allows to exploit the full potential of architecture. This work, which has been validated through experiments with applications in the field of signal and image processing, has been the subject of two publications in international conferences and of two patents.

| Nom                | NGO Thanh Dinh                                                    |

|--------------------|-------------------------------------------------------------------|

| Dates              | 01/02/2012 - 19/06/2015                                           |

| Titre              | Runtime mapping of dynamic dataflow applications on heterogeneous |

|                    | multiprocessor platforms                                          |

| Financement        | projet ANR COMPA                                                  |

| Situation actuelle | Assistant Professor at Danang University, Vietnam                 |

| Mon encadrement    | 60%                                                               |

| Autres encadrants  | Diguet (40%)                                                      |

| Publications       |                                                                   |

- 1 article de revue d'audience internationale indexée JCR [8]

- 1 conférence internationale avec actes et comité de lecture [34]

- 1 communication par affiche [58]

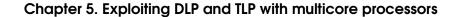

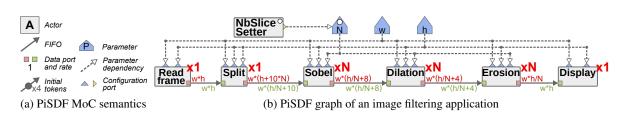

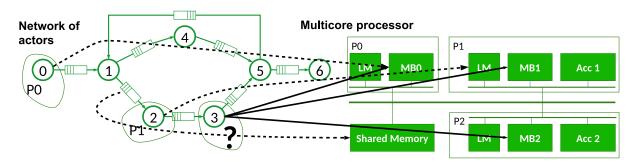

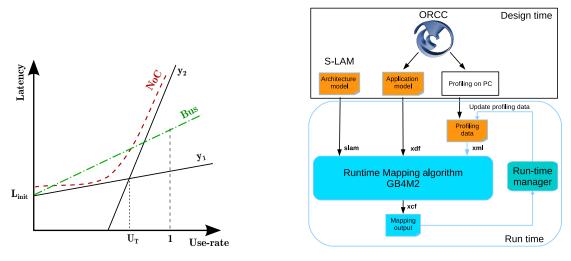

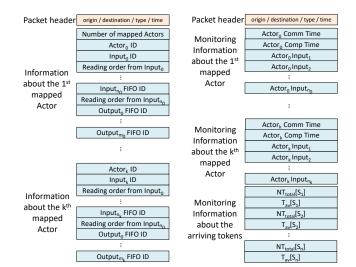

## Résumé