#### Contributions to model based test generation and monitoring strategies and their networking applications

Natalia Kushik

#### ▶ To cite this version:

Natalia Kushik. Contributions to model based test generation and monitoring strategies and their networking applications. Computer Science [cs]. Institut Polytechnique de Paris, 2022. tel-03952742

#### HAL Id: tel-03952742 https://hal.science/tel-03952742

Submitted on 23 Jan 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# I hèse de Habilitation à Diriger des Recherches

## Contributions to model based test generation and monitoring strategies and their networking applications

Habilitation à Diriger des Recherches de l'Institut Polytechnique de Paris préparée à Télécom SudParis

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (EDIPP)

Spécialité de doctorat: Informatique, données, intelligence artificielle

Thèse présentée et soutenue à Palaiseau, le 15/09/2022, par

#### NATALIA KUSHIK

#### Composition du Jury:

**Rob Hierons**

Professor, University of Sheffield Rapporteur

Pascale Le Gall

Professeur, CentraleSupélec Rapporteur

Franz Wotawa

Professor, Graz University of Technology Rapporteur

**Burkhart Wolff**

Professeur, Université Paris-Saclay Président

Roland Groz

Professeur, Grenoble INP UGA Examinateur

Tiziano Villa

Professor, University of Verona Examinateur

Djamal Zeghlache

Professeur, Télécom SudParis Examinateur

#### **Abstract**

The work presents a number of contributions in the area of model based testing (MBT), on the one hand, and some MBT applications, on the other hand. MBT generally relies on a formal specification of the system under test that later on allows to assure that its implementation conforms to the specification (or not). In our case, we mostly focus on the analysis of reactive systems, i.e., the systems working in request-response mode and moreover the behavior of these systems is sequential. Therefore, we mostly study transition or state models that change their states when an input is applied and/or an output is produced. Application areas of this work mostly cover networks and in particular dynamic and programmable networks whose components need to be thoroughly tested and verified. At the same time, as the behavior of reactive systems is not only sequential but also (highly) nondeterministic, we pay additional attention to the methods and techniques developed for testing (with the guaranteed fault coverage) and monitoring against nondeterministic and probably non-observable specifications. We discuss the problems that appear in the latter case and draw a particular attention to the state identification issues in nondeterministic specifications. We present the current state of the art in the area of state identification and propose original solutions for some Finite State Machine (FSM)/Automata classes with the complexity estimation. Note that some particular network components can also have rather a combinational behavior, such as for example, forwarding devices, and thus we also draw our attention to the logic circuit based testing and related fault models. At the same time, sequential circuits can be considered as scalable representations for FSMs and thus, we also consider testing against sequential circuits. Note that some of the contributions of this work remain purely fundamental and we still do not have interesting case studies for the specifications in question, however, for some others we discuss their applications in the area of network management. Moreover, for particular "network-driven" test purposes, we discuss other - sometimes simpler - testing and verification possibilities that allow under certain assumptions, assure the correct functioning of network components.

#### **Acknowledgements**

First of all, I would like to thank the jury members who helped evaluating this work: Rob Hierons, Pascale Le Gall, Franz Wotawa, Roland Groz, Burkhart Wolff, Tiziano Villa, and Djamal Zeghlache, many thanks for accepting to attend this habilitation defense and giving all your valuable feedback.

Particular acknowledgements go of course to the Reviewers, Rob, Pascale, and Franz, and their comments and suggestions on the manuscript, as well.

Since the very first steps, my research activities were guided by my PhD advisor, Nina Yevtushenko. Thank you Nina, for all your efforts, your enthusiasm and opportunities you have opened. Thanks a lot to the professors and colleagues from my Alma Mater Tomsk State University.

Since my arrival to Télécom SudParis, I was greatly accompanied by Ana Cavalli, Stephane Maag, and Djamal Zeghlache, among other colleagues, of course. Thank you very much for your trust and your kind support.

I would like to thank Benjamin Doerr who helped me all the way through the habilitation process at IP Paris.

All my colleagues and co-authors whom I tried to mention in the manuscript, thank you very much for the hard work. My previous and current students, thank you for the constant motivation.

My dearest family members and my friends, your support is appreciated more than anything, thank you very much.

#### **Contents**

| 1 | Intro | oduction                                                                                                                | 13 |

|---|-------|-------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Motivation, context and research challenges                                                                             | 13 |

|   | 1.2   | Major contributions                                                                                                     | 16 |

|   | 1.3   | Structure of the manuscript                                                                                             | 17 |

| 2 | Prel  | iminaries                                                                                                               | 19 |

|   | 2.1   | MBT and monitoring; fault models, and guaranteed fault coverage                                                         | 19 |

|   | 2.2   | Finite State Machines and Automata                                                                                      | 22 |

| 3 | Stat  | e id. in MBT, formal verif. and monitoring                                                                              | 25 |

|   | 3.1   | Reachability and distinguishability in FSM based testing and monitoring                                                 | 25 |

|   | 3.2   | 'Gedanken' experiments: problem statement and related work                                                              | 30 |

|   | 3.3   | Initial and Final State id.                                                                                             | 34 |

|   |       | 3.3.1 Deriving preset and adaptive homing, distinguishing, synchronizing experiments for nondeterministic FSMs/Automata | 34 |

|   |       | 3.3.2 Evaluating the length of state identification sequences and the complexity of related problems                    | 52 |

|   | 3.4   | Making it more practical – possibilities to reduce the complexity, discussing particular cases                          | 57 |

|   |       | 3.4.1 Nondeterministic FSMs with 'good' projections                                                                     | 58 |

Chapter 0 Contents

|   |      | 3.4.2    | ministic specifications                                                                   | 61 |

|---|------|----------|-------------------------------------------------------------------------------------------|----|

| 4 | Test | ing aga  | ainst logic circuits                                                                      | 65 |

|   | 4.1  | •        | round: logic circuits for describing combinational and sequential be-                     | 66 |

|   | 4.2  | Novel    | results in testing logic circuits                                                         | 69 |

|   |      | 4.2.1    | Test generation based on logic circuit verification                                       | 69 |

|   |      | 4.2.2    | (Novel) fault models when testing against the logic circuits and correlation between them | 73 |

| 5 | Test | ing and  | d verification of dynamic and programmable networks                                       | 77 |

|   | 5.1  | Applica  | ation areas: dynamic networks and SDN                                                     | 77 |

|   | 5.2  | Verifyir | ng the topologies and requests in dynamic and programmable networks                       | 80 |

|   | 5.3  | MBT fo   | or SDN enabled switches                                                                   | 82 |

|   | 5.4  | MBT fo   | or SDN frameworks and related fault models                                                | 85 |

|   | 5.5  | Forma    | I verification for pro-active testing when detecting SDN races                            | 88 |

| 6 | Con  | clusion  | ns                                                                                        | 93 |

|   | 6.1  | Some     | concluding remarks                                                                        | 93 |

|   | 6.2  | Future   | / current work and perspectives                                                           | 95 |

#### **List of Figures**

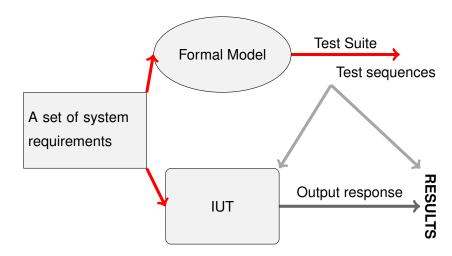

| 2.1  | MBT general schema                                                                 | 20 |

|------|------------------------------------------------------------------------------------|----|

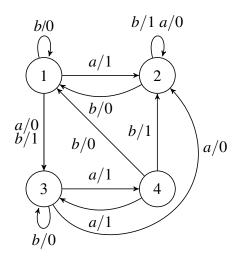

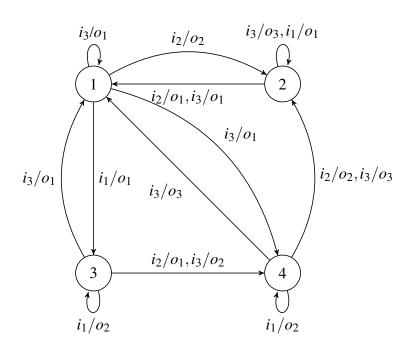

| 2.2  | Complete observable nondeterministic FSM ${f S}$                                   | 23 |

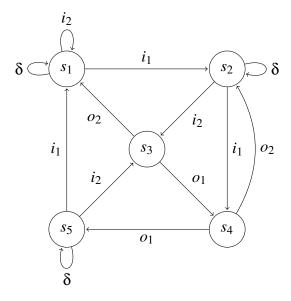

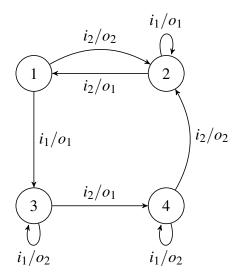

| 2.3  | Input/Output Automaton S                                                           | 24 |

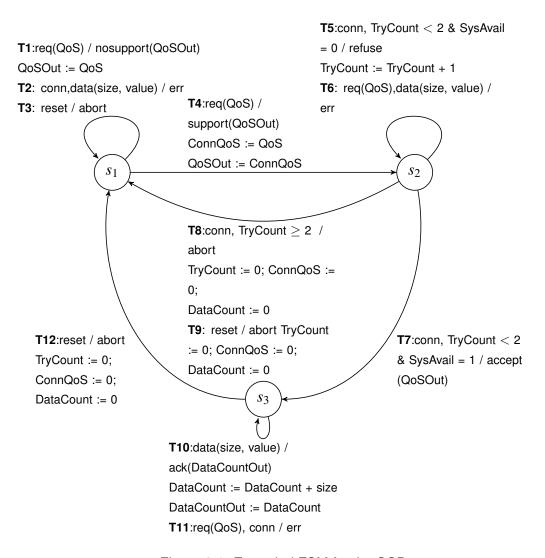

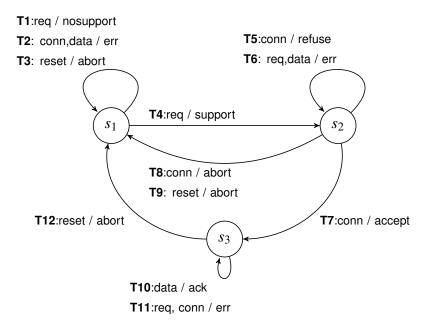

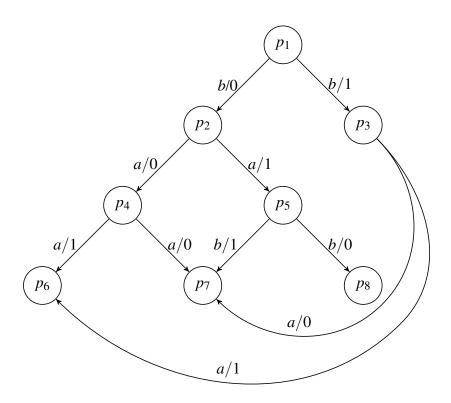

| 3.1  | Extended FSM for the SCP                                                           | 29 |

| 3.2  | FSM slice for the EFSM in Figure 3.1                                               | 35 |

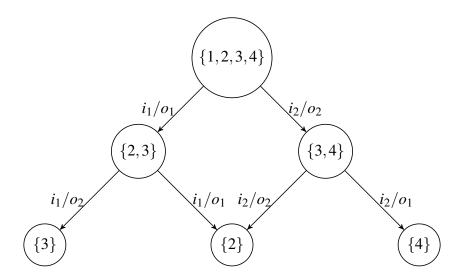

| 3.3  | Truncated successor tree for the FSM in Figure 3.2                                 | 36 |

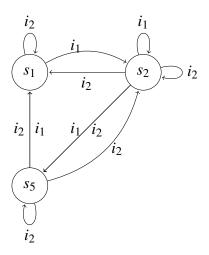

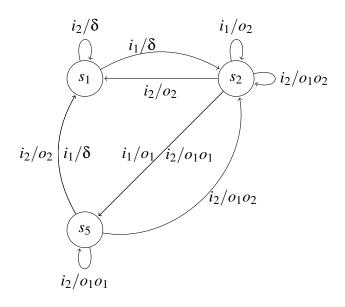

| 3.4  | Automaton ${\it A}$ for SS derivation for the input/output automaton ${\it S}$     | 41 |

| 3.5  | FSM $M$ for the input/output automaton ${\boldsymbol s}$                           | 42 |

| 3.6  | HTC for FSM S in Figure 2.2                                                        | 46 |

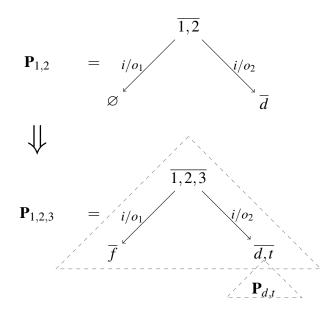

| 3.7  | $P_{1,2,3}$ derivation scheme                                                      | 47 |

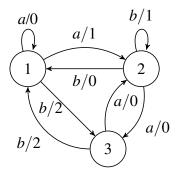

| 3.8  | A complete observable nondeterministic FSM ${f S}$ where state 3 is $d$ -reachable |    |

|      | from states 1 and 2                                                                | 49 |

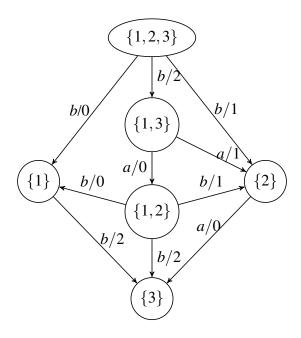

| 3.9  | $\mathbf{STC}$ for FSM $\mathbf{S}$ in Figure 3.8                                  | 50 |

| 3.10 | Complete non-observable nondeterministic FSM ${f S}$                               | 59 |

| 3.11 | Deterministic projection $\mathbf{S}^d$ of the FSM $\mathbf{S}$                    | 60 |

| 3.12 | DTC for FSM $S$ in Figure 3.10                                                     | 60 |

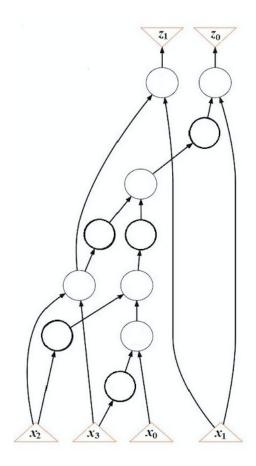

| 4.1  | An example circuit in the form of AIG                                              | 68 |

|     | Chapter 0                                           | List of Fig | ures |

|-----|-----------------------------------------------------|-------------|------|

| 4.2 | Verilog description example                         |             | 70   |

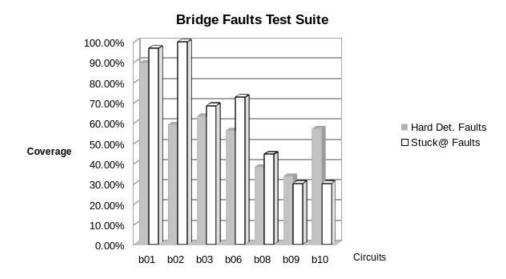

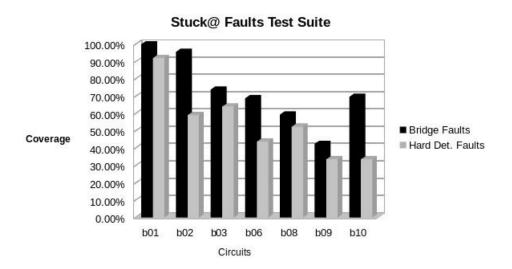

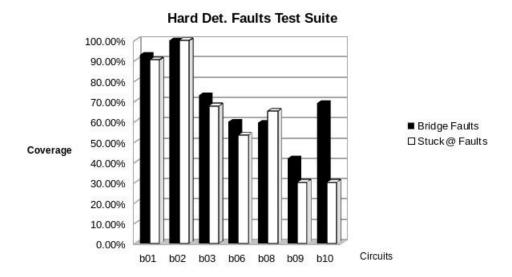

| 4.3 | SBF test suite fault coverage against SSFs and HDFs |             | 74   |

| 4.4 | SSF test suite fault coverage against HDFs and SBFs |             | 74   |

| 4.5 | HDF test suite fault coverage against SSFs and SBFs |             | 75   |

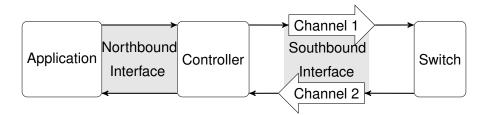

| 5.1 | SDN Topology considered for the races' detection    |             | 89   |

#### **List of Tables**

| 3.1 | Example FSM ${f S}$                                  | 38 |

|-----|------------------------------------------------------|----|

| 3.2 | $S^2_{\mathit{home}}$ automaton for the FSM ${f S}$  | 38 |

| 3.3 | $\mathbf{M}_n$ transitions over the input $i_{dist}$ | 56 |

| 4.1 | Example LUT                                          | 67 |

| 5.1 | Fault Coverage for digital circuit fault models      | 85 |

#### **Chapter 1**

#### Introduction

#### 1.1 Motivation, context and research challenges

As information and software technologies develop rapidly, more and more attention is paid to the correct functioning of the related software and hardware components. Indeed, for example, in critical systems guaranteeing the correct behavior of software/hardware components and their compositions is crucial. At the same time, the complexity of discrete event systems and in particular, communicating systems that are mainly considered in this thesis, increases as well. The behavior of communicating systems such as communication protocols, services, etc. is often nondeterministic (and sometimes non-observable) and thus, their testing and verification become more challenging.

Following the general tendency in testing such systems, we consider state models as relative specifications [vBP94, DEM<sup>+</sup>10, LSKP96, Kön12]. We assume that a System under Test (SUT) can accept the inputs and produce the outputs, moving from one state to another. The internal system state is assumed to be unknown (Black box), and testing is performed via the application of input sequences and the observation of the output reactions, with further conclusions about the correctness of the SUT. Non-intrusive monitoring strategies, on the contrary, aim at omitting the first step, i.e., no inputs are applied, the system behavior is only being observed and in this case, the community sometimes refers to it as *passive testing* (see, for example [LNS<sup>+</sup>97, CMDO09, CRM12, ACC<sup>+</sup>04, CGP03, MHN18]).

If the SUT can be adequately modeled by a Finite State Machine or an Automaton, then the general testing steps should, on the one hand, check the output on each transition, and, on the other hand, verify that the implementation reached the state that was

expected. In fact, *classical* FSM-based testing techniques are known to start with the checking sequence derivation [Hen64]. One can note three main steps that test generation strategies usually rely on: 1) to reach a certain designated state (from the initial one), 2) at a given state, to traverse (to cover) the outgoing transitions under each input, and 3) to distinguish the state that was reached from all others. To execute these steps, state identification sequences for the specification machine are usually applied [LY94, LY96]. Homing and synchronizing sequences are used to identify the final or current state of the machine, while distinguishing sequences are applied to uniquely conclude about its initial state. Such sequences are well studied for complete deterministic FSMs and Automata, where the first work of Moore is related to the 50-s of the last century [Moo56]. At the same time, for nondeterministic and moreover non-observable and/or partial specifications, there are some gaps in the literature for the state identification problems, that this work aims to cover. In particular, this comes to the first three **Research Challenges** (partially) addressed in the manuscript (and related publications):

**RC1**: Methods and techniques for deriving homing, distinguishing and synchronizing sequences for nondeterministic and non-observable specifications should be provided;

**RC2**: The length of the state identification sequences should be assessed, including the reachability of the upper bounds;

**RC3**: The complexity of the existence check and derivation of homing, distinguishing and synchronizing sequences for nondeterministic specifications should be evaluated.

Note also that from the practical point of view, not always the upper bounds established for **RC2** are reachable; same for the complexity classes and related completeness/hardness of the problems in **RC3**. Therefore, another branch of research directions of the author (with the colleagues) is also devoted to studying specific FSM classes where the worst complexity upper bounds are not reachable.

Obviously, state identification problems are essential for *stateful* systems, however, in reality some communication components, such as for example, forwarding devices, can be still adequately modeled with a single state. In this case, the output which is produced at a given time instance only depends on the current input and does not depend on the state, i.e., the behavior is not sequential but rather combinational. Generally, such systems can be modeled as combinational logic circuits and their testing relies on covering the paths in the specification circuit which go from primary inputs to primary outputs and consists of traversing related logic gates. Mutation testing can be effectively applied in this case, when certain faults are inserted directly in the combinational logic and an input pattern that detects this fault is derived. One of the well known faults in this case are *Single Stuck-at* faults when a given gate output is assumed to be stuck at Constant 1 or Constant 0 (see,

for example [KPKR95, MMS15, Pat05]). Related fault models have shown their effectiveness in hardware testing, however their applicability to testing communication components still remains challenging. At the same time, logic circuits can serve as a scalable representation for the FSMs and can be considered at specifications at a lower abstraction level. However, in this case, sequential circuits are considered where the configurations of the latches correspond to FSM states.

Therefore, novel (networking related) fault models and their expressiveness w.r.t. the well studied single stuck-at faults is also interesting to investigate. This work covers the aforementioned issues through addressing the following challenges:

**RC4**: The effectiveness of the well studied fault models for logic circuits should be evaluated for the up to date network components;

**RC5**: Novel fault models for logic circuit testing should be proposed; their effectiveness should be evaluated w.r.t. the single stuck-at faults.

As mentioned above, the main application area of the results is the area of networks and their analysis. Moreover, *classical* or traditional networks and their modeling with state or transition systems have been largely studied (for example, the work [vBP94] summarizes well the related achievements in 90-s of the previous century). We thus make an attempt, through the collaborations with networking research groups, mainly at Télécom SudParis and Airbus Defence and Space, to provide novel model based test generation strategies for dynamic and programmable networks. In this case, the general underlying topology is given beforehand, and this topology mostly describes the physical layer or the fixed non-changeable resources. The virtual links can appear and disappear w.r.t. these physical/resource possibilities. Otherwise, a link can be always kept but its parameters (weights) can dynamically change their values. For example, a bandwidth that is assigned to a given link can be changed dynamically<sup>1</sup>. These networks and their related testing and verification techniques are currently developing and in this work, we aim at addressing the following related challenges:

**RC6**: Novel verification strategies should be proposed for programmable and dynamic networks;

**RC7**: Once verified the dynamic/programmable network description, one should assure the implementation indeed conforms to the user request, i.e., novel MBT techniques should be proposed for that matter.

<sup>&</sup>lt;sup>1</sup>In this case, we assume the potential changes in time, when the parameter values belong to a certain (finite) set.

This work (partially) addresses the challenges mentioned above and presents the related contributions that were obtained by the author in collaboration with the researchers from Télécom SudParis, the Ivannikov Institute for System Programming of the Russian Academy of Sciences, Tomsk State University, Sabanci University, American University of Sharjah, National Taiwan University, and Airbus Defence and Space. In Conclusions, the author (critically) evaluates these contributions and discusses the future research challenges.

#### 1.2 Major contributions

The main contributions of this work can be informally divided into two parts: i) fundamental studies devoted to test generation and monitoring strategies for reactive systems, that can be described as automata or FSMs (with the guaranteed fault coverage, whenever possible); ii) MBT and monitoring strategies for programmable and dynamic networks, i.e., the application of (some fundamental) results. Note that in many cases, contributions from the first part stay rather theoretical as when testing network components in the second part, the specifications quite often get to be much simpler, or on the contrary, much more complex. We nonetheless, continue working in both directions, on the one hand, studying various specifications for possibly nondeterministic and partial reactive systems and solving MBT related problems, and on the other, we continue deriving and applying formal models and methods for up to date network components, using existing test generation strategies and developing novel approaches.

The main contributions of this work can be therefore summarized as follows:

- We provided novel techniques for deriving state identification sequences for nondeterministic, possibly non-observable FSMs; for some classes of input/output automata we also provided the methods for deriving homing and synchronizing sequences.

- We filled in some gaps in the estimation of the complexity of the existence check and derivation of state identification sequences for nondeterministic FSMs; note that in a general case, the existence check problem remains PSPACE-complete for preset sequences.

- We estimated the length of the state identification sequences and showed that differ-

ently from deterministic FSMs, moving from preset to adaptive experiment strategy<sup>2</sup> would not necessarily help to get a polynomial length of the sequence of interest.

- Given the *unpromising* complexity results, we studied and identified specific classes

of nondeterministic machines where the worst complexity upper bounds are not

reachable.

- At a lower abstraction level, we proposed novel fault models based on logic circuits and investigated their effectiveness and their correlation with the known single stuckat faults.

- We investigated the applicability of the logic circuit based fault models for testing programmable network components, in particular, for testing SDN enabled switches.

- We proposed novel fault models, in fact that omit the specification at all, when testing SDN frameworks; we also adjusted model checking based testing approaches for testing SDN frameworks where the test purposes are related to potential races.

- We proposed verification techniques for dynamic and programmable network topologies, as well as their monitoring strategies using model checking approaches.

#### 1.3 Structure of the manuscript

The manuscript consists of 6 chapters. Chapter 1 contains the Introduction which the Reader currently follows.

Chapter 2 briefly presents the necessary background. We start through introducing model based testing in general. As one of the advantages of the related techniques is their exhaustiveness, we discuss the fault coverage, and to be able to guarantee the latter (in some cases) we come to the fault models. Finally, we introduce the main state based models that are used in this work; those are mainly finite state machines, that being at current state, accept an input, produce an output, moving to the next state. Note that this model requests that each input is followed by an output which is a very strict constraint that however allows providing various testing techniques including efficient state identification. Nevertheless, we also investigated other models, such as input/output automata where the constraint mentioned above is not necessarily present.

<sup>&</sup>lt;sup>2</sup>In an adaptive strategy, the next input to be applied is chosen based on the output reaction to the previously applied inputs.

Chapter 3 contains some selected original results in the area of state identification for nondeterministic FSMs. We focus on the preset and adaptive strategies for homing, synchronizing and distinguishing sequences. We analyze the complexity of the corresponding existence check and derivation problems and discuss possible reductions for this complexity. In particular, we identify some specific FSM classes where the worst complexity upper bounds are not reachable.

Chapter 4 continues the contributions to the model based testing strategies, however in this case we use a lower abstraction level and come to logic circuits as related specifications. For the systems that have a single internal state, i.e., rather 'stateless' systems, the input uniquely determines the output to be produced, differently from the sequential behavior (as in FSMs for example), where the current state matters. Stateless systems can be modeled by combinational circuits and in fact, there can be found some network components for which the corresponding model is quite adequate. An example is a switch or a forwarding device which given the values of the network packet parameters, forwards it accordingly (the output port is identified). We therefore present some logic circuit based fault models and the original results on the correlation of these models. Both, combinational and sequential circuits are considered, as the latter can also be considered as a scalable representation for an FSM.

Chapter 5 focuses on the networking applications of the model based testing strategies. We study dynamic and reconfigurable networks and discuss how such *dynamicity* can simplify or complicate the testing and verification steps. Some stateful and stateless specifications have been derived for the network components of interest and we discuss the related test objectives. Note that these objectives reflect not only functional aspects, i.e., conformance testing, but also specific non-functional issues that can occur in distributed systems, such as for example, races in channels.

Chapter 6 summarizes the results presented in the manuscript. We also discuss a number of perspectives concerning the current and future research directions in the area of model based testing, its long standing problems such as, for example state identification, and its current applications in distributed systems, for example in (future) networks.

#### Chapter 2

#### **Preliminaries**

This chapter aims at (briefly) presenting the necessary notions and introducing the notations that are utilized in the manuscript.

## 2.1 MBT and monitoring; fault models, and guaranteed fault coverage

When testing any software or hardware systems, we are usually interested in providing certain guarantees. Ideally, we would like to conclude that a given system *has no bugs at all, no security issues, etc.* However, this task generally is not solvable. At the same time, introducing certain assumptions about the system under test or under verification, can allow drawing some conclusions about the absence of the bugs of certain types, or it can let us assure that a given system possesses certain properties. The more bugs (or the bugs of more types) are guaranteed to be not present is the system, the higher is the fault coverage of the related testing technique. We however cannot provide any guarantees unless we provide a formal specification of the system under test/verification. Therefore, when it comes to MBT, we usually have the System (or Implementation) under Test or SUT/IUT and its formal description - *specification*.

The system specification is used to derive the *test sequences* or *test cases*. A finite set of test sequences or a *test suite*, is applied to an IUT and the output reactions are observed. If the output reactions *observed* are as *expected*<sup>1</sup> by the specification, then the

<sup>&</sup>lt;sup>1</sup>They can be exactly the same, or for example, included in the set of allowed possible reactions, etc.

Figure 2.1: MBT general schema

test suite *passed*, otherwise the test suite *failed*. A general schema of the MBT is shown in Fig. 2.1.

Once a system specification is derived, we assume that the implementation is modelled using the same formalism. For example, if a system behavior is described as a finite state machine then an implementation can only have two types of faults, namely transition and output faults; for combinational and sequential circuits as system specifications *classical* faults are, for example, single stuck-at faults. We aim as deriving test suites with the *guaranteed fault coverage*, i.e., we would like to assure that each output and/or transition fault is detected by the test suite *TS*. However, when it comes to the observation of the output reactions and their comparison with the expected ones, as mentioned above, the conformance relation is what matters. Simply, we can assume the equivalence or equality in this case, but not necessarily - another interesting conformance relation is inclusion or reduction, when an implementation does only what is allowed by the specification and no more than that. Therefore, in order to provide the guarantees when deriving test suites, a fault model is necessary.

A fault model [PYvB96] usually is a triple  $<\mathcal{S},@,FD>$  where  $\mathcal{S}$  is the specification or the formal description of the system behavior, @ represents the conformance relation between an implementation I under test and the specification  $\mathcal{S}$ , while FD is a fault domain which limits the possible implementations, i.e.,  $I \in FD$ . We are interested in an exhaustive test suite that detects each implementation  $I \in FD$  that is not conforming to  $\mathcal{S}$ , i.e.,  $I \not \otimes \mathcal{S}$ . Depending on how the implementations from FD are given, one can consider black, white and grey box testing methodologies. Generally, in the case of black box, we know nothing but the maximum number of states of each machine  $I \in FD$

which is defined by the corresponding conformance relation.

[Vas73, Cho78, SD88, FvBK<sup>+</sup>91]; in white box testing scenario, we assume that all the potential faulty implementations are explicitly enumerated [PM64], [KYC14a] and thus, the fault *diagnosis*<sup>2</sup> can be performed at once with testing [GvBD93, EPYvB03]; for the grey box, a mutation machine can be derived [EDYvB12, KPY99, PNR16], such that submachines of this machine represent potential faulty implementations. In this manuscript, we are mostly interested in black and white box testing which will be further applied to testing network components.

Note that the testing strategy described above is often referred to as *active* testing, which is, in fact, used to emphasize the possibility of controlling the IUT. Indeed, note that the input sequences are being applied to the IUT in Fig.2.1 and only after the testing conclusions are drawn. This is however, not always possible, in particular when it comes to certain crucial network components that cannot be tested in a stand alone mode. In this case, only observations are available and these observations are made where observation points are available. This is where *monitoring* or *passive* testing becomes of a big help (see for example, [KLCY16], [CRM12, ACC<sup>+</sup>04, LNS<sup>+</sup>97, LMM16, Mil98, MA01]).

In the general case, we can assume that input sequences coming to the IUT as well as its output reactions can be observed by the tester or the monitor. For each input/output sequence  $\alpha/\beta$  the tester usually checks that this input/output pair does not violate the specification (this can be done for example, via the simulation of the behavior of  $\mathcal S$  on the input sequence  $\alpha$ ). If on the contrary, a violation is observed for a given input/output pair, then the tester returns the verdict 'fail'. A corresponding input sequence  $\alpha$  can be then alerted together with the verdict.

For the testing and monitoring strategies discussed in the work, we mostly consider  $\mathcal{S}$  to be described as a corresponding finite state machine or an automaton. The former can be represented by a sequential circuit in a scalable way. For a system that does not have a sequential behavior, the specification  $\mathcal{S}$  can be provided as a corresponding combinational circuit. These models are formally introduced further in the manuscript.

<sup>&</sup>lt;sup>2</sup>Note again, that we do not speak here about the software debugging [WGL<sup>+</sup>16] directly, however, the latter is possible if there is an established correspondence between (some) faults in the specification S and those in the source code.

#### 2.2 Finite State Machines and Automata

A finite state machine (FSM) [Gil62], or simply a machine (sometimes referred to as an automaton with output [TB73]), is a 5-tuple  $\mathbf{S} = < S, I, O, h_S, S_{in} >$  where S is a finite nonempty set of states with the set  $S_{in} \subseteq S$  of initial states, I and O are finite input and output alphabets, and  $h_S \subseteq S \times I \times O \times S$  is a transition relation. FSM  $\mathbf{S}$  is non-initialized if  $S_{in} = S$  and in this case, we omit the set  $S_{in}$  of initial states and a non-initialized FSM is denoted as a 4-tuple  $< S, I, O, h_S >$ . FSM  $\mathbf{S}$  is an initialized FSM if  $|S_{in}| = 1$  and FSM  $\mathbf{S}$  with the initial state  $s_j$  is denoted  $\mathbf{S}/s_j$ . Otherwise, we write  $\mathbf{S} = < S, I, O, h_S, s_0 >$  to denote the fact that FSM  $\mathbf{S}$  is initialized with the initial state  $s_0$ . If  $1 < |S_{in}| < |S|$  then FSM  $\mathbf{S}$  often is called weakly initialized.

FSM S is nondeterministic if for some pair  $(s,i) \in S \times I$ , there exist several pairs  $(o,s') \in O \times S$  such that  $(s,i,o,s') \in h_S$ ; otherwise, the FSM is deterministic. FSM S is observable if for every two transitions  $(s,i,o,s_1), (s,i,o,s_2) \in h_S$  it holds that  $s_1 = s_2$ . FSM S is complete if for every pair  $(s,i) \in S \times I$ , there exists a transition  $(s,i,o,s') \in h_S$ ; otherwise, the FSM is partial. An example of a complete observable nondeterministic FSM (taken from [YKK19]) is shown in Figure 2.2. We will not discuss hereafter what are the reasons for the specifications of interest to be nondeterministic, as in fact this question is rather philosophical. We note that in reactive communicating systems, such as telecommunication protocols, services, etc. nondeterministic behavior can be stated directly in the specification, due to possible output responses to the same inputs at the same states (optionality), or it can also come from partial observability and controllability of an SUT [EGGC09]. It is also possible that for the compactness of the formal specification of an SUT, its nondeterministic specification is provided, instead of an equivalent deterministic one.

In FSMs, the behavior relation  $h_S$  is extended to input and output sequences in usual way and given an input sequence  $i_1 \dots i_l$ , we say that an output sequence  $o_1 \dots o_l \in out(s,i_1\dots i_l)$  if and only if there exists a state s' such that  $(s,i_1\dots i_l,o_1\dots o_l,s')\in h_S$ . Given an input/output pair io and a state s of a complete FSM  $\mathbf S$ , a subset of states that contains each state s' of FSM  $\mathbf S$  such that  $(s,i,o,s')\in h_S$  is the io-successor of state s. The io-successor of state s can be empty and then sometimes we say that the io-successor of state s does not exist. A trace tr of FSM  $\mathbf S$  at state s is a sequence of input/output pairs which label consecutive transitions starting from state s,  $tr = i_1o_1\dots i_lo_l$  (or  $i_1/o_1\dots i_l/o_l$ ). A sequence  $i_1\dots i_l$  is an input sequence of the trace while  $o_1\dots o_l$  is an output sequence. If FSM  $\mathbf S$  is complete and observable, given state s and a trace s of the FSM at state s, the s-successor of state s is state s in fact, a singleton s-successor of state s is reached from s-successor of state s is state s in fact, a singleton s-successor of state s is state s-successor of state s is state s-successor of stat

Figure 2.2: Complete observable nondeterministic FSM S

The notion of an FSM is very close to the *Automaton* model that does not support output responses, i.e., automaton transitions are labeled by actions that are not divided into inputs and outputs and usually these actions are called inputs or, simply, *letters*. One may eliminate outputs at each transition of a given FSM in order to get the underlying automaton that can be nondeterministic for a nondeterministic FSM. Note however, that there can be more complex definitions for automata and some of them we utilize in this manuscript. For example, the actions can be split into inputs and outputs, however, differently from an FSM in the automaton behavior not each input is necessarily followed by an output.

A (non-initialized) Input/Output Automaton is a 4-tuple  $\mathbf{S} = < S, I, O, T_S >$  where S is a finite set of states; I and O are finite non-empty disjoint sets of inputs and outputs, respectively;  $T_S \subseteq S \times I \times S \cup S \times O \times S$  is a transition relation where 3-tuples  $(s,i,s') \in T_S$  and  $(s,o,s') \in T_S$  are transitions. The machine can contain a special output  $\delta \in O$  that represents the *quiescence* [Tre96] at the states where only the transitions under inputs are defined. In some sense, it means that no output can be produced after the transition is executed, and this fact is defined by this special output  $\delta$ . An example of such an automaton is given in Figure 2.3. We note that this automaton is even more specific,

Figure 2.3: Input/Output Automaton S

it contains for example a property that not only inputs and outputs are split into disjoint sets but also when at a state where an input is applied, no output can be produced and vice-versa. We study this special class of automata further in the manuscript.

The FSM and automata models briefly introduced above (and their modifications) will further serve as specifications for testing purposes. We will present some of the analysis problems for the related models and our related contributions in the area, which help improving testing or monitoring strategies for communicating systems.

#### **Chapter 3**

## State identification in MBT, formal verification and monitoring

The chapter is devoted to the presentation of some existing and original results in the area of state identification of finite state systems. Most of the results that contain the author's contributions, are obtained for (nondeterministic) FSM state identification. Note that the problem of state identification is one of the major problems in FSM based testing and we first present the relevant motivation, referring the Reader to the so-called W-method (and its modifications) [Vas73, Cho78].

#### 3.1 Reachability and distinguishability in FSM based testing and monitoring

Currently, there exist a number of FSM based test generation strategies, and related methods keep improving. For a survey of such methods, the Reader can for example, refer to [DEM+10], where a short description of them is presented, as well as the relevant experimental results (on the test suite length, in particular). All these methods such as HSI, DS, etc. somehow represent an improvement of the so called W-method that was originally proposed by Vasilevskii [Vas73], and later adjusted by Chow [Cho78]. Below, we briefly introduce the W-method and some related constraints for the exhaustiveness of the returned test suite.

The method is used for deriving test suites with the guaranteed fault coverage against

complete deterministic machines. Note that the specification machine should also be reduced (*minimal*), which means that its states are pair-wise distinguishable. The notion of distinguishability will be introduced a bit later as it refers to the initial state identification. In fact, a distinguishing sequence for a pair or a bigger subset of states allows to uniquely determine the initial state of this subset after the application of the sequence (and the observation of the corresponding output response). When the machine is deterministic it means that the output reactions on this sequence are pair-wise different.

Generally, in W-method, given the initialized specification FSM  $\mathcal{S}$ , one should first reach each FSM state, then traverse each transition at the reached state and in the end, append a so called characterization or W set. The latter consists of the sequences distinguishing each state pair. The sequences that allow reaching each FSM state from the initial one, form the reachability or state cover set, correspondingly. In other words, we first reach a state, assure that the output at the next transition is correct, and then assure that the reached final state in the implementation is exactly the same as it was expected in  $\mathcal{S}^1$ .

Note that this *original* version of the method has been modified in various ways, for example, in order to reduce the height and/or the width of the resulting tree which is obtained via the concatenation of the related reachability set, the input alphabet and the W set. A general idea behind such optimization is to substitute the W set with a smaller one. If there exists a distinguishing sequence for the specification machine, this sequence can be thus appended instead of the W set (DS method). Otherwise, only *targeted* sets can be appended as well which distinguish the reached state from any others (HSI method, for example). As mentioned above, the Reader may check a survey [DEM+10] that presents various W modifications such as DS, HSI, H, etc., and moreover supports the results with the experimental evaluation. We will skip this part as we mostly contribute to the derivation of the related sets, but we note that the obtained results can be and are utilized in the modified W versions. In the current chapter, we will instead focus on the presentation of the (original) results for the reachability and distinguishability for (nondeterministic) specifications.

When it comes to system verification [Hol03] which generally consists of checking certain properties over it, or otherwise, when performing a non-intrusive monitoring of an SUT, reachability analysis can be also of help. In fact, knowing a current state of the system can in some cases reduce the verification/monitoring efforts. Assume that for a given SUT a set  $P = \{p_1, p_2, \dots, p_k\}$  of properties should be checked. Assume also that the specifi-

<sup>&</sup>lt;sup>1</sup>This is done under the assumption that the number of implementation states is no bigger than that of the specification.

cation S contains n states  $s_1, s_2, \ldots, s_n$ , respectively. Not all properties can be relevant for checking at state  $s_j$ , and a subset of properties  $P_j \subseteq P$  can be defined (of those that indeed should be checked). In this case, when verifying the system behavior we could first bring the system to a known state  $s_j$  and after that check the subset  $P_j \subseteq P$ . If the system is tested passively, and no input stimuli are allowed, then the state  $s_j$  can sometimes be deduced from the SUT input/output traces being observed. And later on again only relevant properties would be checked.

As the last point forms one of contributions of the author, in particular, on the use of the final state identification for improving monitoring strategies [KLCY16], we will give more details here and illustrate the idea on an example. In fact, let us consider a Simple Connection Protocol (SCP) for that matter. The SCP is a protocol designed to 'connect' two entities, negotiating the quality of service at the connection establishment [ACC+04]. The SCP allows connecting an entity called the upper layer to an entity called the lower layer. The upper layer dialogues with SCP to fix the quality of service (QoS) desirable for the future connection. Once this negotiation succeeds, the upper layer comes to the lower layer requesting the establishment of a connection satisfying the quality of service previously agreed on. The lower layer accepts or refuses this connection request. If the lower layer accepts the request, then it informs the upper layer that the connection was established and the upper layer can start transmitting data. Once the transmission of data is finished, the upper layer sends a message to close the connection. If the lower layer refuses the connection, the system allows the upper layer to make three requests before informing the upper layer that all the connection attempts failed. If the upper layer would like to be connected to the lower layer, it is necessary to restart the QoS negotiation from the beginning. After the connection gets established (accepted), the upper layer can send data to the lower layer with a guaranteed QoS. Each time the upper layer sends any data, the lower layer acknowledges the total amount of received data. The FSM describing the behavior of this protocol is shown in Figure 3.1. Note that this FSM is more complex than that presented in Section 2, as it contains context variables, predicates and input parameters. It is an Extended machine whose formal definition we omit due to the room constraints; we invite the Reader to see such a definition, for example in [PBG04]. These machines sometimes allow to represent the SUT behavior in a more compact way, partially hiding the states, for example, in the vector of context variable values. We deal with a similar model in Chapter 5, namely we construct extended automata when analyzing the possibilities of races in distributed architectures.

For the SCP, we use an Extended FSM (or EFSM for short) that has the following inputs and outputs [ACC<sup>+</sup>04]. The upper layer can request the desired QoS level with the mes-

sage req(QoS) with QoS in the range [0,3]. The lower layer replies whether it can support the desired QoS level or not with the messages nosupport(QoS) or support(QoS). The upper layer then issues the message conn (an output) trying to establish the connection. The replies can be:

- accept(QoS) if the connection guarantees QoS,

- refuse if the lower layer is busy,

- *abort* if more than two refused attempts have occurred.

The upper layer then can issue the data(size, value) message to transmit the data. Each data message is acknowledged with the message ack(DataCountOut). At any point, if the upper layer decides to end the connection, the message reset can be sent. The reset message should be replied with an abort message by the lower layer. Finally, any input at a wrong state should be replied with an error message (err).

Assume that for the SCP protocol we need to check the following properties.

- Receipt confirmation: When some data are sent to the lower layer, an acknowledgement (ack) should be sent to the upper layer, i.e., the following input/output sequence should be observed: data/ack.

- Connection attempt management: At least two refused attempts should be allowed before definitely rejecting the upper layer connection, which corresponds to the conn/refuse.conn/refuse.connect/abort input/output sequence.

- Client communication termination: Any successful connection must be properly terminated; the upper layer sends a reset after the connection was established, and before requesting a new QoS or connection, the abort message has to be produced.

Thus, the following input/output sequence should be observed: conn/accept(QoSOut). .reset/abort.

As mentioned above, not all the properties are pertinent to each EFSM state. Therefore, when monitoring the SUT, after determining its current state only properties that are related to that state can be checked. For example, if the IUT is at state  $s_3$  the first property should be checked. However, if the SUT is at state  $s_2$ , there is no need to check this property. At the same time, there exist many non-functional requirements that can be checked

Figure 3.1: Extended FSM for the SCP

at state  $s_3$  - one can verify, for example, that the length of transferred data does not exceed the available disk space, or that the QoS provided is indeed the one guaranteed at the QoS negotiation phase. Note that checking such non-functional properties while the SUT is not at state  $s_3$  puts an unnecessary load on the monitoring system. Determining the current state of the SUT can be done through construction of possible homing and/or synchronizing sequences, for example, up to a given length. Further, during the system monitoring the observed sequence is compared to the pre-built ones, and if two coincide, then the current state is uniquely determined and only relevant state properties are thus checked.

Note that in some cases, even the reducing of uncertainty of the current system state, can already minimize the monitoring or verification efforts, and for that matter so called S'-synchronizing sequences can be used [San05] (the final state is not necessarily unique

but definitely belongs to the set S'). We later on present some contributions that were obtained in the area of state identification for nondeterministic specifications, that can thus help, optimizing testing and/or verification efforts.

#### 3.2 'Gedanken' experiments: problem statement and related work

Distinguishing, homing and synchronizing experiments for FSMs form a set of so called 'gedanken' experiments [Moo56] that have been introduced by Moore, in the middle of the previous century. An experiment in this case is the process of applying an input sequence (or a set of those), observing an output reaction of the machine under experiment (if needed) and drawing a conclusion about the final or the initial state of this machine. As mentioned above, homing and synchronizing sequences (HS and SS, respectively) are used to identify the final or the current state of the machine, while distinguishing sequences (DS) are built for the initial state identification. The way the experiment is carried out defines the type of the experiment, which can be either *preset* or *adaptive*; the experiment is adaptive if the next input to be applied is chosen based on the previously observed outputs, and the experiment is preset if the outputs need to be observed only at the end of the experiment, or need not to be observed at all. A preset experiment is thus represented by just an input sequence, whereas an adaptive experiment is represented by a tree-based structure which can be referred to as an adaptive sequence or a test case [LY94, PY05]. Therefore, when it comes to state identification for FSMs and automata, usually we are interested in the existence check of the corresponding preset or adaptive experiment; further, a derivation strategy for such experiment should be proposed. Alongside, the complexity of both problems is another challenging issue, as well as the length of the corresponding sequences or the size of the relevant tree-based structures. Note that studying these tasks for nondeterministic FSMs/automata and some their classes is one of the main areas of interest of the author. This chapter therefore briefly presents the related contributions, and to better highlight those, we first start with a short presentation of the related work.

The problems of checking the existence and derivation of state identification sequences have been widely investigated in the past seventy years. Major results obtained in this area mainly concern the deterministic FSM case: for non-initialized complete deterministic minimal machines the existence decision and derivation of an appropriate sequence for

the final state identification (HS and SS) can be performed in polynomial time [San05]. Moreover, in some cases, such sequences always exist, such as for example, an HS of polynomial length (w.r.t. the number of FSM states) for a complete deterministic connected reduced FSM.

However, even for the 'good' cases of HS and SS for deterministic FSMs the problem becomes much harder when it comes to constructing a shortest HS or SS. Indeed, the problem of deriving a shortest HS/SS is NP-hard even for complete non-initialized deterministic minimal FSMs [San05].

DSs make the above problems much harder; indeed, even for complete deterministic FSMs, the existence check of a DS is PSPACE-complete [LY94]. Note that in some cases, the DS existence check complexity can be reduced via an adaptive strategy. A remarkable example of such complexity reduction for complete deterministic FSMs has been proposed in [LY94] where the existence check of an adaptive distinguishing sequence has been proven to be solved in polynomial time with respect to the number of FSM states.

For nondeterministic FSMs, the paper [ACY95] can serve as another example - the existence check of an adaptive distinguishing sequence for a pair of states of an observable machine can also be solved in polynomial time. Since then, adaptive strategies gained a lot of attention, as the complexity in some cases can be indeed reduced dramatically and some of the contributions presented below, cover adaptive strategies for the state identification, with the polynomial complexity.

For nondeterministic machines, again, the problems listed above become harder. Indeed, as shortest synchronizing sequences can have exponential length in this case [IS04], their existence check and derivation cannot be performed in polynomial time. At the same time, distinguishing a state pair in an observable nondeterministic FSM can also require a sequence of an exponential length [SEY07] (it is linear for complete deterministic FSM).

When it comes to the derivation techniques for preset and adaptive state identification experiments, existing strategies, in our opinion, can be classified into three large groups. Methods of the first group follow a classical successor tree based approach. Techniques from the second group rely on an iterative derivation of the experiment of interest; induction base in this case is usually a set of sequences merging or distinguishing (separating or splitting) state pairs. The third group of techniques is based on the use of various solvers for the final state identification<sup>2</sup>. Successor tree based approaches have been

<sup>&</sup>lt;sup>2</sup>The author partially contributed to all these groups for nondeterministic machines and their 'gedanken' experiments.

largely investigated for deterministic complete automata and FSMs; the interested Reader can for example refer to [San05] where such methods are well presented for homing and synchronizing sequences. Tree based approaches can be utilized when constructing distinguishing sequences as well, moreover, not only a successor tree but also a splitting tree can be exploited [LY96]. The difference between these two is that in a splitting tree, nodes can be labelled by input sequences or by related subset of states; successor tree *unrolls* the behavior of the machine and usually its nodes are labelled by state subsets. Note that splitting tree approaches are utilized for deterministic specifications to make sure that such state subset partitioning is always possible.

**Rule-1**: *P* is the empty set.

**Rule-2**: *P* contains a set *R* without singletons that labels a node at a level j, j < k.

**Rule-3**: *P* has only singletons.

These rules allow establishing the conditions for existence check and derivation of an HS for a nondeterministic FSM. Given a path of the truncated successor tree from the root to a node labeled with the set of singletons or with the empty set, the input sequence  $\alpha$  that labels this path is an HS for the FSM  $\mathbf{S}$ . At the same time, if the successor tree has no nodes labeled with a set of singletons or with the empty set, i.e., is not truncated using Rules 1 or 3, then FSM  $\mathbf{S}$  is not homing.

The same technique can be used for checking the existence and derivation of an SS for the FSM S, the last rule just requires that all the singletons are the same. Similarly, when it is used for deriving a DS, Rule 3 checks for containing a singleton, and the corresponding

<sup>&</sup>lt;sup>3</sup>This part therefore appears in the related work and not in the contributions of the current thesis.

branch thus becomes unpromising. If the successor tree has no nodes labeled with the empty set, i.e., is not truncated using Rule 1 then there is no distinguishing sequence for **S**.

In iterative derivation approaches (second group), state identification sequences are usually pre-calculated for state pairs; in fact, for deterministic automata and their SSs it also serves as a criterion for the existence check [Nat86, Epp90]. Once state identification sequences are derived for each state pair, one can start with the first state pair and apply the corresponding sequence, then another (third) state is added to the set of states. The behavior of the machine is simulated on the first sequence and the related state successors are computed. Whenever these successors are not singletons, the corresponding state identification sequence for the resulting pair is appended to the initial sequence. Another state is then added to the set of states and the process is repeated iteratively. Such approach allows building HSs and SSs, accordingly, moreover, for SSs it automatically proves the cubic upper bound on their length [San05, Epp90].

Currently, the application of solvers for the existence check and/or derivation of state identification sequences becomes very popular. For an SS derivation of potentially partial nondeterministic automata, the interested Reader can refer to [SV19, SV18], where the problem is reduced to SAT solving via a corresponding encoding of inputs and transitions of the machine. SAT and constraint solving has been also applied for the checking sequence generation [NPR18, PAGO19]. In this case, a checking sequence is utilized to distinguish a potential mutant from the specification and to some extent can be treated as a distinguishing sequence for a direct sum of the specification and implementation FSMs, i.e., a sequence identifying the initial state of the machine with two initial states. Note that in the cited works even non-classical FSMs are considered, namely the authors take into account symbolic inputs and outputs.

Below, we present some of the original results, in the area of the existence check and derivation of preset and adaptive homing, distinguishing and synchronizing sequences for nondeterministic FSMs and automata.

## 3.3 Novel results in the area of (adaptive) experiments for initial and final state identification

### 3.3.1 Deriving preset and adaptive homing, distinguishing, synchronizing experiments for nondeterministic FSMs/Automata

Deriving preset HS, DS and SS for nondeterministic FSMs - successor tree based approach

Similar to the existence check and derivation approaches for the state identification, we start with the successor tree. As mentioned above, first results were obtained during the PhD of the author and thus, were listed as a related work. Hereafter, we note that these results are very well adjustable for the case of non-observable machines.

In particular, in [KLCY16] we were interested in deriving a set of non-redundant homing sequences of length l or less, for a subset  $S'\subseteq S$ , |S'|>1, of a given FSM  ${\bf S}$  that can be non-observable. For that matter, one can build a similar truncated successor tree. However, this time the root of the tree is labeled with the set S', while the nodes of the tree are labeled by state subsets such that none of them is a proper subset of another. Edges of the tree are labeled by inputs and there exists an edge labeled by an input i from a node labeled by P at level j,  $j \geq 0$ , to a node labeled by P if P is the set of P concessors of all subsets of P. The set P contains a singleton if non-empty P io-successors of some subset of P do not intersect. Sets which are proper subsets of other items are deleted from the set P.

Given a node labeled with the set P at the level k, k > 0, the node is terminal if one of the following conditions holds.

**Rule-1**: *P* contains only singletons.

**Rule-2**: The depth of the node P is greater than l.

If the successor tree has no nodes labeled with the singletons only, then there is no homing sequence of length l or less for the subset S'. Otherwise, each path to a node labeled with the set of singletons is added to the set of non-redundant homing sequences.

An example of such successor tree and related HSs of length up to two is shown in Figure 3.3. This tree is produced for the *FSM slice* of the Extended FSM in Figure 3.1.

Figure 3.2: FSM slice for the EFSM in Figure 3.1

The latter is obtained after deleting from a given EFSM all the predicates, parameters and update functions (the slice itself is shown in Figure 3.2).

According to the successor tree in Figure 3.3, the resulting set of (non-redundant) homing sequences for the FSM in Figure 3.2 is the following:

{req.reset, req.conn, req.data, reset, data.rec, data.conn, data.reset, conn.req, conn.data, conn.reset}. This set can be used for reducing the monitoring efforts as discussed in Section 3.1.

An interesting remark that we would like to draw the Reader's attention to, is that once obtaining the set of all singletons for the observable machine, we can prolong the corresponding input sequence if we need to. However, for the non-observable machines this is not necessarily the case, indeed, not each prolongation of an HS remains an HS - this is due to the fact that a singleton can produce a state pair, triple, etc. after an application of a given input<sup>4</sup>.

Note that this approach can be applied for generating synchronizing sequences, all the singletons obtained due to Rule-1, should be the same; only in this case the node is declared terminal.

For generating distinguishing sequences for non-observable FSMs, one can build a similar successor tree and make sure that for each node there is no merging at the same

<sup>&</sup>lt;sup>4</sup>One can however put any input as a prefix to any HS for a non-initialized non-observable machine, without loosing the necessary property.

Figure 3.3: Truncated successor tree for the FSM in Figure 3.2

state. Otherwise, such a node should be declared terminal as well. Another option is to proceed, as discussed above, considering the subsets of state pairs, putting in the root all the pairs of set S' and terminate when a node is labelled by the empty set. The sequence that labels a path to such a node is a DS or a separating sequence for the given nondeterministic, possibly, non-observable machine.

### Alternative strategies for preset state identification sequences - reducing the problem to SS in automata

The successor tree built with subsets of state pairs can be naturally considered for deriving a transition diagram of a special automaton whose states are pairs of states of the FSM S together with the designated state *sink*. Note that there are no outputs in this automaton, nor any quiescence, i.e., this is a *classical* automaton considered in the works related to SS derivation [Vol08, IS04, SV18, Mar14]; actions (letters) of the automaton in question correspond to the FSM inputs.

The transitions of the automaton are defined according to the tree branches where the state sink is reached under input i when a corresponding pair is distinguished by the input i or for some  $o \in O$ , the io-successor is a singleton. An HS exists for the FSM S if and only if the obtained automaton has a synchronizing sequence to the sink state. The latter thus provides an alternative way to derive (all) homing sequences for a given FSM. Note that a similar automaton can be derived for the set of all distinguishing sequences,

the automaton can become partial when, given a pair  $\overline{s_p, s_q}$ , for some input i there exists o such that the io-successor of  $\overline{s_p, s_q}$  is a singleton. We further present the strategies for deriving an automaton, that contains either all HSs or all DSs for a given complete nondeterministic observable FSM.

Consider a nondeterministic FSM  $\mathbf{S} = \langle S, I, O, h_S \rangle$ ,  $S = \{s_1, \dots, s_n\}$ , in [KY15c], we propose to derive an automaton  $S^2_{home}$  such that the set of all synchronizing sequences of this automaton coincides with the set of all homing sequences of FSM  $\mathbf{S}$ , i.e.,  $L_{home}(S) = L_{synch}(S^2_{home})$ .

### **Algorithm 1:** Deriving the automaton $S^2_{home}$

**Input**: A complete observable nondeterministic FSM  $\mathbf{S} = \langle S, I, O, h_S \rangle$

**Output:** Automaton  $S^2_{home}$

States of  $S^2_{home}$  are pairs  $\overline{s_j, s_k}$ , j < k, and the designated state sink while actions are inputs of the FSM  $\bf S$  (letters);

for each input  $i \in I$  do

By construction, the automaton  $S^2_{home}$  has the following features. First of all,  $S^2_{home}$  can be nondeterministic. Moreover, for a sequence  $\alpha \in I^\star$ , a pair  $\overline{s_p, s_q}, s_p, s_q \in S, s_p \neq s_q$ ,  $\alpha$  takes the automaton  $S^2_{home}$  from the pair  $\overline{s_p, s_q}$  to the sink state if and only for each trace  $\gamma \in (IO)^\star$  with the input projection  $\alpha$ , the  $\gamma$ -successor of  $\overline{s_p, s_q}$  is the empty set or a singleton. Therefore, the following statement holds.

**Proposition 1** An input sequence  $\alpha$  is a homing sequence for the FSM **S** if and only if  $\alpha$  is a synchronizing sequence for  $S^2_{home}$ .

The set of all homing sequences of the FSM  ${\bf S}$  is thus equal to the set of all synchronizing sequences of the automaton  $S^2_{home}$ , i.e.,  $L_{home}({\bf S})=L_{synch}(S^2_{home})$ . As an example, consider an FSM with a flow table in Table 3.1.

| Input/State | 0       | 1       | 2       | 3       |

|-------------|---------|---------|---------|---------|

| $i_0$       | 3/(0,3) | 1/(0,3) | 2/(0,3) | 3/(0,3) |

| $i_1$       | 1/(0,2) | 0/(0,2) | 2/(0,2) | 3/(0,3) |

|             | 1/(0,3) | 0/(0,3) | 2/(1,2) | 3/(1,3) |

|             | 1/(2,3) |         | 2/(2,3) | 3/(2,3) |

| $i_2$       | 2/(0,1) | 2/(0,1) | 0/(0,1) | 3/(0,3) |

|             | 2/(0,3) | 2/(0,3) | 0/(0,3) | 3/(1,3) |

|             | 2/(1,3) | 2/(1,3) | 1/(1,3) | 3/(2,3) |

|             |         |         |         | 1/(0,1) |

Table 3.1: Example FSM S

Note this example is interesting as it shows an exponential upper bound on the length of a homing sequence<sup>5</sup>. Table 3.1 contains transitions of the corresponding FSM  $\mathbf S$  with four states 0,1,2,3, the set  $I=\{i_0,i_1,i_2\}$  of inputs, and the set  $O=\{(j,k),(j< k)\&(j,k\in\{0,1,2,3\})\}$  of outputs. The sequence  $\alpha=i_0i_1i_0i_2i_0i_1i_0$  is an HS for the FSM  $\mathbf S$ , and this HS is the shortest in this case.

The flow table of the automaton  $S^2_{home}$  returned by Algorithm 1 is shown in Table 3.2.

| Input/State | $\overline{0,1}$ | $\overline{0,2}$ | $\overline{0,3}$ | 1,2              | 1,3              | $\overline{2,3}$ | sink |

|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------|

| $i_0$       | 1,3              | 2,3              | sink             | 1,2              | 1,3              | 2,3              | sink |

| $i_1$       | $\overline{0,1}$ | 1,2              | 1,3              | $\overline{0,2}$ | $\overline{0,3}$ | 2,3              | sink |

| $i_2$       | sink             | $\overline{0,2}$ | $\overline{2,3}$ | $\overline{0,2}$ | 1,2              | $\overline{0,1}$ | sink |

|             |                  | $\overline{1,2}$ | $\overline{1,2}$ | $\overline{1,2}$ | $\overline{2,3}$ | $\overline{0,3}$ |      |

|             |                  |                  |                  |                  |                  | 1,3              |      |

Table 3.2:  $S^2_{home}$  automaton for the FSM S

By direct inspection, one can assure that for the automaton  $S^2_{home}$ , a shortest synchronizing sequence is also the sequence  $i_0i_1i_0i_2i_0i_1i_0$ . Any prolongation of this sequence is a synchronizing sequence for the automaton  $S^2_{home}$  and a homing sequence for the FSM  $\bf S$ .

In order to describe the set of all distinguishing sequences one can rely on the same technique with a very slight difference: when for some  $o \in O$ , the io-successors of states of some pair of P coincide there is no edge from the node labeled by i to the next tree

<sup>&</sup>lt;sup>5</sup>The class of the machines with the reachable exponential upper bound on the length of an HS was proposed and studied in [KY13, Kus13].

level in the corresponding successor tree. Indeed, when building the automaton  $S^2_{dist}$ , for each input  $i \in I$  and each state  $\overline{s_j, s_k}$  of the automaton  $S^2_{dist}$  we check if states  $s_j$  and  $s_k$  are distinguished (separated) by this input; and if so, we add the transition  $(\overline{s_j, s_k}, i, sink)$ . If for each  $o \in O$ , the io-successors of states  $s_j$  and  $s_k$  do not coincide and  $\{s_p, s_t\}$  is the io'-successor of the set  $\{s_j, s_k\}$  for some  $o' \in O$ , p < t and j < k, we add to  $S^2_{dist}$  the transition  $(\overline{s_j, s_k}, i, \overline{s_p, s_t})$ , respectively. The automaton can be partial, since for some pair  $\overline{s_j, s_k}$ , j < k, of states of FSM  $\mathbf{S}$ , there can be no transition under input i if states  $s_j$  and  $s_k$  have the same nonempty io-successor for some output o. The Reader can refer to [KY15c] for more details, examples, and related algorithms and propositions.

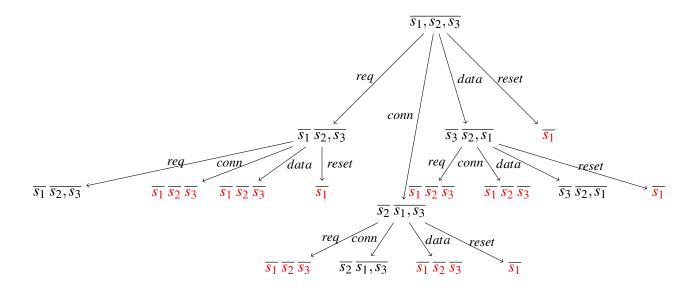

### Deriving Homing and Synchronizing sequences for Input/Output Automata

The automata that were considered above represent a very particular case, as the actions are not divided into inputs and outputs, a potential quiescence at a state is not considered, etc. In fact, synchronizing experiments are mostly studied for this exact class of automata (see for example, [IS04, San05, SV19, Vol08, ÇKY+18] and among the long standing problems for this class there is conjecture that was recently proven. Namely, this is the Cerny conjecture which concerns complete deterministic automata (without outputs) and in particular, the length of a shortest SS. The conjecture claims it is quadratic w.r.t. the number of states of the automaton while it is proven to be no more than cubic [Vol08]. Trahtman recently uploaded his paper to archive where he presented a proof of this conjecture (currently the archive contains the 4-th version of the paper) [Tra20]. Note again that in the aforementioned works, there is a very restricted class of automata, however in testing applications it is more convenient to deal with a reactive system when inputs and outputs are separated. Therefore, in one of our works (together with the researchers from ISP RAS, Russia) we considered a little more generic case of automata which we describe below<sup>6</sup>.

We consider Input/Output Automata briefly introduced in Chapter 2 (see an example automaton in Figure 2.3). Moreover we restrict the automata class under consideration, namely, we are interested only in those input/output automata for which the following holds:

- 1. At each state only inputs or only outputs are allowed, i.e.,  $S = S_1 \cup S_2$ ,  $S_1 \cap S_2 = \emptyset$  and  $T_S \subseteq S_1 \times I \times S \cup S_2 \times O \times S$ ;

- 2. The transition diagram does not contain cycles/loops labeled with outputs, i.e., the

<sup>&</sup>lt;sup>6</sup>The results are published in [KYBK18].

language of the machine does not contain traces with infinite postfix of outputs;

3. The machine has a special output  $\delta \notin O$  that represents the quiescence [Tre96] at the states where the transitions under inputs are defined; at each state  $s \in S_1$ , there is a loop under  $\delta$ , namely  $(s, \delta, s) \in T_S$ .

We return again to the example input/output automaton, consider a machine in Figure 2.3. The automaton  $\bf S$  has five states, namely  $S = \{s_1, \ldots, s_5\}$ , where  $S_1 = \{s_1, s_2, s_5\}$  and  $S_2 = \{s_3, s_4\}$ . At each state from the set  $S_1$  the automaton accepts inputs  $i_1$  and  $i_2$ . However, when the machine is at state  $s_3$  or  $s_4$  no inputs can be accepted and only outputs  $o_1$  or  $o_2$  can be produced. Note that this automaton precisely belongs to the considered class.

In order to define HS and SS for such a class of input/output automata, we introduce the following *experiment hypothesis*:

We assume that before applying any input, a tester (or any experimenting entity) waits for a given maximal output timeout t.

The experiment is performed as follows: the tester expects an output in t time units; if the machine produces one, then the timer is reset and the tester waits for another t time units. If no output is produced by the system in t time units then the tester applies the next input (if any) and resets the timer. In fact, this hypothesis is introduced to somehow avoid an infinite (indeed, "very-very long") waiting time before applying the next input (in FSMs and experiments with them, this never happens as each input we apply requires an immediate output reaction to be produced).

The latter explains the necessity of introducing the specific output  $\delta \notin O$ , namely whenever the output is not observed we assume that the system/machine produced the output  $\delta$ . Such extension of the output alphabet allows to define the corresponding HSs and SSs for an Input/Output automaton. A sequence  $\alpha = i_1 i_2 \dots i_k$  is *synchronizing* for the automaton  $\mathbf{S}$  if there exists a state  $s \in S$  such that for each trace  $\beta_1 i_1 \beta_2 i_2 \dots \beta_k i_k \beta_{k+1}$  where p is the length of a longest sequence of consecutive outputs and  $\beta_j \in (O \cup \{\delta\})^p$ ,  $j = 1, \dots, k+1$ , it holds that the  $\beta_1 i_1 \beta_2 i_2 \dots \beta_k i_k \beta_{k+1}$ -successor of the set S is either empty or equals  $\{s\}$ . A sequence  $\alpha = i_1 i_2 \dots i_k$  is homing for the automaton  $\mathbf{S}$  if for each trace  $\beta_1 i_1 \beta_2 i_2 \dots \beta_k i_k \beta_{k+1}$ ,  $\beta_j \in (O \cup \{\delta\})^p$ ,  $j = 1, \dots, k+1$ , it holds that the  $\beta_1 i_1 \beta_2 i_2 \dots \beta_k i_k \beta_{k+1}$ -successor of the set S is either empty or is a singleton. For example, for the automaton  $\mathbf{S}$  in Figure 2.3,  $\alpha = i_1 i_1$  is a homing sequence.

We propose to derive an SS for an automaton **S** where actions are divided into inputs

and outputs via an iterative elimination of the transitions labeled by outputs. Such transitions can always be omitted as for the automata class considered here, there does not exist a state where transitions under inputs and outputs are defined at the same time. In other words, we propose to derive an automaton where only the transitions under inputs are left and then use the SS derivation strategies for the automata without outputs. Therefore, we build an automaton  $\mathbf{A} = \langle S_1, I, T_A \rangle$  which at the beginning has an empty set of transitions,  $T_A = \emptyset$ . For each transition  $(s, i, s') \in T_S$ , where  $s, s' \in S_1$ , we iteratively add to  $s'' \in S_1$  and  $s'' \in S_2$ , we add to  $s'' \in S_1$  and  $s'' \in S_2$ , we add to  $s'' \in S_1$  and  $s'' \in S_2$  and  $s''' \in S_1$  and  $s''' \in S_2$  and  $s''' \in S_3$  are sult, each synchronizing sequence  $s' \in S_3$  and synchronizing sequence for  $s' \in S_3$ .

The automaton **A** for the example input/output automaton **S** is shown in Figure 3.4.

Figure 3.4: Automaton **A** for SS derivation for the input/output automaton **S**

By direct inspection, one can check that the automaton  $\boldsymbol{A}$  is not synchronizing and thus, there is no SS for  $\boldsymbol{S}$ .

In order to derive an HS for an input/output automaton  $\mathbf{S}$ , one can also reduce the problem to the HS derivation for well studied models, in particular for the HS derivation of a corresponding FSM. This FSM can be obtained via simulation and concatenation of potential output reactions at the relevant states. In fact, we propose to derive an FSM  $\mathbf{M} = \langle S_1, I, O \cup O^2 \cup \cdots \cup O^p \cup \{\delta\}, T_M > \text{which at the beginning has an empty set of transitions, i.e., } T_M = \emptyset$ , where p is the length of a longest output trace of the automaton  $\mathbf{S}$ . Later, for each state  $s \in S_1$ , such that  $(s,i,s') \in T_S$ ,  $s' \in S_1$ , we add to the  $T_M$  the transition  $(s,i,\delta,s')$ . At the same time, for each state  $s \in S_1$ , such that  $(s,i,s') \in T_S$ ,  $s' \in S_2$ , we add to the  $T_M$  the transition  $(s,i,\delta_1,\delta_2,\ldots,\delta_k,s'')$ ,  $k \leq p$ , where  $s'' \in S_1$  is the  $o_1o_2\ldots o_k$ -successor

of state s'. Note, that similar to the SS existence check and derivation, a sequence  $\alpha$  is homing for the automaton  $\mathbf{S}$  if and only if  $\alpha$  is a homing sequence for the FSM  $\mathbf{M}$ .