## Programming adaptative real-time systems

Frédéric Fort

## ▶ To cite this version:

Frédéric Fort. Programming adaptative real-time systems. Programming Languages [cs.PL]. University of Lille, 2022. English. NNT: . tel-03948472v1

## HAL Id: tel-03948472 https://hal.science/tel-03948472v1

Submitted on 20 Jan 2023 (v1), last revised 31 Jan 2023 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

École doctorale Mathématiques, sciences du numérique et de leurs interactions (MADIS-631)

## Programmation de systèmes temps réels adaptatifs Programing adaptative real-time systems

# **Thèse** Informatique

#### Frédéric Fort

Thèse préparée et soutenue publiquement par Frédéric Fort le 04/10/2022 pour obtenir le grade de Docteur en Informatique

4 Octobre 2022

Direction de Thèse

Jury

#### Directeur

#### Giuseppe Lipari

Professeur, Université de Lille

## Encadrant

## Julien Forget

Maître de conférences, Université de Lille

## Rapporteur, Président du Jury Jean-Pierre Talpin

Directeur de recherche, INRIA

## Rapporteur

#### Robert De Simone

Directeur de recherche, INRIA

## Examinateur

#### Timothy Bourke

Chargé de recherche, INRIA

#### Examinateur

## Claire Pagetti

Directrice d'études, ONERA

## Abstract

A *real-time system* is a system whose correctness depends not only on the correctness of the values it produces, but also on the time when it produces those values. The rate at which it must produce values is defined by the environment it operates in.

When programming such a system, it is important that the programming language allows to reason about the constraints introduced by this context. Synchronous languages [14] are well-adapted to the programming of critical real-time systems thanks to their clean formal semantics and to their formally defined compilation process. In this work, we will present extensions to the synchronous language Prelude [67] to tackle two issues: Programming multicore systems predictably and handling system reconfiguration during execution.

Multicore hardware platforms have the potential to increase the performance of real-time systems. However, their architecture, especially the shared central memory, is prone to hard-to-predict delays, outweighing the potential benefits. To address this issue, models such as PREM [71] and AER [32] have been proposed. Our first contribution aims at producing AER-compliant multicore C code from a high-level PRELUDE program. This shifts the responsibility of low-level implementation concerns related to task communications onto the compiler, saving tedious and error-prone development efforts.

A multi-mode real-time system must respect different functional requirements during its execution. A mode of execution represents a possible system configurations, for an aircraft control system these may include take-off, cruise and landing. Mode change protocols define transitions to change safely from one mode to another. Our second contribution proposes clock views to decouple the rate of tasks and transitions. The resulting multi-mode support is both formally defined and generic enough to allows programmers to choose the kind of protocol they need for their application. A clock calculus based on refinement typing [39, 83] infers and checks the consistency of rates and views.

## Résumé

Un système temps réel est un système dont la correction dépend non seulement de la correction des valeurs qu'il produit, mais aussi du temps quand il les produit. Le rythme de production de ces valeurs est défini par l'environnement dans lequel il opère.

La programmation d'un tel système nécessite un langage de programmation permettant de résonner sur les contraintes introduites par ce contexte. Les langages synchrones [14] sont bien adaptés pour la programmation de systèmes critiques temps réel de part leur sémantique et leur processus de compilation formellement définis. Dans ce travail, nous présentons des extensions au langage synchrone Prelude [67] pour aborder deux problèmes: La programmation de systèmes multicœur prédictibles et la reconfiguration du système durant l'exécution.

Les plateformes matérielles multicœurs possèdent un potentiel de performances accrues des systèmes temps réel. Cependant, leur architecture, en particulier la mémoire centrale partagée, est sujette à des délais difficile à prédire, contrebalançant les gains potentiels. Les modèles tel que PREM [71] et AER [32] remédient à cette limitation. Notre première contribution permet de produire du code multicœur en accord avec le modèle AER à partir d'un programme haut-niveau PRELUDE. Ceci permet de transférer la responsabilité des problèmes bas niveau liés aux communications inter-tâches, évitant des efforts de développement fastidieux et sujets aux erreurs.

Les exigences fonctionnelles d'un système temps-réel multi-mode évoluent durant son exécution. Un mode d'exécution représente une configuration possible du système, par exemple décollage, croisière ou atterrissage pour un système de contrôle d'avion. Les protocoles de changement de mode définissent des transitions afin de changer de mode en sécurité. Notre seconde contribution propose les vues d'horloge pour découpler le rythme d'exécution des tâches de celui des transitions. Le mécanisme multi-mode résultant est à la fois formellement défini et générique afin de permettre de choisir le type de protocole approprié à application. Un calcul d'horloge basé sur le typage par raffinement [39, 83] infère et vérifie la cohérence des rythmes et vues.

## Acknowledgements

No work is ever achieved in isolation, our accomplishments are the result of our interactions with each other. This might be in particular the case for such a long-term work as a PhD thesis. Thus, I would like to thank some people who were there along the way.

First of all, I would like to thank my thesis supervisors, Giuseppe Lipari and Julien Forget. You welcomed me in then Émeraude team after I applied for an out-of-date thesis proposal and knew little of what I was getting into. Your continuous support and helpful feedback was crucial in my thesis work and in training a future researcher.

Next, I would like to thank my thesis jury. Thank you to Jean-Pierre Talpin and Robert De Simone for reviewing my thesis manuscript. Your thorough review greatly helped to shape this manuscrit into the form that is now visible. Thank you to Timothy Bourke and Claire Pagetti for participating in my thesis jury. Your feedback has been highly valuable.

Next, I would like to thank my former colleagues, in particular Fabien, Houssam, Pierre and Sandro with whom I shared an office at different times. I would also like to thank the members of the Association des Doctorant  $\cdot$  e  $\cdot$  s en Sciences de Lille, in particular Antonin who invested himself so much as a President.

Finally, I would like to thank Mara. You were there for me whenever I needed you to, and words cannot express my feelings for you. Time is the most real with you.

# Contents

| Co | ontents                                          | 4          |

|----|--------------------------------------------------|------------|

| Ι  | Introduction                                     | 7          |

| 1  | Problem Statement                                | 8          |

|    | 1.1 Real-Time Systems                            | 8          |

|    | 1.2 Synchronous Languages for Real-time Systems  | 8          |

|    | 1.3 Multicore Platforms                          | ç          |

|    | 1.4 Multi-mode Systems                           | S          |

| 2  | Contribution                                     | 11         |

|    | 2.1 Compiling Synchronous Languages on Multicore | 11         |

|    | 2.2 Synchronous Semantics of Multi-mode systems  | 11         |

|    | 2.3 Thesis Overview                              | 12         |

|    |                                                  |            |

| Η  | Background and Definitions                       | 13         |

| 3  | Simple Model for Real-Time Tasks                 | <b>1</b> 4 |

|    | 3.1 Tasks                                        | 14         |

|    | 3.2 Data-dependencies                            | 15         |

|    | 3.3 Scheduling Policies                          | 16         |

|    | 3.4 Schedulability Analysis                      | 17         |

| 4  | Multicore Real-Time Systems                      | 19         |

|    | 4.1 Scheduling                                   | 19         |

|    | 4.2 Hardware model                               | 19         |

|    | 4.3 PREM                                         | 20         |

|    | 4.4 AER                                          | 20         |

|    | 4.5 Related Works                                | 21         |

| 5  | Multi-Mode Real-Time Systems                     | 23         |

|    | 5.1 Mode Change Protocols                        | 23         |

|    | 5.2 Mixed-criticality systems                    | 26         |

| 6  | Synchronous Languages for Real-Time Systems      | 29         |

CONTENTS 5

|           | 6.1                | Synchronous Languages                                   | 29              |

|-----------|--------------------|---------------------------------------------------------|-----------------|

|           | 6.2                | Lustre                                                  | 29              |

|           | 6.3                | Signal                                                  | 31              |

|           | 6.4                | Prelude                                                 | 33              |

|           | 6.5                | Imperative synchronous languages                        | 34              |

|           | 6.6                | Related Works on Multi-Mode Systems                     | 34              |

|           | 6.7                | Related Works on Multicore Systems                      | 38              |

|           | 6.8                | Summary                                                 | 39              |

| 7         | A b                | ase synchronous language: Definitions and reminders     | 40              |

|           | 7.1                | Clocks and Dataflows                                    | 40              |

|           | 7.2                | Language Syntax                                         | 42              |

|           | 7.3                | Running Example                                         | 44              |

|           | 7.4                | Synchronous Kahn Networks                               | 44              |

|           | 7.5                | Clock Calculus                                          | 46              |

|           | 7.6                | Compiling Prelude Equations into Real-Time Tasks        | 46              |

|           | 7.7                | Summary                                                 | 47              |

|           |                    |                                                         |                 |

| п         | ICon               | npiling Synchronous Languages on Multicore              | 48              |

| 8         | Intr               | oduction                                                | 49              |

| Ŭ         | 8.1                | Platform Description                                    | 49              |

|           | 8.2                | Running Example                                         | 50              |

|           | 8.3                | Contribution Goal                                       | 50              |

| 9         | Cad                | e Generation                                            | 52              |

| 9         | 9.1                | Multi-phase Communications                              | 52<br>52        |

|           | 9.1                |                                                         | $\frac{52}{54}$ |

|           | 9.2 $9.3$          | Monocore Compilation                                    | 54 $55$         |

|           | 9.3<br>9.4         | Multicore Code Structure                                | 56<br>56        |

|           | 9.4                | Withticore Code Structure                               | 50              |

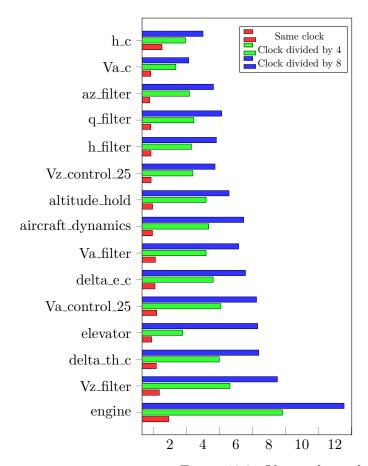

| 10        | Eval               | luation                                                 | 58              |

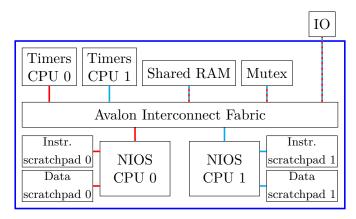

|           | 10.1               | Hardware Platform                                       | 58              |

|           |                    | OSEK-compliant code                                     | 59              |

|           | 10.3               | Measurements                                            | 59              |

|           | 10.4               | Summary                                                 | 60              |

| IX        | $^{7}\mathrm{Syn}$ | chronous semantics of multi-mode multi-periodic systems | 62              |

|           | ŭ                  |                                                         |                 |

| 11        |                    | oduction                                                | 63              |

|           |                    | Current Limitations                                     | 63              |

|           | 11.2               | Overview                                                | 64              |

| <b>12</b> | Clo                | ck views                                                | 65              |

| 13        | Exte               | ended Synchronous Kahn Semantics                        | 72              |

6 CONTENTS

| 14 Extended Language Syntax                                                                                      | <b>7</b> 4        |

|------------------------------------------------------------------------------------------------------------------|-------------------|

| 14.1 Surface Language                                                                                            | 74                |

| 14.2 Core Language                                                                                               | 75                |

| 14.3 Surface-to-Core Transpilation                                                                               | 76                |

| 15 Clock calculus                                                                                                | 83                |

| 15.1 Bidirectional Typing                                                                                        | 83                |

| 15.2 Refinement Typing                                                                                           | 83                |

| 15.3 Overview                                                                                                    | 84                |

| 15.4 Running Example                                                                                             | 85                |

| 15.5 Structural Clock Calculus                                                                                   | 85                |

| 15.6 Refinement Clock Calculus                                                                                   | 95                |

| 15.7 View closing                                                                                                | 111               |

| 16 Evaluation                                                                                                    | 113               |

| 16.1 Drone Case Study                                                                                            | 113               |

| 16.2 Mode Change Protocols                                                                                       | 114               |

| 16.3 Emergent Properties                                                                                         | 117               |

| V Conclusion                                                                                                     | 118               |

| 17 Summary and Perspectives                                                                                      | 119               |

| 17.1 Summary                                                                                                     | 119               |

| 17.2 Perspectives                                                                                                | 120               |

|                                                                                                                  |                   |

|                                                                                                                  | 122               |

| A Proof Program for Clock Deceleration                                                                           | 122               |

|                                                                                                                  | 122 $124$         |

| A Proof Program for Clock Deceleration                                                                           |                   |

| A Proof Program for Clock Deceleration  B Drone Case Study in the Core Language                                  | <b>12</b> 4       |

| A Proof Program for Clock Deceleration  B Drone Case Study in the Core Language  List of Figures                 | 124<br>126        |

| A Proof Program for Clock Deceleration  B Drone Case Study in the Core Language  List of Figures  List of Tables | 124<br>126<br>128 |

# $\begin{array}{c} {\rm Part} \ {\rm I} \\ \\ {\rm Introduction} \end{array}$

## Chapter 1

## Problem Statement

In this Chapter, we will detail the problems this thesis tackles. Together with the next Chapter, you may understand it as an "extended abstract".

## 1.1 Real-Time Systems

A real-time system is a system whose correctness depends not only on the correctness of the values it produces, but also on the time when it produces those values. The rate at which it must produce values is defined by the environment it operates in. A typical example is an aircraft controller which must be able to react to external perturbations, such as a gust of wind, in a timely manner to guarantee the aircraft's safety.

This specific type of constraints results in an approach that is different from more "common" general-purpose computing. In particular, real-time computing should not be confused with high-performance computing. While a certain degree of computing speed is desired, once the system is able to meet its deadlines, further speed gains are superfluous. Indeed, gains in system predictability would be preferred over gains in speed once that point has been reached.

However, designers of real-time systems face the issue that modern computing platforms have an ever increasing complexity. This results in an ever increasing difference between the worst-, average- and best-case scenario. This is an issue for real-time systems as system designers must guarantee that the system respects its deadlines even in the worst case.

The ANR project Corteva [2] aimed at addressing this high variability in next-generation real-time systems by using sound and provably correct programming models. As part of this project, my thesis goal was to extend a programming language to enable the implementation of predictable real-time systems even on modern platforms.

## 1.2 Synchronous Languages for Real-time Systems

To address the complexity of designing real-time systems, it is important that the used programming language allows to reason about the specific constraints introduced by this context. However, most languages have no model of time, beyond the notion that earlier instructions execute before later ones. Thus, this thesis will focus on the family of synchronous languages which have been proven to be well-adapted to the programming of critical real-time systems.

Central to synchronous languages is the notion of *logical time*. Instead of considering time as something continuous, a synchronous language assumes that time is a sequence of discrete clearly-

separated *instants*. Computations are assumed to happen instantaneously. In essence, logical time assumes that the exact, "physical" time of computations does not matter as long as the frequency of instants is sufficient and computations never execute across instants.

To guarantee the temporal consistency of a program, synchronous languages employ a *clock cal-culus*. It is in essence a dedicated type system that tries to assign to each expression a *clock*. Clocks characterize sequences of instants and thus allow to predict statically at which instants computations are evaluated.

#### 1.2.1 Prelude

The PRELUDE language is a synchronous dataflow language and the language we extend in this thesis. A program defines a computational graph operating on infinite streams of values. The particularity of the language is that it allows to express real-time constraints, most notably periodicity. This enables the language to use tools both from synchronous languages and real-time literature. For instance, the system designer can reason about a program using clocks, but then analyze its schedulability using a classical schedulability analysis, or generate multi-task C code targeting a real-time OS.

## 1.3 Multicore Platforms

The first issue tackled in this thesis is the programming of real-time systems on multicore platforms. Indeed, multicore platforms offer a potential for increasing system performances as cores might process tasks in parallel. However, these platforms are characterized by a central memory that is shared between cores. As cores can and must access this memory and the central memory can only answer a limited amount of requests at a time, a core might suffer a delay whenever it tries to access the main memory.

Accurately predicting these delays is difficult as it depends upon minute details within both hardware and software, as well as their interaction. This forces system designers to assume overly pessimistic execution scenarios, even though these scenarios might be highly improbable or even impossible.

Predictable multi-phase models have been proposed to address these issues. Intuitively, they divide system execution into "execution" and "memory" phases. Execution phases perform the actual computations required by the system tasks, while memory phases manage the unpredictability of memory accesses for the execution phases. For instance, a memory phase might perform cache prefetches such that the following execution phase never has to access the shared memory, all memory accesses being answered by the cache.

However, manually implementing these multi-phase models is non-trivial as the underlying hard-ware and software offers the illusion of an uniformly accessible memory. Thus, a deeply-nested function call might alter the system state in an unpredictable way, breaking the assumptions of the multi-phase model.

## 1.4 Multi-mode Systems

The functional requirements of a real-time system may evolve during its execution. For instance, the requirements for an aircraft control system are not identical during take-off, cruise and landing. Meeting all requirements at all times is obviously superfluous and just leads to over-provisioning the system's computing capacities.

A typical pattern in real-time systems is thus to design a system with multiple modes of execution. Each mode handles a specific set of functional requirements and a mode change request triggers a change from one mode to another.

The hardest challenge with this methodology is that while modes might be verified in isolation, the transition from one mode to another requires additional care. Indeed, a system designer has to choose a balance between promptness and system load during a mode change. A mode change with maximal promptness would simply release all new-mode tasks immediately, but this could lead to system overload as old- and new-mode tasks are competing for system resources. On the contrary, delaying the mode change until a "safe" point in time guarantees that the system load remains low, would have poor promptness as the worst-case time until such a point is reached is exponential with the number of tasks within the system.

In addition, the state of the art regarding multi-mode real-time systems is divided between works focusing exclusively on the temporal aspects and works focusing exclusively on functional aspects. However, efficient design of real-time systems requires the ability of both. Ignoring functional aspects would lead to design choices with questionable semantics and ignoring temporal aspects would limit oneself to a restricted set of systems.

## Chapter 2

## Contribution

The tackled problems will be discussed in individual Parts. Handling multicore is related to the back end of a compiler since it focuses on code-generation. In contrast, multi-mode behavior focuses on the front end of the compiler, especially the clock calculus, a form of static analysis. This allows us to consider improvements on all aspects of the language compiler.

## 2.1 Compiling Synchronous Languages on Multicore

Our contribution relies on an adaptation of the AER multi-phase model. It leverages the private memories of cores (e.g. caches or scratchpads) as they are not subject to competition. Task execution is divided into three phases: Acquisition, Execution, Restitution. The Acquisition- and Restitution-phases are memory phases. Their role is to copy data respectively from shared to private memory and from private to shared memory. Executing between those phases, the Execution phase thus does not suffer from memory access delays.

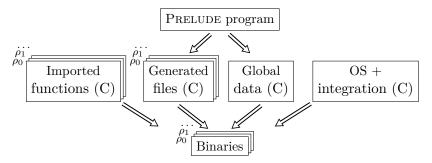

In Part III, the PRELUDE compiler is adapted to generate AER-compliant C code from a high-level PRELUDE program. Thus, the responsibility of low-level implementation concerns related to memory accesses are shifted onto the compiler. The automatic and systematic handling of these concerns by the compiler saves tedious and error-prone development efforts. These extensions is implemented as part of the main PRELUDE compiler <sup>1</sup>.

## 2.2 Synchronous Semantics of Multi-mode systems

Our contribution builds upon the previous work of Synchronous State Machines for LUSTRE. State Machines are an established formalism to reason about stateful, reactive systems. A system designer defines states in which the system behavior is defined in isolation. Transitions allow to switch from one state to another. An interesting property of these state machines, is that they are defined using a transpilation. While the programmer writes programs in a surface language with state machines, the compiler transparently translates them into programs in a core language where the state machines have been replaced by lower-level language constructs.

A limitation of Synchronous State Machines is that have been defined for languages without multiple real-time constraints. Thus, a direct transposition of this feature to Prelude would prevent

<sup>&</sup>lt;sup>1</sup>As part of the ffort\_aer branch, either available at the ONERA forge or my personal mirror.

programmers from using a core aspect of the language. Indeed, this limitation arises from the lower-level constructs used in the transpilation which Prelude directly inherits from Lustre.

Our contribution thus focuses on extending these language constructs. In essence, these extensions allow us to decouple the rate of tasks from the rate of mode changes. This in turn required us to change the clock calculus of the Prelude language. As the required modifications are quite profound, these extensions resulted in a rewrite of the Prelude compiler <sup>2</sup>.

#### 2.3 Thesis Overview

This Section will detail what to expect from and how to read this document.

Part II will present the "Related Works" of this thesis. It presents established models and languages used in the context of real-time systems which will serve as a basis for our contributions. Part III will present the first contribution detailed in Section 2.1. Part IV will present the second contribution detailed in Section 2.2. Finally, Part V will conclude this thesis and discusses perspectives for future works.

While this document is readable from "beginning to end", the contributions are mostly independent. Thus, certain readers might prefer reading first towards one contribution and then towards the second

In all cases, Chapter 3, Chapter 6 and Chapter 7 are must-reads to get a proper understanding of the contribution. Chapter 3 presents a base model for real-time systems which originated from pioneer works in real-time scheduling [55]. However, this model is only suited for analyzing a posteriori an existing system. Thus, Chapter 6 presents languages to actually program real-time systems. It will in particular focus on synchronous languages [14]. Finally, Chapter 7 will present the synchronous language Prelude [67] upon which these contributions build.

For the contribution in Part III, one should read Chapter 4 to better understand the issues introduced by multicore platforms in the context of real-time systems. If it isn't already done, reading Section 6.7 will also detail how these issues have been addressed from the point of view of programming languages in the state of the art.

For the contribution in Part IV, one should read Chapter 5 and Section 6.6 to understand how this issue has been tackled in the state of the art from the point of view of real-time scheduling and programming languages.

<sup>&</sup>lt;sup>2</sup>Available here

# Part II Background and Definitions

## Chapter 3

# Simple Model for Real-Time Tasks

In this Chapter, we present an overview of real-time systems and a simple model for real-time tasks. In the following, Chapters 4 to 5, this model will be expanded upon.

In essence, real-time systems are cyber-physical systems which simultaneously perceive and influence an environment. Their reactions must be provided at a rate that is adapted to the evolution rate of the environment. A failure to do so would have critical consequences, e.g. deaths, high financial or environmental damages. Readers looking for a more in-depth review may consult [21,22].

A real-time system is modeled as a directed acyclic graph  $(\mathcal{T}, \mathcal{D})$  where  $\mathcal{T}$  is a set of tasks  $\tau_i \in \mathcal{T}$  and  $\mathcal{D}$  is a set of data-dependencies between pairs of jobs  $(\tau_i^n, \tau_j^m) \in \mathcal{D}$ .

## 3.1 Tasks

Each task  $\tau_i = (O_i, T_i, D_i, C_i) \in \mathcal{T}$  releases a sequence of non-overlapping jobs where  $\tau_i^n$  denotes the n-th job of  $\tau_i$ . The set of jobs is  $\mathcal{J}$ . A task can be interpreted as an OS thread that executes an infinite loop, while a job represents one execution of the loop. Figure 3.1 illustrates this simplified view.

As alluded above, a task is defined as a tuple of *real-time attributes*. We consider the following attributes.

**Definition 1** (Offset). The offset  $O_i$  denotes the date when the first job  $\tau_i^0$  of  $\tau_i$  is released.

```

void task_i (void)

{

// Start of task \(\tau_i\)

for(int n = 0; true; ++n)

{

// Wait for activation of job \(\tau_i^n\)

wait_activation();

// Perform computation associated to job

do_computation();

}

}

```

Figure 3.1: Simplified view of tasks and jobs

**Definition 2** (Period). The period  $T_i$  denotes the time interval between successive releases of jobs of  $\tau_i$ , i.e.  $\tau_i^n$  is released at date  $r_i^n = O_i + n * T_i$ .

**Definition 3** (Deadline). The relative deadline  $D_i$  denotes the maximum amount of time a job of  $\tau_i$  has after its release to finish its execution. A relative deadline  $D_i$  is implicit, if  $D_i = T_i$ . In most models, non-implicit deadlines are still constrained such that  $D_i \leq T_i$ . In certain models, different jobs of the same task may have different relative deadlines.

The absolute deadline is the point in time at which  $\tau_i^n$  must have finished its execution. It is  $d_i^n = r_i^n + D_i$ .

**Definition 4** (Execution time). The execution time  $c_i$  denotes the amount of time a job requires to compute. An important metric is the Worst-Case Execution Time (WCET)  $C_i$  because of its use in Scheduling Analysis (Section 3.4).

**Definition 5** (Utilization). The system utilization is the total load of the system. It is defined as  $U = \sum_{\tau \in \mathcal{T}} = \frac{C_i}{T_i}$ .

**Definition 6** (Hyperperiod). The *hyperperiod* of a task(sub)set is the least common multiple of the task periods. We denote H the hyperperiod of the entire system and  $H_{i,j}$  the hyperperiod of a pair of tasks  $\tau_i$  and  $\tau_j$ .

**Definition 7** (Job begin). We denote  $begin(\tau_i^n)$  the date at which  $\tau_i^n$  starts executing (which may be after  $r_i^n$ ) for a specific schedule.

**Definition 8** (Job end). We denote  $end(\tau_i^n)$  the date at which  $\tau_i^n$  stops executing (which may be before  $d_i^n$ ) for a specific schedule.

**Definition 9** (Schedule). A schedule is a possible execution trace of a real-time system. Scheduling decisions, e.g. which job should execute at which point in time, are the responsibility of the scheduling policy (Section 3.3). A schedule is valid, iff  $\forall \tau_i^n.r_i^n \leq begin(\tau_i^n) \wedge end(\tau_i^n) \leq d_i^n$ , i.e. all jobs terminated before their deadline and started executing after their release.

## 3.2 Data-dependencies

Each data-dependency, also called communication,  $\tau_i^n \to \tau_j^m = (\tau_i^n, \tau_j^m) \in \mathcal{D}$  indicates that job  $\tau_i^n$  produces data that is used by job  $\tau_j^m$ . We assume that data-dependencies are *causal*.

**Definition 10** (Causal data-dependencies). A causal data-dependency  $\tau_i^n \to \tau_j^m$  requires:

$$end(\tau_i^n) < begin(\tau_i^m)$$

For each data-dependency  $\tau_i^n \to \tau_j^m$ ,  $\tau_i^n$  produces its outputs at  $end(\tau_i^n)$  and  $\tau_j^m$  acquires its inputs at  $begin(\tau_i^m)$ .

Moreover, to efficiently implement a real-time system, we only consider data-dependencies between tasks that follow a predefined sequence. The data-dependency between tasks  $\tau_i$  and  $\tau_j$  is a tuple  $\mathcal{D}_{i,j} = (\mathcal{D}_{i,j}^{pref}, I_{i,j}^{pref}, \mathcal{D}_{i,j}^{pat}, I_{i,j}^{pat})$  where  $I_{i,j}^X$  is an interval length in time units,  $\mathcal{D}_{i,j}^X$  is a data-dependency template, pref indicates that it belongs to the prefix and pat indicates that it belongs to the pattern. The prefix defines the data-dependencies between the two tasks at the start of the system between

dates 0 and  $I_{i,j}^{pref}$ . Thus,  $\mathcal{D}_{i,j}^{pref}$  contains data-dependencies between jobs active between date 0 and  $I_{i,j}^{pref}$ . The pattern is a template that repeats after date  $I_{i,j}^{pref}$  each  $I_{i,j}^{pat}$  time units.

Because of the cyclical nature of data-dependencies, we can define  $\mathcal{D}$  by using  $\mathcal{D}_{i,j}^{pref}$  for the first  $I_{i,j}^{pref}$  time units and then unrolling  $\mathcal{D}_{i,j}^{pat}$  each  $I_{i,j}^{pat}$  time units to obtain data-dependencies between concrete job instances. For instance, the first iteration of  $\mathcal{D}_{i,j}^{pat}$  defines data-dependencies between dates  $I_{i,j}^{pref}$  and  $I_{i,j}^{pref}+I_{i,j}^{pat}$ . Data-dependency  $(\tau_i^0,\tau_j^0)\in\mathcal{D}_{i,j}^{pat}$  then indicates a data-dependency between the first jobs of  $\tau_i$  and  $\tau_j$  released within that interval (typically at date  $I_{i,j}^{pref}+I_{i,j}^{pat}$ ).

**Definition 11** (Data-dependencies by unrolling). Assuming an assignment of data-dependencies prefixes and patterns  $(\mathcal{D}_{i,j}^{pref}, \mathcal{D}_{i,j}^{pat})$  and their length  $(I_{i,j}^{pref}, I_{i,j}^{pat})$ , the set of data-dependencies  $\mathcal{D}$  is defined as:

$$\mathcal{D} = \mathcal{D}^{pref} \cup \mathcal{D}^{pat}$$

$$\mathcal{D}^{pref} = \left(\bigcup_{\tau_{i},\tau_{j} \in \mathcal{T}} \mathcal{D}^{pref}_{i,j}\right)$$

$$\mathcal{D}^{pat} = \left\{ (\tau_{i}^{p}, \tau_{j}^{q}) \mid k \in \mathbb{N}, \tau_{i}, \tau_{j} \in \mathcal{T}, (\tau_{i}^{n}, \tau_{j}^{m}) \in \mathcal{D}^{pat}_{i,j}, \right.$$

$$p = n + \frac{I^{pref}_{i,j}}{T_{i}} + k \frac{I^{pat}_{i,j}}{T_{i}},$$

$$q = n + \frac{I^{pref}_{i,j}}{T_{j}} + k \frac{I^{pat}_{i,j}}{T_{j}} \right\}$$

## 3.3 Scheduling Policies

The pioneer works of the policies Rate-Monotonic (RM), Deadline-Monotonic (DM), and Earliest-Deadline First (EDF) spawned a large field of research with dedicated conferences and journals. Scheduling policies (and analysis) being out-of-scope for this work, we will focus on this short presentation. Curious readers might consider the earlier cited references for more in-depth discussions [21,22].

Because jobs compete for accessing shared resources (most notably the CPU), a scheduling policy is required to determine which job is to execute at each point in time, using real-time attributes to guide its decisions. A real-time system is feasible under a policy, iff the decisions of the scheduling policy guarantee that each job finishes executing before its absolute deadline. A policy is optimal for a specific class of systems, iff it is able to produce a feasible schedule for a feasible systems within that class.

DM belongs to the class of task-level static priority policies. All jobs of a task share the same priority. Jobs with lower relative deadline have a higher priority. EDF belongs to the class of job-level static priority policies. A job's priority is determined by its absolute deadline. Jobs with an earlier deadline have a higher priority. EDF is the more general policy: it is optimal on mono-processor systems. DM is only optimal on mono-processor systems within the class of task-level static priority policies.

## 3.4 Schedulability Analysis

A schedulability analysis is a static analysis that verifies the feasibility of a real-time system. The complexity of the schedulability analysis depends on the scheduling policy and the complexity of the system. For a real-time system scheduled by EDF without data-dependencies and implicit deadlines, the schedulability analysis is  $\sum_{\tau_i \in \mathcal{T}} \frac{C_i}{T_i} \leq 1$ . Adding data-dependencies or non-implicit deadlines requires

to verify that the demand-bound function [12] holds, i.e.  $\forall t \in \mathbb{N}. \ t \geqslant \sum_{\tau_i \in \mathcal{T}} C_i * (\lfloor \frac{t - D_i}{T_i} \rfloor + 1).$

**Example 1** (Real-time systems with and without data-dependencies). Let us consider the following real-time system without data-dependencies.

| $	au_i$ | $O_i$ | $T_i$ | $D_i$ | $C_i$ |

|---------|-------|-------|-------|-------|

| $	au_1$ | 0     | 5     | 3     | 1     |

| $	au_2$ | 0     | 10    | 10    | 3     |

| $	au_3$ | 2     | 6     | 6     | 2     |

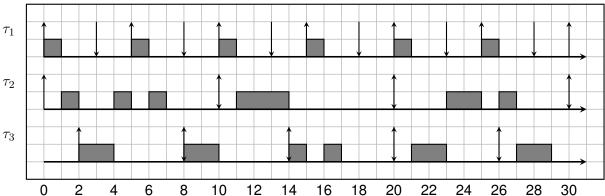

Executing this system according to the *Earliest Deadline First* policy on a monocore platform yields the following schedule shown as a *timing diagram*. The diagram indicates when a given task executes. Each task has its own timeline. A grey box indicates that a task executes during that time interval. Since tasks compete for access to the processor, only one may be active at a time. Arrows pointing upwards indicate a job release, while arrows pointing downwards indicate that corresponding job's absolute deadline.

A selection of attributes:

$$H = 30$$

$H_{1,2} = 10$   $r_1^1 = 5$   $d_1^1 = 8$   $begin(\tau_2^0) = 1$   $end(\tau_2^0) = 7$

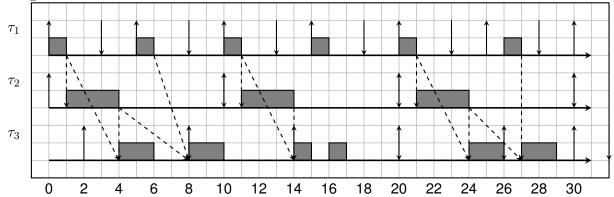

Now, let us consider the same system with data-dependencies. The data-dependency patterns are shown below.

$$\begin{split} \mathcal{D}^{pat}_{1,2} &= \{ (\tau^0_1, \tau^0_2) \} \\ \mathcal{D}^{pat}_{1,3} &= \{ (\tau^0_1, \tau^0_3), (\tau^1_1, \tau^1_3), (\tau^2_1, \tau^2_3), (\tau^4_1, \tau^3_3), (\tau^5_1, \tau^4_3) \} \\ \mathcal{D}^{pat}_{2,3} &= \{ (\tau^0_2, \tau^0_3), (\tau^0_2, \tau^1_3), (\tau^1_2, \tau^1_3), (\tau^2_2, \tau^4_3), (\tau^2_2, \tau^4_3) \} \end{split} \qquad \qquad I^{pat}_{1,2} &= 30 \\ \mathcal{D}^{pat}_{2,3} &= \{ (\tau^0_2, \tau^0_3), (\tau^0_2, \tau^1_3), (\tau^1_2, \tau^1_3), (\tau^2_2, \tau^4_3), (\tau^2_2, \tau^4_3) \} \end{split}$$

Executing this system according to the EDF policy, while respecting data-dependencies, yields the

following schedule.

## Chapter 4

## Multicore Real-Time Systems

Multicore systems pose new issues for real-time systems. On the one hand, they offer a potential for increasing system performances by allowing to execute one job per core simultaneously (i.e. offering parallelism in addition to the inherent concurrency of real-time systems). On the other hand, multicore systems are characterized by a global memory that is shared between cores via a bus. Accesses to this memory may be delayed if multiple cores try to access it simultaneously. These delays, called contentions, have a high variability between their worst-case and average values because they depend upon minute details within task codes, task interferences and the contention resolution mechanisms [72]. This in turn leads to an overly pessimistic WCET even though the conditions for the actual worst-case are highly unlikely or even impossible.

## 4.1 Scheduling

Scheduling policies similar to those used in monocore exist in multicore. However, these policies exist either as a partitioned or as a global variant. In a partitioned policy, tasks are assigned at system design to a core and may only execute on that core. Thus, scheduling decisions need only to take into account core-local properties. In a global policy, tasks may execute on any processor and a single scheduler makes decisions for the whole system. These two variants are incomparable, meaning that there exist real-time systems which are only feasible under partitioned scheduling and others which are only feasible under global scheduling.

## 4.2 Hardware model

To elaborate our hardware model, let us look at how a multicore system is composed. Such a system is composed of processor cores which are connected via a bus to the RAM which is a *shared central memory*. Thus, access to the RAM is subject to contentions. Each core also has access to *private memories* which can only be accessed by that core and are not subject to contentions. The most common are cache memories which can replicate content of the RAM for faster access. When accessing a memory address, if the location is replicated in the cache, the processor can access it faster and contention-free from there.

Certain embedded platforms also have *scratchpad memories* (SPM). These private memories have the same timing properties as caches, but instead of implicitly replicating the shared memory, scratchpad memories possess their own memory space and must thus be manipulated explicitly.

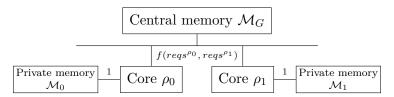

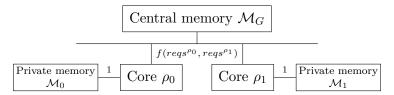

Figure 4.1: An example hardware component graph

Using those observations, we can see that the switch to multicore platforms requires to explicit a hardware component graph. It also exists in monocore platforms, but represents trivial instance of such a graph, i.e. accessing the central memory is trivial when there is only one processor/core accessing it. The edges of this graph are either CPU cores  $\rho_i \in \Pi$  or memories  $\mathcal{M}_i \in \mathfrak{M}$ . The vertices of this graph connect CPU cores to memory components and are annotated with access costs.

Figure 4.1 displays an example graph. Each core  $\rho_i$  has access to its private memory  $\mathcal{M}_i$ , but cannot access to another private memory. The access cost is constant in this example, 1 instruction cycle, which is typical for scratchpads or caches. Each core can however access the central memory  $\mathcal{M}_G$ . The access cost in this case is however a function depending on the memory requests emitted by all CPU cores.

## 4.3 PREM

To address the pessimism induced by contentions, one solution is to reduce the number of instructions they can impact. The PRedictable Execution Model (PREM) [71] achieves this by decoupling contention-inducing (communication) phases from computation phases.

The idea is that most jobs in a real-time system will load values from a shared buffer or sensor, perform computations and then write results back into a buffer or actuator. When writing code without PREM-compliance in mind, one could mix those buffer accesses and computations, e.g. first load a value and perform some computations with it before loading a second value. Worse, those buffer accesses could be located deeply-nested within functions called by the task code.

To write with PREM-compliance in mind, contending accesses have to be isolated such that once all such operations are completed, computations can execute without risking to produce contentions. To do so, all required data and code should be located within memories that are guaranteed contention-free, e.g. registers, private caches or scratchpad-memory.

Figure 4.2 shows a simple task code with and without PREM-compliance. Without PREM-compliance in Figure 4.2a, the task is implemented using opaque subroutines where certain buffers are accessed mid-execution. Figure 4.2b shows an implementation with PREM-compliance in mind. Three distinct phases are visible. First, all necessary buffers are read in a contention-inducing communication phase. Second, subroutines are called in a contention-free computation phase. Note that deeply-nested buffer accesses are replaced by explicit parameters. Lastly, a new communication phase stores the result in an output buffer.

#### 4.4 AER

The AER [32] model is similar to the PREM model but further restricts the structure of tasks. Each job  $\tau_i^n$  of task  $\tau_i$  must be divided into a sequence of 3 phases: Acquisition  $(A_i^n)$ , Execution  $(E_i^n)$ , Restitution  $(R_i^n)$ . In the Acquisition phase, data is copied into private memory from global memory.

4.5. RELATED WORKS 21

```

void g(int x)

int g(int x, int y)

{

x = g1(x);

x = g1(x);

int y = read2();

x = g2(x, y);

x = g2(x, y);

return x;

write3(x);

}

void do_computation()

void do_computation()

{

//Reads buffer 1

int x = load_buf1()

int x = f()

int y = load_buf2()

//Reads buffer 2

x = f(x)

//Writes buffer 3

y = g(x, y)

g(x)

store_buf3(y)

}

```

(a) Without PREM-compliance

(b) With PREM-compliance

Figure 4.2: Job body with and without PREM-compliance

In the Execution phase, computations are executed contention-free using the private memory. Finally, in the Restitution phase, results of the computation are copied from the private memory into the global memory.

This declination is advantageous because it is close to the model of synchrony (Section 7.4) where computations (Execution phase) are assumed to execute without side-effects except input acquisition (Acquisition phase) and output production (Restitution phase). Because of this, we will rely on the AER model in this work.

Looking at Figure 4.2b, this example matches with the AER model. The calls to load\_bufX() are the Acquisition phase. The calls to f and g are the Execution phase and store\_buf3(y) is the Restitution phase.

## 4.5 Related Works

The difficulty of predicting the timing properties of multicore real-time systems because of the minute interactions between task codes, task interferences, and the contention resolution mechanisms, has been identified in [72, 73, 85].

The PREM [71] and AER [32,58] models have been proposed to address this issue. They both divide task execution in *memory phases* which interact with the global memory and *execution phases* which perform computations contention-free, i.e. with accessing the global memory. The main difference between those two is that the AER model is more explicit about the role of the different phases. Unless stated otherwise, we will use PREM and AER interchangeably.

Both models have gained significant attention from the real-time scheduling community such that numerous scheduling algorithms and schedulability analyses have been proposed [4–6,13,18,57,63,84,106,108,109].

Concrete applications of these models have been considered at different levels of the software-stack.

## 4.5.1 OS-level support

At the lowest level, support for PREM can be introduced at the OS-level. This has been studied in [90, 93–95, 105]. The system developers writes their task code using the provided OS primitives. The compilation process will produce an OS image that will use the scratchpad memory as appropriate. Similarly, others have studied the introduction of PREM-support using a hypervisor [51]. In [40], such a technique is introduced to support mixed-criticality systems.

#### 4.5.2 Source code refactoring

Many real-time systems are composed of legacy code, in general non-PREM-compliant C code. Refactoring this code to be PREM-compliant is non-trivial and requires a thorough understanding of the code to be converted. Using memory profiling tools, Light-PREM [59] refactors legacy source code in such manner that it is PREM-compliant.

#### 4.5.3 Binary code generation

Another possibility is to modify the compiler, in this case the LLVM compiler, such that it produces PREM-compliant code. In [71], a new predictable-block is introduced. Code within this block is generated such that it is PREM-compliant. In [62], no new language construct is introduced, but the compiler plugin is required to perform more advanced analyses and ILP-based scheduling. In [91], a specialized LLVM plugin produces PREM-compliant code using SPM.

#### 4.5.4 Predictable GPU-code

The problems of multicore-platforms that led to the development of the PREM-model, also exist on platforms featuring integrated GPUs. Unlike dedicated GPUs which possess their own memory and communicate with the main memory via a bus such as PCI-Express, integrated GPUs share their memory with the CPU. To address this issue, solutions such as HePREM [37,38] and SiGamma [24] have been proposed.

## Chapter 5

# Multi-Mode Real-Time Systems

One restriction of the model in Chapter 3 is that the task set  $\mathcal{T}$  is statically defined at system design. It is not possible to specify changing functional requirements throughout system execution. However, certain real-time systems have a *multi-moded* behavior. A typical example would be an aircraft control system with modes such as take-off, cruise and landing.

In this Chapter, we will discuss two ways to model real-time systems with the ability to perform system reconfiguration during execution. Section 5.1 presents mode change protocols, a generic mechanism to switch between different modes. Section 5.2 presents mixed-criticality systems, a special case of mode change protocols where the current mode sets the minimum criticality of tasks allowed to run.

## 5.1 Mode Change Protocols

When using *Mode Change Protocols* (MCP) [82], the system is defined as a set of distinct task sets. Each task set represents a possible and valid system configuration with potentially different timing constraints. The MCP is then responsible for switching from one task set (the old mode) to another (the new mode) when a *Mode Change Request* (MCR) is emitted. During this *transition phase*, the MCP must guarantee that jobs respect their deadlines.

Note that this approach asks different levels of detail for different aspects of the system. The system designer (or the used tool) must define precisely each individual mode in its "pure" form, i.e. how the mode executes ignoring the arrival of MCRs. However, beyond the choice of a specific mode change protocol, there is little control over how the system behaves between the modes.

In this context, different protocols offer different advantages. We compare MCPs according to two criteria: *promptness* and *overload*. The promptness of a MCP is its worst-case transition time. The overload induced by a MCP is due to the transition phase. For certain MCPs, a dedicated schedulability analysis is required.

A protocol with maximal promptness would start releasing all new-mode jobs immediately upon receiving the MCR. This leads however to poor schedulability because the system would need to be able to schedule both modes simultaneously during the transition phase.

A protocol with maximal schedulability would wait until no job of the old-mode is waiting to be executed. In the worst case, this requires to wait until a date that is a multiple of the hyperperiod. This protocol leads to no temporary overload and is easy to analyze. However the worst-case transition time is exponential with the number of tasks.

There is no best protocol and as a consequence, a system designer must choose a MCP that suits their system. The real-time literature [82] classifies MCPs according to three criteria:

- Overlapping<sup>1</sup>: When do the new-mode tasks start executing?

- Periodicity: Are unchanged tasks impacted by mode changes?

- Retirement: How long can old-mode tasks continue executing?

Non-overlapping protocols release the new-mode tasks only at the end of the transition phase. Tasks of both modes thus never co-exist. Overlapping protocol allow new-mode and old-mode tasks to be both executed during the transition phase. The potential overlap between modes allows for a more prompt transition at the cost of a scheduling analysis specific to the transition phase.

*Periodic* protocols do not interfere with the execution of *unchanged tasks*, i.e. tasks which are present both in the old- and the new-mode. *Aperiodic* protocols suspend unchanged tasks for the duration of the transition phase.

Late-retirement protocols gracefully decommission old-mode tasks by continuing their execution for a given amount of time, e.g. until they complete their current activation. Early-retirement protocols abort old-mode tasks as soon as the MCR is triggered.

One should note that this classification of multi-mode real-time systems [82] does not take into account the semantics of the system. For instance, how do early-retirement or aperiodicity interact with data-dependencies? This issue will be addressed in our work.

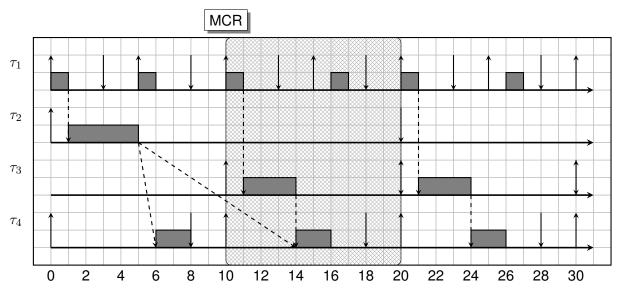

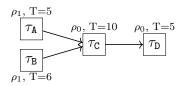

**Example 2** (Multi-mode real-time systems). Let us consider the following real-time system with the modes A and B. For simplicity, we assume that all tasks have  $O_i = 0$ .

| $	au_i$ | $T_i$ | $D_i$ | $C_i$ |

|---------|-------|-------|-------|

| $	au_1$ | 5     | 3     | 1     |

| $	au_2$ | 20    | 20    | 4     |

| $	au_3$ | 10    | 10    | 3     |

| $	au_4$ | 10    | 8     | 2     |

Data-dependencies within mode A are:

$$\mathcal{D}^{pat}_{1,2} = \{ (\tau^0_1, \tau^0_2) \}$$

$$I^{pat}_{1,2} = 20$$

$$\mathcal{D}^{pat}_{2,4} = \{ (\tau^0_2, \tau^0_4), (\tau^0_2, \tau^1_4) \}$$

$$I^{pat}_{1,3} = 20$$

Data-dependencies within mode B are:

$$\mathcal{D}_{1,3}^{pat} = \{(\tau_1^0, \tau_3^0)\} \qquad I_{1,2}^{pat} = 10$$

$$\mathcal{D}_{3,4}^{pat} = \{(\tau_3^0, \tau_4^0)\} \qquad I_{3,4}^{pat} = 12$$

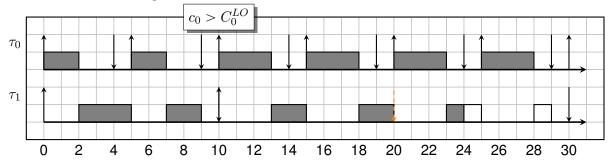

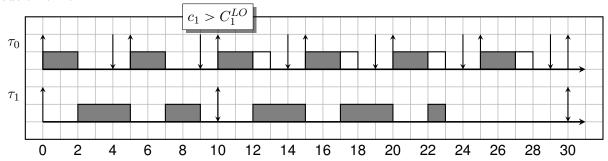

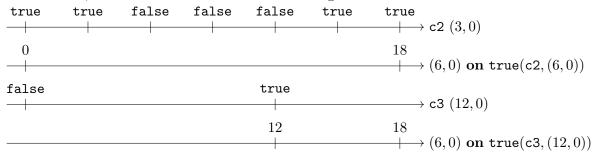

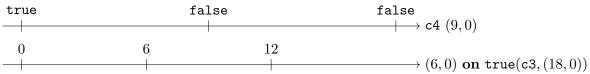

Below we will show a transition from mode A to mode B using an overlapping, periodic protocol with late-retirement. A MCR is emitted at date 10, which starts a transition phase (grey box). As can be seen, during the transition period, tasks  $\tau_2$  and  $\tau_3$  co-exist during this period.

<sup>&</sup>lt;sup>1</sup>Also called synchronicity [82], we renamed it to avoid confusion with synchronous languages.

The diagram below shows a similar, but non-overlapping, transition from mode B to mode A.

#### 5.1.1 Related Works

A survey [82] presents a good overview of real-time scheduling of multi-mode systems.

- The *idle time protocol* [98] waits for an *idle time* (i.e. an instant where no job is waiting to be executed) to transition. The worst-case waiting time is the hyperperiod of old- and new-mode tasks.

- The maximum-period offset protocol [9] waits for a time equal to the maximum of the old- and new-mode task periods to transition.

- The minimum single offset protocol [81] interrupts the release of old-mode jobs upon reception of an MCR and waits for the termination of currently running old-mode jobs;

- The *utilization-based protocol* [86] keeps a ledger of the current system utilization. New-mode tasks are added gradually as old-mode tasks finish executing, reclaiming the liberated utilization.

- Tindell's asynchronous protocol with periodicity [99] is late-retiring. Old-mode jobs finish their current execution, but no new old-mode jobs are released. Unchanged tasks may have different attributes between modes.

- Pedro's asynchronous protocol without periodicity [70] behaves similarly. Breaking periodicity allows however to schedule a greater number of task sets.

- The paper's own protocol is a mixture of Tindell's and Pedro's protocol. It is an extension of Tindell's protocol that takes inspiration from Pedro's protocol to improve promptness. By default, it is a periodic protocol, but it can introduce aperiodicity to guarantee schedulability.

A limitation of this work is that it does not consider data-dependency. Instead, it considers consistency of shared resources, i.e. mutexes, which is too simplified in our opinion.

Later work on *real-time calculus* [75–77,92], improves this by considering that tasks consume data from a buffer. However, it is not considered how these buffers are filled.

Beyond this work, some work expanded upon the study of multi-mode systems for special cases such as multicore systems [65, 66], high-performance multimedia systems [100] or systems with arbitrary deadlines [61]. However, these papers do not solve this limitation.

## 5.2 Mixed-criticality systems

A special case of multi-mode systems are mixed-criticality systems [19, 20, 102]. In the base model of real-time systems, all tasks are considered equally critical: any deadline-miss is considered catastrophic. This is not the case in a mixed-criticality system. In its simplest form, each task has either a high- (HI) or low-criticality (LO). LO tasks may execute in a degraded state, if this may allow HI tasks to respect their deadlines.

The main motivation for mixed-criticality originates from software standards such as the avionics standard DO-178C [30] where software has different levels of criticity. DO-178C defines Software Levels from A, "Catastrophic", to E, "No Effect". Failure in Software Level A could cause deaths, while failure in Software Level E could not negatively impact safety, aircraft operation, or crew workload (but could cause passenger discomfort). Mixed-criticality systems offer a way to execute software of different levels on the same platform while guaranteeing that lower levels have no negative impact on software of higher levels [20].

**Example 3** (Mixed-criticality real-time systems). Let us consider the following, simplified, mixed-criticality real-time system. It has two levels of criticality, LO and HI. In each mode, two tasks execute,  $\tau_0$  and  $\tau_1$ . Task  $\tau_0$  is a high criticality task that must be able to execute at any cost, while task  $\tau_1$  is of lower criticality and may experience a decrease in quality of service.

Their real-time attributes are shown below. As can be seen, task period, deadline and WCET vary between the LO- and HI-mode. Most notably, the WCET in the LO-mode is lower for both tasks. This WCET-value is the "optimistic" WCET which upper-bounds the majority of execution traces. On the other hand, the values for the HI-mode are the actual WCET values which upper-bound all execution traces. The examples below will assume a semi-clairvoyant scheduler (see below) that is able to increase task periods and deadlines during execution, but not abort jobs.

|         |       | LO       |          |          | HI       |          |          |

|---------|-------|----------|----------|----------|----------|----------|----------|

| Task    | $O_i$ | $T^{LO}$ | $D^{LO}$ | $C^{LO}$ | $T^{HI}$ | $D^{HI}$ | $C^{HI}$ |

| $	au_0$ | 0     | 5        | 4        | 2        | 5        | 4        | 3        |

| $	au_1$ | 0     | 10       | 10       | 5        | 20       | 20       | 7        |

The timing diagram below illustrates a potential criticality change due to  $\tau_0$  requiring more execution time than  $C_0^{LO}$ . This means that the absolute deadline of  $\tau_1^0$  is delayed by 10 time units to reflect the increase of  $T_1$  and  $D_1$  (orange doted line at date 10). In white, we indicate the time intervals  $\tau_1^0$  would use in case it too required more execution time.

This second diagram illustrates a criticality change triggered by  $\tau_1$  this time. Again, white boxes indicate time slices that would have been consumed in case jobs of  $\tau_0$  required their high-criticality execution time.

#### 5.2.1 Related Works

A survey [20] presents a good overview of real-time mixed-criticality systems. It is regularly updated which makes it a valuable resource.

The seminal work of mixed-criticality [102] presents the ground works of the mixed-criticality model. While notions such as HI and LO tasks has been reused in further work, this paper presents a simplistic model. Tasks have a set of real-time attributes for each criticality level. Thus, the WCET value represents an execution time budget. The scheduler tracks the execution time of tasks. When a tasks exceeds that budget, the scheduler changes the criticality level. Certain tasks would have no period in the new mode, meaning they would be aborted immediately without taking into consideration data-dependencies. Moreover, the paper defines no mechanism to return to a lower criticality level.

In [19], it has been identified that mixed-criticality systems are a special case of multi-mode systems. Reconsidering them under this optic allows us to reapply previous results. For instance, returning to a lower criticality can be solved by re-using an existing mode change protocol.

Work on *semi-clairvoyant scheduling* for mixed-criticality systems [3, 11], addresses the issue of the nebulous semantics in the original model. A semi-clairvoyant scheduler is able to know at job-release (thus before any instruction is executed) certain properties about the job-execution. A semi-clairvoyant scheduler can use a parametric WCET [10, 23] to compute a more exact WCET value for the current job execution. Thus it may potentially trigger a change in criticality mode.

## 5.2.2 Link with Mode Change Protocols

As has been illustrated, mixed-criticality systems literature often lacks considerations for semantics. Reconsidering them as multi-mode system could solve this issue. Our contribution (Part IV), offers thus a way to program mixed-criticality systems with a formally sound basis.

## Chapter 6

# Synchronous Languages for Real-Time Systems

In Chapters 3 to 5, the presentation of real-time systems was fairly abstract, it focused mostly on the temporal properties of these systems. In this Chapter, we present synchronous languages that have been designed for programming real-time systems. Moreover, we will also evaluate how these languages tackle the problems of programming multicore and multi-mode systems.

## 6.1 Synchronous Languages

Synchronous languages are a family of programming languages that have been designed to tackle the challenges of programming safety-critical real-time embedded systems [14]. They are characterized by combining three properties:

- 1. Synchrony to abstract time as a sequence of discrete instants;

- 2. Deterministic concurrency via explicit language constructs;

- 3. Simple formal underlying models to make verification tractable.

Within that design space, different solutions emerged. In Sections 6.2 to 6.5, we will review these solutions and later contributions. We will both consider the original designs and later contributions that addressed the design of multicore and multi-mode systems.

## 6.2 Lustre

The LUSTRE programming language [42] is based on the formalism of control engineers who define a system via equations or dataflow networks. Under this formalism, a system is a sequence of equations x = e where x is a variable that appears exactly once on the left side of an equation and e is an expression describing the value of x at each point in time.

A LUSTRE program is thus structured around *nodes* rather than functions. The main difference is that in a node variables represent dataflows, i.e. infinite sequences of values, instead of individual scalar values. Instead of being composed of expressions or statements, the node-body is composed of equations. Node equations can be understood like mathematical equations: They define one dataflow by composition of other dataflows.

The synchronous model of time in the LUSTRE language is structured around *clocks*. Each dataflow has a clock and when a clock is *present*, i.e. "it produces a tick", its associated dataflow is present. A *clock calculus* [29] verifies the consistency of clocks within the program. In the case of LUSTRE, it can be solved using techniques similar to Hindley-Milner typing.

A base clock base specifies the fastest possible rate, i.e. base is present at each instant. Externally, the system designer can specify a period for the base clock, e.g. 1ms, but internally the language operates purely on ticks of the base clock. The clock operator ck on C(c) produces a clock that is present at each instant where ck is present and the dataflow c (whose clock is ck) produces a value c.

An expression e when C(c) conditionally sub-samples the dataflow e by keeping only the values of e at instants where dataflow c simultaneously produces the value e. The expression has clock e on e0 while both e and e0 have clock e1.

The expression merge(c, C0->e0, C1->e1) merges the *complementary* dataflows with respective clocks ck on C0(c) and ck on C1(c), i.e. only one dataflow is present each instant and the union of their instants is the instants of clock ck. The resulting dataflow has clock ck. For each instant, the merge operator simply selects the currently present dataflow and produces its value for the current instant. Another operator to manipulate dataflows with on operators is current. It accepts a dataflow with clock ck on C(c) and returns a dataflow with clock ck. For each instant where ck on C(c) is not present, the operator "fills the hole" by repeating the input dataflow's last value. A limitation of this operator is that, unlike the merge operator, it's behavior is undefined is ck on C(c) is not present the first time ck is present.

To relate logical time to physical time, a typical pattern is to define base as the fastest rate in the system, e.g. a period of 10ms, and then define sub-samplings of this clock that define slower rates. For instance, if dataflow each2 is true only once each two successive instants, clock base on true(each2) would represent a clock with a period of 20ms. However, this scheme has the limitation that it does not compose well. For instance, the type system has no knowledge of how base on true(each2), base on true(each3) and base on true(each6) relate to each other.

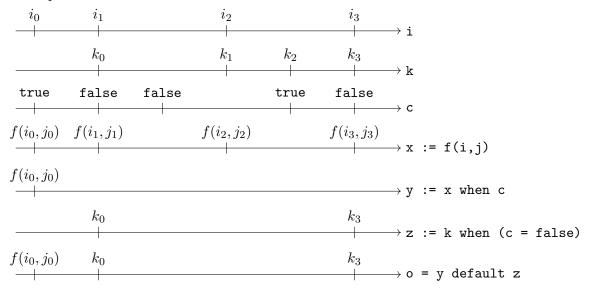

**Example 4** (Lustre). The program below is a minimal Lustre program featuring a single node main. This node has four inputs, i, j, k, and c, and one output, o. The first equation defines the local dataflow x as the result of f(i, j) where f is a function over scalars that has been lifted to operate on dataflows via point-wise application. For consistency reasons, such a lifted function requires its arguments to be *synchronous*, i.e. that they possess the same clock. The next two dataflows are conditional sub-samplings using the when operator. The resulting dataflows have the respective clocks base on true(c) and base on false(c). Finally, the output o is the result of merging the complementary dataflows together to obtain a new dataflow that has clock base.

```

node main(i,j,k,c) returns (o)

var x,y,z;

let

x = f(i, j);

y = x when true(c);

z = k when false(c);

o = merge(c, true->y, false->z);

tel

```

The timing diagram below illustrates a possible trace of this program. It illustrates the values carried by the dataflows over time. Note that it views the values carried by the dataflow from the point of view of logical time, i.e. computations are supposed to execute instantaneously.

6.3. SIGNAL 31

Inputs i and c have clock base and are thus present at each instant. Dataflow x is the result of applying the scalar function f pairwise on the values of i and j. Since the input rate defines the output rate, it also has clock base. Dataflows y and z are not present at each instant because they are on clocks base on true(c) and base on false(c) respectively.

## 6.3 Signal

The Signal language [15, 52, 54] is a synchronous dataflow language similar to Lustre. However, clocks are first-class objects in Signal. Thus, it is possible to express *polychronous* systems, i.e. systems where clocks do not form a single hierarchy. In contrast, Lustre is said to be *endochronous*. Programmers can manipulate clocks the following ways:

- 1. Any boolean dataflow, called *signal* in the language's lingo, can be lifted to a clock. In LUSTRE, the right-hand side of a when expression is always a data constructor and a variable. The LUSTRE expression e when C(c) is written in Signal e when (C = c). More complicated expressions such as e when (n >= 1) are also possible. The expression event e returns the clock of e, it is a short-hand for true when (e=e).

- 2. In addition to dataflow equations v := e where v is a variable and e an expression, Signal allows for *clock equations*. An equation v = e specifies that v and e have the same clock. Equation v = v + z specifies that the clock of v is the union of the clocks of v and v. Dataflow equations themselves also introduce clock equations. For instance, equation v = e when v introduces the equation v = e when v is at most as frequent as v.

To verify the clock consistency of a polychronous program, the clock calculus solves the set of all clock equations. While decidable, solving such equations is NP-hard. To mitigate this, efficient strategies have been proposed that trade-off completeness for efficiency [7,88]. These strategies do not accept all correct programs, but, for typical systems, the clock calculus efficiently verifies consistency. In [97] an approach for basing the clock calculus of SIGNAL on refinement types has been proposed.

For real-time systems, affine clock transformations [88] are of particular interest. An affine clock transformation is a tuple  $(n, \varphi, d)$ . Two clocks H and K are related by such a transformation, if there is a clock P such that: 1. H  $^{<}$  P and K  $^{<}$  P; 2. The i-th instant of H is the n\*i-th instant of P; 3. The i-th instant of K is the  $(d*i+\varphi)-th$  of P. This form of clocks allows to express efficiently

the relations between periodic tasks. However, this formalism does not directly relate instants to physical time. Moreover, compilation of such a model to multi-task code has not been studied to our knowledge.

**Example 5** (Signal). Let us discuss the implementation of Example 4 in Signal. It could be implemented as shown below. Instead of defining a node, a Signal program is a *process* defined via the parallel composition of equations.

We already discussed the when construct. However, signal does not feature a merge expression. Instead, the default operator performs deterministic merge of arbitrary expressions. Expression y default z is the union of the values of y and z. In case both dataflows are present simultaneously, y takes priority.

The clock equation added at the end of the example is not strictly required. We added it to guarantee that both examples exhibit the same behavior. Without it, the example becomes polychronous. Variables i and j must have the same clock because of they are arguments of f, but beyond that, variables may have unrelated clocks.

```

process main =

{ ? int i, j, k; bool c

! int o }

(| x := f(i, j)

| y := x when c

| z := k when (c = false)

| o := y default z

| o ^= i ^= j ^= k ^= c

|)

```

The timing diagram below illustrates a possible execution trace of the program without the clock equation. As can be seen, without added restriction, the output is not guaranteed to be as frequent as the inputs.

6.4. PRELUDE 33

## 6.4 Prelude

As shown in Section 6.2 and Section 6.3, the previously presented dataflow languages possess some limitations in their ability to directly express real-time constraints.

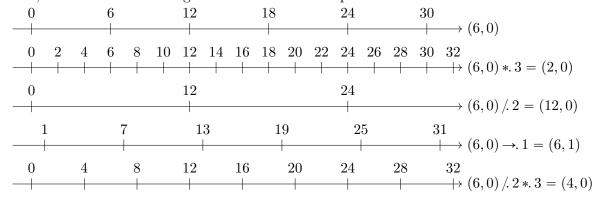

The PRELUDE language [36,67] solves this issue by introducing strictly periodic clocks. Using the tagged-signal model [53], each instant has a tag corresponding to its date, i.e. the first instant has tag/date 0, the second 1, etc. A strictly periodic clock (n,p) produces its i-th tag at date p + i \* n. Note that a clock (n,p) has its i-th tag when a task with T = n and O = p releases its i-th job. These similarities allow for efficient implementation as a set of dependent real-time tasks [35].

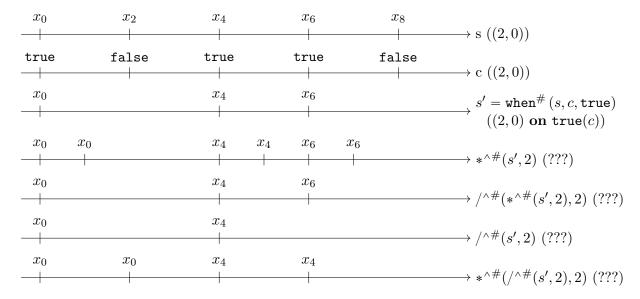

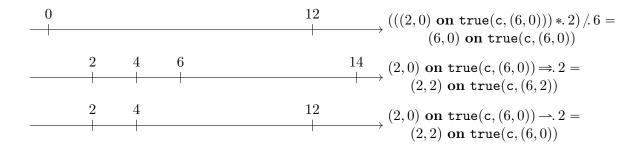

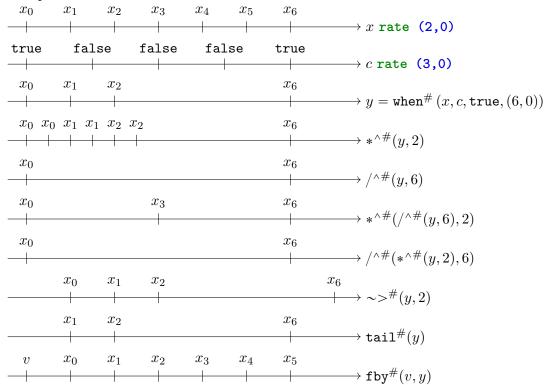

To bridge the gap between dataflows of different clocks, the language defines rate-transition operators. The expression  $e*^k$  produces a dataflow that is k times as fast as e by repeating each value of e times. If e has clock (n,p),  $e*^k$  has clock (n/k,p). In contrary, the expression  $e/^k$  produces a dataflow that is k times slower than e by only preserving the first of k successive values. It has clock (n\*k,p). Note that rate-transition operators introduce new constraints. For instance,  $e*^k$  is well-formed, iff n is a multiple of k. It is the role of the clock calculus to verify the consistency the resulting dataflows.

A current limitation of the language that will be addressed in this thesis is that the operators when and merge directly inherit their definition from LUSTRE. This implies two restrictions. First, the arguments of a when or merge must all have the same clock. Second, it is not possible to apply a rate-transition operator after applying a when.

Chapter 7 will provide an in-depth presentation of a base kernel of the PRELUDE language used throughout this thesis.

**Example 6** (Prelude). Let us discuss the implementation of Example 4 in Prelude. The language reuses a syntax similar to Lustre for most syntactic constructs. To better illustrate the language, we introduced multi-periodicity in our example. Dataflows i, c, o all have clock (10,0) (for c and o it is inferred by the clock calculus). Since j has clock (20,0), it cannot be applied directly as an argument to f with i. A rate-transition is applied first.

```

-- Clocks inferred by the compiler:

-- c: rate (10,0)

-- o: rate (10,0)

-- x: rate (10,0)

-- y: rate (10,0) on true(c)

-- z: rate (10,0) on false(c)

node main(i: rate (10,0); j: rate(20,0); k: rate (5,0); c)

returns (o)

var x, y, z;

let

x = f(i,j*^2);

y = x when true(c);

z = (k/^2) when false(c);

o = merge(c, true->y, false->z);

tel

```

## 6.5 Imperative synchronous languages

Instead of relying on a dataflow semantics, the ESTEREL language [17] relies on *control-flow semantics*. A program is composed of parallel imperative threads that communicate via deterministic signals. This paradigm is especially suited for systems that do not continuously sample their environment but instead react to individual events.

**Example 7** (Esterel). The program below illustrates the typical ABRO example. It implements an ESTEREL module with three inputs, A, B, and C, and one output O. The module implements an infinite loop. The loops restarts when signal R is present, even if the loop body didn't finish executing. In the first instruction of the loop body, the program spawns two threads that respectively wait for A and B to be present. The parallel construct terminates when all threads terminated executing. Both signals need not be present within the same reaction of the system. When both signals have been present, the module emits its output O.

```

module ABRO:

input A, B, R;

output O;

loop

[ await A || await B ];

emit O

each R

end module

```

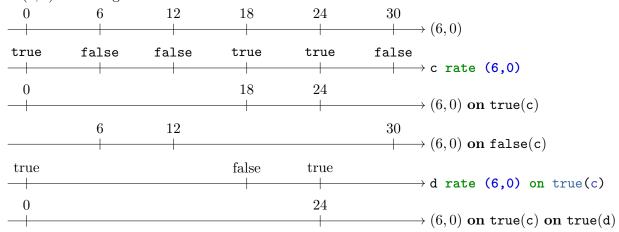

The FOREC language [46,110] is a C-like language that introduces deterministic concurrency via ESTEREL-constructs.