## Security and Trust for Wireless Integrated Circuits

Alán Rodrigo Díaz Rizo

### ▶ To cite this version:

Alán Rodrigo Díaz Rizo. Security and Trust for Wireless Integrated Circuits. Cryptography and Security [cs.CR]. Sorbonne Université - Faculté des sciences; LIP6, 2023. English. NNT: . tel-03941314v1

## HAL Id: tel-03941314 https://hal.science/tel-03941314v1

Submitted on 16 Jan 2023 (v1), last revised 31 Mar 2023 (v3)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

# SECURITY AND TRUST FOR WIRELESS INTEGRATED CIRCUITS

## présentée par ALÁN RODRIGO DÍAZ RIZO

École Doctorale Informatique, Télécommunications et Électronique (EDITE)

réalisée au laboratoire

LIP6

Presentée et soutenue publiquement le 10 janvier 2023

Devant un jury composé de :

Johanna Sepúlveda Rapporteuse

Airbus Defense and Space GmbH, Allemagne

Lilian Bossuet Rapporteur

Professeur, Université Jean Monnet, Laboratoire Hubert Curien, France

Jacques Fournier Examinateur

CEA-LETI, France

Giorgio Di Natale Président du jury, Examinateur

Directeur de Recherche au CNRS, Université Grenoble Alpes, TIMA, France

Ramón Parra Michel Invité

Directeur de Recherche au Cinvestav, Guadalajara, Mexique

Hassan Aboushady Co-direteur de thèse

Maître de conférences, Sorbonne Université, LIP6, France

Haralampos Stratigopoulos Directeur de thèse

Directeur de Recherche au CNRS, Sorbonne Université, LIP6, France

The origin of the hardware security threats is the massively globalized and outsourcing-based Integrated Circuit (IC) supply chain that we see today. The prohibitively cost of owning a first-rate semiconductor foundry forces IC design houses to go fabless and outsource their IC fabrication, assembly, and testing. Outsourcing these tasks intensifies the risk of IC piracy attacks and Hardware Trojan (HT) insertion, and both threats translate into know-how and financial losses for the IC owner. Moreover, complex Systems-on-Chip (SoCs) are built by integrating third-party Intellectual Property (IP) cores from multiple IP providers. However, SoC integrators and IP providers have an imbalanced trust relationship. While IP providers are vulnerable to IP overuse, IP cloning, and IC overproduction, SoC integrators fear integrating HT-infected IPs into their systems.

IC supply chain attackers target wireless ICs because wireless ICs have a critical role in society, government, and industry, and they exchange sensitive and valuable information through a publicly accessible medium. Therefore, this thesis focuses on wireless ICs and addresses two IC supply chain attacks: IP/IC piracy and HT insertion.

To overcome IP/IC piracy of wireless ICs, we propose a locking-based design-for-security methodology. Locking transforms the original design into a functionally equivalent one, but the functionality depends on a correct secret key, otherwise any incorrect key corrupts the functionality. Locking cannot be blindly applied to RF transceivers, to that end we show how to fine-tune state-of-the-art techniques to achieve piracy protection. In addition, we develop an RF transceiver-specific locking methodology that consists in two spatially separated mechanisms. The solution is called *SyncLock* since it locks the synchronization of the transmitter with the receiver. If a key other than the secret key is applied, synchronization and, thereby, communication fails.

To assess the security of wireless ICs, we propose an HT attack that leaks sensitive information from the transmitter within a legitimate transmission. A rogue receiver can recover the sensitive data using signal processing, while the legitimate receiver is inconspicuous and does not realize the information leaking. We demonstrate the stealthiness and robustness of the attack with measurement on a hardware platform.

L'origine des menaces de sécurité matérielle est la globalisation et l'externalisation massives de la chaîne d'approvisionnement des circuits intégrés (CI) que nous connaissons aujourd'hui. Le coût prohibitif de la possession d'une fonderie de semi-conducteurs de haut niveau oblige les sociétés de conception de circuits intégrés à opter pour une production sans usine et à externaliser la fabrication, l'assemblage et le test de leurs circuits. L'externalisation de ces tâches intensifie le risque d'attaques de piratage de CI et d'insertion de chevaux de Troie matériels (HT), et ces deux menaces se traduisent par des pertes de savoir-faire et des pertes financières pour le propriétaire du CI. En outre, les systèmes sur puce (SoC) complexes sont construits en intégrant des noyaux de propriété intellectuelle (IP cores) de tiers provenant de plusieurs fournisseurs des IP cores. Cependant, les intégrateurs de SoC et les fournisseurs des IP ont une relation de confiance déséquilibrée. Alors que les fournisseurs des IP sont vulnérables à la surutilisation de la IP, au clonage de la IP et à la surproduction des CI, les intégrateurs de SoC craignent d'intégrer des IP infectées par des HT dans leurs systèmes.

Les attaquants de la chaîne d'approvisionnement des circuits intégrés ciblent les circuits intégrés sans fil parce que ces derniers jouent un rôle essentiel dans la société, le gouvernement et l'industrie et qu'ils échangent des informations sensibles et précieuses par le biais d'un support accessible au public. Par conséquent, cette thèse se concentre sur les CI sans fil et aborde deux attaques de la chaîne d'approvisionnement des CI : le piratage IP/IC et l'insertion HT.

Pour surmonter le piratage des IP/CI des circuits intégrés sans fil, nous proposons une méthodologie de conception pour la sécurité basée sur le verrouillage. Le verrouillage transforme la conception originale en une conception fonctionnellement équivalente, mais la fonctionnalité dépend d'une clé secrète correcte, sinon toute clé incorrecte corrompt la fonctionnalité. Le verrouillage ne peut pas être appliqué aveuglément aux émetteurs-récepteurs RF. À cette fin, nous montrons comment affiner les techniques de l'état de l'art pour obtenir une protection contre le piratage. En outre, nous développons une méthodologie de verrouillage spécifique aux émetteurs-récepteurs RF qui consiste en deux mécanismes séparés spatialement. La solution est appelée *SyncLock* car elle verrouille la synchronisation de l'émetteur avec le récepteur. Si une clé autre que la clé secrète est appliquée, la synchronisation et, par conséquent, la communication échouent.

Pour évaluer la sécurité des circuits intégrés sans fil, nous proposons une attaque HT qui fait fuir des informations sensibles de l'émetteur au cours d'une transmission légitime. Un récepteur malveillant peut récupérer les données sensibles en utilisant le traitement du signal, tandis que le récepteur légitime est discret et ne se rend pas compte de la fuite d'informations. Nous démontrons la furtivité et la robustesse de l'attaque par des mesures sur une plateforme matérielle.

During the doctorate program, the following scientific articles were published:

- [1] A. R. Díaz Rizo, H. Aboushady, and H.-G. Stratigopoulos. "SyncLock: RF transceiver security using synchronization locking." In: 2022 Design, Automation and Test in Europe Conference and Exhibition (DATE). IEEE. 2022, pp. 1153–1156.

- [2] A. R. Díaz Rizo, J. Leonhard, H. Aboushady, and H.-G. Stratigopoulos. "RF Transceiver Security Against Piracy Attacks." In: *IEEE Transactions on Circuits and Systems II: Express Briefs* (2022), pp. 1–1. DOI: 10.1109/TCSII.2022.3165709.

- [3] A. R. Díaz Rizo, H. Aboushady, and H.-G. Stratigopoulos. "Anti-Piracy Design of RF Transceivers." In: *IEEE Transactions on Circuits and Systems I: Regular Papers* (2022), pp. 1–14. DOI: 10.1109/TCSI.2022.3214111.

- [4] A. R. Díaz Rizo, H. Aboushady, and H.-G. Stratigopoulos. "Leaking Wireless ICs via Hardware Trojan-Infected Synchronization." In: *IEEE Transactions on Dependable and Secure Computing* (2022), pp. 1–16. DOI: 10.1109/TDSC.2022.3218507.

The following scientific articles were published in collaboration:

- [1] J. Leonhard, N. Limaye, S. Turk, A. Sayed, A. R. Díaz Rizo, H. Aboushady, O. Sinanoglu, and H.-G. Stratigopoulos. "Digitally Assisted Mixed-Signal Circuit Security." In: *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 41.8 (2022), pp. 2449–2462. DOI: 10.1109/TCAD.2021.3111550.

- [2] A. A. Ibrahim, H. A. Mohamed, A. R. Díaz Rizo, R. Parra-Michel, and H. Aboushady. "Tunable Filtenna With DGS Loaded Resonators for a Cognitive Radio System Based on an SDR Transceiver." In: *IEEE Access* 10 (2022), pp. 32123–32131. DOI: 10.1109/ACCESS.2022.3160467.

vii

#### **PATENTS**

During the doctorate program, the following patent application was completed:

[1] "Method for securing telecommunication transceiver integrated circuit designs against piracy, counterfeiting and unauthorized use." PCT/FR2022/050437. A. R. Díaz Rizo, H. Aboushady, and H.-G. Stratigopoulos. Mar. 12, 2022.

#### AWARDS

The *SyncLock* project, presented in Chapter 5, is one of the laureates of the 2022 **i-PhD concours d'innovation**.

[1] A. R. Díaz Rizo. "SyncLock: Synchronization Locking to secure RF transceivers against piracy and unauthorized use." In: *Concours d'innovation i-PhD, BPI France*. 2022. URL: https://bit.ly/3x4NYvz.

## CONTENTS

| 1 | INT | RODUC  | CTION                                              | 1  |

|---|-----|--------|----------------------------------------------------|----|

|   | 1.1 | IC suj | pply chain vulnerabilities and threats             | 3  |

|   | 1.2 | Conse  | equences of IP/IC piracy and HT insertion          | 4  |

|   |     | 1.2.1  | A case study of a disruption scenario              | 6  |

|   | 1.3 | IC suj | pply chain threats for wireless communications ICs | 6  |

|   | 1.4 | Thesis | s objectives                                       | 7  |

|   | 1.5 | Thesis | s structure                                        | 7  |

| 2 | PRI | OR ART | ON SECURITY AND TRUST FOR WIRELESS IN-             |    |

|   | TEG | RATED  | CIRCUITS                                           | 9  |

|   | 2.1 | Hardy  | ware Trojans in RF transceivers                    | 9  |

|   |     | 2.1.1  | Hardware Trojans in ICs                            | 9  |

|   |     | 2.1.2  | Covert channel attacks for wireless ICs            | 10 |

|   |     | 2.1.3  | Attack models                                      | 10 |

|   |     | 2.1.4  | Defense mechanisms                                 | 12 |

|   | 2.2 | Anti-l | Piracy design techniques for RF transceivers       | 12 |

|   |     | 2.2.1  | Countermeasures against piracy of IP blocks        |    |

|   |     |        | and ICs                                            | 12 |

|   |     | 2.2.2  | Biasing locking                                    | 14 |

|   |     | 2.2.3  | Calibration locking                                | 14 |

|   |     | 2.2.4  | Logic locking                                      | 15 |

|   |     |        | 2.2.4.1 Evolution of thinking in logic locking     | 15 |

|   |     |        | 2.2.4.2 Generic logic locking techniques for       |    |

|   |     |        | RF transceivers                                    | 19 |

|   |     | 2.2.5  | Passive and active countermeasures                 | 19 |

|   |     | 2.2.6  | Key management                                     | 20 |

|   | 2.3 | Contr  | ibutions to the state-of-the-art                   | 20 |

|   |     | 2.3.1  | Hardware Trojans attacks in RF transceivers        | 20 |

|   |     | 2.3.2  | Anti-piracy RF transceiver design                  | 20 |

| 3 | LEA | KING   | WIRELESS ICS VIA HARDWARE TROJAN-                  |    |

|   | INF |        | SYNCHRONIZATION                                    | 23 |

|   | 3.1 | Propo  | sed attack: Theory                                 | 23 |

|   |     | 3.1.1  | Threat model                                       | 23 |

|   |     | 3.1.2  | Working principle                                  | 24 |

|   |     | 3.1.3  | Applicability                                      | 27 |

|   | 3.2 | Propo  | sed attack: Implementation                         | 28 |

|   |     | 3.2.1  | Circuit-level design                               | 28 |

|   |     | 3.2.2  | Overhead                                           | 31 |

|   |     | 3.2.3  | Rogue receiver                                     | 31 |

|   |     | 3.2.4  | Throughput of the covert channel                   | 32 |

|   | 3.3 |        | urement Results                                    | 32 |

|   |     | 3.3.1  | Hardware platform                                  | 32 |

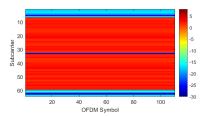

|   |             | 3.3.2          | Transparency to legitimate communication: choice of $\alpha$ |

|---|-------------|----------------|--------------------------------------------------------------|

|   |             |                | Resilience to test-based and run-time defenses .             |

|   |             | 3.3.3          |                                                              |

|   |             | 3.3.4          | Demonstrator                                                 |

|   |             | 3.3.5          | Reliability of the covert channel                            |

|   | 3.4         |                | ed prevention and detection defense mechanisms               |

|   | 3.5         |                | usion                                                        |

| 4 | RF 7        | TRANS          | CEIVERS SECURITY AGAINST PIRACY ATTACKS                      |

|   | THE         |                | LOGIC LOCKING                                                |

|   | 4.1         | RF tra         | ansceiver locking                                            |

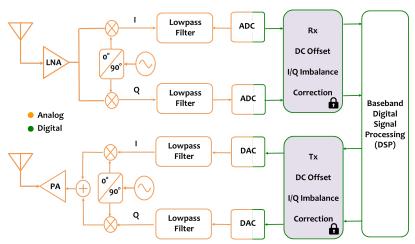

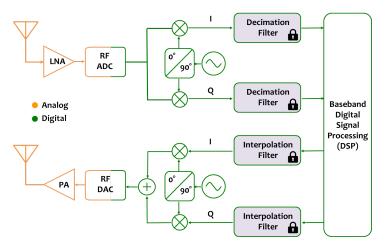

|   |             | 4.1.1          | Overview of RF transceiver architectures                     |

|   |             | 4.1.2          | Locking methodology                                          |

|   | 4.2         | Logic          | Locking with SFLL-rem                                        |

|   | 4.3         |                | rem tuned for RF transceiver locking                         |

|   | 4.4         | Securi         | ity analysis                                                 |

|   |             | 4.4.1          | Threat model                                                 |

|   |             | 4.4.2          | RF transceiver performance corruption for in-                |

|   |             |                | correct keys                                                 |

|   |             | 4.4.3          | Brute-force and optimization attacks                         |

|   |             | 4.4.4          | I/O query and structural attacks                             |

|   | 4.5         |                | rimental results                                             |

|   | <b>T</b> 'J | 4.5.1          | Hardware platform                                            |

|   |             | 4.5.2          | Measured locking efficiency                                  |

|   |             | 4.5.3          | Resiliency to attacks                                        |

|   |             |                | Locking overheads                                            |

|   | 4.6         | 4.5.4<br>Concl | usion                                                        |

| _ | •           |                |                                                              |

| 5 |             |                | CEIVER SECURITY USING SYNCHRONIZATION                        |

|   |             | CKING          | · T 1·                                                       |

|   | 5.1         |                | pronization Locking                                          |

|   |             | 5.1.1          | Principle of operation                                       |

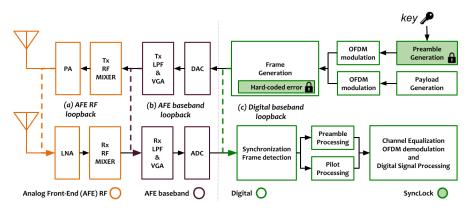

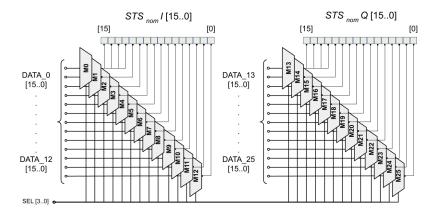

|   |             | 5.1.2          | Preamble generation                                          |

|   |             | 5.1.3          | Locking mechanism                                            |

|   |             | 5.1.4          | Choice of function $f(\cdot)$                                |

|   |             | 5.1.5          | Impact on performance                                        |

|   |             | 5.1.6          | Implementation specifics                                     |

|   |             | 5.1.7          | Key size                                                     |

|   |             | 5.1.8          | Overheads                                                    |

|   |             | 5.1.9          | Practicality                                                 |

|   |             | 5.1.10         | First SyncLock version                                       |

|   | 5.2         |                | ware platform                                                |

|   | 5.3         |                | ured SyncLock efficiency                                     |

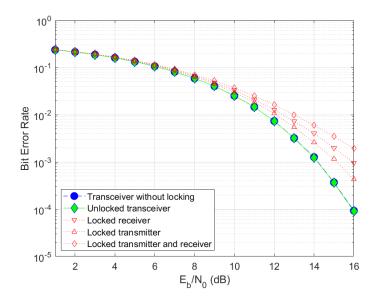

|   | 2 2         | 5.3.1          | BER performance for correct key and incorrect                |

|   |             |                | keys                                                         |

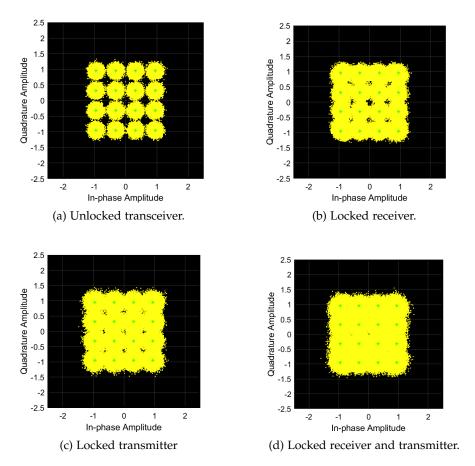

|   |             | 5.3.2          | Constellation diagrams for correct key and incorrect keys    |

|   |             | 5.3.3          |                                                              |

|   |             | ,. 1. 1        |                                                              |

|    | 5.4  | Related locking and obfuscation approaches                | 77 |

|----|------|-----------------------------------------------------------|----|

|    | 5.5  | Threat model and security analysis                        | 78 |

|    |      | 5.5.1 Threat model                                        | 78 |

|    |      | 5.5.2 Resilience to counter-attacks                       | 78 |

|    | 5.6  | Conclusion                                                | 83 |

| 5  | CON  | CLUSION AND PROSPECTIVE RESEARCH                          | 85 |

|    | 6.1  | Conclusion                                                | 85 |

|    | 6.2  | Contributions of the thesis                               | 85 |

|    | 6.3  | Prospective research on RF transceiver security and trust | 88 |

|    |      |                                                           |    |

| BI | BLIO | GRAPHY                                                    | 91 |

|    |      |                                                           |    |

## LIST OF FIGURES

| Figure 1  | Simplified life cycle trajectory of an IC. Illus-  |    |

|-----------|----------------------------------------------------|----|

|           | tration based on "The global journey of a smart-   |    |

|           | phone application processor" [1]                   | 2  |

| Figure 3  | IC supply chain threats at each stage of an IC's   |    |

|           | life cycle                                         | 4  |

| Figure 2  | IC supply chain stakeholders and their role in     |    |

|           | the supply chain.                                  | 8  |

| Figure 4  | Anti-piracy measures used in RF transceivers       |    |

|           | design and fabrication                             | 13 |

| Figure 5  | IC design flow and lifetime using locking as a     |    |

|           | countermeasure against IP/IC piracy                | 14 |

| Figure 6  | Timeline of the evolution of thinking about        |    |

|           | logic locking attacks and defenses                 | 16 |

| Figure 7  | Stripped Functionality Logic Locking (SFLL)-       |    |

|           | hd principle of operation                          | 18 |

| Figure 8  | Threat model                                       | 24 |

| Figure 9  | Physical layer Protocol Data Unit (PPDU) frame     |    |

|           | format of an OFDM IEEE 802.11 transmission.        | 25 |

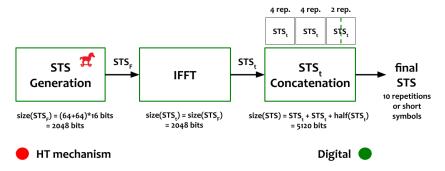

| Figure 10 | The detailed STS generation                        | 26 |

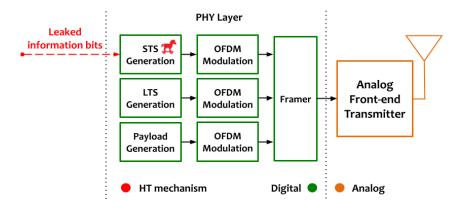

| Figure 11 | AM STS HT location within the architecture of      |    |

|           | a wireless IC, showing only part of the trans-     |    |

|           | mitter's sub-blocks.                               | 26 |

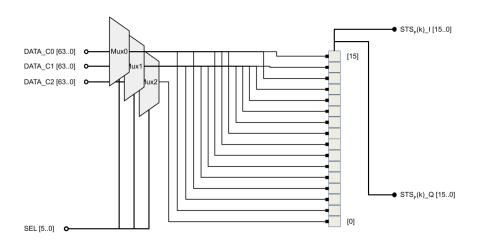

| Figure 12 | Circuit schematic of the nominal STS block         | 28 |

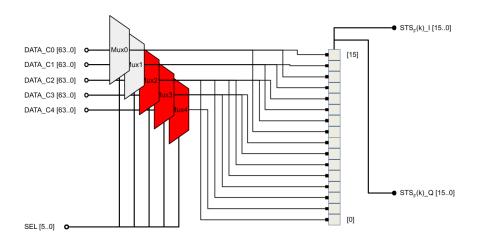

| Figure 13 | Circuit schematic of the HT-infected STS block.    | 30 |

| Figure 14 | Rogue receiver block architecture for the AM       |    |

|           | STS HT attack                                      | 32 |

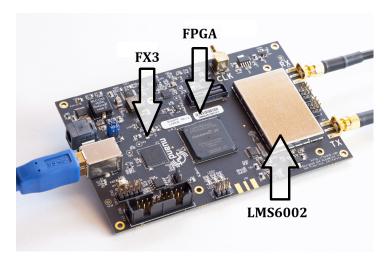

| Figure 15 | Software Defined Radio (SDR) bladeRF board         |    |

|           | from Nuand                                         | 33 |

| Figure 16 | RF transceiver test setup using the loopback       |    |

|           | mode. The Trojan horse shows the stage of the      |    |

|           | attack and the crossed-out Trojan horse show       |    |

|           | the stages of the defense mechanisms               | 33 |

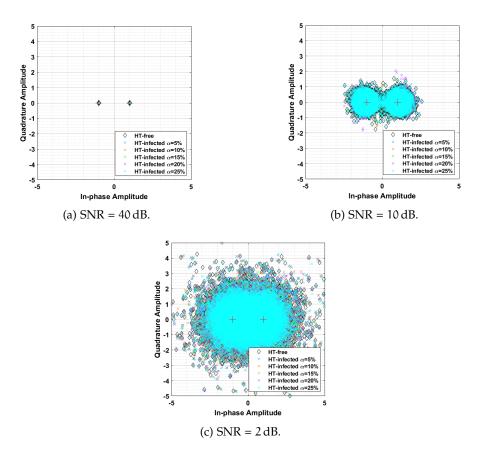

| Figure 17 | Constellation diagrams of the decoded pay-         |    |

|           | load of the received Orthogonal Frequency Di-      |    |

|           | vision Multiplexing (OFDM)-Binary Phase-Shift      |    |

|           | Keying (BPSK) signal for different Signal-to-      |    |

|           | Noise Ratio (SNR) values. The result is shown      |    |

|           | for an HT-free device and an AM STS HT-            |    |

|           | infected device using different values of $\alpha$ | 35 |

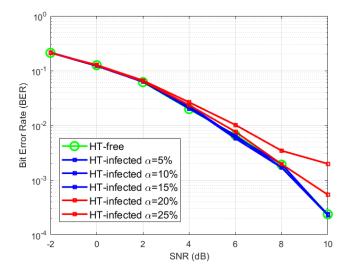

| Figure 18 | Measured Bit Error Rate (BER) of the received OFDM-BPSK signal using an HT-free device and |            |

|-----------|--------------------------------------------------------------------------------------------|------------|

|           | an Amplitude Modulation (AM) Short Training                                                |            |

|           | Sequence (STS) Hardware Trojan (HT)-infected                                               |            |

|           | device for different values of $\alpha$                                                    | 35         |

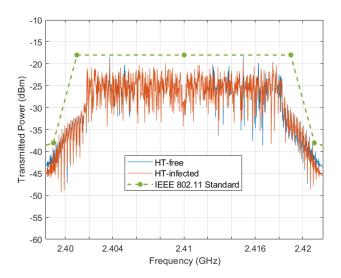

| Figure 19 | Measured Power Spectral Density (PSD) of sig-                                              | 9.         |

| 116416 19 | nals transmitted with an AM STS HT-infected                                                |            |

|           | device and an HT-free device, along with the                                               |            |

|           | IEEE 802.11 standard spectral mask specifica-                                              |            |

|           | tion[124]                                                                                  | 26         |

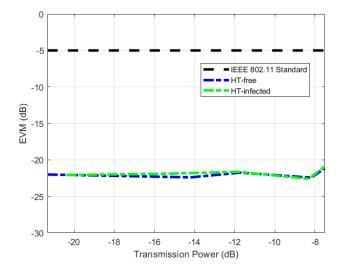

| Figure 20 |                                                                                            | 36         |

| Figure 20 | Measured Error Vector Magnitude (EVM) of the transmitted BPSK signal from an AM STS HT-    |            |

|           | infected device and an HT-free device, along                                               |            |

|           | with the IEEE 802.11 standard EVM specifica-                                               |            |

|           | tion [124]                                                                                 | 37         |

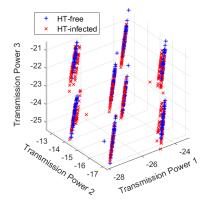

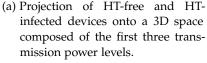

| Figure 21 | Measurement results from the Statistical Side-                                             |            |

|           | Channel Fingerprinting (SSCF) test                                                         | 37         |

| Figure 22 | Measurement results from the post-channel                                                  |            |

|           | equalization of the received payload                                                       | 39         |

| Figure 23 | Measurement results from the STS constella-                                                |            |

|           | tion test                                                                                  | 40         |

| Figure 24 | Measurement results from the single-branch                                                 |            |

|           | STS <sub>t</sub> correlation test                                                          | 41         |

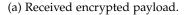

| Figure 25 | Demonstration of the AM STS HT attack: steal-                                              |            |

|           | ing the cypher key and recovering the trans-                                               |            |

|           | mitted encrypted mandrill (a.k.a baboon) image.                                            | 42         |

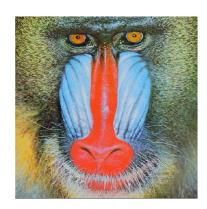

| Figure 26 | Reliability test for five different modulation                                             |            |

| O         | amplitudes $\alpha$ under different SNR scenarios                                          | 43         |

| Figure 27 | Main RF transceiver architectures showing the                                              | •          |

| ,         | most suitable digital block to lock: (a) conven-                                           |            |

|           | tional; (b) highly-digitized                                                               | 48         |

| Figure 28 | The c17 circuit example from the ISCAS bench-                                              |            |

| O         | mark suite [105, 163]                                                                      | 52         |

| Figure 29 | DC Offset and I/Q Imbalance (DCO-IQI) correc-                                              |            |

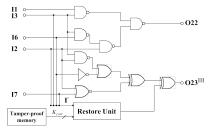

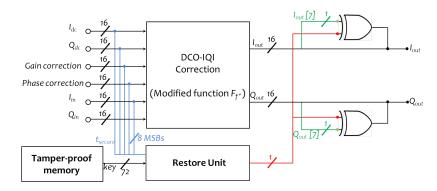

| 0 /       | tion block with the locking mechanism                                                      | 53         |

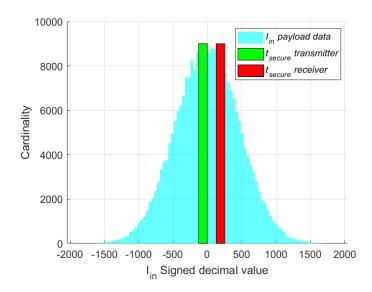

| Figure 30 | Histogram of I <sub>in</sub> payload data during the RF                                    |            |

| 0 9       | transceiver operation                                                                      | 55         |

| Figure 31 | BER measurement results for different config-                                              |            |

| )-        | urations.                                                                                  | 58         |

| Figure 32 | I/Q constellation diagrams                                                                 | 59         |

| Figure 33 | Simplified architecture of a wireless device IC                                            | );         |

| rigare 33 | with SyncLock embedded                                                                     | 62         |

| Figure 34 | Original preamble generation block with no                                                 | J2         |

| 118410 94 | locking                                                                                    | 64         |

| Figure 35 | Preamble and frame generation blocks modi-                                                 | <i>5</i> 2 |

| 116010 33 | fied for SyncLock                                                                          | 66         |

|           | iica ioi bymchoch                                                                          | JU         |

| Figure 36 | transceiver with <i>SyncLock</i> embedded using the correct and incorrect keys                                                                                                                                                                                                                                           |          |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Figure 37 |                                                                                                                                                                                                                                                                                                                          |          |  |

| Figure 38 | Amplitude values of the first 32 samples of the transmitted and received STS <sub>out</sub> for a given key <sub>trial</sub> using the Analog Front-End (AFE) baseband loopback                                                                                                                                          | 82       |  |

| LIST OF T |                                                                                                                                                                                                                                                                                                                          |          |  |

|           |                                                                                                                                                                                                                                                                                                                          |          |  |

| Table 1   | Effect of IP/IC piracy and HT insertion                                                                                                                                                                                                                                                                                  | 5        |  |

| Table 2   | HT attack models and defenses                                                                                                                                                                                                                                                                                            | 11       |  |

| Table 3   | $STS_F$ as defined in the IEEE 802.11 standard [124]                                                                                                                                                                                                                                                                     | 25       |  |

| Table 4   | Input values of MUXes                                                                                                                                                                                                                                                                                                    | 29       |  |

| Table 5   | Concatenation operation of the outputs of the MUXes.                                                                                                                                                                                                                                                                     |          |  |

| Table 6   | Subset of failing input test patterns for logic cone driving I <sub>out</sub> [7] showing only the I <sub>in</sub> seg-                                                                                                                                                                                                  | 29       |  |

| Table 7   | ment                                                                                                                                                                                                                                                                                                                     | 54<br>63 |  |

| Table 8   | Input values of MUXes in the preamble generation block                                                                                                                                                                                                                                                                   |          |  |

| Table 9   | Concatenation operation at the outputs of the MUXes                                                                                                                                                                                                                                                                      | 64<br>65 |  |

| Table 10  | Values of the main signals of the <i>SyncLock</i> locking mechanism for three key cases: incorrect zero key, random incorrect key, and correct key. The example considers a bit rotation function with $b=1$ and shows the computations during the transmission of the first 19 samples of $STS_{nom}$ for the I channel | 70       |  |

| Table 11  | HD test for the first <i>SyncLock</i> implementation in [121]                                                                                                                                                                                                                                                            | 73       |  |

| Table 12  | Comparison between the new and first <i>Syn-cLock</i> implementations                                                                                                                                                                                                                                                    | 74       |  |

| Table 13  | Comparison of different anti-piracy defenses, their scope, attack stage, and resilience to                                                                                                                                                                                                                               | , ,      |  |

|           | known counter-attacks                                                                                                                                                                                                                                                                                                    | 79       |  |

## ACRONYMS

HD Hamming Distance

| 3PIP   | Third-Party Intellectual Property Block                   |

|--------|-----------------------------------------------------------|

| A/M-S  | Analog and Mixed-Signal                                   |

| ACE    | Adaptive Channel Estimation                               |

| ADC    | Analog-to-Digital Converter                               |

| AES    | Advanced Encryption Standard                              |

| AFE    | Analog Front-End                                          |

| ALUT   | Adaptive Look-Up Table                                    |

| AM     | Amplitude Modulation                                      |

| ASIC   | Application-Specific Integrated Circuit                   |

| AWGN   | Additive White Gaussian Noise                             |

| BER    | Bit Error Rate                                            |

| BPSK   | Binary Phase-Shift Keying                                 |

| CAC    | Corrupt-And-Correct                                       |

| CFO    | Carrier Frequency Offset                                  |

| CP     | Cyclic Prefix                                             |

| CSMA/  | CA Carrier Sense Multiple Access with Collision Avoidance |

| DAC    | Digital-to-Analog Converter                               |

| DC     | Direct Current                                            |

| DCO    | DC Offset                                                 |

| DCO-IQ | QI DC Offset and I/Q Imbalance                            |

| DIP    | Distinguishing Input Pattern                              |

| DNN    | Deep Neural Network                                       |

| DSP    | Digital Signal Processing                                 |

| DRAM   | Dynamic Random-Access Memory                              |

| EDA    | Electronic Design Automation                              |

| EDF    | Electronic Disposal Facility                              |

| EVM    | Error Vector Magnitude                                    |

| EMS    | Electronic Manufacturing Services                         |

| FEC    | Forward Error Correction                                  |

| FPGA   | Field-Programmable Gate Array                             |

| GDSII  | Graphic Database System II                                |

## xvi acronyms

HT

| 111    | Tiaraware mojan                               |

|--------|-----------------------------------------------|

| IC     | Integrated Circuit                            |

| IDM    | Integrated Device Manufacturer                |

| IF     | Intermediate Frequency                        |

| IFFT   | Inverse Fast Fourier Transform                |

| IFT    | Information Flow Tracking                     |

| IoT    | Internet-of-Things                            |

| IP     | Intellectual Property                         |

| IQI    | I/Q Imbalance                                 |

| ISM    | Industrial, Scientific and Medical            |

| KPA    | Known-Plaintext Attack                        |

| LNA    | Low Noise Amplifier                           |

| Low-IF | Low Intermediate Frequency                    |

| LR-WP. | AN Low-Rate Wireless Personal Area Network    |

| LSB    | Least Significant Bit                         |

| LTS    | Long Training Sequence                        |

| MAC    | Medium Access Control                         |

| ODM    | Original Device Manufacturer                  |

| OEM    | Original Equipment Manufacturer               |

| OFDM   | Orthogonal Frequency Division Multiplexing    |

| OSAT   | Outsourced Semiconductor Assembly and Testing |

| OSI    | Open Systems Interconnection                  |

| PA     | Power Amplifier                               |

| PCA    | Principal Component Analysis                  |

| PCB    | Printed Circuit Board                         |

| PHY    | Physical Layer                                |

| PIP    | Protected Input Pattern                       |

| PLL    | Phase Locked Loop                             |

| PPA    | Power, Performance, and Area                  |

| PPDU   | Physical layer Protocol Data Unit             |

| PSD    | Power Spectral Density                        |

| PUF    | Physical Unclonable Function                  |

| QAM    | Quadrature Amplitude Modulation               |

| QPSK   | Quadrature Phase-Shift Keying                 |

| RD     | Research and Development                      |

Hardware Description Language

Hardware Trojan

#### ACRONYMS XVII

- RF Radio Frequency Rivest-Shamir-Adleman RSA RTL Register Transfer Level SDR Software Defined Radio Stripped Functionality Logic Locking SFLL SMT Satisfiability Modulo Theory **SNR** Signal-to-Noise Ratio state-of-the-art SoA System-on-Chip SoC SPS Signal Probability Skew SSCF Statistical Side-Channel Fingerprinting STS **Short Training Sequence**

- SVM Support Vector Machine

TPM Tamper-Proof Memory

- WLAN Wireless Local Area Network WPAN Wireless Personal Area Network

- Zero-IF Zero Intermediate Frequency

INTRODUCTION

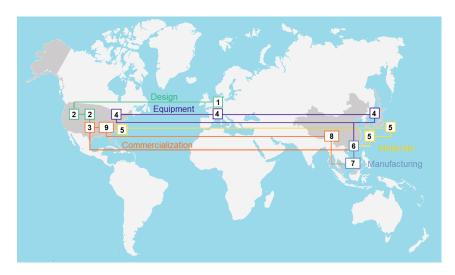

The semiconductor supply chain is massively globalized. Electronic device makers, usually referred to as Original Equipment Manufacturers (OEMs), typically design their products and decide which components to use from which suppliers. OEMs often have their headquarters in one country, their team of design engineers in another country, and have their devices manufactured in a different country or in many different countries. The companies in charge of the various manufacturing tasks are referred to as Original Device Manufacturers (ODMs) or Electronic Manufacturing Services (EMS) [1]. This globalization of the supply chain, can be divided into five specializations: design, equipment, materials, manufacturing, and commercialization. To illustrate the interdependence of these specialization tasks, Fig. 1 shows the global journey of a smartphone application processor [1] having an Intellectual Property (IP) core, or IP block1, of a European design house as a building block. The journey is as follows:

- 1. A European semiconductor company designs and licenses an IP block to a system integrator, also known as a System-on-Chip (SoC)<sup>2</sup> integrator, in the United States of America (U.S.).

- 2. The SoC integrator, which is a *fabless*<sup>3</sup> U.S. company, uses advanced Electronic Design Automation (EDA) tools for chip design to integrate the European IP block, along with other Third-Party Intellectual Property Blocks (3PIPs), and designs the SoC.

- 3. A U.S. smartphone OEM selects the SoC to be embedded in its new smartphone.

- 4. Advanced manufacturing equipment is developed by companies in the U.S., Europe, and Japan, relying on decades of Research and Development (RD) efforts.

- 5. Materials for the semiconductor industry are mined, refined, polished and shipped from the U.S., Japan, and South Korea.

<sup>1</sup> A semiconductor Intellectual Property core, or IP block, is a reusable circuit, cell, or Integrated Circuit (IC) layout design that is the intellectual property of one party.

<sup>2</sup> A system on a chip is a complete system integrated on a single IC consisting of several IP blocks, such as processors, memories, power management units, and peripheral interfaces, to perform the intended function.

<sup>3</sup> A fabless company designs and commercializes ICs while outsourcing their fabrication to a specialized manufacturer called a semiconductor foundry.

- 6. A semiconductor foundry in Taiwan receives the SoC design and materials, then uses the manufacturing equipment to imprint polysilicon wafers with an array of Integrated Circuits (ICs).

- 7. The individual chips are separated, packaged, and tested by an Outsourced Semiconductor Assembly and Testing (OSAT) in Malaysia.

- 8. The fabricated chip is shipped to the smartphone OEM's assembly partner in China for mounting on a Printed Circuit Board (PCB) inside the smartphone.

- 9. The smartphone is sold to an end-user in the U.S.

- 10. After some time of use, the smartphone is discarded.

Figure 1: Simplified life cycle trajectory of an IC. Illustration based on "The global journey of a smartphone application processor" [1].

In contrast to the *fabless model* presented in the previous example, during the early decades of the semiconductor industry, the Integrated Device Manufacturer (IDM) model was prevalent. An IDM is a semiconductor company that designs, manufactures, and commercializes its own ICs. However, the rapid growth in capital expenditure and investment to produce state-of-the-art (SoA) ICs created the need for scale and specialization, which resulted in the advent of the fabless model. In 2020, 33% of the global IC sales where from fabless companies [1], and even IDMs rely on semiconductor foundries and OSATs for a portion of the manufacturing, assembly, packaging, and testing needs [1]. Europe has fallen behind in semiconductor manufacturing, declining from 24% of global production capacity in 2000 to 8% in 2022 [2].

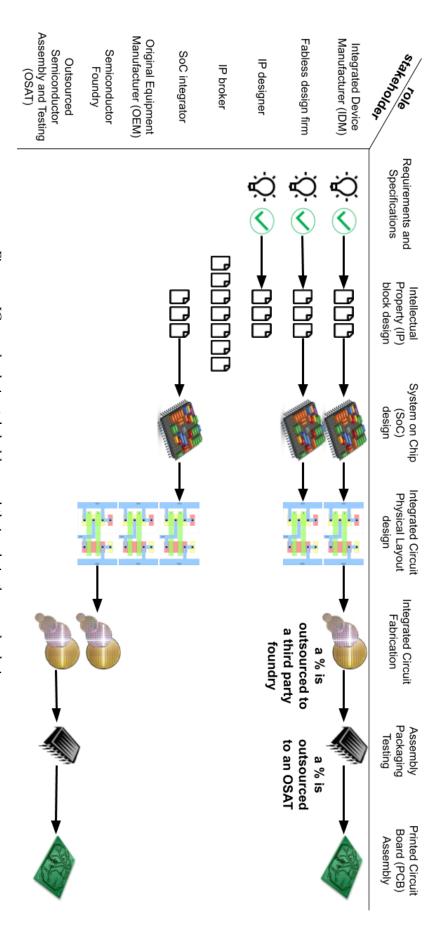

The main stakeholders in the IC supply chain can be identified from the example presented previously and illustrated in Fig. 1. Their role in the supply chain is summarized in Fig. 2. For instance, a fabless design firm may have four roles: (1) establish the requirements and specifications of an IC, (2) develop IP blocks, (3) integrate their IP blocks and likely 3PIP blocks into an SoC, and (4) design the layout of the IC. However, the rest of the tasks in the IC supply chain are outsourced to other stakeholders by the fabless design firm. An IP broker only intervenes in the storage and trading of IP blocks and SoCs. An example of an IP broker is Design & Reuse [3], a French company dedicated to IP and SoCs dissemination. A notable example of an OEM is Apple, a fabless outsourcing-based company.

This globalized, fabless, and outsourcing-based model which characterizes the current IC supply chain and life cycle, raises vulnerabilities and boosts IC supply chain attacks, i.e., the possibility of cloning and tampering ICs [4].

#### 1.1 IC SUPPLY CHAIN VULNERABILITIES AND THREATS

Threats to the IC supply chain consist of counterfeiting<sup>4</sup> and tampering.

To accord the terminology to the SoA, we defined the IC supply chain threats, a.k.a. IC supply chain attacks, as follows:

- 1. Cloning: unauthorized copying of an IP/IC.

- 2. Overproducing (a.k.a. overbuilding): out-of-contract production of ICs by the authorized contractor.

- 3. Remarking: indicating an out-of-specification or defective IC as working.

- 4. Recycling: reintroducing a used IC as new.

- 5. Tampering (a.k.a. Hardware Trojan (HT) insertion): malicious modification of the hardware of an IP block or IC performed by an adversary.

- 6. Unauthorized use: utilization of an IP/IC in an unauthorized application or sector.

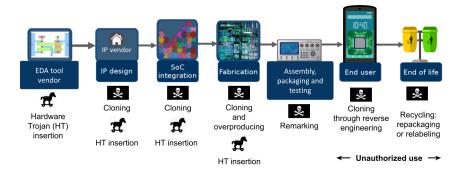

Cloning, overproducing, remarking, and recycling are known as piracy attacks. Tampered (HT-infected) IP/ICs can potentially leak valuable information to an eavesdropper, cause performance degradation, or completely deny service. The tampering and piracy threats associated to each stage of the IC life cycle are illustrate in Fig. 3.

<sup>4</sup> The U.S. department of Commerce defined a counterfeit component as the one that is an unauthorized copy; imitation; does not conform to original design, model, and/or performance standards; is produced by unauthorized contractors; is an off-specification, defective, or used IC sold as new or working; or has incorrect or false markings and/or documentation [5].

Figure 3: IC supply chain threats at each stage of an IC's life cycle.

HT insertion may originate from a malicious EDA tool. It may also be part of the design, implemented during SoC integration, or introduced into the IC design empty spaces by a rogue foundry.

Cloning may be carried out internally by a rogue employee, externally by an SoC integrator who acquires a license for using a 3PIP block, or by a malicious foundry. Specifically, the blueprint, i.e., the Graphic Database System II (GDSII) file of the IP/IC, is given away and, thereby, such a malicious entity can easily clone the IP/IC and illegitimately produce cloned counterfeits without the consent or knowledge of the IP/IC owner. Cloning may also be carried out by a malicious end-user who has capabilities for reverse-engineering the chip to extract its netlist [6, 7]. Nowadays there are increased capabilities for performing reverse-engineering of chips to extract the design netlist and other technology secrets [8]. In addition, a malicious foundry may overproduce chips beyond the number agreed on in the contract with the IP/IC owner and sell them illegitimately. Remarking may be performed by OSATs, and recycling may be done at an Electronic Disposal Facility (EDF). Repackaging (a.k.a. salvaging) is recycling an IC with a new package and a new label, and relabeling is recycling an IC with a used package but a new label. Although recycling ICs from discarded equipment may seem commendable, these chips can have problems with electromigration of metals, reliability, and short life span.

#### 1.2 CONSEQUENCES OF IP/IC PIRACY AND HT INSERTION

IP/IC piracy and HT insertion effects and consequences on government, industry, and society as a whole, are resumed in Table 1.

Piracy of ICs has been a major security threat since the past few decades. For instance, in 2011, VisionTech Components sold counterfeit semiconductor chips to more than 1,100 customers in every sector of the electronics industry, including the military [9]. Among the companies that claimed damages for chip fraud are major chip companies such as Analog Devices and Raytheon [9].

With respect to governments and consumers, in a report [10] out in march 2022, the European Union's law enforcement agency Europol highlighted the risks posed by counterfeit semiconductors to critical infrastructure as well as to people's private devices. The U.S. Department of Homeland Security tied counterfeit components to national security in a January 2022 report [5] about the semiconductor supply chain. Concerning the industry, cloning and overproducing result in know-how and financial losses for the IP/IC owner. IP piracy issues alone incur annual losses up to \$4 billion for the semiconductor industry [11]. In addition to the loss of revenue suffered by counterfeit victims, estimated at \$100 billion annually for the entire electronics industry, due to counterfeit semiconductors, end users and the systems that comprise them can suffer premature or critical failures [5]. The U.S. Semiconductor Industry Association testified in 2011 that it estimated that counterfeiting costs U.S. more than \$7.5 billion per year, translating into nearly 11,000 jobs lost [5]. The commercialization of HT-infected ICs could permanently damage a company's reputation and trust. In addition, an IC leaking users' private information puts security and respect for privacy at risk. A HT could be a time bomb that can be triggered under specific conditions controlled by the attacker, leading in a complete denial-of-service while the chip is in the field.

Table 1: Effect of IP/IC piracy and HT insertion.

| GOVERNMENT INDUSTRY CONS                                                                                                                                                                                                                                                                         | SUMER/SOCIETY                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| terfeit or tampered chips are used in critical infrastructure or defense - Lost tax revenue due to illegal sales of counterfeit parts - Costs of law enforcement - Lost of know-how ucts due reliability pan of content or defense - Costs to mitigate the risk feit parts application if a tamp | o replace failed prod-<br>to lower quality and<br>y and shorter lifes-<br>punterfeit parts<br>concerns if counter-<br>s are used in critical<br>ons, i.e., automotive<br>and safety concerns<br>pered IC leaks users' |

Furthermore, considering that the IC supply chain is complex and not necessarily each actor in the chain knows and controls all the stakeholders involved, the infiltration of counterfeit or tampered ICs affects more than one actor. Therefore, its negative effect is difficult to fully assess.

Security methods deployed in the industry for identifying counterfeit and/or HT-infected ICs relying on human intervention are time-consuming, increasing the time to market of the ICs. Moreover, there are costly to carry out in volume, often cannot detect all counterfeits, and require a high degree of expertise [5]. In addition, because the IC supply chain involves several stages, it is not easy to verify that all of these security methods are carried out from end-to-end. Thus, there is

an urgent need for attack-resistant design methods which can protect an IP/IC against potential piracy attacks occurring at any point in the supply chain, as well as HT detection, prevention, and deactivation mechanisms.

#### 1.2.1 A case study of a disruption scenario

The Covid-19 pandemic disrupted the IC supply from China and spread to other parts of the world. That disruption showed that the semiconductor supply chain is not resilient, and a failure can cause multi-millions losses due to chip shortages [12, 13]. The manufacturing lead time for ICs has increased since the pandemic and even at the date of this work, OEMs and IDMS must wait longer to have their designs manufactured [14–16]. Moreover, the scarcity of semiconductors created a huge demand that could not be met and a growing desperation on the part of the companies as they saw multi-million losses due to the shutdown of their production lines. In such a disruptive scenario, many companies were and are willing to buy (fabricate) the necessary components from (with) unreliable parties. Thus flooding the market with counterfeit chips [17], or further risking the intellectual property of their designs.

ERAI is an online counterfeit electronics database. ERAI monitors, investigates, and reports issues affecting the global electronics supply chain [18]. Since 2019 more ERAI members from automotive and similar industries are requesting ERAI for a counterfeit mitigation solution. Through ERAI, fake electronics can be anonymously reported, which provides tools to its members to avoid counterfeit components. "In 2020, about 80 percent of those reported devices were reported for the very first time that year" [19].

The counterfeit chips resulting from the semiconductor crisis, since the beginning of the pandemic, added to the counterfeits that were already on the rise. Their infiltration into the supply chain causes damage that is difficult to fully quantify as counterfeits affect the products in which they are embedded, the companies that sell them, and the millions of users who use them.

## 1.3 IC SUPPLY CHAIN THREATS FOR WIRELESS COMMUNICATIONS ICS

Wireless communication devices are ubiquitous. A Radio Frequency (RF) transceiver is a fundamental building block in an electronic system that allows it to communicate with another device wirelessly. RF transceivers are present in all devices with wireless connectivity. The wireless connectivity sector can be classified by technology type (Wi-Fi, Bluetooth, NFC, Zigbee, LTE, LoRa, SigFox, 2G, 3G, LTE, 4G, 5G, etc.), by end-user (Internet-of-Things (IoT), wearables, consumer elec-

tronics, healthcare), and by application (aerospace, satellite, automotive, mobile communication, etc.).

With the rise of IoT and 5G, hundreds of new markets are expected to emerge. For example, the number of IoT devices is forecasted to surpass 25.4 billion in 2030 [20]. Moreover, the wireless connectivity sector is one of Europe's strategic industries [2]. Therefore, its development and security is very important to achieve digital sovereignty.

In addition to their widespread use, IC supply chain attackers target wireless integrated circuits for two main reasons: they have a critical role in society, government, and industry; they exchange sensitive and valuable information through a publicly accessible medium. For these reasons, this thesis focuses on securing RF transceiver ICs.

#### 1.4 THESIS OBJECTIVES

The thesis has two primary objectives:

- 1. To investigate and analyze the attack surface for HT insertion into RF transceiver ICs.

- 2. To propose novel solutions to protect the design of RF transceivers and ascertain their security against piracy attempts.

#### 1.5 THESIS STRUCTURE

The overall structure of the thesis takes the form of six chapters, including this introduction. The rest of the thesis is structured as follows. Chapter 2 examines the prior art on security and trust for integrated circuits. The chapter is composed of two sections, the previous work on HTs and the evolution of thinking in anti-piracy design techniques, focusing on RF transceivers. Chapter 3 presents a new HT attack for RF transceivers aiming at leaking sensitive information through a covert channel. Chapter 4 provides a methodology to secure RF transceivers against IP/IC piracy by leveraging a SoA logic locking technique. In Chapter 5, we present *SyncLock*, a domain-specific anti-piracy design technique to secure RF transceivers. Chapter 6 concludes the thesis and discusses prospective investigations and developments on RF transceiver security and trust.

Figure 2: IC supply chain stakeholders and their role in the supply chain.

# PRIOR ART ON SECURITY AND TRUST FOR WIRELESS INTEGRATED CIRCUITS

This chapter gives an overview of the prior art on security and trust techniques to protect IP blocks and ICs against IC supply chain attacks. The chapter is composed of two sections. Section 2.1 deals with the prior art on HT insertion in the context of RF transceivers, and Section 2.2 focuses on the SoA anti-piracy design techniques for RF transceivers.

#### 2.1 HARDWARE TROJANS IN RF TRANSCEIVERS

In this section, we present the prior art on HTs. We introduce different models of insertion and attacks, as well as the defense mechanisms to detect or prevent HTs. The scope of the thesis focuses on the context of RF transceivers, their main threats, and countermeasures.

#### 2.1.1 Hardware Trojans in ICs

A HT is a malicious modification of the hardware performed by an adversary [21–26]. HTs are classified according to the insertion phase (i.e., design, fabrication, assembly, post-silicon, etc.), insertion level (i.e., Register Transfer Level (RTL), gate-level, transistor-level, layout, etc.), location on die (i.e., processor, memory, analog, etc.), triggering mechanism (i.e., always-on, activation after some operation time elapses, activation when some rare input condition is met), and payload or effect (i.e., performance degradation, denial-of-service, or leaking of sensitive data such as a cipher key).

From the attacker's perspective, the goal is to design a small footprint and stealthy HT that evades detection. From the defender's perspective, the goal is to prevent HT insertion or detect the presence of a HT, for example with reverse engineering, post-manufacturing testing, or during run-time.

Numerous HT designs have been proposed in the literature, the vast majority of which target digital ICs. The simplest HT is a combinational circuit that monitors a set of nodes to generate a trigger on the simultaneous occurrence of rare node conditions and, subsequently, once the trigger is activated, the payload is simply flipping the value of another node. Another common HT design are the sequential HTs which are triggered with a sequence of conditions and not with a specific state or condition like the combinational HTs. More complex HTs include silicon wearout mechanisms [27], hidden side-

channels [28], changing dopant polarity in active areas of transistors [29], siphoning charge from victim wires known as A2 attack [30, 31], activating a row in Dynamic Random-Access Memory (DRAM) to corrupt data in nearby rows known as rowhammer attack [32], exploiting capacitive crosstalk effects [33], leveraging characteristics of emerging Non-Volatile Memories (NVMs) [34], etc.

For analog ICs, HT insertion is more challenging because analog performance is sensitive to circuit alterations, thus a HT-infected analog IC is likely not to pass testing, and also because analog layouts have few components, thus a HT can be easily detected via reverse engineering and layout inspection. Proposed HT designs for analog ICs include bringing the circuit into an undesired state or operation mode [35–39] and digital-to-analog HTs that exploit the on-chip test infrastructure [40–42]. In the latter scenario, the HT resides inside a digital IP block where it is triggered. The generated payload is transferred to the victim analog IP via the common test access mechanism and is applied to it via its built-in self-test or programming interface to the test access mechanism. There exist also analog HT designs to infect digital ICs, such as the A2 attack [30, 31]. The A2 attack can be used to infect the digital section of a mixed-signal IC, but it has not been demonstrated inside the analog section.

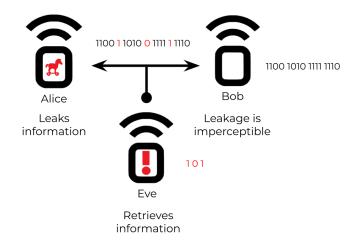

#### 2.1.2 Covert channel attacks for wireless ICs

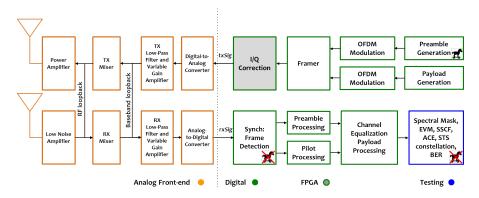

Targeting RF transceivers, a covert channel is a HT attack in wireless ICs aiming at leaking sensitive information from the transmitter within a legitimate signal transmission. A rogue receiver can listen to the transmission to recover the sensitive information, while the legitimate receiver is inconspicuous and does not realize the information leaking. Several studies have demonstrated this type of HT attack. The HT can be embedded within the Medium Access Control (MAC) protocol [43], within the digital baseband Physical Layer (PHY) [44–48], or its payload mechanism can partially act upon the Analog Front-End (AFE) [49–53]. In parallel, these studies propose defenses for detecting the HT attack at test time or during run-time. Table 2 provides a concise summary of existing attack models and corresponding defenses. These are explained below in more detail.

#### 2.1.3 Attack models

In [43], a spyware is demonstrated exploiting the timing channel resulting from inter-arrival times of the legitimate transmitted packets. It can be embedded within any MAC protocol that avoids collision in packet re-transmissions by using an exponential back-off rule, i.e., the Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) protocol. In [44], covert messages are hidden within a "dirty" pay-

Table 2: HT attack models and defenses.

| REF.                    | ATTACK MODEL                                                                                                          | DEFENSE MECHANISM                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| [43]                    | Modifies the MAC layer CSMA/CA protocol to leak data into the timings of the transmitted packet sequence.             | Evades statistical tests that detect covert timing channels. No other defense is studied. |

| [44]                    | Encodes leaked data on the I/Q mapping and hides the encoding by introducing imperfections to the transmitted signal. | Certain tests, such as EVM, show a distinguishing behavior compared to HT-free operation. |

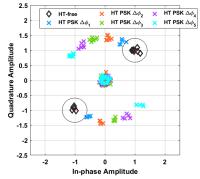

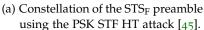

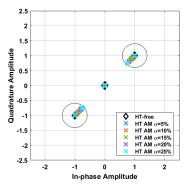

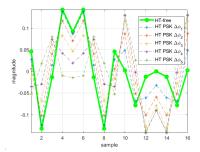

| [45]-1                  | Leaks data by introducing an additional phase shift into all STS symbols of the preamble.                             | Analysis of the preamble constellation.                                                   |

| [45]-2                  | Leaks data by introducing artificial CFO into each OFDM symbol.                                                       | Analysis of CFO changes over time.                                                        |

| [45]-3,<br>[46]         | Leaks data in extra camouflage subcarriers added to the OFDM signal.                                                  | Decode the signal field to determine if the number of subcarriers is correct.             |

| [45]-4,<br>[47]         | Leaks data into parts of the OFDM CP.                                                                                 | Compare the last 16 samples of an OFDM symbol with its CP; spectrum analysis.             |

| [48]                    | Leaks data by substituting some legitimate data in the FEC block.                                                     | Channel noise profiling.                                                                  |

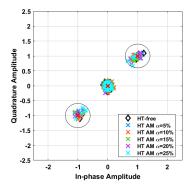

| [49 <del>-</del><br>51] | Leaks data by modulating amplitude and/or frequency of transmitted signal.                                            | SSCF; ACE; Use hardware dithering as a prevention mechanism [54].                         |

| [52]                    | Leaks data using spread spectrum techniques.                                                                          | Spectral analysis.                                                                        |

| [53]                    | Leaks data into artificial controlled impairments.                                                                    | No defenses are studied.                                                                  |

| HT in Ch. 3 [55]        | Leaks data through amplitude modulation of some subcarriers in the STS of the preamble.                               | Evades any known defense for $\alpha <\! 15\%.$                                           |

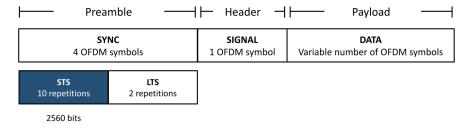

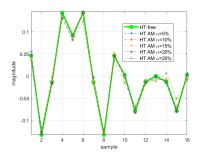

load data constellation by taking advantage of the I/Q impairments and noisy channel conditions. In [45], four covert channel schemes are shown for the PHY of the IEEE 802.11. These include leaking data by: (a) introducing an additional phase shift in the Short Training Sequence (STS) symbols of the preamble; (b) introducing an artificial Carrier Frequency Offset (CFO) into each Orthogonal Frequency Division Multiplexing (OFDM) symbol; (c) introducing camouflaged subcarriers, i.e., extra subcarriers to those of the standard, into the OFDM signal; and (d) by replacement of the OFDM Cyclic Prefix (CP). In [48], the attack is staged in the Forward Error Correction (FEC) block, exploiting the fact that the FEC block offers more error correcting capabilities than the channel needs. In [49–51], the idea is to exploit the margins that exist between the operating point of the circuit and the boundaries defined by the circuit and communication standard specifications. In particular, the HT performs minute modifications in the parameters of the transmitted signal, such as amplitude and frequency, to leak sensitive information from the tampered device. Two HT payload mechanisms are shown in [51], one that uses a single pole double throw switch and a pair of resistors to alter the input termination impedance of the power amplifier, and another one that

reprograms the gain stages. In [52], it is proposed to use spread spectrum techniques to hide an unauthorized transmission signal within the legitimate signal below the noise level. In [53], first feasible transmitter impairments that do not affect appreciably Bit Error Rate (BER) are determined, then leaked data are mapped on such artificially introduced impairments. The adversary learns these impairments and extracts the leaked data using deep learning.

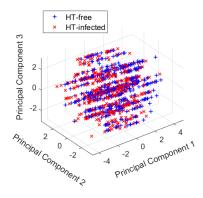

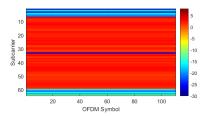

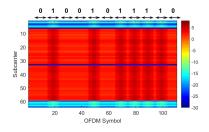

#### 2.1.4 Defense mechanisms

Most of the aforementioned studies also study resilience to various defenses, oftentimes finding a working defense. Defenses range from standard measurements, i.e., measuring SNR, EVM or Bit Error Rate (BER); examining compliance with the spectral mask specifications; analyzing I/Q constellation diagrams, etc., to more elaborate techniques such as Statistical Side-Channel Fingerprinting (SSCF) [50], Adaptive Channel Estimation (ACE) [51], and channel noise profiling. SSCF consists in training a one-class classifier in a feature space composed of parametric measurements, e.g., transmitted power from golden HTfree devices. The HT-infected devices have a feature vector that lies outside the classification boundary and, thereby, can be distinguished from HT-free devices. The ACE defense leverages the slow-fading characteristics of indoor communication channels to distinguish between channel impairments and HT activity. In [51], it is claimed that the ACE defense is successful in detecting any HT regardless of the attack specifics. There exist also defenses that are specific to the attack model focusing on the particular encoding of the leaked data. Finally, it is possible to design a proactive defense mechanism that challenges the operation principle of the HT with the aim to neutralize it. An example is the hardware dithering technique proposed in [54].

#### 2.2 ANTI-PIRACY DESIGN TECHNIQUES FOR RF TRANSCEIVERS

The IP of IC design is protected under patent law in various countries. IP theft is a recurring industrial problem being pursued in the court [56]. However, this deterrent measure does not prevent IP theft or unauthorized use and often involves lengthy litigation to penalize the infringer. Therefore a technological countermeasure against piracy and unauthorized use is needed. In this Section, we present the SoA design techniques to prevent IP/IC piracy.

#### 2.2.1 Countermeasures against piracy of IP blocks and ICs

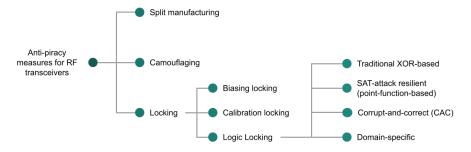

A classification of anti-piracy measures used in RF transceivers design and fabrication is illustrated in Fig. 4. The three major cate-

gories are: (a) split manufacturing, (b) camouflaging, and (c) locking. Unlike split manufacturing and camouflaging, locking offers end-to-end protection against all potential piracy threat scenarios. The DARPA¹ agency has chosen locking as a defense mechanism to prevent "four fundamental silicon security vulnerabilities: side channel attacks, hardware Trojans, reverse engineering, and supply chain attacks, such as counterfeiting, recycling, re-marking, cloning, and over-production" [57]. Locking has also been integrated into the Mentor Graphics framework [58].

Figure 4: Anti-piracy measures used in RF transceivers design and fabrication.

Split manufacturing divides the fabrication process of ICs between two foundries [59]. An untrusted high-end foundry fabricates the front-end of line layers (transistors and lower metal layers), and a trusted low-end foundry manufactures the back-end of line layers (higher metal layers). This approach prevents overproduction and cloning from an untrusted foundry [60]. Split manufacturing has been demonstrated for RF designs in [61]. In [61], the authors claimed that split manufacturing may be more suitable for RF designs than for digital circuits, however, split manufacturing only protects against one piracy entity, i.e., an untrusted foundry.

The purpose of camouflaging is to obfuscate the hardware to protect the IC against reverse engineering [62]. The gates of the camouflaged designs are similar but implement different Boolean functions [63]. Camouflaging ideas for Analog and Mixed-Signal (A/M-S) ICs include multi-threshold transistor design [64] and obfuscating the geometry of layout components [65]. However, camouflaging lacks protection against other piracy attacks, like cloning by an SoC integrator or an end-user, overproducing, remarking, and recycling.

Locking, illustrated in Fig. 5, is performed by the designer and consists in embedding a lock mechanism inside the IP/IC. The lock mechanism is a circuit that is mingled with the original circuit and controlled by a key. The key is typically in the form of a digital bit-string. The lock mechanism is transparent to the IP/IC such that

<sup>1</sup> The Defense Advanced Research Projects Agency (DARPA) is a research and development agency of the United States Department of Defense responsible for the development of emerging technologies for use by the military.

upon application of the correct key the nominal functionality is restored. However, applying an incorrect key corrupts the functionality. IP/IC locking protects an IP/IC against potential attackers located anywhere in the supply chain, as well as against malicious end-users. It can also protect against recycling facilities as long as the key can be reloaded every time the IC is powered on.

Figure 5: IC design flow and lifetime using locking as a countermeasure against IP/IC piracy.

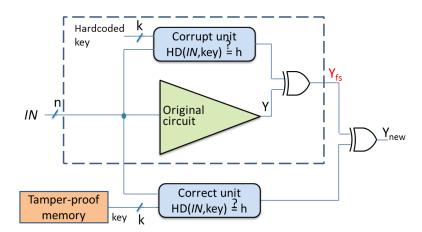

IP/IC locking is considered as the strongest countermeasure against IP/IC piracy [66]. Therefore, we thoroughly studied this design technique and present, in the following subsections, the three main defenses used for the protection of A/M-S and RF transceiver ICs. The three locking defenses are (1) biasing locking, (2) calibration locking, and (3) logic locking.

#### 2.2.2 Biasing locking

For locking analog blocks the existing technique is biasing locking. Biasing locking aims at controlling the bias generation with the key. Unless the correct key is provided, the analog block is incorrectly biased, meaning that the quiescent point of transistors is not the desired one, resulting in performance degradation or malfunction. For RF transceivers, one can perform biasing locking in blocks of the Analog Front-End (AFE), i.e., Low Noise Amplifier (LNA), Power Amplifier (PA), Phase Locked Loop (PLL), data converters, etc. Several embodiments of biasing locking exist, including obfuscating the geometry of a bias transistor [67, 68], designing key-controlled current mirrors [69], and replacing the biasing circuit with an alternative key-controlled bias generator, e.g., based on an on-chip neural network [70] or a programmable memristor crossbar [71]. Biasing locking may result in imprecise or unstable biasing. Besides, recently counterattacks were proposed based on Satisfiability Modulo Theory (SMT) [72] and optimization [73, 74] that break this type of defense.

#### 2.2.3 Calibration locking

Calibration locking achieves system-level locking making the compensation of process variations or adaptation to different operation modes key-dependent. Techniques in this category include locking the digital section of the calibration loop [75], treating digital programmability as a natural secret key [76–78], and making the calibration range key-dependent [79]. Secure calibration locking requires that the calibration algorithm be complex enough to be devised or redesigned in hardware by the attacker. Such an assumption does not always hold.

#### 2.2.4 Logic locking

Logic locking adds supplementary logic to a circuit design to protect the original logic. Logic Locking incurs a justifiable yet non-negligible area and power overhead. The first logic locking, a.k.a. logic encryption, technique was originally proposed for digital circuits [80]. Since then, several logic locking defenses were proposed aiming at reducing Power, Performance, and Area (PPA) penalties, increasing corruption for invalid keys, and circumventing counterattacks that were developed in the meantime aiming at exposing security vulnerabilities of logic locking, i.e., finding the secret key with reasonable effort or identifying and subsequently removing the lock [66]. There is an ongoing "ping-pong" game between logic locking defenses and counterattacks. Every newly introduced logic locking technique is considered secure until shortly after a counterattack heuristic breaks it.

Logic locking had also be used in other applications fields, e.g., for upgrading processors [81], or for locking the bitstream to configure and program a Field-Programmable Gate Array (FPGA) [82].

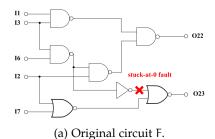

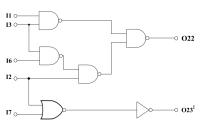

### 2.2.4.1 Evolution of thinking in logic locking

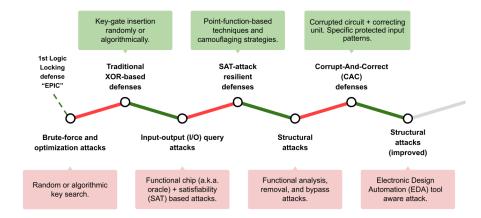

A timeline illustrating the evolution of thinking about logic locking protection techniques and counterattacks in the SoA is presented in Fig. 6. We have grouped **Logic Locking Defenses** into three main sets, traditional XOR-based, SAT-attack resilient, and Corrupt-And-Correct (CAC) defenses. The **Logic Locking Attacks** are also grouped into three major sets, brute-force and optimization, input-output query, and structural attacks. This section presents a walk-through of the multiple attacks and defenses developed using logical locking.

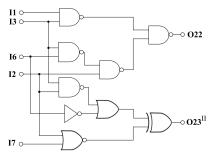

1. Traditional XOR-based defenses: The first logic locking defense, called "EPIC", inserts XOR/XNOR key-gates into the design in a random fashion. A key-gate interrupts a digital line controlling its value with a key-bit. The objective is to guarantee that incorrect keys will produce incorrect output [80]. In a brute-force or optimization attack, the attacker searches in the key space either randomly in a brute-force manner or more efficiently by employing an optimization algorithm hoping to find a key that produces correct outputs. Traditional XOR-based defenses protect against these attacks by setting a larger number of

Figure 6: Timeline of the evolution of thinking about logic locking attacks and defenses.

bits for the key size, thus increasing the search space. Then, the first logic locking specific attack, the sensitization attack, broke the EPIC defense by employing a functional IC (a.k.a an oracle) and querying the locked IC with specific input patterns that propagate key values to the outputs [83].

Since EPIC failed, other traditional techniques, consisting of key-gates insertion [80, 83–88], followed-up targeting high output corruption for incorrect keys [84], resilience to sensitizing the key-bits to the output [86], optimal positioning of the key-gates [85], reducing PPA overheads [87], or thwarting the ability of the attacker to learn the key-bit value from the key-gate type [88]. In all these XOR-based techniques, key-gates are inserted randomly or algorithmically.

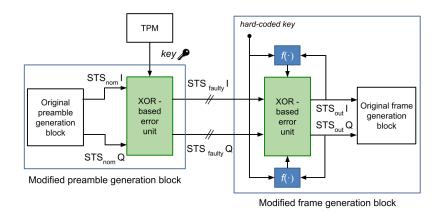

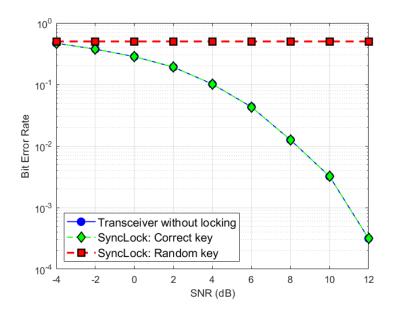

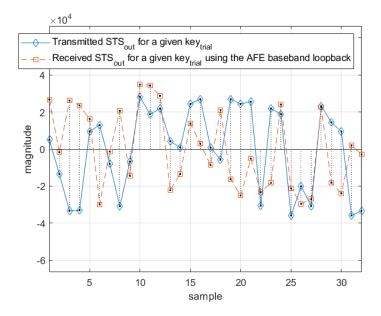

2. **Input-output (I/O) query attacks:** XOR-based defenses are efficient against brute-force and optimization attacks, but vulnerable to I/O query attacks, like the sensitization attack [83]. Attacks based on Boolean satisfiability (SAT) [89] belong to the I/O query attacks category and were shown to be very powerful, breaking traditional logic locking approaches [80, 83, 84, 86, 87] by recovering the key with little effort.