## Improving the reliability of heterogeneous multicore architecture for intelligent transportation systems

Fabien Bouquillon

#### ▶ To cite this version:

Fabien Bouquillon. Improving the reliability of heterogeneous multicore architecture for intelligent transportation systems. Computer Science [cs]. Université de Lille (2018-..), 2022. English. NNT: . tel-03895529v1

# $\begin{array}{c} {\rm HAL~Id:~tel\text{-}03895529} \\ {\rm https://hal.science/tel\text{-}03895529v1} \end{array}$

Submitted on 12 Dec 2022 (v1), last revised 31 Jan 2023 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

École Doctorale - Mathématiques, sciences du numérique et de leurs interactions (EDMADIS)

#### Improving the Reliability of Heterogeneous Multicore Architecture for Intelligent Transportation Systems Améliorer la fiabilité des architectures multicore hétérogènes pour les systèmes de transport intelligents

Thèse de doctorat Informatique

Fabien Bouquillon

Soutenue le 18 Octobre 2022

Supervisors

Jury

#### Rapporteur

#### Christine Rochange

Université Toulouse III-Paul Sabatier

#### Directeur de thèse

Giuseppe Lipari

Université de Lille

#### Rapporteur

**Olivier Sentieys**

Université de Rennes 1

#### **Examinateur**

Florian Brandner

Télécom Paris

#### <u>Directeur de thèse</u>

Smail Niar

INSA Hauts-de-France LAMIH UMR CNRS Université Polytecnique Hauts-de-France

#### Président

Alberto Bosio

École Centrale de Lyon

## Abstract

Real-time systems must provide functionalities that need to produce their results within predefined time windows. Some of these functionalities may be critical: if they produce wrong results or produce good results too late, failures occur which, in some extreme case, may cause the loss of human lives.

Intelligent transportation systems are a good example of real-time systems with critical functionalities. These vehicles embed complex features to enhance the driving experience, like the so-called Advanced Driver-Assistance Systems (ADAS). Such complex functionalities possess non-functional requirements, as the fact that they must produce results within precise time windows, or that must be robust to transient hardware faults. For example, the *automatic obstacle detection* feature assists the driver by alerting on obstacles on the vehicle path, so preventing accidents dues to inattention or fatigue: however the recognition of an obstacle must be performed in due time, otherwise the vehicle will harm someone or destroy itself.

Thus, a precise analysis of the temporal behavior of these systems is required to guarantee that all the timing constraints are respected. For modern vehicles, the electronic boards chosen for these systems need to provide high performance, since there is a pressure to integrate all the critical and non-critical functionalities on the same board and reduce cost. Moreover, with the miniaturization of electronic components and with the reduction in voltage, systems may be subject to transient faults during their lifetime, provoking unexpected failures. Thus, there is a need to have analysis taking into account both reliability and the respect of the timing constraints. In this thesis, we have proposed a set of solutions that are positioned at two levels:

- 1. We have developed models to analyze the execution time of real-time systems that integrate caches. The major scientific contribution of the thesis at this level is an improved analysis of the effect of preemptions on memory access times in a system scheduled by Earliest Deadline First.

- 2. We have also designed techniques to increase the reliability of real-time systems integrating caches. Our approach is novel in the sense that we propose a method to protect tasks code from transient faults in the cache by adding protection mechanisms to the tasks code while respecting the timing constraints.

Our work is original in that it lies at the intersection of several areas:

1. The domain of real-time critical systems;

- 2. The field of processor system architectures in general and that of programmable embedded systems integrating caches in particular;

- 3. The field of reliability and robustness of real-time critical systems.

## Résumé en Français

Les systèmes temps réel implémentent des fonctionnalités qui doivent produire leurs résultats dans une fenêtre de temps donnée. Certaines de ces fonctionnalités peuvent être critiques. Si une fonctionnalité critique produit un résultat erroné ou produit un bon résultat au-delà d'une certaine limite temporelle, une défaillance se produit. Lorsqu'une défaillance se produit, des événements catastrophiques peuvent s'ensuivre, comme la perte d'une vie humaine. Les systèmes de transport intelligents sont un bon exemple de systèmes temps réel dotés de fonctionnalités critiques. Ces véhicules intègrent des fonctionnalités qui améliorent la conduite en aidant le conducteur, comme les systèmes avancés d'assistance au conducteur c(ADAS). Ces fonctionnalités doivent produire de bons résultats dans une fenêtre de temps précise comme pour la détection d'objets pour éviter de blesser des usagers de la route. Une analyse précise du comportement de ces systèmes est par conséquent nécessaire pour garantir que les contraintes de temps sont respectées. Pour les véhicules modernes, les cartes électroniques choisies pour ces systèmes doivent être très performantes, et doivent intégrer toutes les fonctionnalités critiques et non critiques sur la même carte afin de réduire les coûts. Avec la miniaturisation des circuits électronique et la réduction de la tension électrique, les systèmes peuvent subir des fautes transitoires pendant leur durée de vie, provoquant des erreurs dans leurs comportements. Il est donc nécessaire d'avoir une analyse prenant en compte à la fois la fiabilité et le respect des contraintes temporelles. Dans cette thèse, nous avons proposé un ensemble de solutions qui se positionnent à deux niveaux :

- 1. Nous avons mis au point des modèles d'analyse de temps d'exécution des systèmes temps-réels intégrants des mémoires caches. La contribution scientifique majeure de la thèse à ce niveau est une meilleure analyse de l'impact des préemptions entre les tâches sur les temps d'accès à la mémoire dans un système ordonnancé par Earliest Deadline First.

- 2. Nous avons aussi conçu des techniques pour augmenter la fiabilité des systèmes temps-réel intégrant des mémoires caches. Notre approche est nouvelle dans le sens où nous proposons une méthode qui permet de protéger le code des tâches des fautes transitoires dans la mémoire cache en ajoutant des mécanismes de protection au code des tâches tout en respectant les contraintes temporelles.

Comme on peut le voir, notre travail est original du fait qu'il se trouve à l'intersection de plusieurs domaines :

- 1. Le domaine des systèmes temps-réel critiques;

- 2. Le domaine des architectures de systèmes de processeurs en général et celui des systèmes embarqués programmables intégrant des mémoires caches en particulier;

- 3. Le domaine de la fiabilité et de la robustesse des systèmes temps-réels critiques.

## Acknowledgement

I would like to express my gratitude to Giuseppe Lipari and Smail Niar for introducing me to the world of research and guiding me through this thesis. I can't thank them enough for their feedback and support over the last four years. I would also like to express my gratitude to the permanent members of the two teams I joined for their advice, particularly Clément Ballabriga for assisting me with OTAWA and Julien Forget for his precious reviewing. Of course, I'd like to express my gratitude to all of the PhD students, former PhD students, and post-docs who shared my office with me. I would also like to express my sincere thanks to Filip Marković, who assisted me in producing a counter-example of his method.

I would thank Fédération de Recherche Transports Terrestres & Mobilité FR TTM (FR3733), supported by CNRS, Université Polytechnique Hauts-de-France (UPHF), Université de Lille (UL) and Centrale Lille Institut (CLI), for the financial support provided during the 3 years of my Ph.D. This Ph.D. corresponds to a cooperation between two laboratories: LAMIH at UPHF and CRISTAL at UL.

I'd also like to show my thankfulness to the members of my thesis jury for their remarks and advices. Finally, I want to express my sincere thanks to my relatives and friends for their support over the past four years.

## Contents

| A            | bstra | ct                                           | 1          |

|--------------|-------|----------------------------------------------|------------|

| $\mathbf{R}$ | ésum  | é en Français                                | 3          |

| C            | onter | nts                                          | 7          |

| Li           | st of | Figures                                      | 10         |

| Li           | st of | Tables                                       | 11         |

| Ι            | Mo    | tivation and Background 1                    | L <b>3</b> |

| 1            | Pro   | blem & Motivation                            | 15         |

|              | 1.1   | Real-Time Systems                            | 16         |

|              | 1.2   | Intelligent Transportation Systems           | 16         |

|              |       | 1.2.1 Critical functionalities               | 17         |

|              |       | 1.2.2 Functionalities for comfort purpose    | 18         |

|              | 1.3   | Autonomous Vehicles                          | 18         |

|              | 1.4   | Problems                                     | 20         |

|              |       | 1.4.1 Models of cache memories               | 21         |

|              | 1.5   | Contributions and organization of the thesis | 22         |

| 2            | Rea   | l-Time Systems Model                         | 23         |

|              | 2.1   |                                              | 24         |

|              | 2.2   |                                              | 26         |

|              | 2.3   | 0                                            | 27         |

|              | 2.4   | $^{\circ}$                                   | 29         |

|              |       | ı v                                          | 30         |

|              |       |                                              | 30         |

|              | 2.5   | Earliest Deadline First                      | 31         |

|              |       | 1                                            | 31         |

|              |       | 2.5.2 Non-preemptive tasks                   | 32         |

| 3            | Cac   | he memories                                  | 33         |

8 CONTENTS

|    | 3.1 | Cache Memories Hierarchy                           |

|----|-----|----------------------------------------------------|

|    | 3.2 | Structure                                          |

|    |     | 3.2.1 Replacement policy                           |

|    |     | 3.2.2 Write Policy                                 |

|    | 3.3 | Cache Analysis for WCET estimation                 |

|    |     | 3.3.1 Example                                      |

|    |     | 3.3.2 Cache Related Preemption Delay               |

|    | 3.4 | Related Works on CRPD                              |

|    |     | 3.4.1 Avoiding CRPD                                |

|    |     | 3.4.2 Improving CRPD estimation                    |

|    | 3.5 | Reminder on CRPD Analysis                          |

|    |     | 3.5.1 Useful CBs and Evicting CBs                  |

|    |     | 3.5.2 Operations on multisets                      |

|    |     | 3.5.3 EDF analysis with CRPD                       |

|    |     | 3.5.4 UCB-union multiset                           |

|    |     | 3.5.5 ECB-union <i>SOM</i>                         |

|    | 3.6 | Weak robustness in computing systems               |

|    |     | 3.6.1 Example of vulnerability                     |

|    |     | 3.6.2 Estimation of the cache memory vulnerability |

|    |     | 3.6.3 Protection mechanisms                        |

|    | 3.7 | Related Works on Cache Memory Vulnerability        |

|    |     | 3.7.1 Permanent Faults                             |

|    |     | 3.7.2 Transient Faults                             |

| II | Co  | ntributions 55                                     |

| 4  | Imp | proving CRPD analysis under EDF scheduling 57      |

|    | 4.1 | Partitioning-ver1 and ver2                         |

|    |     | 4.1.1 Reminder of the approaches                   |

|    |     | 4.1.2 Counter Example                              |

|    | 4.2 | System model                                       |

|    | 4.3 | Preemption Interval                                |

|    | 4.4 | Reduce the number of UCBs                          |

|    | 4.5 | Complexity                                         |

|    |     | 4.5.1 Complexity of UCB multiset                   |

|    |     | 4.5.2 Complexity of ECB-union $SOM$                |

|    | 4.6 | Evaluation                                         |

|    |     | 4.6.1 Experiments Setup                            |

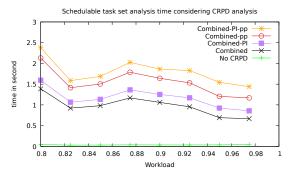

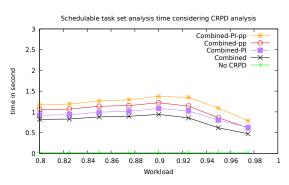

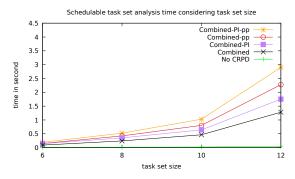

|    |     | 4.6.2 Results                                      |

|    | 4.7 | Conclusions and future work                        |

|    |     |                                                    |

| 5  |     | lucing Task Set Vulnerability 73                   |

|    | 5.1 | System model                                       |

CONTENTS 9

|    | 5.2   | Profile |                                                                 |     |

|----|-------|---------|-----------------------------------------------------------------|-----|

|    |       | 5.2.1   | Computing the vulnerability factor of tasks                     | 75  |

|    |       | 5.2.2   | CB invalidation                                                 | 79  |

|    |       | 5.2.3   | ICM and TAVF                                                    | 82  |

|    |       | 5.2.4   | Transformation to a QP problem                                  | 83  |

|    |       | 5.2.5   | Using ECC SRAM memories                                         | 84  |

|    | 5.3   | Reduc   | ing Task Set Vulnerability Factor                               | 85  |

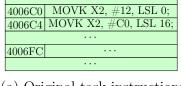

|    | 5.4   | Evalua  | ation                                                           | 86  |

|    |       | 5.4.1   | Experimental setting                                            | 86  |

|    |       | 5.4.2   | Task profiles for the cache invalidation method                 | 87  |

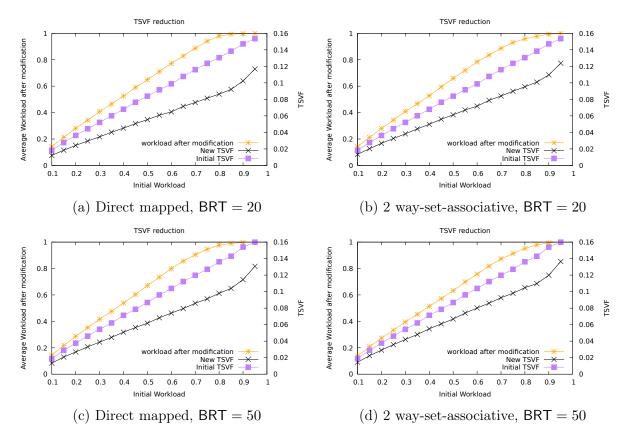

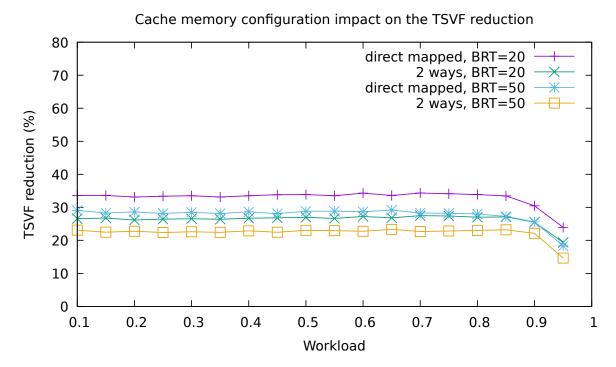

|    |       | 5.4.3   | TSVF reduction                                                  | 89  |

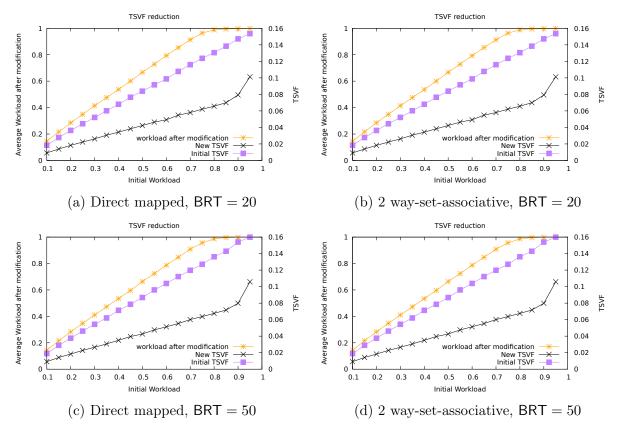

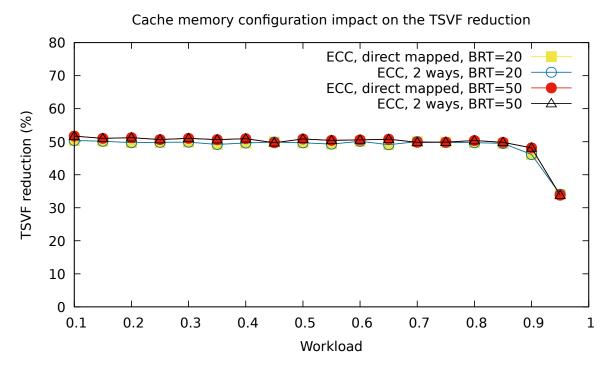

|    |       | 5.4.4   | TSVF reduction with ECC                                         | 90  |

|    | 5.5   | Conclu  | <u>ısion</u>                                                    | 91  |

| Co | onclu | sion    |                                                                 | 95  |

|    | 5.6   | Summ    | ary                                                             | 95  |

|    |       | 5.6.1   | Contributions on Cache Related Preemption Delay                 | 95  |

|    |       | 5.6.2   | Contribution on Cache Reliability in Real-Time Embedded Systems | 96  |

|    | 5.7   | Perspe  | ectives                                                         | 96  |

| Pe | erson | al pub  | lications                                                       | 98  |

| A  | List  | of Syr  | mbols                                                           | 99  |

| В  | List  | of Ab   | breviation of Terms                                             | 104 |

| Bi | bliog | graphy  |                                                                 | 106 |

# List of Figures

| 2.1 | Sporadic task model                                                                                                                                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | Static analysis                                                                                                                                                                                          |

| 2.3 | Task CFG containing a loop                                                                                                                                                                               |

| 2.4 | Scheduling of 2 tasks                                                                                                                                                                                    |

| 3.1 | Example of multicore architecture                                                                                                                                                                        |

| 3.2 | Example of a K-way set-associative with $Z$ cache sets                                                                                                                                                   |

| 3.3 | PIPT cache                                                                                                                                                                                               |

| 3.4 | VIVT cache                                                                                                                                                                                               |

| 3.5 | VIPT cache                                                                                                                                                                                               |

| 3.6 | Relation between CBs and BBs                                                                                                                                                                             |

| 3.8 | Example of task CFG                                                                                                                                                                                      |

| 3.9 | Example vulnerability intervals                                                                                                                                                                          |

| 4.1 | Counter example                                                                                                                                                                                          |

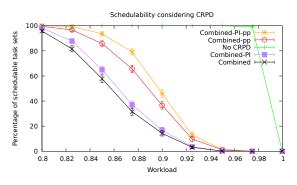

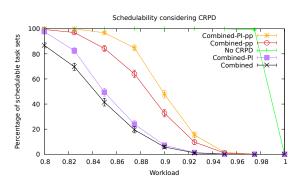

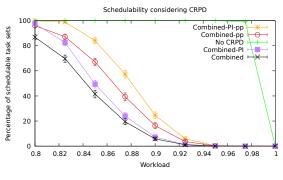

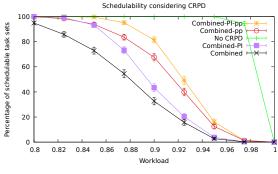

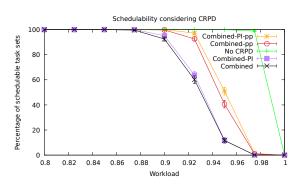

| 4.2 | Impact of cache size                                                                                                                                                                                     |

| 4.3 | Impact of number of ways                                                                                                                                                                                 |

| 4.4 | Impact of number of tasks and BRT                                                                                                                                                                        |

| 4.5 | Impact of their reduce operation on analysis time                                                                                                                                                        |

| 4.6 | Analysis time for a cache memory of 4KB, 2 ways, $U = 0.85$ , BRT = 200 and $M_{reduce} = 4 \dots \dots$ |

|     | $M_{reduce} = 4 \dots 71$                                                                                                                                                                                |

| 5.1 | Example of task CFG (bis) 76                                                                                                                                                                             |

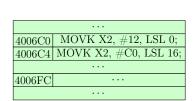

| 5.2 | Invalidation mechanism for direct mapped cache memories 80                                                                                                                                               |

| 5.3 | CB invalidation mechanism for set-associative cache memory 81                                                                                                                                            |

| 5.4 | Case Study task profiles                                                                                                                                                                                 |

| 5.5 | TSVF reduction after CB invalidation with a 16KB-IL1 cache 90                                                                                                                                            |

| 5.6 | TSVF reduction with miss insertion. In these experiments, an average TSVF value is calculated on workloads of 1000 task sets                                                                             |

| 5.7 | TSVF reduction with the ECC mechanism for a 16KB-IL1 cache. ECC exe-                                                                                                                                     |

| J.1 | cution time is set to 3 cycles                                                                                                                                                                           |

| 5.8 | TSVF reduction with ECC mechanism                                                                                                                                                                        |

|     |                                                                                                                                                                                                          |

## List of Tables

| 1.1                               | SAE Autonomous vehicle classifications [30]                                                                                                                | 20 |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1                               | Scheduling Taxonomy                                                                                                                                        | 28 |

| 3.1                               | State of the art methods against our contributions on improving reliability                                                                                | 52 |

| 4.1<br>4.2<br>4.3<br>4.4          | Counter Example                                                                                                                                            | 62 |

| 7.7                               | cycles                                                                                                                                                     | 67 |

| 5.1                               | Vulnerable instructions and path vulnerability for each LB in the example of Figure 5.1                                                                    | 79 |

| <ul><li>5.2</li><li>5.3</li></ul> | List of programs from the 2 benchmarks. In this table we consider a 16KB IL1 and a BRT of 20 cycles.  Cache miss mechanism impact used in the experiments. | 87 |

|                                   | List of symbols used in the thesis                                                                                                                         |    |

# Part I Motivation and Background

# Chapter 1

## Problem & Motivation

| Contents |                                              |    |

|----------|----------------------------------------------|----|

| 1.1      | Real-Time Systems                            | 16 |

| 1.2      | Intelligent Transportation Systems           | 16 |

|          | 1.2.1 Critical functionalities               | 17 |

|          | 1.2.2 Functionalities for comfort purpose    | 18 |

| 1.3      | Autonomous Vehicles                          | 18 |

| 1.4      | Problems                                     | 20 |

|          | 1.4.1 Models of cache memories               | 21 |

| 1.5      | Contributions and organization of the thesis | 22 |

|          |                                              |    |

This chapter will introduce real-time systems and Intelligent Transportation Systems (ITS), using modern vehicles as an illustration. Then, I will describe the unresolved problems and challenge handle by these systems. Finally, this chapter will conclude with a summary of the thesis' contents.

#### 1.1 Real-Time Systems

Real-time systems are computing systems that must react within precise time constraints to events in the environment. As a consequence, the correct behavior of these systems depends not only on the value of the computation but also on the time at which the results are produced [28, 68].

A real-time system interacts with its environment through the use of sensors and/or actuators. Given the dynamic nature of the environment, the system's response to a change in the environment cannot be postponed indefinitely. The state of the system at any point in time must be correct in relation to the state of the environment at the same point in time. Any state of the system that causes an accident in the environment or in the system itself, such as the destruction of system components, is regarded as a failure.

Aircraft autopilots, nuclear power plant system control, robotics and virtual reality applications are just a few examples of real-time systems in use today. Other examples include autonomous vehicles or missile defense applications that are used to detect, track, and intercept missiles in order to prevent the destruction of an area or ship. Indeed, we can find real-time systems in a wide variety of fields, each of these systems must adhere to the temporal constraints defined by their mission in order to perform effectively. This does not imply that all of these systems must respond immediately; rather, they must respond in a timely and appropriate manner. For example virtual reality applications must react to the user's movement at a rate such that the user does not perceive any delay between its actions in the real world and those in the virtual reality. It is also not necessary to select the most performant electronic board if two different electronic boards with varying levels of performance can integrate virtual reality applications while ensuring that their respective timing constraints are respected throughout the system's life. Indeed, a system may seem slow to us, but if we are sure that its temporal constraints will be respected, there is no reason to increase its speed. Also, it is essential to recognize that the average reaction time of a system is not a guarantee of its ability to respect its temporal constraints. For example, a system that reacts very quickly on average but too slowly in some rare situations is not desirable. Indeed, without a guarantee that the system will always react in time, one can assume that accidents will occur, with potentially catastrophic consequences.

#### 1.2 Intelligent Transportation Systems

A real-time system is exemplified by intelligent transportation systems. They evolve in an ever-changing environment and must make decisions based on their perception within certain time constraints imposed by the environment. Intelligent Transportation Systems are transportation management systems; they integrate not only vehicles, roads, communication, and control infrastructures, but also the people who are present in the surrounding area. They seek to alleviate traffic congestion and pollution in the city, while also increasing vehicle and pedestrian safety.

Furthermore, we can consider these systems as cognitive systems according to [34], i.e. systems that learn to respond to a particular situation based on data collected during previous interactions with the environment. Three steps can be used to model the functioning of these systems.

- The collection of data defining the environmental context;

- The analysis of data and the planning of actions;

- Action execution.

Today, ITS are critical, as existing transportation infrastructures are insufficient to solve existing transportation problems [8]. They rely on technologies such as the Global Positioning System (GPS) to estimate traffic congestion, the communication technologies between vehicles and the network to share or get data with vehicles or with the intelligent transportation system's control center. Additionally, they are based on functionalities embedded in modern vehicles that aid the driver in her driving by utilizing Advanced Driver Assistance Systems (ADAS) [76]. Each of these technologies can be classified into two distinct categories

- Critical functionalities;

- Functionalities for comfort purpose.

#### 1.2.1 Critical functionalities

All functions that have a significant control over the vehicle or that have the purpose of preventing an immediate accident are classified as critical features. These features must adhere to strict time constraints in order to avoid collisions. A delayed response can have severe consequences, including the loss of a human life. For instance, the following functionalities can be considered critical:

**Cruise control.** With the Cooperative Adaptive Cruise Control (CACC) [63], cruise control features for automobiles have become a reality. This technology aims to control a vehicle on a road in conjunction with other vehicles, forming what is known as a distributed hybrid system [56].

Collision Avoidance Systems (CAS). These systems are based on active sensors such as radar, laser and lidar or passive sensor as optical camera or acoustic sensors to detect information on the environment and taking decision to avoid collision [65].

Antilock Braking Systems (ABS). These systems are active safety systems and are designed to maintain steering control during heavy braking by preventing the wheels from locking [38].

Autonomous Emergency Braking (AEB). This feature is intended to detect situations in which emergency braking is required and to bring the vehicle to a complete stop in these circumstances [40].

#### 1.2.2 Functionalities for comfort purpose

These features are intended to enhance the driver's overall comfort. They entail automating non-mission critical tasks, as well as advising and providing additional information to the driver. These include the following features:

Automatic Climate Control: which automatically regulates the air humidity and temperature inside the vehicle.

Automatic high beam control: which controls the vehicle's headlights in order to avoid blinding an oncoming vehicle detected by a front-facing camera.

Biometric seat: utilizes a camera to determine the driver's level of stress, distraction, and fatigue. When the driver's fatigue level is too high, for example, this feature alerts him and suggests a break. According to Mukhtar et al. [65], the primary causes of accidents are driver inattention, fatigue, and immature behavior [69]. Additionally, more than half of accidents involving inattention are caused by driver distractions [52] such as eating, drinking, or using a phone or other multimedia device in the vehicle [78]. Fatigue is also a significant factor, accounting for between 25% and 30% of road accidents [36].

**GPS Tracking:** enables the vehicle's position in the environment to be tracked in real time, assisting the driver on his route and alerting him when he exceeds the route's maximum allowed speed.

#### 1.3 Autonomous Vehicles

Additionally, modern vehicles are increasingly becoming self-driving. However, various classifications propose several levels of autonomy, with the final level representing a vehicle with perfect autonomy [31, 1, 30, 12]. We present in Table 1.1 the SAE international classification.

| Level | Name | Description |

|-------|------|-------------|

|-------|------|-------------|

| 0 | No Driving Au-     | The driver must perform all the driving tasks.                                                                  |

|---|--------------------|-----------------------------------------------------------------------------------------------------------------|

|   | tomation           |                                                                                                                 |

| 1 | Driver Assistance  | The driver must perform all tasks that the assistant cannot, as well as supervise and intervene as necessary    |

|   |                    | to ensure that the vehicle behaves appropriately. The                                                           |

|   |                    | driver also has the responsibility to choose when the as-                                                       |

|   |                    | sistance should intervene and when it should stop, more-                                                        |

|   |                    | over he must also be able to regain control of the vehicle at any time, even if he does not want to. When acti- |

|   |                    | vated, the driving automation system performs either                                                            |

|   |                    | the longitudinal <b>or</b> lateral vehicle motion control sub-                                                  |

|   |                    | task and disengages immediately upon driver request.                                                            |

| 2 | Partial Driving    | The driver must perform all tasks that the assistant                                                            |

|   | Automation         | cannot, as well as supervise and intervene as necessary                                                         |

|   |                    | to ensure that the vehicle behaves appropriately. The                                                           |

|   |                    | driver also has the responsibility to choose when the as-                                                       |

|   |                    | sistance should intervene and when it should stop, more-                                                        |

|   |                    | over he must also be able to regain control of the vehicle                                                      |

|   |                    | at any time, even if he does not want to. When acti-                                                            |

|   |                    | vated, the driving automation system performs both the                                                          |

|   |                    | longitudinal and lateral vehicle motion control subtask                                                         |

|   | 0 1:1:             | and disengages immediately upon driver request.                                                                 |

| 3 | Conditional        | The driver decides when to activate the automated driv-                                                         |

|   | Driving Automation | ing system. When it is activated the driver must maintain vigilance and be prepared to regain vehicle control.  |

|   |                    | This may occur if the system requests driver intervention                                                       |

|   |                    | or if the driver detects a system error. The automated                                                          |

|   |                    | driving system performs the tasks that are possible for                                                         |

|   |                    | it to do. If the automated driving system detects a sit-                                                        |

|   |                    | uation that it cannot handle, it requests that the driver                                                       |

|   |                    | regain control of the vehicle. In addition, if the driver                                                       |

|   |                    | requests to regain control of the vehicle, the vehicle must                                                     |

|   |                    | give it back immediately.                                                                                       |

| 4 | High Driving       | When the automated driving system is engaged, the                                                               |

|   | Automation         | driver becomes a passenger. He may request to regain                                                            |

|   |                    | control of the vehicle, but there is no assurance he will                                                       |

|   |                    | receive it immediately. In some instances, the auto-                                                            |

|   |                    | mated driving system may delay handing over control                                                             |

|   |                    | to the driver. When the automated driving system's                                                              |

|   |                    | operating range is exceeded, the system requests the in-                                                        |

|   |                    | tervention of the driver.                                                                                       |

| 5 | Full Driving Au- | When the automated driving system is engaged, the         |

|---|------------------|-----------------------------------------------------------|

|   | tomation         | driver becomes a passenger. He may request to regain      |

|   |                  | control of the vehicle, but there is no assurance he will |

|   |                  | receive it immediately. In some instances, the auto-      |

|   |                  | mated driving system may delay handing over control       |

|   |                  | to the driver.                                            |

Table 1.1: SAE Autonomous vehicle classifications [30]

While fully autonomous vehicles are not yet commercially available, some vehicles already possess advanced levels of autonomy. Indeed, Tesla vehicles already meet the SAE's level 2 autonomy standard. We can conclude that, as innovation for autonomous vehicles advances, correct embedded computing systems will be required to integrate additional functionalities and to handle the increased number of tasks. Additionally, these new functionalities will become increasingly critical, necessitating adherence to extremely stringent time guarantees.

#### 1.4 Problems

The new technologies presented so far are an excellent way to address the lack of safety for vehicles and pedestrians caused by city traffic congestion.

However, at the same time there is a pressure for these vehicles to embed more functionalities to enhance driving, and a budgetary pressure regarding electronic components and design and development costs. In short, there is a need for high performance computing platforms with affordable price. Component-Off-The-Shelf (COTS) microprocessors are good candidates for these platforms. An example of architecture that meets the demand of such systems is the ARM Big Little, which allows a tradeoff between performance and energy consumption [27].

However, system analysis is extremely expensive. In avionics, the verification phase accounts for an average 60% of the project budget [18]. However, when we consider the financial loss caused by an aircraft accident, this cost becomes reasonable. In the automobile industry, budgets are more constrained, but financial losses during an accident can be substantial; therefore, the verification phase is just as crucial. A variety of issues contribute to the cost of the analyses.

The need for a precise model of the hardware for analysis tools: having an accurate model of complex systems becomes increasingly difficult. In addition, the exact specification for certain components, such as GPUs, is not publicily available, it is known only to the manufacturer.

The need for a precise model of the software: obtaining an accurate software model is difficult for the same reason as hardware models, namely the increasing complexity of

1.4. PROBLEMS 21

systems. Tasks can be dependent on one another, requiring the completion of another task before their execution can begin. There is, also, a risk of contention between tasks over shared resources that can be utilized by only one task at a time. In addition to temporal constraints, task scheduling should also take into account system temperature and energy consumption, among other factors.

The need for having the least pessimistic analysis: the majority of system analyses solutions in the literature are static, where an execution time is obtained without executing the code. These analyses extract properties from the binary code as well as the hardware and software models that are valid for the lifetime of the system. However, it is hard to extract certain properties, necessitating a trade-off between accuracy and analysis complexity [81]. The pessimistic nature of these analyses is a result of their consideration of the worst-case scenario.

The COTS microprocessors' high performance is a result of their complex features, which include a shared bus, direct memory access (DMA), pipelines, branch prediction and cache memories. They were designed to boost the average performance of commercially available processors. However, their design does not account for the need to predict their behavior, which makes their analysis extremely complex: for instance, to compute precisely the worst-case execution time of a program, it may be necessary to model domino effects or timing anomalies for pipelines and branch prediction [14]. To circumvent these issues, the models used to represent their behavior contain a large number of assumptions, which add significant amounts of pessimism to the execution time of a task.

#### 1.4.1 Models of cache memories

An important set of simplifying assumptions is done in the analysis of cache memories. Caches are used to bridge the speed gap between the processor and the main memory. These memories store a copy of the data accessed from memory closer to the processor, thereby speeding up subsequent accesses. The speed with which data is accessed is determined by the cache memory's contents. However, its content is contingent upon the memory access history, which is complex to predict. Additionally, these memories are susceptible to transient faults as a result of the miniaturization of electronic chips and the reduction of electric voltage. These faults can result in bit-flipping in the cache memories, resulting in data corruption. The cache memories thus present a lack of predictability and a lack of reliability.

Additionally, cores may request access to memory via the shared bus at the same time in multicore systems, resulting in bus contention [71]. However, these accesses are caused by cache misses. As the classification of a memory access as a cache hit or a cache miss depends on the cache's content, it is difficult to predict bus contention. Thus, enhancing cache prediction can consequently enhance bus-level contention prediction.

### 1.5 Contributions and organization of the thesis

This thesis proposes a more accurate representation of software in the analysis and a reduction in the analysis' pessimism, focusing on the cache memory utilization by real-time tasks.

First in Chapter 2, we describe the model used to represent tasks, as well as the various scheduling algorithms and schedulability analyses proposed in the literature. The cache memories and their vulnerability are then presented in greater detail in Chapter 3. This chapter focuses on the improvements made to the task model and scheduling analysis in order to account for cache memories in these analyses, as well as the state of the art regarding these analyses and models. In addition, we will describe how to measure the vulnerability of a cache memory and the various mechanisms proposed to safeguard these memories from the literature. In Chapter 4 we present our contribution to improve the predictability of the cache memories while in Chapter 5 we address the problem of reliability of the caches. Finally in Chapter 5.5, we conclude our contributions, we sumarize the most important results and we discuss some possible extensions of our work.

# Chapter 2

# Real-Time Systems Model

| Contents |                                                    |  |

|----------|----------------------------------------------------|--|

| 2.1      | Task Model                                         |  |

| 2.2      | WCET estimation                                    |  |

| 2.3      | Real-Time Tasks Scheduling                         |  |

| 2.4      | Fixed Priority                                     |  |

|          | 2.4.1 Preemptive tasks schedulability analysis     |  |

|          | 2.4.2 Non-preemptive tasks schedulability analysis |  |

| 2.5      | Earliest Deadline First                            |  |

|          | 2.5.1 Preemptive tasks                             |  |

|          | 2.5.2 Non-preemptive tasks                         |  |

|          |                                                    |  |

In this chapter, I will discuss how real-time systems are modeled in the literature and in this thesis, as well as the analyses that allow the worst-case execution time of a task to be computed. Also, we will see the various algorithms used to schedule the execution of tasks, as well as the analyses that ensure that this scheduling adheres to temporal constraints.

#### 2.1 Task Model

A real-time system can be model as a set of concurrent software tasks. A task is a software thread, that is a sequential piece of code that executes onto a multi-threaded operating system. In Listing 2.1 we see the pseudo-code of a typical real-time task in a POSIX-like environment: after a first phase that initializes the local and global variables of the task, it enters a (finite or infinite loop) where, after executing its functionality the task suspends itself by invoking a function (in the pseudo-code of Listing 2.1 this function is denoted as wait\_for\_activation(), but it could be different, depending on the operating system). While the thread is suspended, other concurrent threads can execute. To restore execution, the task must be activated either by a timer (e.g. a periodic task) or by an external event (for example, an interrupt from a device driver, or a signal coming from another software task), in which case we have a sporadic or aperiodic task.

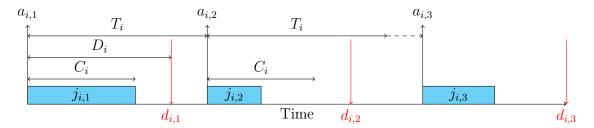

To analyze a system consisting of a set of concurrent tasks, we will now provide a mathematical model of the temporal behaviour of the tasks. In this thesis, we consider a set of N independent real-time tasks, denoted as  $\mathcal{T} = \{\tau_1, \dots, \tau_n\}$ . A real-time task  $\tau_i$  is described as a (possibly infinite) succession of jobs. In Listing 2.1, a job is an instance of the execution of the piece of code inside the while loop, between two consecutive activations. We denote with  $j_{i,k}$  the  $k^{th}$  jobs of  $\tau_i$ . In our model, a job  $j_{i,k}$  is characterized by three parameters. The first parameter is the arrival time, noted  $a_{i,k}$ , that correspond to the moment when the job is ready to start its execution; notice that this instant may not be the start of the execution of the job since other jobs from other task may have to

```

void *mytask(void *args)

{

// Initialization

while(TRUE) {

// code of the task's instance

// (job)

wait_for_activation();

}

```

Listing 2.1: Code of a real-time task

2.1. TASK MODEL 25

finish their execution before. The second parameter is the job's absolute deadline, noted  $d_{i,k}$ , that corresponds to the moment before which  $j_{i,k}$  need to have finished its execution. Finally, the latest parameter is the execution time of the job, noted  $c_{i,k}$ .

We called *periodic task*, a task that has its jobs arriving in a periodic scheme. Periodic tasks are the most predictable tasks since we know exactly the arrival of each of their jobs. In Listing 2.1, the function wait\_for\_activation() suspends the task waiting for activation from the software timer provided by the OS. For example, in the POSIX standard, the function wait\_for\_activation() is replaced by function clock\_nanosleep().

Sporadic tasks are tasks that have their jobs arriving at or after a minimum interarrival time since the arrival time of the previous job. These tasks are less predictable than periodic tasks since we do not know exactly the arrival time of the jobs. They are used to model systems where tasks are activated by external events which are not triggered regularly. For example, the reception of a packet from an Ethernet network is often modelled by a sporadic task. However, since we can establish a minimum interarrival time, we can upper bound the load caused by a sporadic task on the system by considering its jobs to arrive at their earliest time.

Finally, there exists another category of tasks, the *aperiodic tasks* for which we do not have any guarantees concerning the arrival time of their jobs. They are the least predictable type of tasks because we cannot upper bound their workload.

The classic model by Liu and Layland [55] characterizes a task  $\tau_i$  with the tuple  $(C_i, D_i, T_i)$ . With  $C_i$  the worst case execution time of its jobs  $C_i = \max_{\forall k} (c_{i,k})$ ,  $D_i$  the relative deadline, i.e. the length of any interval  $[a_{i,k}, d_{i,k}]$ , and  $T_i$  the minimum interarrival time between two jobs (if we consider sporadic tasks) or the period of the arrival times (if we consider periodic tasks). Thus, in both cases  $T_i = \min_{\forall k} (a_{i,k+1} - a_{i,k})$ .

We denote by  $U_i = C_i/T_i$  the utilization of  $\tau_i$ .

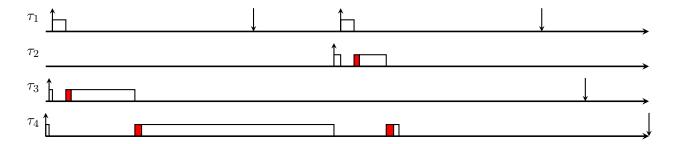

An example of a sporadic task model is shown in Figure 2.1. It shows 3 jobs of task  $\tau_i$ , with their execution represented by the blue boxes.

Also, there are two different models of tasks concerning the deadlines, the constrained deadline tasks and the implicit deadlines tasks. In the first model the relative deadline is inferior or equal to the period  $D_i \leq T_i$ ; in a case of implicit deadline tasks, the deadline is equal to the period  $D_i = T_i$ .

Figure 2.1: Sporadic task model

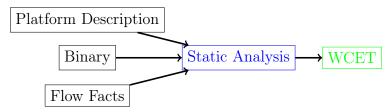

Figure 2.2: Static analysis

#### 2.2 WCET estimation

The execution time of a task depends on several parameters such as the platform characteristics, its status or the data that are handled by the task. To estimate the worst-case execution time  $C_i$  of a task, measuring the execution time of numerous instances of the task might be seen as a good idea. However, it is not the case, since the instance that produce the worst case execution may not be observed during the measurements. In this case the value obtained may be too optimistic. To provide a safe upper bound of worst-case execution time  $C_i$ , we must statically analyze the code of the task.

Static analyses extract properties from the code that are applicable to all instances (jobs) of a program. The analysis can be done on either the source code or the compiled binary. On the other hand, it is impossible to know a large portion of the properties about a code because doing so would require solving undecidable problems. In these instances, static analyses treat those properties as unknown, and if these properties have an impact on the WCET, the worst-case scenario is always considered [81]. The WCET of a program obtained from a static analysis is therefore an upper bound on the actual value.

Additionally, a precise model of the platform on which the program will run is required for static analysis. The more precise the model, the more precise the analysis, and the closer the WCET upper bound is to the actual value. Figure 2.2 shows a generic flow to obtain an estimation of the WCET. In the diagram, the program's binary code and the platform's description serve as inputs for the static analysis. The Flow Facts of the program, are already-known properties of the program's execution, such as the maximum number of loop iterations. In a static analysis, every task is analyzed in isolation. The impact of the other tasks on the execution time of the analyzed task is not considered. This simplifies considerably the analysis, however it represent a source of imprecision: additional analysis will be required when integrating all tasks in the system.

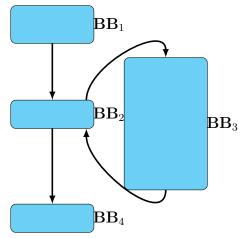

Several estimation strategies have been proposed for the WCET [85]. According to Bai et al. [15], the most prevalent technique for performing a static analysis is the Implicit Path Enumeration Technique (IPET) [54]. This procedure is based on the basic blocks (BBs), those are blocks of sequential instructions that do not contain any branch or call except at their ends. The IPET analysis consists of four steps:

- Analysis of the various execution paths to construct the BBs, the Control Flow Graph (CFG), and to identify the unfeasible paths;

- Analysis considering hardware features based on execution history such as cache memory or branch prediction;

## Control Flow Graph

Figure 2.3: Task CFG containing a loop

- Compute the WCET of the BBs;

- Compute the WCET of the task with an Integer Linear Program (ILP).

The CFG referred to in the first step of the IPET method corresponds to a graph depicting the various possible execution paths of the analyzed task. In order to construct this graph, the analysis connects the BBs with edges representing the destination of the calls or the branches.

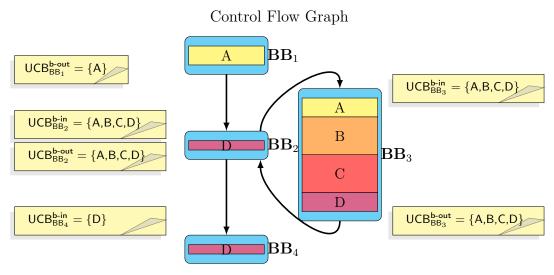

An example of task CFG is shown in Figure 2.3. In this figure we can see a task with 4 BBs, BB<sub>1</sub>, BB<sub>2</sub>, BB<sub>3</sub>, and, BB<sub>4</sub>. Also, this task includes a loop represented by BB<sub>2</sub> and BB<sub>3</sub>. The entry and the exit of the task are respectively BB<sub>1</sub> and BB<sub>2</sub> in this example.

In this thesis we use OTAWA [17] to perform the static analysis of a task, which is based in the IPET method.

## 2.3 Real-Time Tasks Scheduling

According to Section 2, a real-time system comprises numerous tasks. Therefore, these tasks must share physical resources like CPUs and cache memories. Certain resources, such as the CPU, can only be utilized by one task at a time. Therefore, resource utilization must be scheduled between tasks.

The WCET analysis is insufficient to ensure that the time constraints will be met, as this step assumes that each task will run independently on its own platform, without sharing any resource with the others.

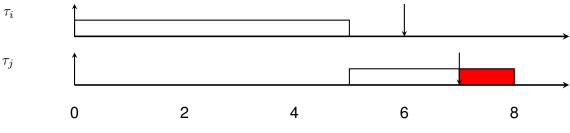

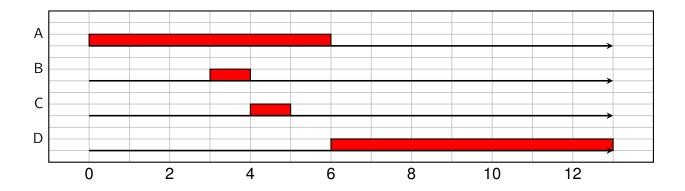

On the Figure 2.4 is a an example of a possible schedule of two tasks  $\tau_i$  and  $\tau_j$  that are sharing a platform with a single core. The task  $\tau_i$  has WCET  $C_i = 5$  and deadline  $D_i = 6$ ,  $\tau_j$  has WCET  $C_j = 3$  and deadline  $D_j = 7$ . If we consider the two tasks independently, both of them will meet their deadlines. Nonetheless, as demonstrated by this example,  $\tau_j$  misses a deadline due to the fact that a single core can only execute one task at a time.

Figure 2.4: Scheduling of 2 tasks.

- Single core

- Multicore

- Global

- Partitioned

- Online scheduling

- Task level fixed priority: Deadline Monotonic (DM),

Rate Monotonic (RM), Fixed Priority in general.

- Job level fixed priority:

Earliest Deadline First

(EDF).

- Dynamic priority:

P-Fair, Least Laxity

First (LLF).

- Offline scheduling

- Time Triggered

- Preemptive

- Limited Preemption

- $\bullet \ \ Non\text{-}Preemptive$

Table 2.1: Scheduling Taxonomy

Therefore, it is necessary to ensure that all time constraints are met when scheduling tasks.

Table 2.1 presents a taxonomy of scheduling algorithms. The left column displays the various methods of task allocation among system cores. In a system with a single core, all tasks will utilize the same core. There are two options for multicore systems: allowing tasks to be scheduled on any core (*Global*) or assigning a specific core to each task (*Partitioned*). In the latter case, each instance of the task must run exclusively on this core. This is equivalent to considering multiple single-core systems, although you must take into account that other system features, such as the bus and cache memory, are still shared.

In the middle column, the various scheduling algorithms are represented, including

online schedulers that will schedule the tasks during the execution of the system and offline schedulers that will determine which task must be executed based on an offline schedule. *Time-triggered* is an example of an offline scheduler.

For online schedulers, there are three distinct categories of algorithms. The first category corresponds to algorithms that assign a fixed priority to each task, and each instance of a task will have that priority. When several tasks are ready for execution, the one with the highest priority will be executed first. This category contains all variations of Fixed Priority (FP) [37, 55], such as Rate Monotonic (RM), which assigns a priority inversely proportional to the period of the task, and Deadline Monotonic (DM), which assigns a priority inversely proportional to the relative deadline of the task, such that the task with the shortest relative deadline will have the highest priority.

The second category corresponds to algorithms that assign a fixed priority to each instance (job), so that two instances of the same task may not have the same priority. This category includes Earliest Deadline First (EDF) [55], an algorithm that executes the job with the earliest absolute deadline that is ready to be executed.

In the last category, algorithms that assign dynamic priority to each instance are presented. In these algorithms, we find Least Laxity First (LLF) [64], which executes the instance with the smallest laxity (the remaining time between the expected end of execution and its absolute deadline).

The right column represents the various preemptions modes permitted for online schedulers. In preemptive systems, all preemptions are permitted, meaning that a task can be interrupted at any point during its execution. In systems with limited preemption, a task can only be preempted at certain specific points of its execution. And finally, there are systems that prohibit preemption.

In this thesis, we focus on single-core systems with EDF scheduling so that we can later adapt the solutions to partitioned multicore systems. In addition, both fully preemptive and non-preemptive systems are addressed.

We will now present the FP and EDF schedulers for single-core systems and their scheduling analysis in greater detail.

## 2.4 Fixed Priority

Fixed Priority (FP) is a family of schedulers rather than a single scheduler. FP consists of assigning each task a fixed priority. Consequently, each job within a task has the same priority. The scheduler executes the ready task with the highest priority at any instant t. This priority can be assigned manually by developers, or calculated by heuristics such as  $Deadline\ Monotonic\ (DM)$ , which assigns a priority  $P_i$  inversely proportional to the relative deadline of the task  $\tau_i\ (P_i\cong 1/D_i)$ . In the case of  $Rate\ Monotonic\ (RM)$ , the priority of a task  $\tau_i$  is inversely proportional to its period that is  $P_i=1/T_i$ . Furthermore, DM is optimal in the class of fixed priority preemptive scheduling of periodic and sporadic tasks with implicit and constrained deadlines, while RM is optimal only if all the deadlines are implicit [53]. In other words, if it exists a schedule with any fixed priority assignment

that respects time constraints, then scheduling with RM or DM will also respect time constraints.

#### 2.4.1 Preemptive tasks schedulability analysis

To ensure that time constraints are respected under RM scheduling, we can verify that the utilization of the system does not exceed  $U_{lub}$  [55],

$$\sum_{i=1}^{N} \frac{C_i}{T_i} \le U_{lub} \qquad U_{lub} = N(2^{1/N} - 1) \tag{2.1}$$

However, this is a sufficient test, as there are schedulable systems that do not satisfy this condition. Conversely, if the system utilization is greater than 1, the system cannot be scheduled.

To ensure that time constraints are met with FP in general when each task has a different priority, we can conduct the exact test below. If the maximum response time  $R_i$  for each task  $\tau_i$  (the maximum time between the activation of a task's job and the completion of its execution) is not greater than  $D_i$  [11], then the system is schedulable.

$$\forall \tau_i \in \mathcal{T} | R_i \le D_i \tag{2.2}$$

A task's response time is calculated iteratively by Equation (2.4). The initial step is to assume that  $R_i = C_i$ . Then, the following iterations consist of adding to the WCET of the task the execution time of tasks that can preempt it based on the response time calculated in the previous iterations. When the response time exceeds the relative deadline or when the response time does not change from one iteration to the next one, we terminate the procedure.

$$R_i^0 = C_i (2.3)$$

$$R_i^{k+1} = C_i + \sum_{\forall j \in hp(i)} \left\lceil \frac{R_i^k}{T_j} \right\rceil \cdot C_j$$

(2.4)

#### 2.4.2 Non-preemptive tasks schedulability analysis

The schedulability analysis for Fixed Priority Non Preemptie (FP-NP) is identical to that for FP with shared critical resources. We assume that the processor is a critical shared resource protected by a semaphore, hence a task that has begun execution cannot be interrupted. Therefore, the response time for FP-NP with a different priority per task can be calculated as follows [32, 33]:

$$R_i = S_i + C_i \tag{2.5}$$

Where  $S_i$  corresponds to the worst start time of the task  $\tau_i$ ,

$$S_i^0 = B_i (2.6)$$

$$S_i^{k+1} = B_i + \sum_{\forall j \in hp(i)} \left( \left\lfloor \frac{S_i^k}{T_j} \right\rfloor + 1 \right) \cdot C_j$$

(2.7)

with  $B_i$  the maximum blocking time a job of task  $\tau_i$  can experience [73].  $B_i$  can be calculated as follows:

$$B_i = \max_{\forall j \in lp(i)} (C_j) \tag{2.8}$$

In the previous equation lp(i) represents the set of tasks with a lower priority than  $\tau_i$ . We denote by hp(i) the set of tasks with a higher priority than  $\tau_i$ .

#### 2.5 Earliest Deadline First

Earliest Deadline First (EDF) is a scheduler that assign a priority for each job of a tasks inversely proportional to its absolute deadline. With EDF, the ready job with the earliest deadline is executed first. The preemption-level is defined for a task  $\tau_i$  as  $\pi_i = 1/D_i$ . Baker [16] proved that, in EDF scheduling, a task  $\tau_j$  may preempt a task  $\tau_i$  only if  $\pi_j > \pi_i$ . We assume that tasks are sorted in non-ascending order of preemption-level: for any two tasks  $\tau_j$  and  $\tau_i$ ,  $\pi_j > \pi_i$  implies j < i. EDF is also optimal, which mean that if there exists an online scheduler that respects the timing constraint for a set of tasks, EDF can also schedule these tasks while respecting their timing constraints. In this chapter, the scheduling analyses for EDF are presented for systems with and without preemptions.

#### 2.5.1 Preemptive tasks

To analyze the schedulability of a preemptive system under EDF scheduling, we can use the processor demand bound analysis first proposed by Baruah et al. [19]. This analysis works for tasks with constrained and implicit deadlines. It consists in computing the processor demand of the task set at each deadline in the interval [0, L], where L is an estimated upper bound on the first idle time. The demand bound function [19] of a task  $\tau_i$  in the interval [0, t] can be computed as:

$$\mathsf{dbf}_i(t) = \eta(i, t) \cdot C_i \tag{2.9}$$

With  $\eta(i,t)$  an upper bound to the number of instances of the sporadic task  $\tau_i$  that have arrival and deadline in interval [0,t]:

$$\eta(i,t) = \max\left(0, \left\lfloor \frac{t - D_i}{T_i} \right\rfloor + 1\right) \tag{2.10}$$

The demand bound of the task consists of the sum of the demand bound for each task in the task set:

$$dbf(t) = \sum_{i=1}^{N} dbf_i(t)$$

(2.11)

If for each deadline the demand bound of the task set is less than the deadline, then the system is schedulable. Otherwise, it is not. Thus, the system is schedulable if and only if:

$$\forall t \le L, \quad \mathsf{dbf}(t) \le t \tag{2.12}$$

#### 2.5.2 Non-preemptive tasks

In the case of non-preemptive tasks, we employ the following test, proposed by Jeffay et al. [46], to ensure that time constraints are guaranteed. However, this test is valid only for systems with tasks that have implicit deadlines.

It consists of two conditions, the first of which verifies that the processor's global usage does not exceed its computing capacity:

$$\sum_{i=1}^{N} \frac{C_i}{T_i} \le 1 \tag{2.13}$$

The second condition verifies that blocking between tasks does not jeopardize conformance to time constraints:

$$\forall i, 1 < i \le n; \ \forall t, T_1 < t < T_i;$$

$$t \ge C_i + \sum_{j=1}^{i-1} \left\lfloor \frac{t-1}{T_j} \right\rfloor \cdot C_j$$

$$(2.14)$$

Similarly to FP, we can consider the processor to be a critical shared resource. The blocking time is also calculated in the same manner, with the exception that lp(i) represents the set of tasks with a lower preemption-level than  $\tau_i$ . Baker et al. [16] proposed another test to verify the schedulability of system with implicit deadlines based on the utilization of the system:

$$\forall k \atop k=1,\dots,N} \left( \sum_{i=1}^{k} \frac{C_i}{D_i} \right) + \frac{B_k}{D_k} \le 1$$

(2.15)

When dealing with tasks that have constrained deadlines, the demand bound function can be modified to consider the blocking time as follows [20]:

$$dbf(t) = B(t) + \sum_{i=1}^{N} dbf_i(t)$$

(2.16)

$$B(t) = \max(C_j|D_j > t) \tag{2.17}$$

# Chapter 3

# Cache memories

| Contents |                                                    |           |

|----------|----------------------------------------------------|-----------|

| 3.1      | Cache Memories Hierarchy                           | 34        |

| 3.2      | Structure                                          | 34        |

|          | 3.2.1 Replacement policy                           | 38        |

|          | 3.2.2 Write Policy                                 | 38        |

| 3.3      | Cache Analysis for WCET estimation                 | 38        |

|          | 3.3.1 Example                                      | 39        |

|          | 3.3.2 Cache Related Preemption Delay               | 40        |

| 3.4      | Related Works on CRPD                              | 41        |

|          | 3.4.1 Avoiding CRPD                                | 41        |

|          | 3.4.2 Improving CRPD estimation                    | 41        |

| 3.5      | Reminder on CRPD Analysis                          | 43        |

|          | 3.5.1 Useful CBs and Evicting CBs                  | 43        |

|          | 3.5.2 Operations on multisets                      | 44        |

|          | 3.5.3 EDF analysis with CRPD                       | 45        |

|          | 3.5.4 UCB-union multiset                           | 46        |

|          | 3.5.5 ECB-union $SOM$                              | 47        |

| 3.6      | Weak robustness in computing systems               | <b>47</b> |

|          | 3.6.1 Example of vulnerability                     | 48        |

|          | 3.6.2 Estimation of the cache memory vulnerability | 49        |

|          | 3.6.3 Protection mechanisms                        | 50        |

| 3.7      | Related Works on Cache Memory Vulnerability        | <b>50</b> |

|          | 3.7.1 Permanent Faults                             | 51        |

|          | 3.7.2 Transient Faults                             | 51        |

The high performance, measured by the number of instructions executed per second, of a microprocessors is limited by the speed of data transfer between the main memory (DRAM) and the processor [43], which necessitates the use of cache memories. Cache memories maintain a copy of the accessed data in order to speed up the data transfer for future accesses. Cache memory access latency is significantly lower than DRAM access latency. However, cost per byte of a cache memory is much higher than DRAM, so only small sizes are possible. Consequently, cache memory cannot replace main memory.

# 3.1 Cache Memories Hierarchy

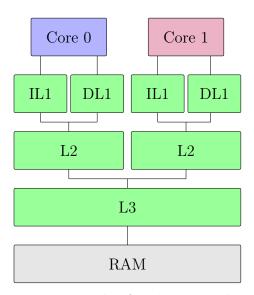

There are multiple cache memories in multicore systems, which can be shared by multiple cores or reserved for a specific core. In addition, some of them may contain only instructions, others only data, or both instructions and data simultaneously. The majority of multicore systems consists of three levels of cache memory. The closest level to the cores consists of an instruction cache (IL1) and a data cache (DL1) for each core. These caches are not shared with other cores and are directly connected to the core. The second level consists of one cache memory (L2) per core; these cache memories are linked to the IL1 and DL1 of their respective core; these caches may contain both instructions and data simultaneously. The third and final level contains a unique cache memory (L3) for all multicore systems; this cache is connected to the L2 caches. An example of multicore architecture with 2 cores and 3 level of caches is presented in Figure 3.1.

# 3.2 Structure

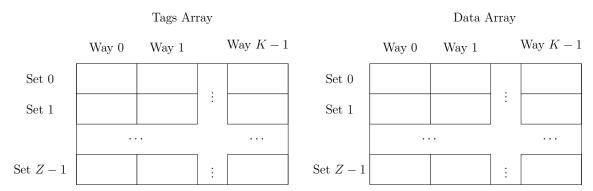

A *K-way set-associative* cache memory is a matrix of **cache lines**, the basic memory block unit of a cache memory. Cache lines are regrouped into **cache sets** of *K* elements, also

Figure 3.1: Example of multicore architecture

3.2. STRUCTURE

Figure 3.2: Example of a K-way set-associative with Z cache sets

known as **ways**. A cache memory with a single way per set is known as a *direct-mapped* cache, and a cache with a single set is known as a *full-associative cache*.

The memory is divided in **cache blocks** (CB), which are memory blocks of the size of a cache line. Each of these CBs is assigned an *index* computed as the modulo between the address of the CB and the number of cache sets, which corresponds to the cache set where the CB may be stored. Two CBs may have the same index: to differentiate them, each one is assigned a *tag* computed from their address. Figure 3.2 represents an exemple of a *K-way set-associative* with *Z* cache sets. It is composed of two matrixes, the data array that contains the CBs and the tags array that contains the tags of the CBs stored in the cache memory. The columns of these matrixes correspond to the *cache ways* and the lines, the *cache sets*.

As it exists two types of memories in a computer, physical and virtual, a cache memory is in one of the followings categories:

- Physically indexed, physically tagged cache memories (PIPT);

- Virtually indexed, virtually tagged cache memories (VIVT);

- Virtually indexed, physically tagged cache memories (VIPT).

The operating system uses virtual addressing for the memory of processes and, by extension, tasks. Each process has a dedicated address space. Consequently, two data coming from separate processes can have the same virtual address. To determine the location of data in physical memory, the Memory Management Unit (MMU) must convert virtual addresses to physical addresses.

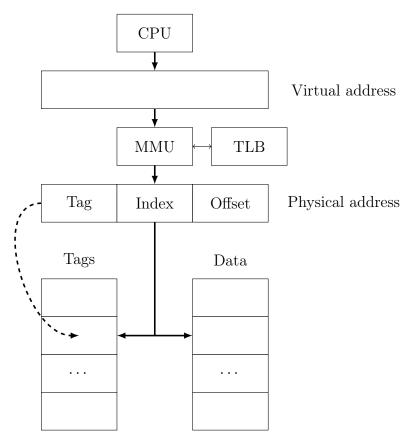

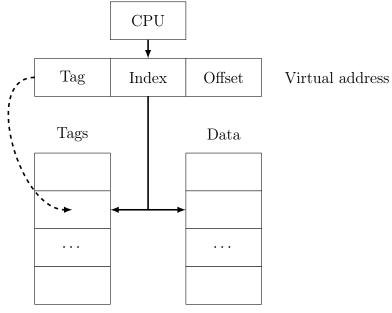

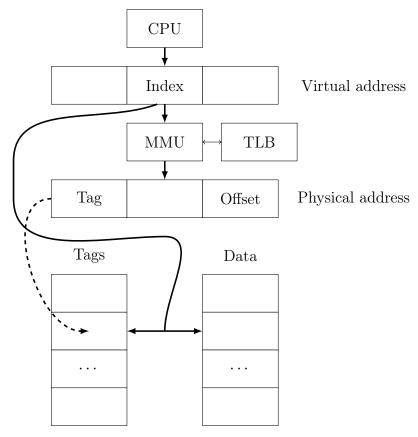

Therefore, PIPT caches must convert the virtual address to a physical address in order to obtain the index and tag of a CB. Figure 3.3 represents this type of cache memory. The virtual address is translated with the MMU that contains the Translation Lookaside Buffer (TLB). The TLB contains the recent translations to speed up the MMU executiontime. VIVT caches use only the virtual address for the calculation of the index and the tag, removing the need to translate the physical address into the virtual address, it is shown with Figure 3.4. This accelerates the access to CBs in comparison to PIPT caches. However, these caches must be invalidated entirely whenever a process is changed.

Figure 3.3: PIPT cache

Figure 3.4: VIVT cache

3.2. STRUCTURE 37

Figure 3.5: VIPT cache

VIPT cachees, describe with Figure 3.3 are a compromise between the two previously mentioned cache types. The translation of the virtual address into a physical address and the calculation of the tag are performed while the index is being calculated from the virtual address and the cache set is being accessed. This enables the same performance as the VIVT caches without invalidating the cache memory when a process is changed. However, a process can have two virtual addresses that point to the same data and, therefore, the same physical address [72]. Consequently, two instances of the same CB can coexist in the cache memory.

It is necessary to ensure that all instances of a CB are updated when writing. Because of this, data or hybrid caches (data and instructions) are typically of the PIPT type, whereas instruction caches that do not support writes are typically of the VIPT type.

When the processor needs to access an instruction, the index and the tag are computed from the virtual address. The tag is compared with all the CBs contained in the corresponding cache set: if a match is found (hit), then its age in the cache set is updated according to the replacement policy; if the tag is not found (miss), the CB is loaded from the main memory and stored in the cache set according to the replacement policy.

In this thesis we only consider a system composed of a single core with an instruction cache virtually indexed and physically tagged. The contribution of this thesis targets direct mapped and set-associative as they are the most frequently used caches. Also,

Fully-associative caches which are caches with only one index are not suited for large cache memory due to the large number of comparators [41].

# 3.2.1 Replacement policy

When a CB must be stored in a cache set, an algorithm chooses in which cache way the block has to be stored. Such algorithm is called a replacement policy algorithm. Several replacement policies exist [50]:

- First In First Out (FIFO). The oldest block present in the cache memory is the one which is replaced by another one if there are no free ways available.

- Least Recently Used (LRU). Each cache way in a cache set is assigned an age: at each access, ages are updated so that a CB with a more recent access than another has a lower age. When a CB has to be loaded in a cache set that is full, the least recently used CB is evicted and all the ages are updated accordingly. This replacement policy is the most predictable.

- Pseudo Least Recently Used (PLRU). LRU is difficult to implement as it needs to track the age of all the blocks in the memory cache. Thus, a family of replacement algorithms with a behavior close to LRU was designed: the PLRU family. This family of algorithms includes tree-PLRU and bit-PLRU.

- Random when a block must be stored, a random way is selected. It is the most unpredictable replacement policy.

In this thesis, we only consider the LRU replacement policy.

# 3.2.2 Write Policy

As a data can have multiple copies stored in multiple cache memory, when data is written all copies must be updated. However updates may be done at different times. They can be done directly after the write, we call this policy "write-trough"; or it can be done when the data is evicted, in this case it is called the "write-back" policy.

In this thesis only **instruction cache memories** are targeted, there is no write policy for this memories since instructions are read only.

# 3.3 Cache Analysis for WCET estimation

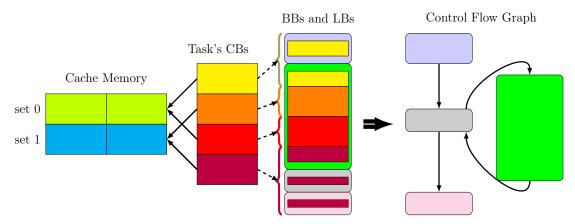

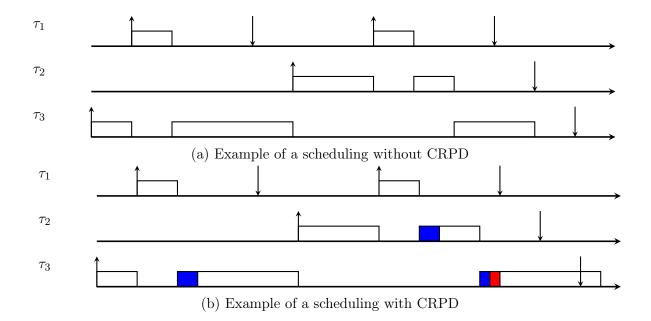

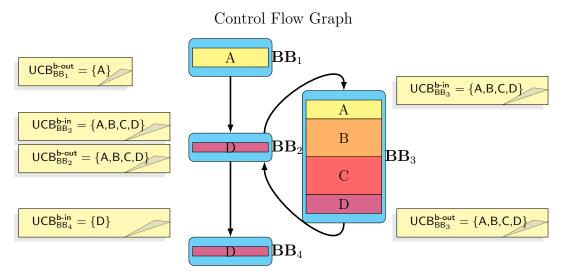

To take cache memory into account when estimating the WCET, an analysis classifying each memory access as a cache hit or a cache miss must be provided. There are two types of cache analysis: *must analysis* and *may analysis*. Instead of classifying each memory access, these analyses assign a category to each line block (LB), a block corresponding to the intersection of a CB and a BB, to determine whether accessing the latter will result in a hit or a miss. The *may analysis* categorizes LBs as either *always miss* or *unknown*.