# Contributions to system-level modelling and simulation of hardware-software architectures of embedded systems.

Sébastien Le Nours

## ► To cite this version:

Sébastien Le Nours. Contributions to system-level modelling and simulation of hardware-software architectures of embedded systems. Electronics. Nantes Université, 2022. tel-03884261

# HAL Id: tel-03884261 https://hal.science/tel-03884261v1

Submitted on 5 Dec 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# HABILITATION A DIRIGER DES RECHERCHES

DE NANTES UNIVERSITE

Par

**Sébastien LE NOURS**

# Contributions to system-level modelling and simulation of hardware-software architectures of embedded systems

Présentée et soutenue à NANTES, le 21 novembre 2022 Unité de recherche : IETR UMR CNRS 6164

**Composition du Jury :**

President of the jury Reviewer Reviewer Examiner Examiner Abdoulaye Gamatié, Senior Researcher CNRS LIRMM Florence Maraninchi, Full Professor INP Grenoble Andy Pimentel, Full Professor University of Amsterdam Olivier Sentieys, Full Professor University of Rennes 1 Liliana Cucu-Grosjean, Senior Researcher INRIA Sébastien Pillement, Full Professor Nantes University Document prepared for obtaining an accreditation to supervise research (*Habilitation à diriger des recherches*)

# Contributions to system-level modelling and simulation of hardware-software architectures of embedded systems

Sébastien Le Nours

Defended on November 21th, 2022 with jury composed of :

| Abdoulaye Gamatié     | Senior Researcher | CNRS LIRMM              | President of the jury |

|-----------------------|-------------------|-------------------------|-----------------------|

| Florence Maraninchi   | Full Professor    | INP Grenoble            | Reviewer              |

| Andy Pimentel         | Full Professor    | University of Amsterdam | Reviewer              |

| Olivier Sentieys      | Full Professor    | University of Rennes 1  | Reviewer              |

| Liliana Cucu-Grosjean | Senior Researcher | INRIA                   | Examiner              |

| Sébastien Pillement   | Full Professor    | Nantes University       | Examiner              |

# Contents

| Li | ist of f | figures                                                                                      | 7  |

|----|----------|----------------------------------------------------------------------------------------------|----|

| Li | ist of t | tables                                                                                       | 9  |

| Sı | ımma     | ary of research and teaching activities                                                      | 13 |

|    | А        | Personal record                                                                              | 13 |

|    | В        | Summary of teaching activities                                                               | 15 |

|    |          | B.1 Teachings                                                                                | 15 |

|    |          | B.2 Responsibilities and services to the community                                           | 16 |

|    | С        | Summary of research activities                                                               | 18 |

|    |          | C.1 Addressed area of research                                                               | 18 |

|    |          | C.2 Supervision activities                                                                   | 18 |

|    |          | C.3 Contracts and research projects                                                          | 20 |

|    |          | C.4 Publications                                                                             | 21 |

|    |          | C.5 Member of boards and committees                                                          | 21 |

|    |          | C.6 Animation of research                                                                    | 21 |

| 1  | Intr     | oduction                                                                                     | 23 |

|    | 1.1      | Context                                                                                      | 23 |

|    |          | 1.1.1 Evolutions and trends in the design of hardware-software architectures of embedded     |    |

|    |          | systems                                                                                      |    |

|    |          | 1.1.2 Principles of electronic system-level design                                           |    |

|    |          | 1.1.3 Issues and addressed problems                                                          |    |

|    | 1.2      | Contributions to the research field                                                          |    |

|    |          | 1.2.1 Development of activities                                                              |    |

|    |          | 1.2.2 Contributions to improving system-level simulation efficiency                          |    |

|    |          | 1.2.3 Contributions to the creation of system-level models of hardware-software architecture |    |

|    |          | 1.2.4 Contributions to online management of hardware-software architectures                  |    |

|    | 1.3      | Organization of the document                                                                 |    |

|    | 1.4      | Publications related to Chapter 1                                                            | 30 |

| 2  | Con      | tributions to system-level modelling and simulation                                          | 31 |

|    | 2.1      | Introduction                                                                                 |    |

|    | 2.2      | Addressed issue                                                                              | 31 |

|    | 2.3      | Principles of the proposed system-level approach                                             | 33 |

|    | 2.4      | Creation of state-based models                                                               |    |

|    | 2.5      | Generic execution model                                                                      | 37 |

|    | 2.6      | Implementation and preliminary results                                                       | 39 |

|    | 2.7      | Conclusion                                                                                   | 40 |

|    | 2.8      | Supervision                                                                                  | 41 |

|    | 2.9      | Publications related to chapter 2                                                            | 41 |

| 3  | Con               | nmunication modelling of multiprocessor architectures                                        | 43         |

|----|-------------------|----------------------------------------------------------------------------------------------|------------|

|    | 3.1               | Introduction                                                                                 | 43         |

|    | 3.2               | Improvement of simulation efficiency for distributed architecture analysis                   | 44         |

|    |                   | 3.2.1 Characteristics of the studied systems                                                 | 44         |

|    |                   | 3.2.2 Application of the simulation method                                                   | 46         |

|    |                   | 3.2.3 Obtained results                                                                       | 47         |

|    | 3.3               | Improvement of simulation efficiency for multiprocessor systems-on-chip analysis             | 47         |

|    |                   | 3.3.1 Characteristics of the studied systems                                                 | 47         |

|    |                   | 3.3.2 Application of the simulation method                                                   | 49         |

|    |                   | 3.3.3 Obtained results                                                                       | 51         |

|    | 3.4               | Conclusion                                                                                   | 52         |

|    | 3.5               | Supervision                                                                                  | 53         |

|    | 3.6               | Publications related to Chapter 3                                                            | 53         |

| 4  |                   | lelling and management of computation resources in multiprocessor systems                    | 55         |

|    | 4.1               | Introduction                                                                                 | 55         |

|    | 4.2               | Modelling and sizing of mobile radiocommunication system architectures                       | 55         |

|    |                   | 4.2.1 Modelling and simulation method for non-functional properties                          | 56         |

|    |                   | 4.2.2 Modelling of dynamic functions                                                         | 59         |

|    | 4.3               | Management strategies of multiprocessor architectures                                        | 61         |

|    |                   | 4.3.1 Related work and contribution of our work                                              | 62         |

|    |                   | 4.3.2 Proposed online management strategies                                                  | 63         |

|    |                   | 4.3.3 Online management architecture modelling and simulation                                | 67         |

|    | 4.4               | Conclusion                                                                                   | 68         |

|    | 4.5               | Suepervision                                                                                 | 69         |

|    | 4.6               | Publications related to Chapter 4                                                            | 70         |

| 5  | Prot              | pabilistic modelling and simulation of multiprocessor systems                                | 71         |

|    | 5.1               |                                                                                              | 71         |

|    | 5.2               | Establishment of a measurement-based characterization flow for the creation of probabilistic |            |

|    |                   | models                                                                                       | 72         |

|    |                   | 5.2.1 Proposal                                                                               | 72         |

|    |                   | 5.2.2 Results                                                                                | 74         |

|    | 5.3               | Adoption of statistical model-checking analysis methods                                      | 76         |

|    |                   | 5.3.1 Proposal                                                                               | 76         |

|    |                   | 5.3.2 Results                                                                                | 78         |

|    | 5.4               | Conclusion                                                                                   | 80         |

|    | 5.5               | Supervision                                                                                  | 80         |

|    | 5.6               | Publications related to Chapter 5                                                            | 81         |

| 6  | Con               | ducion and prospects                                                                         | 83         |

| U  | <b>Con</b><br>6.1 | clusion and prospects<br>Review of the work carried out                                      | <b>8</b> 3 |

|    | 6.1<br>6.2        |                                                                                              | 83<br>84   |

|    | 0.2               | Prospects and directions envisaged                                                           | 04         |

| Li | st of p           | oublications                                                                                 | 87         |

| Bi | bliogr            | raphy                                                                                        | 91         |

# **List of Figures**

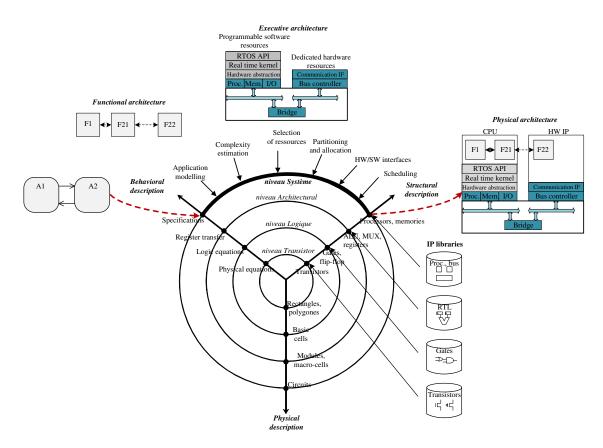

| 1<br>2      | Lessons taught in the field of embedded system design. The titles in bold are modules which I assume the responsibility, the titles in italics are modules which I episodically participated. 10 Position of research activities in the field of hardware/software architectures design of embedded systems                                                                    |        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.1         | The Y diagram with detailed at the system level, inspired from [16]. The main activities led at                                                                                                                                                                                                                                                                                |        |

| 1.0         | the system level are identified                                                                                                                                                                                                                                                                                                                                                | 5      |

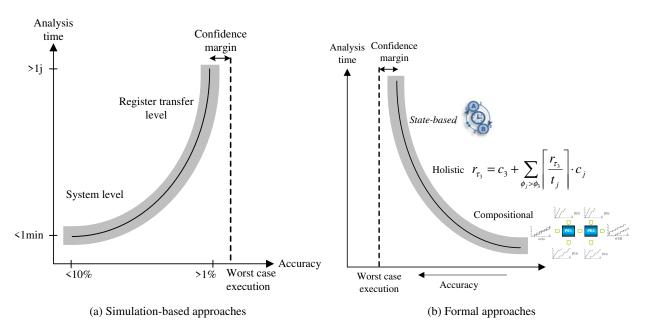

| 1.2         | Illustration of the compromise between accuracy and analysis time for different performance evaluation methods, (a) simulation-based approaches, (b) formal approaches                                                                                                                                                                                                         | 6      |

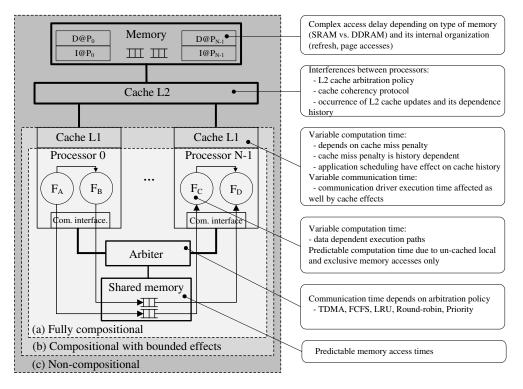

| 1.3         | Different levels of complexity in shared resources of multiprocessor systems                                                                                                                                                                                                                                                                                                   |        |

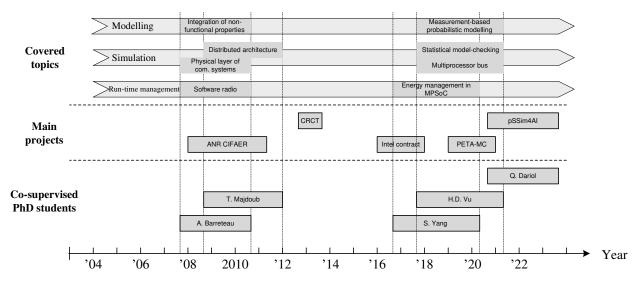

| 1.4         | Position of the covered research topics, main projects and co-supervised PhD thesis 2                                                                                                                                                                                                                                                                                          | 8      |

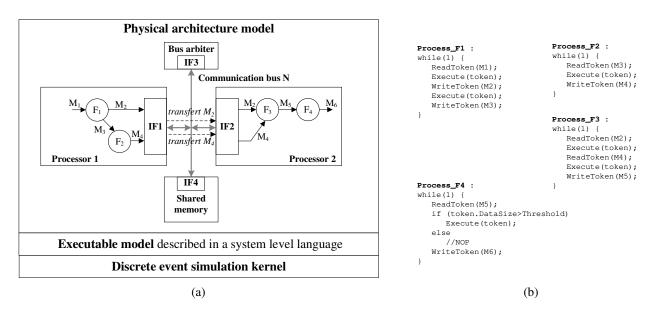

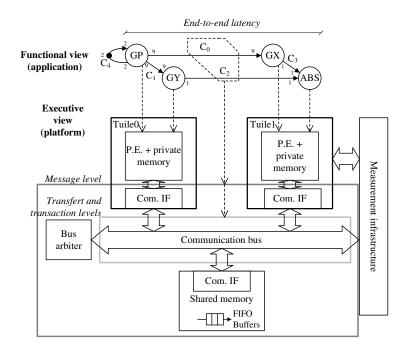

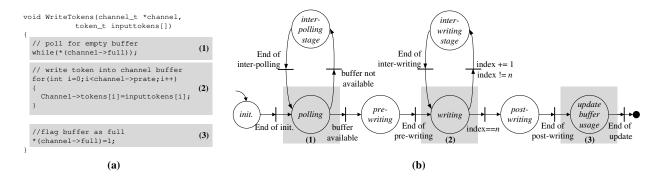

| 2.1         | (a) Example of a system-level model with three architecture viewpoints: functional, executive and physical, physique, (b) description of functions behaviours with elementary communication and computation statements. The execution semantic related to each statement needs to be defined such as illustrated in Figure 2.7.                                                | л<br>Л |

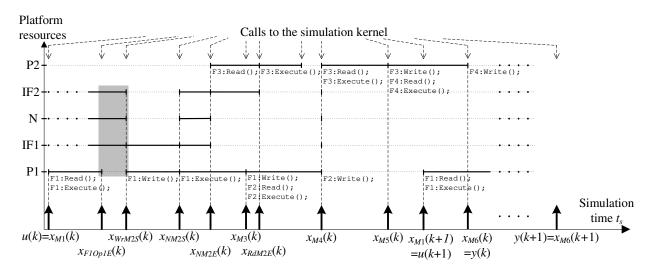

| 2.2         | Discrete event simulation of the architecture model in the figure 2.1. In this example, the instants associated with the communication of $M_2$ via the interfaces IF1 and IF2 and the communication bus N are detailed. The instants associated with the communications of the other relations are not detailed for the sake of readability. The shaded part corresponds to a |        |

| 2.3         | situation of contention on the interface IF1                                                                                                                                                                                                                                                                                                                                   | 3      |

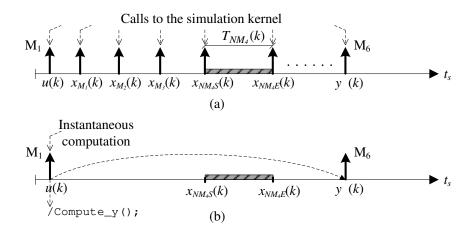

| 2.5         | (a) Execution of a model with classical simulation approach, (b) execution of a model with instantaneous computation of future simulation instants                                                                                                                                                                                                                             | 4      |

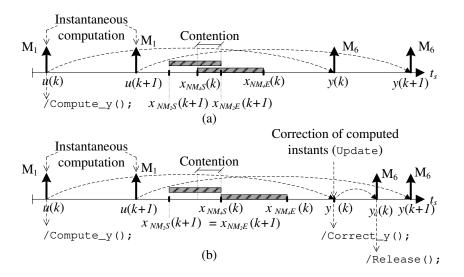

| 2.4         | (a) Situation with erroneous prediction of instants when a shared resource is used, (b) principle<br>of the correction method of resource usage instants.                                                                                                                                                                                                                      |        |

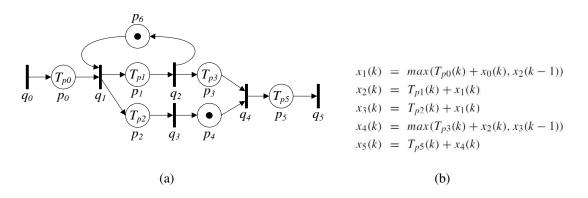

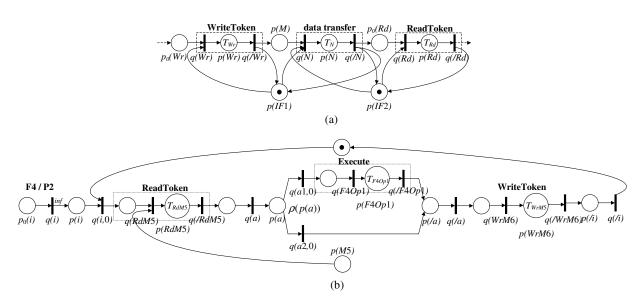

| 2.5         | <ul> <li>(a) Notation of timed Petri nets used to describe the dependencies between simulation instants,</li> <li>(b) expression of the transition instants in the illustrated network</li></ul>                                                                                                                                                                               |        |

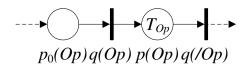

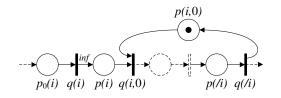

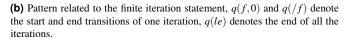

| 2.6         | Examples of elementary patterns used to describe the dependencies between start and end instants of computation and communication statements                                                                                                                                                                                                                                   |        |

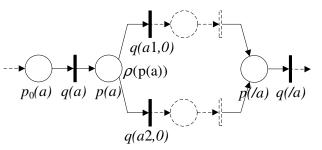

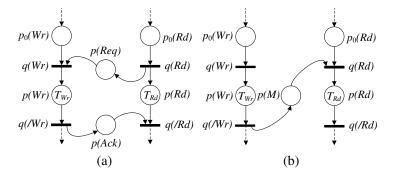

| 2.7         | Examples of patterns related to communication statements: (a) rendez-vous protocole, (b)                                                                                                                                                                                                                                                                                       |        |

| 2.8         | infinite capacity FIFO protocol. $T_{Wr}$ and $T_{Rd}$ denote the write and read durations                                                                                                                                                                                                                                                                                     | /      |

| 2.0         | of communication and computation statements.                                                                                                                                                                                                                                                                                                                                   | 8      |

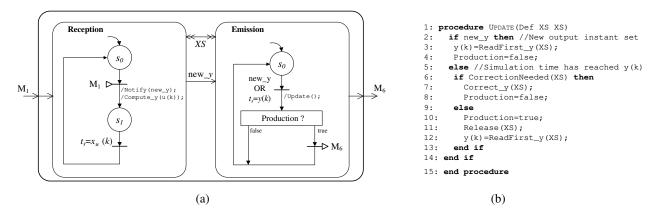

| 2.9         | (a) Structural and behavioral description of the proposed generic execution model, (b) man-                                                                                                                                                                                                                                                                                    |        |

| 2 10        | agement procedure of the computed instants                                                                                                                                                                                                                                                                                                                                     |        |

| 2.10        | Influence of the complexity of the calculation method on the achieved simulation speed-up 39                                                                                                                                                                                                                                                                                   | 9      |

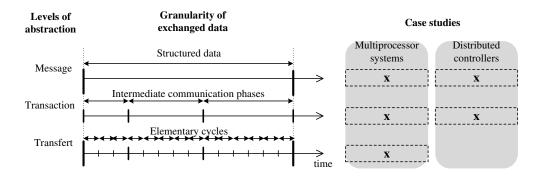

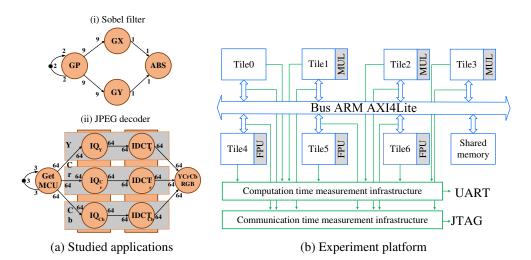

| 3.1         | Illustration of levels of abstraction in communication description for the two case studies 44                                                                                                                                                                                                                                                                                 | 3      |

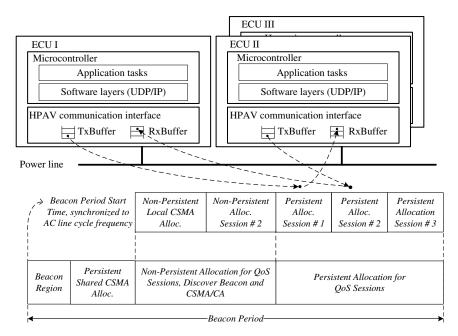

| 3.2         | Illustration of the distributed architecture studied in the scope of the CIFAER project [J3-1]. 4                                                                                                                                                                                                                                                                              | 5      |

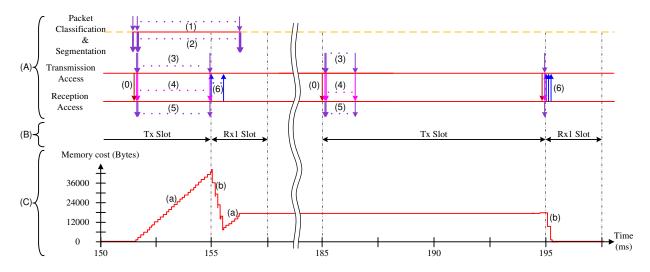

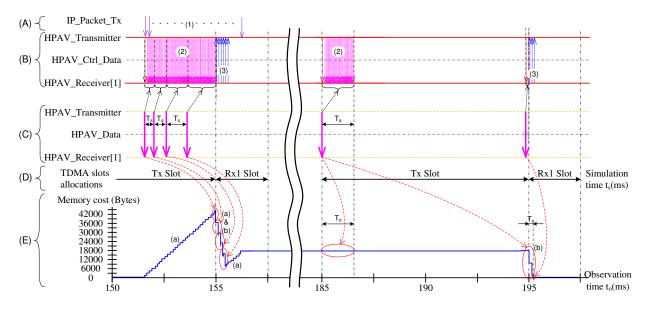

| 3.3         | Illustration of exchanged between two HomePlugAV interfaces and evolution of the interface                                                                                                                                                                                                                                                                                     | _      |

| 3.4         | memory usage during the transmission [J3-1]                                                                                                                                                                                                                                                                                                                                    |        |

| J. <b>T</b> | Evolution over the simulation time of transaction level and message level models [JJ-1].                                                                                                                                                                                                                                                                                       | J      |

| 3.5  | Illustration of the studied multiprocessor systems. They are made of an application described following the SDF model of computation and a platform with multiple tiles connected through                                                                                                                                                                                              | 40       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.6  | a communication bus and a shared memory                                                                                                                                                                                                                                                                                                                                                | 48<br>48 |

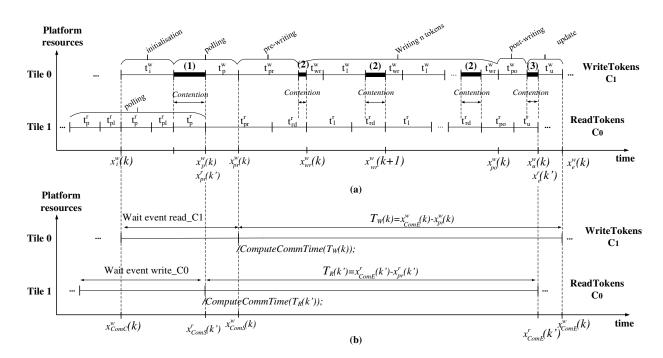

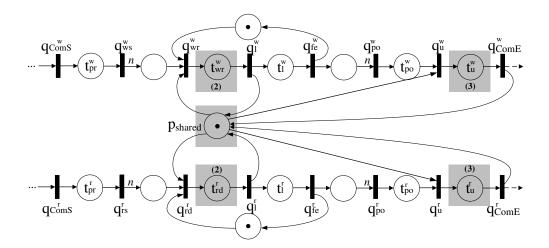

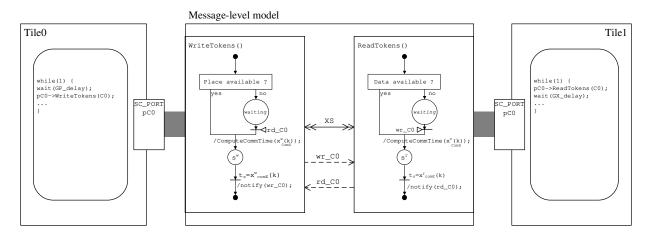

| 3.7  | Execution of models describing the writing of <i>n</i> tokens on channel $C_1$ and the reading of <i>n</i> tokens from channel $C_0$ in the example of Figure 3.5. (a) At the transfer level, the basic delays and penalties caused by contentions are highlighted. (b) At the message level, the communication times (denoted $T_W$ and $T_R$ ) are calculated during the simulation. | 50       |

| 3.8  | Timed Petri net for writing $n$ tokens on channel $C_1$ and reading $n$ tokens from channel $C_0$ .<br>Communication is considered at transaction level with the FCFS arbitration policy. The shaded rectangles correspond to the situation during which the shared resources (bus, memory) are                                                                                        |          |

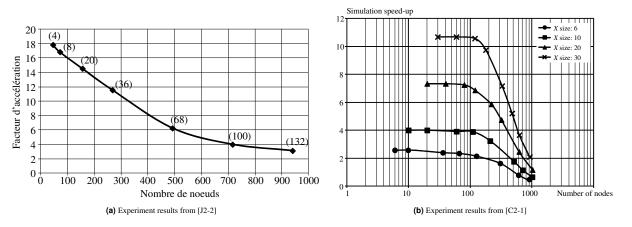

| 3.9  | accessed                                                                                                                                                                                                                                                                                                                                                                               | 50<br>51 |

| 3.10 |                                                                                                                                                                                                                                                                                                                                                                                        | 52       |

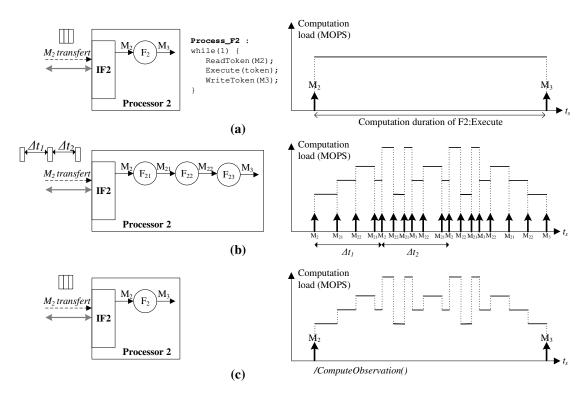

| 4.1  | Modelling and evolution of the computation load according to different approaches. $\Delta t_1$ and $\Delta t_2$ denote the interval of time between two successive data to be processed. Situation (b) corresponds to a pipeline execution of the architecture.                                                                                                                       | 56       |

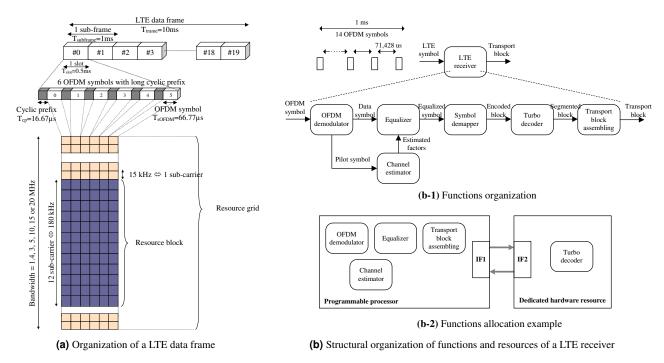

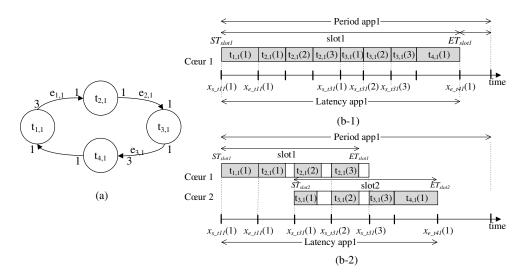

| 4.2  | (a) Organisation of an LTE data frame in the time and frequency domains, (b-1) organization of the functions of the physical layer in reception, (b-2) possible allocation of functions on                                                                                                                                                                                             | 50       |

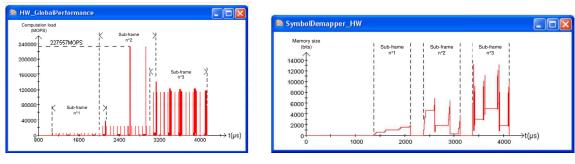

| 4.3  | two types of computing resources                                                                                                                                                                                                                                                                                                                                                       | 57       |

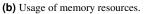

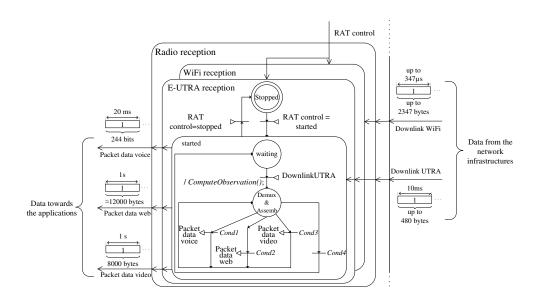

| 4.4  | based on a dedicated hardware resource [50], [J4-1]                                                                                                                                                                                                                                                                                                                                    | 58<br>60 |

| 4.5  | Evolution of the usage of resources according to an operating scenario that modifies the applications executed as well as the network available [J4-2].                                                                                                                                                                                                                                | 60       |

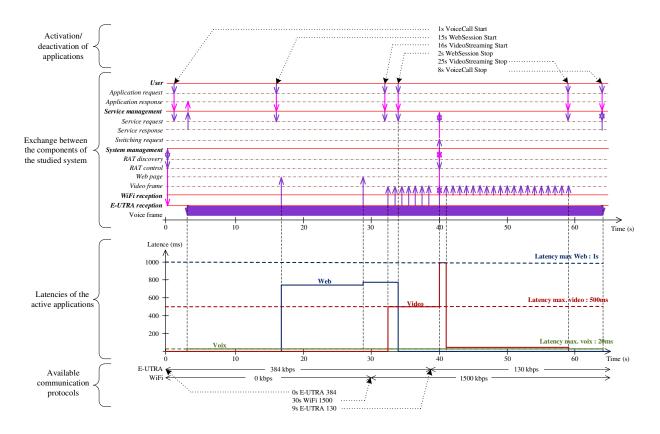

| 4.6  | Observation of the computation loads induced by the physical layer functions of the E-UTRA and WiFi protocols [J4-2].                                                                                                                                                                                                                                                                  | 61       |

| 4.7  | (a) Example of an application described according to the SDF model of computation, (b) Computation resources usage for two distinct mappings associated with the application $app_1$ .                                                                                                                                                                                                 | 62       |

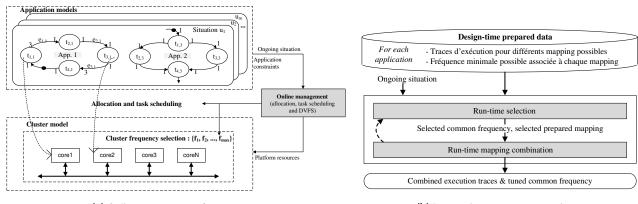

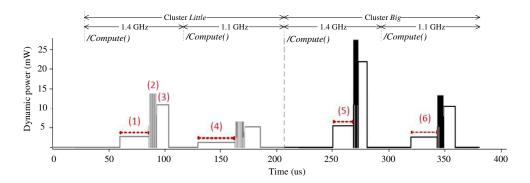

| 4.8  | (a) Position of the online manager in relation to the applications running within the same cluster, (b) Process for selecting the frequency of the cluster operation and defining task allocations.                                                                                                                                                                                    | 63       |

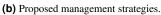

| 4.9  | Different methods of allocating timeslots based on prepared execution traces: (a) prepared execution traces for two active applications, (b) combining traces according to the FCFS method, (c) combining traces according to the LASP method, (d) combining traces according to the proposed GAPVC method.                                                                            | 64       |

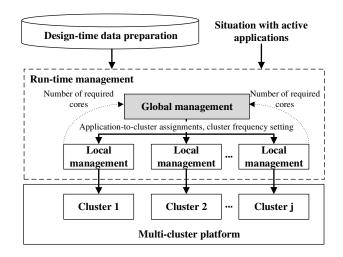

| 4.10 | Hierarchical organization for managing multiple applications running on a platform consisting of multiple clusters.                                                                                                                                                                                                                                                                    | 66       |

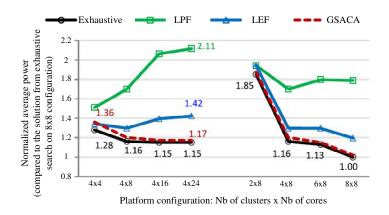

| 4.11 | Comparison of average power relative to the platform configuration $8 \times 8$ [J4-3]. For this comparison, no application re-allocation is necessary.                                                                                                                                                                                                                                | 67       |

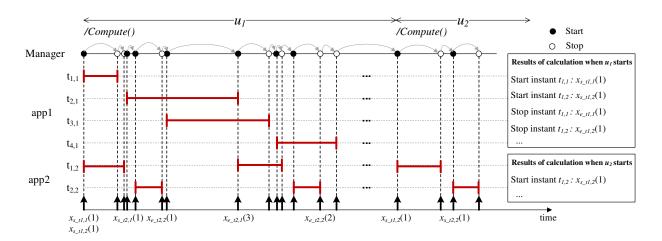

|      | Simulation principle using the traces established during each new operating situation                                                                                                                                                                                                                                                                                                  | 68       |

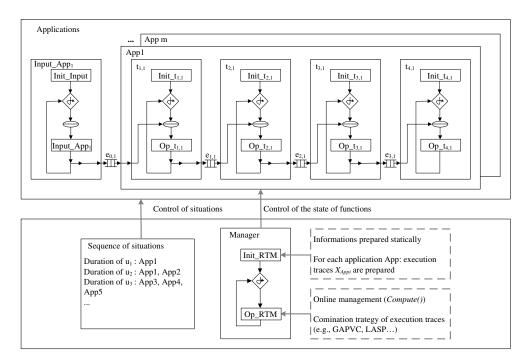

|      | A high-level model of an application and associated online manager within the Intel CoFluent<br>Studio environment                                                                                                                                                                                                                                                                     | 68       |

|      | possible allocations of the considered application [C4-4]. The simulation is conducted within the Intel CoFluent Studio environment using the proposed principle.                                                                                                                                                                                                                      | 69       |

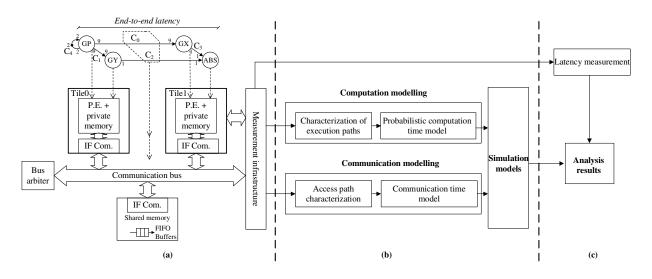

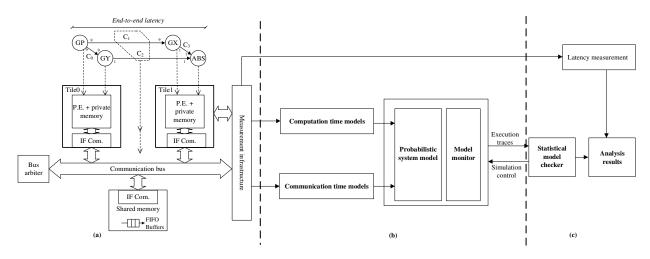

| 5.1 | Measurement-based characterisation flow for the establishment of probabilistic models for            | 70 |

|-----|------------------------------------------------------------------------------------------------------|----|

|     | the temporal properties analysis of MPSoC architectures.                                             | 72 |

| 5.2 | Process of characterization and probabilistic modelling of computation and communication             |    |

|     | resources                                                                                            | 73 |

| 5.3 | Distribution of the TL simulation models.                                                            | 75 |

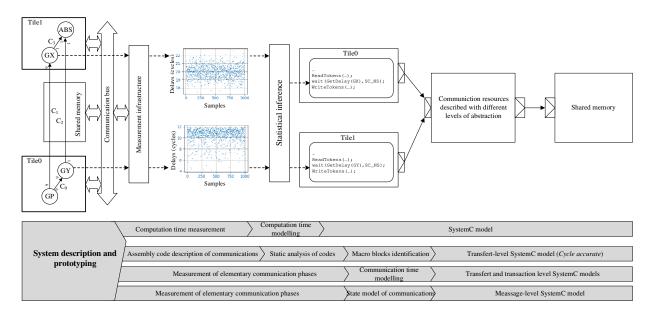

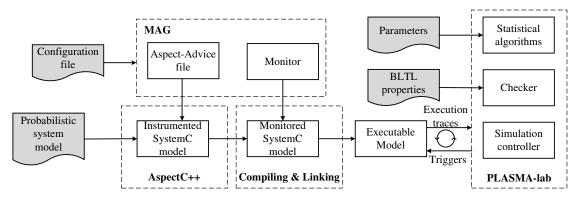

| 5.4 | Extended modelling flow to allow application of SMC methods.                                         | 77 |

| 5.5 | Details about the generation and simulation flow of instrumented and monitored SystemC               |    |

|     | models.                                                                                              | 77 |

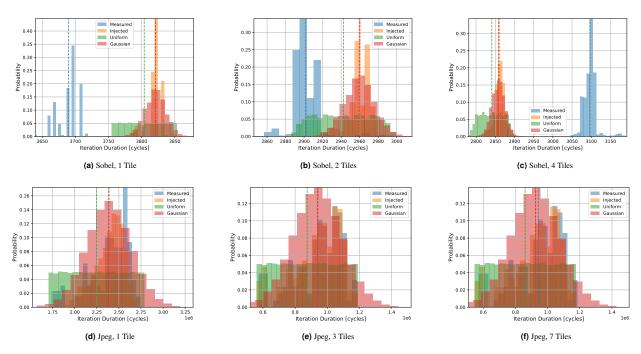

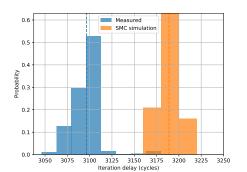

| 5.6 | Distribution of measured data and estimates obtained by simulation for the experiment <i>Sobel4a</i> |    |

| 0.0 | [47]                                                                                                 | 79 |

| 5.7 | Average values expressed in cyces, obtained by measurement on a real target, simulation of           | 17 |

| 5.7 | 1 000 000 iterations of a probabilistic model and simulation controlled by the SMC approach.         |    |

|     | The values given in parentheses indicate the deviation from the mean value measured for the          |    |

|     | first configuration of the platform [47].                                                            | 79 |

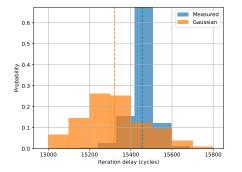

| 5.8 | Distribution of measured data and estimates obtained by simulation for the experiment <i>Sobel4b</i> |    |

| 0.0 | [47]                                                                                                 | 80 |

| 5.9 | Average values expressed in cyces, obtained by measurement on a real target, simulation of           | 00 |

| 5.9 | 1 000 000 iterations of a probabilistic model and simulation controlled by the SMC approach.         |    |

|     |                                                                                                      |    |

|     | The values given in parentheses indicate the deviation from the mean value measured for the          |    |

|     | second configuration of the platform [47].                                                           | 80 |

# **List of Tables**

| 1          | Number of hours and distribution of teachings at the University of Nantes for the 2019-2020 academic year.                                                                               | 15       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | Tested configurations and associated simulation results [J2-1]                                                                                                                           | 40<br>40 |

| 3.1        | Observed simulation duration (in seconds) for execution of transaction and message level models. The models were executed on a Intel Core2 Dual (2.66 GHz) running under Windows7 [C3-2] | 47       |

| 3.2        | Comparison of average execution durations obtained by measurements on a real taget and by simulation of transfer and message level models. The values are expressed in clock cycles.     | 52       |

| 3.3        | Execution durations on real target and simulation durations (in HH:MM:SS) for 1 000 000 of application iterations according to different possible allocations.                           | 53       |

| 4.1        | Comparison of multi-core platform online management strategies for 511 different operating situations.                                                                                   | 65       |

# Prologue

This document presents my research activities since my recruitment at the University of Nantes in September 2004. These activities were successively carried out within the IREENA laboratory (Institute for Research in Electronics and Electrotechnics of Nantes Atlantique) until 2012, then within the IETR laboratory (Institute of Electronics and Digital Technologies). The scope of these activities corresponds to the design of hardware and software architectures of embedded electronic systems. In this context, my research activities have focused on the definition of methods favouring the modelling and simulation of hardware and software architectures in order to optimize them under time, cost and energy constraints.

In this document, during the presentation of each of the covered topics, I report on the framework of this work, the nature of the contributions made and the approach undertaken. In doing so, I also explain my role in the supervision of the students who participated and contributed to this work and more broadly the collaborations set up. This synthesis tries to reconcile clarity and precision of the explanations.

This document has three main parts. The first part corresponds to a detailed CV, summarizing in particular my professional experience with regard to the various activities carried out in research and teaching. The second part details in five chapters the research activities carried out since obtaining the doctoral degree, retracing the most significant results. Finally, the third part presents an assessment of the activities carried out and establishes a potential research program taking into account the identified prospects. Attached to this document is a detailed list of my publications.

#### **Personal record** A

#### Sébastien Le Nours

Associate Professor at Nantes Université Polytech Nantes Email : sebastien.le-nours@univ-nantes.fr http://www.ietr.fr/sebastien-le-nours

Laboratory : IETR, UMR CNRS 6164 Rue Christian Pauc, 44306 Nantes Phone : +33 2 40 68 30 53

> University of Nantes, FR Sept. 2004 - Present

University of Queensland, AUS

University of South Brittany, FR

Oct. 2012 - Oct. 2013

Sept. 2003 - Aug. 2004

**INSA Rennes**, FR Oct. 2000 - Oct. 2003

#### **PROFESSIONAL EXPERIENCES**

#### **Associate Professor**

- Teaching at Polytech Nantes, the engineering school of the University of Nantes. Responsibilities within the Electronics and Digital Technologies (ETN) department of Polytech Nantes.

- Research at the Institute of Electronics and Digital Technologies (IETR), UMR CNRS 6164. Specialization in the modelling and design of hardware and software architectures of embedded systems.

**Invited researcher**

**Assistant Professor**

**PhD** researcher

#### FORMATIONS UNIVERSITAIRES

| Doctoral thesis in electronics                                     | Rennes, FR                                |

|--------------------------------------------------------------------|-------------------------------------------|

| Institut National des Sciences Appliquées (INSA)                   | Oct. 2000 – Oct. 2003                     |

| • PhD Thesis tonic: Study optimization and implementation of MC-CL | MA systems on heterogeneous architectures |

**PhD Thesis topic:** Study, optimization and implementation of MC-CDMA systems on heterogeneous architectures. Jury : E. Martin, D. Roviras (reviewers), M. Auguin, J.P. Calvez, M. Jézéquel (examiners), J. Citerne (supervisor), F. Nouvel, J.F. Hélard (co-supervisors).

#### Master degree in electronic

Université de Lille I

• Master Thesis topic: Design of clock systems based on CMOS micro-resonator for embedded applications. B. Stefanelli (supervisor).

#### **Engineer degree in electronic**

Institut Supérieur de l'Electronique et du Numérique (ISEN)

Sept. 1999 - Sept. 2000

Lille, France

Brest, France Sept. 1997 - Sept. 2000

#### TEACHING ACTIVITIES

| Main responsibilities of teaching modules                      |                              |

|----------------------------------------------------------------|------------------------------|

| SoC Design (ETN5)                                              | ETN Department               |

| Hardware-software codesign (ETN5)                              |                              |

| Digital circuit design (ETN4)                                  |                              |

| Microprocessor systems (ETN4)                                  |                              |

| Hardware-Software Architectures Codesign (M2)                  | International Master program |

| Performance Evaluation of Embedded Systems (M2)                |                              |

| Main responsibilities and services to the community            | ETN Department               |

| Member of the department council                               | 2004-Present                 |

| Head of end-of-studies internships (ETN5)                      | 2016-Present                 |

| Responsible for the first year of the engineering cycle (ETN3) | 2006-2012                    |

| Responsible for international internships                      | 2005-2006                    |

#### RESEARCH ACTIVITIES

#### **Research areas**

*System level design of embedded systems. Performance evaluation of hardware-software architectures. Prototyping of embedded systems.*

#### **Research projects and contracts**

| Publications                                                                                                                 |           |

|------------------------------------------------------------------------------------------------------------------------------|-----------|

| Coordinator for the University of Nantes of a GDR ISIS Young Researcher project                                              | 2007      |

| Coordinator for the University of Nantes of the ANR CIFAER project                                                           | 2007-2011 |

| Visiting researcher at the University of Queensland, Australia                                                               | 2012-2013 |

| Coordinator of an industrial contract with Intel company                                                                     | 2016-2017 |

| Coordinator for the University of Nantes of the international project RFI WISE PETA-<br>MC                                   | 2019-2020 |

| Coordinator for the University of Nantes of the Hubert Curien Partnership (PHC)<br>PETA-MC with the OFFIS institute, Germany | 2019-2020 |

| Coordinator for the University of Nantes of the international RFI WISE pSSim4AI project with the OFFIS institute, Germany    | 2020-2023 |

|                                                                                                                              |           |

9 international journals, 1 national journal

28 international conferences

5 publications in national national conferences

6 research reports

#### Student supervision

4 PhD thesis defended, 1 PhD thesis in progress7 Master thesis defendedParticipation in 2 thesis juries as examiner and 3 juries as guest member

#### Main responsibilities and services to the community

| Elected member of the Polytech Nantes research council                                                                                                      | 2012-2015 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Member elected to the board of the IREENA laboratory                                                                                                        | 2008-2011 |

| <i>Recruitment committees of the 61st section University of Nantes/Ecole Centrale de Nantes specialist commission</i>                                       | 2005-2007 |

| Member of recruitment committees for the University of Nantes, INSA Rennes, Univer-<br>sity of South Brittany                                               |           |

| Organization of conferences DASIP 2007, SDR-WinnComm 2009, 2010.                                                                                            |           |

| Participation in the activities of the GDR (national research consortium) ISIS (image and signal processing) and SoC2 (system-on-chip and embedded systems) |           |

# **B** Summary of teaching activities

### **B.1** Teachings

Since my recruitment in 2004 at the University of Nantes, my teaching activities have mainly been carried out at Polytech Nantes, the engineering school of the University of Nantes. These activities are divided into two distinct formations: within the Electronics and Digital Technologies (ETN) department preparing for the engineering degree and within the framework of the International Master program in Wireless Embedded Technologies (WET) (formerly Electronic Systems and Electrical Engineering, SEGE) from the University of Nantes. I participate to these two formations through different modules related to the field of embedded computer systems. By way of example, Table 1 indicates the distribution of courses I taught during the 2019-2020 academic year.

| Semester | Level   | Title                                      | Lecture | Tutorial | Practical | Project |

|----------|---------|--------------------------------------------|---------|----------|-----------|---------|

|          |         | Circuit design <sup>1</sup>                | 3,75    | 17,5     | 42        |         |

| s.7      | ETN4    | Microprocessor systems <sup>1</sup>        | 2,5     | 17,5     | 21        |         |

|          |         | 3rd year internship supervision            |         |          |           | 1       |

| s.8      | ETN4    | Real-time system design                    |         | 13,5     |           |         |

| 5.0      | E11N4   | Transversal project                        |         |          |           | 15      |

|          |         | SoC design <sup>1</sup>                    | 4,5     | 15       | 9         |         |

|          | ETN5    | HW-SW codesign <sup>1</sup>                | 9       |          | 18        |         |

| s.9      |         | Embedded system architectures              |         |          | 9         |         |

| 8.9      |         | Technical projects                         |         |          |           | 25      |

|          |         | 4th year internship supervision            |         |          |           | 11      |

| s.9      | Master2 | Circui design methodology <sup>1</sup>     |         | 12       | 12        |         |

| 5.7      | Master2 | <b>Performance evaluation</b> <sup>1</sup> |         | 7,5      |           |         |

| s.10     | ETN5    | Final year internship supervision          |         |          |           | 26,5    |

Table 1: Number of hours and distribution of teachings at the University of Nantes for the 2019-2020 academic year.

These different courses are divided into lectures, tutorials, practical work and projects. Since 2004, my teaching load corresponds to an average annual volume of 275 hours (tutorial hours). I describe here more particularly the courses for which I am currently responsible or for which I significantly contribute.

- Design of digital circuits: this course focuses on methods, languages and tools for the design, simulation and production of digital circuits. I am responsible of lectures, tutorials, practical work as well as introduction sessions for incoming students in the fourth year of the ETN department. Over the years, the changes that I have made to this teaching relate to different aspects: teaching in English for a group of tutorials, introduction sessions for incoming international students, evolution of the progress of the project in order to ensure better acquisition with students, rewriting and reorganization of course material, addition of online tests for student self-assessment.

- Microprocessor systems: this course focuses on learning the operation of hardware and software resources that constitute a microprocessor system. I provide lectures, tutorials and practical work. Over the years, I have developed this teaching on different aspects: teaching in English for a tutorial group, change of microcontroller boards and development tools used in practical work, management of the electronic boards loan to the students (Microchip SAMD21), rewriting and reorganization of the course material, the content of the tutorials and the project covered in practical work, addition of online tests for student self-assessment.

- SoC design: this course focuses on learning advanced methods for designing systems on chips. This teaching is provided within a last year option of the ETN department (entitled Real-Time Embedded Systems). I provide the lectures, the follow-up of the case-studies approached by the students and the practical work. Over the years, I have developed this teaching on the following aspects: rewriting and

<sup>&</sup>lt;sup>1</sup> Modules for which I am responsible

reorganization of the course material, use of new FPGA-based electronic boards (Xilinx ML402, Xilinx Zedboard), setting up of practical work sessions on the design of SoC using the Mentor Graphics and Xilinx Vivado suite of tools, conference by an engineer from industry on the subject of circuit testing.

- Hardware/software codesign: this course focuses on methods and languages (SystemC) for the joint design and verification of hardware/software resources of embedded systems. This teaching is provided within a last year option of the ETN department. I provide lectures and practical work. Over the years, I have developed this teaching on the following aspects: rewriting and reorganization of the course material, use of new FPGA-based electronic boards (Xilinx ML402, Xilinx Zedboard), set up of new practical works on SystemC.

- Architecture of embedded systems: this course focuses on the use of advanced resources of a microcontroller (sensor management, optimization of consumption, use of a DMA controller). This teaching is provided within the last Real-Time Embedded System option of the ETN department. For this teaching, I set up and I take care of the practical work sessions. I also set up a conference given by an engineer from industry on the subject of power management within embedded systems.

- Digital circuit design methodology: this course focuses on methods, languages and tools for the design, simulation and production of digital circuits. This teaching is given in English to students of the Master WET program. I set up this module and I provide lectures and practical work.

- Evaluation of the performance of embedded system architectures: this course focuses on learning the methods used to analyze the temporal properties of embedded system architectures (discrete event simulation, formal analysis methods). This teaching is given in English to students of the Master WET program. It is intended to be complementary to the teaching of codesign provided in the engineering degree with a particular focus on certain research works in this field. I set up this module and I provide the lectures.

In summary, my teaching activities focus on the use and design of the typical hardware and software resources of embedded systems. The following figure illustrates the distribution of the various lessons carried out, also positioning those carried out more episodically since 2004.

Figure 1: Lessons taught in the field of embedded system design. The titles in bold are modules which I assume the responsibility, the titles in italics are modules which I episodically participated.

#### B.2 Responsibilities and services to the community

I participate in the organisation of the ETN department of Polytech Nantes. I was thus able to take on the following responsibilities:

• 2005-2006: Responsible for international internships for the ETN department. This responsibility consisted of supporting students in their search for an international internship.

- 2006-2012: Responsible for the 3rd year of training within the ETN department. This responsibility involved setting up timetables, organizing semester juries and monitoring students.

- since 2015: Responsible for monitoring end-of-study internships for the ETN department. This responsibility consists of supporting students in their search for internships, the distribution of internship offers, the assignment of supervisors, the intervention of industrial partners presenting the electronics professions, interaction with the 'Company relationship' service of Polytech Nantes.

I was in charge of the organization and animation of two improvement councils of the ETN department. The first council took place in April 2017 and focused on the theme of follow-up and evaluation of internships. It allowed an assessment of the systems put in place within the ETN department in the monitoring of internships during the three years of training. The second council took place in October 2019 and focused on the theme of entrepreneurship. It allowed an assessment of the various actions implemented within the ETN department and to identify the changes required to raise awareness among students in the department about business creation.

From the 2017-2018 school year, I ensured the implementation of a new procedure for monitoring and evaluating end-of-study internships based on skills. This procedure was initially applied to the ETN department and then extended to Polytech Nantes. At Polytech Nantes, I have been part of the working group on internships since 2018. Since 2021, I have participated in the working group on the creation of a FabLab at Polytech Nantes.

I participated in the implementation of two partnership agreements between companies (ReflexCES and STMicroelectronics) and the Polytech Nantes school. Since 2017-2018, I have been organizing with the company MicroChip, a half-day visit to the Nantes site of this company for final year students of the ETN department. This visit is an opportunity for a presentation of the different activities of the company and potential positions. The constructive collaborations with these companies have benefited the students of the ETN department (technical projects, end-of-study internships, hiring) and the school (numerous donations of materials used in teaching and research, conferences by industrial speakers).

I participated in the seminar organized in November 2017 by the RFI Ouest Industries Créatives, on the theme "Creative methods used in educational transformation". The objective was to work on the redesign of teaching modules by adopting creative methods.

Every year, I participate in the school's various recruitment and promotion actions: open days, student fairs, recruitment interviews, presentations at IUTs (institutions of higher education providing technician level training). As such, in 2016 and 2017, I made various films for the presentation of the ETN department, final year options and student projects. These films are currently available on the school's website <sup>2</sup>.

I was a member from 2005 to 2007 of the commission of specialists 61st joint section University of Nantes / Ecole Centrale de Nantes.

I participated in recruitment committees for the University of Nantes (in 2007 for position labelled 1169 and in 2010 for position labelled 1040), the University of South Brittany (in 2014 for position labelled 0939), INSA Rennes (in 2009 for position labelled 0169).

I initiated two partnership agreements between Polytech Nantes and the following foreign institutions: the University of Engineering and Architecture of Friborg in Switzerland (33 Polytech Nantes students on internship from 2007 to 2014), the University of Queensland in Australia (15 Polytech Nantes students on internship from 2015 to 2018).

I was president of one baccalaureate jury in 2008.

# C Summary of research activities

### C.1 Addressed area of research

The topic addressed in the context of my doctoral thesis was the optimization and implementation of digital communication algorithms on heterogeneous platforms, combining programmable signal processing processors and dedicated hardware resources. This experience was an opportunity to discover the many facets and research issues associated with the design of embedded system architectures. This area of research evolves according to the requirements in applications and possibilities of execution platforms. Thus, since the early 2000s, the constant increase in the dissemination of embedded systems, described in particular in [1], has led to the emergence and concretization of concepts such as the Internet of Things, data science and embedded artificial intelligence. This development requires mastering the complexity of the hardware-software architectures of embedded systems in order to allow the design of devices operating under numerous constraints (functionalities, cost, size, reliability, execution time, power and energy consumption, etc.). The field of research in the design of embedded system architectures to this in particular by proposing approaches, methods, models and tools used by the various participants in the design process.

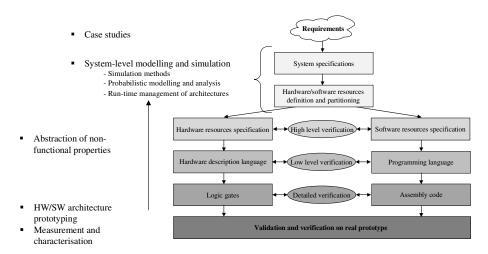

Since my integration at the University of Nantes in 2004, my research activity has gradually focused on system-level design and on the evaluation of the performance of hardware and software architectures. The objective of this work is to promote the modelling and analysis of architectures in order to allow optimized definition of resources under time, power consumption and cost constraints. The positioning of the work carried out in this context is illustrated in Figure 2.

Figure 2: Position of research activities in the field of hardware/software architectures design of embedded systems.

The objective of this work relates to the definition of methods favouring the creation of performance models used for the definition of hardware and software resources of architectures. The originality of this work lies in the combination of the aspects covered: simulation, formal modelling, static analysis and online management, implementations and measurements on real targets. Also, this work was inspired by case studies from different fields of application (mobile radiocommunication, automotive, image processing). This work and the contributions made are detailed in the following chapters of this document. The supervision activities and collaborations set up are listed below.

#### C.2 Supervision activities

#### • PhD thesis co-supervision

| QUENTIN DARIOL<br>Probabilistic symbolic simulation for embedded artificial intelligence multi-core<br>systems<br>Funding: grant from WISE-International (research consortium in Pays de la<br>Loire region).<br>Supervision rate: 50%<br>PhD thesis supervision: Sébastien Pillement (University of Nantes)                | Sep. 2020-xxx xxxx  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| <ul> <li>HAI-DANG VU</li> <li>Fast and accurate performance models for probabilistic timing analysis of SDFGs on MPSoCs</li> <li>Funding: grant from French Ministry of Higher Eduction (MESRI).</li> <li>Supervision rate: 60%</li> <li>PhD thesis supervision: Sébastien Pillement (University of Nantes)</li> </ul>      | Oct. 2017-Mar. 2021 |

| <ul> <li>SIMEI YANG</li> <li>Evaluation and design of a run-time manager for ultra-low power multiprocessor systems on chip</li> <li>Funding: China Scolarship Council (CSC)</li> <li>Supervision rate: 40%</li> <li>PhD thesis supervision: Sébastien Pillement (University of Nantes)</li> </ul>                          | Nov. 2016-June 2020 |

| TAKIEDDINE MAJDOUB<br><i>Transaction-level modelling methods for simulation efficiency improvement for</i><br><i>performance prediction of automotive architectures</i><br>Funding: grant from ANR (French agency for research), CIFAER project<br>Supervision rate: 60%<br>Supervision rate: Fabienne Nouvel (INSA Rennes) | Oct. 2009-Oct. 2012 |

| ANTHONY BARRETEAU<br><i>Transaction-level modelling methods for resource definition of future mobile</i><br><i>radiocommunication systems</i><br>Funding: grant from French Ministry of Higher Eduction (MESRI).<br>Supervision rate: 60%<br>Supervision rate: Jean-François Diouris (University of Nantes)                 | Oct. 2007-Dec. 2010 |

| Supervision of Master thesis                                                                                                                                                                                                                                                                                                |                     |

| DHARMENDER SINGH<br>A dynamic correction method for fast yet accurate simulation of multiprocessor<br>systems                                                                                                                                                                                                               | Feb. 2018-Jun. 2018 |

| JIATONG LI<br>Extraction of stochastic models for computation and communication time on a<br>multicore Zynq platform                                                                                                                                                                                                        | Feb. 2017-Jun. 2017 |

| NADIA GHAZALI<br>Execution trace analysis methods for performance modeling of embedded<br>system architectures                                                                                                                                                                                                              | Feb. 2015-Jun. 2015 |

| CHEN XI<br>Development of hardware-in-the-loop interfaces for ESL tools                                                                                                                                                                                                                                                     | Feb. 2009-Jun. 2009 |

| MARIA CHEIK WAFA<br>Transaction level modelling of a FlexRay communication network                                                                                                                                                                                                                                          | Feb. 2008-Jun. 2008 |

| Feb. 2007-Jun. 2007 |

|---------------------|

|                     |

| Feb. 2006-Jun. 2006 |

|                     |

#### • Participation in juries and thesis monitoring committees

I participated in two thesis juries as an examiner:

- M. Pelcat (INSA Rennes, 2010), Rapid prototyping and code generation for multi-core DSPs with application to the physical layer of 3GPP LTE base stations

- G. Roquier (INSA Rennes, 2008), Study of data flow models for multiprocessor software synthesis

I participated in three thesis juries as a guest member:

- M. Balluet (Université de Rennes 1, 2021), *Creation of an image analysis system for an automated microscope*

- S. Cotard (Université de Nantes, 2013), Contribution to the robustness of multicore real-time systems for the application domain

- L. Dorie (Université de Nantes, 2007), *Performance models for the codesign of reconfigurable systems: application to the software radio*

Finally, I participated in the thesis follow-up committees of Mr. Balluet and Mr. Chagneau.

#### C.3 Contracts and research projects

| <ul> <li>Coordinator for University of Nantes of the RFI WISE-International pSSim4AI<br/>project with OFFIS institute, Germany</li> <li>Object: This project deals with the evaluation and optimisation of performance of<br/>neural networks on multicore platforms.</li> <li>Partner: OFFIS (Oldenburg, Germany)</li> </ul>                                      | 2020-2023 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <ul> <li>Coordinator for University of Nantes of Hubert Curien Partnership PETA-MC with<br/>OFFIS institute, Germany</li> <li>Object: This project deals with the development and evaluation of probabilistic models<br/>and analysis methods for timing and energy prediction of multicore systems.</li> <li>Partner: OFFIS (Oldenburg, Germany)</li> </ul>       | 2019-2020 |

| <ul> <li>Coordinator for University of Nantes of the RFI WISE PETA-MC international project</li> <li>Object: This project deals with the development and evaluation of probabilistic models and analysis methods for timing and energy prediction of multicore systems.</li> <li>Partner: OFFIS (Oldenburg, Germany)</li> </ul>                                    | 2019-2020 |

| • <i>Coordinator of an industrial grant with Intel company</i><br>Object: Development of a C-code generation tool from the environment Intel CoFluent<br>Studio and experimentation with the Intel Galileo2 platform<br>Partner: Intel (Nantes)                                                                                                                    | 2016-2017 |

| <ul> <li>Invited researcher at University of Queensland, Australia</li> <li>Object: Research project about the improvement of simulation efficiency for early performance evaluation of multiprocessor systems.</li> <li>Partners : Adam Postula, Neil Bergmann (School of Information Technology and Electrical Engineering, University of Queensland)</li> </ul> | 2012-2013 |

Coordinator for University of Nantes of the ANR CIFAER project

Object: Design of innovative communication infrastructures for the automotive domain. Study and evaluation of communication infrastructures performance.

Partners: Atmel, See4sys, IRISA, IETR

Coordinator for University of Nantes of a GDR ISIS Young researcher project

2007-2011

2007-2011

2007-2011

2007-2011

2007-2011

2007-2011

2007-2011

2007-2011

2007-2011

2007-2011

Object: Optimisation of scheduling strategies for image and signal applications. Partners: IETR (Image team, INSA Rennes)

More generally, I set up strong exchanges with the team of Dr Kim Grüttner of the OFFIS institute (Oldenburg, Germany), specialized in the design of embedded systems. These exchanges have materialized through various projects by stays for myself in Germany in 2016, 2018 and 2019, stays for doctoral students and researchers in France and Germany in 2019 and 2020, internships for engineering students in Germany (four internships carried out from 2016 to 2019). In 2020, we started a thesis co-funded by OFFIS and RFI WISE.

## C.4 Publications

Over the period 2004-2021, since my installation at the University of Nantes, my scientific publications are distributed as follows:

- 7 publications in international journals

- 24 publications in international conferences

- 5 publications in national conferences

- 6 technical reports and project deliverables

The publications made as part of my doctoral thesis from 2000 to 2003 are divided into: 2 publications in international journals, 1 publication in a national journal, 3 publications in international conferences.

The full list of these publications is given in the appendix to this document.

### C.5 Member of boards and committees

From 2008 to 2011, I participated in the council of the IREENA laboratory as an elected member.

From 2012 to 2015, I participated in the Polytech Nantes research council as an elected member.

### C.6 Animation of research

Proofreading of articles for international journals: Eurasip Journal on embedded systems, Integration the VLSI journal, Eurasip Journal on advances in signal processing, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Elsevier Microprocessors and Microsystems.

Proofreading of articles for the Gretsi and DASIP conferences.

Participation in the program committee of the SDR-WinnComm conference in 2009 and 2010. Participation in the organizing committee of the DASIP conference in 2007.

Member of the ISIS and SOC2 research groups.

Organizer of the inter-GDR ISIS SOC2 day 'Modeling and design of mobile radiocommunication systems' in 2010. Invited talk at CEA in 2015, GDR SoC in 2007, GDR ISIS in 2006, in National Microwave days (JNM) in 2005.

Participation in the science day organized at the University of Nantes in 2019.

Scientific referent of the 'Embedded and secure communicating systems' axis within the new ASIC team of the IETR, from January 2022. Member of the working group 'Scientific Animation' of the IETR laboratory.

# **Chapter 1**

# Introduction

This chapter introduces and positions my research activities carried out since my installation at the University of Nantes in 2004. This work falls within the field of the design of hardware and software architectures of embedded systems. It focuses more particularly on design activities at the so-called system level, that is to say located at the earliest stage of the design process, where the choices of architectures are initially made. The challenges associated with this field of research come from the need to master the complexity of designing architectures. This complexity is induced by the constant increase in the density and diversity of the hardware and software resources that constitute architectures. Therefore, the objective of this work is to improve design practices by proposing methods used for defining under constraints and verifying the non-functional requirements of the architectures (in our work, time, power consumption and cost). This chapter first presents the context of the research work as well as the addressed issues. The nature of the contributions made is then presented. Finally, the organization of this document is explained.

## 1.1 Context

# **1.1.1** Evolutions and trends in the design of hardware-software architectures of embedded systems

A simple observation of the objects manipulated by everyone in our everyday life underlines the strong dissemination of electronic devices. These devices are embedded in equipment belonging to numerous and varied fields of application. The notion of embedded system designates those devices for which the internal architecture consists of an association of hardware and software resources. The design of these architectures strongly depends on the constraints specific to the field of application: constraints on the cost of the solution, execution time, electrical power consumption, robustness, security, dependability. Gradually, the evolution of manufacturing technologies [2] has led to hardware resources that are ever denser in number of transistors and therefore capable of supporting many uses. These hardware resources then make it possible to support the execution of software whose complexity is measured in terms of millions of lines of code that can be executed. This technological evolution is accompanied by a necessary evolution of design practices. This allows the complexity of the designed systems to be controlled. These practices are essential in order to guarantee the development of hardware and software architectures under specific constraints and this according to constrained development time and costs.

In 1983, Daniel Gajski and Robert Kuhn proposed in [3] to organize electronic circuit design practices according to three complementary points of view: the physical point of view, the behavioural point of view and the structural. It was proposed to consider these points of view according to three levels of detail according to which the hardware resources of a circuit can be described: the transistor level, the logic gate level, and the architectural level (also called register transfer level). The design process of hardware resources can thus be presented as a transformation of a behavioural representation (the what) into a structural representation (the how) which, associated with a progressive refinement from the architectural level to the transistor level, leads to an actual realization in a given manufacturing technology. This proposal underlines the need to organize

the design based on structuring principles that can guide the designer in his work.

During the 1990s, integrated circuits made it possible to support complete systems on a chip, combining processor cores, local memories and dedicated hardware resources. To appropriately design these systemson-chips (SoCs) and meet the related constraints, the selection of hardware and software resources must be carefully optimized. Different approaches, such as those presented in [4], emerged in order to guide the designer in the phases preceding the partitioning between hardware and software and the joint optimization of resources (*hardware-software codesign*). Various proposals were made in order to establish levels of abstraction higher than the architectural level [5], [6] in order to capture the specificities of hardware and software resources at the earliest stage of the design process. Also, given the preponderant influence of interactions between resource categories, the importance of distinguishing computation mechanisms from communication mechanisms as soon as possible was highlighted [7], [8]. Added to these trends is the need to promote the reuse of existing resources (*Intellectual Property*, IP), at the different levels of abstraction in the design process. The concept of platform-oriented design (*platform-based design*) emerged [9] in order to have generic and easily adaptable execution supports according to application needs.

During the 2000s, systems-on-chip integrated several heterogeneous processors whose characteristics differ according to the specificities of the software to be executed. These years saw the emergence of so-called system-level design languages (SLD) including SystemC, standardized in 2012 [10], SystemVerilog [11] and SpecC [12]. These languages are adapted to the description of the characteristics of hardware and software resources. They notably support the separation of communication and calculation mechanisms as well as the possibility of modelling and simulating an architecture according to different levels of abstraction. Thus, these languages were used to carry out various design activities (resource sizing, software modelling and validation using virtual prototypes, integration of hardware-software resources) and were adopted by industry [13].

The evolution observed during the 2010s tends towards the integration of multi-core processors and an ever-increasing number of hardware resources within systems on chips. As underlined in [14] and [15], this constant increase in the complexity of systems justifies consolidating the methods used at the system level in order to favour the dimensioning under constraints of hardware-software architectures. According to these tendencies, system-level design therefore plays an essential role in the design process due to the fact that any modification of the initial choices generates additional costs that are all the higher as they are detected late.

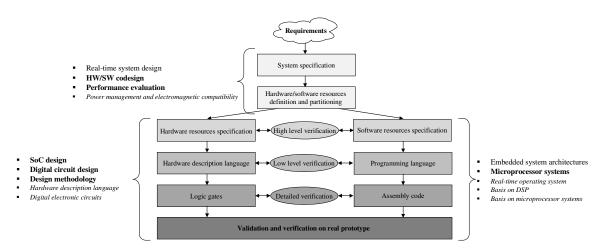

#### 1.1.2 Principles of electronic system-level design

As mentioned previously, electronic system-level design (ESL) aims to establish a hardware-software resource architecture that meets the different requirements of the system under study. Figure 1.1 illustrates some of the principles previously mentioned through the Y diagram used in 2009 by Gajski in  $[16]^1$ . This figure positions in particular the design activities at the system level. These activities assume the use of models capturing the different aspects of the studied architecture and making it possible to estimate its particular properties and to check compliance with the constraints. As illustrated in Figure 1.1, modelling a hardware-software architecture supposes to consider the following different aspects<sup>2</sup>:

- **Functional view**: it is described independently of the targeted technologies, focusing on the expected functionalities for the studied system. This view is represented according to two complementary approaches: structural and behavioural. This representation is generally based on the use of a computational model (MoC, *model of computation*) adapted to the characteristics of the functionalities to be described [18].

- **Executive view**: it displays the components capable of realizing the elements of the functional view. These components are conventionally classified into computation resources, communication resources and storage resources. Subsequently, we will also use the term platform to refer to this view.

- **Physical view**: designates the result of the deployment, the allocation, of the elements described in the functional view onto the components of the executive view.

<sup>&</sup>lt;sup>1</sup> In this simplified representation of the Y diagram, only four levels of abstraction are identified. In more detailed versions, five levels are exhibited, highlighting the functional analysis of the systems to be designed. <sup>2</sup> The terms used to designate these views frequently differ. At this stage, we use the terms used in [17].

Figure 1.1: The Y diagram with detailed at the system level, inspired from [16]. The main activities led at the system level are identified.

As indicated in Figure 1.1, complementary activities are associated with the establishment of these views, in order to favour the selection of resources (through the estimation of the complexity of the elements of the functional architecture) and to establish policies for arbitration and scheduling of shared resources.