# Differential Mode and Common Mode Modeling of Pulse Transformers for Gate-Driver Applications

Loreine Makki

## ► To cite this version:

Loreine Makki. Differential Mode and Common Mode Modeling of Pulse Transformers for Gate-Driver Applications. Electronics. Nantes Université, 2022. English. NNT: . tel-03760232v1

# HAL Id: tel-03760232 https://hal.science/tel-03760232v1

Submitted on 25 Aug 2022 (v1), last revised 8 Nov 2022 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

# NANTES UNIVERSITE

ECOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Electronique – Génie Electrique

# Par Loreine MAKKI

Differential Mode and Common Mode Modelling of Pulse Transformers for Gate-Driver Applications

Thèse présentée et soutenue à Nantes, le 27 Juin 2022 Unité de recherche : IETR UMR CNRS 6164

#### Rapporteurs avant soutenance :

Denis LABROUSSEMaître de Conférences/HDR, CNAM ParisPaul-Etienne VIDALProfesseur des universités, ENI Tarbes

#### **Composition du Jury :**

| Président :             | Jean-Charles LE BUNETEL | Professeur des universités, Université de Tours                 |

|-------------------------|-------------------------|-----------------------------------------------------------------|

| Examinateurs :          | Denis LABROUSSE         | Maître de Conférences/HDR, CNAM Paris                           |

|                         | Paul-Etienne VIDAL      | Professeur des universités, ENI Tarbes                          |

| Directeur de thèse :    | Christophe BATARD       | Maître de Conférences/HDR, Nantes Université                    |

| Co-directeur de thèse : | Nicolas GINOT           | Professeur des universités, Nantes Université                   |

| Co-encadrant de thèse : | Marc Anthony MANNAH     | Associate Professor, Lebanese International University, Lebanon |

# TABLE OF CONTENTS

| GLOSSARY                                                                       |    |

|--------------------------------------------------------------------------------|----|

| ACKNOWLEDGMENTS                                                                | 7  |

| DEDICATION                                                                     |    |

| RESUME EN FRANÇAIS                                                             |    |

| GENERAL INTRODUCTION                                                           |    |

| CHAPTER I: STATE-OF-THE-ART                                                    |    |

| A. POWER CONVERSION SYSTEMS' STRUCTURE                                         |    |

| A.1 Overview                                                                   | 10 |

| A.1 OVERVIEW<br>A.1.1 Power Conversion System Background                       |    |

| A.1.2 Switched-Mode Converters                                                 |    |

| A.1.3 Fundamentals of DC-AC Converters                                         |    |

| A.2 Power Semiconductor Devices                                                |    |

| A.2.1 State-of-the-Art: Power Semiconductors                                   |    |

| A.2.2 Innovations in WBG Power Devices                                         |    |

| A.2.2.1 SiC MOSFETs                                                            |    |

| B. GATE DRIVER TOPOLOGIES                                                      |    |

|                                                                                |    |

| B.1     FUNCTIONAL SPECIFICATIONS       B.2     GALVANIC ISOLATION REQUIREMENT |    |

| B.2 GALVANIC ISOLATION REQUIREMENT<br>B.3 PLANAR TECHNOLOGY                    |    |

| B.3.1 Galvanic Isolation: Pulse Planar Transformers                            |    |

| B.3.2 Dielectric Material                                                      |    |

|                                                                                |    |

| C. ELECTROMAGNETIC COMPATIBILITY COMPLIANCE                                    |    |

| C.1 INTERPRETATION OF EMC, EMI, EME AND EMS                                    |    |

| C.2 CATEGORIZATION OF EMI IN POWER CONVERTERS                                  |    |

| C.2.1 Conducted Signals in Electrical Circuits                                 |    |

| C.2.1.1 Differential Mode Noise                                                |    |

| C.2.1.2 Common Mode Noise                                                      |    |

| C.3 EMC CHALLENGE: PULSE TRANSFORMERS IN GATE DRIVERS                          |    |

| C.4 STANDARDS AND REGULATIONS                                                  |    |

| C.4.1 PCB Optimal Assembly                                                     |    |

| D. CM NOISE REDUCTION TECHNIQUES IN SMPS                                       | 41 |

| D.1 OVERVIEW                                                                   |    |

| D.2 FARADAY SHIELDING INSERTION MECHANISMS                                     |    |

| D.2.1 Convenient Shielding Designs                                             |    |

| D.2.1.1 Single or multi-Shield                                                 |    |

| D.2.1.2 Novel Shielding Designs                                                |    |

| D.3 NUMERICAL ANALYSIS                                                         |    |

| E. CONCLUSIONS                                                                 |    |

| CHAPTER II: NUMERICAL ANALYSIS APPROACH                                        | 47 |

| A. EMC MODELLING                                                               | 47 |

| A.1 State-of-the-Art                                                           |    |

| A.1.1 Choke Modelling                                                          |    |

| A.1.1.1 Physical Model                                                         |    |

| A.1.1.2 Behavioral Model                                                       |    |

| A.1.2 Multiconductor Cable Modelling                                           |    |

| A.1.3 Motor Modeling                                                           |    |

|      | A.1.4 HF Capacitor and Resistor Models                           |    |

|------|------------------------------------------------------------------|----|

|      | A.1.5 PCB and Interconnects                                      |    |

|      | A.1.6 Power Semiconductor Models                                 |    |

| A.2  |                                                                  |    |

| A.3  |                                                                  |    |

| B. F | PARASITIC EXTRACTION TOOL                                        | 52 |

| B.1  | Ansys Q3D Extractor                                              | 52 |

| B.2  |                                                                  |    |

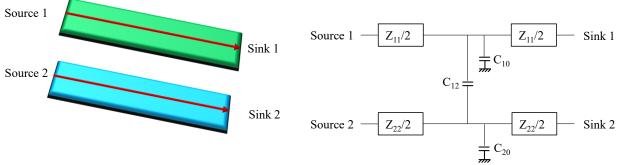

| B.3  | Parasitic Capacitance Computation                                | 54 |

| C. / | ARTIFICIAL ANALYSIS                                              | 56 |

| C.1  | 010112110                                                        |    |

|      | C.1.1 Computer-Aided Design                                      |    |

|      | Automated Design Scheme                                          |    |

|      | C.2.1 Data Exchange Files                                        |    |

|      | C.2.2 AnsTranslator                                              |    |

|      | C.2.3 Generic Design Blueprint                                   |    |

| D. ( | CASE STUDY: POWER TRANSFORMER ANALYSIS                           | 61 |

| D.1  |                                                                  |    |

| D.2  |                                                                  |    |

| D.3  |                                                                  |    |

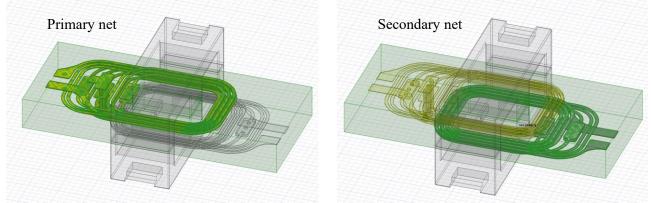

|      | D.3.1 Identifying Nets                                           |    |

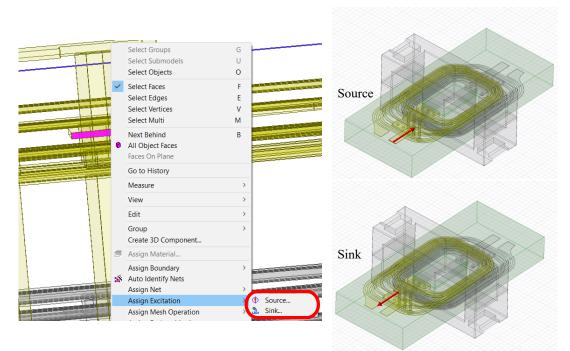

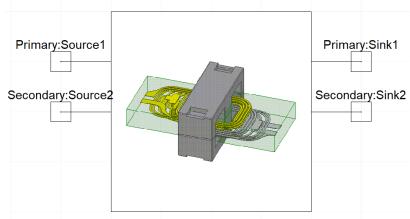

|      | D.3.2 Assign Excitations                                         |    |

|      | D.3.3 Defining Mesh Operations<br>D.3.4 Specify a Solution Setup |    |

| L    | D.3.4 Specify a Solution Setup<br>D.3.4.1 Frequency Sweep        |    |

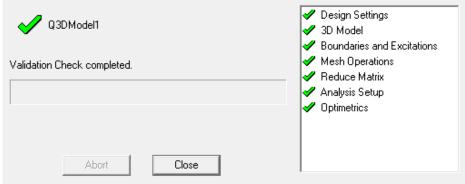

| Ĺ    | D.3.5 Q3D Validation and Analysis                                |    |

| Ĺ    | D.3.6 Post Processing and Generating Reports                     |    |

| Ĺ    | D.3.7 Reducing Matrices                                          |    |

|      | D.3.7.1 Float Net                                                | 71 |

|      | D.3.7.2 Ground Net                                               |    |

|      | D.3.7.3 Float Terminal<br>D.3.7.4 Float at Infinity              |    |

|      | D.3.7.5 Return Path                                              |    |

| D.4  |                                                                  |    |

| E. ( | CONCLUSIONS                                                      | 73 |

|      | PTER III: ENDORSEMENT OF SIMULATION MODELLING TECHNIQUE          |    |

|      | GALVANICALLY ISOLATED GATE DRIVERS                               |    |

|      |                                                                  |    |

| B. F | PULSE PLANAR TRANSFORMER DESIGN                                  |    |

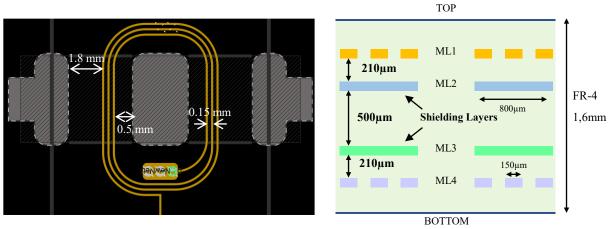

| B.1  | Transformer Scheme                                               | 79 |

| B.2  |                                                                  |    |

| B.3  | SIGNAL TRANSMISSION AND ELECTRONIC CIRCUITRY                     | 81 |

| C. 1 | TRANSFORMER SCATTERING PARAMETERS                                | 83 |

| C.1  | Pulse Transformer Efficient Frequency Band                       |    |

| C.2  |                                                                  |    |

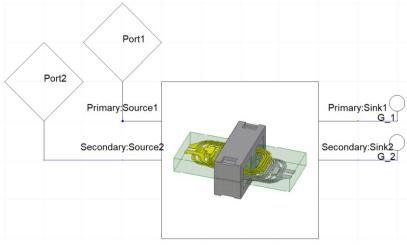

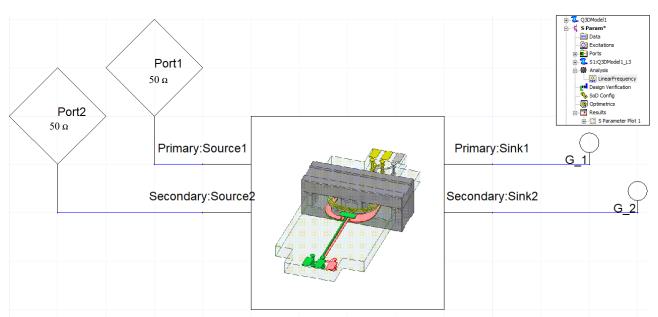

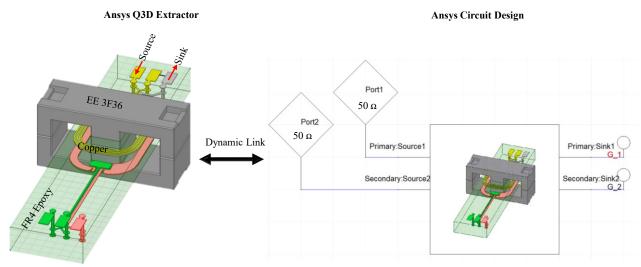

| (    | C.2.1 Ansys Circuit Design Dynamic Link                          |    |

| C.3  |                                                                  |    |

| D. ( | COMMON MODE TRANSIENT IMMUNITY                                   | 91 |

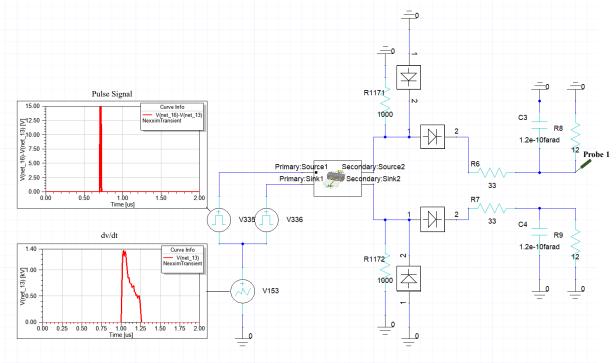

| D.1  | Sub-Circuit dv/dt Immunity Test                                  |    |

| D.2  |                                                                  |    |

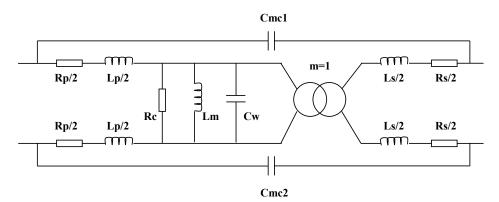

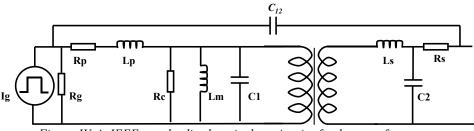

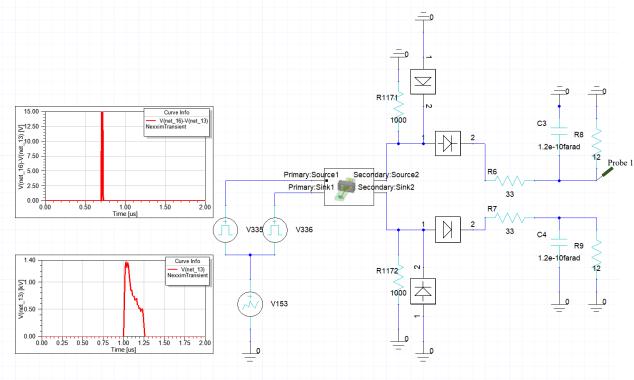

| L    | D.2.1 Generic Corresponding Circuit Model                        |    |

|      |                                                                  |    |

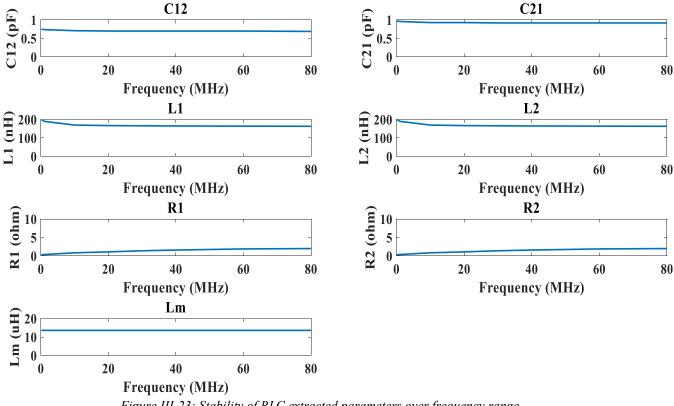

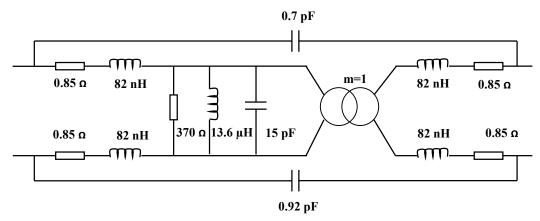

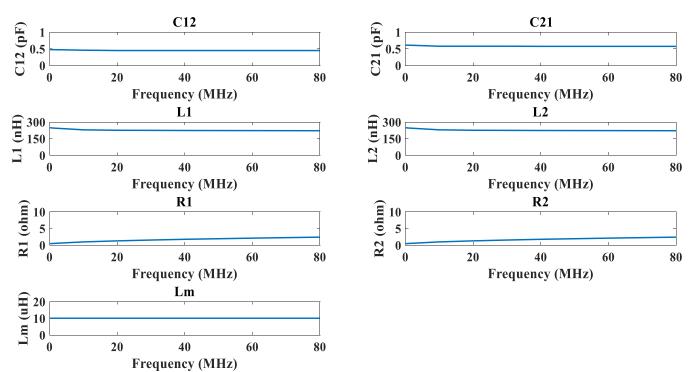

|    | D.2.2 Pulse Transformer Parameter Extraction                                                                    |     |

|----|-----------------------------------------------------------------------------------------------------------------|-----|

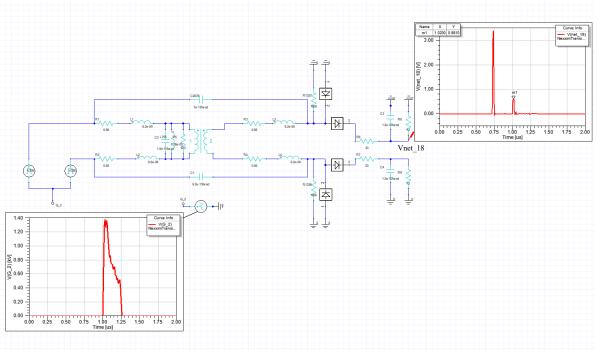

|    | D.2.3 Equivalent Model Susceptibility Test                                                                      | 95  |

| C  | .3 Experimental Examination                                                                                     |     |

|    | D.3.1 Experimental Circuit Arrangement                                                                          |     |

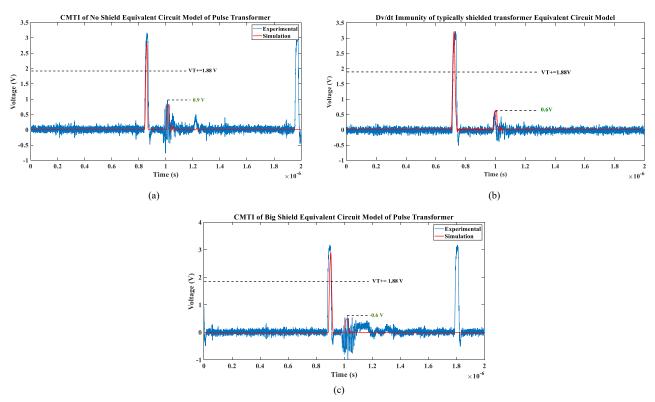

|    | D.3.2 dv/dt Immunity Results                                                                                    |     |

| Ε. | CONCLUSIONS                                                                                                     | 99  |

| CH | APTER IV: SHIELDING STRUCTURE DESIGN FOR MULTI-LEVEL GATE DRIVER OF SIC                                         |     |

| MO | SFETS                                                                                                           | 102 |

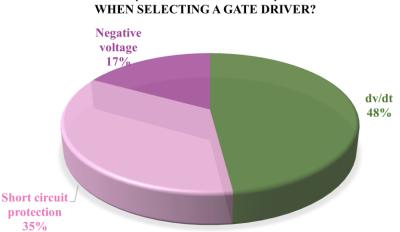

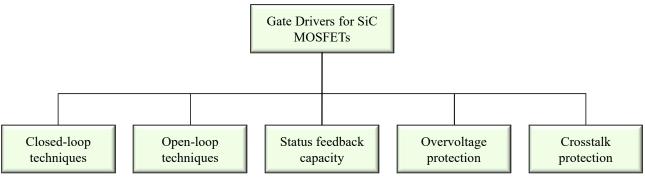

| Α. | GATE DRIVERS FOR SIC MOSFETS                                                                                    | 102 |

| A  | .1 COMMERCIAL SIC MOSFET GATE DRIVERS                                                                           | 103 |

| A  | .2 MULTI-LEVEL ACTIVE GATE DRIVER TOPOLOGY FOR SIC MOSFETS                                                      | 105 |

| в. | RENOVATED PULSE TRANSFORMER SCHEME                                                                              | 106 |

| B  | .1 COMPLIANCE TO STANDARDS                                                                                      | 107 |

| E  | .2 Pulse Transformer Synopsis                                                                                   | 107 |

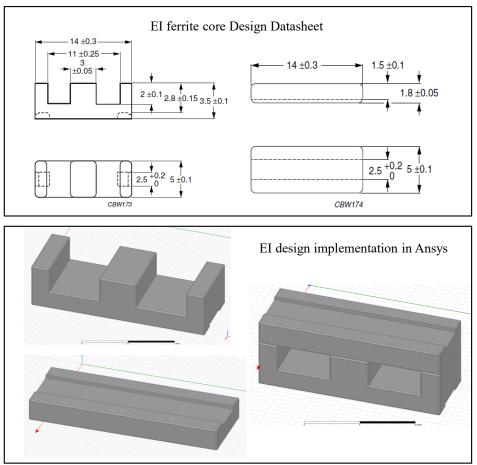

|    | B.2.1 Magnetic Core Specifications                                                                              | 107 |

|    | B.2.2 Winding Number of Turns                                                                                   | 108 |

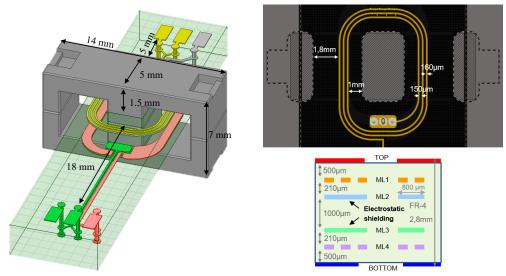

|    | B.2.3 Definite Transformer Scheme                                                                               |     |

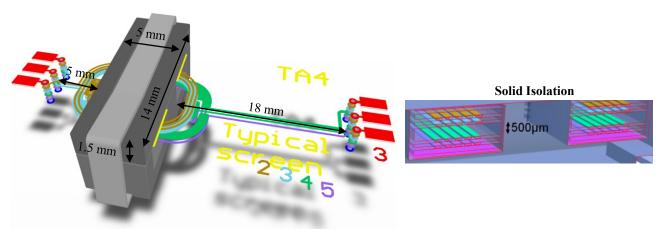

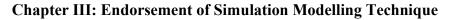

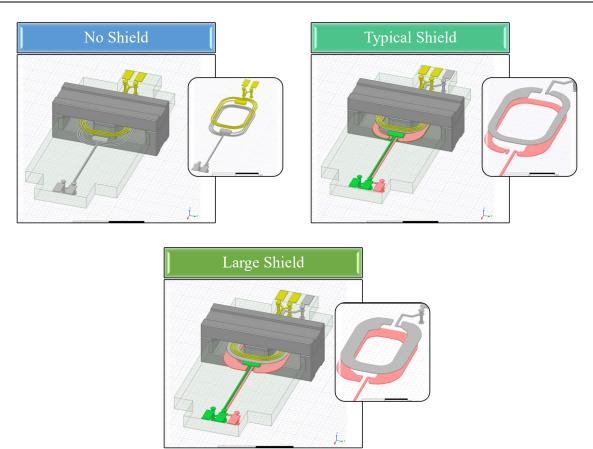

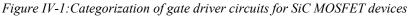

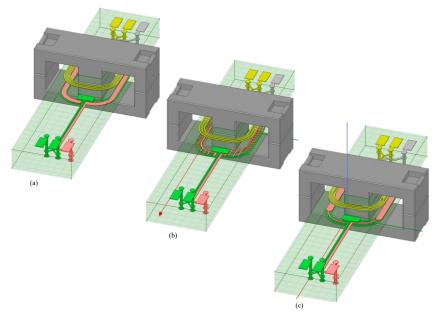

| B  | .3 Shielding Structure Designs                                                                                  | 109 |

| C. | SHIELDING EFFECTIVENESS ON TRANSFORMERS' CMTI                                                                   | 113 |

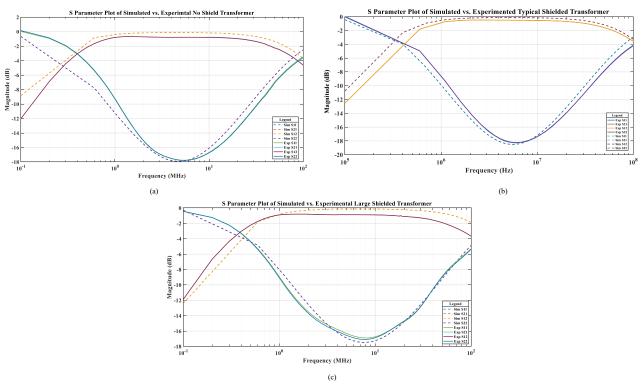

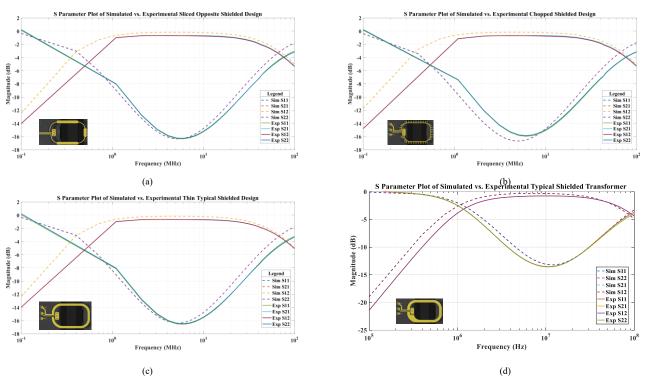

| C  | 1 S Parameter Examination                                                                                       |     |

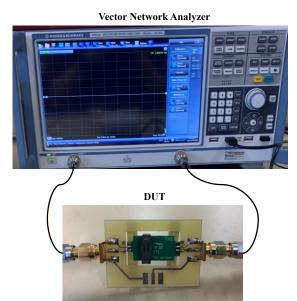

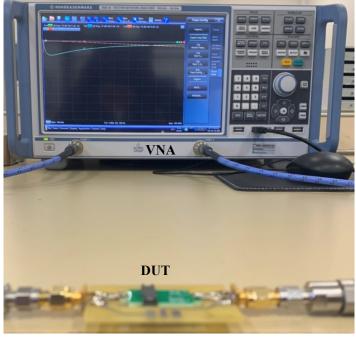

|    | C.1.1 S Parameter Authentication                                                                                |     |

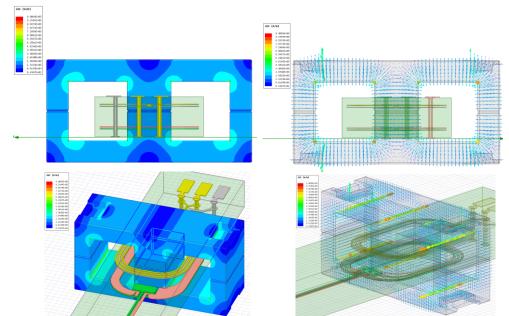

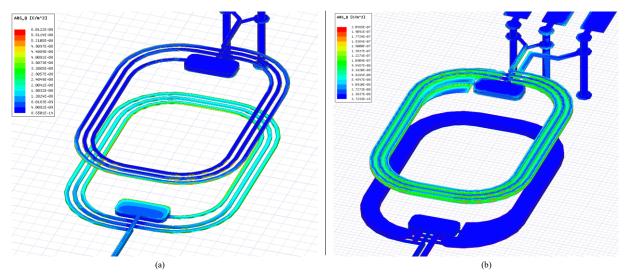

| -  | 2 Ansys Q3D Field Plot Generation                                                                               |     |

| -  | 3 Shield Efficacy on CMTI – Subcircuit Analysis                                                                 |     |

| -  | 4 CM Equivalent Circuit Model                                                                                   |     |

| C  | 5 EXPERIMENTAL VALIDATION                                                                                       |     |

|    | C.5.1 Transformer Susceptibility Experimental Set-Up<br>C.5.2 Shielded Transformers Susceptibility Test Results |     |

|    |                                                                                                                 |     |

| D. | EXPLORATIONS AND PERSPECTIVES                                                                                   |     |

| C  | .1 DIELECTRIC MATERIAL SIGNIFICANCE                                                                             |     |

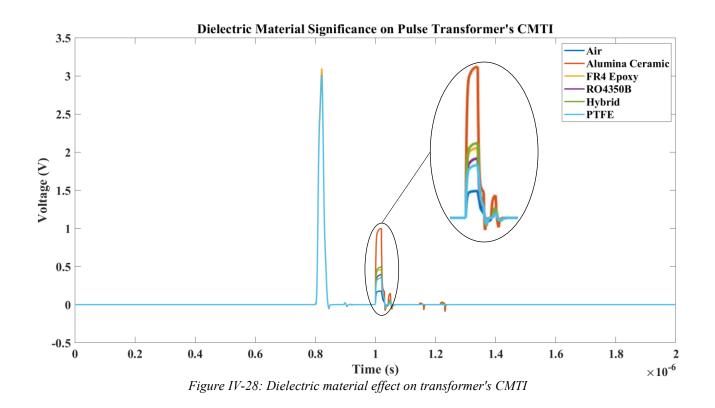

|    | D.1.1 Dielectric Material Consequence on CMTI                                                                   | 127 |

| Ε. | CONCLUSIONS                                                                                                     | 129 |

| GE | NERAL CONCLUSION AND OUTLOOK                                                                                    | 130 |

| А. | CONCLUSIONS AND CONTRIBUTIONS                                                                                   | 130 |

| A  | .1 Simulation Analysis                                                                                          | 130 |

| A  | .2 Pulse Transformer Modelling                                                                                  | 131 |

| A  | .3 Shielding Structure Design                                                                                   |     |

| A  | .4 DIELECTRIC MATERIAL IMPORTANCE                                                                               | 133 |

| в. | RECOMMENDATIONS AND FUTURE WORK                                                                                 | 133 |

| RE | ERENCES                                                                                                         | 135 |

# GLOSSARY

| AC   | Alternating Current                     |  |

|------|-----------------------------------------|--|

| AGD  | Active Gate Drivers                     |  |

| AEF  | Active EMI Filters                      |  |

| BJT  | Bipolar Junction Transistor             |  |

| CAD  | Computer-Aided Design                   |  |

| CAGR | Compound Annual Growth Rate             |  |

| СМ   | Common Mode                             |  |

| CMR  | Common Mode Rejection                   |  |

| CMTI | Common Mode Transient Immunity          |  |

| CMTN | Common Mode Transient Noise             |  |

| CMTV | Common Mode Transient Voltage           |  |

| DC   | Direct Current                          |  |

| DK   | Dielectric Constant                     |  |

| DM   | Differential Mode                       |  |

| EMC  | Electromagnetic Compatibility           |  |

| EMI  | Electromagnetic Interference            |  |

| EMS  | Electromagnetic Susceptibility          |  |

| ΕΤΟ  | Emitter Turnoff                         |  |

| EV   | Electric Vehicle                        |  |

| FCC  | Federal Communications Commission       |  |

| FEM  | Finite Element Method                   |  |

| GaN  | Gallium Nitride                         |  |

| GTO  | Gate Turn-off                           |  |

| HFET | Heterojunction Field Effect Transistors |  |

| HFPT | High Frequency Planar Transformers      |  |

| HPDC | High-Power Density Converters           |  |

| НТЕ  | High Thermal Electronics                |  |

|      |                                         |  |

| IEC                                                          | International Electrochemical Commission                                                                                                                                                                        |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IGBTs                                                        | Insulated Gate Bipolar Transistors                                                                                                                                                                              |  |  |

| IGCT                                                         | Integrated Gate Commutated Thyristors                                                                                                                                                                           |  |  |

| JFET                                                         | Junction-Gate Field-Effect Transistor                                                                                                                                                                           |  |  |

| LNA                                                          | Linear Network Analysis                                                                                                                                                                                         |  |  |

| MoM                                                          | Method of Moments                                                                                                                                                                                               |  |  |

| MOSFETs                                                      | Metal Oxide Semiconductor Field Effect Transistors                                                                                                                                                              |  |  |

| РСВ                                                          | Printed Circuit Board                                                                                                                                                                                           |  |  |

| PCSs                                                         | Power Conversion Systems                                                                                                                                                                                        |  |  |

| PE                                                           | Power Electronics                                                                                                                                                                                               |  |  |

| PGS                                                          | Patterned Grounded Shield                                                                                                                                                                                       |  |  |

| PPE                                                          | Personal Protective Equipment                                                                                                                                                                                   |  |  |

| PTFE                                                         | Polytetraflouorethylene                                                                                                                                                                                         |  |  |

|                                                              |                                                                                                                                                                                                                 |  |  |

| S Parameters                                                 | Scattering Parameters                                                                                                                                                                                           |  |  |

| S Parameters<br>SBD                                          | Scattering Parameters<br>Schottky Barrier Diodes                                                                                                                                                                |  |  |

|                                                              | C C                                                                                                                                                                                                             |  |  |

| SBD                                                          | Schottky Barrier Diodes                                                                                                                                                                                         |  |  |

| SBD<br>Si                                                    | Schottky Barrier Diodes<br>Silicon                                                                                                                                                                              |  |  |

| SBD<br>Si<br>SiC                                             | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide                                                                                                                                                           |  |  |

| SBD<br>Si<br>SiC<br>SCR                                      | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide<br>Silicon-Controlled Rectifiers                                                                                                                          |  |  |

| SBD<br>Si<br>SiC<br>SCR<br>SGS                               | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide<br>Silicon-Controlled Rectifiers<br>Solid Ground Shields                                                                                                  |  |  |

| SBD<br>Si<br>SiC<br>SCR<br>SGS<br>SMD                        | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide<br>Silicon-Controlled Rectifiers<br>Solid Ground Shields<br>Surface Mount Device                                                                          |  |  |

| SBD<br>Si<br>SiC<br>SCR<br>SGS<br>SMD<br>SOC                 | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide<br>Silicon-Controlled Rectifiers<br>Solid Ground Shields<br>Surface Mount Device<br>State of Charge                                                       |  |  |

| SBD<br>Si<br>SiC<br>SCR<br>SGS<br>SMD<br>SOC<br>SMPS         | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide<br>Silicon-Controlled Rectifiers<br>Solid Ground Shields<br>Surface Mount Device<br>State of Charge<br>Switch Mode Power Supplies                         |  |  |

| SBD<br>Si<br>SiC<br>SCR<br>SGS<br>SMD<br>SOC<br>SMPS<br>UVLO | Schottky Barrier Diodes<br>Silicon<br>Silicon Carbide<br>Silicon-Controlled Rectifiers<br>Solid Ground Shields<br>Surface Mount Device<br>State of Charge<br>Switch Mode Power Supplies<br>Undervoltage-Lockout |  |  |

# **ACKNOWLEDGMENTS**

First and foremost, I would like to express my sincere gratitude to all my directors, as words alone cannot reveal how grateful I am and will always be. I would like to wholeheartedly thank Dr. Christophe Batard for his continuous support throughout all my PhD study period. His immense knowledge and observation, motivation and recognition, trustworthiness and compassion will forever be treasured. I deeply acknowledge his continued assistance and consideration under all circumstances, which demonstrated an exceptional international collaboration that actually made me always feel at home. I would like to profoundly thank my co-directors Prof. Nicolas Ginot and Dr. Marc Mannah. I highly acknowledge Prof. Nicolas Ginot for his constant support, intellectual ideas, guidance, assistance and mentorship, this research would not have been possible without his expertise and encouragement. I would like to reveal my appreciation towards Dr. Marc Mannah for granting me this research opportunity, his constant consultation and feedback and his trust in my abilities. In addition, a heartfelt thank you to Dr. Anne-Sophie, for her appreciated support and motivation throughout the course of my study. I am truly very fortunate and privileged and could not ask for better mentors.

I profoundly acknowledge Nantes University and all its administrative staff which paved the pathway to realize this research study. Likewise, I would also like to deeply thank the Lebanese International University, especially Vice President, Dr. Samir Abou-Nassif, for his support, recommendation, cooperation and assistance. In addition, deep appreciation goes to all my faculty members at the school of Engineering, directed by Dean of School of Engineering, Prof. Amin Haj-Ali, as their transferred expertise and knowledge is the foundation of this research work.

Many thanks are further directed to my examination committee members, Prof. Paul-Etienne Vidal, Prof. Jean-Charles le Bnetel and Dr. Denis Labrousse, as their constructive review and feedback and professional advice farther improved this research study. Their support and appreciated consideration of the hardships experienced in Lebanon in addition to a worldwide pandemic, while conducting the study, is dearly acknowledged and did not go unnoticed.

Furthermore, I truly appreciate Julien Weckbrodt, for all the clarification given at the beginning of this thesis and his offering of the needed information for the effective launching of the thesis.

I would like to thank Sandrine Charlier for taking care of all necessitated administrative documents and her recognized cooperation.

I had the privilege to share the office with friends from different countries and cultures whom made my experience lively and worthwhile. Naming a few, thank you, Antoine Laspeyres, Corentin Darbas, Guillaume Martin, Quentin Dariol, Tamar Mosiashvili, Roua Boulifa, Alexis Duhamel, Fatima El Bouchikhi, May Myat Thu and all colleagues at IETR lab. This cultural blend further enriched my doctoral experience and brought me to meet admirable acquaintances.

I dedicate this thesis to my parents Zeinab Youssef and Ali Makki, as an expression of gratitude and admiration, as this achievement would not have been possible without their cherished guidance and never-ending support. No words could ever describe how grateful, thankful and blessed I am to have you by my side, everything I am is because of you. I heartily acknowledge my brother Dr. Issa Makki and his beloved wife Malak, and my dearest sisters Sandra and Sara for their encouragement, reinforcement and assurance.

To my beloved husband, Hussein Fneiche, your love, reassurance, faith in my abilities and standing by myside through this long journey is graciously treasured.

# **DEDICATION**

To my parents, Zeinab Youssef and Ali Makki

# **Resume en Français**

Dans les années 1990, l'arrivée de composants de puissance à base de silicium (MOSFET, IGBT) a permis le développement de convertisseurs d'énergie électrique à forte densité de puissance. De nos jours, la mise en œuvre de composants à base de matériaux dits « grand gap » tels que le carbure de silicium (SiC) fait l'objet de nombreux travaux de recherche. Ces nouveaux matériaux autorisent le fonctionnement des convertisseurs à de plus hautes températures et à des tensions plus élevées, permettant un nouvel accroissement de la densité de puissance. De plus, la réduction drastique des durées de commutation (donc des pertes par commutation) des composants SiC permet d'envisager au moins deux scénarios. Le premier consiste à ne pas augmenter la fréquence de découpage des convertisseurs actuels ce qui a pour conséquence d'accroitre le rendement de ces derniers. Un deuxième scénario consiste à accroitre la fréquence de découpage des interrupteurs tout en conservant le rendement du convertisseur. Le gain est alors porté sur la discrétion de la compatibilité électromagnétique (CEM) du convertisseur. Ces dernières années, les industriels ont commercialisé des diodes et des transistors SiC sous la forme de modules de puissance de type MOSFET. Ces composants sont actuellement disponibles dans des boîtiers dédiés aux systèmes sur PCB ou sous la forme de modules pour des convertisseurs de moyenne puissance (> 10kVA) et basse tension (< 3kV).

L'augmentation de la densité de puissance s'appuie généralement sur l'augmentation de la tension d'alimentation des convertisseurs. La traction électrique est un exemple parmi d'autres où les réseaux s'échelonnent de quelques centaines de volts à plusieurs dizaines de kilovolts pour les applications à très fortes puissances. L'arrivée sur le marché de composants MOSFET SiC crée de nouvelles opportunités pour des domaines de l'électronique de puissance avides de densité de puissance toujours plus grande. Des recherches en cours pour fabriquer des puces SiC dont le calibre en tension de 3,3 kV permet d'imaginer des convertisseurs avec des réseaux d'alimentation proches de 2 kV.

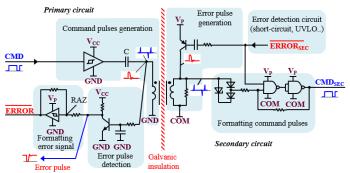

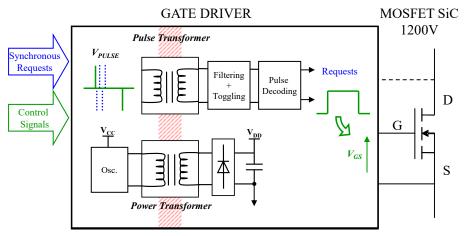

L'utilisation optimale de ces composants passe par le développement d'un étage de commande rapprochée (nommé gate-driver) adapté et prenant en compte la spécificité de la technologie SiC. Les drivers de base assurent une fonction de pilotage en régime bloqué - passant du semi-conducteur. Les drivers plus évolués, dédiés aux composants équipant les convertisseurs de moyenne puissance, possèdent en plus des fonctions sécuritaires (essentiellement sous-tension d'alimentation et désaturation) qui indiquent la présence ou non d'un défaut de fonctionnement de la puce. Les informations échangées entre les étages au plus près du composant de puissance (étages secondaires) et l'étage primaire (relié directement au système de contrôle qui gère l'ensemble des commandes et la sécurité) sont transmises par l'intermédiaire de transformateurs d'impulsions ou de fibres optiques.

L'énergie électrique nécessaire aux voies de commande nécessite aussi une alimentation isolée galvaniquement. Pour les applications de moyenne puissance, cette dernière se fait systématiquement par un transformateur d'impulsions.

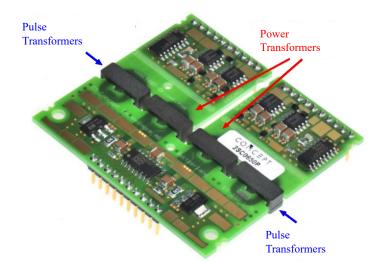

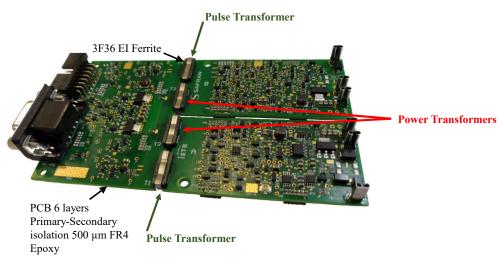

Les gate-drivers développés au laboratoire IETR mettent en œuvre 4 transformateurs d'impulsions : 2 sont dédiés à la transmission de l'énergie électrique du primaire aux voies de

#### **Résumé En Français**

commande, 2 autres sont dédiés à la transmission des ordres de commandes et sont aussi un canal de transmission de données. Pour garantir la sécurité des utilisateurs, des normes imposent des distances minimales à respecter entre l'étage primaire et les étages secondaires d'un gate-driver. Des travaux de recherche actuels au sein de l'IETR portent sur l'intégration de nouvelles fonctions de monitoring au sein des gate-drivers.

Ce projet de recherche traitera uniquement de la problématique de l'isolation galvanique des signaux de commande par l'intermédiaire de transformateurs d'impulsions, car leurs capacités à fonctionner à une fréquence élevée ont amené de nouveaux défis à résoudre tels que les problèmes d'interférence électromagnétique (EMI). De plus, l'augmentation de la vitesse de commutation des MOSFETs SiC entraîne des dv/dt de plus en plus élevés, ce qui induit des courants de mode commun traversant les capacités parasites du transformateur. Ces perturbations peuvent provoquer une transmission de commandes défectueuses au module de puissance et entraîner un court-circuit de bras.

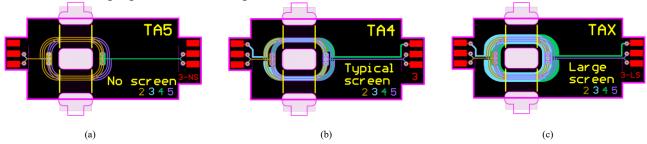

L'objectif visé est l'amélioration du design du transformateur d'impulsion. Il est composé d'une ferrite et deux enroulements, un primaire et un secondaire. Au primaire comme au secondaire, des écrans électrostatiques (appelés aussi écrans de Faraday ou blindage) sont disposés. Chaque écran est relié au potentiel de référence des circuits électroniques auxquels ils sont associés. Ainsi, l'un est au potentiel de référence de l'électronique du primaire et l'autre au potentiel de référence de la voie de commande. Ils sont destinés à drainer les courants de mode commun vers un point particulier du circuit électronique afin de limiter les perturbations qu'ils induisent. Le design actuel de ces écrans ne repose sur aucune étude théorique, mais sur un savoir-faire et une expérience acquise depuis des années. Un des objectifs de la thèse est de définir le design de ces écrans électrostatiques par le biais de modèles et de simulations.

De même, le design de ces transformateurs d'impulsions est variable selon les habitudes des industriels ou des laboratoires de recherche. Le transformateur d'impulsion développé à l'IETR est de type planaire avec ces enroulements intégrés au PCB. Il possède également un écran électrostatique par enroulement.

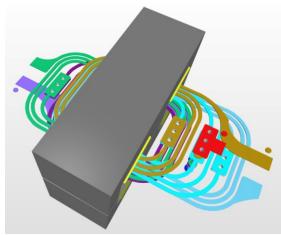

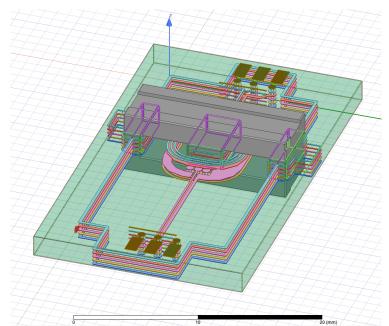

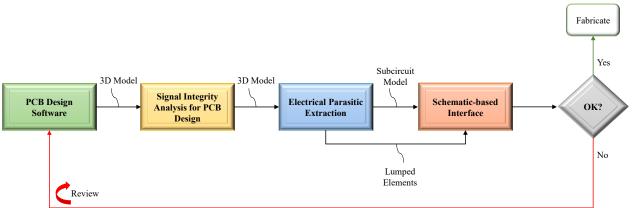

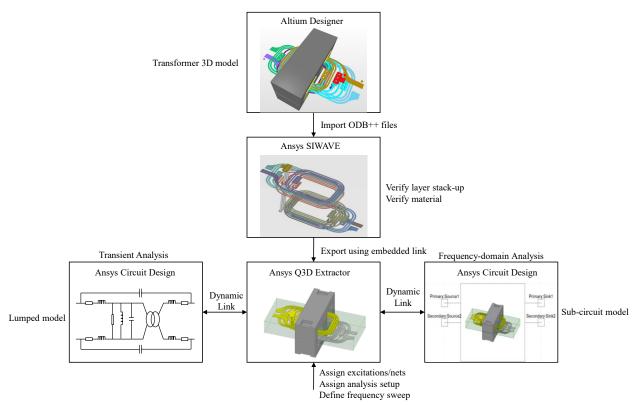

Le but principal de cette thèse est de définir l'importance de ces écrans dans les transformateurs planaires. Le fil conducteur de ces travaux est le suivant : dessinés à partir du logiciel Altium Designer, les transformateurs sont ensuite modélisés avec l'outil Ansys Q3D Extractor et différents modèles sont obtenus. L'immunité des transformateurs est ensuite testée en simulation et les meilleurs designs de transformateurs sont sélectionnés. Les transformateurs sélectionnés sont ensuite fabriqués et des tests expérimentaux sont effectués afin de confirmer les simulations. Ainsi, le mémoire de thèse est constitué d'une introduction générale, quatre chapitres, une conclusion et des perspectives.

Au chapitre I, une introduction générale présente l'état de l'art de tous les aspects importants d'un système de convertisseur de puissance : introduction aux bases des systèmes de conversion de l'énergie électrique, aux bases des semi-conducteurs de puissance, à l'émergence des matériaux à large bande interdite et à leurs intégrations dans les applications de commande de grille. La topologie du gate-driver et de ces principales fonctions sont discutées. Ce chapitre met en évidence l'importance

#### **Résumé En Français**

du transformateur à technologie planaire et à son intégration dans les gate-drivers, en présentant les avantages et les inconvénients de cette technologie.

Les normes de compatibilité électromagnétique sont présentées et la catégorisation des interférences électromagnétiques dans les convertisseurs de puissance est expliquée. Enfin, les techniques de réduction du bruit en mode commun dans les systèmes de convertisseurs de puissance sont précisées et les techniques d'atténuation sont examinées. En particulier, les techniques d'insertion d'écrans de Faraday dans les transformateurs planaires sont présentées avec des aspects pratiques tout en discutant de l'importance de l'outil de simulation avant la phase de fabrication de prototypes.

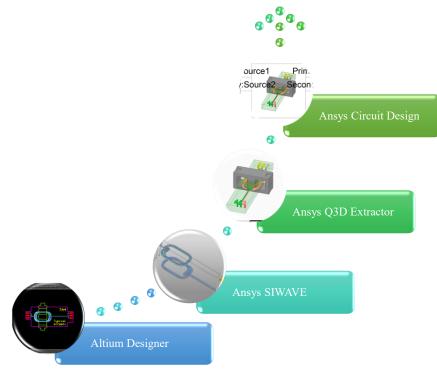

Le chapitre II établit la chaîne complète de modélisation, avec plusieurs outils logiciels tels que Altium Designer, Ansys SIWAVE, Ansys Q3D Extractor et Ansys Cicuit Design. Le processus de modélisation est présenté à l'aide d'un exemple. L'étude en simulation de l'immunité du transformateur soumis à des forts dv/dt, tels que ceux rencontrés expérimentalement, permet de réduire le temps de conception des transformateurs et accroit la sureté de fonctionnement des gate-drivers.

Le processus de simulation décrit précédemment est exploité au chapitre 3. Des transformateurs planaires déjà fabriqués pour une précédente thèse et qui étaient destinés à piloter des MOSFET SiC 1,2 kV sont modélisés et simulés. La modélisation avec l'outil Ansys Q3D Extractor prend en compte le comportement du transformateur en mode différentiel et en mode commun. Elle intègre également une impédance de source et de charge connectées respectivement au primaire et au secondaire du transformateur. La validation de cette approche est effectuée en comparant des résultats de simulation à des mesures expérimentales. Un train d'impulsions d'amplitudes 1,4 kV avec un dv/dt égal à 125 kV/µs a été appliqué entre les 2 enroulements du transformateur et le niveau de bruit au niveau de l'étage secondaire a été mesuré et comparé aux simulations.

En parallèle, un modèle électrique équivalent pour le transformateur a été déduit. Dans un premier temps, une analyse spectrale de la forme des impulsions a été effectuée pour déterminer la bande de fréquences utiles. Dans un second temps, cette bande de fréquence est fournie à Ansys Circuit Design, ce qui permet d'obtenir les paramètres S du transformateur. Ces paramètres sont ensuite comparés à la mesure des paramètres S du transformateur 'réel'. La comparaison des paramètres S simulés avec ceux mesurés est satisfaisante. Dans un troisième temps, cette bande fréquentielle est ensuite paramétrée dans Ansys Q3D Extractor afin de déduire les paramètres électriques équivalents du transformateur. Ainsi, un modèle de type LTspice a été établi pour une fréquence définie de 50 MHz, cette fréquence étant choisie après l'analyse spectrale des impulsions. Puis ce modèle est simulé dans les conditions expérimentales précédentes. Les résultats de simulation et les mesures effectuées sont proches. En conclusion, la méthodologie mise en place pour modéliser des transformateurs mis en œuvre dans une précédente thèse est validée et est mise en œuvre au chapitre suivant pour concevoir de nouveaux designs de transformateurs intégrés dans des gate- drivers pilotant des modules MOSFETs SiC de 3,3 kV.

Dans le chapitre IV, des nouveaux écrans de Faraday sont dessinés et étudiés en simulation. L'immunité de ces nouveaux transformateurs soumis à des forts dv /dt est testé en simulation pour

#### **Résumé En Français**

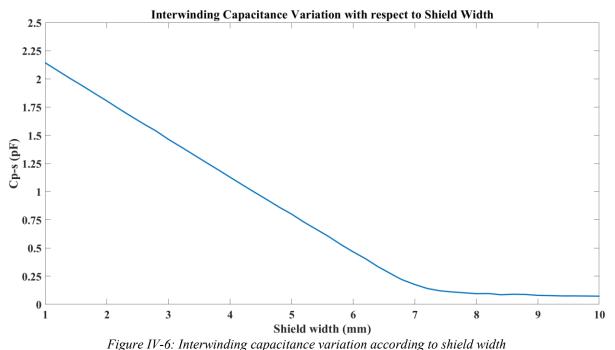

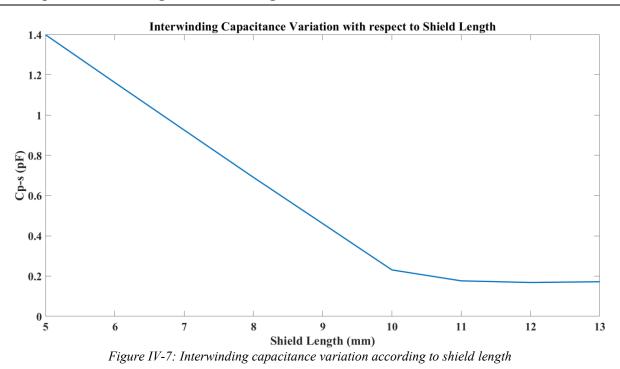

différents paramètres géométriques. L'influence de la forme des écrans, de leur longueur, leur largeur et leur épaisseur est étudiée. Deux structures de blindage, solides et fragmentés, sont simulés. Le niveau de bruit au secondaire du transformateur est quantifié en simulation et les meilleurs designs de transformateurs sont sélectionnés. Les transformateurs sélectionnés sont ensuite fabriqués et des mesures expérimentales sont effectuées. La comparaison entre les mesures et les simulations valide l'approche effectuée. De plus, ce chapitre met en évidence l'effet du choix des matériaux diélectriques employés sur la variation de la susceptibilité des transformateurs d'impulsions.

Le chapitre V résume les travaux de recherche menés durant cette thèse et des perspectives de travaux futurs sont proposées.

# **GENERAL INTRODUCTION**

Scientific exchange and collective contribution to the pool of knowledge is the primary objective of researching and economic growth. This research has been conducted under the framework of international thesis co-supervision. It is a mutually supervised doctoral program by the University of Nantes (UN), France and the Lebanese International University (LIU), Lebanon. In Lebanon, theoretical research was conducted and simulative analysis was performed. Moreover, financial support was granted upon performing research and instructing activities at the university. In France, simulation and experimental validation was conducted at IETR laboratory with the entire team. In addition, financial assistance and accommodation was granted during the research visit period.

For several years, the IETR laboratory team at University of Nantes conducted alternative researches encompassing gate driver circuit topologies. The established studies are always harmonized with the continual advancements of those topologies persevering substantial improvement in this domain. During the period in France, the research was conducted at IETR laboratory, Chantrerie site, accompanied with the ASIC team. Research and scientific exchange with scholars at the site, naming Antoine Laspeyres and Corentin Darbas, was very perceptive as intellectual cooperation is opportune for advanced and auspicious ideas. This thesis explicitly focuses on the common mode and differential mode modelling of pulse planar transformers integrated in gate driver applications, serving as the product of a previous thesis conducted at IETR laboratory and a complementary thesis to Antoine's prospective dissertation, which will be outlined thereafter.

In the 1990s, silicon-based power semiconductor devices (MOSFETs, IGBTs), piloted the development of high-power density converters. Moreover, continual advancements lead to the breakthrough of wide bandgap (WBG) semiconductor materials based on silicon carbide (SiC) and gallium nitride (GaN), permitting power electronic components to operate at higher temperatures, superior voltages, further power density attainments and realizing exceptional switching speeds. Adequately harnessing these capabilities, whilst safeguarding electromagnetic compatibility (EMC) standards, can lead to dramatic energy savings in diversified industrial applications. Recently, the market encountered a substantial commercialization of SiC diodes and MOSFET power modules. These components are currently serviceable as elements devoted for PCB system integration or as modules for medium power and low voltage converters.

The optimal exploitation of these distinctive devices is by means of PCB-integrated gate driver technologies. A gate driver circuit is an indispensable constituent of a power electronic system, it serves as an interface between microcontrollers that manage the switching operations (low voltage side) and the connected power module (high voltage side). This requires a galvanic isolation barrier that electrically isolates primary to secondary circuitry with discrete ground references. Gate drivers provide at least two operations, that include signal transmission and power supply. The fundamental concern of this thesis is the examination of switching order transmission through the galvanic isolation. Technologies such as optocouplers and pulse transformers are commonly recognized for

realizing the latter. For medium power applications, planar pulse transformers serve as the predominantly shared isolation technology amongst semiconductor manufacturers.

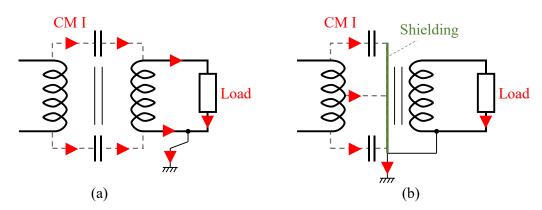

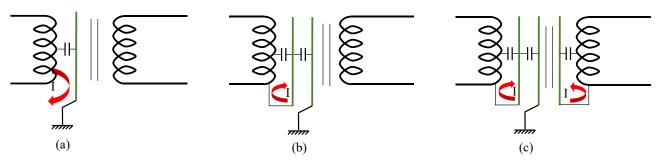

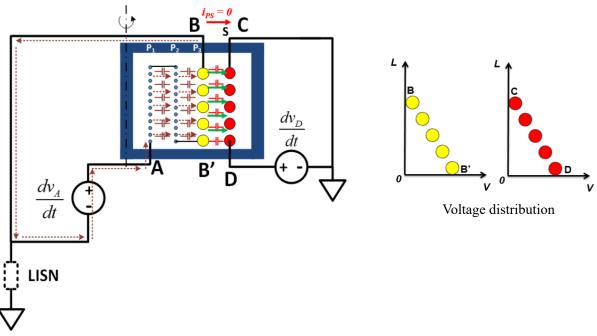

Nonetheless, this constructive blend of advanced technologies, originates severe alertness towards sustaining electromagnetic compatibility (EMC) standards. The realization of higher switching frequencies is worthwhile as long as it does not contribute to electromagnetic disturbances. However, an ample potential variation induces the development of common mode (CM) currents in gate driver circuits, which are mainly routed through interwinding capacitances of pulse planar transformers. This issue is alarming, as a faulty trigger of the semiconductor device originating from the unwanted pulsating currents can lead to hazardous results. Therefore, this highlights the necessity to mitigate CM current passage through the transformers by reducing the stray capacitance, renowned as the interwinding capacitance between the primary and the secondary windings. This dilemma can be resolved by acquiring proper installation of securely grounded electrostatic screens, which are acknowledged as faraday shielding layers. The actualized pulse planar transformers at IETR lab, which were integrated in a realized gate driver card intending to drive 1.2 kV SiC MOSFETs, were based on knowledge and expertise in the field; laying the foundation of this conducted thesis.

The main focus of this thesis is to groundwork the importance of faraday shielding insertion in pulse planar transformers by primarily modelling and analyzing the realized planar transformer prototypes via Ansys Q3D Extractor tool. Firstly, the objective is to set a theoretical and a simulative prospective that legitimize the formerly obtained experimental results. The agreeable results will affirm the dv/dt immunity of the transformers, hence, ensuring faraday shielding integration significance when responding to a steep potential variation applied between the primary and the secondary distinctive grounds. Moreover, novel ameliorated designs of the pulse transformer will be presented, examining alternative shielding design configurations, aiming to study the common mode transient immunity (CMTI) of the transformers and construct a corresponding equivalent circuit model that represents individual transformers. Accordingly, the thesis will be sectioned into four main chapters and a conclusion with perspectives.

**Chapter I**, a collective introduction, will present the state of the art of all prominent aspects of a power converter system. Initiating with basics of power conversion systems, fundamentals of power semiconductors, emergence of wide-band-gap material and the integration in gate driver applications. Moreover, challenges comprising the utilization of the latter technology will be presented, specifically regarding pulse transformers in gate driver applications, and means of mitigation techniques highlighted in literature will be reviewed.

**Chapter II** will accurately define the simulation methodology utilized with collective software tools, primarily Ansys Q3D Extractor, aiming to model, analyze and investigate the intended pulse planar transformer. The process will be explicitly and exceptionally presented in this thesis using a demonstrative example in this chapter.

**Chapter III** will verify the simulation process discussed in chapter II, by investigating already realized shielded pulse planar transformers that intended to drive 1.2 kV SiC MOSFETs. The latter will be simulated to duplicate an experimental realization and investigate the transformer's endurance to abrupt dv/dt application. Moreover, similar analysis will be implemented on a constructed equivalent circuit model of the transformers.

**Chapter IV** demonstrates an altered pulse planar transformer integrated into a distinctive gate driver card aiming to drive 3.3 kV SiC MOSFETs, where novel and ameliorated shielding designs will be investigated whilst evaluating the transformers' persistence to high switching transients. In addition, this section will also highlight the effect of dielectric material selection on the interwinding capacitance of the pulse transformers.

Finally, **Chapter V** concludes the thesis and briefly summarizes the main contributions and essential propositions. In addition, a forecast on possible future works is established.

# **CHAPTER I: STATE-OF-THE-ART**

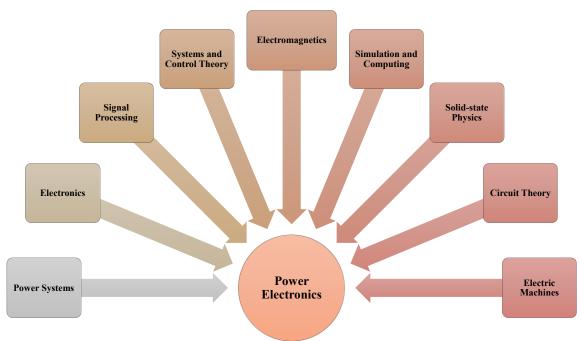

Power Electronics (PE) is a preeminent field of study in electrical engineering which acquires boundless areas of development and improvement, entitled as a "quiet revolution" [1]. As depicted in figure I-1, this field is enforced in wide ranges of electrical energy operations, granting it a multidisciplinary attribute.

Figure I-1: Multidisciplinary attribute of Power Electronics

The evolution of electronic devices over the past few years has resulted in compelling impacts on the community and industry. Gradual technological leaps in the field of semiconductors and power devices are forecasted to structure the mechanized sector of the revolutionized globe [2], [3]. Robust power electronic systems are demanded in automotive, energy management, telecommunication, medical, and aeronautic applications [4]. Since 1970, the power density of power electronic converters in diverse operations has nearly doubled every ten years [5]. The primary agent of this trend was the proficiency to increase the switching frequency by a multiple of ten every decade, which was realized by the incessant improvement of power semiconductor device technologies [6]. This continual advancement of power density converters is portrayed by the demanded requirements for higher efficiency and reliability, volume reduction, lightweight materials, and cost effectiveness. Substantial research and examinations have been applied to different aspects of the aforementioned power converter system constituents to attain significant efficiency and power density objectives. However, optimization always comes with a cost; with every advancement, researchers and analysts are confronted with challenges and impediments to realize upgraded power converter designs.

# A. POWER CONVERSION SYSTEMS' STRUCTURE

# A.1 Overview

## A.1.1 Power Conversion System Background

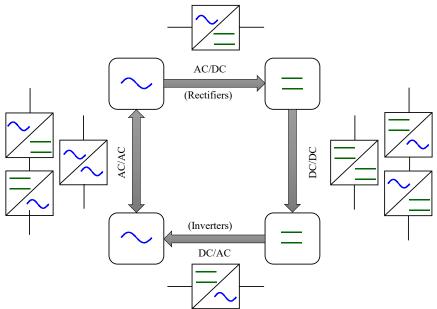

The fundamental objective of power electronic technology is to transform and regulate the flow of electrical energy aiming to supply optimum voltages and currents that fulfill user-defined requirements. Power Conversion Systems (PCSs) serve as an interconnection between incongruent types of electricity, such as alternating current (AC) sources with distinctive frequencies, direct current (DC) sources of dissimilar voltage magnitudes, AC and DC supplies, and a merger of all the latter as depicted in figure I-2. As observed, inverters and rectifiers are represented by a single-stage energy conversion model, whereas, AC/AC and DC/DC converters can additionally be realized by implementing two conversion stages using a DC and an AC link, respectively [7]. Formerly, sophisticated rather inefficient, electromechanical devices were used to attain such conversions, where the competency to interconnect two varied DC voltages was practically unattainable. This discloses the governance of AC technology for power transmission and distribution during that period. Currently, economical, competent and versatile power electronic converters are extensively used universally [8].

Figure I-2: Basic forms of power converters

A prevalent example is one's cellphone, which requires fixed and secured DC voltages for convenient functioning. This is achieved by converting the AC supply at the household to a compatible DC voltage using an AC/DC converter or rectifier. Furthermore, DC/DC converters are needed to convert the wavering DC voltage due to the battery's state of charge (SOC) into a steady DC voltage for the electronics. As for non-digital devices, motors that are driven directly from the AC grid acquire the grid's rotational frequency and their manufactured frequency, where it is beneficial to decouple these two frequencies. This is attained by using an AC/DC rectifier, followed by a DC to AC inverter at any relevant frequency, creating a variable speed drive (VSD) [8].

#### A.1.2 Switched-Mode Converters

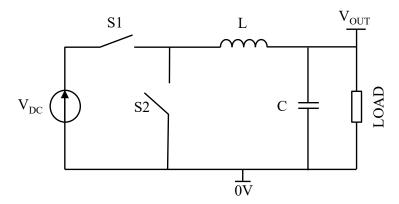

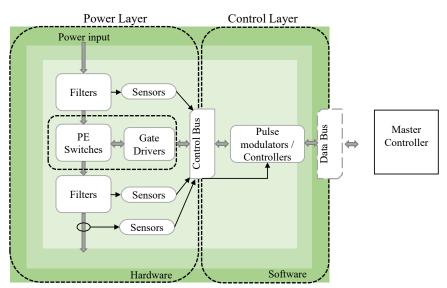

Power electronic converters such as controlled rectifiers or choppers can be utilized to regulate the DC power for DC drives, contrarily, AC drives employ inverters to modify the voltage and frequency of the AC power. Switched-mode converters are DC-DC converters that supply DC loads with regulated output voltage that is either stepped up or stepped down, referred to as boost converter and buck converter, respectively. The chopper circuit is termed as a boost converter if the output voltage is greater than the input voltage, whereas a buck converter is identified when the output voltage is lower than the input voltage. Moreover, a buck-boost converter combines the functions of the latter in a single circuit and can be utilized in wide applications such as battery power systems. A fundamental DC-DC conversion solution is depicted in figure I-3 below, comprising switches S1 and S2 which represent at least one active device such as a power semiconductor and one passive component such as a diode, that operate in accordance to an external control signal. Thus, a 'control circuit' is utilized in all power converter applications as presented in figure I-4, to constantly monitor and compare the output voltage against an embedded 'reference voltage', initiating corrective action if the output drifts from its appointed value.

Figure I-3: Ideal DC-DC step-down converter circuit (buck converter)

Figure I-4: Block diagram of power electronics arrangement

#### A.1.3 Fundamentals of DC-AC Converters

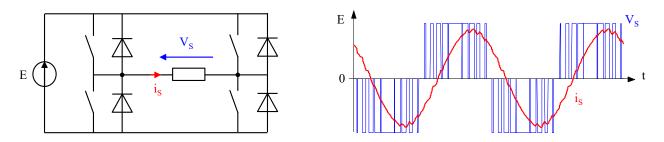

DC-AC converters are well-known as inverters, their role is to change a DC input voltage into a symmetric AC output voltage of intended magnitude and frequency. Applications such as adjustable-speed ac motor drives, uninterrupted power supplies (UPS), grid integration of renewable energy resources and electric vehicle battery charging systems demand the utilization of inverters [9]. Ideally, the output voltage waveforms of inverters are sinusoidal. However, practically, the waveforms are non-ideal and contain harmonics as shown in the exemplary of a full bridge inverter represented in figure I-5 thereafter.

Figure I-5 : Single-phase full bridge inverter with associated waveforms

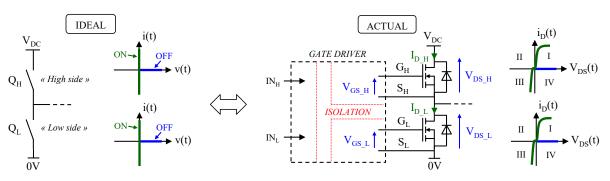

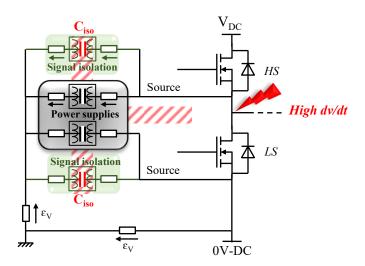

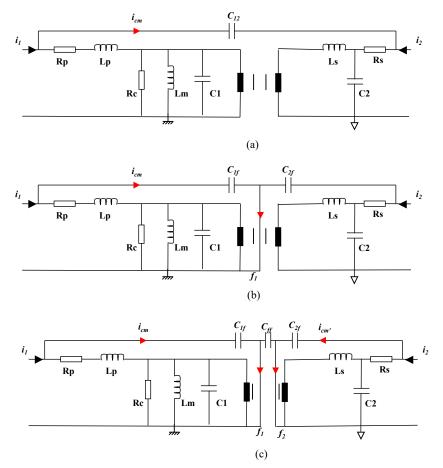

A full bridge inverter requires four diodes and four self-commutating switches which can be controlled (ON/OFF) using modulation signals. Each diode is connected in antiparallel to the switch. The useful power level application of such inverters ranges from 200 to 2000 VA. There are diverse contemporary and controllable power electronic switches that can be utilized such as relays, thyristors, Insulated Gate Bipolar Transistors (IGBTs) and Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) [10]. The output frequency of this type of inverter may be controlled by regulating the switch on and off times of the latter mentioned components. Figure I-6 represents an example of a half bridge switching cell, known as the vertical arm of a full bridge inverter, comprising two N-type MOSFETs that are unidirectional in voltage and bidirectional in current. The depiction highlights that the practical switching time of the MOSFETs are relatively prolonged with respect to the theoretical switching times, in addition to the inevitability of a galvanic isolation safeguarding independent transistor control [11]. It is imperative to protect the depicted switching cell against a short circuit occurrence [12]. Henceforth, it is common to integrate a time delay, termed as 'dead time', between the conducting and blocking phases of the transistors, to compensate for the difference between the conducting and blocking times. MOSFET transistors operate in the '1st quadrant' and  $3^{rd}$  quadrant' corresponding respectively to the phases where (V<sub>DS</sub> >0, I<sub>D</sub>>0) and (V<sub>DS</sub> <0, I<sub>D</sub><0) as revealed in figure I-6.

Figure I-6: Basic example of a switching arm with N-MOSFET transistors

## A.2 Power Semiconductor Devices

#### A.2.1 State-of-the-Art: Power Semiconductors

Power semiconductor devices resemble the concrete foundation of power electronic systems. They play an indispensable role in determining the system's efficiency, size and cost. Originating from the invention and marketing of silicon (Si) bipolar junction transistor (BJT) sixty years ago, a considerable collection of Si power semiconductor devices have been promoted and commercialized, enabling power electronic systems to attain ultra-high efficiencies and power capacities required for various applications [13].

Currently, power converters are designed to envelope a broad range of power levels, from gigawatt in high-voltage direct current (HVDC) transmission systems to a few watts necessitated to function a mobile phone. As mentioned earlier, since power conversions can be processed various times before reaching the end-user, it is excessively crucial to realize high energy conversion efficiency in power electronic converters. This is associated to the amelioration of power semiconductor devices by the reduction of conduction and switching losses. In the last six decades, to meet high power density demands, more reliability, superior switching frequency levels whilst maintaining cost effectiveness, diversified current conduction mechanisms have been developed. The main innovation stimulant is to achieve power devices that can conduct more current for a defined chip area and breakdown voltage, hence improving the conductivity of the device when it is in the ON state, and the controllability of the alternating ON/OFF state occurrences.

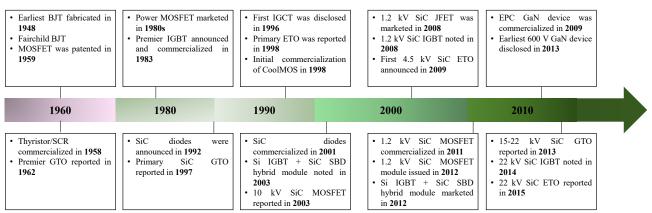

A historical perspective of the latest development of power semiconductor devices is presented thenceforth in figure I-7 highlighting their augmentation and commercialization events.

Figure I-7: Pivotal power semiconductor development and commercialization story line

As illustrated above, the inauguration of this technology with a transistor based on Germanium material took place at Bell Lab in 1948 [13]. Silicon bipolar junction transistor (BJT) and siliconcontrolled rectifiers (SCR), or thyristors were marketed in 1958. Controlled three terminal switches such as BJTs and gate turn-off (GTO) thyristors were popularized in the 1960s and 1970s for power supply and motor drive applications [14]. In the 1980s, two popular inventions were developed that displaced the utilization of BJTs: MOSFETs which possesses exceptional static and dynamic performance and a gate control interface [15], and IGBTs [16] which profited from the power MOSFET fabrication process, however depended on a different physics where both electrons and holes contribute to current conduction, replacing GTO in most high power applications. In the mid-1990s, inventive super junction MOSFETs further reduced the conduction loss of power MOSFETs below the renowned 'silicon limit' [17]. The spotlight in the late 1990s was on integrated gate commutated thyristors (IGCT) and emitter turnoff (ETO) thyristors, which made high power GTOs feasible in ultra-high power converters [18], [19]. Subsequently, major innovative outbreaks occurred such as Schottky barrier diodes (SBD) [20], silicon carbide (SiC) MOSFETs [21] and heterojunction field effect transistors (HFET) based on gallium nitride (GaN) material [22].

#### A.2.2 Innovations in WBG Power Devices

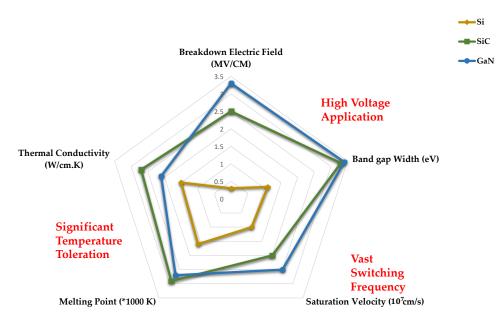

Although Si-based IGBTs have been on the market for more than thirty years, they have reached their physical limits when confronted with the demand of high-power density converters (HPDC) and therefore higher switching frequencies [23]. The breakthrough of WBG device technology gained tremendous momentum serving as a pivotal enabler to achieve miniaturization of power electronic systems [24]–[30]. Furthermore, the emergence of commercial WBG semiconductor devices based on SiC- silicon combined with carbon-, GaN- gallium and nitrogen- and also diamond, prompted ample reduction in conduction losses due to their lower on-resistance. Moreover, they are featured with notable inferior gate capacitance, permitting them to operate at exceptional frequencies[31]. This technology farther lifted the borderline of power semiconductor devices to realize superior voltages, greater frequencies and higher temperatures as disclosed in figure I-8 below [32], [33]. Harnessing these capabilities, will allow WBG semiconductors to foreshadow intriguing innovations in power electronics, solid-state lighting and other various applications across numerous industrial and renewable energy sectors.

Figure I-8: Intrinsic properties of semiconductor materials: Si, SiC, GaN

The elemental agents that stirred the engagement and commercialization of SiC and GaN over their Si counterpart are their intrinsic material properties – bandgap, electric field and electron mobility, compared thereafter in table I-1.

| Parameter                      |                          | Si   | GaN  | SiC |

|--------------------------------|--------------------------|------|------|-----|

| Band GapeV                     |                          | 1.12 | 3.4  | 3.2 |

| <b>Critical Electric Field</b> | MV/cm                    | 0.3  | 3.3  | 2.2 |

| <b>Electron Mobility</b>       | $cm^2/V. s$              | 1400 | 1800 | 950 |

| Permittivity                   | ε <sub>r</sub>           | 11.8 | 9    | 9.7 |

| Thermal Conductivity           | W/cm°C                   | 1.5  | 1.3  | 4.9 |

| Saturation Velocity            | $10^7 \cdot \text{cm/s}$ | 1    | 2.7  | 2.7 |

Table I-1: Comparison of semiconductor material properties [34]

As conferred, Si comprises a band gap just above an electron volt with a critical electric field of 0.3 MV/cm, differently, these specifications are much wider and greater for GaN and SiC revealing a tighter bond between the compositions of the material. The opportune realization of a high critical electric field, E<sub>c</sub>, enables slimmer, more eminently doped voltage blocking layers in the devices, resulting in a considerable on-resistance reduction amounting to 1/10 in comparison to Si devices. To minimize conduction losses, high voltage Si MOSFETs are characterized with large chip areas, creating a high gate capacitance and notable losses at high switching frequencies. On the other hand, Si IGBTs exploit minority carriers and conductivity modulation, thus, acquire smaller die footprints than MOSFETs, yet the durability of minority carriers restrains the device's maximum switching frequency attainments. Accordingly, in correlation to a Si-based device, the integration of a high breakdown electric field, moderate conduction losses and short-term carrier lifetime, WBG materials can operate at a considerably higher frequency with a miniature footprint of 1/5 in comparison to Si

devices, using the same blocking voltage and on-resistance. The sparse intrinsic carrier concentration of these materials enables robust high-temperature operation due to low leakage currents [35].

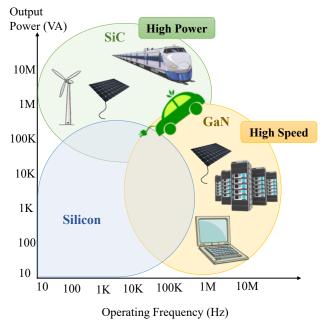

SiC is leading in high voltage applications such as automotive, with massive growth in the electric vehicle sector (EV), information technology, grid infrastructure, electric motor drives and aerospace. Similarly, GaN is featured in applications such as DC/DC converters, motor drives and satellite electronics. Currently, SiC is considered to possess the best bargain regarding properties, commercialization, high power devices and high thermal electronics (HTE) [36]. Although GaN can offer superior frequency and voltage performances, however its thermal conductivity is lower than SiC, granting the latter better performance under high temperature conditions. Moreover, pure GaN is ten times more expensive than SiC, legitimizing the reason behind commercializing Si-substrate GaN instead of bulk GaN, which actually offers incomparable cost effectiveness over all other substrates including SiC.

As a concluding settlement of the tradeoff between SiC and GaN, the coexistence of both semiconductor material in the market is worthwhile in their respective categorized applications [37] as conferred in figure I-9 below. SiC devices grant higher breakdown voltage, greater temperature endurance and reliability. While, GaN present lower conduction losses (high power efficiency), lower cost and phenomenal performance at high frequencies [38].

Figure I-9: Applications of SiC and GaN relative to operating frequency and output power

## A.2.2.1 SiC MOSFETs

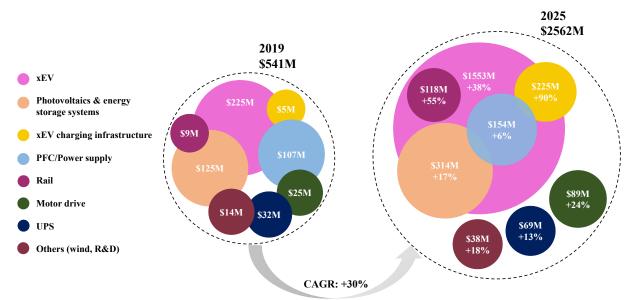

Over the past few years, accelerated endorsement of SiC devices played as a key trend in the power electronics industry [39], [40]. Figure I-10 below demonstrates the foretell of the compound annual growth rate (CAGR) and the application distribution of the power SiC market between 2019-2025 according to YOLE development.

Figure I-10: Projection of power SiC market according to application by Yole Development<sup>1</sup>

MOSFETs are now employed in ubiquitous quantities in SiC-based power electronic systems. Compared with SiC JFET and BJT, they are the favored SiC three terminal switches. SiC MOSFETs are regarded as the upcoming generation of power switching devices for high power and high blocking voltage operations. It has been commercially popularized from 600 V to 1700 V reaching a new third generation of 3.3 kV with power loss and reverse current capacity improvement; in addition to higher current modules attaining 15 kV SiC MOSFETs have been prototyped and used in developing high-voltage-high-frequency solid state transformers [41], [42]. When compared to IGBT systems, a realization of one to two orders of magnitude incrementation in the operation frequency of SiC MOSFET based converters has been verified. Furthermore, a zero switching loss can also be actualized under precise conditions such as the operation of a 1.2 kV SiC module manufactured by Cree and integrated in a gate driver card at 3.38 MHz frequency is demonstrated in [43]. Considering their low conduction loss, they can also function in the third quadrant as a synchronous rectifier whilst reducing the third quadrant conduction loss and contributing to almost nil reverse recovery loss. The synchronous rectifier concept, despite being used with Si-MOSFET applications of less than 100 V, can now be applied to voltages ranging up to 3.3 kV with SiC MOSFETs.

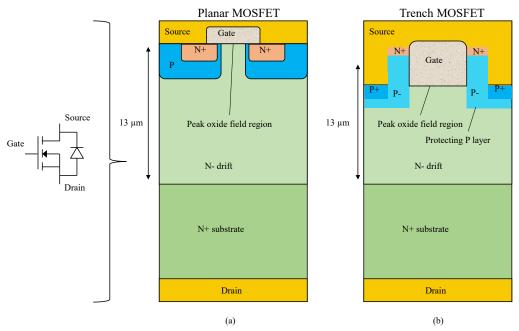

As shown in figure I-11, there are two basic device architectures used in commercial SiC MOSFET compounds: a planar structure and a trench structure. It is imperative to declare that especially at lower voltages, there are three prospects that cannot be forsaken in a planar structure, which are: channel resistance, junction-gate field-effect transistor (JFET) resistance between the two P regions and the substrate resistance. Wafer slimming to less than 100  $\mu$ m is efficient in reducing the substrate resistance, whereas improving the channel mobility meliorates the channel resistance. On the other hand, the superiority of the trench design is due to cell pitch reduction allowing channel density expansion hence reducing channel resistance as well as the eradication of the JFET region[44].

<sup>&</sup>lt;sup>1</sup><u>https://s3.imicronews.com/uploads/2020/11/YDR20119\_Power\_SiC\_Materials\_Devices\_Applications\_2020\_Sample.</u> pdf

Figure I-11: Typical structure demonstration of a SiC MOSFET (a) planar; (b) trench

# **B.** GATE DRIVER TOPOLOGIES

## **B.1** Functional Specifications

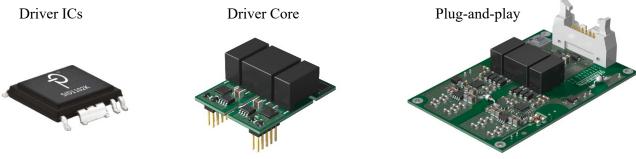

Due to the sublime convenience of WBG devices, the market witnessed immense employment of this technology [45]. Nonetheless, to benefit from the technologies' distinguished performance, it is vital to upgrade its performance and system environment [46]. One of the imperative constituents of a power electronic system is a gate driver, as the terminology implies, it's the supply of a high current drive input for a gate of a high-power transistor such as a MOSFET. It serves as an interface between the low-voltage microcontroller and the high-voltage power modules (including MOSFETs, IGBTs, SiC MOSFETs, etc.). As illustrated in figure I-12, three basic classes of commercial IGBT/MOSFET gate drivers are available and categorized as follows:

• Driver ICs: From basic level shifters to completely molded integrated driver circuits including logic and isolation, this label encompasses a wide range of integrated circuits.

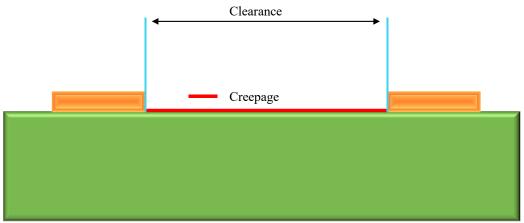

•Driver cores: On a larger range than a driver IC, a driver core provides all the functionalities for medium to high power applications. The entire circuit is manufactured on a printed circuit board (PCB) that can be further plugged or soldered on an alternative PCB, offering an adaptable design to fine-tune gate resistance and trip levels for peculiar modules. Moreover, isolation techniques are usually realized with pulse transformers and optocouplers permitting higher operating voltages and superior clearance/creepage distances. The aforementioned prospects will be further explained in the forthcoming section.

• Plug-and-play: These PCBs are designed to be instantly connected to a defined module housing. They are complete boards comprising all the features of a driver core, in addition

to equipped preconditioned gate resistors and structured components for a specific module type.

Integrated circuit drivers were commercialized by considerable manufacturers such as Texas Instruments, Infineon, On-semiconductor, Rohm semiconductor, Microchip, CISSOID, Power Integrations-Concept and Analog Devices. Moreover, the manufacturers that are prominent for high power applications are Wolfspeed-Cree, Semikron, Power Integrations-Concept and Infineon-Eupec.

Figure I-12: Basic classes of gate drivers<sup>2</sup>

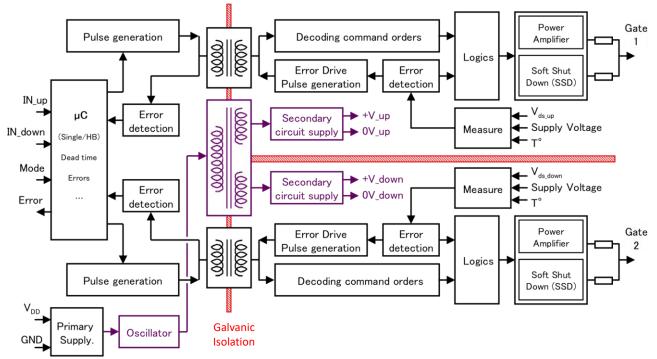

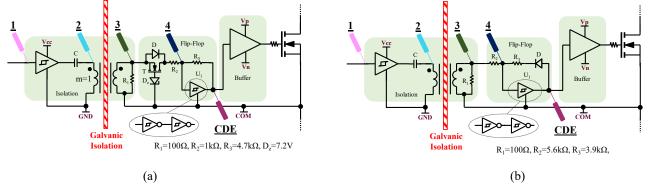

A conventional two-channel gate driver circuit is constructed in accordance to figure I-13, considering vital safety features and an apparent depiction of the isolation necessitated between the primary (low voltage) and secondary (high voltage) sides [47]. The controller cooperates with the primary side by transmitting control signals across the isolation barrier which is crucial to certify competent system functioning and user's safety [48]. Furthermore, an isolated power supply provided by a DC-DC converter, is essential to provide the potential needed to switch the power devices. Lastly, the secondary side is equipped with fast-acting protection and feedback schemes [49], [50]. It is imperative that the output stage, which allows signal buffering to drive the gate of the transistors, to be situated as close as possible to the power semiconductor devices. In case of a an application comprising SiC MOSFETs, to attain optimal switching the gate voltage required ranges from +20/-5 V for second generation modules and +15/-4 V for third generation components [51].

<sup>&</sup>lt;sup>2</sup> <u>https://www.semikron.com</u>

Figure I-13: Conventional gate driver circuit galvanically isolated using pulse transformers [47] [52]

## **B.2** Galvanic Isolation Requirement

Galvanic isolation, a prevailing gate driver characteristic used to provide optimal command orders for power devices, is an isolation barrier that electrically isolates primary to secondary circuitry, by founding segregated ground references. It concerns the isolation of the control signal transmission and the power supply circuit of the driver card. Gate drivers provide at least two functions that include signal transmission and power transmission as depicted in figure I-13 above. The power supply circuit is usually achieved by an isolated DC-DC converter, yet, the transmission of control signals or switching commands through the galvanic isolation barrier can be realized by the following technologies, appointed based on the voltage and power range of specific applications: optocoupler, transformer (with core/coreless), optical fiber, capacitive link and piezoelectric coupling [52]–[55]. Conventional isolators were obtained by means of optocouplers and/or discrete transformers[56]–[58]. However, these solutions are not adequate when it comes to expenses and restricted applications, respectively [59]–[61]. Presently, bulky and pricey methods are being replaced and dismissed by economical on-chip galvanically isolated modules [61], [62]. Table I-2 below compares some commonly used isolated gate driving solutions highlighting main parameters and features[60], [63].

| Parameter            | Optocoupler                        | ion solutions for gate dr<br>Traditional<br>Pulse<br>Transformer | Isolated Gate-<br>Driver IC<br>(Coreless pulse<br>transformer) | Digital<br>Capacitive<br>Isolator  |

|----------------------|------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------|

| Isolation Level      | Reinforced, basic<br>or functional | Reinforced, basic or functional                                  | Reinforced, basic<br>or functional                             | Reinforced, basic<br>or functional |

| Propagation<br>Delay | $\geq$ 400 ns                      | $\geq$ 35 ns                                                     | $\approx 35 \text{ ns}$                                        | $\approx 50 \text{ ns}$            |

| Stray<br>Capacitance | $\leq$ 2 pF                        | ≥ 10 pF                                                          | $\leq 2 \text{ pF}$                                            | ≤1 pF                              |

| CMTI                 | $\leq$ 25 kV/µs                    | $\geq$ 50 kV/µs                                                  | $\geq$ 150 kV/µs                                               | $\geq$ 100 kV/µs                   |

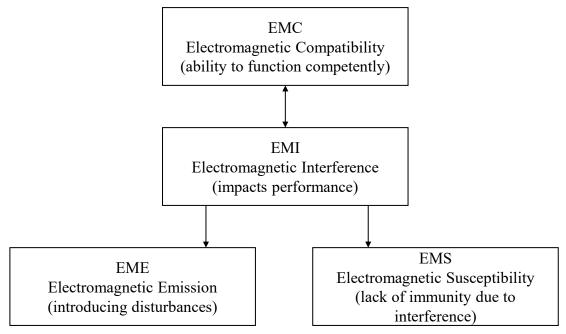

In high power applications, fiber optic isolators are seldom used due to their parasitic capacitances and complexities of incorporating fiber optic commands. Despite the extensive adoption of advantageous optocouplers in low to medium power applications, these devices suffer from aging, temperature drift and alternating current gain issues. In addition, they comprise significant parasitic capacitances which induce common mode (CM) current circulations between primary and secondary circuits, instigating electromagnetic disturbances. Modern gate drivers mainly employ digital isolators and pulse transformers. Digital capacitive isolators depend on high-voltage capacitors to withstand the required voltage rating and support isolation. Although they endure total immunity to magnetic fields, these devices have higher current consumption than transformer isolation. Moreover, a common consideration of capacitive isolators is their sensitivity to electric fields and common mode transients, originating common mode currents which can circulate through isolation capacitors and distort data transfer. Thus, an isolator's endurance and robustness to common mode transients is one of the essential parameters that determines an isolators' significance, this is demonstrated as the isolator's common mode rejection (CMR) or common mode transient immunity (CMTI) [64], [65]. It is measured by applying steep voltage pulses between two isolated ground references of the component, and it is defined by the maximal potential variation that the isolation can tolerate without impacting its data transfer efficiency. For optocouplers typical values for CMTI is less than 25 kV/µs, whereas capacitive isolators can attain up to 100 kV/µs considering their differential signaling.

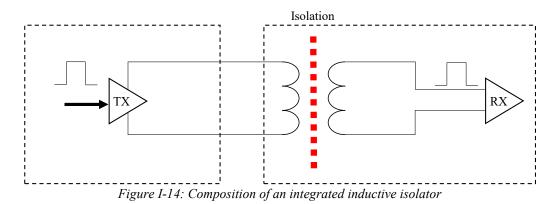

Ultimately, magnetic isolators, particularly inductive ones as demonstrated in figure I-14, serve as the remarkably dispersed isolation technology among semiconductor manufacturers. This is exclusively attained with the expansion and progression of PCB-integrated gate driver technology, discussed thereafter.

**B.3 Planar Technology**

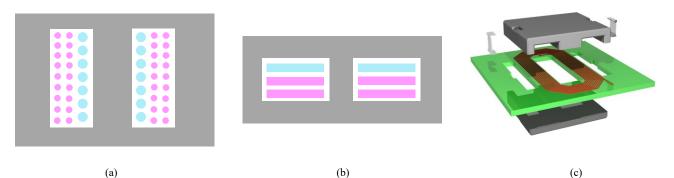

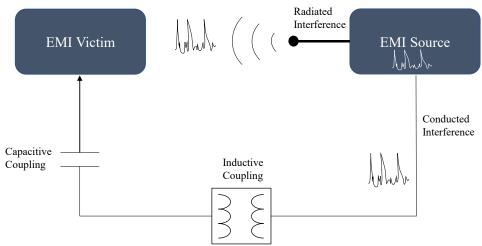

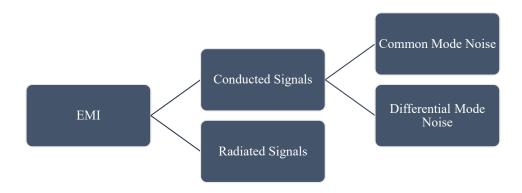

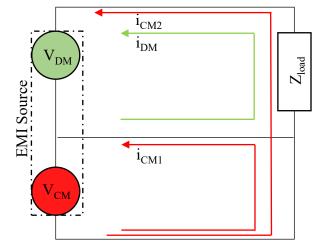

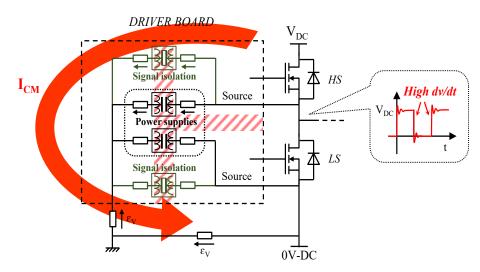

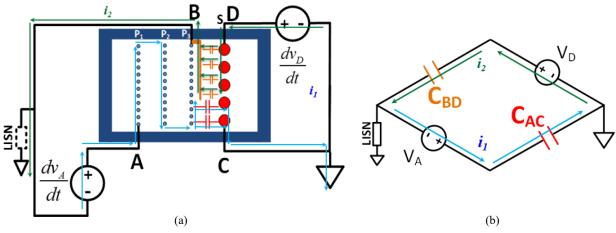

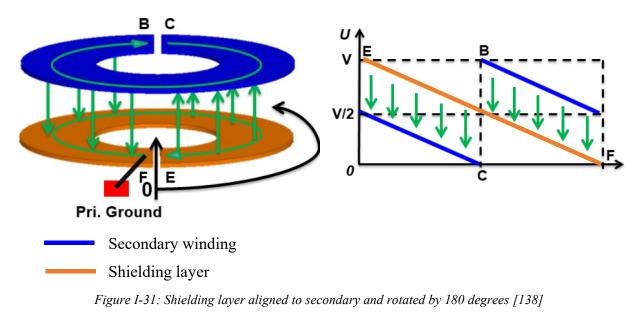

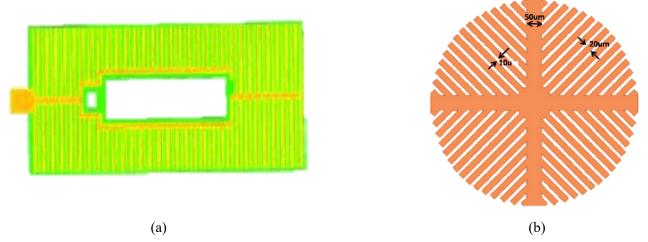

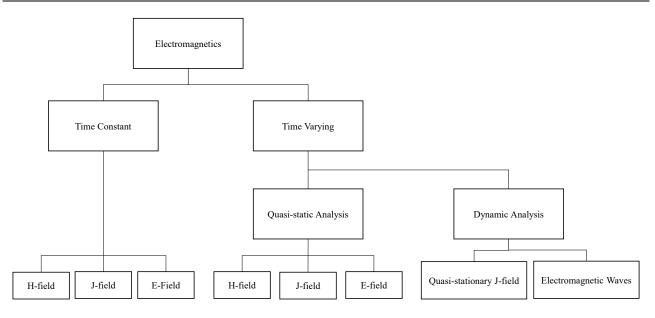

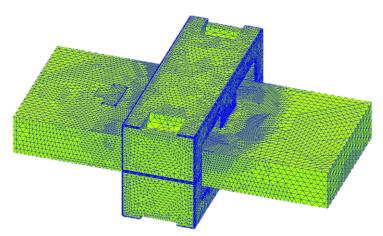

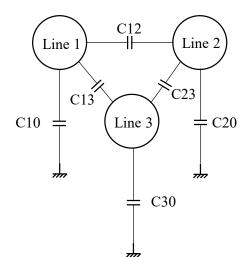

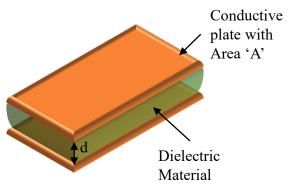

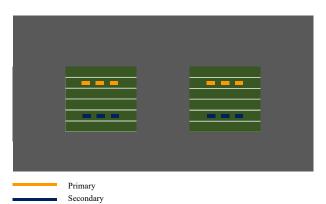

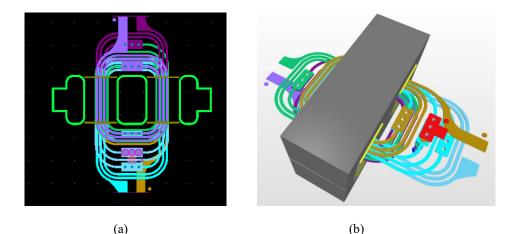

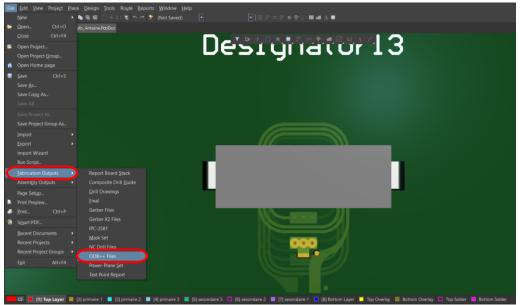

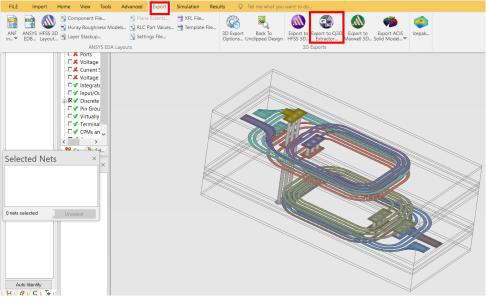

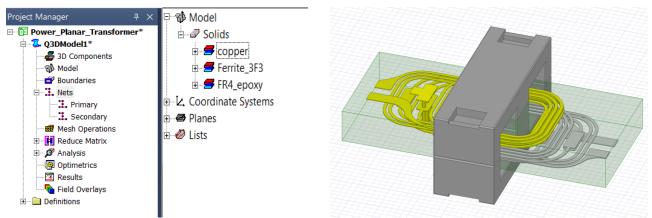

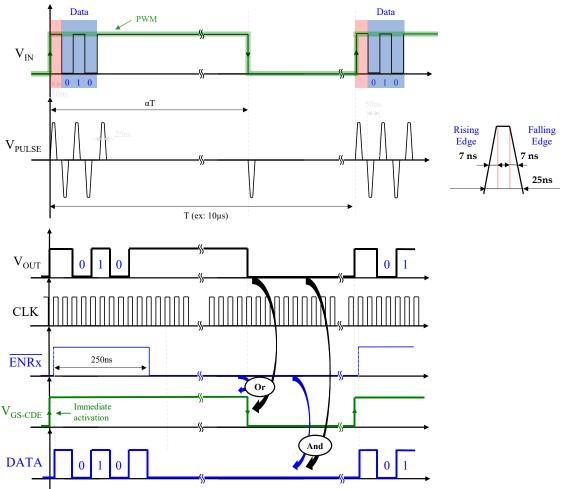

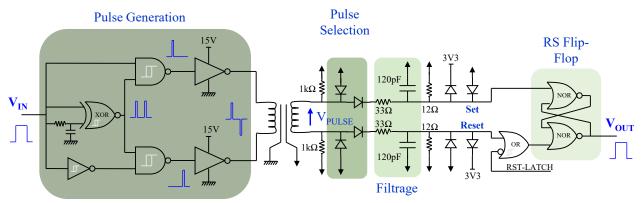

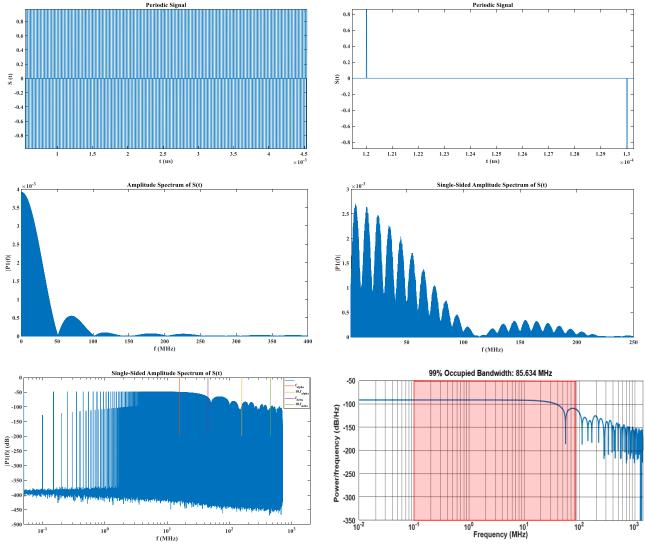

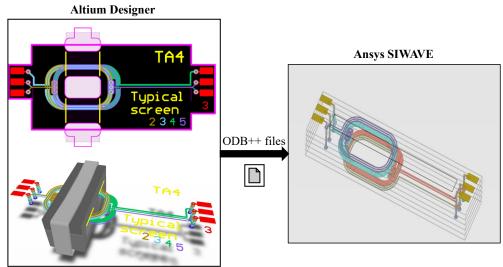

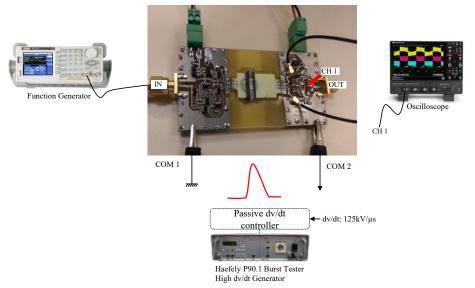

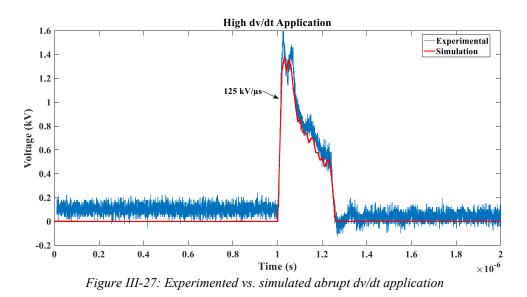

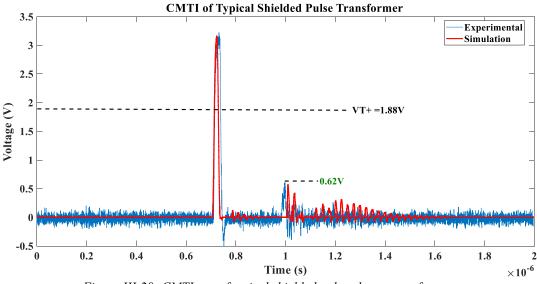

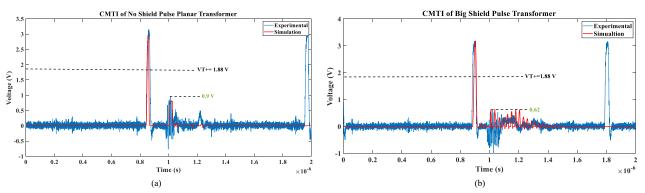

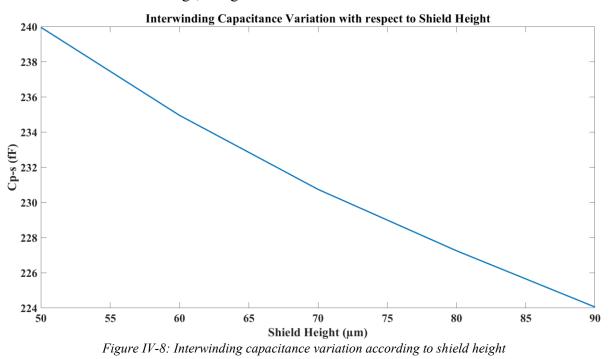

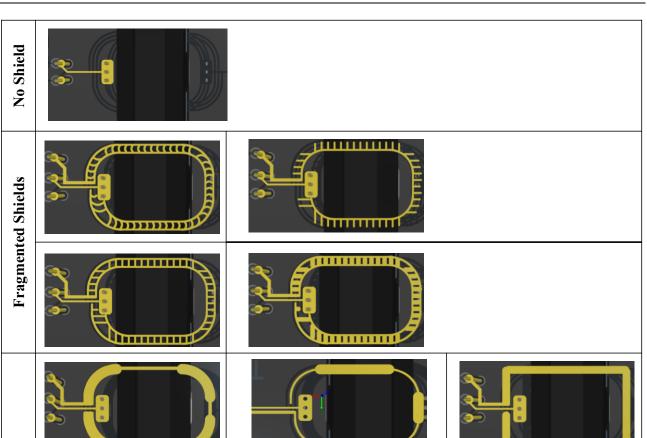

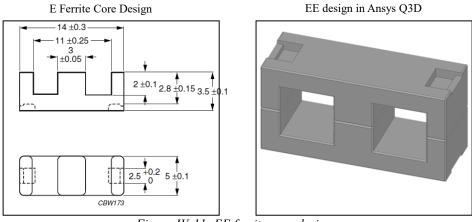

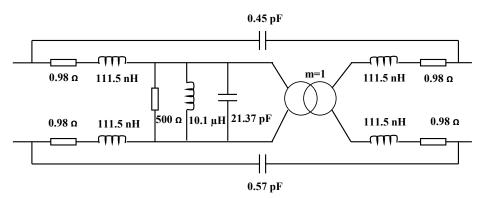

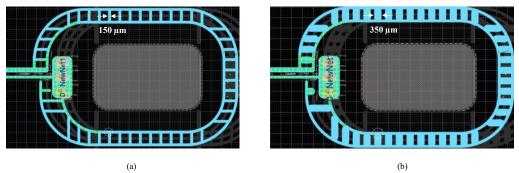

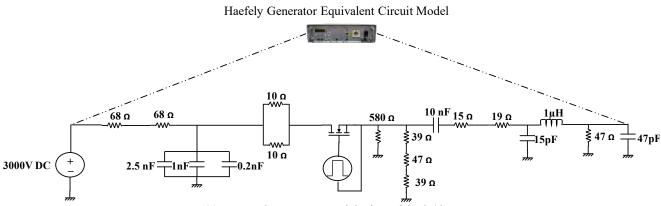

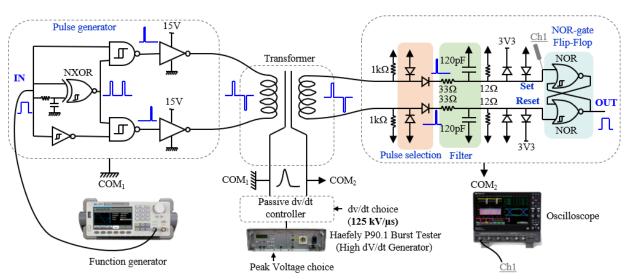

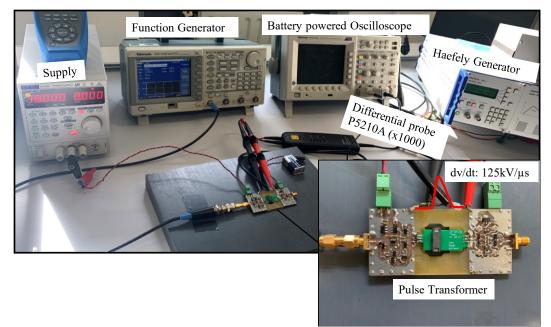

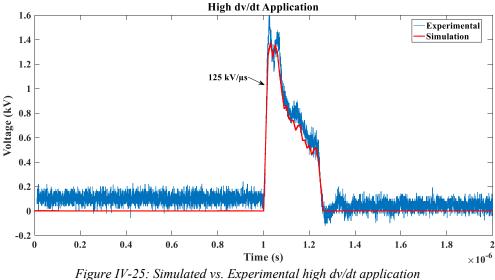

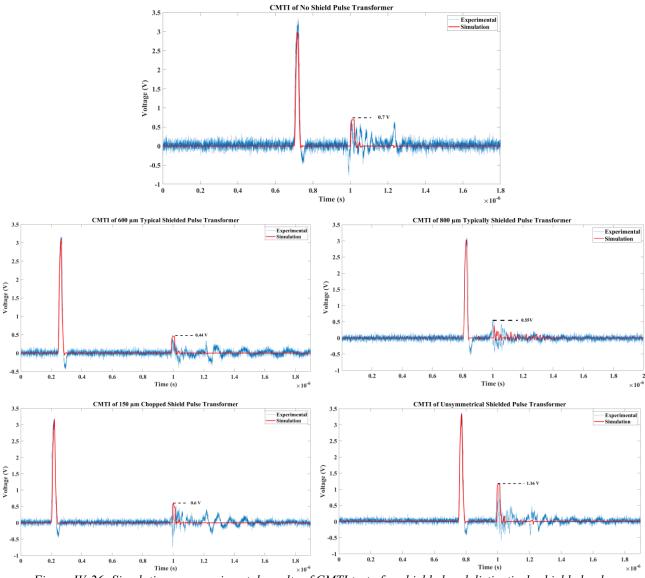

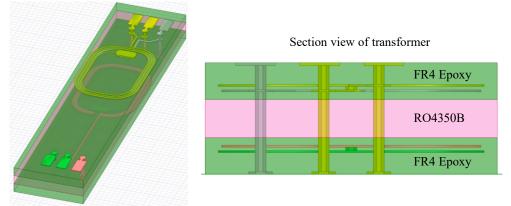

The tendency toward high power density, high operating frequency, and low profile in power converters has disclosed a number of restraints in the employment of conventional wire-wound magnetic component structures. Favorable high switching frequency attainment becomes conflicting and challenging when considering the design of the magnetics which are the bulkiest components of power supplies. Nonetheless, at higher frequencies, skin and proximity effects increase leading to more winding losses and parasitic effects. Hence, to profit from the encouraging advancements, while inspecting the demerits, PCB-integrated gate drivers for WBG technology have been explored [66]. Electromagnetic compatibility (EMC) conformity is crucial when designing gate driver circuits amid preserving high power density and minimum isolation capacitance. This is attained by the utilization of planar transformers, which harmonize with the growing demand of slim-profile power supplies, and comprising low leakage inductance, repeatability and low thermal resistance [67], [68]. Research on the manufacturing of planar magnetic components has been investigated since the 1960s [69], mainly concentrating on thin film technology [70]. In the early 1990s, research relevant to planar magnetic components' design, modelling and optimization has emanated [71]. Recently, accelerated development of PCB technology and exploration of attaining miniature power converters with integrated PCB windings stirred far-reaching international attention and industrial and academic fields [72]–[75].