## Ultra-low power continuous time digital signal processing circuits in 28nm FDSOI technology for audio applications

Ángel de Dios González Santos

#### ▶ To cite this version:

Ángel de Dios González Santos. Ultra-low power continuous time digital signal processing circuits in 28nm FDSOI technology for audio applications. Micro and nanotechnologies/Microelectronics. Université de Lille, 2020. English. NNT: 2020LILUI047. tel-03582251

## HAL Id: tel-03582251 https://hal.science/tel-03582251

Submitted on 29 Mar 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Présentée à l'Université de Lille, Ecole doctorale sciences pour l'ingénieur

pour obtenir le grade de

# Docteur

Spécialité : Electronique, microélectronique, nanoélectronique et micro-ondes

par

# Ángel de Dios González Santos

Circuits de traitement de signal numérique en temps continu ultra-faible consommation en technologie 28nm FDSOI pour applications audio

Ultra-low power Continuous Time Digital Signal Processing Circuits in 28nm FDSOI technology for audio applications

Soutenu publiquement le 29 septembre 2020 devant le jury composé de

Monsieur Dominique Dallet, Bordeaux INP, Rapporteur Madame Marie-Minerve Louërat, CNRS, Rapporteuse Monsieur Gilles Jacquemod, Université Côte d'Azur, Président du Jury Monsieur Andrei Vladimerescu, UC Berkeley – ISEP, Examinateur Monsieur Andreas Kaiser, Université de Lille, Directeur de thèse Monsieur Antoine Frappé, Yncréa Haut-de-France – IEMN, Encadrant Monsieur Philippe Cathelin, STMicroelectronics, Encadrant, Invité Monsieur Benoit Larras, Yncréa Haut-de-France – IEMN, Invité

UNION EUROPÉENNE

This project is co-financed by the European Union with the European Regional Development Fund (FEDER)

"Sometimes you look in a field and you see a cow and you think it is a better cow that the one you've got on your own field. It's a fact. Right? And it never really works out that way. Probably the same cow it's as good as your own cow"

-Sir Alex Ferguson

"There is a driving force more powerful than steam, electricity, and nuclear power: the will"

-Albert Einstein

### Abstract

The focus of this work is the study and development of a feature extraction system using Continuous-Time Digital Signal Processing (CT DSP) techniques, to mitigate the drawbacks of existing implementations based on traditional analog and digital solutions of always-on monitoring sensors for the Internet of Things (IoT).

The target is to extract the spectral content of an audio signal using a novel architecture based on a cascade of configurable CT DSP Finite Impulse Response (FIR) filters. An efficient cascade scheme is enabled by the proposed glitch elimination and delta encoding techniques. Additionally, this work introduces a CT function to estimate the instantaneous power within selected frequency bands to build an output spectrogram. The proposed 12-band system has been validated using behavioral simulations.

The key element for the implementation of this system is the digital delay element. A new delay element has been designed and fabricated in 28nm FDSOI technology and achieves a record tuning range from 30 ns to 97  $\mu$ s with a power consumption of 15 fJ/event. By extrapolating this result, the system would have an overall peak power consumption of 2.85  $\mu$ W when processing typical female speech, while consuming approximately 100 nW when no events are generated. Thus, the average system power consumption outperforms state-of-the-art feature extraction circuits.

## Résumé

L'objectif de ce travail c'est l'étude et développement d'un système d'extraction des caractéristiques en utilisant techniques de traitement de signal en temps continu, afin de mitiger les inconvénients des implémentations existantes basées en techniques analogiques et numériques conventionnelles, d'un système toujours en veille pour l'Internet des Objets.

La cible est l'extraction du contenu spectral d'un signal audio en utilisant une nouvelle architecture basée en une cascade configurable de filtres à réponse impulsionnelle finie en temps continu. Un schéma efficace pour cascader des filtres est obtenu grâce aux techniques proposées pour l'élimination des glitches et du codage delta. Par ailleurs, ce travail introduit une fonction en temps continu pour estimer la puissance instantanée dans des bandes de fréquences sélectionnées et construire un spectrogramme à la sortie. Le système proposé à 12-bandes fréquentielles a été validée par des simulations comportementales.

L'élément-clé pour l'implémentation de ce système est un élément de délai numérique. Un nouvel élément de retard a été conçu et fabriqué en technologie 28 nm FDSOI et atteint une plage de délai record entre 30 ns et 97 µs avec une consommation de puissance de 15fJ/événement. En extrapolant ce résultat, le système proposé atteint une consommation approximée de 2.85 µW lors du traitement d'un signal vocal généré par une femme, tandis que la consommation statique est autour de 100 nW dans les périodes où il n'y a pas d'activité. Donc, la performance en matière de consommation moyenne d'énergie de ce système surpasse celle des implémentations dans l'état de l'art.

## Acknowledgements

Above all I want to thank the Holy Trinity, God Almighty The Father "The I Am That I Am" (Exodus 3:14), God the Son our Lord Jesus Christ and God the Holy Spirit. I will have never started nor finished this project without powerful divine intervention aligning cosmos forces at the right time and the right place. This work with its merits and its shortcomings belongs to God.

I thank M. Andreas Kaiser my PhD. Director for his exhaustive commitment in this project, his time, his patience and the constant thrill to improve this work.

To my Industrial assessor Philippe Cathelin, I have really enjoyed working 3 meters away from him for the last year, thank you so much for the patience, the support and the invaluable design knowledge and experience that helped to bring this work to fruition.

To Antoine Frappe for hist commitment and for open me the doors to this project.

To Benoit Larras for his time and commitment.

To the members of the jury Marie-Minerve Louërat, Dominique Dallet, Gilles Jacquemod and Andrei Vladimerescu, thank you so much for your time and for all your valuable remarks and comments that have contributed to increase the quality of this work.

To all the ST designers Raphael Paulin, Robin Wilson, Mathilde Sie, Patrick Scheer, Andreia Cathelin, Clement Charbuillet that passed me invaluable design knowledge. A special mention to Nicolas Pelloux and Jasmina Antonijevic, who made me feel like just another colleague.

To my now friend Jeff Nowakoswki for his encouragement and support during measurements.

To Ioanna Kriekouki, I will have never finished this project without you, the MVP award goes to you, thank you for the encouragement and for helping me in recovering my passion and swagger for electronics. Thank you for all the discussions and for helping me to see things in life from your rational perspective. I wish you the absolute best.

To Annemarie thank you so much for the support.

To my dear friends and former office colleagues in Lille Dipal Ghosh and Alexis Clemente, thank you so much for the magnificent working environment we created, and the free-speech zone where we had awesome discussions. To Dipal my admiration for always keeping his coolness, I'll cherish all those restaurants we visited together. Alexis, you are very good, one day you will be the best. Also, greetings to Fabien "El Patron" VanLaehre.

To Henry Happy for his help and to Nora Benbahlouli for her support and kindness.

To Bruno Stefanelli for his help and Jean Marc Capron for giving me the opportunity of teaching.

To those women seated next to me in a train trip, that helped me with the orthography corrections of an important document I wrote in French

To all my friends in Saint Claude, Anne, Greg, Claire, Anna, Victor, Camille, Hamdi, Eveline, Sébastien, Virginie, Emmanuelle, Florine and Mathilde. I lived awesome moments with you. But particularly Claire and Anna I would have never discover that I love riding roller coasters without you.

Greetings also to the army (past and present) of PhD students at ST particularly to Rodrigo Iga and Francesco Renzini, my best wishes to you.

My Mexican Grenoble friends, sister from another mother Karina, Sahara, Adela and the legend from the day he was born in Alcalá de Henares, Spain the one and only Ricardo Gómez Gómez.

Finally to all my friends in Mexico, and my family, specially my grandfather Ramiro Santos the integrated circuit designed in this work was named Gallo in part to honor him, to my grandmothers Lili Vara all the way to heaven, and Alicia González for all her support, to my aunt Carmen Santos for her support and finally to my mother Violeta Santos who has always showed me immense support and who planted on me the interest for science.

To my aunt Marilú González de

Elizondo:

Salmo 34: 15:19

15 Los ojos de Jehová están sobre los justos, Y atentos sus oídos al clamor de ellos. 16 La ira de Jehová contra los que hacen mal, Para cortar de la tierra la memoria de ellos. 17 Claman los justos, y Jehová oye, Y los libra de todas sus angustias. 18 Cercano está, Jehová a los quebrantados de corazón; Y salva a los contritos de espíritu. 19 Muchas son las aflicciones del justo, Pero de todas ellas le librará, Jehová.

## Contents

| Abstrac   | .t                                                  | IV   |

|-----------|-----------------------------------------------------|------|

| List of F | -igures                                             | XIII |

| List of T | 「ables                                              | XVII |

| Chapter   | 1 Introduction                                      | 1    |

| 1.1       | Background (IoT)                                    | 1    |

| 1.2       | Motivation for this work                            | 2    |

| 1.3       | Feature extraction                                  | 3    |

| 1.4       | Thesis contributions                                | 5    |

| 1.5       | Thesis Layout                                       | 5    |

| Chapter   | 2 Continuous-Time Digital Signal Processing Systems | 7    |

| 2.1       | Description                                         | 7    |

| 2.2       | Introduction and context                            | 7    |

| 2.3       | CT vs DT ADC conversion                             |      |

| 2.3.      | 1 Quantization                                      |      |

| 2.3.      | 2 Sampling                                          |      |

| 2.3.      | 3 Comparison between CT and DT ADC conversion       |      |

| 2.4       | CT-ADC State of the art                             |      |

| 2.4.      | 1 Level crossing Analog-to-Digital converter        |      |

| 2.4.      | 2 CT Level crossing sampling limitations            |      |

| 2.4.      | 3 Variable resolution level crossing ADC            |      |

| 2.4.      | 4 Integrator embedded ADC                           |      |

| 2.5       | Overall review of CT ADC                            |      |

| 2.6       | Digital signal processing in CT                     |      |

| 2.6.      | 1 CT Receiver – General considerations              |      |

| 2.6.      | 2 FIR FILTERS                                       |      |

| 2.6.      | 3 CT DELAY TAP                                      |      |

| 2.6.      | 4 IIR FILTER                                        |      |

| 2.7       | CT DAC                                              |      |

| 2.8       | Continuous time to discrete time converter          |      |

| 2.9       | Performance assessment                              |      |

| 2.10      | Challenges                                          | 19   |

| 2.11      | Conclusion                                          |      |

| Chapter   | 3 Feature Extraction for audio signals              | 22   |

| 3.1       | Description                                         |      |

| 3.2       | Audio feature extraction applications               |      |

| 3   | .3           | Pow  | ver-scalable sensing                                                   | 23 |

|-----|--------------|------|------------------------------------------------------------------------|----|

| 3   | .4           | Cha  | racteristics of audio signals and human hearing                        | 24 |

|     | 3.4.         | 1    | Characteristics of audio and voice signals                             | 24 |

|     | 3.4.2        | 2    | Human Hearing functioning                                              | 27 |

| 3   | .5           | Stat | te-of-the-Art of audio feature extraction applications                 | 28 |

|     | 3.5.         | 1    | VAD Applications                                                       | 29 |

| 3   | .6           | Con  | nclusion                                                               | 31 |

|     | -            |      | roposed System: Continuous Time filter bank suitable for audio feature |    |

|     |              |      | !··                                                                    |    |

| -   | .1           |      | oduction                                                               |    |

| 4   |              |      | posed CT DSP system for feature extraction                             |    |

|     | 4.2.         |      | Targeted performance                                                   |    |

| 4   |              |      | hitectural choices                                                     |    |

|     | 4.3.         |      | ADC Type                                                               |    |

|     | 4.3.2        |      | ADC Dimensioning                                                       |    |

| 4   | 4.3.:<br>.4  | -    | Filter bank dimensioning                                               |    |

| 4   | .4<br>4.4.'  |      | er bank implementation<br>Global architecture                          |    |

|     | 4.4.<br>4.4. | -    | Design of 16 <sup>th</sup> order filters                               |    |

|     | 4.4.         | _    | Design of event-reduction and encoding circuits                        |    |

| 4   | 4.4<br>.5    | -    | rgy estimation                                                         |    |

| 4   | .5<br>4.5.'  |      | Energy estimation principles                                           |    |

|     | 4.5.         |      | CT instantaneous power estimation                                      |    |

|     | 4.5.         | _    | Energy accumulation                                                    |    |

| Л   | 4.J<br>.6    | -    | tem performance                                                        |    |

|     | .0           | -    | ernative implementation approach by using low pass filters and energy  | 50 |

|     |              |      | n                                                                      | 51 |

| 4   | .8           | Con  | nclusions                                                              | 56 |

| Cha | apter        | 5 D  | igital Delay Cells in 28 nm FDSOI technology                           | 57 |

| 5   | .1           | Des  | cription                                                               | 57 |

| 5   | .2           | Den  | nonstrator strategy                                                    | 57 |

| 5   | .3           | Digi | ital delay line state of the art                                       | 57 |

|     | 5.3.         | 1    | Conclusion                                                             | 61 |

| 5   | .4           | Тес  | hnology choice                                                         | 61 |

| 5   | .5           | Digi | ital-delay cell design                                                 | 63 |

|     | 5.5.         | 1    | Current source in weak inversion                                       | 63 |

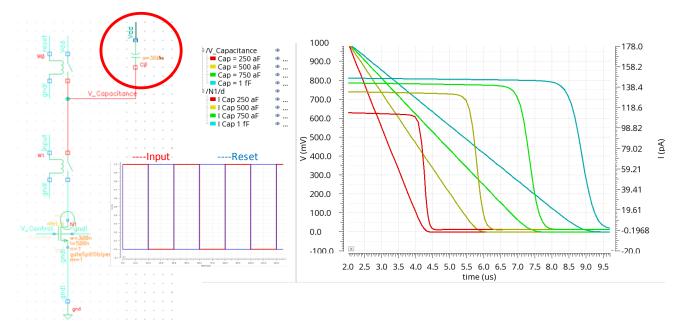

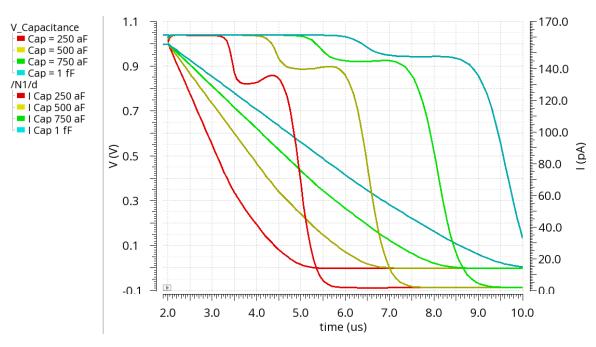

| 5.5                                                                                                | 5.2 Analysis of capacitance charging                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66             |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5.5                                                                                                | 5.3 Complete delay element evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67             |

| 5.5                                                                                                | 5.4 Input signal dependency                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68             |

| 5.6                                                                                                | Elements for handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71             |

| 5.7                                                                                                | Reducing power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 74             |

| 5.7                                                                                                | 7.1 EGVLVT transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75             |

| 5.7                                                                                                | 7.2 Inverter to control the cascode source                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76             |

| 5.8                                                                                                | Other modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76             |

| 5.8                                                                                                | B.1 EGVLVT Transistors as a transmission gate                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76             |

| 5.8                                                                                                | <b>PMOS switch to control the fast discharge source</b>                                                                                                                                                                                                                                                                                                                                                                                                                               | 77             |

| 5.9                                                                                                | Delay final version schematic and performance                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79             |

| 5.9                                                                                                | 9.1 Power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79             |

| 5.9                                                                                                | 9.2 Mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80             |

| 5.10                                                                                               | Delay taps layout implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 5.11                                                                                               | Single delay layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82             |

| 5.12                                                                                               | Post layout simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83             |

| 5.13                                                                                               | Delay tap and test circuit layout                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| 5.14                                                                                               | Final performance assessment                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86             |

|                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| 5.15                                                                                               | Overall system performance and comparison with the State-of-                                                                                                                                                                                                                                                                                                                                                                                                                          | the-art 88     |

| 5.15<br>5.16                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| 5.16                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90             |

| 5.16                                                                                               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90<br>91       |

| 5.16<br>Chapte                                                                                     | Conclusion<br>er 6 Measurements and validations                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90<br>91<br>91 |

| 5.16<br>Chapte<br>6.1                                                                              | Conclusion<br>er 6 Measurements and validations<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 5.16<br>Chapte<br>6.1<br>6.2                                                                       | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging                                                                                                                                                                                                                                                                                                                                                                                    |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3                                                                | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results                                                                                                                                                                                                                                                                                                                                      |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4                                                         | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element                                                                                                                                                                                                                                                                                                  |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4                                                  | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics                                                                                                                                                                                                                                                             |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4                                                  | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics<br>4.3 Measurement variability                                                                                                                                                                                                                              |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4                                           | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics<br>4.3 Measurement variability<br>4.4 Delay tuning range                                                                                                                                                                                                    |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4<br>6.4                                    | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics<br>4.3 Measurement variability<br>4.4 Delay tuning range<br>4.5 Delay power consumption                                                                                                                                                                     |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4               | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics<br>4.3 Measurement variability<br>4.4 Delay tuning range<br>4.5 Delay power consumption                                                                                                                                                                     |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4               | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics<br>4.3 Measurement variability<br>4.4 Delay tuning range<br>4.5 Delay power consumption<br>4.6 Input signal delay dependency<br>4.7 Delay error                                                                                                             |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4        | Conclusion         er 6 Measurements and validations         Description         Integrated circuit and packaging         Experimental setup         Experimental results         4.1 Biasing of the delay element         4.2 Delay element characteristics         4.3 Measurement variability         4.4 Delay tuning range         4.5 Delay power consumption         4.6 Input signal delay dependency         4.7 Delay error         4.8 Unit cells and delay tap mismatches |                |

| 5.16<br>Chapte<br>6.1<br>6.2<br>6.3<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4<br>6.4 | Conclusion<br>er 6 Measurements and validations<br>Description<br>Integrated circuit and packaging<br>Experimental setup<br>Experimental results<br>4.1 Biasing of the delay element<br>4.2 Delay element characteristics<br>4.3 Measurement variability<br>4.4 Delay tuning range<br>4.5 Delay power consumption<br>4.6 Input signal delay dependency<br>4.7 Delay error<br>4.8 Unit cells and delay tap mismatches                                                                  |                |

| 6.7      | System performance estimation with measured results |  |

|----------|-----------------------------------------------------|--|

| 6.8      | Conclusion                                          |  |

| Chapter  | 7 Conclusion and perspectives                       |  |

| 7.1      | Conclusion                                          |  |

| 7.2      | Research Perspectives                               |  |

| 7.2.     | 1 Short term perspectives                           |  |

| 7.2.     | 2 System architecture improvements                  |  |

| 7.2.     | 3 Delay element improvements                        |  |

| 7.2.     | 4 Alternative paths                                 |  |

| 7.3      | A personal note on the future of CT systems         |  |

| Bibliogr | aphy                                                |  |

## List of Figures

| Figure 1 Different IoT applications, in some cases the CAGR of the sector is indicated [1]            | 1    |

|-------------------------------------------------------------------------------------------------------|------|

| Figure 2 Expected growth of the IoT Market by Application in North America [2]                        | 2    |

| Figure 3 Architecture of a feature extraction system [7]                                              | 4    |

| Figure 4 Quadrant showing the different types of electronic signal processing                         | 7    |

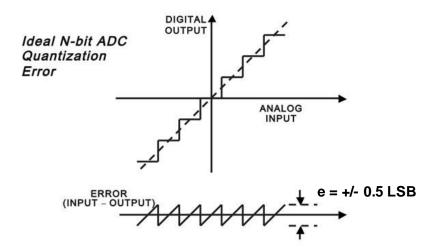

| Figure 5 Ideal N-bit ADC Quantization Error                                                           |      |

| Figure 6 Example waveforms of a 3-b ADC quantification. Time domain waveforms are normalized          | d to |

| the input period, of the (a) input sinusoid, (b) quantization error, (c) quantized input and their    |      |

| corresponding frequency spectrums, in (d), (e), and (f), respectively [20]                            | 9    |

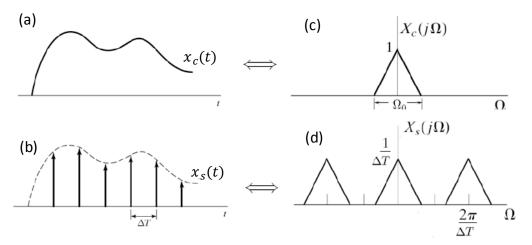

| Figure 7 Example waveforms of a sampled signal. Time domain waveforms, of the (a) Input signal        |      |

| continuous in time, (b) sampled input signal and their corresponding frequency spectrums, in (c),     | and  |

| (d).                                                                                                  |      |

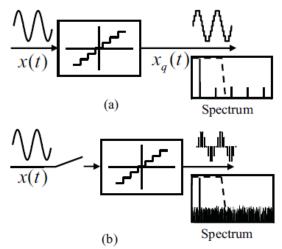

| Figure 8 Input waveform, output waveform, and output spectrum with (a) quantization only, (b)         |      |

| sampling and quantization [18]                                                                        | 11   |

| Figure 9 Level crossing sampling scheme                                                               |      |

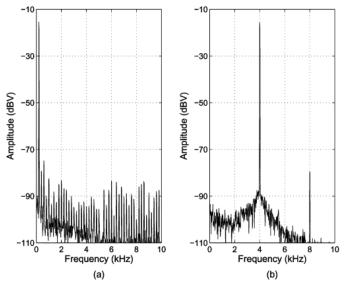

| Figure 10 Output spectra of a CT system configured as a 10kHz low-pass filter, given (a) a full-scale |      |

| 200Hz sinusoid input and (b) a full-scale 4 kHz sinusoidal input [24]                                 |      |

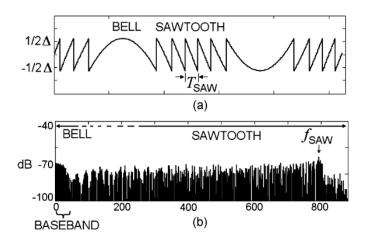

| Figure 11 Six bit quantizer waveforms for a sinusoidal input. (a) Quantization error waveform,        |      |

| normalized to the quantization level, (b) Spectrum of the quantization error, normalized to the in    | put  |

| frequency                                                                                             |      |

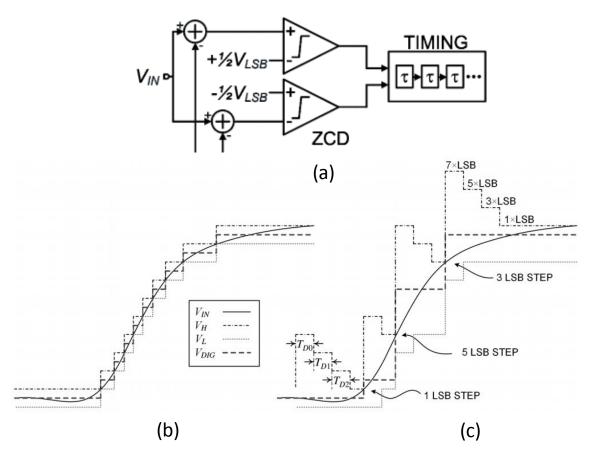

| Figure 12 Variable resolution CT ADC principle (a) Time-varying comparisson window circuit [28]       |      |

| (b)(c) Input signal (solid line), upper and lower comparison levels (dot-dashed and dotted lines      |      |

| respectively), and quantized signal (broken line), for (b) conventional level crossing ADC, and (c)   |      |

| adaptie-resolution level-crossing ADC [22]                                                            | 14   |

| Figure 13 Model of the ADC with embedded integrator [23]                                              |      |

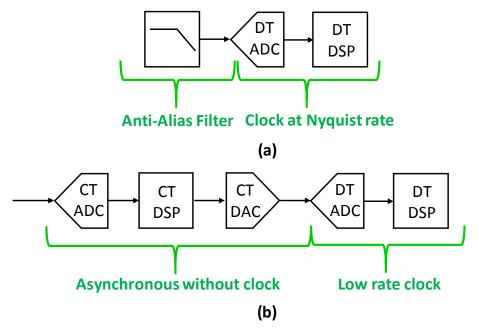

| Figure 14 Classical receiver architecture (a) CT receiver architecture (b)                            |      |

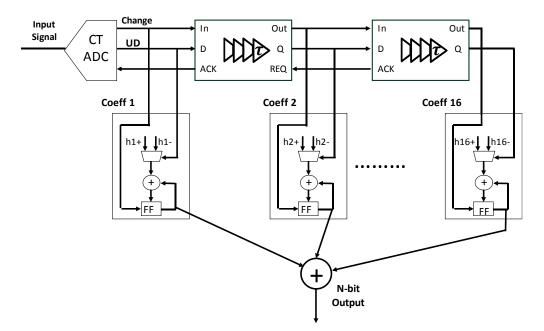

| Figure 15 CT DSP FIR filter scheme                                                                    |      |

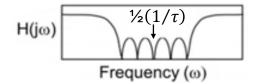

| Figure 16 The frequency response of a CT Filter is repetitive around 1/TD                             |      |

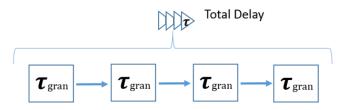

| Figure 17 Structure of delay taps in Continuous time                                                  |      |

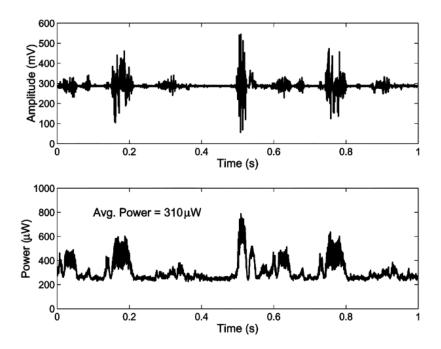

| Figure 18 Plot of input speech signal (top) and the instantaneous power consumption (bottom) of       |      |

| CT ADC/DSP/DAC from [24]                                                                              |      |

| Figure 19 Typical architecture of audio recognition systems                                           |      |

| Figure 20 Power scalable sensing inspired by [11]                                                     |      |

| Figure 21 Architecture of a Hierarchical and/or near sensor computing recognition system              |      |

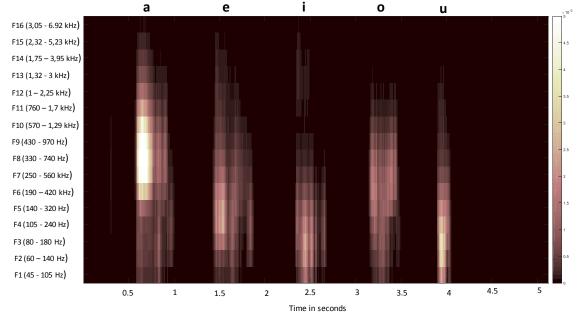

| Figure 22 Spectrogram of Spoken Vowels                                                                |      |

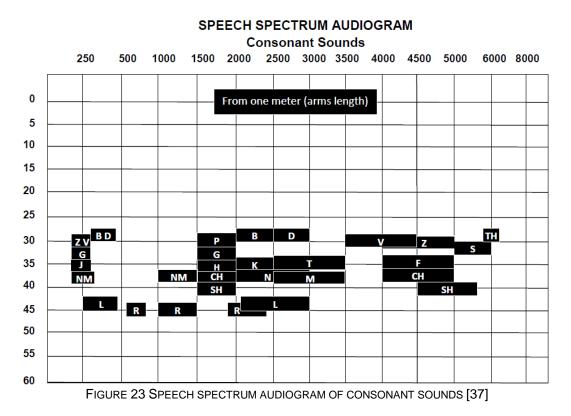

| Figure 23 Speech spectrum audiogram of consonant sounds [37]                                          |      |

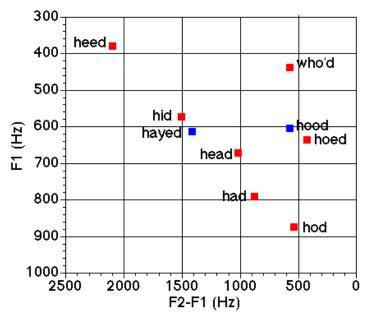

| Figure 24 Formant frequencies of vowels [38]                                                          |      |

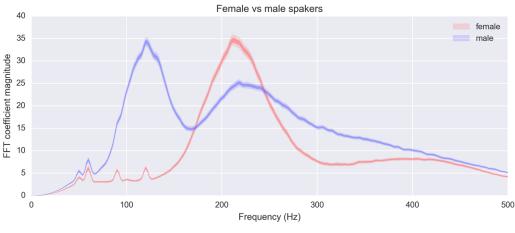

| Figure 25 Frequency Spectrum of male and female speech [39]                                           |      |

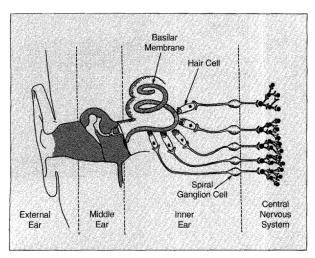

| Figure 26 Diagram of the human ear [34]                                                               |      |

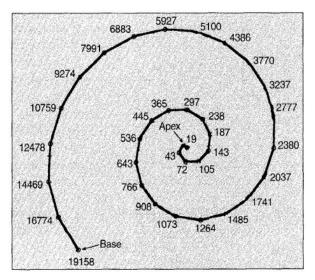

| Figure 27 Diagram of the basilar membrane [34]                                                        |      |

| Figure 28 Basic Architecture of Audio recognition systems                                             |      |

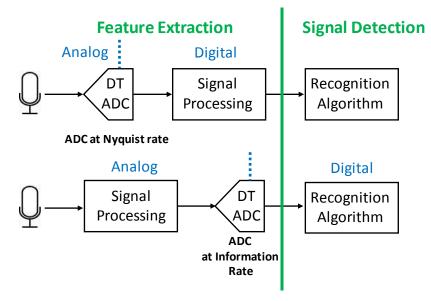

| Figure 29 Approaches to compute the spectral content of a signal Top: Digital at Nyquist Rate.        |      |

| Bottom: Analog-to-Information. Image inspired from [32]                                               | 30   |

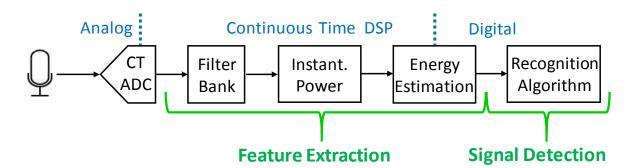

| Figure 30 Proposed approach to compute the spectrogram of a signal                                    |      |

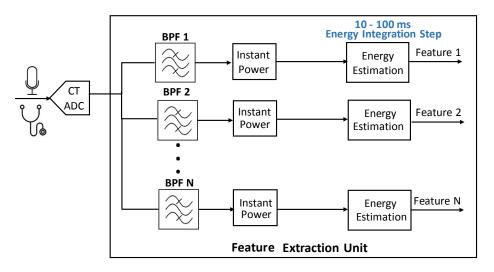

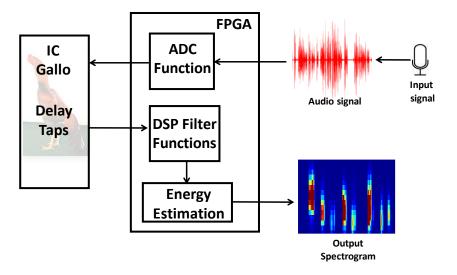

| Figure 31 Feature extraction SYSTEM IN CT DSP                                                         |      |

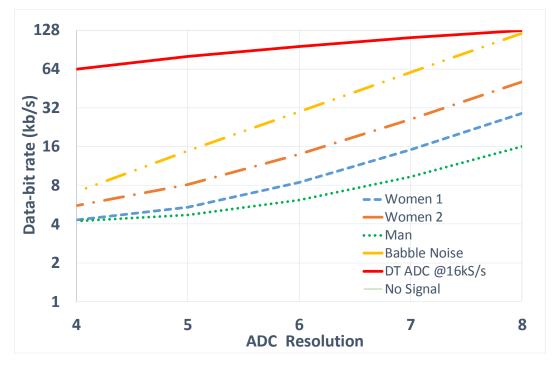

| Figure 32 Number of samples generated by a CT ADC for different input signals                         |      |

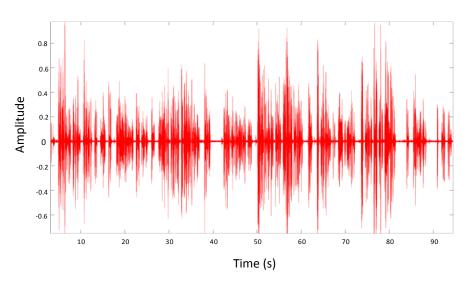

| Figure 33 Male speech plot used to generate Figure 32                                                 |      |

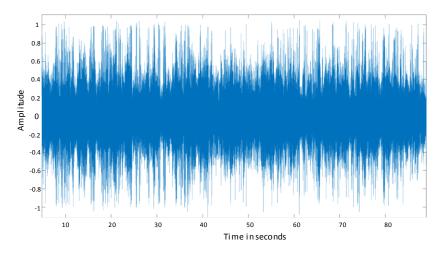

| Figure 34 Babble noise plot used to generate Figure 32                                                |      |

|                                                                                                       |      |

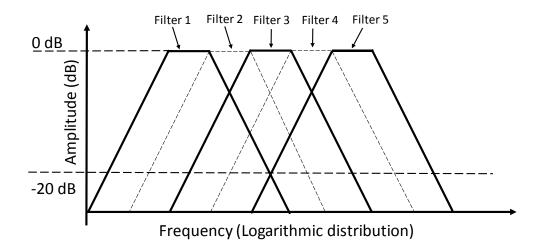

| Figure 35 Filter bank representation, illustrating the 20 dB stop band rejection at the central                |    |

|----------------------------------------------------------------------------------------------------------------|----|

| frequencies of their second closest neighbors                                                                  | 38 |

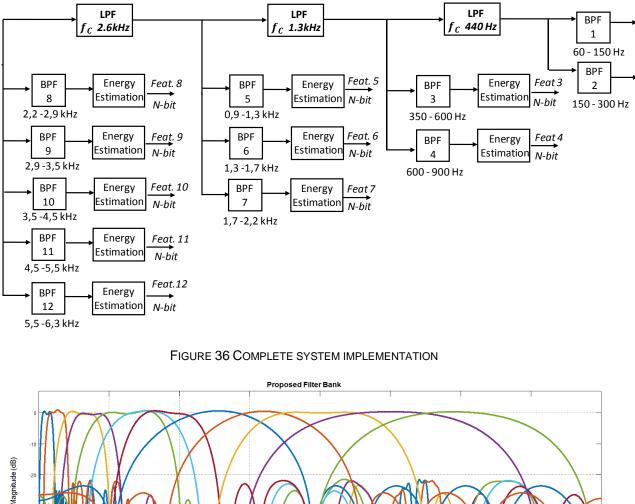

| Figure 36 Complete system implementation                                                                       | 39 |

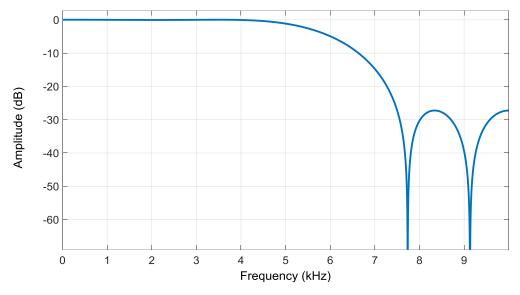

| Figure 37 Frequency response of the filter bank                                                                | 39 |

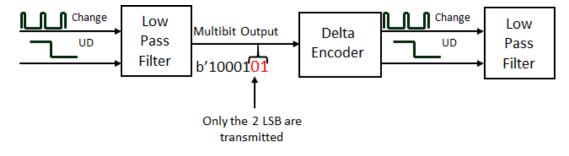

| Figure 38 Proposed low pass filter cascade operation                                                           | 40 |

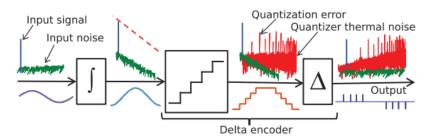

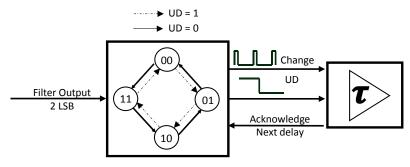

| Figure 39 Delta Encoder circuit                                                                                | 40 |

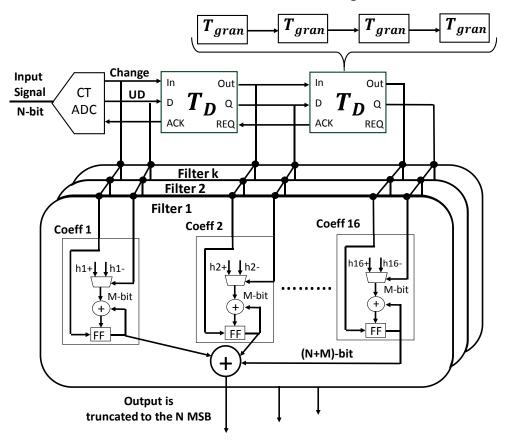

| Figure 40 16TH ORDER CTDSP FIR Filter section                                                                  | 41 |

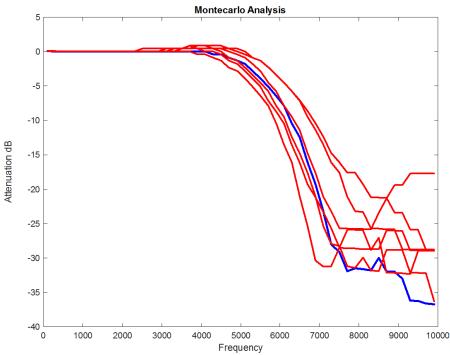

| Figure 41 Effects of mismatch in the frequency response for a delay tap mismatch value ( $\sigma\mu$ ) of 10%. |    |

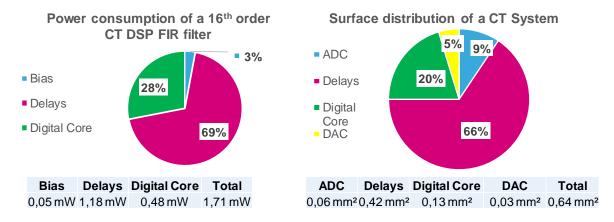

| Figure 42 Power consumption and surface of a CT DSP System                                                     |    |

| Figure 43 Concept of the glitch eliminator acting as a decimator                                               |    |

| Figure 44 Glitch eliminator circuit                                                                            |    |

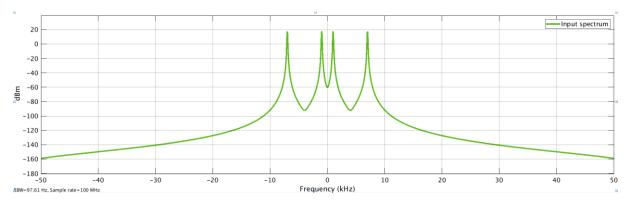

| Figure 45 Spectrum of the signal used to evaluate the glitch eliminator                                        |    |

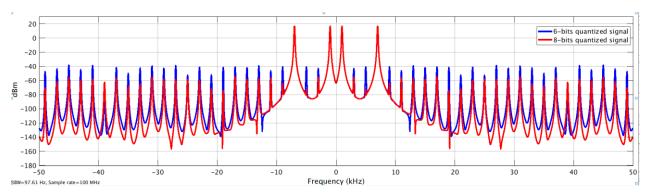

| Figure 46 Spectrum of the quantized signal used to evaluate the glitch eliminator                              |    |

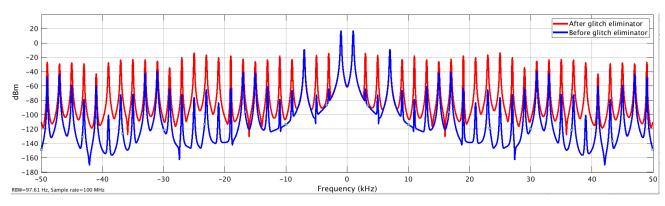

| Figure 47 Spectrum at the input and output of the clitch eliminator                                            |    |

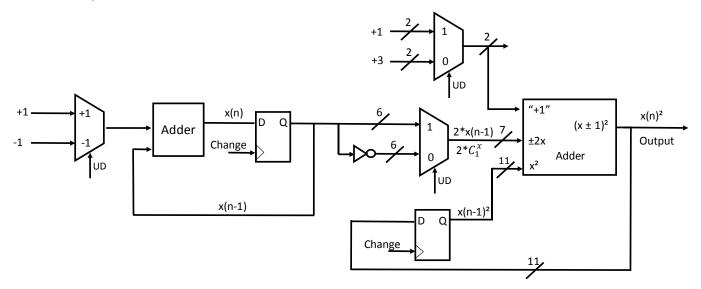

| Figure 48 Proposed circuit to calculate the instantaneous power of a signal in CT                              |    |

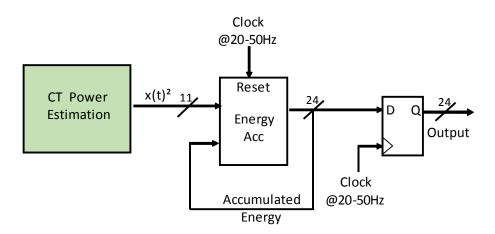

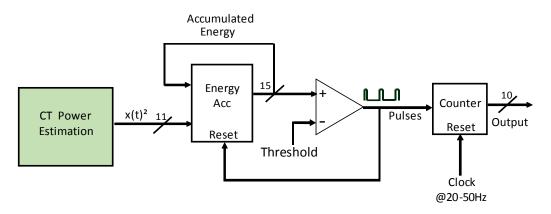

| Figure 49 Circuit to compute the energy of a signal by accumulating Instantaneous power                        |    |

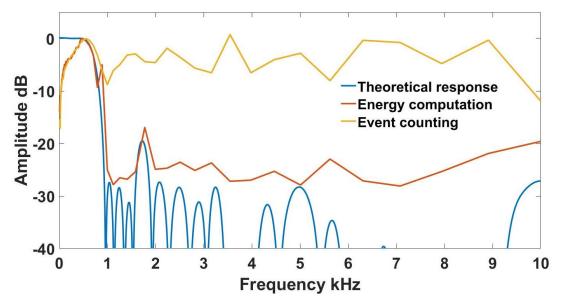

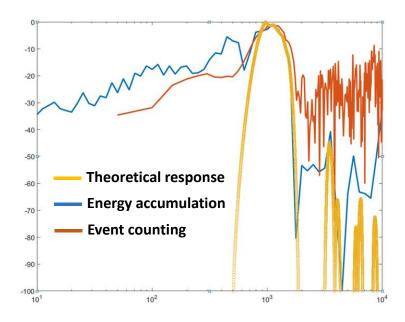

| Figure 50 Comparison of filter transfer functions obtained for the even-counting method and the                |    |

| proposed energy calculation method, with respect to the continuous-time equivalent filter function             |    |

| (blue curve)                                                                                                   |    |

| Figure 51 Alternative circuit to compute the energy of a signal in CT                                          |    |

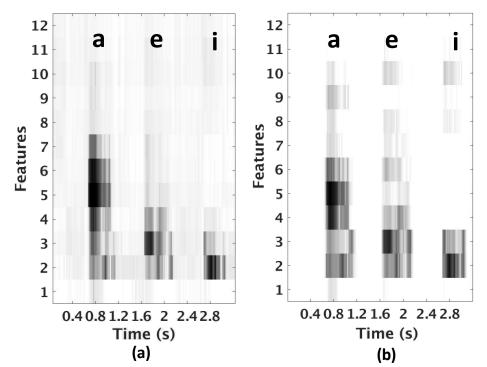

| Figure 52 Comparison of spectrograms of spoken vowels generated with (a) our proposed system                   |    |

| and (b) an FFT algorithm                                                                                       |    |

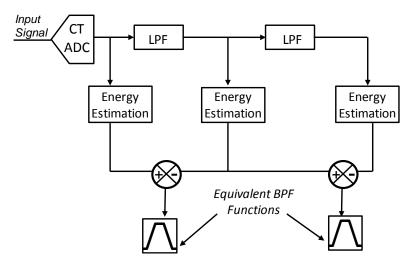

| Figure 53 Diagram of band-pass filters created by subtracting energy of low pass filters                       |    |

| Figure 54 Low-pass filter used to cascade filters                                                              |    |

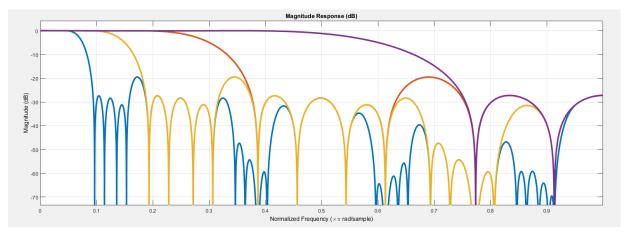

| Figure 55 Frequency response of the cascaded low-pass filters used to create band-pass filters                 |    |

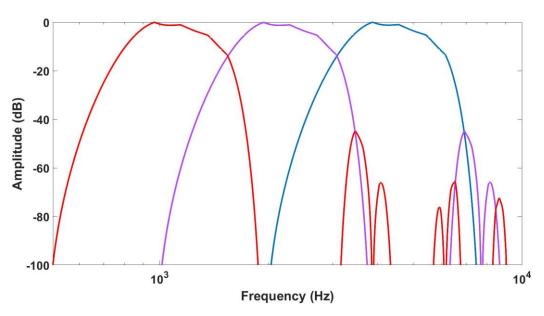

| Figure 56 Frequency response of the theoretical band-pass filters                                              |    |

| Figure 57 Comparison between event counting and energy accumulation                                            |    |

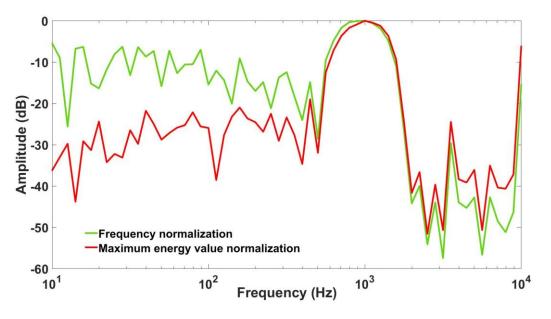

| Figure 58 Comparison between different normalizations                                                          | 54 |

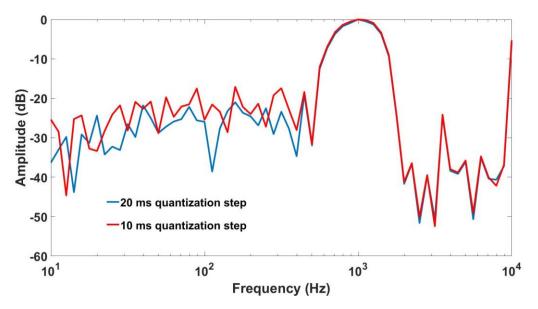

| Figure 59 Comparison of filter function obtained with energy estimation for different integration              |    |

| steps                                                                                                          |    |

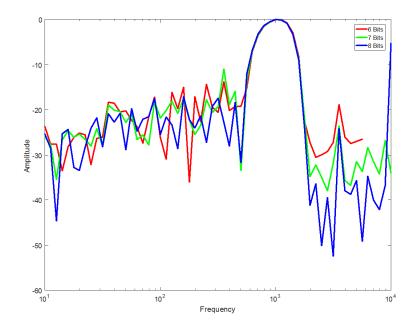

| Figure 60 Comparison of filter function obtained with energy estimation for different ADC resolution           |    |

|                                                                                                                |    |

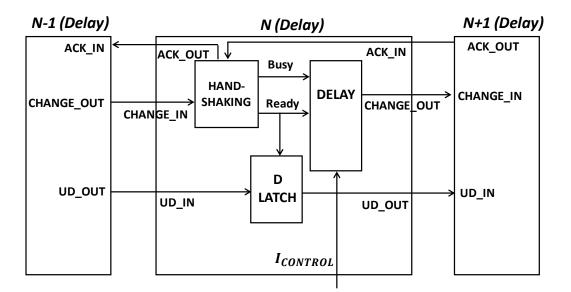

| Figure 61 Top level schematic of a delay cell in a CT digital filter                                           |    |

| Figure 62 Delay element proposed by [49]                                                                       |    |

| Figure 63 Delay element proposed by [50]                                                                       |    |

| Figure 64 Thyristor based delay element                                                                        |    |

| Figure 65 Functionning principle of the thyristor based delay                                                  |    |

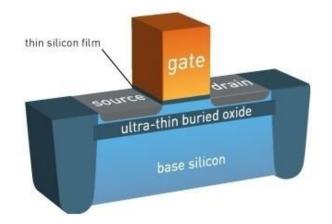

| Figure 66 Structure of an FDSOI UTBB transistor                                                                |    |

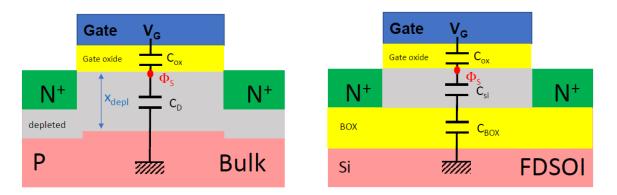

| Figure 67 Comparison between bulk and FD-SOI technologies                                                      |    |

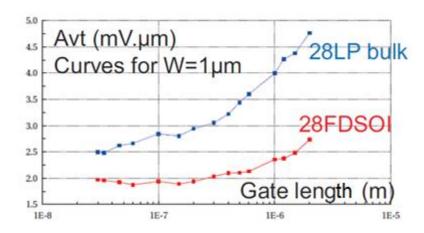

| Figure 68 Avt Comparison between the 28nm bulk and the 28nm FD-SOI transistors [55]                            |    |

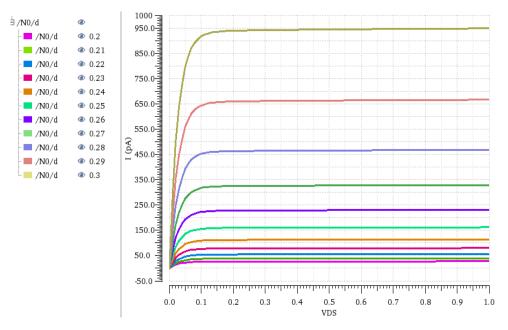

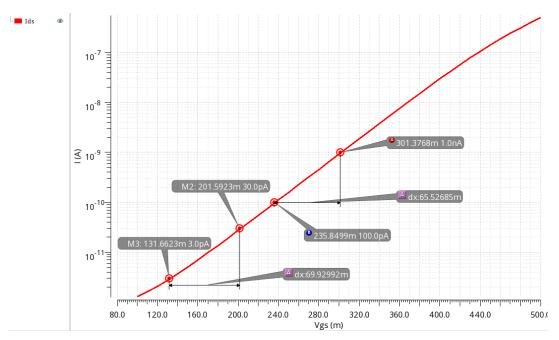

| Figure 69 DC Analysis of a W=300nm L = 500nm FD-SOI transistor                                                 |    |

| Figure 70 Subthreshold slope of a W=300nm L=500nm transistor                                                   |    |

| Figure 71 Slow charge current source variations due to Capacitor coupling                                      |    |

| Figure 72 Slow current source value with a cascode pair                                                        |    |

| Figure 73 Delay element first version                                                                          |    |

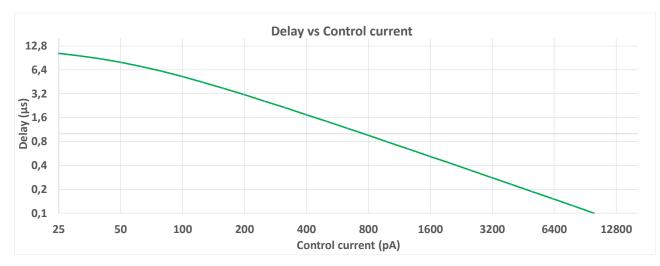

| Figure 74 Delay time vs control current for the first delay element version                                    |    |

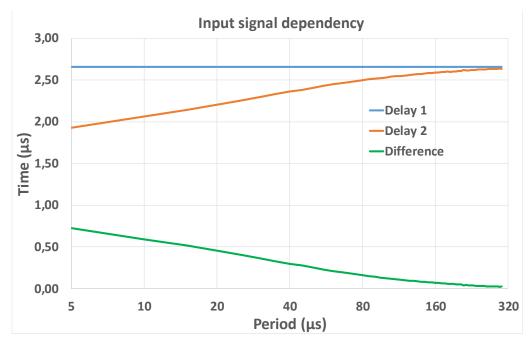

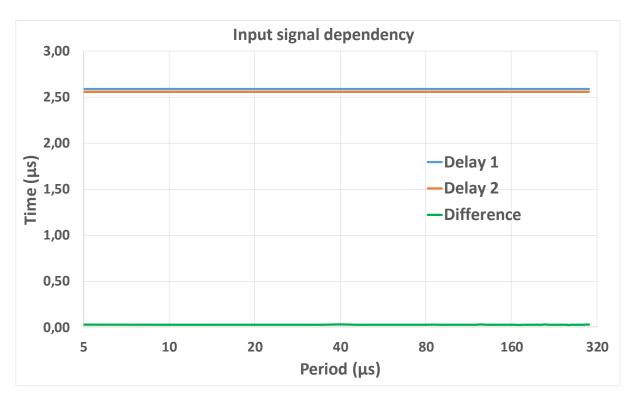

| Figure 75 Input signal dependency analysis                                                                     | 68 |

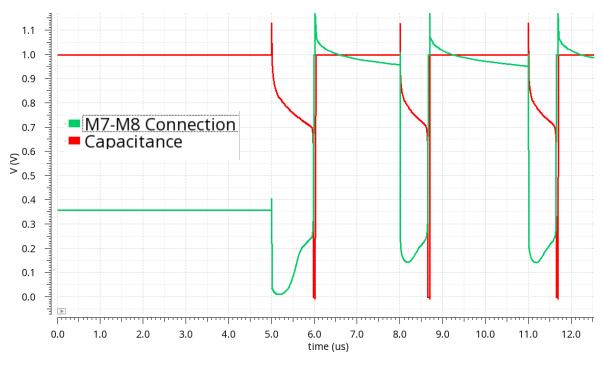

| Figure 76 Input signal dependency for the first delay element version                                | . 69 |

|------------------------------------------------------------------------------------------------------|------|

| Figure 77 Stored charge in the node that connects the transistors M7 and M8                          | . 69 |

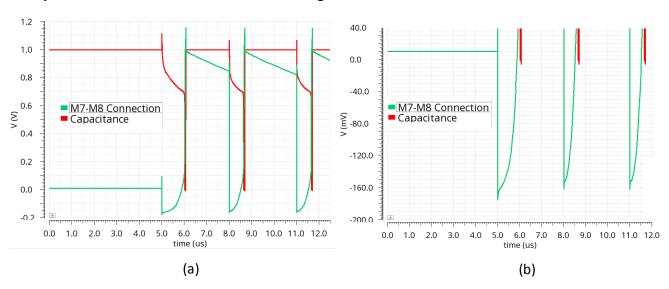

| Figure 78 (a) Effect of adding a NMOS transistor in parallel to M8 to create a MOS passgate; (b) Sat |      |

| figure as (a) with a different scale to better appreciate the voltage variations                     | . 70 |

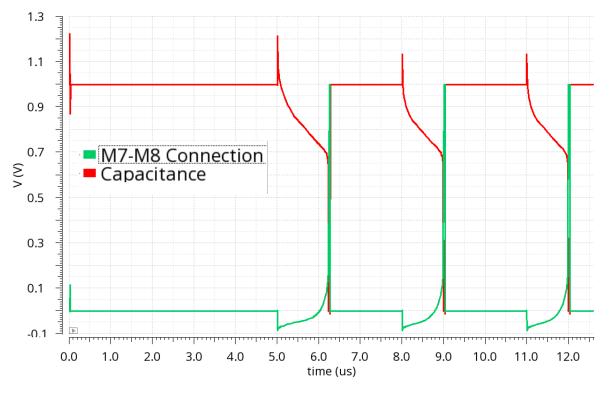

| Figure 79 Tension at the PMOS switch node after adding an nmos switch transistor                     | . 70 |

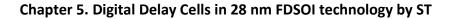

| Figure 80 Input signal dependency for the second delay element version                               | . 71 |

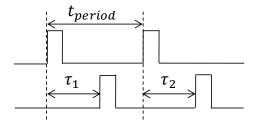

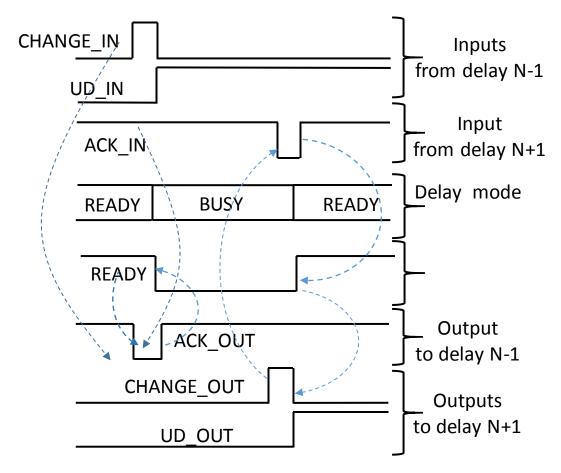

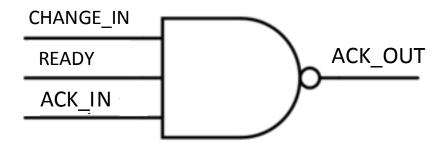

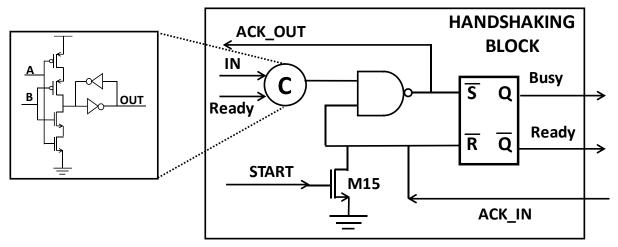

| Figure 81 Handshaking protocol                                                                       | . 72 |

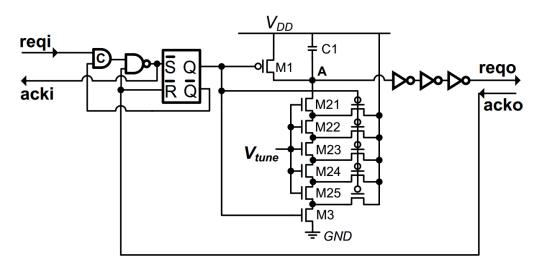

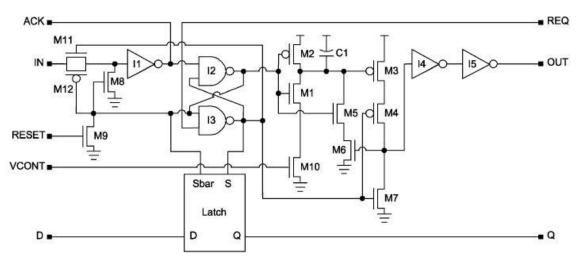

| Figure 82 Acknowledge signal generation in [50]                                                      | . 72 |

| Figure 83 Handshaking hazard                                                                         |      |

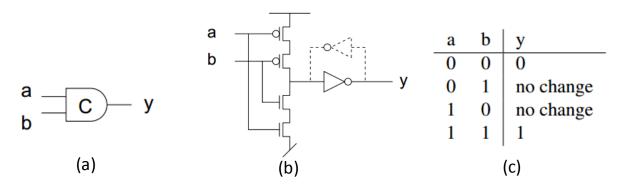

| Figure 84 Characteristics of a Muller gate. (a) Symbol, (B) Common implementation (c) Truth table    |      |

| [56]                                                                                                 |      |

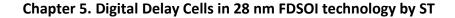

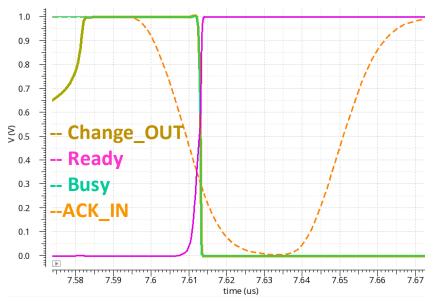

| Figure 85 Hazard free handshaking circuit                                                            | . 74 |

| Figure 86 Simulation demonstrating the functionning of the handshake elements                        | . 74 |

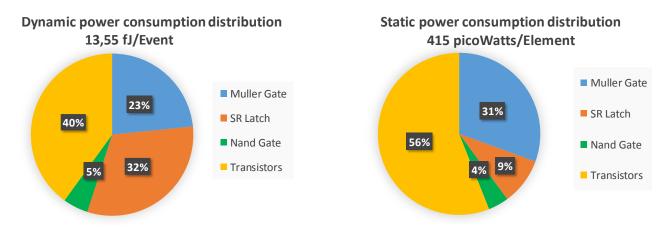

| Figure 87 Dynamic and Static power consumption of the delay element                                  | . 75 |

| Figure 88 Inverter used to control the cascode transistor                                            | . 76 |

| Figure 89 EGVLVT MOS passgate to control the discharge capacitance                                   |      |

| Figure 90 Overshoot voltage before the implementation of the PMOS switch                             |      |

| Figure 91 Reduction on the voltage overshoot due to the use of an EGVLVT CMOS switch                 |      |

| Figure 92 PMOS transistor used to control the fast discharge source                                  |      |

| Figure 93 Delay operation with the PMOS switch controlling the fast charge source                    |      |

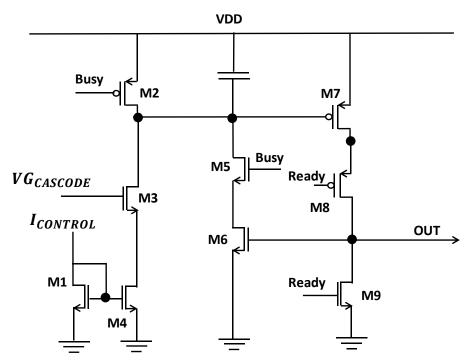

| Figure 94 Final delay version (handshake elements not included)                                      |      |

| Figure 95 Monte-Carlo simulation RUN (a) Delay time for the first pulse, (b) delay time for the seco |      |

| pulse                                                                                                |      |

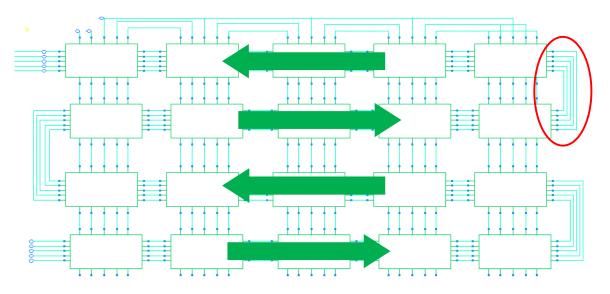

| Figure 96 Ladder-snail structure, employed for cascading granular delays                             |      |

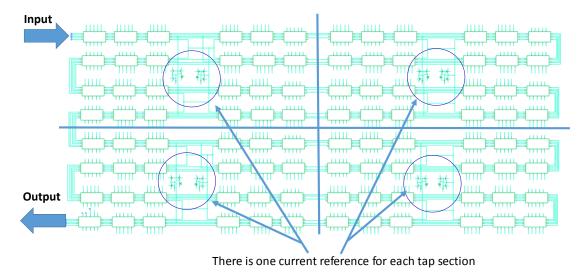

| Figure 97 Delay tap implementation                                                                   |      |

| Figure 98 Final delay cell Layout modify to correct Density Errors                                   |      |

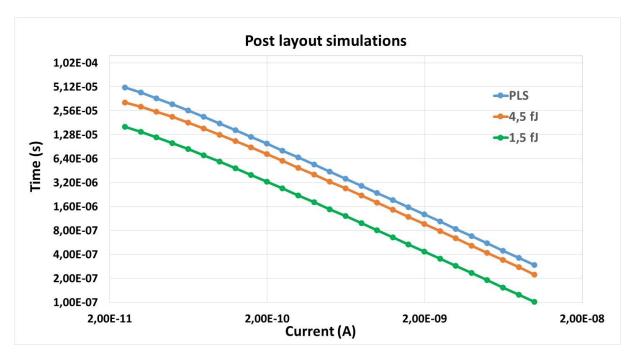

| Figure 99 Post layout simulations considering all parasitics, the implemented capacitance value 4.5  |      |

| and the original design with a 1.5fJ capacitance                                                     |      |

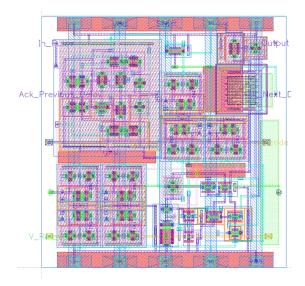

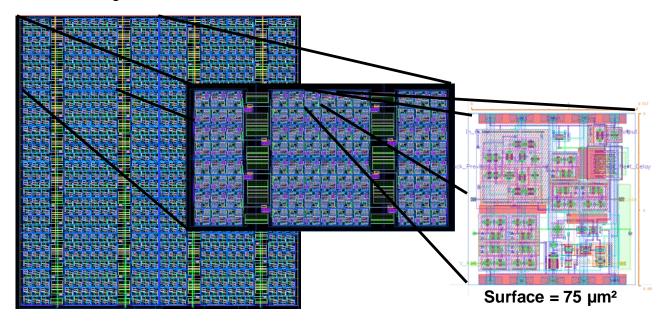

| Figure 100 Layout implementation of the delay taps                                                   |      |

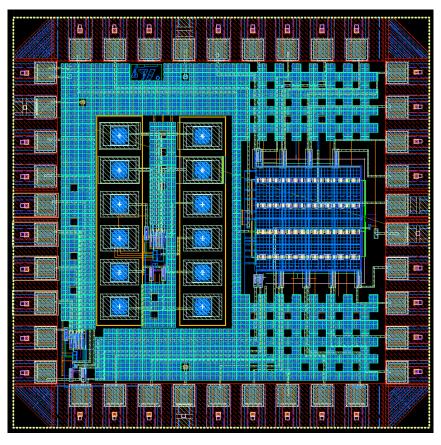

| Figure 101 Integrated circuit layout                                                                 |      |

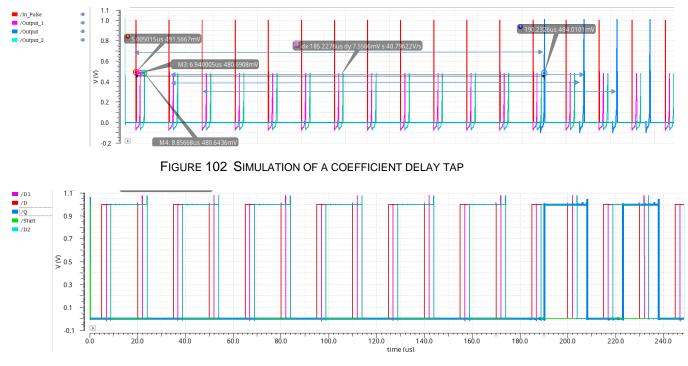

| Figure 102 Simulation of a coefficient delay tap                                                     |      |

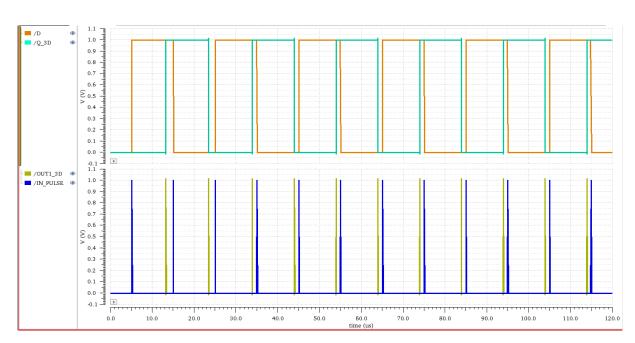

| Figure 103 Propagation of the binary information through the delay tap                               |      |

| Figure 104 3 Delay simulation with output buffers                                                    |      |

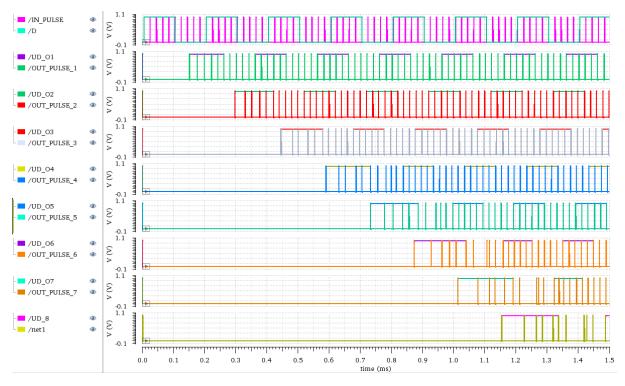

| Figure 105 Eight delay tap structure simulation                                                      |      |

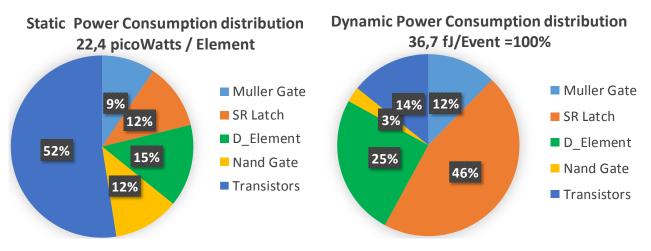

| Figure 106 Power consumption breakdown of the delay element with D latch                             |      |

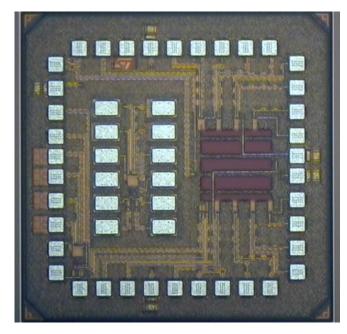

| Figure 107 Chip Photograph                                                                           |      |

| Figure 108 Packaged integrated circuit                                                               |      |

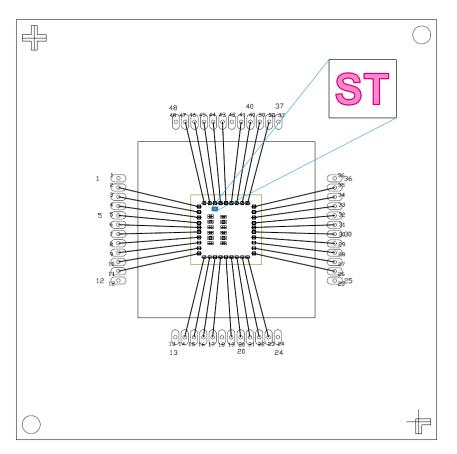

| Figure 109 Wire bonding connections between the die and the package                                  |      |

| Figure 110 Socket and board employed for measurements                                                |      |

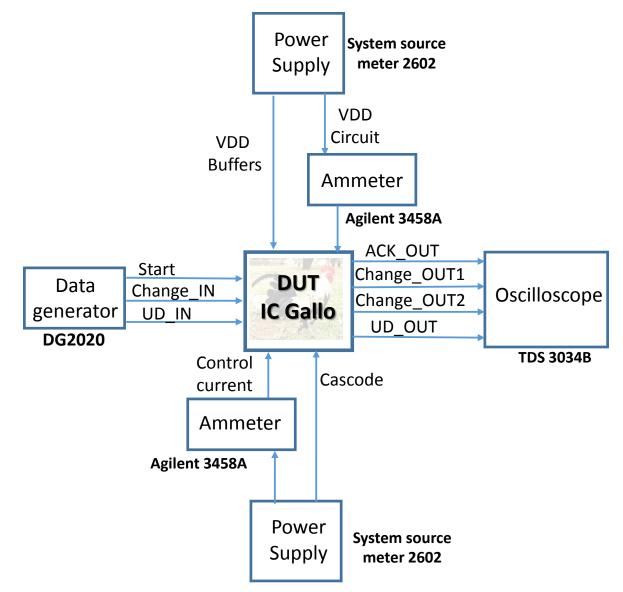

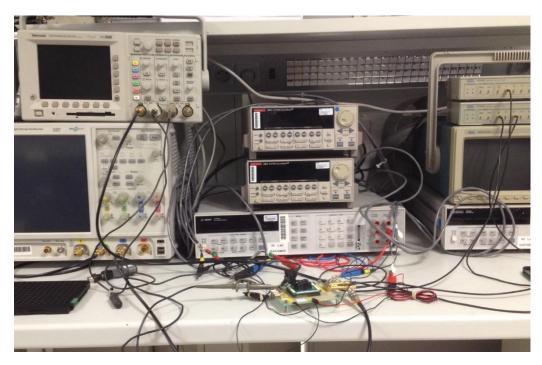

| Figure 111 Test bench schematic                                                                      |      |

| Figure 112 Test bench implementation                                                                 |      |

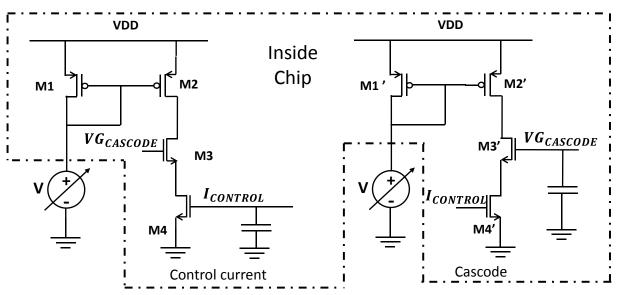

| Figure 113 Biasing circuit of the delay structure                                                    |      |

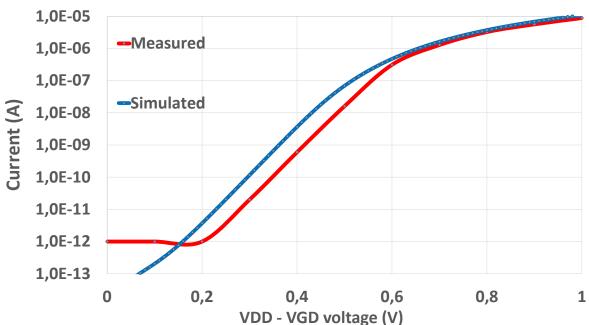

| Figure 114 Characterization of the pmos transistor employed as current reference                     |      |

|                                                                                                      |      |

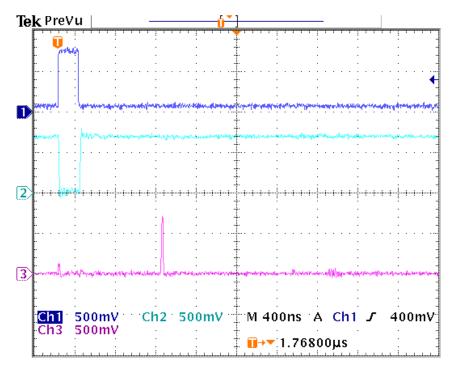

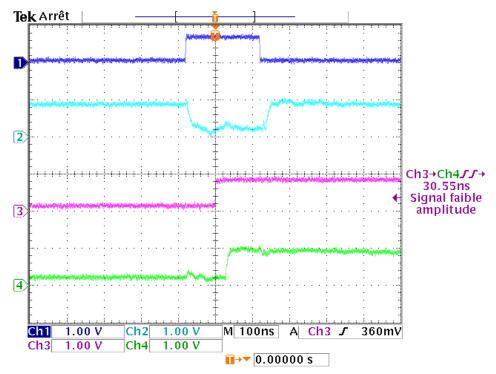

| Figure 115 Delay signals: Input signal (Blue), Acknowledge signal (Cyan), Output (Pink)              |      |

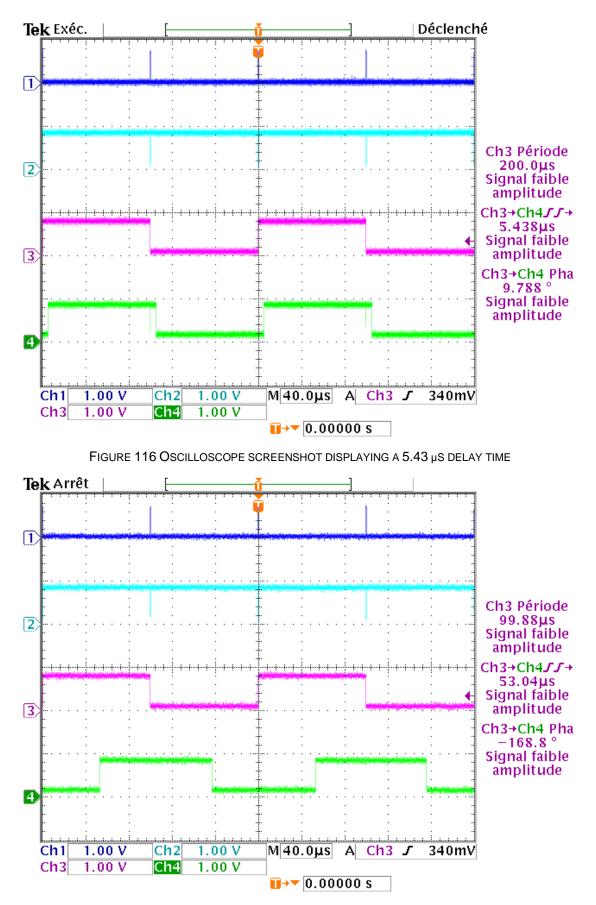

| Figure 116 Oscilloscope screenshot displaying a 5.43 µs delay time                                   |      |

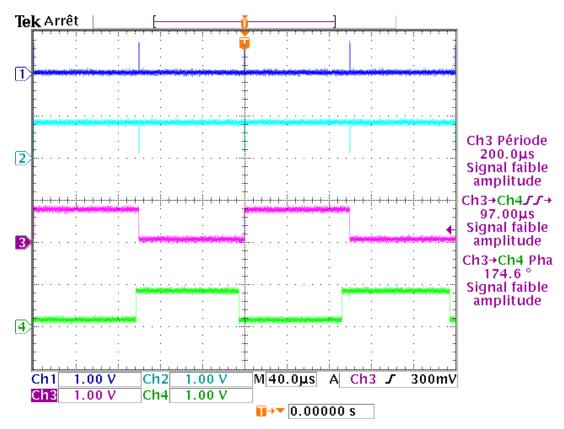

| Figure 117 Oscilloscope screenshot displaying a 53 μs delay time                                     |      |

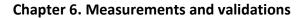

| Figure 118 Oscilloscope screenshot displaying a 97 $\mu$ s delay time                                |      |

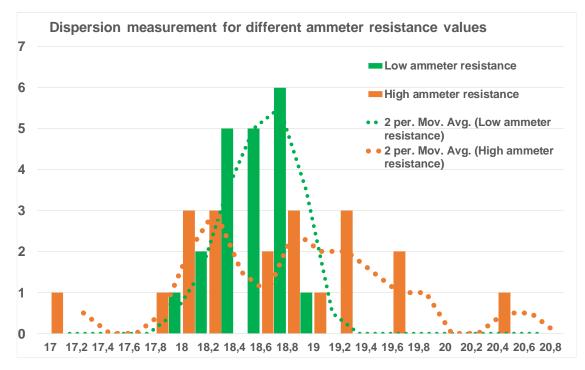

| Figure 119 Effects of the internal ammeter resistance on dispersion                                  | 100  |

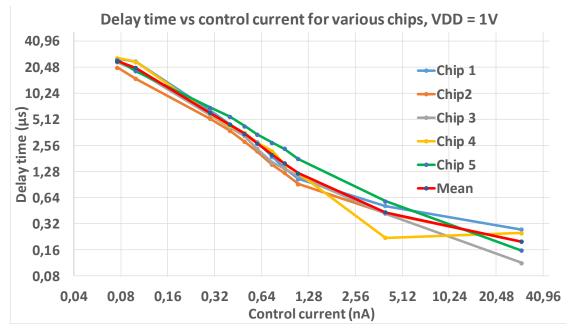

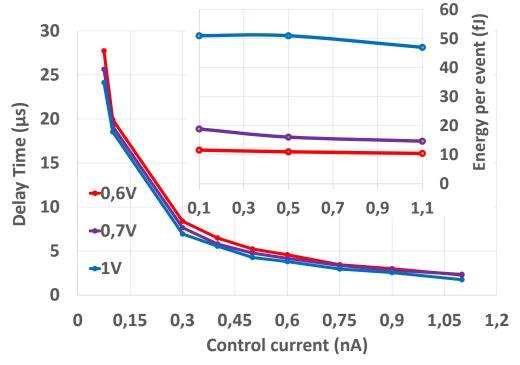

| Figure 120 Delay time vs control current for various chips                                           | 100   |

|------------------------------------------------------------------------------------------------------|-------|

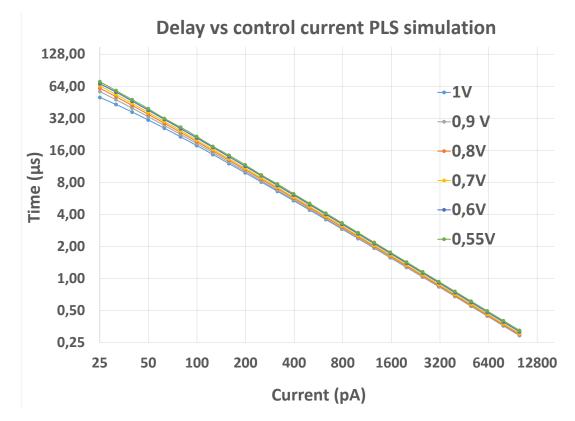

| Figure 121 Simulated delay time for different vdd values                                             | 101   |

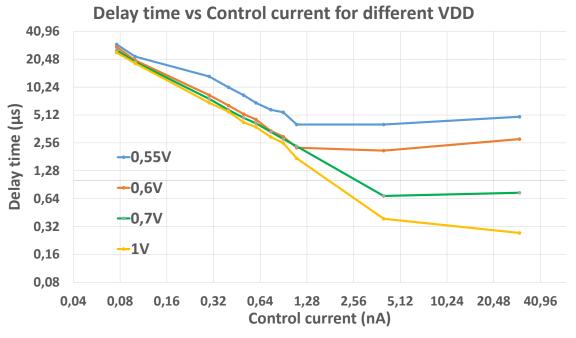

| Figure 122 Delay time for different VDD values                                                       | . 101 |

| Figure 123 Shortest delay obtained in measurements for a VDD OF 0.7V                                 | . 102 |

| Figure 124 Dynamic power consumption for different vdd voltages, the corresponding delay time        | is    |

| also indicated                                                                                       | 103   |

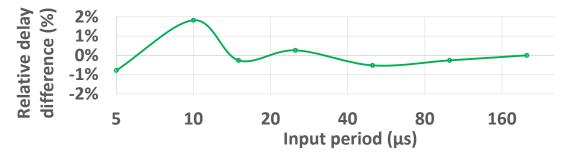

| Figure 125 Measured delay time versus the period of the repetitive input pulses for a delay cell     |       |

| configured at 3.84 μs and a supply voltage of 0.7 V                                                  | . 103 |

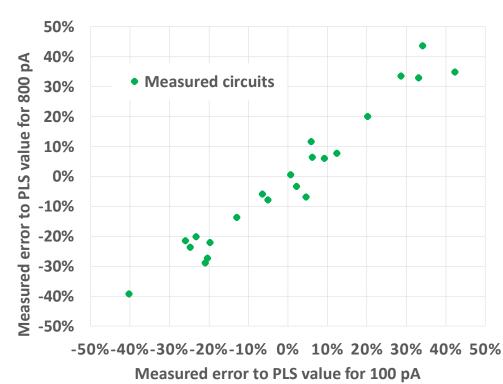

| Figure 126 Statistical dispersion in relative percentage with respect to the simulated values, for 2 |       |

| control currents measured for 22 circuits                                                            | . 104 |

| Figure 127 Proposed demonstrator scheme                                                              | 110   |

## List of Tables

| Table 1 Largest harmonic and SFDR for different bit resolutions 1                                 | 10             |

|---------------------------------------------------------------------------------------------------|----------------|

| Table 2 Comparison between DT and CT ADC conversion 1                                             | 15             |

| Table 3 Power consumption of different audio feature extraction tasks [43] 2                      | 29             |

| Table 4 State of the art of low power INTEGRATED FEATURE extractor filter banks                   |                |

| Table 5 Comparison of Different CT ADC Architectures                                              | 35             |

| Table 6 Dynamic power consumption of the delay elements in a CT System in function of the ADC     |                |

| Resolution                                                                                        | 35             |

| Table 7 Characteristics of the proposed filter bank                                               | 38             |

| Table 8 Characteristics of the delay taps for different ADC resolutions                           | 11             |

| Table 9 Delay element specifications for different ADC resolutions                                | 13             |

| Table 10 Comparison between number of transitions with and without a glitch eliminator circuit    |                |

| quantified over a 5ms period 4                                                                    | 15             |

| Table 11 Worst case scenario dynamic power consumption5                                           | 51             |

| Table 12 Typical case scenario power consumption5                                                 |                |

| Table 13 State-of-the-art of digital delay elements6                                              | 51             |

| Table 14 Device sizes of the delay shown in Figure 947                                            | 79             |

| Table 15 Power consumption comparison between the first and final versions of the delay element 7 | 79             |

| Table 16 Mismatch results of the delay element 8                                                  | 30             |

| Table 17 Performance comparison between the State-of-the-art and our designed delay element 8     | 38             |

| Table 18 Comparison of system performance with state-of-the-art implementations                   | 39             |

| Table 19 Pinout connections between the die and the package                                       | <del>)</del> 3 |

| Table 20 Statistical analysis of delay variations due to mismatch10                               | )4             |

| Table 21 Measured mismatch for different delay taps 10                                            | )5             |

| Table 22 Static power consumption as a function of the temperature 10                             | )6             |

| Table 23 Comparison with state-of-the-art delay cells10                                           | )6             |

| Table 24 Comparison of system performance with state-of-the-art implementations based on          |                |

| measured delay performance                                                                        | )7             |

## List of abbreviations

| ADC    | Analog to Digital converter               |

|--------|-------------------------------------------|

| ASR    | Automatic speech recognition              |

| BPF    | Band-pass filter                          |

| СА     | Continuous amplitude                      |

| CAGR   | Compound annual growth rate               |

| CMOS   | Complementary Metal Oxide Semiconductor   |

| СТ     | Continuous-time                           |

| CT-DSP | Continuous-time digital signal processing |

| DA     | Discrete amplitude                        |

| DAC    | Digital to Analog converter               |

| DIBL   | Drain induced barrier lowering            |

| DSP    | Digital signal processing                 |

| DT     | Discrete time                             |

| EEG    | Electroencephalogram                      |

| ENOB   | Effective number of bits                  |

| FD-SOI | Fully depleted silicon-on-insulator       |

| FFT    | Fast Fourier Transform                    |

| FIR    | Finite impulse response                   |

| IIR    | Infinite impulse response                 |

| ΙοΤ    | Internet of Things                        |

| LCS    | Level crossing sampling                   |

| LPF    | Low-pass filter                           |

| LSB    | Least significant bit                     |

| LVT    | Low voltage threshold                     |

| NBA    | National basketball association           |

| NMOS   | N-channel Metal Oxide Semiconductor       |

| NTPS   | Number of tokens produced per second      |

| PD-SOI | Partially depleted silicon-on-insulator   |

|        |                                           |

| PMOS | P-channel Metal Oxide Semiconductor  |  |

|------|--------------------------------------|--|

| Ρ٧Τ  | Process, voltage and temperature     |  |

| RDF  | Random dopant fluctuations           |  |

| RVT  | Regular voltage threshold            |  |

| SER  | Signal to error ratio                |  |

| SFDR | Spurious-free dynamic range          |  |

| SNDR | Signal to noise and distortion ratio |  |

| SNR  | Signal to noise ratio                |  |

| SR   | Set-Reset                            |  |

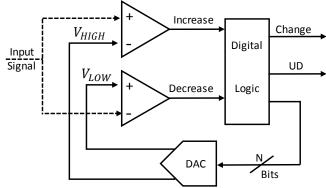

| UD   | Up-down                              |  |

| ULP  | Ultra-low power                      |  |

| US   | United States of America             |  |

| UTBB | Ultra-thin body and box              |  |

| VAD  | Voice activity detection             |  |

| VFC  | Voltage to frequency converter       |  |

| VFS  | Full-scale voltage                   |  |

| VR   | Variable resolution                  |  |

| ZCD  | Zero-crossing detectors              |  |

## Chapter 1 Introduction

### 1.1 Background (IoT)

The Internet of Things (IoT) is a communication paradigm that will allow every day's objects to communicate and interact with each other and with the users. Alwayson wireless sensors networks will be deployed to gather environmental data, the combination of which will make available an enormous amount of information in a very wide range of applications from medical aids to smart farming.

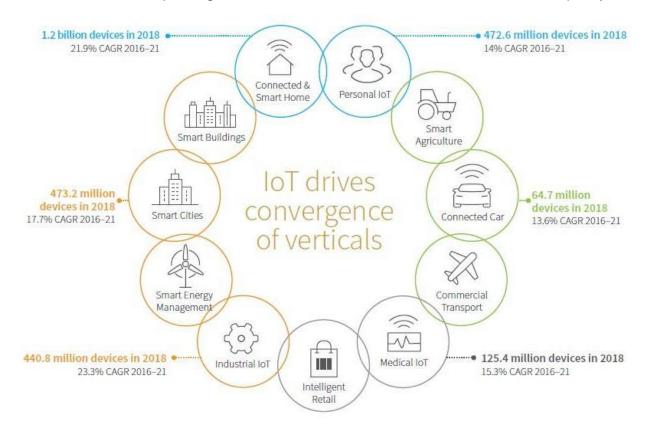

Figure 1 from [1] shows the different markets/sectors of IoT, also presented in some cases are the number of existing IoT devices and the compound annual growth rate (CAGR) which is a reliable economic measure to quantify the growth of an industry and/or market sector. At the current growth rate, the number of IoT devices for certain applications like smart homes, smart cities and manufacturing can be expected to double over the next five years.

Furthermore, IoT drives the convergence of verticals, which is the process through which different industries increase their bonds and cooperation with one another (for instance, manufacturing and intelligent retail, or smart energy management with smart cities and smart buildings). Overall, the new information gathered thanks to the IoT, will increase the productivity and efficiency across each economic sector, improving our interaction with the environment and our life quality.

FIGURE 1 DIFFERENT IOT APPLICATIONS, IN SOME CASES THE CAGR OF THE SECTOR IS INDICATED [1]

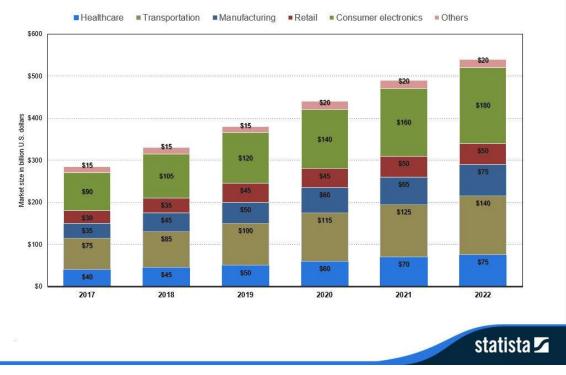

Figure 2 from [2] shows the market size and the expected growth of the IoT market in North America in billion U.S. dollars. The Figures indicate the contribution of each application sector to the overall market share. By 2022 the market size is expected to be above half a trillion dollars. The main sectors driving the growth of the IoT market are consumer electronics, transportation, and health care.

FIGURE 2 EXPECTED GROWTH OF THE IOT MARKET BY APPLICATION IN NORTH AMERICA [2]

#### **1.2 Motivation for this work**

IoT demands efficient detection systems, with high configurability capable to operate in wide spectrum of backgrounds, with high levels of integration to operate among other systems, with ultra-low-power consumption which is particularly critical for battery powered systems and with low production cost.

To comply with the demands posed by the implementation of IoT systems several aspects come into play: Circuit design techniques to improve configurability and overall performance of existing systems; novel advanced technologies that offer a larger integration, and improved performance in speed and power consumption; the need for applications in new domains like medical IoT or smart farming that drives innovation by posing new problems, for which existing implementation don't offer an optimal solution. For instance in order to finish the NBA season despite the coronavirus pandemic, the league has instaured the use of monitoring rings for the players and coaching staff [3]. These titanium made rings monitor the heart rate, temperature, sleep and motion patterns, of the individuals wearing it, detecting the symptoms of a coronavirus infection at least 72 hours in advance with a 90% accuracy.

Techniques for data acquisition through analog-to-digital conversion are well studied. There are many implementations for different applications as described by [4].

However, as new applications emerge conventional techniques where the analog input is converted into a stream of uniformly time spaced digital values, may not be best suited to answer the ultra-low-power specifications of IoT applications as further described in the next section. As described by [4] the race of the analog-to-digital conversion has been driven by the need of increasing the signal to noise ratio of signals, however for IoT applications the most critical parameter is power consumption.

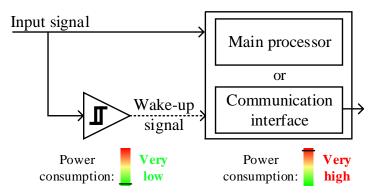

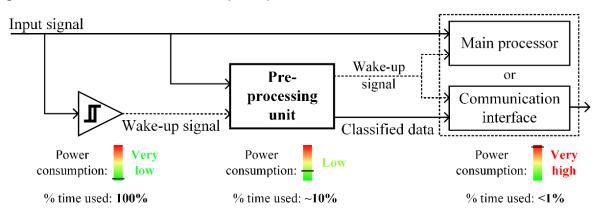

In traditional sensors implementations, the device does not embed significant processing units and thus its role is limited to sensing and transmitting the information. The largest contributor to the overall power consumption is thus the transmission of raw data to the remote unit in charge of recognition and signal processing [5]. To drastically reduce the consumption of a battery-powered sensor (which means increasing its lifetime), a new generation of intelligent sensors capable of performing recognition tasks, whatever the background is, is needed. Additional energy reduction is obtained by activating the different processing units when strictly required and by transmitting data only in the presence of relevant information. Thus an important issue is to find the best balance between local and remote processing.

Therefore, the motivation of this work is to explore novel design techniques that may be suitable to implement a new generation of sensors, highly configurable, capable of performing a significant part of the signal processing tasks, while exploiting the benefits offered by advanced technologies. Furthermore, demonstrate the feasibility of an implementation for a given application offering a performance that meets the configurability, low cost and low power consumption required by IoT applications.

### **1.3 Feature extraction**

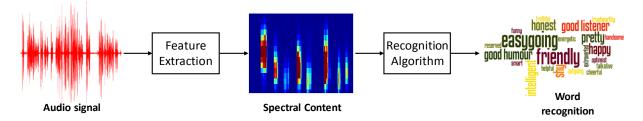

Sensor data acquisition systems typically use an analog-to-digital converter (ADC) at a constant sampling rate, scaled to the signal bandwidth, to digitize the incoming waveforms for subsequent processing. This approach may however not have optimal efficiency for detection and recognition applications for two reasons. The first one is that many signals (particularly those involve in the monitoring of natural phenomena) have a physical bandwidth which is much higher than the actual information rate. Take the example of speech recognition systems, although audible sounds have a frequency up to 20kHz (one new data each 25µs in a sampled system), the "useful information" rate is less than 10 Hz (the average duration of a syllable is 150 ms) [6]. Thus instead of implementing a system that digitize the audio signal generating and transmitting 40 thousand samples per second to a complex processing unit, we can envision a system that transmits only 10 samples per second. The second reason is that, in many applications, the information is very sparse in time, meaning long time periods without any useful information. Therefore, a complete signal reconstruction may not be required. Instead, specific information called features can be sufficient for further processing [7].

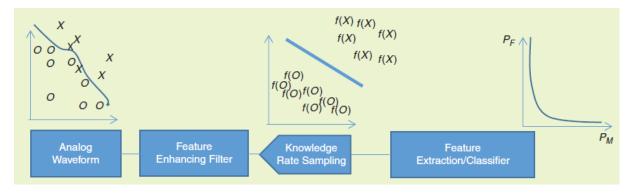

Figure 3 shows the architecture of a feature extraction system. The analog waveform is first processed using a feature enhancing filter that can be implemented in both the analog and digital domains. This block applies a signal processing that increases the difference between signals containing specific characteristics. The next step is to sampled the signal at knowledge/information rate and finally send it to a classification/detection algorithm. The overall performance of a feature extraction systems is evaluated in terms of hit rate, which is the percentage of correct decisions that the system makes for a given signal in a certain scenario.

It is to note that in the case where the feature enhancing filter is implemented in the digital domain, two samplings occur, the first at Nyquist-rate in the feature enhancing block and the second one at information rate to send the information to the feature extraction classifier. Additionally the feature enhancing filter is adapted to the complexity of the classification/detection algorithm.

FIGURE 3 ARCHITECTURE OF A FEATURE EXTRACTION SYSTEM [7]

An implementation of a feature extraction system is presented in [8]. The system is a scalable electroencephalogram (EEG) acquisition system which predicts seizure events of people suffering from epilepsy. The task is to differentiate between normal neural spikes employed to move a limb and abnormal spikes that will trigger a seizure episode. To perform this task, it is required to extract the spectral content analysis of neural spikes, in effect spikes that will trigger a seizure episode and normal neural spikes have a different spectral content.

A bank of filters is used to generate a feature vector that is latter employed to classify the signals accordingly.

Feature extractions systems are currently implemented in both the analog and the digital domains. Digital implementations occupy a smaller silicon area [9], have high configurability [10], and may easily be implemented in advanced technology nodes. Analog implementations have a lower power consumption [11], [12] but lack configurability, occupy a large silicon area and are not easily integrated into advanced technology nodes.

Since, each approach has advantages and drawbacks that are complementary an alternative approach capable of combing the best attributes of both analog and digital systems is needed. A possible alternative is continuous-time digital signal processing systems (CT-DSP) and will be presented in the next chapter.

## **1.4 Thesis contributions**

The framework of this work is the implementation of a CT-DSP system applied for the feature extraction of audio signals. Thus, the main contributions of this work are the following:

- A study of the implementation requirements of an audio feature recognition application [13].

- A novel architecture inspired by the human cochlea to generate spectrograms of an audio signal using CT-DSP.

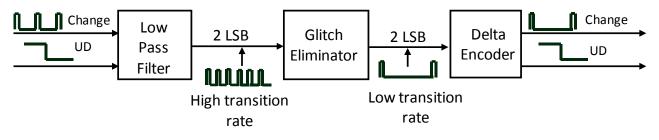

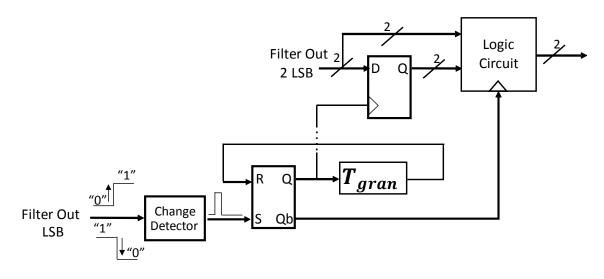

- A new technique based on glitch elimination and delta encoding to enable the cascade of CT-DSP finite impulse response (FIR) filters.

- A new CT-DSP block that calculates the instantaneous power of a signal and integrates it over a time window to estimate the corresponding energy, needed to create spectrograms [Patent filed].

- A delay element in 28nm FD-SOI technology, exhibiting a record tuning range between 30ns – 97µs and a dynamic power consumption below 15fJ for a VDD voltage of 0.7 V [14].

As a summary, this work gives a significant step forward towards the implementation of CT-DSP systems for audio feature extraction applications. System-level performance estimations based on the measured delay values show the system could be able to process typical speech with an event-drive power consumption below  $2\mu$ W in range of existing analog implementations and a silicon area inferior to 1.5mm<sup>2</sup> in range of existing digital implementations.

The principles presented can be used for any other detection or recognition application that demands the extraction of spectral content information.

## 1.5 Thesis Layout

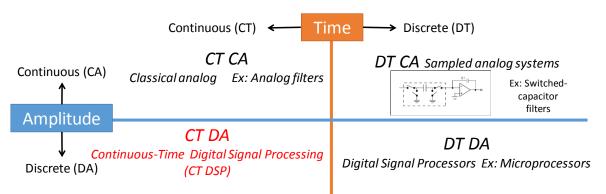

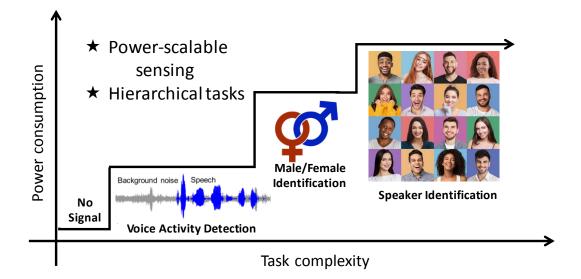

The rest of the thesis is organized as follows. *Chapter 2* introduces the theoretical concepts required for understanding CT-DSP systems, such as signal quantization, aliasing, and sampling. For this purpose, a comparison between continuous-time (CT) and discrete-time (DT) systems is presented. Next, the state-of-the-art of existing CT systems is detailed and advantages and challenges are identified. This analysis concludes that the implementation of CT-DSP systems is particularly interesting for applications in which signal activity is sparse in time, with a varying spectral content. The research directions to meet the challenges of implementing and improving the performance of a CT-DSP system are traced.

In *Chapter 3* we show that the recognition and detection of audio signals could benefit from a CT-DSP implementation. The basic characteristics of audio signals and

the functioning of human hearing are presented. Audio recognition applications require a unit to extract the spectral content (spectrogram) of the signal. For low-complexity recognition tasks, like voice activity detection (VAD), the unit that generates spectrograms consumes most of the system resources. Thus, the state-of-the-art of existing solutions to generate spectrograms, such as Fast-Fourier transforms (FFT), analog filter banks and digital filter banks, is presented. Since the advantages and disadvantages of each approach are complementary, a new approach encompassing the positive aspects and overcoming the drawbacks of existing implementations is proposed.

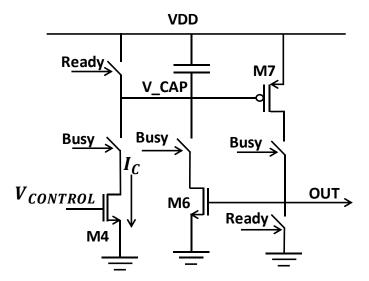

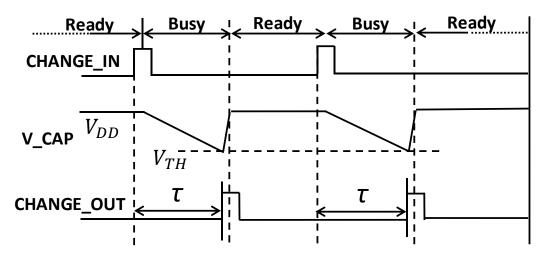

*Chapter 4* introduces the proposed system to generate spectrograms of an audio signal using CT-DSP. The system requirements and the architectural choices made to size the system are presented. Novel approaches to overcome the challenges of CT systems, such as the cascade of CT FIR filters and the estimation of the instantaneous power of a signal are detailed. Delay lines are a key element of CT-DSP systems, representing approximately 70% of the total system power consumption and silicon area for the envisaged application. The design of ultra-low-power and low area digital delay elements is therefore required. The requirements on the digital delay element are detailed and an estimation of the overall system performance for the targeted delay line requirements is derived. Additionally a novel alternative approach that combines cascaded low-pass filters and energy estimation circuits to create equivalent and band-pass filter functions is presented.

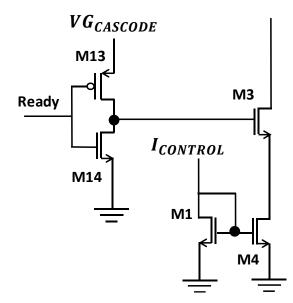

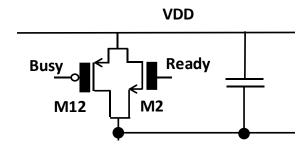

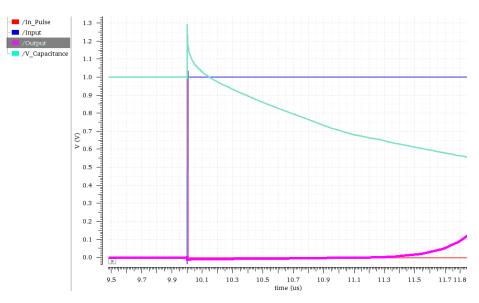

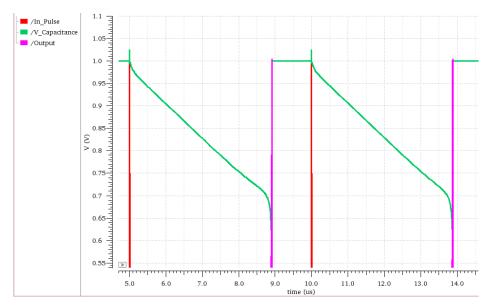

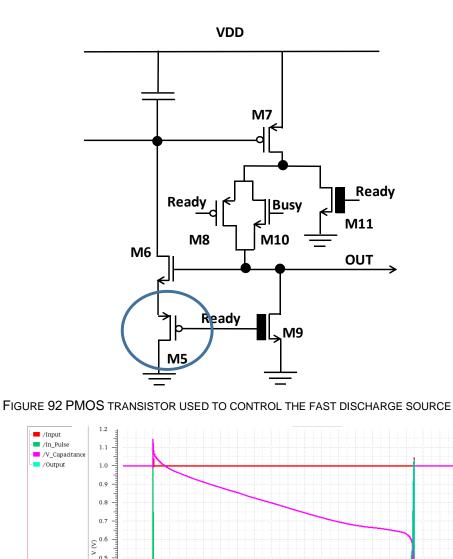

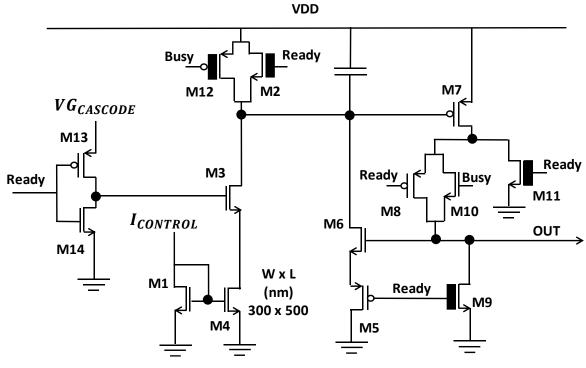

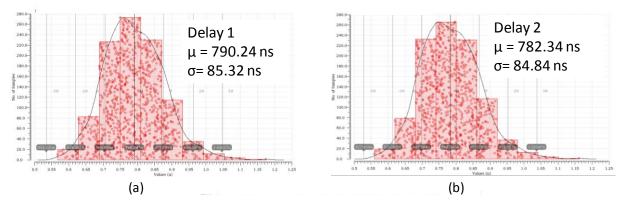

*Chapter 5* describes the design of a novel digital delay element in 28nm CMOS FD-SOI technology by STMicroelectronics, compatible with the system-level constraints detailed in Chapter 4. This has been possible thanks to the specific properties of the FD-SOI technology. A detailed description of implemented solutions to improve the performances of the digital delay element are presented. Finally, the design of an integrated circuit containing individual delay structures for single delay characterization and a delay line with several hundreds of cascaded delay elements is presented.