## **Analog Hardware Fault Diagnosis**

#### Antonios Pavlidis

#### ▶ To cite this version:

Antonios Pavlidis. Analog Hardware Fault Diagnosis. Electronics. Sorbonne Université, 2021. English. NNT: . tel-03526323v1

# $\begin{array}{c} {\rm HAL~Id:~tel\text{-}03526323} \\ {\rm https://hal.science/tel\text{-}03526323v1} \end{array}$

Submitted on 27 Jan 2022 (v1), last revised 22 Jul 2022 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

# ANALOG HARDWARE FAULT DIAGNOSIS (DIAGNOSTIC DE FAUTES MATÉRIELLES DANS LES CIRCUITS ANALOGIQUES)

# présentée par ANTONIOS PAVLIDIS

# École Doctorale Informatique, Télécommunications et Électronique

réalisée au Laboratoire d'Informatique Paris 6

#### soutenue le 13 July 2021

#### devant le jury composé de :

| M.   | Patrick Girard, DR CNRS, LIRMM, Montpellier, France           | Rapporteur             |

|------|---------------------------------------------------------------|------------------------|

| M.   | Manuel Barragan, CR CNRS, TIMA, Grenoble, France              | Rapporteur             |

| M.   | Yann Deval, Prof., Université Bordeaux, IMS, Bordeaux, France | Président du Jury      |

| M.   | Wim Dobbelaere, On Semiconductor, Oudenaarde, Belgium         | Examinateur            |

| M.   | Andreas Kaiser, DR CNRS, IEMN, Lille, France                  | Examinateur            |

| M.   | Stephen Sunter, Siemens Digital Industries Software, Canada   | Examinateur            |

| Mme. | Marie-Minerve Louërat, CR CNRS, LIP6, Paris, France           | Co-directrice de Thèse |

| M.   | Haralampos-G. Stratigopoulos, DR CNRS, LIP6, Paris, France    | Directeur de Thèse     |

| M.   | Eric Faehn, STMicroelectronics, Crolles, France               | Invité                 |

Nowadays, the number of Integrated Circuits (ICs) used in safety- and mission-critical applications, i.e., automotive, smart health-care, defense, critical infrastructure, etc., is ever increasing. These applications demand that ICs carry functional safety properties. In this thesis, we develop a Built-In Self Test (BIST) approach for Analog and Mixed-Signal (A/M-S) ICs, called *Symmetry-Based Built-In Self Test (SymBIST)*, which achieves several objectives towards the functional safety goal.

SymBIST is a generic BIST paradigm based on identifying inherent invariances and constructing them by processing internal signals. By construction, invariances should hold true only in error-free operation, while their violation points to abnormal operation. The invariances are being checked using dedicated on-die checkers. SymBIST is a one-stop solution for three different functional safety goals. First, it can be used for defect-oriented test with high defect coverage towards post-manufacturing test quality improvement. Second, it can be applied for on-line test concurrently with the operation towards detecting aging, latent defects, and single event upsets. Third, it can be used for fault diagnosis with high diagnosis resolution and small diagnosis cycle towards yield learning and implementing corrective actions to avoid failure re-occurrence.

We demonstrate *SymBIST* on an industrial Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) Intellectual Property (IP). We also demonstrate the design of on-chip digital test stimulus generators and minimal re-configurations required in the defect-oriented and diagnosis operation modes. For the defect-oriented test use case, SymBIST offers a fast time in the order of sub-µs and Likelihood-Weighted (L-W) defect coverage of over 86%. For the on-line test use case, SymBIST checks the invariances in real-time without interrupting the operation of the circuit and irrespective of the input and detects aging, latent defects, and transient errors. For the diagnosis use case, the SymBIST response is used as a digital diagnostic measurement. To reduce defect ambiguity, we use the same test infrastructure, but with different *SymBIST* setups. SymBIST shows high diagnosis resolution, i.e., 73% correct diagnosis of defects while over 96% of defects are in ambiguity groups of maximum size 5, and offers a fast diagnosis cycle in the order of a few μs. Last but not least, SymBIST features no performance penalty, an area overhead of around 5%, and has a fully digital interface making it compatible with modern digital test access mechanisms based on two external pins.

Aujourd'hui, le nombre de circuits intégrés (CIs) utilisés dans les applications liées à des missions critiques et à la sûreté, comme l'automobile, la e-santé, la défense, les infrastructures critiques, ne cesse d'augmenter. Pour être utilisés dans ces applications, les CIs doivent présenter des propriétés de sûreté fonctionnelle. Cette thèse introduit un auto-test intégré (BIST) pour les CIs analogiques et à signaux mixtes (AMS), appelé autotest à symétrie (SymBIST), qui offre plusieurs voies pour obtenir la sûreté fonctionnelle.

SymBIST repose sur le principe du BIST et sur l'existence de signaux invariants, inhérents au CI. Les invariants retenus (tension ou courant) possèdent une valeur constante pour un fonctionnement nominal du CI, et une valeur bien distincte en cas de fonctionnement erroné. Les invariants sont vérifiés à l'aide de dispositifs intégrés spécifiques. SymBIST est une solution qui répond à trois objectifs de sûreté fonctionnelle. Il est utilisé tout d'abord pour tester les défauts du CI avec une couverture de test élevée. Il est également utilisé pour le test en ligne, lors du fonctionnement du CI, afin de détecter le vieillissement, les défauts latents et les perturbations dues à un événement aléatoire. Enfin, il est utilisé pour diagnostiquer les défauts avec une grande précision, avant de la mise en œuvre d'actions de correction.

SymBIST est démontré sur un convertisseur analogique-numérique à approximations successives. Nous présentons également des générateurs de stimuli numériques pour le test sur puce qui nécessitent une reconfiguration mineure pour passer de la détection de défauts au diagnostic. SymBIST, utilisé pour tester les défauts, a un temps de réponse inférieur à la µs et offre une couverture de test, pondérée de la vraisemblance, supérieure à 86%. Pour le test en ligne, SymBIST effectue une mesure des invariants en temps réel, sans interrompre le fonctionnement normal du circuit et indépendamment de l'entrée, pour détecter le vieillissement, les défauts latents, et les erreurs transitoires. En ce qui concerne le diagnostic, la réponse de SymBIST offre une représentation numérique du diagnostic. Pour réduire l'ambiguïté de la détection des défauts, nous tirons parti de la même infrastructure de test, en modifiant sa configuration. SymBIST offre une précision de diagnostic élevée, avec un diagnostic de défaut valide à 73%, tandis que plus de 97% des défauts appartiennent à des ensembles inférieurs ou égaux à 5 éléments, le tout en quelques µs. Enfin, SymBIST n'entraîne aucune pénalité de performance du CI, requiert une augmentation de surface d'environ 5%, et possède une interface entièrement numérique qui le rend compatible avec les mécanismes modernes d'accès aux tests numériques basés sur deux connecteurs externes.

#### **PUBLICATIONS**

The following body of work has been published in the course of the thesis at hand:

- [1] A. Pavlidis, M.-M. Louërat, E. Faehn, A. Kumar, and H.-G. Stratigopoulos, "Symmetry-based A/M-S BIST (SymBIST): demonstration on a SAR ADC IP," in *Design*, *Automation & Test in Europe Conference Exhibition*, 2020, pp. 282–285.

- [2] A. Pavlidis, M.-M. Louërat, E. Faehn, A. Kumar, and H.-G. Stratigopoulos, "SymBIST: symmetry-based analog and mixed-signal built-in self-test for functional safety," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2021.

- [3] A. Pavlidis, E. Faehn, M.-M. Louërat, and H.-G. Stratigopoulos, "BIST-assisted analog fault diagnosis," in *IEEE European Test Symposium (ETS)*, 2021.

The following body of work has been published in collaboration with other projects:

- [1] S. El-Sayed, T. Spyrou, A. Pavlidis, E. Afacan, L. A. Camuñas-Mesa, B. Linares-Barranco, and H.-G. Stratigopoulos, "Spiking neuron hardware-level fault modeling," in 2020 IEEE 26th International Symposium on On-Line Testing and Robust System Design (IOLTS), 2020, pp. 1–4.

- [2] M. Elshamy, G. Di Natale, A. Pavlidis, M. Louërat, and H.-G. Stratigopoulos, "Hardware Trojan attacks in analog/mixed-signal ICs via the test access mechanism," in 2020 IEEE European Test Symposium (ETS), 2020, pp. 1–6.

- [3] M. Elshamy, G. Di Natale, A. Sayed, A. Pavlidis, M.-M. Louërat, H. Aboushady, and H.-G. Stratigopoulos, "Digital-to-analog hardware Trojan attacks," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2021.

Science may set limits to knowledge but should not set limits to imagination.

— Bertrand Russell, History of Western Thoughts, p.26 1945

#### ACKNOWLEDGMENTS

This thesis and a little bit more than 3-year of research finally come to an end with the support and the help of many people.

First of all I would like to thank Haralampos. Thanks for letting me find my way and for directing me whenever it was required. I was really lucky to have such a supervisor, and I am pretty sure all your PhD students will have the same opinion. The second person I would like to thank is my co-supervisor, Marie-Minerve. Marie-Minerve was always there to find a solution to any problem. Without her help our every day life in the lab would be much more difficult.

My every day life wouldn't be that amazing had I not shared my office with these amazing people. Thanks Julian, Sarah, Gabriel, Mohamed, Alan, Rodrigo, Ning, Ilias and Theofilos. We made so many wonderful things and I really miss most of them.

I would also like to acknowledge the financial support in the framework of the French National Research Agency (ANR) Electrical Diagnosis for IoT SoCs in Automotive (EDITSoC) project with N° ANR-17-CE24-0014-02. I would like to thank everyone who participated in the EDITSoC project from LIRMM and STMicroelectronics, and shared with me his knowledge. Especially, I would like to thank Eric Faehn and Anand Kumar from STMicroelectronics who worked with me in this project. I would also like to thank Stephen Sunter from Mentor, A Siemens Business, for the technical advice on the Tessent®DefectSim mixed-signal defect simulator. Finally, I would like to thank everyone I have worked with from Sorbonne University, LIP6 and EDITE. It was a pleasure working with you.

#### CONTENTS

| Ι | MAI                 | N PAR   | T                                                    |                                 |

|---|---------------------|---------|------------------------------------------------------|---------------------------------|

| 1 | INT                 | RODUC   | CTION                                                | 3                               |

|   | 1.1 Problem Outline |         |                                                      |                                 |

|   |                     | 1.1.1   | The Need for Testing                                 | 3                               |

|   |                     | 1.1.2   | The Need for Diagnosis                               | 4                               |

|   | 1.2                 | Functi  | ional Safety as a Requirement in Modern Applications | 5                               |

|   | 1.3                 | BIST t  | towards Functional Safety                            | 6                               |

|   | 1.4                 | Thesis  | s Contribution                                       | 7                               |

|   | 1.5                 | Thesis  | s Structure                                          | 8                               |

| 2 | PRI                 | OR ART  | T ON ANALOG HARDWARE TESTING AND DIAGNOSIS           | 9                               |

|   | 2.1                 | Prior 2 | Art on Analog BIST                                   | 9                               |

|   |                     | 2.1.1   | Generic Defect-Oriented BIST                         | 9                               |

|   |                     |         | 2.1.1.1 Topology Modification BIST                   | 9                               |

|   |                     |         | O 111 II DIOTE                                       | 10                              |

|   |                     | 2.1.2   | ADC BIST                                             | 11                              |

|   |                     |         | 2.1.2.1 ADC BIST Measuring Dynamic Specifica-        |                                 |

|   |                     |         |                                                      | 11                              |

|   |                     |         | A D C DIOTE A C                                      | 12                              |

|   |                     |         |                                                      | 13                              |

|   |                     | 2.1.3   | DE DIOT                                              | 13                              |

|   |                     | 2.1.4   |                                                      | 14                              |

|   |                     | •       |                                                      | 14                              |

|   |                     |         | - 1 0 · 1                                            | 15                              |

|   |                     | 2.1.5   |                                                      | 15                              |

|   |                     | 2.1.6   |                                                      | 16                              |

|   |                     | 2.1.7   |                                                      | 16                              |

|   | 2.2                 | •       |                                                      | 17                              |

|   |                     | 2.2.1   |                                                      | ,<br>17                         |

|   |                     | 2.2.2   | 3.6 1.1 D 1.D.                                       | - <i>7</i><br>17                |

|   |                     | 2.2.3   | T 1. D                                               | - <i>,</i><br>19                |

|   |                     | 2.2.4   | T 1. D II DIOTE                                      | 20                              |

|   | 2.3                 | •       |                                                      | 20                              |

| 3 |                     |         |                                                      |                                 |

| ) | 3.1                 |         | TOTE DATE A 1 A CO.                                  | <ul><li>23</li><li>23</li></ul> |

|   | 3.2                 | -       |                                                      |                                 |

|   | 3.3                 | _       |                                                      | <ul><li>25</li><li>26</li></ul> |

|   | 3·3                 |         |                                                      |                                 |

|   | 3·4<br>3·5          |         | <del>-</del>                                         | 27<br>28                        |

|   |                     | _       | · ·                                                  |                                 |

|   | 3.6                 | COLICI  | usions                                               | 30                              |

| 4 | CAS        | E STUI | DY AND BIST INFRASTRUCTURE                                                            | 31                |

|---|------------|--------|---------------------------------------------------------------------------------------|-------------------|

|   | 4.1        | Case S | Study: SAR ADC                                                                        | 31                |

|   |            | 4.1.1  | SAR ADC Principle                                                                     | 31                |

|   |            | 4.1.2  | SAR ADC IP by STM                                                                     | 32                |

|   | 4.2        | Invari | iances in SAR ADC IP                                                                  | 36                |

|   | •          | 4.2.1  | SymBIST <sub>1</sub>                                                                  | 36                |

|   |            | 4.2.2  | SymBIST2                                                                              | 37                |

|   |            | 4.2.3  | SymBIST <sub>3</sub>                                                                  | 37                |

|   |            | 4.2.4  | SymBIST4                                                                              | 38                |

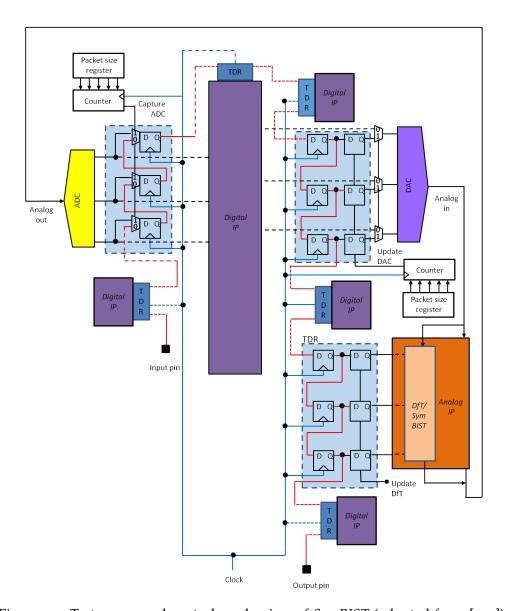

|   | 4.3        |        | SIST Infrastructure                                                                   | 38                |

|   | 13         | 4.3.1  | Test Stimulus and Re-configuration for Applying                                       | )                 |

|   |            | 13     | SymBIST                                                                               | 38                |

|   |            | 4.3.2  | Checker Design                                                                        | 40                |

|   |            | 4.3.3  | Checker Self-Test                                                                     | 43                |

|   |            | 4.3.4  |                                                                                       | 43                |

|   | 4.4        |        | SIST Efficiency                                                                       | 46                |

|   | 7.7        | 4.4.1  | SymBIST Test Time                                                                     | 46                |

|   |            | 4.4.2  | Overheads                                                                             | 46                |

|   | 4.5        |        | usions                                                                                | 47                |

| 5 |            |        | OVERAGE ESTIMATION FRAMEWORK                                                          | 49                |

| ) | 5.1        |        | t Simulation Workflow                                                                 | 49<br>49          |

|   | 5.2        |        | t Model                                                                               | 49<br>49          |

|   | 5.2<br>5.3 |        | t Simulator                                                                           | 50                |

|   | 5.5        | 5.3.1  | Sampling Techniques in previous Fault Simulators                                      | 90                |

|   |            | 9.3.1  | before Tessent®DefectSim                                                              | 51                |

|   |            | 5.3.2  | Likelihood-Weighted Random Sampling (LWRS) .                                          | 51                |

|   |            | 5.3.3  | Additional Settings that Reduce the Defect Simula-                                    | <i>J</i> <b>•</b> |

|   |            | 9.9.9  | tion Time                                                                             | 54                |

|   |            | 5.3.4  | Defect Injection in Tessent®DefectSim                                                 | 55<br>55          |

|   | E 1        |        | usions                                                                                | 55<br>57          |

| 6 | 2.4        |        | OF SYMBIST APPLICATION TO THE SAR ADC IP                                              |                   |

| U | 6.1        |        | ker Self-Test                                                                         | 59<br>50          |

|   | 6.2        |        | ne Testing Using SymBIST                                                              | 59<br>50          |

|   | 0.2        | 6.2.1  | Test Stimulus                                                                         | 59<br>50          |

|   |            | 6.2.2  | Setting the Comparison Window for Desired Test                                        | 59                |

|   |            | 0.2.2  | <u>.</u>                                                                              | 61                |

|   |            | 622    | Coverage vs. Yield Loss Trade-off SymBIST Transient Simulations in Off-line Test Mode |                   |

|   |            | 6.2.3  |                                                                                       |                   |

|   | 6.2        | 6.2.4  | Defect Coverage Analysis                                                              | 64                |

|   | 6.3        |        | e Testing Using SymBIST                                                               | 67                |

|   |            | 6.3.1  | Test Stimulus                                                                         | 67                |

|   |            | 6.3.2  | Transient Error                                                                       | 67<br>68          |

|   | <i>c</i> . | 6.3.3  | Latent Defect                                                                         | 68                |

|   | 6.4        |        | Assisted Analog Fault Diagnosis                                                       | 68                |

|   |            | 0.4.1  | SymBIST and other Diagnosis Setups                                                    | 69                |

|   |     | 6.4.2 Diagnosis Results     |

|---|-----|-----------------------------|

|   | 6.5 | Conclusions                 |

| 7 | CON | CLUSIONS AND FUTURE WORK    |

|   | 7.1 | Conclusions                 |

|   | 7.2 | Contributions of the Thesis |

|   | 7.3 | Future Work                 |

#### II APPENDIX

### LIST OF FIGURES

| Figure 1.1  | IC lifetime                                                | 4   |

|-------------|------------------------------------------------------------|-----|

| Figure 2.1  | Example of a bandgap circuit (from [17]) with              |     |

|             | topology modifications                                     | 10  |

| Figure 3.1  | SymBIST principle                                          | 24  |

| Figure 3.2  | Invariance in FD circuit                                   | 25  |

| Figure 3.3  | Invariance in identical blocks                             | 26  |

| Figure 3.4  | Invariance with pseudo-duplication                         | 26  |

| Figure 3.5  | SymBIST strategy                                           | 27  |

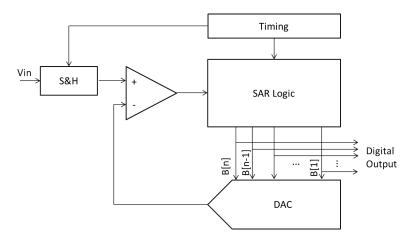

| Figure 4.1  | High-level architecture of a SAR ADC                       | 32  |

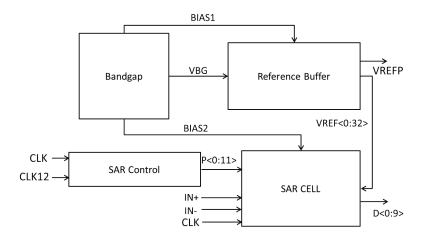

| Figure 4.2  | Top-level architecture of the SAR ADC IP                   | 33  |

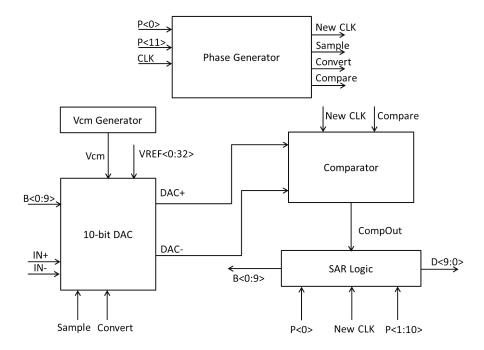

| Figure 4.3  | SARCELL block architecture                                 | 34  |

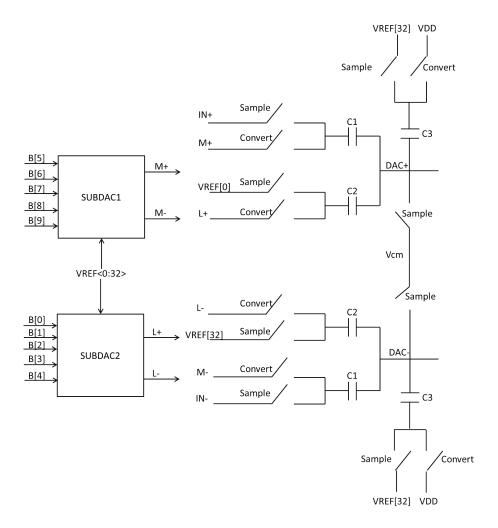

| Figure 4.4  | 10-bit DAC block architecture                              | 35  |

| Figure 4.5  | Comparator block architecture                              | 36  |

| Figure 4.6  | On-chip generation of dynamic test stimulus                | 40  |

| Figure 4.7  | Checker design for the invariances in Equations            |     |

|             | (4.3)-(4.4) and (4.6)-(4.8). The switches disconnect       |     |

|             | the checker when SymBIST is disabled or set the            |     |

|             | checker into self-test mode                                | 41  |

| Figure 4.8  | Checker design for the invariance in Equation (4.9).       | 42  |

| Figure 4.9  | Test access and control mechanism of SymBIST               |     |

| 0 , ,       | (adapted from [152])                                       | 45  |

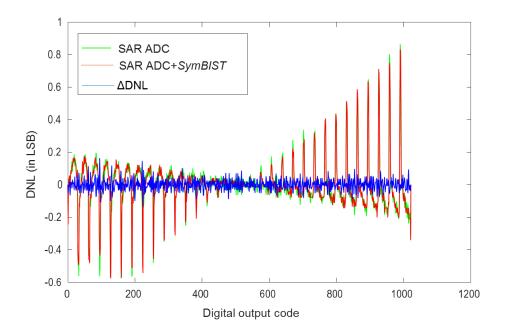

| Figure 4.10 | DNL of original design and original design with            | 10  |

| ,           | embedded <i>SymBIST</i>                                    | 46  |

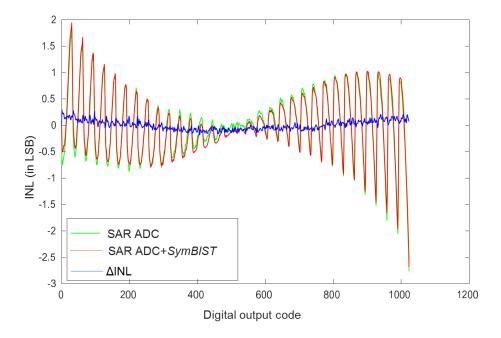

| Figure 4.11 | INL of original design and original design with            |     |

| ,           | embedded SymBIST                                           | 47  |

| Figure 5.1  | Defect Simulation Workflow                                 | 50  |

| Figure 5.2  | Defect model from [7]                                      | 51  |

| Figure 5.3  | Injection of defects 5.1 and 5.2                           | 57  |

| Figure 6.1  | Re-configuration for applying the test stimulus in         |     |

| O           | off-line test mode                                         | 60  |

| Figure 6.2  | L-W defect coverage as a function of tolerance             |     |

| O           | window placement                                           | 61  |

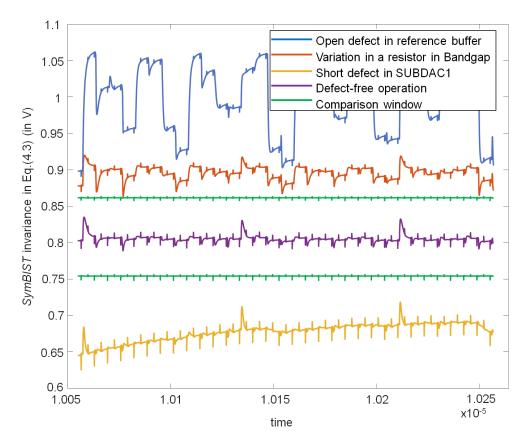

| Figure 6.3  | Transient simulation of <i>SymBIST</i> invariance in Equa- |     |

| 0 9         | tion (4.3) for different defect scenarios and blocks.      | 62  |

| Figure 6.4  | Transient simulation of <i>SymBIST</i> invariance in Equa- |     |

| 0 1         | tion (4.3) for different defect scenarios in SUBDAC1.      | 63  |

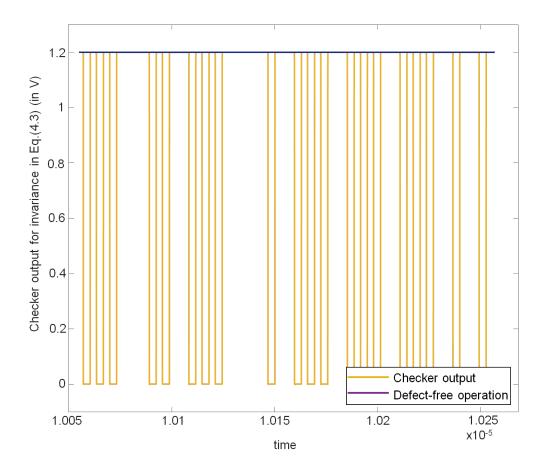

| Figure 6.5  | Checker output for the short defect simulation in          | - ) |

| 6           | SUBDAC1 shown in Figure 6.4                                | 64  |

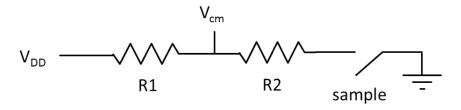

| Figure 6.6  | Schematic of $V_{cm}$ generator                            | 66  |

|             |                                                            | - 0 |

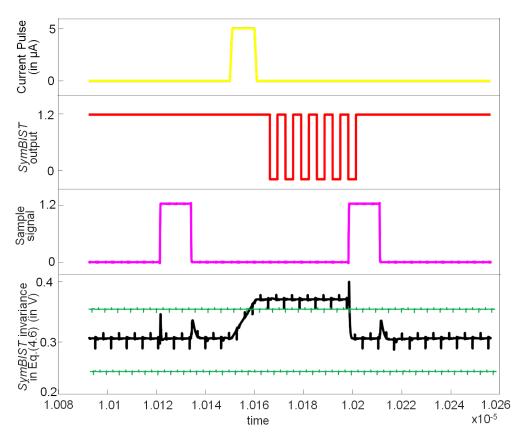

| Figure 6.7 SymBIST response to transient error injected in the DAC |                                                                                                           |       |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|--|--|--|

| Figure 6.8                                                         | SymBIST response to transient error injected in the                                                       | 68    |  |  |  |

| O                                                                  | bandgap                                                                                                   | 69    |  |  |  |

| Figure 6.9                                                         | SymBIST response to a latent defect                                                                       | 70    |  |  |  |

| Figure 6.10                                                        | Transient simulation of <i>SymBIST</i> invariance in Equa-                                                |       |  |  |  |

|                                                                    | tion 4.4 for $\pm 50\%$ variation defect in a resistor in                                                 |       |  |  |  |

|                                                                    | Bandgap, considering two different <i>SymBIST</i> setups.                                                 | $7^2$ |  |  |  |

| Figure 6.11                                                        | Transient simulation of <i>SymBIST</i> invariance in Equa-                                                |       |  |  |  |

|                                                                    | tion (4.4) for two short defects within the SUBDAC,                                                       |       |  |  |  |

| Eigene (                                                           | considering two different <i>SymBIST</i> setups                                                           | 73    |  |  |  |

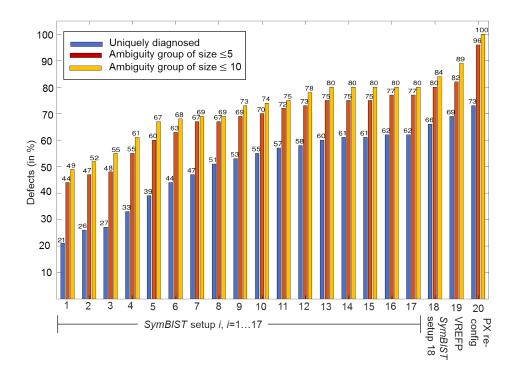

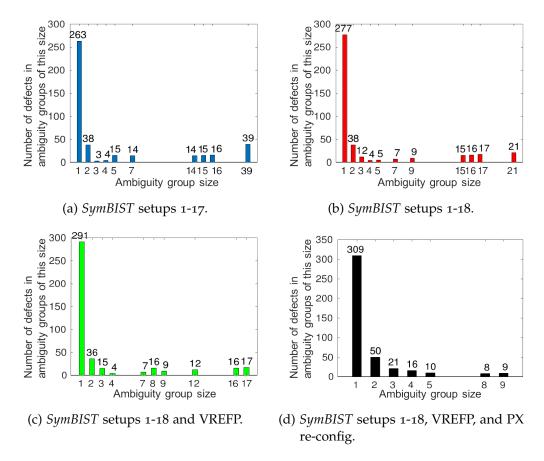

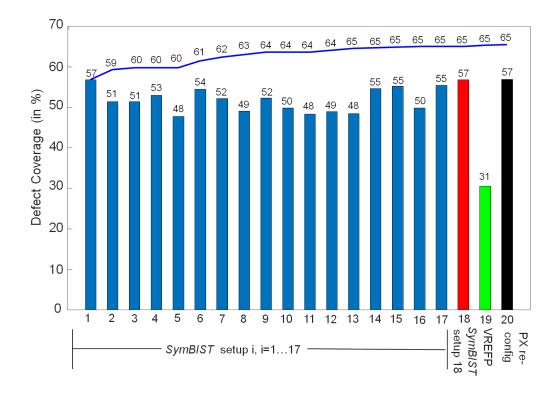

| Figure 6.12                                                        | ure 6.12 Percentage of defects uniquely diagnosed and in ambiguity groups of sizes $\leq 5$ and $\leq 10$ |       |  |  |  |

| Figure 6.13                                                        | Gradual diagnosis resolution improvement                                                                  | 74    |  |  |  |

| Figure 6.14                                                        | Absolute defect coverage per test setup and cumu-                                                         | 75    |  |  |  |

| 116010 0.14                                                        | lative absolute defect coverage                                                                           | 76    |  |  |  |

|                                                                    | A DI EC                                                                                                   |       |  |  |  |

| LIST OF TA                                                         | ABLES                                                                                                     |       |  |  |  |

| Table 4.1                                                          | Matrix showing correspondence between BIST ap-                                                            |       |  |  |  |

|                                                                    | proaches and SAR ADC IP blocks                                                                            | 39    |  |  |  |

| Table 6.1                                                          | L-W defect coverage results with the comparison                                                           |       |  |  |  |

|                                                                    | window set at $k = 5$                                                                                     | 65    |  |  |  |

| LISTINGS                                                           |                                                                                                           |       |  |  |  |

| Listing 5.1                                                        | Short circuit injection in a MOS transistor                                                               | 56    |  |  |  |

| Listing 5.2                                                        | Injection of a $+50\%$ variation in a resistor                                                            | 56    |  |  |  |

| LIST OF A                                                          | LGORITHMS                                                                                                 |       |  |  |  |

| Algorithm 1                                                        | Random Sampling of Defects from [1]                                                                       | 53    |  |  |  |

|                                                                    |                                                                                                           |       |  |  |  |

## ACRONYMS

| AC    | Alternating Current                                |

|-------|----------------------------------------------------|

| ADC   | Analog-to-Digital Converter                        |

| ANN   | Artificial Neural Network                          |

| ANR   | French National Research Agency                    |

| ATE   | Automated Test Equipment                           |

| ATPG  | Automatic Test Pattern Generation                  |

| A/D   | Analog-Digital                                     |

| A/M-S | Analog and Mixed-Signal                            |

| A     | Analog                                             |

| BER   | Bit Error Rate                                     |

| BIST  | Built-In Self Test                                 |

| CPU   | Central Processing Unit                            |

| CUT   | Circuit Under Test                                 |

| DAC   | Digital-to-Analog Converter                        |

| DC    | Direct Current                                     |

| DfT   | Design for Testing                                 |

| DNL   | Differential Non-Linearity                         |

| DPPM  | Defective Parts per Million                        |

| DSP   | Digital Signal Processor                           |

| DTMF  | Dual-Tone Multifrequency                           |

| D     | Digital                                            |

| EDA   | Electronic Design Automation                       |

| EDITS | oc Electrical Diagnosis for IoT SoCs in Automotive |

| ENOB  | Effective Number of Bits                           |

| EVM   | Error Vector Magnitude                             |

| FD    | Fully-Differential                                 |

| FFT   | Fast Fourier Transform                             |

| HCI   | Hot Carrier Injection                              |

| HD    | Hamming Distance                                   |

Integrated Circuit

IC

xvii

RF

Radio Frequency

#### xviii ACRONYMS

RL

Relative Likelihood

Root Mean Square **RMS RSN** Re-configurable Scan Network Successive Approximation Register **SAR** SC Switched-Capacitor Spurious-Free Dynamic Range **SFDR** Sample-and-Hold SH Segment Insertion Bit SIB SiP System-in-Package Scan In SI SNDR Signal-to-Noise-and-Distortion Ratio Signal-to-Noise Ratio **SNR** System-on-Chip SoC SO Scan Out SPICE Simulation Program with Integrated Circuit Emphasis Std. Standard ST Microelectronics STM SymBIST Symmetry-Based Built-In Self Test **TDC** Time-to-Digital Converter TDDB Time-Dependent Dielectric Breakdown **TDR** Test Data Register **Total Harmonic Distortion THD** USER-SMILE Ultrafast Stimulus Error Removal and Segmented Model **Identification of Linearity Errors** UTL **Upper Test Limit** Voltage Controlled Oscillator VCO **VLSI** Very Large-Scale Integration

# Part I MAIN PART

INTRODUCTION

#### 1.1 PROBLEM OUTLINE

Nowadays, electronic devices are widely used in almost every aspect of everyday life. These are products ranging from daily used devices, i.e., mobile phones and laptops, to more sophisticated and complicated automated equipment in health care, automotive, aeronautics and defense industry. The extensive use of these products has only been made possible with the advances in microelectronics.

Principal component of every electronic device is the IC, which is a device packing numerous electronic components like transistors, resistors and capacitors on one single chip. Modern systems include increasing numbers of ICs, i.e., the number of ICs in a typical automobile today exceeds 400 and continues to increase. Additionally, the trend nowadays is towards heterogeneous System-on-Chip (SoC) devices where different ICs, i.e., analog, digital processor, memory, etc., are integrated onto the same substrate. This reduces the system size and power consumption and also increases the speed of operation. The IC design complexity and number of ICs on a SoC are increasing rapidly and the technology limits are pushed to increase performance and market competitiveness.

Although the expected lifetime of the majority of the ICs is usually several years, ICs might fail due to various failure mechanisms. The main categories are the following: (a) defects induced during the several steps of the manufacturing process, i.e., dust particles, over/under etching etc.; (b) defects induced during packaging; (c) global process variations affecting complete regions of a wafer; (d) local process variations causing component mismatch; (e) defects caused by component ageing, i.e., electromigration, Negative Bias Temperature Instability (NBTI), Hot Carrier Injection (HCI), Time-Dependent Dielectric Breakdown (TDDB). A detailed survey regarding the failure mechanisms of electronic components is given in [2] and in [3].

The numerous failure mechanisms generate the need for testing in order to have a robust IC. Moreover, it is also very important after a failure is detected to identify the mechanism that caused the IC to fail.

#### 1.1.1 The Need for Testing

The process from the initial conception of an IC design until the actual use of it in an application is lengthy and consists of the high-level stages, as

#### 4 INTRODUCTION

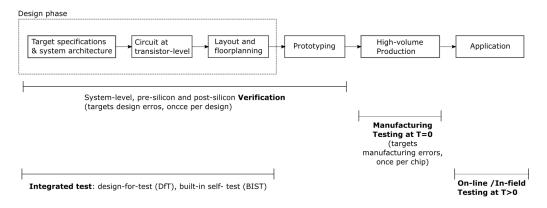

Figure 1.1: IC lifetime

illustrated in Figure 1.1. Testing is undertaken on an IC at different points in time from design concept through to full fabrication until the actual use in the application. Design phase starts with system architecture, circuit design at transistor level and layout design. Once this design phase is over and the chip is prototyped, it needs to pass the first type of test which is the system-level, pre- and post- silicon verification. The verification targets at design errors and runs once per design. If the design passes the verification, then a high-volume production of chips follows. At this stage, manufacturing tests are designed to ensure that every part of an IC is functional and that each chip meets the datasheet requirements and can be used adequately in real applications. Unlike verification which is performed once per design, testing is performed for every fabricated chip. Thus, it is crucial to minimize test application time and cost while guaranteeing the quality of passing chips. If an IC fails to pass any of the post-manufacturing tests, then it will be discarded. But even if a chip passes successfully the post-manufacturing test phase and meets all specifications at time zero, it can fail during the application, for example due to aging and environmental stress. Thus, especially for critical applications, there is a need for on-line testing in order to guarantee safety. On-line test means that the chip tests itself without depending on external test equipment. It can take place in idle times or concurrently with the operation as long as it is non-intrusive. Although the on-line testing only occurs in the latest stage, an integrated test needs to be considered already from the design phase. The integrated test consists of Design for Testing (DfT) and BIST approaches which need to be co-designed with the initial design.

#### 1.1.2 The Need for Diagnosis

The next step after detecting a failure in an IC is actually to diagnose it. Fault diagnosis refers to the analysis performed to identify the root cause of failure that occurred in an IC either during manufacturing or in the

field during normal operation following a customer return. The output is the isolation of the defect responsible for the failure and its localization at transistor-level.

Diagnosis is a crucial step in a product life-cycle. It can reveal important statistics, such as defect distribution and yield detractors. In this way, it provides valuable feedback for improving the design to prevent failure re-occurrence and expand the safety features, and also for evaluating and improving the quality of post-manufacturing tests.

In a first step, diagnosis generates a set of candidate defects based on diagnostic measurements or observed syndromes. In a second step, the IC is physically examined, for example using a thermal camera, to highlight anomalies in the operation and narrow down further the set of candidate defects. In the third and last step, the IC is submitted to Physical Failure Analysis (PFA) where de-layering and cross-sectioning of the die is performed to confirm the defect using imaging. Since PFA is destructive and irreversible, ideally the first step should pinpoint the actual defect. However, very often the first step results in an ambiguity group of candidate defects. According to industrial experience, its size should be less than 5-10 candidate defects to increase the PFA success rate.

Diagnosis metrics include: (a) resolution, i.e., the size of the ambiguity group; (b) accuracy, i.e., whether a reported candidate corresponds to the actual defect; and (c) diagnosis cycle time, i.e., the time required to complete the diagnosis since the number of diagnoses performed per week per design can be in the order of thousands [4].

#### 1.2 FUNCTIONAL SAFETY AS A REQUIREMENT IN MODERN APPLI-CATIONS

The number of ICs used in safety- and mission-critical applications, i.e., automotive, smart health-care, defense, critical infrastructure, etc., is ever increasing. This requires that ICs should be robust and defect-tolerant to meet the functional safety criteria. This implies that more ICs should be equipped with functional safety mechanisms. Moreover, modern systems include increasing numbers of ICs, i.e., the number of ICs in a typical automobile today exceeds 400 and continues to increase. This implies that the quality of individual ICs must increase to prevent decrease in the system's functional safety. The quality of the IC is measured by Defective Parts per Million (DPPM) and more specifically, it is desired that failure rate is in the order of sub-parts per million (ppm) [5].

Functional safety refers to the requirements to: (a) avoid IC malfunctions in the field by following robust design guidelines; (b) perform comprehensive post-manufacturing testing with proven high defect coverage and effective outlier screening; (c) detect reliability hazards in the

field before failures occur; (d) prevent failures in the field that could be detrimental; (e) detect failures in the field when they occur; (f) adding automatic protection to control failures when they occur in the field and recovering from them at an acceptable time span using fault-tolerance, self-repair, or self-healing principles; (g) ensure correct and uninterrupted operation in response to all inputs even under non-intended use or sometimes even misuse. Functional safety is regulated by standards depending on the application domain, e.g. International Organization for Standardization (ISO) 26262 for automotive and and International Electrotechnical Commission (IEC) 61508 for industrial systems.

#### 1.3 BIST TOWARDS FUNCTIONAL SAFETY

The purpose of BIST is to migrate part of the functionality of the Automated Test Equipment (ATE) onto the chip with the aim to facilitate test and reduce test cost. At an abstract level, BIST consists of (a) embedded test instruments, whose role is to generate test stimuli, perform measurement acquisition, and process measurements for building a comprehensive test response, and (b) a mechanism for accessing and controlling these test instruments from external pins. BIST can be defect-oriented, targeting detection of structural defects, or functional, in which case it targets measuring performances that are promised in the datasheet of the IC.

BIST is traditionally used for post-manufacturing testing, but it has also found application for silicon debugging, for guiding on-chip calibration, for facilitating fault diagnosis, and for on-line test where the status of the IC is checked in the field concurrently with the application or in idle times.

Functional safety has emerged as a new major application domain for BIST. In this context, BIST can help gaining better insight into the IC and improving defect coverage. In fact, many case studies have shown that the standard specification tests performed on an ATE offer no guarantee to meet the quality requirement [6]. A defect is always considered a potential threat and reliability hazard. An IC with a detected defect should be preferably discarded for safety reasons [5], [7], [8]. Even if from a functional viewpoint the performance complies with the specifications promised in the datasheet during post-manufacturing test time, i.e., time zero of the application, a defect may manifest itself later in the field of application referred to as a latent defect [9]. To this end, performing defect-oriented BIST on top of the standard specification tests and proving high defect coverage can address safety concerns. Thus, defect-oriented BIST is no longer expected to replace standard specification tests, which was the use case the community was hoping for in the early days, but it aims at enhancing confidence in ICs passing the test. The premise of BIST in this context is that it can detect defects that are reliability hazards, will manifest themselves later in the field, or will be triggered in the context of system operation in the field, provoked by environmental stress, for example heat, humidity or vibration. In the same context, a BIST that can be performed on-line in the field concurrently with the application or in idle times can help detecting reliability hazards and failures at the time of occurrence [10]. It is also a key block in feedback loops that enable fault-tolerance, self-repair, or self-healing. Finally, it can facilitate fault diagnosis to understand the root-causes of errors towards improving the design and manufacturing processes [11].

It should be mentioned that there are additional approaches towards meeting quality requirements before deployment in the field, i.e., burn-in stress [12] and outlier screening [13]–[15].

Embedding BIST into A/M-S ICs is a complex task presenting several challenges. In particular: (a) the BIST circuitry should be transparent to the IC without degrading its performance and without requiring significant re-configuration or re-design; (b) the BIST circuitry should incur low and justifiable area overhead; (c) for defect-oriented BIST the simulation should be fast for enabling large-scale defect simulation in reasonable time and for allowing to perform defect simulation multiple times for several refined BIST versions and for comparing with other BIST approaches; (d) for on-line BIST real-time response should be fast for enabling lowlatency error detection; (e) the BIST ideally should be flexible and reusable for different IC classes and different architectures within each IC class; (f) the BIST principle ideally should have proven quality before moving to high-volume production; (g) the BIST circuitry should be more robust than the IC having low failure probability, which typically implies that ideally the BIST wrapper should be fully digital; (h) the BIST ideally should be portable from one technology node to another without requiring significant re-design; and (i) the BIST instruments ideally should be interfaced to standard digital test access mechanisms.

#### 1.4 THESIS CONTRIBUTION

In this thesis, a novel BIST paradigm for A/M-S ICs, called *SymBIST* is proposed. *SymBIST* exploits inherent symmetries in an A/M-S IC to construct signals that are invariant by default, and subsequently checks those signals against a tolerance window. Violation of invariant properties points to the occurrence of a defect or abnormal operation. *SymBIST* is designed to serve as a functional safety mechanism. It is reusable ranging from post-manufacturing test, where it targets defect detection, to on-line test in the field of operation, where it targets low-latency detection of transient failures and degradation due to aging. We demonstrate *SymBIST* on real SAR ADC IP by ST Microelectronics (STM). *SymBIST* has the following appealing attributes:

- 1. It offers high defect coverage.

- 2. It offers a fast test cycle, which is a key for making the defect simulation tractable.

- 3. It incurs low area overhead.

- 4. It achieves zero performance penalty.

- 5. It has a fully digital interface making it compatible with modern 2-pin test access and control mechanisms, e.g. Institute of Electrical and Electronics Engineers (IEEE) 1687.

*SymBIST*, originally proposed for defect-oriented post-manufacturing test and on-line test, can also be seamlessly reused for the purpose of diagnosis. Fault diagnosis methodologies for analog circuits lag far behind those for their digital counterparts. BIST can offer better insights into the circuit and, thereby, can assist diagnosis towards resolving ambiguity groups. Using *SymBIST* for diagnosis we demonstrate:

- 1. High diagnosis resolution, i.e., a high percentage of uniquely diagnosed defects and ambiguity groups of small size.

- 2. Fast diagnosis cycle in the order of  $\mu$ s.

#### 1.5 THESIS STRUCTURE

The thesis is structured as follows. In Chapter 2, we provide a review of previous work (a) on A/M-S BIST with a focus on ADCs and (b) on diagnosis approaches for A/M-S ICs. In Chapter 3, we present the SymBIST concept. In Chapter 4, we present the SAR ADC case study, that is used for demonstrating SymBIST. In Chapter 5, we discuss the defect simulation framework, including the defect modeling approach and the mixed-signal defect simulator used to accelerate and automate defect simulations. In Chapter 6, we present the results of applying SymBIST for off-line defetoriented post-manufacturing test, on-line test and fault diagnosis. Chapter 7 concludes this thesis and discusses future work and perspectives.

# PRIOR ART ON ANALOG HARDWARE TESTING AND DIAGNOSIS

#### 2.1 PRIOR ART ON ANALOG BIST

There is a large body of literature on A/M-S BIST. In general, A/M-S BIST is proposed for mainly three uses, namely: (a) defect-oriented test; (b) direct on-chip measurement of performances, e.g. functional test; and (c) on-line test, either concurrently with the operation or in idle times. Additional uses include calibration for yield boosting and fault diagnosis. For any of these uses, BIST is in general specific to the circuit class and very often specific to different architectures within a given circuit class. Furthermore, BIST is in general designed and/or demonstrated for one use only.

#### 2.1.1 Generic Defect-Oriented BIST

For defect-oriented test, generic BIST proposals include topology modification by inserting Pull-Up (PU) or Pull-Down (PD) transistors and oscillation-based test.

#### 2.1.1.1 Topology Modification BIST

Topology modification BIST originally proposed in [16] is enabled by the addition of PD and PU transistors. A PD transistor connects a circuit node to ground, while a PU transistor connects a circuit node to the power supply. PD and PU transistors are activated by applying a logic 1 and 0 at their gates, respectively. In general, given a Circuit Under Test (CUT) with M nodes, in each node a PD and/or a PU transistor can be added. Therefore, the total number of possible PU and PD transistors in a CUT is  $2^{M}$ . If N PU and PD transistors are added in total, where N  $\leq 2^{M}$ , then the circuit can be configured into  $2^{N}$  topologies, including the original one when all PD and PU transistors are deactivated. The underlying principle is that by these re-configurations we are able to expose the presence of additional defects that are undetectable in the original topology.

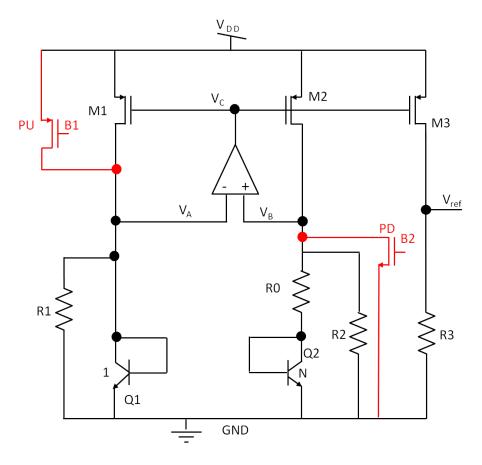

Figure 2.1 illustrates an example of topology modifications in a bandgap circuit. In this case, a PU transistor controlled by signal B1 brings the node  $V_A$  to VDD and a PD transistor controlled by signal B2 brings the node  $V_B$  to ground.

Figure 2.1: Example of a bandgap circuit (from [17]) with topology modifications.

#### 2.1.1.2 Oscillation BIST

Oscillation-Based BIST (OBIST) has been widely used for testing different classes of ICs, i.e., filters [18]–[26], ADCs [27]–[29], Radio Frequency (RF) circuits [30] and Micro-Electro-Mechanical Systems (MEMSs) [31]. The underlying idea of OBIST is to apply feedback loops inside the CUT and convert it to multiple oscillators, where an oscillator is an electronic circuit that produces a sinusoidal or pulse wave signal without any input stimulus other than the Direct Current (DC) supply. The oscillation frequency and magnitude of a block configured into an oscillator depends on its components' parameters. Any deviation of the oscillation frequency or magnitude away from the nominal expected values points to defect detection. In [32], an algorithm to estimate the limits of the test metrics is described in order to achieve the desired test coverage versus yield loss trade-off.

As a few examples, in [22], a Switched-Capacitor (SC) biquadratic filter is considered as a case study and a non-linear feedback is applied to convert the filter into an oscillator. In [28], OBIST is shown for a  $\Sigma\Delta$  ADC, where two oscillation frequencies are extracted and used together

with the output of a functional test to distinguish the defect-free circuits from the defective ones. In [33] the required re-configurations applied to the analog subsystem of a Dual-Tone Multifrequency (DTMF) receiver to implement OBIST are described.

Overall, oscillator-based test has been a very popular test mechanism showing numerous advantages: (a) it is applicable to a large number of IC classes, (b) there is no requirement for an external test stimulus since the CUT is used in a feedback loop, (c) digital test signatures can be extracted off-chip from processing the oscillation frequency and magnitude, (d) test parameters can be extracted as an average over several periods to minimize the noise impact, (e) it is very efficient for catastrophic and parametric faults [34].

#### 2.1.2 ADC BIST

The majority of the BIST techniques for ADCs that have been published up to date are functional. The main reason is that a single simulation of the ADC already requires a very long time in the order of hours, thus defect simulation time is prohibitive to be able to demonstrate defect-oriented BIST.

ADCs are characterized by dynamic specifications, such as (a) Signal-to-Noise Ratio (SNR), (b) Signal-to-Noise-and-Distortion Ratio (SNDR), (c) Total Harmonic Distortion (THD), (d) Effective Number of Bits (ENOB), (e) Spurious-Free Dynamic Range (SFDR), etc. and static specifications such as (a) Differential Non-Linearity (DNL), (b) Integral Non-Linearity (INL), (c) offset (d) gain, etc.

#### 2.1.2.1 ADC BIST Measuring Dynamic Specifications

The standard approach to measure the dynamic specifications of an ADC consists of applying a high-resolution sinusoidal at the input and computing the Fast Fourier Transform (FFT) at the output.

However, there is a requirement for the resolution of the sinusoidal input, which typically needs to be at least two bits higher than the effective resolution of the ADC. This poses a great design challenge for BIST implementation and several methods have been proposed to overcome this challenge.

A classical approach for generating on-chip an analog sinusoidal is to employ a closed-loop oscillator that involves a highly selective bandpass filter and a comparator [35]. To improve the resolution of the sinusoidal generators they can be combined with harmonic cancellation techniques [36]–[38]. In [36], a technique is proposed to suppress the low-frequency harmonics with a digital harmonic cancellation block and the high-frequency ones with a passive filter. In [37], a method is de-

scribed to compute the weights for summing the outputs of a Phase Shift Oscillator (PSO) to cancel the harmonics. In [38], numerous harmonic cancellation approaches are presented with the aim to simplify the on-chip implementation of the scaling weights.

Another classical approach is to employ an open-loop oscillator. The starting point is to use an ideal  $\Sigma\Delta$  modulator in software that converts a high-resolution sinusoidal to a bit stream which, thereafter, is loaded and periodically reproduced in an on-chip circular shift register [39]. The bit stream can be converted on-chip to a high-resolution sinusoidal by passing it through a 1-bit Digital-to-Analog Converter (DAC) followed by a low-pass filter to remove the quantization noise. Interestingly, in the case of SC  $\Sigma\Delta$  ADCs, the bit stream can be fed directly into the modulator by adding simple circuitry at its input [40]–[43].

Another challenge of an ADC BIST approach is the analysis of the test response since performing FFT on-chip incurs a high area overhead [44]. If the FFT cannot be performed in the Digital Signal Processor (DSP), then in the case of a full BIST implementation, the FFT algorithm needs to be replaced with an alternative less computationally-intensive algorithm, such as the sine-wave fitting algorithm [45].

#### 2.1.2.2 ADC BIST Measuring Static Specifications

The standard approach to measure the static specifications of an ADC is to apply a ramp at the input and obtain the histogram of the number of occurrences of each code at the output.

Again, the first challenge concerns the on-chip test stimulus generation. Adaptive ramp generators can be employed, as proposed in [46], [47], or, alternatively, an exponential waveform can be used [48]. Another approach is based upon first identifying and computationally removing the source non-linearity, and then, accurately estimating the ADC static performances [49].

Regarding the test response analysis, it is required to store both the experimental and the reference histograms and use the DSP to perform the comparison. An efficient BIST implementation of the histogram analysis is proposed in [50]. For ADCs having a repetitive structure, such as pipeline, cyclic, and successive approximation ADCs, what is broadly known as reduced code testing can be applied [51]–[55]. Only a few codes need to be judiciously targeted and from this information the complete histogram can be extrapolated. For such ADCs that present an INL curve that is somewhat periodic and can be segmented, the Ultrafast Stimulus Error Removal and Segmented Model Identification of Linearity Errors (USER-SMILE) algorithm can be applied [56]. This algorithm relaxes the test stimulus linearity requirement by employing two non-linear input signals and, thereafter, it uses some post-processing to remove the

test stimulus error and recover accurate static test accuracy by orders of magnitude faster than the standard histogram method.

#### 2.1.2.3 Other ADC BIST Approaches

Instead of targeting a BIST approach aiming at measuring directly the dynamic and static specifications of the ADC, it is also possible to consider a BIST approach where the aim is to obtain measurements that reveal important design parameters, such as the poles and settling errors of the integrators in the case of  $\Sigma\Delta$  ADCs [57]. An approach proposed also specifically for pipeline ADCs is to reconfigure consecutive pipeline stages to form  $\Sigma\Delta$  modulators and then test instead the  $\Sigma\Delta$  modulators through digital means [58].

#### 2.1.3 *RF BIST*

For RF transceivers, a common BIST technique consists in creating a loop-back connection between the transmitter and the receiver, in order to test the whole RF transceiver. The Power Amplifier (PA) output of the transmitter is connected to the Low Noise Amplifier (LNA) input of the receiver using an attenuator and a switch. Next, digitally modulated baseband signals are transmitted and the baseband response signals are used to evaluate the response, i.e., measure the Error Vector Magnitude (EVM), extract parameters from the response, etc. [59]–[66].

Sensor-based testing is another common BIST technique, which can be employed inside the blocks of RF transceivers.

A type of sensor that is commonly used to implement BIST is the current sensor [67]–[69]. The parasitic resistor of the line provides a voltage drop which unbalances the CUT. The output current is proportional to the RF power supply current of the CUT and the output current is switched to the input of an envelope detector to obtain a DC signature, which nevertheless carries information about the RF amplitude of the power supply current.

A second way to extract DC signatures is through envelope (a.k.a. amplitude or power detectors) detectors that transfer directly information about the RF amplitude by monitoring current or voltage of internal nodes [70]–[75].

There exist also non-intrusive sensors, i.e., process variation-aware sensors [68], [76], [77] and temperature sensors [78]–[81], that can extract information without being electrically connected to the CUT. The process variation-aware sensors monitor the process variations which are correlated to the performances of the CUT. Thereafter, the performances of the CUT can be predicted from the sensor measurements using the alternate test paradigm [82]–[92]. However, defect detection is not feasible with

variation-aware sensors since they are not electrically connected to the CUT. To overcome this problem, temperature sensors can be also used to provide defect detection by monitoring the temperature of the CUT [93]. When the CUT is powered-on, it is self-heated due to the power dissipation and the heat is diffused in the substrate creating a temperature profile in the vicinity of the CUT. In the presence of a defect, the power dissipation will alter, resulting in a shift of the temperature profile. A temperature sensor captures the temperature shift and indicates the presence of the defect.

#### 2.1.4 PLL BIST

A Phase-Locked Loop (PLL) is a fundamental building block used to synthesize clocks for data synchronization and to provide the frequency sources for up-conversion and down-conversion in RF transceivers. For PLLs, BIST techniques exist for measuring the performances, i.e., jitter, loop gain, lock time, etc., and for facilitating defect-oriented tests.

#### 2.1.4.1 PLL BIST Measuring Performances

A key performance parameter of a PLL is the high-frequency jitter. Jitter must be low to guarantee data synchronization and low Bit Error Rate (BER) in communication systems. There are a few ways to define the PLL's jitter [94]: (a) timing jitter, defined as difference between the edge timing and the ideal edge timing, (b) period jitter, defined as the difference between each period and the average period, and (c) cycle-to-cycle jitter, defined as the difference between the period and the preceding period. Measuring jitter off-chip is difficult and costly since high speed sampling oscilloscopes are very costly and the measurement requires long test times. Moreover, the signal gets further polluted when it is extracted off-chip due to pad, probing, and coupling parasitics. Therefore, there is a need for designing a BIST to measure jitter on-chip.

There is a large body of literature describing on-chip jitter measurement [94]–[100]. For example in [100], a jitter measurement technique is proposed, where the PLL's response is undersampled and the count of unstable bits at the clock rising edges is correlated to the high-frequency jitter. Instead of measuring the jitter it is also possible to estimate the transfer function of the jitter [101], [102].

Finally, there have been several approaches for measuring other PLL parameters such as the Voltage Controlled Oscillator (VCO) gain, lock time, etc. [95], [103]–[105]. In [95], logic gates are used to develop a BIST mechanism to measure the lock range, lock time, loop gain, as well as the Root Mean Square (RMS) jitter.

#### 2.1.4.2 Defect-Oriented PLL BIST

Defect-oriented BIST approaches for PLLs have been proposed in [106]–[108]. In [108], a Pseudo-Random Bit Sequence (PRBS)-based test is proposed, where a digital PRBS is injected in the charge pump perturbing the PLL, and the cross-correlation of the PRBS pattern with the output of the phase/frequency detector is considered for defect detection. The major challenge of this technique is to select the most suitable injection and observation points in the loop, so as to detect defects in the whole bandwidth.

#### 2.1.5 On-line Test

BIST can also be used to perform on-line test in the field either concurrently with the application or in idle times. In the concurrent test mode, no re-configurations are allowed in the CUT and its inputs are defined by the application that it is used. On the contrary, in on-line test mode during idle times, it is possible to perform non-intrusive re-configurations in the CUT and apply a desired test stimulus, however all these actions need to be performed by the BIST itself.

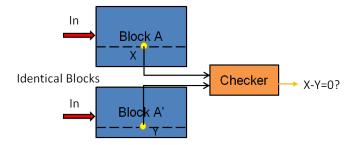

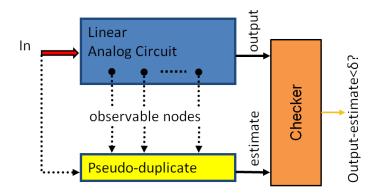

For on-line test, generic BIST includes duplication or triple modular redundancy, but these approaches are very costly. Cost-effective BIST for on-line test has been proposed only for linear time-invariant circuits, i.e., filters, using pseudo-duplication concepts [109]–[111] and for Fully-Differential (FD) circuit implementations [112]–[114]. Regarding linear time-invariant circuits, in [109], a strategy is proposed for switched-capacitor filters where a programmable biquad that can mimic every filter stage is configured to monitor successively the filter stages. In [110], the matrices of the state-variable equations are encoded into a continuous checksum which is implemented by small extra hardware. In [111], it is shown how to generate with small extra hardware an estimator that monitors some observable nodes of the circuit and, once fully connected to the circuit, produces an output that converges exponentially fast to the output of the circuit and follows the output for any input change.

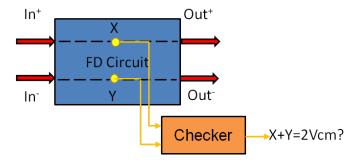

For FD circuits, node pairs carrying FD signals should satisfy the following property:

$$V_1 + V_2 = 2V_{\rm CM} \tag{2.1}$$

where  $V_1$ ,  $V_2$  are the node voltages and  $V_{\rm CM}$  is the common-mode voltage. An on-line test approach can be built based on monitoring that this property always holds. Any deviation of the sum from the common-mode voltage points to erroneous operation. In practice the sum is expected to stay within a tolerance window due to noise and voltage and temperature variations.

Analog comparators or checkers that compare duplicate or FD signals with adaptive tolerance windows are proposed in [113], [114].

#### 2.1.6 BIST Evaluation

Any functional BIST approach should be evaluated in terms of parametric test metrics, i.e., resultant test escapes and yield loss, before moving to high-volume production. Ideally, the evaluation should take place at simulation level so as to provide early feedback towards refining the BIST and making a decision whether to pursue the BIST or summarily reject it. The challenge is that analog simulations are time-consuming. In fact, test escape and yield loss events have low-probability and a Monte Carlo (MC) analysis with a reasonable number of runs will produce very few such events, if any at all, so as to be able to compute test metrics that have statistical significance. Analog test metric estimation algorithms for assessing functional BIST techniques have been proposed based on parametric density estimation [115], Copulas theory [116], and statistical blockade and extreme value theory [117]-[119]. In [120], a practical simulation flow for evaluating test metrics for ADCs and, in general, for circuits with long simulation times, is proposed based on statistical behavioral modeling and fast behavioral-level MC using the statistical blockade technique.

#### 2.1.7 BIST for Calibration

Calibration schemes are oftentimes utilized in A/M-S and RF ICs with the aim to boost yield, i.e., by compensating against process variations and non-idealities.

At a minimum, a calibration scheme utilizes digitally controlled tuning knobs that act on the circuit performances. Tuning knobs may include bias voltages, current sources, or single tunable components, such as resistors, capacitors, and varactors.

The standard calibration algorithm consists in multiple testing/tuning iterations where in each step the performances are measured and the next best tuning knob setting is decided based on some optimization algorithm.

The calibration scheme may also utilize BIST for performance measurement which can speed-up the test cycle and alleviate the dependence on complex ATE. For example, one-shot calibration schemes based on process-variation-aware sensors and machine learning are proposed in [121], [122].

The most advance calibration schemes are fully implemented on-chip rendering the circuit self-healing. These schemes can be also used during the lifetime of the circuit to compensate against aging. They comprise tuning knobs or actuators, sensors for extracting information-rich measurements or directly the performances, and a digital processor engine that maps the outputs of the sensors to tuning knob values and aims at driving the optimization so as to identify a good balance among multiple competing performance goals [123]–[125].

#### 2.2 PRIOR ART IN ANALOG FAULT DIAGNOSIS

While for digital ICs there exist several in-house frameworks and commercial diagnosis Electronic Design Automation (EDA) tools [4], [126]–[130], for analog ICs there is neither a commercial tool nor a standardized diagnosis approach. Analog fault diagnosis is still a manual, tedious, and time-consuming process very often resulting in large ambiguity groups and no actionable diagnosis information. In fact, there is a vast literature on analog fault diagnosis, yet none of the proposed solutions has matured enough to meet industry standards.

#### 2.2.1 Rule-Based Diagnosis

The traditional approach is a rule-based system which takes the form "IF symptom(s) THEN fault(s)". In this approach, rules are developed to match the symptoms of an IC to an actual fault.

In [131], assembly faults in RF circuits embedded in System-in-Package (SiP) are diagnosed. These SiP assembly faults are:

- 1. Power supply faults.

- 2. Bias network faults.

- 3. RF load component faults.

- 4. Signal path faults.

The symptoms used to diagnose the above mentioned faults are: (a) DC measurements, (b) current consumption, and (c) noise power. In general, it is difficult to acquire the knowledge to build a rule-based system for diagnosis.

#### 2.2.2 Model-Based Diagnosis

Model-based diagnosis approaches have also been studied extensively. The idea is to first build a model linking diagnostic measurements to circuit parameters. Then, given the diagnostic measurements from the real failing device, the model is used to identify the faulty circuit parameter, as well as its deviation from the nominal value. The model can be

constructed using nonlinear circuit equations [132], sensitivity analysis [133], [134], regression [135], [136], or behavioral modeling [137], [138].

In [132], fault diagnosis using frequency measurements for linear systems is proposed. However, even for a linear system described by a set of linear equations

$$\mathfrak{m} = \mathfrak{f}(\mathfrak{p}) \tag{2.2}$$

the corresponding diagnosis equations

$$p = f^{-1}(m) \tag{2.3}$$

are non-linear.

In [133] and [134], the sensitivity matrix S is used to build the diagnosis equations. The sensitivity matrix is defined as the relation between the vector of the normalized output measurement deviations , denoted by  $\frac{\Delta M}{M}$ , and the vector of the normalized component deviations , denoted by  $\frac{\Delta P}{P}$ :

$$S \cdot \frac{\Delta P}{P} = \frac{\Delta M}{M} \tag{2.4}$$

Assuming that we have N output measurements and K components, the elements that construct the sensitivity matrix are given by:

$$s_{P_{j}}^{M_{i}} = \frac{\frac{\Delta M_{i}}{M_{i}}}{\frac{\Delta P_{j}}{P_{j}}}, i = 1, ..., N, \text{ and } j = 1, ..., K$$

(2.5)

where  $s_{P_j}^{M_i}$  is the differential sensitivity of the output measurements  $M_i$  with respect to component  $P_i$  for a given input signal.

Diagnosis aims at extracting the component parameters, therefore we are interested in solving:

$$\frac{\Delta P}{P} = S^{-1} \cdot \frac{\Delta M}{M} \tag{2.6}$$

In [135] and [136], non-linear regression models are constructed for the purpose of diagnosis. Firstly, in the pre-diagnosis phase, regression models mapping diagnostic measurements to component parameters are trained using simulations. After the device has failed, the same diagnostic measurements are obtained from the CUT and given as an input to the regression model that predicts the components' deviation. Another model-based diagnosis approach found in literature aims at building a behavioral model of the IC [137], [138]. The underlying idea is that all possible faults are injected in the behavioral model until the test parameter of the model matches the one of the actual faulty chip. The fault injection stops when a match is found and the fault causing the failure is identified. More specifically, in [137] a mathematical model was constructed to estimate the behavior of a biquad filter, whereas in [138] a behavioral model of a second-order SC  $\Sigma\Delta$  ADC was designed, including the critical non-idealities, i.e., clock jitter, KT/C noise, and Operational Amplifier (op-amp) non-idealities .

The model-based diagnosis approach can be used for diagnosis of soft faults, i.e., deviations of circuit parameters; however, it is recognized that hard faults, i.e., defects such as short- and open-circuits, are the main root cause of IC failures [139]. Besides, it is challenging to construct a model that faithfully reproduces the analog IC behavior.

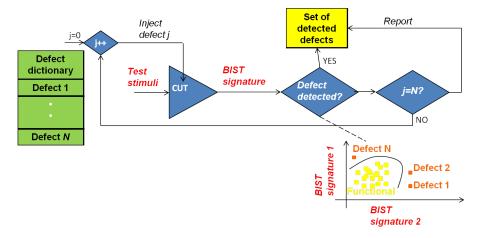

# 2.2.3 Fault Dictionary-Based Diagnosis

Perhaps the most common diagnosis approach is based on the use of a fault dictionary. Given a list of defects generated by Inductive Fault Analysis (IFA) [139], one defect is injected at a time in the netlist, and the IC is simulated to obtain the diagnostic measurement pattern. The fault dictionary contains the pairs of defects and diagnostic measurement patterns. Then, the diagnostic measurement pattern from the failed IC is mapped to one of the logged diagnostic measurement patterns of simulated defects based on some similarity metric. The mapping can be established after training a multi-class classifier using the fault dictionary dataset [11].

A growing body of literature has evaluated different combinations of (a) test stimuli, (b) measurement post-processing, (c) classifier types, as a way to resolve ambiguity groups [140]–[144].

In [140], the authors used white noise input as test stimulus and an Artificial Neural Network (ANN) classifier to diagnose faults. The white noise targets to excite all the transistors and scale the frequency response of the circuit. The training data of the ANN will contain diagnostic measurements from both faulty and fault-free circuit instances and multiple networks can be trained in order to improve the diagnosis results. During diagnosis these networks are used to localize the fault that has occurred.

In [141], an ANN classifier was proposed that uses wavelet decomposition as feature pre-processing. The features used by the ANN for the classification are generated after wavelet transformation is performed in the output of the CUT and the wavelet coefficients are then processed by Principal Component Analysis (PCA) for feature selection and are

normalized. Wavelet decomposition transforms time-varying signals into wave-like signals that oscillate, known as wavelets.

In [142], the proposed test stimulus is power supply ramping and the signatures used to train the ANN classifier are constructed by the power supply current response at different time stamps. In [143], a sinusoidal input test stimulus is used and FFT is performed in the output of the CUT. Then, the harmonics of the output are used as features and are classified using a two-stage Multilayer Perceptron (MLP) ANN.

Finally, there exist methods for selecting the minimal number of multifrequency test sets [145] and the optimum test points based on the entropy [144].

The challenge with the fault dictionary approach is the long fault simulation time. However, the recently proposed analog fault simulators [7], [8], [146] can help in speeding up the fault dictionary development, as demonstrated in [147].

## 2.2.4 Fault Diagnosis Using BIST

Traditionally, BIST aims at adding on-chip test structures to facilitate and reduce the cost of post-manufacturing test. BIST can offer better insights into the circuit and, thereby, can assist diagnosis towards resolving ambiguity groups. Despite this, in the literature there are few examples of using BIST in this field. In [148], BIST is used for diagnosis for the class of fully differential analog filters and in [149] an Automatic Test Pattern Generation (ATPG) algorithm is described for generating the sinusoiodal test stimulus.

#### 2.3 CONCLUSIONS

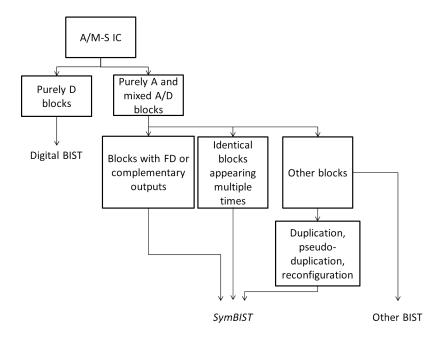

The main contributions of this thesis with respect to the state-of-the-art can be summarized as follows:

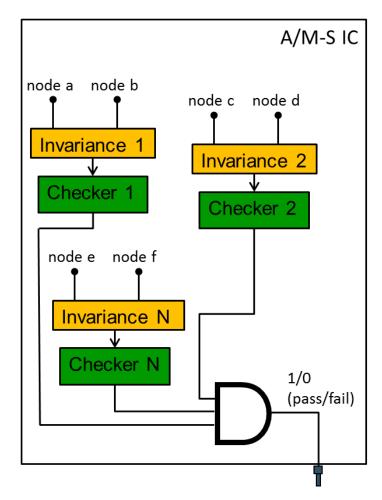

- 1. A new generic defect-oriented BIST approach is proposed, called *SymBIST*, virtually applicable to all A/M-S ICs. SymBIST relies on constructing or identifying existing invariances and checking whether those invariances are satisfied.

- 2. *SymBIST* is a reusable BIST approach for defect-oriented test, on-line test and diagnosis. These test-related tasks can be accomplished using the same *SymBIST* test infrastructure. The operation mode is set externally by the user and *SymBIST* generates internally the appropriate test stimulus and makes the necessary re-configurations depending on the operation mode.

- 3. *SymBIST* is the first BIST demonstrated for post-manufacturing defectoriented test of ADCs. This is thanks to the short test time of *SymBIST*, which allows performing large-scale defect simulation of the ADC in reasonable time.

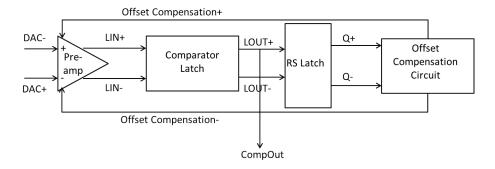

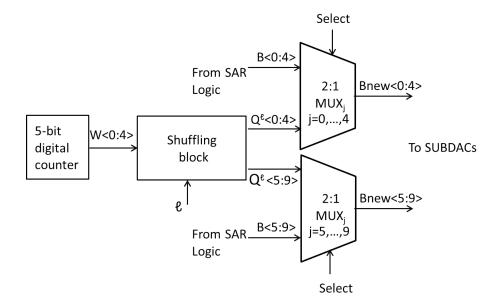

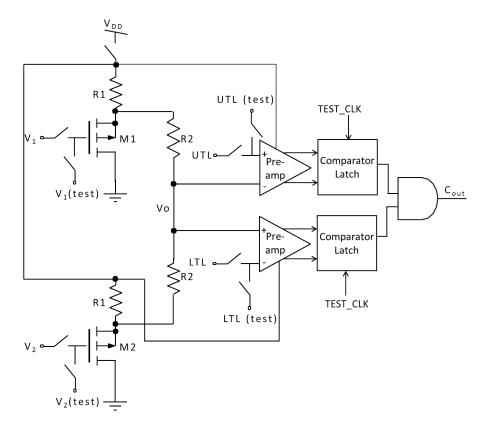

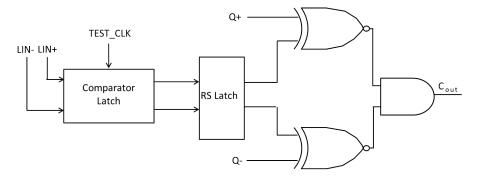

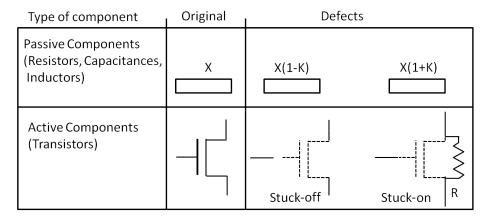

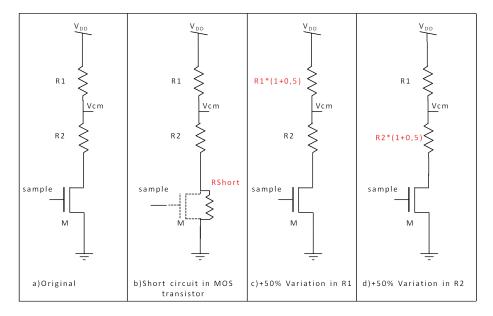

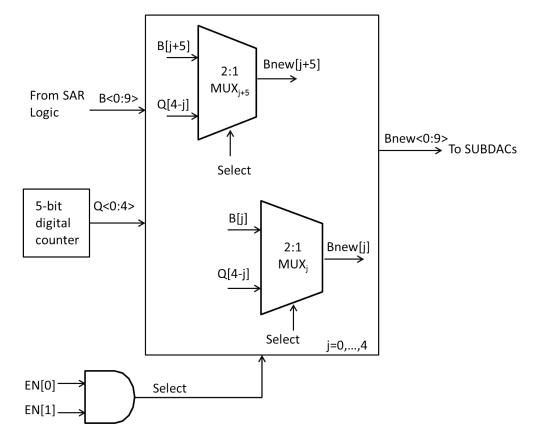

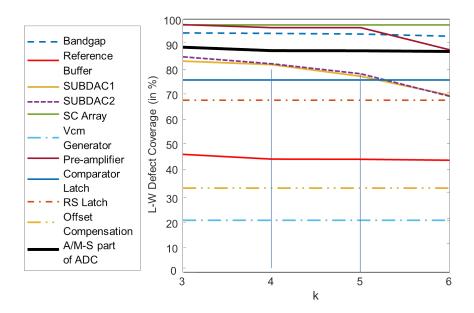

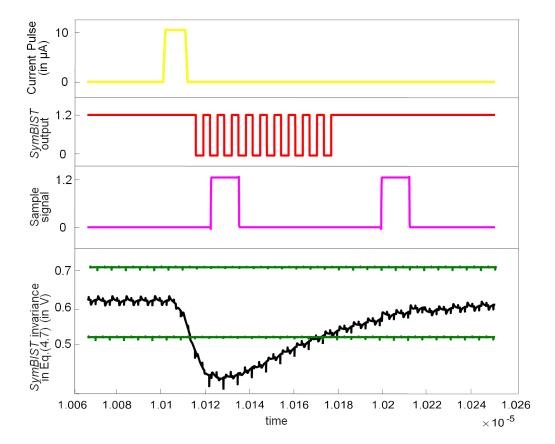

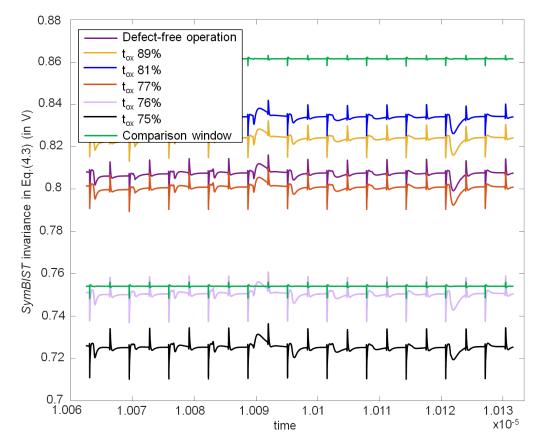

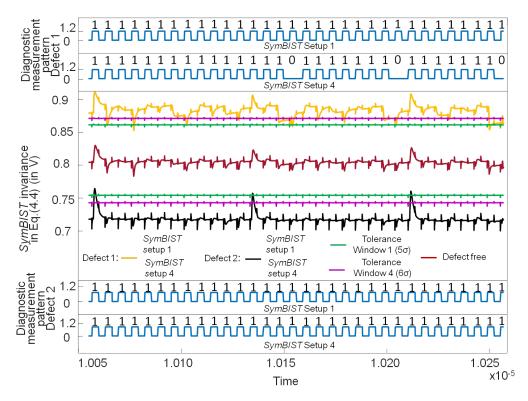

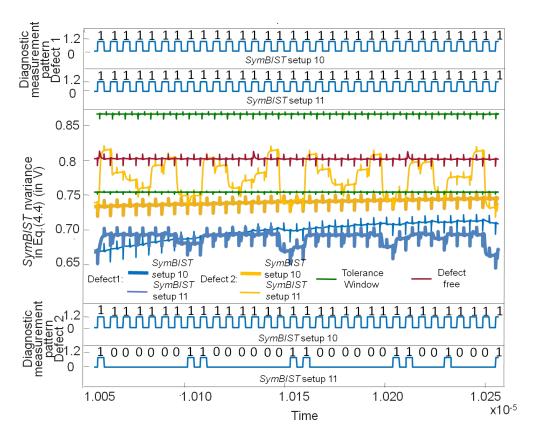

- 4. *SymBIST* is in addition the first BIST demonstrated for on-line test of ADCs. *SymBIST* checks the health status of the ADCs concurrently with its operation and independently of the input. This use is demonstrated for latent defects and single event upsets.