## Evaluation and consideration of security in multi-core management systems

Safouane Noubir

### ► To cite this version:

Safouane Noubir. Evaluation and consideration of security in multi-core management systems. Electronics. UNIVERSITE DE NANTES, 2021. English. NNT: . tel-03520419

## HAL Id: tel-03520419 https://hal.science/tel-03520419v1

Submitted on 11 Jan2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE NANTES

ÉCOLE DOCTORALE Nº 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Électronique - Génie Électrique

## Par Safouane NOUBIR

Evaluation and consideration of security in multi-core management systems

Thèse présentée et soutenue à l'Université de Nantes, le 17 décembre 2021 Unité de recherche : IETR UMR 6164

### **Rapporteurs avant soutenance :**

M. BOSSUET Lilian Professeur, Université Jean Monnet, Saint-Étienne Mme. ENCRENAZ Emmanuelle Maître De Conférences/ HDR, Sorbonne Université, Paris

### **Composition du Jury :**

| Président :           | M. GOGNIAT Guy           |

|-----------------------|--------------------------|

| Examinateurs :        | M. BOSSUET Lilian        |

|                       | Mme. ENCRENAZ Emmanuelle |

| Dir. de thèse :       | M. PILLEMENT Sébastien   |

| Encadrante de thèse : | Mme. MENDEZ REAL Maria   |

Professeur, Université Bretagne Sud, Lorient

Professeur, Université Jean Monnet, Saint-Étienne

Maître De Conférences/HDR, Sorbonne Université, Paris

Professeur, Ecole polytechnique de Université de Nantes

Maître De Conférences, Ecole polytechnique de l'université de Nantes

Les travaux de cette thèse ont été réalisés dans le cadre du projet SECURE IoT sélectionné par le RFI WISE avec le soutien financier de la Région des Pays de la Loire.

## ACKNOWLEDGEMENT

I would like to start this document by expressing my gratitude to all the people I met and received help during the course of my PhD.

First, I would like to thank both of my thesis supervisor Sébastien Pillement and Maria Mendez Real for providing me with the opportunity to pursue my PhD. I am highly grateful for the guidance and the support they provided me through my work which helped me better understand my subject and guided me in the right direction.

I would like to thank the reviewers and the jury committee Guy Gogniat, Lilian Bossuet and Emmanuelle Encrenaz for reviewing my thesis and accepting to evaluate my work. I would also like to extend thanks to my CSI members Quentin Meunier and Arnaud Tisserand for their constructive remarks that helped me complete my work.

Moreover, I would like to thank all the members of the IETR laboratory for their administrative and technical support. I would also like to address my gratitude to all my colleagues and fellow PhD students as they have enriched my daily life during my PhD.

Finally, I would like to thank my parents and brother for their unconditional and unwavering support that helped greatly through this journey.

# **R**ÉSUMÉ LONG

Les architectures multi-cœurs présentent aujourd'hui une grande complexité du fait du grand nombre de ressources les constituants. Afin de gérer cette complexité et de répondre à des contraintes de performances ou de consommation d'énergie, il est nécessaire d'implémenter des gestionnaires dynamiques (e.g., mapping de tâches, adaptation dynamique de la fréquence et de la tension). Par exemple, les smartphones ont été conçus en mettant des architectures complexes dans un espace limité tout en s'assurant du bon fonctionnement de l'appareil (i.e., durée de vie de la batterie, température du processeur). Cependant, dans la majorité des cas, ces gestionnaires n'ont pas été conçus pour la sécurité et présentent des vulnérabilités.

Durant les dernières années, un grand intérêt s'est porté sur les vulnérabilités matérielles présentes lors de la conception du circuit. Différents types d'attaques ont fait surfaces (e.g., Meltdown [1], Spectre [2], Clkscrew [3]) dont le but principal est d'extraire une information cachée (e.g., une clef de chiffrement). Ces attaques s'avèrent de plus en plus dangereuses étant donné que les systèmes embarqués (comme les smartphones) sont aujourd'hui utilisés pour des opérations sensibles, comme par exemple, des applications bancaires, paiement par téléphone, suivi de santé, ou les véhicules autonomes.

Cette thèse vise donc d'une part à étudier les gestionnaires actuels des architectures multi et many-core et à évaluer de possibles vulnérabilités. Il existe peu des travaux étudiant ces gestionnaires dans le cadre de la gestion d'architectures simples qui nous ont servis de base pour étudier leur pertinence/adaptation aux systèmes plus complexes de type many-core. D'autre part ces travaux visent à proposer et évaluer de possibles contre-mesures adaptées à ce type d'architecture. Dans cette thèse, nous nous intéressons à deux types de gestionnaire dynamique : le gestionnaire d'énergie et le gestionnaire de température. Trois attaques différentes sur ces deux gestionnaires sont ainsi présentées ainsi que de possibles contre-mesures.

Dans un premier temps, nous nous sommes intéressés à évaluer les vulnérabilités des gestionnaires d'énergie actuels. Ces gestionnaires permettent de réduire la consommation d'énergie en modifiant dynamiquement la tension et la fréquence de l'architecture, communément appelé DVFS (Dynamic Voltage and Frequency Scaling). Ce gestionnaire est composé de deux parties : i) Une partie logicielle composée d'une application qui gère la consommation énergétique de l'appareil en choisissant un couple de tension et fréquence. On retrouve aussi un driver kernel qui assure la communication entre l'application et la partie matérielle. ii) Une partie matérielle composée de régulateurs fixant les tensions d'alimentation des c/oe urs et de PLLs (Phase Locked Loop) fixant leurs fréquences.

Le contrôle sur la tension et la fréquence joue un grand rôle dans la gestion d'énergie d'un appareil. Cependant, ces deux grandeurs sont liées à la stabilité du système, et un microprocesseur ne peut fonctionner correctement que lorsque la fréquence et la tension respectent certaines conditions. En effet, dans un système combinatoire, la période de l'horloge doit être plus grande que le temps de propagation des signaux dans le circuit ainsi que le temps de *setup* et de *hold* des bascules. Une modification malveillante de tension sans adapter la fréquence peut donc rendre le système instable et générer des erreurs. Une première attaque sur la gestion malveillante de régulateurs DVFS a été publié en 2017 [[3]] dans une architecture de ARM. Cette attaque se base sur le principe précèdent et a pour but d'injecter des erreurs dans une tâche victime (e.g., chiffrement AES, RSA), ce qui permet de déduire les informations qui nous intéressent notamment la clef cryptographique secrète. Il existe aussi une autre attaque PlunderVolt [4] exploitant la même vulnérabilité sur une architecture Intel.

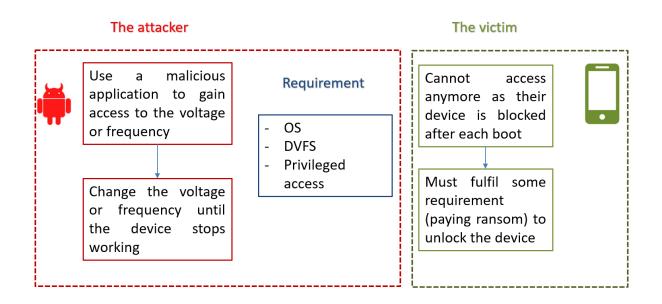

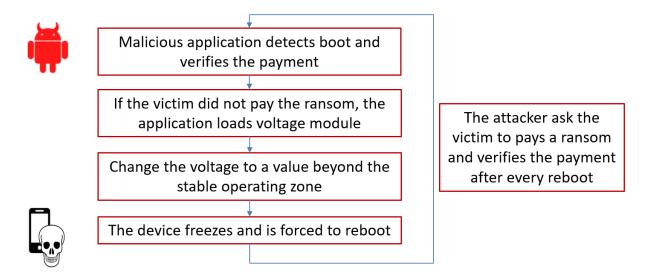

Le but principal de cette contribution est d'exploiter cette vulnérabilité différemment. En effet, des expérimentations ont démontrés qu'un changement malicieux de tension bloque l'appareil complètement à partir d'un certain seuil. Il est donc possible d'utiliser cette vulnérabilité comme une attaque par déni de service et peut même rendre un appareil inaccessible. Dans un scénario d'exploitation possible, en considérant un smartphone comme cible de l'attaque, un attaquant peut modifier la tension avec une application malicieuse et bloquer l'accès à l'appareil. Par la suite, l'attaquant peut demander une rançon à la victime pour débloquer son appareil.

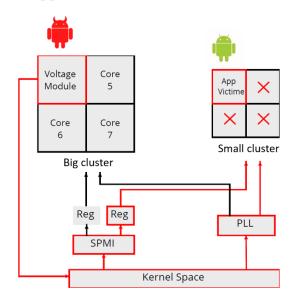

Cette attaque a été implémentée sur une carte Odroid XU4 [5] équipée d'un Exynos 5422 (ARM A7, A15) et une carte Hikey 960 équipée d'un Kirin 960 (A73 et A53). Ces deux cartes récentes utilisent la technologie big.LITTLE de ARM. Cette dernière utilise deux clusters séparés physiquement (un cluster big pour les hautes performances, et un cluster LITTLE pour l'optimisation de la consommation) chacun avec un régulateur de tension et un générateur de fréquence.

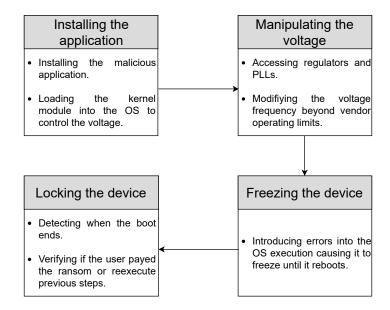

Finalement, l'implémentation de l'attaque se fait en 4 étapes : 1) Il faut une application malicieuse avec un accès privilégié installée sur l'appareil victime. Cet accès privilégié dans un téléphone peut s'être procuré facilement si la victime utilise une ROM customisée (e.g., Magisk) ou même en utilisant d'autres vulnérabilités classiques des téléphones. Ces utilisateurs seront la cible principale de cette attaque. 2) Un module afin de contrôler la tension est nécessaire, dans un cas général, il suffit d'utiliser l'API kernel pour les régulateurs. Celle-ci nous permet de contrôler les régulateurs justes en utilisant le nom assigné par le constructeur. Dans le cas de la Hikey960, un module permettant de contrôler la tension est déjà présent. 3) En utilisant le module précédent, il est possible de bloquer l'appareil en changeant la valeur de la tension en dessous du seuil nécessaire pour le fonctionnement étant donné qu'il n'y a aucune limite logicielle ou matérielle. 4) Finalement, il suffit de bloquer l'appareil de manière permanente en chargeant le module à chaque démarrage. Pour ce faire, il suffit d'utiliser l'application malicieuse pour détecter le démarrage et de charger le module malicieux avant même que la victime ne puisse débloquer son téléphone.

Cette attaque montre qu'il est possible d'utiliser malicieusement les gestionnaires d'énergie dans le cas où la précision n'est pas nécessaire pour injecter les fautes et extraire de l'information. La contre-mesure la plus directe de cette attaque serait de rajouter des limites aux valeurs de tensions possibles en fonction de la fréquence. Une autre contremesure serait de limiter l'accès aux régulateurs et que seule une application exécutée dans un environnement sécurisé (TEE – Trusted Execution Environment) puisse changer la tension.

Dans une deuxième partie, nous nous sommes intéressés aux gestionnaires de température. Ces gestionnaires sont aujourd'hui présents dans tous les systèmes afin d'assurer que les processeurs restent dans une température idéale et ainsi éviter la surchauffe et la détérioration des circuits intégrés. Normalement, des moyens de refroidissement actif (e.g., radiateur, ventilateur) sont utilisés. Cependant, dans le cas d'un téléphone mobile ou des appareils qui priorisent la portabilité, il n'est pas possible d'implémenter ces moyens. Dans ce cas, des outils de refroidissement passif sont utilisés, généralement, c'est la fréquence qui est réduite afin de refroidir le processeur.

Afin que les gestionnaires de température puissent prendre des décisions, ils doivent être capable de mesurer activement la température du processeur, pour ce faire, des capteurs de température ont été implémentés sur la plupart des processeurs modernes. Les capteurs sont généralement utilisés pour aider les gestionnaires mais dans notre travail, il a été possible de les utiliser afin d'extraire de l'information d'un programme victime. Dans les travaux déjà publiés, la température est généralement utilisée comme canal caché [6] afin de transmettre de l'information, dans ce cas aucune information n'est extraite, un autre travail a utilisé la température pour déduire le type d'applications qui est exécutée sur une architecture victime (e.g., explorateur internet, chiffrement RSA, ...) mais aucune information au niveau des instructions ou opérandes n'a été extraite.

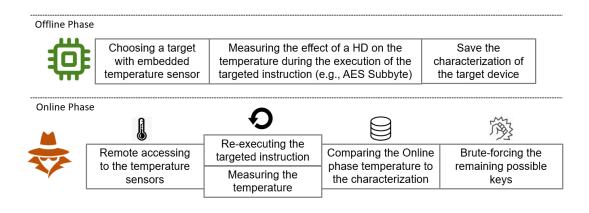

Dans notre scénario d'attaque, un attaquant doit caractériser l'effet d'une caractéristique d'une information secrète (une clef de chiffrement AES 128 bits dans notre étude) sur la température. Pendant la caractérisation, l'attaquant doit avoir accès à une copie de l'architecture cible et d'être capable de modifier la clef de chiffrement. Pendant l'attaque, il doit réaliser des mesures de températures à distance sur un appareil victime lors de l'exécution d'un chiffrement AES 128 bits avec une clef inconnue. L'attaquant peut par la suite analyser les mesures et les comparer à la caractérisation réalisée afin d'extraire des caractéristiques de la clef lui permettant de réduire l'espace d'exploration et même de réaliser une force brute dans certains cas.

Afin d'implémenter cette attaque, il faut tout d'abord caractériser la cible. Pour ce faire, des mesures ont été réalisés afin d'observer l'effet des instructions et des opérandes sur la température, la cible de cette expérimentation est le microprocesseur STM32F303 [7]. Dans ce cas, l'accès au capteur de température a été fait par DMA (Direct Memory Access) afin de limiter les effets de la mesure. Dans le cas d'un processeur multicœurs, il est possible de réaliser les mesures à partir d'un autre cœur.

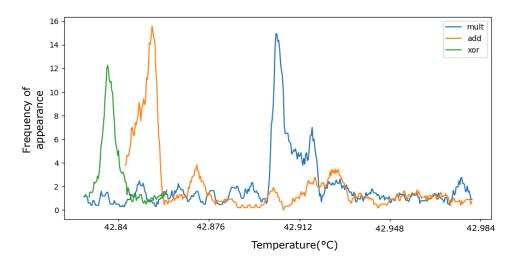

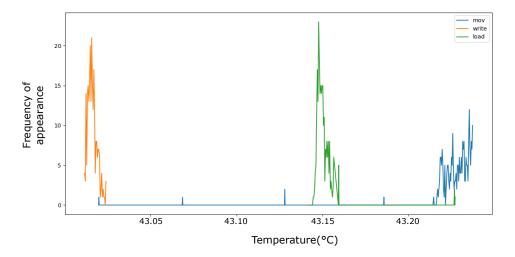

Une première caractérisation a été d'observer l'effet de différentes instructions lorsque les opérandes sont fixés, 3 instructions arithmétiques et logiques (multi, add et xor) en plus de 3 instructions de mémoires (load, write et mov) ont été exécutés dans une boucle et la température a été mesurée en parallèle afin de caractériser son évolution. Après l'analyse des mesures, il est possible de distinguer entre les différentes instructions de chaque type. En effet, même si la variation de température est petite, de l'ordre de 10 m°c, il est toujours possible de distinguer les instructions en utilisant uniquement la température. Par la suite, l'effet des opérandes pour certaines instructions a été caractérisée, notamment l'effet du poids de Hamming dans les multiplications sur 32 bits. La même configuration de mesures a été réutilisée, en plus, on fixe un opérande de la multiplication et on fait varier l'autre mais seulement pour des valeurs ayant les 3 poids de Hamming 8, 14 et 24. Cette limitation a été appliquée pour des raisons de temps de mesures. Après l'analyse des mesures, il est possible de clairement distinguer entre les 3 poids de Hamming dans la plupart des cas. Par la suite, nous nous sommes intéressés à caractériser l'effet des deux premières instructions de l'AES, la SBOX et l'ADDKEY sur la température, pour ce faire, la distance de Hamming (nombre de bits qui ont changé entre deux états d'un registre) a été étudiée. Tout d'abord, l'ADDKEY est calculée entre une valeur fixée (celleci représente un octet de la clef de chiffrement) et une autre qui varie (celle-ci représente un octet du texte à chiffrer), étant donné que les calculs se font sur 8 bits, il était possible de faire les mesures pour toutes les valeurs possibles du deuxième opérande. Le résultat est enregistré dans un registre 'r' qui est par la suite utilisé pour calculer la SBOX et pour enregistrer les résultats de ce calcul. La distance de Hamming caractérisée est donc celle entre les deux états du registre 'r'. Finalement, en observant les mesures de températures effectuées, il est clairement possible de distinguer les 9 distances de Hamming possible pour des opérandes de 8 bits.

La caractérisation a permis de corréler la température aux instructions et aux opérandes, de plus, la dernière expérimentation nous a même permis de caractériser l'effet de certaines instructions d'AES sur la température, dans ce cas la clef de chiffrement étant connue. Afin d'utiliser cette caractérisation dans une attaque sur un chiffrement AES, il faut que l'attaquant soit capable de re-exécuter indifféremment l'ADDKEY pour un octet spécifique comme lors de l'expérimentation réalisée. Pour ce faire, nous avons utilisé des techniques similaires à SGXSTEP [8], le principe est de déclencher des interruptions périodiquement à la fin de l'exécution des instructions à l'aide d'un compteur matériel. Finalement, l'attaquant doit effectuer des mesures de température à distance sur l'appareil victimes pendant un chiffrement à l'aide d'une application malicieuse ayant accès aux capteurs. Dans ce cas, la clef n'est pas connue, cette mesure est donc comparée à la caractérisation déjà réalisée (la clef était connue) et cette comparaison permet de déduire quelle distance de Hamming à une valeur de température proche ou égale. En utilisant la distance de Hamming déduite, il a été possible de réduire l'espace d'exploration de 98.27% dans le meilleur des cas pour un octet de la clef et 74% dans le pire des cas.

Pour cette attaque, deux contre-mesures ont été proposé. La plus simple est de réduire la précision des capteurs de températures mais cela augmente seulement le nombre de mesures nécessaires pour réaliser l'attaque, la deuxième contre-mesure serait de limiter l'accès aux capteurs à des applications fiables (en TEE par exemple) tout comme pour les régulateurs dans l'attaque sur les gestionnaires d'énergie.

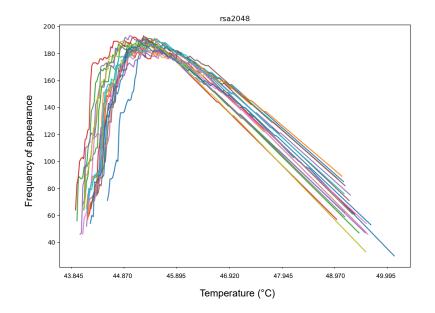

La troisième contribution de cette thèse est de réaliser une attaque similaire avec les capteurs de température sur une architecture plus complexe, la Hikey960 [9] présenté précédemment, et un chiffrement RSA 2048 bits. Le scénario de l'attaque est le même, un attaquant caractérise la cible et identifie l'effet d'une certaine caractéristique de la clef de chiffrement (dans ce cas, la clef est connue) sur la température. Par la suite, il effectue des mesures à distance et utilise ces mesures avec la caractérisation réalisée afin de déduire des caractéristiques de clef et de réduire l'espace d'exploration.

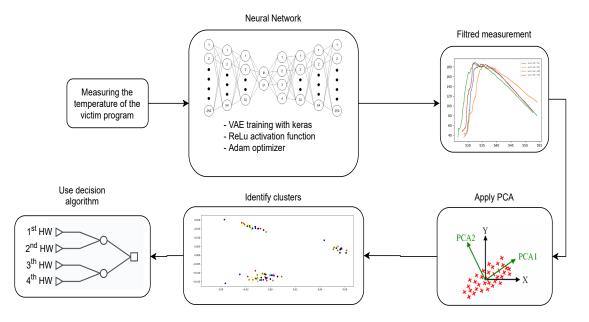

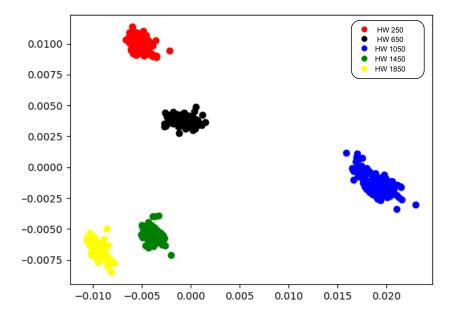

Sur cette architecture complexe, une simple étude et comparaison de température n'était pas suffisante, il a été nécessaire d'utiliser des analyses plus poussées, notamment, de l'apprentissage automatique. Deux algorithmes ont été utilisés : i) un premier algorithme qui filtre les mesures, VAE (Variational Autoencoder), ce dernier est composé de deux réseaux de neurones entièrement connecté dont le but est de compresser l'information et puis de la décompresser. Les neurones d'entrée et de sortie doivent donc avoir la même donnée mais le nombre de neurones diminue progressivement jusqu'à 4 neurones dans notre cas et puis augmente jusqu'à attendre le même nombre de neurones d'entrée. Cette phase permet d'éliminer le bruit. ii) Un deuxième algorithme pour clustériser les données, PCA (Principal Component Analysis), ce dernier traite les données filtrées précédemment par le VAE et forme des clusters en fonction de la caractéristique de la clef. Dans notre cas, la caractéristique utilisée est le poids de Hamming de la clef. Finalement, cette attaque a été validée sur certain poids de Hamming et en utilisant l'analyse proposée, il était possible d'identifier cette caractéristique dans un scénario réel. Cependant, le nombre de cas possible restant ne permet pas de réaliser une brute-force et nécessite d'autres approches additionnelles pour identifier la clé secrète (de 2048 bits pour rappel).

Dans cette thèse, nous avons exploré de possibles vulnérabilités présentes dans les gestionnaires dynamiques requis par les architectures embarquées modernes. Il a été prouvé à travers trois attaques qu'il est possible de malicieusement exploiter ces gestionnaires, et quelques contre-mesures ont été proposés. Les analyses proposées peuvent être poussées plus loin surtout dans la dernière contribution, le VAE peut-être aussi utiliser pour identifier l'effet d'une certaine caractéristique (un poids de Hamming spécifique) même si aucune mesure n'a été fait pour celle-là tant que l'on a assez de mesures pour les autres poids de Hamming. Cette analyse peut être aussi utilisée pour les attaques de consommation dans le cas où le nombre de mesures est limité.

# TABLE OF CONTENTS

| In       | Introduction                             |        | 17                                                      |    |

|----------|------------------------------------------|--------|---------------------------------------------------------|----|

| 1        | Bac                                      | kgroui | nd and state of the art                                 | 19 |

|          | 1.1                                      | Energ  | y managers                                              | 19 |

|          | 1.2                                      | Side C | Channel Attacks                                         | 24 |

|          |                                          | 1.2.1  | Differential fault analysis                             | 25 |

|          |                                          | 1.2.2  | Attacks exploiting DVFS                                 | 26 |

|          | 1.3                                      | Tempe  | erature managers                                        | 28 |

|          | 1.4                                      | Tempe  | erature related vulnerabilities                         | 29 |

|          | 1.5                                      | Integr | ated Sensors and hardware counters                      | 32 |

|          | 1.6                                      | Power  | analysis based attacks                                  | 34 |

|          |                                          | 1.6.1  | Power Analysis Attacks using embedded sensors           | 36 |

|          |                                          | 1.6.2  | Template attacks                                        | 36 |

|          |                                          | 1.6.3  | Profiling attack with machine learning                  | 37 |

|          | 1.7                                      | Conclu | usion                                                   | 38 |

| <b>2</b> | Maliciously exploiting energy management |        | 39                                                      |    |

|          | 2.1                                      | Scenar | rio                                                     | 40 |

|          | 2.2                                      | Target | t device                                                | 41 |

|          |                                          | 2.2.1  | ARM architecture and big.LITTLE Technology              | 41 |

|          |                                          | 2.2.2  | Hikey960 & Odroid XU4                                   | 42 |

|          | 2.3                                      | Exper  | imental Setup                                           | 43 |

|          |                                          | 2.3.1  | Accessing and controlling the voltage and the frequency | 43 |

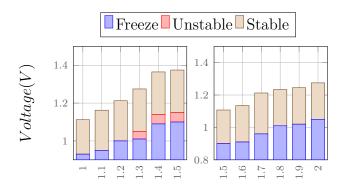

|          |                                          | 2.3.2  | Characterisation of the targets                         | 45 |

|          |                                          | 2.3.3  | Conclusion on the characterisation                      | 47 |

|          | 2.4                                      | Malici | ous exploitation of the DVFS                            | 48 |

|          |                                          | 2.4.1  | Implementation steps                                    | 48 |

|          |                                          | 2.4.2  | Implementation of the attack                            | 50 |

|          |                                          | 2.4.3  | Discussion and counter-measures                         | 52 |

### TABLE OF CONTENTS

|   | 2.5        | Conclu  | usion                                                       | 53       |

|---|------------|---------|-------------------------------------------------------------|----------|

| 3 | Exp        | loiting | g integrated temperature sensor                             | 55       |

|   | 3.1        | Metho   | odology                                                     | 56       |

|   | 3.2        | Exper   | imental setup                                               | 57       |

|   |            | 3.2.1   | Distinguishing instructions                                 | 58       |

|   |            | 3.2.2   | Distinguishing between operands                             | 60       |

|   |            | 3.2.3   | Distinguishing operands based Hamming Distance              | 63       |

|   | 3.3        | Extra   | cting AES key characteristics using temperature sensors     | 64       |

|   |            | 3.3.1   | Methodology of the attack main steps                        | 64       |

|   |            | 3.3.2   | AES reminder                                                | 66       |

|   |            | 3.3.3   | Attack implementation and results                           | 66       |

|   |            | 3.3.4   | Offline Phase                                               | 68       |

|   |            | 3.3.5   | Online Phase                                                | 69       |

|   |            | 3.3.6   | Results analysis                                            | 70       |

|   | 3.4        | Discus  | ssion                                                       | 72       |

|   | 3.5        | Conclu  | usion                                                       | 73       |

| 4 | Hai        | na ma   | chine learning to analyze temperature variation and extract |          |

| 4 |            | 0       | ormation                                                    | 75       |

|   | 4.1        |         | s scenario                                                  | 76       |

|   | 4.2        |         |                                                             | 77       |

|   | 1.2        | 4.2.1   | Distinguishing operands HWs                                 | 78       |

|   | 4.3        |         | ne learning methods                                         |          |

|   | 1.0        | 4.3.1   | Variational Autoencoder                                     |          |

|   |            | 4.3.2   | Principal Component Analysis                                |          |

|   | 4.4        |         | ng the HW of RSA private key                                |          |

|   | 7.7        | 4.4.1   | Main implementation steps of attack                         | 85       |

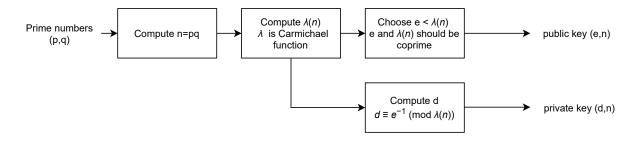

|   |            | 4.4.2   | RSA reminder                                                | 86       |

|   |            | 4.4.2   | Experimental setup                                          | 87       |

|   |            | 4.4.4   | Attack implementation and results                           | 88       |

|   | 4.5        |         |                                                             | 90       |

|   | 4.5<br>4.6 |         | usion                                                       | 90<br>91 |

|   | 4.0        | Conci   | usion                                                       | 91       |

|   |            |         |                                                             |          |

## Bibliography

97

# LIST OF FIGURES

| 1.1  | The increase of microprocessor complexity over the years showing two sep-        |    |

|------|----------------------------------------------------------------------------------|----|

|      | arate phases, the first phase focus on increasing the frequency while the        |    |

|      | second phase focus on increase the number of logical cores [13]                  | 20 |

| 1.2  | The hardware implementation of DVFS showing different elements neces-            |    |

|      | sary to the control of the frequency and voltage of a core or cluster $\ldots$ . | 21 |

| 1.3  | A general implementation of the software part of DVFS highlighting the           |    |

|      | three different levels and its connection to the hardware part $\hdots$          | 22 |

| 1.4  | The time constraints condition is represented through the schematic, by          |    |

|      | showing how the frequency is dependant on the voltage                            | 23 |

| 1.5  | highlighting of two types of SCA, the Physical Extraction and Functional         |    |

|      | Extraction [18]                                                                  | 24 |

| 1.6  | Clkscrew steps showing how the normal core running the malicious appli-          |    |

|      | cation faults the target running the encryption program while the normal         |    |

|      | core stays protected from the changes of frequency                               | 27 |

| 1.7  | Thermal throttling for core 0, frequency and power are decreased to keep         |    |

|      | temperature from going beyond junction temperature at 95°C. Results of           |    |

|      | this figure were presented in $[27]$                                             | 30 |

| 1.8  | Different heat generated depending on the HW of the operand during the           |    |

|      | operation 'mov' $[28]$                                                           | 31 |

| 1.9  | Transmitting data from one "secure" core to another "normal" core using          |    |

|      | intensive processing to raise the temperature $[6]$                              | 31 |

| 1.10 | Profiling the type of application the user is running based on the tem-          |    |

|      | perature measurements. This figure is one of results that were presented         |    |

|      | in [6]                                                                           | 32 |

| 1.11 | Dynamic manager functions as an autonomous closed loop. The decision is          |    |

|      | made based on the sensor's measurement, the CPU switch to a new state            |    |

|      | and the manager keeps monitoring ensuring the desired state is reached           | 33 |

| 1.12 | The different steps and tools necessary to execute a classical power based       |    |

|      | attack                                                                           | 35 |

| 2.1 | Summary of the scenario of the attack from both the attacker and the                                                             |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------|----|

|     | victim point of view plus the conditions required to implement the attack                                                        | 41 |

| 2.2 | ARM big.LITTLE technology and DVFS implementation                                                                                | 42 |

| 2.3 | The experimentation used to characterise the SoC. In this case, we char-                                                         |    |

|     | acterise the LITTLE cluster, but with the same methodology we can also                                                           |    |

|     | characterise the big cluster by switching voltage module to the LITTLE                                                           |    |

|     | cluster and the victim app to the big cluster                                                                                    | 45 |

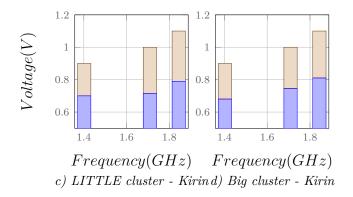

| 2.4 | Characterization of Exynos 5422 and Kirin 960 clusters effects of the the                                                        |    |

|     | modification of voltage for each frequency level.                                                                                | 47 |

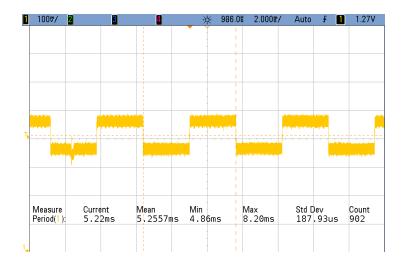

| 2.5 | The measured voltage at the output of PMIC for the Exynos shows an                                                               |    |

|     | average minimum time of 2.5ms between each voltage changes $\ldots$ .                                                            | 48 |

| 2.6 | Required steps from the attacker point of view                                                                                   | 49 |

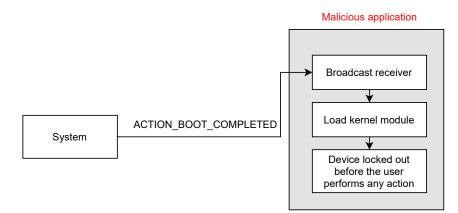

| 2.7 | Summarized usage of <i>intent</i> used by android to ensure communication be-                                                    |    |

|     | tween applications $\ldots$                     | 51 |

| 2.8 | Summarized steps performed by the attacker on the victim device $\ldots$ .                                                       | 51 |

| 3.1 | Required steps for the proposed temperature driven attack from the at-                                                           |    |

|     | tacker point of view.                                                                                                            | 57 |

| 3.2 | Comparison of the integrated temperature values generated by each con-                                                           |    |

|     | sidered arithmetic and logic instruction with the same operands $\ldots \ldots$                                                  | 59 |

| 3.3 | Comparison of the integrated temperature values generated by each con-                                                           |    |

|     | sidered memory instruction with the same operands $\ldots \ldots \ldots \ldots \ldots$                                           | 60 |

| 3.4 | The main steps used for measuring the effect of the operands on the tem-                                                         |    |

|     | perature                                                                                                                         | 61 |

| 3.5 | Comparison of the temperature generated by 32-bit width multiplication,                                                          |    |

|     | with the non-constant operand having HW of $[8,16,24]$ and multiplied by                                                         |    |

|     | the constant value $23 \ldots \ldots$ | 62 |

| 3.6 | Comparison of the temperature depending on the HD between two states                                                             |    |

|     | of the same register after a <i>xor</i> and a <i>load</i> operation                                                              | 64 |

| 3.7 | Operations in the first round of AES                                                                                             | 67 |

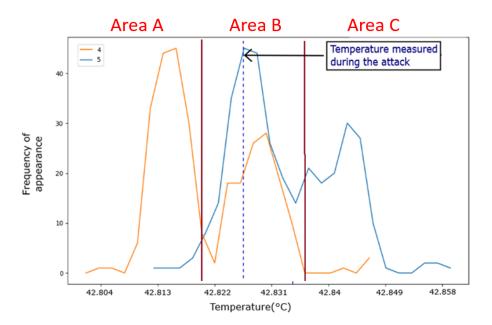

| 3.8 | For the STM32F303 platform, the temperature characterization for two                                                             |    |

|     | arbitrary HDs of $r$ (4 and 5) during the Offline Phase. There are 500 dots                                                      |    |

|     | in each graph and each point represents the mean value of 30,000 tem-                                                            |    |

|     | perature measurements. The blue dotted line represents the temperature                                                           |    |

|     | measurement during the Online Phase                                                                                              | 69 |

### LIST OF FIGURES

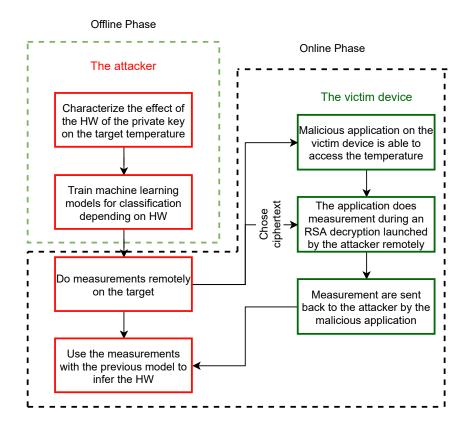

| 4.1  | The main steps of the proposed temperature separated into the Offline                              |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | Phase where the attacker characterize the victim device and Online phase                           |    |

|      | where the attacker access the temperature sensor on the victim device and                          |    |

|      | measure the temperature remotely                                                                   | 76 |

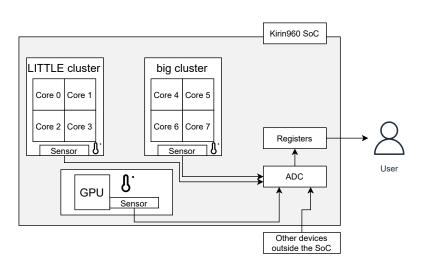

| 4.2  | The 5 different temperature sensors on the Hikey960 board                                          | 78 |

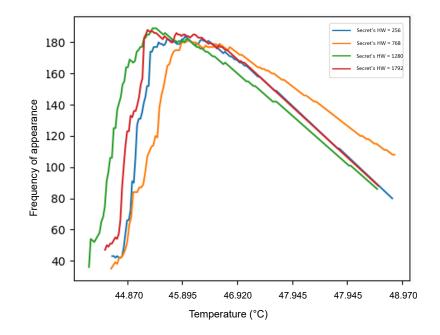

| 4.3  | Comparison of the integrated temperature values generated by different                             |    |

|      | HW values of the secret (hidden operand)                                                           | 79 |

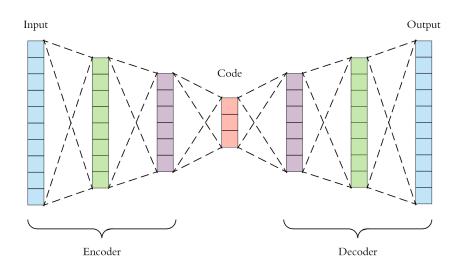

| 4.4  | The classic structure of an Autoencoder were the Encoder compress the                              |    |

|      | data into a 3 dimension layer Code (also called latent space), meanwhile,                          |    |

|      | the Decoder reconstruct the data from the latent space. The reconstructed                          |    |

|      | data has its insignificant information filtered $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 81 |

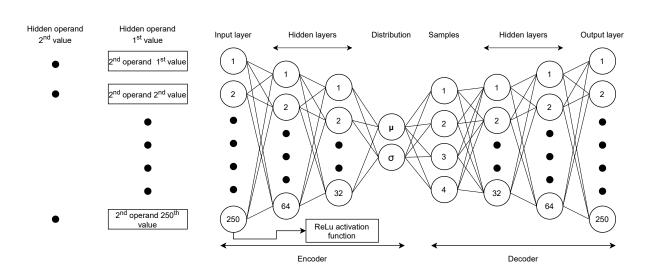

| 4.5  | The structure of the VAE used during this work                                                     | 82 |

| 4.6  | Comparison of the integrated temperature values generated by different                             |    |

|      | HW values of the secret after being filtered using a VAE $\ldots$                                  | 83 |

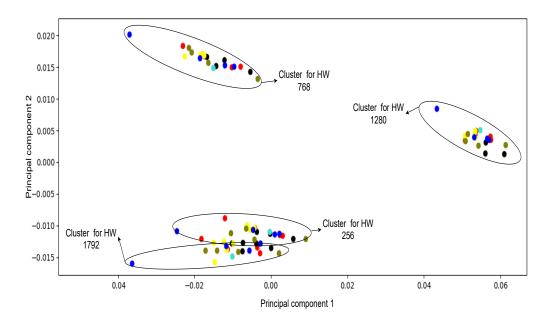

| 4.7  | Different clusters are formed depending on the HW of the hidden operand                            |    |

|      | after using PCA on the dataset filtered by the VAE $\ldots$                                        | 83 |

| 4.8  | All the steps used in the characterization of the 2048 bits multiplication,                        |    |

|      | from measurement to identifying the HW of a fixed operand $\ldots \ldots \ldots$                   | 84 |

| 4.9  | The main step to generate the public and private key of the RSA algorithm                          | 87 |

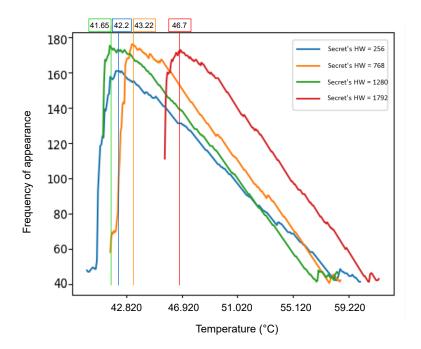

| 4.10 | Temperature characterization of RSA2048, each trace shows a different $\rm HW$                     |    |

|      | from (80 to 2000 with a step of 80). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 88 |

| 4.11 | Clusters for each HW $(250, 650, 1050, 1450, 1850)$ of the private key formed                      |    |

|      | after executing the PCA on the dataset of RSA2048 using 200 keys per HW.                           | 89 |

## INTRODUCTION

Embedded systems architectures are becoming more and more complex to support the ever increase of algorithmic complexity requirements. This led to an increase in the number of transistors within chips, the number of logical cores and their running frequencies which gave rise to an increase in energy consumption and heat generated by the chips. This is problematic for devices such as smartphones, these devices were designed to fit complex architectures in the smallest space while ensuring that the processor runs in stable conditions. This includes maximizing the battery life and making sure that the processor does not overheat (Temperature goes beyond the limit specified by the manufacturer). This phenomenon is even more important for advanced 3D stacking technologies [10]. Moreover, overheating also cause chip to age faster [11],[12]. Thus, it was necessary to manage both of the temperature and power consumption, for this different dynamic managers were deployed.

As for the increase of logical cores, it was also necessary to implement resources managers to optimise their usage and have a better scheduling. To summarize, it is necessary to use dynamic managers to fully exploit state-of-art architectures. The goal of these dynamic managers is either to optimize resources usage (*e.g.*, cores, memory) and/or to reduce the energy consumption of the system under performance constraints. However, these managers have not been designed to be secure and present vulnerabilities.

In recent years, there has been an increase in the number of attacks based on hardware vulnerabilities (*e.g.*, Meltdown [1], Spectre [2], Clkscrew [3]). This type of attacks have shown to be dangerous for everyone including mobile devices for example, this can highly affect the privacy of the users. Moreover, smartphone are used more and more for sensitive operations such as payment, banks applications and healthcare. Furthermore, this is not limited to mobile phone and can be extended to IoT, connected devices (*e.g.*, autonomous car, smartTV) and even health electronics.

In this thesis, we aim at evaluating the security of different dynamic managers used in today's devices, study possible vulnerabilities and finally discuss some countermeasures. We are going to focus on two important managers present in almost every device today: energy and temperature managers. Three different attacks targeting the two managers are presented in this work and implemented on different target devices. Two of the target devices are processors used by the smartphone industry, the Kirin960 [9] and the Exynos5422 [5], these targets are heterogeneous octa-cores based on ARM architectures while the third target is an STM32F303 [7] single core mainly used for IoT.

The rest of the thesis is divided as follows:

- Chapter I: Background and State of art presents the context of our work and contains the basics functioning of the dynamic managers we target in the other chapters. This chapter also presents related State-of-Art vulnerabilities and previous attacks on the managers.

- Chapter II: Maliciously exploiting energy management presents our first contribution. It presents a case of malicious usage of energy management, more specifically, the Dynamic Voltage & Frequency Scaling mechanism (DVFS). Experimentations shows that it is possible to remotely lock out a device, denying access to all services and data, requiring for example the user to pay a ransom to unlock it. As the main target of this exploit is embedded systems, we demonstrate this work by its implementation on two different commercial ARM-based devices (Odroid XU4 and Hikey960). Finally, some possible countermeasures were discussed.

- Chapter III: HEXotherm presents our second contribution. It targets IoT devices and uses the integrated temperature sensors to extract secret information. We demonstrate the feasibility of this attack and show that it is possible to use the extracted information to deduce characteristics on an AES secret key. Our different experiments on a real hardware platform show a reduction from 74% in the worst case scenario to 98.27% of the exploration space for each byte of the 128 bits key in the best case scenario.

- Chapter IV: Using machine learning with temperature sensors presents the last contribution of this work. It is an extension of the previous work and it target a more complex architecture. In this chapter, we prove through experimentations that it is possible to use machine learning techniques to analyze the temperature issues from embedded sensors and use it to infer the hamming weight of the private key of the RSA algorithm.

- Conclusion: resume all the contributions of this thesis and propose possible further works to perform.

## **BACKGROUND AND STATE OF THE ART**

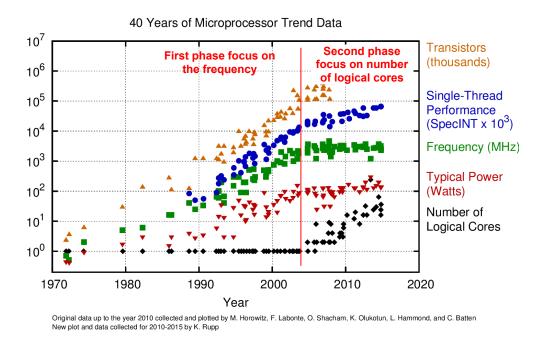

Over the years, there has been a continuous increase in microprocessor's performance to follow up with the increase of application complexity as can be seen in Figure 1.1. During a first phase, the focus was on increasing the performance of single cores/processors and mainly through the increase of their frequency. However, due to the technological constraints the increase in frequency stagnated, a second phase started where the focus switched toward the increasing number of logical cores per microprocessor. During both phases, the density of the integrated circuit and its energy consumption continued to increase with the heat emitted. Moreover, with the continuous increase in available resources, it has been necessary to implement dynamic managers. Those managers have 3 main usages and can be separated into the following types:

- Resources manager in order to optimize resources usage and increase general performance.

- **Energy manager** which intend to reduce energy consumption, improve system portability and increase battery life.

- Temperature manager regulate temperature in order to avoid overheating and increase the chip life time.

### **1.1** Energy managers

In the embedded system industry, energy management has become a necessity to optimize system performance and reduce energy consumption to improve system portability, and increase battery life.

An efficient energy manager is composed of a software part that controls a hardware dedicated block. The software is generally a decision-making algorithm monitoring different parameters of the architecture (e.g., the CPU load, battery level and current energy consumption). On the other hand, the hardware part is responsible for applying

Figure 1.1 – The increase of microprocessor complexity over the years showing two separate phases, the first phase focus on increasing the frequency while the second phase focus on increase the number of logical cores [13].

the decisions and collecting information on the current state of the microprocessor using embedded sensors.

The amount of energy consumed in a system is the product of power and time. It refers to the total amount of resources utilized by a system to complete a task over time. In the case of an integrated circuit, power P at the instant t is directly proportional to the product of operating frequency F, voltage V and C the switching capacity of the circuit [14]:

$$P_t \equiv C * V_t^2 * F_t. \tag{1.1}$$

It is clear at this point that modifying the frequency and specially the voltage can drastically reduce the power consumption in exchange of reducing the computation speed. Nowadays, the most used energy management mechanism that implements this feature is the Dynamic Voltage & Frequency Scaling (DVFS) [15]

### DVFS

DVFS was first introduced in 1994 [15] and is one of the most used energy saving mechanisms today, especially in embedded systems such as in the smartphone industry where portability and increasing the device's battery life is of most importance.

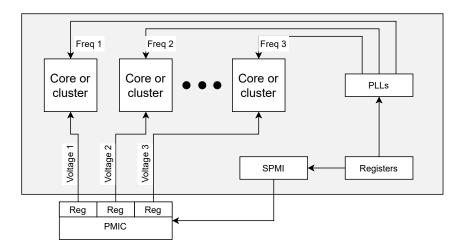

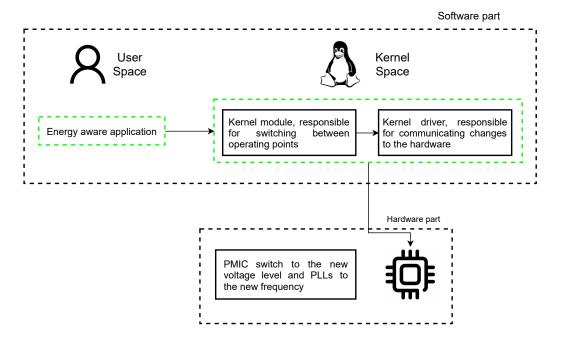

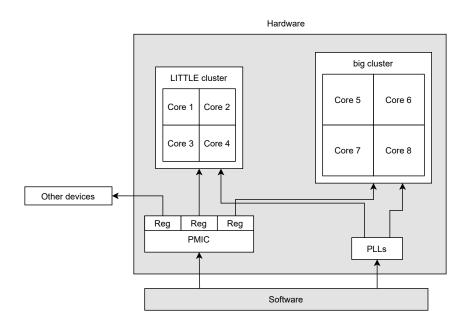

DVFS relies on the ability to control frequency and voltage levels of a core or a cluster of cores in a System On Chip (SoC) in order to dynamically trade processing speed for energy consumption according to the system requirements. DVFS is based on several part as shown in Figure 1.2 and Figure 1.3.

Figure 1.2 – The hardware implementation of DVFS showing different elements necessary to the control of the frequency and voltage of a core or cluster

#### Hardware part

In Figure 1.2, the hardware components required include at least one voltage regulator and Phase Locked Loop (PLL). Voltage regulators are part of the Power Management Integrated Circuit (PMIC), generally a dedicated component outside of the SoC due to analog part in regulators, while PLL are more often within the SoC. There are different implementations of the hardware part depending on the architecture. For example, in ARM big.LITTLE architecture, the PMIC and PLLs use the same voltage and frequency for the 4 cores within each cluster while in most INTEL and AMD processors each core's frequency and voltage values are independent from other core. This choice of having all cores independent is rarer in embedded systems, especially in ARM based architectures. However, it is still possible to find old devices using individual regulators for each core (e.g., Qualcom implementation of Snapdragon 800 [16]). The frequency of core or cluster is controlled by the PLL circuit built in the SoC.

Figure 1.3 - A general implementation of the software part of DVFS highlighting the three different levels and its connection to the hardware part

#### Software part

The software part of the manager is generally composed of two different levels as shown in Figure 1.3. The first layer running in the user space represents the energy aware application which has a set of predefined frequency and voltage couples called Operating Points (OP) predefined by the manufacturer. The application will select between those OP depending on different parameters. For example, when the device is idle or the load is low, both frequency and voltage are reduced to save energy. It also depends on the current level of battery depletion and the energy governor chosen by the user (either prioritizing performance or battery life). The second layer running in the kernel space is composed of a kernel module and a driver responsible for communicating to the hardware the frequency and voltage of the chosen OP. Most of the manufacturers use their own drivers for the PMIC, while the frequency is mostly controlled by open-source software like *cpufreq* [**cpufreq**] available in Linux-based Operating Systems (OS).

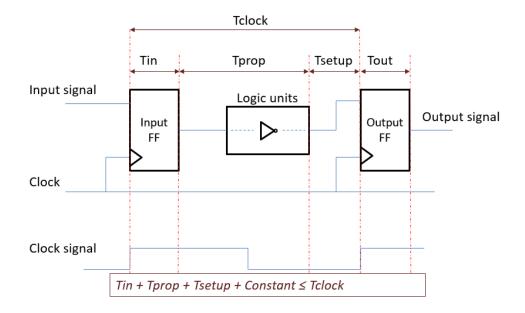

The frequency and voltage are not independent from each other as they are together

responsible for the stability of the system. In a sequential system, the propagation time  $T_{prop}$  in the logic units highly depend on the voltage and the higher its value, the shorter the propagation time is in the circuit. On the other hand, the period of the clock  $T_{clock}$  is used by the FlipFlops (FF) to lock on the data. As shown in Figure 1.4, the circuit has logic units between two FFs. For the device to function properly, the second FF at the output of the logic units must lock on the data one tick after the first FF at the input. Thus,  $T_{clock}$  must be superior to the maximum  $T_{prop}$  in the circuit plus a Constant (to take into account possible variation due to temperature and other factors) to ensure that both FFs are synchronized. In general, a device equipped with DVFS has predefined

Figure 1.4 – The time constraints condition is represented through the schematic, by showing how the frequency is dependent on the voltage

OP predefined by the manufacturer to guarantee that the processor works in perfect and stable conditions. These OP can be changed in the kernel source code but the frequency and voltage can be modified using specific Kernel API (*e.g.*, Voltage and current regulator API) or functionalities made available by the vendor. This make it possible to maliciously change the voltage or frequency beyond the recommended range. Thus, breaking the timing constraints and introduce faults within a device. Using a type of Side Channel Attack (SCA) called Differential Fault Analysis (DFA) [17] it was possible to exploit those faults to extract secret from a device.

### 1.2 Side Channel Attacks

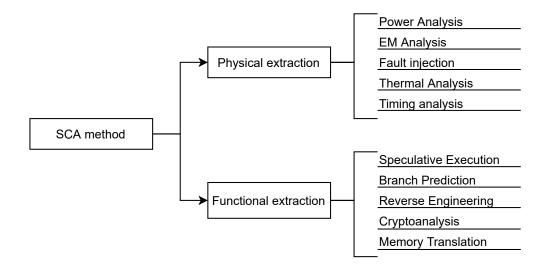

Side channel attacks are well known practices which goal aims at using different possible sources of information to extract secret information (*e.g.*, encryption keys). The work [18] summarize the state-of-art of SCA methods and techniques in Figure 1.5

Figure 1.5 – highlighting of two types of SCA, the Physical Extraction and Functional Extraction [18].

The most established methods among SCA are:

- Memory based attacks: attacks based on attacker's ability to monitor cache or memory accesses made by the target in a shared physical system.

- Timing attacks: attacks based on measuring the time required to perform certain computations.

- Power attacks: attacks that make use of the variation of the power consumption induced by the hardware during the computation of target programs like AES and RSA

- Electromagnetic attacks: attacks based on leaked electromagnetic radiation during specific operations..

- Differential fault analysis: in which secrets are discovered by introducing faults in a computation.

All those attacks utilize information (leakage) created or induced by certain operations. Those leakages hide information about the current state of the processor and what is being computed, thus, using specific analysis, it is possible to infer secret data such as encryption.

In the previous Section 1.1, it was shown that it is possible to inject fault within a device by maliciously exploiting DVFS [4],[3],[19]. Thus, we will now focus on DFA as it used to recover secrets by introducing fault within the victim device.

### **1.2.1** Differential fault analysis

DFA is a type of side channel attacks using cryptanalysis. This attack uses fault injection during the victim program execution, mainly encryption, to obtain faulted cyphertexts, this faulted date are then used to reveal the internal states of the target processor. The fault can be created using different methods such as high temperature, unsupported supply voltage or current, excessive overclocking, strong electric or magnetic fields, or even ionizing radiation to influence the operation of the processor. However, it is important to have a certain control and precision over the fault injection in order to perform this analysis. In [17], the authors recovered an AES secret key using DFA. In this case, the fault must be injected during a specific part of the encryption computation to be able to recover the key. This targeted part varies depending on the byte of the encryption key we wish to infer. For example, to infer the last 4 bytes of the 9th subkey a fault must be introduced during the key expansion during the computation of 9th subkey, just before the computation of the 10th subkey.

In [17], the full AES key of 128 bits was obtained using around 250 faulted cyphertext. However, having the ability to inject faults does not guarantee a successful attack as a certain precision is required. This precision depends on the target device but as seen previously, the fault needs to introduce during dozens of operations within a specific part of the target program. In the case of the AES, the fault is generally injected during the key expansion. Moreover, this type of attack usually requires a physical access to the target device, as most precise fault injection tools can only be used by interacting with the target device, for example, injection by laser. However, recently, a new type of attacks proved that it is possible to successfully execute a remote DFA through the exploration of DVFS capabilities.

### 1.2.2 Attacks exploiting DVFS

As shown in Section 1.1, timing constraints conditions are required to ensure the stability and error free sequential circuits. However, when the frequency is too high, or the voltage is too low the constraints can be broken. This will result in the input and output flip-flop desynchronization and in the introduction of faults (meta stability) during the execution of certain instructions in the CPU.

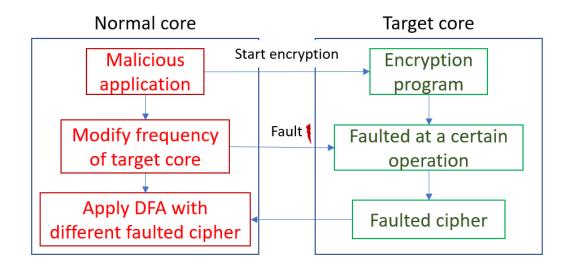

The work presented in [3] was the first to introduce this vulnerability and to exploit it, to remotely inject faults into a processor core. The authors fixed the voltage of the target device and changed the frequency to break the timing constrains. Using this vulnerability, they prove that it is possible to use DFA to recover secret encryption keys. The target of [3] is the smartphone Nexus 6, using 4 of *Krait 450* cores based on the ARM Cortex A53 architecture. The 4 cores have separate voltage and frequency islands, thus, when the attacker modifies the frequency to cause instability and to inject faults within a certain core (running the encryption), the attacker is not affected and continue running on stable conditions. The study of the fault model is also provided, for this purpose, the authors used delay loops to control when the faults are injected and kept track on where the fault occurred. Using this data, they were able to establish a model showing the most probable part to be affected of the AES encryption algorithm depending on the delay before breaking the time constraints. Finally, the attack is executed as shown in Figure 1.6.

The first target of this work was an AES 128 encryption, using the embedded instruction counter within the ARM cores, the attacker was able to have a certain control over the fault injection. This attack is not guaranteed to work all the time as the fault does not always occur within the specific part of the victim program.

This technique was also used to corrupt the execution of an RSA signature [20] verification algorithm by combining it with a cache side channel attack (Prime+Probe)é[21]. Using this second attack, the authors were able to follow the execution of the RSA and fault certain parts of the verification causing it to allow the execution of a malicious application within an ARM TrustZone [22] (trusted execution environment of ARM).

The previous work focused on fixing the voltage of the target core and modifying the frequency, in another work [19], they proved also the feasibility of this attack by fixing the frequency and modifying the voltage to fault the victim. However, they used the same target device and never proved its feasibility on more recent and complex SoCs. On the other hand, in [4], the authors extended this work to Intel processors as their architecture

Figure 1.6 – Clkscrew steps showing how the normal core running the malicious application faults the target running the encryption program while the normal core stays protected from the changes of frequency

uses separate frequency and voltage islands for each core and proved that it is possible to extract data using the same vulnerability.

This kind of fault injection does not require any kind of physical access to the system as DVFS can be remotely manipulated. However, compared to classical fault injection, one of the main challenges of this technique is the necessity for very high fault injection precision. As seen in Section 1.2.1 faults must be injected within specific part during a few instructions. Furthermore, accessing the voltage and frequency regulators requires for the attacker to have root privileges.

A different work in [23] uses the DVFS mechanism as covert channel. The main goal of this usage is to secretly transfer information from a malicious application being executed in the secure world of the ARM TrustZone (or from a non-secure third-party IP), to a malicious task executing in the "normal" (*i.e.*, non-secure) world by using the DVFS mechanism as a hidden channel of communication. The data to be transmitted being encoded into different levels of voltage or frequency. For example, the bit '0' can be encoded into a low level of voltage, while '1' can be encoded into a high level of voltage. The application on the normal world reads the current value of the voltage or the frequency and infer if the transmitted bit is '0' or '1'. This technique does not require any of the previous attack precision as its goal is not to steal information, but an already corrupted task is required to be executed within the secure world of the processor. The same researcher group started to work on possible leads to prevent the malicious usage of energy managers. In 2019, they proposed a machine learning algorithm to detect malicious usage of the DVFS [24], this requires to add an integrated circuit which separate malicious changes to voltage and frequency from the rest, thus, protecting the potential target program. Moreover, a different work proposed a chip called Fame [25], in order to detect and mitigate hardware faults which also applies to fault introduced by the malicious usage of the DVFS. Both solutions are interesting but require adding an integrated circuit to the SoC. These and other possible countermeasures are further discussed in Chapter 2. In this work we target very recent commercial devices, that do not encompass any additional hardware for fault injection mitigation.

In related works, when maliciously manipulating energy management mechanisms, it is necessary to have high precision to target specific instruction in the victim task when introducing faults. In Chapter 2, we explore the possibilities of a malicious manipulation of DVFS mechanisms on recent commercial devices under realistic conditions. Contrary to these previous works, our goal is not to steal secret information on the device but to take control and make every device service and data inaccessible.

### **1.3** Temperature managers

Same as energy management, temperature management has become a necessity to regulate the heat inside modern chips in order to ensure its functional stability [26] and manage aging issues [11],[12]. This phenomenon is even more true for advanced 3D stacking technologies [10]. Thus, maintaining a safe operating temperature is crucial for long-term functioning SoC.

Usually, temperature managers are implemented using active hardware (*e.g.*, fans). However, with continuous increase in-chip density and heat generation, these previous solutions are not enough to keep high performing devices from overheating. Moreover, on embedded systems that prioritize portability (*e.g.*, smartphones and IoT), active cooling cannot be used. Thus, these devices have to rely on other solutions such as passive cooling(*e.g.*, radiators). In this case, the SoC itself monitors its own temperature and provides automatic thermal throttling mechanisms to stay in stable conditions.

In general, modern chip contains multiple thermal sensors (e.g.), one sensor per core) to keep track of its internal temperature. When a temperature is higher than the max allowed temperature (junction temperature), the operating frequency is decreased to stay

within thermal constraints. Mechanisms like DVFS previously introduced are used for this purpose, thus along with frequency, the voltage is also reduced. If the junction temperature is exceeded by a certain amount, a more aggressive throttling (typically to the minimum supported frequency) is performed in order to quickly reduce the chip temperature. This is commonly referred to as a critical temperature event.

Beyond the junction temperature, each core is fused with a catastrophic trip temperature on its hardware. When the temperature exceeds this fused limit, the SoC will immediately signals to the device that an immediate hardware shutdown (without OS intervention) should be performed. A dedicated asynchronous hardware is responsible for this part and has priority over all other tasks. This mechanism is also intended to function in all conditions even if other failures occur.

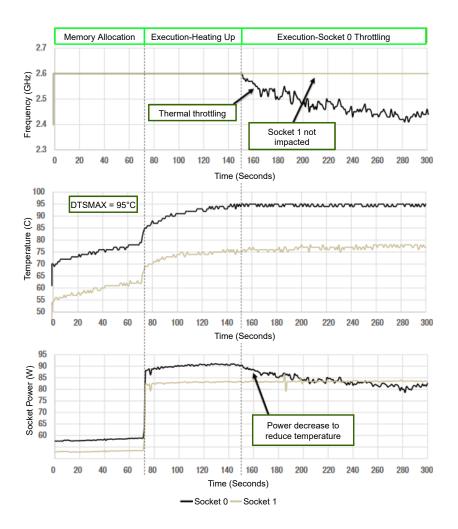

An example of thermal throttling is given in [27], Figure 1.7 shows the results of their experiments. Core 0 (also called Socket 0 in the figure) is pushed to its limit using heavy load application. The thermal throttling begins when the junction temperature reach 95°C is reached. At this point, the frequency and power are decreased to keep the temperature below its critical level. It is also possible to see that frequency keep fluctuating (up and down) as a way to keep the temperature stable while the core is still running at a the highest frequency. On the other hand, the Socket 1 has a stable frequency and power consumption as temperature never reaches the junction value for this core.

### **1.4** Temperature related vulnerabilities

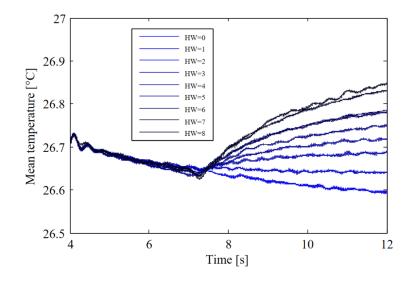

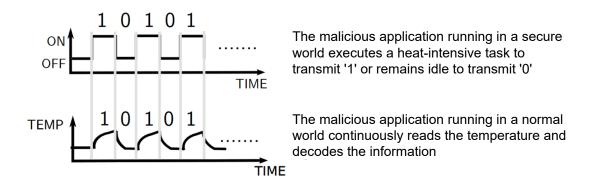

Attacks based on temperature are rarer compared to power-based attacks. The temperature can always be used to cause faults by overheating and executing DFA strategy. However, only few works focused on extracting information by measuring the temperature. In [28], authors showed through experimentation they were only able to distinguish between the Hamming Weight (HW) of the operands manipulated by a 'mov' and an external sensor was used to measure the temperature. Their results are shown in Figure 1.8, it is possible to easily distinguish between 7 of the HWs from the temperature measurements and only the HW of 5 and 6 overlap with each other making it hard to distinguish between them. On other hand, in [6], the authors used the temperature to create a covert channel and transmit information from one "core running" in the TEE to another core in the normal world as seen in Figure 1.9. This type of attack requires the secure core to already be infected by a malicious application, this application execute an

Figure 1.7 – Thermal throttling for core 0, frequency and power are decreased to keep temperature from going beyond junction temperature at 95°C. Results of this figure were presented in [27]

intensive task to raise the temperature to transmit a '1' or stay idle for the temperature to drop to transmit a '0'. Meanwhile, the application running on the normal world uses sensors to monitor the emitted heat and decode the transmitted information by analyzing the changes in temperature.

Figure 1.8 – Different heat generated depending on the HW of the operand during the operation 'mov' [28]

Figure 1.9 – Transmitting data from one "secure" core to another "normal" core using intensive processing to raise the temperature [6]

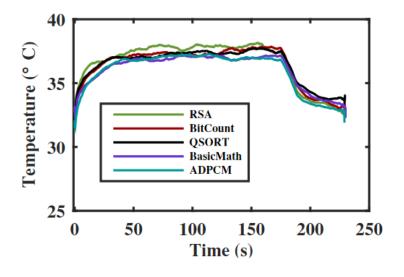

In the same work [6], it has also been proven that it is possible to use temperature to differentiate between some applications running in a cloud as can be seen in Figure 1.10. In fact, different applications will cause the processor to emit a different amount of heat depending on the instructions and operands. Within the cloud server where the same processor is shared between different users, an attacker can use the integrated temperature

sensors to spy on the activity of another user (the victim) using the same processor. This work do not extract any secret information. However, it can be used to affect the privacy of different users in the cloud.

Figure 1.10 - Profiling the type of application the user is running based on the temperature measurements. This figure is one of results that were presented in [6]

In [29], authors were able to measure the temperature of the SoC without any sensor by using DRAM memory. Authors showed that by deactivating memory refresh there is a correlation between bit flips in memory and the temperature. Same as before, the application of this attack is more focused on the privacy of users as those measurements were used to read the ambient temperature of the room where an IoT device is located. Depending on the variation of the temperature, it was possible to infer whether a person were present in the room where the device is located and detect event like entering and exiting the room.

For these works, the obtained results mainly focused on people privacy and behavior analysis, but they did not extract any critical information from within the device.

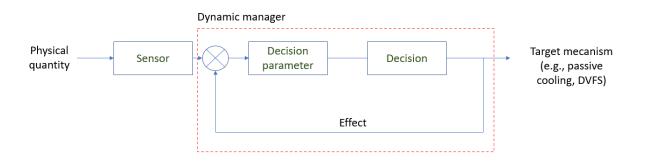

### **1.5** Integrated Sensors and hardware counters

As seen in the two previous sections, both temperature and power managers work in a closed loop as shown in Figure.1.11. Constant feedback is required from the hardware part to make the adequate decision and then ensure that the decision is correctly implemented.

Different sources of feedback are usually used but the most popular and straightforward are embedded sensors. The most used sensors are:

- Thermal sensors used to monitor the temperature of the chip to make sure it does not reach junction temperature. Those sensors are found within every device as they are crucial to ensure its operation. Usually, sensors are implemented within every core and important components such as DRAM and GPU. They also require a response time of a few µs to allow the managers to respond within appropriate time.

- Current and voltage sensors are also used often in embedded system. However, compared to thermal sensor, they are rare as they are not as crucial. They are used to improve the response of the energy manager, for example, Odroid Xu3 uses voltage sensor to monitor the energy consumption of each core. Moreover, in the smartphone industry, voltage sensors are used in almost every device to keep track of the battery level.

Figure 1.11 – Dynamic manager functions as an autonomous closed loop. The decision is made based on the sensor's measurement, the CPU switch to a new state and the manager keeps monitoring ensuring the desired state is reached

The choice of feedback depends on the manufacturer and the mechanism they implement. For example, Intel Running Average Power Limit (RAPL) [30] mechanism is a closed loop mechanism that keeps the CPU within desired thermal and power constraints. By design, the mechanism is similar as it modifies the voltage and the frequency. Moreover, it includes power-measurement feedback by estimating the energy consumption in the core using hardware counters. Main CPU manufacturers (*e.g.*, AMD, ARM) have similar mechanisms, either through sensors or hardware counters to estimate the power consumption. Those sensors provide crucial information on the current state of the SoCs, this information is available through 3rd party software such as energy and temperature aware applications. However, this information can be maliciously used to extract information. It was already shown and will be discussed in the next chapter, that energy consumption is correlated to instructions and operands manipulated during the execution of victim programs, making extraction of information possible (*e.g.*, encryption keys).

## 1.6 Power analysis based attacks

Using power consumption to extract secrets from a device is not a new practice, as presented previously in Section 1.2, Power Analysis based attack is a well-established field among SCA and different types of attacks were proposed. Those attacks are built upon the observation that the power consumption of CMOS digital circuits is data dependent by design. On any integrated circuit, a bit flip is represented by one or more voltage transitions from low to high (or vice versa). Different data values and operations typically entail different numbers of bit flips and therefore produce very different power traces. In previous work [31], it was proved that the power generated by the transistors switching from one level to another is more important than the passive consumption. Additionally, the power variation observed is correlated to execute operations and manipulated operands. Therefore, any circuit not designed to be resistant to power attacks has a datadependent power consumption. However, if the circuit has a high complexity circuit or if an attacker's sampling rate is limited, it becomes harder to extract information from a single power trace. Thus, it becomes important to use more analysis techniques such statistical techniques such as Differential Power Analysis (DPA) [31] and Correlation Power Analysis (CPA) [32] across multiple power traces.

In Simple Power Analysis (SPA) attacks [31], the secret key is inferred by analysing the power consumption differences during an operation (*e.g.*, SBox in AES encryption). This attack consists of studying the detectable spike in power consumption as bits in the key will have a different impact depending on their values. In this case, only a small number of traces are required to infer the key. However, this approach is only possible if the secret has a significant impact on the power consumption of the device, and the traces are relatively noise-free. Noise can be averaged by computing the mean of the multiple collected traces.

DPA attacks [31] are based on a more complex approach and consists on statistical

analysing a larger number of traces with varying input data. This attack study the power consumption at fixed instants and how it is a function of the secret data being processed. In this case, smaller and less secret-dependent power variation can be detected even in the presence of noise compared to SPA. However, DPA is also limited within noisy environment, it can be still used to recover parts of the secret key, but it becomes harder to recover the whole key. However, CPA [32] which is an extension of DPA, provides a more accurate analysis. As it correlates the variations in the set of traces and a leakage model depending on the characteristics of intermediate values.

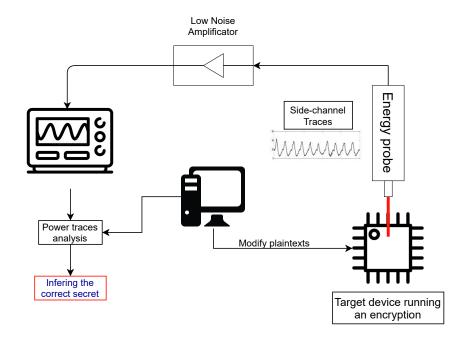

The usual setup for this type of attacks is shown in Figure 1.12. Most often external power measuring tools are used to provide enough accuracy for this type of attacks, these tools requires a physical access to the target device. Especially with the different countermeasures implemented to reduce the power footprint of key-dependent instruction and the electronics to smooth power traces. However, with the introduction of sensors for energy managers, it was proven that state-of-art sensors have enough precision to use power analysis attack. Allowing to run those attacks remotely. Different works have already shown the feasibility of such attacks.

Figure 1.12 – The different steps and tools necessary to execute a classical power based attack

## **1.6.1** Power Analysis Attacks using embedded sensors

Using sensors integrated in modern SoC is not a new practice, and it has been previously exploited to extract different information depending on the used sensor. The most popular target is power sensors as they are more precise and easier to use compared to other sensors (*e.g.*, temperature sensor). In [33], authors were able to distinguish between different RSA keys by measuring the system power consumption using the integrated power sensors. It was proven that depending on the HW of the secret key the power consumption measured is different, however no full key were recovered or other characteristics beyond the HW.

In a more recent work [34], the authors went even further and were able to recover secret keys of different encryption algorithms. In this case, the main target was an Intel processor, and they were able to use RAPL [30]. RAPL provides an approximate average measurement for a period of time thus making the observable effect of the secret-dependent power variation small. However, with enough measurements, they were able to successfully recover the AES secret key in around 10 days using CPA. On the other hand, to recover RSA keys, another technique was used to measure more accurately specific part of the encryption. SGXSTEP [8] is a technique that allows the attacker to control the flow of the target program by re-executing instructions or pausing between each instruction. This can be achieved by using well timed interruption and it was possible to isolate specific instructions. Thus, instead of measuring the average power consumption of the whole RSA decryption, the authors were able to measure the effect of each bit of the private key on the power keys. Moreover, these attacks can be combined with other types of analysis such as Template Attacks or Deep Learning based attacks.

#### **1.6.2** Template attacks

Another form of SCA that focus on extracting information from power consumption of a SoC is template attacks. It aims at creating a profile for a target device. In other word, the attacker models the variation of power consumption depending on the secret and uses it later to recover the secret. In this case, the attacker needs a copy of the target device and have full control over it. However, this attack requires a lot of traces to create the profile but once the profile is created, it is viable for most of the devices with the same processor model.

There are 3 main steps for a template attack:

- Creating a template of the device. This part consists of measuring the power for different values of a known secret. For example, in the case of AES, the power is measured for different values of a subkey.

- Measuring the power consumption on the victim device. In this case, the secret is not known, but it is possible to measure the power consumption during an encryption.

Only a limited numbers of measurements are required.

- Using the template to infer the secret. By using the measurement on the victim device, it is possible to compute using the previous template the most probably value of the secret key.

This attack requires a more complex setup compared to DPA and CPA. However, the number of traces required during the attack are lower as long as the template is already established. Moreover, the noise is no more an obstacle as templates are created by analyzing the variation of power and models the noise distribution using a Gaussian distribution. The main drawback in this case, the important number of power traces required for the characterization and the creation of the template. For example, in the case of an AES128, each byte secret key is inferred separately, thus, it is necessary to have at least 256 different measurements (1 for each possible value of the byte) for each template. Moreover, a total of 16 templates are required (1 for each byte of the secret key). The number of measurements can be reduced by inferring the HW of the byte instead of its value as there is only 9 possibles values instead of 256.

#### **1.6.3** Profiling attack with machine learning

Another type of profiling attacks which has gained a lot of popularity is deep learningbased side-channel attacks. This type of attacks are similar to the template attacks as they require to create a profile of the target device for each secret. Moreover, deep learningbased attacks offer several types of analysis, depending on the use cases, different type of machine learning algorithms can be used.

- Unsupervised learning techniques such as clustering (e.g., K-means) and dimensional reduction [35],[36](e.g., principal component analysis) were used to perform either key recovery

- ML was also used to filter power traces [37],[38] and reduce the noise. In this case, the key is not directly guessed but it reduces the number of traces needed for CPA and DPA

- Supervised learning techniques such as support vector machines, self-organizing maps, random forests and different types of artificial neural networks were successful in recovering the key [39],[40],[41],[42],[43],[44] not only from unprotected, but also from protected implementations of cryptographic algorithms.

- Multilayer perceptron and convolutional neuronal networks were also used to recover secret key [45],[46],[47], they also outperform template attacks on noisy traces.

These methods rely on creating a model by either training neuronal networks to recover a key characteristic (*e.g.*, subkey, HW) or by having a dataset large enough for unsupervised algorithms. This is not a problem for power-based attack as multiple public datasets are available such as DPAContest. These datasets have already been used by different works to prove their implementation.

## 1.7 Conclusion

In the literature, there are different types of physical attacks, some requires physical access, some are even invasive and cause permanent damage to the target devices. However, in this chapter, we only focus on attacks that has the following characteristics.

- Maliciously uses dynamic manages.

- Maliciously uses embedded sensors.

- No additional hardware or physical access was necessary for the attacks.

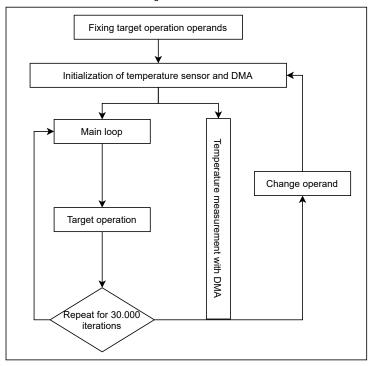

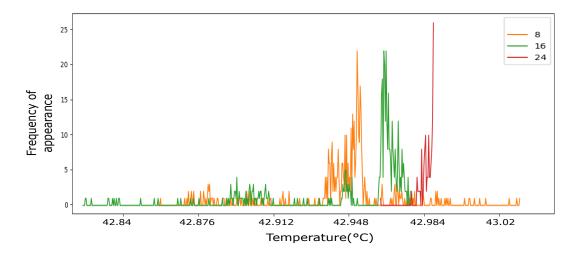

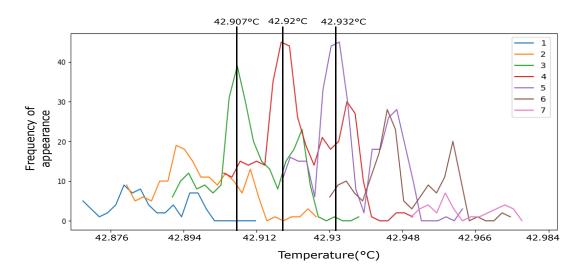

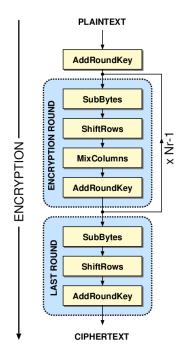

- Possible usage of ML.