# Security at the Hardware/Software Interface Guillaume Hiet

#### ▶ To cite this version:

Guillaume Hiet. Security at the Hardware/Software Interface. Cryptography and Security [cs.CR]. Université de Rennes 1, 2021. tel-03511334

# HAL Id: tel-03511334 https://hal.science/tel-03511334

Submitted on 6 Jan 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Université de Rennes 1 Spécialité Informatique

# Security at the Hardware/Software Interface

Habilitation à Diriger des Recherches

Guillaume Hiet

# Contents

| A        | crony                            | rms                                                     | 3                |

|----------|----------------------------------|---------------------------------------------------------|------------------|

| 1        | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | Oduction  Context                                       | 7<br>7<br>9<br>9 |

| <b>2</b> | Har                              | dware-assisted intrusion detection                      | 10               |

| _        | 2.1                              |                                                         | 10               |

|          |                                  | 2.1.1 Hardware-based security mechanisms                | 10               |

|          |                                  | 2.1.2 Coprocessor-based intrusion detection             | 11               |

|          |                                  | 2.1.3 Our contributions                                 | 12               |

|          | 2.2                              | Detecting intrusions against the SMM                    | 13               |

|          | 2.2                              | 2.2.1 Introduction to SMM monitoring                    | 13               |

|          |                                  | 2.2.2 SMM intrusion detection approach                  | 14               |

|          |                                  | 2.2.3 Evaluation and results                            | 19               |

|          |                                  | 2.2.4 Conclusion                                        | 21               |

|          | 2.3                              | Hardware-assisted Information Flow Tracking             | 22               |

|          |                                  | 2.3.1 Introduction to Dynamic Information Flow Tracking | 22               |

|          |                                  | 2.3.2 HardBlare: a hardware/software codesign for DIFT  | $\frac{1}{24}$   |

|          |                                  | 2.3.3 Evaluation and results                            | 32               |

|          |                                  | 2.3.4 Conclusion                                        | 34               |

|          | 2.4                              | Perspectives                                            | 35               |

|          |                                  |                                                         |                  |

| 3        | Hos                              | t-based intrusion survivability                         | 37               |

|          | 3.1                              | Introduction to OS-based intrusion survivability        | 37               |

|          |                                  | 3.1.1 Intrusion recovery and response                   | 38               |

|          |                                  | 3.1.2 Intrusion survivability                           | 38               |

|          |                                  | 3.1.3 Our contribution                                  | 39               |

|          | 3.2                              | Intrusion survivability approach at the OS-level        | 39               |

|          |                                  | 3.2.1 General overview of our approach                  | 39               |

|          |                                  | 3.2.2 Response selection                                | 41               |

|          |                                  | 3.2.3 Optimal response selection                        | 46               |

|          | 3.3                              | Evaluation and results                                  | 48               |

|          |                                  | 3.3.1 Implementation                                    | 48               |

|          |                                  | 3.3.2 Security evaluation                               | 49               |

|          |                                  | 3.3.3 Performance evaluation                            | 50               |

|   | 3.4  | Conclu  | asion and perspectives                                            | 52         |

|---|------|---------|-------------------------------------------------------------------|------------|

| 4 | For  | mal sp  | ecification and verification of hardware-assisted security mecha- |            |

|   | nisn | ns      |                                                                   | 54         |

|   | 4.1  | Introdu | uction to formal specification of hardware-assisted mechanisms    | 54         |

|   |      | 4.1.1   | Hardware-based Security Enforcement Mechanisms                    | 57         |

|   |      | 4.1.2   | Using formal methods to reason about HSE mechanisms               | 58         |

|   |      | 4.1.3   | Our contribution                                                  | 59         |

|   | 4.2  | A form  | nal model to specify HSE mechanisms                               | 59         |

|   |      | 4.2.1   | Hardware model and HSE mechanisms                                 | 59         |

|   |      | 4.2.2   | Security policy                                                   | 63         |

|   |      | 4.2.3   | Code injection policy                                             | 64         |

|   | 4.3  | A mini  | imal x86 hardware model                                           | 65         |

|   |      | 4.3.1   | Model scope                                                       | 65         |

|   |      | 4.3.2   | Tracking memory ownership                                         | 66         |

|   |      | 4.3.3   | Hardware states                                                   | 67         |

|   |      | 4.3.4   | Transitions                                                       | 68         |

|   | 4.4  | -       | ying and verifying a BIOS HSE mechanism                           | 70         |

|   | 1.1  | 4.4.1   | Requirements over states                                          | 71         |

|   |      | 4.4.2   | Requirements over transitions                                     | 71         |

|   |      | 4.4.3   | Verifying HSE laws                                                | 72         |

|   |      | 4.4.4   | Proving the correctness of the BIOS HSE mechanism                 | 72         |

|   | 4.5  |         | ision and perspectives                                            | 72         |

|   | 4.0  | Concid  | ision and perspectives                                            | 12         |

| 5 | Con  | clusior | and perspectives                                                  | <b>7</b> 5 |

# Acronyms

| AXI         | Advanced eXtensible Interface. 31, 34                                                                                   |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIOS        | Basic Input/Output System. 13, 14, 18, 20, 39, 53, 57, 59, 65, 66, 70–73                                                |  |  |  |  |

| BRAM        | Block RAM. 34                                                                                                           |  |  |  |  |

| C&C         | Command and Control. 43, 49, 50                                                                                         |  |  |  |  |

| CDI         | Control-Data Isolation. 52                                                                                              |  |  |  |  |

| CFI         | Control-Flow Integrity. 12, 16, 19–21, 35, 74                                                                           |  |  |  |  |

| COW         | Copy-On-Write. 48                                                                                                       |  |  |  |  |

| CPU         | Central Processing Unit. 11, 13–15, 18, 19, 21, 23–26, 28, 34, 36, 49, 54–56, 59, 60, 64–67, 69, 71, 74                 |  |  |  |  |

| CSME        | Converged Security and Management Engine. 11                                                                            |  |  |  |  |

| CTI         | Cyber Threat Intelligence. 41, 42, 46                                                                                   |  |  |  |  |

|             |                                                                                                                         |  |  |  |  |

| DBI         | Dynamic Binary Instrumentation. 52, 53, 77                                                                              |  |  |  |  |

| DDoS        | Distributed Denial-of-Service. 49                                                                                       |  |  |  |  |

| DFI         | Data-Flow Integrity. 35                                                                                                 |  |  |  |  |

| DIFT        | Dynamic Information Flow Tracking. 12, 22–28, 32–36, 74, 77                                                             |  |  |  |  |

|             | . –,                                                                                                                    |  |  |  |  |

| DMA         | Direct Memory Access. 55, 60                                                                                            |  |  |  |  |

| DMA<br>DRAM |                                                                                                                         |  |  |  |  |

|             | Direct Memory Access. 55, 60<br>Dynamic Random Access Memory. 18, 29, 54–56, 66–69,                                     |  |  |  |  |

| DRAM        | Direct Memory Access. 55, 60<br>Dynamic Random Access Memory. 18, 29, 54–56, 66–69, 71                                  |  |  |  |  |

| DRAM<br>DRM | Direct Memory Access. 55, 60<br>Dynamic Random Access Memory. 18, 29, 54–56, 66–69, 71<br>Digital Rights Management. 11 |  |  |  |  |

| DRAM<br>DRM | Direct Memory Access. 55, 60<br>Dynamic Random Access Memory. 18, 29, 54–56, 66–69, 71<br>Digital Rights Management. 11 |  |  |  |  |

FIFO First In First Out. 15, 20, 21, 26, 28, 31, 33

FP Frame Pointer. 32

FPGA Field-Programmable Gate Array. 10, 25–27, 31, 34–36,

58, 74

GPIO General Purpose Input/Output. 55

GPU Graphics Processing Unit. 36, 54

HDL Hardware Description Language. 36, 58, 74

HIDS Host-based Intrusion Detection System. 10

HLS High Level Synthesis. 36

HSE Hardware-based Security Enforcement. 57, 59–66, 70–74

HTTP Hypertext Transfer Protocol. 50, 51

IDMEF Intrusion Detection Message Exchange Format. 41

IDS Intrusion Detection System. 10, 37, 40, 41, 43, 46, 76

IR Intermediate Representation. 19

ISA Instruction Set Architecture. 10

JIT just-in-time. 76, 77

LSM Linux Security Module. 32

LTS Labeled Transition System. 59

MAC Mandatory Access Control. 40

MAEC Malware Attribute Enumeration and Characterization.

41, 43, 45

MMU Memory Management Unit. 56

MOO Multi-Objective Optimization. 46, 47

MSSP Managed Security Service Provider. 37

MTRR Memory Type Range Registers. 56

OS Operating System. 9, 11–13, 22, 24, 26, 29, 32, 38, 39,

41, 48, 53, 56, 57, 60, 64–67, 70–72, 76

P2P Peer-to-peer. 49

PAT Page Attribute Table. 56

PC Program Counter. 28, 29, 31

PCH Platform Controller Hub. 54, 56, 73

PCI Peripheral Component Interconnect. 56

PFT Program Flow Trace. 28, 33

PID Process IDentifier. 28

PL Programmable Logic. 25, 28

PS Processor System. 25

PSP Platform Security Processor. 11, 14

PTM Program Trace Macrocell. 26–29, 35

QPI QuickPath Interconnect. 15, 19

ROM Read-Only Memory. 55

ROP Return-Oriented Programming. 16

SEP Secure Enclave Processor. 11

SGX Software Guard Extensions. 11

SIEM Security Information and Event Manager. 37

SMBASE SMRAM Base address. 13, 18, 20, 21, 67, 71, 72

SMI System Management Interrupt. 13, 18–21, 69, 70

SMM System Management Mode. 13–22, 53, 57, 61, 65–72

SMRAM System Management RAM. 13, 16, 18–20, 65, 66, 68, 69,

71, 72

SMRAMC System Management RAM Control. 66, 68, 69, 71, 72

SMRR System Management Range Register. 66–69, 71, 72

SOAR Security Orchestration, Automation, and Response. 37

SOC Security Operations Center. 37

SoC System on a Chip. 25, 28, 33

SOO Single-Objective Optimization. 47

SP Stack Pointer. 32

SSD Solid-State Drive. 54

STIX Structured Threat Information expression. 41, 46

TCB Trusted Computing Base. 29, 61

TEE Trusted Execution Environment. 11

TLB Translation Lookaside Buffer. 56

TMC Tag Management Core. 27, 34

TOLUD Top of Low Usable DRAM. 56

TPIU Trace Port Interface Unit. 28

TPM Trusted Platform Module. 11, 13

TXT Trusted Execution Technology. 11, 57

UEFI Unified Extensible Firmware Interface. 7, 13, 14, 39, 53,

57

UIO Userspace I/O. 31

VM Virtual Machine. 57

WCET Worst Case Execution Time. 35

# Chapter 1

# Introduction

This document gives a synthetic overview of my research activities in the CIDRE team of the IRISA laboratory since October 2010. After completing my Ph.D. in 2008 on policy-based intrusion detection, I worked for Amossys as a security expert. In October 2010, I joined CentraleSupélec as an Assistant Professor. Since then, I have pursued my research works on cybersecurity.

In the last few years, my research has been mainly focused on Host-based Intrusion Detection Systems. I became more and more interested in the security of software close to hardware, such as operating systems or UEFI (Unified Extensible Firmware Interface) firmware, and I proposed detection approaches specifically targeting these systems. This evolution led me to be interested in the security of interfaces between software and hardware in a more general way. I was in secondment at Inria from 2018 to 2019 (partial time) and then from 2019 to 2020 (full time) to develop my research project in that domain.

### 1.1 Context

Software security is still one of the main concerns of today's systems, although much research has been done on the subject. Indeed, many vulnerabilities still affect computer systems, which are increasingly targeted by a wide range of sophisticated attacks. These attacks are strongly connected to the underground economy and military/intelligence activities. They can combine different malicious behaviors, exploiting vulnerabilities at different levels, e.g., hijacking the control flow of a program by exploiting a buffer overflow or accessing some restricted part of the file system by exploiting a directory traversal.

Cybersecurity consists of ensuring the fundamental properties of data confidentiality (only legitimate users can read information), data integrity (only legitimate users can modify information), and data availability (legitimate access to data cannot be prevented or disturbed). These properties are defined by a security policy that some protection mechanisms must enforce (e.g., authentication and access control, cryptography, anti-virus, etc.).

The best strategy to secure embedded systems would be to avoid vulnerabilities. Indeed, many preventive approaches have been proposed, such as static analysis of software code, dynamic verification enforced by the runtime environment (e.g., the Android Virtual Machine), or the use of cryptographic mechanisms. In practice, however:

- Preventive approaches are not systematically used (e.g., a lot of Android applications are still using C code, which is not protected by the Android Virtual Machine runtime verification);

- These approaches are insufficient to prevent all attacks (e.g., using Java or OCaml does not prevent all the logical errors that could lead to potential vulnerabilities).

It is thus also essential to monitor systems to **detect intrusions at runtime**. However, detecting attacks or intrusions is just the first step of reactive security. Different **reactions** must be implemented, such as notifying security incidents to administrators, stopping or modifying the execution of systems under attack, or putting the computer system in quarantine. Moreover, the addition of new security mechanisms raises the question of the confidence we can have in these mechanisms. In this context, **formal specification and proof** can enhance the trust in such security mechanisms.

In my research, I mainly focus on the security of hardware platforms. Such platforms consist of all the hardware and the low-level software components (operating system, hypervisor, firmware) that enable the execution of user applications. Even if it is essential to implement security mechanisms at the network level to protect the data that passes through it and the network itself, it is also fundamental to secure the platforms that ultimately allow executing applications and storing data. Moreover, these platforms are not always connected to a network.

In this work, we only consider software attacks in which the attacker provides the system with data or malicious code to exploit a vulnerability present on a hardware platform. This type of attack differs from physical attacks (e.g., fault injection or side-channel attacks) that require externally measuring or influencing a physical quantity (e.g., current or electromagnetic field). In contrast to the latter, software attacks can be executed at a significant distance from the targeted device, even if they exploit vulnerabilities in low-level components. This type of attack requires paying attention to the interactions between software and hardware.

The evolution of my research field led me to take a more general interest in the security of interfaces between software and hardware. In this perspective, I proposed, with my colleagues Clémentine Maurice (CNRS, IRISA EMSEC), Frédéric Tronel (CentraleSupélec, IRISA CIDRE), Jean-Louis Lanet (Inria, IRISA CIDRE) and Ronan Lashermes (Inria), a project for a Thematic Semester on the Security of Software/Hardware Interfaces (SILM), which has been selected by the partners of the PEC (Pôle d'Excellence Cyber) research centre. Such a semester was funded by the DGA and managed by Inria.

As the chair-holder of the SILM thematic semester<sup>1</sup>, I organized various events and invited many researchers from academia, industry, and governmental organizations working in this field. I also wrote a white paper for the DGA (the French Defence Procurement Agency), outlining the state of the art of the domain and the strategic axes to be developed, both from a scientific and industrial point of view. During this semester, I was in partial secondment (50%) at Inria from October 2019 to October 2020.

<sup>1</sup>https://silm.inria.fr/

# 1.2 Challenges

The research I detail in this manuscript focuses on computer security at the software/hardware interface, focusing on intrusion detection and reaction. More precisely, I am interested in finding solutions to respond to the following challenges:

- 1. How to leverage hardware features to isolate HIDS and bridge the semantic gap resulting from the isolation?

- 2. How to automatically react to intrusions at the host level?

- 3. Using formal methods, how to specify and verify security mechanisms that require interactions between software and hardware?

## 1.3 Other contributions in security monitoring

I have also conducted researches in various security monitoring fields, which I do not detail in this manuscript. Thus, I co-advised the Ph.D. thesis of Georges Bossert with Ludovic Mé from CentraleSupélec and Frédéric Guihéry from AMOSSYS. In this project, we worked on the reverse engineering of communication protocols. Indeed, for intrusion detection purposes, it is often necessary to analyze network flows whose protocols are proprietary or whose specification is not public (for example, protocols used in botnets). This work was published at the ACM AsiaCCS 2014 conference [21].

Today, many attacks target the web browser and, more particularly, the JavaScript language. In the SecCloud project, funded by the Labex CominLabs, we proposed a DIFT approach implemented within the web browser with my Ph.D. student Deepak Subramanian. I co-advised Deepak with my colleague Christophe Bidan, and we published our results in FPS 2016 [18] and ACM SIN 2016 [19] conferences. The latter publication won the best paper award.

From 2015 to 2018, I also co-advised the Ph.D. thesis of Oualid Koucham in collaboration with Jean-Marc Thiriet and Stéphane Mocanu, from GIPSA-Lab in Grenoble, and Frédéric Majorczyk from the Direction Générale de l'Armement. We proposed intrusion detection and alert correlation approaches for industrial control systems. This work has been published in the NordSec 2016 [16] and SafeProcess 2018 [8] conferences.

# 1.4 Organisation of the manuscript

This manuscript highlights the main results of my research on the security of software/hardware interfaces since 2010. Chapter 2 presents our different contributions in the field of hardware-assisted intrusion detection. We detail the different approaches we proposed to isolate the monitor and solve the semantic gap resulting from this isolation. Chapter 3 focuses on the step following the detection, i.e., attack reaction, and gives an overview of our work on intrusion survivability at the OS (Operating System) level. Chapter 4 describes our effort in formalizing hardware-based security mechanisms. Finally, Chapter 5 concludes this manuscript and gives future directions I would like to explore.

# Chapter 2

# Hardware-assisted intrusion detection

#### 2.1 Introduction to hardware-assisted intrusion detection

Intrusion detection approaches can be split into two different categories. Misuse-based approaches, commonly used in the IDS (Intrusion Detection System) available on the market, define the malicious behavior using attack signatures. Such approaches are only effective in detecting attacks that are publicly known at the time of signature definition. It is, therefore, necessary to regularly update these signatures, and new attacks, exploiting so-called zero-day vulnerabilities, can remain undetected. I am focusing my research on the second category, i.e., anomaly detection. Such approaches rely on the definition of legal behavior and consider any significant deviation from this behavior as intrusions.

The use of intrusion detection systems directly located on monitored machines, i.e., HIDS (Host-based Intrusion Detection System), poses several challenges:

- These approaches can be costly in terms of execution time, which can penalize the performance of programs running on the monitored system;

- The intrusion detector is located on the monitored target and must also protect itself from attacks initiated from a compromised target.

My current research aims at addressing these challenges by taking advantage of dedicated hardware components. Using a dedicated coprocessor allows for offloading the detection computation from the target processor. Moreover, placing the IDS in an isolated hardware component protects it from software attacks executed on the target processor.

## 2.1.1 Hardware-based security mechanisms

Several academic works have focused on using hardware support to detect or prevent software attacks. Some approaches rely on the existing mechanisms of the processors available on the market, e.g., virtualization extensions or existing enclave mechanisms. Other approaches propose new hardware features, e.g., ISA (Instruction Set Architecture) extensions or security coprocessors. Such approaches cannot be validated on existing processors but require implementations on FPGA (Field-Programmable Gate Array) or simulations. Zhao et al. provide a survey of these different hardware-based security mechanisms, the properties they guarantee, and the vulnerabilities that affect them [Zha+19].

The advantages of hardware-based solutions compared to purely software-based approaches are multiple:

- hardware features cannot be modified, which makes them more robust against software attacks;

- they offer better efficiency of execution time and energy consumption;

- the security mechanisms expose a reduced and controlled interface, which allows better protection of data and code.

Historically, processors have implemented mechanisms to isolate different user applications and the OS kernel. Many processors also provide hardware extensions to isolate different virtual machines and the hypervisor that controls them. These mechanisms rely on a vertical trust hierarchy: isolation between components located in the same level is implemented and controlled by a component located in a lower level, which must be trusted. This approach requires trusting the low-level software components, such as OSes or hypervisors. Some work also proposed enclave mechanisms to isolate the critical parts of an application without trusting these low-level components.

Some work also proposed enclave mechanisms to isolate the critical parts of an application without trusting the low-level components. Such approaches can rely on pre-existing processor features, such as Intel TXT (Trusted Execution Technology) [McC+08] or virtualization extensions [RR18]. Other projects have proposed modifying the architecture of the processors to implement dedicated mechanisms [Owu+13; Noo+13]. Hardware manufacturers also adopted these approaches to provide dedicated hardware features to implement enclaves in their processors, such as Intel SGX (Software Guard Extensions) [Cor] or ARM TrustZone [Lim].

However, such approaches execute the isolated software component within the platform processor. They rely on isolation mechanisms provided by the processor but the trusted and isolated software share hardware resources, e.g., CPU (Central Processing Unit) cores, caches, RAM, and peripherals. This sharing of hardware resources makes them, in general, vulnerable to side-channel attacks [Wan+17; Cho+18; Sch+20]. In addition, they may be vulnerable to a defect in the isolation mechanism [She; 19a].

## 2.1.2 Coprocessor-based intrusion detection

Some approaches have proposed using a dedicated processor, physically separated from the main processor of the platform, to strengthen the isolation of security mechanisms. Historically, IBM was one of the first manufacturers to follow this approach with the IBM 4758 processor [Dye+01]. The goal was to provide a TEE (Trusted Execution Environment) to run secure applications. In addition, IBM researchers proposed using this coprocessor to implement a monitoring service for applications running on the main processor to detect possible intrusions [Zha+02a].

Nowadays, various processor or motherboard manufacturers integrate such coprocessors into their platforms, e.g., AMD PSP (Platform Security Processor) [EB20], Intel CSME (Converged Security and Management Engine) [Cor20], Apple SEP (Secure Enclave Processor) [MSW], or HP SureStart [HP 19; ANS]. However, their intrusion detection capabilities are limited. They are mainly used to implement cryptographic primitives or DRM (Digital Rights Management), protect confidential data (e.g., cryptographic keys or biometric data), or implement a virtual TPM (Trusted Platform Module). Some of these coprocessors can provide services to verify the

integrity of the firmware [HP 19; ANS] or the hypervisor [BS08a]. Nevertheless, these different technologies are proprietary, and little public information is available about their internal design. Moreover, their implementation details have often been revealed thanks to reverse engineering efforts that exploit vulnerabilities [EB20; FO18; GE19]. In addition, they essentially allow the implementation of security services provided by the platform designer.

Some research works have also focused on using an isolated coprocessor to monitor applications running on the main processor, including the OS and the hypervisor [Zha+02a; Pet+04a; Pet+06a; WSG10]. Such snapshot-based approaches regularly inspect the content of the system memory. However, they are vulnerable to transient attacks, which attack the monitored system and then clean up their trace between two memory acquisitions. The inability to detect transient attacks motivated researchers to develop event-driven approaches where the monitor observes events generated by the monitored system to detect intrusions [Moo+12a; Lee+13a; Lee+15b; Kor+16; Zho+21].

These different approaches focus on integrity checking. However, coprocessor-based intrusion detection can verify more complex security policies, such as DIFT (Dynamic Information Flow Tracking) [KDK09a; Lee+15a] or CFI (Control-Flow Integrity) [Tim+14; Lee+15c]. These approaches are an alternative to software-based approaches or verifications implemented inside the main processor. The use of hardware support allows to protect the detection mechanism and to speed up the processing. In addition, offsetting in an external processor has the advantage of not involving invasive modification of the main processor microarchitecture.

#### 2.1.3 Our contributions

By isolating the security monitor, the problem of the semantic gap arises [Jai+14; BAL15b]. The external processor has limited visibility into the status of the main processor. To bridge this gap, we have to extract the necessary information from the main processor and send it to the security coprocessor. This information depends on the implemented security policy.

We proposed different approaches to isolate intrusions detection monitors in dedicated coprocessors. More precisely, we explored different strategies to bridge the semantic gap resulting from the isolation of the monitor. We designed solutions that do not require any modification of existing processors, which could ease their adoption by manufacturers.

In the Ph.D. of Ronny Chevalier, we developed a coprocessor-based monitoring approach to detect intrusions against the runtime services of the BIOS. We rely on the static analysis of the BIOS to extract the legitimate behaviors of the monitored services, i.e., their control flow and some data invariants. Moreover, we instrument the code of the services to send information to the monitor at runtime and bridge the semantic gap. We detail this first contribution in Section 2.2.

In the HardBlare project, funded by the Labex CominLabs, we defined a coprocessor-based approach to monitor the execution of Linux applications. We implemented a DIFT monitor on the FPGA part of a ZYNQ SoC. We rely on a combination of different strategies to bridge the semantic gap. We use the ARM PTM trace mechanism available on the hardcore CPU of the ZYNQ SoC to send information about application control flows to the monitor implemented on the FPGA. The monitor combines those traces with annotations computed during the compilation of the application to track information flows. Section 2.3 presents this second contribution.

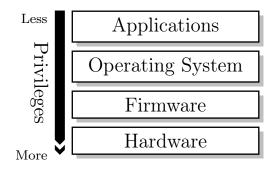

Figure 2.1: Computer abstraction layers

## 2.2 Detecting intrusions against the SMM

#### 2.2.1 Introduction to SMM monitoring

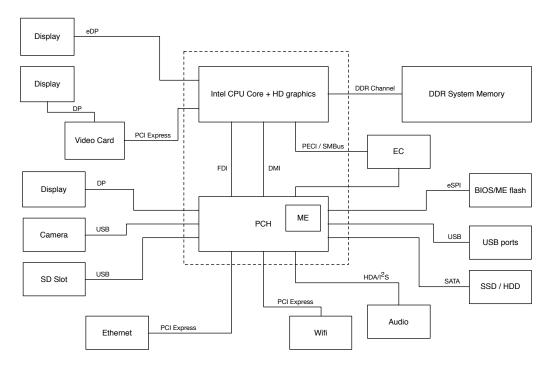

Firmware, such as UEFI boot firmware or BIOS (Basic Input/Output System), is one of the most privileged software components in the hardware platform, as illustrated by Figure 2.1. Indeed, it has direct access to hardware, is the first piece of software executed during the boot sequence, and is in charge of the initialization of the platform. Any alteration of the behavior of the firmware can have dramatic consequences for the integrity, confidentiality, or availability of the upper layers, i.e., the OS and applications. As a consequence, attackers are increasingly targeting such a privileged component [Lin13; Liv11; Gal13; Res18]. Indeed, classical anti-malware tools are not able to monitor the behavior of the firmware. Such malware can survive after a complete reinstallation of the OS and applications, even if the hard drive is changed.

The SMM (System Management Mode) is the most privileged execution mode on the x86 architecture, introduced by Intel in its 386SL processor. It allows the execution of privileged runtime services [ZRM10, Chapter 5] of the boot firmware, even after the boot sequence, during the execution of the OS [Int19d; YZZ14]. Such services can access a dedicated part of the memory called the SMRAM (System Management RAM), which is only accessible in SMM. The SMBASE (SMRAM Base address) register stores the base address of the SMRAM, and a dedicated interrupt called SMI (System Management Interrupt) switches the processor into SMM. Software code can also make the hardware trigger this interrupt. When receiving the interrupt, the CPU saves its context, switch to SMM, and executes code located at SMBASE + 0x8000. Leaving the SMM is done by executing a special-purpose instruction called rsm (for resume).

The SMM was initially not designed for security but for allowing the OS to delegate specific tasks to the firmware that are very dependent on the hardware configuration, such as power management. Indeed, the motherboard manufacturer is partially involved in the development of the boot firmware. However, this mode has, over time, acquired fundamental importance in the security of the hardware platform. It isolates the execution of some critical services, such as updating the firmware code or configuring the TPM. Indeed, only a service executed in SMM can unlock the flash memory containing the firmware code to modify its content.

Existing security mechanisms used to protect the boot firmware mainly consist in verifying its integrity at boot time using signed updates [Coo+11; Reg18], Intel Boot Guard [YZ], or TPM measurements [Tru11]. However, such approaches let the runtime services unprotected between two consecutive reboots. Those services are not exempt from vulnerabilities that attackers

can exploit to disable boot time protections and remain persistent [Ole16b; WT09; Ole16a; Baz+15; Bul+17; Puj16]. In particular, they are prone to memory corruption bugs [Cor13; Cor16; Len16a; Len16b] since they are developed using low-level languages, like C or assembly language.

Even if a vulnerability related to the SMM has been found, reported, and patched in the BIOS's source code, all affected platforms need to update their BIOS. In practice, however, the BIOS is not updated frequently [KK15]. Consequently, there is a need to protect privileged runtime services at runtime to prevent attackers from altering their legitimate behavior. In the following section, we present our contribution to runtime firmware intrusion detection.

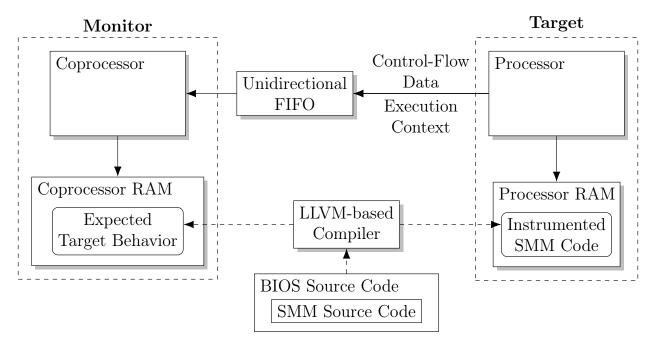

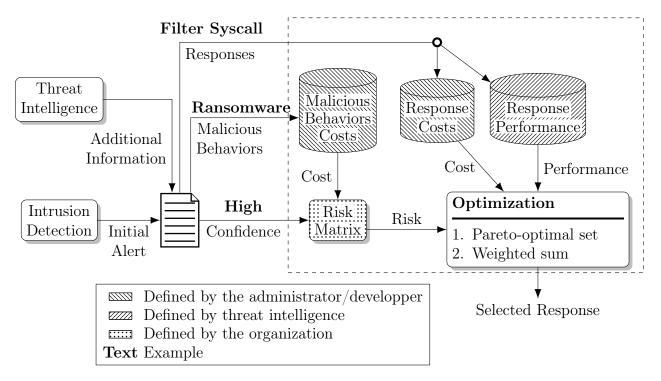

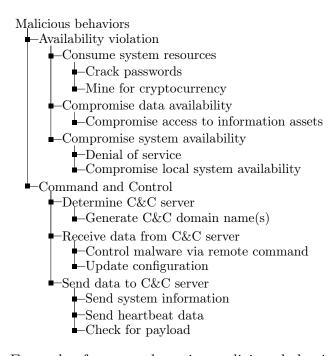

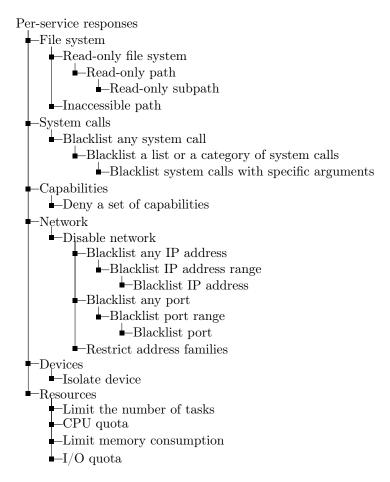

### 2.2.2 SMM intrusion detection approach

In the context of Ronny Chevalier's Ph.D., we proposed an event-based behavior monitoring approach that relies on a dedicated coprocessor to isolate the monitor. This work has been funded and realized in collaboration with HP Labs. Figure 2.2 gives a general overview of our approach and how we apply it to detect intrusion against UEFI privileged runtime services. The main goal was to propose a solution to protect the BIOS of HP laptops using a dedicated micro-controller located on the motherboard. However, this approach is quite generic and could be adapted to monitor other targets and use different detection approaches.

The main characteristics of our approach are the following:

- We isolate the monitor into a coprocessor separated from the main CPU, which uses a dedicated memory;

- To bridge the semantic gap created by the isolation of the monitor, we rely on a unidirectional communication channel between the monitored processor and the monitor, and we enforce the communication by instrumenting the monitored code;

- We rely on a compile-time static analysis of the source code of the monitored software to extract the expected legitimate behavior of the target. Then, the monitor uses this model at runtime to detect intrusions.

#### Isolation of the monitor

The monitor is a trusted component that we rely on to detect intrusions in our system. In the future, we could also use it to start remediation strategies and restore the system to a safe state. It is thus crucial to ensure its integrity.

When the target and the monitor share the same resources (e.g., CPU or memory), it gives the attacker a broad attack surface. Thus, it is necessary to isolate the monitor from the target. Modern CPUs provide hardware isolation features (e.g., SMM or ARM TrustZone [ARM09]). However, we cannot rely on those mechanisms to monitor the code running inside such isolated environments.

In our approach, we use a coprocessor to execute the monitor. Our design relies on an ARM Cortex A5 coprocessor, similar to AMD PSP. Such a coprocessor uses a dedicated memory. Thus, attackers cannot directly access this isolated memory even if they successfully compromised the target. Instead, they could only influence the monitor's behavior via the communication channel, which becomes the only remaining attack surface. However, the simplicity of such an

Figure 2.2: High-level overview of our approach

interface makes it harder to find vulnerabilities and attack the monitor. Thus, such a design reduces the attack surface.

#### Communication channel

Being isolated from the target, the monitor cannot retrieve all the execution context of this target. The isolation creates a semantic gap between the current behavior of the target and what the monitor can infer about this behavior. For example, the monitor does not have sufficient information to infer the virtual to physical address mapping or the current execution trace.

We introduce a communication channel between the monitor and the target. It allows the target to send different types of information, such as the value of a variable stored in memory or inside a register. The nature of such information depends on the detection approaches implemented on the monitor, providing flexibility in our approach.

We propose implementing this communication channel with a dedicated FIFO (First In First Out), connected between the main CPU and the coprocessor. This FIFO is memory-mapped into the main CPU physical memory, and the monitored code can only write into it. Thus, attackers cannot modify or delete messages sent to the coprocessor.

We ensure that the monitored code has exclusive access to the FIFO to prevent other software and hardware component from forging messages faking a legitimate behavior. In our use case, we rely on the SMIACT# signal of the CPU, which is only active is once the CPU is in SMM. We configure the FIFO such that the code executed on the CPU can only write into the FIFO if the CPU is in SMM. This configuration prevents malware executed in kernel or user mode from sending fake messages to the monitor.

We propose to use a fast interconnect between the main CPU executing the monitored component and the FIFO such as QPI (QuickPath Interconnect) [Int09b] from Intel or HyperTrans-

port [Hol+08] from AMD.<sup>1</sup>

#### Intrumentation and static analysis

We rely on static analyses and code instrumentation performed at compile time to infer the legitimate behavior of the target and enforce the communication between the target and the monitor.

We can implement different detection methods using our approach. Since we target the SMM, we chose the detection methods based on the vulnerabilities most likely to affect the privileged runtime services. Those services being written in C, the lack of memory safety is one of the primary sources of vulnerability. Attackers can corrupt the memory, e.g., by exploiting some buffer overflow to alter the control flow or modify the service data. Since we can rely on page table protections to prevent the attacker from modifying the code and executing code injected into data, ROP (Return-Oriented Programming) is one of the most significant remaining threats. Attackers can also perform non-control data attacks to modify some sensitive data used by the privileged services.

Thus, in our work, we decided to implement two different types of detection methods:

- CFI, to prevent attackers from altering the control flow;

- integrity verification of some critical data saved in the SMRAM.

We consider the two methods the most relevant based on the state-of-art attacks targeting the SMM.

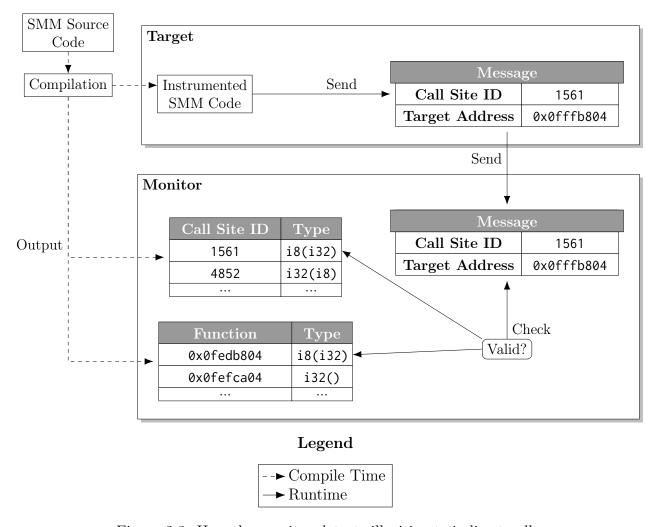

We enforce a CFI policy to protect the forward edges (targets of indirect calls) and the backward edges (return addresses) of the CFG.

We propose a type-based CFI [NT14; Tic+14; PaX15] approach to protect the forward edges. It ensures that the address used in an indirect call matches the address of a function having an expected type signature known at compile time. For example, the call site s->func(s, 1, "abc") is an indirect call where the function pointer func has the following type signature: int (\*func)(struct foo\*, int, char \*). Our approach ensures that the address of func used at that call site always points to a function having the same signature.

Our approach over-approximates the set of expected pointers with all functions with the same type signature. In practice, type-based CFI gives small equivalence classes [Bur+17b] containing all the possible targets for each call site.

Figure 2.3 illustrates our approach to protect indirect calls. During the compilation of the privileged runtime services:

- 1. We assign a unique identifier (call site ID) to each indirect call site.

- 2. We also generate a mapping between each indirect call site ID and the corresponding type of the function called.

- 3. Then, we instrument each indirect call site to send the call site ID and the branch target address to the monitor before executing the indirect call.

<sup>&</sup>lt;sup>1</sup>At the time of this work, these were the interconnects used by Intel and AMD. Recent architectures now use newer versions called Intel Ultra Patch Interconnect [Int17] and AMD Infinity Fabric [Lep+17].

Figure 2.3: How the monitor detects illegitimate indirect calls

4. Finally, we generate a mapping between the address and the type of all the functions targeted by indirect calls.

Both the mappings are sent to the monitor at boot time.

At runtime, the monitor receives the message sent by the monitored code before each indirect branch. The monitor then checks if the function type of the called function is the same as the one associated with the call site.

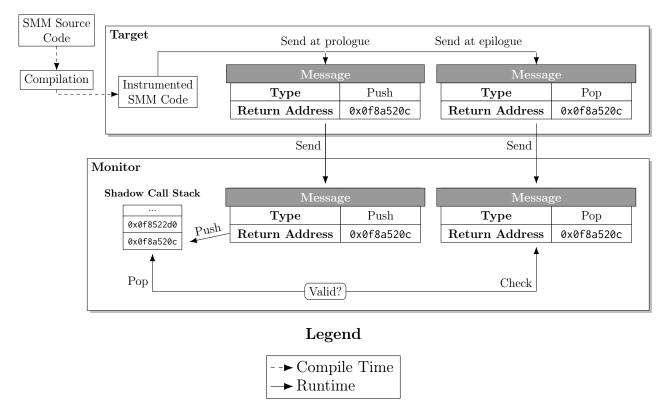

To protect backward edges, we implement a shadow call stack. This structure is a copy of the regular stack, which only contains the succession of return addresses. Contrary to the regular stack, this structure is protected in the memory of the coprocessor, and attackers cannot modify it.

To implement such an approach, we instrument the SMM code at the prologue and epilogue of each function. The instrumented code sends a push message at the epilogue and a pop message at the prologue, as illustrated by Figure 2.4. Each message contains the return address pushed or popped from the regular stack by the function code. At runtime, the monitor performs the following actions:

• If it receives a push message, it pushes the return address of the message on the shadow stack;

Figure 2.4: How the monitor detects illegitimate returns using a shadow call stack

• If it receives a pop message, it pops the address from the shadow stack and compares it with the message's return address.

Compared to other shadow call stack implementations, we do not have to deal with exceptions, longjmp, or even multi-threading due to the SMM environment and constraints [PC03].

We also check the integrity of some sensitive data saved in the SMRAM to detect any malicious data modifications. For example, when entering SMM, the CPU stores its context, including the value of the SMBASE register, in the save state area [Int19d]. The processor uses this register every time an SMI is triggered to jump to the SMM entry point. When exiting the SMM, it restores the value of the SMBASE register from the value stored in the save state area.

Attackers do not have direct access to the SMBASE register, but they can modify the SMBASE value stored in the save state area. In that case, the SMBASE register will be restored with this modified value when the processor leaves the SMM. Thus, the next time an SMI is triggered, the processor will use the new value of SMBASE. This behavior is genuine at boot time to relocate the SMRAM to another location in the DRAM (Dynamic Random Access Memory). At runtime, however, there is no valid reason to modify this value. If an attacker changes the SMBASE value, it may result in arbitrary code execution when the next SMI is triggered.

To detect this attack, our approach checks that the SMBASE value does not change between two successive SMI. We instrumented the BIOS code to send the value of the SMBASE initialized at the end of the boot sequence to the monitor. At runtime, we send the current value of the SMBASE just before the rsm instruction that returns from SMM. The monitor can then detect if an attacker modified the SMBASE to compromise the SMM.

In addition, MMU-related registers, like CR3 (i.e., an x86 register holding the physical address

of the page directory), are interesting targets for attackers [Jan+14]. We need to protect their integrity since recent firmware use page tables [Wil15; YZ15; YZF15]. The CPU resets these registers at the beginning of each SMI with a value stored in memory. Such a value is not supposed to change at runtime. If an attacker succeeds in modifying this value stored in memory, then the corresponding register is under the control of the attacker at the beginning of the next SMI.

Similarly, to detect this attack, we instrument the SMM code to register at boot time the expected value of CR3 and to send at runtime the value of CR3 saved in memory before the rsm instruction. The monitor can then detect attacks similar to the one described by Jang et al. [Jan+14].

#### **Implementation**

We rely on LLVM 3.9 [LA04], a compilation framework widely used in the industry and the research community, to analyze and instrument the SMM code. Ronny Chevalier implemented two LLVM passes with approximately 600 lines of C++ code.

We execute our passes at link time. The first pass enforces the forward-edge CFI, i.e., that indirect calls always branch to legitimate targets. It is performed on the LLVM IR (Intermediate Representation) since it provides us with all the type information that we need.

The second pass enforces the backward-edge CFI, i.e., a shadow call stack. It is done in the backend since it is architecture-specific. Moreover, and more importantly, we want to ensure that it will not be optimized away or placed outside the prologue or epilogue of the functions.

#### 2.2.3 Evaluation and results

At the time of the experiments, to the best of our knowledge, no off-the-shelf FPGA-based solution with direct access to HyperTransport or Intel QPI was commercially available. Therefore, we used a more flexible simulation-based prototype to evaluate our approach.

#### Experimental setup

We used EDK II [Tia17] and coreboot [The17], two real-world implementations of code running in SMM. We built these implementations using our modified LLVM toolchain, and we only instrumented their SMM-related code.

We both used a simulator and an emulator to validate our approach. The main goal of emulators is to be as feature-compatible as possible. However, they are not cycle-accurate and do not accurately model x86 or ARM platforms' performance.

On the other hand, simulators try to model the performance of the platforms accurately but often do not implement all their features (e.g., no possibility to lock the SMRAM). Therefore, we use an emulator to have all the SMM features for the security evaluation and a simulator to model the performance of our implementation accurately.

We used the QEMU 2.5.1 emulator [Bel05] for the security evaluation, and we modified it to emulate our communication channel.

We used the gem5 cycle-accurate simulator [Bin+11] to estimate the performance impact on the main CPU by modeling an x86 system and on the coprocessor by modeling an ARM Cortex A5. We modified gem5 to simulate our FIFO communication channel. It allowed us to specify the delay (in nanoseconds) it takes to send or receive information.

#### Security evaluation

There is no public data set of vulnerable SMM codes in contrast to userland applications. Indeed, attacks targeting the SMM are highly dependent on the architecture and the proprietary BIOS code. However, these BIOS codes are not publicly available and would not execute on our experimental setup.

Consequently, we have implemented SMI handlers with vulnerabilities similar to previously disclosed ones affecting real-world firmware. We reproduced attacks exploiting the following vulnerabilities giving arbitrary execution:

- a buffer overflow in an SMI handler, which allows an attacker to modify the return address stored on the stack [Kal+13];

- an arbitrary write allowing an attacker to modify a function pointer used in an indirect call [Ole16a];

- an arbitrary write allowing an attacker to modify the SMBASE [Puj16];

- an insecure indirect call that retrieves the function pointer from a data structure controlled by the attacker [Ole16b].

As shown in Table 2.1, the monitor detected all these attacks since they modified the control flow of the SMM code. We did not encounter false positives, which we expected since we used a conservative strategy regarding indirect calls. Also, while poor software engineering practices using function typecasting could introduce false positives, we did not encounter such cases in our evaluation.

| Vulnerability   | Attack Target    | Security Advisories   | Detected |

|-----------------|------------------|-----------------------|----------|

| Buffer Overflow | Return address   | CVE-2013-3582 [Cor13] | Yes      |

| Arbitrary write | Function pointer | CVE-2016-8103 [Cor16] | Yes      |

| Arbitrary write | SMBASE           | LEN-4710 [Len16a]     | Yes      |

| Insecure call   | Function pointer | LEN-8324 [Len16b]     | Yes      |

Table 2.1: Effectiveness of our approach against state-of-the-art attacks

Notice that our CFI implementation performs a sound analysis to recover the potential targets of an indirect call. Therefore, the analysis is not complete, and it would be possible for an attacker to exploit a type collision and redirect the control flow to another function with the same type signature.

Nonetheless, we argue that a type-based CFI increases the difficulty for the attacker since the only available targets for an indirect call are a subset of the existing functions within the SMRAM with the right type signature. We analyzed the code of EDK II and found that the vast majority of function types only correspond to a unique function, as illustrated by Table 2.5.

| Number of Distinct Equivalent Classes | 158 | 24 | 42 | 2 | 1 | 1  |

|---------------------------------------|-----|----|----|---|---|----|

| Size of the Equivalent Classes        | 1   | 2  | 3  | 5 | 9 | 13 |

Figure 2.5: Function types equivalent classes in EDK II

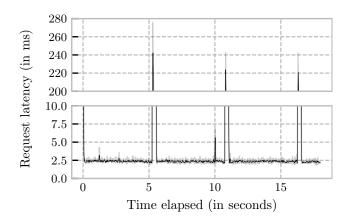

#### Performance evaluation

The additional SMM code added with our instrumentation introduces two costs: the raw communication delay between the main CPU and the hardware FIFO; and the instrumentation overhead. The former is related to the time it takes the main CPU to push the packets to the FIFO. The latter is due to multiple factors, such as fetching and executing new instructions or storing intermediate values resulting in register spilling (e.g., the return address of a function fetched from the stack).

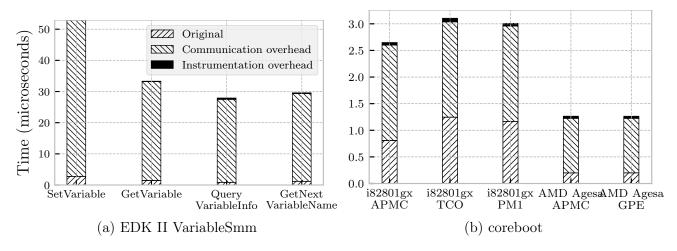

We performed 100 executions of each SMI handler we selected for our evaluation. For each SMI handler, we measured the time it takes for the original handler to execute, the cost of the communication, and the additional instrumentation overhead. Figure 2.6 illustrates the results we obtained.

Figure 2.6: Time (in microseconds) to execute each SMI handler (averaged over 100 executions)

We can observe a high overhead due to the communication, even with a low latency communication channel (128 ns). The instrumentation overhead, on the other hand, is negligible in comparison. Nevertheless, for each SMI handler, even with the overhead of our solution, we observe that the time spent in SMM is below the 150 µs threshold recommended by Intel [Int11]. Thus, the impact of our approach on the system's performance is low and not noticeable for the user.

#### 2.2.4 Conclusion

In this section, we proposed an event-based detection approach for low-level software using three key components: a coprocessor to isolate the monitor, a communication channel to reduce the semantic gap, and a compilation phase to extract the correct behavior of the target. We show that we can use this approach to detect intrusions targeting SMM services by verifying a CFI policy and the integrity of security-critical registers (CR3 and SMBASE). Unlike

other approaches, we solve the challenges of the semantic gap and the transient attacks while remaining flexible.

We implemented our approach by instrumenting and monitoring real-world firmware and simulating the coprocessor executing our monitor. The results show that we detect state-of-the-art attacks against the SMM while remaining below the 150 µs threshold, thus avoiding any noticeable impact on the user.

This work was presented and published at ACSAC 2017 conference [10] and was done during the Ph.D. of Ronny Chevalier. I co-advised Ronny with David Plaquin, in a bilateral collaboration project with HP Labs at Bristol. Ronny realized all the development of the prototype, which is the property of HP and has not been released in open source. This work has also been the subject of two patent applications currently in progress: EP3413531A1 and EP3413532A1.

The following section presents our second contribution in the field of hardware-assisted intrusion detection.

## 2.3 Hardware-assisted Information Flow Tracking

In the HardBlare project, we proposed a generic anomaly-based approach to detect software attacks against confidentiality and integrity at different levels, e.g., low-level attacks such as control-flow hijacking and more high-level attacks such as confidential files leakage. In that context, we propose a hardware-assisted DIFT approach.

### 2.3.1 Introduction to Dynamic Information Flow Tracking

DIFT consists in:

- 1. Attaching **labels** called tags to **containers** (e.g., files, program variable, or registers) and specifying an information flow **policy**, i.e., relations between tags;

- 2. **Propagating** tags at runtime to reflect information flows that occur during execution and **detecting** any **policy violation**.

DIFT can be implemented at different levels. OS-level DIFT [Efs+05; Zel08; Roy+09; Geo+17] is a coarse-grained approach which only monitors system calls. OS-level containers are files or memory pages. The monitor is usually implemented in the OS kernel in such approaches, protecting it from userland applications. Moreover, the end-user can easily specify the policy by tagging files. These approaches also have a relatively low runtime overhead on the execution. However, they suffer from two main limitations:

- They over-approximate the internal behavior of applications;

- They cannot be used to detect low-level attacks such as control-flow hijacking, which requires handling more fine-grained containers such as registers.

To illustrate the problem of over-approximation, let us consider an application that reads the file  $f_1$  and then writes some data into the file  $f_2$ . OS-level approaches consider that the read syscall on  $f_1$  followed by a write syscall on  $f_2$  always results in an information flow from  $f_1$  into  $f_2$ . However, if the application code does not use the data read from  $f_1$  to compute the data written into  $f_2$ , there is indeed no information flow.

Fine-grained software approaches [Qin+06; NS05] monitor each instruction executed by an application. They consider fine-grained containers such as registers or words stored in memory. Such approaches can track information flows more precisely and detect low-level attacks, e.g., control-flow hijacking. However, DIFT monitors implemented in software [Qin+06; NS05] are not isolated from their target since they weave the monitor into the application code.

Figure 2.7: In-core DIFT (adapted from [KDK09b])

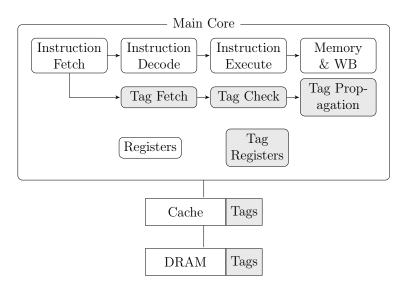

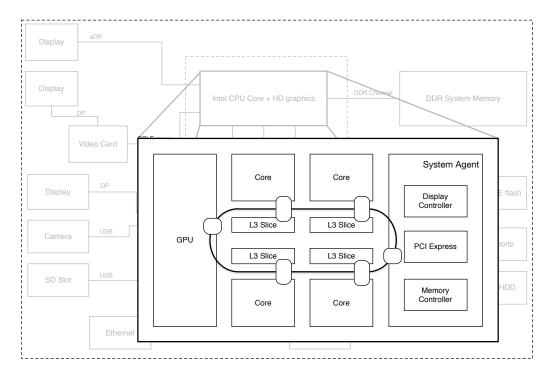

Implementing a fine-grained approach in hardware is a solution to protect the monitor from software attacks. In-core approaches [DKK07; Dha+15; Suh+04], illustrated by Figure 2.7, modify the microarchitecture of the CPU to compute tags in parallel to regular operations. Such approaches extend memory and caches with tag bits. Each stage of the pipeline is duplicated with a specific hardware module to realize tag-related operations all along with the program execution. However, those modifications to the core microarchitecture are invasive, which limits their adoption and industrialization. Thus, those approaches are only validated on simulation or implemented in softcores.

Figure 2.8: Offloading DIFT (adapted from [KDK09b])

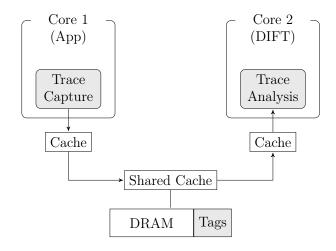

As illustrated by Figure 2.8, offloading approaches [Che+08a; Ruw+08] take advantage of multi-core systems to offload tag computation on a general-purpose core. In addition to program execution, the monitored core also compresses and stores the information required for

DIFT inside a shared buffer located in memory or cache. The second core decompresses this information and realizes tag computation to check whether an illegal information flow occurred. This approach does not require invasive modification of the processor. However, it wastes a general-purpose core for DIFT operations, which is not energy efficient.

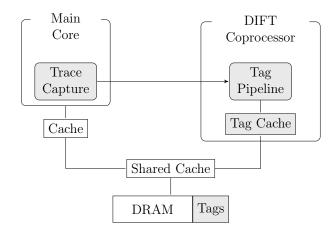

Off-core approaches [KDK09b; Ven+08] use a custom DIFT coprocessor to compute and check tags. The idea is similar to the offloading solution, but instead of wasting a general-purpose core, this approach uses a custom DIFT coprocessor. The coprocessor is thus dedicated and optimized for DIFT. However, some modifications on the main core are still required to send the execution trace to the coprocessor. Figure 2.9 illustrates such approaches.

Figure 2.9: Off-core DIFT (adapted from [KDK09b])

# 2.3.2 HardBlare: a hardware/software codesign for DIFT

In the HardBlare project, we target embedded systems using rich OSes in security-critical contexts. Such systems cannot be redeveloped from scratch for economic reasons. However, it is possible to make changes to the hardware and software for security, provided that we maintain compatibility with the OS's applications and drivers. In this context, we proposed an off-core DIFT approach to detect a broad range of attacks. The originality of our approach lies in the following:

- We combine fine-grained DIFT with OS-level tagging to be able to attach tags to files. This hybrid approach can save the security contexts between reboots, files being persistent containers. It also helps the end-user to specify the security policy.

- We implement tag propagation in a hardware coprocessor to isolate the monitor. Contrary to other hardware approaches, our coprocessor approach requires no modification of the main CPU.

Isolating the monitor in a dedicated coprocessor creates a semantic gap between the monitor and the monitored system. This semantic gap leads to the following challenge: how can the isolated coprocessor extract some information from the main CPU to infer the behavior of the monitored code? Reducing this gap without modifying the main CPU is one of the main challenges of the project. We solve the semantic gap issue by an original combination of approaches:

• We pre-compute **annotations** during the compilation of applications. Those annotations reflect the information flows in each basic block;

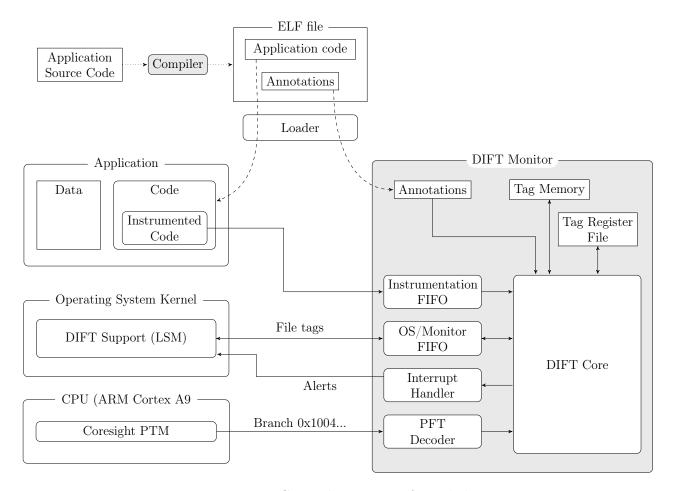

Figure 2.10: General overview of HardBlare

- We send branching information using hardware trace mechanisms at runtime;

- We send addresses of data memory accesses by **instrumenting** the application code.

Our approach can be implemented on systems using an SoC (System on a Chip) that combines a CPU and an FPGA, such as Xilinx ZYNQ<sup>2</sup> or Intel/Altera Cyclone VS<sup>3</sup>. In this type of SoC, the CPU corresponds to the PS (Processor System) and the FPGA to the PL (Programmable Logic). We execute the monitored system on the PS and the DIFT monitor on the PL. Our experiment relies on the Digilent ZedBoard<sup>4</sup>. This board uses a Xilinx ZYNQ SoC, which combines a dual-core ARM Cortex-A9 CPU with a Xilinx FPGA.

Figure 2.10 gives a general overview of our approach. The DIFT monitor is implemented on the FPGA of the SoC. It monitors the behavior of applications executed on the main CPU and manages tags corresponding to fine-grained containers (CPU registers and words stored in the application's memory). Those tags are themselves stored in two different memory regions:

- Tags corresponding to registers of the main CPU are stored in *shadow registers* inside the FPGA (Tag Register File);

- Tags corresponding to the application memory are stored into a dedicated part of the memory (Memory tags) that only the DIFT monitor can access.

<sup>&</sup>lt;sup>2</sup>https://www.xilinx.com/products/silicon-devices/soc/zyng-7000.html

<sup>&</sup>lt;sup>3</sup>https://www.intel.com/content/www/us/en/products/programmable/soc/cyclone-v.html

<sup>4</sup>http://zedboard.org/

To capture the runtime behavior of the applications and solve the semantic gap issue without modifying the main CPU, we rely on four communication channels: trace, annotation, instrumentation, and OS/monitor channels.

We configure the ARM CoreSight PTM (Program Trace Macrocell) hardware trace mechanism so that the CPU automatically sends branching information to the monitor executed on the FPGA. This trace mechanism was initially designed for debugging purposes. In HardBlare, we use it to monitor the executed application for security purposes. However, the PTM can only send sparse information about the behavior of the monitored application. It only provides the address taken in branching instructions and exceptions. Thanks to this mechanism, the monitor can track the address of each basic block executed by the application. Nevertheless, this information is not sufficient to retrieve the information flow that occurred in each basic block.

During the compilation of each application, we statically analyze application's code and compute annotations for each basic block. Then, we saved those annotations in a dedicated section of the elf binary file. Annotations correspond to information flows that will occur in each basic block. They describe the tag propagations that the monitor will have to perform at runtime. We also modified the OS loader to send annotations to the coprocessor while loading the application on the main CPU.

Each time the main CPU executes a basic block of the application, the PTM trace mechanism sends the address of this basic block to the DIFT monitor. The monitor then retrieves the annotations corresponding to this basic block and executes them to propagate the tags stored inside the tag register file or the tag memory. It also checks the security policy and sends an interrupt to the OS in case of intrusion. The handling of this interrupt, i.e., the reaction part, is not in this project's scope.

To handle tags corresponding to application data stored in memory, the monitor needs to know the virtual address of each memory access performed by the application. Thus, the monitor can maintain a map between those addresses and the corresponding tags. Sometimes, the address of memory accesses is computed at runtime and saved in a register by the application code. In this case, the address can be difficult to predict at compile time. We instrument the program code to solve this issue. The instrumented code sends the address to the coprocessor via a dedicated FIFO just before accessing the memory.

Finally, we associate a tag to each file of the system. We saved those tags in the extended attributes of the file. We propagate the file's tag to the tag corresponding to the memory buffer each time the monitored application reads a file. We do the opposite when the application writes into files. Tags associated with files cannot be handled directly by the DIFT monitor but only by the OS. To manage such cases, we modified the Linux kernel. Our modified kernel sends the file tag to the coprocessor for each read syscall thanks to a dedicated FIFO. For each write syscall, the kernel retrieves the tag corresponding to the buffer from the FIFO and propagates it to the file attributes.

#### **DIFT** coprocessor

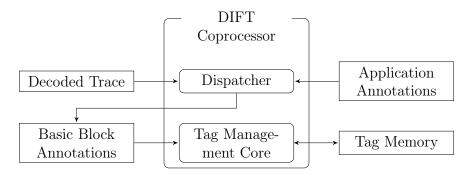

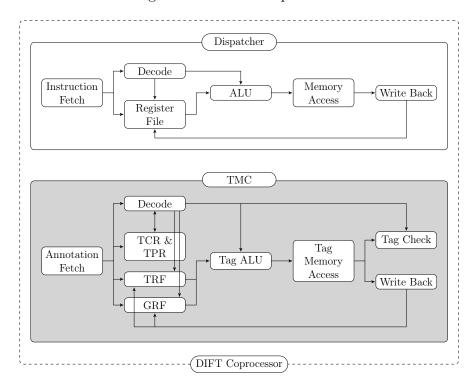

We use different strategies to implement the coprocessor. Our first solution, mainly developed by Mounir Nasr Allah during his Ph.D., relies on a generic MIPS-based soft core. In this case, the firmware executed by the coprocessor implements all the DIFT logic. Mounir has integrated this flexible solution with all the other software components of HardBlare.

Figure 2.11: DIFT coprocessor.

Figure 2.12: DIFT coprocessor internal architecture.

We also designed and implemented a dedicated multi-core DIFT coprocessor on FPGA. Muhammad Abdul Wahab is the principal contributor to this work, he realized during his Ph.D.

Figure 2.11 gives a general overview of this coprocessor, and Figure 2.12 illustrates its internal design. The first core (Dispatcher) is a generic fully-pipelined MIPS processor. It executes a firmware that parses the trace from the PTM, identifies the current basic block, and retrieves the corresponding annotations from the annotation memory. The dispatcher then sends those annotations to the internal program memory of the second core, i.e., the TMC (Tag Management Core). The TMC executes the annotation to propagate tags and checks the security policy.

In such a multi-core design, we can use multiple TMCs to handle the following use-cases:

- We can enforce different tag propagation and check policies in parallel (one policy by TMC). This approach therefore detect different types of attacks.

- We can monitor different applications in parallel (one application by TMC).

#### Trace generation and decoding

In HardBlare, we rely on instruction tracing mechanisms provided by existing processors to bridge the semantic gap between the application executed on the main CPU and the DIFT monitor isolated on the coprocessor. We implemented our approach on the ARM Coresight PTM tracing mechanisms available on the Zynq SoC.

When this component is activated and correctly configured, it generates traces at waypoints. These points correspond to modifications of the value of the PC (Program Counter) register and therefore allow us to follow the path taken by the processor in the control flow graph. The component receiving the traces should have access to the application code, making it possible to infer all the instructions executed in the trace. More precisely, the PTM generate traces for the following waypoints:

- when the CPU executes direct and indirect branching instructions;

- when an exception is triggered;

- when the instruction set or the security state of the processor change.

For branching instructions, the trace contains the target address and the result of the conditional code. For exceptions, the trace describes the exception reasons, the address at which this event occurred, and the return address in the application code. Finally, the trace describes the reasons and the consequences of modification of the CPU state.

In our design, these traces are compressed and sent in packets to the TPIU (Trace Port Interface Unit) and then to the security monitor located in the PL using the EMIO (Extended Multiplexed Input/Output) bus. The traces follow the specification of the PFT (Program Flow Trace) [Ltd11]. Finally, the PFT decoder, an hardware component mainly developed by Muhammad Abdul Wahab, decompresses the trace, decodes the messages, and sends the results to a dedicated FIFO.

The PTM has to be configured by kernel code. We had to patch the official Linux PTM driver, which did not fully support all the features of the PTM. This patch, mainly developed by Muhammad Abdul Wahab, has been officially adopted by the vanilla Linux kernel distribution<sup>5</sup>. We also modified the Linux kernel to trace only some processes, based on their PID (Process IDentifier). It is necessary to activate the PTM only when the CPU executes the monitored application. Thus, the trace mechanism has to be stopped when the OS schedules another process or executes some kernel code.

#### Annotations

The trace provided by the PTM is not sufficient to retrieve all the necessary information needed to track application information flows. It provides only the addresses of the basic blocks that the processor has executed so far. However, the DIFT monitor has to infer the information flow that occurred inside each basic block. We proposed to compute such information at compile-time and to store the results in a dedicated section of the binary application code. We implemented the generation of annotations by modifying the LLVM backend for ARM V7.

We compute the sequence of tag propagation operations, called annotations, that the coprocessor must execute at runtime for each basic block. Each operation of such a sequence corresponds

<sup>&</sup>lt;sup>5</sup>https://lore.kernel.org/patchwork/patch/723740/

to one or several instructions of the coprocessor. Annotations of a basic block reflect the information flows resulting from the execution of the basic block.

We propose associating a tag to each register of the processor and each word stored inside the DRAM. We use a 32 bit ARM Cortex-A9 processor in our implementation, and we store tags in 32-bit tag registers of the coprocessor and 32-bits words of the tag memory area. Only the coprocessor can access tag registers and tag memory area.

We note  $\underline{Rn}$  the tag corresponding to the register Rn and  $\underline{[Rn]}$  the tag of the memory word stored at the address pointed by this register value. We assume that the monitored application is executed on top of an OS that uses pagination. In that case, the PTM reports virtual addresses in the generated trace. Thus, we associate tags to virtual addresses. To handle implicit flows, we manage the APSR and PC registers differently than other registers. We associate a tag to each field of the APSR status register used in conditional branching instructions, and we associate a stack of tags to the PC register.

In the ARM ISA, instruction operands can be immediate values or registers. Thus, we also associate a default tag to immediate values, noted  $\underline{Imm}$ . The administrator can specify the value of this default tag at runtime.

We only support the standard ARM processor instruction set, and we do not manage the different complementary instruction sets such as Thumb. Some instructions allow switching from one instruction set to another. In our approach, we assume that these instructions should not be present in the application code. We enforce such a restriction at compile time.

The ARM instruction set offers the possibility to execute most instructions conditionally. However, the PTM generates traces exclusively when executing waypoints. Since conditional instructions that do not operate on the PC register are not waypoints, the PTM does not generate any trace for these instructions. Therefore, analyzing the traces produced by the PTM, we cannot infer whether the ARM processor has executed those instructions and whether the coprocessor has to execute annotations corresponding to these instructions. Therefore, we also modified the compiler's back-end to disable conditional forms for instructions that do not correspond to waypoints. In practice, this restriction is not very penalizing [Che+10b]. ARM took a similar decision for the following versions of their architecture, namely the 64-bit ARMv8 [Che+10b].

The monitor does not track instructions executed in kernel mode since the OS kernel is part of our TCB (Trusted Computing Base). Moreover, we only generate annotations for application instructions that generate information flows from their sources to their destination operands. For some instructions, we have to combine the tags of their different sources before propagating the resulting tag to the destination. We also have to combine the source tags with the destination tags when the instruction only modifies part of the destination operand (e.g., the least significant bytes of the destination operand).

We rely on different combining functions, noted  $\bigoplus_T$ , where T is the type of the instruction producing the information flow. The operation performed by each combining function can be selected at runtime by the administrator. Thus, we express each annotation as  $\underline{s_1} \oplus \underline{s_2} \dots \oplus \underline{s_n} \to \underline{d_1}, \dots \underline{d_m}$ , with  $s_1, \dots s_n$  the source operands and  $d_1, \dots d_m$  the destination operands. When executing this annotation, the coprocessor combines all the source tags and propagates the result to each destination tag.

We manually analyzed the specification of all the instructions of the ARM V7 ISA. We de-

fine three types of annotations: register-based explicit flows, implicit flows due to conditional branching, and memory-based explicit flows.

Table 2.2 gives an overview of the different types of annotations we can generate to handle explicit flows.

| Instruction Type                    | Example                      | Annotations                                                                                                            |

|-------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Data move                           | $mov \ Rd, OpSrc_1$          | $OpSrc_1 \to \underline{Rd}$                                                                                           |

| Arithmetic & logic                  | $add\ Rd, OpSrc_1, OpSrc_2$  | $OpSrc_1 \oplus OpSrc_2 \to \underline{Rd}$                                                                            |

| Comparison                          | $cmp\ OpSrc_1,\ OpSrc_2$     | $\underbrace{OpSrc_1}_{C} \oplus \underbrace{OpSrc_2}_{C} \to \underbrace{APSR}_{C}$                                   |

| Arithmetic & logic with APSR update | $adds\ Rd, OpSrc_1, OpSrc_2$ | $\underbrace{OpSrc_1}_{ALC} \underset{ALC}{\oplus} \underbrace{OpSrc_2} \rightarrow \underline{Rd}, \underbrace{APSR}$ |

| Memory load                         | $ldr \ Rn, [Ra]$             | $[Ra] \to \underline{Rn}$                                                                                              |

| Memory store                        | $str\ Rn, [Ra]$              | $\underline{Rn} \to \underline{[Ra]}$                                                                                  |

Table 2.2: Annotations generated for explicit flows

Implicit flows occur due to conditional branching, as illustrated by Listing 2.1. In this example, there is an implicit flow from the conditional expression to variables a and b. Consequently, at line 3, the tag of variable i should be propagated to variable a. However, this control flow dependence only occurs until the immediate post-dominator of the conditional branching. Thus, there is no implicit flow from i to c at line 9.

Notice that implicit flows can also occur due to the non-execution of some branches. For example, assume i = 0 in the example. There is still an implicit flow from i to b at line 3, even if b is not modified in the executed branch. Indeed, since b is modified in the alternative branch, an attacker can infer some information on i by observing b.

A pure dynamic approach cannot handle such types of implicit flows. Instead, it would be possible to rely on static analyses to infer the variables modified in alternative branches. However, the problem is quite complex in the general case, since the alternative branch can call functions and use pointers. Static analyses handle those cases by over-approximating the set of modified variables, leading to false positives. Designing such a static analysis is out of the scope of our work, and we do not handle such implicit flows in our implementation. However, we could generate additional annotations corresponding to the flows occurring in alternative branches by relying on external static analysis.

```

b = 0;

if (i == 0) {

a = 1;

}

else {

```

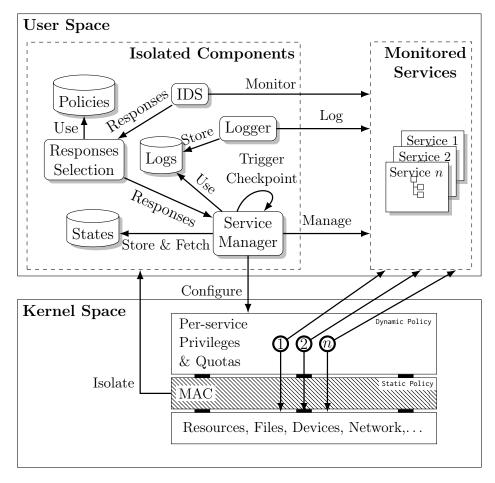

Listing 2.1: Example of indirect information flows