# Integrated circuits and systems for energy-efficient processing and advanced communication systems

Antoine Frappé

### ▶ To cite this version:

Antoine Frappé. Integrated circuits and systems for energy-efficient processing and advanced communication systems. Electronics. Université de Lille, 2019. tel-03482315

# HAL Id: tel-03482315 https://hal.science/tel-03482315

Submitted on 15 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Habilitation à Diriger des Recherches

Ecole Doctorale Sciences Pour l'Ingénieur

INTEGRATED CIRCUITS AND SYSTEMS FOR ENERGY-EFFICIENT PROCESSING AND ADVANCED COMMUNICATION SYSTEMS

CIRCUITS ET SYSTEMES INTEGRES POUR LE TRAITEMENT ENERGETIQUEMENT EFFICACE ET LES SYSTEMES DE COMMUNICATION AVANCES

# Antoine FRAPPÉ

14 Juin 2019

# Habilitation à Diriger des Recherches

Ecole Doctorale Sciences Pour l'Ingénieur

INTEGRATED CIRCUITS AND SYSTEMS FOR ENERGY-EFFICIENT PROCESSING AND ADVANCED COMMUNICATION SYSTEMS

# Antoine FRAPPÉ

June 14th 2019

Président : Yann DEVAL Univ. Bordeaux

Rapporteurs: Christian ENZ EPFL

Sven MATTISSON Lund Univ.

Dominique MORCHE CEA - Leti

Andreas KAISER Univ. Lille

Andreia CATHELIN STMicroelectronics

Patricia DESGREYS Telecom ParisTech

Garant:

Jury:

# Document outline

| Chapter 1        | Introduction                                                           | 13 |

|------------------|------------------------------------------------------------------------|----|

| Chapter 2        | Research directions                                                    | 15 |

| 2.1. Pas         | ssion for electronics                                                  | 15 |

| 2.2. Ph.         | D. thesis on IC design and digital transmitters                        | 16 |

| 2.3. A y         | year of discoveries at UC Berkeley                                     | 18 |

| 2.4. As          | sistant Professor position at ISEN Lille                               | 19 |

|                  | O research group leadership                                            |    |

|                  | nclusion                                                               |    |

| 2.7. Bib         | oliography                                                             | 23 |

| Chapter 3        | Contributions to Digital RF Transmitters                               | 25 |

| -                | roduction to digital RF transmitters                                   |    |

| 3.1.1.           | Traditional transmitters                                               |    |

| 3.1.2.           | Switching to digital-intensive transmitters                            |    |

| ,                | Quadrature transmitters                                                | 27 |

| <i>'</i>         | Polar transmitters                                                     |    |

| 3.1.3.<br>a) I   | Challenges in digital RF transmitters                                  |    |

| b) I             | ow voltage power supply in CMOS technology                             | 33 |

| ,                | Out-of-band interference                                               |    |

|                  | gh-speed digital operation                                             |    |

| 3.2.1.           | Generation of digital RF signals based on 1-bit delta-sigma modulation |    |

| 3.2.2.           | Time-interleaving                                                      |    |

| 3.2.3.           | Up to higher sample rates (digital mmW transmitters)                   |    |

|                  | tput stage topologies for integrated transmitters                      |    |

| 3.3.1.           | Power combination with passive networks                                |    |

|                  | Switched-capacitor output stage                                        |    |

| 3.4. Ou 3.4.1.   | t-of-band interference                                                 |    |

| 3.4.1.<br>3.4.2. | Analog BAW filtering                                                   |    |

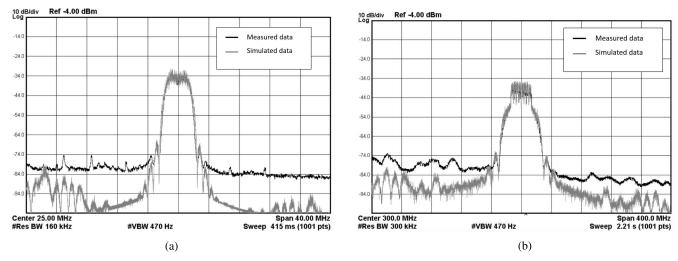

|                  | Demonstration of quantization noise filtering                          |    |

| b) 7             | ransmitter experiment with BAW filters and duplexers                   | 54 |

| 3.4.3.           | Engineering of the Noise Transfer Function (NTF)                       |    |

| ,                | RF digital mixing with integrated FIR filter                           |    |

| 3.4.4.           | FIR DAC                                                                | 59 |

| /                | TR-DAC principles                                                      |    |

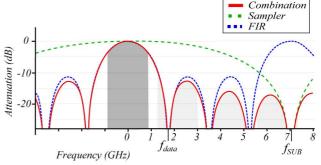

|                  | Semi-digital RF frequency filtering                                    |    |

|                  | ime-interleaved high-pass transmitter architecture                     |    |

| 3.5. Sur         | nmary and perspectives                                                 | 67 |

| 3.6. Bib         | oliography                                                             | 69 |

| Chapter 4      | Contributions to baseband circuits for mmW receiver systems       | 75  |

|----------------|-------------------------------------------------------------------|-----|

| 4.1. 60        | GHz adaptive high data rate baseband receiver                     | 75  |

| 4.1.1.         | Position of the problem                                           | 75  |

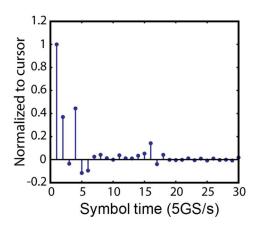

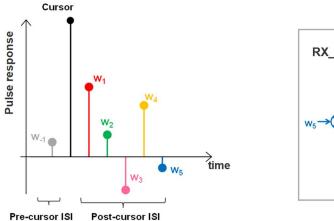

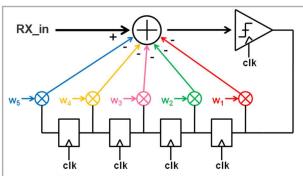

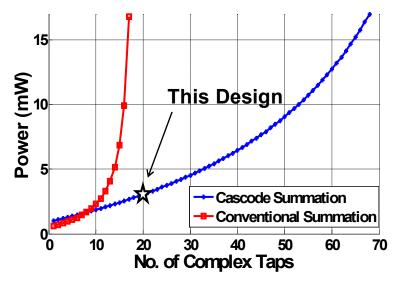

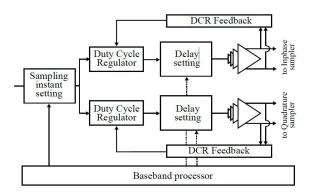

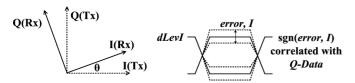

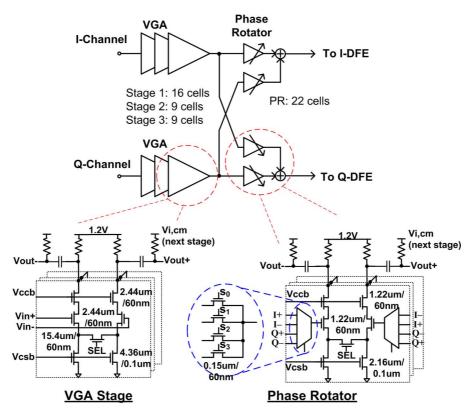

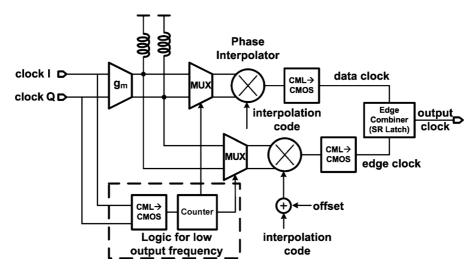

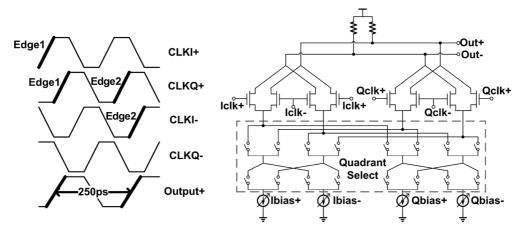

| 4.1.2.         | 60 GHz baseband receiver design                                   | 76  |

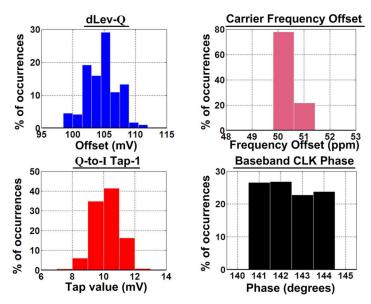

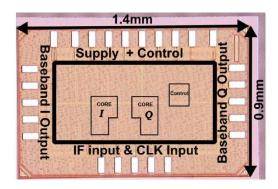

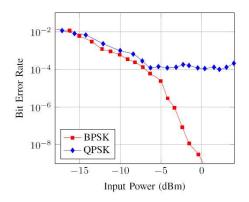

| 4.1.3.         | Chip measurement results                                          | 79  |

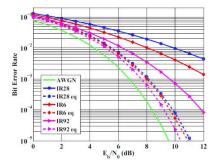

| 4.2. C         | ontinuous-time digital signal processing for equalization         | 81  |

| 4.2.1.         | Introduction                                                      |     |

| 4.2.2.         | System-level architecture                                         | 82  |

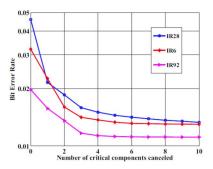

| a)             | Critical-tap cancellation                                         |     |

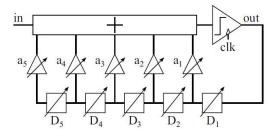

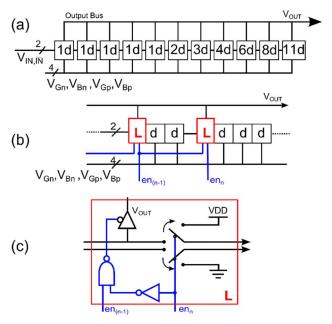

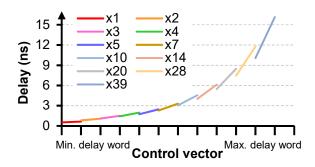

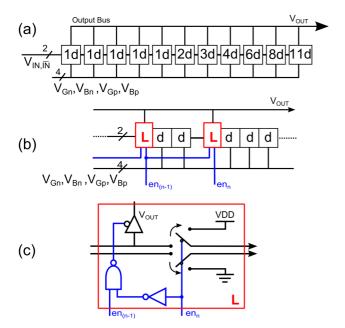

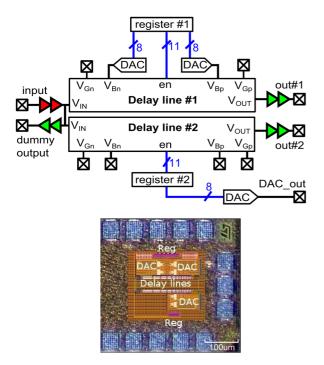

| b)<br>4.2.3.   | Digital Delay Line                                                |     |

| 4.2.3.<br>a)   | Context and state-of-the-art                                      |     |

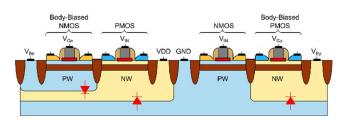

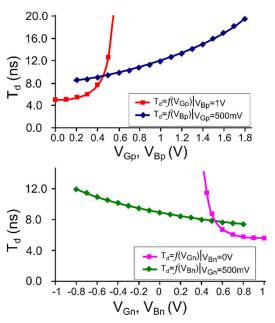

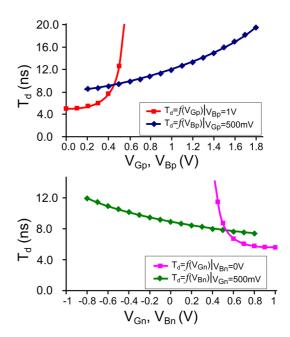

| b)             | Delay Element Design in FDSOI                                     |     |

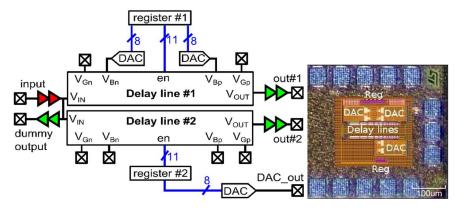

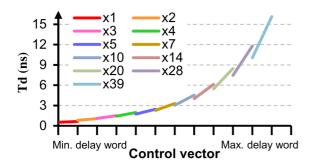

| c)<br>d)       | Prototype delay line architecture                                 |     |

| 4.2.4.         | Conclusion and perspectives                                       |     |

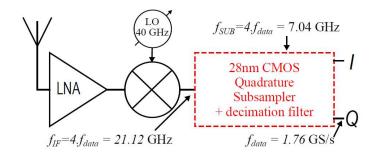

|                | ubsampling of mmW signals                                         |     |

| 4.3.1.         | Introduction                                                      |     |

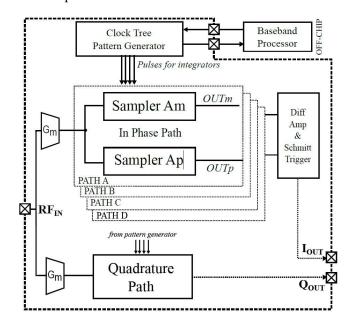

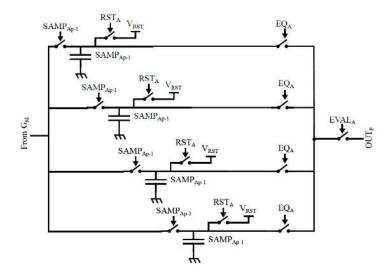

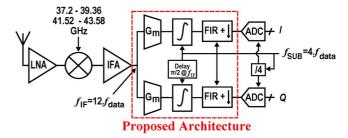

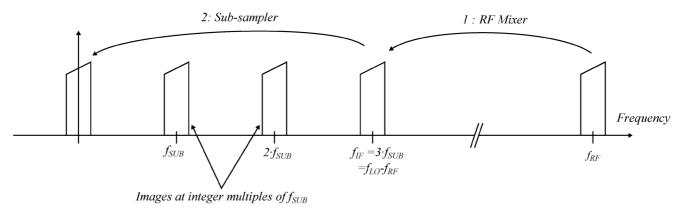

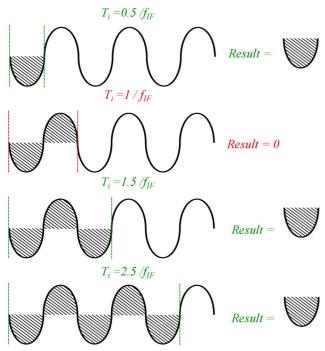

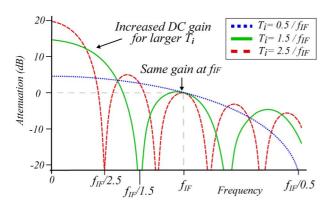

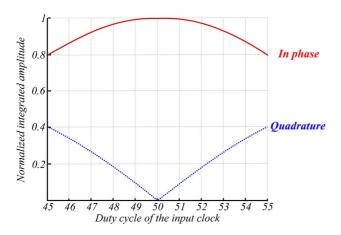

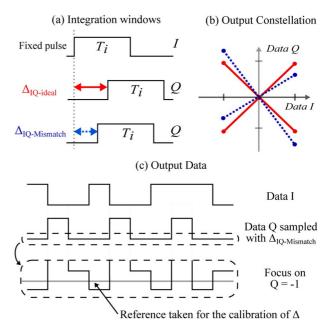

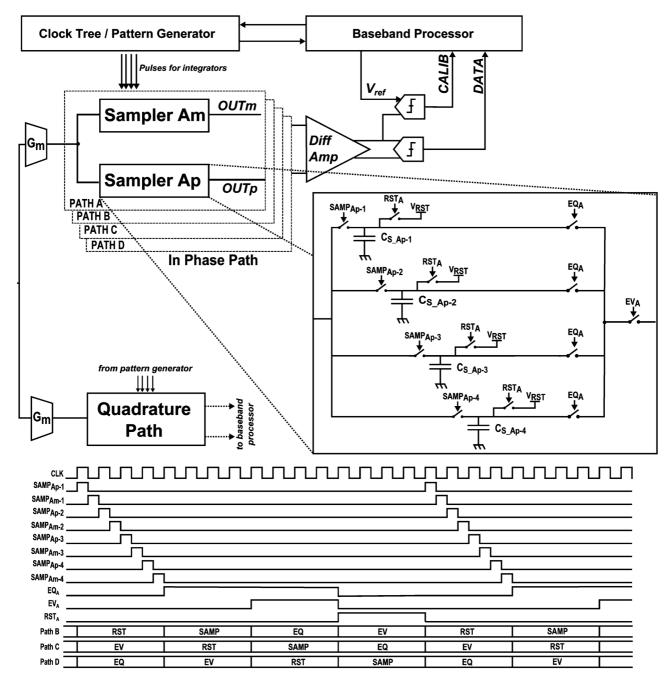

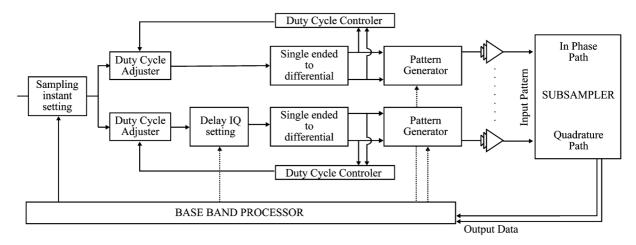

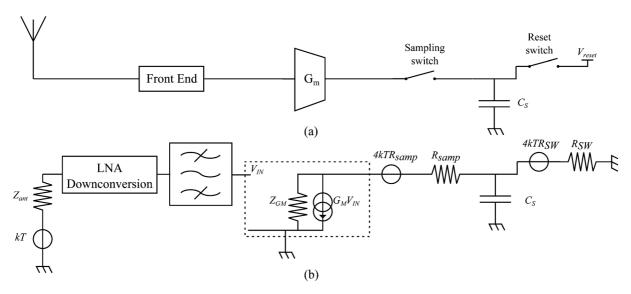

| 4.3.2.         | 60 GHz receiver architecture                                      |     |

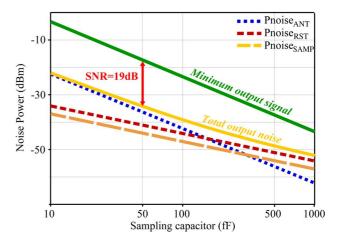

| 4.3.3.         | Design of an IF subsampler for 60 GHz receivers                   |     |

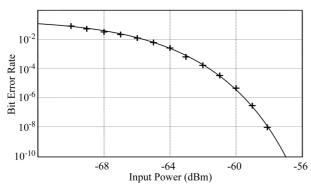

| 4.3.4.         | Results and discussion                                            |     |

| 4.4. C         | onclusion / Summary                                               | 100 |

|                | napter bibliography                                               |     |

| Chapter 5      | Perspectives and future directions                                | 103 |

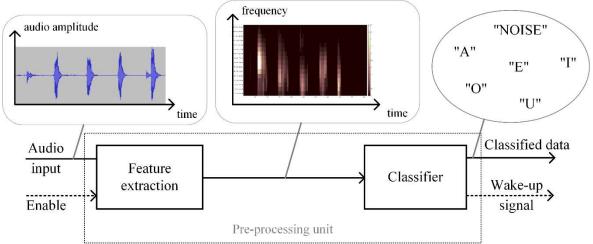

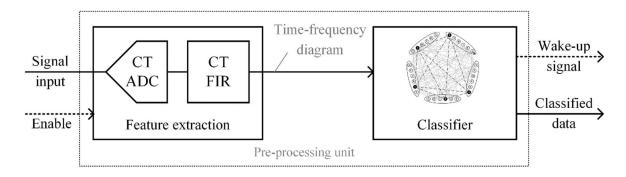

| •              | ear-sensor computing for audio signals                            |     |

| 5.1.1.         | Context                                                           |     |

| _              | State of the art in audio pre-processing units                    |     |

| 5.1.2.         | Proposed research directions                                      |     |

|                | rcuits and Systems for Personal Area Networks                     |     |

| 5.2. C. 5.2.1. | Context                                                           |     |

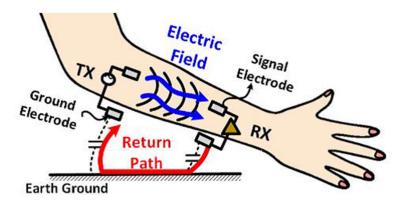

| 5.2.1.         | Human body communications                                         |     |

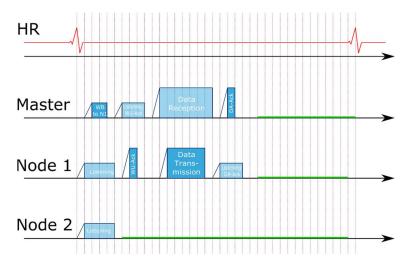

| 5.2.3.         | Near-sensor computing and machine learning for Body Area Networks |     |

| 5.2.4.         | Connected textiles                                                |     |

|                | hapter bibliography                                               |     |

| <i>3.3.</i> C  | napter bibliography                                               | 114 |

| Chapter 6      | Professional activities                                           | 117 |

| 6.1. St        | udent mentoring                                                   | 117 |

| 6.1.1.         | Supervision of M.Sc. students                                     | 117 |

| 6.1.2.         | Supervision of Ph.D. students                                     | 118 |

| 6.1.3.         | Supervision of post-doctoral researchers and research engineers   | 119 |

| 6.2. To        | eaching                                                           | 120 |

| 6.2.1.         | Delivered courses                                                 | 120 |

| $\sim$ | .1.    |   |

|--------|--------|---|

| ( )11  | tlınd  | ρ |

| Ou     | tilli, | _ |

| 6.2                                         | .2.                                                                        | Student Projects supervision                                                                                                                                                                             | 121                             |

|---------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 6.3.                                        | Nat                                                                        | ional and international outreach                                                                                                                                                                         | 121                             |

| 6.3.1.<br>6.3.2.                            |                                                                            | Participation in national committees                                                                                                                                                                     | 121                             |

|                                             |                                                                            | Ph.D. committees                                                                                                                                                                                         | 122                             |

| 6.3                                         | .3.                                                                        | Expertise works                                                                                                                                                                                          | 123                             |

| 6.3.4.<br>6.3.5.<br>6.3.6.                  |                                                                            | Reviews of scientific articles.  Membership in conferences  Awards                                                                                                                                       |                                 |

|                                             |                                                                            |                                                                                                                                                                                                          |                                 |

|                                             |                                                                            |                                                                                                                                                                                                          | 6.3                             |

| 6.3                                         | .8.                                                                        | Involvement in national and international instances                                                                                                                                                      | 126                             |

| 6.4.                                        | Loc                                                                        | cal administrative duties and management responsibilities                                                                                                                                                | 126                             |

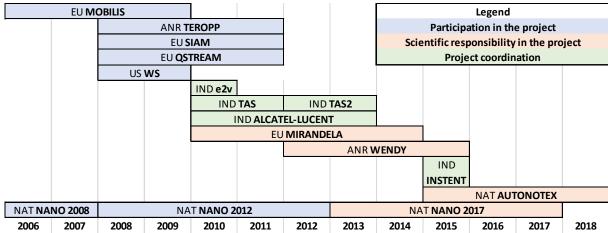

| 6.5.                                        | Col                                                                        | laborative projects                                                                                                                                                                                      | 126                             |

| 6.6.                                        | Pat                                                                        | ents                                                                                                                                                                                                     | 130                             |

| Chapte                                      | er 7                                                                       | Conclusion                                                                                                                                                                                               | 131                             |

| •                                           |                                                                            |                                                                                                                                                                                                          |                                 |

| Annex                                       | A                                                                          | Chip gallery                                                                                                                                                                                             | 133                             |

|                                             |                                                                            |                                                                                                                                                                                                          |                                 |

| Annex                                       | В                                                                          | Scientific publications                                                                                                                                                                                  | 145                             |

| Annex<br>B.1.                               |                                                                            | Scientific publicationsliographical summary                                                                                                                                                              |                                 |

|                                             | Bib                                                                        | •                                                                                                                                                                                                        | 145                             |

| B.1.                                        | Bib<br>Pub                                                                 | liographical summary                                                                                                                                                                                     | 145                             |

| B.1.<br>B.2.<br>B.2                         | Bib<br>Pub                                                                 | liographical summarylication list                                                                                                                                                                        | 145<br>147                      |

| B.1.<br>B.2.<br>B.2<br>B.2                  | Bib<br>Pub<br>2.1.                                                         | liographical summaryblication list                                                                                                                                                                       | 145<br>147<br>147               |

| B.1.<br>B.2.<br>B.2<br>B.2                  | Bib<br>Pub<br>2.1.<br>2.2.                                                 | liographical summary                                                                                                                                                                                     | 145<br>147<br>147<br>148        |

| B.1.<br>B.2.<br>B.2<br>B.2<br>B.2<br>B.2    | Bib<br>Pub<br>2.1.<br>2.2.<br>2.3.                                         | liographical summary                                                                                                                                                                                     | 145<br>147<br>147<br>148<br>151 |

| B.1.<br>B.2.<br>B.2<br>B.2<br>B.2<br>B.2    | Bib<br>Pub<br>2.1.<br>2.2.<br>2.3.<br>2.4.                                 | liographical summary                                                                                                                                                                                     | 145<br>147<br>147<br>148<br>151 |

| B.1.<br>B.2.<br>B.2<br>B.2<br>B.2<br>B.2    | Bib<br>Pub<br>2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.<br>2.6.                 | liographical summary  Peer-reviewed international journals – Regular papers  Invited conferences  International conferences  National conferences  Other communications                                  | 145<br>147<br>148<br>151<br>152 |

| B.1. B.2. B.2 B.2 B.2 B.2 B.2 B.2 B.2       | Bib<br>Pub<br>2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.<br>2.6.<br>2.7.         | liographical summary  plication list  Peer-reviewed international journals – Regular papers  Invited conferences  International conferences  National conferences  Other communications  Book chapters   |                                 |

| B.1. B.2. B.2 B.2 B.2 B.2 B.2 B.2 B.2 B.2   | Bib<br>Pub<br>2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.<br>2.6.<br>2.7.<br>2.8. | liographical summary  Peer-reviewed international journals – Regular papers  Invited conferences  International conferences  National conferences  Other communications  Book chapters  Seminars         |                                 |

| B.1. B.2. B.2 B.2 B.2 B.2 B.2 B.2 B.2 B.2 B | Bib<br>Pub<br>2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.<br>2.6.<br>2.7.<br>2.8. | liographical summary  Peer-reviewed international journals – Regular papers  Invited conferences  International conferences  National conferences  Other communications  Book chapters  Seminars  Thesis |                                 |

# Antoine FRAPPÉ, PhD

20 rue du Quai 59110 La Madeleine, France Mobile +33.6.64.35.09.41

E-mail: antoine.frappe@yncrea.fr Born 27 Aug 1981 in Lille, France Office +33.3.59.57.44.09

## **Associate Professor in Electrical Engineering Head of Integrated Circuit Design Research Group**

#### **EDUCATION**

PhD in Microelectronics University of Lille, France. 2007

"All-digital RF signal generation using  $\Delta\Sigma$  modulation for mobile communication terminals"

2004 Master degree - Microwave and Microtechnologies - Grade B - ranking 1st

University of Lille, France.

2004 **Engineering diploma - Major in Microelectronics.**

Institut Supérieur de l'Electronique et du Numérique (ISEN), Lille, France.

#### PROFESSIONAL EXPERIENCE

2009 -Yncréa Hauts-de-France - ISEN Lille, France

Associate Professor / Head of the Integrated Circuit Design Research Group

Berkeley Wireless Research Center, University of California, Berkeley, CA

Fulbright Visiting Postdoctoral Researcher

2007 - 2008 IEMN – ISEN – STMicroelectronics, Lille, France

Research Associate on RF circuit design

2004 - 2007 ISEN, Lille, France

Teaching Assistant in Electrical Engineering

#### **LANGUAGES**

French by mother tongue, Fluent English, Basics of German, Spanish and Mandarin

#### **PUBLICATIONS**

9 peer-reviewed journals / 29 international conferences / 3 book chapters / 320 citations / h-index: 8 Major publications:

- A. Frappé, A. Flament, B. Stefanelli, A. Kaiser, A. Cathelin, "An All-Digital RF Signal Generator Using High-Speed ΔΣ Modulators", IEEE Journal of Solid-State Circuits, vol.44, no. 10, pp. 2722-2732, Oct 2009

- C. Thakkar, L. Kong, K. Jung, A. Frappé, E. Alon, "A 10Gb/s 45mW Adaptive 60GHz Baseband in 65nm CMOS", IEEE Journal of Solid-State Circuits, vol.47, no. 4, pp. 952-968, Apr 2012

- A. Flament, A. Frappé, A. Kaiser, B. Stefanelli, A. Cathelin, H. Ezzeddine, "A 1.2 GHz Semi-Digital Reconfigurable FIR Bandpass Filter with Passive Power Combiner", Proceedings of the 34th European Solid-State Circuits Conference, ESSCIRC 2008, Edinburgh, Scotland, UK, September 15-19, 2008

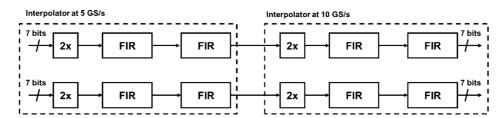

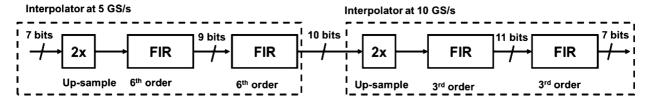

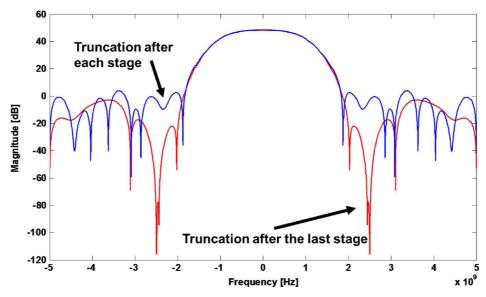

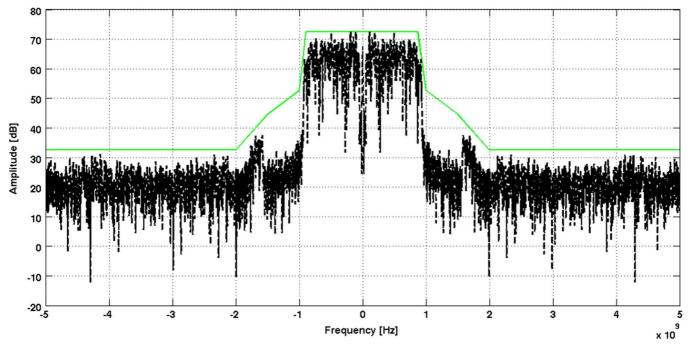

- J. Muller, B. Stefanelli, A. Frappé, L. Ye, A. Cathelin, A. Niknejad, A. Kaiser, "A 7 -bit 18th order 9.6 GS/s FIR up-sampling filter for High Data Rate 60-GHz Wireless Transmitters", IEEE Journal of Solid-State Circuits, vol.47, no. 7, pp. 1743-1756, Jul 2012

- F. Gebreyohannes, A. Frappé, A. Kaiser, "A configurable transmitter architecture for IEEE 802.11ac and 802.11ad standards", IEEE Trans. Circuits Syst. II-Express Briefs, 63, 1, pp. 9-13, January 2016

#### **GRANTS AND AWARDS**

Best student project 16-17 Yncréa HDF, for a project on audio keyword recognition

Best research project 15-16 Yncréa HDF, for a project on electronic textiles

Best Student Paper Award IEEE VLSI 2011, Kyoto, Japan

Fulbright grant obtained in 2008-2009 as a postdoctoral researcher at UC Berkeley, CA

#### **OTHER ACTIVITIES**

TPC Member IEEE ESSCIRC (2015 – 2016), IEEE ICECS (2014 – 2018), IEEE RFIC (2018 - ) IEEE Senior Member - Secretary and Treasurer IEEE Circuits and Systems (CAS) Society France Elected board member of Yncréa Hauts-de-France

# Acknowledgements

I would first like to thank Andreas Kaiser, without whom this work would not have been possible. He trusted me, let me lead the research team and has always been there to advise and support me. He still is today, and I hope it will continue for many years to come.

All the people of the team who work or have worked tirelessly to carry out ambitious and quality projects are heartily thanked, Bruno, Jean-Marc, Axel, Benoit, Crépin, Jonathan, Arnaud, Baptiste, Ilias, Fikre, Pietro, Stéphane, Walid, Matteo, Cristian, Dipal, Angel, Julien, Robin, Guillaume, Kevin, and of course Florence, without whom we would not do much. I take this opportunity to thank Valérie for her support for many years.

I express gratitude to the members of the SMART department of ISEN, especially Jean-François, with whom I share my office, and Emmanuel, who is a great head.

Thank you to all ISEN staff and students who are at the heart of our daily lives. Thanks to people at IEMN and in the technology platforms for their support.

Thanks to all the persons I collaborated with. It is always a pleasure to meet you during conferences, project meetings or teleconference calls. Special thanks to Andreia for the long-lasting collaboration in the ST-IEMN common lab.

I also thank the jury members and reviewers of this work. Your feedbacks are very important to me.

I thank all my friends and family for their active support.

My warmest acknowledgment goes to my wife Louise, who accompanies me on a daily basis, and to my three children, Valentine, Jean and Raphaël, who are adorable and allow me to be multi-tasking. I love you.

How not to forget someone in this acknowledgement part? Please excuse me if I did and to catch up, I would be happy to discuss with you about electronic stuffs or lighter topics around a nice beer ②.

# Chapter 1 **Introduction**

This manuscript is the result of more than 10 years of research in the Integrated Circuit Design Research Group at ISEN, an engineering school in Lille, France. This research activity is also part of a research group at IEMN in Villeneuve d'Ascq, on the campus of the University of Lille, where we benefit from the equipment and laboratory environments. In addition, a common lab has been active between STMicroelectronics and IEMN since 2003 and provides a common settlement for the development of ambitious projects taking into account industry-related considerations and for access to the most advanced integration technology nodes for our demonstrations. This fertile environment is the ground that allowed me to develop interesting research topics, which are mainly discussed and detailed in this manuscript. The philosophy and essence of the work is to start by studying specific concepts and to develop systems that can prove the validity and utility of the proposed concept. We then move towards hardware demonstrations in the form of the design, fabrication and measurement of integrated circuits. In this manuscript, you will find an overview of the results of the research, where the selected contributions are detailed and placed in the appropriate context.

This manuscript is composed of 7 chapters and two annexes:

- After this introduction, the second chapter is entitled "Research directions" and is an attempt to trace the paths that led me to the research presented here.

- The technical contributions are presented in Chapter 3 and 4. They detail the contributions to digital RF transmitters and baseband circuits for mmW receivers, respectively. In the first chapter on digital transmitters, I have tried to highlight the many works thematically, drawing on the main challenges in digital RF transmitters, rather than a chronological description. I hope that the reader will find an interest in the concepts that are demonstrated and that it will open new ideas and research directions, whether for digital RF transmitters or applied to other areas of research, for example, optical links or body area communication systems. The next section on

baseband circuits highlights three research works on energy-efficient systems for high data-rate receivers. It is partly related to my postdoctoral experience at UC Berkeley and includes further work on the same topic.

- In Chapter 5, research perspectives are developed. I want to emphasize here that the focus is now on energy-efficient systems for smart embedded devices. In fact, the Internet of Things (IoT) connects devices and objects with built-in sensors and has to deal with tons of data to be transmitted, while artificial intelligence (AI) brings intelligence to machines. Behind the idea of near-sensor computing (also known as edge computing or AIoT for Artificial Intelligence of Things), we want to include analysis and decisions as close as possible to the source of sensed data, by developing an energy-efficient integrated hardware. Investigations include audio signal processing (for local tasks such as voice activity detection, speech recognition or event detection) and biological signal processing (ECG, ECoG, etc.) for body area networks. Implementation issues will also be addressed by examining body-coupled communications or connected textiles.

- Chapter 6 provides a detailed list of professional activities related to the research works. This includes student mentoring and supervision, teaching activities, involvement in the national and international academic context, such as project expertise, reviews, Ph.D. juries or membership in conferences, local administrative duties and collaborative projects.

- Finally, a general conclusion is drawn in Chapter 7.

- In the first Annex, I wanted to describe a gallery of chips, offering an overview of the diversity of the fabricated chips and a brief description of the technical details.

- The last Annex concerns scientific publications. A short summary is given at the beginning, followed by the complete list of publications and the reproduction of 8 selected publications for easy reference.

I hope you will like to read as much as I liked to write this manuscript!

# Chapter 2 **Research directions**

Opportunities, fruitful encounters, and thoughtful choices trace a path in the research landscape. This chapter aims at relating my professional career path in relation to the research context and to expose the main research directions taken.

## 2.1. Passion for electronics

I have always been curious about electronic systems and how they work. My father injected me the virus of electronics at a very early age. He was CTO of a small local company delivering custom-made audio and video electronic products, like commutation matrices or PAL/NTSC conversion modules. I remember helping him assemble and weld PCB boards all day long on the production line. He even offered me a multimeter and soldering iron as a birthday gift.

Having spent my childhood in Dunkerque, it was natural for me to study electrical engineering at ISEN (Institut Supérieur d'Electronique et du Numérique) in Lille since it would fulfill my desire for technical deepness in this field. I discovered many domains, as diverse as telecommunication systems, computer science, quantum physics, cryptography, or acoustic modeling. I even ended up studying the details of a piezoelectric sensor design and simulating it with Finite Element Method (FEM)-based tools through a project and an internship in a start-up in Besançon that develops systems for non-intrusive defect detection.

As I wanted to dig further into microelectronic systems, I discussed with several professors at ISEN that described me advanced research projects and registered to the microwave and micro technologies Master program at the University of Lille 1, with the goal to attain a degree that would allow me to pursue my studies in a Ph.D. program. I have then chosen to do my research internship in Pr. Andreas Kaiser's integrated circuit design group, at the same time as 3 other colleagues, including my friend Axel Flament. Dimitri Galayko supervised my work on digital  $\Delta\Sigma$  modulators. I got the engineering diploma from ISEN and the Master of Advanced Studies (Diplôme d'Etudes Approfondies–DEA) from the University of Lille 1 in 2004. Based on the results achieved in the DEA program, I received a research grant from

the Ministry of National Education, Higher Education, and Research to start a Ph.D. program supervised by Pr. Andreas Kaiser.

## 2.2. Ph.D. thesis on IC design and digital transmitters

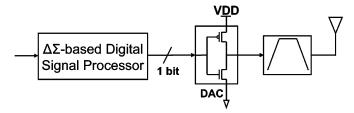

During my research internship at Master level, I performed system-level studies in Matlab of  $\Delta\Sigma$ -based transmitters and concretized that digital transmitters built upon these techniques would be a great research object for the Ph.D. thesis. At first, after compiling bibliographical data, one of the motivation point of this research was the publication in 2001 from Pr. Asbeck, Larson and Galton from UC San Diego entitled "Synergistic Design of DSP and Power Amplifiers for Wireless Communications" [1], in which they describe the potentiality of class-S amplifiers. In the conclusion, they derive future directions, reproduced below together with the associated figure.

As the speed of DSP advances, algorithms in which the DSP provides signals at RF can be envisioned (particularly for switching amplifiers, in which the inputs are inherently digital signals). An entirely digital implementation of the transmitter chain is shown in Fig. 13. Upconversion to RF and bandpass delta-sigma modulation accomplished digitally. With a 1-bit digital output, the inaccuracies of high-resolution digital-to-analog converters at high frequency can be circumvented. In the scenario shown,

Fig. 13. Comparison of traditional wireless transmitter architecture, based on analog circuits, with a possible DSP-based architecture.

the clock frequency of the DSP is 4× higher than the center frequency of the RF signal. The digital transmitter potentially offers many benefits, including programmability and reconfigurability, absence of tuning or aging problems, as well as easy integrability and testing. It can be an important element in a "software defined radio".

No need to explain that when I came to read these statements, the objectives of my research stand clear. I wanted to go there! My work focused on proposing solutions to generate RF signals with only digital components. Digital gates were available in design kits in 130 nm and 90 nm CMOS, but preliminary investigations on straight-forward structures showed speed limitations. So, I re-opened the bedside book from Jan Rabaey on digital integrated circuits [2] and designed my computation cells. Selecting an effective logic style was not enough, and I needed to think about the structural approach to the problem. During a visit to

the LIP6 laboratory in Paris, a short discussion about the issues I faced opened a large new panel of possibilities. I went on exchanging with Raphaël Daouphars about redundant arithmetic schemes and how to do the required operation from an arithmetic computational point of view. This is the beauty of inter-disciplinarity since this meeting was the turning point to bring about high-speed delta-sigma modulators (I would learn later that the straightforward approach would be reachable in more advanced technology nodes). I built a first  $3\times1$  mm² 96-pad 90 nm chip, in which we could only characterize the output stage since there were huge supply variations in the clock domain that prevent proper operation. I learned a lot in understanding the incorrect behavior and re-spun a second successful version, now sizing  $4\times0.8$  mm², counting 103 pads and code-named Fulbert II. The obtained results on this prototype chip matched the expected ones and we published the work in the IEEE Journal of Solid-State Circuits [3], the premier journal covering integrated circuits.

The diversity of technical challenges and acquired experience is large as the Ph.D. work has included system-level behavioral modeling, integrated circuit design in advanced CMOS technologies, custom packaging, test, interfaces, PCB design, FPGA prototyping and programming, and hands-on lab measurements of the demonstrator. Even if I performed an academic thesis, the Nano 2008 program and STMicroelectronics – IEMN common lab supported the developments. I acknowledge the constant help of ST staff through regular meetings and training.

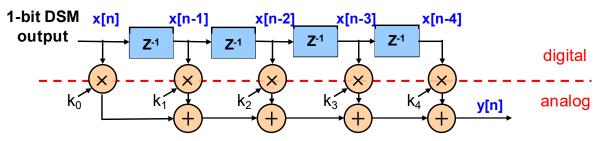

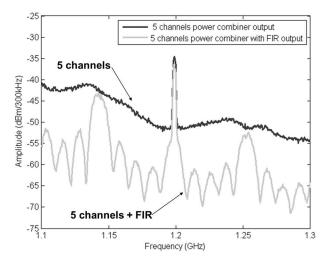

Though the digital signal produced by the delta-sigma modulator is of high fidelity in the considered band, the process of noise shaping pushes the noise outside the band of interest thus polluting the complete spectrum with large noise. In parallel to my investigations, Axel Flament studied means such as a passive power combination to boost the channel power and to include noise filtering using mixed-signal concepts such as semi-digital FIR filtering. This work showed enough originality to pave the way to further concepts.

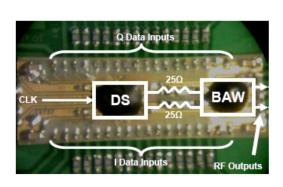

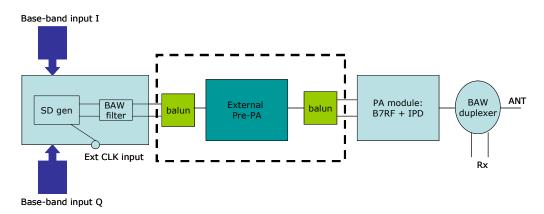

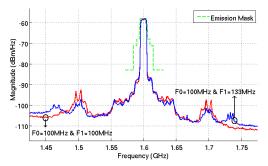

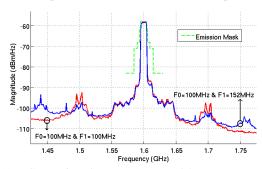

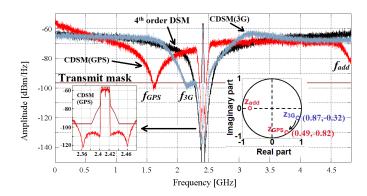

We extended our work in the MOBILIS European project, in which larger demonstrators included the developed circuits to promote transmitter chains based on bulk acoustic waves (BAW) devices. We have then shown that BAW filters can solve the problem of noise filtering outside the band of interest and on the nearby receive bands.

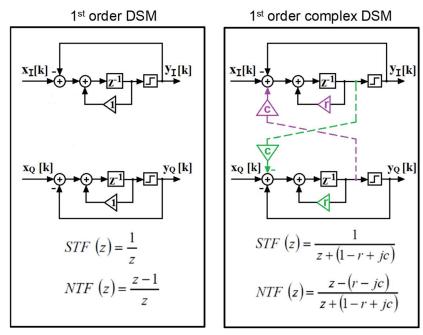

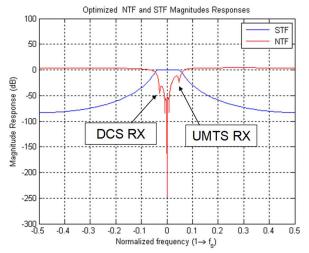

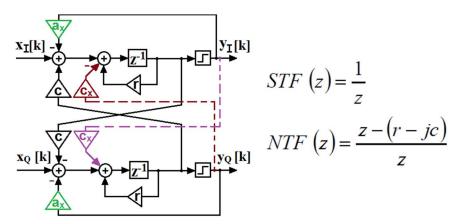

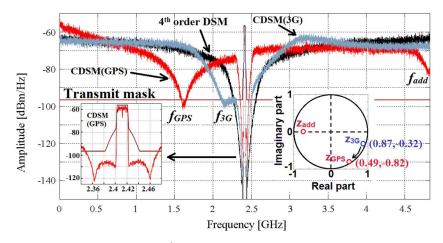

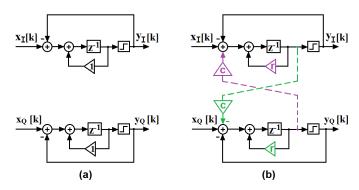

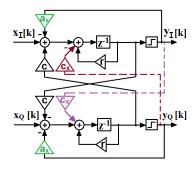

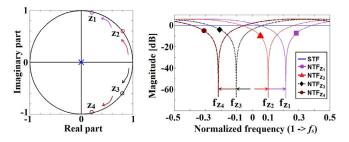

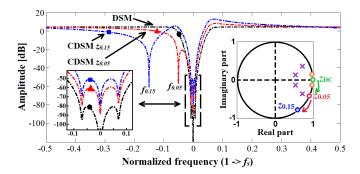

Finally, as we continued the development of digital transmitters, Crépin Nsiala Nzéza, a postdoctoral researcher with a background on telecommunication systems, joined the group and we have investigated complex digital delta-sigma modulators in which the noise transfer function can be engineered to relax the filtering requirements in selected frequency bands.

## 2.3. A year of discoveries at UC Berkeley

I had the great opportunity to get selected by the Franco-American Fulbright Commission to pursue research for a year in an American institution. My application has focused on circuit design for future communication systems in a renowned group at UC Berkeley. The Fulbright grant not only offers a financial support for this stay but also a complete experience, through the Fulbright enrichment program and the fruitful meeting of people from different horizons and cultures. Throughout the stay, I also discovered how prestigious being a Fulbrighter is in the US.

I worked in Elad Alon's group at the Berkeley Wireless Research Center as a post-doctoral scholar through the Fulbright program from September 2008 to September 2009.

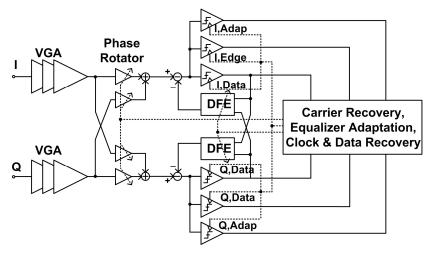

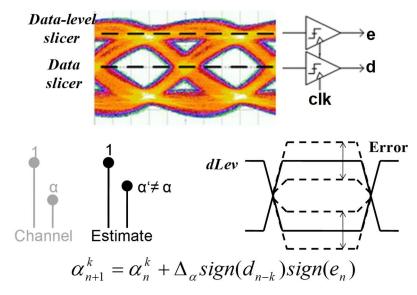

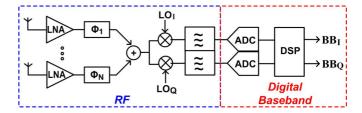

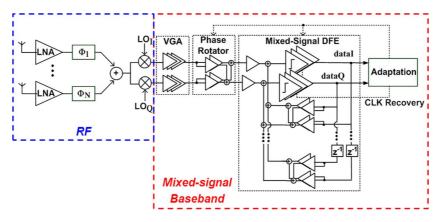

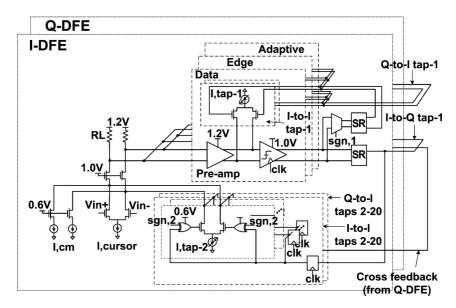

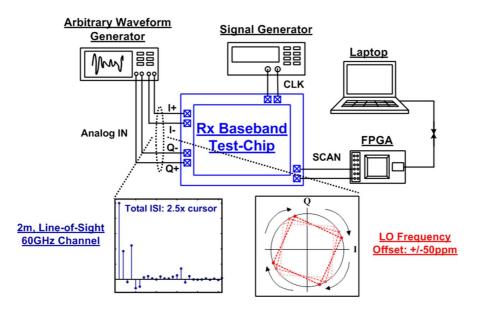

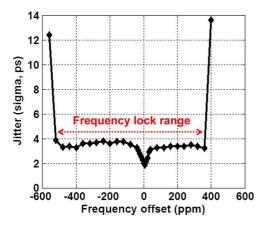

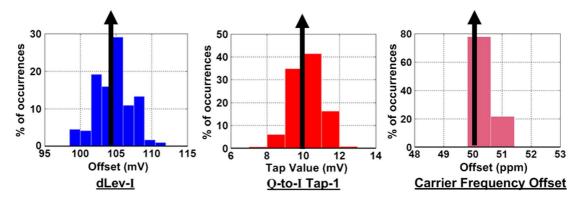

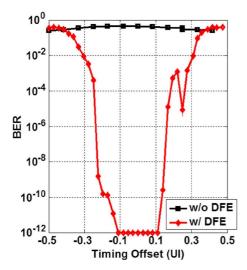

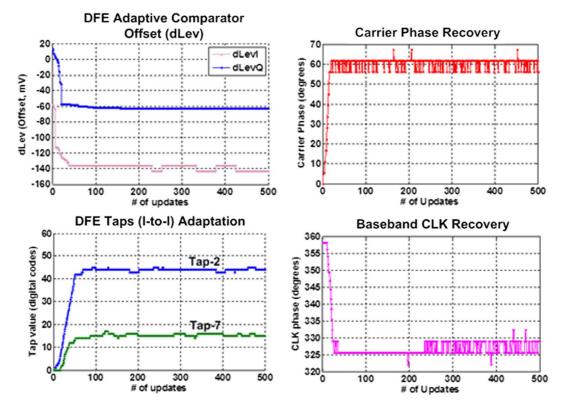

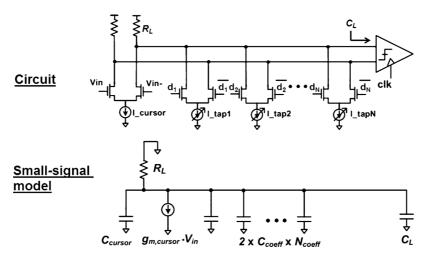

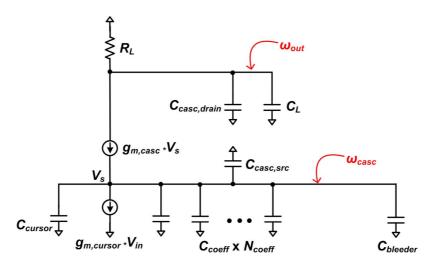

During my time in the lab, my research focused in two areas: (1) clock distribution for a wafer-scale radio using standing wave oscillators, and (2) on the architecture and implementation of an energy-efficient 10 Gb/s baseband for 60 GHz wireless communications. The second project resulted in a higher overall impact on the community.

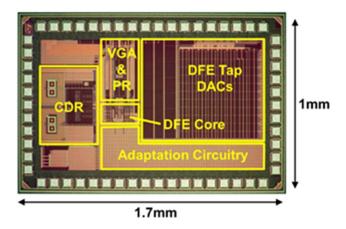

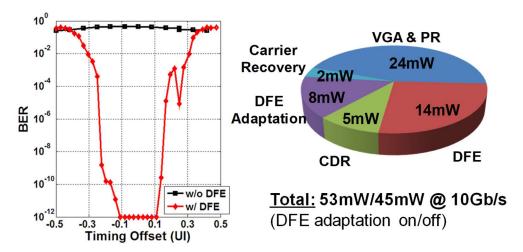

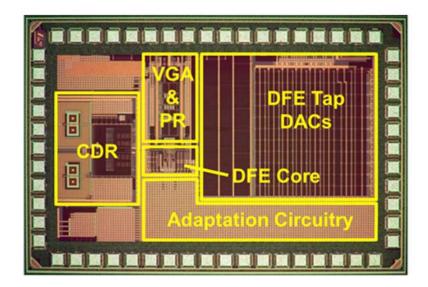

The main motivation for this work was to reduce the power consumption of such 60GHz basebands to enable multi-Gb/s wireless links within mobile devices such as a cell-phone. Our approach breaks from traditional transceiver design paradigms, and rather than perform most of the high-speed signal processing in the digital domain, do so in the mixed-signal domain. The advantage of this approach is that at the dynamic ranges of interest in this system, analog processing requires less power than digital processing. Such a design still requires large digital processing to adapt and control the analog circuitry. The experimental results from the transceiver design (which dissipated ~50 mW at 10 Gb/s in a 65 nm process — an order of magnitude better than earlier designs) were published in the 2011 IEEE Symposium on VLSI Circuits in June 2011 [4], received the Best Student Paper Award and an extension appeared in the IEEE Journal of Solid-State Circuits in 2012 [5].

During the time I spent in UC Berkeley, Jonathan Muller started a CIFRE Ph.D. program with STMicroelectronics and IEMN and joined the Berkeley Wireless Research Center as a visiting student. I worked with him and encouraged his research towards ultra-high-speed signal processing for a 60 GHz transmitter baseband. His developments helped in understanding limits of high-speed operation in advanced CMOS technology.

# 2.4. Assistant Professor position at ISEN Lille

When I came back from the US in 2009, I got an Assistant Professor position in the electrical engineering department at ISEN Lille, under the responsibility of Andreas Kaiser. I joined the group I used to work with, so I knew the other professors and appreciated the context and research methods. As an Assistant Professor, I undertook 3 main objectives. The first duty concerned teaching responsibilities. I oversaw the introductory courses in analog and digital electronics for Computer Science students and more advanced courses related to electronic systems. Teaching involved diverse learning sequences, ranging from traditional lectures to codesign-based projects. The second mission concerned establishing a research activity within the group. The tasks went from defining potential impactful subjects, submitting applications to gather funding and support, supervising Master or Ph.D. students, and following technical advancement of granted projects. Developing industrial collaborations and contracts makes up the third direction.

The STMicroelectronics – IEMN common lab was established for many years and supported by the Nano 2012 national program. It offered a privileged link with ST staff and access to advanced CMOS technology. Thus, the research in integrated circuit design was positioned to leverage these digital technologies by showing the potential for analog and mixed-signal integrated systems.

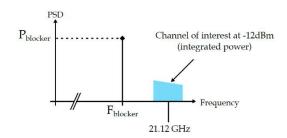

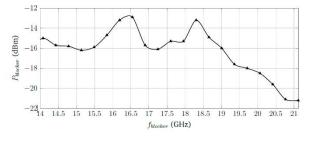

I contributed to several already started projects. The TEROPP ANR project concerned the study RF terminals for opportunistic radio applications, while in the European MEDEA+ SIAM and QSTREAM projects, the focus was on silicon-based high data-rate communication systems in the mmW bands. In this context, we started two Ph.D. thesis: Arnaud Werquin studied digital RF power amplifiers (PA) and Baptiste Grave considered baseband systems for mmW applications. They both came up with very innovative ideas, such as a multi-rate multi-path approach to deal with image replicas in digital RF PA or subsampling methods to demodulate mmW signals.

In 2010, we collaborated for the launch of the ENIAC MIRANDELA project, which involved over 30 European partners. I was at first responsible for the work carried by ISEN Lille, but as our position evolved inside the project, I eventually led the cluster on mmW systems and sensors and co-animate the work-package on the full application demonstrator. This was rewarding and challenging since I coordinated the work from many institutes,

including researchers from CEA-Leti, Aalto (Finland), IEMN, STMicroelectronics, and ST-Ericsson.

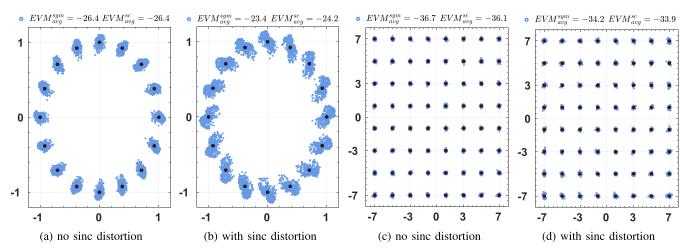

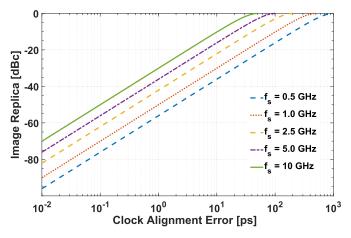

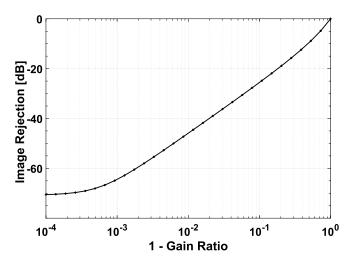

Apart from a strong collaboration with STMicroelectronics, I started other industrial contracts with e2v, Thalès Alenia Space, and Alcatel-Lucent. e2v is a leader in high-speed high-resolution data converters and solicited us for a study on delta-sigma data converters. I worked with them on the Verilog-AMS modeling and simulation of an integrated high-speed converter with excessive in-loop delays. Thalès Alenia Space (TAS) considered our developments in digital RF transmitters and wanted to explore the architectural solutions for wideband signals (>250 MHz) in the Ku band (12 – 18 GHz). The collaboration with TAS started with a Master-level internship (Guillaume Rembert), followed by some specific studies on an in-depth understanding of LO leakage and image rejection due to IQ mismatch.

The collaboration with Alcatel-Lucent consisted in the study and design of a delta-sigma-based digital RF transmitter for base-station applications. We built a complete demonstrator composed of a 4.2×2 mm² 40 nm integrated circuit. The integrated delta-sigma digital quadrature modulators operated up to 8 GS/s and delivered a 4-bit output, compatible with the input of an RF PWM InP ASIC under development. I am glad to have led this very ambitious and successful project, which has been a collaborative work with my colleagues Axel Flament, Baptiste Grave and Bruno Stefanelli. Scientific publications on these industrial collaborations are lacking, but we produced many internal reports, listed in the publications list in Annex A.

# 2.5. ICD research group leadership

In late 2011, the ISEN Lille electrical engineering department has been re-organized and named SMART (as an acronym for Systèmes Microélectroniques, Automatique, Robotique, Telecommunications in French), supervised by Emmanuel Dubois. I took the responsibility of the integrated circuit design (ICD) research group. The missions involved managing and animating the group, defining the research directions, and dealing with financial, HR and administrative aspects of the research group. I was further responsible for finding contractual opportunities and executing current collaboration contracts. I took part in the ISEN Lille Research Council and Executive Committee-at-Large.

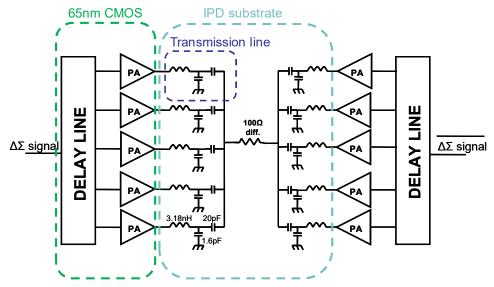

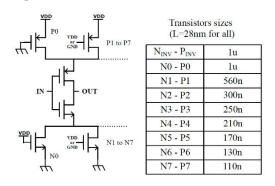

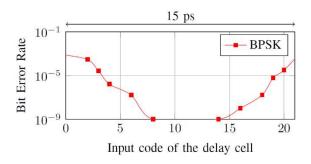

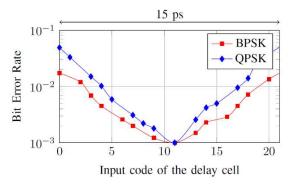

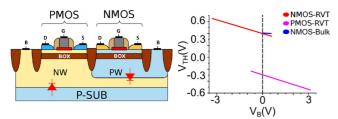

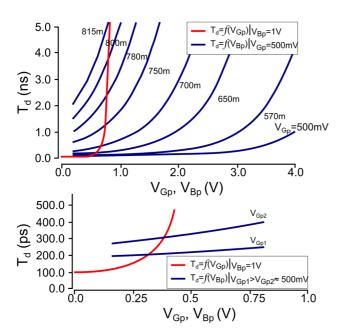

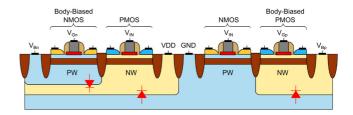

While the MIRANDELA project and industrial collaboration with Alcatel-Lucent on communication systems were running, I was eager to develop some new trends into our research scope. Through an invited lecture at CMOS Emerging Technologies Symposium in Whistler, Canada, about digital transmitters, I attended a short presentation by Mariya Kurchuk, a former Ph.D. student in Yannis Tsividis' group at Columbia University on continuous-time digital signal processing (CT DSP) [6]. I found interest in these computation systems and the discussions I had with her showed all the potential and advantages of these solutions—and the associated challenges. Back in Lille, since we carried investigations on mmW baseband receiver architectures, the event-driven nature of the continuous-time digital signal processing seemed to offer great interest as it would remove the problems associated with the clock recovery and phase interpolation implementation. On top of this, digital CT filters proved competitive compared to analog implementations and envisioning an equalization scheme based on discrete events would be helpful for channels with long responses, such as 60 GHz channels. This has set the objectives of Ilias Sourikopoulos' thesis. His work contributed to the design of tunable digital delay cell that leverages the 28 nm FDSOI technology features and showed state-of-the-art performance.

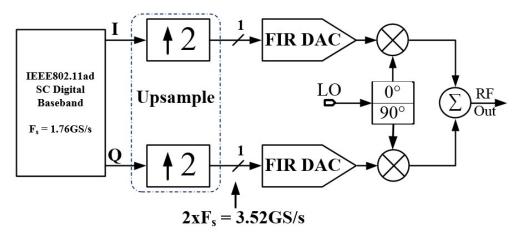

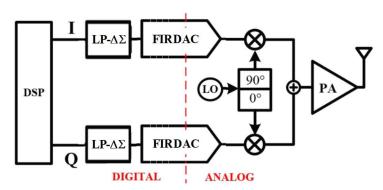

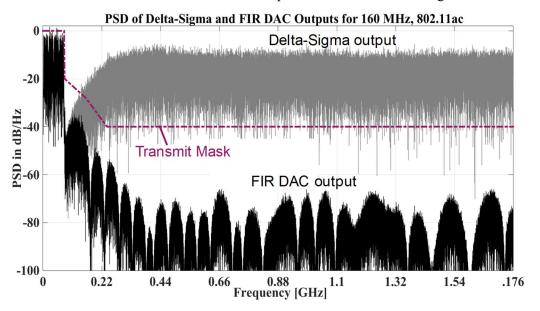

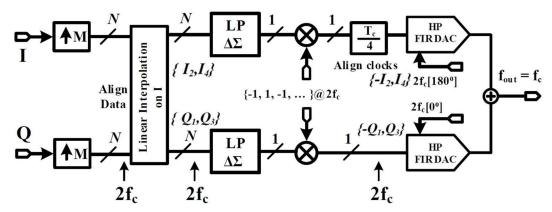

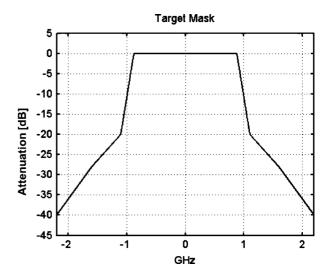

Even though systems for communications in the 60 GHz band standardized, scenarios of deployment remained unclear and developments of circuit-level architectures for these bands stayed at a low level of maturity for integration into portable devices. With STMicroelectronics and IMS Bordeaux, we discussed the scenarios and a convergence of the WiFi (the emerging 802.11ac) and WiGig (802.11ad) systems into a configurable and shared structure sounded to be interesting to investigate. From an implementation point of view, the complexity of the interfaces was similar with a narrow bandwidth (20 to 40 MHz) and high resolution on one side, and a wide bandwidth (>1.5 GHz) and low resolution on the other side. We built the WENDY project that got accepted into the ANR INFRA program. This has led to the developments of Fikre Tsigabu Gebreyohannes' thesis on a configurable semi-digital filtering DAC (FIR-DAC), whose number of coefficients is adaptable and act as a reconstruction filter for the WiFi signals and as a channel filter for WiGig signals.

The STMicroelectronics – IEMN common lab renewed in the frame of the Nano 2017 program and I took an active part in this initiative as co-chair of the theme on Communication Systems (together with Andreia Cathelin from STMicroelectronics and Nathalie Rolland from CSAM group at IEMN). The work program targeted to show the potentiality of the 28 nm FDSOI technology, through ASIC design and integrated demonstrators. This created a favorable framework for new Ph.D. students: Cristian Marin investigated integrated digital transmitters and Matteo Causo started a research path on neuro-inspired computing architectures in collaboration with Jan Rabaey at UC Berkeley. Later, the same framework

helped in funding further Ph.D. subjects. Dipal Ghosh worked on multi-Gbps chip-to-chip communications as a collaborative effort between CSAM group and ours at IEMN, Angel Gonzalez pursued investigations on continuous-time DSP for feature extraction on audio signals and Robin Benarrouch started as a CIFRE Ph.D. student on integrated human body communications systems, again in collaboration with UC Berkeley. The ST – IEMN common lab creates a fertile ground on which we can aggregate competencies and attract complementary funding. I hope the support of future nation-wide programs for Microelectronics could sustain these efforts.

Since research funding is often very opportunistic, we got contacted by the Centre Européen des Textiles Innovants (CETI) in Tourcoing, who was building a consortium of companies, research centers, and academic groups to develop the future industrial sector on connected and autonomous textiles. This industrial project named AUTONOTEX emerged within a month and a half and got accepted to the PIAVE call from the BPI. I have never experienced such a fast build-up for a consortium involving 13 partners. A strong collaboration between the partners - Nicomatic (electrical connectors manufacturer), Percall (IoT solutions provider) and Mulliez-Flory (professional clothing company) - helped build a connected safety sheet for disoriented hospital patients. In this project, I want to point out the challenges related to inter-disciplinarity. Exchanging ideas and concepts on electronics and integrated systems with people specialized in textile dyeing or in polymer chemical analysis leads to a need for a non-negligible volume of pedagogy in explaining developments and agreeing on potential solutions. Meeting the project objectives entails understanding partners requests and constraints. This requires efforts but is valuable when achieved.

I want to close this part by mentioning that the research subjects we are carrying are evolving and that the focus is shifting towards low-power embedded systems for smart sensors. We have the competences to show novel integrated architectures to overcome the challenges of near-sensor computing. Benoit Larras joined as a new faculty in the group to build upon these new perspectives. He has a complementary education in the design of integrated silicon neural networks.

## 2.6. Conclusion

My experience as a researcher is personally very fruitful and I want as a conclusion to underline some rewarding activities. First, supervising students, so that they can eventually

defend their work and achieve their career goals, is a day-to-day challenge. This includes follow-ups and weekly meetings, as well as personalized support and coaching. I maintain an open-door policy so that the Ph.D. students are always welcome to come and discuss any matter with me. In Section 6.1, a list of M.Sc. students, Ph.D. students, and post-doctoral researchers I supervised details the position in industry or academia they are holding after graduation. I am very grateful to see that I was able to reveal the potential of the students I followed. I am convinced the HDR diploma will confirm my ability to lead a research group and supervise students.

Additionally, since the HDR also gives the opportunity to report on thesis works, I would be very happy to contribute to the evaluation of the research outcome of Ph.D. students from other laboratories in France. I have already been active in Ph.D. committees in other countries (detailed in Section 6.3.2). I served as an opponent at Chalmers University of Technology in Gothenburg, Sweden and as a preliminary examiner at Victoria University, Melbourne, Australia and at Aalto University, Helsinki, Finland. These were interesting and rewarding experiences.

Finally, I am regularly solicited for expertise works, reviews of journal papers and participation to technical program committees for several conferences. A complete list can be found in 6.3. This promotes the level of research I try to carry within my field of expertise and opens new horizons.

The story goes on...

# 2.7. Bibliography

- [1] P. M. Asbeck, L. E. Larson, and I. G. Galton, "Synergistic design of DSP and power amplifiers for wireless communications," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 11, pp. 2163–2169, 2001.

- [2] J. Rabaey, A. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits : A Design Perspective (2nd Edition)*. Prentice Hall, 2003.

- [3] A. Frappe, A. Flament, B. Stefanelli, A. Kaiser, and A. Cathelin, "An All-Digital RF Signal Generator Using High-Speed Delta-Sigma Modulators," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2722–2732, Oct. 2009.

- [4] C. Thakkar, Lingkai Kong, Kwangmo Jung, A. Frappe, and E. Alon, "A 10Gb/s 45mW adaptive 60GHz baseband in 65nm CMOS," in 2011 Symposium on VLSI Circuits Digest of Technical Papers, 2011, pp. 24–25.

- [5] C. Thakkar, L. Kong, K. Jung, A. Frappe, and E. Alon, "A 10 Gb/s 45 mW Adaptive

- 60 GHz Baseband in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 4, pp. 952–968, Apr. 2012.

- [6] M. Kurchuk, C. Weltin-Wu, D. Morche, and Y. Tsividis, "GHz-range continuous-time programmable digital FIR with power dissipation that automatically adapts to signal activity," in *2011 IEEE International Solid-State Circuits Conference*, 2011, vol. 53, no. May 2010, pp. 232–234.

# Chapter 3 Contributions to Digital RF

## **Transmitters**

This chapter will present research developments in the research group under my supervision around digital RF transmitters, from the origins of my PhD thesis work to recent demonstrations of integrated digital transmitters.

First, an introduction will explain why and how to move from traditional architectures to digital transmitters. An analysis of the existing concepts and architectures will be exposed, and this part will be concluded by presenting the key challenges. Then, the three subsections will develop specific research related to each challenge and show how our research has helped to address some of them. The structure of this chapter is not chronological. I chose to present the work thematically, using the many developments to illustrate the research carried out.

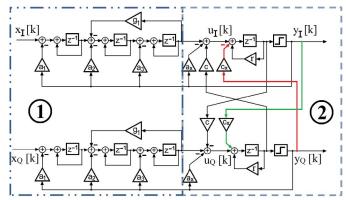

The first subsection will address the digital high-speed operation necessary to enable digital transmitters. It will consist of a description of my doctoral thesis work, focused on the digital generation of RF signals, followed by a more complete implementation of delta-sigma multibit modulators for base stations, in collaboration with Alcatel-Lucent. Time-interleaved delta-sigma modulation is then presented through a description of the work of Cristian Marin. Finally, high speed digital processing is pushed to its limit to reach bandwidths compatible with mmW frequency communications. Jonathan Muller has studied this last part.

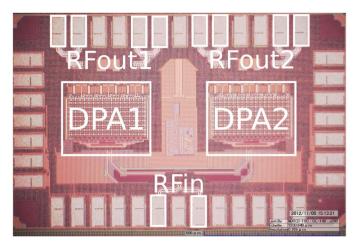

The next subsection discusses output stage topologies for embedded transmitters. It will briefly cover the use of an inverter-based output stage with a passive network combination and the integrated switched-capacitor preamplifier as part of a digital RF transmitter demonstrated by Cristian Marin.

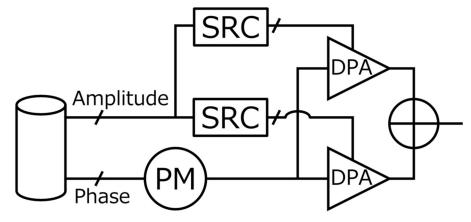

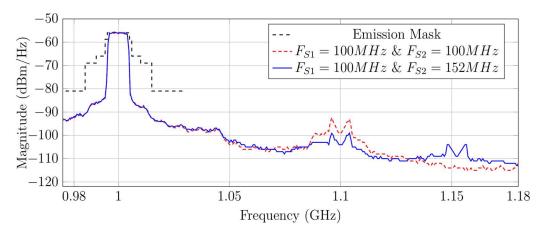

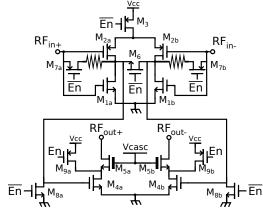

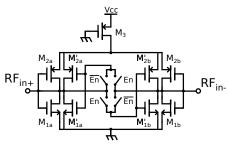

Last section deals with the management of out-of-band spurious emissions. Four contributions are identified here. The multi-rate multi-path approach for polar DPAs,

developed by Arnaud Werquin, is presented first. Then, techniques to deal with shaped quantization noise of delta-sigma modulators include the integration of analog bulk acoustic wave filters (MOBILIS project), the engineering of the noise transfer function (Crépin Nsiala Nzéza and Cristian Marin works) and finally the use of semi-digital FIR-DAC (Axel Flament, Fikre Tsigabu Gebreyohannes, Cristian Marin).

## 3.1. Introduction to digital RF transmitters

#### 3.1.1. Traditional transmitters

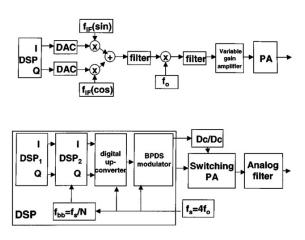

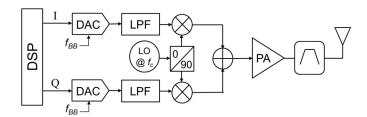

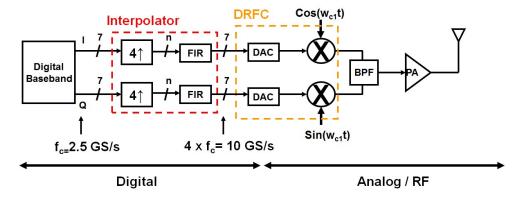

A traditional analog direct conversion quadrature transmitter architecture is shown in Figure 3-1. The generated quadrature I and Q signals are converted in the analog domain by DACs at a  $f_{BB}$  rate and then low-pass filtered to remove unwanted image replicas at multiples of  $f_{BB}$ . The quadrature baseband signal is then converted to the local oscillator frequency  $f_c$  before being amplified by the power amplifier and eventually band-pass filtered.

Figure 3-1 Traditional direct-conversion transmitter architecture including Digital Signal Processor (DSP), Digital-to-Analog Converters (DACs), Low-pass Filters (LPF), Local Oscillator (LO), and Power Amplifier (PA).

Environment-aware radios require the transmitters to reconfigure themselves and adapt their physical key settings to take into account, for example, a specific carrier frequency, signal bandwidth, dynamic range, or consumption target. A flexible transmitter, adjusted using the receiver's spectrum-sensed information, adds intelligence to the system [1], must meet existing wireless standards, and provide a scalable platform for future standards.

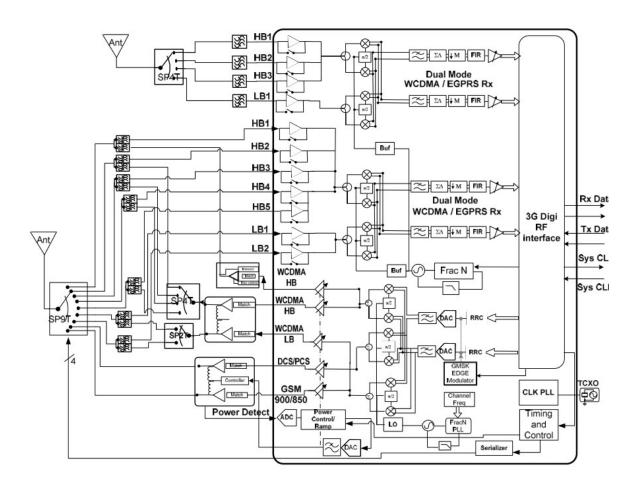

Single-chip multiband solutions have emerged and have proposed sharing the digital interface and most mixed-signal blocks, local oscillators, and mixers. However, many elements of the transmission and reception chain are still redundant, placed in parallel and activated on demand. In addition, the removal of external components, such as SAW filters, is in essential element of integrated transceivers. As an illustration, Skyworks highlighted at the ISSCC 2009 a 25 mm² 7-band 2G / 3G single-chip transceiver in 0.13  $\mu$ m [2]. Figure 3-2 shows the block diagram of the transmitter system, in which 13 discrete components (7 Page 26

duplexers / filters, 3 switches and 3 PA modules) are needed to meet the proposed standards and bands.

Figure 3-2 Block diagram of the multi-band single-chip transceiver presented in [2]

As advanced CMOS technologies are major drivers for digital signal processors, integrated radios have to deal with process scalability and major challenges of integrating radio-frequency (RF) functions into these digital intensive technologies [3]. In these technologies, the digital signal processing density scales with the technology, but performance and area of analog and RF components do not improve, and it becomes more difficult to meet the design specifications. Therefore, flexible RF front-end interfaces should rely primarily on digital-type circuits, while taking into account energy consumption, signal quality, and coexistence with other standards.

## 3.1.2. Switching to digital-intensive transmitters

#### a) Quadrature transmitters

In this context, there is a growing interest in digital-intensive RF transmitter solutions. Many topologies have emerged, from the simplest digital-to-RF converters to true digital

transmitters. This part offers an overview of each type of solution as well as the respective advantages and disadvantages.

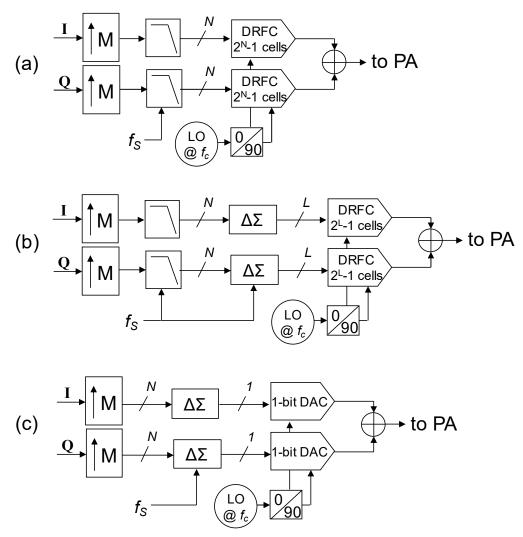

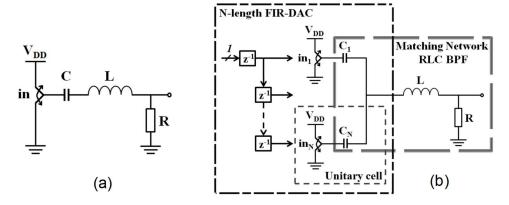

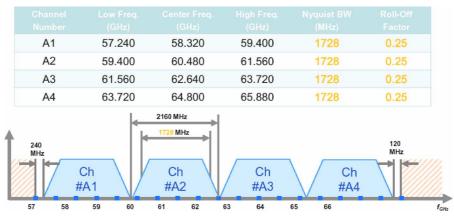

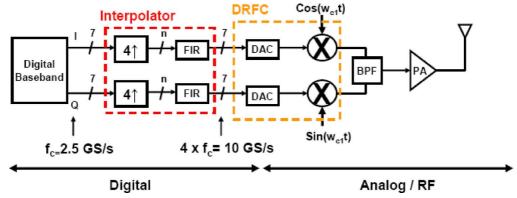

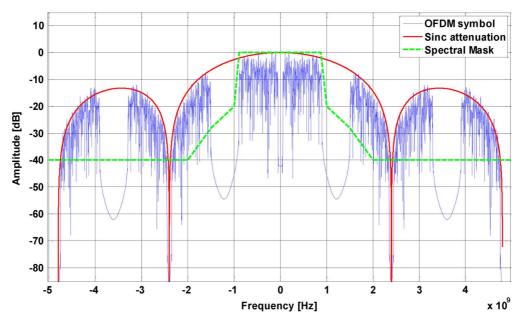

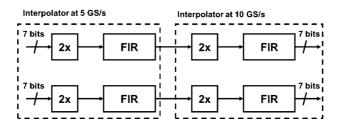

A digital-to-RF converter (called DRFC, RF-DAC or DDRM in the literature) is a unique block that combines the digital-to-analog conversion and the upconverting mixing process. Such an architecture is shown in Figure 3-4(a). This greatly simplifies the implementation of the circuit and reduces the sources of non-linearity and noise. The main difference from traditional architectures is that the baseband low-pass filter needed to eliminate DAC replicas at multiples of the sampling rate is removed. This transfers the constraint to the output bandpass filter. A simple solution to the problem of the image is to oversample the digital signals and to digitally filter the images beforehand, as shown in Figure 3-4(a) with a factor M. The filters are well-known digital interpolation filters, in which there is a compromise between the quality of the signal in the band and the possible attenuation of the images. The oversampling process pushes the image replicas away from the carrier and attenuates them considerably, but the increase of the sampling rates entails a not insignificant cost, since the energy consumption increases linearly with the frequency of operation. Significant work has been done on the digital-to-RF conversion from Nokia, imec, MediaTek and Delft UT research groups [4]-[8] with DRFC resolution between 10 and 13 bits and moderate oversampling ratios.

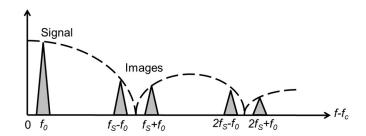

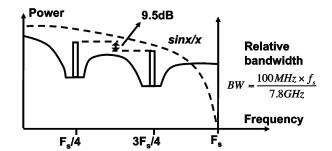

To illustrate the image problem, Figure 3-3 details the output spectrum of the DRFC block when working at a  $f_S$  sample rate. The images are present in the spectrum at offsets equal to  $f_S$  around the carrier frequency  $f_C$ . They are attenuated by the frequency response of a zero-order hold (ZOH) function. Note that these images may be attenuated by other functions if a different output waveform is used in the digital-to-analog conversion process. The presence of images can be very troublesome for two reasons. First, adjacent and alternate channels of the same standard may be disturbed by close-band image replicas. This is exacerbated for broadband signals where attenuations are lower when  $f_S$ - $f_0$  approaches  $f_0$ . In [7], the implemented DRFC can handle channels up to 154 MHz wide. Nevertheless, the sampling frequency  $f_S$  is about 300 MHz. This involves high image levels that interfere with other channels. Secondly, other coexisting standards may suffer from out-of-band spurious emissions. For example, the coexistence of a Wi-Fi transmitter and a GPS receiver on the same chip represents a considerable challenge because the sensitivity levels of the GPS receiver are extremely low (< -174 dBm/Hz) and the Wi-Fi transmitter sends noise and spurs in these bands [9].

Figure 3-3 Single-sided spectrum of the signal at the output of the DRFC assuming zero-order hold (ZOH) behavior and with  $f_0$ , the center frequency of the signal,  $f_S$  the sampling clock frequency and  $f_C$  the carrier frequency of the local oscillator.

Figure 3-4 Comparison of different architectures for digital transmitters. (a) Oversampled DRFC requiring high-speed high-resolution DAC. (b) DRFC based on oversampled  $\Delta\Sigma$  modulator with reduced resolution and shaped quantization noise (L<N). (c) Single-bit DAC based on oversampled single-bit  $\Delta\Sigma$  modulator.

The design of high-resolution multi-bit linear digital-to-RF converters is a challenge and can be alleviated by reducing the number of bits from the converter to relax the linearity requirements. Since oversampling is mandatory for digital transmitters,  $\Delta\Sigma$  modulation is a means of physically reducing the number of bits of the signal to be converted, while maintaining good performance and good resolution in a given bandwidth. In return, the quantization noise is increased outside this bandwidth. Thus, the  $\Delta\Sigma$  modulation trades off linearity and flexibility for out-of-band quantization noise. This is sketched in Figure 3-4(b) and has been extensively explored by many groups in [10]–[18], with RF-DAC resolutions between 3 and 10 bits.

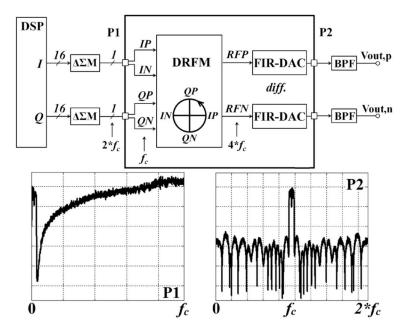

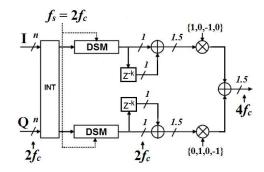

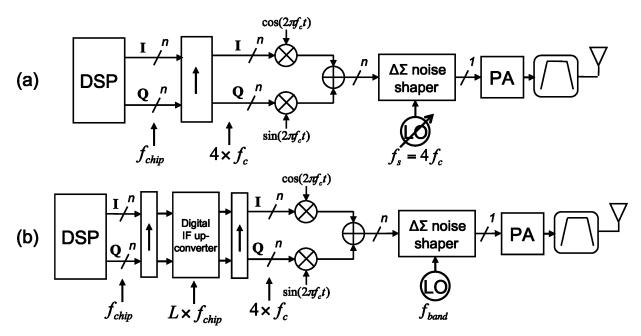

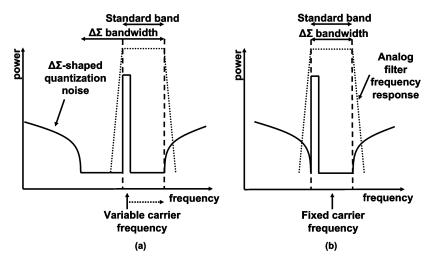

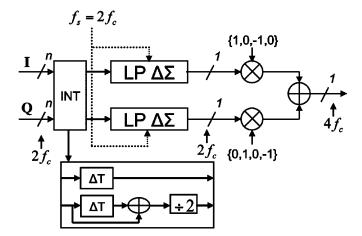

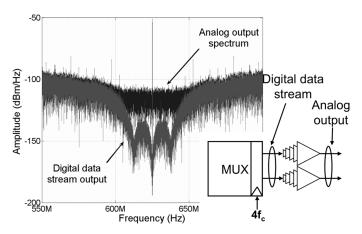

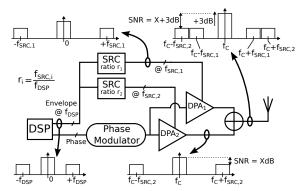

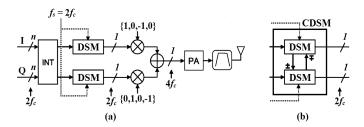

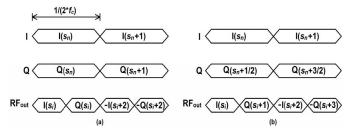

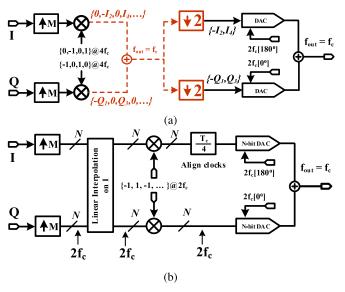

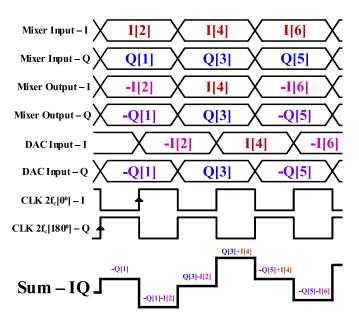

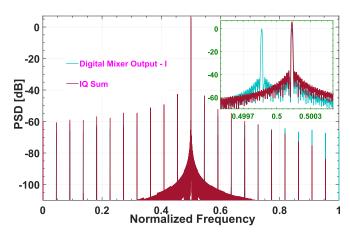

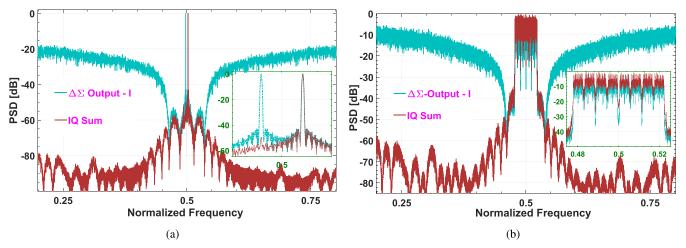

If the concept is pushed to the extreme case of single-bit  $\Delta\Sigma$  modulators as in Figure 3-4(c), a highly digital implementation for the baseband can be considered, as well as the design of digital upconverting mixers and efficient switched power amplifiers. The input data I and Q are oversampled to  $f_S$  with a high oversampling ratio. It should be noted that the digital oversampling filter can be a simple ZOH process because the resulting images will in all cases be smaller than the quantization noise added by the  $\Delta\Sigma$  modulation block. The data is quantized into a 1-bit high-speed data stream using low-pass  $\Delta\Sigma$  modulation. The resulting spectrum contains the initial information in the given bandwidth and only shaped quantization noise outside this band. The upconversion of this digital signal to a carrier frequency  $f_C$  is performed by a digital image-reject mixer [19]. If this block is operated at 4 times  $f_C$ , its behavior is similar to that of a multiplexer between I and Q input streams, providing the output sequence {I, Q, -I, -Q}. The minus sign in this expression indicates the logical inverse of the I and Q 1-bit values. Note that there is an inherent integer relationship between  $f_C$  and  $f_S$ .

Another important aspect of providing a 1-bit digital RF signal to the power amplifier is to be able to increase the efficiency of the output stage. Switching mode PAs (such as class D) are known to provide very high efficiency [20]. An ideal class D PA has a 100% drain efficiency in the absence of conduction or switching losses. This becomes all the more relevant as the output power is high, as is the case for transmitters in base station applications, and thus the power consumption of the previous digital stages becomes negligible.

In early 2000, a research group at University of California at San Diego demonstrated the concept of bandpass  $\Delta\Sigma$  modulation and class S amplification using a pattern generator and discrete NPN or FET transistors [21]–[23]. The first integrated demonstration in a 0.13  $\mu$ m CMOS process was presented at ESSCIRC 2004 by researchers at the Helsinki University

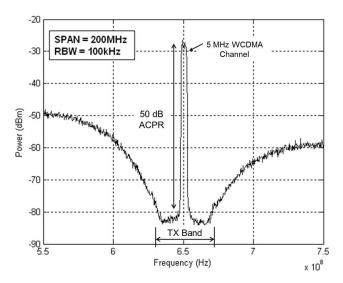

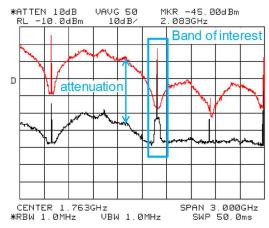

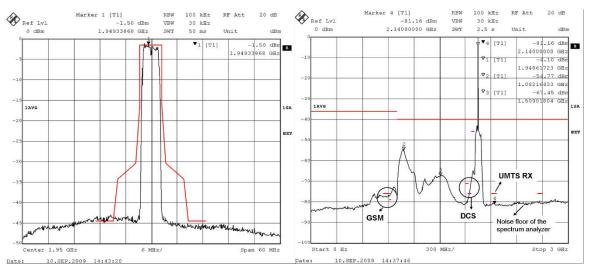

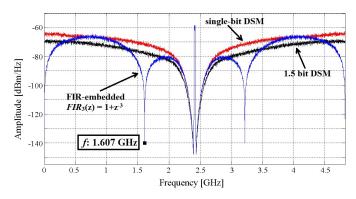

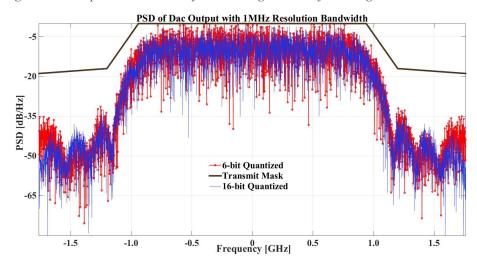

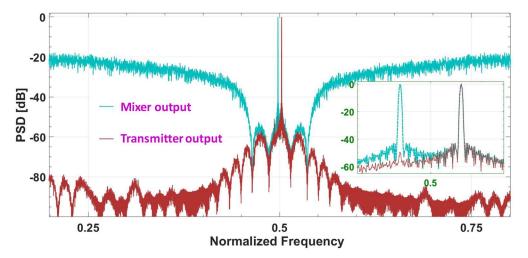

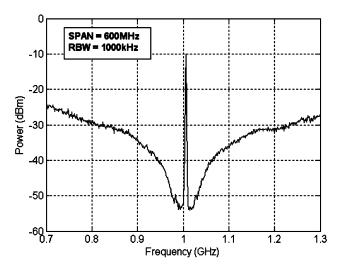

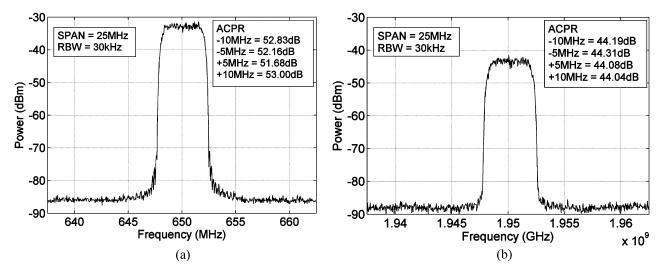

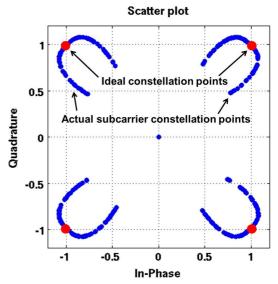

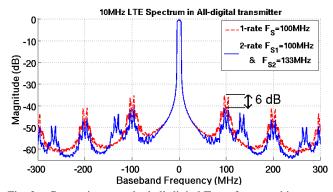

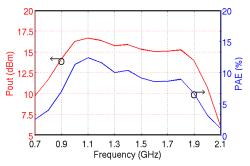

of Technology [24]. The IC generated GSM and WCDMA signals at a sampling frequency of 700 MHz, reaching a carrier frequency of 175 MHz. In 2008, Arizona State University [25] showed a more complete system in 0.25  $\mu$ m CMOS, including a 250 MS/s  $\Delta\Sigma$ modulator and a digital-IF-to-RF converter based on an analog mixer and semi-digital filtering. Higher frequency of operation and larger bandwidths were obtained through investigations conducted as part of my Ph.D. works at the University of Lille in 2008 [26], [27]. I designed a 90 nm CMOS IC that generates RF modulated channels in a bandwidth of up to 50 MHz. The carrier frequency of these signals can be configured from 200 MHz to 3 GHz. Figure 3-5 shows an example of the output spectrum of such a digital RF signal generator. Nevertheless, the circuit is custom-designed in a 90 nm CMOS technology and the power budget is around 50 mW at full speed for the complete digital core. In more recent technologies, the  $\Delta\Sigma$  modulator block can be designed using automated synthesis tools with a smaller power budget, as demonstrated in 2010 by Intel Labs in a 45 nm CMOS technology [28]. In 2016, researchers at Fudan University also integrated a single-bit  $\Delta\Sigma$ -based digital modulator with a current-mode class-D power amplifier in a 65 nm CMOS process [29]. To complete the picture, NEC Corporation proposed an envelope  $\Delta\Sigma$  modulation for the amplitude path and to multiply it digitally with a phase-modulated path, which can lead to a single-bit RF output with lower activity rate [30]. Apart from these works, no other significant circuit implementation has been reported for single-bit digital transmitters. Nevertheless, several proofs of concepts have been realized using FPGA and discrete components [31]-[33].

Figure 3-5 An example of a broadband output spectrum measured from a delta-sigma modulated 1-bit stream converted at a carrier frequency of 650 MHz. The channel is 5 MHz, while the total band is about 50 MHz. The adjacent channel power ratio (ACPR) is approximately 50 dB. We can clearly observe the shape of the noise provided by the delta-sigma modulators.

#### b) Polar transmitters

Significant work has also been done on polar transmitters, in which the signal is decomposed in phase and amplitude rather than in quadrature components. The digital phase signal is used to modulate a local oscillator that generates a square wave carrier. The amplitude path is either a multi-bit or quantized signal and, depending on the choice of implementation, modulates the supply of the digital PA, activates the corresponding number of cells, or is directly multiplied by the phase-modulated LO to provide bursts of bits to a switched mode PA. The circuits presented in [34] by KU Leuven and Infineon and [35] by KTH are very good examples of digital polar transmitters exploiting advanced CMOS technologies.

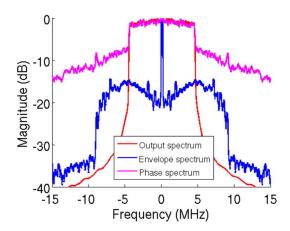

An advantage of polar modulators is the energy efficiency of the solution, especially when a switched-mode PA, such as class D or class E PAs, amplifies bursts of a square-wave phase-modulated carrier. However, polar modulators have certain disadvantages compared to quadrature transmitters. First, the bandwidths of the phase and amplitude signals are typically 3 to 6 times larger than the quadrature I and Q components, as shown in Figure 3-6, which poses problems for implementing the processing blocks. The recent CMOS technologies offer a high speed of operation of the transistors and contribute to the realization of efficient systems. Secondly, the processing in the amplitude and phase paths are essentially different, and it can be difficult to match their respective delays and synchronize the two paths when they are recombined. This limitation induces effects such as spectral regrowth [36] and raises architectural problems.

Figure 3-6 Envelope and phase spectra in polar representation

## 3.1.3. Challenges in digital RF transmitters

Examining the topologies in the previous section has shown some interesting potential for integrated digital transmitters, but challenges remain for creating robust, efficient, and

integrated digital RF transmitters. The main objective of this sub-section is to identify these challenges in order to position the work done in our group in the past 10 years in the study of potential solutions to overcome these challenges.

### a) High-speed operation

Since most digital transmitter topologies require oversampling, they necessitate the use of high-speed operation of the digital logic. Fortunately, this is in line with the evolution of CMOS technologies and digital RF transmitters have a lot to gain from being integrated into very advanced nodes to benefit from speed and reduction of energy consumption per operation.

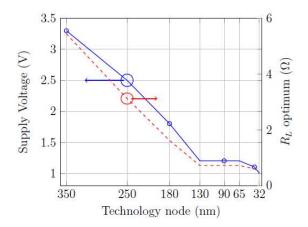

## b) Low voltage power supply in CMOS technology

Advanced CMOS technologies offer supply voltages as low as 1 V. It is then very difficult to provide output powers in the order of 30 dBm, since this would require a low resistive load and a large current. Differential PA configurations are often used, as well as power combination schemes. This is probably the main limitation to extreme integration, since passive components such as inductors or transformers would often be needed.

#### c) Out-of-band interference

Flexible transmitters can produce and transmit data with many modulation schemes, data rates, carrier frequencies, and specific standards. They must comply with regulations on maximum emission in selected bands to allow the coexistence of several systems in the same neighborhood. This becomes particularly difficult with highly integrated digital transmitters because many spurious tones or noise are generated at the output. This includes spectral images and replicas, tones from clocks leaking from poorly isolated digital domains, or quantization noise produced by low-resolution coding schemes. Spurious out-of-band mitigation techniques take into account the reduction of all spurious and noises to an acceptable level or selective filtering in specific receive bands (such as very sensitive GPS bands).

## 3.2. High-speed digital operation

# 3.2.1. Generation of digital RF signals based on 1-bit delta-sigma modulation

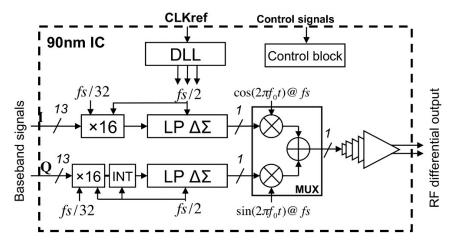

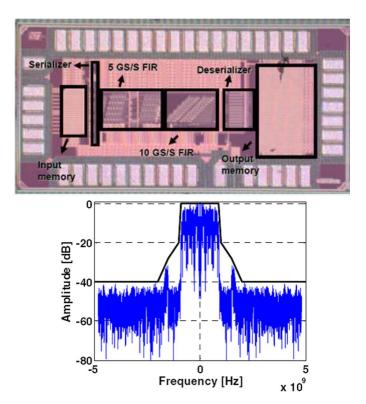

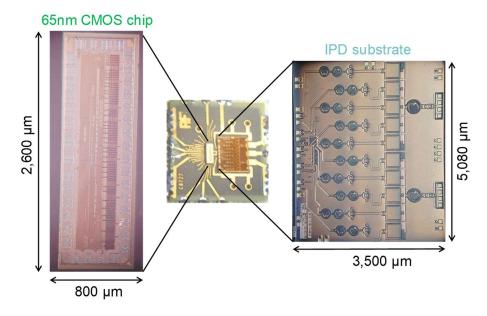

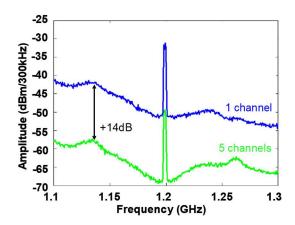

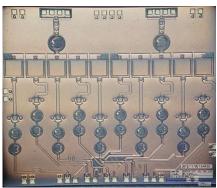

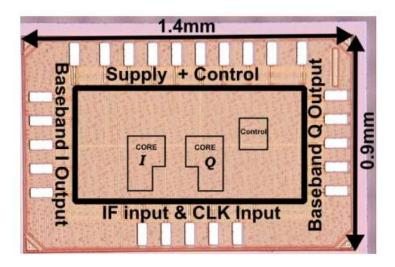

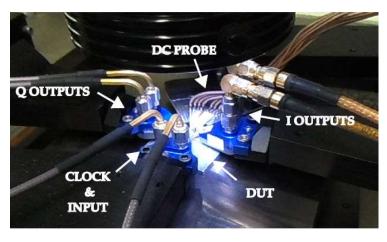

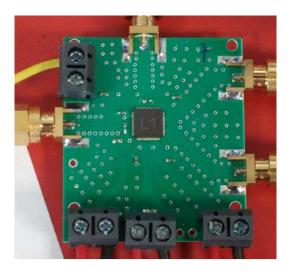

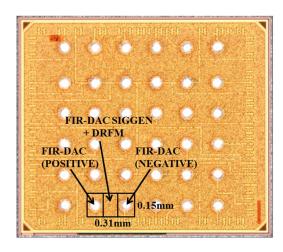

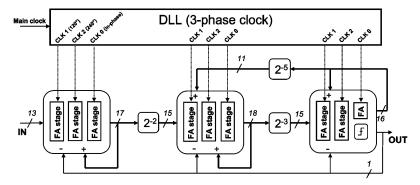

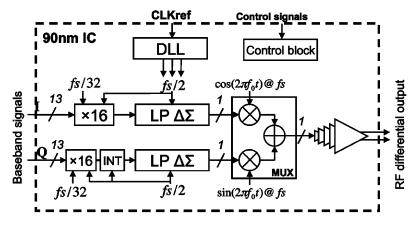

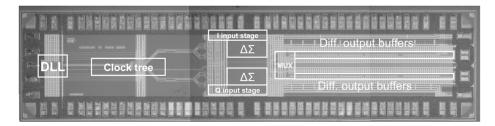

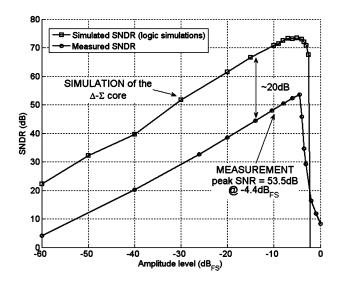

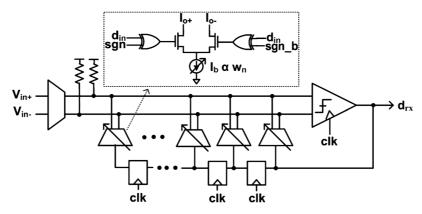

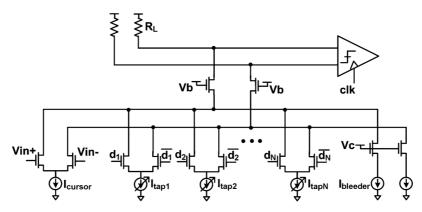

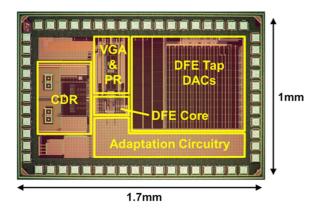

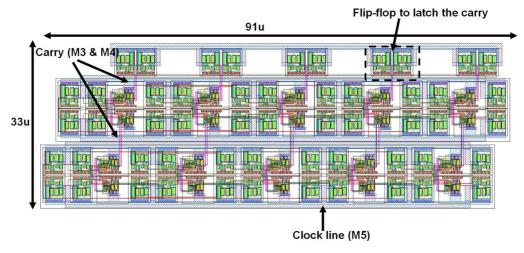

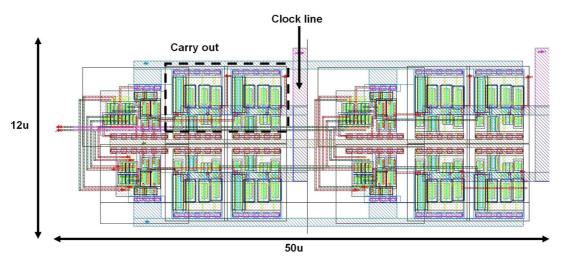

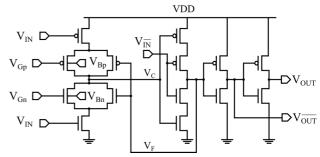

As briefly described in the previous section, single-bit delta-sigma modulators push the digital-to-analog limit to the antenna. The advances and maturity of deep submicron CMOS technologies allow the DAC to achieve higher sample rates, reaching RF frequencies. Our team introduced the first 90 nm CMOS 1-bit  $\Delta\Sigma$  RF signal generator suitable for integration into a complete transmitter chain [26]. A bandwidth of 50 MHz centered on 1 GHz can be obtained when the circuit is clocked at 4 GHz. Signals up to 3 GHz can be synthesized when using the first image band. The maximum output power into a differential 100  $\Omega$  load is 3.1 dBm with 53.6 dB SNDR. The digital core consumes 49 mW at the maximum clock rate. The active area is 0.15 mm<sup>2</sup>. An overview of the signal generator chip is shown in Figure 3-7.

Figure 3-7 System view of the 1-bit  $\Delta\Sigma$  RF signal generator (from [26])

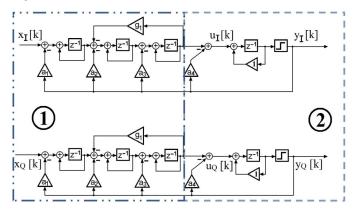

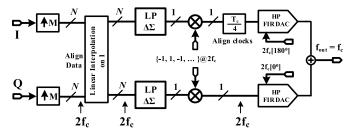

After the off-chip baseband signal processing and the low-IF upconversion, the I and Q input channels are upsampled 16 times up to  $f_s/2$ . The  $\Delta\Sigma$  modulators quantize the signals into 1-bit signals and shape the quantization noise with a third-order transfer function, including an optimized zeros placement. The 1-bit digital image-reject mixer replaces the conventional mixer and converts the I and Q signals into the desired RF carrier frequency before being pre-amplified by sized inverters. Note that a linear interpolation stage is inserted on the Q channel to reject the image channel.

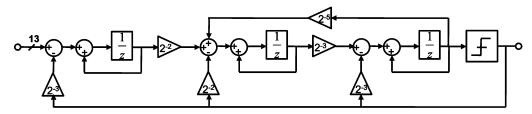

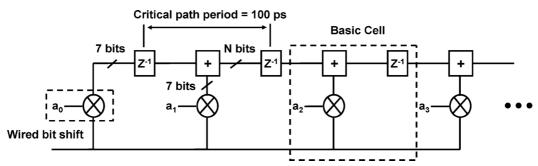

The key innovation to achieve a clock frequency of 4 GHz is the development of a specific implementation of the core of the delta-sigma modulator. A redundant representation, named

borrow-save (BS), instead of the classical 2's complement representation has been proposed for the implementation of high-speed  $\Delta\Sigma$  modulators [37]. This type of arithmetic allows additions without carry by simply calculating bit positions in parallel and saving carries in its representation, each bit position being doubled. Nevertheless, since output quantization cannot be easily calculated without reintroducing a carry propagation path, pre-computed non-exact quantization has been introduced. This output stage can be implemented with a digital (logic equations) or mixed-signal approach (sum of currents corresponding to the bit values). A patent covers the implementation of this type of architecture [38]. More details on the logical representation can be found in [37] or [39].

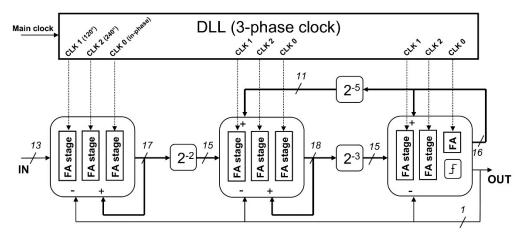

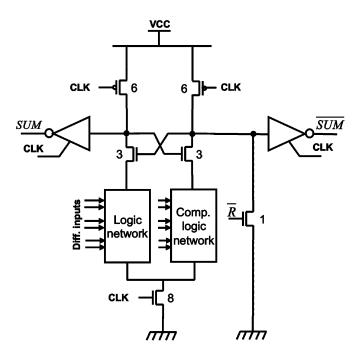

Figure 3-8 Third-order  $\Delta\Sigma$  modulator with optimized zero placement (from [26])

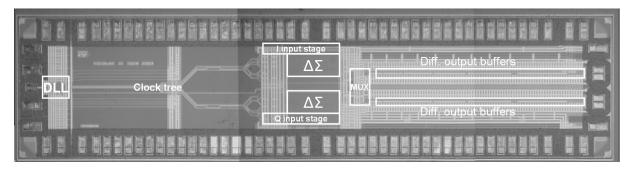

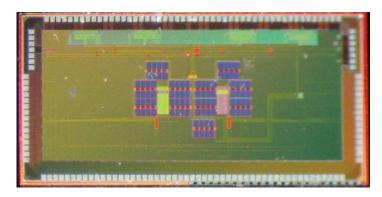

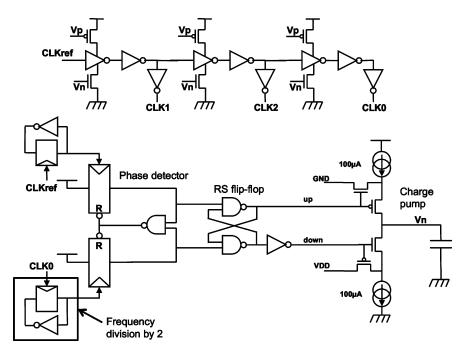

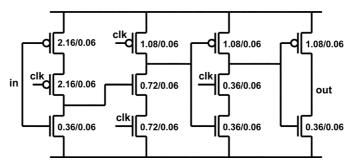

A third-order 1-bit low-pass  $\Delta\Sigma$  modulator with optimized zero placement was designed and successfully measured up to a sampling rate of 2 GS/s (Figure 3-8). It consists of 3 computation units, composed of 3 consecutive full-adder stages. To synchronize the operation, a 3-phase clock generated by a delay-locked loop (DLL) alternatively launches the calculation of each dynamic stage. A 90 nm CMOS integrated circuit, shown in Figure 3-9, was fabricated and tested to validate the concept. An SNDR of 72 dB over a bandwidth of 50 MHz was measured. However, the SNDR measured at the output of the chip degrades to 54 dB, due to the ringing of the supply voltage and the correlated jitter introduced into the output stage. This work is the first demonstration of a single-bit digital RF transmitter.

Figure 3-9 Integrated circuit microphotography of the 90 nm CMOS digital delta-sigma modulator (4  $\times$  0.8 mm²)

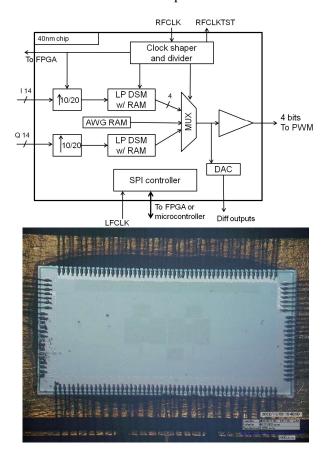

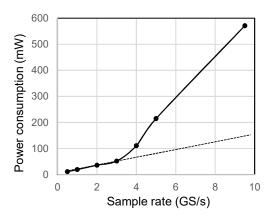

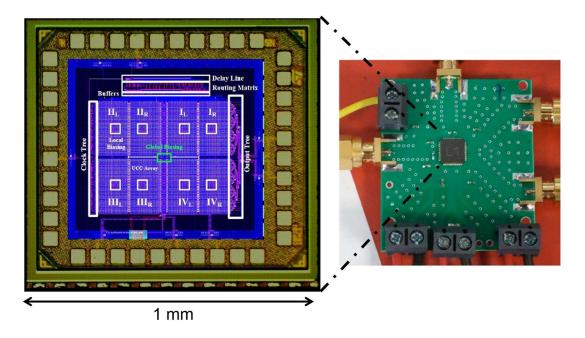

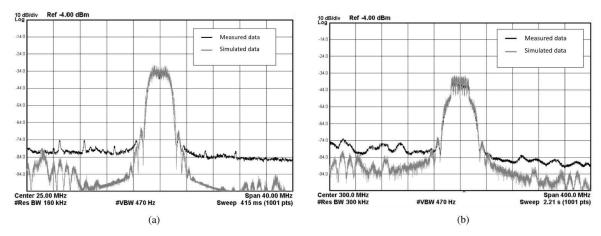

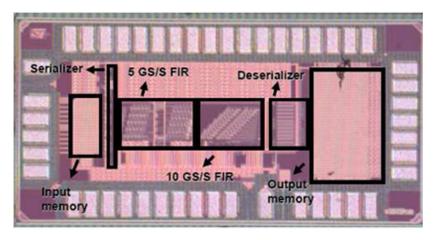

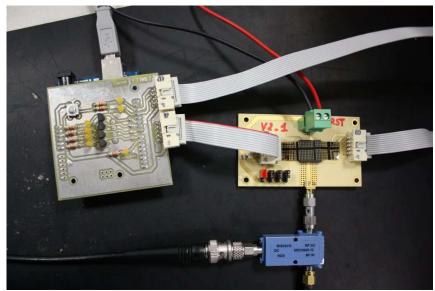

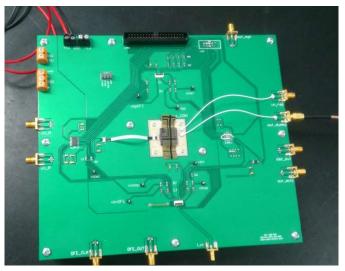

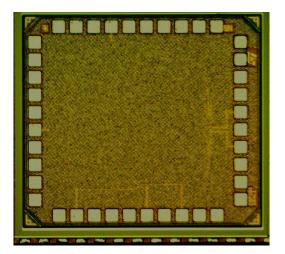

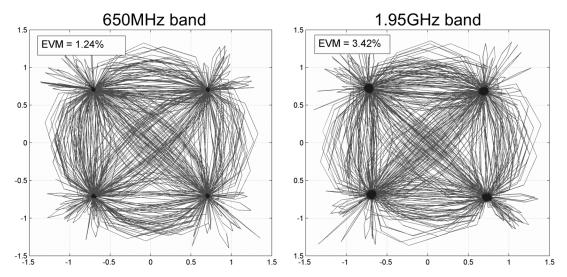

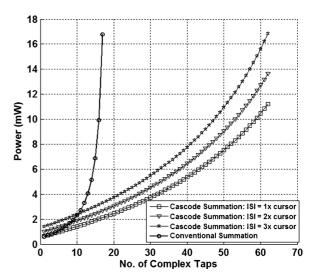

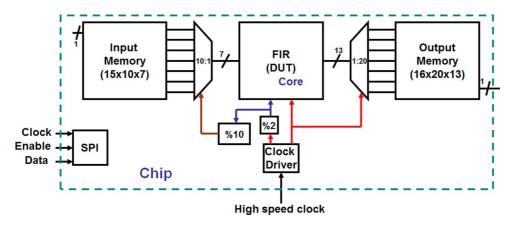

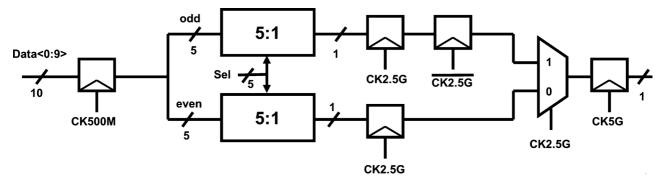

As a result of this work, an ambitious collaborative project with Alcatel-Lucent focused on the use of baseband delta-sigma modulator for base stations. Some extracted performances describe the challenge. The system should offer instantaneous bandwidths of 200 MHz and modulated signals with high spectral quality (>70 dB ACLR and <6% EVM on the air). For low power consumption and heating problems, the spectral efficiency should be close to 90%. The proposed transmitter would consist of an FPGA generating digital baseband data at approximately 400 MS/s. It includes channeling, up-sampling and frequency shift. This signal is transmitted to a multi-chip module (MCM) built with a 4-bit 4 GS/s CMOS delta-sigma modulator and an RF PWM modulator and integrated drivers in InP technology, generating an output signal at 64 GS/s. Finally, a class S GaN power amplifier is integrated in another MCM with baluns and reconstruction filters. In this project, I supervised the development of the CMOS delta-sigma modulator chip.

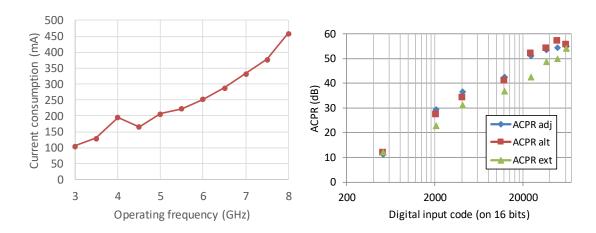

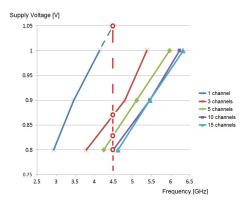

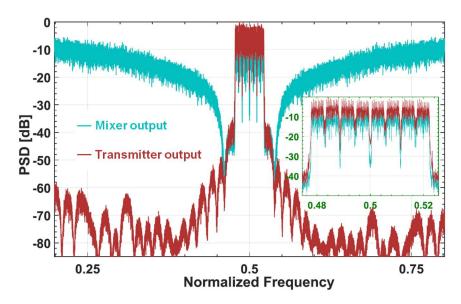

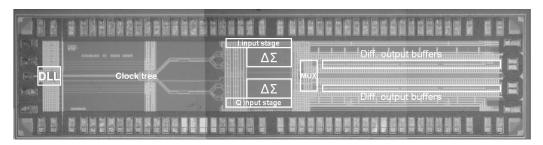

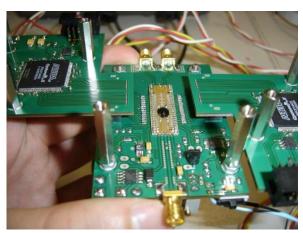

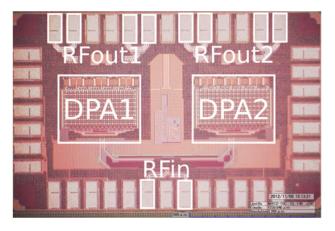

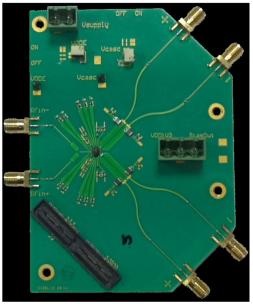

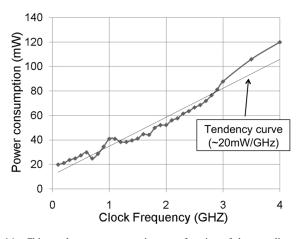

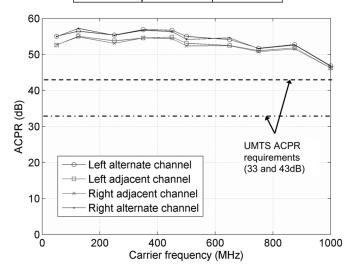

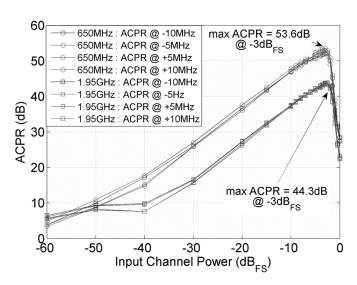

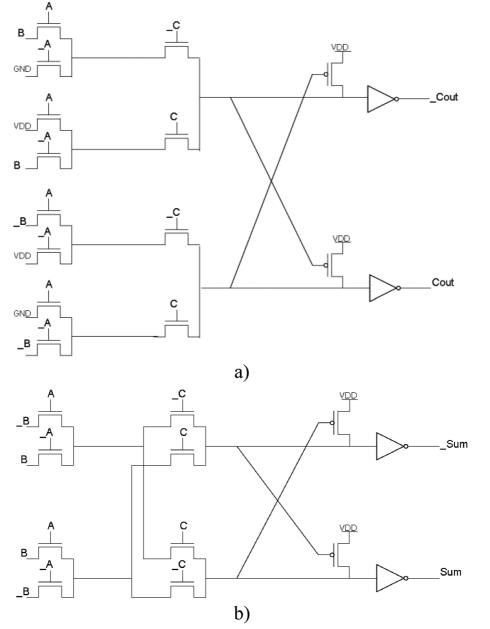

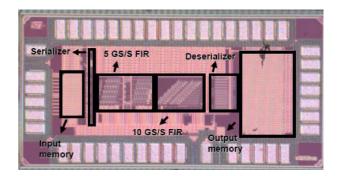

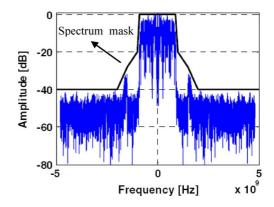

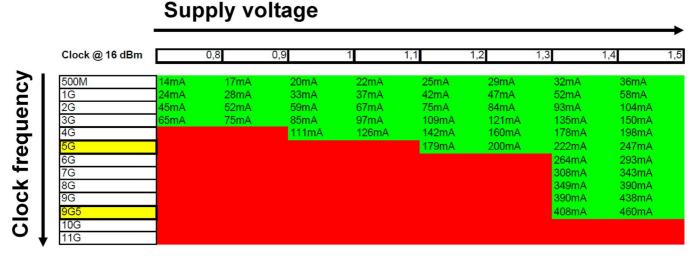

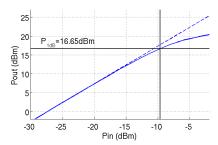

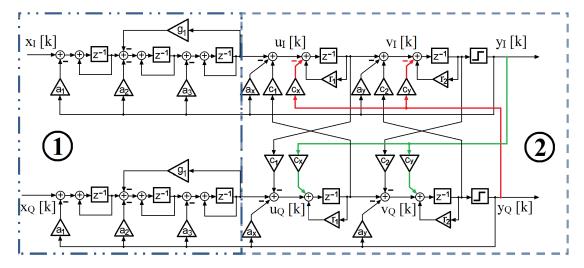

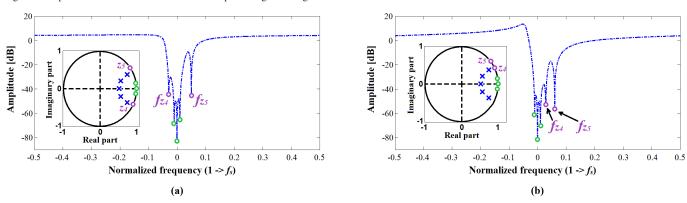

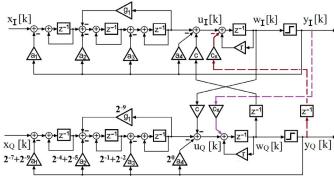

A single-bit CMOS delta-sigma modulator cannot achieve the expected performance. Thus, a 4-bit solution has been proposed in conjunction with a digital PWM to transform this multibit signal into a 1-bit signal at a higher speed. Digital pre-distortion tables are integrated to achieve the targeted performance. Figure 3-10 shows the internal structure and the photograph of a 40 nm integrated circuit designed to produce a 4-bit high-speed data stream containing the modulated channels in a 500 MHz bandwidth. Design techniques, such as redundant arithmetic, are implemented to achieve GS/s operating frequencies. The circuit is fully functional up to an operating frequency of 8 GHz, that is, a 50 dB SNR is maintained in a 10 MHz bandwidth. The associated power consumption is shown in Figure 3-11. The circuit operates at a minimum voltage of 0.65 V at 3 GHz and 1.05 V for an 8 GHz clock. Measurements were made with a 50 MHz modulated channel and this shows that an ACPR of more than 53 dB is provided over a 500 MHz bandwidth (Figure 3-11). There is no publication associated with this work, but internal research and design reports have been produced as part of the collaboration with Alcatel-Lucent.

Figure 3-10 (left) Structure of the 40 nm integrated circuit based on  $4^{th}$  order  $\Delta\Sigma$  modulators associated with the random access memories (for predistortion) (right) Microphotography of the 40 nm chip  $(4.2 \times 2 \text{ mm}^2)$

Figure 3-11 Measurement results of the integrated circuit: (left) Evaluation of the total consumption of the chip in relation to the operating frequency. For this plot, the VDD power supply is set at the minimum voltage that guarantees a measured SNR of 50 dB over a 10 MHz bandwidth; (right) Evaluation of the Adjacent Channel Power Ratio (ACPR) for a 50 MHz channel relative to the digital input code (directly related to the power of the output channel). The series represent the adjacent, alternate and extreme channel (measured at the edge of the 500 MHz total bandwidth).

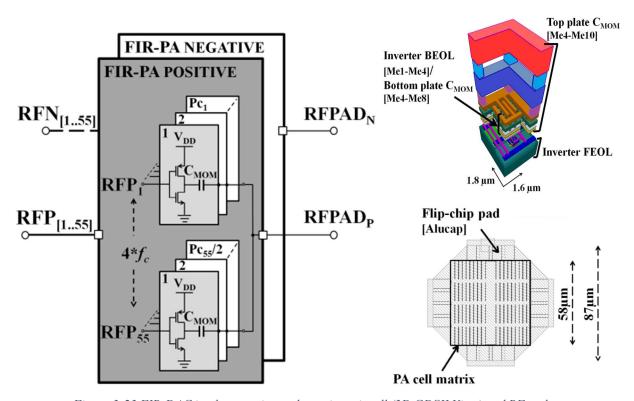

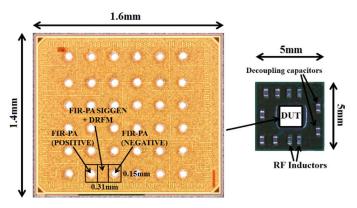

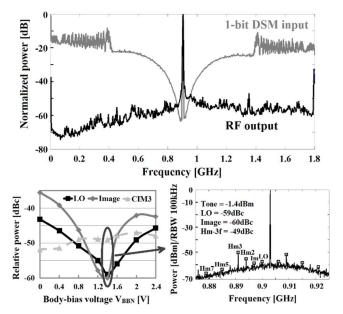

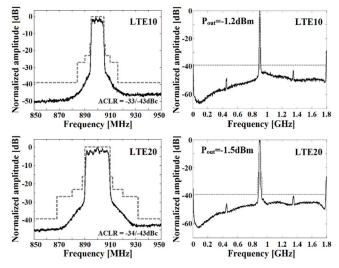

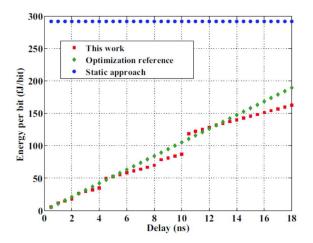

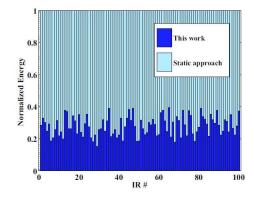

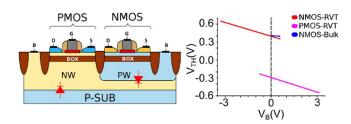

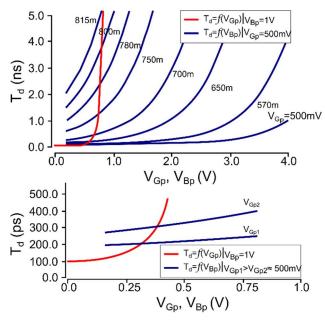

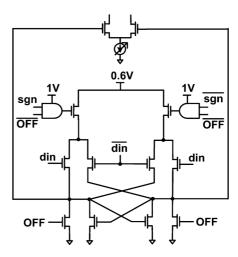

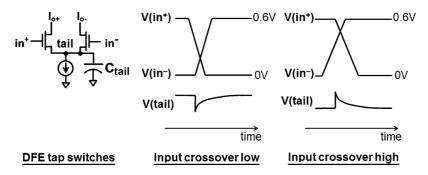

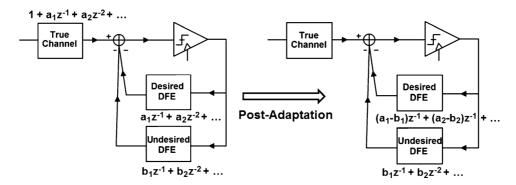

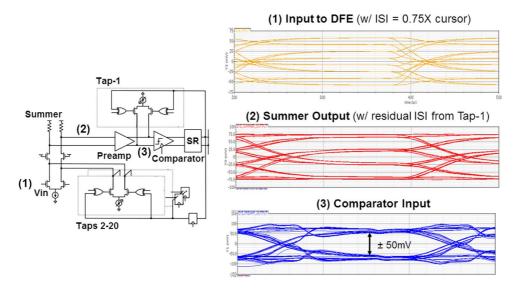

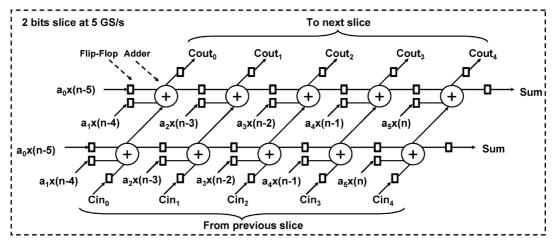

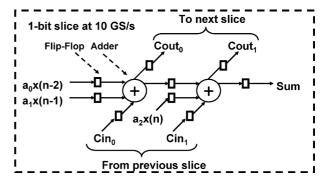

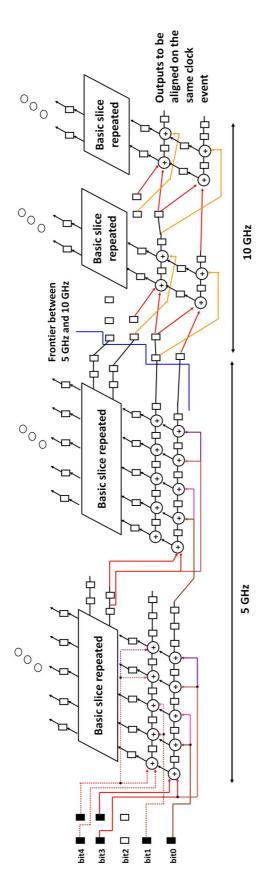

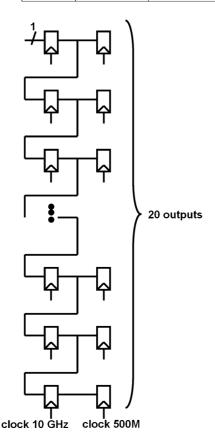

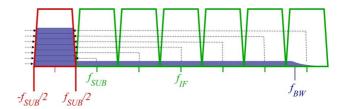

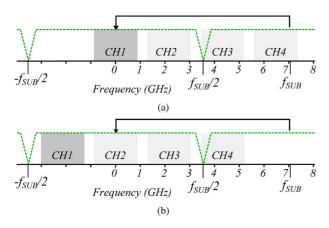

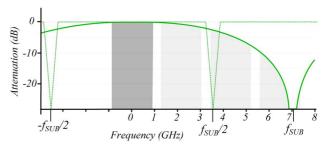

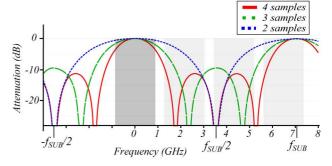

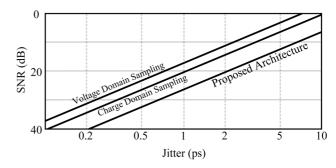

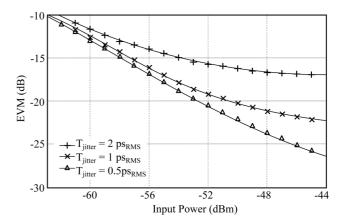

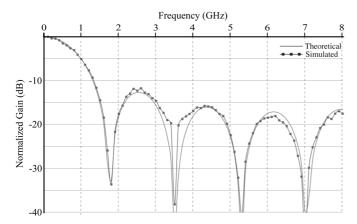

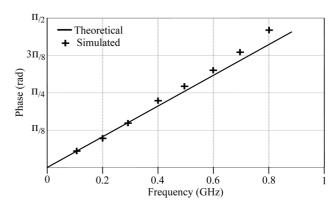

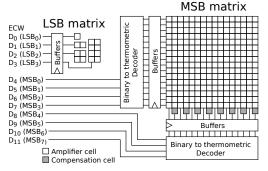

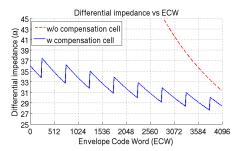

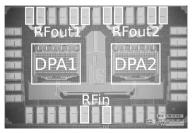

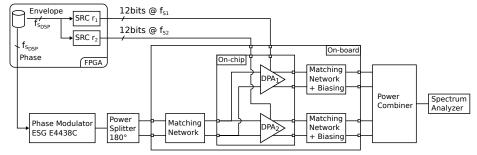

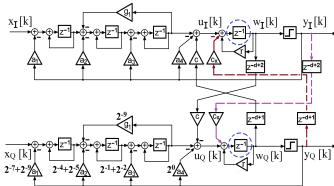

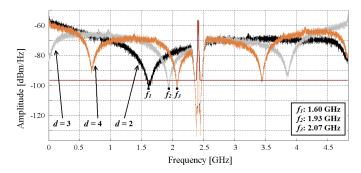

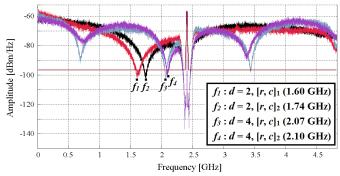

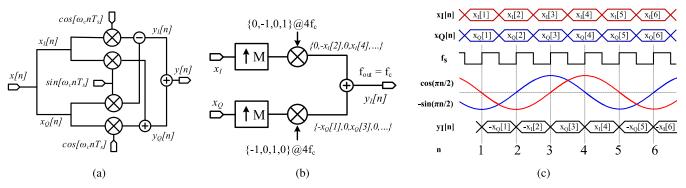

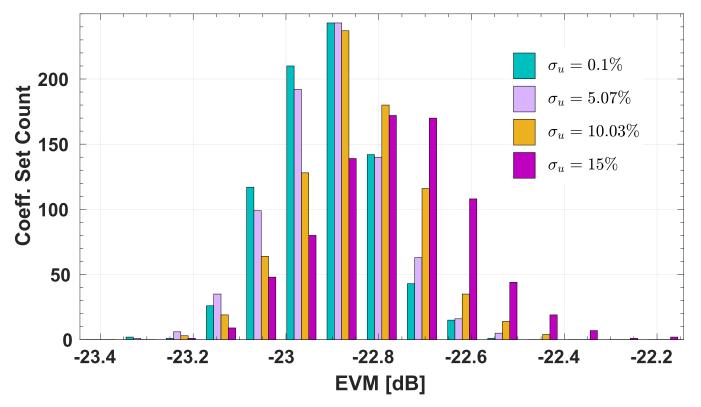

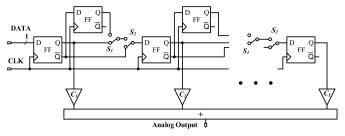

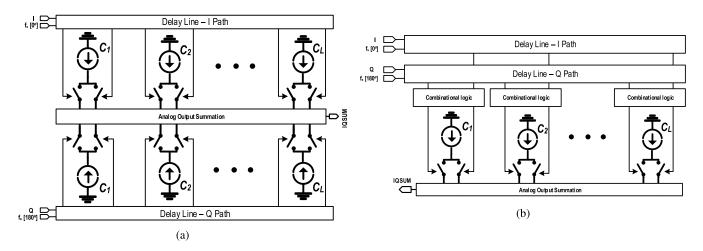

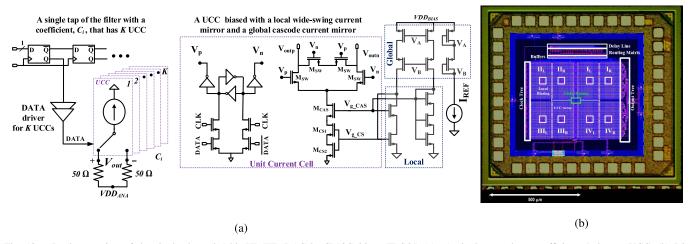

### 3.2.2. Time-interleaving