### Strengthening fonctional validation of critical system by using Model Checking: Application to Instrumentation and Control systems in nuclear power plants

Y. Sun

### ► To cite this version:

Y. Sun. Strengthening fonctional validation of critical system by using Model Checking: Application to Instrumentation and Control systems in nuclear power plants. Computer Science [cs]. Telecom ParisTech, 2017. English. NNT: . tel-03419751v1

### HAL Id: tel-03419751 https://hal.science/tel-03419751v1

Submitted on 24 Apr 2018 (v1), last revised 8 Nov 2021 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Doctorat ParisTech**

# THÈSE

pour obtenir le grade de docteur délivré par

## **TELECOM** ParisTech

### Spécialité « Informatique et Réseaux »

présentée et soutenue publiquement par

### Yanjun SUN

le 9 octobre 2017

### Strengthening fonctional validation of critical system by using Model Checking : Application to

### Instrumentation and Control systems in nuclear power plants

Directeur de thèse : **Gérard MEMMI** Co-encadrement de la thèse : **Sylvie VIGNES**

Jury

| Mme Lydie DU BOUSQUET, Professeur, Université Grenoble-Alpes, LIG  |        |

|--------------------------------------------------------------------|--------|

| M. Alessandro FANTECHI, Professeur, Université de Florence, Italie |        |

| M. Luc COYETTE, Esterel technologies/ ANSYS                        |        |

| M. Frédéric DAUMAS, Expert Sûreté de Fonctionnement CC, EDF R&D    |        |

| M. Elie NAJM, Professeur, Télécom ParisTech                        | Prés   |

| M. Gérard MEMMI, Professeur, Télécom ParisTech                     | Direct |

| Mme Sylvie VIGNES, Maître de conférence, Télécom ParisTech         | Direct |

| TELECOM ParisTech                                                  |        |

Rapporteur Rapporteur Examinateur Examinateur Président du jury Directeur de thèse Directeur de thèse

école de l'Institut Mines-Télécom - membre de ParisTech

# Acknowledgment

I would like to thank my thesis supervisors Gérard Memmi and Sylvie Vignes for their precious guidance and support during the past four years. I truly could not have imagined having better mentors than them.

I would like to thank the members of my committee for their insightful comments and encouragement: Lydie du Bousquet, Alessandro Fantechi and Elie Najm.

My thanks also go to "CONNEXION" colleagues: Catherine Devic, Frédéric Daumas, Maxime Neyret, Gaëtan Robin from EDF; Luc Coyette and François-Xavier Dormoy from ESTEREL Technologies; Benjamin Blanc, Jean-Yves Pierron from CEA; François Chastrette from ALL4Tech; Olivier Bruneau from CORYS. This thesis is partially funded by the "CONNEXION" project. A special gratitude to Adrien Champion for his valuable help and advice.

I am grateful to other colleagues at École Télécom ParisTech for their advice and friendship. I am also grateful to school staff for their unfailing assistance.

Finally I would like to thank my parents, my parents-in-law, my husband and my son, for their love and support.

# Abstract

The verification and validation of safety-critical real-time system are subject to stringent standards and certifications. Recent progress in model-based system engineering should be applied to such systems since it allows early detection of defects and formal verification techniques. The French project "CONNEXION" proposes an innovative process introducing multi-level model-based functional validation supporting the nuclear I&C system development life cycle. Various modeling and verification tools provided by project partners automate this process as much as possible. "CONNEXION" also proposes a verification platform integrating various models and tools, which allows closed-loop simulation of the control/command system and its physical environment.

As part of the "CONNEXION" project, this thesis proposes a model-based testing methodology dedicated to functional validation of safety-critical real-time systems. The methodology focuses on an iterative use of a model checker to generate coverage-based open-loop test sequence. We also propose a refinement technique of progressively adding environment constraints during test generation. The refinement is expected to support the passage from coverage-based open-loop test sequence to functional requirements-based closed-loop test case. Our methodology also considers the state explosion problem of a model checker and proposes a heuristic called hybrid verification which combines model checking and simulation. Finally we design an information system of traceability to support the co-simulation verification platform.

Part of our methodology has been tested on a "CONNEXION" case study, with support of "CONNEXION" tools. To implement the complete methodology, in particular hybrid verification, we have tested several academic model checking tools for the synchronous data-flow language Lustre (choice of "CONNEXION"). We review state of the art of Lustre regarding version evolution, related model checking tools, translator of Lustre to other modeling languages, etc. For Lustre-based models, implementation of the complete methodology may require an integration of several model checking tools.

# Résumé français

### Introduction

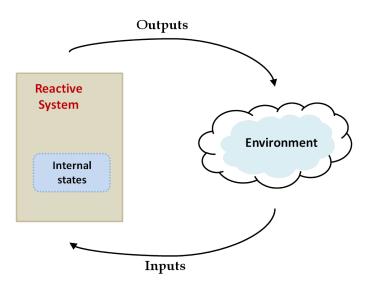

Contrôle de processus industriels, contrôle de véhicules (automobiles, trains, avions...), systèmes militaires de contrôle-commande..., voici quelques exemples de systèmes réactifs temps réel. Le terme "réactif" indique que le système interagit en permanence avec son (éventuellement physique) environnement; nous réservons le terme "temps réel" pour les systèmes réactifs soumis à des contraintes temporelles externes, comme suggéré par Benveniste et Berry[26]. Les systèmes hautement critiques en sûreté de fonctionnement sont en général des systèmes réactifs temps réel, tels que le système de contrôle-commande dans une centrale nucléaire ou le système de contrôle de vol de l'avion. Ce domaine d'application nécessite une conception très soignée et une vérification ainsi qu'une validation très rigoureuses. La sûreté de fonctionnement est une propriété cruciale ici car un simple défaut peut produire des conséquences extrêmes et catastrophiques.

Historiquement, la conception des systèmes réactifs temps réel a longtemps été la préoccupation des automaticiens. La théorie du contrôle automatique a été appliquée à la conception des systèmes dont le comportement est attendu, d'une manière dite "bottom-up". Au niveau de Vérification et Validation (V&V), la tâche ne peut être approchée que tardivement dans le cycle de développement. Prototypes physiques des systèmes (ou sous-systèmes) sont connectés à la plateforme de simulation "Hardware-in-the-Loop (HIL)", pour étudier le comportement au niveau du système. Pour les système unitaires avec un nombre limité des variables d'entrée et de sortie, il est possible de les tester de manière exhaustive. Mais le défi reste à effectuer une validation complète et systématique, étant donné le grand nombre de situations pertinentes pour les systèmes complexes [160].

Au cours des décennies précédentes, des contributions majeures ont été faites pour établir des approches dites "basées sur modèles" (model-based en anglais) pour la description, la conception et l'analyse de systèmes [71]. Divers langages de modélisation graphique ont été développés, afin de rendre les modèles plus visuels et de faciliter la communication avec les parties prenantes. En 2007, l'INCOSE (International Council on Systems Engineering) a lancé l'initiative "INCOSE MB-SE"<sup>1</sup>, où MBSE indique **l'Ingénierie dirigée par les modèles** (Model-Based Systems Engineering). Depuis les deux dernières décennies, divers méthodologies et outils MBSE ont été développés. Un résumé peut être trouvé dans l'enquête INCOSE portant sur les méthodologies MBSE [79].

**Definition 1.** Ingénierie des systèmes dirigée par les modèles (MBSE) est l'application formalisée de la modélisation pour soutenir les exigences, la conception, l'analyse, la vérification et validation du système, à partir de la phase de conception et tout au long des phases de développement et de cycle de vie ultérieur [7].

En bref, MBSE donne aux modèles un rôle central dans le processus de l'ingénierie de la spécification à la conception, l'intégration et la validation d'un système [79]. Les approches MBSE comprennent l'analyse comportementale, l'architecture du système, la traçabilité des exigences, l'analyse de la performance, la simulation, les tests, etc. Cela résulte en une transition de l'ingénierie système traditionnellement "documents-centriques" vers une approche "modèles-centriques" préconisée par l'INCOSE[7]. De plus MBSE permet aux ingénieurs logiciels et systèmes de mieux comprendre l'impact de changement de conception, de communiquer l'intention de conception et d'analyser la conception d'un système avant le développement.

L'application des progrès récents en MBSE aux systèmes industriels réactifs temps-réel et critique constitue le contexte de cette thèse. La vérification et la validation de ces systèmes sont soumises à des normes strictes [9]. Des méthodes formelles sont parfois nécessaires, au moins en ce qui concerne les propriétés hautement critiques. La thèse s'appuie sur le cluster de projets R&D français "CON-NEXION" dans le domaine nucléaire. À partir d'un cas d'étude industriel et d'un ensemble préconisé d'outils, nous avons eu l'occasion d'examiner les difficultés d'adopter les techniques modernes MBSE dans un contexte industriel critique. De plus, MBSE permet de réaliser la V&V tôt dans les phases de conception et donc de détecter des défauts au plus tôt possible. Cette approche est très rentable pour les systèmes réactifs temps-réel et critiques puisque le coût des défauts trouvés plus tard dans le système peut être extrêmement élevé.

<sup>&</sup>lt;sup>1</sup>http://www.incose.org/ChaptersGroups/WorkingGroups/transformational/ mbse-initiative

### Problématique

Depuis 2012, les principaux partenaires industriels de nucléaire français et académiques ont initié un ambitieux programme de R&D appelé "CONNEXION". Regroupant plusieurs projets, "CONNEXION" [71] vise à améliorer le processus de développement du système d'instrumentation et contrôle (I&C) dans des centrales nucléaires. "CONNEXION" s'appuie sur les expertises existantes des opérateurs dans l'industrie nucléaire française: EDF, ALSTOM, AREVA et RRCN; ainsi que sur divers outils fournis par des partenaires: CEA, CORYS, ESTEREL Technologies et ALL4TEC.

**Definition 2.** Validation Fonctionnelle [9] est en fait la vérification des modèles du système construits en amont de la conception par rapport aux exigences fonctionnelles du système.

La conception du système I&C se décline en plusieurs phases. Les modèles de plus en plus détaillés décrivant le comportement du système sont construits dans les phases amont. La vérification des ces modèles par rapport aux exigences fonctionnelles du système, définie comme Validation Fonctionnelle, est actuellement réalisée d'une manière manuelle. Un objectif de "CONNEXION" est d'automatiser autant que possible la validation fonctionnelle, en s'appuyant sur l'outillage fournie par des partenaires.

#### Contribution de thèse

Dans le cadre du projet "CONNEXION", notre travail de recherche s'appuie sur différents outils fournis par des partenaires et traite un cas d'étude industriel du système I&C. Nous proposons une méthodologie de test dirigée par les modèles (**Model-Based Testing ou MBT**), pour renforcer la validation fonctionnelle des modèles du système I&C. La méthodologie proposée n'est pas limitée au secteur nucléaire et peut être généralisée et appliquée à d'autres systèmes réactifs temps-réel et critiques en sûreté de fonctionnement.

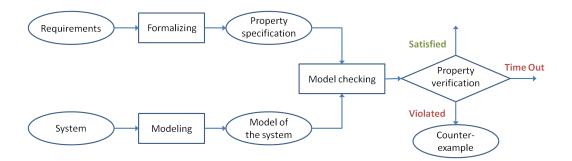

Notre méthodologie repose principalement sur la technique dite "model checking" [19]. Cette technique a été proposée initialement comme une méthode formelle pour vérifier l'exactitude d'un modèle par rapport à un ensemble de propriétés. L'outil qui automatise la technique model checking est un model checker. Dans notre méthodologie, un model checker est utilisé de façon itérative, comme un outil de génération de test. En effet la validation fonctionnelle du système I&C doit être réalisée non seulement par rapport aux exigences fonctionnelles, mais également par rapport aux critères de couverture structurelle comme MC/DC. Les objectifs de test basés sur la couverture sont spécifiés comme des "propriétés de piège" [91] pour forcer le *model checker* à générer des contre-exemples. Ces contre-exemples sont ensuite élaborés en cas de test permettant améliorer la couverture structurelle.

Le système I&C est composé de deux sous systèmes: un système contrôlecommande et un environnement physique. Le contrôle-commande est en réaction permanente et en temps-réel avec l'environnement physique. En raison de leurs différentes caractéristiques, l'environnement et le contrôle-commande sont en général spécifiés par deux différents langages de modélisation. Une solution est de reconstruire l'environnement avec le même langage de spécification du contrôlecommande, tel que présenté dans [43]. Mais ce n'est pas le choix de "CONNEX-ION". Par conséquent, nous avons décidé d'utiliser des hypothèses sur l'environnement pour raffiner la génération de test par *model checking*. Nous proposons une technique qui ajoute progressivement ces hypothèses pour obtenir un test de plus en plus réaliste. Cela aide les experts du système à concevoir un test en boucle fermée à partir d'un test en boucle ouverte. Nous donnons ci-dessous les définitions de "boucle fermée" et "boucle ouverte":

**Definition 3.** Boucle fermée: un test en boucle fermée est une co-exécution d'un système réactif temps-réel avec son environnement physique.

**Definition 4.** Boucle ouverte: un test en boucle ouverte exécute seulement un système réactif temps-réel, sans prendre en compte les réactions de son environnement physique.

Enfin, dans notre méthodologie, nous considérons le "Time Out" d'un *model* checker suite au problème d'explosion des états. Nous proposons une heuristique dite **vérification hybride** qui combine simulation et *model checking*. Model checking explore l'ensemble de l'espace d'état tandis que la vérification hybride n'explore qu'un sous-ensemble de tous les états possibles. Nous proposons également les éléments pour mettre en pratique la vérification hybride. Ces éléments comprennent:

- Chercher un *model checker* puissant et complet pour effectuer la vérification hybride sur un modèle en Lustre. Nous passons en revue les différentes versions du langage Lustre et nous avons testé plusieurs outils académiques sur le cas d'étude "CONNEXION".

- Nous avons également considéré la traduction d'un modèle en Lustre vers un autre langage de modélisation, SMV par exemple, pour bénéficier d'autres outils de *model checking*.

Nous arrivons à la conclusion qu'un seul outil n'est pas suffisant pour appliquer la vérification hybride à un modèle en Lustre de taille industrielle. La vérification hybride combine plusieurs techniques: exploration exhaustive de l'espace d'état, mémorisation des traces d'exploration, génération avant et arrière de traces, simulation pas-à-pas, etc. Une intégration de plusieurs outils est une solution.

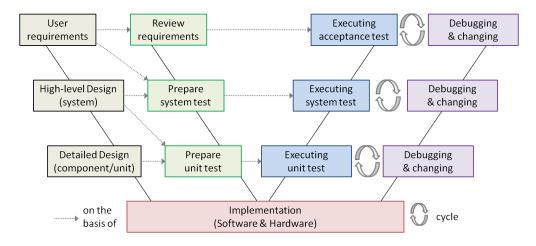

### Model checking et son application

#### Model checking

La vérification formelle est une technique qui applique des méthodes mathématiquement formelles à la vérification de systèmes. L'objectif est de prouver l'exactitude (ou l'inexactitude) du système sous test d'une manière rigoureuse. La recherche sur la vérification formelle au cours des deux dernières décennies a abouti à des techniques prometteuses. Ces techniques sont aussi soutenues par de puissants outils logiciels qui peuvent être utilisés pour automatiser divers étapes de vérification et ainsi réduire le coût.

Au début des années 1980, le *model checking* est proprosé comme une technique de vérification formelle. Il provient du travail indépendant de deux équipes: Clarke et Emmerson [61]; Sifakis et Queille [145]. Un model checker est l'outil qui automatise model checking. A une spécification formelle du système (c'est-à-dire un modèle du système), un *model checker* explore tous les états possibles du système. L'objectif est de prouver avec une rigueur mathématique l'exactitude du modèle de système par rapport à une propriété. Des model checkers d'avant garde peuvent gérer des espaces d'état d'environ  $10^8$  à  $10^9$  états avec des algorithmes explicites d'exploration. De plus grands espaces d'état, de  $10^{20}$  jusqu'à  $10^{476}$  états, peuvent être traités pour des problèmes spécifiques, en utilisant des algorithmes intelligents et des structures de données sur mesure [19]. Cependant, le problème d'explosion d'état reste fondamental pour le *model checking*. En raison de ce problème, les model checkers peuvent s'arrêter sur un "time out" (TO), c'est à dire terminer le calcul sans donner une réponse au problème de vérification. Au cours des dernières années, les techniques de *model checkinq* ont suscité l'intérêt de nombreuses industries ayant des besoins en sûreté de fonctionnement, telles que la signalisation ferroviaire [42], l'avionique [43, 132, 133] et le nucléaire [172, 118, 171, 116].

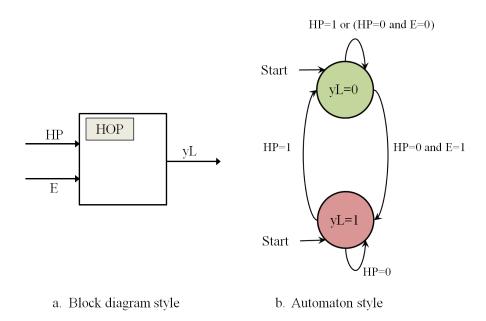

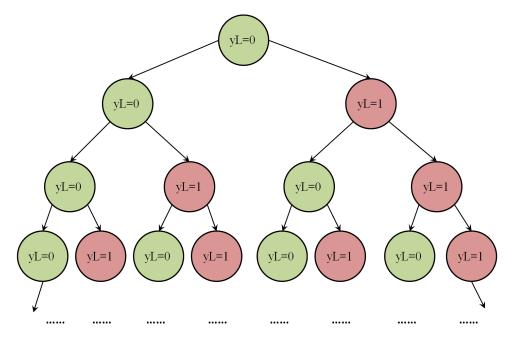

Le premier prérequis pour utiliser le *model checking* est de disposer d'un modèle du système considéré. En informatique, les systèmes de transition sont souvent utilisés comme modèles pour décrire le comportement des systèmes. Ils sont illustrés par des graphes orientés où les nœuds représentent les états et les arêtes représentent les transitions entre états. Un état décrit quelques informations sur le comportement du système à un moment donné. Les transitions précisent comment le système peut évoluer d'un état à l'autre. Le système ne peut se trouver que dans un état à la fois. L'état dans lequel il se trouve à un moment donné est appelé l'état actuel.

Le modèle du système et les propriétés à vérifier doivent être décrits de manière précise et non ambiguë. La logique temporelle est un formalisme mathématique adapté aux déclarations et au raisonnement où le temps est impliqué. Elle offre des opérateurs spécifiques pour le temps, proches du langage naturel (les adverbes comme "toujours", "jusqu'à" par exemple). Elle vient aussi avec une sémantique formelle, faisant de la logique temporelle un outil indispensable pour formaliser les propriétés concernant les comportements dynamiques d'un système. Les logiques temporelles les plus courantes sont les LTL (Linear Time Logic) [142] et CTL (Computation Tree Logic) [62].

Etant donné un modèle M et une propriété  $\phi$  du système considéré, l'algorithme de *model checking* répond à la question "M satisfait-il la propriété  $\phi$ ?". Si une violation de propriété est détectée, un *model checker* est capable de retourner un contre-exemple, illustrant comment la violation se produit. Dans la littérature, plusieurs algorithmes de *model checking* ont été proposés: le *model checking* explicite [124, 63, 145, 167] étant la première génération; le *model checking* symbolique [128] la deuxième génération et le *model checking* borné [37] la dernière génération.

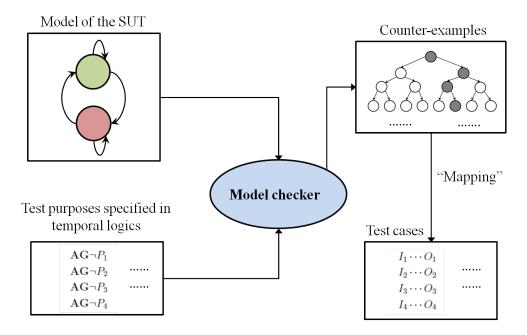

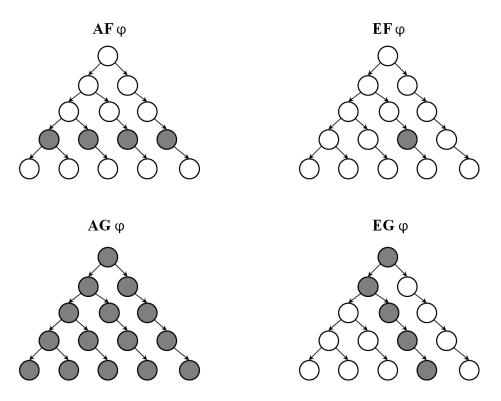

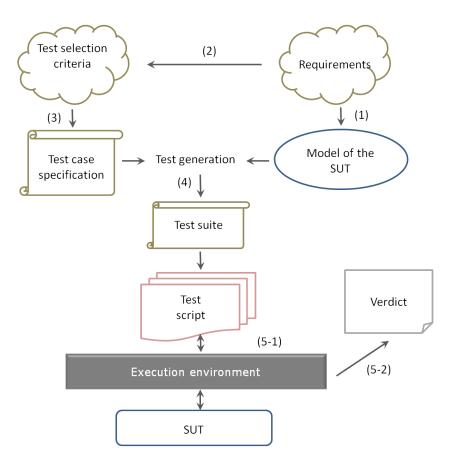

Un problème de *model checking* est généralement un problème de vérification de propriété. D'autre part, les cas de test sont liés à certains objectifs de test. Si les objectifs du test peuvent être spécifiés dans la logique temporelle, puis utilisés comme propriétés pour forcer le *model checker* à générer des contre-exemples, le problème de génération de test est en fait transformé en un problème classique de *model checking*. L'idée principale de tester avec les *model checkers* est de forcer les *model checkers* à générer des contre-exemples, et puis interpréter ces contreexemples comme des cas de test, comme montré par la Fig. 2.5. C'est important de noter que la spécification de propriété devrait être la négation d'un objectif de test de sorte qu'un contre-exemple violant la propriété, en fait, satisfait le test objectif.

Une approche répandue consiste à créer des propriétés en fonction des critères de couverture. En effet, de tels critères sont des objectifs de test très couramment utilisés. Les propriétés basées sur les critères de couverture sont initialement ap-

Figure 1: Testing with model checkers

pelées "trap properties" [91]. Une telle propriété déclare que certains éléments ne pourraient jamais être couverts par une exécution. Dans ce cas-là, le *model checking* de cette propriété va générer un contre-exemple illustrant comment l'élément peut être couvert si la propriété est violée. La majorité de générations de tests basées sur la couverture utilisent des critères de couverture structurelle. Il est parfois souhaitable de créer les cas de test basés sur d'autres objectifs de test. Différentes techniques comprennent, par exemple, l'approche basée sur les exigences [51, 170] et l'approche basée sur la mutation [15].

#### Approche synchrone pour les systèmes réactifs et temps réel

Autour des années 90s, trois langages de programmation synchrones ont été proposés par des groupes académiques français: Esterel [36, 32], Signal [122, 28, 29] et Lustre [52, 101]. Ces langages de programmation partagent les mêmes principes: hypothèse synchrone et concurrence déterministe. En pratique, l'hypothèse synchrone suppose que le programme est capable de réagir à un événement externe avant qu'un autre événement se produise. Ces langages synchrones diffèrent les uns des autres dans le style, ce qui correspond à leur usage dans différents domaines d'application. On s'intéresse dans ce document à Lustre puisque c'est le choix du projet "CONNEXION" ainsi que la thèse. Lustre est un langage déclaratif synchrone, basé sur les flots de données (dataflow). Lustre est basé sur deux notions fondamentales: (1) flot: chaque variable et expression Lustre est considérée comme un flot, c'est-à-dire, une séquence de valeurs d'un type donné; (2)horloge: une horloge représente une séquence de temps. Chaque flot est implicitement associé à une horloge: le flot prend la  $n^i ème$  valeur de sa séquence au  $n^i ème$  instant de son horloge. Si le comportement d'un système peut être décrit de manière cyclique, alors ce cycle qui définit une séquence de temps est appelée l'horloge globale (ou l'horloge de base). Tout flot dont l'horloge est l'horloge globale prend la  $n^i ème$  valeur au  $n^i ème$  cycle d'exécution. D'autres horloges différentes peuvent être définies par rapport à l'horloge globale en utilisant un flot de valeur booléenne: par exemple, l'horloge est une séquence de temps où le flot booléen prend la valeur "vrai".

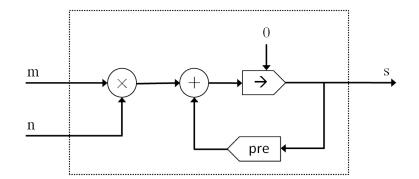

Un programme Lustre décrit les relations entre ses entrées et ses sorties par les variables et équations. Chaque variable est un flot, donc les variables X et Y sont respectivement  $(x_1, x_2, ..., x_n)$  et  $(y_1, y_2, ..., y_n)$ . L'équation X = Y dénote  $x_i = y_i$  où  $0 \le i \le n$ . Lustre propose des types de données de base et des opérateurs habituels (arithmétiques, booléens, relationnels, contrôle). Lustre offre également deux opérateurs temporels: (1) l'opérateur **pre** fait référence à la valeur de son opérande au cycle précédent; (2) l'opérateur  $\rightarrow$  est utilisé pour attribuer à son opérande la valeur au cycle initial.

Lustre a eu du succès dans deux projets industriels (l'un nucléaire et l'autre avionique) dans les années 1980. Par conséquent, Lustre a été commercialisé et donne lieu à SCADE (Safety-Critical Application Development Environment). SCADE propose un environnement synchrone dirigé par les modèles pour la conception, la validation et la mise en œuvre de logiciels embarqués. Combinant diagrammes de blocs et machines à états hiérarchiques, SCADE permet aux utilisateurs de créer les modèles graphiques de haut niveau avec des spécifications formelles rigoureuses. SCADE supporte également la simulation visuelle et l'analyse de couverture de test ainsi que des techniques de vérification formelle. Le kit complet SCADE est maintenant largement utilisé dans les industries critiques telles que l'avionique, l'automobile, la ferroviaire, etc. SCADE est également le choix de "CONNEXION" pour spécifier des modèles du système I&C.

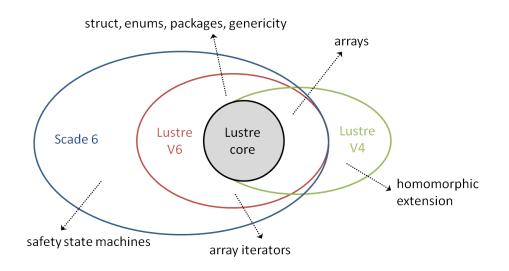

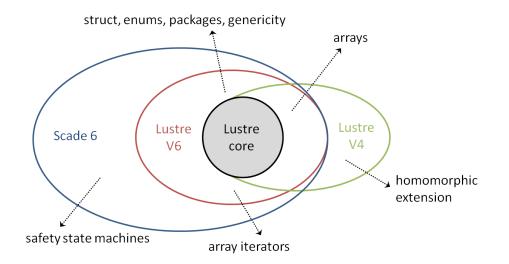

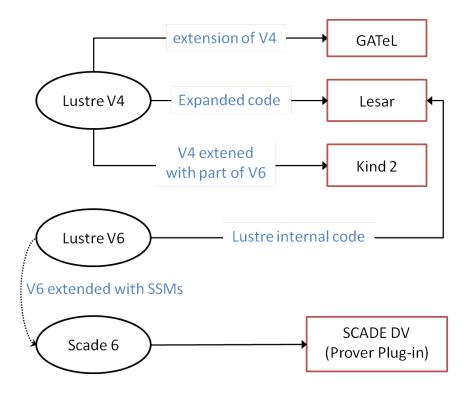

Côté académique Lustre continue à évoluer depuis plus de vingt ans et a abouti à deux versions couramment utilisées: Lustre V4 et Lustre V6. Le formalisme de la version actuelle de SCADE est Scade 6 [65]. Le formalisme Scade 6 est constitué de diagrammes de blocs (block diagrams) et de machines à états (safety state machines). Lustre V6 est le langage textuel sous-jacent des diagrammes de blocs. Les machines à états de sécurité ont évolué à partir du langage Esterel et du modèle SyncCharts des statecharts synchrones. Il a été démontré que les machines à états sont adaptables aux grands systèmes de contrôle [33]. La Fig. 2.10 illustre la relation entre différentes versions de Lustre et Scade 6.

Figure 2: Relationship between academic Lustre versions and Scade 6

Le langage Lustre bénéficie déjà de divers outils de vérification. Ils comprennent des *model checkers* open-source: Lesar [99, 100], Kind 2 [57], PKind [114], jKind [89], Zustre [117]). Ces outils sont orientés vers *model checking* traditionnel: vérification de propriété. Il y a également des outils plus orientés pour la génération de test: Lutess [44, 72, 140], Lurette [149, 111, 109, 110] et GATEL [126, 127]. GATEL a été choisi par le projet "CONNEXION". Dans cette thèse, on étudie Lesar, Kind 2 et GATEL.

### Projet "CONNEXION": vers un environnement complet de V&V

Les objectifs de "CONNEXION" concernent les Systèmes de Contrôle Nucléaire et les Technologies Opérationnelles pour maintenir un haut niveau de sûreté de fonctionnement, pour offrir de nouveaux services améliorant l'efficacité des activités opérationnelles. Avec l'approche actuelle de l'ingénierie, des modèles de plus en plus détaillés décrivant le comportement du système I&C ont été construits dans les phases amont de conception. Ces modèles sont spécifiés avec un langage métier qui est formel mais pas directement exécutable. Par conséquent, la validation fonctionnelle de ces modèles est actuellement réalisée d'une manière manuelle. Les tests automatisés ne sont possible qu'au niveau de l'implémentation.

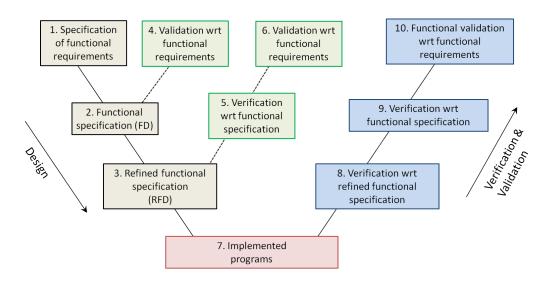

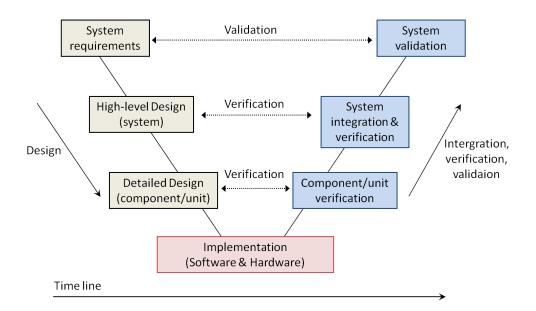

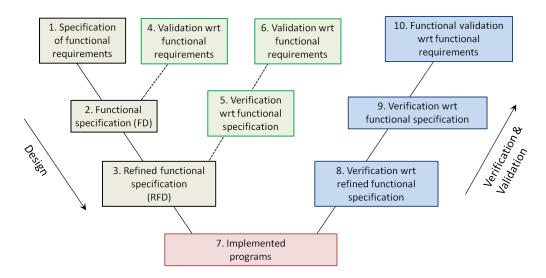

Un objectif du projet est donc d'automatiser autant que possible la validation fonctionnelle. "CONNEXION" rassemble un ensemble unique et complet d'outils de modélisation et de vérification. Intégrant les progrès récents de MBSE, "CON-NEXION" propose de renforcer le cycle en V de développement en introduisant deux sous-cycles de validation fonctionnelle. Les deux sous-cycles effectuent la vérification de la conception en modèles par rapport aux exigences fonctionnelles, résultant en un cycle innovant en triple V, schématisé par la Fig. 3.1. Le processus de développement est aligné avec la norme CEI [5], en encourageant les outils d'automatisation des tests. Le cycle de vie actuel repose sur une approche document-centrique; "CONNEXION" permet la transition vers un pratique centrée sur les modèles préconisée par l'INCOSE [7].

Figure 3: Triple V system life cycle of the I&C system

Le système I&C d'une centrale nucléaire est composé de plusieurs centaines de systèmes élémentaires (SE), contrôlant avec un très haut niveau de sécurité des milliers d'actionneurs commandés à distance: environ 8000 signaux binaires et 4000 signaux analogiques envoyés à la salle de contrôle, concernant plus de 10 000 sous fonctions I&C et plus de 300 armoires I&C. Chaque SE est un ensemble de circuits et de composants, remplissant une fonction essentielle au fonctionnement de la centrale nucléaire. Chaque SE est documenté par un dossier de système élémentaire (DSE), contenant des documents détaillant le SE dans différents aspects: fonctionnement, contrôle-commande, équipement, etc.

Un système élémentaire est composé de deux sous-systèmes:

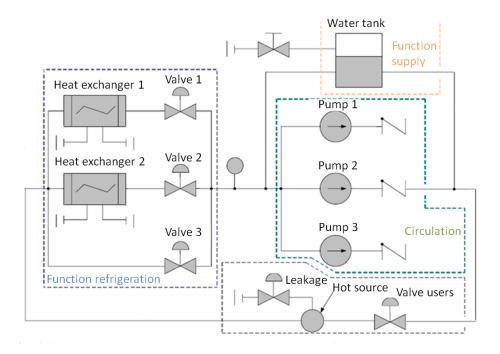

- le **procédé** représente l'infrastructure physique et l'équipement, par exemple, échangeurs de chaleur, vannes, tuyaux, etc.

- le contrôle-commande (CC) est un système réactif temps-réel réagissant en permanence avec le procédé. Il est responsable de la protection, du contrôle et de la supervision du fonctionnement du procédé.

Le procédé et le contrôle-commande représentent différents aspects du SE et donc correspondent à différents documents dans le DSE. Le contrôle-commande, décrivant l'aspect fonctionnel du SE, est spécifié par **diagramme fonctionnel** (**DF**). Le DF est un langage formel dédié au secteur nucléaire basé sur blocs prédéfinis.

Le cycle en V, correspondant à l'approche actuelle, contient les phases 1, 2, 3, 7, 8, 9 et 10 (voir Fig. 3.1). Le côté descendant du modèle V (1, 2, 3, 7) représente la conception et l'implémentation du système et le côté montant (8, 9, 10) représente la vérification et la validation. Il est important de noter que le côté descendant du modèle V concerne un seul système élémentaire, mais les activités de V&V sont réalisées en intégrant ce SE à une abstraction de son environnement [71]. De plus, la granularité du modèle de procédé utilisé en co-simulation est adapté aux objectifs de validation spécifiques à chacune de ces trois dernières phases (8, 9 et 10).

La conception commence en phase 1 avec une modélisation globale de la spécification fonctionnelle du SE à partir d'un schéma simplifié du procédé et de ses divers configurations opérationnelles. Le schéma simplifié du procédé est une spécification fonctionnelle pour l'environnement physique et son contrôle-commande [71]. En phase 2, une spécification fonctionnelle dédiée au contrôle-commande est développée sous la forme d'un diagramme fonctionnel par des ingénieurs de système. Ce DF représente une spécification explicite du comportement de contrôle-commande cohérent avec le diagramme du procédé et la description des exigences fonctionnelles produits dans la phase 1. Cette spécification de conception est ensuite progressivement détaillée dans un diagramme fonctionnel raffiné (DFR) en phase 3, qui est prêt à être transformé en programmes implémentés en phase 7. La V&V du système commence dans la phase 8 en vérifiant l'implémentation (en sortie de la phase 7) par rapport à sa spécification de conception (phase 3). En phase 9, le contrôle-commande du SE est intégré aux autres systèmes élémentaires déjà validés. A la fin du cycle de vie (phase 10), les techniques Hardware-In-the-Loop (HIL) [30] sont appliquées à tous les SEs interconnectés et validés en phase 9.

Le projet "CONNEXION" cherche à améliorer la validation fonctionnelle en introduisant un premier sous-cycle en V (phases 1, 2 et 4) et un second souscycle en V (phases 1, 2, 3, 5 et 6). Les deux sous-cycles introduisent des modèles exécutables de contrôle-commande: en phase 2 et 3, les spécifications exécutables correspondant à la DF et DFR sont développées. Phase 1 présente un modèle de haut niveau décrivant le système élémentaire. Le modèle exécutable du DF produit en phase 2 est vérifié par rapport aux exigences fonctionnelles (phase 4). Le modèle exécutable du DFR produit en phase 3 sera (i) vérifié par rapport au modèle de spécification fonctionnelle développé en phase 2 (phase 5) et (ii) vérifié par rapport aux exigences fonctionnelles (phase 6). Les deux sous-cycles V se traduisent par un cycle de vie innovant du système en triple V.

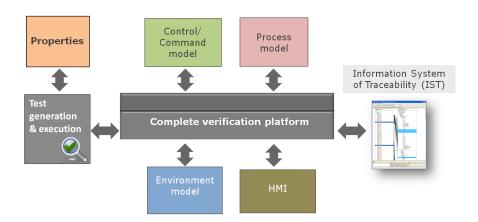

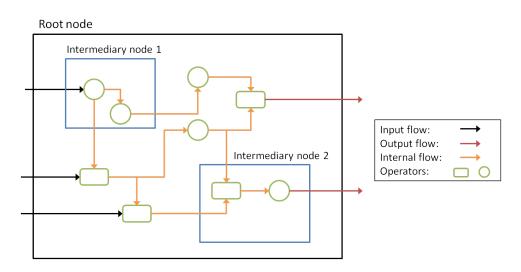

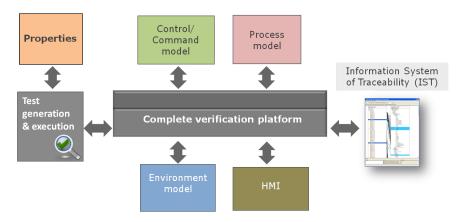

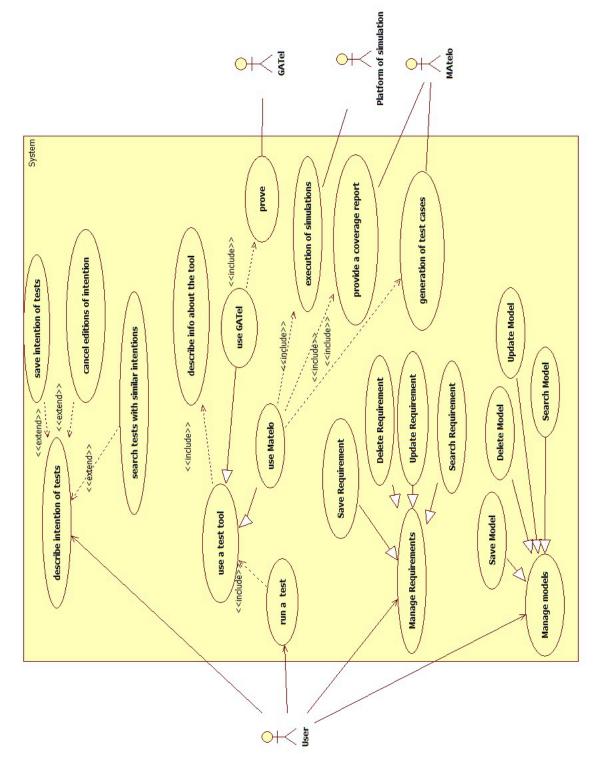

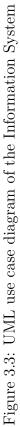

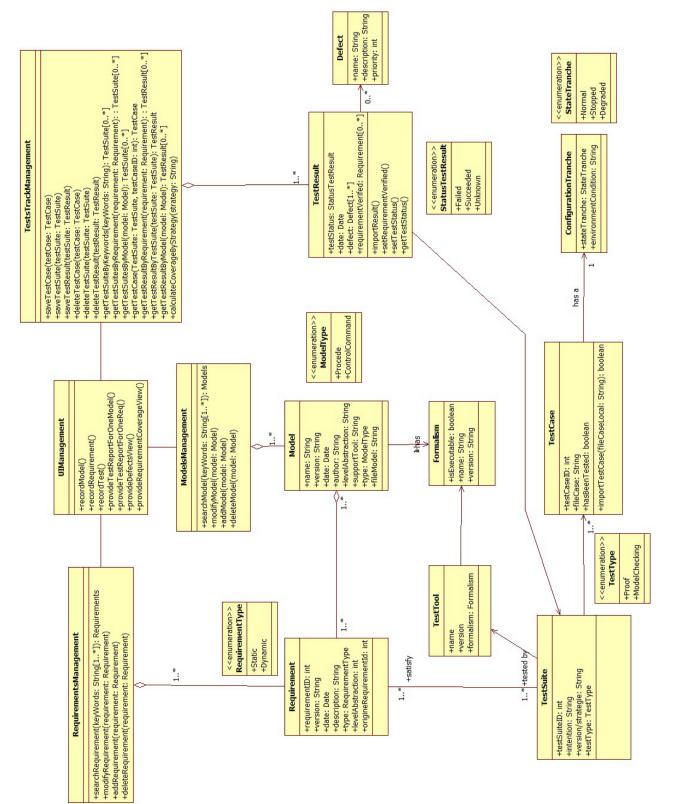

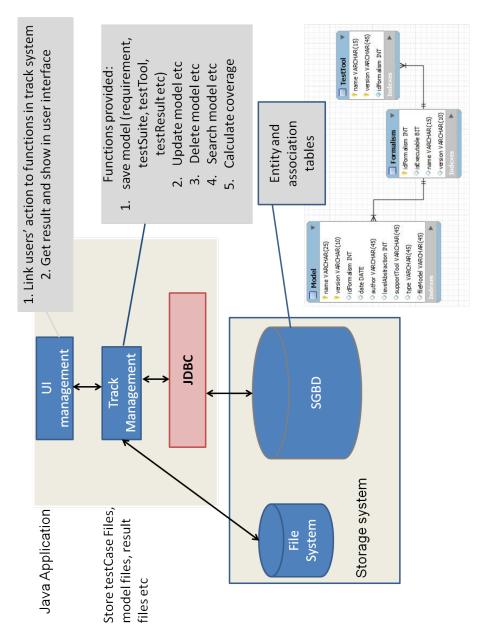

Un autre objectif de "CONNEXION" est de développer une plateforme complète de V&V soutenant les méthodologies de validation fonctionnelle présentées ci-dessus. La plateforme accompagnerait toutes les activités de V&V nécessaires au développement du système I&C tout au long de son cycle de vie. La Fig. 3.2 illustre le principe d'une telle plate-forme au niveau d'un système élémentaire. Grâce à la co-simulation du procédé et du contrôle-commande, cette plateforme permet aux ingénieurs de vérifier divers aspects du système pendant ses phases de développement. Le modèle des propriétés attendues du système et le modèle d'environnement, tel que perçu par le contrôle-commande, est également nécessaire pour décrire en particulier les exigences que le SE doit respecter et les contraintes sur sa sollicitation. Nous spécifions que le modèle d'environnement introduit les contraintes qui proviennent d'autres systèmes élémentaires interconnectés au SE sous test. Il est tout à fait possible d'effectuer une vérification sans contexte du SE sous test, qui dans ce cas ne nécessite aucun modèle d'environnement particulier. Enfin, nous pensons que la plateforme devrait être supportée par un système d'information de traçabilité (SIT). Le SIT accompagne les activités de V&V et enregistre non seulement les données mais aussi l'historique de leur relations.

Les outils préconisés par les partenaires de "CONNEXION" peuvent être divisés en deux catégories: outils de modélisation et outils de vérification. Les outils de modélisation contiennent: (1) Papyrus [90] de CEA (basé sur SysML) est utilisé pour créer un model de haut niveau d'un système élémentaire; (2) Dymola (outil commercial basé sur Modelica) pour modéliser le procédé; (3) SCADE Suite pour

Figure 4: A complete verification platform

spécifier le contrôle-commande à différents niveaux d'abstraction, correspondant à DF et DFR. Les outils de vérification sont résumés dans le tableau 1 ci-dessous.

| MaTeLo    | outil de génération de test dirigé par les modèles |

|-----------|----------------------------------------------------|

| GATeL     | Model checker pour modèles en Lustre               |

| SCADE QTE | analyse de couverture pour modèles Scade           |

| ALICES    | plateforme de co-simulation                        |

| ARTiMon   | observateur temps-réel                             |

Table 1: Aperçu des outils V&V dans "CONNEXION"

- MaTeLo [58] de ALL4TECH est un outil de génération de test dirigé par les modèles pour test d'usage statistique [123]. La génération de test est basée sur un modèle d'usage (chaîne de Markov), créées manuellement à partir de la spécification des exigences fonctionnelles. Un cas de test correspond à un chemin choisi au hasard dans le modèle d'utilisation. Dans "CONNEXION", le modèle d'utilisation est construit en fonction des exigences et les cas de test générés sont destinés aux simulations en boucle fermée.

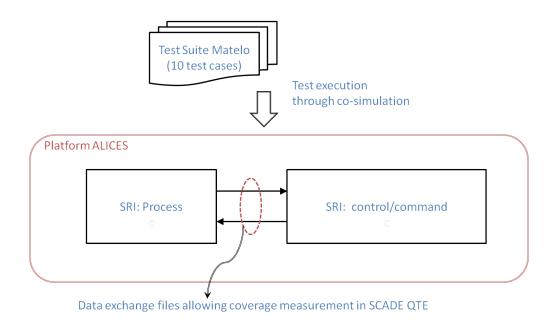

- Puisque le modèle procédé et le modèle contrôle-commande sont spécifiés dans différents languages, la simulation en boucle fermée est réalisée sur une plateforme: ALICES [136] de CORYS. ALICES est responsable de l'échange et de la synchronisation de données entre les modèles via le standard open source FMI/FMU.

- Pendant la co-simulation, ARTiMon [90] du CEA fournit une observation temps-réel des résultats d'exécution de sorte que toute violation des propriétés sera enregistrée. ARTiMon est également intégré sur ALICES.

- SCADE QTE (Qualified Testing Environment) est utilisé pour mesurer le taux de couverture structurelle à partir des résultats d'exécution.

- GATEL du CEA est un model checker pour les modèles en Lustre. Avec un objectif de test exprimé dans une version étendue de Lustre, GATEL génère des données de test qui conduisent le système à un état satisfaisant l'objectif du test. Les modèles Scade peuvent être automatiquement transformés en modèles Lustre par l'outil s2d<sup>2</sup>.

# MBT pour Validation Fonctionnelle: vers vérification hybride

Dans cette thèse, une méthodologie est définie comme une collection de processus, méthodes, et outils. Une méthodologie de MBT (Model-Based Testing) est donc la collection de processus, méthodes et outils, utilisée pour effectuer la V&V d'un système dans un contexte dirigé par les modèles. Nous proposons une nouvelle méthodologie de MBT pour des systèmes réactifs temps-réel et critique. Dans "CONNEXION", cette méthodologie est appliquée à la validation fonctionnelle des modèles du système I&C développés dans les phases amont de conception.

#### Terminologie

**Definition 5.** Unité structurelle (structural unit ou SU en anglais) Une SU est la mesure de l'unité de couverture sur le modèle, indépendamment des critères de couverture choisis.

**Definition 6.** Vérification de l'accessibilité. Pour une unité structurelle donnée, un model checker vérifie formellement si cette unité structurelle peut être exécutée par n'importe quel test. Si oui, cette unité structurelle est dite accessible.

**Definition 7.** Test en boucle ouverte. Dans un test en boucle ouverte, seul le système réactif temps réel lui-même est exécuté. Comportement de son environnement physique n'est pas pris en compte.

**Definition 8.** Test en boucle fermée. Dans un test en boucle fermée, le système réactif temps réel et son environnement sont exécutés ensemble, également appelé co-exécution. Le comportement du système réactif temps réel est donc influencé par son environnement.

<sup>&</sup>lt;sup>2</sup>The s2d tool is developed and provided by Laboratoire Sûreté des Logiciels, CEA/DRT/DT-SI/SOL, 91191 Gif sur Yvette, France

#### Workflow et outils

Notre méthodologie est composée de trois phases principales:

- Phase 1: Génération de cas de test basés sur des objectifs de test dérivés de exigences fonctionnelles de haut niveau. Ces cas de test fonctionnels sont ensuite exécutés en boucle fermée. Un outil MBT est utilisé pour la génération de test (MaTeLo dans "CONNEXION"). Un simulateur soutenant l'exécution de tests en boucle fermée est également requis. (la plate-forme ALICES dans "CONNEXION").

- Phase 2: Après l'exécution, la couverture structurelle de ces cas de test est mesurée (couverture MC/DC dans "CONNEXION"). Il est important de noter que la couverture est mesurée uniquement sur le système réactif temps réel. Les unités structurelles non couvertes sont collectées. Un outil de l'analyse de la couverture est requis dans cette phase (SCADE QTE dans "CONNEXION").

- Phase 3: Pour chaque unité non couverte, un model checker est utilisé pour générer les séquences de test exécutant l'unité considérée. Le model checker travaille sur le modèle du système réactif temps réel et donc génère des séquences de test en boucle ouverte. Avec l'aide des experts du système, les cas de test en boucle fermée peuvent être développés à partir de ces tests en boucle ouverte. Les nouveaux cas de test ne devraient pas seulement améliorer la couverture structurelle, mais également être liés aux exigences fonctionnelles. Ce processus est itéré sur chaque unité non couverte jusqu'à ce que les critères de couverture soient satisfaits. L'outil requis dans cette phase comprend un model checker (GaTeL in "CONNEXION"), pour la génération de tests basés sur la couverture. L'outil utilisé en phase 1 est aussi nécessaire pour en construire un test fonctionnellement réaliste couverant l'unité structurelle considérée.

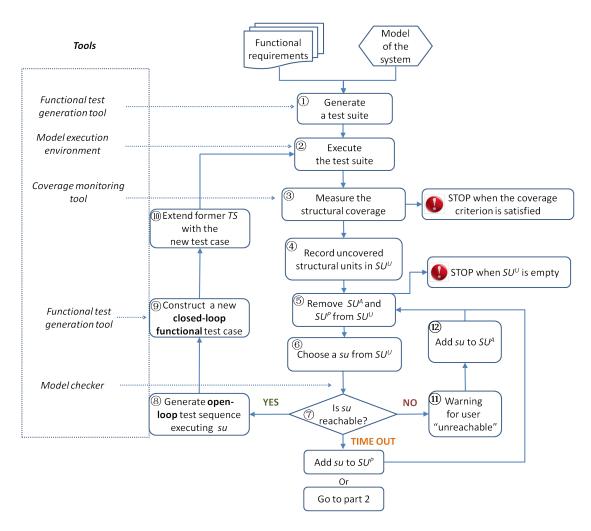

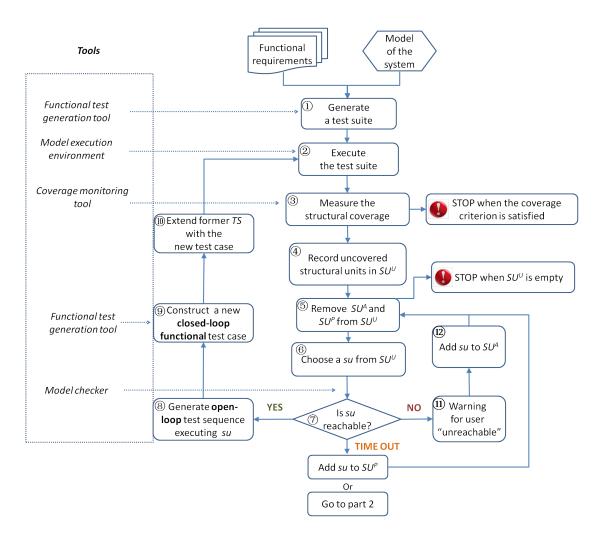

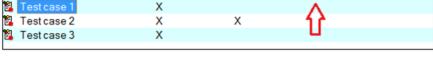

#### Méthodologie MBT: Partie 1 sur 2

La première partie de la méthodologie est schématisée par la Fig. 4.2. Un outil de génération de tests fonctionnels est d'abord utilisé pour dériver une suite de tests fonctionnels (TS) selon les exigences fonctionnelles (étape 1). Cette suite de tests est ensuite exécutée en co-simulation sur les modèles du système (étape 2). La couverture structurelle (SC) de la suite de tests est mesurée par un outil de l'analyse de couverture (étape 3). Nous définissons  $SU^U$  comme l'ensemble de toutes les unités structurelles non couvertes après l'exécution de TS (étape 4).  $SU^A$  est l'ensemble de toutes unités réellement inaccessibles et  $SU^P$  l'ensemble

de toutes les unités potentiellement inaccessibles, pour lesquelles la méthode n'a pas réussi à répondre à la question d'accessibilité. Initialement ces trois ensembles sont tous vides. Prenez une unité structurelle non couverte su de  $SU^U$  (étape 6) et appliquez un *model checker* pour vérifier si su est accessible (étape 7):

- Si su n'est pas accessible, envoyez un message d'alerte à l'utilisateur (étape 11) et enregistrez su comme une unité structurelle réellement inaccessible (étape 12):  $SU_j^A = SU_{j-1}^A \cup su$ . Passez à l'étape 5 et continuez les étapes suivantes.

- Si su est accessible, le model checker doit avoir produit des séquences de test en boucle ouverte qui forcent le système à atteindre su. Ces données seront utilisées pour construire un cas de test fonctionnel en boucle fermée (noté ntc) qui couvre cette unité structurelle particulière et probablement d'autres unités (éventuellement dans SU<sup>P</sup> qui devait être calculé à nouveau) (étape 9). À ce stade, un retour au niveau des exigences fonctionnelles est nécessaire pour assurer la réalité fonctionnelle de ntc. Complétez l'ancienne suite de tests TS avec ce nouveau cas de test (étape 10): TS<sub>i</sub> = TS<sub>i-1</sub> ∪ ntc. Passez à l'étape 2 et continuez les étapes suivantes.

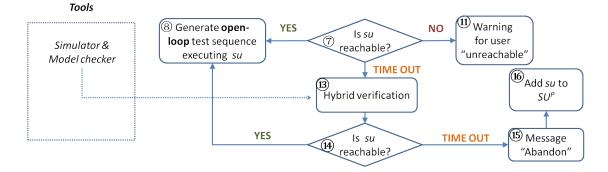

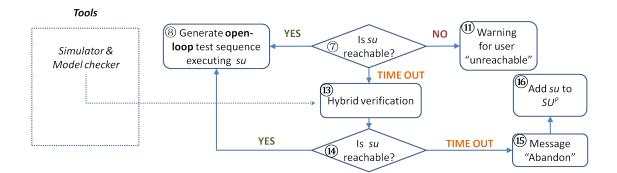

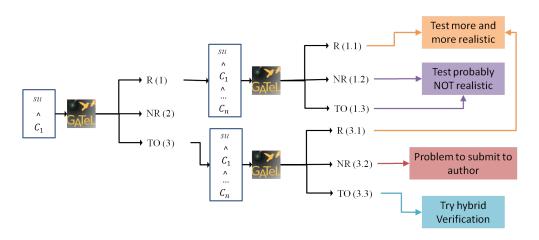

#### Méthodologie MBT: Partie 2 sur 2

La Fig. 4.3 représente la deuxième partie de notre méthodologie. La troisième possibilité de la vérification d'accessibilité d'une unité (étape 7) est TO: le model checker arrête son exécution sans donner une réponse. Notre solution est d'abord d'augmenter TO puis d'appliquer la vérification hybride (une combinaison de model checking et simulation) de manière similaire à [131] pour vérifier l'accessibilité de cette unité (étape 13). Si su est accessible alors allez à étape 8 et continuez le processus suivant. La vérification hybride peut aussi produire un TO, ce qui conduit à envoyer un message "abandon" à l'utilisateur (étape 15) puis enregistrer su comme potentiellement inaccessible (étape 16):  $SU_k^P = SU_{k-1}^P \cup su$ . Passer ensuite à l'étape 5 et poursuivre le processus suivant. Notez qu'à l'étape 5, nous avons  $SU_i^U = SU_i^U - SU_k^A - SU_k^P$ .

Ce processus converge lorsque le critère de couverture structurelle est satisfait ou s'il n'y a plus d'unités structurelles non couvertes inexplorées, c'est-à-dire  $SU_i^U = \emptyset$ . Comme  $TS_i \supset TS_{i-1}$ , ceci entraîne  $SU_i^U \subset SU_{i-1}^U$  et  $SC_i > SC_{i-1}$  car au moins une unité structurelle en plus est couverte.

Il est possible que le processus se termine immédiatement après l'exécution de la suite de tests fonctionnels initiaux  $TS_0$ , si le  $SC_0$  correspondant est déjà

Figure 5: Model-based testing methodology: part 1 of 2

Figure 6: Model-based testing methodology: part 2 of 2

satisfaisant. Sinon, à la fin du processus, si la boucle à gauche est exécutée au moins une fois, nous avons une couverture de test améliorée; si la boucle à droite est exécutée au moins une fois, c'est-à-dire  $SU^A \cup SU^P \neq \emptyset$ , une analyse plus approfondie avec les auteurs de la spécification est requise car au moins une unité structurelle est suspectée d'être code mort ou même un bug.

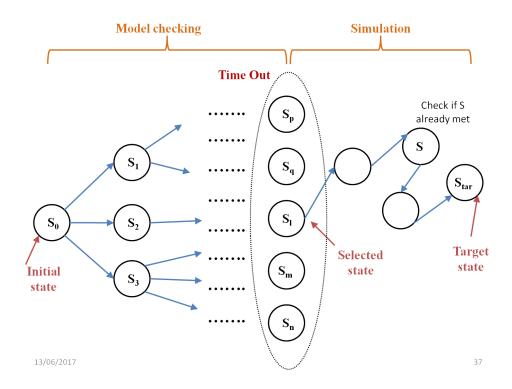

#### Une heuristique: vérification hybride

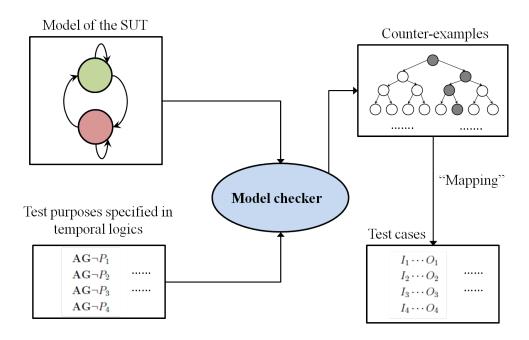

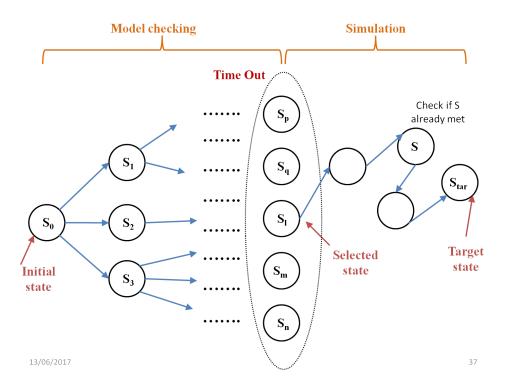

La vérification hybride [158, 157, 55] est une technique combinant *model check*ing et simulation. Le *model checking* explorer tous les états possibles tandis que la simulation explore partiellement l'ensemble de l'espace d'état. La Fig. 4.4 représente le principe de vérification hybride. La vérification hybride nécessite diverses techniques telles que l'exploration de l'espace d'état, la mémorisation des traces d'exploration, la génération avant/arrière, la simulation étape par étape, etc.

Figure 7: Principles of hybrid verification

Supposons que nous ayons un modèle du système sous test et que le problème à vérifier est le suivant: à partir d'un état initial  $S_0$ , pouvons-nous trouver un cas de test qui arrive à l'état cible  $S_{tar}$ . Dans le cadre de notre méthodologie, une unité

structurelle non couverte peut être considérée comme l'état cible. Le model checker effectue le calcul jusqu'à épuisement du temps ou de la mémoire (Time Out). Nous supposons que le model checker est capable de mémoriser les traces d'exploration des états déjà explorées juste avant TO. Par exemple, le model checker s'est arrêté à un cycle de calcul où les cinq états  $S_p, S_q, S_l, S_m et S_n$  ont été explorés. Nous sélectionnons parmi les cinq états un candidat, disons  $S_l$ , comme l'état candidat pour démarrer une simulation étape par étape. La sélection de l'état candidat est basée sur une distance informelle définie par l'utilisateur entre chaque état candidat potentiel et l'état cible. La définition d'une telle sélection reste la partie la plus délicate et la plus difficile de la technique. Certaines heuristiques peuvent être facilement trouvées, cependant, nous doutons qu'une distance formelle peut être établie. Si tel était le cas, cela pourrait être intégré au model checker.

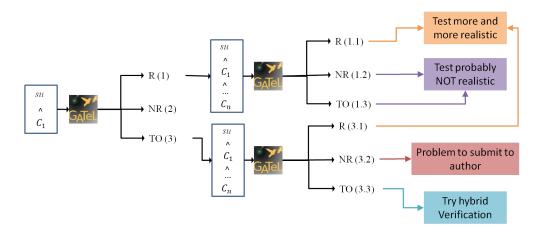

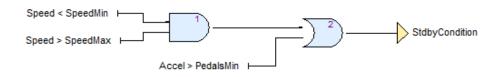

#### Raffinement par ajout progressif des contraintes

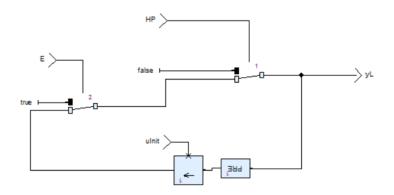

Cette section présente une technique pour raffiner la génération de test en boucle ouverte présentée dans la méthodologie ci-dessus. La technique est illustrée avec le *model checker* GATeL. GATeL prend le modèle Lustre du système de contrôlecommande comme une entrée. Il permet également deux autres entrées: un objectif de test et une description de l'environnement. Notre objectif de test est de vérifier si une unité *su* donnée peut être couverte par n'importe quel test, c'est-à-dire l'accessibilité de *su*. Au cas où *su* est atteignable, GATeL génère des séquences de test atteignant *su* désirée au dernier cycle de calcul. La description de l'environnement est composée d'expressions booléennes destinées à sélectionner parmi toutes les valeurs possibles de variables celles correspondant aux réactions réalistes de l'environnement physique. Chaque expression de sélection est indiquée comme une directive "assert" qui doit être vraie à chaque cycle de séquences générées. Ces expressions sont utilisées par GATeL pour dériver des contraintes définissant des relations entrées/sorties.

Les contraintes sont divisées en trois catégories: (1) Contraintes physiques: filtrer les valeurs qui ne pouvaient pas apparaître dans le système réel physique où le modèle est appliqué. Ces contraintes concernent seulement des variables d'entrée. (2) Contraintes d'initialisation: définir les valeurs de variables au cycle initial. Ces contraintes concernent seulement des variables d'entrée. (3) Contraintes d'exigences: dérivées des exigences fonctionnelles du système, définir les relations entre des variables d'entrée et de sortie. L'ordre pour ajouter progressivement les contraintes est en premier ajout des contraintes physiques, puis ajout des contraintes d'initialisation et finalement ajout des contraintes d'exigences. Notez que toutes les exigences fonctionnelles ne peuvent être traduites en contraintes invariantes. Dans cette thèse nous ne traitons que les exigences invariantes.

Figure 8: Refining test generation by adding constraints to the model checker

La Fig. 4.14 illustre le principe de la technique de raffinement. Étant donné une unité structurelle su non-couverte, GATeL vérifie si su est accessible tout en respectant les contraintes définies dans la description de l'environnement. D'abord cette description contient seulement une contrainte  $C_1$  et la vérification d'accessibilité peut produire trois résultats:

- (1) su est accessible (R);

- (2) su est trouvé non-accessible (NR). À ce stade, il n'est pas nécessaire d'ajouter plus de contraintes. su sera enregistrée comme une unité non accessible.

- (3) GATeL a un TO.

Pour le résultat (1) ou (3), de nouvelles contraintes sont ensuite ajoutées progressivement à la description de l'environnement, une à la fois. Après chaque ajout d'une nouvelle contrainte, GATeL vérifie à nouveau l'accessibilité de su. Avec plus de contraintes, les résultats possibles sont:

- (1.1) su est toujours accessible. Dans ce cas, GATeL génère des séquences de test où su est couverte au dernier cycle. Les séquences construisent un nouveau cas de test en boucle ouverte satisfaisant les contraintes  $C_1 \wedge C_2 \wedge$ ... $C_n$ . Cela aide à construire un cas de test en boucle fermée couvrant su.

- (1.2) su devient NR avec la nouvelle contrainte, ce qui signifie que le résultat précédent R (1) n'était pas réaliste. Cela pourrait suggérer que su est un unité structurelle inaccessible qui nécessite une analyse plus approfondie.

Cela pourrait aussi indiquer un bug quelque part: la contrainte n'est peut être pas correctement formalisée ou bien il peut y avoir une violation de l'exigence décrite par la contrainte.

- (1.3) GATEL a un TO. En général, ajouter des contraintes réduit l'espace d'état que GATEL doit explorer. Une explication possible est que les séquences de test précédemment générées dans (1) sont éliminées par la contrainte nouvellement ajoutée et GATEL, exactement comme dans (1.2), ne peut pas trouver une autre nouvelle trace couvrant *su* dans une période de temps restreinte.

- (3.1) Avec plus de contraintes ajoutées à la description de l'environnement, GATeL génère des séquences de test de plus en plus réalistes couvrant *su*.

- (3.2) Nous avons une hypothèse plus forte que "su est inaccessible".

- (3.3) Un TO. D'après Fig. 4.3 la vérification hybride est la dernière solution à envisager.

### Cas d'étude "CONNEXION": SRI

L'étude de cas proposée dans "CONNEXION" est SRI: un système élémentaire présent dans le système I&C de toutes les centrales nucléaires françaises. La première partie de notre méthodologie a été testée sur SRI et les résultats seront présentés ci-dessous. Bien que la deuxième partie de la méthodologie n'ait pas été testée avec succès, nous avons essayé trois *model checkers* (GATeL, Lesar, Kind2) sur SRI et les avons comparés par rapport aux techniques requises pour la vérification hybride.

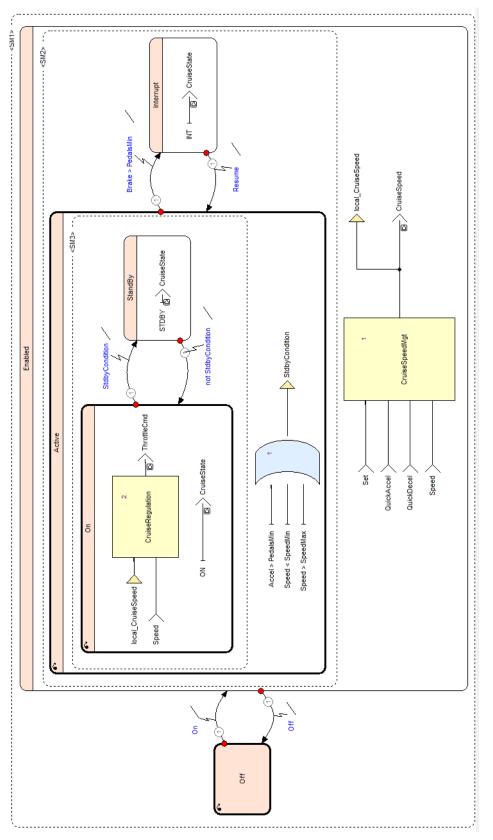

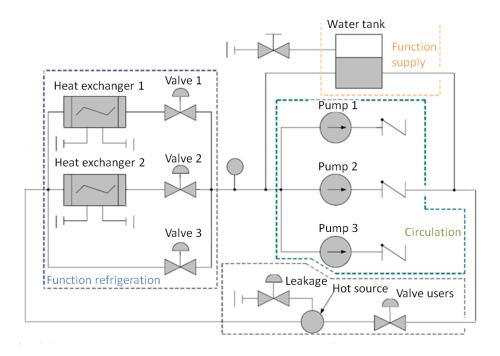

La fonction principale de SRI est d'assurer la réfrigération de plusieurs autres systèmes élémentaires en interface, dits les clients de SRI. SRI s'interface également avec une source de refroidissement SEN à travers des échangeurs de chaleur. Le procédé de SRI comprend deux échangeurs de chaleur en parallèle, où l'eau froide de SEN et l'eau chaude de ses clients se mélangent. La température de l'eau à la sortie des échangeurs de chaleur est régulée par trois vannes parallèles, variant par leur ouverture le débit et donc l'efficacité des échangeurs. Un réservoir d'eau est utilisé pour compenser la fuite éventuelle du circuit. Trois pompes en parallèle assurent la circulation de l'eau dans le système (La troisième pompe n'est utilisée qu'un remplacement). La Fig.5.1 illustre un schéma simplifié du procédé de SRI. Le contrôle-commande de SRI est modélisé en diagramme de blocs dans SCADE Suite.

Figure 9: A simplified schema of SRI

Les résultats d'expérimentations sont organisés en trois phases, de la même manière que la méthodologie est présentée précédemment.

#### Phase 1

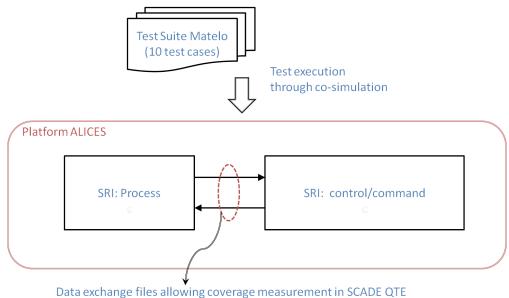

Les activités réalisées pendant cette phase comprennent la génération de tests fonctionnels avec l'outil MaTeLo et l'exécution de ces tests en boucle fermée sur la plateforme ALICES. À partir des exigences fonctionnelles, AREVA, un partenaire du projet, a créé un modèle d'usage de SRI dans MaTeLo et a généré une suite de test contenant 10 cas de test. Ensuite, nous exécutons ces 10 cas de test par simulation en boucle fermée sur ALICES. Nous obtenons les scripts enregistrant les données d'échange entre le procédé et le contrôle-commande pendant la simulation.

#### Phase 2

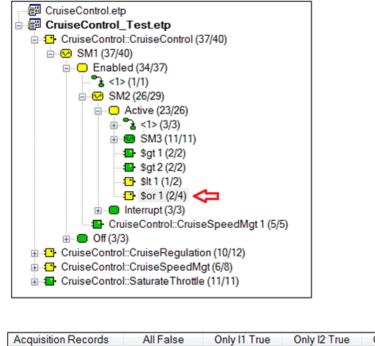

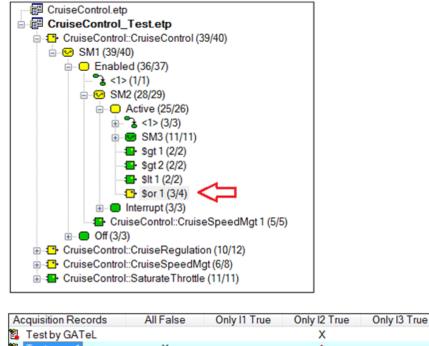

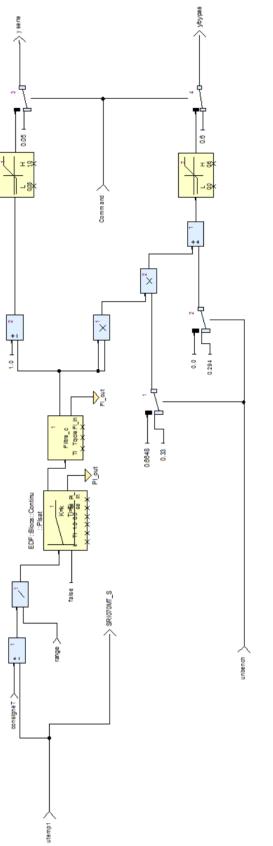

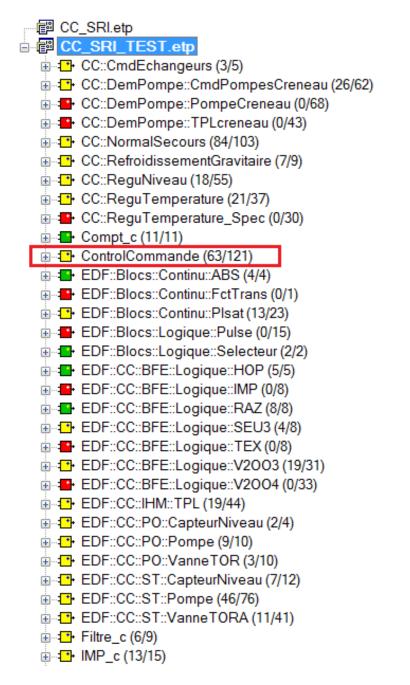

Les scripts obtenus en phase 1 sont maintenant utilisés pour mesurer la couverture MC/DC sur chaque opérateur composant le modèle de contrôle-commande, comme indiqué dans la Fig. 5.3. Plus de détails concernant les métriques de couverture des modèles Scade peuvent être trouvés dans [80]. Le modèle du système de contrôle-commande en Scade est structuré comme une hiérarchie d'opérateurs. Au niveau

de l'opération racine (l'opérateur du plus haut niveau), le taux de couverture MC/DC mesuré d'environ 50%.

Figure 10: Coverage measurement

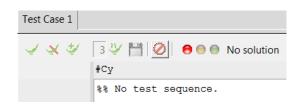

### Phase 3

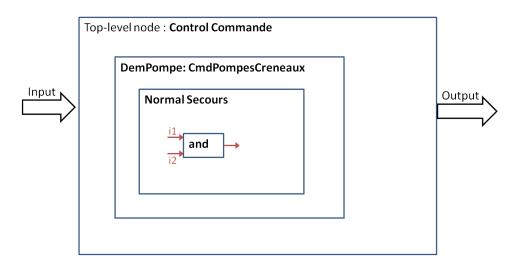

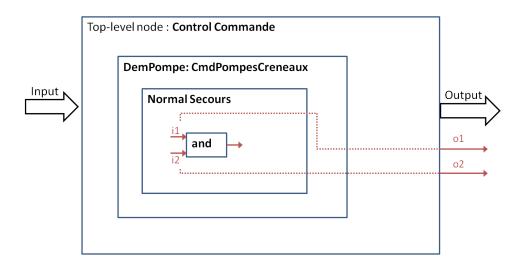

Nous devons choisir une unité structurelle non couverte pour effectuer la vérification d'accessibilité. Une suggestion est de commencer avec un opérateur au plus "profond" possible, qui ne contient pas d'autres opérateurs. L'avantage est qu'un test exécutant cette unité au bas niveau a une grande chance de couvrir également d'autres SU au niveau supérieur qui n'ont pas été couvertes. L'unité structurelle que nous avons choisie est à trois niveaux plus bas par rapport à l'opérateur racine: les deux entrées booléennes d'un opérateur "and" logique n'ont jamais pris la valeur VRAI tous les deux à la fois.

GATeL est ensuite utilisé pour vérifier l'accessibilité de cette unité structurelle selon la technique de raffinement: ajouter progressivement des hypothèses sur le comportement de l'environnement. Ces hypothèses sont traduites en contraintes invariantes pour GATeL. Ces contraintes peuvent être trouvées dans l'annexe A. Au début il y avait une seule contrainte physique C1. Cette contrainte suppose trois situations: (1) la température de l'eau est comprise entre 0°C et 100°C; (2) le niveau d'eau dans le réservoir est compris entre 0 et le niveau maximum; (3) les variables booléennes représentant l'état de la pompe et le défaut de la pompe ne peuvent pas prendre la valeur VRAI en même temps (si la variable d'état est vraie, cela signifie que la pompe n'a pas de défaut).

Sous la contrainte C1, cette unité structurelle a été trouvée accessible et une séquence de test contenant 3 cycles a été généré. Nous avons mesuré à nouveau la couverture MC/DC, y compris ce nouveau test généré. Le nouveau test a non seulement couvert l'unité considéré mais aussi il a augmenté le taux de couverture de 50% à 80% au niveau de l'opération racine. Cela signifie que d'autres unités structurelles non couvertes précédemment ont également été exécutées par le nouveau test.

Ensuite, une contrainte d'initialisation C2 a été ajoutée à la description de l'environnement. C2 suppose que dans l'état initial du système, tous les deux échangeurs de chaleur fonctionnent normalement. Nous avons rencontré TO au départ: GATeL a arrêté l'exécution sans donner de résultat. En fait, la configuration dans GATeL concernant le nombre maximum de cycles générés avait été fixé à 20, ce qui n'est pas suffisant sous les hypothèses  $C_1 \wedge C_2$ . Nous avons donc augmenté cette configuration à 30 et nous avons obtenu une séquence de test de 23 cycles. Le temps de calcul est 6391 secondes et la mémoire utilisée 272309 kilo-octets.

Ce résultat indique que la séquence de test à trois cycles obtenue la première fois n'est pas réaliste. Cela prouve que le raffinement en ajoutant progressivement des contraintes peut aider à améliorer la réalité fonctionnelle de test généré. Nous admettons qu'à partir d'un test en boucle ouverte de 23 cycles, construire un test en boucle fermée ne sera pas facile. Mais la profondeur du test suggère aussi que la conception manuelle d'un test couvrant l'unité structurelle peut être très difficile.

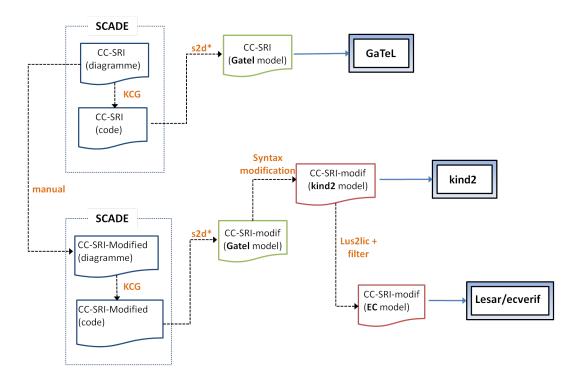

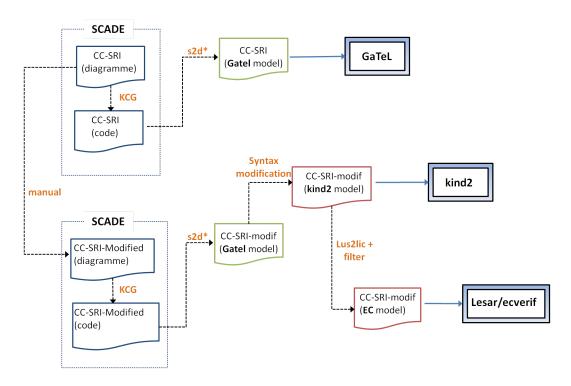

#### Vers la vérification hybride

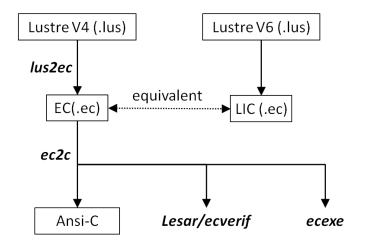

Nous avons testé trois *model checkers* pour le langage Lustre: GATeL, Lesar et Kind 2, pour mettre en œuvre la méthodologie complète, y compris la vérification hybride en particulier. Lesar prend en entrée un model en Lustre V4; Kind2 accepte Lustre V4 étendu avec une partie de V6; alors que GATeL travaille sur une extension spécifique de Lustre V4. La première étape de cette expérimentation consiste à construire un modèle d'entrée correct pour chaque *model checker*. Nous avons commencé avec le modèle du contrôle-commande de SRI en Scade textuel, généré automatiquement à partir du modèle graphique par SCADE KCG (générateur de code). Ce modèle est ensuite traduit par l'outil s2d en une extension de Luster V4 directement acceptable par GATeL.

L'unité structurelle non couverte choisie pour l'expérience est à trois niveaux plus bas par rapport à l'opérateur racine. Par conséquent, les entrées et sorties de cette unité sont considérées comme variables internes ou locales. Cependant, pour Kind 2 et Lesar, il est nécessaire de spécifier une propriété concernant uniquement les entrées et les sorties de l'opérateur racine. Donc nous décidons de modifier le modèle graphique en Scade de manière à faire ressortir ces variables internes pertinentes aux sorties du niveau racine. Ensuite, en suivant la procédure ci-dessus, nous obtenons un modèle modifié du contrôle-commande de SRI pour GATeL.

Le modèle d'entrée pour GATeL n'est pas directement lisible pour Kind 2 et Lesar. Heureusement, le modèle pour GATeL ne contient pas de syntaxe non incluse ni dans Lustre V4 ni dans V6. Cependant, il doit encore être soumis à une modification de syntaxe incluant:

- Pour la définition de données complexes, par exemple, type T\_NS = {T1: real, T2: real, 'toutes les virgules , doivent être remplacées par des points-virgules ;.

- GATeL permet d'écrire assume expression\_1 pour indiquer que expression\_1 est toujours vrai. Dans Lustre, la directive assume doit être remplacée par assert avec la même sémantique.

- Scade et GATeL offrent les ID utilisateur #1, #2, #3 pour identifier différentes instances du même opérateur. Cette définition n'existe pas dans Lustre V4 ou V6.

- Dans Scade et GATeL, l'évaluation d'une variable structurée peut être effectuée à travers un opérateur make comme make T = (v1, v2, v3) où T est une variable de type T\_NS. Dans Lustre, cela devrait écrire comme T.T1=v1; T.T2=v2; T.T3=v3.

- Scade et GATeL offrent un opérateur caseof comme une déclaration "switch". Dans Lustre, caseof doit être remplacé par plusieurs if then else.

Après ces modifications, le modèle GATeL a été traduit en modèles d'entrée pour Kind2 et Lesar. La figure 5.9 donne un aperçu de la relation entre les différents modèles.

Les trois *model checkers* répondent assez différemment au même problème:

• Lesar est à court de mémoire, c'est-à-dire Time Out. En fait, Lesar est un *model checker* qui gère exclusivement les valeurs booléennes. Il est donc clairement non adapté pour le modèle de contrôle-commande de SRI. Lesar n'enregistre pas les résultats temporaires pendant l'exploration de l'espace

Figure 11: Applying different model checkers to the SRI CC

d'état. En conséquence, il est pas possible d'effectuer la vérification hybride, ce qui nécessite une mémorisation de traces d'exploration.

- GATeL réussit à générer des séquences de test qui améliorent la couverture structurelle, comme discuté dans la section précédente. Cependant, GATeL n'offre que la génération de test en arrière (backward) et donc il n'est pas adapté pour la vérification hybride.

- Kind 2 repose sur les solveurs SMT disponibles sur le marché. Les solveurs SMT ne sont pas adaptés pour les expressions non-linéaires telles que la multiplication/division des variables (présentes dans le modèle du contrôlecommande de SRI). Une solution consiste à remplacer ces expressions non linéaires par des abstractions définies dans des contrats de type "assumegrantee". Le modèle ainsi obtenu peut convenir à la vérification des propriétés, s'il est prouvé équivalent au modèle original. Mais notre objectif est la génération de test.

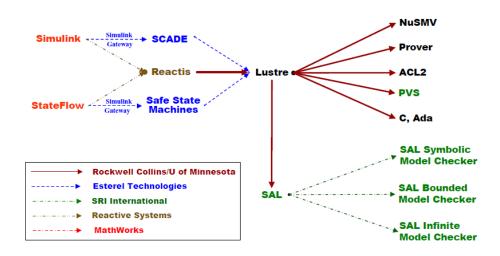

Nous avons également cherché des traducteurs de Lustre vers d'autres langages de modélisation afin de profiter d'autres outils puissants tels que NuSMV. Il existe un framework du traducteur Lustre qui est propriétaire de Rockwell Collins et l'Université du Minnesota. Mais le projet n'est plus financé. Un autre traducteur académique de Lustre à SMV n'est plus maintenu. Concernant SCADE Design Verifier (basé sur le *model checker* Prover), sa licence n'était pas incluse dans "CONNEXION". Par conséquent nous sommes arrivés à la conclusion que la mise en œuvre de notre méthodologie complète nécessite une intégration de plusieurs outils. Une solution alternative est de développer un nouveau *model checker* avec les caractéristiques suivantes: génération en avant et arrière; vider les états inexplorés après TO; reprendre l'exploration après simulation.

### Conclusion

La vérification et validation du système réactif temps-réel et critique sont soumises aux normes et certifications rigoureuses. Intégration des progrès récents dans l'ingénierie des systèmes dirigée par les modèles (MBSE) dans le cycle de vie de cette catégorie de systèmes constitue le contexte de cette thèse. Approches MB-SE, telles que "Model-Based Design" (MBD) et "Model Based Testing" (MBT), encouragent la vérification dans les étapes amont de conception, permettant une détection des défauts le plus tôt possible. C'est très rentable pour de tels systèmes puisque le coût des défauts découverts dans le système réel peut être extrêmement élevé.

Nous proposons une méthodologie MBT dirigée par la couverture structurelle et exigences fonctionnelles. La méthodologie repose sur une utilisation répétitive de *model checker* pour générer des séquences de test en boucle ouverte basées sur la couverture. Le passage de boucle ouverte à boucle fermée nécessite une expertise des ingénieurs du système et n'est pas dans le champ de notre recherche. Cependant, nous proposons un raffinement de génération de test en ajoutant progressivement des contraintes de l'environnement. Ces contraintes sont dérivées des conditions physiques, des conditions d'initialisation et des exigences fonctionnelles. Sous ces contraintes, les séquences de test générées doivent respecter les comportements réalistes par rapport au système complet. Notre méthodologie considère également qu'un model checker peut TO en raison de problème d'explosion d'état et propose une heuristique dite vérification hybride qui combine le *model* checking et la simulation. Le principe est de collecter les états explorés au cycle de calcul juste avant le TO, sélectionner un état candidat qui devrait être le plus proche de l'état cible, et de commencer une simulation étape par étape à partir de cet état candidat en essayant d'atteindre l'état cible.

La méthodologie proposée dans cette thèse est très coûteuse et donc adaptée exclusivement pour les systèmes hautement critiques en sûreté de fonctionnemen-

t. Les activités de V&V de ce type de systèmes sont soumises à des normes rigoureuses. De tels systèmes nécessitent un niveau de couverture très élevé audelà des exigences fonctionnelles. Notre méthodologie offre une solution pour automatiser autant que possible la génération de test basée sur la couverture, qui est un processus purement manuel dans l'approche d'ingénierie actuelle. Deuxièmement, la méthodologie inclut un raffinement de génération de test en boucle ouverte. Le passage de la boucle ouverte à la boucle fermée nécessite une collaboration des experts du système. Notre raffinement peut aider les experts du système à intervenir efficacement dans la préparation de cas de test fonctionnels en boucle fermée. Notre méthodologie est donc rentable car il permet aux experts du système de gagner du temps. Enfin nous avons examiné divers model checkers pour le langage Lustre pour mettre en œuvre la méthodologie. Nous arrivons à la conclusion qu'une intégration de plusieurs outils est nécessaire. À notre avis, il est également avantageux de revisiter les versions académiques de Lustre et les outils associés. Cependant, ces recommandations argumentées dépassent le travail de cette thèse.

Les travaux futurs concernent (1) la définition et éventuellement le développement d'un nouvel outil pour effectuer la vérification hybride; (2) la proposition de stratégies de sélection utilisées en vérification hybride, c'est-à-dire, comment définir une distance entre deux états dans l'espace d'état d'un système de transition; (3) un framework généralisé de raffinement de la génération de test en boucle ouverte; (4) l'exploration de la génération de test par Kind 2 en utilisant les contrats "assumegarantee" par rapport à la vérification hybride.

# List of Figures

| 1    | Testing with model checkers                                              | 9  |

|------|--------------------------------------------------------------------------|----|

| 2    | Relationship between academic Lustre versions and Scade 6                | 11 |

| 3    | Triple V system life cycle of the I&C system                             | 12 |

| 4    | A complete verification platform                                         | 15 |

| 5    | Model-based testing methodology: part 1 of 2                             | 19 |

| 6    | Model-based testing methodology: part 2 of 2                             | 19 |

| 7    | Principles of hybrid verification                                        | 20 |

| 8    | Refining test generation by adding constraints to the model checker      | 22 |

| 9    | A simplified schema of SRI                                               | 24 |

| 10   | Coverage measurement                                                     | 25 |

| 11   | Applying different model checkers to the SRI CC                          | 28 |

| 1.1  | Embedded systems, reactive systems and real-time systems                 | 37 |

| 1.2  | Reactive systems                                                         | 38 |

| 1.3  | V-model: system development lifecycle                                    | 41 |

| 1.4  | W-model: extension of V-model strengthening the bond between             |    |

|      | design and test                                                          | 42 |

| 2.1  | Model checking approach                                                  | 52 |

| 2.2  | Graphical representation of a finite transition system                   | 55 |

| 2.3  | Execution tree of the transition system HOP                              | 56 |

| 2.4  | Comparison of path quantifiers $\mathbf{A}$ and $\mathbf{E}$             | 60 |

| 2.5  | Testing with model checkers                                              | 62 |

| 2.6  | Two common execution schemes for reactive systems $\ldots \ldots \ldots$ | 66 |

| 2.7  | A simple counter described using Lustre operators                        | 71 |

| 2.8  | Lustre program structure                                                 | 72 |

| 2.9  | Function HOP depicted in Scade block diagram                             | 75 |

| 2.10 | Relationship between academic Lustre versions and Scade 6                | 77 |

| 2.11 | Model checking tools for Lustre and Scade                                | 79 |

| 2.12 | An overfiew of Lustre V4 and V6 formats and tools                        | 84 |

| 2.13 | Translator Framework                                                     | 85 |

| 3.1  | Triple V system life cycle of the I&C system                                               |

|------|--------------------------------------------------------------------------------------------|

| 3.2  | A complete verification platform                                                           |

| 3.3  | UML use case diagram of the Information System                                             |

| 3.4  | UML class diagram of the Information System                                                |

| 3.5  | Prototype                                                                                  |

| 4.1  | Model-based testing process                                                                |

| 4.2  | Model-based testing methodology: part 1 of 2                                               |

| 4.3  | Model-based testing methodology: part 2 of 2                                               |

| 4.4  | Principles of hybrid verification                                                          |

| 4.5  | Cruise control model in SCADE Suite                                                        |

| 4.6  | Original structural coverage of cruise control model                                       |

| 4.7  | GATeL interface: node of test                                                              |

| 4.8  | GATeL interface: test case generated                                                       |

| 4.9  | New structural coverage of cruise control model $\ .$                                      |

| 4.10 | Operator modified in cruise control model                                                  |

| 4.11 | GATeL interface: unreachable branch detected                                               |

| 4.12 | Cruise control model complexity: Nesting Level metrics                                     |

| 4.13 | Cruise control model complexity: Data Flow metrics                                         |

| 4.14 | Refining test generation by adding constraints to the model checker 123                    |

| 5.1  | A simplified schema of SRI                                                                 |

| 5.2  | A part of the SRI control/command in SCADE Suite                                           |

| 5.3  | Coverage measurement                                                                       |

| 5.4  | $\rm MC/DC$ coverage on each operator of the control/command model . 129                   |

| 5.5  | The uncovered SU chosen for experiment                                                     |

| 5.6  | MC/DC coverage at the $su$ level                                                           |

| 5.7  | MC/DC coverage at the top level: before and after $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |

| 5.8  | The uncovered SU chosen for experiment: modify the top level node $133$                    |

| 5.9  | Applying different model checkers to the SRI CC                                            |

# List of Tables

| 1   | Aperçu des outils V&V dans "CONNEXION"                         | 15 |

|-----|----------------------------------------------------------------|----|

| 2.1 | Application of function HOP in regulating water level          | 56 |

| 2.2 | CTL and LTL syntax comparison                                  | 58 |

| 2.3 | A summarize of some model checkers for different languages and |    |

|     | techniques                                                     | 61 |

| 2.4 | Some basic Esterel statements                                  | 67 |

| 2.5 | A sampling of Signal operators                                 | 68 |

| 2.6 | Example of an execution of the counter                         | 71 |

| 2.7 | Example of an execution of the function HOP                    | 73 |

| 2.8 | Comparison of Esterel, Signal and Lustre                       | 73 |

| 3.1 | Overview of "CONNEXION" verification tools                     | 95 |

# Contents

| 1        | ion                                    | 36      |                                                  |    |  |

|----------|----------------------------------------|---------|--------------------------------------------------|----|--|

|          | 1.1                                    | Proble  | em statement                                     | 43 |  |

|          | 1.2                                    | Thesis  | contributions                                    | 44 |  |

|          | 1.3                                    | Thesis  | organization                                     | 48 |  |

| <b>2</b> | Mo                                     | del che | ecking and its application                       | 50 |  |

|          | 2.1                                    | Model   | checking preliminaries                           | 53 |  |

|          |                                        | 2.1.1   | Transition systems                               | 53 |  |

|          |                                        | 2.1.2   | Temporal Logic and properties                    | 57 |  |

|          |                                        | 2.1.3   | Model checking algorithms                        | 59 |  |

|          | 2.2                                    | Testin  | g with model checkers                            | 61 |  |

|          | 2.3                                    | Synch   | ronous approach for real-time systems            | 65 |  |

|          |                                        | 2.3.1   | Esterel                                          | 66 |  |

|          |                                        | 2.3.2   | Signal                                           | 67 |  |

|          |                                        | 2.3.3   | Lustre                                           | 68 |  |

|          |                                        | 2.3.4   | A brief summary                                  | 72 |  |

|          | 2.4                                    | The st  | tory of Lustre                                   | 74 |  |

|          |                                        | 2.4.1   | SCADE and Lustre                                 | 74 |  |

|          |                                        | 2.4.2   | Lustre versions                                  | 76 |  |

|          |                                        | 2.4.3   | Model checking tools for Lustre                  | 77 |  |

|          |                                        | 2.4.4   | Lustre translators                               | 83 |  |

| 3        | Pro                                    | ject "( | CONNEXION": Towards a complete testing environe- |    |  |

|          | mer                                    | nt      |                                                  | 87 |  |

|          | 3.1                                    | Functi  | ional validation objectives                      | 88 |  |

|          | 3.2 Unique and complete tool box       |         |                                                  |    |  |

|          | 3.3                                    |         |                                                  |    |  |

|          | 3.4 Information system of traceability |         |                                                  |    |  |

| 4            | Mod          | del-based testing for functional validation: Towards       | hybrid |

|--------------|--------------|------------------------------------------------------------|--------|

|              | verification |                                                            |        |

|              | 4.1          | Model-based testing process                                | 104    |

|              |              | 4.1.1 Coverage criteria                                    | 107    |

|              |              | 4.1.2 A new MBT methodology for safety-critical systems .  | 108    |

|              |              | 4.1.3 A heuristic: hybrid verification                     | 113    |

|              |              | 4.1.4 An first example: cruise control                     | 114    |

|              | 4.2          | Refinement by gradually adding constraints in GATeL        | 121    |

|              |              | 4.2.1 Three categories of constraints                      |        |

|              |              | 4.2.2 Refinement by adding progressively the constraints . | 124    |

| 5            | "CC          | ONNEXION" Case study: SRI                                  | 125    |

| 0            | 5.1          | Description of SRI                                         |        |

|              | 5.2          | Experimentation results of part 1                          |        |

|              | 5.3          | Lustre model checkers toward hybrid verification           |        |

| 6            | Con          | clusion                                                    | 136    |

| Δт           | nen          | dices                                                      | 139    |

| <b>~</b> }   | pen          |                                                            | 105    |

| $\mathbf{A}$ | Con          | straints coded in GATeL to refine test generation          | 140    |

# Chapter 1 Introduction

Our daily life relies more and more on all kinds of software and hardware systems. The complexity of these systems is also increasing rapidly. No longer standalone, these systems are typically embedded in a larger environment, connecting and interacting with other components. **Embedded systems**, first appeared in large industrial applications: factories, power plants, transportation systems, avionics and automotive. Nowadays they also concern a wide variety of everyday smart objects: cell phones, digital watches, microwave ovens, etc. Embedded system can be considered as a combination of software, hardware, and sometimes additional mechanical, electronic or other parts. These components are interconnected, designed to perform a dedicated function. This distinguishes an embedded system from a general-purpose computer for multiple tasks. An embedded computer is just one functional element of a system (another brick in the wall), rather than a stand-alone versatile computing machine. Embedded systems are vulnerable to errors since the number of defects grows exponentially with the number of interacting system components.

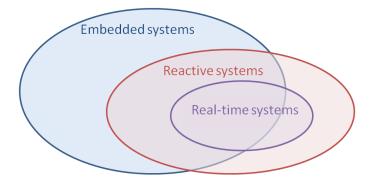

Most embedded systems are **reactive** systems and **real-time** systems. We call "reactive" systems that are permanently interacting with its (possibly physical) environment; and we reserve the term "real-time" for reactive systems that are subject to externally defined timing constraints, as suggested by Benveniste and Berry [26]. In other words, we distinguish two kinds of time constraints:

- 1. Synchronous hypothesis assumes that the system is able to react to an external event from its environment before any further event occurs. Synchronous hypothesis concerns the *input frequencies*, meaning between two successive inputs, the environment is considered unchanged.

- 2. *Real-time constraint* requires that the system is not only able to react to its environment but also to guarantee response within specified time constraints.

Figure 1.1: Embedded systems, reactive systems and real-time systems