# Analysis and performance improvement in high frequency wide-band LNAs

Masoumeh Sabzi

#### ▶ To cite this version:

Masoumeh Sabzi. Analysis and performance improvement in high frequency wide-band LNAs. Electronics. Université de Nantes; Université de Téhéran, 2021. English. NNT: . tel-03345226

## HAL Id: tel-03345226 https://hal.science/tel-03345226

Submitted on 15 Sep 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT DE

#### L'UNIVERSITE DE NANTES L'UNIVERSITE DE TEHERAN

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité: Electronique

Par

### **Masoumeh SABZI**

# Analysis and performance improvement in high frequency wide-band LNAs

Thèse présentée et soutenue à l'Université de Téhéran - Iran, le 31 août 2021 Unité de recherche : IETR UMR CNRS 6164

#### Rapporteurs avant soutenance :

Abolali ABDIPOUR Professeur, Amir Kabir University, Tehran, Iran

Valérie VIGNERAS Professeur, INP Bordeaux, France

#### **Composition du Jury:**

Président : Nasser MASOUMI Professeur, University of Tehran, Iran

Examinateurs: Abdolali ABDIPOUR Professeur, Amirkabir University of Technology, Tehran, Iran

Abdolreza NABAVI Professeur, Tarbiat Modares University, Tehran, Iran

Jean Marie PAILLOT Professeur, Université de Poitiers, France

Valérie VIGNERAS Professeur, INP Bordeaux, France

Dir. de thèse : Tchanguiz RAZBAN Professeur, Université de Nantes, France Co-dir. de thèse : Mahmoud KAMAREI Professeur, University of Tehran, Iran

Encadrant: Yann MAHE Maître de Conférences, Université de Nantes, France

Invité

Samad SHEIKHAEI Maître de Conférences, University of Tehran, Iran

## **ACKNOWLEDGEMENT**

I would like to thank the following people without whom, I could have never been able to complete this research. First I would like to thank my supervisors Professor M. Kamarei, Professor T. Razban and Mr. Y. Mahe. in both University of Tehran and University of Nantes for their incredible help for the project, their support, encouragement and patience.

Special thanks to the love of my life, my loving and supportive husband— I simply couldn't have done this without your patience and encouragement.

And I am also grateful to my parents, who set me off on the road to this Ph.D. a long time ago- I couldn't have been able to pursue my dreams without your love and support.

# **TABLE OF CONTENTS**

| R  | esum                  | ne                                                                     | 11         |

|----|-----------------------|------------------------------------------------------------------------|------------|

| In | $\operatorname{trod}$ | uction                                                                 | 17         |

| 1  | Lite                  | erature Review                                                         | 25         |

|    | 1.1                   | Introduction                                                           | 25         |

|    | 1.2                   | Common Gate Topology                                                   | 25         |

|    | 1.3                   | Common Source Topology                                                 | 32         |

|    |                       | 1.3.1 Common Source Topology with Resistive Feedback                   | 32         |

|    |                       | 1.3.2 Common Source Topology with Inductive Degeneration               | 34         |

|    | 1.4                   | Linearization Techniques in LNAs                                       | 38         |

|    | 1.5                   | Study of Different Technologies for Implementation of RF circuits      | 46         |

| 2  | Firs                  | st Approach: Optimization Of LNA's First Stage To Reduce Overall       |            |

|    | Noi                   | se Figure in Multi-Stage LNAs                                          | <b>4</b> 9 |

|    | 2.1                   | Introduction                                                           | 49         |

|    | 2.2                   | Noise Analysis                                                         | 51         |

|    | 2.3                   | Circuit design with proposed approach in discrete mode                 | 57         |

|    | 2.4                   | Design method of Inductively degenerated common source stage with pro- |            |

|    |                       | posed method                                                           | 61         |

|    |                       | 2.4.1 Design analysis and calculations                                 | 62         |

|    |                       | 2.4.2 Simulation Results                                               | 65         |

|    |                       | 2.4.3 Conclusion                                                       | 67         |

| 3  | Sec                   | ond Approach: Parallel Amplifier Design Technique                      | 71         |

|    | 3.1                   | Introduction                                                           | 71         |

|    | 3.2                   | Noise Analysis                                                         | 72         |

|    | 3.3                   | Noise Analysis of parallel path                                        | 75         |

|    | 3.4                   | Simulation Results                                                     | 78         |

|    | 3.5                   | Layout Results                                                         | 81         |

#### TABLE OF CONTENTS

| 4  | Thir   | d App   | proach: New Noise Cancellation Topology In Common-gate      |    |

|----|--------|---------|-------------------------------------------------------------|----|

|    | LNA    | S       |                                                             | 85 |

|    | 4.1    | Introdu | action                                                      | 85 |

|    | 4.2    | Noise A | Analysis                                                    | 87 |

|    | 4.3    | Circuit | Design                                                      | 90 |

| Co | onclus | sion    |                                                             | 95 |

|    |        | 4.3.1   | First Approach: Optimization Of LNA's First Stage To Reduce |    |

|    |        |         | Overall Noise Figure in Multi-Stage LNAs                    | 95 |

|    |        | 4.3.2   | Second Approach: Parallel Amplifier Design Technique        | 96 |

|    |        | 4.3.3   | Third Approach: New Noise Cancellation Topology In Common-  |    |

|    |        |         | gate LNAs                                                   | 96 |

|    |        | 4.3.4   | Limitation of the research                                  | 97 |

|    |        | 4.3.5   | Perspectives for future works                               | 97 |

| Bi | bliogi | raphy   |                                                             | 99 |

# LIST OF FIGURES

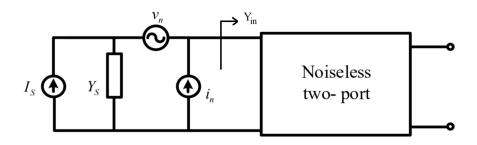

| 1    | Two-port noise model                                                            | 18 |

|------|---------------------------------------------------------------------------------|----|

| 1.1  | Common gate topology [4]                                                        | 26 |

| 1.2  | Cascaded common gate [4]                                                        |    |

| 1.3  | Common gate topologies                                                          |    |

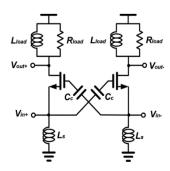

| 1.4  | Common gate with cross-coupled capacitors [6]                                   | 28 |

| 1.5  | Common gate with positive feedback between gate and drain [7]                   |    |

| 1.6  | Common gate with two feedbacks [8]                                              |    |

| 1.7  | Common gate with two differential feedbacks [8]                                 |    |

| 1.8  | Application of current-reuse with interference-rejection in common gate         |    |

|      | topology [9]                                                                    | 31 |

| 1.9  | Noise cancellation topology in common gate LNAs [11]                            | 31 |

| 1.10 | Schematic and small signal noise model of resistive feedback topology $$ . $$ . | 33 |

| 1.11 | Noise cancellation method in common source topology with resistive feed-        |    |

|      | back [4]                                                                        | 34 |

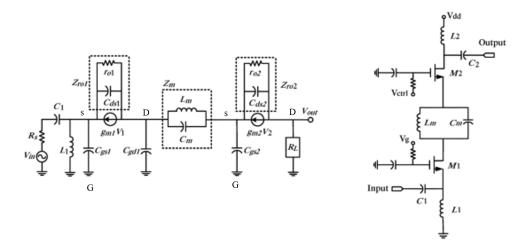

| 1.12 | Schematic and small signal noise model of IDCS stage                            | 35 |

| 1.13 | Cascaded IDCS stage [4]                                                         | 36 |

| 1.14 | Re-configurable multi-band LNA using a switch in gate $[15]$                    | 36 |

| 1.15 | Gate and source inductor coupling for performance improvement of IDCS           |    |

|      | stage [18]                                                                      | 38 |

| 1.16 | Current reuse in gate and source inductor coupling for performance im-          |    |

|      | provement of IDCS stage[18]                                                     | 36 |

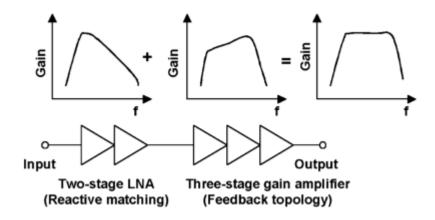

| 1.17 | Frequency behavior of different stages to achieve smooth gain in multistage     |    |

|      | amplifier with input IDCS stages [19]                                           | 39 |

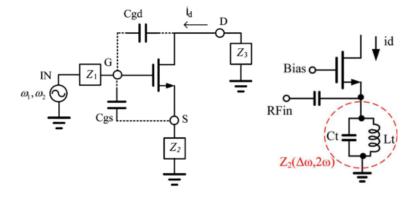

| 1.18 | Using feedback for linearization in LNAs [21]                                   | 41 |

| 1.19 | Common source and common-gate LNA with harmonic termination $[22]$              | 41 |

| 1.20 | linearization method by optimal biasing [23]                                    | 42 |

|      | Linearization method using an auxiliary path in amplifier [24]                  |    |

| 1.22 | Derivative Superposition technique to linearize amplifier [20]                  | 43 |

| 1.23 | Linearization technique using second order intermodulation injection [25].      | 44 |

#### LIST OF FIGURES

| 1.24 | Noise and distortion cancellation technique for LNA linearization [26]-[27].  | 45 |

|------|-------------------------------------------------------------------------------|----|

| 1.25 | Post-distortion linearization and implementation in a [28], b [29] and c [30] | 45 |

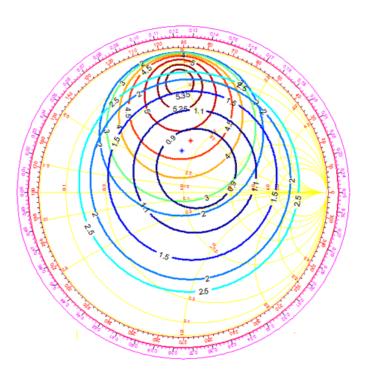

| 2.1  | Gain and NF contours for optimal conventional design                          | 50 |

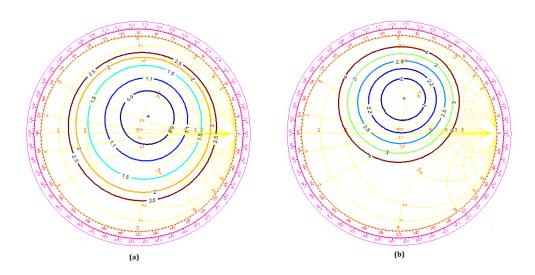

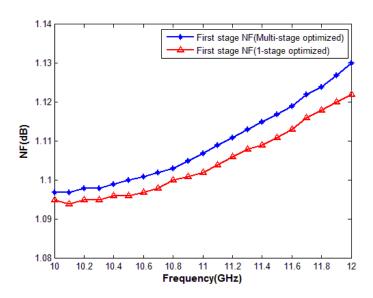

| 2.2  | (a) NF contours, (b) overall-NF contours                                      | 56 |

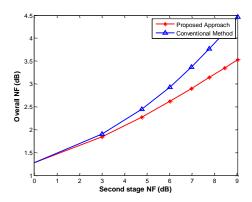

| 2.3  | Effect of second stage's NF in overall NF                                     | 56 |

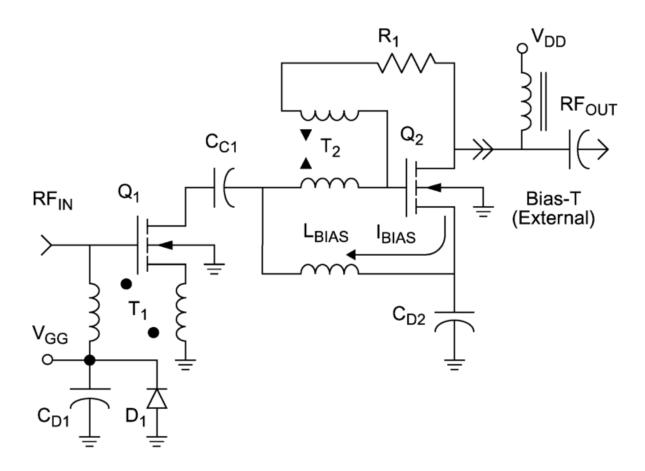

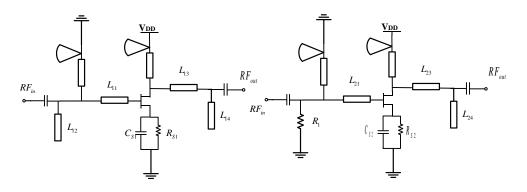

| 2.4  | Schematic of designed LNAs                                                    | 59 |

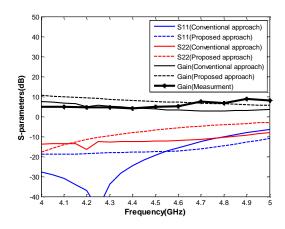

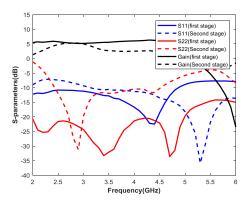

| 2.5  | S-parameter comparison of two LNAs                                            | 59 |

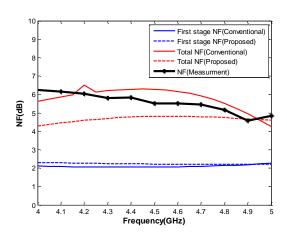

| 2.6  | Overall NF and first stage NF comparison of two LNAs                          | 60 |

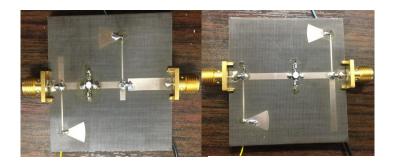

| 2.7  | PCB of designed LNAs: Proposed first stage and Second stage                   | 60 |

| 2.8  | Measurement S-parameters of each stage                                        | 60 |

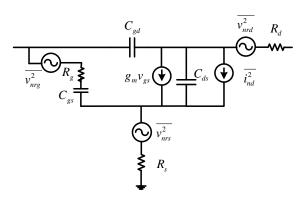

| 2.9  | Noise model of transistor                                                     | 63 |

| 2.10 | Small signal model of IDCS LNA                                                | 63 |

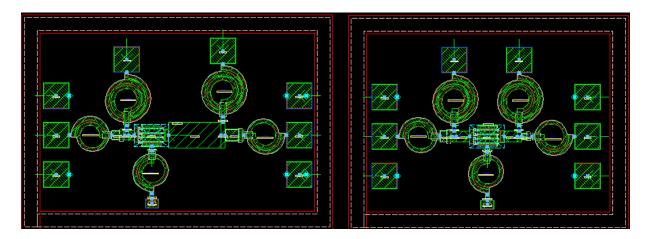

| 2.11 | Layout micrograph of (a) multi-stage optimized LNA (b) single-stage op-       |    |

|      | timized LNA                                                                   | 65 |

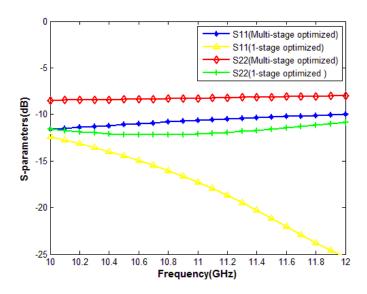

| 2.12 | S-parameter of LNAs                                                           | 66 |

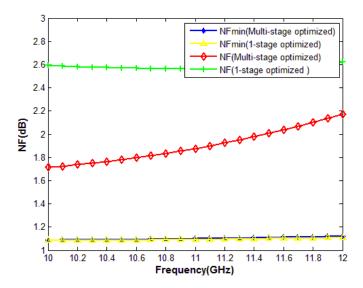

| 2.13 | NF of LNAs                                                                    | 67 |

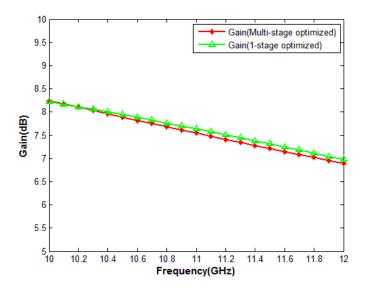

| 2.14 | Gain of LNAs                                                                  | 68 |

| 2.15 | First stage's NF of LNAs                                                      | 68 |

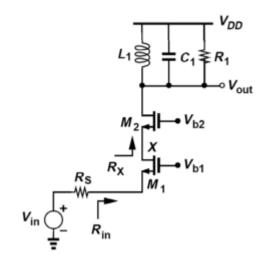

| 3.1  | Two-port noise model                                                          | 74 |

| 3.2  | GaAs-pHEMT transistor noise model                                             | 74 |

| 3.3  | Noise model of single path LNA                                                | 74 |

| 3.4  | Parallel amplifiers noise model                                               | 76 |

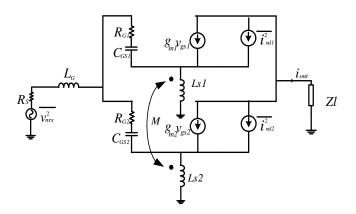

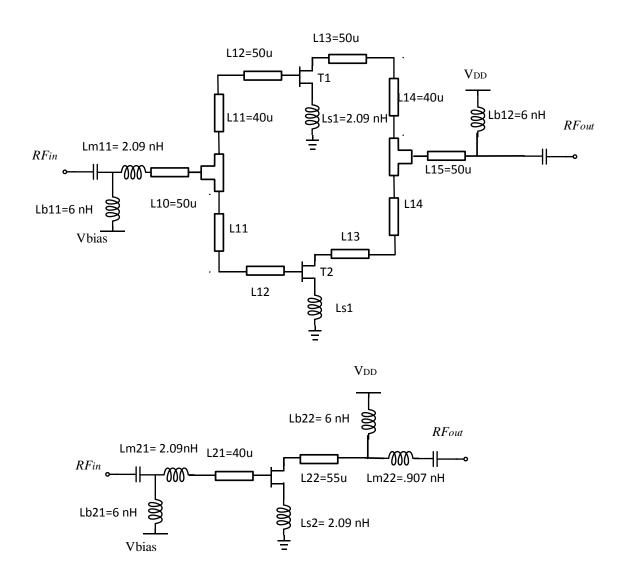

| 3.5  | Schematic of designed parallel and single path LNAs                           | 78 |

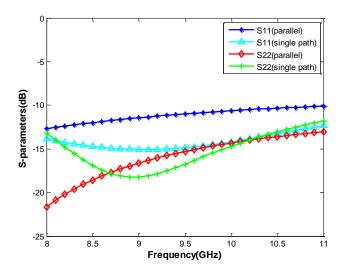

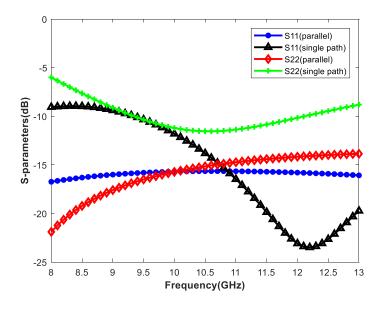

| 3.6  | S-parameter of both LNAs                                                      | 79 |

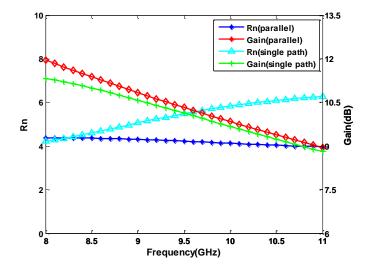

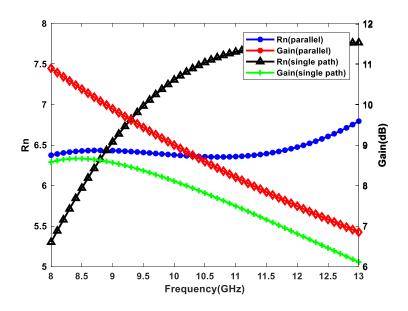

| 3.7  | $R_n$ and gain of both LNAs                                                   | 79 |

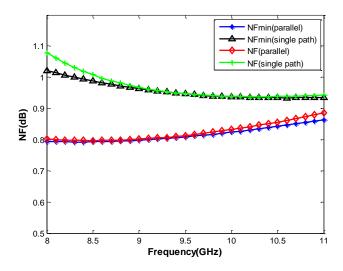

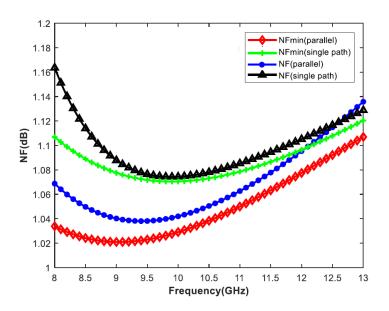

| 3.8  | NF and $NF_{min}$ of both LNAs                                                | 80 |

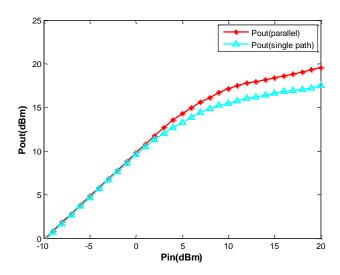

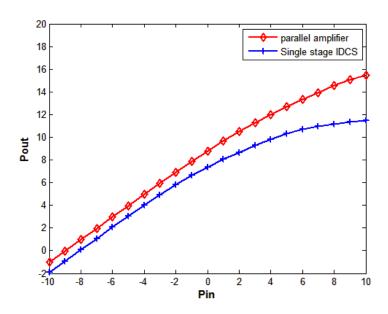

| 3.9  | Output power versus input power for both LNAs                                 | 80 |

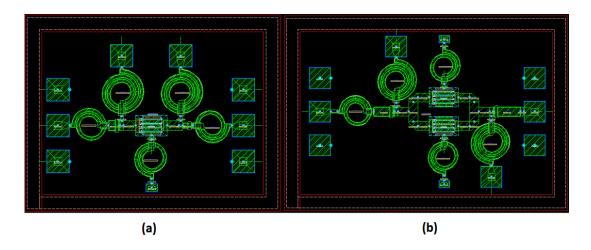

| 3.10 | Layout micrography of LNAs (a) Single stage LNA (b) Parallel LNA              | 82 |

| 3.11 | S-parameter of both LNAs                                                      | 82 |

| 3.12 | $R_n$ and gain of both LNAs                                                   | 83 |

| 3.13 | NF and $NF_{min}$ of both LNAs                                                | 83 |

| 3.14 | Output power versus input power for both LNAs                                 | 84 |

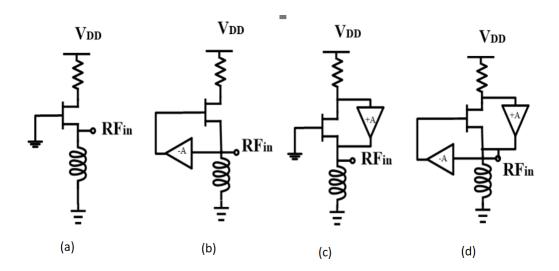

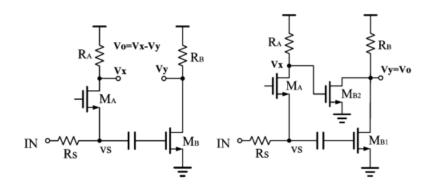

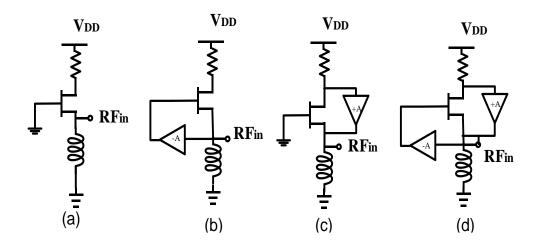

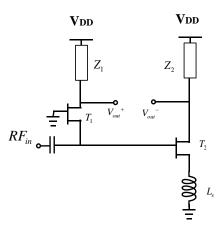

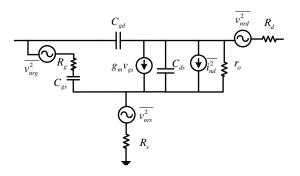

| 4.1 | Different common gate LNAs                                              | 86 |

|-----|-------------------------------------------------------------------------|----|

| 4.2 | Schematic of new noise cancellation technique                           | 88 |

| 4.3 | Noise model of transistor                                               | 88 |

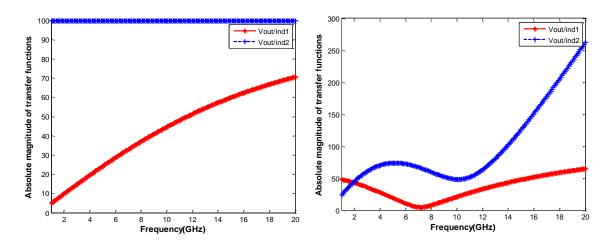

| 4.4 | Absolute magnitude of transfer functions: (a) Conventional method (b)   |    |

|     | Proposed method                                                         | 88 |

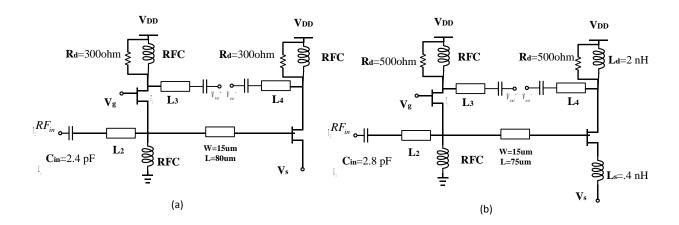

| 4.5 | Schematic of designed LNAs: (a) Conventional method (b) Proposed method | 90 |

| 4.6 | Layout micro-graph of designed LNAs: (a) Conventional method (b) Pro-   |    |

|     | posed method                                                            | 91 |

| 4.7 | NF and Gain of both LNAs                                                | 92 |

| 4.8 | S-parameters of both LNAs                                               | 92 |

# LIST OF TABLES

| 0.1 |                                                                       | F = |

|-----|-----------------------------------------------------------------------|-----|

| 2.1 | Change of $\Gamma_{opt}$ in Multistage LNAs                           | ) ( |

| 2.2 | Elements of designed LNAs                                             | 59  |

|     |                                                                       |     |

| 4.1 | Performance comparison of LNAs with similar design approach and band- |     |

|     | width                                                                 | 92  |

## RESUME

### In English

In this thesis three different approaches are presented in order to improve the performance of high frequency wide band LNAs. In the first approach, a new procedure for the design of multi stage LNAs with consideration of following stages noise is presented. This approach and its results has been previously published in [32]. In this approach, a new analytical solution for designing first stage of multi stage LNAs is presented. Conventional methodology for LNA design is to set source reflection coefficient of first stage equal to its  $\Gamma_{opt}$  to achieve minimum possible NF. At RF and microwave frequencies, because of transistor's gain roll-off, to achieve the desired gain, multi-stage LNA is often required. In these cases, the design procedure is much more complicated due to following stage's noise factor and the effect of first stage's gain on overall-NF. To find optimized value for first stage's source admittance to achieve minimum overall-NF, optimum source impedance of first stage should be obtained by consideration of its gain and NF as well as the effect of following stages' noise. In this thesis, the analytical calculations for obtaining the optimum source impedance of first stage to achieve simultaneously noise and impedance matching as well as best gain and overall NF performance in multi stage LNAs is presented. By using these equations, numerical solution for optimum design of first stage in multi-stage LNAs can be obtained. This method can be used for optimization of gain and NF simultaneously. The analytical solution shows consideration of overall LNA in optimization of gain and NF, leads to improvement of its performance.

To validate the theoretical results and check the feasibility of proposed method and also its comparison to the traditional approach, two different LNAs with conventional and proposed approach have been designed using ADS. These LNAs are two stages LNAs. To be consistent, the second stage remains the same and the first one is optimized through traditional approach and the proposed one respectively. This stage is chosen to present relatively high NF to emphasize the effect of the change in  $\Gamma_{opt}$  in multistage LNAs by considering the following stages' effect. The performance comparison is done according to momentum simulation in ADS and the results confirm the proposed method's perfor-

mance improvement in comparison to conventional design method. The designed LNA with proposed method shows lower NF and higher gain according to ADS momentum simulation in comparison to conventional method because it have better input impedance optimization. The LNA with better performance (proposed approach) is fabricated in order to confirm the validity of theoretical calculations. The results show the improvement in the performance of the proposed approach compared to conventional design method. It has been shown, despite slight increment in first stage's NF, the overall NF decreases due to higher first stage gain. Measurement results confirm the performance of designed LNA with proposed approach.

The second approach concerns about parallel amplifier usage for LNA design. The noise parameter is calculated and the procedure of achieving as low as possible NF with desirable input impedance matching, with high linearity LNA is described in this section. The analysis and design procedures of this part have been previously published in [33], [34]. Parallel amplifiers technique for achieving higher output power is a known method for power amplifier design, yet it has not been investigated as a practical topology for LNA design. Adding a parallel path demonstrates a number of virtues, including stability, higher output power, more tolerance to input signal power and better linearity, making it a reliable topology. Along with these advantages it also has drawbacks such as complexity of input power divider and output power combiner design. The loss of input divider increases the NF, and the loss of output power combiner decreases the gain of the LNA.

In this thesis, noise analysis results for parallel amplifier in general and in special case of two parallel IDCS in both coupled and uncoupled source inductors are represented. This analysis showed that the  $R_n$  decreases in parallel amplifier which can lead to better NF with the same input impedance matching condition. To confirm proposed theory, two LNAs (single path and parallel amplifiers) are designed in 0.1- $\mu$  GaAs pHEMT process in both schematic and layout simulation. The parallel LNA in schematic design have the average gain of 10.5 dB along 8 to 11 GHz. The impedance matching in input and output are better than -10 dB and -14 dB respectively. The single stage IDCS LNA shows an average gain of 10 dB from 8 to 13 GHz and also the impedance matching in both input and output are better than -12 dB. In layout design, the parallel LNA exhibits the gain of 11 dB at 8 GHz with 3-dB gain bandwidth of 8-11.5 GHz, with input and output impedance matching better than -14 dB. In layout design also single stage IDCS LNA shows a gain of 9 dB at 8 GHz with 3-dB gain bandwidth of 8-13 GHz, with input and

output impedance matching better than -10 and -7 dB respectively. Output saturation power in both schematic and layout design improves 3dB because of parallel path, therefore this topology is considered as linear LNA. In this method input matching circuit design is simplified because of decrement in  $R_n$ . Simulation results show with no considerable change in  $NF_{min}$  and similar input matching condition  $(S_{11} < -10dB)$ , that NF in parallel topology is less than single path amplifier. As a result, even though the input divider and output combiner have losses and increase the NF slightly, the effect of  $R_n$  decrement makes overall NF to be lowered in parallel amplifier.

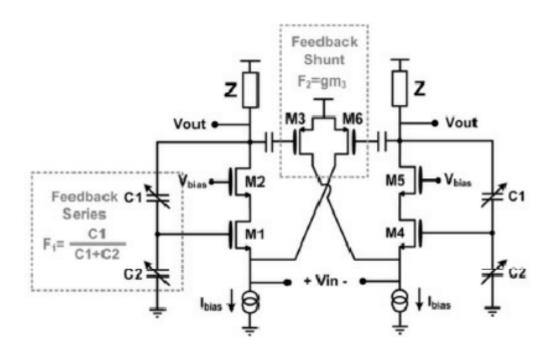

The third design method presents a new approach in designing noise canceling common gate LNAs. In this part the condition of noise canceling are calculated and a design procedure is given to obtain low-NF, high gain, with appropriate impedance matching in common gate noise-canceling LNAs. The analytical design procedure and its results are also published in [35].

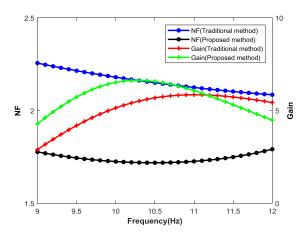

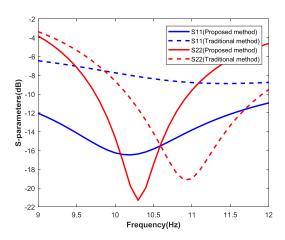

In this thesis, design procedure of new noise cancellation technique by using an IDCS stage instead of CS stage, is discussed. In spite of the conventional method which uses CS stage to cancel out the noise of CG, IDCS parallel with CG stage is used. The analytical calculation for achieving noise cancellation condition is calculated and MATLAB simulation is used to show the reduction of noise in proposed method in comparison to conventional one. To validate the theoretical analysis, two different LNAs with conventional method and proposed one are designed and compared using ADS with technology file of GaAs pHEMT 0.1  $\mu m$ . The EM simulation results have shown that in proposed method the NF is decreased and better input impedance matching is obtained. It also shows that the NF decreases in the proposed approach and the gain is slightly improved. The  $S_{11}$  of the proposed method is better than -12 dB while in conventional method, it is no more better than -8 dB. The output matching in both topologies have a narrow band behavior and at the center frequency the  $S_{22}$  of both LNAs are better than -10 dB.

### En Français

Dans cette thèse, trois approches différentes sont présentées afin d'améliorer les performances des LNA hautes fréquences à large bande. Dans la première approche, une nouvelle procédure pour la conception de LNA à plusieurs étages en tenant compte des propriétés en bruit des étages suivants est présentée. La procédure de design ainsi que les principaux résultats obtenus ont été publiés dans [32]. Dans cette approche, une nouvelle solution

analytique pour la conception du premier étage des LNA à plusieurs étages est présentée. La méthodologie typiquement suivie pour la conception de tels amplificateurs consiste à imposer l'adaptation à l'entrée du premier étage sur son  $\Gamma_{opt}$  afin de garantir la NF de ce premier étage la plus faible possible (i.e.  $NF_{min}$ ). Aux fréquences RF et micro-ondes, en raison du compromis entre la maximisation du gain et de la minimisation de la figure de bruit, pour obtenir un gain répondant aux spécifications systèmes, il est souvent nécessaire de concevoir un LNA à plusieurs étages. Dans ce cas, la procédure de conception est beaucoup plus compliquée puisque le facteur de bruit global est aussi conditionné par le ratio entre le facteur de bruit de l'étage suivant et le gain du premier étage. L'admittance ramenée à la source du premier étage doit alors être optimisée pour présenter une figure de bruit minimum. Pour cela, il est impératif de prendre en considération non seulement le gain et le facteur de bruit du premier étage mais aussi le facteur de bruit des étages suivants.

Dans cette thèse, les calculs analytiques permettant de déterminer l'impédance de source optimale du premier étage afin de garantir simultanément le compromis entre adaptation en entrée, gain et figure de bruit globale dans les LNA à plusieurs étages sont présentés. En utilisant ces équations, une solution numérique pour une conception optimale du premier étage d'un LNA à plusieurs étages peut être obtenue. La solution analytique montre que la prise en compte de tous les étages du LNA pour l'optimisation globale du gain et de la figure de bruit, conduit à une amélioration globale de ses performances.

Pour valider les résultats théoriques et vérifier la pertinence de la méthode proposée comparativement à la méthode traditionnelle, deux amplificateurs LNA ont été conçus et optimisés à l'aide du logiciel ADS. Ces LNA sont constitués de deux étages dont le second est laissé identique dans les deux cas. Afin de mettre en évidence l'intérêt de cette méthode d'optimisation, le second étage est choisi pour présenter une figure de bruit relativement élevée tandis que le premier étage est optimisé dans un premier temps suivant la méthode traditionnelle puis celle proposée. La comparaison des performances est réalisée en nous appuyant sur des simulations électromagnétique 2,5D en utilisant le logiciel Momentum de la suite ADS. Les résultats obtenus confirment l'amélioration des performances globales obtenues par la méthode proposée. Ainsi, le LNA conçu avec cette nouvelle approche présente une figure de bruit plus faible conjointement avec un gain plus élevé (comparativement à celui conçu avec la méthode conventionnelle). Il présente, de plus, une meilleure adaptation en son entrée. Le LNA présentant les meilleures performances (méthode proposée) est fabriqué afin de valider pratiquement les calculs théoriques. Les

résultats montrent l'amélioration des performances de l'approche proposée par rapport à la méthode de conception conventionnelle. Malgré une légère augmentation du facteur de bruit du premier étage, le gain de ce dernier augmente. L'effet de masquage du facteur de bruit du second étage par ce gain est alors plus important et entraîne une amélioration globale du facteur bruit de l'ensemble.

La deuxième approche concerne l'utilisation d'amplificateurs parallèles pour la conception de LNA. Dans cette section, après avoir calculé le paramètre de bruit, la procédure de conception afin d'obtenir conjointement le plus faible facteur de bruit, la meilleure adaptation d'impédance en entrée ainsi que l'amélioration de la linéarité du LNA est décrite. Ces procédures d'analyse et de conception ont fait l'objet de publications [33] et [34]. L'utilisation d'une architecture parallèle pour augmenter la puissance de sortie disponible en sortie est une méthode connue pour la conception d'amplificateurs de puissance. Cependant son potentiel n'a pas, à l'heure actuelle, été exploité dans la conception d'amplificateurs faible bruit. L'ajout d'un chemin parallèle démontre un certain nombre de vertus, comme notamment une meilleure stabilité, une puissance de sortie plus élevée, une plus grande tolérance à la puissance du signal d'entrée et une meilleure linéarité. Outre ces avantages, il présente également des inconvénients tels que la complexité de conception du diviseur d'entrée et du sommateur de sortie. Les pertes du diviseur d'entrée augmentent le facteur de bruit, et les pertes du combineur de sortie diminuent ou en tout cas affectent le gain du LNA. Dans cette thèse, les résultats d'analyse du bruit pour l'amplificateur parallèle en général et dans le cas particulier de deux IDCS (Inductively degenerated common source) parallèles dans le cas où les inductances de source sont couplées puis non couplées sont représentés. L'analyse a montré que la résistance équivalente de bruit  $R_n$  diminue pour l'amplificateur parallèle, ce qui peut conduire à une meilleure figure de bruit dans les mêmes conditions d'adaptation d'impédance d'entrée. Pour confirmer les théories proposées, deux LNA (amplificateurs à voie unique et amplificateurs parallèles) sont conçus en utilisant le design kit de la technologie pHEMT  $0,1-\mu m$  GaAs dans la simulation circuit (1D) et pour la simulation électromagnétique 2,5D.

Pour la simulation circuit, la structure LNA parallèle présente un gain moyen de 10,5dB entre 8 et 11GHz. L'adaptation en entrée et en sortie est, quant à elle, meilleure que -10dB et -14dB sur 8 et 11 GHz. Comparativement, la structure à un transistor (IDCS LNA) présente un gain moyen de 10dB sur la bande de 8 à 13GHz et une adaptation d'impédance en entrée et en sortie sur cette bande meilleure que -12dB. En ce qui concerne la simulation électromagnétique, le LNA à architecture parallèle présente un gain maximum de

11dB à 8GHz pour une bande passante à 3dB en gain couvrant 8 à 11,5GHz pour une adaptation d'impédance en entrée et en sortie meilleure que -14dB. L'amplificateur IDCS LNA, quant à lui, ne présente qu'un gain de 9dB à 8GHz pour une bande passante à 3dB en gain couvrant 8 à 13GHz. L'adaptation d'impédance en entrée et en sortie, dans ce cas, n'est alors que de -10 et -7dB respectivement.

Quel que soit le simulateur, une amélioration de l'ordre de 3dB est obtenue sur la puissance de saturation en faveur de la structure parallèle améliorant ainsi la linéarité du circuit. Dans cette méthode, la conception du circuit d'adaptation d'entrée est simplifiée en raison de la diminution de  $R_n$ . Les résultats de la simulation montrent que, sans changement considérable sur la  $NF_{min}$  et pour des conditions d'adaptation d'entrée similaires  $(S_{11} < -10dB)$ , la figure de bruit présentée par la topologie parallèle est inférieure à celle présentée par l'amplificateur seul. En conséquence, même si le diviseur d'entrée et l'additionneur de sortie des pertes qui pénalisent légèrement la NF, l'effet de la diminution de  $R_n$  permet une diminution globale de la figure de bruit de la structure globale.

La troisième méthode de conception présente une nouvelle approche dans la conception de LNA à grille commune. Dans cette partie, les conditions de suppression de bruit sont calculées et la procédure de conception a permis de concevoir un amplificateur ayant un faible NF, un gain élevé, une adaptation d'impédance à l'état de l'art pour ce type de structure. La procédure de conception analytique et ses résultats ont également été publiés dans [35].

Dans cette thèse, la procédure de conception d'une nouvelle technique d'annulation du bruit en utilisant un étage IDCS au lieu d'un étage CS (Common Source) est discutée. La condition d'annulation du bruit est calculée analytiquement et une simulation MAT-LAB est utilisée pour démontrer la réduction effective du bruit par la méthode proposée par rapport à la méthode conventionnelle. Afin de valider l'analyse théorique, deux LNA différents avec la méthode conventionnelle et celle proposée sont conçus et comparés en utilisant ADS avec le design Kit de la technologie GaAs pHEMT  $0.1~\mu m$ . Les résultats de la simulation EM ont montré que pour la méthode proposée, la NF est diminuée et une meilleure adaptation d'impédance d'entrée est obtenue. Le gain quant à lui augmente légèrement. Le coefficient de réflexion est ainsi meilleur que -12dB dans la bande passante alors qu'il n'est que de -8dB pour la méthode conventionnelle. L'adaptation d'impédance en sortie dans les deux topologies a un comportement à bande étroite et à la fréquence centrale, coefficient de réflexion de sortie S22 des deux LNA conçus restent inférieurs à -10dB.

## INTRODUCTION

The rapid extension of wireless networks in diverse areas increased the demand of efficient receivers with high reliability and minimum sensibility. Amplifiers are one of the key blocks in receivers whose characteristics greatly affect the overall specification of a receiver. Due to the low power level of the received signal and also the loss of first passive circuits, it is necessary to amplify the received signal as soon as possible without introducing extra noise: this is the main objective of low noise amplifiers (LNA). To maintain the signal integrity, the added noise should be as low as possible. Thus, the main characteristics of any LNA are its gain and noise figure (NF). In most receiver architectures, LNA is the first block, so it contributes most of the NF of a receiver. The most important parameters of an LNA, considering its application and required specification are its: NF, gain, bandwidth, power consumption, input and output return losses, Linearity and area on the chip. It is necessary to trade off between these parameters based on the application intended for the LNA.

#### Crucial Parameters on an LNA

### Noise figure

Noise factor (F) in low-noise amplifiers is a factor that indicates the signal-to-noise ratio of the amplifier at the input to the output. Using this factor, the noise performance can be examined. [1]

$$F = \frac{SNR_{in}}{SNR_{out}} = \frac{S_{in}/N_{in}}{S_{out}/N_{out}} = \frac{S_{in}/N_{in}}{GS_{in}/G(N_{in} + N_{added})} = 1 + \frac{N_{added}}{N_{in}}$$

(1)

Most of time this noise Factor (F) is expressed in dB and is then called Noise Figure (NF). Sometimes these two definition are mistaken and Noise Figure is used inspite of Noise Factor. Nevertheless, this is commonly accepted as their definition are very close  $(NF = 10 \log_{10} F)$ .

There exists a minimum NF for each amplifier that can be achievable while the source

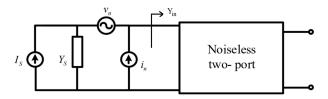

impedance of the LNA is equal to its optimum noise impedance. Assuming LNA as a two-port network, it can be shown that any of its noise sources can be transferred back at its input and represented by two main noise sources (Fig 1). According to this model  $v_n$  is then an equivalent input voltage noise source and  $i_n$  is equivalent input current noise source.

Figure 1 – Two-port noise model

Assuming that the amplifier is fed by a current source modeled through an ideal current source associated with its equivalent output impedance  $Y_s = G_s + jB_s$ , the input current of the noiseless amplifier can be calculated by the use of Eq (2).

$$i_{i} = I_{s} \frac{Y_{in}}{Y_{in} + Y_{s}} + i_{n} \frac{Y_{in}}{Y_{in} + Y_{s}} + v_{n} \frac{Y_{in}}{Y_{in} + Y_{s}} Y_{s}$$

$$(2)$$

The noise factor of the two-port can simply be calculated by use of Eq (3).

$$F = \frac{\overline{i_i^2}}{\left. \frac{\overline{i_i^2}}{i_i} \right|_{i_n = 0, v_n = 0}} = 1 + \frac{\overline{(i_n + Y_s v_n)^2}}{\left. i_s^2 \right.}$$

(3)

Since the two noise sources of  $v_n$  and  $i_n$  are not uncorrelated, it has been assumed that  $i_n$  consists of two parts:  $i_c$  which is correlated to  $v_n$  by factor of correlation admittance of  $Y_c$  ( $i_c = Y_c v_n$ ) and  $i_u$  which is the uncorrelated part. By considering  $\overline{v_u^2} = 4kTR_n\Delta f$  and  $\overline{i_u^2} = 4kTG_u\Delta f$ , where k is the Boltzmann constant and T is the temperature and  $R_n$  is noise equivalent resistance  $(1/G_n)$  and  $G_u$  is equivalent uncorrelated noise conductance

and  $\Delta f$  is the frequency range, Eq (3) can be written in form of Eq (4).

$$F = 1 + \frac{G_n}{G_s} + \frac{R_n}{G_s} |Y_c + Y_s|^2 = F_{min} + \frac{R_n}{G_s} |Y_s + Y_c|^2$$

(4)

By derivation of F with respect to source admittance, the optimum admittance in which the minimum achievable F can be obtained.

$$B_{opt} = -B_c, G_{opt} = \sqrt{\frac{G_u}{R_n} + G_c^2} \tag{5}$$

In this situation the minimum F would be [2]:

$$F_{min} = 1 + 2R_n \left( Y_{opt} + Y_c \right) = 1 + 2G_c R_n + 2\sqrt{R_n G_u + \left( R_n G_c \right)^2}$$

(6)

Therefore, the noise factor of a two port can also be represented in form of Eq (7) by use of reflection coefficients.

$$F = F_{\min} + \frac{4R_n Y_0 |\Gamma_{opt} - \Gamma_s|^2}{(1 - |\Gamma_s|^2)|1 + \Gamma_{opt}|^2}$$

(7)

By use of Eq (7), noise constant circles in smith chart can be shown in form of Eq (8).

$$\left|\Gamma_s - \frac{\Gamma_{opt}}{N+1}\right| = \frac{\sqrt{N(N+1 - \left|\Gamma_{opt}\right|^2)}}{N+1}$$

(8)

while  $N = \frac{F - F_{\min}}{4R_n Y_0} |1 + \Gamma_{opt}|^2$ . Concluding these equations, in an amplifier with specific noise parameters to achieve the desired noise factor, the source admittance should be optimized by use of constant noise circles in the smith-chart. However, the noise factor is not the only parameter to be achieved, some specifications could deal with gain or input impedance impedance matching. So one but not least challenge in LNA design is to find a specific point which realize the trade-off between all the specifications.

#### Gain

LNA's gain is one of its most important characteristic. Achieving the highest possible gain without considerable changes in the frequency band is necessary in design optimization. Considering an amplifier as a two-port, its gain can be calculated through its reflection coefficient. Maximizing the gain of amplifier requires impedance matching in

the input and output and in case of multi-stage circuits, the impedance matching of interstages. The transfer gain of the amplifier can be calculated from Eq (9). In this regard,  $P_{avs}$  is the maximum available power from the source. It should be noted this can be achieved in case of input impedance matching.  $P_L$ , is the power reached to the load.

$$G_{T} = \frac{P_{L}}{P_{avs}} = \frac{P_{L}}{P_{in}|_{\Gamma_{s} = \Gamma_{in}^{*}}} = \frac{\frac{|V_{S}|^{2}}{8Z_{0}} \frac{|S_{21}|^{2} (1 - |\Gamma_{L}|^{2})|1 - \Gamma_{s}|^{2}}{|1 - S_{22}\Gamma_{L}|^{2} |1 - \Gamma_{in}\Gamma_{s}|^{2}}}{\frac{|V_{S}|^{2}}{8Z_{0}} \frac{|1 - \Gamma_{s}|^{2}}{1 - |\Gamma_{s}|^{2}}} = \frac{|S_{21}|^{2} (1 - |\Gamma_{S}|^{2})(1 - |\Gamma_{L}|^{2})}{|1 - \Gamma_{S}\Gamma_{in}|^{2} |1 - S_{22}\Gamma_{L}|^{2}}$$

(9)

In single-stage amplifiers, the noise optimum source admittance does not necessarily satisfy the input impedance matching condition. Therefore, it is not possible to achieve the maximum gain and minimum NF at the same time. Considering this, it is necessary to trade-off between the gain and NF of the amplifier. In multi-stage LNAs this trade-off is more challenging because in this case, not only the first stage need to have very low NF, but also due to the effect of first stage's gain on the overall NF, it has to have highest achievable gain.

In order to achieve the minimum NF and maximum gain, the LNA can be designed in a way that, the source impedance has to be equal to the optimal noise impedance  $(Y_s = Y_{sopt})$  and on the other hand, the matching condition of input impedance is satisfied when  $Y_s = Y_{in}^*$ . In this case, by use of simultaneous noise and impedance matching, the optimal design can be obtained  $(Y_{sopt} = Y_{in}^*)$ .

### Stability

By considering an amplifier as a two-port network, it is known that it is stable when the power of reflected signal is smaller than the incident signal in the input and output of the amplifier. Therefore when the amplifier is unilateral, it is unconditionally stable. In this case, with any magnitude in source and load impedance the circuit is stable. The scattering matrix of device can be also used to evaluate its stability. These conditions are  $|S_{11}| < 1$  and  $|S_{22}| < 1$  which is almost the case for unilateral amplifier..

When the transistor is not unilateral, for evaluating the stability while the circuit is connected to any other magnitude of impedance in input and output by using its sparameters the conditions of  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  should be met. It can be represented as Eq (10).

$$|\Gamma_{in}| = \left| S_{11} + \frac{S_{21}S_{12}\Gamma_L}{1 - S_{22}\Gamma_L} \right| = 1 \tag{10}$$

Using Eq (10), the circle of stability in smith chart can be found. Its radius and center is represented in Eq (11).

$$r_L = \left| \frac{S_{21} S_{12}}{\left| S_{22} \right|^2 - \left| \Delta \right|^2} \right|, c_L = \left| \frac{\left( S_{22} - \Delta S_{11}^* \right)^*}{\left| S_{22} \right|^2 - \left| \Delta \right|^2} \right|$$

(11)

where  $\Delta = S_{11}S_{22} - S_{21}S_{12}$ , the stability condition can be easily estimated using the K stability factor and delta.

$$K = \frac{1 + |S_{11}S_{22} - S_{12}S_{21}|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{12}||S_{21}|} > 1, \ |\Delta| = |S_{11}S_{22} - S_{12}S_{21}| < 1$$

(12)

While this test can evaluate the stability of a circuit, it can not represent the level of instability and it does not provide a way to compare the level of instability between two different circuits. Therefore, there is another test named  $\mu$  test which can not only represents the stability but also specifies how stable or unstable a circuit is. This factor is represented in Eq (13).

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11}^* \Delta| + |S_{12} S_{21}|} \tag{13}$$

In multi-stage circuits, the  $\mu$  test is not sufficient for evaluation of stability of the circuit. It is also needed to analyze each stage separately to be sure that there is no oscillation in the circuit.

### Input and output impedance matching

One of the most important issues in LNA design is its impedance matching, which is done in order to transfer the signal properly by minimizing the reflected signal. Impedance matching at inputs and outputs are necessary because while connecting circuits, it is important that the output impedance of the first circuit and the input impedance of the second one, are matched so that they can transfer the maximum power between each other or from the first to the second one.

Impedance matching is typically done by passive elements of matching circuits. As the frequency response of transistors are mostly low-pass, to reach a flat gain over a specified bandwidth high-pass matching circuits with minimum losses with wide-band frequency response can help us to achieve the desired results.

The design of matching circuits is one of the most important issues in optimization of the

LNA specially for broadband amplifiers.

#### Linearity

One of the specifications of any amplifier is its linearity. The linearity of the amplifier determines the range of input signal power in which the amplifier can amplify without distortion. One of the factors that determines an linearity of the amplifier is its 1 dB compression point (P-1dB). This point is actually a power indicator at which the gain of the amplifier deviates and decreases by 1 dB from the gain of the ideal linear region. In multi-stage amplifiers, the linearity of the amplifier is mostly dependent to the linearity of final stages because saturation of these stages occurs in lower power since the signal power is larger in the final stages.

Another factor for evaluating the linearity of a circuit is the third-order intercept point (IP3). It is based on the idea that the device non-linearity can be modeled using a low-order polynomial, derived by means of Taylor series expansion. IP-3 relates nonlinear products caused by the third harmonic non-linear term to the first harmonic signal. The intercept point is a purely mathematical concept and does not correspond to a practically occurring physical power level. In many cases, it lies far beyond the damage threshold of the device. IP-3 can be obtained by finding the intercept point of the output power versus the input power for first and third harmonic both on logarithmic scales. This point can be a representative for the non-linearity of the amplifier.

#### Overview

The above mentioned factors are some of the most important specifications in design of an LNA. In different approaches and topologies for LNA design optimization method, it is essential to meet all required conditions with consideration of all trade-offs in the design. This thesis concerns about analytical approaches for wide-band high frequency LNA design methods and consists of three main ideas.

In the first section, a new optimization method based on analytical calculation for multi stage LNAs is presented. While numerical optimization methods for multi stage LNAs based on design of each stage as individual block have been previously developed [37]- [41], the effect of following stage's noise has not been investigated previously. In this thesis, new design procedure in multi-stage LNAs is investigated. In spite of conventional method which emphasizes of first stage regardless to gain reduction from maximum available gain, this approach optimizes gain and NF simultaneously considering the effect of following stage's noise. Analytical calculation, for optimum multi-stage LNA design, show that the optimum noise impedance at the input of the first stage can differ. Using this new optimum input impedance can then lead to decrease the overall NF.

In the second section, parallel amplifier technique in LNA design is presented. Noise parameter have been calculated in order to achieve the best performance of this topology. The results show that the performance of the LNA can be improved and it can achieve higher gain, better input impedance matching, better linearity and robustness without any degradation in NF.

In the third section, a new noise cancellation topology in common-gate LNAs are presented. In this section, instead of common source stage for noise canceling stage, inductively degenerated common source stage is utilized which can lead to better simultaneously noise and impedance matching. The noise parameter calculations represent the required condition for noise cancellation. The obtained results show that using this approach, better NF, gain and input impedance matching can be obtained.

## LITERATURE REVIEW

#### 1.1 Introduction

The design of low noise amplifier is always associated with many challenges such as achieving to simultaneous optimum NF with desirable input impedance matching or optimal linearity with low power consumption while small area on chip is occupied in integrated circuits. In previous studies, different topologies as well as various design methods have been investigated in order to achieve appropriate gain and NF, or to have optimal input and output impedance matching, or to increase the linearity as well as reduction of the power consumption and LNA's occupied are on the chip. In these studies, the frequency band and bandwidth of the amplifier are a very important design factor. In microwave amplifiers, due to losses in transmission lines, and unavoidable reflections as well as transistor's gain roll-off, it is needed to focus more on topologies with the lowest possible NF [4]. In this chapter, two main topologies including common gate and common source LNAs will be examined. The approaches that have been proposed in these LNAs in order to improve their gain, NF, or impedance matching performance will be discussed with more details. The approaches for linearity improvement of LNAs are also investigated in this chapter.

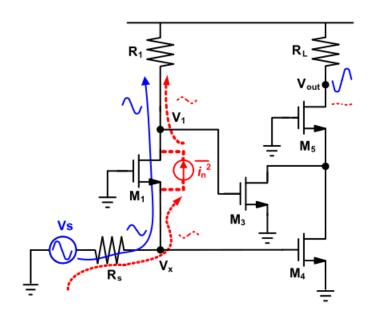

### 1.2 Common Gate Topology

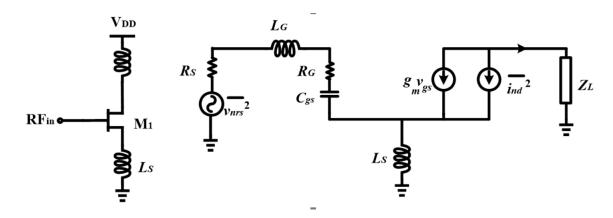

The common gate topology is considered as a broadband topology with a relatively low NF. Even though the input impedance matching condition is satisfied, the NF obtained remains much higher compared to the common source topology. This topology is mostly used because of its wideband behavior. The common gate topology is shown in Fig.1.1. In this circuit, the NF can be obtained by (1.1) [4], where  $\gamma$  is a parameter for the thermal noise of the channel.  $(\overline{i_{nd}^2} = 4kT\gamma g_m)$ .

Figure 1.1 – Common gate topology [4]

Figure 1.2 – Cascaded common gate [4]

$$NF = 1 + \frac{\gamma}{g_m R_s} + \frac{R_s}{R_1} (1 + g_m R_s)^2 \tag{1.1}$$

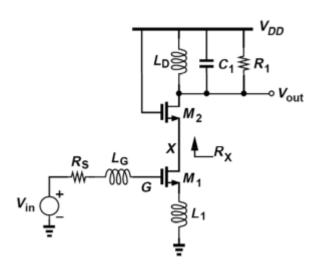

When the input impedance adaptation condition  $g_m = 1/R_s$  is met, the NF is then  $1+\gamma+\frac{4R_s}{R_1}$ . Depending on the technology, this NF can be greater than 2 or 3, which is pretty much higher than the NF of the common source topology with the inductive degeneration with similar impedance matching conditions. Another problem of the common gate circuit is its dependence on the input impedance to the load resistor, which can be reduced by usage of cascaded common gate as represented in Fig.1.2. [4]. In this method, the input resistor is isolated from the load resistor. The noise from transistor M2 can increase the NF, which can become considerable at higher frequencies (the frequency at which node X is

Figure 1.3 – Common gate topologies

AC-grounded). The common gate topology faces a major challenge of trading-off between its NF and the matching of the input impedance. Number of solutions to overcome this challenge have been previously proposed [5]-[9]. These methods are based on adding one or more feedback paths. Figure (1.3) shows different types of common gate topologies. Figure (1.3-a) shows a simple common gate circuit whose main problem is high NF while its input impedance is fully matched. Using this method, by effectively increasing the  $g_m$  of the transistor, the effect of channel noise at the output decreases and the input impedance matching conditions, the effect of noise is improved by a factor of  $1 + A_{neg}$  (where  $A_{neg}$  is the gain of the negative feedback path). One of the practical methods of this topology is the use of cross-coupled capacitors [6]. In this case, in addition to reducing the NF with an effective increase in  $g_m$ , the linearity is also improved by reducing the second-order distortion. The schematic of this topology is shown in Fig 1.4.

In this case, the coefficient of  $A_{neg}$  will always be less than 1, so the input impedance is obtained from  $Z_{in} = 1/(g_m(1 + A_{neg}))$  and the NF in the input impedance matching condition would be  $1 + \frac{\gamma}{2} + \frac{4R_s}{R_1}$ .

As we can see the NF is decreased using this approach compared to the previous method. Another topology is shown in Fig. (1.3-c). This approach investigated the use of a positive feedback between drain and source [7]. In this method, as shown in Fig.1.5. stability of the amplifier must be carefully considered because by use of positive feedback path, instability

Figure 1.4 – Common gate with cross-coupled capacitors [6]

can occur.

According to this case the input impedance matching is calculated by  $Z_{in} = 1/(g_m(1 - A_{pos}))$  and the NF can be obtained by Eq. (1.2)

$$NF = 1 + \frac{\gamma}{g_m R_s} + \gamma g_{m2} R_s + \frac{(1 + g_m R_s)^2}{g_m^2 R_s R_1}$$

(1.2)

In this method in case of input impedance matching  $(R_s = Z_{in}^*)$  the NF can be obtained by Eq (1.3) which is less than common gate topology (Eq (1.1)).

$$NF = 1 + \frac{\gamma}{2} + \gamma g_{m2} R_s + \frac{4R_s}{9R_1}.$$

(1.3)

Another way to improve NF in common gate topology is to use these two positive and negative feedbacks simultaneously, as shown in Figure (1.3-d). In this case, the input impedance will be  $Z_{in} = 1/(g_m(1 + A_{neg})(1 - A_{pos}))$  and in the matching conditions, with  $A_{neg} = 1$  and  $A_{pos} = 0.5$  the NF can be calculated as:

$$NF = 1 + \frac{\gamma}{4} + \gamma g_{m2} R_s + \frac{4R_s}{9R_1} \tag{1.4}$$

It can be seen that by adding any of the feedback paths, the input matching conditions as well as the NF can be improved [5]. In another circuit shown in the Fig. 1.6, the simultaneous use of two feed-backs has improved the NF of common gate. In this method, the  $G_m$  feedback path in fig.1.6 increases the transmittance while maintaining the broadband behavior of the input impedance matching [8]. In this circuit, the NF decreases with effective increase of  $g_m$  while the input matching is fully matched. The simulation results represent that the effect of feedback path noise on the NF is negligible and this topology can decrease the overall NF. This method is used to design a low NF common gate dif-

Figure 1.5 – Common gate with positive feedback between gate and drain [7]

Figure 1.6 – Common gate with two feedbacks [8]

Figure 1.7 – Common gate with two differential feedbacks [8]

ferential LNA. Fig 1.7. represents the schematic design of this kind of circuit. The main issue will still be the conflict between the input impedance matching and the NF, this means that unlike inductively degenerated common source topology which can achieve simultaneous noise and impedance matching, these conditions cannot be met in commongate topology at the same time. In two-stage LNAs with a common gate topology, the method of current-reusing can also be used to reduce power consumption. One sample of these method is shown in Fig.1.8. As it can be seen the two stages are connected using an LC matching circuit [9]. In this circuit, to eliminate interference, the matching circuits at the input and output are also used as filters to pass just the desired frequency so this method is narrow band method.

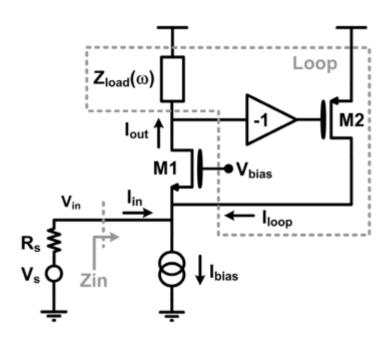

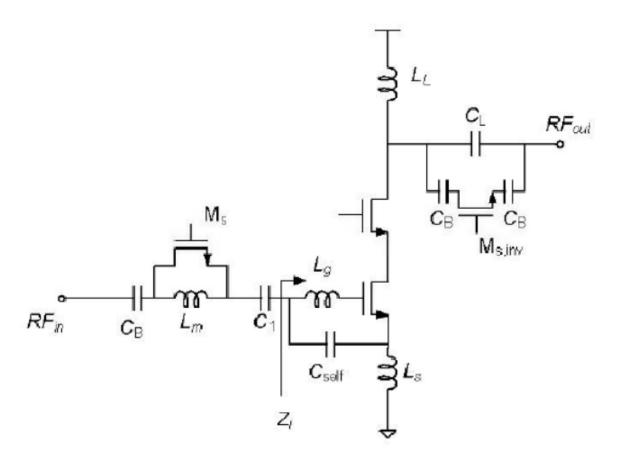

In similar works, the same topology of common gate with current reuse has been used for reducing power consumption in order to achieve gain and have input impedance matching in InP-HEMT technology in a wide frequency range from 68 to 110 GHz [10]. Noise cancellation method is another approach which is performed in common gate LNAs in order to improve the NF. In this topology a common source stage [11] as shown in Fig.1.9. is paralleled with common gate stage to cancel its channel's noise. The noise of common gate in the output would be equal to  $\overline{V_{nout,M1}^2} = 4kT\gamma g_m \Delta f(\frac{R_1}{R_s}g_{m3} - g_{m4})^2 (R_s \parallel \frac{1}{g_m})^2$

Figure 1.8 – Application of current-reuse with interference-rejection in common gate topology [9]

Figure 1.9 – Noise cancellation topology in common gate LNAs [11]

and by appropriate selection of circuit coefficients such as  $g_{m3}$  and  $g_{m4}$ , it can be canceled out.

In the common gate topology, feedback paths are added to increase the degree of freedom to select the  $g_m$  of transistor so that the input impedance matching condition and minimum NF can be met simultaneously. This topology has been widely used in broadband low noise amplifiers. Another topology that has been known in LNA design is the common source topology, which will be examined in the next section.

## 1.3 Common Source Topology

The common source topology is considered as a known topology in the design of low noise amplifiers. This topology is widely used in two different modes to be able to meet input impedance matching condition including: resistive feedback between gate and drain, and with inductive degeneration. In the case of resistive feedback, the noise behavior is degraded due to resistor noise. On the other hand, the amplifier exhibits a better linearity and wider frequency band. The other topology, common source with the inductive degeneration, can achieve simultaneous noise and input impedance matching. Even though this method is narrow-band, it is widely used due to its appropriate noise and input impedance performance [4]. The first topology studied in this section is the amplifier topology with feedback resistance.

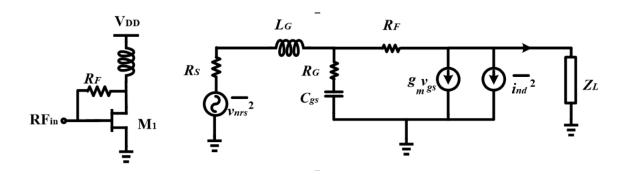

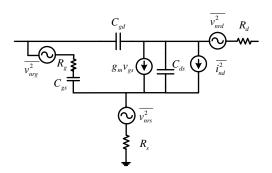

### 1.3.1 Common Source Topology with Resistive Feedback

Fig.1.10 shows the small signal noise model of a common source stage with resistive feedback. The resistance  $R_g$  indicates the gate noise and the noise source of  $i_{nd}$  indicates the transistor channel noise. In designing a common source LNA with resistive feedback, it is important to choose the appropriate feedback resistor. In a preliminary calculation, regardless of the thermal noise of the gate  $(R_g)$ , it can be considered that in order to have input impedance matching the  $g_m$  of transistor should be equal to  $1/R_s$ . In this case, the gain can be obtained from  $A_v = \frac{1}{2}(1 - \frac{R_F}{R_s})$ , assuming  $R_F$  to be large, the gain magnitude would be  $-\frac{R_F}{2R_s}$ . In this case the NF can be calculated using Eq (1.5)

$$NF = 1 + \frac{4R_F}{R_S(1 - \frac{R_F}{R_S})^2} + \frac{\gamma g_m (R_F + R_S)^2}{R_S(1 - \frac{R_F}{R_S})^2} \approx 1 + \frac{4R_S}{R_F} + \gamma$$

(1.5)

Figure 1.10 – Schematic and small signal noise model of resistive feedback topology

This topology has the NF larger than 2 or 3 dB depending on the process and the magnitude of  $\gamma$ . A closer look to the performance of this topology reveals that this resistor leads to decrement on sensitivity of this topology to the source impedance matching which can lead to wide-band amplifier design [12].

$$R_n = \frac{G_f + \gamma g_m + R_g g_m^2}{|Y_f - g_m|^2} \tag{1.6}$$

$$|Y_{opt}| = \sqrt{\frac{(g_m^2 + C_{gs}^2 \omega^2)(G_f + R_g Y_f^2) + \gamma g_m (G_f^2 + C_{gs}^2 \omega^2)}{G_f + \gamma g_m + R_g g_m^2}}$$

(1.7)

Using these equations in numerical analysis, by placing this  $R_f$  resistor, the NF sensitivity to the input impedance matching can be reduced so the bandwidth of the circuit can be increased. In this topology, with increasing the resistance, the NF decreases and gain increases, but the effect of this resistance in the input impedance matching decreases so there is an optimal amplitude in which both desirable gain and NF can be achieved. The input impedance of this topology can be obtained using (1.8).

$$Z_{in} = \frac{Z_L/R_F + 1}{Z_L/R_F (C_{qs}s + g_m) + C_{qs}s + 1/R_F}$$

(1.8)

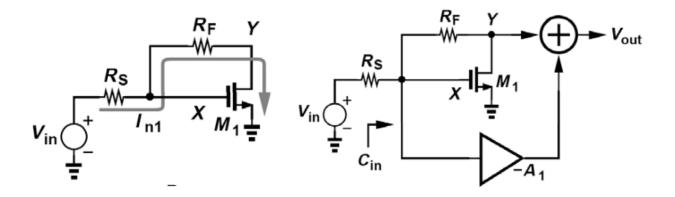

This topology is mostly used by some methods that can improve NF. One of these methods is noise-cancellation as represented in Fig.1.11. In this case by choosing  $A_1 = (1 + \frac{R_F}{R_s})$  the gain would be:

$$\frac{V_{out}}{V_x} = \left(1 - \frac{R_F}{R_s}\right) - A_1 = \left(1 - \frac{R_F}{R_s}\right) - \left(1 + \frac{R_F}{R_s}\right) \tag{1.9}$$

Figure 1.11 – Noise cancellation method in common source topology with resistive feedback [4]

In this case, the NF can be obtained from the Eq. (1.10) [4].

$$NF = 1 + \frac{R_s}{R_F} + \frac{\overline{V^2}_{nA1}}{4kTR_s} \left(1 + \frac{R_s}{R_F}\right)^2 \tag{1.10}$$

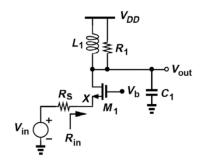

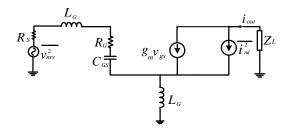

#### 1.3.2 Common Source Topology with Inductive Degeneration

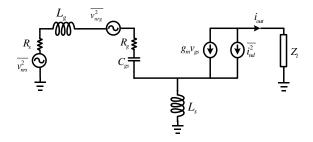

The Inductively degenerated common source (IDCS) topology is one of the most widely used topologies in the design of low-noise amplifiers. This topology is used in the design of broadband circuits with very low NF [13], [14]. One of the best features of this topology is the possibility to achieve simultaneous noise and impedance matching. Fig.1.12. represents the schematic of this topology and its small-signal noise model. The resistance of  $R_G$  indicates the gate's noise and the noise source of  $i_{nd}$  indicates the transistor channel noise. For designing this circuit, two general approaches can be utilized. A more common and simpler method is to select the degenerate inductor to match the input impedance at the operating frequency and then calculate the circuit's NF. The obtained NF in this method will not necessarily be minimal. In the second method, which is called simultaneous noise and impedance matching (SNIM) by calculating the optimum noise impedance of the circuit ( $Z_{sopt}$ ), it tries to achieve the condition of  $Z_{in}^* = Z_{sopt}$  so that the minimum possible NF and high gain can be achievable. The input impedance of this circuit can be obtained by Eq. (1.11).

$$Z_{in} = R_G + (L_s + L_G)s + 1/C_{gs}s + \frac{g_m L_s}{C_{gs}}$$

(1.11)

Figure 1.12 – Schematic and small signal noise model of IDCS stage

By placing  $L_G$  in the input, input impedance can be achieve by setting  $R_s = R_g + \frac{g_m L_s}{C_{gs}}$ . In this case, the NF is obtained by neglecting the noise of  $R_g$  as shown in Eq. (2.12).

$$NF = 1 + g_m R_s \gamma \left(\frac{\omega_0}{\omega_T}\right)^2 \left(where \,\omega_T \approx \frac{g_m}{C_{qs}}\right)$$

(1.12)

To decrease the effect of the  $C_{gd}$  cascading can be used as represented in Fig.1.13. In this approach, neglecting the noise of the cascaded transistor and considering the noise the load resistance the NF would be:

$$NF = 1 + g_m R_s \gamma \left(\frac{\omega_0}{\omega_T}\right)^2 + \frac{4R_s}{R_1} \left(\frac{\omega_0}{\omega_T}\right)^2 \left(where \, \omega_T \approx \frac{g_m}{C_{as}}\right)$$

(1.13)

In similar researches, the same topology has been used by adding a switch to the re-configurable IDCS LNA in order to switch the frequency band as shown in Fig.1.14. [15].

IDCS stage is known as a topology capable of achieving simultaneous matching of noise and impedance (SNIM) [16]. To achieve minimum NF while input impedance is fully matched, further studies on this topology for SNIM condition is needed. The conditions for achieving SNIM have already been calculated with the CMOS noise model [17]. Here noise model of GaAs-pHEMT transistor has been investigated. The reason for choosing this process is its suitable behavior for high frequency design. It is necessary to calculate the noise correlation matrix by obtaining the equivalent noise sources of the two-port so that the accurate noise parameters including minimum NF, source optimum noise impedance and  $R_n$  can be obtained. The equivalent noise sources are represented in

Figure 1.13 – Cascaded IDCS stage [4]

Figure 1.14 – Re-configurable multi-band LNA using a switch in gate [15]

Eq (1.14-1.15).

$$i_n = \frac{C_{gs}s}{q_m}i_{nd} \tag{1.14}$$

$$v_n = \frac{C_{gs}L_s s^2 + 1}{g_m} i_{nd} + v_{R_G} \tag{1.15}$$

Also the noise parameters can be calculated by Eq. (1.16)-(1.18).

$$R_n = R_g + \frac{\gamma}{q_m} (1 - L_s C_{gs} \omega^2)^2 \tag{1.16}$$

$$NF_{\min} = 1 + 2C_{gs}\omega\sqrt{\frac{\gamma R_g}{g_m}} \tag{1.17}$$

$$Z_{opt} = \frac{1}{C_{gs}\omega} \left( \sqrt{\frac{R_g g_m}{\gamma} + R_g^2 C_{gs}^2 \omega^2} + (1 - L_s C_{gs}\omega^2) j \right)$$

(1.18)

It can be seen that  $R_n$  can be minimized at  $\omega = \frac{1}{\sqrt{L_s C_{gs}}}$  so it can be expected to be able to design a circuit with low sensitivity to the source impedance around this frequency. To achieve SNIM, the condition  $Z_{opt}^* = Z_{in}$  is needed.

$$Z_{in} = \frac{1 - L_s C_{gs} \omega^2}{C_{gs} \omega} j + \frac{g_m L_s}{C_{gs}} + R_g$$

(1.19)

Therefore:

$$L_s\omega = \sqrt{\frac{R_g}{\gamma g_m} + \frac{R_g^2 C_{gs}^2 \omega^2}{g_m^2}} + \frac{R_g C_{gs}}{g_m}$$

(1.20)

Therefore, in this topology, by properly choosing the source inductor, simultaneous noise and impedance matching can be achieved, and if our design is such that the frequency at which  $R_n$  is minimized is the central frequency of our circuit, then we can achieve a wide-band design because around this frequency the sensitivity of the circuit to the optimal impedance change is minimized and thus the circuit NF will remain close to the minimum noise number.

One of the modifications that has been done in this topology to increase the bandwidth and improve the gain is the use of a coupled gate inductor to the source inductor [18]. In this circuit, as represented in Fig.1.15. and Fig.1.16. to reduce the power consumption, current-reuse method is utilized. The shared current path of these two stages would ultimately leads to a reduction in power consumption. The usage of this topology in newer

Figure 1.15 – Gate and source inductor coupling for performance improvement of IDCS stage [18]

technologies such as InP, which generally have lower NF, has also been considered, and ultimately has made it possible to achieve a very low NF in the wide-band LNA designs. In [19] as shown in Fig.1.17. a 5-stage LNA, by use of this topology in the first two stages has been designed in order to achieve the low NF. In the last three stages, common source topology with resistive feedback are used to achieve appropriate input and output impedance matching as well as smooth gain in the frequency range of 18 to 43 GHz.

In this section all used topologies in high frequency wide-band LNAs are investigated. These topologies can be used without or eventually with some improvement or with combination of different topologies in high frequency LNA circuits. Given that, the common gate topology is considered in the broadband impedance matching and relatively low NF. The topology of common source resistive feedback can be considered as linear amplifier with low sensitivity to source impedance and good input impedance matching while it has relatively high NF. Common source with inductive degeneration topology is widely used in applications with very low NF. In this topology, it is possible to achieve the lowest NF of transistor while matching the input impedance.

# 1.4 Linearization Techniques in LNAs

Linearity is one of the important parameters in LNA design which can greatly affect the performance of the receiver. The nonlinearity of the LNA is due to the intrinsic prop-

Figure 1.16 – Current reuse in gate and source inductor coupling for performance improvement of IDCS stage[18]

Figure 1.17 – Frequency behavior of different stages to achieve smooth gain in multistage amplifier with input IDCS stages [19]

erties of the transistor, which is mainly happens because of to two main reasons: [20]

- 1- Non-linearity due to the nonlinear behavior of  $g_m$  that causes the input signal not to appear linearly at the output, which is called input non-linearity.

- 2-Non-linearity caused by a large signal in the output which is due to nonlinear behavior of  $g_{ds}$  which is called output non-linearity. Linearization methods in amplifiers generally include the following approach:

- Feedback

- Harmonic termination

- Optimal Biasing

- Feed Forward

- Derivative Superposition

- Second order intermediation injection (IM2 Injection)

- Noise / distortion cancellation

- Post distortion

- EER (Envelope Elimination and Restoration)

- LINC (Linear amplification with Nonlinear Components)

- Pre distortion

- Linearization method based on specific architectures such as DOHERTY amplifier

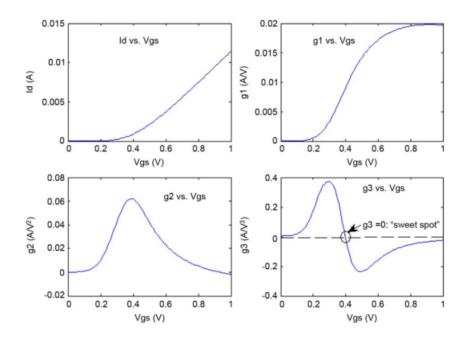

EER and LINC methods are mostly being used in power amplifiers. The output signal of an amplifier can be modeled as polynomial such as  $Y = g_1X + g_2X^2 + g_3X^3$  in which Y and X are output and input signal and  $g_1$  is the linear gain of the amplifier, and  $g_2$ ,  $g_3$  are weighting coefficient of the second and third order non linearity of the amplifier. Eq. (1.21) represents the nonlinear relationship between input and output of a transistor amplifier.

$$i_d = g_1(V_{qs} - V_s) + g_2(V_{qs} - V_s)^2 + g_3(V_{qs} - V_s)^3$$

(1.21)

$$g_1 = \frac{\partial I_D}{\partial V_{gs}}; g_2 = \frac{1}{2} \frac{\partial^2 I_D}{\partial V_{gs}^2}; g_3 = \frac{1}{6} \frac{\partial^3 I_D}{\partial V_{gs}^3}.$$

(1.22)

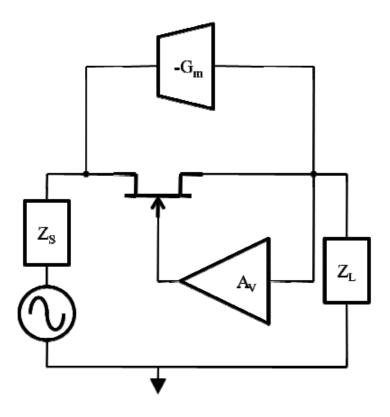

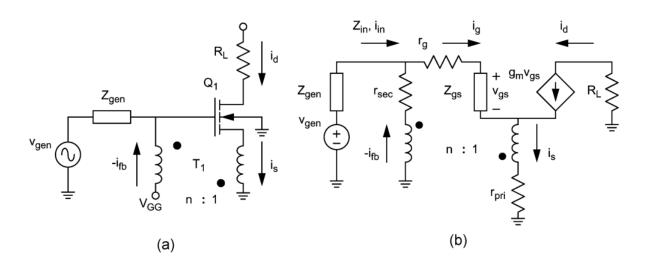

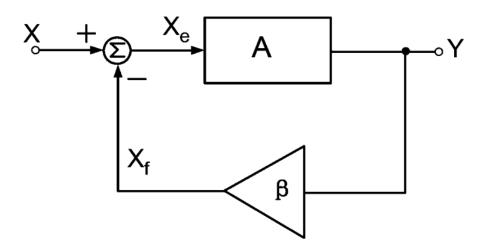

One way to linearize the amplifier is to use the feedback path. With the presence of feedback as shown in Fig.1.18., the input-output relationship is calculated as follows [21]:

$$Y = b_1 X + b_2 X^2 + b_3 X^3 (1.23)$$

$$b_1 = \frac{g_1}{1+T}; b_2 = \frac{g_2}{(1+T)^3}; b_3 = \frac{g_3}{(1+T)^4}; (T=g_1\beta)$$

(1.24)

Figure 1.18 – Using feedback for linearization in LNAs [21]

Figure 1.19 – Common source and common-gate LNA with harmonic termination [22]

where  $\beta$ isthefeedbackgaininFig.1.18.GiventhatA<sub>Ip2</sub> =  $\sqrt{\frac{g_1}{g_2}}$  and  $A_{Ip3} = \sqrt{\frac{4}{3} \left| \frac{g_1}{g_3} \right|}$  [4], so  $A_{Ip2}$  improves by the factor of 1 + T and  $A_{Ip3}$  by the factor of  $(1 + T)^{1.5}$ . It should be noted that in this method, the loop-gain should be so small that its effect on the noise and gain should be negligible. The second method, shown in the Fig. 1.19. [22], is harmonics termination, in which a node of the circuit is grounded at a second-order intermodulation frequency, leading to no second-order intermodulation.

Another linearization method is biasing the transistor at its optimal point. In this method, the current in the transistor is plotted according to the gate-source voltage, then the second and third derivatives of this relation are also plotted. At the point where  $g_3$

Figure 1.20 – linearization method by optimal biasing [23]

of the transistor equals zero, this bias point is selected for the transistor. This is shown in the Fig.1.20. for an NMOS transistor in the 90nm process with  $\frac{w}{l} = 20/.08$  and with  $v_{ds} = 1V$ . This bias point is called the sweet spot [23].

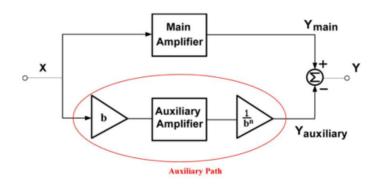

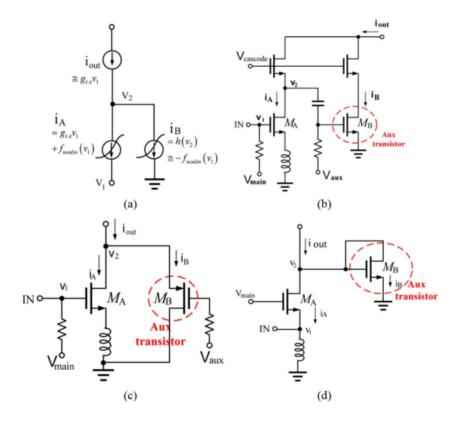

In order to eliminate non-linear elements of  $g_2$  and  $g_3$  with the least effect on  $g_2$ , a higher degree of freedom is needed. Therefore, an auxiliary path from input to output consist of an auxiliary amplifier can be used. By controlling its gain and linearity, the linearity of overall amplifier can be improved. In this method as shown in Fig. 1.21., by selecting the appropriate magnitude for the coefficient of b and n, the linearity of amplifier can be controlled. The equations associated with this method is represented in Eq. 1.25-1.27. Although in this method the gain is slightly reduced, but nonlinear parameters are further reduced which leads to more linear amplifier [24].

$$Y_{main} = g_1 X + g_2 X^2 + g_3 X^3 (1.25)$$

$$Y_{aux} = (g_1(bX) + g_2(bX)^2 + g_3(bX)^3) \frac{1}{b^n}$$

(1.26)

$$Y_{tot} = g_1 X \left(1 - \frac{1}{b^{n-1}}\right) + g_2 X^2 \left(1 - \frac{1}{b^{n-2}}\right) + g_3 X^3 \left(1 - \frac{1}{b^{n-3}}\right)$$

(1.27)

Figure 1.21 – Linearization method using an auxiliary path in amplifier [24]

Figure 1.22 – Derivative Superposition technique to linearize amplifier [20]

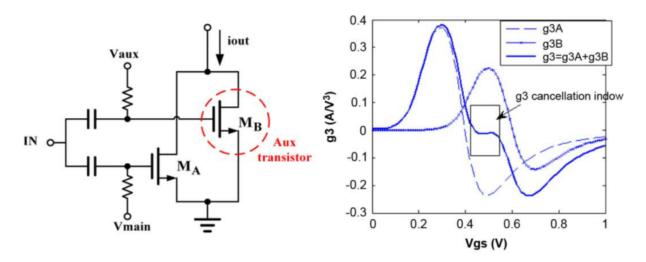

Another method is the Derivative Superposition method, which is a special case of the above mentioned method. In this technique, b = 1 is selected. The main difference is that the two amplifiers does not exhibit the same behavior. For example, in CMOS technology, the two transistors are not biased at the same biasing point. Choosing appropriate biasing can lead to a more linear amplifier through the combination of these two transistors. As represented in Fig. 1.22. it can be seen that, this method is called derivative superposition because the third-order derivative of overall amplifier is the summation of two main and additional amplifiers so it can eliminate the non-linearity of main amplifier [20].

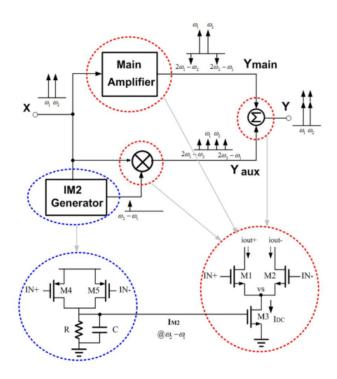

Another linearization method is the second-order intermodulation injection. As can be seen in Fig. 1.23. a new parallel path composed of a mixer will generate  $2\omega_2 - \omega_1$  and  $2\omega_1 - \omega_2$  components by multiplying the input signal with the second order intermod-

Figure 1.23 – Linearization technique using second order intermodulation injection [25]

ulation with a negative magnitude. Therefore, by choosing appropriate coefficients, the nonlinear components of the main amplifier can be eliminated [25].

Another method is noise and distortion cancellation in which common gate and the common source stages are parallelized. Since the output of common gate is in phase with the input and output of common source is in opposite phase to the input, the parameters of the two stages can be selected in such way that the noise and distortion can be canceled. The idea is represented in Fig.1.24 for a differential output on the left [26] and a single output [27] on the right.

The final method is to use the post-distortion method in which similar to Derivative Superposition method, the non-linearity behavior of the main amplifier is eliminated by the nonlinear behavior of the additional amplifier. It has two advantages in comparison to that: it has less effect on the impedance matching, and since all transistors are in the saturation region, it is a more reliable method. In this method as shown in Fig.1.25, the output of the two main and auxiliary amplifiers will be as Eq. 1.28-1.30, in which the input voltage of the auxiliary amplifier is dependent to the voltage of the first amplifier.

Figure 1.24 – Noise and distortion cancellation technique for LNA linearization [26]-[27]

Figure 1.25 – Post-distortion linearization and implementation in a [28], b [29] and c [30]

$$i_A = g_{1A}v_1 + g_{2A}v_1^2 + g_{3A}v_1^3 (1.28)$$

$$i_B = g_{1B}v_2 + g_{2B}v_2^2 + g_{3B}v_2^3 (1.29)$$

$$v_2 = -b_1 v_1 - b_2 v_1^2 - b_3 v_1^3 (1.30)$$

In this way, the output relation to the input is obtained as Eq.1.31, which makes the overall amplifier be more linear by minimizing the coefficient of the second and third order distortions.

$$i_{out} = (g_{1A} - b_1 g_{1B})v_1 + (g_{2A} - b_1^2 g_{2B} - b_2 g_{1B})v_1^2 + (g_{3A} - b_1^3 g_{3B} - b_3 g_{1B} - 2b_1 b_2 g_{2B})v_1^3$$

(1.31)

# 1.5 Study of Different Technologies for Implementation of RF circuits

The ever-increasing growth of high-frequency wireless technologies has created a broad possibility for making efficient, cost-effective circuits as well as a reasonable complexity of the manufacturing process.

This has led to a variety of technologies ranging from low-cost CMOS technology with rather poor performance to third and fourth generation technologies to be considered according to the required performance in the designing of RF circuits. There is a great variety of manufacturing technologies each of which meet part of required constrains.

CMOS technology, as one of the most available technologies is a low-cost, high-yield technology with a large wafer surface. It also enjoys benefits of the vast experience gained in this technology over decades in the construction of circuits. Despite the fact that this technology has been widely used for digital integration, due to its poor noise performance and hard integration of passive elements, it is associated with a great challenges in designing RF circuits. Therefore, it is not a good option in the construction of low-noise RF circuits [31].

In this technology, as the size of the transistors decreases, the high frequency behavior is improved and also the power consumption is reduced, but all these happen at the expense of worsening the noise behavior.

Other technologies are SiGe-BiCMOS and SiGe-HBTs that have relatively balanced the construction cost, performance and manufacturing complexity. The process of making SiGe-BiCMOS is only slightly more complex than conventional CMOS. The new SiGe-HBT process has the same working frequency as the GaAs, which is the first choice in

the construction of integrated microwave circuits. However, GaAs behave better in the integration of passive and high power elements. In general, SiGe will be a good choice whenever we want good high frequency behavior with good noise performance at a moderate to high cost. GaAs technology can be considered as the first choice in the design of microwave circuits due to its very good performance. The progress of this process and the increasing use of pHEMT has made the performance of this process even better. Thus, GaAs technology even with its higher cost is preferred among technologies available at high power and low noise application at higher frequencies.

In addition to this, in newer and more expensive manufacturing processes, it is possible to achieve lower noise and better high frequency behavior. For example, SOI technology, due to an insulating layer, causes the circuit elements to be isolated from each other, which improves noise behavior vastly[31]. To conclude according to what has been said, among all the available technologies for IC design, in this thesis, based on the required specifications which are to achieve the minimum possible NF and high output power at high frequencies, GaAs-pHEMT  $0.1\mu$ m technology is chosen. The noise model for this process is detailed in the following chapters. In this section, an overall literature review to LNA design is presented. Considering the previous works, three different method for performance improvement in high frequency wide band LNAs are proposed in this thesis. The following three chapters will have a detailed discussion on these three approaches.

# FIRST APPROACH: OPTIMIZATION OF LNA'S FIRST STAGE TO REDUCE OVERALL NOISE FIGURE IN MULTI-STAGE LNAS

## 2.1 Introduction

In the previous chapter, we have defined all critical parameters for LNA design. We have shown the importance of the technology as well as the topology of mounted LNAs. So, in a first approach, the consideration of following stages noise for designing a multistage LNAs is looked forward. In this approach, a new procedure for design of multi stage LNAs with consideration of following stages noise is presented. This approach and its result previously published in [32].

At RF and microwave frequencies, to meet the required gain specification, usually more than one stage is needed. While analytical solution for design method of a single stage LNA is previously presented [36], optimization for a multi-stage LNAs and specially its first stage has not been investigated thoroughly yet. Designing a multi-stage LNAs are considered more complicated than single stage LNAs according to the importance of specifying the number of stages to achieve required gain as well as optimal design of each stage based on its constant-noise factor (F), available gain and input return circles in the  $\Gamma_S$  plane. Therefore, all the consideration on the trade-off between these constrains to meet the required specifications should be taken into account.

Conventional methods in different topologies and approaches for LNA design with optimized NF consist of specifying the number of stages to achieve the required gain in the desired bandwidth and designing each stage based on:

• constant-noise factor (F)

Figure 2.1 – Gain and NF contours for optimal conventional design

- constant-available gain  $(G_{av})$  circles in the source reflection coefficient plane  $(\Gamma_s \text{ plane})$

- constant-input return loss  $(RL_{in})$  circles in the source reflection coefficient plane  $(\Gamma_s)$