# Design for security in mixed analog-digital integrated circuits

Mohamed Elshamy

#### ▶ To cite this version:

Mohamed Elshamy. Design for security in mixed analog-digital integrated circuits. Micro and nanotechnologies/Microelectronics. Sorbonne Université, 2021. English. NNT: 2021SORUS093. tel-03343690v2

# HAL Id: tel-03343690 https://hal.science/tel-03343690v2

Submitted on 8 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

# DESIGN FOR SECURITY IN MIXED ANALOG-DIGITAL INTEGRATED CIRCUITS

# présentée par MOHAMED ELSHAMY

# École Doctorale Informatique, Télécommunications et Électronique

réalisée au

Laboratoire d'Informatique Paris 6

#### soutenue le 7 Juillet 2021

#### devant le jury composé de :

| M.   | Yiorgos MAKRIS            | Prof., UT Dallas, USA                | Rapporteur             |

|------|---------------------------|--------------------------------------|------------------------|

| M.   | Bruno ROUZEYRE            | Prof., LIRMM, Montpellier, France    | Rapporteur             |

| Mme. | Sule OZEV                 | Prof., Arizona State University, USA | Examinatrice           |

| M.   | Giorgio DI NATALE         | DR CNRS, TIMA, Grenoble, France      | Examinateur            |

| M.   | Vincent BEROULLE          | Prof., LCIS, Valence, France         | Examinateur            |

| M.   | Michele PORTOLAN          | MCF, TIMA, Grenoble, France          | Examinateur            |

| Mme. | Marie-Minerve LOUËRAT     | CR CNRS, LIP6, Paris, France         | Co-directrice de Thèse |

| M.   | Haralampos STRATIGOPOULOS | DR CNRS, LIP6, Paris, France         | Directeur de Thèse     |

| M.   | Hassan ABOUSHADY          | MCF, LIP6, Paris, France             | Invité                 |

| To my family, without your support and encouragement I would never reach this point. |

|--------------------------------------------------------------------------------------|

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

|                                                                                      |

Recently, the enormous cost of owning and maintaining a modern semi-conductor manufacturing plant has coerced many companies to go fabless. By outsourcing the manufacturing of integrated circuit/intellectual property (IC/IP) to third-party and often off-shore companies, the process has been extended to potentially untrustworthy companies. This has resulted in several security threats to the semiconductor industry such as counterfeiting, reverse engineering, and hardware Trojans (HTs) insertion. In this thesis, we propose an anti-piracy countermeasure to protect analog and mixed-signal (AMS) ICs/IPs, a novel HT attack for AMS ICs/IPs, and a novel physical unclonable function (PUF).

More specifically, we propose an anti-piracy technique based on locking for programmable analog circuits. The proposed technique leverages the programmability fabric to implement a natural lock-less locking. We discuss its implementation and its resilience capabilities against foreseen attacks, and we demonstrate it with simulation analysis and hardware measurements of programmable  $\Sigma\Delta$  Analog-to-Digital Converters (ADCs) intended for use in highly-digitized, multi-standard RF receiver applications. The proposed HT attack for analog circuits leverages the test infrastructure. The HT is hidden effectively in a digital core and transfers its payload to the analog circuit via the test bus and the interface of the analog circuit to the test bus. Its key characteristic is that it is invisible in the analog domain. The proposed HT is demonstrated on two case studies. The first case study shown with simulation is a low-dropout (LDO) regulator and the second case study shown with hardware measurements is a programmable RF receiver front-end. This thesis sheds light on the importance of developing new security and trust countermeasures tailored for analog circuits. The proposed locking technique illustrates the feasibility of securing a large number of analog circuits while keeping their design intact, which is a crucial requirement for analog designers, in order for the locking technique to be widely adopted. For the proposed HT, it reveals the possibility of digital-to-analog HT attacks. The proposed PUF, called neuron-PUF, uses a single spiking neuron as the source of entropy. Its key characteristic is that it uses a single PUF cell and temporal redundancy to generate an arbitrarily long key, which results in significant low area and power overheads compared to mainstream PUFs, such as delay-based and memory-based PUFs.

Récemment, les coûts faramineux pour construire et entretenir une usine de fabrication de semi-conducteurs ont contraint de nombreuses entreprises à renoncer à avoir une usine de fabrication en propre. En externalisant la fabrication de circuits intégrés/propriété intellectuelle (CI/PI) à des sociétés tierces et souvent extraterritoriales, le procédé de fabrication a été confié à des sociétés potentiellement peu fiables. Il en résulte plusieurs menaces de sécurité pour l'industrie des semi-conducteurs, telles que la contrefaçon, la rétro-ingénierie et l'insertion de chevaux de Troie matériels (HT). Dans cette thèse, nous proposons une contre-mesure anti-piratage pour protéger les CI/PI analogiques et à signaux mixtes (AMS), une nouvelle attaque HT pour les CI/PI AMS et une nouvelle fonction physique non clonable (PUF).

La technique anti-piratage que nous proposons est basée sur le verrouillage des circuits analogiques configurables. Notre technique exploite le mécanisme de configuration intrinsèque du circuit pour y introduire une fonction verrouillage. Nous discutons de son implémentation et de ses capacités de résilience contre les attaques prévues, et nous la démontrons par une analyse en simulation et des mesures physiques d'un convertisseur analogique-numérique  $\Sigma\Delta$  destiné à être utilisé dans des applications de récepteurs RF multistandard. L'attaque HT proposée pour les circuits analogiques exploite l'infrastructure de test. Le HT est introduit dans le sous-système numérique du système AMS et transfère sa charge utile au circuit analogique via le bus de test jusqu'à l'interface du circuit analogique à ce bus. Sa caractéristique principale est d'être invisible dans le domaine analogique. Le HT est démontré par deux études de cas. La première, en simulation, concerne un régulateur de tension (LDO) et la seconde, illustrée par des mesures en laboratoire, met en œuvre un récepteur RF configurable. Cette thèse montre l'importance de nouvelles contre-mesures de sécurité et de confiance adaptées aux CI analogiques. La technique de verrouillage proposée prouve la faisabilité de sécurisation d'un grand nombre de CI analogiques sans affecter leur conception, ce qui est une exigence majeure des concepteurs pour adopter cette technique. L'attaque par HT proposée révèle la possibilité d'attaques HT de système sur puce, ou SoC, AMS. La fonction PUF proposée utilise un neurone à impulsions comme source d'entropie. Sa caractéristique principale est de n'utiliser qu'une seule cellule PUF et une redondance temporelle pour générer une clé arbitrairement longue, ce qui permet de réduire considérablement les coûts additionnels en surface et en énergie par rapport aux fonctions PUF traditionnelles, telles que les PUF à retard et à mémoire.

As a result of this thesis the following publications have appeared:

- [1] M. Elshamy, A. Sayed, M.-M. Louërat, A. Rhouni, H. Aboushady, and H.-G. Stratigopoulos, "Securing Programmable Analog ICs Against Piracy," in *Proc. Design, Automation and Test in Europe Conference*, 2020.

- [2] M. Elshamy, G. Di Natale, A. Pavlidis, M.-M. Louërat, and H.-G. Stratigopoulos, "Hardware Trojan Attacks in Analog/Mixed-Signal ICs via the Test Access Mechanism," in *Proc. IEEE European Test Symposium*, 2020.

- [3] J. Leonhard, M. Elshamy, M.-M. Louërat, and H.-G. Stratigopoulos, "Breaking analog biasing locking techniques via re-synthesis," in 26th Asia and South Pacific Design Automation Conference, 2021.

- [4] M. Elshamy and H.-G. Stratigopoulos, "Neuron-PUF: Physical Unclonable Function Basedon a Single Spiking Neuron," in *The* 27th IEEE International Symposium on On-Line Testing and Robust System Design, 2021.

vii

With one step far from finishing this chapter of my academic life, I have mixed feelings. While I am happy to finish my doctoral degree, I will miss these wonderful days, my amazing team, and my supportive supervisors. It was really a great privilege to work side by side with such brilliant minds.

First of all, I would like to express my sincere gratitude to my supervisor, my mentor, and my academic father Haralampos. Thanks, Haralampos for strengthening my academic personality. Our meetings and conversations were vital in inspiring me to think from multiple perspectives to form comprehensive and objective thoughts. Thanks for helping me with the apartment renting and understanding my personal circumstances. Thanks for letting me be part of this incredible scientific environment. I am also thankful to Marie-Minerve for her support and help. Thanks, Marie-Minerve for your precise review and your fast responses. Thanks for helping to get my "convention d'accueil".

I would like to say a special thank you to Hassan Aboushady. Thanks for letting us use your precious chips to prove our hypothesis. Thanks for your explanations and your constructive discussions. Further, I would like to thank Alhassan. Thank you for your time, support, and translations. It is truly a pleasure to know you, not just as a work mate but also a great friend.

I want to extend my thanks to my team, my academic brothers, and my lab-mates Julian, Antonios, Theofilos, Gabriel, Ilias, Alán, and Sara. It was my pleasure to spend those joyful days with you guys.

And I'd like to express my heartfelt gratitude to my family for their unwavering support and encouragement throughout this research, which is the culmination of three years of study abroad. For my parents, thank you is not enough to express how grateful I am to you. For my wife, thanks for all your support and for proof-reading my thesis, you have been amazing. For my daughter, sorry for being nervous than normal whilst I wrote this thesis! and I will now have some time to play with you as I promised!

From the bottom of my heart I would like to say to all of you guys

شكراً جزبلاً

Ευχαριστώ πολύ Merci beaucoup Tausend Dank Thanks a lot

## CONTENTS

| I | NAAT | N PAR   | т         |                                             |    |

|---|------|---------|-----------|---------------------------------------------|----|

|   |      |         |           |                                             | 0  |

| 1 |      | RODUC   |           | in the Comican dustay Cumply Chain          | 3  |

|   | 1.1  |         |           | in the Semiconductor Supply Chain           | 3  |

|   |      | 1.1.1   | -         | ion of the Supply Chain                     | 3  |

|   |      | 1.1.2   |           | ns Caused by Malice Actors in the Supply    |    |

|   |      |         |           |                                             | 4  |

|   |      |         | 1.1.2.1   | Side-Channel Attacks                        | 4  |

|   |      |         | 1.1.2.2   | Hardware Trojans Attacks                    | 5  |

|   |      |         | _         | 0 0                                         | 6  |

|   |      |         | 1.1.2.4   | Counterfeiting                              | 7  |

|   |      | 1.1.3   | Vulnera   | bilities' Impact                            | 7  |

|   | 1.2  |         |           | arity and Trust                             | 8  |

|   | 1.3  | Count   |           | re against Hardware Attacks                 | 9  |

|   |      | 1.3.1   |           | ation                                       | 9  |

|   |      |         |           | Locking                                     | 10 |

|   |      |         | 1.3.1.2   | o o                                         | 10 |

|   |      |         | 1.3.1.3   | Split Manufacturing                         | 10 |

|   |      | 1.3.2   | HTs Pre   | evention and Detection                      | 11 |

|   |      | 1.3.3   | Physica   | l Unclonable Functions (PUFs)               | 11 |

|   | 1.4  |         | _         | Demand for Analog DfTr Techniques           | 12 |

|   | 1.5  | Thesis  | s Contrib | utions                                      | 14 |

|   | 1.6  | Thesis  | Structur  | e                                           | 15 |

| 2 | PRIC | OR ART  | Γ         |                                             | 17 |

|   | 2.1  | Prior . | Art on A  | nalog Obfuscation                           | 17 |

|   |      | 2.1.1   | Analog    | Locking                                     | 17 |

|   |      |         | 2.1.1.1   | Locking the Biasing Circuit                 | 17 |

|   |      |         | 2.1.1.2   | Locking the Calibration Module              | 19 |

|   |      |         | 2.1.1.3   | Locking the Digital Section within a Mixed- |    |

|   |      |         |           | Signal Circuit                              | 20 |

|   |      |         | 2.1.1.4   | Locking via Emerging Technologies           | 21 |

|   |      |         | 2.1.1.5   | Compound Locking                            | 22 |

|   |      | 2.1.2   | Analog    | Camouflaging                                | 22 |

|   |      | 2.1.3   |           | Split Manufacturing                         | 23 |

|   | 2.2  | Prior . |           | nalog HTs                                   | 24 |

|   |      | 2.2.1   |           | Circuits for Triggering HTs                 | 24 |

|   |      | 2.2.2   | _         | acks in the Analog Domain                   | 24 |

|   |      | 2.2.3   |           | enses in the Analog Domain                  | 25 |

|   |      | -       | 2.2.3.1   | HT Prevention in the Analog Domain          | 25 |

|   |      |         | 2.2.3.2   | HT Detection in the Analog Domain           | 25 |

|   | 2.3          | Prior Art on PUF                                           | 26               |

|---|--------------|------------------------------------------------------------|------------------|

|   | 2.4          | Conclusion                                                 | 28               |

| 3 | LOC          | KING BY UNTUNING: A LOCK-LESS APPROACH FOR ANA-            |                  |

|   | LOG          | G AND MIXED-SIGNAL ICS                                     | <b>2</b> 9       |

|   | 3.1          |                                                            | <b>2</b> 9       |

|   | 3.2          |                                                            | 30               |

|   | 3.3          | T 1 T T 1. 1.12 FO TO                                      | 33               |

|   |              | - 1                                                        | 33               |

|   |              |                                                            | 37               |

|   |              |                                                            | 37               |

|   |              |                                                            | 37               |

|   |              |                                                            | 37               |

|   |              | 3.3.2.4 Brute-Force and Multi-Objective Optimiza-          | •                |

|   |              |                                                            | 37               |

|   |              |                                                            | 38               |

|   | 3.4          |                                                            | 39               |

|   | <i>J</i> 1   |                                                            | 39               |

|   |              |                                                            | ر<br>40          |

|   |              |                                                            | 42               |

|   | 3.5          |                                                            | 1<br>44          |

|   |              |                                                            | י י<br>44        |

|   |              | •                                                          | 46               |

|   |              |                                                            | 47               |

|   | 3.6          |                                                            | т <i>і</i><br>52 |

|   | <i>J</i> . c | 3.6.1 Brute-Force and Multi-Objective Optimization Attacks |                  |

|   |              |                                                            | 53               |

|   | 3.7          |                                                            | 55<br>54         |

| 4 |              |                                                            | 57               |

| 4 | 4.1          | · · · · · · · · · · · · · · · · · · ·                      | 57<br>57         |

|   | •            |                                                            | 57<br>58         |

|   | 4.2          | C 11 C 1 PT TC                                             |                  |

|   |              | · · · · · · · · · · · · · · · · · · ·                      | 59<br>60         |

|   | 4·4          |                                                            | 62               |

|   | 4.5          | 1                                                          | 62               |

|   |              | • •                                                        |                  |

|   |              |                                                            | 63<br>64         |

|   |              |                                                            | 64<br>66         |

|   | . 6          | , , ,                                                      |                  |

|   | 4.6          | y .                                                        | 68<br>68         |

|   |              | ,                                                          | 68<br>           |

|   |              | •                                                          | 70               |

|   |              |                                                            | <b>7</b> 3       |

|   | 4.7          | DED 1 D 11 A 11.                                           | 74               |

|   |              |                                                            | 74               |

|   |              | 4.7.2 HT Payload Design                                    | <b>7</b> 6       |

| ON BASED | 81<br>81<br>81 |

|----------|----------------|

|          | 81<br>81       |

|          | 81             |

|          | -              |

|          | 82             |

|          | 83             |

|          | 85             |

|          | 87             |

|          | 89             |

|          | 91             |

|          | 91             |

|          | 91             |

|          | 93             |

|          |                |

|          |                |

|          |                |

|          | 97             |

|          |                |

## LIST OF FIGURES

| Figure 2.1  | Existing biasing locking methodologies for analog                          | - 0 |

|-------------|----------------------------------------------------------------------------|-----|

| Eigene a a  | ICs                                                                        | 18  |

| Figure 2.2  | Existing locking via the calibration module for                            | •   |

| Eigene o o  | analog ICs.                                                                | 20  |

| Figure 2.3  | Locking the digital section within a mixed-signal                          |     |

| Eiguno o 4  | circuits [55]                                                              | 21  |

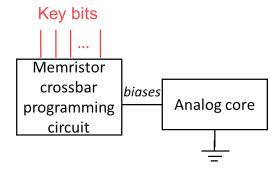

| Figure 2.4  | Biasing locking based on memristor crossbar [96].                          | 21  |

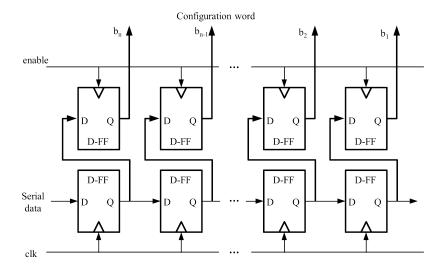

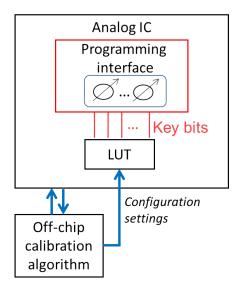

| Figure 3.1  | Configuration word loading and storage                                     | 32  |

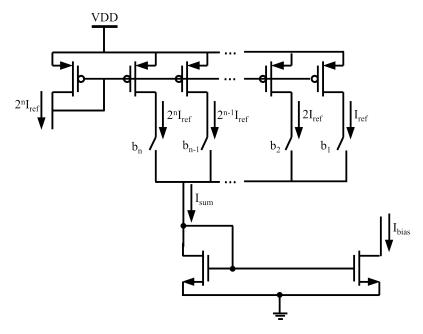

| Figure 3.2  | Programmable current mirror                                                | 33  |

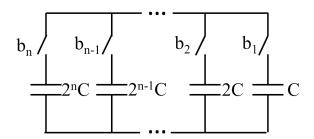

| Figure 3.3  | Programmable capacitor array                                               | 33  |

| Figure 3.4  | Lock-less locking via the programmability interface.                       | 34  |

| Figure 3.5  | Key management schemes                                                     | 35  |

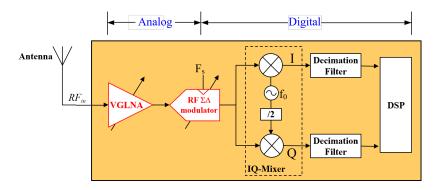

| Figure 3.6  | Architecture of programmable multi-standard RF                             |     |

|             | receiver                                                                   | 39  |

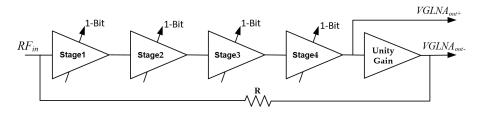

| Figure 3.7  | Architecture of tunable variable gain LNA                                  | 40  |

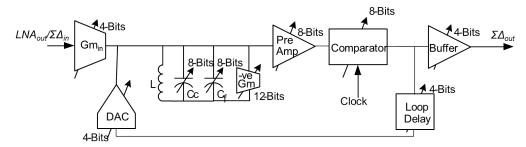

| Figure 3.8  | Architecture of tunable 2nd order BP RF $\Sigma\Delta$ mod-                |     |

|             | ulator                                                                     | 40  |

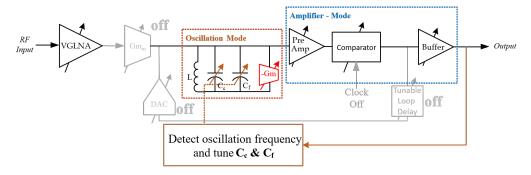

| Figure 3.9  | The 2nd order $\Sigma\Delta$ modulator configured for cali-                |     |

|             | brating the LC loop filter                                                 | 41  |

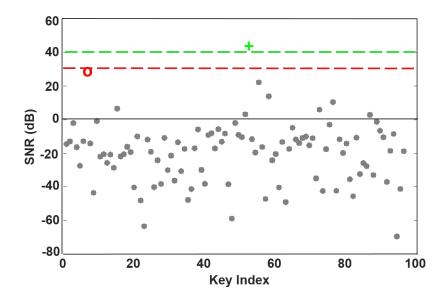

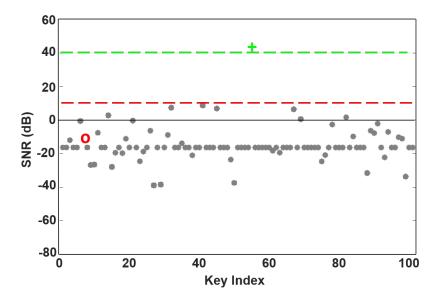

| Figure 3.10 | SNR for correct key (green cross) and invalid keys                         |     |

|             | (gray dots and red dot with index 7) computed at                           |     |

|             | the output of the BP RF $\Sigma\Delta$ modulator                           | 42  |

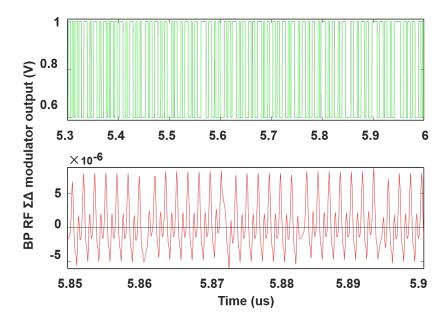

| Figure 3.11 | Transient output of BP RF $\Sigma\Delta$ modulator for the                 |     |

| O O         | correct key (top) and the invalid key with index 7                         |     |

|             | in Fig. 3.10 (bottom)                                                      | 43  |

| Figure 3.12 | SNR for correct key (green cross) and invalid keys                         | 10  |

| 0 9         | (gray dots and red dot with index 7) computed at                           |     |

|             | the output of the RF receiver                                              | 44  |

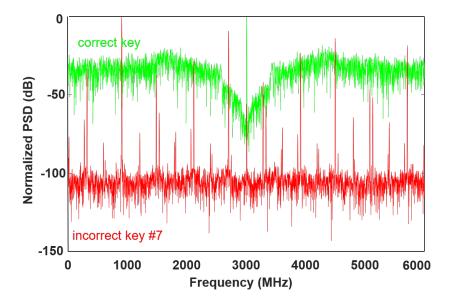

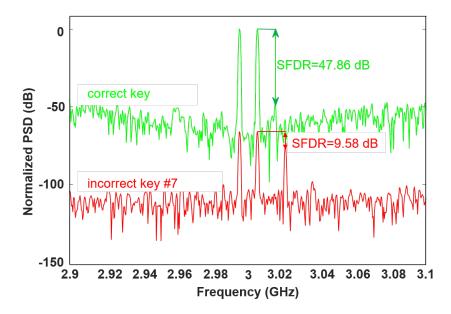

| Figure 3.13 | PSD at the output of the BP RF $\Sigma\Delta$ modulator for                |     |

| 8           | the correct key (green) and the invalid key with                           |     |

|             | index 7 in Figs. 3.10 and 3.12 (red)                                       | 45  |

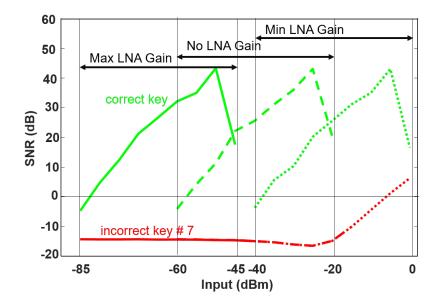

| Figure 3.14 | SNR versus input power with different LNA gain                             | 4)  |

| 118410 3.14 | settings for the correct key (green) and the invalid                       |     |

|             | key with index 7 in figures 3.10 and 3.12 (red)                            | 46  |

| Figure 3.15 | SFDR for the correct key (green) and the invalid                           | 40  |

| rigule 3.15 | • •                                                                        | 4=  |

| Eiguro 2 16 | key with index 7 in Figs. 3.10 and 3.12 (red)                              | 47  |

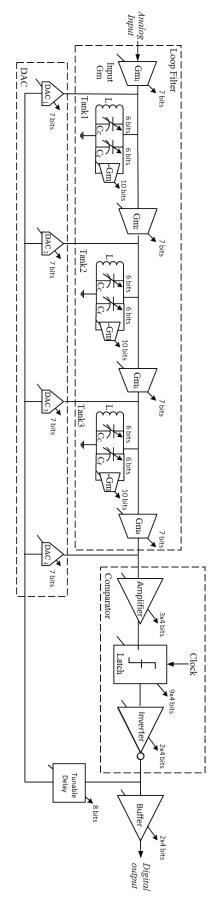

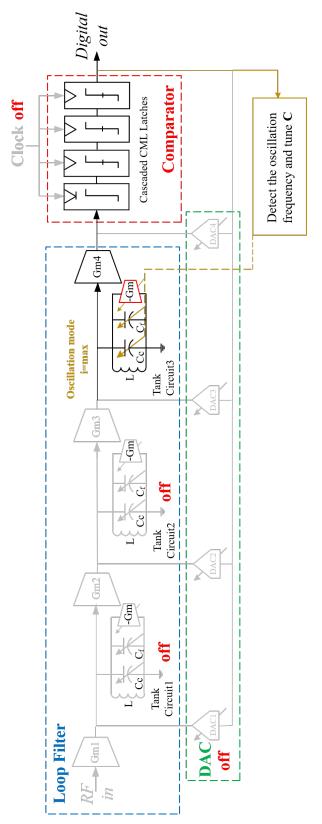

| Figure 3.16 | Architecture of $\Sigma\Delta$ modulator                                   | 48  |

| Figure 3.17 | The $\Sigma\Delta$ modulator configured for calibrating the LC loop filter |     |

|             | LA TOOD TITET                                                              | 40  |

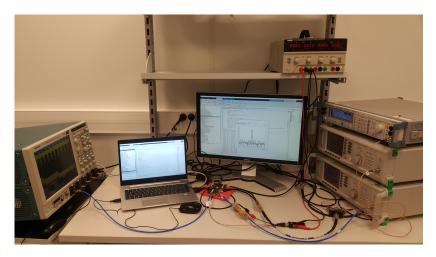

| Figure 3.18  | Test bench for measuring the performance of the             |            |

|--------------|-------------------------------------------------------------|------------|

|              | modulator under the unlocking and the different             |            |

| П•           | locking scenarios                                           | 50         |

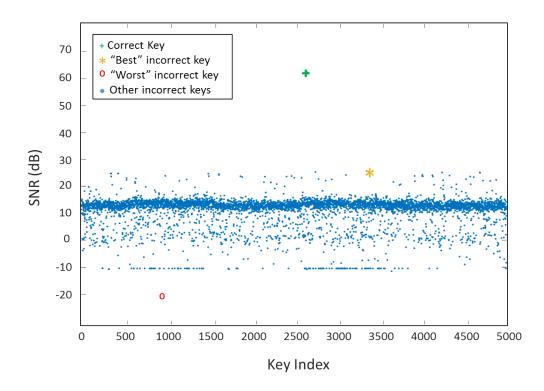

| Figure 3.19  | SNR for correct (green cross) and invalid (blue             |            |

|              | dots) keys. Invalid key (orange star) has a rela-           |            |

|              | tively high SNR, and invalid key (red circle) has           |            |

|              | the min SNR                                                 | 51         |

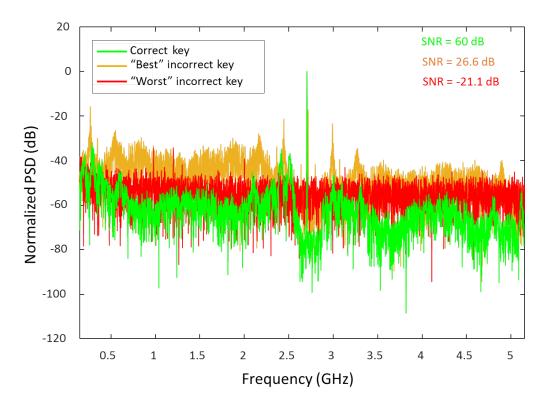

| Figure 3.20  | PSD at the output of the BP RF $\Sigma\Delta$ modulator for |            |

|              | the correct key (green) and the invalid key with            |            |

|              | max SNR (orange) and the invalid key with min               |            |

|              | SNR (red) in Fig. 3.19                                      | 52         |

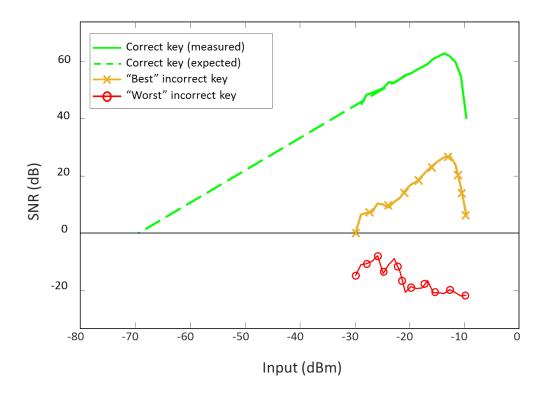

| Figure 3.21  | SNR versus input power for the correct key (green)          |            |

|              | and the invalid key with max SNR (orange) and               |            |

|              | the invalid key with min SNR (red) in Fig. 3.19             | 53         |

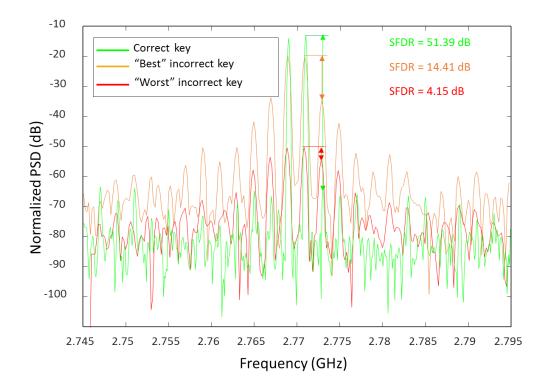

| Figure 3.22  | SFDR versus input power for the correct key (green)         |            |

|              | and the invalid key with max SNR (orange) and               |            |

|              | the invalid key with min SNR (red) in Fig. 3.19             | 54         |

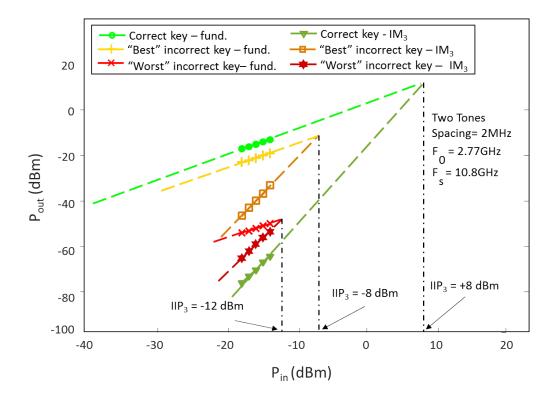

| Figure 3.23  | IIP3 under unlock and lock operation                        | 55         |

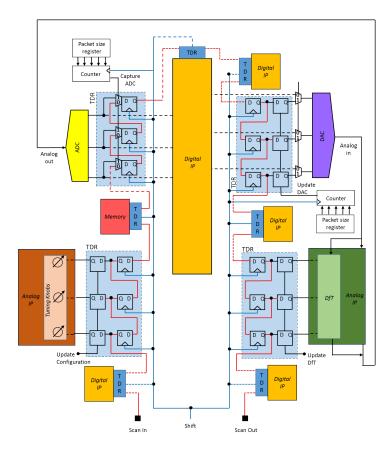

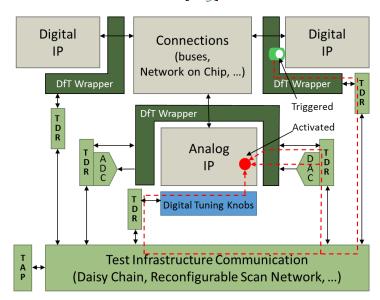

| Figure 4.1   | Scan access including analog IPs (adapted from              |            |

|              | [174])                                                      | 60         |

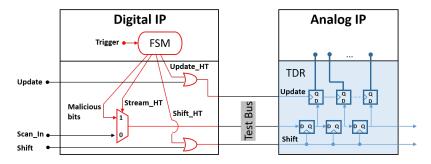

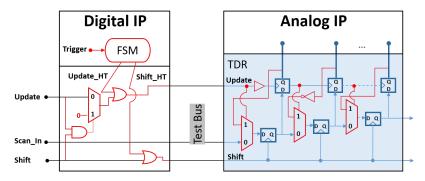

| Figure 4.2   | HT scenario exploiting the SoC test infrastructure.         | 63         |

| Figure 4.3   | Payload mechanism based on transporting the ma-             |            |

| 0 , 0        | licious bit pattern to the victim analog IP                 | 65         |

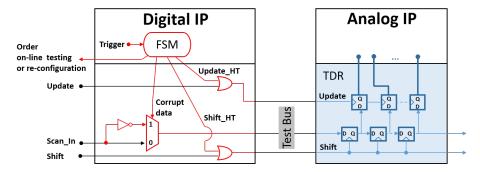

| Figure 4.4   | Payload mechanism based on updating the TDR                 |            |

| 0 11         | of the victim analog IP                                     | 65         |

| Figure 4.5   | Payload mechanism based on requesting on-line               |            |

| 0 15         | testing or re-configuration and subsequently cor-           |            |

|              | rupting the transported data                                | 66         |

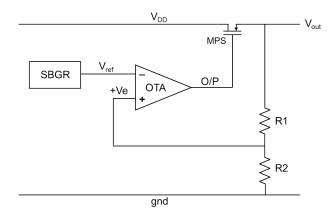

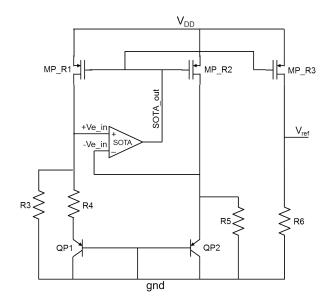

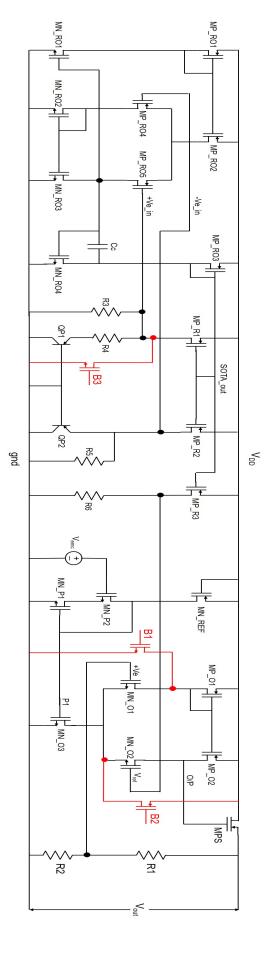

| Figure 4.6   | Block-level schematic of the LDO                            | 68         |

| Figure 4.7   | Schematic of the error amplifier within the LDO             |            |

|              | implemented with an OTA                                     | 69         |

| Figure 4.8   | Schematic of SBGR generator                                 | 69         |

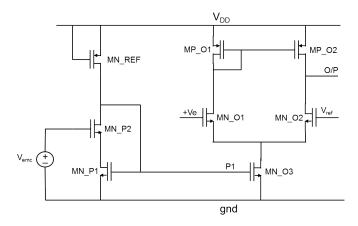

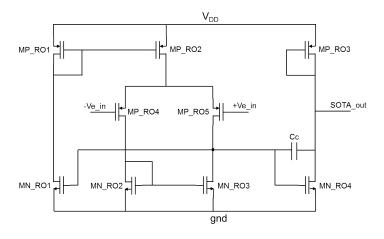

| Figure 4.9   | Schematic of SOTA                                           | 70         |

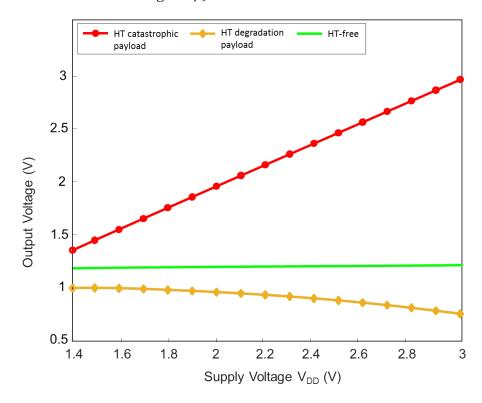

| Figure 4.10  | LDO output variation as a function of power sup-            | 70         |

| 118410 4.10  | ply variation                                               | 70         |

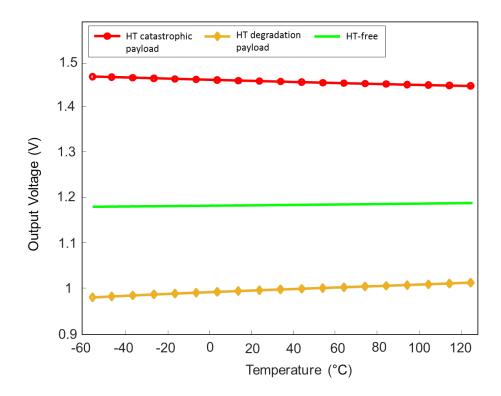

| Figure 4.11  | LDO output variation as a function of temperature           | 70         |

| 118010 4.11  | variation                                                   | 71         |

| Figure 4.12  | Transient response of the LDO for a variation of            | /1         |

| 115010 4.12  | load current.                                               | 71         |

| Figure 4.13  | LDO with DfT. The added PD and PU transistors               | 71         |

| 1 18416 4.13 |                                                             |            |

|              | to enable topology modifications are shown in red           | <b>7</b> 0 |

| Eigura       | color                                                       | 72<br>-6   |

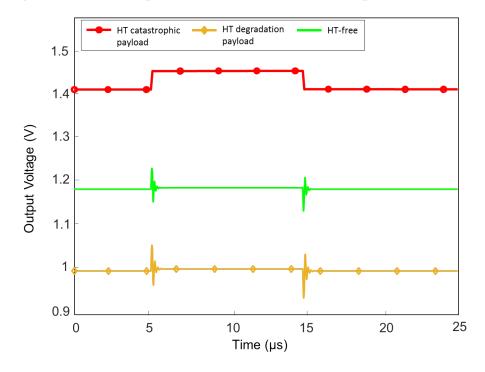

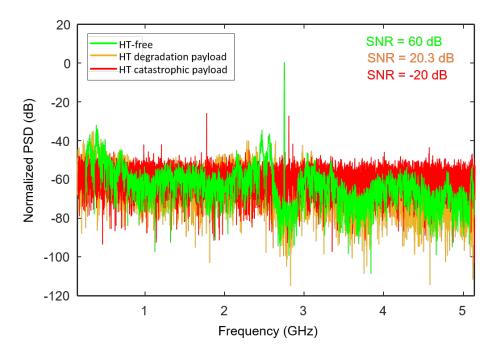

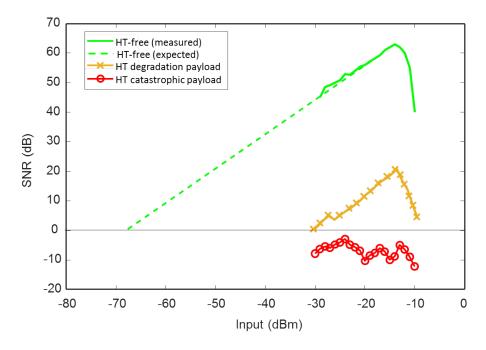

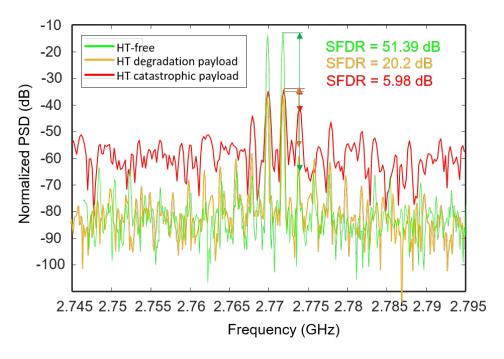

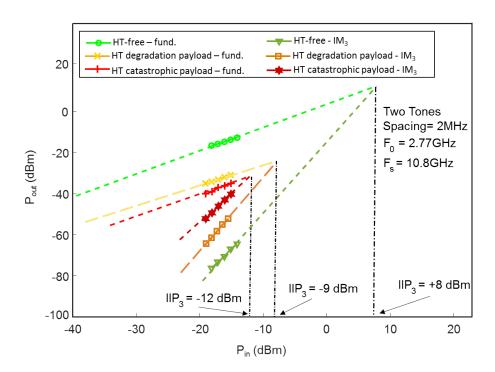

| Figure 4.14  | PSD under HT-free and HT-infected operation                 | 76         |

#### xvi LIST OF FIGURES

| Figure 4.15 | Dynamic range under HT-free and HT-infected            |    |

|-------------|--------------------------------------------------------|----|

|             | operation                                              | 77 |

| Figure 4.16 | SFDR under HT-free and HT-infected operation           | 78 |

| Figure 4.17 | IIP3 under HT-free and HT-infected operation           | 79 |

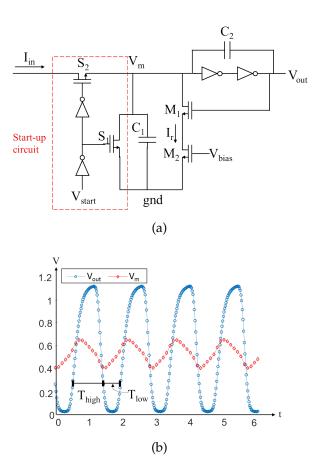

| Figure 5.1  | The axon hillock circuit: (a) schematic; (b) transient |    |

| _           | response                                               | 82 |

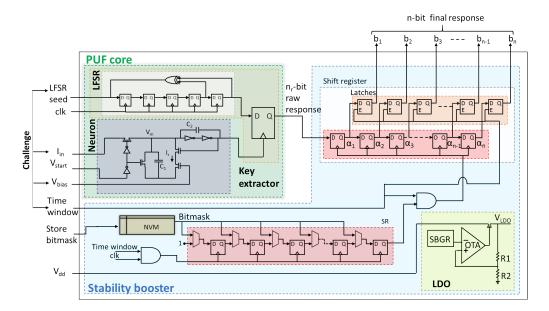

| Figure 5.2  | Neuron-PUF architecture                                | 83 |

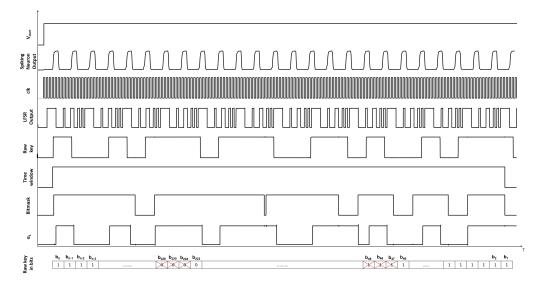

| Figure 5.3  | Transient simulation of neuron-PUF showing rele-       |    |

| 0           | vant signals.                                          | 87 |

## LIST OF TABLES

| Table | 5.1 Neuron-PUF quality metrics                       |

|-------|------------------------------------------------------|

|       |                                                      |

|       |                                                      |

| ACR   | ONYMS                                                |

| 3PIP  | Third party IP                                       |

| ACE   | adaptive channel estimation                          |

| ADC   | Analog-to-Digital Converter                          |

| AES   | Advanced Encryption Standard                         |

| AFGT  | Analog Floating-Gate Transistor                      |

| AMS   | Analog, Mixed-Signal                                 |

| ATE   | Automatic Test Equipment                             |

| BEOL  | back-end-of-line                                     |

| BIST  | Built-in Self-test                                   |

| BP    | band-pass                                            |

| CAD   | Computer-Aided Design                                |

| CE    | Consumer Electronics                                 |

| CRP   |                                                      |

|       | challenge-response pair  Digital to Apples Convertor |

| DAC   | Digital-to-Analog Converter  Design for Test         |

| DfT   | Design-for-Test                                      |

| DfTr  | design-for-trust                                     |

| DNL   | Differential Non-Linearity                           |

| DR    | dynamic range                                        |

| ECC   | error correcting code                                |

| EM    | Electromagnetic                                      |

| EVM   | Error Vector Magnitude                               |

| FEOL  | front-end-of-line                                    |

| FFT   | Fast Fourier Transform                               |

| FSM   | finite state machine                                 |

## xviii ACRONYMS

GA

Genetic Algorithm

| 011              | 30110110 1 11001111111                     |

|------------------|--------------------------------------------|

| HD               | hamming distance                           |

| HDL              | Hardware Descriptive Language              |

| HT               | hardware Trojan                            |

| IC               | Integrated Circuit                         |

| IDM              | integrated device manufacturer             |

| IIP <sub>3</sub> | input third-order intercept point          |

| $IM_3$           | third-order intermodulation                |

| INL              | Integral Non-Linearity                     |

| IP               | Intellectual Property                      |

| LDO              | low-dropout                                |

| LFSR             | linear-feedback shift register             |

| LNA              | low noise amplifier                        |

| LUT              | look-up table                              |

| MC               | Monte Carlo                                |

| NVM              | non-volatile memory                        |

| OFDM             | orthogonal frequency division multiplexing |

| OSR              | Oversampling Ratio                         |

| OTA              | operational transconductance amplifier     |

| PA               | power amplifier                            |

| PD               | Pull-Down                                  |

| PDK              | Process Design Kit                         |

| PLL              | Phase-Locked Loop                          |

| PRBS             | Pseudo-Random Bit Sequence                 |

| PSD              | power spectral density                     |

| PU               | Pull-Up                                    |

| PUF              | Physical Unclonable Function               |

| RE               | reverse engineering                        |

| RF               | Radio Frequency                            |

| RO               | Ring Oscillator                            |

| RSN              | reconfigurable scan network                |

| RTL              | Register Transfer Level                    |

| SAT              | Satisfiability                             |

| SBGR             | sub-band gap reference voltage generator   |

|                  |                                            |

SFDR spurious-free dynamic range

SFLL Stripped Functionality Logic Locking

SI scan in

SIB segment insertion bit

SMT Satisfiability Modulo Theory

SNN Spiking Neural Network

SNR Signal-to-Noise Ratio

scan out

SoC System-on-Chip

SOTA self-biased operational transconductance amplifier

SRAM Static Random-Access Memory

TAP test access port

TDR test data register

TPM Tamper-Proof Memory

TSMC Taiwan semiconductor manufacturing company

VGLNA Variable Gain Low Noise Amplifier

Vth various threshold voltage

WLAN wireless local area network

# Part I MAIN PART

INTRODUCTION

#### 1.1 VULNERABILITIES IN THE SEMICONDUCTOR SUPPLY CHAIN

#### 1.1.1 Expansion of the Supply Chain

Over the course of the past years, the business model of Integrated Circuits (ICs), which is a key component in Consumer Electronics (CE), has evolved. It shifts from vertical model to horizontal model motivated by the increasing cost of ICs fabrication. In the vertical model, all of the capacity required to construct a working IC and delivering it to the market, including knowledge, design software, manufacturing instruments, integrating capabilities, and testing equipment, is incorporated into the same entity. Firms that utilize the vertical model are known as integrated device manufacturers (IDMs). These IDMs such as Intel, Samsung, and SK Hynix have held the largest market share since the beginning, although this situation steadily changes over time [1], [2].

In the late 1980s and particularly in 1987, the foundation of Taiwan semiconductor manufacturing company (TSMC) paved the way for a new business model, namely the foundry model. The raising of such a model has contributed to the emergence of fabless companies, which are corporations or small startups focused on IC design but lack the ability to fabricate their own ICs. By outsourcing the IC fabrication, fabless companies have been able to reduce their capital requirements by at least tenfold [3]. The cooperation between foundries and fabless companies is referred to as the horizontal model. Utilizing the horizontal model not only reduces risks by eliminating the capital required to construct, maintain, and upgrade the fabrication facility, but it also provides other benefits such as reducing the time span from IC design to mass production. This operational efficiency is achieved by incorporating pre-approved modules into the IC design. All of these advantages have assisted the expansion of fabless companies, e.g., Qualcomm, Broadcom, Nvidia, and Apple, in terms of market share. Over the past ten years, the revenue of fabless companies has more than doubled [1].

Back at the procedure of reusing pre-approved modules, this sparked the creation of the System-on-Chip (SoC). SoC is the integration of conventional functions and special functions required for implementing a complex electronic system on a single silicon substrate. This, in turn, broadens the business model even further to include new models that are suitable for the new companies currently involved in the production of SoCs. These new models can be categorized into different categories such as: (a) Computer-Aided Design (CAD) tool providers: firms that develop specialized software for designing and simulating electronic circuits; (b) Intellectual Property (IP) block providers: firms concerned with designing ICs that perform specific functions and assembling them into IP blocks; (c) Third party IP (3PIP) vendors: platforms used to identify and sell those IP blocks; (d) SoC integrators: specialized firms in constructing complex systems by incorporating several IP blocks into a single chip.

The continuous development of the business model has led to the expansion of the supply chain by introducing new companies. In more detail, the first step in the supply chain is the design stage, in which the chip is designed to perform a specific task. The chip design can be done internally, integrated from outsourced IPs, or a hybrid of the two. In terms of the business model, this stage combines the IP providers and the SoC integrators. Moving to the next stage, the chip is fabricated based on the design layout created in the previous step. This stage is called the fabrication stage and is performed in the foundry. The next actor in the supply chain is the packaging firm, which packages the chip then sends it to the testing facility. At the test facility, a production test bench is used to test the chips, then the chips that pass the test are sold in the market. Finally, the life cycle of a chip will reach an end at some point in time and it will be discarded.

#### 1.1.2 Problems Caused by Malice Actors in the Supply Chain

The horizontal semiconductor business model has added fragility into the semiconductor supply chain. Despite its benefits, the outsourcing of IC fabrication and the distributed design flow involves multiple entities placed around the world and makes the semiconductor industry face several challenging security threats such as hardware Trojan (HT) insertion, reverse engineering (RE), and counterfeiting. Moreover, several side-channel attacks have been demonstrated with the aim of stealing sensitive data. The said threats' applicability and effect strongly depend on the supply chain phase where they are inserted. These threats will be explained in more detail the next subsections.

#### 1.1.2.1 Side-Channel Attacks

Side-channel attacks aim at deducing sensitive data, i.e., secret key, from a chip or a system, through precise measurement and analysis of physical parameters, e.g., power consumption, processing time, or electromagnetic emission. The leaked information from indirect sources or channels relies on the intermediate values generated during the execution of a cryptoalgorithm and are correlated with the applied inputs and the secret key of

the encryption [4]. An adversary can easily extract the encryption key by monitoring and analyzing the leaked information with substantially low-cost tools and in a short period of time. For example, an adversary, i.e., a malicious end-user, can apply an input while monitoring the processing time to get an output and then use the collected data, i.e., the applied inputs and the time taken for the computation, to reveal the secret key [5].

Another category of side-channel attack is based on fault injection (aka fault injection attacks). It aims to mitigate or weaken the implemented cryptographic systems in the chips by injecting malicious faults into the encryption module, which facilitates the leak of sensitive data. Unlike the other types of side-channel attacks that are considered passive attacks, fault injection is an active attack. For instance, an attacker can deploy an attack by applying a shorter clock pulse than normal to induce a clock glitch, making a rapid transient in the supply voltage to induce a power glitch, or exposing the under attack chip to Electromagnetic (EM) signals to disturb the operation of the chip.

These attacks pose a serious threat, especially to chips that integrate cryptographic modules and provide easy access to their physical parameters, e.g., smart cards. Side-channel attacks have proven effective in breaking powerful encryption techniques such as Advanced Encryption Standard (AES) and extracting the secret cipher [4], [6]–[9].

#### 1.1.2.2 Hardware Trojans Attacks

A HT is a malicious modification of the design performed by an attacker within the IC supply chain that is intent to stay hidden and evade detection by the end-user who is the defender in this case. The HT is an undocumented functionality for the end-user and is designed in such a way that once activated it is capable of performing an undesired effect for the end-user. Any HT is in general composed of a trigger, i.e., activation mechanism, and a payload mechanism [10]. The HT may be always-on, in which case strictly speaking there is no trigger mechanism, it may be activated under rare conditions leaving a time bomb into the design, or it may have a well-timed activation controlled by the attacker. The payload mechanism refers to the HT effect on the chip's functionality.

The motivation for inserting a HT includes leaking sensitive information out of the chip, e.g., cipher keys, degrading the performance of the chip, or leading to complete malfunction, e.g. denial-of-service [11], [12]. A HT may be inserted by the CAD tool provider, i.e., by compromising the synthesis or verification scripts, by an IP design team, by a SoC integrator that can manipulate both the 3PIP cores and the test infrastructure comprising the test access and control mechanism and several embedded test instruments, and by a foundry that receives the GDSII file [13]–[17].

There is a multitude of HT designs proposed in the literature that range from simple to very complex attack modes. The simplest HTs are combinational circuits that monitor a set of nodes to generate a trigger on the simultaneous occurrence of rare node conditions and, subsequently, once the trigger is activated, the payload is simply flipping the value of another node. Another category of simple HTs is the sequential HTs which also have a condition-based activation, but they are triggered with a sequence of conditions and not with a specific state or condition like the combinational HTs. More complex HTs include silicon wearout mechanisms [18], hidden side-channels [19], changing dopant polarity in active areas of transistors [14], siphoning charge from victim wires [20], etc.

From the attacker's perspective, the goal is to achieve the desired effect via the use of a stealthy and minimum footprint HT such that it evades pre-silicon prevention and post-silicon detection methods applied by the defender.

#### 1.1.2.3 Reverse Engineering Attacks

The term reverse engineering refers to the derivation of IC/IP proprietary information, i.e., architecture, netlist, layout, etc. It aims at reducing the attacker's technological disadvantage against the "author" of the IC/IP, gathering the necessary information for producing a similar or an identical IC/IP, e.g., a counterfeit, or locating the root-of-trust part of the IC/IP to steal secret information such as cipher keys. The attacker's target is to successfully reverse engineer the under attack IC to a specific abstraction level. This level can vary depending on the objective of the attacker, i.e., pirate the design, insert HTs, or assist counterfeiting attacks. For instance, the physical design level, the gate level, or the Register Transfer Level (RTL) could be the targeted abstraction level if the attacker wants to pirate the design. On the other hand, it is enough to abstract the gate level or the RTL if the attacker's target is to insert HT.

Nowadays, there exist equipment and software tools to successfully reverse engineer any unprotected IC/IP [21]. Reverse engineering involves the following steps: (a) de-packaging of the IC; (b) de-layering the individual layers of the IC using corrosive chemicals; (c) imaging the top-view of each layer using, for example, Scanning Electron Microscopy (SEM); (d) aligning and stitching the images of the different layers; and (e) extracting the netlist from the annotated images using dedicated software tools [22].

This attack can be initiated by any malicious actor in the supply chain, i.e., a SoC integrator, a test facility, a foundry, an end-user, or a recycling facility.

#### 1.1.2.4 Counterfeiting

A counterfeit chip is a forgery or an unauthorized reproduction of an original chip. It includes cloning, recycling, overproducing, remarking, and out-of-specs [23]. A cloned counterfeit is an IC/IP that is being illegally cloned and sold as original. It may aim at copying the entire IC/IP or part from it. Cloning can be performed by an untrusted SoC integrator, foundry, or an adversary, e.g., end-user, via reverse-engineering. A recycled counterfeit is a used and possibly aged IC that is illegally recycled and resold as new. Overproduced ICs are ICs that are produced by an untrusted foundry beyond the number agreed in the contract and are illegitimately sold after in the market. Remarked ICs are ICs whose performances have been changed by a rogue test facility so that these ICs appear as higher-performing ICs. Out-of-spec ICs are ICs that have been proven through testing to be unreliable or have inadequate performance, but a rogue test facility can sell them in the market with forged documentation.

#### 1.1.3 Vulnerabilities' Impact

The threats discussed in Section 1.1.2 have serious implications on the technological value chain (e.g. CAD tool providers, IC/IP providers, original equipment manufacturers, and users), on governments, and on the society as a whole [24]. This thesis focuses on the piracy and HT insertion threats, therefore herein we focus on the posed impacts of these threats.

Piracy has piqued great concern of the community, industry, and government because of its wide impact. It can emerge at any stage in the supply chain, resulting in a loss of company revenue or reputation, unreliability in the chip functionality, or catastrophic consequences, especially when used in critical applications such as healthcare and military applications. The broad spread of IC/IP piracy can be illustrated as an adversary's need to break down knowledge barriers with the IC/IP author to compete effectively in the market or get financial gain. For example, annual losses in the semiconductor industry due to counterfeit ICs/IPs are estimated to be \$169 billion [25]. Despite being widespread, the practice of hardware piracy is highly dependent on the phase at which the threat is deployed in terms of complexity and cost. For example, while it is easy for a rogue foundry to clone a chip, cloning is quite a challenge for a rogue test facility. More specifically, the rogue foundry can benefit from the original blueprint of the chip to clone it, whereas the rogue test facility has to RE the chip to expose its design before cloning it, which dramatically increases the cost and the complexity of cloning. To that end, some threats may be considered less acute than others. But, it is

worth noting that the attack's complexity, and thus the cost, is gradually reduced due to the rapid development in the piracy capacities [21], [22], [26].

HT attacks are also a main preoccupation for society, industry, governments, and military since they pose severe risks with possibly disastrous outcomes. For this reason, HTs have received major attention in the scientific community throughout the last two decades [10], [11]. In the real world, HT hides effectively in the original design, evades testing, activates on a rare condition, as well as has various implications, hence it is hard to accurately gauge its impact. Though, its implications are obvious in different sectors. For example, the Syrian military sector exposed a HT being inserted in the radar system that caused the defense system to fail [27]. In 2012, a HT that allows an adversary to control a Boeing 787's navigation system was detected [28]. In 2018, HTs insertion into data servers resulted in leaking sensitive trade secrets and national security data from more than 30 companies in the United States as reported in [29]. However, the number of HTs reported thus far is significantly lower than the true number, and it is expected that more sophisticated HTs will be exposed in the near future [30].

#### 1.2 HARDWARE SECURITY AND TRUST

Hardware security and trust is a topic that has attracted a lot of interest in recent years. It refers to protecting physical systems, i.e., ICs/IPs, by understanding the threats imposed by different actors through their lifecycle as a first step, then developing effective countermeasures against such threats.

One level of IP protection is the granting of patents. Patent guarantees the author's legal ownership of intellectual property rights and plays an important role in protecting intellectual property rights and copyrights. However, obtaining a patent takes a long time and seems to be useless in countries where intellectual property rights are not strictly applied. It is also not easy to determine and prosecute patent infringement. Usually, patents are important for intellectual property owners, but they can preferably be supplemented by additional levels of security.

Another level of protection is software-based, which can serve the hardware security through one of the following methods:

Language-based design security assessment is an automated process aiming at checking the trustworthiness of an IC/IP design at the RTL. It is conducted while compiling the Hardware Descriptive Language (HDL). At the RTL level, it is critical to inspect the IC/IP design for potential security issues such as vulnerable logic and design flaws. These potential issues, if not detected, will then lead to a multitude of threats, e.g., information leakage and HT insertion [31]–[35].

Cryptography aims at developing suitable algorithmic protocols or techniques for preventing adversaries from accessing sensitive information. It is vital for practicing confidentiality, i.e., defining allowed parties from accessing sensitive information, authenticity, i.e., specifying trustworthy individuals, and integrity, i.e., checking message's contents from being altered during the transmission phase. To that end, different cryptographic algorithms such as symmetric cryptography, asymmetric cryptography, AES, Blowfish cipher, etc., can be used [36]–[38].

However, software-based protections suffer from scalability issues and their defense against different threats is questionable. Furthermore, cryptographic techniques depend on a hardware root of trust, which increases the required area overhead [24], [39].

Finally, hardware-based security includes hardware design-for-security and design-for-trust (DfTr). Hardware design-for-security aims at designing hardware techniques to secure sensitive data in hardware, while hardware DfTr aims at dealing with hardware threats, i.e., counterfeiting and HTs [24], [40], [41]. Hardware-based security offers protection by leveraging fabrication non-idealities to produce unique chip's signature, injecting noise to make all the performed operations even in terms of power consumption and processing time, modifying the design to obfuscate it, or inserting additional components to protect the design, e.g., locking. It provides effective tailored countermeasures for each threat while taking into account the IC/IP design and its targeted application. These countermeasures are discussed next.

#### 1.3 COUNTERMEASURE AGAINST HARDWARE ATTACKS

To be consistent with the objective of this thesis, below we focus on antipiracy countermeasures, i.e., locking, camouflaging, and split-manufacturing, Physical Unclonable Functions (PUFs), and HTs detection and prevention.

#### 1.3.1 Obfuscation

Obfuscation is the process of concealing the functionality or layout of a design by incorporating a locking mechanism, camouflaging the design geometry, or splitting the layout fabrication process. Obfuscation techniques that aim at hiding the design's functionality are known as *Locking*, while they are referred to as *Camouflaging* if they are used to hide the design's layout, and finally *Split manufacturing* aims at dividing

the fabrication process between trusted and untrusted foundries. These techniques are discussed in the following subsections.

#### 1.3.1.1 *Locking*

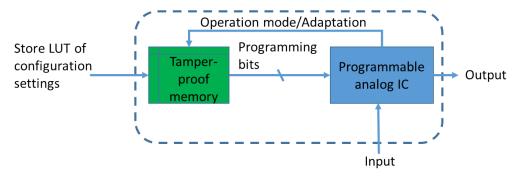

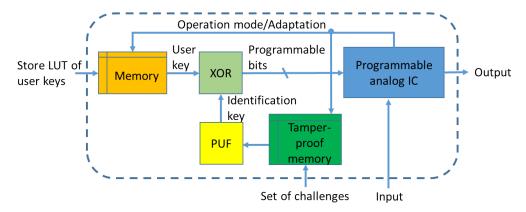

Locking is an end-to-end protection mechanism. It consists of inserting a lock into the design such that unless the valid key is used the functionality breaks [25], [42]-[44]. The key is kept as the IC/IP design house secret. Locking thwarts cloning by the SoC integrator or foundry and overbuilding by the foundry as the blueprint of the IP/IC is useless without knowing the key. It also thwarts cloning via reverse-engineering as the key is stored in a Tamper-Proof Memory (TPM) that cannot be read. It thwarts remarking for digital ICs since structural testing can be equivalently performed on a locked chip using any invalid key and, thereby, chips can be unlocked after testing [45]. Protection against remarking can be achieved for any IC type by remotely activating the chips during testing using asymmetric cryptography [25]. Finally, it thwarts recycling as long as the key is reloaded every time the IC is powered-up. This requires a different key management scheme that makes use of a public user-key and a chip identification-key generated, for example, by an on-chip PUF [46]. The user-key and chip identification-key are XORed to produce the secret key.

#### 1.3.1.2 Camouflaging

Camouflaging addresses the RE threat, and hence counterfeiting threats that rely on RE, by making stealthy alterations in the design using mechanisms at the device and interconnect level, resulting in an extracted netlist that is deceiving for the attacker. These alterations have to defend against RE without affecting the chip's performance or corrupting its outputs. For example, the designer camouflages the developed design by using standard cells that can perform one of several possible functions, whereas he controls the positions of dummy contacts and real contacts to set the cell's actual function. When an adversary attempts to delayer the chip in order to extract its netlist, it is nearly impossible for him to distinguish between dummy contacts and real contacts. As a result of the inability to detect cell functionality, the adversary extracts a nonfunctional netlist [47], [48].

#### 1.3.1.3 Split Manufacturing

Split manufacturing protects only against an untrusted foundry by manufacturing only the lowest layer of the target design at the untrusted foundry and the remaining part at a trusted low-end foundry, i.e., the upper layer. The untrusted foundry is refereed to as front-end-of-

line (FEOL) foundry, while the trusted foundry is refereed to as backend-of-line (BEOL) foundry. As the FEOL foundry receives just a portion from the layout, that usually contains nothing more than the individual transistors and resistors, then it lacks the required data to successfully reverse engineer the layout.

#### 1.3.2 HTs Prevention and Detection

Countermeasures against HT attacks include pre-silicon and post-silicon methods. Pre-silicon methods are used to prevent HTs insertion or make their detection easier, whereas post-silicon methods are used to expose HTs that have already been inserted.

Pre-silicon prevention methods include: (a) functional verification of 3PIP cores [49]; (b) structural analysis of HDL codes [49]; (c) targeted automatic test pattern generation algorithms [50] or simulating the circuit using specific test benches, i.e., performing aging simulations along with over-clocking [51]; (d) searching for unused components during design-time verification and removing them as potentially suspicious [52]; (e) filling in all unused spaces on the layout, which are most likely insertion areas for HTs, with functional filler cells and checking if those have changed [53]; and (f) design obfuscation, for example using locking [54]–[56], camouflaging [47], [57], or split manufacturing [58], aiming at obscuring the IC functionality so as to make it difficult for the attacker to insert the HT.

Post-silicon detection methods include: (a) destructive reverse engineering, which involves de-packaging and de-layering the chip, imaging the chip's layers, and using software to stitch together the prepared images, thereby recovering the layout and netlist, which thereafter can be carefully examined to detect the presence of HTs [22], [59]; (b) optical circuit analysis aiming at measuring optical emissions of the IC and comparing them with a trusted emission image of a "golden" IC [60]; (c) functional testing aiming at exposing the HT by applying test vectors similar to presilicon prevention methods [50]; (d) statistical side-channel fingerprinting aiming at exposing the HT by its effect on parametric measurements, i.e., delay, power, temperature, etc. [17], [61]; and (e) using run-time monitors, i.e., current sensors [62] and thermal sensors [63].

#### 1.3.3 *Physical Unclonable Functions (PUFs)*

A PUF is a circuit that leverages statistical manufacturing variations of circuit parameters to generate a chip-unique signature. When queried with an input, referred to as *challenge*, it generates an output, referred to as *response*, that typically is a bitstring composing a digital key. PUF applications include among others device authentication, secret key gen-

eration, hardware anti-piracy, security in Internet-of-Things (IoT) devices, etc. In device authentication, the PUF is used as a silicon biometric to generate a unique fingerprint or ID per chip [64], [65]. In secret key generation, a PUF is used to generate the key on-the-fly at power-on, thus avoiding explicit key storage [64]. In hardware anti-piracy, the PUF can be used to provide each chip an ID such that it can be traced along its lifetime for anti-counterfeiting purposes [23], [66]. In addition, a PUF can be used in the key management scheme of chip locking techniques [25], [55], [56]. In a resource-constrained smart IoT edge device, a PUF can be used for lightweight low-cost authentication protocols [67], [68].

The PUF concept was originally introduced in [69]–[71] and several silicon PUF implementations have been proposed since then. The most popular PUFs are delay-based PUFs and memory-based PUFs. Delay-based PUFs exploit some race condition that is built-up inside the circuit, while memory-based PUFs exploit the natural tendency of a memory cell towards one of its two states as it will be discussed in more detail in Chapter 2.

No PUF is inherently robust and a percentage of PUF cells may generate unstable bits that should be handled accordingly. Stability boosting techniques include temporal majority voting to stabilize noisy bits, burnin hardening to accelerate aging, masking of "dark" bits that are unstable across varying operating conditions, and error correcting codes (ECCs) circuits [72]–[76]. For this reason, PUFs typically generate an excess number of bits which can be thereafter down-sampled to a fully stable key.

Another categorization of PUFs takes into consideration the number of challenge-response pairs (CRPs) that the PUF can support. A PUF that can support only a small number of CRPs is called a *weak* PUF, while a PUF that can support a very large number of CRPs that cannot be tried out in a reasonable time frame is called a *strong* PUF.

#### 1.4 THE GROWING DEMAND FOR ANALOG DFTR TECHNIQUES

While hardware security and trust aspects have been extensively studied for digital circuits, the space of vulnerabilities and solutions for analog circuits is largely unexplored and little understood as of today [77], [78]. The great dearth of techniques for Analog, Mixed-Signal (AMS) and Radio Frequency (RF) IC/IP countermeasures, the reasons for their lagging behind digital countermeasures, and the importance of broadening the development of such countermeasures can be summarized as follows:

Analog applications are everywhere: Since all elements in nature are analog, e.g., light, sound, and EM signals, every chip must at least have an analog interface for interacting with its environment. Analog circuits act as a link between the analog and the digital regimes. For instance, an AMS interface is needed for receiving the signals and preparing them for any additional digital operations in each communication standard receiver. From a system-level perspective, analog circuits are perhaps nowadays the weakest link in achieving the global security and trust requirements. As a result, the demand for securing analog circuits has been increased.

- Design difficulties: Analog IC design is complex because it has to deal with process variation effects on the chip performance, as well as be robust against fluctuations in temperature, noise, etc. On the other hand, achieving such reliability makes analog ICs very sensitive to design changes or the addition of new components. From another aspect, and in contrast to digital design, there are no mature and reliable enough automated means for designing analog circuits from a high-level design specification, nor automated synthesis software to synthesize these circuits until today. Due to the design complexity and sensitivity besides the lack of automated aid, analog designers are rather reluctant to change the design flows for adding features into the design unrelated to functionality, i.e., design-fortest, design-for-security, etc.

- Analog chips are valuable: The value of an analog chip is extremely

high due to the complexity and challenges that its design presents.

Even for a highly experienced and knowledgeable designer, designing a functionally reliable IC is a challenge because he normally

needs to go through many design cycles and make a lot of modifications in the design to achieve his goal. As their values rise, so

does the need to protect them.

- Lag of technology developments: In general, developments around analog circuits (i.e. CAD tools, migration of designs into more advance technology nodes, methodologies for design-for-test, design-for-yield, design-for-reliability, etc.) lag behind those for their digital counterparts. Hardware security is not an exception. Although solutions in the digital domain have been explored for over a decade now, the solution space for analog has only started being explored in the last 4 years or so, that is, with a delay of almost a decade.

- Vulnerability to piracy: According to collected data on counterfeit incidents, among all component types (i.e. analog, microprocessor, memory, programmable logic, etc.), about 25% of reported incidents concern analog ICs [23]. This is understandable considering the high value of analog chips and their vulnerability to IC/IP piracy. This vulnerability is due to the relatively low number of transistors in analog ICs and their association with distinct layout patterns, which facilitates rogue adversary to RE and counterfeit these valuable designs.

#### 1.5 THESIS CONTRIBUTIONS

The thesis makes the following contributions:

- We propose an anti-piracy security approach for the class of highlyprogrammable analog ICs [79]. The security approach relies on functionality locking by leveraging the inherent programmability and utilizing the configuration settings as secret keys or, equivalently, the programming bits as key-bits. When invalid keys are applied, the circuit is untuned and, as a result, its functionality breaks, i.e., at least one of the performances violates its specification. As long as the calibration algorithm that produces the configuration settings can be concealed, the proposed approach can serve as a countermeasure against all types of counterfeiting, i.e., cloning, overbuilding, remarking, and recycling. An important advantage of the proposed approach is that it is lock-less. It leaves the design intact, there is no change to the design flow, and there are no performance penalties and no area or power overheads due to the lock operation. We demonstrate it on a  $\Sigma\Delta$  Analog-to-Digital Converter (ADC) with high programmability and complex calibration algorithm used in the context of highly-digitized, multi-standard RF receivers.

- We propose a HT attack for analog circuits with its key characteristic being that it cannot be prevented or detected in the analog domain [80]. The HT attack works in the context of Systems-on-Chip comprising both digital and analog IP blocks. The attacker could be either the SoC integrator or the foundry. More specifically, the HT trigger is placed inside a dense digital IP block where it can be effectively hidden, whereas the HT payload is in the form of a digital pattern transported via the test bus or generated within the test bus, reaching the Design-for-Test (DfT) or programmability interface of the victim analog IP with the test bus. The HT payload unexpectedly activates the DfT and sets the victim analog IP into some possibly partial and undocumented test mode or changes the nominal programmability. The HT payload can be designed to result in performance degradation or complete malfunction, i.e., denial of service. We demonstrate this HT attack scenario on two analog IPs, namely a low-dropout (LDO) regulator using simulation and an RF receiver using hardware measurements.

- We propose a novel PUF concept based on a single spiking neuron [81]. The inherent variability of the neuron results in a chip-unique analog spiking pattern that is digitized to produce a chip-unique digital key. A stability booster is also employed based on selfmasking to obtain a fully stable digital key. The PUF is area and

power effective since a single PUF cell is used to produce an arbitrarily sized digital key. We demonstrate PUF quality metrics close to ideal values and argue that the PUF is resilient against various physical attacks. Our results from this preliminary work provide a starting point to address this new concept.

#### 1.6 THESIS STRUCTURE

The thesis is structured as follows: in Chapter 2, we review the prior art in analog hardware security related to piracy and HTs, as well as the prior art on PUFs. In Chapter 3, we present the proposed locking technique for the class of highly-programmable analog ICs. In Chapter 4, we present the HT attack for analog IPs in the context of SoCs. In Chapter 5, we present the design of the neuron-PUF. In Chapter 6, we conclude pointing to future work and perspective in the field of analog hardware security.

#### 2.1 PRIOR ART ON ANALOG OBFUSCATION

## 2.1.1 Analog Locking

As discussed in Chapter 1, locking has piqued the attention of the research community since it can defend against any rogue adversary positioned anywhere in the IC supply chain. The locked, i.e., functionally obfuscated, netlist moves through different stages in the supply chain, that potentially include malicious parties, without the secret key. This guarantees (a) the uselessness of reverse-engineering the design's netlist, and (b) the functionality failing of the counterfeited ICs, e.g., cloned ICs, overproduced ICs, etc. The activation of locked IC is done by loading the activation key into a TPM within the IC [82]–[84].

In contrast to digital designs, it is not favorable to modify analog designs by inserting locking mechanisms such as logic gates and look-up tables (LUTs), as this usually affects the IC's performance. Consequently, this increases the challenges to develop locking techniques for analog ICs.

The prior work on analog hardware security tailored for locking analog circuits can be categorized as follows:

- Locking the biasing circuit

- Locking the calibration module

- Locking the digital section within a mixed-signal circuit

- Locking via emerging technologies

- Compound locking

In the sections that follow, we use these categories to present and discuss previous work on locking analog circuits.

## 2.1.1.1 Locking the Biasing Circuit

Analog circuit performance is very sensitive to changes in biasing conditions, i.e., currents and voltages. In more detail, the analog circuits are designed through two steps: performance design and biasing design. In the first step, the circuit is designed to perform a specific function. During this step, the biasing conditions for the transistors are set to achieve the

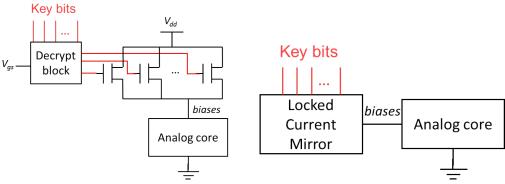

- (a) Biasing locking based on transistor width obfuscation [85].

- (b) Biasing locking based on current mirror locking [86].

- (c) Biasing locking using mesh-based transistor obfuscation [87].

- (d) Locking through neural network-based biasing [88].

Figure 2.1: Existing biasing locking methodologies for analog ICs.

targeted performance. The biasing circuit is then designed to keep the desired operating points for these transistors at a certain level. This is critical for analog circuit functionality and reliability. Another important aspect of the biasing circuit is that it is not part of the analog circuit's core, but rather is connected to it. Based on that, biasing circuits can provide an efficient way for locking analog circuits.

Biasing locking re-designs the biasing circuit so that the secret key can be used to control its parameters and thus its output. Applying a wrong key leads to non-negligible fluctuations in the biasing conditions, which force the circuit to violate one or more of its performances. Using the secret key, on the other hand, causes the circuit to behave as expected. Biasing locking must be designed to have a large enough key size to prevent brute-force attacks while also ensuring that no incorrect keys can drive the analog circuit into or close to its normal performance.

In [85], a transistor that sets the current or voltage bias in a node is obfuscated by replacing it with parallel-connected transistors whose gates are controlled by key-bits as illustrated in Fig. 2.1(a). The key-bits activate transistors whose aggregate width equals the nominal width of the original transistor. However, the proposed technique does not guarantee that only one key can activate the biasing circuit or that the wrong keys will degrade the performance well enough. In [86], it is shown how to redesign a current mirror so as to insert key-bits as illustrated in Fig. 2.1(b). Extra mirroring branches are inserted, where each branch is comprised of the mirroring transistor and possibly several switches that are controlled by the key-bits. The resultant current bias will depend on which branches are switched-on, as well as on the geometry of the mirroring transistor in these branches. They used a Satisfiability Modulo Theory (SMT) solver to overcome the issues in the previous technique. The solver is used to search for the appropriate size for each mirroring transistor so that only the correct key-bits make the circuit to perform well while other keys cannot. In [87], a mesh-based obfuscation of biasing transistors is proposed as illustrated in Fig. 2.1(c). Each transistor in the mesh is of a different size and is controlled by a key-bit. The valid key sets the effective transistor length and width to generate the correct bias. In [88], it is proposed to add on-chip a neural network that is trained to map the secret analog key, which is in the form of analog DC voltages presented as inputs to the neural network, to the correct bias as illustrated in Fig. 2.1(d). For invalid keys, the neural network is trained to give the same erroneous bias.

Biasing locking is a generic methodology applicable to any analog IC and offers an elegant way for inserting a digital key-enabled lock into an analog IC. Although the lock is not inserted into the analog core, biasing circuits are fundamental units for proper operation of analog ICs and their design should be carefully done to meet requirements such as biasing accuracy, temperature stability, bandwidth, input/output compliance voltage, input/output resistance, etc. The above works have not considered the effect of locking on the performance of the biasing circuit.

On the other hand, counter-attacks were proposed recently that break biasing locking allowing the attacker to recover the secret key or to remove the lock by re-synthesizing the biasing circuit [89]–[92].

## 2.1.1.2 Locking the Calibration Module

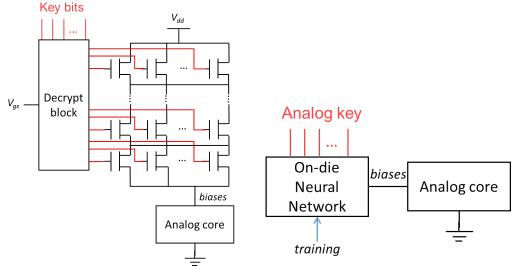

Another category of locking methodologies considers inserting the lock into the on-chip calibration mechanism. In this case, locking acts on the tuning knobs that compensate for process variations and non-idealities. In [93], a calibration loop is considered that uses an ADC to digitize the output of the circuit, followed by a digital optimizer that maps the output

- (a) Logic locking of digital optimizer in on-chip calibration loop [93].

- (b) Locking of the programming range of AFGTs [94].

Figure 2.2: Existing locking via the calibration module for analog ICs.

to appropriate tuning knobs that improve the performance trade-off of the circuit. It is proposed to insert the lock into the digital optimizer using logic locking as shown in Fig. 2.2(a). The used logic locking technique is known as Stripped Functionality Logic Locking (SFLL) [44]. Unless the valid key is provided, the tuning operation is affected.

Although no modifications are needed in the analog part of the IC, which is important for the analog designer, the proposed technique is vulnerable to removal attacks as the locked optimizer module is not part of the circuit's core and can be easily replaced with a non-locked optimizer. Moreover, SFLL can only protect a portion of the feasible input patterns, necessitating a diligence selection of the secured pattern and tuning knobs to ensure the protection of the chip. Logic locking, also, results in some justifiable yet non-negligible areas and power overheads. Finally, the system protection is determined by the strength of the employed logic locking technique, which means that breaking the employed logic locking technique renders the analog circuits unprotected.

In [94], a calibration scheme is considered enabled by Analog Floating-Gate Transistors (AFGTs) as shown in Fig. 2.2(b). A locking principle is proposed where the lock controls the programmability range of the AFGTs. The full tuning range is inhibited unless the AFGTs are first programmed in a certain order and with certain voltages, which are termed waypoints and constitute the secret analog key. This condition is validated by a key checker block. The limitations of this approach are that AFGTs are not standard tuning knobs to enable programmability and that the lock mechanism can be straightforwardly removed by the attacker, thus this approach offers resilience only against overbuilding.

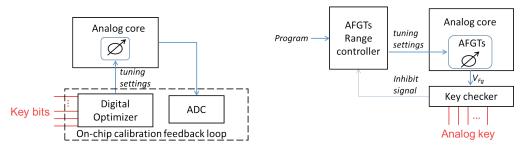

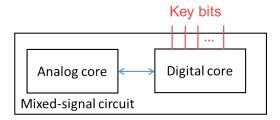

#### 2.1.1.3 Locking the Digital Section within a Mixed-Signal Circuit

The third locking methodology, shown in Fig. 2.3, leverages logic locking of digital sections within a mixed-signal circuit to gain control over the signal-processing flow [55]. They suggested that, by employing a state-of-

Figure 2.3: Locking the digital section within a mixed-signal circuits [55].

Figure 2.4: Biasing locking based on memristor crossbar [96].

the-art logic locking technique, e.g., SFLL, it is feasible to lock the entire system functionality. Using an invalid key, the output of the locked digital sections will be corrupted, which will in turn corrupt the mixed-signal IC performance trade-off in a complex and unpredictable way.

In [95], the authors presented a real showcase of their work in the context of audio applications. They used the technique that they proposed in [55] to lock an audio input interface by locking the underlying decimation filter in the  $\Sigma\Delta$  ADC, and then they showed the effect of using the incorrect key as well as the correct key on the recorded audio.

Similar to [93], logic locking will result in some justifiable yet non-negligible area and power overheads and the system protection is determined by the strength of the employed logic locking. Removing and redesigning the entire digital part is not an easy task and is beyond the assumed capabilities of the attacker.

# 2.1.1.4 Locking via Emerging Technologies