# Optimized and formally verified compilation for a VLIW processor

Cyril Six

### ▶ To cite this version:

Cyril Six. Optimized and formally verified compilation for a VLIW processor. Programming Languages [cs.PL]. Université Grenoble Alpes, 2021. English. NNT: . tel-03326923v1

# $\begin{array}{c} {\rm HAL~Id:~tel\text{-}03326923} \\ {\rm https://hal.science/tel\text{-}03326923v1} \end{array}$

Submitted on 26 Aug 2021 (v1), last revised 10 Dec 2021 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

### **Cyril SIX**

Thèse dirigée par **David MONNIAUX**, Université Grenoble Alpes et codirigée par **Sylvain BOULME**, Grenoble INP

préparée au sein du Laboratoire VERIMAG dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

# Compilation optimisante et formellement prouvée pour un processeur VLIW

# Optimized and formally-verified compilation for a VLIW processor

Thèse soutenue publiquement le **13 juillet 2021**, devant le jury composé de :

### **Monsieur David Monniaux**

DIRECTEUR DE RECHERCHE, Université Grenoble Alpes, CNRS, Grenoble INP, Verimag, Directeur de thèse

#### **Monsieur Adam Chlipala**

MAITRE DE CONFERENCE, MIT, Rapporteur

### **Monsieur Xavier Leroy**

PROFESSEUR, Collège de France, PSL Research University, Rapporteur

### **Madame Laure Gonnord**

MAITRE DE CONFERENCE, Université Lyon1, LIP, Inria, Examinatrice

### **Madame Delphine Demange**

MAITRE DE CONFERENCE, Université Rennes, Inria, CNRS, IRISA, Examinatrice

#### **Monsieur Alain Girault**

DIRECTEUR DE RECHERCHE, Inria, Université Grenoble Alpes, Examinateur

## **Abstract**

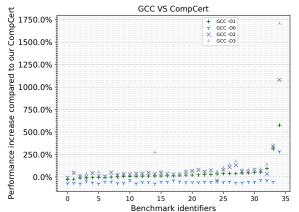

Software programs are used for many critical roles. A bug in those can have a devastating cost, possibly leading to the loss of human lives. Such bugs are usually found at the source level (which can be ruled out with source-level verification methods), but they can also be inserted by the compiler unknowingly. CompCert is the first commercially available optimizing compiler with a formal proof of correctness: compiled programs are proven to behave the same as their source programs. However, because of the challenges involved in proving compiler optimizations, CompCert only has a limited number of them. As such, CompCert usually generates low-performance code compared to classical compilers such as GCC. While this may not significantly impact out-of-order architectures such as x86, on in-order architectures, particularly on VLIW processors, the slowness is significant (code running half as fast as GCC -O2). On VLIW processors, the intra-level parallelism is explicit and specified in the assembly code through "bundles" of instructions: the compiler must bundlize instructions to achieve good performance.

In this thesis, we identify, investigate, implement and formally verify several classical optimizations missing in CompCert. We start by introducing a formal model for VLIW bundles executing on an interlocked core and generate those bundles through a postpass (after register allocation) scheduling. Then, we introduce a prepass (before register allocation) superblock scheduling, implementing static branch prediction and tail-duplication along the way. Finally, we further increase the performance of our generated code by implementing loop unrolling, loop rotation and loop peeling – the latter being used for Loop-Invariant Code Motion. These transformations are verified by translation validation, some of them with hash-consing to achieve reasonable compilation time.

We evaluate each introduced optimization on benchmarks, including Polybench and TACleBench, on the KV3 VLIW core, ARM Cortex A53, and RISC-V "Rocket" core. Thanks to this work, our version of CompCert is now only 16% slower (respectively 12% slower and 30% slower) than GCC -O2 on the KV3 (respectively ARM and RISC-V), instead of 50% (respectively 38% and 45%).

Keywords: Embedded, Optimization, Formal Verification, VLIW, Compilation

## Résumé

On utilise des logiciels pour différents rôles, parfois critiques. La présence d'un bogue dans un logiciel peut avoir un coût dévastateur, pouvant aller jusqu'à la perte de vies humaines dans les cas les plus extrêmes. Les bogues viennent en général du code source (ceux-là peuvent être détectés par des méthodes de vérification formelle sur le langage source), mais ils peuvent être également générés par le compilateur. CompCert est le premier compilateur optimisant commercialisé comportant une preuve formelle de correction : il est formellement prouvé que les programmes compilés avec cet outil ont le même comportement que leurs programmes sources originels. Cependant, comme prouver les optimisations d'un compilateur relève d'un défi considérable, CompCert n'en a qu'un nombre limité. Ainsi, en général CompCert génère du code moins performant comparé à d'autres compilateurs classiques tels que GCC. Bien que cela n'impacte peu les architectures à exécution dans le désordre telles que x86, sur des architectures à exécution dans l'ordre, et en particulier sur des processeurs VLIW, le ralentissement est important (le code résultant est deux fois plus lent que GCC -O2). Sur un processeur VLIW, le parallélisme d'instructions est explicite et spécifié dans le code assembleur par des bundles (paquets) d'instructions : le compilateur doit paquétiser les instructions pour obtenir une bonne performance.

Le but de cette thèse est d'identifier, d'enquêter, d'implémenter et de vérifier formellement plusieurs optimisations classiques manquantes dans CompCert. Tout d'abord, j'introduis un model formel d'exécution de *bundles* VLIW sur processeur à pipeline imbriqué. Nous génèrons ces *bundles* à partir d'un réordonnancement en *postpass* (après allocation de registres). Ensuite, j'introduis un réordonnancement de superblocks en *prepass* (avant allocation de registres). Ce travail implique aussi l'introduction d'une prédiction statique de branchements, et une duplication de queue. Enfin, pour continuer d'augmenter la performance du code généré, j'introduis du déroulage, rotation, et pelage de boucles – ce dernier étant utilisé dans du déplacement d'invariants de boucles. Ces transformations sont vérifiées par validation de translation, et certaines utilisent du partage maximal afin d'obtenir des temps de compilation raisonnables.

Nous avons évalué chacune de ces optimisations sur des tests de performance, dont Polybench et TACLeBench, sur le coeur VLIW KV3, l'ARM Cortex A53, et le coeur RISC-V "Rocket". Grâce à nos travaux, notre version de CompCert est maintenant seulement 16% plus lente (respectivement 12% et 30% plus lente) que GCC -O2 sur KV3 (respectivement ARM et RISC-V), au lieu de 50% (respectivement 38% et 45%).

Mots-clefs: Embarqué, Optimisations, Vérification Formelle, VLIW, Compilation

# Acknowledgements

I deeply thank Adam Chlipala and Xavier Leroy for their detailed and insightful reviews. I also thank Laure Gonnord, Delphine Demange and Alain Girault for taking part in this thesis jury. It is an honor for me.

I started this thesis without any prior notion of formal proofs or functional programming and barely any practical experience in compilers. This adventure was quite interesting (but very rewarding), to say the least. I was glad to have Sylvain Boulmé by my side for helping me navigate through the jungle of formal proof engineering in Coq and formal concepts in general. I have learned a lot from him and his teachings; his deep knowledge of Coq and proof methods has been invaluable. Complementary to Sylvain, David Monniaux was also very helpful both for general thesis direction and for having excellent ideas that, more often than not, led to promising results. Last but not least, I want to thank Benoît Dupont de Dinechin for ensuring I have an excellent environment at Kalray for working on my thesis and for his helpful insights on optimizing compilers.

I want to thank the persons of the VERIMAG laboratory for providing me with a great work environment. I also want to thank the doctoral school EDMSTII for having been very understanding and amenable throughout the thesis. In particular, they participated in the opportunity for me to attend the DeepSpec Summer School of 2018 (DSSS'18) at the Princeton University. Thanks to their most excellent program and teachers, my knowledge level of Coq and formal proofs got boosted through the roof.

I want to thank two additional persons: Florent-Bouchez Tichadou and Fabrice Rastello. I believe that most of life is the result of lucky opportunities; these two persons introduced me to the CORSE research team and gave me the will to pave my own way into optimizing compilers studies. I sincerely thank both of them. I also want to thank my wonderful teacher Christophe Brouillard, who showed me the wonderful world of mathematics and gave me the first glimpse of what research looks like. Finally, I thank Duco Van Amstel for having such a pleasant and memorable discussion, after which I was sure to head towards doctoral studies!

I thank my lab and company student mates Amaury, Arthur, Bai, Clément, Maëva, Matheus, Rémy, Valentin, Vincent, Yanis. Many meals, funny discussions, and horoscopes were shared. I also thank my former lab (CORSE) student mates for all the interesting discussions about compilation, performance, or any other subject. Among them, I'm thinking of Antoine, Diogo, Emmanuelle, Fabian, Imma, Luis, Nicolas, Thomas; but there are others!

Three years (and a half) is a lot of time, during which I met many people who inspired me on a personal level and have encouraged me throughout this adventure. I want to thank the Rainbow Swingers chorus, particularly Andrea, Antoine (x2), Benjamin, Cécile, Charlotte,

Chloé, Clémentine, Cyrielle, Geoffroy, Juliette, Kevin, Marion, Maxime, Maximin, Raphaël, Solène, Sophia, Véronique (and many others!) with who I had such a wonderful time. Lastly, I want to thank my other wonderful friends who have inspired me on many occasions: Alex, Aurélien, Bastien, Clémentine, Corentin, Freddy, Guillaume, Hannah, Inès, Jean, Joseph, Julien, Laurie, Lucie, Marine, Maxime, Nicolas, Olga, Pierre, Virginie.

Lastly, I want to thank the three persons that are the most important to me.

My grandmother has always adored me and has been ever-loving since I was born.

My father taught me to always keep working for my goals and never give up.

My mother encouraged me to follow my dreams, whatever happens.

These persons have always been there to support me throughout my whole life.

Thank you immensely for being there and believing in me!

## Remerciements

Je remercie profondément Adam Chlipala et Xavier Leroy qui ont pris le temps de lire cette thèse en tant que rapporteurs : leurs remarques détaillées ont été extrêmement utiles. Je remercie également Laure Gonnord, Delphine Demange et Alain Girault pour faire parti de ce jury. C'est un immense honneur pour moi.

Le démarrage de cette thèse fut une épopée. Je n'avais pratiquement aucune connaissance en matière de preuve formelle, programmation fonctionnelle, ou même de l'expérience pratique en compilation. Cette thèse a été une aventure fructueuse et formatrice, notamment grâce à mon encadrant Sylvain Boulmé. Sylvain était mon guide dans la jungle des preuves formelles en Coq et des formalismes en général. J'ai énormément appris de lui, autant de par sa personne que de par ses enseignements; sa connaissance de Coq et des méthodes formelles a été un atout indispensable pour ma thèse. Mon directeur de thèse, David Monniaux, a également été formidable, autant pour la direction de la thèse que pour ses idées qui ont quasiment toujours mené à des résultats prometteurs. Enfin, je remercie Benoît Dupont de Dinechin pour m'avoir instauré un cadre de travail idyllique à Kalray, en plus d'avoir été une référence en matière de compilation optimisante.

J'ai passé trois super années de thèse au sein de VERIMAG, et je remercie toutes les personnes de ce laboratoire pour cela. Je remercie également l'école doctorale EDMSTII : ça a toujours été un plaisir d'avoir affaire à eux sur le côté administratif, et ils m'ont donné l'opportunité de participer à des écoles d'été, en particulier l'école d'été DeepSpec Summer School 2018 (DSSS'18) à l'université de Princeton. Les cours exemplaires de DSSS'18 m'ont permis de relever de façon conséquente mon niveau de connaissances en preuves formelles, ce qui s'est révélé être un atout considérable pour ma thèse.

Je tiens également à remercier Florent-Bouchez Tichadou et Fabrice Rastello. Si je devais résumer ma vie, je dirais que c'est tout d'abord des rencontres — ces deux personnes en particulier m'ont introduit au sujet de la recherche en compilation, et m'ont donné l'envie de poursuivre dans cette voie! Je tiens également à remercier mon professeur de prépa Christophe Brouillard; il m'a montré la beauté des mathématiques, et m'a permis d'avoir un premier aperçu de la recherche. Enfin, je remercie Duco Van Amstel pour une discussion autour d'un verre qui a scellé mon envie de poursuivre en doctorat.

Je remercie mes camarades du laboratoire ou de Kalray : Amaury, Arthur, Bai, Clément, Maëva, Matheus, Rémy, Valentin, Vincent, Yanis. Avec eux j'ai passé beaucoup de repas partagés, de discussions intéressantes, et même d'horoscopes amusants. Je remercie aussi les collègues de mon ancienne équipe (CORSE) pour les discussions orientés performance, compilation, ou juste

tout autre sujet. Je pense à Antoine, Diogo, Emmanuelle, Fabian, Imma, Luis, Nicolas, Thomas; mais il y en a d'autres!

Trois ans (et un petit demi) c'est une sacré durée. J'ai eu l'occasion de rencontrer beaucoup d'autres personnes qui m'ont encouragé tout au long de ma thèse, et qui ont été source d'inspiration sur un plan personnel. Je remercie les personnes de la chorale des Rainbow Swingers, en particulier Andrea, Antoine (x2), Benjamin, Cécile, Charlotte, Chloé, Clémentine, Cyrielle, Geoffroy, Juliette, Kevin, Marion, Maxime, Maximin, Raphaël, Solène, Sophia, Véronique (et beaucoup d'autres!) avec qui j'ai passé des moments inoubliables. Je remercie également tous mes autres amis proches et adorables: Alex, Aurélien, Bastien, Clémentine, Corentin, Freddy, Guillaume, Hannah, Inès, Jean, Joseph, Julien, Laurie, Lucie, Marine, Martin, Maxime, Nicolas, Olga, Pierre, Virginie. Cela a été un réel plaisir de partager du temps avec vous tout au long de ma thèse!

Enfin, je veux remercier trois personnes qui ont été là tout au long de ma vie, et ont toujours cru en moi.

Mamie, tu as toujours été très aimante et une grande confidente depuis que je suis né.

Papa, tu m'as appris à ne jamais abandonner et à toujours viser plus haut.

Maman, tu as toujours été là pour m'encourager dans ma vie peu importe les situations.

Vous avez toujours été là pour me soutenir dans ma vie, et je suis fier de vous avoir comme parents et grand-parent.

# Contents

| Co | Contents     |                                                |                                                                       |    |  |  |  |

|----|--------------|------------------------------------------------|-----------------------------------------------------------------------|----|--|--|--|

| I  | Background   |                                                |                                                                       |    |  |  |  |

| 1  | Introduction |                                                |                                                                       |    |  |  |  |

|    | 1.1          | Gener                                          | al motives                                                            | 3  |  |  |  |

|    |              | 1.1.1                                          | Software Verification                                                 | 3  |  |  |  |

|    |              | 1.1.2                                          | Compilation                                                           | 4  |  |  |  |

|    |              | 1.1.3                                          | The need for formally verified compilation                            | 5  |  |  |  |

|    |              | 1.1.4                                          | Verifying software with Coq                                           | 6  |  |  |  |

|    |              | 1.1.5                                          | VLIW processors in the context of critical applications               | 7  |  |  |  |

|    | 1.2          | The K                                          | alray KV3 architecture                                                | 9  |  |  |  |

|    | 1.3          | The C                                          | OMPCERT formally-verified compiler as of today                        | 11 |  |  |  |

|    |              | 1.3.1                                          | Overview of CompCert                                                  | 11 |  |  |  |

|    |              | 1.3.2                                          | CompCert 's framework for proving transformation passes correctness . | 13 |  |  |  |

|    | 1.4          | Motiv                                          | ations of this thesis and contributions                               | 15 |  |  |  |

| 2  | Rela         | ated W                                         | ork                                                                   | 19 |  |  |  |

|    | 2.1          | 2.1 Compiler optimizations for VLIW processors |                                                                       |    |  |  |  |

|    |              | 2.1.1                                          | Instruction scheduling                                                | 19 |  |  |  |

|    |              | 2.1.2                                          | Loop transformations                                                  | 20 |  |  |  |

|    |              | 2.1.3                                          | Other optimizations                                                   | 21 |  |  |  |

|    | 2.2          | Forma                                          | ally proven compiler transformations                                  | 22 |  |  |  |

|    |              | 2.2.1                                          | Advanced compiler optimizations in CompCert                           | 22 |  |  |  |

|    |              | 2.2.2                                          | Other related work                                                    | 24 |  |  |  |

| II | Fo           | rmally                                         | y Verified Optimizations                                              | 25 |  |  |  |

| 3  | For          | mal Ve                                         | rification of Basic-Block Scheduling at Asm level                     | 27 |  |  |  |

|    | 3 1          | ∆sm\/                                          | I IW: semantics for a VI IW assembly language                         | 30 |  |  |  |

|   |     | 3.1.1                                                                                                       | Overview of CompCert's Asm IR                              | 30                                                                |

|---|-----|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------|

|   |     | 3.1.2                                                                                                       | Syntax of Bundles & Basic Blocks                           | 31                                                                |

|   |     | 3.1.3                                                                                                       | Parallel Semantics of AsmVLIW                              | 32                                                                |

|   |     | 3.1.4                                                                                                       | Sequential Semantics in Asmblock                           | 34                                                                |

|   | 3.2 | Retriev                                                                                                     | ving the basic block structure with Machblock              | 35                                                                |

|   |     | 3.2.1                                                                                                       | The Mach IR of CompCert                                    | 35                                                                |

|   |     | 3.2.2                                                                                                       | Necessity of Constructing Basic Blocks at the Mach Level   | 37                                                                |

|   |     | 3.2.3                                                                                                       | Machblock: generating basic blocks from Mach               | 37                                                                |

|   | 3.3 | Asmbl                                                                                                       | ock: adapting the Mach to Asm translation for basic blocks | 38                                                                |

|   |     | 3.3.1                                                                                                       | Translating and proving Mach code to Asm                   | 39                                                                |

|   |     | 3.3.2                                                                                                       | Translating Machblock to Asmblock                          | 41                                                                |

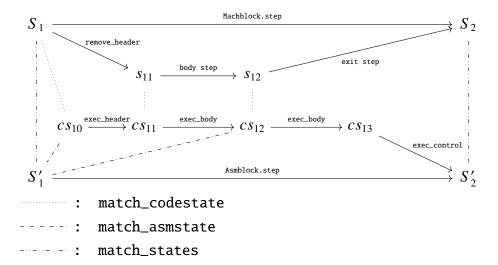

|   |     | 3.3.3                                                                                                       | Proof of Forward Simulation                                | 46                                                                |

|   | 3.4 | Forma                                                                                                       | l verification of the basic block postpass scheduling      | 51                                                                |

|   |     | 3.4.1                                                                                                       | AbstractBasicBlock IR                                      | 53                                                                |

|   |     | 3.4.2                                                                                                       | Parallelizability Checker                                  | 54                                                                |

|   |     | 3.4.3                                                                                                       | Verifying Intrablock Reordering                            | 55                                                                |

|   |     | 3.4.4                                                                                                       | Generic and Verified Hash-Consing                          | 57                                                                |

|   |     | 3.4.5                                                                                                       | Peephole Optimization                                      | 58                                                                |

|   |     | 3.4.6                                                                                                       | Atomic Sequences of Assignments in AbstractBasicBlock      | 59                                                                |

| 4 | Gen | eral Co                                                                                                     | oncepts of Superblock Scheduling                           | 61                                                                |

|   | 4.1 | Guidir                                                                                                      | ng trace selection with branch prediction                  | 62                                                                |

|   |     | 4.1.1                                                                                                       | What we expect out of static branch prediction             | 63                                                                |

|   |     |                                                                                                             | Storing the prediction                                     | 65                                                                |

|   |     | 4.1.2                                                                                                       | Storing the prediction                                     | 05                                                                |

|   |     | 4.1.2<br>4.1.3                                                                                              | Acquiring prediction information                           | 66                                                                |

|   |     |                                                                                                             | Acquiring prediction information                           |                                                                   |

|   | 4.2 | 4.1.3<br>4.1.4                                                                                              |                                                            | 66                                                                |

|   | 4.2 | 4.1.3<br>4.1.4                                                                                              | Acquiring prediction information                           | 66<br>68                                                          |

|   | 4.2 | 4.1.3<br>4.1.4<br>Supert                                                                                    | Acquiring prediction information                           | 66<br>68<br>70                                                    |

|   | 4.2 | 4.1.3<br>4.1.4<br>Superb<br>4.2.1<br>4.2.2                                                                  | Acquiring prediction information                           | 66<br>68<br>70<br>73                                              |

|   |     | 4.1.3<br>4.1.4<br>Superb<br>4.2.1<br>4.2.2                                                                  | Acquiring prediction information                           | 66<br>68<br>70<br>73<br>73                                        |

|   |     | 4.1.3<br>4.1.4<br>Superb<br>4.2.1<br>4.2.2<br>Superb                                                        | Acquiring prediction information                           | 66<br>68<br>70<br>73<br>73<br>75                                  |

|   |     | 4.1.3<br>4.1.4<br>Superb<br>4.2.1<br>4.2.2<br>Superb<br>4.3.1                                               | Acquiring prediction information                           | 66<br>68<br>70<br>73<br>73<br>75<br>77                            |

|   |     | 4.1.3<br>4.1.4<br>Supert<br>4.2.1<br>4.2.2<br>Supert<br>4.3.1<br>4.3.2<br>4.3.3                             | Acquiring prediction information                           | 66<br>68<br>70<br>73<br>73<br>75<br>77                            |

|   | 4.3 | 4.1.3<br>4.1.4<br>Supert<br>4.2.1<br>4.2.2<br>Supert<br>4.3.1<br>4.3.2<br>4.3.3                             | Acquiring prediction information                           | 66<br>68<br>70<br>73<br>73<br>75<br>77<br>79<br>80                |

|   | 4.3 | 4.1.3<br>4.1.4<br>Superb<br>4.2.1<br>4.2.2<br>Superb<br>4.3.1<br>4.3.2<br>4.3.3<br>Superb                   | Acquiring prediction information                           | 666<br>688<br>700<br>733<br>755<br>777<br>799<br>800<br>811       |

| 5 | 4.3 | 4.1.3<br>4.1.4<br>Superb<br>4.2.1<br>4.2.2<br>Superb<br>4.3.1<br>4.3.2<br>4.3.3<br>Superb<br>4.4.1<br>4.4.2 | Acquiring prediction information                           | 666<br>688<br>700<br>733<br>755<br>777<br>79<br>800<br>811<br>822 |

|   |      | 5.1.1    | Overview of RTL                                                       | 86  |

|---|------|----------|-----------------------------------------------------------------------|-----|

|   |      | 5.1.2    | Modeling speculative loads in RTL                                     | 89  |

|   |      | 5.1.3    | Modeling branch prediction                                            | 91  |

|   | 5.2  | Repres   | senting superblocks as execution paths in RTLpath                     | 92  |

|   |      | 5.2.1    | RTLpath syntax and informal semantics                                 | 93  |

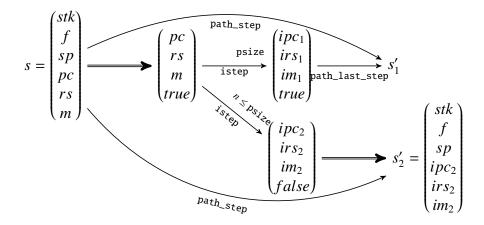

|   |      | 5.2.2    | RTLpath formal semantics                                              | 96  |

|   |      | 5.2.3    | Bisimulation between RTLpath and RTL semantics                        | 98  |

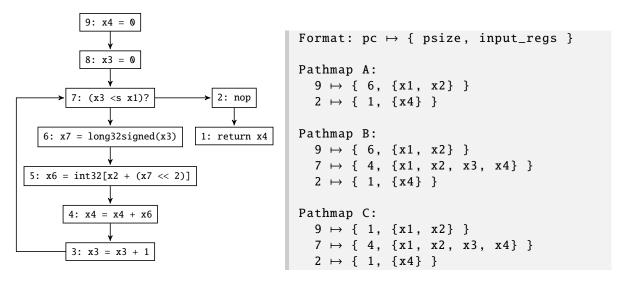

|   | 5.3  | Genera   | ating RTLpath paths from RTL                                          | 101 |

|   |      | 5.3.1    | RTLpath generation oracle                                             | 103 |

|   |      | 5.3.2    | Pathmap verifiers                                                     | 107 |

|   |      | 5.3.3    | RTLpath state equality modulo liveness                                | 109 |

| 6 | Fori | nal Vei  | rification of Code Duplication Transformations                        | 111 |

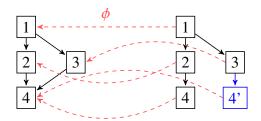

|   | 6.1  | Proof    | of correction through a forward simulation                            | 112 |

|   | 6.2  | Verifie  | r implementation                                                      | 114 |

|   | 6.3  | Modul    | e system                                                              | 114 |

|   | 6.4  | Modifi   | cations to support branch swapping                                    | 115 |

| 7 | Fori | nal Vei  | rification of Superblock Scheduling                                   | 117 |

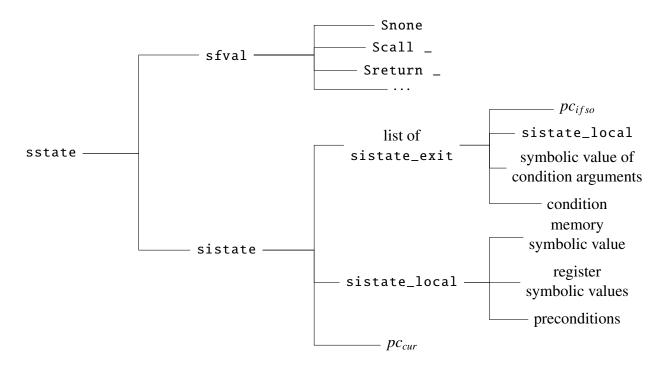

|   | 7.1  | Abstra   | ct Symbolic Execution for Superblocks                                 | 119 |

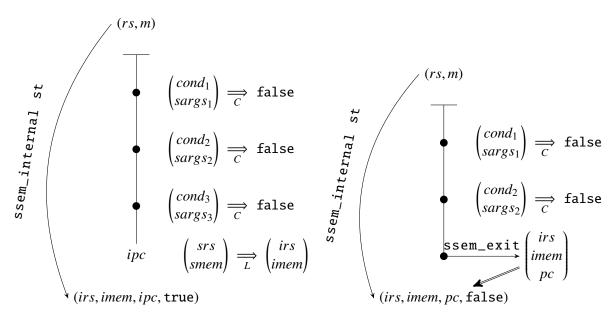

|   |      | 7.1.1    | Abstract symbolic states and execution semantics                      | 121 |

|   |      | 7.1.2    | Superblock symbolic execution                                         | 129 |

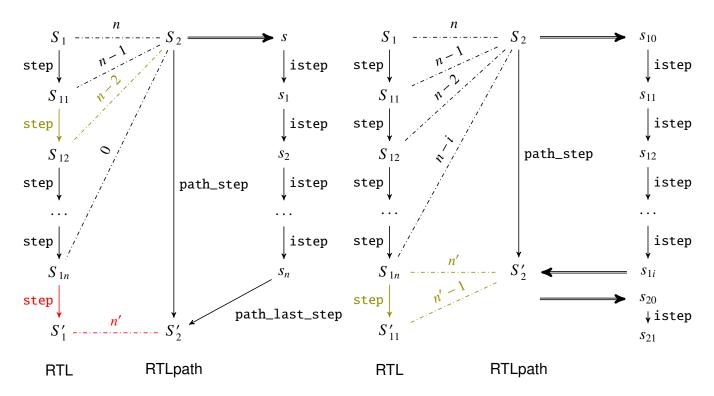

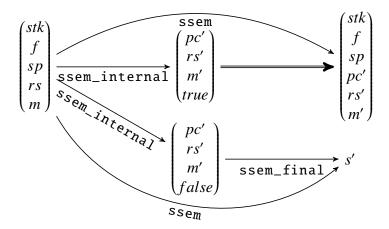

|   |      | 7.1.3    | Bisimulation between RTLpath and symbolic execution semantics         | 130 |

|   | 7.2  | Provin   | g Lockstep Simulation of Scheduling from Sufficient Conditions on Ab- |     |

|   |      | stract S | Symbolic Executions                                                   | 134 |

|   |      | 7.2.1    | Simulation of superblocks                                             | 134 |

|   |      | 7.2.2    | Simulation Test Specification and Superblock Scheduling Lockstep Sim- |     |

|   |      |          | ulation                                                               | 140 |

|   | 7.3  | Refine   | d Simulation Test with Hash-Consing                                   | 143 |

|   |      | 7.3.1    | Refined Symbolic States and Refinement Relations                      | 144 |

|   |      | 7.3.2    | Simulation test specifications and implementation                     | 150 |

|   |      | 7.3.3    | Canonization of Refined Symbolic Values                               | 155 |

| Ш | Ex   | perim    | ents 1                                                                | 159 |

| 8 | Perf | Orman    | ce Tuning of Superblock Formation, Selection, Linearization           | 161 |

| J | 8.1  |          | selection and tail-duplication                                        | 161 |

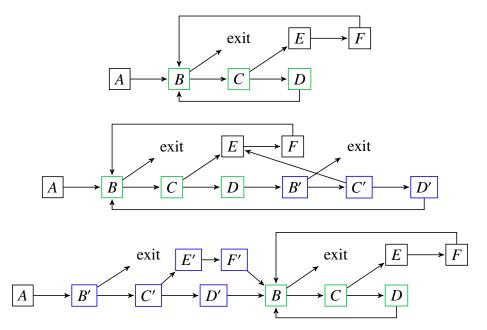

|   | 0.1  | 8.1.1    | Trace partitioning                                                    | 163 |

|   |      |          | Tail-duplication                                                      | 165 |

|   |      | U. I. ∠  | Tall Qui/IIVallVII                                                    | 111 |

|    | 8.2  | Loop u   | unrolling, peeling and rotation                                            | 168   |

|----|------|----------|----------------------------------------------------------------------------|-------|

|    |      | 8.2.1    | Innermost loop detection                                                   | 170   |

|    |      | 8.2.2    | Loop unrolling                                                             | 171   |

|    |      | 8.2.3    | Loop rotation                                                              | 172   |

|    | 8.3  | Adapti   | ng the Linearize oracle for superblocks                                    | 173   |

|    |      | 8.3.1    | Original Linearize heuristics from CompCert                                | 175   |

|    |      | 8.3.2    | Modifications to the heuristics for superblocks                            | 178   |

|    | 8.4  | Static 1 | branch prediction                                                          | 179   |

|    |      | 8.4.1    | Implementing Branch Prediction for Free                                    | 179   |

|    |      | 8.4.2    | A new heuristic for predicting branches inside loops                       | 180   |

| 9  | Imp  | lement   | ing the Scheduling Oracles                                                 | 183   |

|    | 9.1  | Postpa   | ss Scheduling Oracle                                                       | 184   |

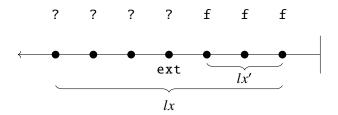

|    |      | 9.1.1    | Postpass frontend                                                          | 185   |

|    |      | 9.1.2    | Postpass backend                                                           | 188   |

|    | 9.2  | Prepas   | s Scheduling Oracle                                                        | 189   |

|    |      | 9.2.1    | Additional dependencies for conditional branches                           | 190   |

|    |      | 9.2.2    | Prepass scheduling algorithms                                              | 191   |

| 10 | Expe | erimen   | tations                                                                    | 195   |

|    | 10.1 | Experi   | mental setup                                                               | 195   |

|    |      | 10.1.1   | Measured processors                                                        | 196   |

|    |      | 10.1.2   | Measuring methods                                                          | 197   |

|    |      | 10.1.3   | Benchmarks used                                                            | 197   |

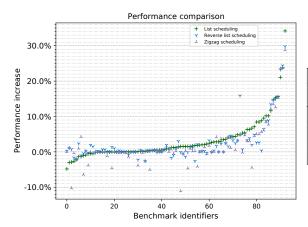

|    | 10.2 | Impact   | t of postpass scheduling                                                   | 199   |

|    |      | 10.2.1   | Performance                                                                | 199   |

|    |      | 10.2.2   | Compilation times of postpass scheduling on KV3                            | 201   |

|    | 10.3 | Impact   | t of superblock scheduling related optimizations                           | 202   |

|    |      | 10.3.1   | Evaluation of our static branch prediction                                 | 202   |

|    |      | 10.3.2   | Evaluation of our superblock linearizer                                    | 204   |

|    |      | 10.3.3   | Evaluation of loop unrolling, loop rotation and tail-duplication threshold | s 205 |

|    |      | 10.3.4   | Performance impact of each added optimization                              | 208   |

|    |      | 10.3.5   | Evaluation of the different prepass scheduling strategies                  | 209   |

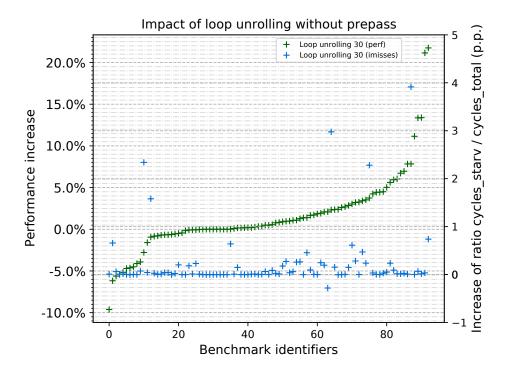

|    |      | 10.3.6   | Gains of loop unrolling without prepass scheduling                         | 210   |

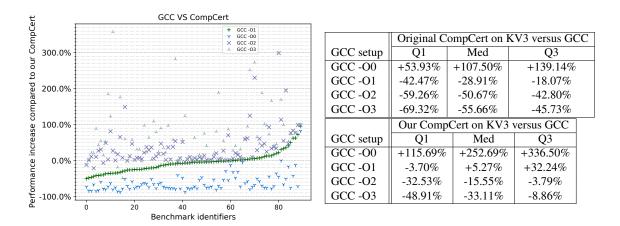

|    | 10.4 | СомРС    | CERT VS GCC in our current iteration                                       | 212   |

|    |      | 10.4.1   | COMPCERT VS GCC on the KV3 architecture                                    | 212   |

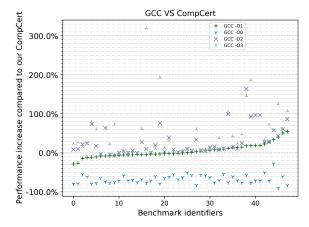

|    |      | 10.4.2   | COMPCERT VS GCC on AArch64 and RiscV architecture                          | 217   |

| 11 | Con  | clusion  | 1                                                                          | 219   |

|    | 111  | Summ     | 0777                                                                       | 210   |

|    | 11.2 Reflexions and Future Work                    | 220        |

|----|----------------------------------------------------|------------|

| A  | Non-exhaustive instruction listing of the KV3 core | <b>A</b> 1 |

| Bi | ibliography                                        |            |

# Part I

Background

# Introduction

## 1.1 General motives

### 1.1.1 Software Verification

In the past decades, our reliance on software to conduct repetitive and sensitive tasks has grown tremendously. Whether it be to fly a space rocket, manage bank deposits, or just ordering your next meal, software programs are now almost everywhere.

Due to their human manufacturing, software programs are prone to errors. A wrong design, a miscommunication within the development team, or just a faulty line inserted on a Friday afternoon: it suffices of a tiny error, a tiny misconception, to make a software program crash – or worst, behave erratically. These errors (called "bugs" <sup>1</sup>) may have varying effects based on the nature of the application.

If there is a bug on your meal ordering application, you could probably have the wrong meal ordered or have to order it a second time because the application crashed. A bug in your message delivery service and your message might not get sent at all. These represent classes of applications that are non-critical: a bug in these might make people lose time, or in general, have minor inconveniences.

Some other applications can have more nasty repercussions if there is a bug in them. In 2013, software defects were found in the United Kingdom's Post Office computer system: people were wrongly accused of stealing money, some of them even going to jail as a result, even though the actual cause was a false accounting within the software [68].

Software bugs in aerospace applications can have dire consequences. In 1996, the Ariane 5 space rocket physically exploded on its maiden flight because of miscasting a 64-bits floating-point variable into a 16-bits integer, causing the propulsion system to flip the rocket [59]. In 2009, four unfortunate passengers of an ES350 Toyota car died after their car's accelerator pedal got stuck and the brakes did not apply enough pressure to stop the car. Several investigations were led in the early 2010s to investigate this incident among others; software bugs were found to be the

<sup>&</sup>lt;sup>1</sup>The term "bug" became popular after an unfortunate moth caused a hardware error on the Mark II computer, though it has been part of the engineering jargon since the 1870s [60].

likely cause of this incident [45]. In 2021, a software bug from Orange made all urgency calls unreachable for several hours in France, resulting in at least five deaths [35].

The prevention and detection of software bugs have been an ongoing area of research for the past decades. Ensuring that critical software is bug-free (or at least free of any bug that could cause harm) may involve various techniques. Some involve executing the program to look for faulty behaviors, either through extensive testing (Parnas et al. [70]; Parnas et al. [69]) or runtime verification (Leucker and Schallhart [53]; Bartocci et al. [7]). Others rely on deriving properties based on the source code itself: this can be done through static analysis (Blanchet et al. [12]) or formal verification (Yoo et al. [101]).

## 1.1.2 Compilation

The execution of software programs on processors requires them to be encoded in binary machine code. Traditionally, this machine code is obtained by translating a textual representation called *assembly language*. Each separate code module, written in assembly, is translated into *object machine code* through an *assembler*. Then, a *linker* is used for gathering all objects code into one binary machine code, ready to be executed on a given machine.

One caveat of assembly language is that it is too close to the machine: it does not provide enough abstraction for developing software. As such, producing software directly in machine code is inefficient and error-prone.

To leverage this issue, high-level languages were invented to ease software development. Among them, the C language became one of the most popular for embedded systems primarily because of its portability (the same C code can be compiled on many different processor architectures) and its closeness to actual machine code, making it possible to fine-tune C code to get similar performance than with concrete machine code.

The process of translating C code to machine code is called *compilation* and is done through a *compiler*. The compilation process is usually split into several passes: a *frontend* that transforms C code into a given *intermediate representation* (*IR*) of the compiler, and finally a *backend* that gradually transforms this IR into an assembly code suitable for the target machine. Once this is done, the *assembler* and *linker* can then generate the final machine code.

During the compilation process, the compiler can optimize the code: performing transformations that aims to have a faster machine code, a smaller machine code, or sometimes both.

## 1.1.3 The need for formally verified compilation

The compiler, assembler and linker are all pieces of software: there may be bugs in those. In particular, compilers are considered one of the most complex pieces of software; they usually involve intricate transformation passes, especially when optimizing the code.

As such, properties that were proved at a source level might not be valid anymore if the compiler introduced a bug. Compilers are usually thoroughly tested to trim out any major bug. However, it is not physically possible to test all the possible cases because there are infinitely many of them: even with thorough testing, there might still be bugs hidden in corners.

While this is of little to no concern for most applications, it is concerning for critical applications. The probability of having a major accident happening one day because of a compiler bug is not null.

To tackle this potential issue, some classes of applications require traceability between the object code and the source code (for example, the DO-178B requirements for avionics [42]). Such traceability is generally challenging to get on compilers without relying on manual annotations [79]. It is also compromised by many compiler optimizations, though some recent research attempts at tackling this issue (Li et al. [54]). In some critical systems, traceability is ensured by turning off all optimizations of compilers [8].

Turning off all optimizations comes with a downside: the resulting code is usually bigger and takes more time to execute. This, in turn, increases the worst-case execution time (WCET) and the energy consumption (more cycles are spent for performing the same task).

One way to tackle these issues is to use a formally verified compiler.

The CompCert certified compiler (Leroy [50, 51]) is the first optimizing C compiler with a formal proof of correctness that is used in industry [8; 43]. In particular, it does not have the middle-end bugs usually found in compilers [100], thus making it a significant success story of software verification.

CompCert features several middle-end optimizations (constant propagation, inlining, common subexpression elimination, etc.) as well as some backend optimizations (register allocation using live ranges, clever instruction selection on some platforms).

Using CompCert allows to have both compiler optimizations and formal guarantees: it proves a property of semantic preservation between the source code and the generated assembly code. In other words, the proofs done on the C source code remain valid on the assembly code generated by CompCert. <sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Small note: CompCert proof of semantic preservation only holds for executions free of undefined behaviours.

CompCert is used in several projects, among which:

- Vélus[18; 17], a formally-verified compiler for the Lustre dataflow language [39]. It consists of a Lustre frontend branched into the Clight IR of CompCert. Our version of CompCert is compatible with a modified version of Vélus [80].

- CertiKOS: an architecture for building formally-verified concurrent OS kernels [38]. They use CompCertX, a thread-safe version of CompCert [37].

- The Verified Software Toolchain [2], comprising tools to prove properties about the program's behavior at source level using a dialect of C (Verifiable C [3]). The program is then plugged into CompCert via the Clight intermediate representation.

### 1.1.4 Verifying software with Coo

Using Coq is one possible technique to verify software. [10] Coq is both a (functional) programming language and a proof description language. The typical workflow in Coq is to write code in Gallina (Coq's programming language) and then specify theorems about that code. Coq's code is then extracted to other languages, typically OCAML or Haskell.

Given a list sorting algorithm sort\_list written in Gallina, an example of theorem could be "For each possible input list 1, (sort\_list 1) is sorted".

To prove such theorems, one writes a list of tactics to apply, such as destructing the theorem into different cases, introducing variables from forall quantifiers, or using the result of another (previously proved) theorem.

The trusted computing base (TCB) of Coq is intentionally small: most of its datatypes are provided in the form of formally proven libraries instead of built-in types. For example, Coq does not natively support integers or even booleans: instead, several integer libraries exist, each supplying their definition of what integers (or booleans) are, the possible operations on them and their associated lemmas (such as the associativity of the addition).

Coo proofs give a high level of assurance; if there is a bug in code verified in Coo, it may come from either:

- The Coq extractor (the part of Coq that converts a Gallina program into OCAML (or Haskell), which can then be compiled); though recent work has been done towards a fully verified Coq extractor, such as Savary Bélanger et al. [84] or Forster and Kunze [34].

- The compiler of the language used after extraction (e.g. OCAML's compiler).

- A problem in the specification written in Coq: under-specification, wrong modeling, or axiomatizing wrong hypotheses.

Most of the time, bugs of programs written in Coo come from the latter.

A disadvantage of Coq is that some proofs can be very tedious to perform (it usually takes much more time to prove code than writing it). Proving code in Coq usually involves cutting each piece of code finely into smaller fragments, each of which can then be proven more easily and then patching all these fragments together into one bigger theorem. When the code can hardly be cut in such fragments, one must rely on finding proof invariants or other techniques. In particular, most of the time, the Coq proof must be changed when the Coq code is modified; though some automation tactics exist to remedy that, an overly-automated proof can be very tricky to untangle when it becomes invalid because of a change.

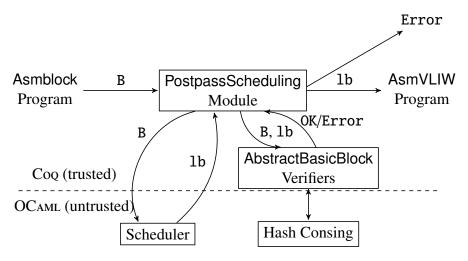

One way to avoid this caveat for some challenging problems, as has initially been explored by Tristan and Leroy [95], is to apply *a posteriori* verification: an untrusted oracle (e.g. written in OCAML) returns its result to a formally proven verifier written in Coq. The verifier then checks the oracle's result for correctness: if the verdict is positive, we have the formal proof that the result is correct.

With this approach, it is also much easier to modify the program transformation (performed by the oracle). Indeed, if it stays within a certain class of program transformations, and if the verifier is complete in regards to that class, then modifying the oracle does not require to modify the verifier or its proof. This is a major advantage, especially for complex optimizations that might require slight changes before reaching their full potential.

The other advantage is that it opens up the range of possible proofs: some problems that would be very hard to prove structurally may become much easier to prove through an a posteriori verifier.

In this thesis, we used a posteriori verification profusely: this allowed us to fine-tune our compiler optimizations without much need for proof modification.

### 1.1.5 VLIW processors in the context of critical applications

In most architectures, processors are synchronous entities that execute instructions under the beat of a clock. Executing an instruction involves a several-step process: fetching the instruction from memory, decoding the instruction, reading the registers indicated by the instruction, performing the instruction's operation, and finally writing back the result to the destination registers. As such, each instruction typically take several cycles to be completed.

Modern processors processors are organized so that several instructions are evaluated in parallel. Each step is assigned to a processor unit: while a given instruction is decoded, another instruction is getting fetched, and yet another instruction is being evaluated. This process is called *instruction*

*pipelining*, and the hardware responsible for that is the *processor pipeline*. Most processors have an *interlocked* pipeline: if an operand of an instruction to be executed is not yet ready, the processor inserts *stalls* in the pipeline, which halts the execution of that instruction until its data is ready.

Thanks to this method, as long as there is no starvation in the pipeline and no stall is inserted, processors can virtually execute one instruction per cycle. The process of feeding an instruction through the pipeline is called *issuing* an instruction.

In addition to instruction pipelining and the ever-going quest to get more performance, various techniques have emerged to have processors execute code faster. A first technique has historically been to increase the processors' frequencies; in just decades, the processor frequencies' order of magnitude increased from the MHz all the way to the GHz. However, this technological progress soon hit a wall, as increasing frequency further started to pose challenging issues in terms of miniaturization and temperature increase within the chips.

Another technique has been to issue several instructions per cycle instead of just one, either by allowing the pipeline to process two or more instructions per step or having different distinct pipelines.

In the most extreme case, some processors, including all current x86 architecture processors, can execute instructions ahead of time to fill idle units: these are categorized as *out-of-order* processors since the concrete order of execution might not be the same as the original order of the assembly code. Having such processors allows to have good performance without having to change the assembly code: they minimize the number of cases where instructions have to wait on each other in the pipeline.

However, this comes with a cost: their design is more complex (their hardware circuit requires more space), they are more susceptible to side-channel information leaks (especially when speculative execution is used to decrease the cost of control branches), and they tend to be less energy-efficient.

In contrast, *in-order* processors do not try to reorder instructions. Their design is then simpler, more energy-efficient, and they are also more predictable, which makes them a good fit for embedded systems. Indeed, reasonably tight bounds on worst-case execution time (in most safety-critical applications, the WCET must be estimated by a sound analysis [9]) are more easily obtained on in-order processors than on out-of-order processors. In addition, a simpler design may be more reliable. <sup>3</sup>

In-order superscalar processors have hardware logic to detect code dependency at runtime and issue multiple independent instructions in the same cycle. VLIW (Very Large Instruction Word)

<sup>&</sup>lt;sup>3</sup>For instance, Intel's Skylake processor had a bug that crashed programs under complex conditions [52].

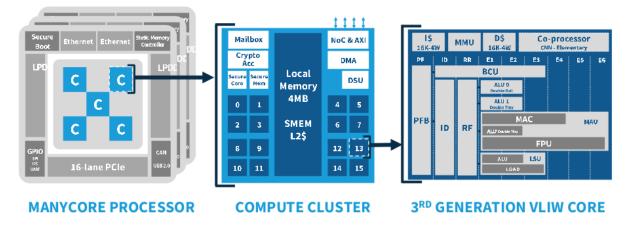

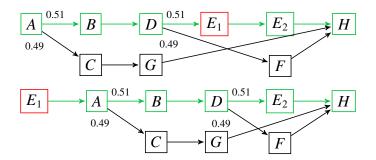

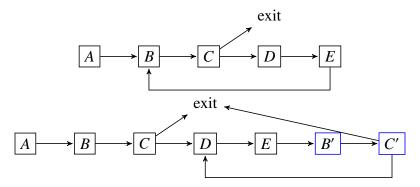

Figure 1.1.: The Coolidge architecture

processors can also issue several instructions in parallel [32], but unlike superscalar processors, the groups of instructions to be issued together (called *bundles*) are expressed directly in the assembly code: each bundle is syntactically separated by a ; ; token.

The caveat of these processors is that since they do not have any reordering at runtime, they rely on compilers' optimizations to produce adequate bundles, and more generally, to ensure good performance. In this thesis, we will mostly tackle two levels of performance issues for VLIW processors:

- The instruction ordering: a bad ordering could lead to either the processor spending most

of its cycles stalling or having certain units to be idle while they could be executing an

instruction. Modern out-of-order architectures do not suffer from that, thanks to their

runtime reordering.

- The cost of branching: on such processors, taking a branch induces a penalty because the pipeline has to be refilled. This penalty is bigger for a conditional branch than for an unconditional branch. Again, modern out-of-order architectures suffer less from this, thanks to their speculative branch execution.

# 1.2 The Kalray KV3 architecture

The Kalray Coolidge is a manycore processor, as displayed in figure 1.1. It features 5 compute clusters interconnected by a Network-on-Chip. Each compute cluster runs its own code: to deploy an application to the Coolidge architecture, one uses the Kalray compilation tools to create a multi-binary file, which can then be deployed to the processor. External libraries handle the matters of spawning and communication between the clusters; the compiler does not have to worry about it: as such, in this thesis, we focus on programs running on a single cluster.

Each compute cluster contains 16 KV3 VLIW cores, sharing a local memory of 4 MB. Support for parallelism is provided either through libraries made available in a C API or through higher-level languages such as OpenCL combined with specific compiler support [90]. In our case, CompCert has no support for anything related to multi-threading, so we focus here on the execution on one single core (of a single compute cluster).

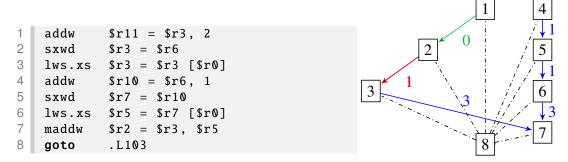

The Kalray KV3 core implements a 6-issue Fisher-style VLIW architecture [33] (partial predication, dismissible loads, no rotating registers), with an instruction pipeline of 8 stages. It has 64 general-purpose registers of 64-bits used for both integer and floating-point data (a given register can store an integer or a float). It sequentially executes blocks of instructions called *bundles*, with parallel execution within them.

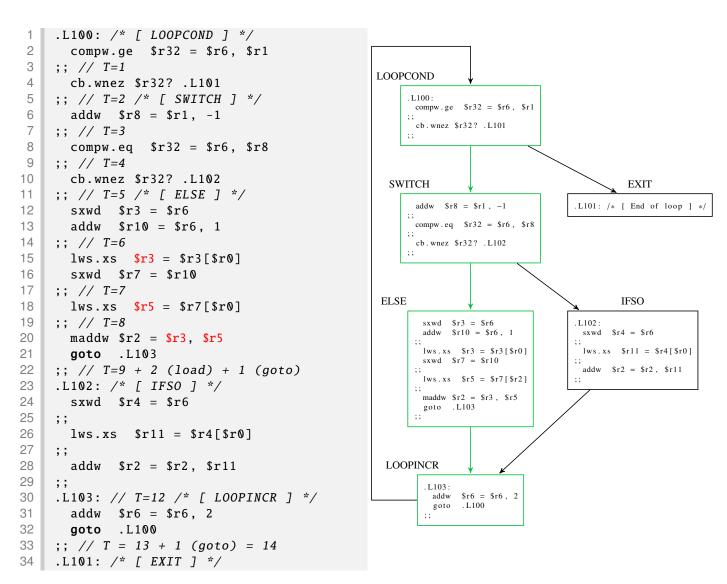

**Bundles** A *bundle* is a block of instructions that are to be issued into the pipeline at the same cycle. They execute in parallel with the following semantics. If an instruction writes into a register that is read by another instruction of the same bundle, then the value that is read is the value of the register before executing the bundle. If two instructions of the same bundle write to the same register, then the behavior at runtime is non-deterministic. For example, the bundle written in pseudo-code " $R_1 := 1$ ;  $R_1 := 2$ " assigns  $R_1$  non-deterministically. On the contrary, " $R_1 := R_2$ ;  $R_2 := R_1$ " is deterministic and swaps the contents of  $R_1$  and  $R_2$  registers in one atomic execution step. In assembly code, bundles are delimited by ; ; (Fig. 1.2). Compilers must ensure that each bundle does not require more resources than available—e.g., the KV3 has only one load/store unit, thus a bundle should contain at most one load/store instruction. The assembler refuses ill-formed bundles.

**Execution Pipeline** In the case of the KVX, bundles are executed through an 8-stage interlocked pipeline: the first stage prefetches the next bundle (PF stage), the second decodes it (ID stage), the third reads the registers (RR stage), then the last five stages (E1 through E5) perform the actual computation and write to the destination registers; depending on the instructions, the writes occur sooner or later (e.g., an addition takes fewer stages than a multiplication). If, during the RR stage<sup>4</sup>, one of the read registers of an instruction in the bundle is not available, the pipeline *stalls*: the bundle stops advancing through the pipeline until the register gets its result (Fig. 1.2).<sup>5</sup>

<sup>&</sup>lt;sup>4</sup>Or the ID stage, for some instructions such as conditional branching.

<sup>&</sup>lt;sup>5</sup>When a register is read before some prior instruction has written to it, *non-interlocked* VLIW processors use the old value. The compiler must then take instruction latencies and pipeline details into account to generate correct code, including across basic blocks. This is not the case for the KVX, where these aspects are just matters of code efficiency, not correctness.

| Cycle | ID | RR | E1    | E2    | E3    | E4+E5 | $B1: R_1 := load(R_0 + 0);$                |

|-------|----|----|-------|-------|-------|-------|--------------------------------------------|

| 1     | B1 |    |       |       |       |       | • • • • • • • • • • • • • • • • • • • •    |

| 2     | B2 | B1 |       |       |       |       | $B2: R_2 := load(R_0 + 4);;$               |

| 3     | В3 | B2 | B1    |       |       |       | $B3: R_3 := R_1 + R_2; R_4 := R_1 * R_2;;$ |

| 4     | B4 | В3 | B2    | B1    |       |       | $B4: R_3 := R_3 + R_4;$                    |

| 5     | B4 | В3 | STALL | B2    | B1    |       | $B5: store(R_0, R_3);$ ;                   |

| 6     | B4 | В3 | STALL | STALL | B2    |       | , , , , ,                                  |

| 7     | B5 | B4 | В3    | STALL | STALL |       | $B6: R_6 := R_7 + R_8;$ ;                  |

**Figure 1.2.:** The pipeline stalls at cycles 5 and 6 because B3 is waiting for the results of  $R_1$  and  $R_2$  from bundles B1 and B2, which are completed at stage E3. Stage PF (not shown here) happens just before the ID stage.

# 1.3 The CompCert formally-verified compiler as of today

### 1.3.1 Overview of CompCert

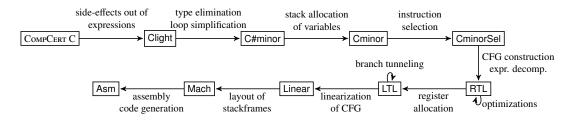

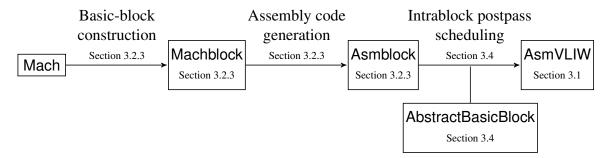

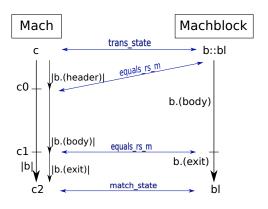

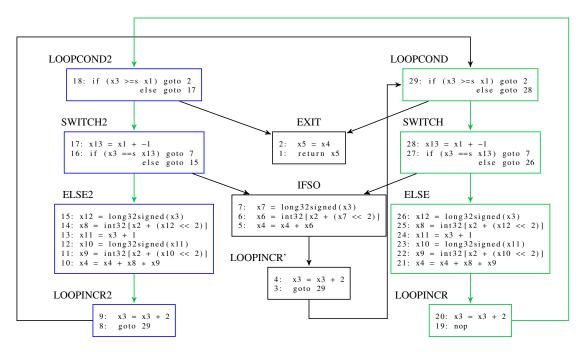

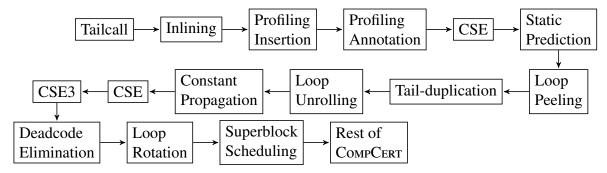

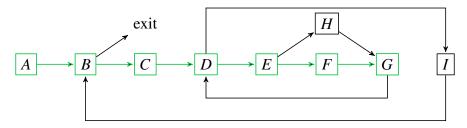

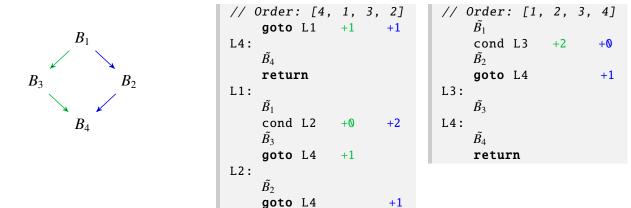

Usual compilers (GCC, Clang/LLVM, ICC) split the compilation process into several components. In the case of CompCert, a *frontend* first parses the source code into an *intermediate representation* (IR)—called Cminor—that is independent of the target machine [13]. Then, a *backend* transforms the Cminor program into an assembly program for the target machine [51]. Each of these components introduces several IRs, which are linked by *compilation passes*. A compilation pass can either transform a program from an IR to another (transformation pass) or optimize within an IR (optimization pass). As illustrated in Fig. 1.3, CompCert introduces more IRs than usual compilers. This makes its whole proof more modular and manageable because each compilation pass comes with its own proof of *semantic preservation*.

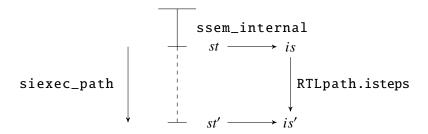

Figure 1.3.: The Intermediate Languages of CompCert

The CompCert compiler [41] executes an external C preprocessor then parses the result. It accepts a large subset of the C99 language [1], <sup>6</sup> as well as some C11 extensions.

<sup>&</sup>lt;sup>6</sup>The main C99 features absent from CompCert C are variable-length arrays and certain forms of unstructured "switch" statements. On most platforms, the setjmp()/longjmp() system is not supported either.

### In particular:

- The *backend* starts at the CminorSel level: we have at this level a precise abstract syntax tree of the C program.

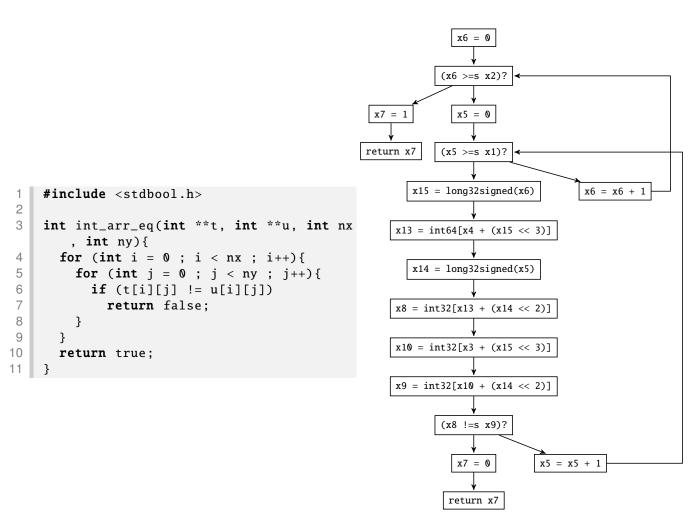

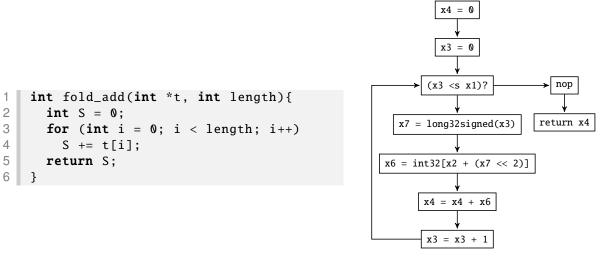

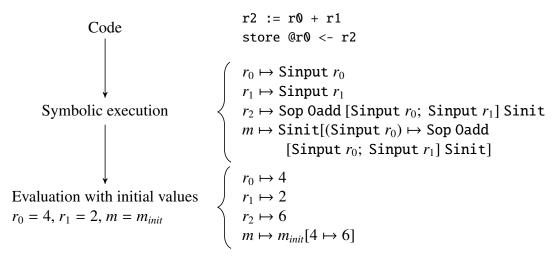

- From CminorSel to RTL is the construction of the Control-Flow Graph, using an infinite amount of *pseudo-registers*. Most of the optimizations are done on the RTL level, such as constant propagation, common subexpression elimination, tail call elimination. Compared to more traditional compilers whose control-flow graph is organized in basic blocks, in RTL, each node of the control-flow graph is a single 3-address instruction. RTL will be detailed in chapter 5.

- The *register allocation* pass transforms an RTL program (infinite amount of registers) into an LTL program (finite amount of registers). Another difference between LTL and RTL: each node is a basic-block instead of a single instruction.

- The Linear language is a linearized (laid out) version of the control flow. A certain positioning is chosen for each basic block, then control-flow instructions (conditional or unconditional jumps, labels) are inserted to replicate the control-flow graph. The original CompCert heuristics used by this pass are detailed in chapter 8.

- The Mach language lays out the activation records. Mach is a language close to assembly that abstracts from the ABI (Application Binary Interface) and the ISA (Instruction Set Architecture). It is further detailed in chapter 3.

- The final language Asm models the concrete assembly's semantics, with all the necessary instructions, functionally modelled.

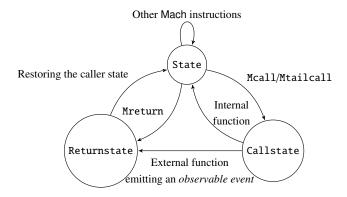

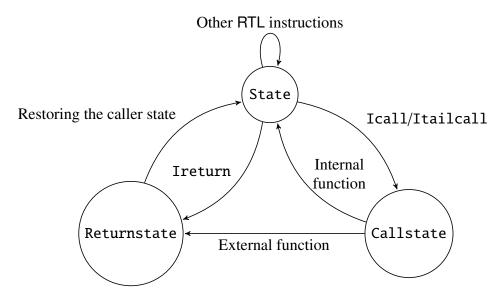

As detailed in Section 1.3.2, the semantics of each IR are specified using a Labeled Transition System (LTS)—a set of transitions between states, with a (possibly empty) execution trace assigned to each transition. While the intermediate languages of the frontend have a very rich state, with various environment variables, the intermediate languages of the backend have increasingly simple states, with the final language Asm featuring a very barebone state mainly containing the state of the registers (including Program Counter (PC) and Return Address (RA)) and the state of the memory.

These semantics (from Clight to the target assembly) are designed as deterministic. <sup>7</sup> Indeed, this design choice simplifies the correctness proof of the compiler. It reduces to prove the following: if the source code execution is valid (does not end in an invalid state) and produces an execution trace, then the execution of the compiled assembly code will also be valid and will produce the same execution trace. For instance, for a program containing just arithmetic computations and printf() calls, the execution of the assembly code should produce the same sequence of printf() calls as dictated by the semantics of the source program.

<sup>&</sup>lt;sup>7</sup>Undefined behaviours [1, §3.4.3] are either defined to lead to an invalid execution or are assigned precise semantics. Unspecified behaviours [1, §3.4.4] are also given precise semantics.

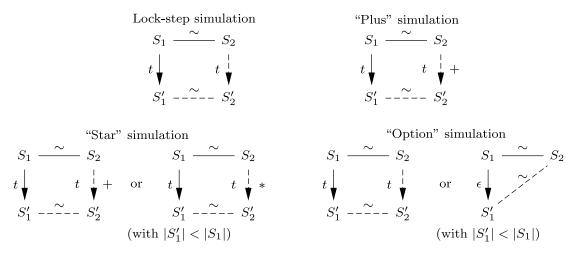

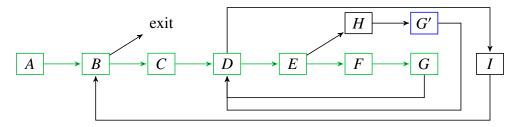

Figure 1.4.: Examples of Simulation Diagrams in CompCert, from Leroy [51]

Within the backend, compilers usually first introduce an unbounded number of *pseudo-registers*, which are then mapped to actual machine registers, with possible spills (saving on the stack, then reloading) when needed. This mapping is performed by the register allocation pass. Compiler backend passes can then be divided into two groups: those happening before register allocation (prepass) and those happening after (postpass).

As of today, the mainstream version of CompCert [26] does not have any reordering optimization, nor does it have any loop optimization such as loop unrolling, loop rotation or loop-invariant code motion. Because of that, CompCert's performance on in-order processors err on the low side compared to GCC, despite the already present optimizations.

# 1.3.2 CompCert 's framework for proving transformation passes correctness

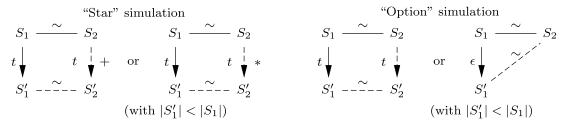

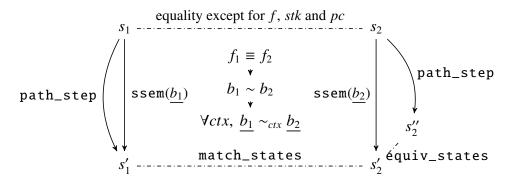

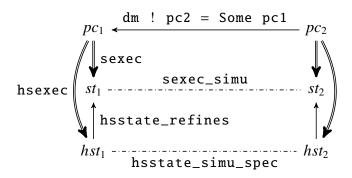

In CompCert [51], the semantics of a program P consists of predicates for describing initial and final states, as well as a predicate  $S \xrightarrow{t} S'$  (usually named step) indicating if *one* execution step can run from state S to state S' by generating a trace t—where t is either a single observable event (e.g. an external call or an access to a volatile variable) or  $\epsilon$  (absence of observable event). The formal correctness property of CompCert expresses that, given a source program  $P_1$  without undefined behavior (i.e. that can always run step from a non-final state), if the compilation of  $P_1$  produces some assembly program  $P_2$ , then the "observational behaviors" of  $P_2$  are included in those of  $P_1$ , as formalized by Leroy [50, 51]. In order to simplify correctness proofs of its successive passes (Fig. 1.3), CompCert uses an alternative definition for the correctness. One of them is the *forward simulation* applicable on passes between *deterministic* languages.

In its simplest form (*lockstep simulation*), given a relation ( $\sim$ ) matching states between  $P_1$  and  $P_2$ , a forward simulation involves proving that:

- 1. the initial (resp. final) states of  $P_1$  match those of  $P_2$ ;

- 2. given two matching states, if  $P_1$  steps to a state  $S'_1$ , then  $P_2$  steps to a state  $S'_2$  matching  $S'_1$ .

In the semantic model of CompCert, each external call, access to volatile variable and builtin will produce an *event*. An event is composed of a list of input values (e.g. the arguments to a function call), and a return value if any (e.g. the return value of the function call). A *trace* is then defined as a sequence of events. At last, CompCert classifies program *behaviors* in three categories:

- converges(r, t): the program eventually terminates, with a return code *r* and a finite trace *t*.

- diverges(t): the program never terminates, with a possibly infinite trace t.

- goeswrong(t): the program fails (e.g. division by zero or out-of-bound access), with a finite trace *t*.

Let S and C be respectively the source and compiled programs. The notation  $S \Downarrow B$  denotes that B is an observed behavior of the source program S. Let S pec be a set of behaviors that do not go wrong (i.e. without undefined behaviors like invalid memory accesses). The notation  $S \models S$  pec means that all the observed behaviors of S are in S pec:

$$S \models S \ pec \ iff \ \forall B, \ S \ \downarrow B \implies B \in S \ pec$$

(1.1)

CompCert proves a property of semantic preservation: if S verifies a specification S pec, then so does C.

$$S \models S pec \implies C \models S pec$$

(1.2)

The modular design of CompCert splits the compilation into different Intermediate Representations (IR), and proves the semantics preservation between each of these IR (Fig. 1.3). Actually, when languages at both sides of the pass are deterministic, CompCert proves the semantic preservation from an easier property known as forward simulation: it states that if S has an observable behavior B that does not go wrong, then C will observe the same behavior: [50; 51]

$$\forall B \notin Wrong, S \downarrow B \implies C \downarrow B \tag{1.3}$$

Given semantics of the source and target languages (that is, a mapping from a program to its observable behaviors), the property can be proven using structural induction on the predicate

$S \downarrow B$ . This is still not practical to prove directly, so CompCert uses specific schemes (e.g., lock-step simulation) that each imply the forward simulation.

A semantic of a language *L* in CompCert consists of:

- An inductive type State describing the states of execution of a program in a language L

- A predicate (step  $L_1 S_1 t S_1'$ ) indicating if we can transition from state  $S_1$  to state  $S_1'$  by generating a trace t in the language  $L_1$

- A predicate (initial\_state *prog S*) indicating if state *S* is an initial state of the program *prog*

- A predicate (final\_state *S ret*) indicating if state *S* returning with value *ret* is a final state.

Let us assume we want to write a compilation pass from language  $L_1$  to  $L_2$ , and that we have a (match\_state  $S_1$   $S_2$ ) predicate indicating if the states  $S_1$  from  $L_1$  and  $S_2$  from  $L_2$  match. Let us also assume the following hypotheses:

- The public symbols are preserved across the transformation (not formalized here)

- The initial states match:  $\forall S_1$ , initial\_state  $L_1 S_1 \implies \exists S_2$ , initial\_state  $L_2 S_2 \land$  match\_state  $S_1 S_2$

- The final states match:  $\forall S_1 \ S_2 \ r$ , match\_state  $S_1 \ S_2 \land$  final\_state  $L_1 \ S_1 \ r \implies$  final\_state  $L_2 \ S_2 \ r$

Lock-step simulation consists of: "if the source program can take a step, then the transformed program can take a matching step". It is expressed as:

$$\forall S_1 \ t \ S_1' \ S_2$$

, step  $L_1 \ S_1 \ t \ S_1' \land \text{match\_states} \ S_1 \ S_2$

$\implies \exists S_2'$ , step  $L_2 \ S_2 \ t \ S_2' \land \text{match\_states} \ S_1' \ S_2'$

Lock-step simulation can be visually represented as a diagram, along with other kinds of simulation that also imply a forward simulation (cf figure 1.4).

The "plus" simulation is like the lock-step one, but one may execute several instructions of the target program for one in the source program, instead of just one.

## 1.4 Motivations of this thesis and contributions

The motivations of this thesis have then been the following:

- To identify optimizations that would increase performance on in-order processors, and in particular on VLIW processors.

- Implement those optimizations and measure whether they were successful in improving the performance.

- Find efficient ways to formally verify these optimizations.

In this thesis, I focused on the KV3 interlocked VLIW processor from Kalray, though most of its results also extend to other in-order processors including non-VLIW processors such as ARM Cortex A53 and RiscV Rocket (for which our optimizations have been easily ported, with the help of Léo Gourdin).

With the help of David Monniaux and Sylvain Boulmé, I contributed the following:

- A port of CompCert on the KV3 architecture, inspired from the existing RiscV port and the partial port of Barany [5] on the prior KV2 architecture. <sup>8</sup>

- A modelling of instruction bundles for the KV3 (chapter 3). This work could be adapted for any other interlocked VLIW processor.

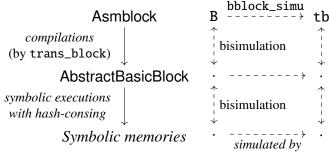

- A postpass scheduling optimization: an instruction reordering pass happening after register allocation (see chapter 3). In our case, it happens directly at the assembly IR of Comp-Cert and transforms each basic block into a list of bundles that are then emitted by the assembly printer. The verification is done using a similar symbolic execution technique to that of Tristan and Leroy [95], but in Asm instead of Mach, and with hash-consing. To formally verify this optimization, we also had to define semantics for basic-block execution, reconstructing them at the Mach level and re-adapting the Mach to Asm translation accordingly (chapter 3). When designing this optimization, we kept in mind ease of adaptation to other architectures; Léo Gourdin, Sylvain Boulmé and David Monniaux later ported it to AArch64 with relative ease (a couple of person-months) [89].

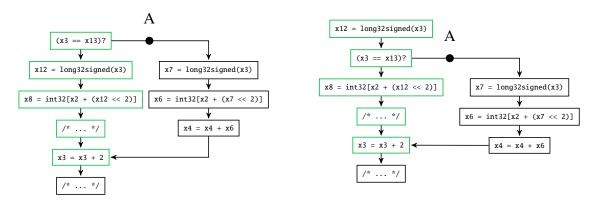

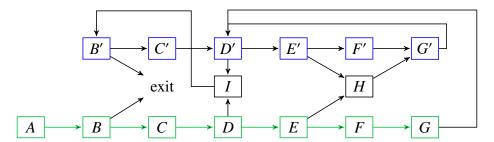

- A superblock scheduling optimization: an instruction reordering pass before register allocation, on the scope of superblocks (a kind of extended basic-blocks). This work includes the implementation of a static branch prediction (chapter 8), the definition of new superblock execution semantics in RTL (chapter 5), a minor change of the Linearize oracle for laying out superblocks contiguously in memory (chapter 8), and the verified superblock scheduling transformation itself (chapter 7) with hash-consing.

- A series of more minor optimizations consisting of duplicating instructions to increase optimization opportunities (chapter 8): loop unrolling, tail-duplication, loop peeling and loop rotation. These transformations are all verified a posteriori within a lightweight

<sup>&</sup>lt;sup>8</sup>Barany's backend generates only one instruction per bundle. He also faced the challenge of representing pairs of 32-bit registers in CompCert for handling 64-bit floating-point values on the KV2. The KV3 natively has 64-bit registers, so that has not been an issue for us.

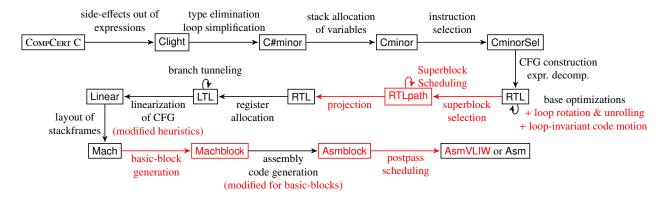

Figure 1.5.: CompCert compilation flow with our added optimizations in red

module described in chapter 6. In particular, when loop peeling is combined with the new CSE3 pass of David Monniaux, we achieve Loop Invariant Code Motion [63].

• An evaluation of CompCert on the Polybench and TACleBench benchmarks, with an evaluation of the performance gain induced by each introduced optimization, and some results obtained for other in-order processors (chapter 10). In addition to the Kalray KV3 core, with the further help of Léo Gourdin, we evaluated CompCert with our optimizations on an ARM Cortex A53 (on a Raspberry Pi 3) and a "Rocket" RiscV core (on FPGA).

I also participated in the following publications:

- Six et al. [88] describes the formally verified postpass basic-block scheduling with bundles semantics, published in OOPSLA'20.

- Monniaux and Six [63] describes a formally verified Loop Invariant Code Motion, using code duplication to hoist instructions outside of the loop (in particular, the loop-invariant instructions are hoisted), then CSE3 to eliminate loop-invariant computations within the loop. This was published in LCTES'21.

- Six et al. [89] describes the formally verified prepass superblock scheduling, submitted for publication.

Figure 1.5 shows the new compilation flow of CompCert with our new optimizations.

Thanks to this work, compared to GCC -O2, and for most of our benchmarks, code compiled with CompCert is now, on average, only 16% slower (instead of 50% slower) on KV3, 12% slower (instead of 38%) for the ARM Cortex A53, and 30% slower (instead of 45%) for the "Rocket" RiscV core.

The full source code of this work is available on https://gricad-gitlab.univ-grenoble-alpes.fr/certicompil/compcert-kvx.

During my thesis, I was an employee of Kalray under CIFRE (Convention Industrielle de Formation par la REcherche) agreement number 2018/0441.

# Related Work

# 2.1 Compiler optimizations for VLIW processors

### 2.1.1 Instruction scheduling

Scheduling methods (for the *compaction* problem: how to parallelize a sequential micro-code) have been thoroughly studied by Fisher [30], Rau et al. [78], Chang and Hwu [20]. Some of these methods were implemented in the Multiplow compiler [55] for a VLIW architecture. Dupont de Dinechin [25] did a thorough study of adapting the machine scheduling algorithms from the litterature to VLIW processors.

Instruction scheduling for micro-code is a particular instance of scheduling with timing and resource constraints, which is a classical problem [62, §5.4].

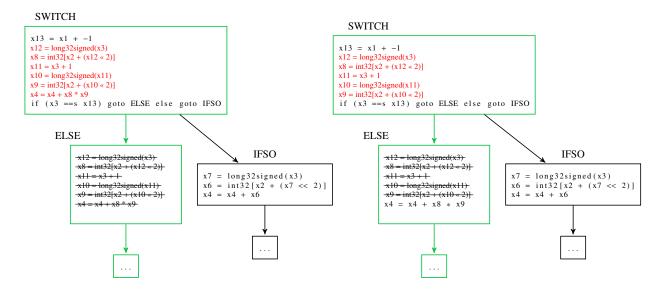

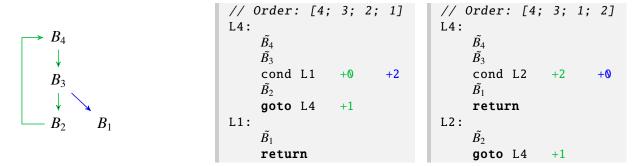

In its simplest form, instruction scheduling is done in basic blocks; however, scheduling on super blocks (sequences of basic blocks where each basic block has a single predecessor, except the first) yields better results due to the bigger scheduling scope. The scheduling can be acyclic or cyclic if the scope is a whole inner loop. Lastly, it may run before (prepass scheduling) or after (postpass scheduling) register allocation.

If the scheduling happens before register allocation, then extra care must be given to not increase register pressure too much — that is, the register allocation should not generate more register spills as a result of the prior scheduling. On the other hand, if the scheduling happens after register allocation, the reuse of registers introduced by the register allocation may hamper the scheduling (*false dependencies*).

Ideally, having the register allocation and instruction scheduling in a single pass would solve this issue; however doing so is challenging, though there are existing work like Motwani et al. [65], or more recently Lozano et al. [57]. Instead, the approach usually taken by compilers is to have two separate scheduling passes: one before register allocation, and another after register allocation.

Pouzet [77] considered the scheduling of functional programs on VLIW architectures, including forms of software pipelining (for tail-recursive programs), with equivalence defined as term

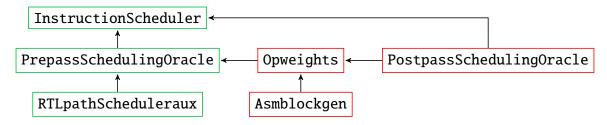

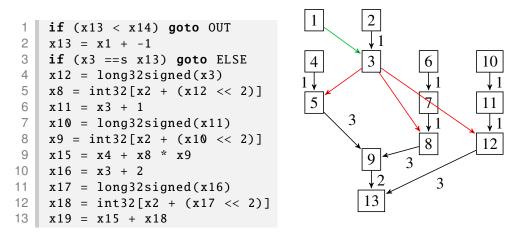

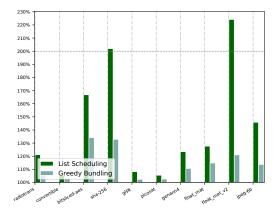

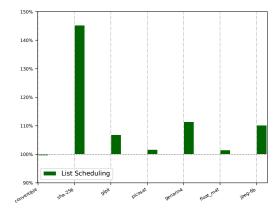

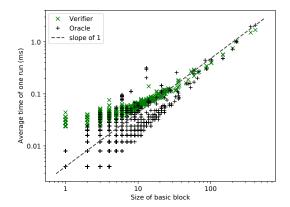

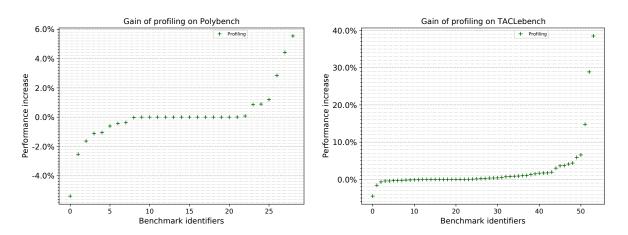

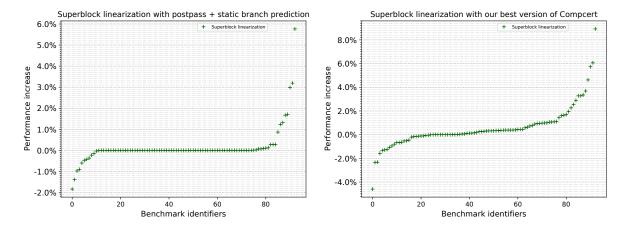

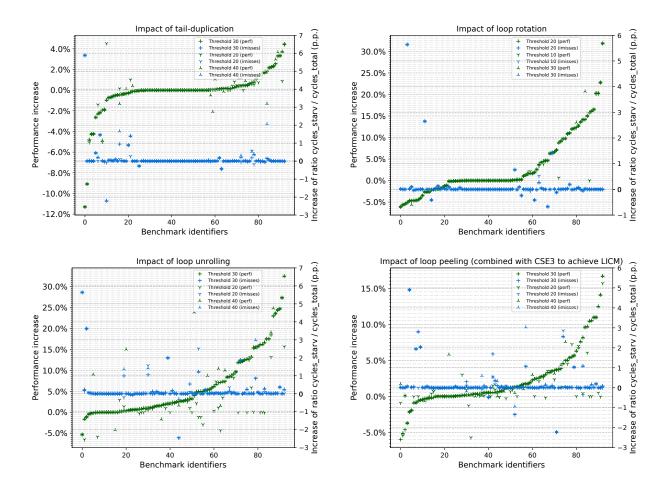

equivalence, possibly up to rewriting. The work is similar to our scheduling transformations, however Pouzet did not investigate formal proofs of the transformation.