## Fast and Accurate Performance Models for Probabilistic Timing Analysis of SDFGs on MPSoCs

Hai-Dang Vu

#### ▶ To cite this version:

Hai-Dang Vu. Fast and Accurate Performance Models for Probabilistic Timing Analysis of SDFGs on MPSoCs. Electronics. Université de Nantes, 2021. English. NNT: . tel-03171880

### HAL Id: tel-03171880 https://hal.science/tel-03171880v1

Submitted on 17 Mar 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT DE

#### L'UNIVERSITE DE NANTES

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité : Électronique

Par

## Hai Dang VU

# Fast and Accurate Performance Models for Probabilistic Timing Analysis of SDFGs on MPSoCs

Thèse présentée et soutenue à Nantes, le 04/03/2021 Unité de recherche : IETR UMR CNRS 6164

#### Rapporteurs avant soutenance :

Liliana CUCU-GROSJEAN Chargée de Recherche/HDR, INRIA, Paris François VERDIER Professeur, Université Côte d'Azur

#### **Composition du Jury:**

Présidente Laurence PIERRE Professeur, Université Grenoble Alpes

Examinateurs : Liliana CUCU-GROSJEAN Chargée de Recherche/HDR, INRIA, Paris

François VERDIER Professeur, Université Côte d'Azur

Dir. de thèse : Sébastien PILLEMENT Professeur, Université de Nantes

Co-encadrant : Sébastien LE NOURS Maître de Conférences, Université de Nantes

## **ACKNOWLEDGEMENT**

Before you read my thesis, I would like to tell you about the people who have accompanied me throughout my wonderful PhD journey.

First of all, I would like to thank my supervisor, Mr. Sébastien PILLEMENT, Professor at the Université de Nantes. He has given to me the right instructions at the right moments to prevent me from going to the wrong ways.

I would like to thank my co-supervisor, Mr. Sébastien LE NOURS, Lecturer at the Université de Nantes. He asked me a lot of interesting questions to not only help me to understand better about my topic, but also create new ideas.

I would like to express my sincere gratitude to all members of the jury. I would like to thank Madam Liliana CUCU-GROSJEAN, Researcher at INRIA, Paris and Mr. François VERDIER, Researcher at LEAT, Université Côte d'Azur for having accepted the responsibility of rapporteurs. I express my gratitude to Madam Laurence PIERRE, Professor at the Université Grenoble Alpes, to have participated in the jury.

Special thanks to the secretary, Sandrine CHARLIER at IETR Polytech Nantes for taking care of all my administrative issues during my thesis with her ultimate kindness.

I would like to thank all colleagues at IETR for interesting time to discuss about working, to exchange their ideas, their cultures during the coffee time. I also would like to thank to my colleagues at OFFIS: Mr. Kim GRUETTNER and Mr. Ralf STEMMER who have been working together in the Pssim4MC project.

To my dear family in Vietnam, I would like to express my gratitude and love to my father Hai Duong VU, my mother Thi Tam DOAN, my younger brother Hai Thien Long VU, my sister and brother-in-law Thi Thuong Thuong VU and Minh Hai DANG, my nephew Vu Binh Nguyen DANG, my niece Vu Thao Nguyen DANG and finally my love Thi Diem Huong BUI who always love me unconditionally. They gave me a lot of motivations and encouragements to finish my thesis from thousands of miles away in Vietnam.

I would like to thank all my dear friends who supported me during my time in Nantes.

And finally, I would like to conclude this section by a poem of Walter Savage Landor (1775-1864):

I strove with none, for none was worth my strife.

Nature I loved, and, next to nature, Art;

I warm'd both hands before the fire of Life;

It sinks, and I am ready to depart.

## TABLE OF CONTENTS

| Li           | ist of | acron   | yms                                                                       | 6  |

|--------------|--------|---------|---------------------------------------------------------------------------|----|

| Li           | ist of | figure  | es e                                  | 11 |

| Li           | ist of | tables  | 5                                                                         | 12 |

| $\mathbf{R}$ | ésum   | ıé      |                                                                           | 13 |

| 1            | Intr   | roduct  | ion                                                                       | 18 |

|              | 1.1    | Timir   | ng predictability issues in multi-processor system-on-chip                | 18 |

|              |        | 1.1.1   | Hardware and software resources of multi-processor system-on-chip         | 18 |

|              |        | 1.1.2   | Influence of shared resources on timing predictability of MPSoC systems . | 20 |

|              |        | 1.1.3   | Timing compositionality of MPSoC systems                                  | 23 |

|              | 1.2    | Perfor  | rmance evaluation of MPSoC systems                                        | 25 |

|              |        | 1.2.1   | Hardware/software codesign                                                | 25 |

|              |        | 1.2.2   | Simulation-based analysis approaches                                      | 27 |

|              |        | 1.2.3   | Formal analysis approaches                                                | 27 |

|              |        | 1.2.4   | Probabilistic analysis approaches                                         | 29 |

|              | 1.3    | Contr   | ributions and organization of the manuscript                              | 30 |

| 2            | Sta    | te of t | he art                                                                    | 32 |

|              | 2.1    | Perfor  | rmance analysis approaches                                                | 32 |

|              |        | 2.1.1   | Simulation-based approaches                                               | 32 |

|              |        | 2.1.2   | Formal approaches                                                         | 36 |

|              | 2.2    | Proba   | abilistic approaches                                                      | 41 |

|              | 2.3    | Simul   | ation speed/Accuracy improvement methods                                  | 47 |

| 3            | Wo     | rking   | environment                                                               | 51 |

|              | 3.1    | Overv   | riew of the proposed workflow                                             | 51 |

|              | 3.2    | System  | m model                                                                   | 52 |

|              |        | 3.2.1   | Model of computation                                                      | 53 |

|              |        | 3.2.2   | Model of architecture                                                     | 55 |

|              |        | 3.2.3   | Mapping model                                                             | 55 |

#### TABLE OF CONTENTS

|                                                                |      | 3.2.4   | Measurement infrastructure                                              | 56 |

|----------------------------------------------------------------|------|---------|-------------------------------------------------------------------------|----|

| 3.3 Probabilistic modeling of computation and communication ti |      |         | bilistic modeling of computation and communication times                | 56 |

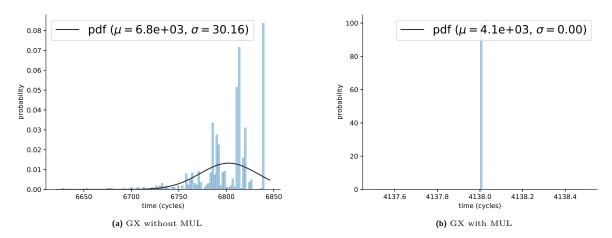

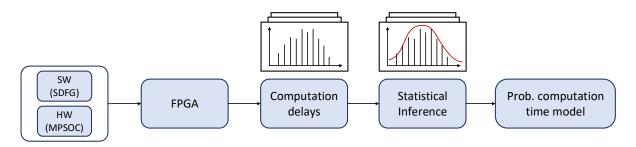

|                                                                |      | 3.3.1   | Computation time modeling approach                                      | 57 |

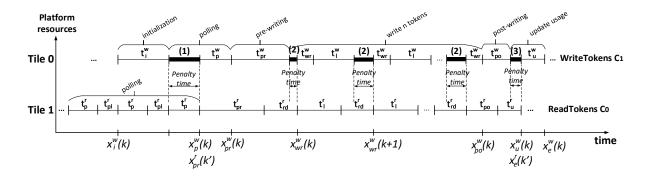

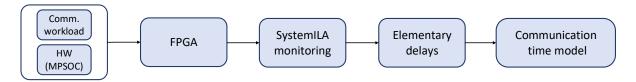

|                                                                |      | 3.3.2   | Communication time modeling approach                                    | 58 |

|                                                                |      | 3.3.3   | Simulation model                                                        | 60 |

|                                                                | 3.4  | Evalua  | ation of the proposed framework                                         | 62 |

|                                                                |      | 3.4.1   | Case studies                                                            | 62 |

|                                                                |      |         | Sobel filter                                                            | 63 |

|                                                                |      |         | JPEG decoder                                                            | 63 |

|                                                                |      | 3.4.2   | Hardware platform                                                       | 64 |

|                                                                |      | 3.4.3   | Experiment setup                                                        | 65 |

|                                                                |      | 3.4.4   | Results                                                                 | 66 |

|                                                                | 3.5  | Conclu  | usion                                                                   | 69 |

| 4                                                              | Defi | inition | of a fast yet accurate message-level communication model                | 71 |

|                                                                | 4.1  | Propo   | sal of a message level communication model                              | 71 |

|                                                                |      | 4.1.1   | Message-level model principles                                          | 72 |

|                                                                |      | 4.1.2   | Application of the proposed modeling approach to a FCFS bus arbitration |    |

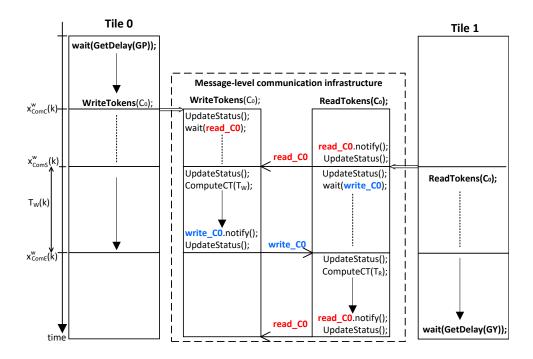

|                                                                |      |         | policy                                                                  | 73 |

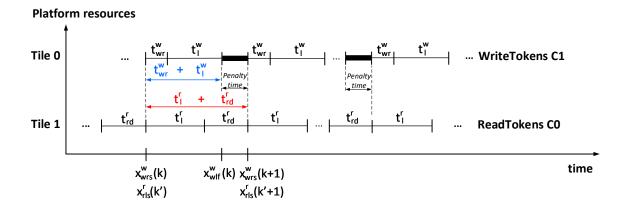

|                                                                |      | 4.1.3   | Definition of the analytical model                                      | 76 |

|                                                                |      | 4.1.4   | Message-level model creation                                            | 79 |

|                                                                | 4.2  | ML de   | escription of the communication model                                   | 80 |

|                                                                |      | 4.2.1   | Message-level evolution of the communication model                      | 80 |

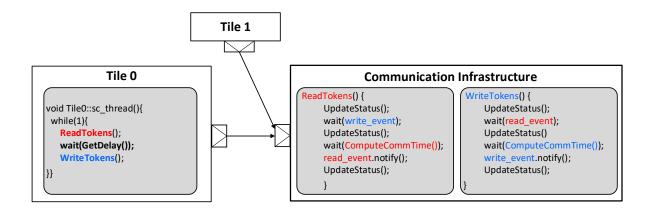

|                                                                |      | 4.2.2   | Simulation model                                                        | 81 |

|                                                                | 4.3  | Exper   | iments                                                                  | 83 |

|                                                                |      | 4.3.1   | Communication characterization phase for the AXI4LITE bus               | 83 |

|                                                                |      | 4.3.2   | Results                                                                 | 86 |

|                                                                |      | 4.3.3   | Discussion                                                              | 88 |

|                                                                | 4.4  | Conclu  | usion                                                                   | 89 |

| 5                                                              | Pro  | babilis | stic timing analysis approach                                           | 90 |

|                                                                | 5.1  | Statist | tical model checking                                                    | 90 |

|                                                                |      | 5.1.1   | Overview of statistical model checking                                  | 90 |

|                                                                |      | 5.1.2   | Qualitative analysis                                                    | 91 |

|                                                                |      | 5.1.3   | Quantitative analysis                                                   | 92 |

|                                                                |      | 5.1.4   | Bounded Linear Temporal Logic                                           | 92 |

|                                                                | 5.2  | SMC i   | for SystemC model of MPSoC systems                                      | 93 |

|                                                                |      | 5 2 1   | Proposed workflow                                                       | 03 |

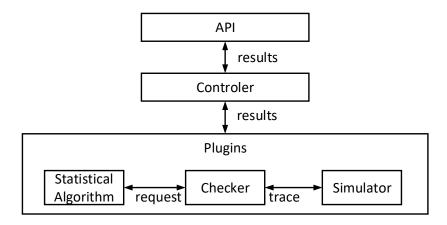

|               |                  | 5.2.2   | PLASMA Statistical Model Checker                             | . 94  |

|---------------|------------------|---------|--------------------------------------------------------------|-------|

|               |                  | 5.2.3   | Monitor and aspect-advice generator and SystemC plugin       | . 95  |

|               | 5.3              | Exper   | iments                                                       | . 96  |

|               |                  | 5.3.1   | Case studies                                                 | . 96  |

|               |                  | 5.3.2   | Definition of used computation and communication time models | . 97  |

|               |                  | 5.3.3   | Analysis results for the first hardware setup                | . 99  |

|               |                  |         | Quantitative analysis                                        | . 99  |

|               |                  |         | Simulation time                                              | . 101 |

|               |                  |         | Influences of the parameters                                 | . 102 |

|               |                  |         | Qualitative analysis                                         | . 103 |

|               |                  | 5.3.4   | Analysis results for the second hardware setup               | . 104 |

|               | 5.4              | Concl   | usion                                                        | . 106 |

| 6             | Cor              | ıclusio | ns and perspectives                                          | 108   |

|               | 6.1              | Concl   | usions                                                       | . 108 |

|               | 6.2              | Perspe  | ectives                                                      | . 110 |

| Bi            | bliog            | graphy  |                                                              | 111   |

| $\mathbf{Li}$ | $\mathbf{st}$ of | public  | cations                                                      | 122   |

## LIST OF ACRONYMS

AADL Architecture Analysis and Design Language

AHB Advanced High-performance Bus ALTL Adaptive Linear Temporal Logic

AMBA Advanced Microcontroller Bus Architecture

AP Atomic Proposition

ARM Advanced Risc Machine

ATLM Arbitrated Transaction Level Model

BC Best Case

BIP Behavior Interaction Priority

BFM Bus Functional Model

BLTL Bounded Linear Temporal Logic BRAM Block Random Access Memory

CAN Controller Area Network

COST Commercial Off-The-Shelf

CPU Central Processing Unit

CTL Computation Tree Logic

CTMC Continuous Time Markov Chains

DMA Direct Memory Access

DOL Distributed Operation LayerDSE Design Space ExplorationDSP Digital Signal Processors

DTMC Discrete Time Markov Chains

ESL Electronic System Level

ESPAM Embedded System-level Platform synthesis and Application Mapping

ET Event Triggered

FCFS First Come First Served

FIFO First In First Out

FFT Fast Fourier Transform

FPGA Field Programmable Gate Arrays

FPU Floating Point Unit FSM Finite State Machine GCSL Goal and Contract Specification Language

GPP General Purpose Processors

GPU Graphical Processing Unit

GSL GNU Scientific Library

GSM Global System for Mobile Communication

GUI Graphical User Interface

HW Hartware

IO Input Output

IP Intellectual Property

JPEG Joint Photographic Experts Group

JTAG Joint Test Action Group

KPN Kahn Process Network

LTL Linear Temporal Logic

LRU Least-Recently Used

LUT Lookup Table

MA Markov Automata

MAC Medium Access Control

MAG Monitor and Aspect Advice Generator

MDP Markov Decision Process

ML Message Level

MoC Model of Computation

MoA Model of Architecture

MoP Model of Performance

MoS Model of Structure

MP3 MPEG-1/2 Audio Layer III

MPA Modular Performance Analysis

MPSoC Multiprocessor System-on-Chip

MUL Multiplier

MUV Model Under Verification

NoC Network on Chip

NPTA Network of Priced Timed Automata

PA Probabilistic Automata

PCTL Probabilistic Computation Tree Logic

PE Processing Element

PLASMA Platform for Learning and Advanced Statistical Model checking Algorithms

PLRU Pseudo Least-Recently Used

PTA Priced Timed Automata

RML Reactive Module Language ROM Result Oriented Modeling

RR Round Robin

RTL Register Transfer Level

RTOS Real-Time Operating System

SADF Scenario Aware Dataflow

SBIP Stochastic Behavior Interaction Priority

SCE System-on-Chip Environment

SCHM Single Chip Heterogeneous Multiprocessors

SCM Statistical Contention Model SCL Stochastic Contention Level

SDF Synchronous Dataflow

SDFG Synchronous Dataflow Graph SLDL System level design language SMC Statistical Model Checking

SPRT Sequential Probability Ratio Test

SLD System Level Design SUA System Under Analysis SSP Single Sampling Plan

SW Software

SystemILA System Integrated Logic Analyzer

TA Timed Automata

TAS Task Allocation Scheduling

TDMA Time Division Multiple Access

TL Transaction Level

TLM Transaction-Level Model

TMC Time Measurement Controller

TMU Time Measurement Unit

TPN Timed Petri Net

TT Time Triggered

UML Unified Modeling Language

VHDL Very-high-speed integrated circuits hardware description language

WLAN Wireless Local Area Network

WCRT Worst Case Response Time

WFS Wave Field Synthesis

WCET Worst Case Execution Time

WMTL Weighted Metric Temporal Logic

WC Worst Case

XML Extensible Markup Language

## **LIST OF FIGURES**

| 1.1  | Overview of multiprocessor system on chip         | 9 |

|------|---------------------------------------------------|---|

| 1.2  | Shared resources in MPSOCs                        | 0 |

| 1.3  | Interference on FCFS bus                          | 1 |

| 1.4  | Accessing to the main memory via cache            | 2 |

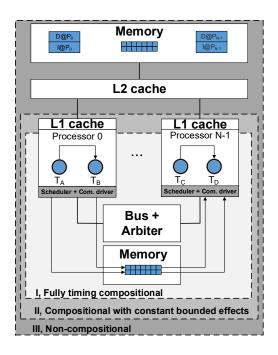

| 1.5  | Classification of compositional architectures     | 4 |

| 1.6  | Hardware/software co-design                       | 5 |

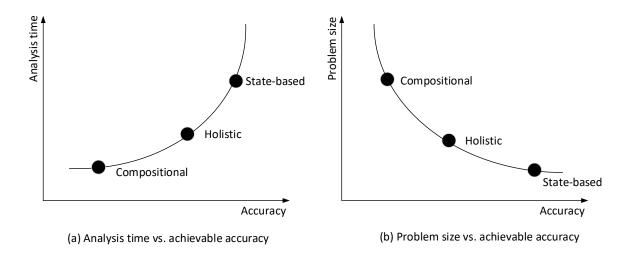

| 1.7  | Comparison different formal approaches            | 8 |

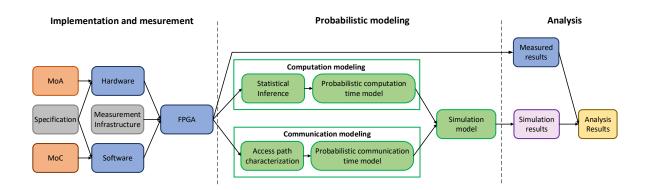

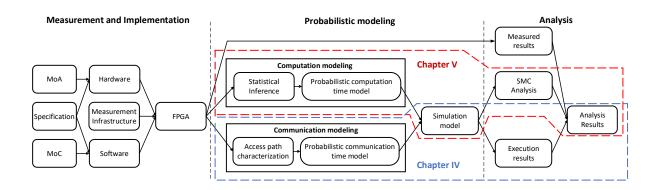

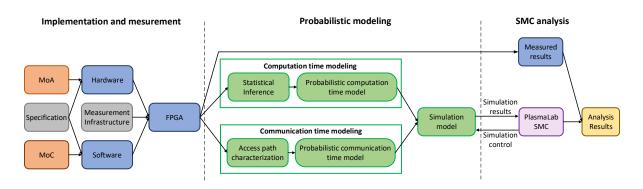

| 3.1  | Methodology                                       | 2 |

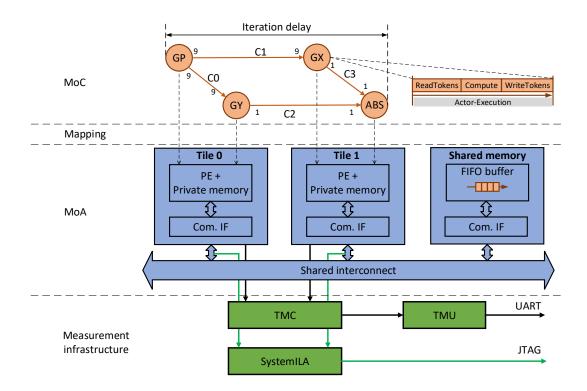

| 3.2  | System model                                      | 3 |

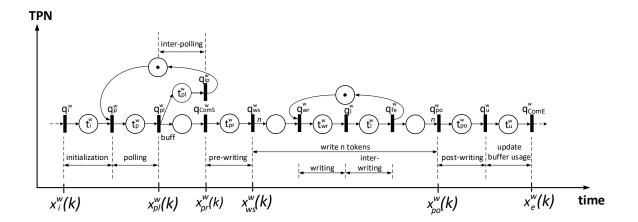

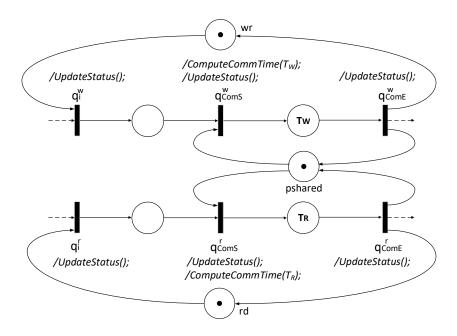

| 3.3  | Write process diagram                             | 4 |

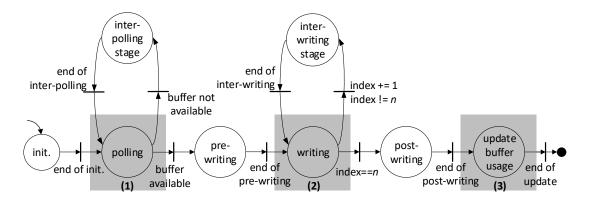

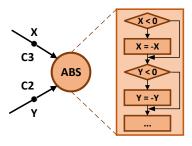

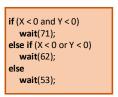

| 3.4  | Example the computation branches of the ABS actor | 7 |

| 3.5  | Distribution of the TL simulation models          | 8 |

| 3.6  | Computation model                                 | 8 |

| 3.7  | Transaction level communication model             | 9 |

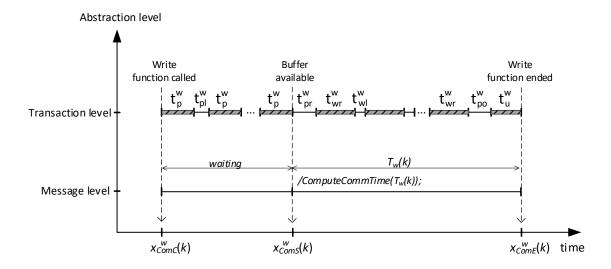

| 3.8  | Communication time modeling                       | 0 |

| 3.9  | Simulation model                                  | 1 |

| 3.10 | Applications                                      | 3 |

| 3.11 | Measurement infrastructure                        | 4 |

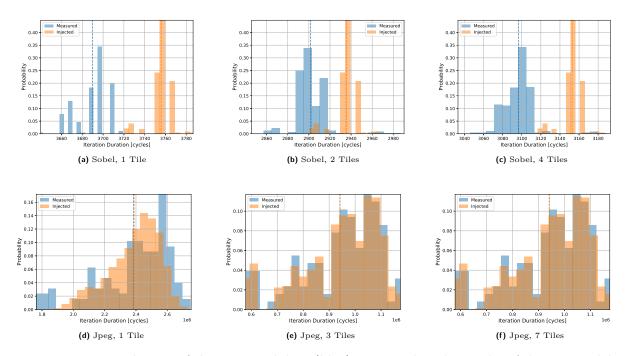

| 3.12 | Distribution of the TL simulation models          | 8 |

| 3.13 | Methodology                                       | 0 |

| 4.1  | Principle                                         | 2 |

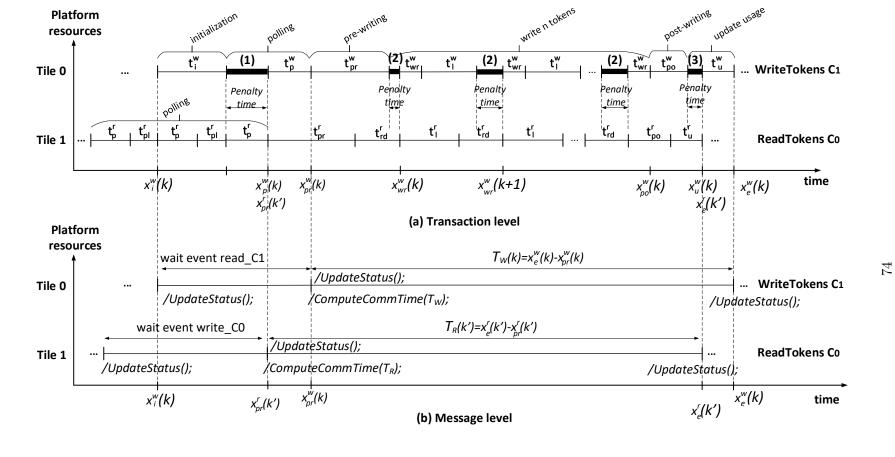

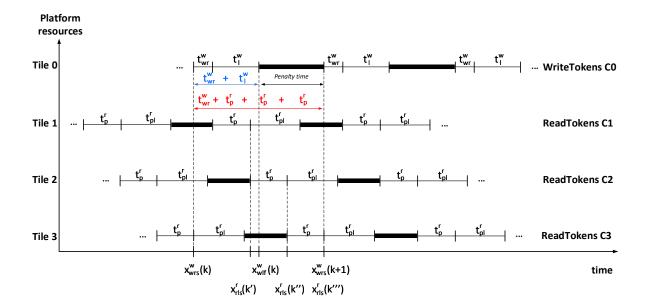

| 4.2  | Penalty time                                      | 4 |

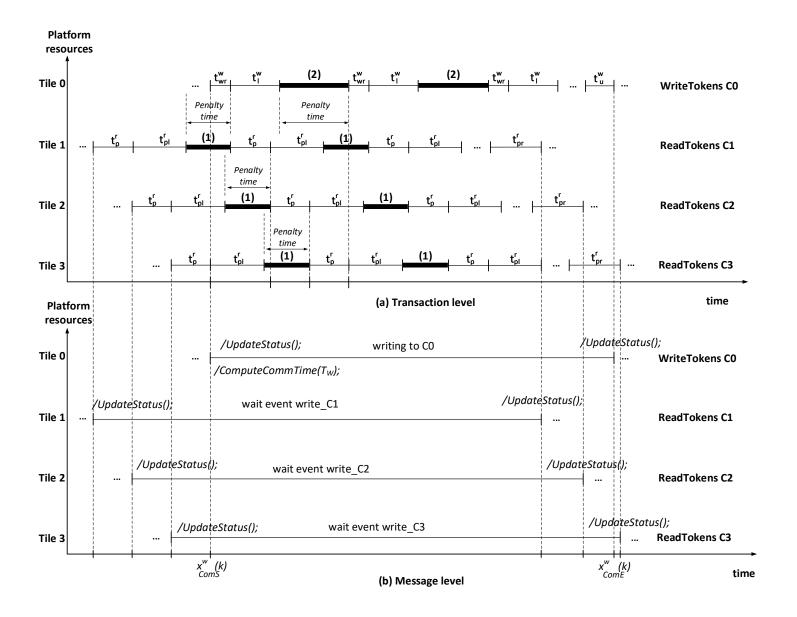

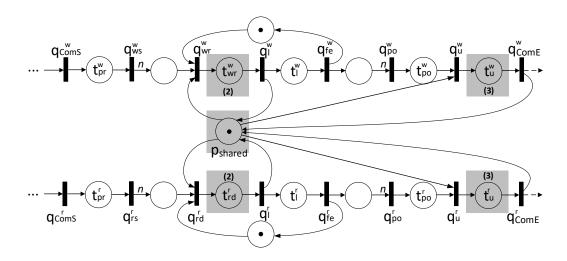

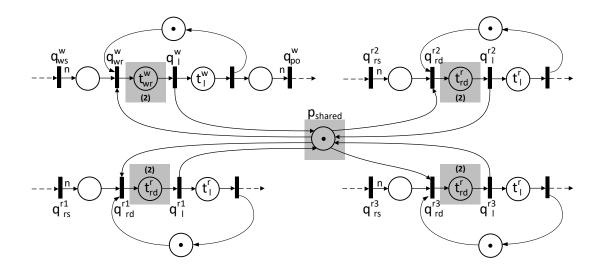

| 4.3  | Four tile contention                              | 5 |

| 4.4  | Petrinet of WriteTokens                           | 7 |

| 4.5  | Petrinet TL                                       | 7 |

| 4.6  | Petrinet ML                                       | 9 |

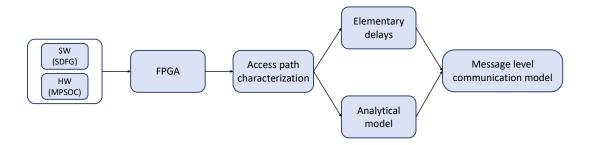

| 4.7  | Workflow to create a ML model                     | 0 |

| 4.8  | Petri net at message-level                        | 1 |

| 4.9  | Message-level systemc model                       | 2 |

| 4.10 | Message-level systems model                       | 3 |

| 4.11 | Communication characterization phase for the AXI4LITE bus for 2 tiles | 84 |

|------|-----------------------------------------------------------------------|----|

| 4.12 | Communication characterization phase for the AXI4LITE bus for 4 tiles | 85 |

| 4.13 | Distribution of the ML simulation models                              | 88 |

|      |                                                                       |    |

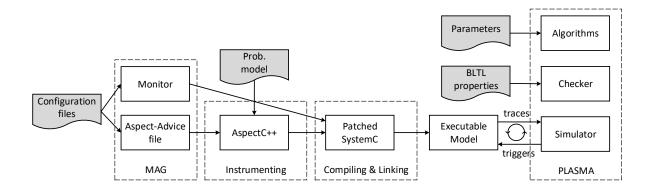

| 5.1  | SMC analysis methodology                                              | 93 |

| 5.2  | Plasma Architecture                                                   | 94 |

| 5.3  | Plasma workflow with SystemC plugin                                   | 96 |

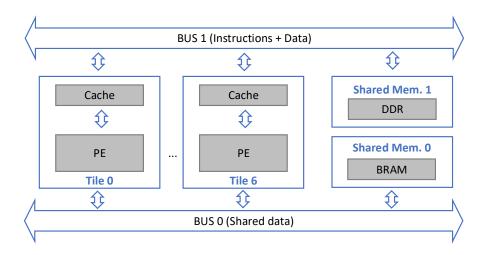

| 5.4  | Hardware platform with cache activated                                | 97 |

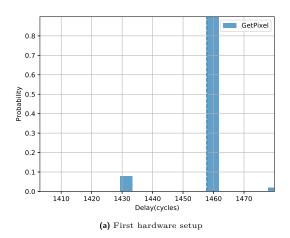

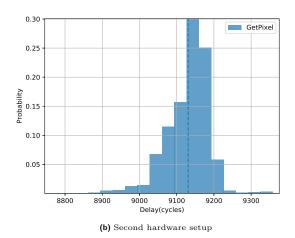

| 5.5  | GetPixel in two hardware setups                                       | 98 |

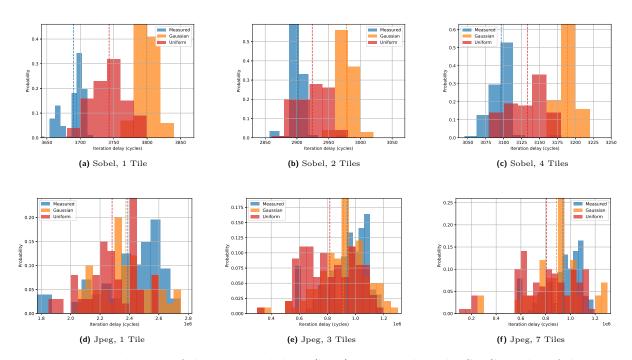

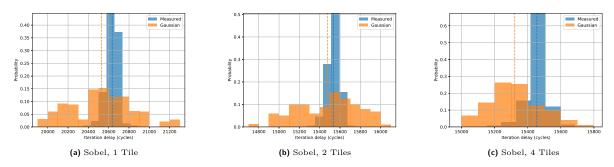

| 5.6  | Distribution of the ML simulation models using SMC                    | 01 |

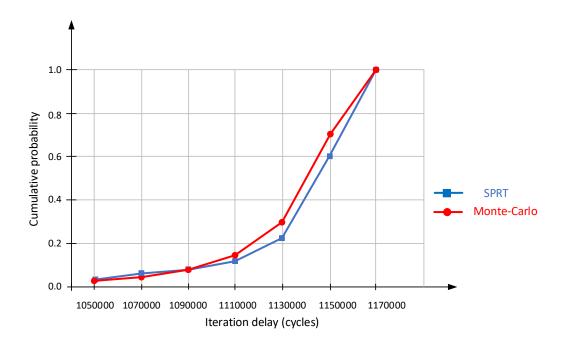

| 5.7  | Cumulative probability comparison using Monte Carlo and SPRT          | 04 |

| 5.8  | Distribution of the ML simulation models using SMC                    | 05 |

## **LIST OF TABLES**

| 2.1 | Classification of simulation-based approaches                                      |

|-----|------------------------------------------------------------------------------------|

| 2.2 | Classification of formal approaches                                                |

| 2.3 | Specifications of the presented probabilistic approaches                           |

| 3.1 | Elementary delays notion                                                           |

| 3.2 | Mapping of the Sobel filter and JPEG decoder                                       |

| 3.3 | Elementary delays                                                                  |

| 3.4 | Results of the TL simulation models                                                |

| 3.5 | Simulation time of TL simulation models                                            |

| 4.1 | ML model                                                                           |

| 4.2 | Simulation time of ML simulation models                                            |

| 5.1 | Mapping of the Sobel filter and JPEG decoder on two hardware platforms 97          |

| 5.2 | Variation of the elementary delays                                                 |

| 5.3 | Results of the ML simulation models using PLASMA                                   |

| 5.4 | Simulation time of ML simulation models using PLASMA                               |

| 5.5 | Parameter tuning of Monte Carlo                                                    |

| 5.6 | Results of the ML simulation models using PLASMA for the second hardware setup 105 |

| 5.7 | Simulation time of ML simulation models using PLASMA                               |

## RÉSUMÉ

#### Motivations

Les systèmes multi-processeurs sur puce (MPSoC) sont largement appliqués dans de nombreux domaines en raison de leur ratio performance/consommation d'énergie élevé. La vérification des propriétés temporelles de ces systèmes au plus tôt dans le processus de conception est très importante. Cette vérification vise à garantir que les contraintes de temps sont pleinement respectées. Cependant, les ressources partagées au sein des MPSoCs peuvent impliquer de fortes variations du temps d'exécution du logiciel et compliquent donc la prévision des propriétés temporelles de ces systèmes. Par conséquent, il est essentiel de créer un modèle de performance capable de capturer les effets des ressources partagées. De plus, il faut choisir une approche d'analyse appropriée qui propose non seulement un bon compromis entre la précision et le temps d'analyse, mais aussi permette une bonne scalabilité. Cette thèse vise à étudier l'adoption de méthodes de modélisation et d'analyse probabilistes pour améliorer l'efficacité des approches d'analyse temporelle des systèmes MPSoC.

#### Contexte de la thèse

Les systèmes multiprocesseurs système sur puce (MPSoC) sont apparus dans de nombreux domaines en quelques décennies. Un système MPSoC se compose de trois parties principales: une application, un système d'exploitation et une plate-forme matérielle. L'application peut être divisée en plusieurs tâches exécutées sur une plate-forme matérielle. Le système d'exploitation est composé des logiciels du système (les services de gestion de la mémoire, l'ordonnanceur, etc.) et des pilotes d'abstraction. La plate-forme matérielle se compose de différents composants tels que des éléments de traitement (processing elements, PEs), des bus, des mémoires et des périphériques. Dans un système MPSoC, ces composants matériels sont conçus sur une même puce. Un MPSoC homogène contient plusieurs PE du même type et offre des capacités de paral-lélisation des applications. Un MPSoC hétérogène présente différents types de PE conçus pour des fonctionnalités spécifiques. La complexité des systèmes MPSoCs augmente rapidement dans les deux parties logicielles et matérielles. Du côté matériel, les interactions entre différents composants matériels accédant aux ressources partagées compliquent la prévision des comportements du système. Du côté logiciel, les fonctionnalités des applications sophistiquées avec des millions de lignes de code nécessitent d'énormes efforts pour être testées et vérifiées. La vérification de

la performance de ces systèmes est donc indispensable car elle permet de vérifier le respect des fonctionnalités mais aussi des exigences dites non fonctionnelles. Lors de l'exécution du programme, les ressources logicielles et matérielles influencent le temps d'exécution du programme. Dans cette thèse, nous nous concentrons principalement sur l'étude des influences des ressources partagées sur l'analyse temporelle des systèmes MPSoC.

Dans les systèmes MPSoC, les éléments de traitement partagent des ressources du système telles que des bus, des mémoires (mémoire globale, caches privées), des caches partagées, etc. Les accès simultanés à ces ressources partagées provoquent des interférences qui entraînent des délais supplémentaires dans le temps d'exécution des tâches. Ces ressources partagées influent sur les comportements temporels des systèmes MPSoC.

Les interférences des accès concurrents aux résources partargées causent des difficultés à prévoir la performance du système. Le temps d'exécution d'une tâche peut varier en fonction du logiciel de la tâche et des ressources matérielles où la tâche est exécutée.

- Du point de vue logiciel, le temps d'exécution d'une tâche dépend de ses données d'entrée. Différentes données d'entrée peuvent être traitées en suivant différents chemins d'exécution à travers le programme, et donc fournir des temps d'exécution différents.

- Du point de vue matériel, la variabilité du temps d'exécution est causée par les interférences entre les tâches accédant aux ressources partagées.

Étant donné que de nombreuses ressources matérielles sont impliquées dans l'exécution de la tâche, le temps d'exécution de la tâche devient plus difficile à prévoir. La caractérisation de ces temps élémentaires est cruciale pour la prévision des comportements temporels du système.

Différentes approches ont été proposées pour estimer la performance du système, par exemple: les approches basées sur la simulation, les approches formelles, les approches probabilistes.

Les approches basées sur la simulation testent partiellement les propriétés du système en se basant sur un ensemble limité de stimuli. Dans les approches existantes, des modèles d'architectures matériel-logiciel sont formés en combinant un modèle d'application et un modèle de plate-forme. Au début de la phase de conception, une description complète des fonctionnalités de l'application n'est pas obligatoire et des modèles de charge de travail de l'application sont utilisés. Un modèle de charge de travail exprime les charges de calcul et de communication (par exemple, le temps d'exécution, la consommation d'énergie, le coût de la mémoire) qu'une application provoque lorsqu'elle est exécutée sur les ressources de la plateforme. Les modèles de performances capturés sont générés sous forme de descriptions exécutables et simulés. Le temps d'exécution de chaque primitive de chargement est approximé comme un délai. Les délais sont généralement estimés à partir de mesures sur des prototypes réels ou de l'analyse de simulations de bas niveau. Les approches basées sur la simulation nécessitent une analyse approfondie de l'architecture dans divers scénarios de travail possibles. Les modèles d'architecture créés ne peuvent pas être simulés de façon exhaustive et les pires scénarios de travail peuvent être difficilement identifiés

et évalués. Un autre problème important concerne la précision des modèles créés. Enfin, avec la complexité croissante des plates-formes MPSoC, l'exécution des modèles de simulation nécessite plus de temps de simulation.

Différentes approches formelles ont été proposées pour analyser les systèmes multicœurs et fournir des bornes de temps. Ces approches formelles sont généralement classées comme méthodes analytiques et méthodes basées sur l'état. Les méthodes analytiques ont l'avantage d'être évolutives pour analyser des systèmes à grande échelle. Par contre, ces méthodes analytiques font abstraction de nombreux détails de fonctionnement du système analysé, tels que les protocoles d'arbitrage complexes ou les dépendances de tâches de communication inter-processeurs, ce qui conduit à des résultats pessimistes par rapport aux résultats des méthodes basées sur l'état. Les méthodes basées sur les états representent le système consideré comme un système de transition (états et transitions). Étant donné qu'elles reflètent les états de fonctionnement réels du comportement du système, des résultats plus précis peuvent être obtenus par rapport aux méthodes analytiques. De nombreuses approches récentes pour l'analyse temporelle du logiciel sur des architectures multicoeur sont construites sur des techniques d'analyse basées sur l'état. Les approches basées sur les états permettent une analyse exhaustive des propriétés du système au prix d'effort de modélisation et d'analyse importants.

Les approches probabilistes sont une combinaison de modèles probabilistes et de techniques d'analyse. Dans le contexte des systèmes embarqués, ils représentent un moyen de capturer la variabilité du système. La variabilité provient principalement de la sensibilité du système à l'environnement et des effets de bas niveau des plate-formes matérielles. Les modèles probabilistes peuvent être utilisés pour capturer de manière appropriée cette variabilité. Les modèles probabilistes sont des extensions du système de transition et permettent de prendre en compte les variations des temps d'exécution et des transitions d'état. L'analyse de ces modèles probabilistes permet d'obtenir des mesures quantitatives. Les approches probabilistes qui combinent la simulation et les approches formelles est un bon compromis entre la précision et les efforts d'exploration. Le model-checking statistique (SMC) a été proposé comme alternative aux approches formelles pour éviter une exploration exhaustive du modèle de l'espace d'états. SMC fait référence à une série de techniques utilisées pour explorer une sous-partie de l'espace d'états et fournit une estimation sur la performance du système. SMC désigne un ensemble de techniques statistiques présentant les avantages suivants:

- SMC est basé sur une sémantique formelle des systèmes qui permet de vérifier les propriétés comportementales. SMC répond à des questions qualitatives (Est-ce que la probabilité pour un modèle de satisfaire une propriété donnée est supérieure ou égale à un certain seuil?) et des questions quantitatives (quelle est la probabilité pour un modèle de satisfaire une propriété donnée?).

- Il nécessite simplement un modèle exécutable du système qui peut être simulé et vérifié par

rapport aux propriétés basées sur l'état exprimées en logiques temporelles. Les exécutions observées sont traitées pour décider avec une certaine confiance si le système satisfait une propriété donnée.

— En tant qu'approche basée sur la simulation, SMC demande moins de mémoire et de temps que les approches exhaustives. SMC peut donc être considéré comme un compromis entre les tests et la vérification formelle.

SMC permet d'approcher des systèmes qui ne peuvent être évalués avec une approche exhaustive. Il nécessite simplement un modèle de simulation du système, qui peut être vérifié par rapport aux propriétés basées sur l'état. Cependant, l'adoption de techniques SMC pour l'analyse des systèmes MPSoC a rarement été envisagée. Cela peut s'expliquer par les efforts considérables déployés pour mettre en place cette approche. La création de modèles probabilistes reste donc une tâche difficile et n'est pas bien prise en charge pour les systèmes MPSoC. Cette thèse vise à fournir des lignes directrices pratiques pour faciliter la création de modèles probabilistes et favoriser l'adoption d'approches d'analyse probabiliste pour les systèmes multicœurs.

#### Contributions

Dans le cadre de cette thèse, nous cherchons à étudier l'adoption de méthodes de modélisation probabiliste et d'analyse temporelle des systèmes MPSoC. Nos principales contributions sont:

- 1. Cette thèse vise à fournir des lignes directrices pratiques pour faciliter l'adoption de méthodes probabilistes dans le flot de conception au niveau système. Ce flot de travail est basé sur trois parties principales. (1) Une approche basée sur la mesure est d'abord utilisée pour caractériser l'exécution d'une application sur une plateforme réelle. Cette caractérisation se fait à la fois dans les parties calcul et communication, (2) L'approche modélise à la fois les parties logicielles et matérielles et se base sur un langage de modélisation de niveau système. Cette modélisation capte la variation du temps d'exécution en utilisant les approches probabilistes, (3) Une approche d'analyse probabiliste est basée sur le model checking statistique (SMC) qui estime la probabilité que notre modèle probabiliste puisse satisfaire une propriété temporelle.

- 2. Au niveau transactionnel, le processus de simulation reste lent, ce qui pose des difficultés pour analyser des systèmes complexes. Nous proposons un modèle de communication au niveau message d'un bus multiprocesseur pour fournir des résultats de simulation rapides mais précis. Le modèle proposé a montré une accélération significative de la simulation par rapport au modèle au niveau transactionnel (TLM) sans dégrader la précision de l'analyse.

- 3. Une approche d'analyse probabiliste utilisant la méthode de model checking statistique est mise en place. Cette approche SMC explore partiellement l'espace d'état du système,

tout en rendant possible pour limiter la probabilité de faire une erreur sur les prédictions en contrôlant le nombre d'exécutions de simulation à l'aide d'algorithmes statistiques. Dans cette analyse, les effets des paramètres des algorithmes statistiques sur les résultats d'analyse sont étudiés.

#### Contenu du manuscrit

Ce manuscrit est organisé comme suit:

- Chapitre 1 introduit les motivations, le contexte de la thèse, les contributions proposées.

- Chapitre 2 donne un aperçu de l'état de l'art, la comparaison des approches et des méthodes d'amélioration de la vitesse de simulation.

- Chapitre 3 présente notre démarche de travail, comme le modèle de l'architecture (MoA), le modèle de calcul (MoC), l'infrastructure de mesure et le modèle de simulation. Quelques premières études de cas sont présentées et les résultats obtenus avec l'environnement développé sont donnés.

- Chapitre 4 introduit le modèle de communication au niveau des messages. Ce modèle de haut niveau améliore le modèle de simulation à la fois en précision et en vitesse de simulation. Les résultats de la simulation montrent une accélération significative par rapport au modèle de niveau transactionnel (TLM).

- Chapitre 5 présente l'approche d'analyse temporelle probabiliste. Nous visons à démontrer l'efficacité de l'approche de vérification des modèles statistiques pour l'analyse temporelle des MPSoCs. Une étude plus approfondie sur différents algorithmes statistiques est fournie dans ce chapitre. Une extension de l'architecture matérielle avec cache privé activé pour chaque tuile est présentée. Les résultats d'analyse d'un tel système montrent un bon niveau de précision.

- Chapitre 6 résume les contributions et fournit différentes perspectives et les possibles travaux futurs.

## INTRODUCTION

Multi-processor system-on-chip (MPSoC) systems are widely applied in many domains because of their high performance/energy consumption ratio. A key property to allow early performance evaluation of such systems in the design process is timing predictability. It represents the capability to predict timing properties of MPSoC in order to verify that timing constraints are met. However, shared resources in MPSoC can cause high variations of software execution time and thus make timing prediction of such systems a challenging task. Therefore, it is crucial to create performance models that can capture the shared resources effects. In this chapter, we first introduce the context of our research. Then we discuss different analysis approaches which are currently being considered for timing analysis. Finally, we present our main contributions and the organization of this manuscript.

### 1.1 Timing predictability issues in multi-processor system-onchip

#### 1.1.1 Hardware and software resources of multi-processor system-on-chip

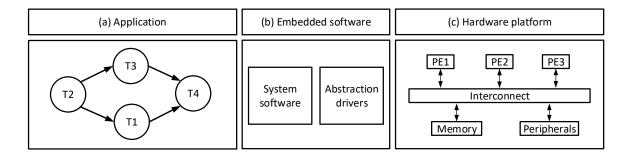

Multi-processor system-on-chip (MPSoC) systems have emerged in many domains in few past decades. We define a MPSoC system as composed of three main parts: an application, an embedded software and a hardware platform. Application can be divided into multiple tasks which are executed on a hardware platform. Embedded software is composed from system softwares (operating system, memory management services, arbitration policies, etc.,) and abstraction drivers. Hardware platform consists of different components such as processing elements (PEs), buses, memories and peripherals. In MPSoC system, multiple PEs and other hardware components are designed on a same chip. In Fig. 1.1, we present an overview of a MPSoC system. A four-task application is executed on a hardware platform consisting of three processing elements that communicates to a shared memory and peripherals via an interconnection.

We can classify a MPSoC system as homogeneous or heterogeneous depending on the type of PEs. A homogeneous MPSoC contains multiple PEs which are of same type. Homogeneous MPSoCs are designed to execute a same application on their PEs for parallelism perspectives. Heterogeneous MPSoC have different types of PEs which are designed for specific functionalities.

For example, these PEs can be General Purpose Processors (GPPs), Digital Signal Processors (DSPs), Graphical Processing Units (GPUs), hardware accelerators.

Figure 1.1 – Overview of a multiprocessor system-on-chip consisting of an application (a), an embedded software (b) and a hardware platform (c).

Along with the growth of system complexity, designers have to consider several challenges in the design process. Different design challenges were discussed by Teich [1] and Nouri [2]:

- 1. Heterogeneous system-on-chip technology challenges the designers to integrate a heterogeneous system into a single multi-billion transistor system-on-chip. The current tendency to get higher performance is to put more transistors on smaller size of chip. However, the higher density of transistor on a chip requires much more higher efforts for physical design and optimization of different aspects such as energy consumption, temperature, etc.

- 2. Hardware/software complexity: From the hardware side, interactions between different complex hardware components accessing shared resources cause the unpredictability of system behaviors. From the software side, the functionalities of sophisticated applications with millions lines of code need enormous efforts to be tested and verified.

- 3. Hardware/software verification checks in the design process whether the MPSoCs can meet its functionalities and requirements. Since MPSoCs become more and more complex, the performance verification of such system is inevitable. In [3], Radetzki presented two aspects which has to be taken into account in the performance verification: functional and extrafunctional properties. Functional properties are verified to check the system functionality correctness by analyzing possible testing scenarios to detect potential problems. This avoids costly iterations in the design/manufacturing process. Extra-functional properties consist of the timing behavior, power consumption, reliability, security, etc. Early performance verification reduces not only the design time but also save the time-to-market windows.

- 4. Uncertain environment effects: Embedded systems are designed for specific functionalities where they can continuously interact with their environment. Thus their performance get

influenced by different uncertain and unpredictable environment contexts. Therefore, the environment uncertainties should be taken into account in the design process.

In the program execution, both software and hardware resources influence the program execution time. In this thesis, we mainly focus on studying the shared resources influences to the timing analysis of MPSoC systems. Thus in the next Section, we aim to present such influences.

## 1.1.2 Influence of shared resources on timing predictability of MPSoC systems

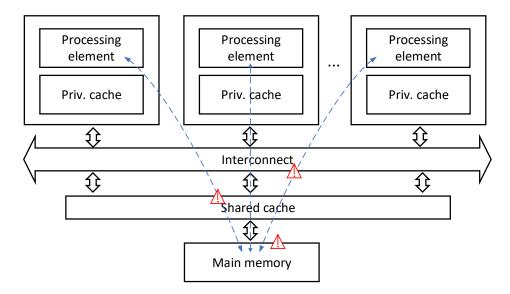

In MPSoC systems, the processing elements share system resources such as buses, memories, caches, etc. These shared resources provide different influences to timing behaviors of MPSoC systems. Fig. 1.2 presents different types of shared resources existing in a MPSoC system. A private cache is accessible only by each PE. A shared cache is used by all the PEs. Both private and shared caches are used to temporarily store data to reduce the large latency between the PE and main memory. The PEs access to the shared caches and main memory via an interconnect.

Figure 1.2 – Different types of shared resources in MPSoCs: buses, memories (main memory, private caches), shared caches. Interferences occur while the processing elements access to the shared resources at same time.

Concurrent accesses to shared resources cause interferences. These interferences lead to undesired additional delays in the application execution time. Different mechanisms causing additional delays in Commercial off-the-shelf (COST) multi-processors were presented by Kotaba et al. in [4]. For example, contention on shared bus can come from concurrent accesses of multiple cores, or other device, such as IO, DMA, etc. In shared memory, interleaved accesses by multiple

cores cause additional delays for cores. For dynamic memory, additional delays can come from memory refresh.

In [5], Abel et al. classified shared resources into two classes: bandwidth resources and storage resources. The bandwidth resource corresponds to the situation when several tasks access to this resource at the same time. However, this resource only allows one access at a time. An arbitration policy is thus used to manage the order of access of these tasks. It allows one task to access to this resource and delays the others. One example of bandwidth resource is shared bus. The arbitration policies are divided into three main classes:

- *Time-driven arbitration* uses a predefined bus schedule which assigns time slot of fixed size to particular PEs (e.g., *Time Division Multiple Access* (TDMA)).

- Event-driven arbitration decides at run-time, which PE is granted the access to the resource during the next time slot. These decisions usually depend on the access histories of all PEs (e.g., Round Robin or First Come First Serve (FCFS)).

- *Hybrid arbitration* splits their arbitration period into segments of fixed length. Static segments use *Time-driven resource arbitration* and dynamic segments use *Event-driven resource arbitration* (e.g., *FlexRay* a bus protocol used in the automotive industry of this strategy).

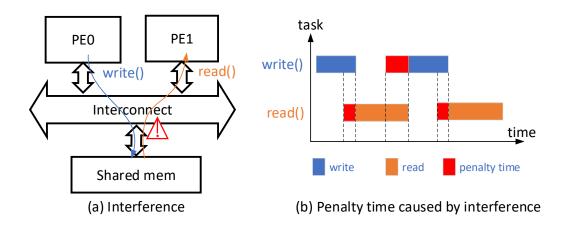

Figure 1.3 – Interference on bus to access to the shared memory (a) causes penalty time (b).

Fig. 1.3 presents the interferences caused by concurrent accesses to the bus. In Fig. 1.3 (a), two PEs attempt to access the shared memory via an interconnect. One PE tries to write data to the shared memory and another one tries to read data from the shared memory. The bus arbitration policy in this case is First-Come-First-Served. Then in Fig. 1.3 (b), the execution process of these two PEs is presented. The first write function is executed and the first read function is delayed. The second write function is also delayed until the end of the first read

function. Similarly, the second read function is delayed by the second write function. The delay duration caused by the bus interference is called *penalty time*.

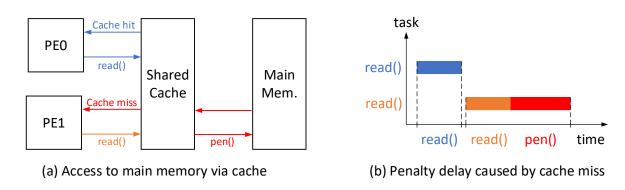

The storage resource relates to the situation when one task changes the state of the shared resource which is being used by a second task. This situation causes an additional delay for the second task. The examples of storage resource are shared memories and shared caches. Multiple accesses to main memory via shared cache might cause penalty delays. In Fig. 1.4 (a), we present an example in which two PEs access to main memory via a shared cache. Cache hit occurs when PE0 attempts to read data from the main memory and this data is available on shared cache. For PE1, the data is not available on the shared cache (i.e, cache miss) and it has to load data

Figure 1.4 – Accessing to the main memory via cache (a) and a penalty delay caused by a cache miss (b) leads to longer execution time.

from main memory. In Fig. 1.4 (b), the execution time to read data of two PEs is presented. The first read function needs only the read time from the cache. The second read function gets slower execution time with additional penalty delay caused by the cache miss. Different cache replacement policies are used to reduce cache misses. These policies help the cache to identify which data should be removed to make space for new data that needs to be added. Furthermore, they improve both precision and efficiency of a cache analysis. In [6], Monniaux et al. presented in detail some following cache replacement policies.

- Least-Recently Used (LRU) evicts the data block least recently used when a cache miss occurs. On a miss, the oldest block is replaced by a new one, which has age 0 and the ages of all other blocks are incremented.

- Pseudo-LRU (PLRU) improves the performance of the LRU algorithm by evicting data block using approximate measures of age rather than maintaining the exact age of every data block in the cache.

- *First-In-First-Out* (FIFO) evicts the data block in the order they were added without depending on how often or how many times they were accessed before.

In the performance verification of MPSoC systems, timing behaviors are among priorities to be analyzed, especially the task execution time. As summarized by Mitra et al. in [7], the task execution time can variate depending on both software tasks and hardware resources where the tasks are executed.

- From the software perspective, the execution time of a task depends on its input. Different input data can be processed following different execution paths through the program leading to different execution times.

- From hardware perspective, the variability in the execution time is caused by interferences between tasks accessing shared resources.

We denote the ability to predict timing behaviors of MPSoC systems as timing predictability. Since many hardware resources are involved in the task execution, the execution time becomes more difficult to be predicted. We refer the task execution time on each hardware element as elementary timing. The characterization of these elementary timings is crucial for the timing predictability of an application made of multiple tasks and allocated to a multip-processor platform. In the scope of this thesis, we focus on capturing timing variability from hardware perspectives caused by shared resource effects. In the next section, we introduce the notion of timing compositionality which represents the ability to exhibit different shared resource effects of MPSoC systems.

#### 1.1.3 Timing compositionality of MPSoC systems

Before defining the timing compositionality, Hahn et al. [8] provided a notion of decomposition of a system's timing into the timing contributions of its components. The system states are related with the corresponding states of each component by the decomposition. Furthermore, the decomposition provides a combination function that combines the timings of the individual components and captures the type of composition. The complexity of the combination function depends on the chosen decomposition. The timing compositionality is then defined that the timing behavior of a system can be inferred from the timing contributions of its constituent components and the type of composition. For example, given a MPSoC system consisting of multiple processors that access to a shared memory via a shared bus, the execution time of the program running on one processor can be predicted from its computation time, the memory access time and the bus blocking time.

The type of composition is classified based on two following notions *timing anomalies* or *domino effects* as defined in [9, 10, 11].

— A timing anomaly is a situation where the local worst-case does not contribute to the global worst-case. In [12], different potential sources can lead to timing anomalies, such as: scheduling, branch prediction, cache and cache replacement policy.

Figure 1.5 – Classification of architectures according to the level of resources compositionality

— A domino effects is a situation where the difference in timing between two states cannot always be bounded by a constant. For example, given a program loop, the difference in execution time between states of the pipeline (or caches, or other hardware resource) increases in each iteration.

In [13], Cullmann et al. classified three types of MPSoC architectures depending on whether they exhibit timing anomalies and/or domino effects. These architectures are illustrated in Fig. 1.5.

- 1. Fully timing compositional architectures does not exhibit timing anomalies or domino effects. In this case, a local worst-case path can be analyzed safely without considering other paths. In this thesis, we consider a hardware platform with predictable computation time due to un-cached local and exclusive data and instruction memory.

- 2. Compositional with constant bounded effects architectures exhibit timing anomalies but no domino effects. The analysis has to consider the effects of local data/instruction caches (L1 caches as illustrated in Fig. 1.5). Possible cache misses are caused by the difference between cache size and data in the main memory. In general, an analysis has to consider all execution paths. A trade-off between precision and efficiency is to safely discard local non-worst-case paths by adding a constant number of cycles to the local worst-case path. The Infineon TriCore [14] is an example of this class.

3. Non-compositional architectures exhibit domino effects and timing anomalies. Different level of caches are taken into account in the analysis. Possible cache misses are caused by the replacement of data on shared cache (L2 cache) by processors. For such architectures timing analyses always have to follow all paths since a local effect may influence the future execution arbitrarily. In [15], Schneider presented a domino effect in the pipeline of the PowerPC 755.

To evaluate such architectures, appropriate modeling and analysis approaches are needed to describe and analyze timing behaviors. In the next section, we aim to present the performance evaluation of MPSoC systems related to different timing analysis approaches.

#### 1.2 Performance evaluation of MPSoC systems

#### 1.2.1 Hardware/software codesign

Hardware/software codesign approaches aims to concurrently design hardware and software components of embedded systems. The main objective is first to meet design constraints such as cost, performance, and power of the product and secondly to reduce the time-to-market of the product [16].

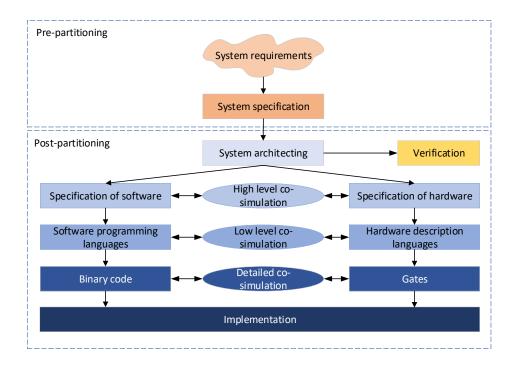

Figure 1.6 – Hardware/software codesign with pre-partitioning and post-partitioning phases. System level verification captures the system performance early in the design process.

In Fig. 1.6, the hardware and software codesign steps with the pre-partitioning and post-partitioning are illustrated. In the pre-partitioning, the codesign process first identifies the system requirements to be satisfied. The system architecting represent the considered system using system level design (SLD) tools. This high level system design avoids detailed consideration of the system. However, it requires availability of reliable estimations about component models to create an accurate system. As illustrated in [16], a 10% error is acceptable at this phase. At system level, a high level of modeling language can be used to describe the considered system, for example Unified Modeling Language (UML). In this thesis, we focus on the verification step which allows early exploration of the system performance by using the simulation-based or formal approaches.

Different abstraction levels of hardware/software codesign are then illustrated in the post-partitioning steps of Fig. 1.6. From the software side, the functional specification of software such as the computation and communication parts can be mapped and scheduled on one or multiple processing elements. This step can be done by using a target programming languages such as C, C++. At the binary code level, the software code such as a function, a method or a basic block is compiled and linked to the selected hardware platform to build an executable description [1]. From the hardware side, processes and tasks are implemented as hardware accelerators are synthesized down to RTL description by using hardware description languages such as VHDL, Verilog. At the gates level, the granularity of the objects considered during logic synthesis are implemented by using logic gates and flip flops. Finally, the implementation of an application executing on a hardware platform is for validation and verification purposes. The efficiency of the proposed system level model can be evaluated by comparing the simulation results with the implemented results.

Several languages have been proposed as intermediate solution for system design, for example SystemC [17] and SpecC [18], [19]. SystemC is a class library of C++, while SpecC is a superset of ANSI C. They provide useful data types and concurrent programming structures for describing both software and hardware parts.

System level design approaches have been proposed to allow estimation of HW/SW architecture performances early in the design process. In system level design approaches, workload models are used to capture the influence of application execution on platform resources. Timing properties of architectures and related power consumption can then be assessed under different working scenarios. However, the efficiency of system level design approaches strongly depends on the created HW/SW architecture models that should deliver both fast analysis time and good accuracy. Especially, captured workload models should correctly abstract low-level details of system components but still provide good estimations about the whole system performance. High-level models must capture the possible variability in multi-core platform resources usage caused by cache management, bus interleaving, and memory contention. The creation of efficient

architecture models represents thus a time-consuming effort that limits the efficiency of current system level approaches.

The different categories of system-level analysis approaches are discussed in the next sections.

#### 1.2.2 Simulation-based analysis approaches

Simulation-based approaches are proposed to partially test system properties. Different simulation-based approaches have been compared in [20] to support evaluation of multi-core architecture performance early in the design process. In the existing approaches, models of hardware-software architectures are formed by combining an application model and a platform model. In the early design phase, full description of application functionalities is not mandatory and workload models of the application are used. A workload model expresses the computation and communication loads (e.g., time, power consumption, memory cost) that an application causes when executed on a hardware platform. The captured performance models are generated as executable descriptions and simulated. The execution time of each load primitive is approximated as a delay. Delays are typically estimated from measurements on real prototypes or analysis of low level simulations. SystemCoDesigner [21], Daedalus [22], SCE [19], and Koski [23] are good examples of academic approaches. Other existing academic approaches are presented by Kreku et al. in [24] and by Arpinen et al. in [25]. Simulation-based approaches require extensive architecture analysis under various possible working scenarios. Since the possible working scenarios of the created models are very huge, the created models can not be exhaustively simulated in a reasonable analysis duration and worst-case working scenarios are hardly identified and assessed. One other important issue concerns the accuracy of created models. As architecture components are modeled as abstractions of low level details, there is no guarantee that the created architecture model reflects with good accuracy the whole system performance. Finally, with the rising complexity of MPSoC platforms, execution of simulation models requires more simulation time. In the next section, formal analysis approaches are presented which provide a more exhaustive analysis of system state space.

#### 1.2.3 Formal analysis approaches

Due to insufficient corner case coverage, simulation-based approaches are limited to determine guaranteed bounds of system properties. Different formal approaches have thus been proposed to analyze multi-core systems and provide time bounds. These formal approaches are commonly classified as *analytical* methods and *state-based* methods.

Most of the available static real-time methods are of analytical nature. An overview of such methods are given in [26]. Since analytical methods depend on solving closed-form equations, they have the advantage of being scalable to analyze large-scale systems. However, analytical methods abstract from state-based modus operandi of the system under analysis (SUA) leads

to pessimistic over-approximated results compared to state-based real-time methods [26]. For example, such systems can be complex state-based arbitration protocols or inter-processor communication task dependencies. Analytical methods that combine analysis of processor and bus scheduling for distributed embedded systems can be classified as *holistic* methods [27], [28], [29] and *compositional analytical* methods [30], [31].

State-based real-time methods are based on representing the SUA as a transition system (states and transitions) and since they reflect the real operation states of the actual system behavior, tighter results can be obtained compared to analytical methods. Many recent approaches for software timing analysis on many- and multi-core architectures are built on state-based analysis techniques. The two main considered application classes are streaming applications (modeled as synchronous data flow graphs) [32], [33] and generic real-time task-based applications [34], [35].

Figure 1.7 – Comparison different formal approaches according to the achievable accuracy and analysis time (a) and the obtained accuracy with the rising of problem size (b).

In Fig. 1.7, we compare different formal approaches according to the achievable accuracy and analysis time (a) and the potential gain in addressable problem size (b). As illustrated, state-based approaches provide tighter results compared to analytical (holistic and compositional) approaches. However, state-based approaches allow exhaustive analysis of system properties at the expense of time-consuming modeling and analysis effort. Analytical approaches can address more complex systems.

#### 1.2.4 Probabilistic analysis approaches

Probabilistic approaches are a combination of probabilistic models and analysis techniques. In the context of embedded systems, they represent a means of capturing system variability. In this context, variability mainly comes from system sensitivity to environment and low level effects of hardware platforms. Probabilistic models can be used to appropriately capture this variability. Probabilistic models are extensions of labeled transition system and allow variations about execution times and state transitions to be considered, for example the discrete time Markov chains or Markov automata, etc. Analysis of probabilistic models allow quantitative measures to be obtained. As an illustration, the adoption of probabilistic model checking for evaluation of dynamic data-flow behaviors is presented in [32]. Markov automata is used as the fundamental probabilistic model to capture and analyze architectures. Characteristics as application buffer requirements, timing performance, and platform energy consumption are estimated. However, this approach is restricted to fully predictable platforms, with low influence of platform resources on timing variations.

Probabilistic approaches that combine simulation and formal approaches appear to be a good compromise to deliver both accuracy and limited exploration effort. Statistical Model Checking (SMC) [36] has been proposed as an alternative to formal approaches to avoid an exhaustive exploration of the state-space model. SMC refers to a series of techniques that are used to explore a sub-part of the state-space and provides an estimation. SMC designates a set of statistical techniques that present the following advantages:

- As classical model checking approach, SMC is based on a formal semantic of systems that allows inference of behavioral properties. SMC is used to answer qualitative questions (Is the probability for a model to satisfy a given property greater or equal to a certain threshold?) and quantitative questions (What is the probability for a model to satisfy a given property?).

- It only requires an executable model of the system that can be simulated and checked against state-based properties expressed in temporal logics. The observed executions are processed to decide with some confidence whether the system satisfies a given property.

- As a simulation-based approach, it is less memory and time intensive than exhaustive approaches. SMC can thus be seen as a trade-off between testing and formal verification.

This approach has been considered in various application domains [37]. First, SMC allows to approximate systems that can not be assessed with an exhaustive approach. Second, it only requires a simulation model of the system, that can be checked against state-based properties. Various existing probabilistic model checkers have been extended to support statistical approach. PRISM [38] is based on a symbolic model checker that relies on numerical techniques. UPPAAL-SMC [37] is a statistical model checking extension for the UPPAAL model checker. Plasma-Lab

[39] is a modular and extensible statistical model checker that can be extended with external simulator and checkers. The use of Plasma-Lab to carry out statistical analysis for systems modeled in SystemC is presented in [40]. SMC has been adopted in [41] to evaluate a many-core architecture. A statistical model checking tool called BIP-SMC was proposed in [42]. It was used to evaluate the probability that some timing aspects (e.g. execution time, variability of processing time) were bounded. A very recent work in [43] demonstrates the applicability of SMC for a quantitative evaluation of uncertainty-aware hybrid AADL designs [43] (of a train control system) against various performance queries. However, adoption of SMC techniques to analysis of multi-core systems have rarely been considered. This can be explained by the large amount of required effort to setup this approach. Creation of probabilistic models remains a difficult task and is not well supported for multi-core systems. This thesis aims at delivering some practical guidelines to facilitate the creation of probabilistic models and favour the adoption of probabilistic analysis approaches for multi-core systems.

#### 1.3 Contributions and organization of the manuscript

In the scope of this thesis, we aim to study the way adoption of probabilistic modeling and timing analysis methods of MPSoC systems. The main contributions of this work are:

- 1. Since the lack of a systematic evaluation workflow leads to difficulties to use probabilistic approaches, a new evaluation workflow is proposed to evaluate the these approaches. This workflow is based on three main parts: (1) A measurement-based approach is first used to characterize timing behaviors of the execution of application on a real platform. This characterization is done in both computation and communication parts, (2) A probabilistic modeling approach implements both software and hardware parts on a specific programming language. This implementation captures the variation of the execution time by using the statistical timing models, and (3) A probabilistic analysis approach is based on statistical model checking (SMC) which estimates a probability that our probabilistic model can satisfy a timing property.

- 2. At transaction-level, the simulation process remains slow which causes difficulties to analyze complex systems. We propose a message-level communication model of a multiprocessor bus to deliver fast yet accurate simulation results.

- 3. A probabilistic analysis approach which considers statistical model checking (SMC) approach for MPSoCs is taken into account. This SMC approach partially explore system state-space, but still makes possible to bound the probability of making an error about predictions by controlling the number of simulation runs by using statistical algorithms. In this analysis, the effects of the statistical algorithms parameters to the analysis results are further investigated.

The remains of this manuscript is organized as follows:

- Chapter 2 gives an overview of the state of the art, comparing the existing timing analysis approaches and accuracy/simulation speed improvement approaches.

- Chapter 3 presents our workflow which is the working environment with the related the model of architecture (MoA), the model of computation (MoC), the measurement infrastructure and the simulation model. Some case-studies are presented and results achieved with the developed environment are given.

- Chapter 4 introduces the message level communication model. This high level model improves the simulation model in both accuracy and simulation speed. The proposed model showed a significant simulation speed-up comparing to the transaction-level model (TLM) without degrading the analysis accuracy.

- Chapter 5 presents the probabilistic timing analysis approach. We aim to demonstrate the efficiency of statistical model checking approach for timing analysis of MPSoCs. A further study about different statistical algorithms is provided in this chapter. An extension of the hardware architecture with private cache for each tile is presented. Analysis results of such system show a good level of accuracy.

- Chapter 6 summarizes the contributions and provides different perspectives and future work.

## STATE OF THE ART

In the previous chapter, we introduced the context of our work. Different analysis approaches can be used to verify the performance of MPSOC systems. Probabilistic approaches are proposed to capture the variability of the execution time caused by contentions at shared resources. In this chapter, we first review the performance analysis approaches for MPSoC systems. These approaches are compared regarding their analysis effort, their accuracy and their scalability. Second, we specifically discuss some existing works that were proposed to improve the efficiency of system-level simulation-based approaches.

#### 2.1 Performance analysis approaches

Analysis approaches are commonly classified as (1) simulation-based approaches, which partially test system properties based on a limited set of stimuli, (2) formal approaches, which check system properties in an exhaustive way, and (3) hybrid approaches, which combine simulation-based and formal approaches.

#### 2.1.1 Simulation-based approaches

In this section, we present simulation-based approaches. We emphasize the way performance models are created. Then we present the considered use-cases and the obtained results. Several simulation-based approaches were compared in [44], such as SystemCoDesigner [21], Daedalus [45, 46], system-on-chip environment (SCE) [19, 47] and Koski [48] which are good examples of academic approaches.

SystemCoDesigner presented in [21] is an SystemC-based electronic system level (ESL) design framework for design space exploration (DSE). It allows to automatically map applications into a heterogeneous MPSoC platform. The SystemCoDesigner design flow starts by describing an application as an actor-oriented model using SystemC. Some or all actors are then generated using behavioral synthesis to create architecture templates. An architecture template contains all possible hardware modules, processors and the communication infrastructure. Design space exploration is used to select the best architecture solution that fulfills the user requirements, such as the overall throughput and required hardware resources. From a set of obtained solu-

tions, the designer selects promising implementations for rapid prototyping on FPGAs. In [21], Keinert et al. implemented a Motion-JPEG decoder case study. The DSE evaluated 7600 different solutions over  $5.10^{33}$  possible solutions in 2 days 17 hours 46 minutes. The exploration time for each solution is about 30 seconds. In fact, it took a lot of time to explore a very small part of the solution space and good solutions could be missed. There were 366 solutions found and several of these solutions were implemented onto a Xilinx Virtex II FPGA (XC2V6000). Different objectives were evaluated such as: 1) throughput; 2) latency; 3) number of required flip-flops; 4) lookup tables (LUTs); and 5) block random access memories (BRAMs). The FPGA implementations results showed differences in latency and throughput up to 30% comparing to the performance estimations during DSE due to scheduling overhead. The estimated hardware resources during DSE required 15% more than in the implementation on FPGA. The accuracy of the performance model of this approach still needs to be improved.

Daedalus is a system-level design flow for MPSoC based embedded multimedia systems. It provides a high automation of design space exploration (DSE), system-level synthesis, application mapping, and system prototyping of MPSoCs. The Daedalus design flow is detailed in [45, 46], it consists of three main steps implemented by the KPNgen, Sesame and ESPAM tools. In the first step, a sequential application specification written in C or C++ is automatically converted into a parallel Kahn Process Network (KPN) specification using the KPNgen tool. In the second step, the generated KPNs are then used by the Sesame modeling and simulation environment to perform system-level architectural DSE. Sesame evaluates the performance of different applications to architecture mappings, hardware/software partitionings, and target platform architectures. More details about Sesame tool can be found in [49]. In the third step, the ESPAM tool takes as input the specifications of promising candidate system designs obtained from the previous step. It automatically generates synthesizable VHDL that implements the candidate MPSoC platform architecture. The target MPSoC of Daedalus is composable MP-SoCs, in which the IP components are strictly composed. This prototyping allows to calibrate and validate the created performance models. Several case studies were used to demonstrate the feasibility of Daedalus approach. In [45], Thompson et al. explored different implementation option for a Motion-JPEG encoder case study running on a 4 heterogeneous processor MPSoC. The case study state space was exhaustively explored with 10148 solutions in 2.5 hours. The exploration time for each solution is less than 1 second which is much faster than in the System-CoDesigner approach. Several solutions were used for the prototyping on Xilinx Virtex II Pro FPGA (xc2cp20). The estimated simulations showed an average error of 12% and worst-case error of 19% to the FPGA implementations which still need to be improved. Another work about Daedalus approach presented by Nikolov et al. in [46] that performed a DSE study of a JPEG encoder application executing on both homogeneous (MicroBlaze processors) and heterogeneous (MicroBlaze processors and Discrete Cosine Trans-form (DCT) IP cores) MPSoCs. The number

of processing cores is up to 30. They achieved a performance speed-up of up to 20x compared to a single processor system. The DSE experiments and the real implementation of 25 different hardware solutions on Xilinx Virtex II-6000 FPGA were performed within 5 days with around 70% of this duration taken by the low-level commercial synthesis and place-and-route FPGA tools. They presented a very good accuracy with the error between the estimated models and real implementation is around 5%. However the experiment duration is still long while exploring a limited number of hardware solutions.

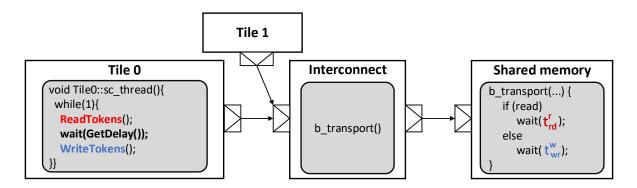

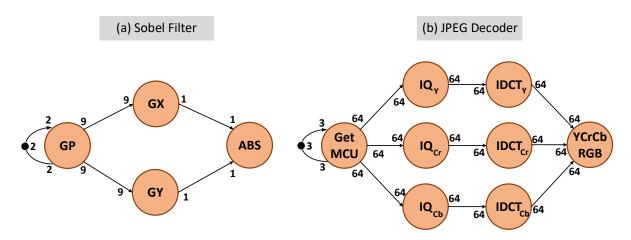

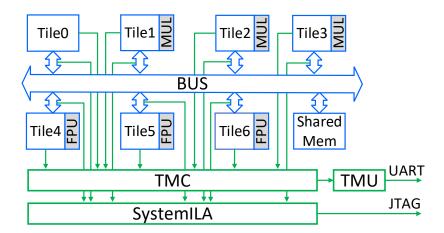

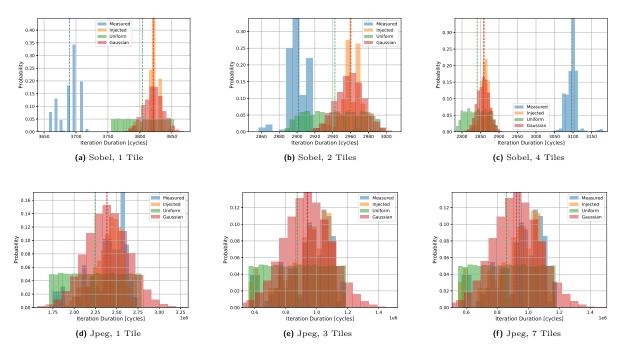

The system-on-chip environment (SCE) [19, 47] implements an automated system design flow from specification down to hardware/software implementation. The SCE design flow starts with an abstract model specifying the design functionality. The design flow then explores the design space consisting of the architecture, scheduling and network exploration to make different design decisions. A new lower level of abstraction model is refined by integrating design decisions into the previous model. In the next phase, hardware/software synthesis is performed. Hardware synthesis takes behavioral hardware models down to structural register-transfer level (RTL) descriptions. While in software synthesis, application written in SpecC [18], middleware, drivers and interrupt handlers are generated, cross-compiled, and targeted toward and linked against real time operating system (RTOS) to create a final target binaries. In SCE, all design steps are integrated under a common graphical user interface (GUI). The GUI provides interactive and visual design model and database browsing, decision entry, and design analysis. For the case study, they demonstrated the design space exploration of their approach by considering six industrial examples: the JPEG encoder, the GSM voice codec, floating- and fixed-point versions of an MP3 decoder and the GSM vocoder. For each example, they considered different architectures using Motorola DSP56600, Motorola ColdFire and ARM7TDMI processors together with custom hardware coprocessors and I/O units. They used various communication architectures with DSP, CF, ARM (AMBA AHB) and simple handshake busses. The exploration duration of the design space for each example is about few seconds. Timing errors range from 12.5% down to an average of 3% depending on back annotation of profiling or trace-based estimates.