# Secure Hardware Accelerators for Post Quantum Cryptography

Timo Zijlstra

#### ▶ To cite this version:

Timo Zijlstra. Secure Hardware Accelerators for Post Quantum Cryptography. Cryptography and Security [cs.CR]. Université Bretagne Sud, 2020. English. NNT: tel-02953277v1

### HAL Id: tel-02953277 https://hal.science/tel-02953277v1

Submitted on 30 Sep 2020 (v1), last revised 26 Feb 2021 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

# L'UNIVERSITÉ DE BRETAGNE SUD

Comue Université Bretagne Loire

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Informatique

Par

### « Timo ZIJLSTRA »

« Accélérateurs matériels sécurisés pour la cryptographie postquantique »

Thèse présentée et soutenue à « Lorient », le « 28/09/2020 »

Unité de recherche : Lab-STICC

Thèse Nº: 564

#### Rapporteurs avant soutenance :

Lilian BOSSUET Professeur des Universités, Université Jean Monnet Saint-Étienne Régis LEVEUGLE Professeur des Universités, Grenoble INP, Université Grenoble Alpes

**Composition du Jury:**

Président : Jean-Claude BAJARD Professeur des Universités, Université de Paris (UPMC)

Examinateurs: Nele MENTENS Professeur des Universités, Université Leiden / Université KU Leuven

Jean-Claude BAJARD Professeur des Universités, Université de Paris (UPMC)

Dir. de thèse: Arnaud TISSERAND Directeur de Recherche, CNRS

Co-enc. de thèse : Karim BIGOU Maître de conférences, Université de Bretagne Occidentale

Invité(s):

Benoît GÉRARD Expert, DGA

# Contents

| 1 | Intr | roduction                                              | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Context                                                | 1  |

|   | 1.2  | Objective and outline of the thesis                    | 8  |

| 2 | Def  | finitions and Notations                                | 11 |

| 3 | Stat | te of the Art                                          | 15 |

|   | 3.1  | Introduction                                           | 15 |

|   | 3.2  | Public-Key Encryption                                  | 15 |

|   | 3.3  | Lattice Problems                                       | 16 |

|   |      | 3.3.1 Cryptosystem                                     | 19 |

|   | 3.4  | Ideal Lattices and RLWE                                | 20 |

|   |      | 3.4.1 CPA and CCA Security                             | 21 |

|   |      | 3.4.2 Generalization and Module LWE                    | 23 |

|   |      | 3.4.3 NTRU                                             | 26 |

|   |      | 3.4.4 LWR                                              | 26 |

|   | 3.5  | Implementation of LWE-based Cryptography               | 27 |

|   |      | 3.5.1 Modular arithmetic                               | 27 |

|   |      | 3.5.2 Polynomial arithmetic                            | 28 |

|   |      | 3.5.3 Lattice Cryptography on FPGA                     | 32 |

|   | 3.6  | Side-Channel Attacks                                   | 35 |

|   |      | 3.6.1 SCAs on Lattice Cryptography and Countermeasures | 37 |

| 4 | Imp  | plementation Environment                               | 41 |

|   | 4.1  | Introduction                                           | 41 |

|   |      | 4.1.1 FPGAs                                            | 41 |

|   |      | 4.1.2 High Level Synthesis                             | 43 |

|   |      | 4.1.3 HLS and Cryptography                             | 43 |

|   | 4 2  | Finite-Field Arithmetic using HLS                      | 4: |

|   |                        | 4.2.1 Implementation results                              | 46            |  |  |  |  |  |  |  |

|---|------------------------|-----------------------------------------------------------|---------------|--|--|--|--|--|--|--|

|   | 4.3                    | Schoolbook Algorithm for Polynomial Multiplication        | 50            |  |  |  |  |  |  |  |

| 5 | $\mathbf{L}\mathbf{W}$ | E, RLWE and MLWE on FPGA                                  | 59            |  |  |  |  |  |  |  |

|   | 5.1                    | Introduction                                              | 59            |  |  |  |  |  |  |  |

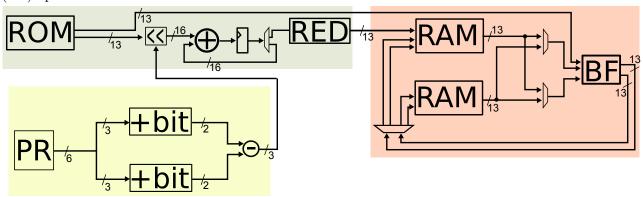

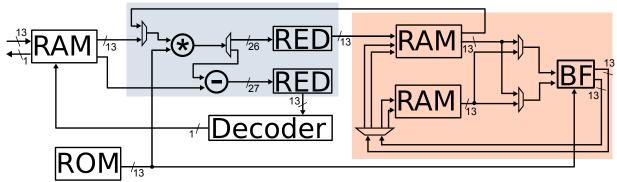

|   | 5.2                    | Implementation of main operations                         | 60            |  |  |  |  |  |  |  |

|   | 5.3                    | FPGA Implementation of LWE                                | 62            |  |  |  |  |  |  |  |

|   |                        | 5.3.1 Parameters used in the implementations              | 32            |  |  |  |  |  |  |  |

|   |                        | 5.3.2 Matrix arithmetic for LWE                           | 63            |  |  |  |  |  |  |  |

|   |                        | 5.3.3 Parallelization using HLS                           | 64            |  |  |  |  |  |  |  |

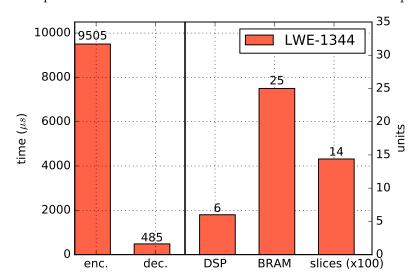

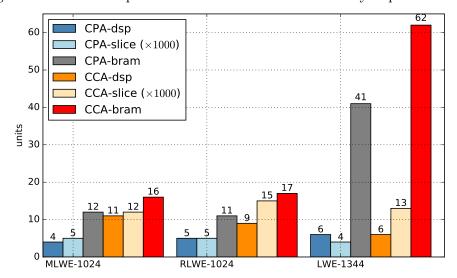

|   |                        | 5.3.4 Implementation results                              | <sub>35</sub> |  |  |  |  |  |  |  |

|   | 5.4                    | RLWE Implementations                                      | 66            |  |  |  |  |  |  |  |

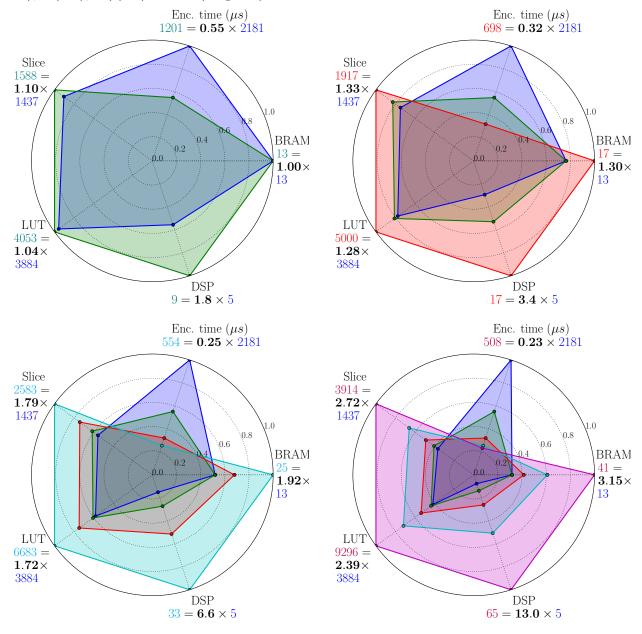

|   |                        | 5.4.1 Optimizing the area utilization                     | 69            |  |  |  |  |  |  |  |

|   | 5.5                    | MLWE implementations and comparison                       | 70            |  |  |  |  |  |  |  |

|   |                        | 5.5.1 Modifying the RLWE implementation                   | 70            |  |  |  |  |  |  |  |

|   |                        | 5.5.2 Parallelization of operations in $\mathcal{R}_q^k$  | 72            |  |  |  |  |  |  |  |

|   |                        | •                                                         | 72            |  |  |  |  |  |  |  |

|   |                        | 5.5.4 Implementation results                              | 74            |  |  |  |  |  |  |  |

|   | 5.6                    | Randomness generation and CCA implementations             | 76            |  |  |  |  |  |  |  |

|   |                        | 5.6.1 Rejection sampling                                  | 76            |  |  |  |  |  |  |  |

|   |                        | 5.6.2 Alternative PRNG                                    | 76            |  |  |  |  |  |  |  |

|   |                        | 5.6.3 CCA secure implementations                          | 77            |  |  |  |  |  |  |  |

|   | 5.7                    |                                                           | 80            |  |  |  |  |  |  |  |

|   | 5.8                    | Conclusion                                                | 32            |  |  |  |  |  |  |  |

|   |                        |                                                           |               |  |  |  |  |  |  |  |

| 6 |                        | ountermeasures against Side-Channel Attacks 84            |               |  |  |  |  |  |  |  |

|   | 6.1                    |                                                           | 34            |  |  |  |  |  |  |  |

|   |                        | v                                                         | 34            |  |  |  |  |  |  |  |

|   | 6.2                    |                                                           | 38            |  |  |  |  |  |  |  |

|   | 6.3                    | New Variants of State of the Art Protections              | 92            |  |  |  |  |  |  |  |

|   |                        |                                                           | 92            |  |  |  |  |  |  |  |

|   |                        | 6.3.2 Modified Shifting                                   | 95            |  |  |  |  |  |  |  |

|   |                        | 6.3.3 Blinding                                            | 95            |  |  |  |  |  |  |  |

|   |                        | 6.3.4 Shifting and Blinding Combined                      | 96            |  |  |  |  |  |  |  |

|   | 6.4                    | New Protections                                           | 96            |  |  |  |  |  |  |  |

|   |                        | 6.4.1 Shuffling                                           | 96            |  |  |  |  |  |  |  |

|   |                        | 6.4.2 Randomization using Redundant Number Representation | 00            |  |  |  |  |  |  |  |

|   | 6.5                    | Comparison of all Protections                             | )2            |  |  |  |  |  |  |  |

|   | 6.6                    | Gener  | alizing the Countermeasures to Apply to MLWE/LWE | 104 |  |  |

|---|------------------------|--------|--------------------------------------------------|-----|--|--|

|   |                        | 6.6.1  | Masking                                          | 104 |  |  |

|   |                        | 6.6.2  | Blinding                                         | 107 |  |  |

|   |                        | 6.6.3  | Shifting                                         | 107 |  |  |

|   |                        | 6.6.4  | Shuffling                                        | 108 |  |  |

|   |                        | 6.6.5  | Redundant number representation                  | 109 |  |  |

|   | 6.7                    | Conclu | usion and Discussion                             | 109 |  |  |

| 7 | Con                    | clusio | n                                                | 110 |  |  |

| R | Résumé en français 113 |        |                                                  |     |  |  |

# Chapter 1

## Introduction

#### 1.1 Context

An increasing number of electronic devices require the ability to exchange data in a secure manner. A secure application for sending and receiving messages for example, must ensure the confidentiality and authenticity of exchanged messages. *Encryption* is the cryptographic tool that is used to guarantee confidentiality. It uses mathematical functions that are easy to compute but hard to invert. Only with a so-called *key* the inverse function can be computed. An encryption of the message is obtained by applying such a function to the message, or *plaintext*. The content of the encrypted message, or *ciphertext*, can only be read by those who hold the key to invert the encryption function. Inverting the encryption and recovering the message is called *decryption*. Symmetric-key cryptography deals with the encryption and decryption of the message, assuming that both sender and receiver have the key to encrypt and decrypt. It is symmetric in the sense that the same key must be used for both encryption and decryption.

Symmetric-key encryption requires that both sender and receiver already have a shared key. Before being able to use symmetric-key encryption, such a key must be created and shared in a secure way. A key exchange protocol consists of an (unsecure) exchange of data over a public channel between two parties Alice and Bob. The goal of the protocol is to have both parties ending up with the same piece of pseudo-random information, which can then be used as a key for use in symmetric-key encryption. It must be ensured that the public data exchanged over the public channel do not reveil any information about the shared key created using this data.

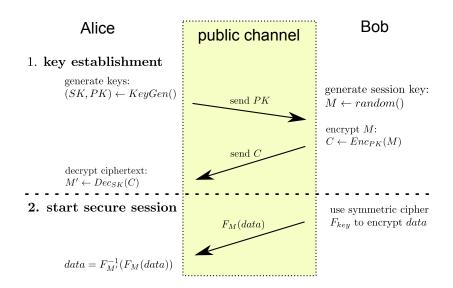

The data exchanged between Bob and Alice is sent over a public channel (see figure 1.1). It is assumed that there is always an eavesdropper that is able to intercept anything sent over this channel. This makes a secure key establishment particularly difficult. The problem is that any straightforward method of sharing a key would give away information about the key to the eavesdropper. The solution is found in a clever use of *computationally hard problems*. These are mathematical problems for which no efficient algorithm is known. Such a problem cannot be solved within a reasonable computation

Figure 1.1: Using symmetric and asymmetric cryptography to exchange confidential data from Bob to Alice. SK is the secret key, PK the public key and C the ciphertext. If C is decrypted correctly, then M = M' and the data that Alice obtains is equal to Bob's data.

time. Computationally hard problems allow to construct *trapdoor* functions, which are typically used as decryption function in public-key encryption schemes.

The discrete logarithm is an example of a computationally hard problem. Let g be a multiplicative generator of  $(\mathbb{Z}/p\mathbb{Z})^*$  for some prime number p. The discrete logarithm problem is to find the value of a given g and  $g^a \mod p$  for some integer a. The number of computations needed to solve this problem is proportional to the size of the parameter p. To find the discrete logarithm of  $g^a \mod p$  using a brute force approach, one must compute  $g^i \mod p$  for increasing i until finding a value for which  $g^i \equiv g^a \mod p$ . For sufficiently large p, it may take years to solve an instance of the discrete logarithm problem. Key exchange protocols are designed in such a way that the (secret) key can only be deduced from the (publicly) exchanged data by solving the underlying hard problem.

The Diffie-Hellman protocol [47] uses a prime number p and a multiplicative generator g of  $(\mathbb{Z}/p\mathbb{Z})^*$  as public parameters. Alice and Bob pick a random integer a and b and compute the values  $g^a \mod p$  and  $g^b \mod p$  respectively. These values are then sent over the public channel. The random integers a and b are kept secret. Alice receives  $g^b \mod p$  and computes  $(g^b)^a \mod p$ . Bob, who picked b, receives  $g^a \mod p$  and computes  $(g^a)^b \mod p$ . Since  $(g^a)^b \equiv g^{ab} \equiv (g^b)^a \mod p$ , both Alice and Bob end up with the same element  $g^{ab} \mod p$ . This element forms the secret key to be used with a symmetric encryption method for the remainder of the encrypted communication between Alice and Bob.

The eavesdropper on the public channel intercepts  $g^a \mod p$  and  $g^b \mod p$ . To compute  $g^{ab} \mod p$ , either a or b has to be computed using only the information  $g^a \mod p$  and  $g^b \mod p$ . This is the discrete logarithm problem described above: to *break* the protocol (i.e. to find the key), one must compute a

discrete logarithm. Assuming that p is sufficiently large, it is not practical to solve this problem and therefore the key exchange is secure. In order for the protocol to be useful in practice, it is essential that the number of computations needed by the eavesdropper to break the scheme, be significantly greater than the number of computations performed by the two legitimate parties. In the worst case, the eavesdropper will compute  $g^i \mod p$  for integer 0 < i < p-1, before finding a or b. Alice and Bob on the other hand, only perform two exponentiations each. Let  $n = 1 + \lfloor \log_2(p) \rfloor$ , that is, n is equal to the length of the binary representation of p. The worst-case hardness of breaking the Diffie-Hellman protocol is exponential in n: between  $2^{n-1}$  and  $2^n$  exponentiations have to be computed. Increasing by 1 the size of p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol. A Diffie-Hellman instance of parameters p and p where p doubles the hardness of breaking the protocol is exponential to p doubles the hardness of breaking the protocol is exponential to p doubles the hardness of breaking the protocol is exponential to p doubles the hardness of breaking the protocol is exponential to p doubles the hardness of p doubles the ha

On average, the brute force algorithm solves the discrete logarithm in  $\Theta(2^n)$  exponentiations. There exist various algorithms that compute discrete logarithms faster than the brute force approach, significantly lowering the security of the protocol. To compensate, the parameter n (and therefore also p) has to be increased. A side effect of this increase is that Alice and Bob have to perform more operations and on larger values to compute their 2 exponentations, and the size of  $g^a \mod p$  and  $g^b \mod p$ , sent over the public channel, is increased. Increasing the parameter n too much, may make the protocol impractical for use because of computation time requirements or bandwidth limitations. Luckily, the fastest discrete logarithm algorithms are of a complexity that is at least subexponential in the parameter n. This means that a linear increase of n causes a subexponential increase in the computation time of the discrete logarithm algorithms. The modification to n required to make the computation of these algorithms impractical, is acceptable in terms of computation time and bandwith requirements for the Alice and Bob.

The Diffie-Hellman protocol is not limited to the group  $(\mathbb{Z}/p\mathbb{Z})^*$ . Any cyclic group  $G = \langle g \rangle$  in which the discrete logarithm is significantly harder to compute than its group operation, can be used. Another example is the additive group of points generated by some point P on an elliptic curve over some finite field  $\mathbb{K}$ . The discrete logarithm in such a group consists of finding some scalar  $a \in \mathbb{K}$  given the generator P and the point aP on the curve. For the right choice of parameters, this is a hard problem. More background on elliptic curve cryptography (ECC) can be found in [39].

Public-key encryption is a slightly different approach to creating and sharing a symmetric encryption key. It allows Alice and Bob to exchange a small message without already having a pre-shared symmetric key. In practice, this small message consists of a symmetric encryption key, therefore it does not differ from key exchange protocols in its main purpose. The RSA public-key encryption scheme [104] is the most famous example. The security of RSA is not based on the hardness of the discrete logarithm problem, but instead on the hardness of the integer factorization problem. This problem consists of factorizing an integer that is a product of two large prime numbers. Given a

number  $N = p \cdot q$  for two large prime numbers p and q, it is very hard to find the factors p and q. As is the case for the Diffie Hellman protocol, the security of RSA depends on the complexity of the algorithms solving the underlying problem of integer factorization.

The integer factorization problem and the discrete logarithms over certain groups can be solved in polynomial time by Shor's quantum algorithm [108]. This means that, using a quantum computer, these problems are easy to solve. The cryptographic protocols based on the hardness of these problems, such as RSA, Diffie Hellman and ECC, are broken against attackers using sufficiently large quantum computers. While the quantum computers that are operational are still too small to pose a threat today, development is in progress. It is difficult to predict exactly when there will be quantum computers that are sufficiently large to to break RSA and ECC. Some experts believe that it might happen in the next 20 years [89], with a  $\frac{1}{2}$  chance of breaking RSA-2048 by 2031. Development in practical quantum computing depends on the ability to produce reliable fault-resistant qubits and its scalability. Regardless of the accuracy of this prediction, there are various reasons to start developing quantum-safe alternatives to RSA/ECC. It may take a lot of time to develop and standardize new cryptographic algorithms. The NIST hash function competition, with its goal to standardize a secure hashing algorithm, lasted 5 years. It should be assumed that encrypted communication is stored by adversaries that may in the future use quantum computers to break the encryption. Therefore it is not sufficient to use cryptographic algorithms that we know will become obsolete. Some communication is supposed to remain secret for over 20 years. For these cases it is imperative to use alternatives to RSA/ECC that will be resistant against quantum algorithms.

These alternatives are called *post-quantum cryptography* (PQC). The NIST competition for the standardization of post-quantum cryptography was launched in 2016 [36]. Its goal is to select and standardize post-quantum algorithms for public-key encryption and digital signatures. The standardized algorithms should in time replace RSA/ECC. The security of post-quantum primitives relies on mathematical hard problems for which quantum computers do not offer significant speedup, as opposed to the large integer factorization problem. The most studied proposed post-quantum algorithms fall in one of four different catagories:

• Lattice-based cryptography uses hard problems like Learning with Errors (LWE) [100] and NTRU [59], which are both related to the Shortest Vector Problem (SVP). These problems have been studied intensively, and known quantum algorithms cannot solve them efficiently. Schemes based on LWE and NTRU use relatively simple algebraic structures, such as matrices, vectors and polynomials. They are known to be fast to compute, especially the variants using polynomial ring structures. An important drawback to lattice-based cryptography is the size of the keys and ciphertexts when compared to ECC. The size of the public key of the Frodo cryptosystem for example, is 21.6 kB (see Table 1.1), while the total communication of the ECC Diffie-Hellman key exchange does not exceed 1 kB [16]. Other examples include Kyber [27], NewHope [4] and NTRUPrime [21].

- Code-based cryptography is based on the problem of decoding a random linear code. Code-based cryptosystems use some error correcting code  $\mathcal{C}$  that can be decoded using a fast decoding algorithm  $\mathcal{A}$ . The specification of the code, in the form of a matrix, is kept as part of the secret key. The public key is created by applying linear transformations and permutations to the secret matrix in order to obtain a scrambled code. This scrambled code is the public key and can be used by anyone to encode messages. The ciphertext then consists of a codeword in the scrambled code. The holder of the secret key can undo the linear transformations and permutations to the codeword and use her fast decoding algorithm  $\mathcal{A}$  to decode and obtain the plaintext. The McEliece cryptosystem [85] using Goppa codes was proposed in 1978 and has never been broken. It is not much used in practice, due to the large public key (over 1 MB, see Table 1.1) which makes it impractical. Variants of the McEliece scheme use different techniques in order to decrease the key size, such as replacing the Goppa code by some other linear code.

- Isogeny-based cryptography uses the Diffie-Hellman key exchange framework. Instead of the group  $(\mathbb{Z}/p\mathbb{Z})^{\times}$  or the additive group of points on elliptive curves, a different group is used. An isogeny graph is defined by vertices representing elliptic curves and edges between each pair of elliptic curves that is connected by some isogeny. The group operation enables random walks over such an isogeny graph. It is assumed that it is computationally hard to solve the problem of finding an explicit isogeny between two given elliptic curves. It also seems that quantum computers offer no significant speed-up in solving this problem. Advantages of isogeny-based cryptography include small key sizes (less than 1 kB, also see Table 1.1) and the ressemblance to the existing Diffie Hellman key exchange. An important inconvenient is the long computation time needed to compute the group action. SIKE [10] is the only isogeny-based submission in the NIST post-quantum contest.

- Multivariate polynomial cryptography is based on the hardness of solving a system of multivariate quadratic equations. It seems most promising for digital signatures but is not used much for public-key encryption.

The submissions to the NIST post-quantum contest differ in many aspects, and it can be challenging to make a fair comparison. The theoretical security is one of the criteria that must be satisfied. The submissions focus on several pre-defined security levels. Their claims that certain security levels are obtained by their proposal, are to be verified by cryptanalysts. The practicality of proposed solutions is a second criterium. In real world applications, there are constraints on computation time and transmission of data. The size of the public keys and ciphertexts is an important measure of the efficiency of a cryptosystem. A key establishment mechanism typically requires the transmission of one public key and one ciphertext. The sum of the public key and ciphertext size is equal to the total

<sup>&</sup>lt;sup>1</sup>Key and ciphertext sizes and cycle count are for the parameter set for a security equivalent to AES-192.

<sup>&</sup>lt;sup>2</sup>Key and ciphertext sizes and cycle count are for the parameter set targeting only 128 bits of security.

Table 1.1: A selection of round 2 submissions to NIST's post-quantum PKE contest. Key and ciphertext sizes are for parameter sets of the highest security level (equivalent to AES-256) unless stated otherwise. The cycle count for the computation of the encryption algorithm is taken from [22] who used an Intel Core i3-2310M processor.

| Cryptosystem                | category | type          | public   | secret   | ciphertext | cycles          |

|-----------------------------|----------|---------------|----------|----------|------------|-----------------|

|                             |          |               | key (kB) | key (kB) | (kB)       | $(\times 10^3)$ |

| Classic McEliece [20]       | code     | binary Goppa  | 1,044    | 13.9     | 0.2        | 318             |

| BIKE-1 [6]                  | code     | QC-MDPC       | 8.2      | 0.5      | 8.2        | 802             |

| Frodo [28]                  | lattice  | LWE           | 21.6     | 21.6     | 21.6       | 52,672          |

| NewHope [4]                 | lattice  | RLWE          | 1.8      | 1.8      | 2.2        | 498             |

| Kyber [27]                  | lattice  | MLWE          | 1.6      | 1.6      | 1.6        | 471             |

| Saber [45]                  | lattice  | MLWR          | 1.3      | 1.8      | 1.5        | 377             |

| NTRUPrime [21] <sup>1</sup> | lattice  | NTRU          | 1.2      | 0.6      | 1.0        | 11,032          |

| SIKE [10] <sup>2</sup>      | isogeny  | supersingular | 0.4      | 0.1      | 0.4        | 26,587          |

transmission required for one key establishment. Table 1.1 shows key and ciphertext sizes for a number of candidates in the NIST's post-quantum contest. Besides the size of the data transmission, speed is another essential measure. A solution that is very secure but requires a long computation time, may not be practical. The cycle counts shown in Table 1.1 are very high for some schemes. Improvement to satisfy computation time constraints can be obtained using hardware acceleration. Hardware units dedicated to the computation of specific cryptographic algorithms are faster than general purpose processors. The efficiency of hardware implementations is therefore an indicator of the practicality of a proposed cryptographic algorithm.

The security of hardware implementations does not only depend on the hardness of the mathematical problem underlying the cryptosystem, but also on the way it is implemented. Side-channel analysis (SCA) [71] makes use of physical properties that are measured while the device under attack is running. These physical properties often depend on the exact values that are being used in the computations. During decryption, the secret key is part of these values. Measuring the exact time of the computation of  $g^a \mod q$  during a Diffie-Hellman key exchange for example, may reveal information about the secret value a. In fact, if the exponentation is implemented using the Square-and-Multiply algorithm [86], the computation time depends directly on the binary representation of a. This algorithm iterates over the zeroes and ones in the binary representation of a and computes a square operation if a bit is equal to 0, while computing both a square and a multiplication if a bit is equal to 1. If the exponentation takes relatively little time to compute, one can deduce that the binary representation of a contains many zeroes. On the other hand, if the exponentation takes a long time to compute, there must be many ones in the binary representation of a. The Diffie-Hellman key exchange can thus be attacked, without attacking the underlying mathematical problem. These attacks are called side-channel attacks. The computation time is referred to as a side channel.

Another example of a side channel is the power consumption of a device executing a cryptographic

operation. Power analysis uses measured power traces, showing the exact power consumption of a device during the computation of an algorithm that uses the secret key. In the example of the Square-and-Multiply algorithm, power analysis may reveal the complete secret key a. During a multiplication a device consumes more power than during a square. The power trace thus reveals a unique pattern of squares and multiplications that correspond to zeroes and ones of the secret key. The same attack applies to the exponentation during an RSA decryption, and even to scalar multiplication in ECC using the Double-and-Add algorithm [58] to compute a (secret) multiple of a point on the curve. These attacks use only one power trace and are therefore called *simple* power attacks (SPA).

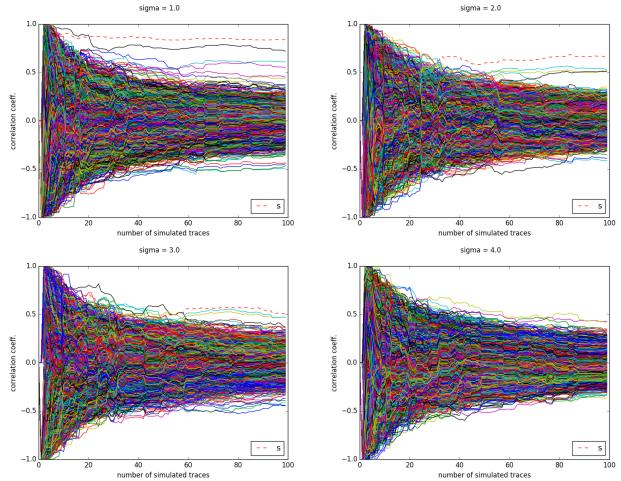

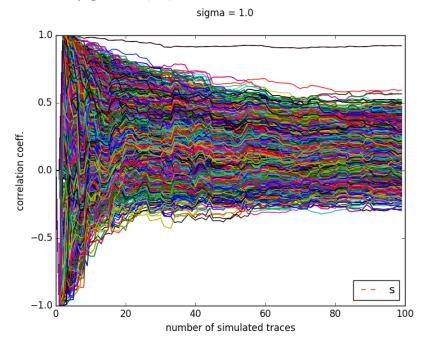

Using more traces, less straightforward relations between power consumption and secret keys may be detected. It is often assumed that there is a linear relation between the power consumption and the number of non-zero bits in the registers at any given moment during a computation. This is called the Hamming Weight model [82]. The power consumption of a device can thus be modelled for given inputs. Another model is defined by the Hamming Difference, in which it is assumed that the power consumption depends linearly on the number of bits that change value in the registers at any given moment. It is common practice to focus on a small part of the (unknown) secret key and the exact period that this part is being manipulated by the algorithm. The power consumptions for all the possibilities of the small part of the secret key are predicted by the attacker, using a prediction model. Then these predictions are compared to the observed power trace. Statistical tools are used to determine which one of the predictions fits the observed pattern most accurately. Correlation Power Analysis [30][84] observes and predicts many traces for many known inputs, and uses the Pearson's correlation coefficients to select the most likely correct value for the small part of the secret key. The attack then continues for the next small part of the secret key, until the full key is recovered. Alternatively, the side-channel attacker may stop at the point at which a large enough part of the secret key is known, so that a brute force approach can be used to recover the remaining unknown parts of the key.

Side-channel attacks show that the theoretical security of a cryptographic protocol is not sufficient to guarantee the security of its implementation in practice. Implementations should be protected by countermeasures against side-channel attacks. Timing attacks, as the one described on the Square-and-Multiply algorithm, can be avoided by making the implementation constant time. The computation time of constant-time implementations does not depend directly or indirectly on the secrets in the algorithm. A classic method of making the Square-and-Multiply algorithm constant time, is to add dummy operations. Whenever a zero appears in the binary representation of the secret key, not only a square is computed, but also a multiplication of some dummy variable. This ensures that the final result does not change, while timing attacks are avoided by constantly squaring and multiplying, independently of the secret key. This countermeasure may also prevent SPA, provided that the other potential sources of information leakage, such as the control part of the implementation, are protected as well.

Power attacks using multiple traces may be avoided by randomizing the computations. If the operations in the algorithm are linear, then masking may be used. This method involves generating a random value s' and adding it the the secret key s. The algorithm is then computed twice: the first time using s' as secret key, and the second time using s + s'. The two results are then recombined to obtain the correct outcome. The algorithm computes on randomized values only, provided that during each call to the algorithm a new random value s' is generated. The randomized computations yield randomized power traces for the attacker observing the power consumption of the device. There is no correlation between the random traces and those predicted (using the Hamming Weight model). Masking can thus thwart attacks using correlation power analysis. A major drawback of masking is that the algorithm is essentially computed twice by the device, dramatically increasing computation time. Moreover, the presence of non-linear operations in the cryptographic algorithm might make the masking method impractical. Other randomization methods may be possible, depending on the cryptographic algorithm to be protected.

Among physical attacks, fault injection constitute another common threat for cryptographic implementations, but this aspect is not addressed in this thesis due to lack of time and kept for future prospects.

### 1.2 Objective and outline of the thesis

In this thesis we will study hardware acceleration for various lattice-based encryption schemes in PQC. We implement LWE, Ring-LWE (RLWE) and Module-LWE (MLWE) based public-key encryption schemes on FPGA in order to compare their performances in hardware for multiple parameter sets, degrees of parallelism and other implementation and algorithm choices. The aim is to obtain implementations that are fast but use limited resources. In this thesis, we take a particular interest in hardware security. We analyse side-channel vulnerabilities and propose countermeasures against side-channel attacks. The countermeasures are implemented on FPGA to evaluate their cost in terms of area and computation time. Various trade-offs between security and computation time provide insight in the practicality of the post-quantum cryptosystems.

In chapter 2 we provide definitions and notations commonly used in the domain. This chapter briefly provides some mathematical notions required in order to read this thesis. In lattice cryptography, a basic understanding of finite fields and linear algebra is needed in order to appreciate the functionality of the cryptosystems.

Chapter 3 provides further background and the state of the art of lattice based cryptography. Mathematical problems involving lattices, such as the shortest vector problem, are introduced. Cryptographic constructions rely on the computational hardness of solving these problems. We discuss various algorithms to compute the operations required by the cryptosystems, such as modular reduction and polynomial multiplication. An overview of the state of the art of side-channel attacks, with

a focus on lattice cryptography, is presented in section 3.6.

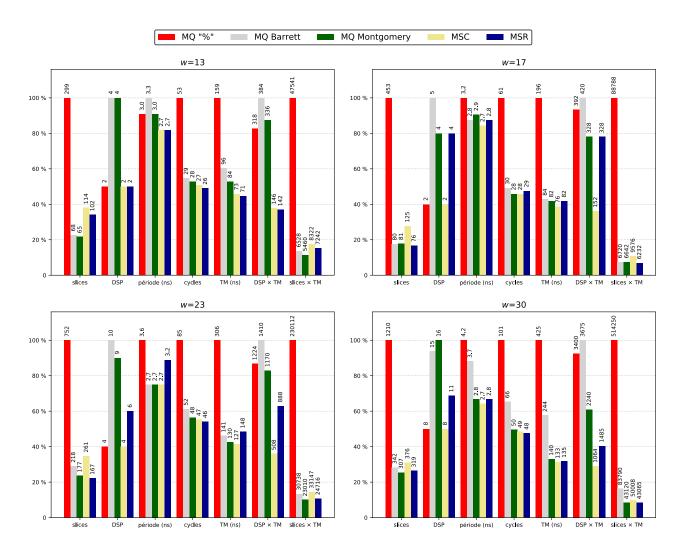

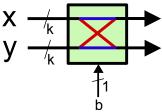

In chapter 4 we discuss the methodology used for our FPGA implementations. Our method relies on High Level Synthesis (HLS), a tool that can be used to generate FPGA implementations starting from a description in a high level programming language, such as C or C++. Section 4.1 provides an introduction to FPGAs and HLS and discusses the application of HLS in cryptography. The use of HLS is not very common among cryptographers, who typically use VHDL/Verilog languages for FPGA implementations. The HLS synthesis of the modular reduction operator in C (%), essential in public-key cryptography, yields poor performances. Section 4.2 aims to improve the computation of modular reduction by replacing the % operator. We implement finite-field arithmetic on FPGA using HLS and compare the implementation results for different modular reduction algorithms, implementation styles and parameters. In section 4.3 we explore the implementation of polynomial multiplication, an important component of lattice based cryptosystems. We compare implementation results of the schoolbook algorithm using different coding styles. We evaluate the impact of parallelization on the speed and area utilization of the implementations.

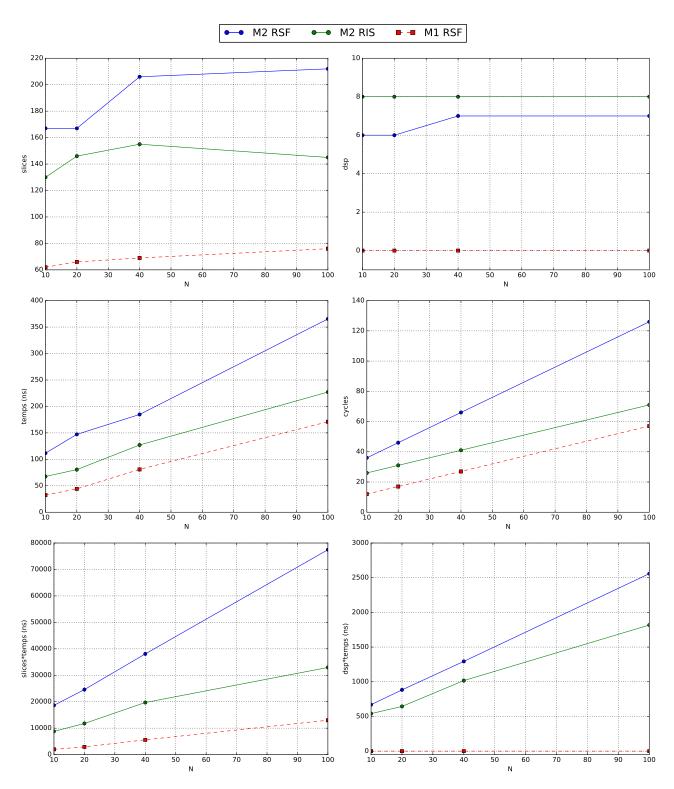

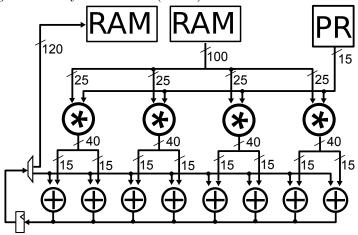

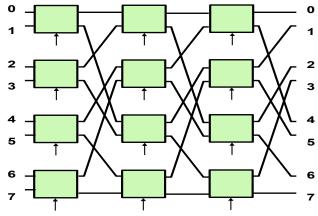

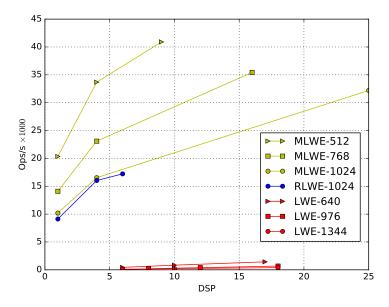

In chapter 5 we implement lattice based cryptosystems on FPGA. The objective of this chapter is to provide a comparison of the practicality of the implemented cryptosystems. The differences between the algorithms used by LWE, RLWE and MLWE based public-key encryption make some cryptosystems more practical than others. LWE based cryptosystems typically suffer from low performance compared to RLWE or MLWE. The bottleneck in the LWE encryption algorithm is the multiplication of large matrices. To accelerate this multiplication, we study the effectiveness of parallelism in the FPGA implementation. By dividing the computations over a number of dedicated hardware units, the computation time can be reduced. The same effort is made for the implementations of RLWE and MLWE based encryption, where polynomial multiplication is the most important arithmetic operation. This chapter also discusses randomness generation and chosen ciphertext attack (CCA) secure implementations. All lattice based public-key algorithms rely on the ability to generate random bits. Efficient pseudo-random number generators (PRNG) are therefore an important part of the implementation. Fast PRNGs however, are less cryptographically secure than the more conservative ones. This results in another trade-off between security and performance, discussed in section 5.6.

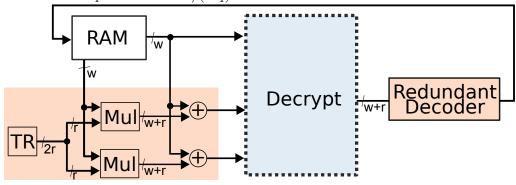

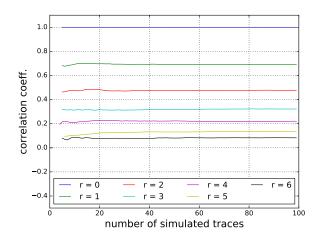

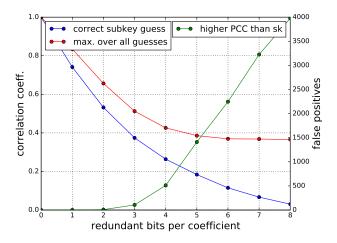

The topic of chapter 6 is the hardware security of our RLWE based decryption implementation. We highlight the vulnerabilities of the algorithm and show how these vulnerabilities might be exploited by an attacker using side-channel attacks. To prevent side-channel attacks, various countermeasures are proposed. Our countermeasures are based on the randomization of the operations, in order to randomize the information leakage through side channels. State of the art countermeasures include masking, shifting and blinding. We discuss these protections and present various improvements. We propose new countermeasures, such as a redundant representation of finite-field elements, and two shuffling techniques. All of the countermeasures from the state of the art, with improvements, and our proposed countermeasures are implemented on FPGA. We compare the difference in computation

time and area utilization for each countermeasure implementation. In section 6.6, the countermeasures are generalized in order to be applied to LWE and MLWE based implementations.

## Chapter 2

# Definitions and Notations

- $\mathbb{Z}$  is the ring of integers. The  $\mathbb{Z}$ -module  $\mathbb{Z}^n$  consists of vectors of length n whose coefficients are in  $\mathbb{Z}$ . Vectors are written in bold font:  $\mathbf{a} \in \mathbb{Z}^n$ .

- ullet R is the field of real numbers.

- For any  $a \in \mathbb{R}$ ,  $\lfloor a \rfloor$  is the integer  $a' \in \mathbb{Z}$  that is closest to a and for which  $a' \leq a$ . The integer a'' closest to a such that  $a'' \geq a$  is noted  $\lceil a \rceil$ .

- For any integer q > 0,  $\mathbb{Z}_q := \mathbb{Z}/q\mathbb{Z}$  is the ring of integers modulo q, represented by the q elements  $\{0,1,\ldots,q-1\}$ . In this ring two elements are equivalent if and only if their difference in  $\mathbb{Z}$  is an integer multiple of q. Equivalence is noted with the  $\equiv$  symbol, for instance  $q \equiv 0 \mod q$ . If q is a prime number, then  $\mathbb{Z}_q$  is a field, that is, each non-zero element a in  $\mathbb{Z}_q$  has an inverse  $a^{-1}$  such that  $a^{-1}a \equiv 1 \mod q$ . In  $\mathbb{Z}_5$  for example:  $2 \cdot 3 = 6 \equiv 1 \mod 5$ , therefore the inverse  $2^{-1}$  of 2 in  $\mathbb{Z}_5$  is equal to 3. The inverse of 3 in  $\mathbb{Z}_5$  is 2 and  $4^{-1}$  mod 5 = 4 because  $4 \cdot 4 = 16 \equiv 1 \mod 5$ . The multiplicative group of inversible elements of  $\mathbb{Z}_q$  is noted  $\mathbb{Z}_q^{\times}$ . Each element a in this group has a multiplicative order Ord(a). The order of some a is the smallest non-zero integer i for which  $a^i \equiv 1 \mod q$ . A primitive n-th root of unity  $\omega \in \mathbb{Z}_q$  is an element of order n. The order of each element in  $\mathbb{Z}_q^{\times}$  divides the number of elements in  $\mathbb{Z}_q^{\times}$ . If q is prime, then  $\mathbb{Z}_q^{\times} = \mathbb{Z}_q \setminus \{0\}$  and there exists an element  $g \in \mathbb{Z}_q^{\times}$  such that Ord(g) = q 1. Such an element is called a generator of  $\mathbb{Z}_q^{\times}$ , since it generates the group:  $\mathbb{Z}_q^{\times} = \{g, g^2, g^3, \ldots, g^{Ord(g)} = 1\}$ .

- $\mathbb{Z}[x]$  is the ring of polynomials with coefficients in  $\mathbb{Z}$ . Its contains all the elements in the set:

$$S = \left\{ \sum_{i} a_i x^i : a_i \in \mathbb{Z} \text{ for } i = 0, 1, 2, \dots \right\}$$

Polynomials are written in bold font:  $\mathbf{a} \in \mathbb{Z}[x]$ . Addition in  $\mathbb{Z}[x]$  is defined by the map

$$+: S \times S \longrightarrow S$$

$$\left(\sum_{i} a_{i} x^{i}, \sum_{j} b_{j} x^{j}\right) \longmapsto \sum_{i} (a_{i} + b_{i}) x^{i}$$

that is, the sum of two polynomials is obtained by computing the sum of each pair of coefficients  $(a_i, b_i)$  for each degree i. Multiplication of two elements in  $\mathbb{Z}[x]$  is computed by the map:

$$\bullet: S \times S \longrightarrow S$$

$$\left(\sum_{i} a_{i} x^{i}, \sum_{j} b_{j} x^{j}\right) \longmapsto \sum_{i} \sum_{j \leq i} a_{j} b_{i-j} x^{i}$$

Let  $\mathbf{a} \in \mathbb{Z}[x]$ . The *ideal* generated by  $\mathbf{a}$  is noted (a). It contains all elements in the set

$$(\mathbf{a}) = \{ \mathbf{ab} : \mathbf{b} \in \mathbb{Z}[x] \}.$$

If for instance  $\mathbf{a}=x^2$ , then  $(\mathbf{a})\subset\mathbb{Z}[x]$  is the set of polynomials whose first and second coefficients are equal to zero:  $(\mathbf{a})=\left\{\sum_{i\geq 2}a_ix^i:a_i\in\mathbb{Z}\text{ for }i=2,3,\ldots\right\}$ . The ring  $\mathbb{Z}[x]/(\mathbf{a})$  is defined by the ring of polynomials in which two elements are considered to be equivalent if and only if their difference is in  $(\mathbf{a})$ . Let  $\mathbf{a}=x^2$  for example, so that  $\mathbb{Z}[x]/(\mathbf{a})=\mathbb{Z}[x]/(x^2)$ . Elements x+3 and  $x^7+x^4+x+3$  are equivalent since their difference is  $x^7+x^4=x^2(x^5+x^2)\in(x^2)$ , therefore  $x+3\equiv x^7+x^4+x+3$  in  $\mathbb{Z}[x]/(x^2)$ . Each polynomial is equivalent to some polynomial of degree smaller than 2. The ring  $\mathbb{Z}[x]/(x^2)$  can therefore be represented by the elements of the set  $\{a_0+a_1x:a_0,a_1\in\mathbb{Z}\}$ .

- $\mathcal{R} = \mathbb{Z}[x]/(x^n + 1)$  for some integer n, is the ring of polynomials in which two elements are equivalent if and only if their difference in  $\mathbb{Z}[x]$  is a multiple of  $x^n + 1$ . In other words:  $x^n + 1 \equiv 0$ . Polynomials in this ring are of degree smaller than n, because  $x^n \equiv -1$ .

- $\mathcal{R}_q = \mathbb{Z}_q[x]/(x^n+1)$ . This is a finite ring, i.e. there is a finite number of elements in this ring. This number is equal to  $q^n$ , which is the number of polynomials of degree < n with coefficients in  $\mathbb{Z}_q$ . If there exists a 2n-th primitive root of unity  $\phi$  in  $\mathbb{Z}_q$ , then  $\phi^n \equiv -1 \mod q$  and the map

$$\sigma: \mathcal{R}_q \longrightarrow \mathbb{Z}_q^n$$

$\mathbf{a}(x) \longmapsto (\mathbf{a}(\phi), \mathbf{a}(\phi^3), \mathbf{a}(\phi^5), \dots, \mathbf{a}(\phi^{2n-1}))$

defines an isomorphism between  $\mathcal{R}_q$  and  $\mathbb{Z}_q^n$ .

- An error distribution  $\chi$  is a symmetric probability distribution centered around 0. The error distribution  $\chi$  over the integers is denoted  $\chi(\mathbb{Z})$ . Samples from error distributions must be close to 0 with high probability. Examples include the Gaussian  $\mathcal{N}(0,\sigma)$  distribution and the distribution  $\mathcal{U}([-a,a])$  that is uniform on the interval [-a,a] for some a close to zero.

- $\mathcal{B}_{\lambda}$  is the binomial (n, p) distribution with  $p = \frac{1}{2}$  and integer parameter  $n = \lambda$  centered around 0.

### List of acronyms

AES Advanced Encryption Standard

BRAM Block RAM

CPA Chosen Plaintext Attack

CC Clock Cycles

CCA Chosen Ciphertext Attack

CVP Closest Vector Problem

DIF Decimation-In-Frequency

DIT Decimiation-In-Time

DPA Differential Power Analysis

DSP Digital Signal Processing block

ECC Elliptic Curve Cryptography

FPGA Field Programmable Gate Array

GapSVP<sub>\gamma</sub> Decisional Approximate Shortest Vector Problem

HLS High Level Synthesis

HW Hamming Weight

KEM Key Exchange Mechanism

LFSR Linear Feedback Shift Register

LUT Look up Table

LWE Learning With Errors

LWR Learning With Rounding

LSB Least Significant Bit

- MLWE Module Learning With Errors

- MLWR Module Learning With Rounding

- MSB Most Significant Bit

- NIST National Institute of Standards and Technology (U.S.)

- NTT Number Theoretic Transform

- PCC Pearson's Correlation Coefficient

- PKC Public Key Cryptography

- PKE Public Key Encryption

- PRNG Pseudo Random Number Generator

- RLWE Ring Learning With Errors

- RLWR Ring Learning With Rounding

- RSA Rivest Shamir Adleman (cryptosystem)

- RNG Random Number Generator

- SCA Side Channel Analysis

- SHA Secure Hash Algorithm

- SHAKE Secure Hash Algorithm with Keccak

- SPA Simple Power Analysis

- SVP Shortest Vector Problem

- $SVP_{\gamma}$  Approximate Shortest Vector Problem

- TRNG True Random Number Generator

### Chapter 3

# State of the Art

#### 3.1 Introduction

This chapter introduces cryptographic primitives, computationally hard lattice problems and the concept of implementation security. Section 3.2 explains the mechanisms used in public-key encryption, with RSA as an example. Lattice based PKEs rely on the hardness of lattice problems. A number of these mathematical problems are discussed in section 3.3. This section also provides a description of the first LWE based cryptosystem. Variations, optimizations and generalizations of this cryptosystem are discussed in section 3.4. Section 3.5 deals with the computational aspect of the presented schemes. This includes algorithms for modular reduction and polynomial multiplication in finite rings. Finally, section 3.6 provides the state of the art of side-channel attacks. Different methods, ranging from simple-power analysis to fault attacks, are introduced. The most relevant side-channel attacks on lattice based cryptography from the state of the art are presented. Countermeasures to improve the security of implementations against these attacks are also discussed.

### 3.2 Public-Key Encryption

A public-key encryption scheme, or cryptosystem, is defined by three publicly known algorithms: key generation  $(\mathcal{G})$ , encryption  $(\mathcal{E})$  and decryption  $(\mathcal{D})$ . Algorithm  $\mathcal{G}$  generates a secret key SK and corresponding public key PK. The encryption takes as input a public key and a message (plaintext) and returns the ciphertext that encrypts the message using the public key. The decryption takes a ciphertext and a secret key and computes the plaintext. The algorithms must satisfy the following properties [47]:

1. For any plaintext m,

$$\mathcal{D}(SK, \mathcal{E}(PK, m)) = m,$$

that is, the decryption of an encrypted message is equal to the plaintext.

- 2. It is easy to evaluate the algorithms  $\mathcal{E}$  and  $\mathcal{D}$  for any input.

- 3. Given only the public key PK and a ciphertext  $c = \mathcal{E}(PK, m)$ , there is no easy way to compute m.

- 4. For all possible secret keys SK, algorithm  $\mathcal{G}$  can compute a public key PK.

RSA [104] and the McEliece cryptosystem [85] were the first examples of public-key encryption schemes. To generate a pair of RSA keys, two large prime numbers p and q are needed, and kept secret. The public key is given by  $M = p \cdot q$  and some random number e that is inversible mod (p-1)(q-1). The secret key consists of  $d = e^{-1} \mod (p-1)(q-1)$ .

#### Algorithm 1 RSA encryption and decryption

Encryption of plaintext  $\mu \in \mathbb{Z}_M$  using public key PK = (M, e).

- 1: function  $Enc(\mu, PK)$

- 2: **return**  $\mu^e \mod M$

Decryption of ciphertext  $c \in Z_m$  using secret key SK = d.

- 1: function Dec(c, SK)

- 2: **return**  $c^d \mod M$

The decryption of a ciphertext returns the plaintext. Using Fermat's Little Theorem, it holds that:

$$c^{d} = \mu^{ed} \mod M$$

$$= \mu^{1+k(p-1)(q-1)} \mod M, \text{ for some } k \in \mathbb{Z}$$

$$= \mu \cdot (1 \mod M)^{k}$$

$$= \mu.$$

The security of RSA relies on the hardness of the factorization problem. An attacker who factors the public key  $M = p \cdot q$ , can compute the inverse of  $e \mod (p-1)(q-1)$ .

#### 3.3 Lattice Problems

A lattice L is a subgroup of  $\mathbb{R}^n$  defined by a set of basis vectors  $\{\mathbf{b}_1, \dots, \mathbf{b}_n\}$ . It contains all linear integer combinations of the basis vectors [100]:

$$L = \left\{ \sum_{i=1}^{n} x_i \mathbf{b}_i : x_i \in \mathbb{Z} \right\}$$

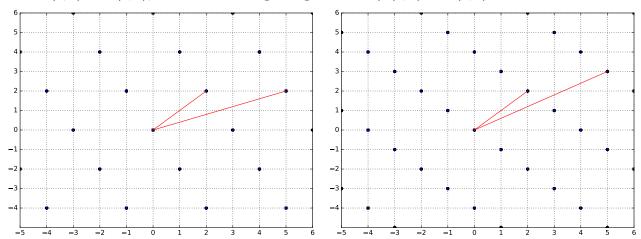

Figure 3.1: Examples of lattices of dimension 2 over  $\mathbb{Z}/12\mathbb{Z}$ . The one on the left is generated by basis vectors (2,2) and (5,2), the one on the right is generated by (2,2) and (5,3).

Examples of lattices of dimension 2 over the finite ring  $\mathbb{Z}/12\mathbb{Z}$  are shown in Figure 3.1. The lattice generated by  $\mathbf{b}_0 = (2,2)$  and  $\mathbf{b}_1 = (5,2)$ , contains for example the points  $\mathbf{b}_1 - \mathbf{b}_0 = (3,0)$  and  $2\mathbf{b}_0 + 3\mathbf{b}_1 = (19,10) \equiv (-5,-2) \mod 12$ .

The problem of finding the shortest non-zero vector in a lattice L given a basis for L, is called the Shortest Vector Problem (SVP). The smallest non-zero vectors in the lattice on the left in Figure 3.1 are (1,-2) and (-1,2). For the lattice on the right, the smallest vectors are (-1,1) and (1,-1). Let  $\lambda_1(L)$  denote the length of the smallest non-zero vector in L. The approximate version of SVP consists of estimating  $\lambda_1(L)$ . The decisional approximate shortest vector problem (GAPSVP $_{\gamma}$ ) is to decide whether  $\lambda_1(L) \leq 1$  or  $\lambda_1(L) > \gamma$ , where  $\gamma = \gamma(n)$  is some approximation factor. The Closest Vector Problem (CVP) is to find the lattice point that is closest to some given point that is not on the lattice. The computational hardness of these problems depends on the given basis vectors that define the lattice. Since the basis is not unique, any lattice can be defined by many different basis vectors. If the given lattice basis includes the shortest non-zero vector of this lattice, then SVP is trivial. If the given basis consists of large vectors (a hard basis) on the other hand, SVP becomes very hard to solve. It is conjectured that, given a hard basis, SVP and its variants cannot be solved for polynomial approximation factors in polynomial time. The LLL algorithm [76] can be used to find a relatively short basis for a lattice given by some hard basis. This algorithm runs in polynomial time but can only be used to solve the problem for subexponential approximation factors at best.

Let  $\mathbf{s} \in \mathbb{Z}_q^n$  be some unknown vector and  $\chi$  some distribution over  $\mathbb{Z}_q$ . Let  $\mathbf{a}$  be some vector sampled from the uniform distribution over  $\mathbb{Z}_q^n$ , and  $e \stackrel{\$}{\leftarrow} \chi(\mathbb{Z})$ . An *LWE sample* for  $\mathbf{s}$  is given by the pair  $(\mathbf{a}, b)$ , where  $b = \mathbf{a}^{\mathsf{T}}\mathbf{s} + e$ . The decisional LWE problem [100] is to distinguish between LWE samples and samples from the uniform random distribution over  $\mathbb{Z}_q$ . The search variant of the LWE problem consists of finding  $\mathbf{s}$  given a number m of LWE samples for this vector. The problem can

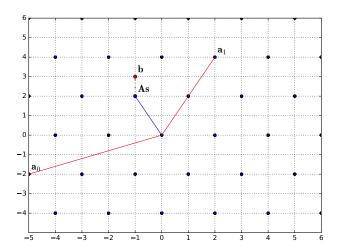

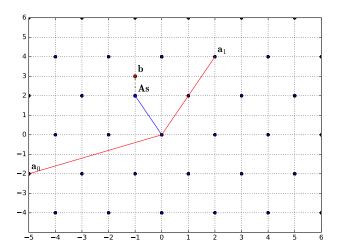

Figure 3.2: The LWE problem in a lattice over  $\mathbb{Z}_{12}$  of dimension 2: given some random basis  $A = (\mathbf{a}_0, \mathbf{a}_1)$  and a point **b** close to the lattice, find **s** such that  $A \cdot \mathbf{s}$  is close to **b**.

be seen as solving a system of linear equations over  $\mathbb{Z}_q$ , in which only approximations of the true equations are given:

$$\mathbf{a}^{(1)} \cdot \mathbf{s}^{(1)} \approx \mathbf{b}^{(1)}$$

$$\vdots$$

$$\mathbf{a}^{(m)} \cdot \mathbf{s}^{(m)} \approx \mathbf{b}^{(m)}$$

Using matrix notation: given  $\mathbf{A} \stackrel{\$}{\leftarrow} \mathbb{Z}_q^{n \times m}$  and an approximation  $\mathbf{b}$  of the product  $\mathbf{A}\mathbf{s}$ , the LWE problem is to find  $\mathbf{s}$ . The approximation of  $\mathbf{A}\mathbf{s}$  is determined by some *error vector*  $\mathbf{e}$ . This vector contains the  $\chi$ -distributed values needed to obtain the exact equation  $\mathbf{A}\mathbf{s} + \mathbf{e} = \mathbf{b}$ . The LWE problem in dimension 2 is visualized in Figure 3.2.

The classical and quantum hardness of LWE and related problems have been studied extensively, after first results by [1] and [100] showed that these problems are suitable for use in post-quantum cryptography. Let parameters n, q and  $\alpha \in (0,1)$  such that  $\alpha q > 2\sqrt{n}$ , and  $\chi$  a discrete Gaussian distribution with standard deviation  $\alpha q$ . For these parameters, [100] showed that if there is an efficient quantum algorithm to solve this problem, then there is an efficient quantum algorithm to solve Gapsvp $_{\gamma}$  on arbitrary lattices of dimension n with approximation factor  $\tilde{O}(n/\alpha)$ . This result implies that a random instance of LWE is as hard as a worst case instance of Gapsvp $_{\gamma}$ , i.e. given a hard basis. Since it is conjectured that worst case instances of Gapsvp $_{\gamma}$  are hard to solve, there must be no efficient quantum algorithm to solve average case LWE instances. The fastest methods to solve LWE include the BKW algorithm [25], Babai's nearest plane algorithm [12], BKZ [107][37],

sieving [2][19] and enumeration [55][57].

#### 3.3.1 Cryptosystem

The first public-key encryption scheme based on the hardness of LWE was presented by Regev in [100]. The secret key is given by a uniform random vector  $\mathbf{s} \in \mathbb{Z}_q^n$ . The public key is a set of m LWE samples for this vector, given by  $(\mathbf{A}, \mathbf{b} := \mathbf{A}\mathbf{s} + \mathbf{e})$ , where  $\mathbf{A}$  is sampled from the uniform distribution over  $\mathbb{Z}_q^{n \times m}$  and the m coefficients of  $\mathbf{e}$  are sampled from  $\chi$ .

#### Algorithm 2 LWE-based Encryption [100]

```

Input: Plaintext \mu \in \{0, 1\}, public key PK = (\mathbf{A}, \mathbf{b})

Output: Ciphertext (\mathbf{c}_1, c_2)

1: function \text{ENC}(\mu, PK)

2: \mathbf{v} \overset{\$}{\leftarrow} \{0, 1\}^m

3: \mathbf{c}_1 \leftarrow \mathbf{v}^{\intercal} \mathbf{A}

4: c_2 \leftarrow \mathbf{v}^{\intercal} \mathbf{b} + \mu \left\lfloor \frac{q}{2} \right\rfloor

```

#### Algorithm 3 LWE-based Decryption [100]

```

Input: Secret key SK = \mathbf{s}, ciphertext (\mathbf{c}_1, \mathbf{c}_2)

Output: Plaintext \mu

1: function \mathrm{DEC}(C, SK)

2: d \leftarrow c_2 - \mathbf{c}_1^{\mathsf{T}} \mathbf{s}

3: if d is closer to 0 than to \left\lfloor \frac{q}{2} \right\rfloor then

4: \mu \leftarrow 0

5: else

6: \mu \leftarrow 1

```

The value of  $c_2 - \mathbf{c}_1^{\mathsf{T}} \mathbf{s}$  is close to  $\mu \left\lfloor \frac{q}{2} \right\rfloor$ , as can be seen by the following equations:

$$c_2 - \mathbf{c}_1^{\mathsf{T}} \mathbf{s} = (\mathbf{A} \mathbf{s} + \mathbf{e})^{\mathsf{T}} \mathbf{v} + \mu \left\lfloor \frac{q}{2} \right\rfloor - \mathbf{v}^{\mathsf{T}} \mathbf{A}^{\mathsf{T}} \mathbf{s}$$

$$= \mu \left\lfloor \frac{q}{2} \right\rfloor + \mathbf{e}^{\mathsf{T}} \mathbf{v}$$

$$\approx \mu \left\lfloor \frac{q}{2} \right\rfloor,$$

where the last approximation holds because the coefficients of  $\mathbf{v}$  are binary and those of  $\mathbf{e}$  are sufficiently small with high probability. This allows to decrypt the ciphertext using the secret key.

#### 3.4 Ideal Lattices and RLWE

Regev's cryptosystem is not very efficient in terms of data transmission and computations per plaintext bit. To exchange one encrypted bit, n+1 coefficients in  $\mathbb{Z}_q$  have to be sent. To increase the efficiency and reduce the size of the public key, one can add structure to the matrix  $\mathbf{A}$ . Let  $\mathbf{a} = (a_0, \ldots, a_n)$  be a vector sampled from the uniform distribution over  $\mathbb{Z}_q^n$ . This vector will be the first row vector of  $\mathbf{A}$ . The n-1 remaining rows will be defined by applying an *anti-cyclic* shift to this row. This yields the following matrix:

$$\mathbf{A} := \begin{pmatrix} a_0 & a_1 & a_2 & \dots & a_{n-2} & a_{n-1} \\ -a_{n-1} & a_0 & a_1 & \dots & a_{n-3} & a_{n-2} \\ -a_{n-2} & -a_{n-1} & a_0 & \dots & a_{n-4} & a_{n-3} \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ -a_1 & -a_2 & -a_3 & \dots & -a_{n-1} & a_0 \end{pmatrix}$$

Let  $\mathcal{R}_q := \mathbb{Z}_q[x]/(x^n+1)$  and define the element  $\mathbf{v} \in \mathcal{R}_q$  by  $\mathbf{v} = \sum_{i=0}^{n-1} v_i x^i$  for each  $\mathbf{v} \in \mathbb{Z}_q^n$ . That is, each vector is considered to be a coefficient vector of an element in  $\mathcal{R}_q$ . Since  $x^n \equiv -1 \mod (x^n+1)$ , applying an anti-cyclic shift to a coefficient vector  $\mathbf{v}$  is equivalent to computing  $x\mathbf{v} \mod (x^n+1)$ . The row vectors of the matrix  $\mathbf{A}$  are obtained by computing  $x^i\mathbf{a}$  in  $\mathcal{R}_q$  for  $0 \leq i < n$ , so that  $\mathbf{A} = (\mathbf{a}, x\mathbf{a}, x^2\mathbf{a}, \dots, x^{n-1}\mathbf{a})^{\intercal}$ . The multiplication  $\mathbf{w}^{\intercal}\mathbf{A}$  can be written as

$$\mathbf{w}^{\mathsf{T}} \mathbf{A} = \sum_{i=0}^{n-1} w_i \cdot x^i \mathbf{a} \bmod (x^n + 1)$$

$$= \mathbf{a} \sum_{i=0}^{n-1} w_i x^i \bmod (x^n + 1)$$

$$= \mathbf{a} \mathbf{w} \bmod (x^n + 1),$$

that is, multiplication by an anti-cyclic matrix can be seen as multiplication in  $\mathcal{R}_q$ . The lattice generated by  $\mathbf{A}$ :

$$\mathcal{L} = \{\mathbf{w}^{\intercal}\mathbf{A} : \mathbf{w} \in \mathbb{Z}_q^n\}$$

is equivalent to the ideal in  $\mathcal{R}_q$  generated by **a**:

$$I = {\mathbf{aw} \bmod (x^n + 1) : \mathbf{w} \in \mathcal{R}_a}.$$

These *ideal lattices* are central to the Ring-LWE (RLWE) problem and RLWE based cryptography. An example of an ideal lattice over  $\mathbb{Z}_{12}[x]/(x^2+1)$  is given in Figure 3.3. It is generated by  $\mathbf{a}(x)=$

Figure 3.3: Ideal lattice over  $\mathbb{Z}_{12}[x]/(x^2+1)$  generated by  $\mathbf{a}(x) := 2+4x$ .

2 + 4x, corresponding to the basis vector (2,4). The second basis vector, (-4,2), is obtained by computing  $x \cdot \mathbf{a}(x) \mod (x^2 + 1) = 2x + 4x^2 \equiv -4 + 2x$ . Every point on the lattice can be obtained by multiplying  $\mathbf{a}$  by some polynomial in  $\mathbb{Z}_{12}[x]/(x^2 + 1)$ . Let  $\mathbf{b} = 8 + 5x$  for instance. Then  $\mathbf{ab} = 16 + 42x + 20x^2 \equiv -4 + 6x$ . Therefore, (-4,6) is a lattice point.

**Definition 1** (RLWE (informal version) [81]). Let  $s \stackrel{\$}{\leftarrow} \mathcal{R}_q$  be uniformly random. RLWE samples for s are of the form (a, as + e), where  $a \stackrel{\$}{\leftarrow} \mathcal{R}_q$  and the coefficients of e are drawn from some error distribution  $\chi$ . The decisional version of RLWE is to distinguish between RLWE samples and uniformly random pairs (v, w) in  $\mathcal{R}_q$ .

It is shown by [81] that a generalized version of this problem is computationally hard, on the condition that it is hard for any polynomial-time quantum algorithm to approximate the search version of SVP in the worst case on ideal lattices. While there exist quantum algorithms solving SVP over ideal lattices by exploiting the algebraic structure of ideal lattices [43], their approximation factor is too large to affect the security of RLWE-based cryptography. The RLWE problem remains hard when the secret polynomial  $\mathbf{s}$  is sampled from the error distribution. The RLWE based cryptosystem defines the secret key  $\mathbf{s} \stackrel{\$}{\leftarrow} \chi(\mathcal{R}_q)$ , and public keys  $(\mathbf{a}, \mathbf{b} := \mathbf{a}\mathbf{s} + \mathbf{e})$ , where  $\mathbf{a} \stackrel{\$}{\leftarrow} \mathcal{R}_q$  and  $\mathbf{e} \stackrel{\$}{\leftarrow} \chi(\mathcal{R}_q)$ . Encryption and decryption are defined by Algorithms 4 and 5.

#### 3.4.1 CPA and CCA Security

The cryptosystem described by algorithms 4 and 5 is secure in the Chosen Plaintext Attack (CPA) model. In this attack model, the adversary is given two plaintexts and a ciphertext that encrypts one of the two, and must determine which plaintext is encrypted by the ciphertext. To do this, the adversary may query an encryption oracle. If such an adversary cannot succeed, then the cryptosystem is called CPA-secure (or IND-CPA). The RLWE encryption scheme essentially masks the plaintext using an

#### Algorithm 4 RLWE Encryption [81]

```

Input: Plaintext \mu \in \{0,1\}^n, Public key (\mathbf{a},\mathbf{b}) \in \mathcal{R}_q^2

Output: Ciphertext (\mathbf{c}_1,\mathbf{c}_2) \in \mathcal{R}_q^2

1: function \text{ENC}(\mu,\mathbf{a},\mathbf{b})

2: \mathbf{e}_1,\mathbf{e}_2,\mathbf{e}_3 \stackrel{\$}{\leftarrow} \chi(\mathcal{R}_q)

3: View \mu as a polynomial in \mathcal{R}_q

4: \mathbf{c}_1 \leftarrow \mathbf{a}\mathbf{e}_1 + \mathbf{e}_2

5: \mathbf{c}_2 \leftarrow \mathbf{b}\mathbf{e}_1 + \mathbf{e}_3 + \left\lfloor \frac{q}{2} \right\rfloor \mu

```

#### Algorithm 5 RLWE Decryption [81]

```

Input: Secret key \mathbf{s} \in \mathcal{R}_q, ciphertext (\mathbf{c}_1, \mathbf{c}_2) \in \mathcal{R}_q^2

Output: Plaintext \mathbf{d} \in \{0, 1\}^n

1: function \mathrm{DEC}(\mathbf{c}_1, \mathbf{c}_2, \mathbf{s})

2: \mathbf{d} \leftarrow \mathbf{c}_2 - \mathbf{c}_1 \mathbf{s}

3: for all coefficients d of \mathbf{d} do

4: if d is closer to 0 than to \left\lfloor \frac{q}{2} \right\rfloor then

5: d \leftarrow 0

6: else

7: d \leftarrow 1

```

RLWE sample. Since samples from the RLWE distribution are indistiguishable from pseudorandom samples, the ciphertext is pseudorandom. It is therefore not possible for the adversary, given two plaintext and a ciphertext, to determine which plaintext is encrypted by the given ciphertext. The RLWE-scheme is CPA-secure.

In practice, security in the CPA model may not be sufficient, as it assumes a fairly weak attacker. The Chosen Ciphertext Attack (CCA) model assumes a more powerful attacker, who has access to a decryption oracle. The adversary may send any query to the decryption oracle, except for the given ciphertext. The goal, again, is to choose the correct plaintext given two plaintexts and an encryption of one the two. To succeed in this goal, the adversary could try to find the secret key using the decryption oracle. Let  $(\mathbf{c}_1, \mathbf{c}_2)$  be a ciphertext such that all the coefficients are equal to zero, except for the first coefficient of  $\mathbf{c}_1$  which is equal to -1. Then algorithm 5 computes  $\mathbf{d} \leftarrow 0 - (-1) \cdot \mathbf{s}$ , which is equal to the secret key. For each coefficient  $s_i$  of  $\mathbf{s}$ , the output of the decryption oracle reveals whether  $s_i$  is closer to 0 than to  $\lfloor \frac{q}{2} \rfloor$ . By making multiple queries and varying the coefficients of  $\mathbf{c}_2$ , the adversary can thus recover the complete secret key. Therefore, algorithm 5 is not secure in the CCA model.

The Fujisaki-Okamoto transform [56] is a generic method to convert CPA-secure encryption and decryption algorithms to a CCA-secure Key-Exchange Mechanism (KEM). The transform uses some cryptographic hash functions G and H, and is described by algorithms 6 and 7. In order to prevent CCA on the decryption function, the decrypted ciphertext is re-encrypted and compared to the received

ciphertext. This allows to verify that the ciphertext is valid, that is, it was generated using the encryption function. Chosen ciphertext attacks like the one described above are prevented by returning a string of random bits if the re-encryption is not equal to the received ciphertext. One technicality remains however, since the encryption function in non-deterministic. In order to make the CCA-secure encapsulation deterministic, the source of randomness used during the encryption is uniquely determined by evaluating a hash function on the public key and the plaintext. This ensures that a re-encryption of the plaintext can be correctly reconstructed using the decrypted ciphertext. To the contrary of the CPA-secure scheme, the plaintext in the CCA-secure scheme is not the same as the session key. The session key is created by hashing public key and plaintext dependent data together with the ciphertext.

```

Algorithm 6 CCA-secure Encapsulation [56]

Input: Public key PK, random \mu \in \{0,1\}^n

Output: Ciphertext C and session key K

1: function Encaps()

2: (r,d) \leftarrow H(PK||\mu)

3: C \leftarrow \text{Enc}(\mu, PK, r)

4: K \leftarrow G(C||d)

```

```

Algorithm 7 CCA-secure Decapsulation [56]

Input: Ciphertext C, Public key PK and secret key SK

Output: Session key K'

1: function Decaps()

\mu' \leftarrow \text{Dec}(C, SK)

(r', d') \leftarrow H(PK||\mu')

3:

C' \leftarrow \text{Enc}(\mu', PK, r')

4:

if C' == C then

5:

K' \leftarrow G(C'||d')

6:

7:

K' \stackrel{\$}{\leftarrow} \{0,1\}^{256}

8:

```

#### 3.4.2 Generalization and Module LWE

Module LWE (MLWE) was introduced by [75]. It is a generalization of RLWE and uses small matrices and vectors over the polynomial ring  $\mathcal{R}_q$ .

**Definition 2** (MLWE [75]). For some integer parameter k > 0, an MLWE sample for some secret vector of polynomials  $\mathbf{s} \in \mathcal{R}_q^k$  is given by some uniformly random vector  $\mathbf{a} \stackrel{\$}{\leftarrow} \mathcal{R}_q^k$ , together with the polynomial  $\mathbf{b} = \mathbf{a}^{\mathsf{T}}\mathbf{s} + \mathbf{e}$ , where  $\mathbf{e} \stackrel{\$}{\leftarrow} \mathcal{B}_{\lambda}(\mathcal{R}_q)$ . The search MLWE problem is to find  $\mathbf{s}$  given a number of samples.

Table 3.1: Parameter sets to distinguish between LWE, RLWE, and MLWE based cryptosystems. The number of rows and columns indicated are for the secret key matrix/vector/polynomial.

|           |            |              | ,            | ,                  |

|-----------|------------|--------------|--------------|--------------------|

|           | polynomial | number of    | number       |                    |

|           | degree     | columns      | of rows      | modulus            |

| algorithm | n          | m            | k            | q                  |

| LWE       | 1          | small, $> 1$ | large        | $large^1$          |

| RLWE      | $large^1$  | 1            | 1            | large <sup>2</sup> |

| MLWE      | $large^1$  | 1            | small, $> 1$ | large <sup>2</sup> |

Note that for the polynomial degree n=1 the MLWE problem is similar to the LWE problem with vectors of length k. For k = 1, MLWE is equivalent to RLWE over the ring  $\mathcal{R}_q$ . In the MLWE variant, small matrices and vectors with polynomial coefficients are used. Table 3.1 shows how parameters n, kand m allow to distinguish between LWE, RLWE and MLWE. It has been shown by [75] that MLWE is at least as hard as solving some hard lattice problems using quantum algorithms.

Algorithms 8 and 9 describe the framework used for instance by NewHope, Kyber and FrodoKEM. Variations of this framework include the use of deterministic errors ("Learning with Rounding", LWR) [45] or using Gaussian noise (used in FrodoKEM) instead of sampling the binomial distribution. The private key is defined by sampling some  $\mathbf{s} \stackrel{\$}{\leftarrow} \mathcal{B}_{\lambda}(\mathcal{R}_q^{k \times m})$ . Then the public key is determined by computing a number of LWE/RLWE/MLWE samples for this secret. That is, sample a uniform random  $\mathbf{A} \stackrel{\$}{\leftarrow} \mathcal{R}_q^{k \times k}$  and  $\mathbf{e}_0 \stackrel{\$}{\leftarrow} \mathcal{B}_{\lambda}(\mathcal{R}_q^{m \times k})$ . The public key is given by  $(\mathbf{A}, \mathbf{b})$  where  $\mathbf{b} := \mathbf{s}^{\intercal} \mathbf{A} + \mathbf{e}_0$ .

### Algorithm 8 Encryption [27]

**Input:** Plaintext  $\mu \in \{0, \dots, 2^B\}^{m^2n}$ ,  $PK = (\mathbf{A}, \mathbf{b})$

Output: Ciphertext  $(\mathbf{c}_1, \mathbf{c}_2)$

1: function  $Enc(\mu, PK)$

$\mathbf{e}_1, \mathbf{e}_2 \stackrel{\$}{\leftarrow} \mathcal{B}_{\lambda}(\mathcal{R}_q^{k \times m})$

$\mathbf{e}_{3} \overset{\$}{\leftarrow} \mathcal{B}_{\lambda}(\mathcal{R}_{q}^{m \times m})$  $\mathbf{c}_{1} \leftarrow \mathbf{e}_{1}^{\intercal} \mathbf{A} + \mathbf{e}_{2}^{\intercal}$ 3:

$\mathbf{c}_2 \leftarrow \mathbf{b}\mathbf{e}_1 + \mathbf{e}_3 + \text{ENCODE}_B(\mu)$ 5:

#### **Algorithm 9** Decryption [27]

**Input:** Secret key  $SK = \mathbf{s}$ , ciphertext  $C = (\mathbf{c}_1, \mathbf{c}_2)$

Output: Plaintext  $\mu$

1: function Dec(C, SK)

$\mathbf{d} \leftarrow \mathbf{c}_2 - \mathbf{c}_1 \mathbf{s}$

$\mu \leftarrow \text{DECODE}_B(\mathbf{d})$ 3:

<sup>&</sup>lt;sup>1</sup>For computational reasons such as simplifying modular reduction or using the NTT, these parameters are often chosen to be powers of 2.

<sup>&</sup>lt;sup>2</sup>These parameters need to be prime numbers in order to use the NTT for polynomial multiplication.

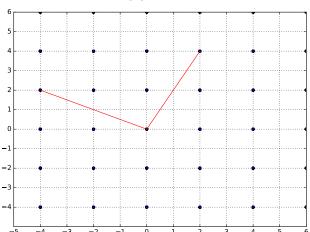

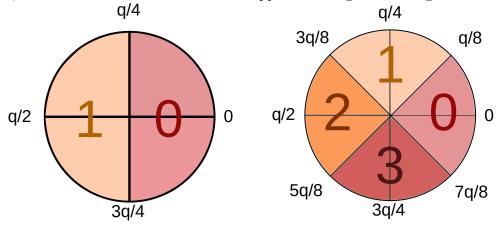

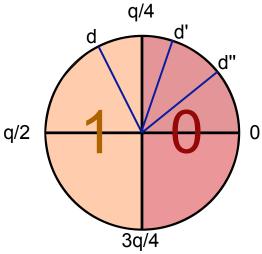

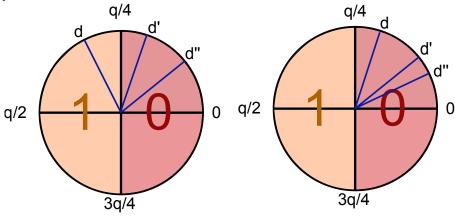

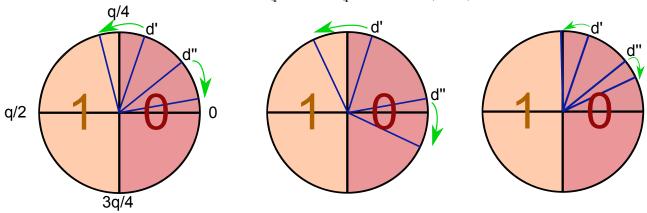

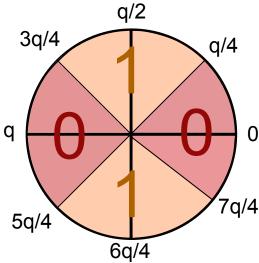

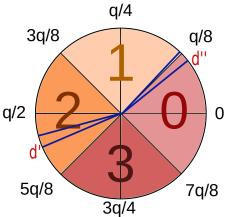

Figure 3.4: Left: Decoding the coefficients when B=0. Coefficients closer to 0 than to  $\lfloor \frac{q}{2} \rfloor$  are mapped to 0, while all the other coefficients are mapped to 1. Right: decoding when B=1.

The number of bits encoded in each plaintext coefficient is equal to B+1. For RLWE and MLWE, the parameter B is set to zero and  $\text{ENCODE}_B(\mu)$  lifts  $\mu$  to the ring  $\mathcal{R}_q$  in a straightforward coefficientwise manner and returns  $\mu \left\lfloor \frac{q}{2} \right\rfloor$ . The  $\text{DECODE}_B(\mathbf{d})$  function maps coefficients of  $\mathbf{d}$  to 0 if they are in the interval  $\left\{ \left\lfloor \frac{-q}{4} \right\rfloor, \ldots, \left\lfloor \frac{q}{4} \right\rfloor \right\}$ , else they are mapped to 1 (as depicted on the left in Figure 3.4). In LWE each coefficient encodes a number of bits  $B \geq 1$ . Encoding then lifts  $\mu$  to the module  $\mathbb{Z}_q^{m \times m}$  and involves a scalar multiplication by  $\left\lfloor \frac{q}{2^{B+1}} \right\rfloor$ . Decoding is generalized by dividing  $\mathbb{Z}_q$  up into  $2^{B+1}$  intervals as shown on the right in Figure 3.4.

For n > 1 and k = m = 1, Algorithms 2 and 3 describe the RLWE-based encryption scheme. Ciphertexts, plaintexts and keys are then polynomials in  $\mathcal{R}_q$ . For n = 1 and k, m > 1 the ring  $\mathcal{R}_q$  is equal to  $\mathbb{Z}_q$  and the plain LWE scheme is obtained, with ciphertexts, plaintexts and keys in the form of matrices over  $\mathbb{Z}_q$ . The intermediate parameter sets for which n, k > 1 define the MLWE variant of the scheme.

If k = 2, for example, an MLWE secret key is a vector  $\mathbf{s} = (\mathbf{s}_1(x), \mathbf{s}_2(x))^{\mathsf{T}}$ , where the coefficients of both polynomial are sampled from the uniform distribution over  $\mathbb{Z}_q$ . To create a public key, four uniformly random (in  $\mathcal{R}_q$ ) polynomials  $\mathbf{a}_{00}(x)$ ,  $\mathbf{a}_{01}(x)$ ,  $\mathbf{a}_{10}(x)$  and  $\mathbf{a}_{11}(x)$  must be sampled, and two error polynomials  $\mathbf{e}_0(x)$ ,  $\mathbf{e}_1(x)$  are sampled from  $\mathcal{B}_{\lambda}(\mathcal{R}_q)$ . Then the public vector  $\mathbf{b} = (\mathbf{b}_0(x), \mathbf{b}_1(x))$  is computed as follows:

$$\begin{pmatrix} \mathbf{b}_0(x) & \mathbf{b}_1(x) \end{pmatrix} = \begin{pmatrix} \mathbf{s}_1(x) & \mathbf{s}_1(x) \end{pmatrix} \begin{pmatrix} \mathbf{a}_{00}(x) & \mathbf{a}_{01}(x) \\ \mathbf{a}_{10}(x) & \mathbf{a}_{11}(x) \end{pmatrix} + \begin{pmatrix} \mathbf{e}_1(x) & \mathbf{e}_1(x) \end{pmatrix}$$

(3.1)

An important advantage of MLWE-based cryptosystems is the flexibility in choosing parameters, while still benefiting from fast arithmetic in  $\mathcal{R}_q$  using the NTT. In RLWE, efficient use of the NTT means that the degree n has to be a power of 2, restricting the lattice dimension to a very limited subset. In MLWE one would also fix n to be a power of 2, but the total dimension of the lattice is

determined by  $n \times k$ , allowing more choices. To instantiate the MLWE scheme for a higher security level, it suffices to increase the vector size k. In [27] the MLWE-based Kyber key-exchange mechanism is defined for k = 2, 3 and 4, where k = 4 aims for the highest level of security, equivalent to AES-256.

#### 3.4.3 NTRU

Similar to RLWE-based PKE, the NTRU cryptosystem [59] is defined over a polynomial ring  $\mathcal{R} = \mathbb{Z}[x]/(x^n-1)$ . Let q be some integer coprime with 3 and such that q > 3. The secret key is some  $\mathbf{f} \in \mathcal{R}$  with small coefficients that is inversible modulo 3 and modulo q. A random polynomial  $\mathbf{g} \in \mathcal{R}$  with small coefficients is used to compute  $\mathbf{h} = (\mathbf{f} \mod q)^{-1}\mathbf{g}$ . This  $\mathbf{h}$  will be the public key. Encryption and decryption are defined in Algorithm 10.

### Algorithm 10 NTRU encryption and decryption [59]

```

Encryption of \mu \in \mathcal{R} with coefficients in \{-1,0,1\}^n using public key PK = \mathbf{h}.

```

- 1: **function** Enc( $\mu$ , PK)

- 2:  $\phi \stackrel{\$}{\leftarrow} \mathcal{R}$  with small coefficients

- 3:  $\mathbf{c} \leftarrow 3\phi \cdot \mathbf{h} + \mu \mod q$

- 4: return c

Decryption of ciphertext  $\mathbf{c} \in \mathcal{R}$  using secret key  $SK = \mathbf{f}$ .

- 1: function  $Dec(\mathbf{c}, SK)$

- 2:  $\mathbf{a} \leftarrow \mathbf{f} \cdot \mathbf{c} \mod q$

- 3: **return**  $(\mathbf{f} \mod 3)^{-1} \cdot \mathbf{a} \mod 3$

#### 3.4.4 LWR

The use of the NTT restricts the choice of the parameters n and q for the ring  $\mathbb{Z}_q[x]/(x^n+1)$ . The degree n must be a power of 2. In practice, one would want to instantiate an RLWE cryptosystem for some  $2^9 < n < 2^{10}$ . An encryption scheme for  $2^9 = 512$  would be considered not secure enough, while  $n = 2^{10}$  would be overkill. Parameters used for NTRU schemes include for example n = 653,761 and 857 [21]. Flexibility in parameters is one of the reasons why some RLWR/MLWR schemes such as Round5 and Saber choose alternative multiplication methods over the NTT. The transmission of keys and ciphertexts consisting of polynomials of degree 700 is cheaper than the transmission of polynomials of degree 1024. This choice also allows them to use a power of 2 modulus q, so that modular reduction needed for arithmetic in  $\mathbb{Z}_q$  is trivial to compute. When using a power of 2 modulus, it is possible to simplify the error sampling process. Instead of sampling from an error distribution and adding the error to the ciphertext during encryption, a number of least significant bits of each coefficient of the ciphertext is removed, thereby "rounding" each coefficient. The security of cryptosystems using this technique is based on the hardness of the Learing With Rounding (LWR) problem, and its ring (RLWR) and module (MLWR) variants. The rounding function denoted  $\lfloor \cdot \rceil_p : \mathbb{Z}_q \to \mathbb{Z}_p$  is defined for

p < q by:

$$\lfloor a \rceil_p = \lfloor (p/q) \rceil \ a \bmod p \tag{3.2}$$

If p and q are both powers of 2, then this rounding function corresponds to removing the  $\log_2(q) - \log_2(p)$  least significant bits. For some secret polynomial  $\mathbf{s} \in \mathcal{R}_q$ , an RLWR sample is generated by sampling an uniform random  $\mathbf{a} \stackrel{\$}{\leftarrow} \mathcal{R}_q$  and returning  $\mathbf{a}$  and  $\lfloor \mathbf{a} \mathbf{b} \rfloor_p$ . This problem was first studied in [14]. MLWR/RLWR based cryptosystems include Round5 [11] and Saber [45].

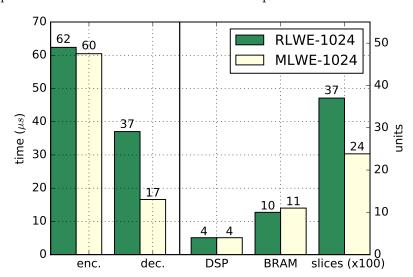

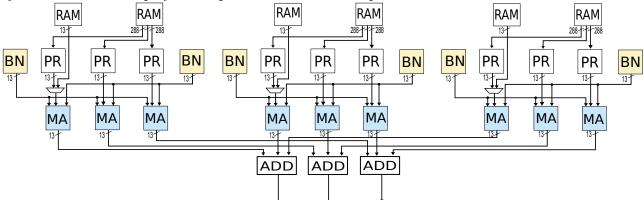

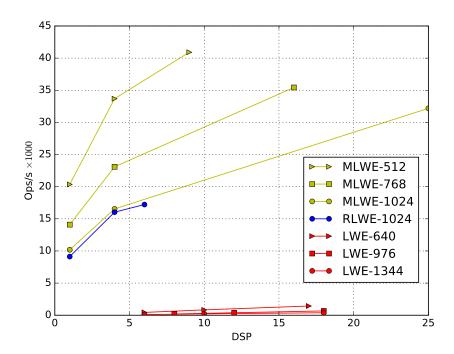

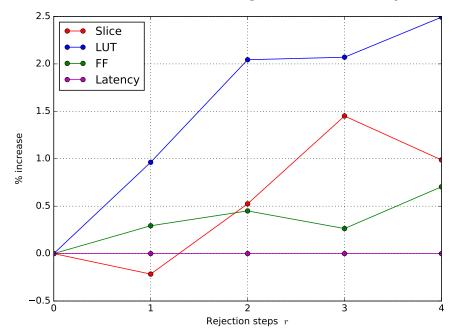

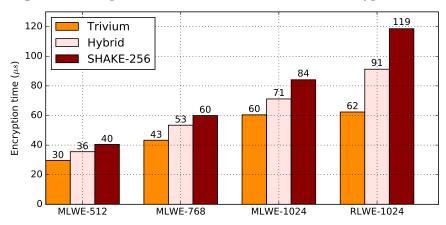

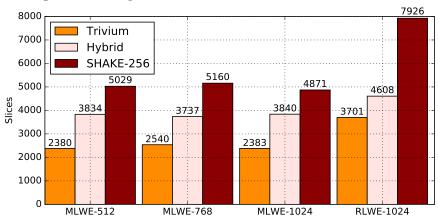

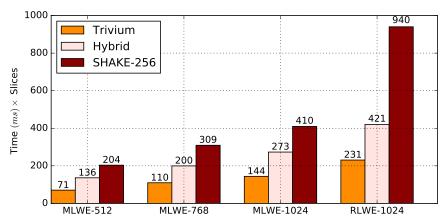

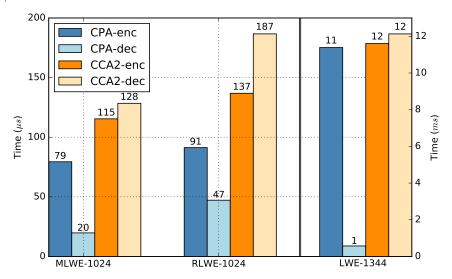

### 3.5 Implementation of LWE-based Cryptography