## Circuit-level approaches to mitigate the process variability and soft errors in FinFET logic cells

Alexandra Lackmann Zimpeck

### ▶ To cite this version:

Alexandra Lackmann Zimpeck. Circuit-level approaches to mitigate the process variability and soft errors in FinFET logic cells. Micro and nanotechnologies/Microelectronics. Institut Supérieur de l'Aéronautique et de l'Espace (ISAE); Universidade Federal do Rio Grande do Sul (Brésil), 2019. English. NNT: . tel-02890418

## HAL Id: tel-02890418 https://hal.science/tel-02890418v1

Submitted on 6 Jul 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ONERA

THE FRENCH AEROSPACE LAB

## En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut Supérieur de l'Aéronautique et de l'Espace

Universidade Federal do Rio Grande do Sul (Brésil)

### Présentée et soutenue par : Alexandra LACKMANN ZIMPECK

le mardi 24 septembre 2019

### Titre :

Circuit-level approaches to mitigate the process variability and soft errors in FinFET logic cells

Approches au niveau du circuit pour atténuer la variabilité de fabrication et les soft errors dans les cellules logiques FinFET

#### École doctorale et discipline ou spécialité : ED GEET : Micro et nanosystèmes

**Unité de recherche :** Équipe d'accueil ISAE-ONERA OLIMPES

ipe d'accueil ISAE-ONERA OLIMPE

### Directeur(s) de Thèse :

M. Ricardo REIS (directeur de thèse) M. Laurent ARTOLA (co-directeur de thèse)

Jury :

Mme Lirida NAVINER, Professeur Télécom Paris - Rapporteur, Présidente M. Ricardo REIS, Professeur UFRGS Brésil - Directeur de thèse M. Laurent ARTOLA, Ingénieur de Recherche ONERA - Co-directeur de thèse M. Remi BARBIER, Professeur ISAE-SUPAERO Mme Karine COULIÉ, Maître de Conférences Université Aix-Marseille - Rapporteure M. Marc GALLARDIN, Ingénieur CEA M. Paul LEROUX, Professeur KU Leuven Belgique Mme Cecilia MEZZOMO, Ingénieur Thales Alenia Space

# Acknowledgments

I would like to start by thanking my parents, Alexandre and Dulcinara, for the study encouragements since the earliest stages of my life, for all support provided me to achieve my goals, and for never letting me give up on my dreams. I thank my brother, Lucas, for unconditional love even though sometimes he didn't understand the reasons for the distance between us. Thank you for always been close to me, even when I have been a few thousand kilometers away from you. I also thank my husband, André Furlan, for your patience, support to achieve my goals and mainly, for accompanying me during my internship in Toulouse. I take the opportunity also to thank all my family and friends who always sent positive vibes for me and understood the several important moments when I could not be present.

I would like to thank my colleagues from UFRGS, Gracieli Posser, Calebe Micael, Tania Ferla, Jucemar Monteiro, Felipe Rosa, Walter Calienes, Vitor Bandeira, Geancarlo Abich, Mateus Fogaça, Lucas de Paris, Louise Etcheverry, Vladimir Afonso, Leonardo Brendler, Leonardo Moraes, Pablo Silva, for the friendship, confidence and the countless hours discussing a variety of subjects. My thanks to all my colleagues from ONERA, especially to Raphael Vieira and Neil Rostand for sharing studies, knowledge, and ideas, and Virnigie Inguimbert for helping me understand better the French language. I would thank especially Prof. Cristina Meinhardt for all support in my scientific research since 2010, for the professional partnership on most varied subjects and her friendship during all these years.

I want to thank my advisor, Prof. Ricardo Reis, for always believing in my potential and for encouraging me to be better every day. I thank so much Prof. Fernanda Kastensmidt for her collaborations, discussions, and all support given for this work. I also thank Laurent Artola and Guillaume Hubert for the research opportunity and for all knowledge obtained inside of ONERA as well as for providing me a fantastic internship in France. Finally, I would like to thank all the supernatural forces that make us go forward until the end.

To all of you, my sincere thanks.

## Abstract

Process variability mitigation and radiation hardness are relevant reliability requirements as chip manufacturing advances more in-depth into the nanometer regime. The parameter yield loss and critical failures on system behavior are the major consequences of these issues. Some related works explore the influence of process variability and single event transients (SET) on the circuits based on FinFET technologies, but there is a lack of approaches to mitigate the effects caused by them. For these reasons, from a design standpoint, considerable efforts should be made to understand and reduce the impacts introduced by reliability challenges. In this regard, the main contributions of this Ph.D. thesis are: 1) to investigate the behavior of FinFET logic cells under process variations and radiation effects; 2) to evaluate four circuit-level approaches to attenuate the impact caused by work-function fluctuations (WFF) and soft errors (SE); 3) to provide an overall comparison between all techniques applied in this work; 4) to trace a trade-off between the gains and penalties of each approach regarding performance, power, area, and SET cross-section. Transistor reordering, decoupling cells, Schmitt Trigger, and sleep transistor are the four circuit-level mitigation techniques explored in this work. The potential of each one to make the logic cells more robust to the process variability and radiation-induced soft errors are assessed comparing the standard version results with the design using each approach. This Ph.D. thesis also establishes the mitigation tendency when different levels of variation, transistor sizing, and radiation particles characteristics such as linear energy transfer (LET) are applied in the design with these techniques. The process variability is evaluated through Monte Carlo (MC) simulations with the WFF modeled as a Gaussian function using SPICE simulations. The SE susceptibility is estimated using the radiation event generator tool MUSCA SEP3 (developed at ONERA), also based on an MC method, which deals both with radiation environment characteristics, layout features and the electrical properties of devices. In general, the proposed approaches improve the state-of-the-art by providing circuit-level options to reduce the process variability effects and SE susceptibility, at fewer penalties and design complexity. The transistor reordering technique can increase the

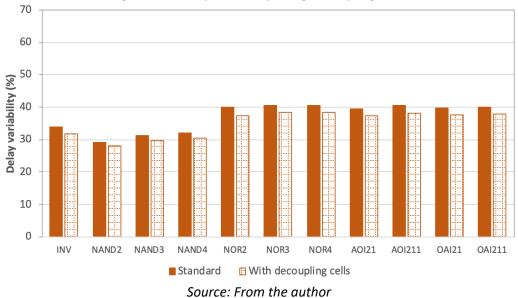

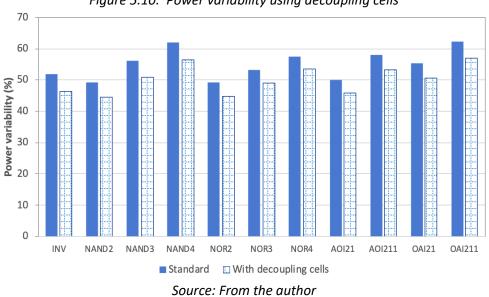

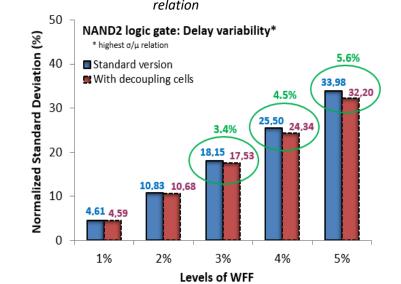

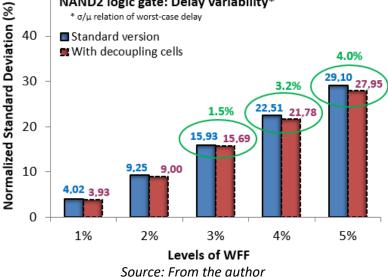

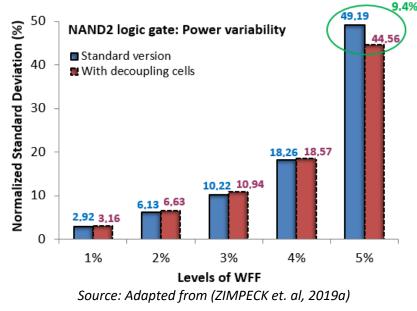

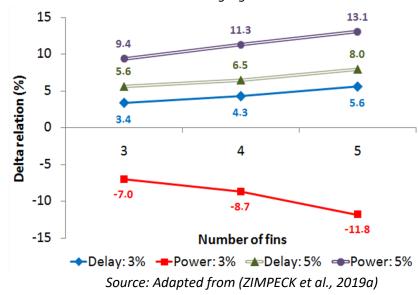

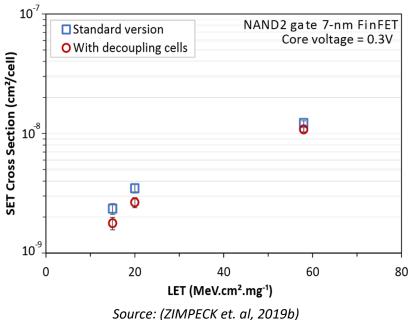

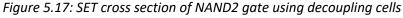

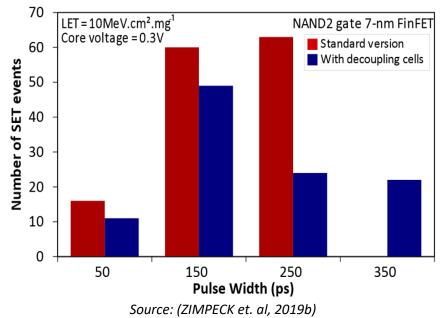

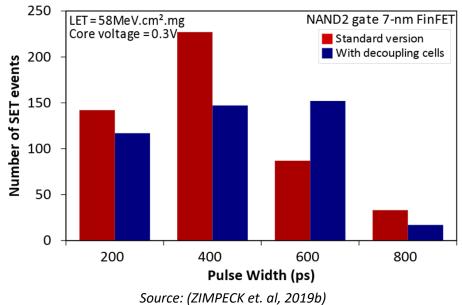

robustness of logic cells under process variations up to 8%, but this method is not favorable for SE mitigation. The insertion of decoupling cells shows interesting outcomes for power variability control with levels of variation above 4%, and it can attenuate until 10% the delay variability considering manufacturing process with 3% of WFF. Depending on the LET, the design with decoupling cells can decrease until 10% of SE susceptibility of logic cells. The use of Schmitt Triggers in the output of FinFET cells can improve the variability reaching around 12% for WFF of 5%, but the advantages of this method to delay variability depends how the transistors are arranged with the sleep transistor in the pull-down network. The addition of a sleep transistor become all logic cells studied free of faults even at the near-threshold regime. In this way, the best approach to mitigate the process variability is the use of Schmitt Trigger technique, is the most efficient for the SE mitigation. However, the Schmitt Trigger technique presents the highest penalties in area, performance, and power. Therefore, depending on the application, the sleep transistor or decoupling cells technique can be the most appropriate to mitigate the process variability effects.

## Resumo

A variabilidade de processo e a resistência a radiação são requisitos de confiabilidade relevantes à medida que a fabricação de chips avança mais a fundo no regime nanométrico. A perda de rendimento paramétrico e as falhas críticas no comportamento do sistema são as principais consequências destes problemas. Alguns trabalhos relacionados exploram a influência da variabilidade de processo e dos eventos transientes únicos (SET) nos circuitos projetados nas tecnologias FinFET, mas existe uma ausência de abordagens para mitigar eles. Por estas razões, do ponto de vista de projeto, esforços consideráveis devem ser feitos para entender e reduzir os impactos introduzidos pelos desafios de confiabilidade. Dessa forma, as principais contribuições desta tese de doutorado são: 1) investigar o comportamento de células lógicas FinFET sob variações de processo e efeitos de radiação; 2) avaliar quatro abordagens em nível de circuito para atenuar o impacto causado por flutuações na função trabalho (WFF) and soft errors (SE); 3) fornecer uma comparação global entre todas as técnicas aplicadas neste trabalho; 4) Traçar um balanceamento entre os ganhos e as penalidades de cada abordagem em relação ao desempenho, potência, área, seção transversal SET e largura de pulso SET. Reordenamento de transistores, e o uso de decoupling cells, Schmitt Triggers e sleep transistors são as quatro técnicas de mitigação em nível de circuito exploradas neste trabalho. O potencial de cada uma delas para tornar as células lógicas mais robustas à variabilidade de processo e aos soft errors induzidos pela radiação são avaliados comparando os resultados da versão padrão com o projeto usando cada uma das técnicas. Esta tese também estabelece a tendência de mitigação quando diferentes níveis de variação, dimensionamento de transistores e características das partículas de radiação, tais como a transferência linear de energia (LET), são aplicados no projeto com estas técnicas. A variabilidade de processo é avaliada através de simulações Monte Carlo (MC) com a WFF modelada como uma função Gaussiana usando simulações SPICE enquanto a susceptibilidade à SE é estimada usando a ferramenta gerado de eventos de radiação MUSCA SEP3 (desenvolvida na ONERA) também baseada em um método MC que lida com as características do ambiente de radiação, os recursos de leiaute e as propriedades elétricas dos dispositivos. De modo geral, as técnicas propostas melhoram o estado da arte, fornecendo opções à nível de circuito para reduzir os efeitos da variabilidade de processo e a susceptibilidade à SE, com menos penalidades e complexidade de projeto. A técnica de reordenamento de transistores pode aumentar a robustez das células lógicas sob variação de processo até 8%, mas este método não é favorável para a mitigação de SE. A inserção de *decoupling cells* mostra resultados interessantes para o controle da variabilidade de potência com níveis de variação acima de 4%, e esta técnica pode atenuar até 10% a variabilidade de atraso considerando um processo de manufatura com 3% de WFF. Dependendo do LET, o projeto com decoupling cells pode diminuir até 10% a susceptibilidade à SE das células lógicas. O uso de Schmitt Triggers na saída das células FinFET podem melhorar a sensibilidade à variabilidade até 50%. A abordagem com sleep transistors melhora a variabilidade de potência em torno de 12% para 5% de WFF, mas as vantagens desse método para o atraso dependem de como os transistores estão posicionados em relação ao sleep transistor na rede pull-down. A adição de um sleep transistor torna todas as células lógicas estudadas livre de falhas mesmo no regime quase limiar. Neste contexto, a melhor abordagem para mitigar a variabilidade de processo é o uso de Schmitt Triggers, bem como a técnica de sleep transistor é a mais eficiente para a mitigação de SE. No entanto, a técnica de Schmitt Triggers apresenta as maiores penalidades de área, desempenho e potência. Sendo assim, dependendo da aplicação, a técnica de sleep transistors pode ser a mais apropriada para mitigar os efeitos da variabilidade de processo.

## Résumé

#### **1.** INTRODUCTION GENERALE

De nouveaux matériaux et de nouvelles architectures de dispositifs ont dû être mis en œuvre dans les circuits intégrés pour assurer la mise à l'échelle de la technologie (PRADHAN; SAHU; RANJAN, 2016). L'adoption des appareils FinFET présentait plusieurs avantages, en maintenant le rythme des performances, en réduisant la consommation d'énergie et en augmentant la densité. Cependant, les petits motifs géométriques imposés par les nœuds technologiques avancés soulèvent des questions essentielles liées à la fiabilité des systèmes électroniques. L'utilisation de technologies inférieures à 22nm entraîne une complexité de conception accrue avec davantage de sources potentielles de variabilité ainsi qu'une densité plus élevée permettant à une seule particule énergétique d'affecter plusieurs nœuds adjacents (ENDO et al., 2009) (BHUVA et al., 2015).

La variation de fabrication représente un écart aléatoire par rapport aux spécifications de conception typiques, qui stimule la dégradation du circuit, la consommation électrique anormale et la divergence des performances (TASSIS et al., 2014). Les principales sources de variations de processus sont la longueur d'onde adoptée dans l'étape de la lithographie, qui ne suit pas le rythme de la mise à l'échelle du dispositif et l'utilisation de diélectriques à k élevé pour améliorer le contrôle de grille sur la région du canal. Bien que l'utilisation de métal comme matériau de grille soit utile pour contrôler certains défis, elle modifie les orientations du grain en générant différentes fonctions de travail alignées de manière aléatoire, ce qui implique des fluctuations plus élevées de la fonction de travail (DADGOUR et al., 2010).

Le soft error (SE) provient de l'interaction de particules énergétiques provenant de l'espace et de radiations terrestres avec le silicium. En général, les technologies nanométriques plus approfondies sont plus sensibles à la SE en raison de tensions d'alimentation faibles, de capacités intrinsèques réduites et d'un fonctionnement à fréquence plus élevée (BAUMANN, 2005). Cependant, la structure 3D de FinFET minimise le volume de silicium exposé au mécanisme de collecte de charge et, par conséquent, diminue la susceptibilité du SE sur ces dispositifs (SEIFERT et al., 2015). Cependant, les effets ne peuvent pas encore être considérés comme négligeables car la variabilité de fabrication peut modifier le seuil de transfert d'énergie linéaire (LET) pour induire un *soft error*.

#### **MOTIVATION**

La réduction de la variabilité des processus et la dureté du rayonnement sont des exigences de fiabilité pertinentes alors que la fabrication de puces progresse plus en profondeur dans le

régime nanométrique. Les circuits intégrés à variabilité de fabrication peuvent ne pas satisfaire à certains critères de performance ou de consommation électrique, ce qui augmente la perte de rendement paramétrique et la nécessité de plusieurs étapes de la refonte. Les erreurs logicielles induites par les radiations peuvent provoquer une perte temporaire de données, entraînant des défaillances critiques du comportement du système, même au niveau du sol. La feuille de route des industries des semi-conducteurs les plus renommées souligne encore l'utilisation de dispositifs FinFET pour la prochaine génération de nanotechnologies. En outre, un kit prédictif de conception de processus (PDK) FinFET 7-nm est devenu disponible pour une utilisation académique, ce qui permet une recherche approfondie au niveau de la structure (CLARK et al., 2016). Du point de vue de la conception, ces défis nécessitent des estimations précises du comportement du circuit, en soulignant l'importance d'indiquer de nouvelles directives de conception capables de gérer ces controverses tout en préservant l'avancée technologique.

Plusieurs travaux ont étudié l'impact de la variabilité des processus et des effets du rayonnement sur les technologies FinFET, principalement au niveau des dispositifs et de l'électricité, mais beaucoup moins de connaissances ont été acquises au niveau de la disposition. De plus, seuls quelques travaux ont proposé des solutions pour atténuer les effets causés par celles-ci. Les approches les plus efficaces dans la littérature pour atténuer les variations de processus et les défauts transitoires sont généralement liées à l'utilisation d'une structure et d'un matériau différents au cours du processus de fabrication, ou de la réplication matérielle, respectivement. Cependant, les modifications de fabrication ont un coût élevé et une complexité de conception accrue, ainsi que la redondance matérielle, entraînent des frais généraux importants.

#### **OBJECTIFS DE THESE**

Les techniques d'atténuation au niveau du circuit qui modifient la conception des cellules logiques au niveau de la disposition constituent des alternatives potentielles pour parvenir à des solutions plus robustes et plus précises, avec un coût de mise en œuvre moins élevé et moins de pénalités. De cette manière, les objectifs principaux de cette thèse sont :

1. étudier le comportement des cellules logiques FinFET sous les variations de processus et les effets de rayonnement ;

2. Évaluer quatre approches au niveau du circuit pour atténuer l'impact causé par les fluctuations du travail et les erreurs logicielles.

3. Fournir une comparaison globale entre toutes les techniques appliquées dans ce travail ;

4. Tracez un compromis entre les gains et les pénalités de chaque approche concernant la surface, les performances, la consommation d'énergie, la durée d'impulsion SET et la section transversale SET.

Les quatre approches d'atténuation au niveau du circuit explorées dans ce travail sont le *transistor reordering, decoupling cells, Schmitt Trigger* et *sleep transistor*. Le *transistor reordering* est basée sur l'optimisation des dispositions des transistors. L'utilisation de *decoupling cells* est une méthode capacitive. Schmitt Trigger agit en tant que mécanisme de retour afin de minimiser la dégradation de la sortie. Le *sleep transistor* est une stratégie de *power-gating*. Tout d'abord, la version standard des cellules logiques FinFET, c'est-à-dire sans aucune technique au niveau du circuit, a été mise en œuvre dans des scénarios de variabilité de fabrication et de rayonnement à des fins de comparaison. Ensuite, le potentiel de chaque approche pour rendre les cellules logiques FinFET plus robustes aux fluctuations de la fonction de travail et aux erreurs logicielles est évalué en comparant la version standard à la conception adoptant chaque technique selon des métriques prédéfinies bien connues.

Ce travail établit également la tendance à l'atténuation lorsque différents niveaux de variation de processus, de dimensionnement de transistor et de caractéristiques de particule de rayonnement, tels que le LET, sont appliqués dans la conception utilisant ces techniques. Cette thèse contribue à l'avancement de l'état de la technique en fournissant des options au niveau du circuit pour atténuer la variabilité des processus et la susceptibilité aux *soft errors* dans une technologie FinFET avec moins d'inconvénients techniques et une mise en œuvre plus simple, si on la compare aux autres approches disponibles dans la littérature. De plus, l'ensemble des informations fournies dans ce travail aide les concepteurs à choisir le schéma de présentation le plus approprié pour une application donnée, en connaissant tous les avantages et les inconvénients de son adoption.

#### **2.** FONDEMENT THEORIQUE

Ce chapitre présente les concepts fondamentaux liés aux technologies FinFET, tels que la structure, le mode de fonctionnement et les propriétés des transistors FinFET, une analyse de l'évolution technologique dans l'industrie des semi-conducteurs ainsi que des informations sur le schéma de configuration, les modèles prédictifs et les kits de conception de processus.

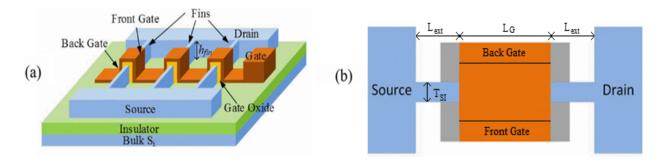

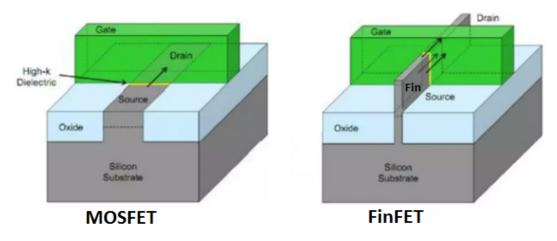

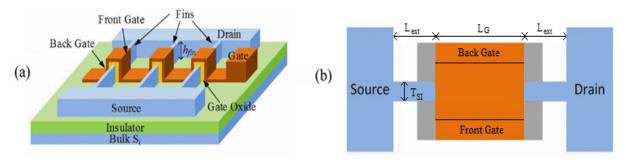

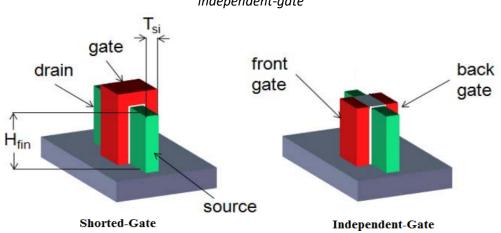

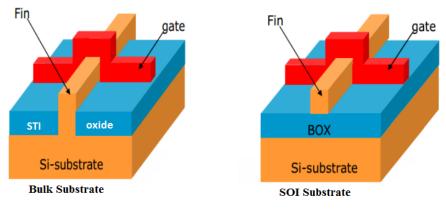

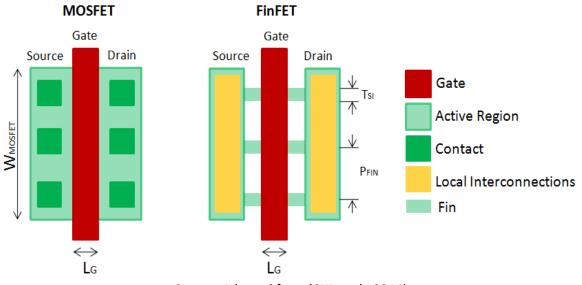

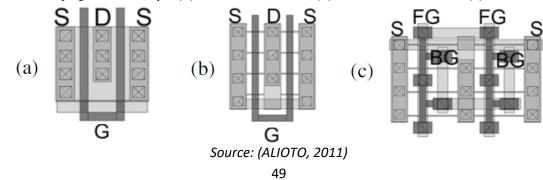

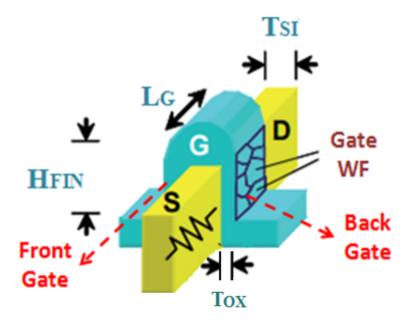

Le dispositif FinFET se compose d'ailettes de silicium verticales pour former la région de canal et pour connecter les régions de source et de drain à chaque extrémité. Ces ailettes verticales enveloppent la région de la porte et des canaux MOS sont formés sur les deux parois latérales et sur le dessus de l'aileron. Les principaux paramètres géométriques d'un FinFET selon la figure 1 sont la longueur de la porte (L<sub>G</sub>), la hauteur de l'ailette (H<sub>FIN</sub>), l'épaisseur de l'aile (T<sub>SI</sub>/ T<sub>FIN</sub>/ W<sub>FIN</sub>) et l'épaisseur de l'oxyde (T<sub>OX</sub>). Les structures à porte courte (SG) et à porte indépendante (IG) sont les deux principaux types de dispositifs FinFET. Ce travail adopte le modèle SG dans un substrat en vrac tel que la porte arrière et la porte avant soient liées ensemble, physiquement court-circuitées. Dans ce mode, les deux portes fournissent une commande de porte maximale assurant le contrôle électrostatique du canal. Cependant, le

courant à l'arrêt est plus élevé car il n'est pas possible de réguler la tension de seuil de l'appareil (V<sub>TH</sub>) électriquement.

Figure 1 : Structure SG FinFET dans (a) une vue en perspective et (b) une vue de dessus (GUPTA; ROY, 2013)

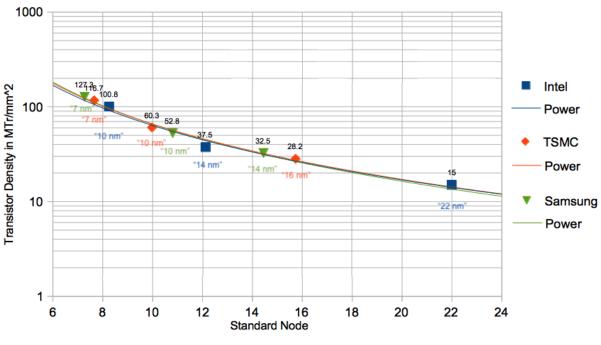

Le prix élevé des équipements de recherche, de développement et de fabrication a entraîné une réduction du nombre d'industries de semi-conducteurs qui investissent dans des nœuds technologiques avancés. De nos jours, la course aux puces plus compactes et technologiques se produit principalement parmi les sociétés Intel, Samsung et TSMC (HIBBEN, 2018).

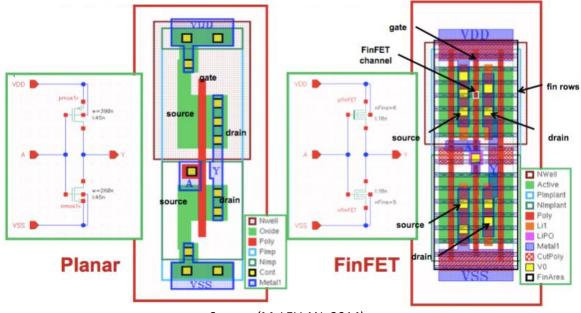

La conception FinFET est composée de rangées d'ailettes reliant les régions de source et de drain, avec des barrettes de grille orthogonales. Les portes simples violent généralement les règles de conception des technologies FinFET. Ainsi, la conception d'un seul FinFET comporte trois portes car chaque transistor doit être terminé avec des portes factices de chaque côté. De plus, il n'est pas possible de couper la diffusion en terminant simplement le polygone comme dans les dispositifs plans.

Actuellement, le modèle de technologie FinFET le plus précis pour les simulations SPICE est le PTM-MG développé par ASU (SINHA et al., 2012) (PTM, 2018). D'autre part, le PDK ASAP7 développé par ASU en partenariat avec ARM Ltd se démarque car il admet des conjectures de conception réalistes concernant l'étape de lithographie et les compétences technologiques actuelles (CLARK et al., 2016).

#### **3. DEFIS TECHNOLOGIQUES FINFET**

Ce chapitre présente un aperçu général des problèmes rencontrés dans les appareils FinFET. De plus, il présente en détail les deux défis de fiabilité évalués dans ce travail : la variabilité de fabrication et les erreurs logicielles induites par le rayonnement. La dernière sous-section de ce chapitre décrit les quatre techniques d'atténuation au niveau du circuit étudiées et comment chacune d'elles a été mise en œuvre.

#### **VARIABILITE DE FABRICATION**

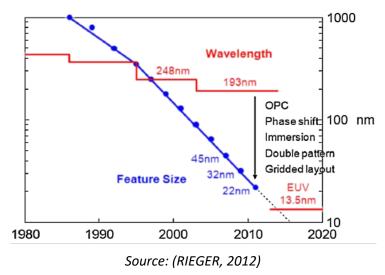

Les technologies FinFET sont plus susceptibles de subir des variations de processus telles que la rugosité de bord de ligne (LER) et la granularité de grille métallique (MGG). La variabilité de fabrication représente une déviation aléatoire qui modifie la structure du transistor et, par conséquent, modifie les propriétés électriques d'un circuit. De cette manière, les spécifications de conception typiques subissent des modifications stimulant la dégradation du circuit, une consommation électrique anormale et une divergence de performances, augmentant la perte de rendement paramétrique. Généralement, l'étape de lithographie au cours du processus de fabrication utilise une lumière ultraviolette pour transférer les motifs géométriques sur les tranches minces de silicium. Les technologies FinFET ont essayé d'adopter une technologie ultraviolette extrême (EUV) pour toutes les couches afin de fournir des conceptions simples et rentables. Cependant, la longueur d'onde n'a pas suivi le rythme de la mise à l'échelle du dispositif et de multiples approches de modélisation doivent être adoptées (RIEGER, 2012). Tous ces facteurs contribuent au LER, ce qui signifie une déviation des bords du transistor par rapport à la forme attendue.

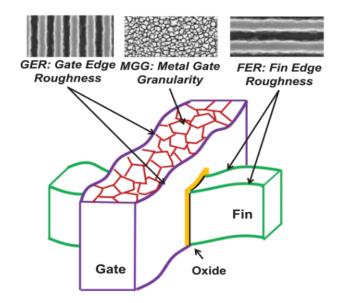

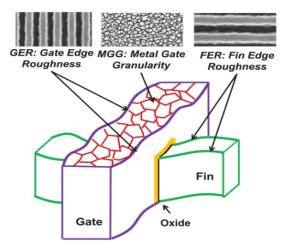

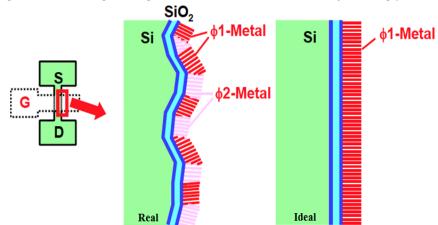

Les imperfections de la région de la porte sont classées comme rugosité du bord de la porte (GER), tandis que les variations de la surface des ailettes sont appelées rugosités du bord de la fin (FER), comme le montre la Figure 2. Le MGG a pris de l'importance depuis l'adoption des diélectriques à améliorer le contrôle de porte sur la région de canal dans les technologies inférieures à 45 nm. La différence d'énergie entre le niveau de vide et le niveau de Fermi d'un solide s'appelle la fonction de travail (WF). L'orientation du grain de la porte en métal provoque une déviation de la fonction de travail de la porte. Dans le processus de fabrication, les dispositifs à grille en métal sont généralement fabriqués en utilisant des métaux avec différentes fonctions de travail ( $\varphi$ m) alignées de manière aléatoire, ce qui implique des fluctuations de fonction de travail plus élevées (WFF) (DADGOUR; DE; BANERJEE, 2008). Des recherches antérieures indiquent que la fluctuation des fonctions de travail est la principale source de variabilité des dispositifs FinFET (MEINHARDT; ZIMPECK; REIS, 2014b).

Figure 2 : Principales sources de variation aléatoire dans le FinFET: GER, MGG, and FER (JIANG et al., 2016)

#### **EFFETS DE RAYONNEMENT NATUREL**

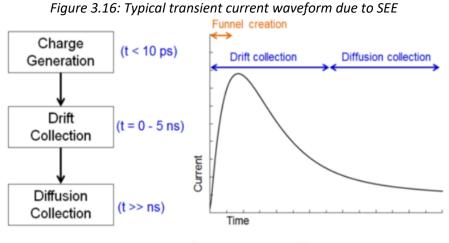

Une autre préoccupation liée à la fiabilité des nœuds technologiques avancés est la susceptibilité aux environnements de rayonnement naturel. Initialement, les effets des radiations dans les systèmes électroniques n'étaient considérés comme pertinents que dans les cas de conception militaire, avionique ou spatiale. Néanmoins, avec l'avancement de la microélectronique, des défauts induits par les radiations peuvent se produire même au niveau de la mer (DODD et al., 2010). Au cours de l'ère de la CMOS, la dose ionisante totale (TID) était la principale source de défauts de radiation entraînant des dommages fonctionnels permanents et irréversibles. À mesure que la technologie évoluait, les événements transitoires à événement unique (SEE) gagnaient en importance et devenaient de plus en plus importants pour les systèmes électroniques aux niveaux spatial et terrestre. SEE se produit en raison de l'interaction de particules énergétiques avec le silicium (tels que neutrons, électrons, protons, particules alpha et ions lourds) dans les drains sensibles des transistors, provenant de rayonnements spatiaux et terrestres. La charge déposée par une seule particule ionisante peut produire une déviation temporaire sur un court intervalle de temps qui peut altérer ou non le comportement du système. Les effets non destructifs les plus connus sont les événements uniques (SEU) et les événements transitoires (SET). Le SEU se produit lorsqu'une particule énergétique frappe un circuit séquentiel, tel qu'un verrou ou une bascule, en modifiant le bit stocké. Sinon, le SET se produit lorsque la particule rencontre un circuit combinatoire, tel que des portes de base ou des additionneurs complets, générant une impulsion transitoire, qui peut ou non être capturée par un élément de mémoire.

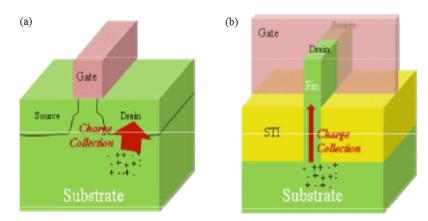

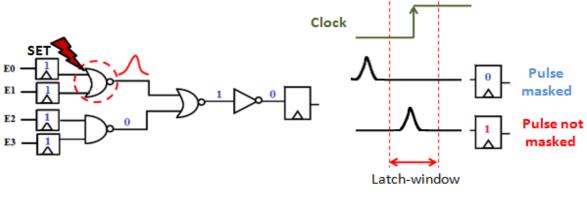

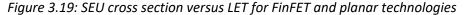

En général, les technologies nanométriques diminuent la charge minimale requise pour induire un SET en raison de faibles tensions d'alimentation et de capacités intrinsèques réduites (SEIFERT et al., 2015). Le fonctionnement en fréquence supérieure augmente également la probabilité qu'un élément de mémoire verrouillant un SET généré dans la logique combinatoire ainsi que le phénomène de partage de charge deviennent plus fréquents dans les circuits intégrés à densité supérieure. Cependant, la nature perturbatrice des FinFET minimise le volume de silicium exposé au mécanisme de collecte de charge, comme illustré à la figure 3, ce qui diminue la susceptibilité aux soft errors sur ces dispositifs. La controverse est la variabilité de fabrication qui peut changer le transfert d'énergie linéaire (LET) pour induire un soft error. De cette manière, même si la structure 3D des dispositifs FinFET est moins sensible aux erreurs logiques, les autres problèmes de fiabilité ne permettent pas que les effets du rayonnement puissent être négligeables.

Figure 3: Mécanisme de collecte de charges dans des dispositifs (a) plans et (b) FinFET (LEE et al., 2015)

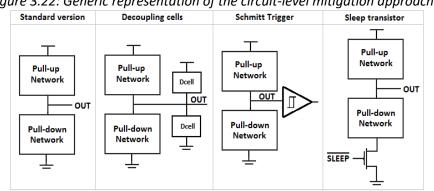

#### **APPROCHES DES DURCISSEMENT AU NIVEAU DU CIRCUIT**

Plusieurs techniques peuvent être appliquées à différents niveaux d'abstraction pour améliorer la fiabilité des circuits intégrés. Habituellement, des techniques d'atténuation basées sur l'utilisation de différents dispositifs, matériaux ou profils de dopage estiment votre efficacité à l'aide de simulations TCAD. Bien que ce niveau d'abstraction présente des résultats très précis, il nécessite un temps de calcul plus long pour les conceptions VLSI. Une solution consiste donc à étudier des approches au niveau du circuit qui modifient la conception des cellules logiques afin d'obtenir des solutions plus robustes. Les ajustements de conception peuvent être liés à l'insertion de composants ou d'éléments de filtrage, à l'exploration de différents arrangements de transistors, à l'optimisation de grille, au repliement de transistors, à la redondance matérielle, à l'augmentation de la capacité des nœuds les plus sensibles et à l'utilisation de la conception à plusieurs niveaux cellules complexes. Les quatre approches d'atténuation au niveau du circuit explorées dans ce travail sont le transistor reordering, decoupling cells, Schmitt Trigger et sleep transistor.

#### **TRANSISTOR REORDERING**

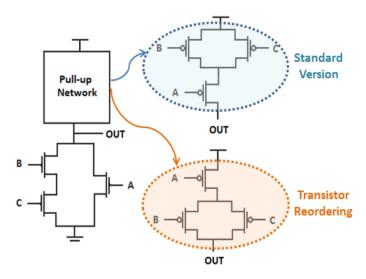

L'optimisation de la disposition des transistors est une méthode généralement utilisée pour concevoir des circuits plus rapides, pour réduire les courants de fuite ou pour traiter les effets d'instabilité de la température de polarisation (BTI); (SILVA; REIS; RIBAS, 2009) (BUTZEN et al., 2010) ( CHUN; CHEN, 2016). Le principe de cette technique est de modifier les agencements de transistors en conservant la même fonction logique pour toutes les topologies. Les possibilités peuvent être obtenues en utilisant différents styles logiques tels que CMOS complémentaires, logique pondérée et logique passe-transistor, ou par *transistor reordering*. La réorganisation du transistor modifie les caractéristiques électriques et physiques des cellules logiques et, par conséquent, la susceptibilité à la variation de fabrication et aux erreurs logiques est également modifiée.

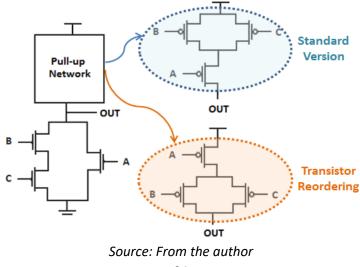

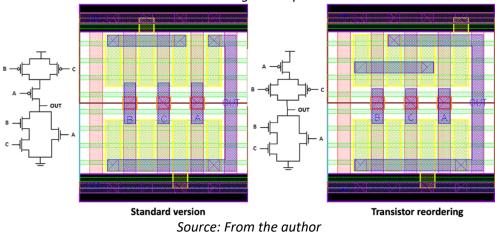

La figure 4 montre deux topologies alternatives pour la cellule AOI21 qui sont logiquement équivalentes. Dans le réseau de réception, le transistor série (signal d'entrée A) peut être placé à proximité ou à distance de la sortie de la cellule. Certaines portes logiques, telles que AOI221 et OAI221, peuvent également explorer un emplacement intermédiaire entre les associations parallèles pour placer le transistor en série. La topologie de fermeture est définie comme la version standard de ce travail car elle est la plus utilisée dans les bibliothèques de cellules standard. Lorsque les transistors du réseau complémentaire n'ont qu'une association parallèle, le réarrangement n'est pas nécessaire car il n'influence pas les résultats tels que la consommation d'énergie et les performances. L'absence de pénalité de surface est le principal avantage de cette technique.

Figure 4 : Version standard de la cellule logique AOI21 et avec le transistor reordering

#### **DECOUPLING CELLS**

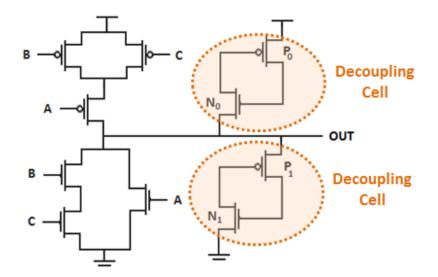

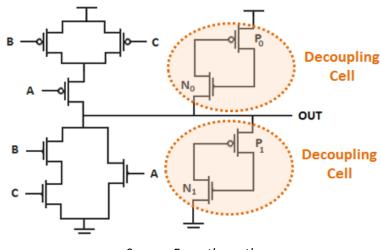

L'ajout de cellules de découplage est une méthode capacitive couramment utilisée dans plusieurs conceptions industrielles pour assurer une plus grande immunité au bruit sur les rails d'alimentation et les lignes de signaux (EVANS et al., 2002) (SU et al., 2003). Les *decoupling cells* sont connectées à la sortie de grille et sont composées de deux transistors agencés en mode de couplage croisé, comme illustré à la figure 5 pour la cellule AOI21. Ces cellules augmentent la capacité totale dans le noeud de sortie, augmentant la charge critique pour produire une impulsion SET et rendant ce noeud moins sensible à l'impact des particules énergétiques. Dans (ANDJELKOVIC et al., 2018), cette technique a été utilisée pour filtrer les impulsions SET générées par des particules de basse énergie dans un ensemble de portes logiques conçues à l'aide de la bibliothèque numérique CMOS en masse de l'IHP de 130 nm avec l'injection de défaut via le double courant exponentiel au niveau de SPICE.

De plus, les *decoupling cells* fournissent du courant aux portes lors de la commutation, protégeant les circuits des perturbations causées par les variations de processus. Pour obtenir de meilleurs résultats en ce qui concerne l'atténuation, il est recommandé d'utiliser deux cellules de découplage de telle sorte qu'une cellule soit connectée entre la sortie et le rail d'alimentation, tandis que l'autre est placée entre le rail de sortie et le sol. Comme l'insertion de *decoupling cells* est une méthode capacitive, les cellules de découplage plus grandes contribuent encore plus à l'atténuation de la variabilité de fabrication et des *soft errors* induites par le rayonnement. L'inconvénient est la superficie et les frais généraux de consommation d'énergie dus à l'ajout de quatre transistors supplémentaires dans la conception.

Figure 5 : Conception de la cellule logique AOI21 reliant les decoupling cells en sorti

#### SCHMITT TRIGGER

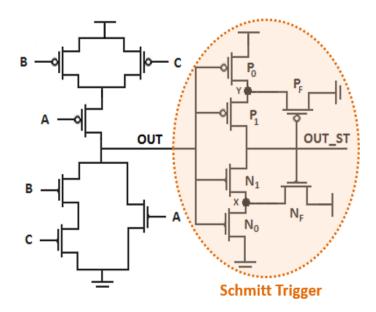

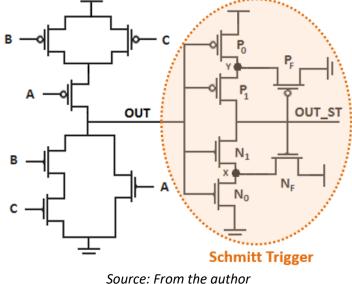

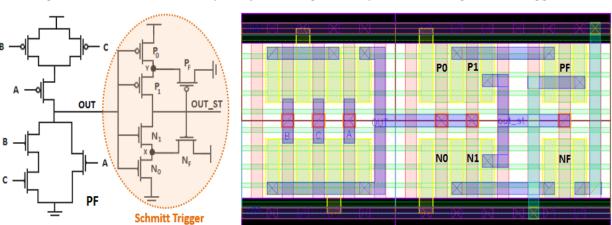

Les Schmitt Triggers ont une propriété d'hystérésis inhérente couramment utilisée pour améliorer la stabilité du signal et une immunité élevée au bruit. Ce travail explore une topologie bien connue de Schmitt Trigger où la principale différence par rapport aux versions les plus courantes est la présence de dispositifs P<sub>F</sub> et N<sub>F</sub> qui sont responsables d'un système de rétroaction, comme le montre la figure 6 (LOTZE; MANOLI, 2017). Par exemple, si la sortie est à un niveau haut, le transistor N<sub>F</sub> est activé, entraînant le noeud X à un potentiel élevé, forçant la tension drain-source du transistor N<sub>1</sub> presque nulle et sa tension grille-source dans la région négative. Ce type de topologie réduit le courant de fuite dans N<sub>1</sub> de façon exponentielle, en augmentant le rapport de courant I<sub>ON</sub>/I<sub>OFF</sub> et en minimisant la dégradation de la sortie.

Le principal effet de la variabilité de fabrication est un décalage de la courbe de transfert de tension (VTC) dû à la variation de la tension de seuil. L'impact de variabilité sur le VTC est réduit dans le déclencheur de Schmitt en raison de la forte influence de la tension grille-source des transistors internes (N<sub>1</sub> et P<sub>1</sub>) sur son point de commutation. Le remplacement des onduleurs traditionnels par Schmitt Triggers sur des additionneurs complets s'avère être une alternative attrayante pour atténuer les effets des variations de fabrication sur les technologies planaires (DOKANIA; ISLAM, 2015) (TOLEDO et al., 2018) ainsi que pour une technologie FinFET (MORAES et al., 2018). L'inconvénient principal de cette technique est également la surcharge en surface et en puissance due à l'ajout de six transistors supplémentaires dans le circuit.

Figure 6 : Conception de la cellule logique AOI21 reliant un Schmitt Trigger à la sortie

#### **SLEEP TRANSISTOR**

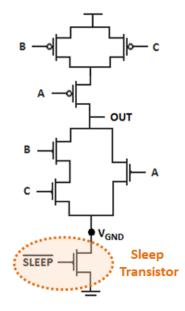

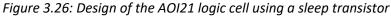

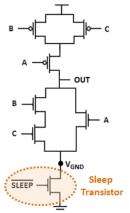

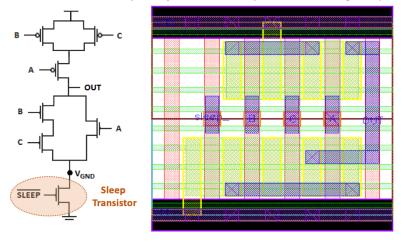

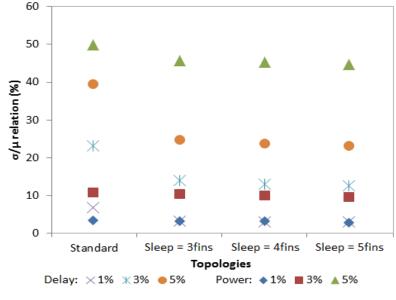

Le *power-gating* est une stratégie largement utilisée dans les conceptions de faible puissance pour couper les blocs de circuit qui ne sont pas utilisés, améliorant ainsi la puissance globale d'une puce (CALIMERA et al., 2015). La différence entre les conceptions à commande de puissance réside dans la granularité des blocs. Ce travail se concentre sur un modèle à grain fin dans lequel un *sleep transistor* est ajouté à chaque cellule. Cependant, pour les circuits plus importants, le style à blocs est plus indiqué pour éviter la surcharge. La figure 7 illustre la cellule AOI21 avec un *sleep transistor* placé entre le réseau de tirage et le rail de masse. Le signal de veille permet de contrôler les états "actif" (veille = 0) et "inactif" (veille = 1) du transistor.

Lorsque le transistor de veille est en mode actif, il garantit une connexion typique de la cellule logique au rail de masse, agissant en tant que régulateur de tension d'alimentation. En mode veille, le transistor de veille est désactivé, déconnectant ainsi la terre virtuelle (V<sub>GND</sub>) de la terre physique. Ce comportement vise à réduire les courants de fuite, les défauts transitoires et les effets BTI. De plus, l'ajout de transistors de sommeil s'est avéré très efficace pour atténuer l'impact des variations de processus dans les technologies planaires (REIS; CAO; WIRTH, 2015). Cependant, pour appliquer avec succès la technique du transistor veille, il faut considérer deux points fondamentaux: 1) le contrôle correct du signal de veille; et 2) l'adoption d'un dimensionnement approprié. Le principal inconvénient de cette technique est la dégradation des performances lorsque le transistor de veille est en mode actif, ce qui en fait le retard dans le pire des cas pour les cellules logiques.

Figure 7 : Conception de la cellule logique AOI21 utilisant un sleep transistor

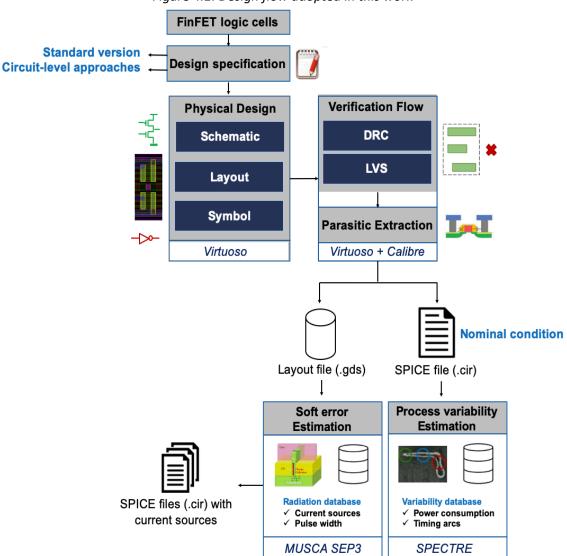

#### 4. METHODOLOGIE D'EVALUATION

Ce chapitre explique la méthodologie utilisée dans ce travail depuis la conception de FinFET jusqu'à l'évaluation de la variabilité de fabrication et de la susceptibilité aux radiations. Il présente également le comportement typique des cellules logiques FinFET à des fins de comparaison, c'est-à-dire sans appliquer d'approche au niveau du circuit pour atténuer les effets des variations de WF et des *soft errors*. Premièrement, le flux de conception a été effectué en tenant compte de la version standard des cellules à des fins de comparaison, puis le schéma de chaque cellule a été modifié à l'aide des approches au niveau du circuit décrites dans la section 3.3 afin d'obtenir des circuits plus fiables.

Les cellules logiques passent par trois étapes élémentaires : conception physique, flux de vérification et extraction parasite. Dans la conception physique, le schéma, la présentation et le symbole de toutes les cellules logiques ont été implémentés à l'aide de l'outil Virtuoso de Cadence. Ensuite, chaque mise en page a été soumise au flux de vérification composé des étapes de vérification des règles de conception (DRC) et de mise en forme par rapport au schéma (LVS).

Dans ce travail, les étapes DRC et LVS sont basées sur les règles technologiques du PDK FinFET à 7 nm appelé ASAP7 développé par ASU en collaboration avec ARM Ltd (CLARK et al., 2016). Ce PDK implémente le modèle à porte courte, dans lequel une cellule TAP est utilisée pour connecter la porte arrière à la porte avant, garantissant ainsi le bon fonctionnement des transistors. Enfin, les résistances et capacités parasites (RC) des fils sont extraites de la structure. Une nouvelle liste de circuits est générée de telle sorte que chaque réseau possède un sous-système avec l'arborescence RC et les connexions entre les réseaux parasites. Les outils Calibre de Mentor, ainsi que Virtuoso, ont été utilisés pour exécuter les étapes de flux de vérification et d'extraction parasite. Le flux de données géométriques (GDS) est un fichier généré par l'outil Virtuoso qui représente toutes les formes géométriques de la présentation au format binaire. Ce fichier peut être utilisé pour reconstruire tout ou partie d'une mise en page, pour transférer la mise en page entre différents outils ou pour créer des photomasques pour le processus de fabrication.

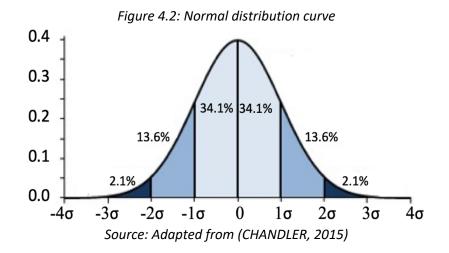

#### ÉVALUATION DE LA VARIABILITE DE FABRICATION

Cette thèse considère deux simulations MC effectuées dans SPECTRE à partir de Cadence pour estimer le comportement des cellules logiques FinFET sous des variations de fabrication (ALIOTO; CONSOLI; PALUMBO, 2015). Comme la fonction de travail (WF) est le paramètre le plus impacté par la variabilité de fabrication dans les technologies FinFET, la WF est modélisée comme une fonction gaussienne, en supposant un écart de 3-sigma ( $\sigma$ ). Toutes les cellules logiques ont été évaluées en utilisant des niveaux de WFF variant de 1% à 5% en raison du manque d'informations de l'industrie sur les niveaux de WFF dans les technologies FinFET actuelles. Ces variations ont été adoptées en tant que référence aux valeurs nominales du modèle de tension de seuil régulière (RVT) de ASAP7.

La base de données sur la variabilité fournit un résumé des résultats statistiques des simulations MC, telles que les valeurs minimale (minimale) et maximale (maximale), la moyenne ( $\mu$ ) et l'écart type ( $\sigma$ ) pour tous les arcs de synchronisation ainsi que pour la consommation d'énergie. Malgré les données fournies par la base de données de variabilité pour les mesures de délai et de puissance, ce travail a également retenu deux valeurs de mérite pour permettre une comparaison plus détaillée: 1) l'écart type normalisé ( $\sigma$ / $\mu$ ) pour indiquer la sensibilité des cellules logiques au WF les fluctuations; et 2) la relation delta ( $\Delta$ ) pour spécifier l'ampleur du changement de sensibilité aux variations de processus lorsque les cellules logiques sont conçues en utilisant une approche d'atténuation au niveau du circuit au lieu de la version standard.

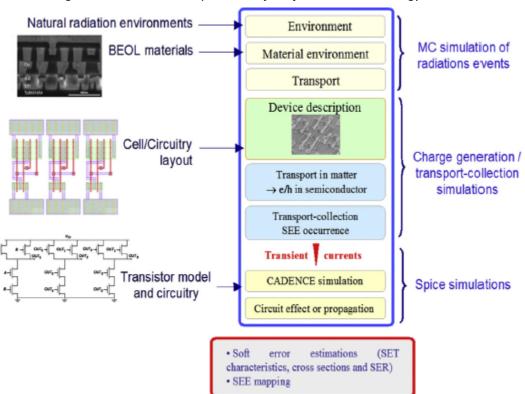

#### **ESTIMATION DES SOFT ERRORS**

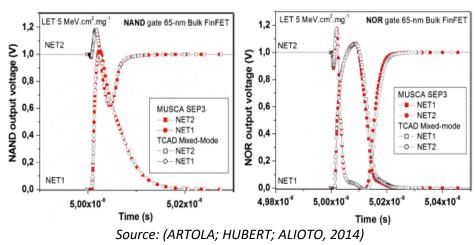

La susceptibilité aux erreurs logiques des cellules logiques FinFET a été estimée à l'aide de l'outil MUSCA SEP3 développé par l'ONERA, le laboratoire aérospatial français (HUBERT et al., 2009) (ARTOLA et al., 2013). MUSCA SEP3 est un outil générateur d'événements de rayonnement, basé également sur la méthode de Monte Carlo, qui modélise toutes les étapes depuis l'introduction d'une particule énergétique dans la matière jusqu'à la manifestation d'une impulsion transitoire sur les circuits. Les particules de rayonnement disponibles pour l'analyse sont les neutrons, les protons, les ions lourds, les muons et les particules alpha. Cet outil prend en compte l'environnement de rayonnement ciblé (espace, avionique, sol), les caractéristiques de rayonnement (LET, angle d'incidence, type de particule énergétique), les mécanismes de transport dynamique et de collecte de charges, la tension de polarisation, les caractéristiques de tracé, le circuit électrique réponse, l'oxyde de STI et les détails du processus de fabrication

Les frais de collecte de chaque transistor sont calculés en fonction de la structure de l'appareil, qui peut être extraite à partir d'une ingénierie inverse ou à l'aide du rapport FEOL du fichier GDSII. Le transport de modélisation et la collecte des porteurs libres dans le silicium sont effectués à l'aide de modèles analytiques 3D, via les informations BEOL, qui adoptent les mécanismes suivants: diffusion ambipolaire, collecte dynamique, amplification bipolaire à collections multiples pour évaluer le partage de charge et le phénomène d'extinction d'impulsion, recombinaison et dépendance de biais. L'impact de la température (jusqu'à 50K) est pris en compte pour tous les modèles physiques et électriques utilisés pour le transport et la collecte de charge dans les semi-conducteurs. Le modèle mis en œuvre pour l'amplification bipolaire bipolaire dépend de deux aspects. Premièrement, le modèle utilise les résistances d'accès équivalentes du dispositif multi-états pour déterminer le déclenchement du transistor

bipolaire. En outre, le modèle considère la variabilité de l'amplification de la collecte de charges en fonction de la technologie LET due aux technologies FinFET.

La base de données SET générée par l'outil est très précise car elle prend en compte toutes les caractéristiques présentées ci-dessus. Une nouvelle base de données SET est créée pour chaque configuration différente. Une fois cela fait, il est composé d'un ensemble de sources de courant à injecter dans les noeuds sensibles, c'est-à-dire le drain des transistors. L'injection de faute est effectuée automatiquement à l'aide d'un script associé à SPECTRE de Cadence. Après, les résultats sont évalués pour déterminer la susceptibilité de *soft error* des circuits.

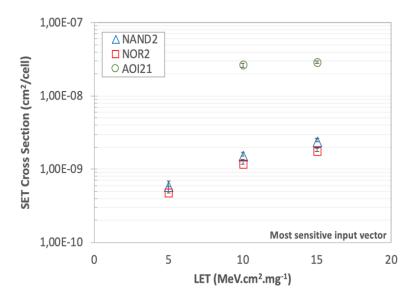

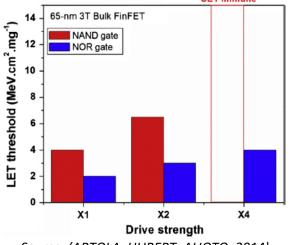

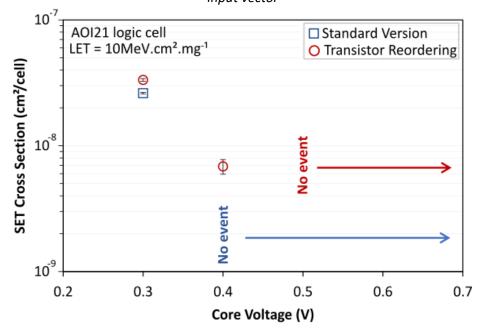

Ce travail explore l'irradiation par des ions lourds sous un angle d'incidence normal, à la température ambiante (27°C) et avec une tension d'alimentation variant de la valeur nominale (0,7V) au régime proche du seuil (0,3V). Les cellules logiques NOR2, NAND2 et AOI21 ont été évaluées sous faible LET, c'est-à-dire moins de 15MeV.cm<sup>2</sup>.mg<sup>-1</sup> ce qui correspond aux particules secondaires représentatives induites par des neutrons ou des protons dans les applications avioniques et terrestres. La susceptibilité à la SE a également été étudiée dans des LET plus élevés (30 et 58MeV.cm<sup>2</sup>.mg<sup>-1</sup>) représentant l'environnement spatial. Pour obtenir une estimation plus précise, la base de données SET a été simulée pour tous les vecteurs d'entrée. De plus, la sortie de chaque cellule est connectée à une chaîne de quatre inverseurs, permettant l'évaluation des effets de propagation. Un défaut est comptabilisé si l'amplitude de tension du noeud de sortie dépasse la tension de seuil de grille (V<sub>DD</sub>/2). Ce travail adopte la section transversale ( $\sigma_{cs}$ ) comme facteur de mérite central pour estimer la susceptibilité des cellules logiques à la SE.

#### **COMPORTEMENT TYPIQUE DES CELLULES LOGIQUES FINFET**

#### **SENSIBILITE A VARIABILITE DE FABRICATION**

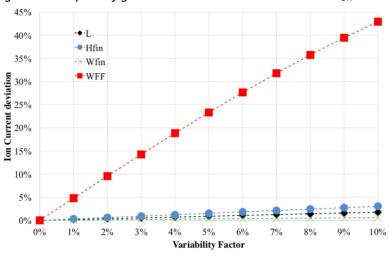

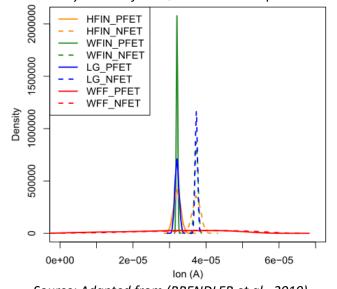

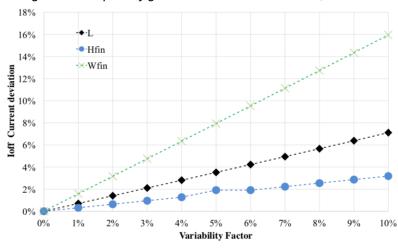

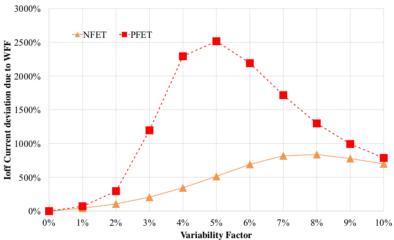

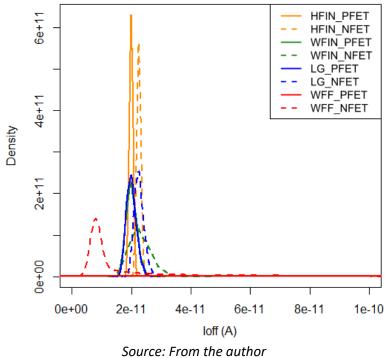

La caractérisation des dispositifs adoptant le modèle électrique fourni par ASAP7 est cohérente avec ceux obtenus à l'aide d'autres technologies multi-serveurs (MEINHARDT; ZIMPECK; REIS, 2014a). Les fluctuations de la fonction de travail dominent l'impact sur les courants I<sub>ON</sub>/I<sub>OFF</sub> des appareils FinFET. L'augmentation du nombre d'ailettes est un moyen de protéger les dispositifs contre les variations géométriques, mais cette méthodologie ne permet pas d'atténuer les effets de fluctuation de la WF. Pour cette raison, désormais, cette thèse adopte toujours les fluctuations du travail pour toutes les évaluations de la variabilité de fabrication.

Les fluctuations WF sur les périphériques FinFET peuvent générer de la puissance et retarder les écarts. Ces écarts sont estimés à l'aide de l'écart type normalisé (relation  $\sigma/\mu$ ). Dans ce travail, nous adoptons les termes « variabilité de puissance » et « variabilité de délai » pour indiquer les écarts de puissance et de retard dus aux fluctuations de la WF, respectivement.

Comme prévu, la sensibilité des cellules logiques à la variation de processus ( $\sigma/\mu$ ) augmente lorsque des niveaux plus élevés de fluctuations de la WF ont été explorés pour les deux métriques. Les cellules logiques avec un plus grand nombre d'entrées sont moins robustes aux fluctuations de WF. Par exemple, le NAND4 est au moins 9,2% et 20,6% plus sensible que le NAND2 à la variabilité du délai et de la puissance, respectivement.

En comparant la sensibilité des cellules de base, les variations de processus affectent davantage les cellules NOR que les cellules NAND. En ce qui concerne les cellules complexes, les cellules AOI21 et OAI211 sont plus robustes pour retarder la variabilité que les cellules OAI21 et AOI211. Le comportement de ces cellules est similaire à celui de la variabilité de puissance, sauf lorsque la cellule AOI21 présente une déviation de 1 à 3% et que la cellule OAI211 présente une variation de 5% par rapport aux valeurs nominales. En général, les cellules logiques FinFET sont plus sensibles à la variabilité de retard pour des déviations jusqu'à 4%, mais un comportement opposé peut être vérifié pour des variations de 5%, c'est-à-dire que les cellules logiques deviennent plus sensibles à la variabilité de puissance. De plus, des variations de 5% triplent presque la sensibilité des cellules logiques à la variabilité de puissance par rapport à 4% d'écart. La moyenne ( $\mu$ ) des simulations de MC en version standard est considérée ultérieurement pour estimer les pénalités imposées par les techniques d'atténuation au niveau du circuit.

#### **SENSIBILITE AUX SOFT ERRORS**

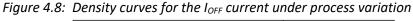

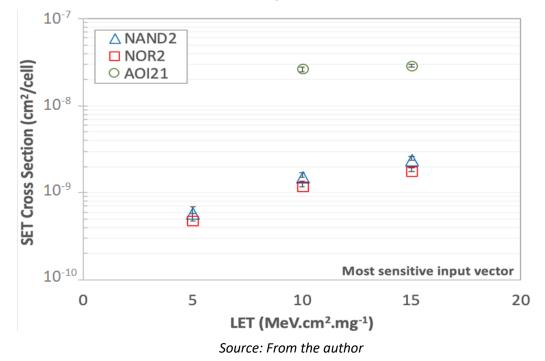

Les soft errors sont des événements transitoires à court intervalle de temps induits par des particules énergétiques provenant de radiations terrestres et spatiales. Les erreurs logicielles induites par les radiations peuvent entraîner des défaillances critiques du comportement du système, pouvant entraîner des pertes de vies humaines ou financières. Cette section évalue l'impact des erreurs logicielles dans trois cellules logiques FinFET sous des valeurs LET faibles, c'est-à-dire inférieures à 15MeV.cm<sup>2</sup>.mg<sup>-1</sup>. Ces valeurs de LET ont été ciblées car correspondent à des particules secondaires induites par des neutrons dans les applications avioniques et terrestres. La métrique utilisée pour l'évaluation des erreurs logicielles est la section transversale SET en considérant le vecteur d'entrée le plus sensible ainsi que la moyenne de tous les vecteurs d'entrée. La figure 8 montre la sensibilité de soft error des cellules NAND2, NOR2 et AOI21 à un régime proche du seuil (0,3 V) en considérant le vecteur d'entrée le plus sensible. Pour toutes les technologies LET étudiées, les trois portes logiques sont exemptes de défauts à 0,6V et de tension principale. La cellule AOI21 est exempte de défauts avec une LET de 5MeV.cm<sup>2</sup>.mg<sup>1</sup>, et des erreurs logicielles ne sont observées que dans les cellules NAND2 et NOR2 en sortie à 0,3V. Par ailleurs, il est possible d'observer certaines failles à 0,4V et à 0,5V lorsqu'on étudie une valeur LET plus élevée (15MeV.cm<sup>2</sup>.mg<sup>-1</sup>). La réduction du nombre de défauts est due à la nature FinFET qui augmente la charge minimale requise pour induire une impulsion SET.

Figure 8 : SET section transversale de cellules logiques fonctionnant à un régime proche du seuil en tenant compte du vecteur d'entrée le plus sensible

#### 5. ATTENUATION DE LA VARIABILITE DE FABRICATION E DES SOFT ERRORS

Ce chapitre évalue l'utilisation d'approches au niveau du circuit dans la conception des cellules logiques FinFET afin d'améliorer les effets de la variabilité des processus et la susceptibilité aux *soft errors*. En plus des avantages de chaque technique, ce chapitre présente également la tendance à l'atténuation lorsque différents niveaux de fluctuations de WF, de dimensionnement et de valeurs de LET ont été utilisés. Les résultats présentés dans ce chapitre cherchent à: 1) prouver l'efficacité des quatre approches d'atténuation au niveau du circuit étudiées dans cette thèse en considérant différents scénarios de test, 2) indiquer les avantages et les inconvénients de l'adoption de chacune d'elles, et 3) fournir une comparaison globale pour permettre aux concepteurs de choisir la meilleure technique en fonction de l'application cible.

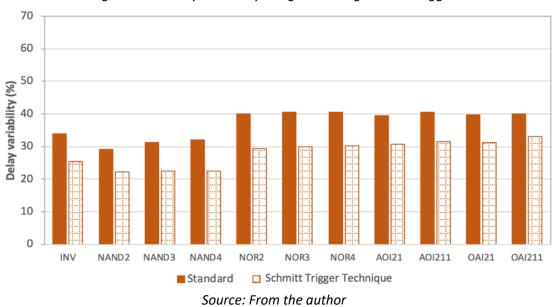

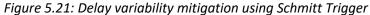

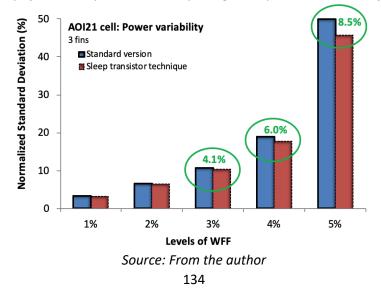

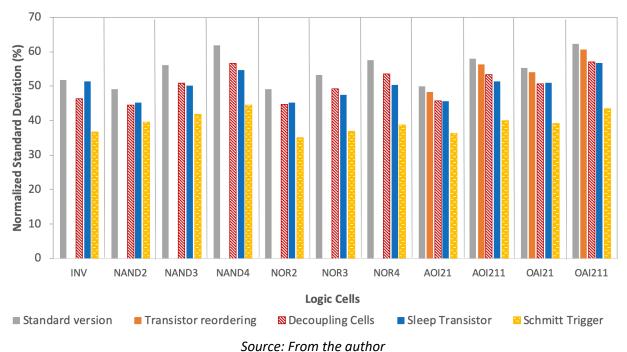

Les cellules logiques peuvent être soumises à des fluctuations élevées (5%), moyennes (3%) ou faibles (1%), de sorte que ces variations peuvent avoir une incidence sur la puissance, les retards de propagation ou les deux. La sensibilité des cellules logiques aux variations du processus est mesurée par l'écart type normalisé (relation  $\sigma/\mu$ ). Comme précédemment présenté. les déviations de puissance et de propagation dues aux variations de processus sont dénominées dans ce travail par variabilité de puissance et de retard.

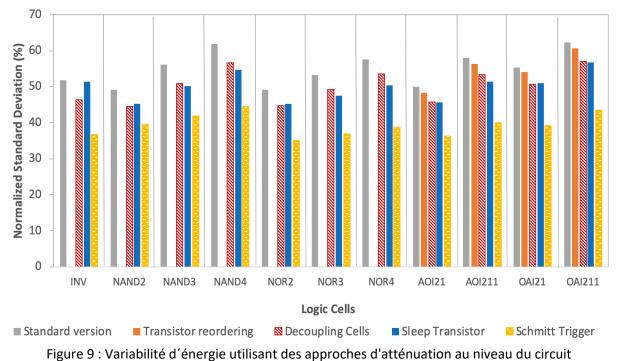

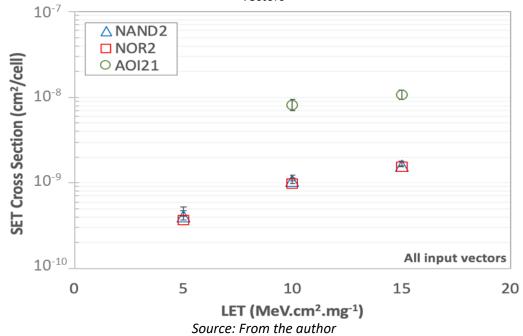

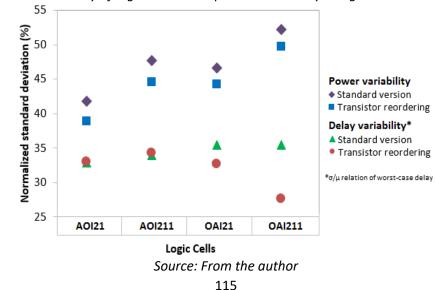

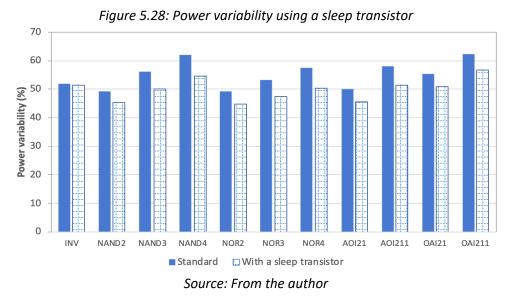

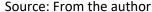

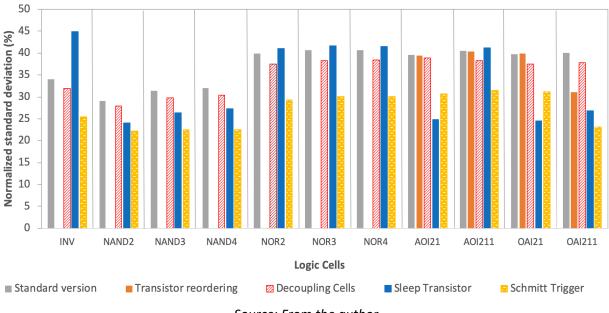

La figure 9 montre l'impact d'un processus de fabrication avec un écart de 5% lorsque les approches d'atténuation de version standard ou au niveau du circuit sont adoptées dans la conception. La meilleure technique pour atténuer l'impact sur la variabilité de la puissance est basée sur l'insertion de *Schmitt Triggers*. Même pour les écarts les plus faibles, l'ajout de Schmitt Trigger reste le plus avantageux. Après cela, la technique la plus indiquée pour atténuer

la variabilité consiste à insérer des *sleep transistors* ou des *decoupling cells*. Pour les conceptions avec 5% d'écart, l'amélioration des deux techniques est similaire. Toutefois, pour les faibles niveaux de fluctuation de WF (1-4%), l'approche par *sleep transistor* est la deuxième meilleure option. Enfin, la technique avec moins d'atténuation de la variabilité d'énergie est le *transistor reordering*.

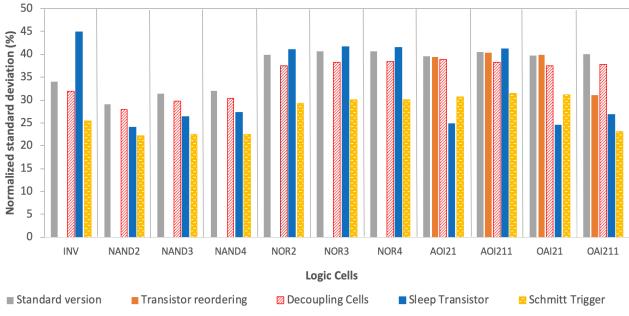

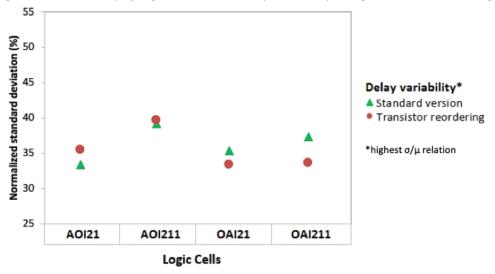

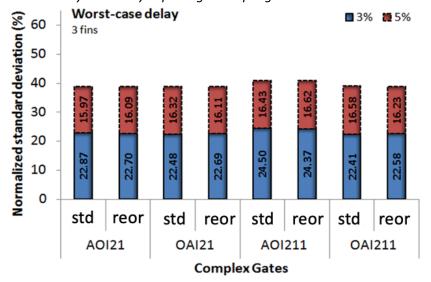

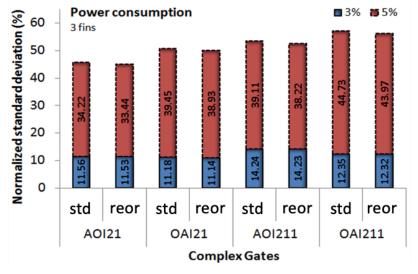

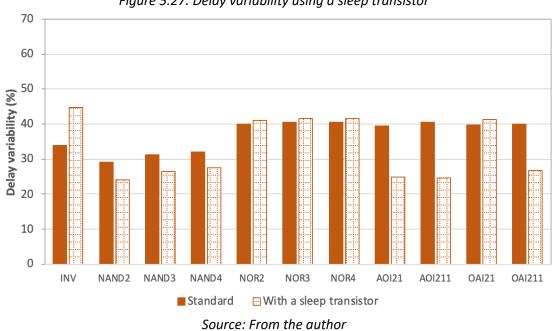

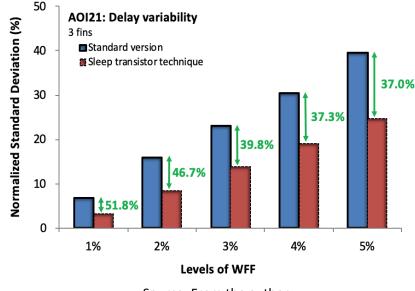

Pour atténuer la variabilité du délai, il est plus difficile de dégager une tendance générale pour toutes les cellules logiques évaluées, comme le montre la figure 10. À l'exception des cellules AOI21 et OAI21, l'insertion de *Schmitt Trigger* est la meilleure technique pour améliorer la variabilité du délai. La seconde alternative varie également en fonction des cellules logiques. Par exemple, l'adoption d'un *sleep transistor* est préférable au *decoupling cells* pour les cellules NAND et OAI211, mais l'inverse se produit pour les cellules INV, NOR et AOI211. Pour les cellules AOI21 et OAI21, la première meilleure option consiste à utiliser les *sleep transistors*. Après, le *Schmitt Trigger* est plus indiqué. La technique de *transistor reordering* n'a apporté que des avantages significatifs en termes d'atténuation de la variabilité de performance pour la cellule OAI211. Pour des niveaux inférieurs de fluctuations de WF (1-4%), la même tendance a été observée pour toutes les cellules logiques.

Figure 10 : Variabilité de performance en utilisant des approches d'atténuation au niveau du circuit

Les quatre techniques utilisées pour atténuer les effets des variations de processus et des erreurs commises induites par un rayonnement ont entraîné certaines pénalités en termes de surface, de consommation électrique et de performances. La technique de *transistor reordering* n'entraîne aucune pénalité de zone et son impact sur la puissance et les performances est faible. Cependant, cette technique n'a pas apporté d'améliorations significatives aux effets causés par les variations de processus sur des cellules complexes. De plus, la réorganisation des transistors devient la cellule logique plus sensible aux *soft errors*.

La connexion de *Schmitt Trigger* à la sortie des cellules logiques est le meilleur moyen de réduire considérablement l'impact des variations de fabrication et d'obtenir des cellules logiques exemptes de défauts, même à un régime proche du seuil. Cependant, des pénalités plus élevées sont observées, principalement en ce qui concerne la consommation d'énergie et les performances. L'insertion de *decoupling cells* a la même pénalité en surface que la technique de *Schmitt Trigger*, mais les inconvénients en termes de consommation d'énergie et de performances sont divisés par deux. De plus, une conception avec *decoupling cells* diminue la susceptibilité aux *soft errors* des cellules logiques exemptes de pannes, même à un régime proche du seuil, mais l'impact sur la consommation et les performances est considérable. Pour la plupart des techniques et des cellules logiques analysées, les pénalités sont plus lourdes lorsque les fluctuations de WF sont faibles.

Les *decoupling cells* avec un plus grand nombre d'ailettes augmente, voire plus, la robustesse des cellules logiques. Cependant, les pénalités augmentent en même temps que le nombre

d'ailerons. Mais pour cette technique, les pénalités introduites sont encore agréables. De la même manière, des *Schmitt Trigger* plus importants dans la conception augmentent l'atténuation de la variabilité d'énergie, mais les inconvénients techniques de la consommation et des performances sont inacceptables. D'autre part, les transistors de sommeil avec un plus grand nombre d'ailettes ne minimisent pas la sensibilité des cellules logiques de manière significative. Pour cette raison, les grands *sleep transistors* ne sont pas conseillés en raison des pénalités élevées introduites.

En général, en considérant les résultats moyens des cellules logiques obtenues pour toutes les approches d'atténuation au niveau du circuit ainsi qu'une évaluation globale de tous les sujets et scénarios de test présentés dans ce travail, il est possible de conclure que :

1. Schmitt Trigger est la meilleure technique si les concepteurs ne font qu'améliorer l'impact de la variabilité, sans aucune exigence de domaine, de performance ou de puissance ;

2. Le *sleep transistor* est la meilleure option si les concepteurs s'attachent à accroître la robustesse de la variabilité de fabrication, mais qu'ils ont des restrictions de zone ;

3. Les *decoupling cells* sont indiquées si l'objectif des concepteurs est d'améliorer l'impact de la variabilité, mais qu'elles ont des exigences en matière de puissance ou de performances ;

4. Les *sleep transistors* ou *Schmitt Triggers* sont les meilleurs choix si les concepteurs se concentrent uniquement sur la susceptibilité aux *soft errors* ;

5. Les *sleep transistors* sont plus indiqués si les concepteurs s'attachent principalement à atténuer l'impact des *soft errors*, mais qu'ils ont des contraintes de zone ;

6. Les *decoupling cells* sont la meilleure alternative si les concepteurs s'attachent à améliorer les effets de la variabilité de fabrication et à devenir un circuit plus robuste aux défauts transitoires, avec des pénalités acceptables en termes de surface, de performances et de consommation d'énergie.

#### **6.** CONCLUSIONS

Les dispositifs FinFET ont été largement adoptés par l'industrie des semi-conducteurs pour les nœuds technologiques de moins de 22 nm, soulevant des questions essentielles liées à la fiabilité des systèmes électroniques. Les petites configurations géométriques imposées par les technologies avancées intensifient les variations de processus, ainsi que la densité plus élevée permettant à une seule particule énergétique d'affecter plusieurs nœuds adjacents. Les principales conséquences de ces défis sont la perte de rendement paramétrique et les défaillances critiques du comportement du système, qui peuvent entraîner des pertes en vies humaines ou financières. L'impact de la variabilité des processus continue d'augmenter à chaque nouveau nœud technologique, et il est de plus en plus difficile de limiter la technologie à l'échelle utilisant des dispositifs FinFET. Du point de vue de la conception, les variations de processus et les erreurs réduites induites par le rayonnement dans les nœuds FinFET nécessitent une estimation précise ainsi que de nouvelles méthodologies de conception capables de réduire les effets causés par celles-ci.

Selon la revue de la littérature, peu de travaux proposent des techniques permettant d'atténuer l'impact des variations de processus et des erreurs logicielles, en particulier pour les technologies FinFET. En outre, il n'existe pas d'approches d'atténuation au niveau des circuits permettant d'examiner les modifications de la conception afin d'obtenir des solutions plus robustes. De cette manière, cette thèse fait progresser l'état de la technique en fournissant:

1. L'évaluation des cellules logiques FinFET sous variabilité de fabrication et effets de rayonnement à l'aide d'un kit de conception de processus prédictif FinFET à 7-nm;

2. La conception de cellules logiques utilisant quatre approches différentes au niveau du circuit pour atténuer l'impact causé par les fluctuations du travail et les erreurs logicielles.

3. un compromis entre les gains et les pénalités de chaque approche concernant la surface, les performances, la consommation d'énergie, la durée d'impulsion SET et la section transversale SET;

4. La tendance d'atténuation des techniques au niveau du circuit lorsque différents niveaux de variation de processus, de dimensionnement de transistor et de LET ont été appliqués dans la conception.

Les approches d'atténuation au niveau du circuit explorées dans cette thèse étaient la réorganisation des transistors et l'insertion de cellules de découplage, de déclencheurs de Schmitt et de transistors de sommeil.

En général, toutes ces techniques réduisent les effets de variabilité de fabrication et la susceptibilité aux *soft errors*, introduisant moins de pénalités, de coûts de mise en œuvre et de complexité de conception par rapport aux rares solutions disponibles dans la littérature.

La technique de réordonnancement des transistors peut augmenter jusqu'à 8% la robustesse des cellules complexes sous des variations de processus (5% d'écart). Cependant, cette méthode n'est pas favorable à l'atténuation des erreurs logicielles, augmentant la sensibilité des cellules complexes jusqu'à 20% pour les faibles LET. Parmi toutes les techniques évaluées, le réordonnancement des transistors présentait moins de frais généraux de puissance et de performances, de plus, il ne comporte aucune pénalité de surface.

L'adoption de *decoupling cells* montre des résultats intéressants pour le contrôle de la variabilité de puissance sous des niveaux de variation supérieurs à 4%. D'autre part, cette technique est efficace pour la réduction de la variabilité du délai indépendamment des niveaux de variation. Les améliorations les plus importantes de la variabilité du délai peuvent être constatées pour des niveaux de variation plus faibles (1 à 3%). La conception avec cellules de découplage diminue la susceptibilité à le *soft error* d'environ 10% pour une valeur LET élevée (58MeV.cm<sup>2</sup>.mg<sup>-1</sup>). Les gains avec des LET inférieurs peuvent atteindre un maximum de 4%.

Cette technique présentait une surcharge de zone importante, mais un impact moindre sur les métriques de puissance et de performance.

La meilleure approche pour contrôler les variations de fabrication consiste à connecter un *Schmitt Trigger* à la sortie des cellules FinFET. Cette technique peut améliorer la variabilité des retards jusqu'à 50%, principalement pour les processus de fabrication avec 2 à 4% d'écarts WF. Pour la variabilité de puissance, une robustesse plus élevée a été obtenue avec des niveaux de variation plus élevés (4-5%). De plus, toutes les cellules logiques étudiées sont exemptes de défauts, même au régime proche du seuil (0,3V) et sous l'influence d'une forte LET (58MeV.cm<sup>2</sup>.mg<sup>-1</sup>). Cependant, comme cette technique ajoute six transistors supplémentaires, elle introduit des pénalités plus sévères en termes de surface et de puissance.

L'insertion d'un *sleep transistor* entre le réseau déroulant et le rail de masse est avantageuse principalement pour le contrôle de la variabilité de la puissance. Les améliorations pour certaines cellules dépassent 10% pour des niveaux de variation plus élevés (4-5%). D'autre part, l'efficacité de cette méthode pour la réduction de la variabilité du retard dépend de la manière dont les transistors sont disposés avec le *sleep transistor* dans le réseau déroulant. Cette technique est également exempte de défauts, même au régime proche du seuil (0,3V) et sous l'influence d'une forte LET (58MeV.cm<sup>2</sup>.mg<sup>-1</sup>). La disposition avec un transistor de veille introduit une petite surface supplémentaire, mais l'impact sur les métriques de puissance et de performance est très important.

Une conception avec de plus grandes *decoupling cells* (quatre ou cinq ailettes) est avantageuse pour atténuer la variabilité des processus, avec une augmentation acceptable des frais généraux. Le *Schmitt Trigger* avec un plus grand nombre d'ailettes améliore également la sensibilité aux fluctuations de la WF, mais les inconvénients techniques impliqués sont inacceptables. D'autre part, l'augmentation du dimensionnement du *sleep transistor* ne modifie pas de manière significative la sensibilité à la variabilité de fabrication.

Le choix de la technique la plus appropriée dépend de l'application cible et de ses exigences en matière de zone, de consommation électrique et de performances. La technique de Schmitt Trigger a présenté les meilleurs résultats pour l'atténuation de la variabilité de fabrication et la dureté du rayonnement. Cependant, cette approche introduit des pénalités critiques sur la surface, les retards et la consommation d'énergie. De cette manière, si un concepteur souhaite améliorer la fiabilité du circuit en introduisant des pénalités plus acceptables, une conception avec des *decoupling cells* est plus indiquée pour contrôler la variabilité du retard. D'autre part, pour obtenir une réduction de la variabilité de puissance et de la susceptibilité aux *soft errors*, la meilleure option consiste à utiliser la technique du *sleep transístor*.

Enfin, cette thèse fournit un ensemble d'informations utiles pour aider: 1) l'industrie des semi-conducteurs à obtenir des améliorations de rendement paramétriques en évitant les

nombreuses étapes de la reconception; 2) les concepteurs introduisent une technique d'atténuation au niveau de la disposition pour une application donnée, connaissant tous les avantages et les inconvénients de son adoption; et 3) l'industrie aérospatiale telle que l'ONERA, le laboratoire aérospatial français, à concevoir des systèmes plus fiables pour la prochaine génération de constellations de nano-satellites.

#### **TRAVAUX FUTURS**

Il existe plusieurs possibilités de nouvelles expériences et scénarios de test pouvant être réalisés à partir de cette thèse. Premièrement, il est possible d'étendre cette recherche en explorant deux autres approches potentielles pour améliorer la robustesse des cellules logiques FinFET : la conception à plusieurs doigts (FORERO et al., 2017) et le pitch à double porte (MARELLA et al., 2015). Les deux techniques doivent être mises en œuvre au niveau de la mise en page.

Une étude approfondie peut être réalisée pour déterminer les meilleurs endroits pour placer ces cellules dans une chaîne de portes, de sorte qu'il n'est pas pratique d'appliquer des *decoupling cells, Schmitt Trigger* ou des *sleep transistors* dans toutes les cellules logiques de circuits intégrés. En outre, il est crucial de mieux comprendre car chaque technique contribue à atténuer les effets des variations de fabrication et des *soft errors* induites par les radiations. De plus, certains moyens de réduire les inconvénients techniques (surface, puissance, délai) imposés par les approches d'atténuation au niveau du circuit explorées dans ce travail doivent être examinés.

Une autre possibilité de travail futur est l'évaluation des fluctuations de la WF et des erreurs logicielles, en considérant le cas le plus défavorable de défaillances pour introduire les variations de processus sur les circuits. En outre, l'impact des variations de processus peut également être estimé en utilisant comme métrique le produit de délai-énergie (PDP), qui offre un compromis précis entre les résultats de variabilité de puissance et de délai. Enfin, depuis cette thèse, une bibliothèque de cellules pour les conceptions numériques peut être développée, se concentrant sur des questions de fiabilité, telles que l'atténuation de la variabilité des processus et la dureté du rayonnement.

| Chapter 1: Introduction                           | .32 |

|---------------------------------------------------|-----|

| 1.1 Motivation                                    | 33  |

| 1.2 Objectives                                    | 34  |

| 1.3 Work Organization                             | 35  |

| Chapter 2: Theoretical Foundation                 | 37  |

| 2.1 Multigate Devices                             | 37  |

| 2.2 General Background of FinFET Technology       | 42  |

| 2.3 The Advancement in the Semiconductor Industry | 44  |

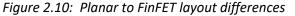

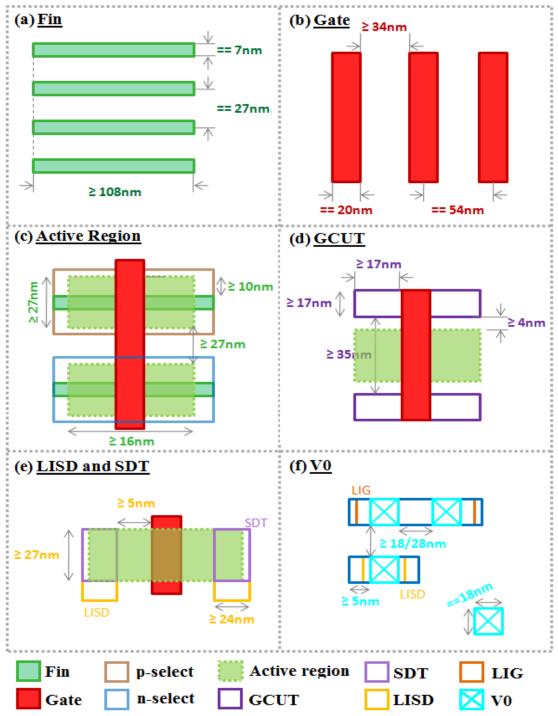

| 2.4 Layout Design using FinFET Devices            | 47  |

| 2.5 FinFET Predictive Models                      | .51 |

| 2.5.1 Technology models for SPICE simulations     | .51 |

| 2.5.2. Process Design Kit (PDK)                   | .53 |

| Chapter 3: FinFET Technology Challenges           | .58 |

| 3.1 Process Variability                           | 60  |

| 3.1.1 Sources of Process Variability              | 63  |

| 3.1.1.1. Line Edge Roughness                      | 64  |

| 3.1.1.2 Metal Gate Granularity                    | 67  |

| 3.1.1.3 Random Dopant Fluctuation                 | 67  |

| 3.1.2 Literature review about process variability | .68 |

| 3.1.2.1 General Background                        | .68 |

| 3.1.2.2 State-of-the-art works                    | .69 |

| 3.2 Radiation-Induced Soft Errors                 | .76 |

| 3.2.1 Radiation environment                       | .76 |

### **Table of Contents**

| 3.2.2 Radiation effects on devices                                      | 77  |

|-------------------------------------------------------------------------|-----|

| 3.2.3 Fault masking                                                     | 79  |

| 3.2.4 Charge collection mechanism in FinFET devices                     | 82  |

| 3.2.5 Literature review about radiation effects                         | 84  |

| 3.2.5.1 General background                                              | 84  |

| 3.2.5.2 State-of-the-art works                                          | 86  |

| 3.3 Circuit-Level Mitigation Techniques                                 | 93  |

| 3.3.1 Transistor reordering                                             | 94  |

| 3.3.2 Decoupling cells                                                  | 95  |

| 3.3.3 Schmitt Trigger                                                   |     |

| 3.3.4 Sleep Transistor                                                  | 97  |

| Chapter 4: Evaluation Methodology                                       | 98  |

| 4.1 Process Variability Evaluation                                      | 101 |

| 4.2 Soft Error Estimation                                               |     |

| 4.3 Typical Behavior of FinFET Logic Cells                              | 105 |

| 4.3.1 Effects of process variability                                    | 105 |

| 4.3.1.1 Characterization of devices from ASAP7 under process variations | 105 |

| 4.3.1.2 Sensitivity to process variations                               | 109 |

| 4.3.2 Susceptibility to Soft Errors                                     |     |

| Chapter 5: Process Variability and Soft Error Mitigation                | 114 |

| 5.1 Design with Circuit-Level Mitigation Approaches                     | 114 |

| 5.1.1 Transistor reordering                                             | 114 |

| 5.1.1.1 Soft error susceptibility                                       |     |

| 5.1.2 Decoupling cells                                                  | 120 |

| 5.1.2.1 Impact of different levels of WF fluctuations         | 122 |

|---------------------------------------------------------------|-----|

| 5.1.2.2 Sizing influence                                      |     |

| 5.1.2.3 Exploring decoupling cells with transistor reordering | 124 |

| 5.1.2.4 Soft error susceptibility                             | 126 |

| 5.1.3. Schmitt Trigger                                        | 128 |

| 5.1.3.1 Impact of different levels of WF fluctuations         | 130 |

| 5.1.3.2 Sizing influence                                      |     |

| 5.1.3.3 Soft error susceptibility                             | 131 |

| 5.1.4. Sleep Transistors                                      | 132 |

| 5.1.4.1 Impact of different levels of WF fluctuations         |     |

| 5.1.4.2 Sizing influence                                      |     |

| 5.1.4.3 Soft error susceptibility                             | 136 |

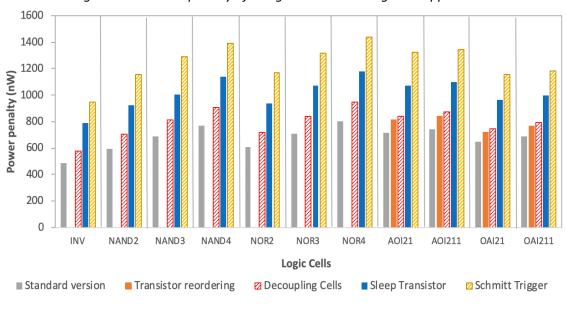

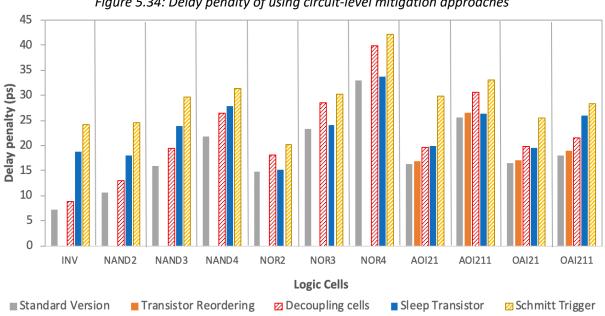

| 5.2 Technique Drawbacks                                       |     |

| 5.2.1 Area                                                    | 137 |

| 5.2.2 Power Consumption                                       | 138 |

| 5.2.3 Performance                                             | 141 |

| 5.3 Overall Comparison                                        | 143 |

| Chapter 6: Conclusions                                        | 148 |

| 6.1 Future Works                                              |     |

| References                                                    |     |

# **Chapter 1: Introduction**

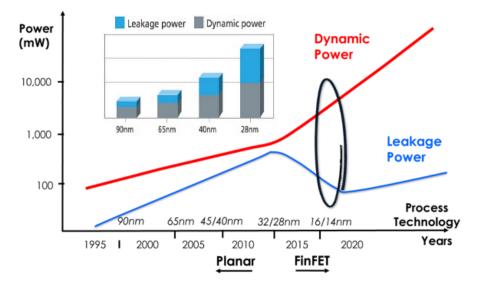

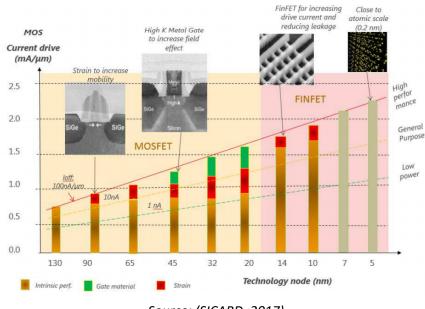

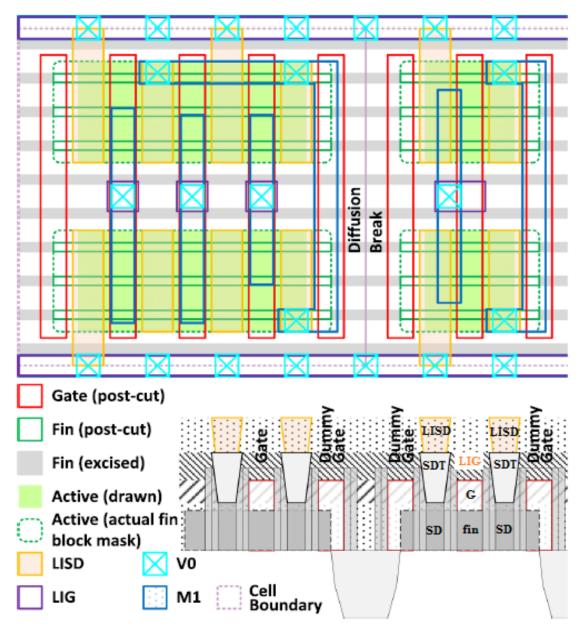

Novel materials and new device architectures had to be implemented in the integrated circuits to ensure the technology scaling sub-22nm (PRADHAN; SAHU; RANJAN, 2016). The 3D structure and the lightly doped channel of FinFET devices imply in a significant reduction of leakage currents, superior immunity to the short channel effects (SCE), the increase of carrier mobility and a decrease of random dopant fluctuations (RDF) (KING, 2005) (AGOSTINELLI et al., 2010). All these characteristics helped to enhance the electrostatic control of the channel, one of the main challenges faced during the planar scaling. In this way, the adoption of FinFET devices brought several benefits for the semiconductor industry, maintaining the pace of less power consumption, better performance, and higher density.

On the other hand, the small geometric patterns imposed by the advanced technology nodes raise essential topics related to the reliability of electronic systems. At nanometer regime, there are more potential sources of variability (COLLINS, 2014), the lower supply voltages increase the sensitivity to the external noise as well as the higher density allows that a single energetic particle affects multiple adjacent nodes (ENDO et al., 2009) (BHUVA et al., 2015). These factors can compromise entire blocks of logic cells because they can modify the transistor structure and/or alter the electrical properties, decreasing the integrated circuits robustness.

The process variability represents a random deviation from the typical design specifications that stimulates the circuit degradation, abnormal power consumption, and performance divergence (TASSIS et al., 2014). FinFET technologies are more prone to the process variations due to the wavelength adopted in the lithography step and the use of high-k dielectrics to improve the gate control on the channel region (DESHMUKH et al., 2015). In the first case, as the wavelength has not kept pace with the technology scaling, the transfer of small geometric standards to the substrate surface results in a deviation in the device structure after the manufacturing process. On the other hand, the use of metal as gate material modifies the

orientation of the grains, generating different work-functions (WF) aligned randomly that implies in higher work-function fluctuations (DADGOUR et al., 2010).

The soft error (SE) arises from the interaction of energetic particles with the silicon, coming from space and terrestrial radiations. In general, nanometer technologies decrease the minimum charge required to induce a single event transient (SET) pulse. This happens due to reduced nodal capacitances, low supply voltages, and also due to the higher frequency operations, which increases the probability of a memory element latching a SET generated in the combinational logic (BAUMANN, 2005). However, the FinFET disruptive nature is favorable to reduce the SE susceptibility. The connection between the transistor channel and the substrate occurs through a narrow region surrounded by isolation oxides, decreasing the volume of silicon exposed to the charge collection process. This modifies the sensitive areas, and consequently, it limits the increase of soft errors in the FinFET technologies (SEIFERT et al., 2015).

Although the FinFET devices present attractive properties to control the radiation-induced soft errors, other reliability challenges, such as the process variability, can modify the linear energy transfer (LET) threshold to induce a soft error. In this way, process variability mitigation and radiation hardness became two relevant reliability requirements as chip manufacturing advances more in-depth into the nanometer regime.

#### 1.1. Motivation

Integrated circuits with process variations can fail to meet some performance or power consumption criteria, leading to the parametric yield loss and demanding several redesign steps. Radiation-induced soft errors can provoke temporary data loss inducing to critical failures on system behavior even at the ground level. Depending on the target application, soft errors also can result in human life losses. These consequences emphasize the importance of creating new design guidelines able to deal with the challenges imposed by sub-22nm technologies.

The roadmap of most renowned semiconductor industries still points out the use of FinFET devices for the next generation of nanotechnologies. Additionally, a predictive 7-nm FinFET

process design kit (PDK) became available for the academic use allowing in-depth research at the layout level (CLARK et al., 2016). From a design standpoint, these challenges require a detailed and accurate evaluation considering several tests scenarios and verifying all the unwanted effects caused on FinFET circuits. Furthermore, the exploration of mitigation approaches and the development of electronic design automation (EDA) tools are essential since the early steps of design to obtain more reliable circuits.

Several techniques can be applied in different abstraction levels for enhancing the reliability of circuits. On the literature, some works investigated the impact of process variability and the radiation effects on FinFET technologies, mainly at the device and electrical levels, but much less understand has been gained at the layout level. Moreover, only a few works proposed solutions to attenuate the effects caused by them. The most effective approaches in the literature for mitigating the process variations and transient faults are commonly related to the use of a different structure and/or material during the fabrication process, or hardware replication, respectively. However, manufacturing changes have an expensive cost with higher complexity involved, besides the hardware redundancy introduces large overheads. Circuit-level approaches that modify the circuit design can be interesting alternatives to achieve more robust solutions, with smaller cost of implementation and fewer penalties.

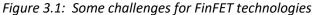

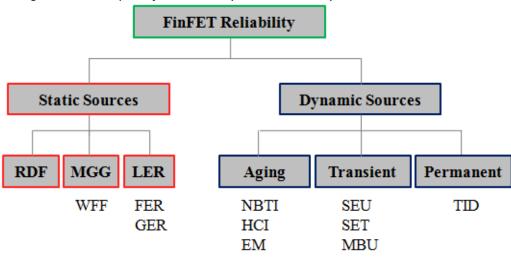

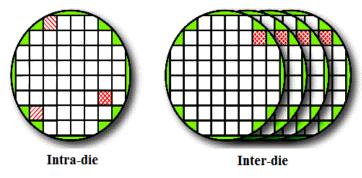

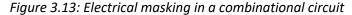

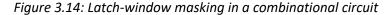

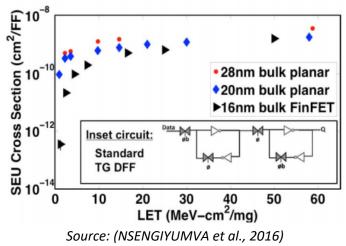

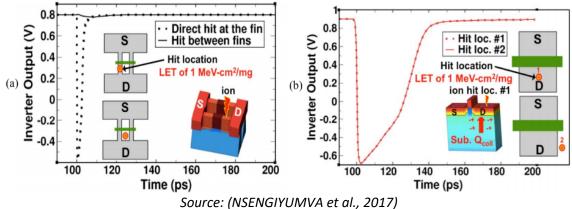

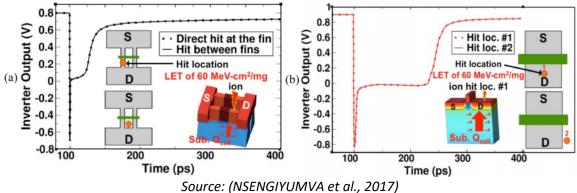

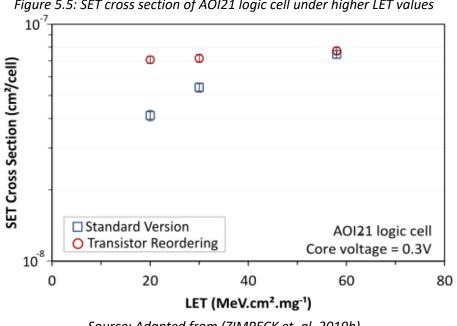

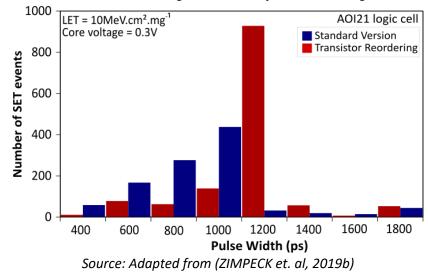

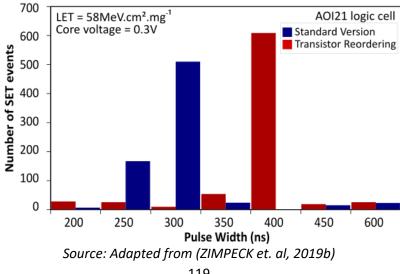

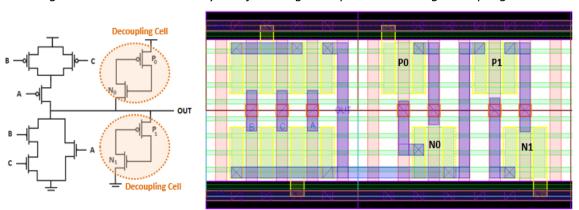

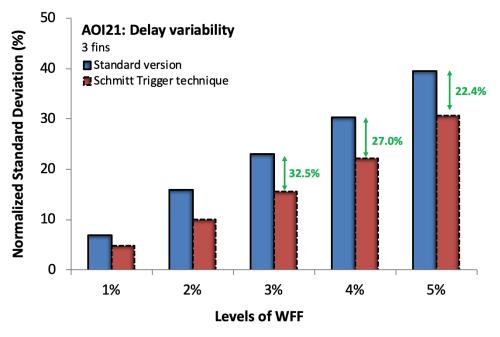

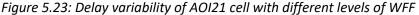

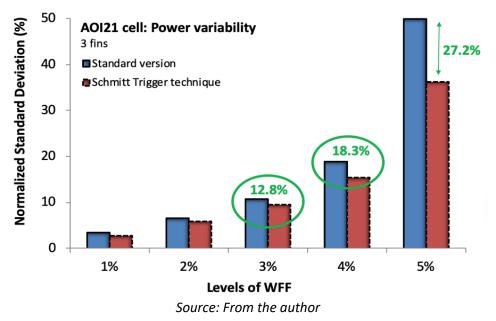

#### **1.2.** Objectives