## Model-Driven Physical-Design for Future Nanoscale Architectures

Ciprian Teodorov

#### ▶ To cite this version:

Ciprian Teodorov. Model-Driven Physical-Design for Future Nanoscale Architectures. Emerging Technologies [cs.ET]. Université de Bretagne Occidentale (UBO), Brest, 2011. English. NNT: . tel-02515931

## HAL Id: tel-02515931 https://hal.science/tel-02515931

Submitted on 23 Mar 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE / UNIVERSITÉ DE BRETAGNE OCCIDENTALE

sous le sceau de l'Université européenne de Bretagne

pour obtenir le titre de

DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE OCCIDENTALE

Mention : Informatique

École Doctorale SICMA

présentée par

## Ciprian TEODOROV

Préparée à Lab-STICC UMR 3128

## Model-Driven Physical-Design for Future Nanoscale Architectures

#### Thèse soutenue le 28 novembre 2011

devant le jury composé de :

#### Jacques-Olivier KLEIN

Professeur, Université Paris Sud 11 / examinateur (président du jury)

#### **Dominique LAVENIER**

Directeur de Recherches, IRISA Rennes / rapporteur

#### Ian O'CONNOR

Professeur, Ecole Centrale de Lyon / rapporteur

#### **Bernard POTTIER**

Professeur, Université de Bretagne Occidentale / directeur de thèse

#### Loïc LAGADEC

Habilite a diriger des recherches, Université de Bretagne Occidentale / co-directeur de thèse

#### **Catherine DEZAN**

Maitre de Conférences, Université de Bretagne Occidentale / co-directeur de thèse

#### CIPRIAN TEODOROV

## $\begin{array}{c} \texttt{MODEL-DRIVEN PHYSICAL-DESIGN FOR FUTURE NANOSCALE} \\ & \texttt{ARCHITECTURES} \end{array}$

## MODEL-DRIVEN PHYSICAL-DESIGN FOR FUTURE NANOSCALE ARCHITECTURES

#### CIPRIAN TEODOROV

Integrated Circuit Design in Nanoscale Era2011

${\bf Ciprian\ Teodorov:}\ {\it Model-Driven\ Physical-Design\ for\ Future\ Nanoscale\ Architectures,\ Integrated}$ Circuit Design in Nanoscale Era, © 2011 SUPERVISORS: Bernard Pottier Loïc Lagadec Catherine Dezan

$\label{eq:Discovery} Discovery \mbox{ consists in seeing what everyone else has seen} \\ \mbox{ and thinking what no one else has thought.}$

— Albert Szent-Gyorgyi

Dedicated to the memory of Dan Ioan Marcean 1985-2004

#### Abstract

In the context where the traditional CMOS technology approaches its limits, some nanowire-based fabric proposals emerged, which all exhibit some common key characteristics. Among these, their bottom-up fabrication process leads to a regularity of assembly, which means the end of custom-made computational fabrics in favor of regular structures. Hence, research activities in this area, focus on structures conceptually similar to today's reconfigurable PLA and/or FPGA architectures[165, 160]. A number of different fabrics and architectures are currently under investigation, e. g.CMOL[165], FPNI[160], NASIC[115]. These proof-of-concept architectures take into account some fabrication constraints and support fault-tolerance techniques. What is still missing is the ability to capitalize on these experiments while offering a one-stop shopping point for further research, especially at the physical-design level of the circuit design tool-flow. Sharing metrics, tools, and exploration capabilities is the next challenge to the nano-computing community.

We address this problem by proposing a model-driven physical-design toolkit based on the factorization of common domain-specific concepts and the reification of the tool-flow. We used this tool-flow to drive the design-space exploration in the context of a novel nanoscale architecture, and we showed that such an approach assures design convergence based on frequent quantitative evaluations, moreover it enables incremental evolution of the architecture and the automation flow.

## Résumé

Actuellement, comme la technologie CMOS arrive à ses limites, plusieurs alternatives architecturales nanométriques sont étudiées. Ces architectures partagent des caractéristiques communes, comme par exemple la régularité d'assemblage, qui contraint le placement de dispositifs physiques à des motifs réguliers. Par conséquence, les activités de recherche dans ce domaine sont focalisées autour des structures régulières similaires, d'un point de vue conceptuel, aux architectures réconfigurables de type PLA et FPGA[165, 160]. Parmi ces différents travaux, ont peut citer CMOL[165], FPNI[160], NASIC[115]. Ces prototypes architecturaux sont conçus pour répondre à des contraintes de fabrication et incluent des politiques de tolérance aux défauts. Par contre, il manque la possibilité d'exploiter ces expériences et d'offrir une solution qui, en capitalisant les résultats obtenus, puisse offrir une infrastructure unique pour les futurs recherches dans ce domaine. Ceci est vrai surtout au niveau du flot de conception physique ciblant l'automatisation du processus de création de circuit. Le partage de métriques, outils et supports d'exploration est le futur défi de la communauté nano-électronique.

On répond à ce problème en proposant un flot de conception physique, reposant sur une méthodologie de développement dirigé par les modèles, qui factorise les concepts métiers et réifie les éléments du flot de conception. Nous avons utilisé ce flot pour explorer l'espace de conception d'une nouvelle architecture nano-métrique et on a montré qu'une telle démarche permet la convergence du processus de conception à l'aide de fréquentes évaluations quantitatives. De plus, cette méthodologie permet l'évolution incrémentielle de l'architecture et du flot de conception.

We have seen that computer programming is an art, because it applies accumulated knowledge to the world, because it requires skill and ingenuity, and especially because it produces objects of beauty.

—Donald E. Knuth

## Acknowledgments

First of all, I want to express my gratitude to the members of my dissertation committee, starting with the foreman of the jury, prof. Jacques-Olivier Klein, along with prof. Dominique Lavenier, prof. Ian O'Connor, prof. Bernard Pottier, prof. Loic Lagadec, and prof. Catherine Dezan which all have contributed significantly to this work through the preparation, the revision and the evaluation of this manuscript.

I want to thank prof. Lavenier, and prof. O'Connor for accepting the role of external reviewers and for blessing my work with their attention and appreciation during the review and evaluation process.

I am deeply grateful to my supervisors prof. Bernard Pottier, prof. Loic Lagadec, and prof. Catherine Dezan. Bernard courageously assumed the role of principal advisor and never hesitated to steer my energy into the right direction through his encouragements, advices and fatherly mentoring. It has been an honor to work with Catherine who dedicated a lot of her time to my work, and with whom we inquisitively evaluated numerous ideas, and research directions. Her patience and understanding were limitless during the tough times in the PhD pursuit, and her joy and enthusiasm were contagious. I am profoundly indebted to Loic that has not only been a supervisor but also a friend, and a direct supporter of many of my strange ideas.

Part of this work was supported by European University of Britanny (UEB) through a student exchange fund, which enabled me to work 5 months at the University of Massachusetts in Amherst under the supervision of prof. Csaba Andras Moritz. I want to thank the UEB committee for giving me the opportunity to work directly with one of the best nano-computing research teams in the world. Moreover, I want to thank prof. Moritz and the members of Nanoscale Fabrics Lab for integrating me into their team and supporting my research. Besides prof. Moritz, I want to great here Pritish Narayanan, Rahman Mostafizur, Pavan Panchapakeshan, and Prasad Shabadhi for making me feel at home in Amherst, and for the many hours that we have spent discussing everything from research to lifestyle.

I was very fortunate to work with a group of very dynamic people, members of the Lab-STICC's MOCS team. I want to thank all the former and present members of this team who have helped through collaborations and invaluable discussions, especially Damien Picard, Samar Yazdani, Jalil Boukhoubza, Erwan Fabiani, Ahcene Bounceur, and Hritam Dutta.

Besides everybody else, my close friends starting with Sebastien Tripodi, Jean Paul Soleil, and Amara Touil, played one of the most important roles during these last three years by keeping me a socially engaged human being. They were all there whenever I would need them, for whatever reason, and without asking too many questions.

My heart goes also to my family, back in Romania, especially to my parents and my grandma, for their support and patience during the last 28 years of the bull ride that brought me here.

Lastly, but not the least, I want to thank Anamaria, my sweetheart, for her understanding and tolerance during my sleepless nights, for her encouragements and support during the harsh days, and for her heart and love throughout all the way.

Thank you all, thanks for being with me!

## Contents

| Al  | bstract                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Ré  | ésumé                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\mathbf{v}$                                                         |

| Ac  | cknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                          | vii                                                                  |

| Co  | ontents                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                                   |

| Li  | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                           | xi                                                                   |

| Lis | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                            | xiii                                                                 |

| 1   | Introduction  1.1 Context                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>17<br>17<br>19<br>20                                           |

| 2   | The Future of Integrated Circuits  2.1 Introduction  2.2 Integrated Circuits - Overview  2.3 CMOS Technology and Its Limits  2.4 Emerging technologies  2.4.1 Taxonomy  2.4.2 Requirements for Competitiveness  2.4.3 Some Fabric Propositions  2.5 From crossbars to digital circuits  2.5.1 Fabrication process  2.5.2 Working Circuits on Unreliable Technology  2.5.3 Logic Implementation  2.5.4 Nano/CMOS Interface  2.5.5 Crossbar-based Fabrics | 21<br>21<br>22<br>26<br>27<br>27<br>29<br>32<br>32<br>33<br>35<br>35 |

| 3   | Bridging the Gap Between Applications and Technology  3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                  | 37 39 40 40 41 47 48 49 53                                           |

X CONTENTS

| Bi | iblio             | raphy 11.                                                           |

|----|-------------------|---------------------------------------------------------------------|

| 6  | Con<br>6.1<br>6.2 | clusion & Perspectives10'Summary of Contributions10'Perspectives10' |

| _  |                   |                                                                     |

|    | 5.6               | Summary                                                             |

|    | 5.5               | Pipelined Routing at Nanoscale                                      |

|    |                   | 5.4.1 Routing Segments Impact                                       |

|    | 5.4               | Results         9           5.4.1 Routing Segments Impact         9 |

|    | 5.4               | 5.3.2 CAD Flow Tuning - Routing algorithm                           |

|    |                   | 5.3.1 FPGA CAD Flow for Nano-scale Architecture                     |

|    | 5.3               | Physical-Design with MoNaDe and Madeo                               |

|    | <u> </u>          | 5.2.5 Evaluation Metrics                                            |

|    |                   | 5.2.4 Parameters                                                    |

|    |                   | 5.2.3 Sequencing schemes                                            |

|    |                   | 5.2.2 Lithographic Cluster I/O                                      |

|    |                   | 5.2.1 Logic and Interconnect                                        |

|    | 5.2               | Regular 2D NASIC-based Architecture Template                        |

|    | 5.1               | Introduction                                                        |

| 5  |                   | oscale Architecture Template and Associated Tools  Litra dusting    |

| _  | 76 T              |                                                                     |

|    | 4.6               | Summary                                                             |

|    |                   | 4.5.3 Refactoring Domain-Models                                     |

|    |                   | 4.5.2 Extensions for Nanoscale Physical Design                      |

|    |                   | 4.5.1 Improving on Legacy – First steps                             |

|    | 4.5               | From Legacy to MDE Toolkit                                          |

|    | 4.4               | Tool-flow Modeling                                                  |

|    | 4.3               | Transformation Metaphor for Tool Design                             |

|    |                   | 4.2.5 Application Model                                             |

|    |                   | 4.2.4 Circuit Modeling                                              |

|    |                   | 4.2.3 Crossbar-level modeling                                       |

|    |                   | 4.2.2 Transversal concerns                                          |

|    | -                 | 4.2.1 Fame-based Abstract Model                                     |

|    | 4.2               | Domain Modeling                                                     |

|    |                   | 4.1.3 Enabling Technologies                                         |

|    |                   | 4.1.2 Model-driven HLS                                              |

|    | 7.1               | 4.1.1 Model-driven development                                      |

| 4  | 4.1               | Introduction                                                        |

| 4  | Ma                | del-Driven Physical Design Flow                                     |

|    | 3.6               | Summary                                                             |

|    |                   | 3.5.3 Domain Specific Requirements                                  |

|    |                   | 3.5.2 Application Specific Requirements                             |

|    |                   | 3.5.1 Transversal Requirements                                      |

|    | 3.5               | Requirements for an Emerging-Fabric CAD Toolkit                     |

|    |                   | 3.4.4 Comparing Nanoscale Architectures                             |

|    |                   | 3.4.3 DSE at nanoscale                                              |

|    |                   | 3.4.2 Some Tools for AAA                                            |

|    |                   | 3.4.1 Algorithm-Architecture Adequacy                               |

|    | 3.4               | Taming the Complexity - Design Space Exploration                    |

|    |                   | 3.3.5 Routing                                                       |

## List of Figures

| 2.1  | A taxonomy of digital IC design styles                                   | 23 |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Four different IC design styles                                          | 24 |

| 2.3  | MOSFET Structure                                                         | 26 |

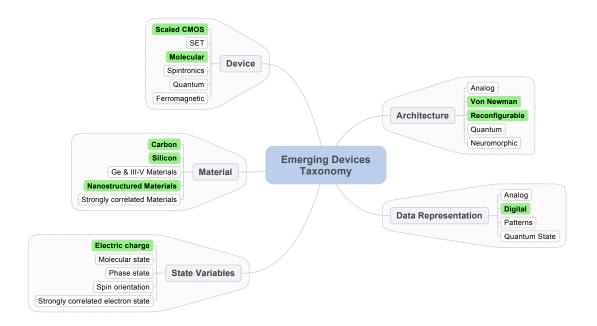

| 2.4  | Emerging Circuits Taxonomy                                               | 28 |

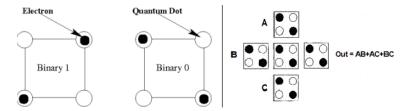

| 2.5  | Left, QCA cell polarizations; Right, QCA majority gate                   | 30 |

| 2.6  | Example of a Nanocell Tile                                               | 31 |

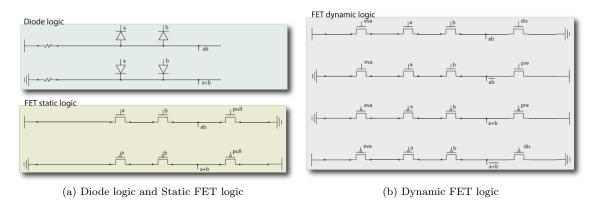

| 2.7  | Different logic styles                                                   | 35 |

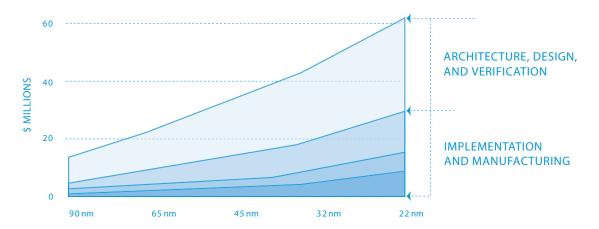

| 3.1  | SoC development costs in terms of design and manufacturing               | 40 |

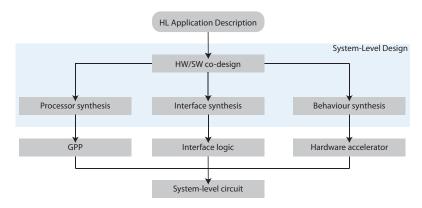

| 3.2  | Typical system-level design flow                                         | 41 |

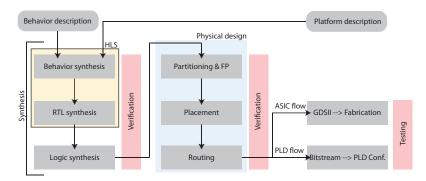

| 3.3  | Classical EDA design flow                                                | 42 |

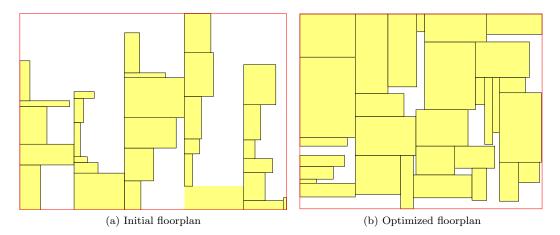

| 3.4  | Floorplanning using TCG-S representation[102]                            | 44 |

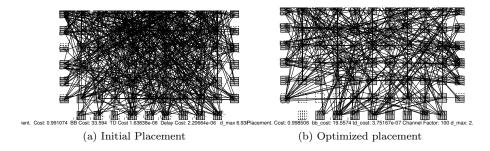

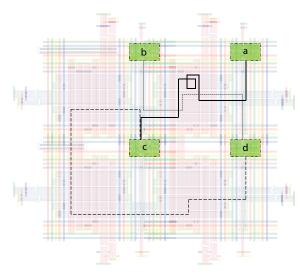

| 3.5  | A FPGA placement instance optimized using VPR placer                     | 44 |

| 3.6  | Abstract structural model of a tile composed of 6 crossbars              | 50 |

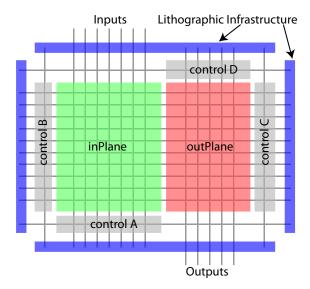

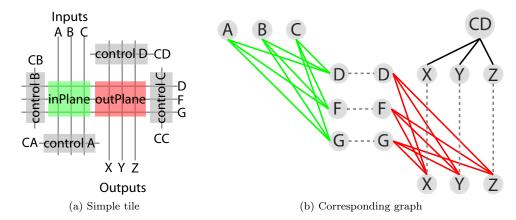

| 3.7  | Abstract tile model and corresponding graph                              | 51 |

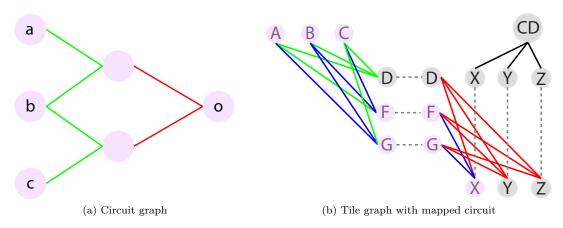

| 3.8  | Logic mapping on a defect-free tile graph                                | 51 |

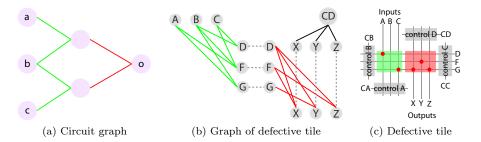

| 3.9  | Logic mapping on a defective tile graph                                  | 52 |

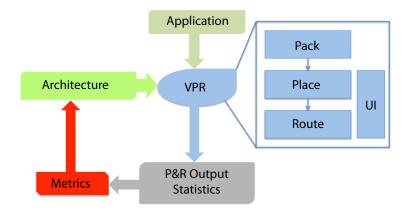

| 3.10 | VPR tool-flow                                                            | 56 |

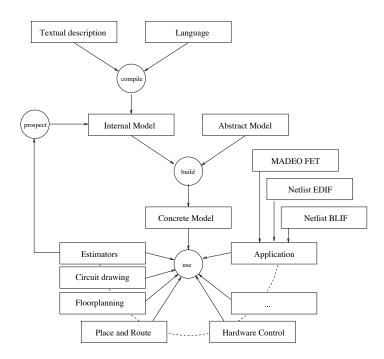

| 3.11 | Madeo toolkit overview                                                   | 57 |

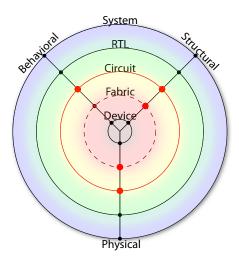

| 4.1  | Adaptation of the Gajski-Kuhn Y Chart for nano-electronics               | 68 |

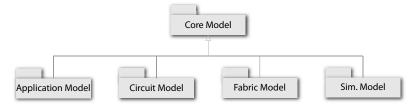

| 4.2  | Global view of the domain models and their relation with the core model  | 69 |

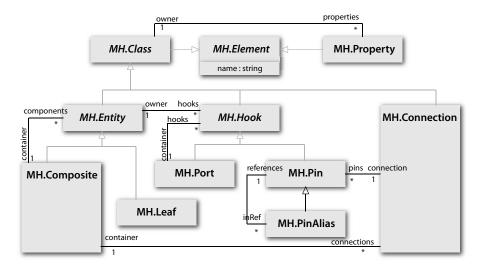

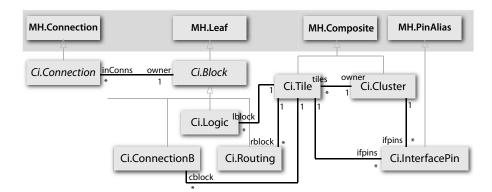

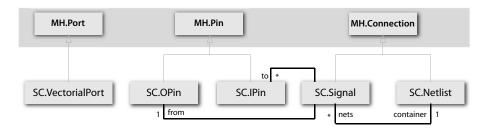

| 4.3  | A view of the core structure of the proposed meta-model                  | 70 |

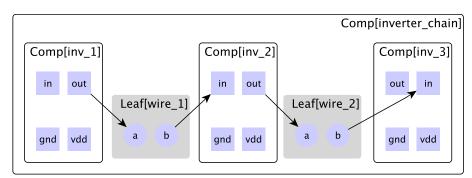

| 4.4  | Visualization of an inverter chain modeled at the fabric-level           | 70 |

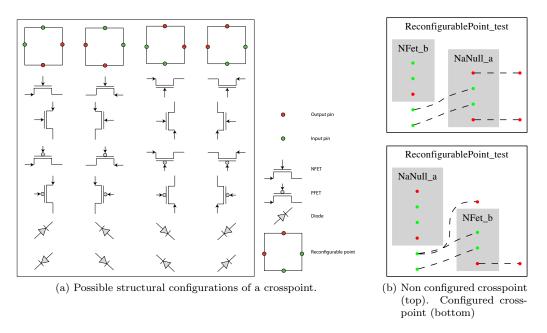

| 4.5  | Crossbar-level reconfigurable point. Possible configurations and example | 72 |

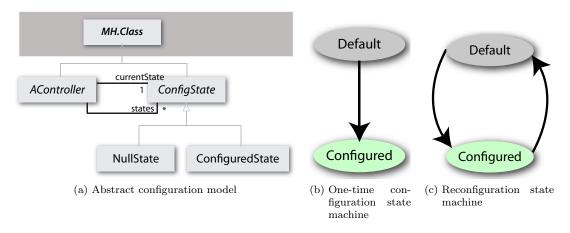

| 4.6  | Configuration model and two different configuration policies             | 72 |

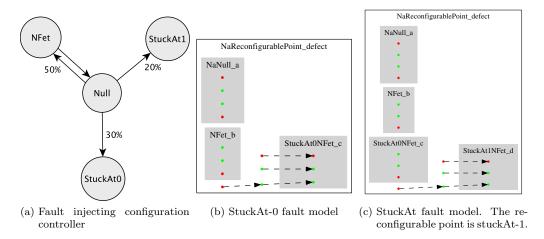

| 4.7  | Fault-configuration and examples of defective reconfigurable point       | 73 |

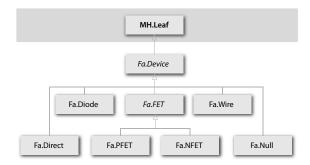

| 4.8  | Primitives for crossbar-level modeling                                   | 74 |

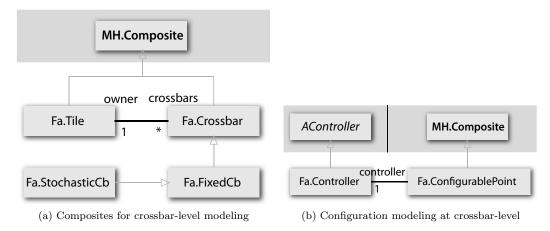

| 4.9  | Crossbar-level composites and configuration models                       | 75 |

| 4.10 | Dynamic style NASIC tile modeled using CVA                               | 76 |

|      | NanoPLA tile modeled by CVA                                              | 77 |

| 4.12 | Circuit model extension of the core meta-model                           | 77 |

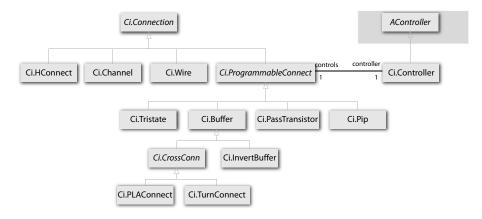

|      | Connection hierarchy                                                     | 78 |

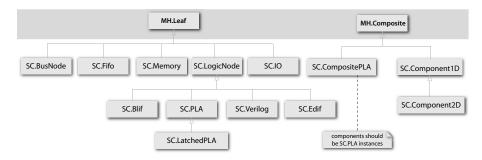

|      | Extension of the core meta-model for application modeling (entities)     | 79 |

|      | Extension of the core meta-model for application modeling (connection)   | 79 |

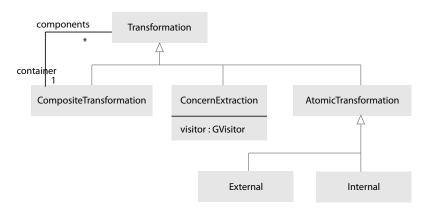

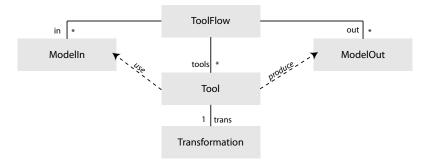

|      | Transformation metaphor model                                            | 80 |

|      | DAG representation of the composite routing transformation               | 82 |

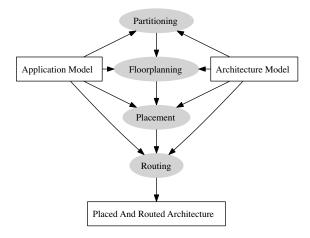

|      | Standard physical design flow                                            | 83 |

|      | The abstract toolflow meta-model                                         | 83 |

|      | Madeo viewer on an nanoscale tile instance                               | 85 |

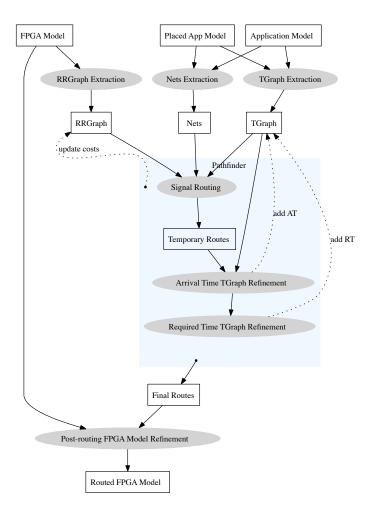

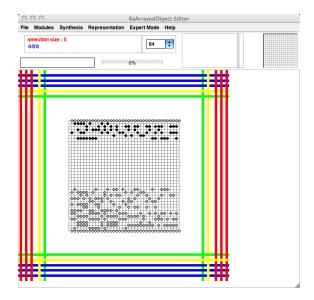

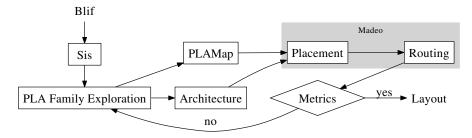

|      | The R2DNasic CAD flow                                                    | 85 |

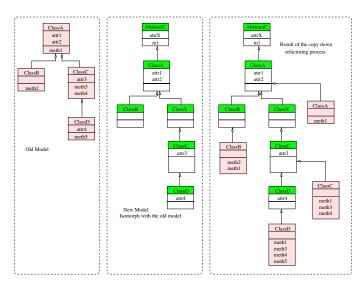

|      | Isomorph Model Refactoring                                               | 86 |

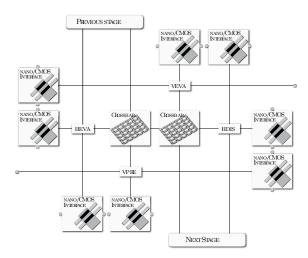

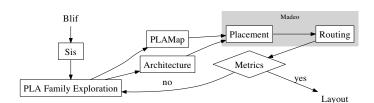

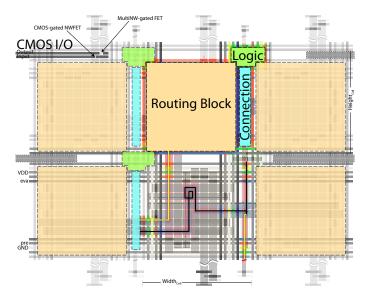

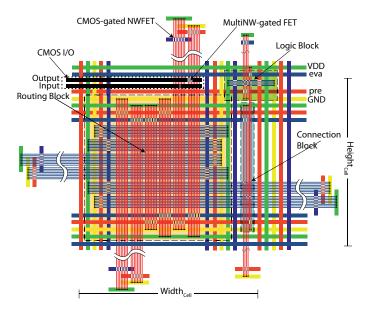

| 5.1  | R2D NASIC cluster                                                        | 91 |

xii LIST OF FIGURES

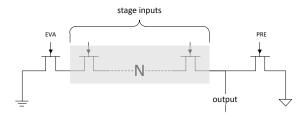

| 5.2  | Dynamic NAND stage                                                                      | 1 |

|------|-----------------------------------------------------------------------------------------|---|

| 5.3  | The layout of a R2D NASIC Cell                                                          | 2 |

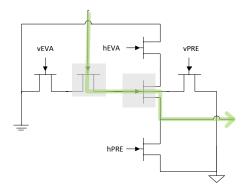

| 5.4  | Two stage dynamic routing                                                               | 2 |

| 5.5  | R2D NASIC signal routing example                                                        | 3 |

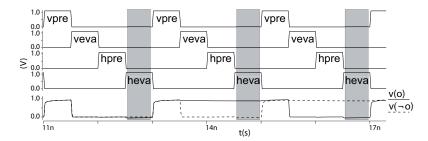

| 5.6  | Pipelined R2D NASIC circuit HSpice simulation                                           | 4 |

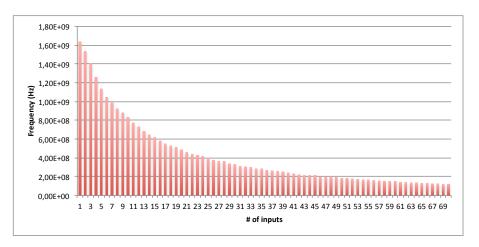

| 5.7  | NAND stage frequency wrt. $\#$ of inputs                                                | 6 |

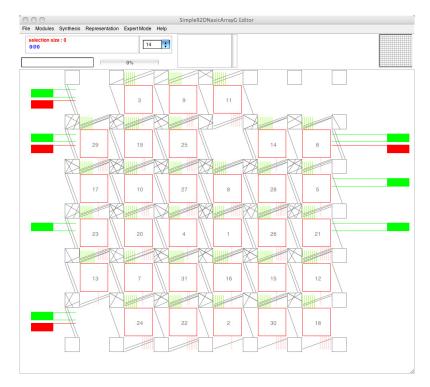

| 5.8  | R2D NASIC tiles using MADEO visualization                                               | 7 |

| 5.9  | Design automation flow for R2D NASIC                                                    | 7 |

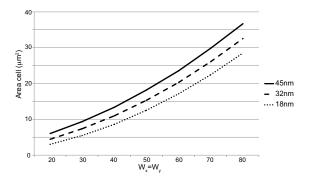

| 5.10 | R2D Nasic Cell Area for 3 technology nodes as a function of routing segments $9$        | 9 |

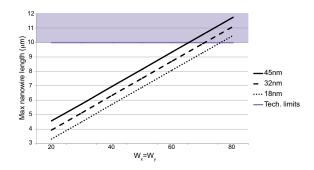

| 5.11 | Maximum nanowire length for $3$ technology nodes as a function of routing segments $10$ | 0 |

| 5.12 | PLA exploration                                                                         | 0 |

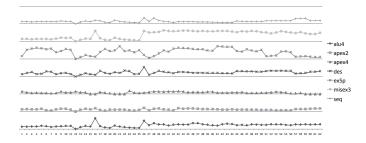

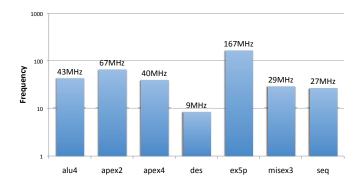

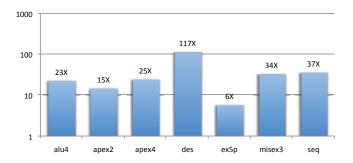

|      | Resulting frequency for the place and routed benchmarks                                 | 1 |

| 5.14 | Frequency improvement over the baseline evaluation                                      | 1 |

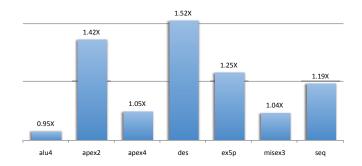

|      | The impact of pipeline equalisation on the circuit latency                              | 2 |

| 5.16 | Net performance gain of the pipelined version over baseline                             | 2 |

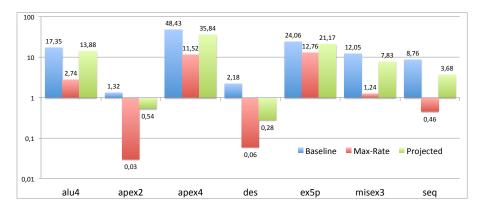

|      | Normalized density advantage of R2D NASIC over $45 \text{nm}$ standard cell CMOS $10$   | 3 |

|      | The performance per unit area advantage of the max-rate pipelined designs 10            |   |

| 5.19 | Deviation of the computed layout area from the projected bound                          | 4 |

| 5.20 | Standard deviation of RB usage for the benchmark circuits                               | 4 |

## List of Tables

| 2.1 | Crossbar-based fabrics and associated fault-models | 35  |

|-----|----------------------------------------------------|-----|

| 3.1 | CAD tools used for different fabrics               | 47  |

| 4.1 | Fame vs. Platypus vs. EMF – comparison             | 66  |

| 5.1 | Mapped MCNC benchmark netlists                     | 100 |

xiv LIST OF TABLES

# Introduction

#### 1.1 Context

This thesis explores the tight connection between integrated circuits and their associated design tools in the context where the traditional CMOS technology approaches its limits, and a number of alternatives have been investigated. Amongst these alternatives, the designs using silicon nanowire crossbars are very promising, mainly due to their high integration densities and their bottom-up fabrication process - which can drastically reduce the fabrication costs. A number of different fabrics and architectures are currently under investigation, for example NanoPLA[31], CMOL[165], FPNI<sup>1</sup>[160], NASIC<sup>2</sup>[115]. They are based on a variety of devices such as field effect transistors (FET)[121], spin-based devices[152], diodes, and molecular switches[161]. All these fabrics include support in CMOS: some, like FPNI, would move the entire logic into CMOS, others, like NASIC, would only provide the control circuitry in CMOS. The rationale for this varies but includes targeted application areas as well as manufacturability issues [122]. However, there is a gap between these technological developments and the tools used to design and exploit them. This gap comes mainly from the lack of flexible and evolutive electronic computer-aided design tools, which limits the reuse of algorithms and sound CAD solutions, forcing the fabric and architecture designers to create proprietary tool-flows. This hinders shared improvement over fabric design, and slows the evolution of the field, mainly due to the poor support for multi-fabric design space exploration. In this work, we rethink the circuit physical design tool-flow. Borrowing ideas from computer science research and software engineering, we propose a flexible and re-targetable tool-flow. This tool-flow improves on the state of the art and creates the necessary environment for future nanoscale CAD research and development.

#### 1.2 Research questions

Over the last half century, computer architects have followed the trend imposed by Moore's law, addressing the need for ever-increasing performances. CMOS technology has scaled along with Moore's law for many years, allowing the architects to build performant systems. Unfortunately, CMOS technology suffers from a problem that deepens everyday. As the technology progresses, CMOS devices become smaller and smaller, nowadays reaching deep sub-micron range(less than 50nm); at this order of magnitude, sooner or later, CMOS devices will cease to scale because

<sup>&</sup>lt;sup>1</sup>Field Programmable Nanowire Interconnect

<sup>&</sup>lt;sup>2</sup>Nanoscale Application Specific Integrated Circuits

of their physical properties. But this is not the only problem: as the devices shrink, the cost of fabrication plants increases exponentially, while the ability to handle fabrication process variations decreases. To address these problems, during the last years research groups and industry focused on finding the technology that will permit the evolution of integrated circuits past CMOS limits. A number of alternative technologies are currently under investigation, amongst which the designs based on silicon nanowire (SiNW) crossbar are very promising.

During the last years tremendous progress on the physical, technological, manufacturing, and fabric design greatly improved our understanding on the advantages and the limitations of the SiNW crossbar technology. However, little or no significance was given to design and exploitation tools which in fact are the limiting factors hindering shared improvement over multiple fabrics. The creation of proprietary automation solutions for each new fabric design is very costly in terms of development effort, the resulting tools are not reusable even for closely related projects, and such targeted effort closes the tool exploration axis of the whole design-space exploration problem by directly providing *supposedly* optimized solutions.

In the electronic CAD community the design-space exploration (DSE) problem is typically studied from the perspective of the adequacy application/architecture. In this context, there has been a lot of research to automatically or semi-automatically tune a specific application to match the underlying architectural constraints. The tool optimization is viewed as an independent problem, and many improvements in terms of algorithm complexity, scalability and flexibility were achieved for each step of the circuit design automation tool-flow. Moreover, since the technological and architectural framework was stable, the small number of new challenges addressed at each new CMOS technology node did not disrupt the design-automation flow. However, in the current technological context, with the traditional technology approaching its fundamental limits and the apparition of a large number of emerging technologies competing for adoption, we argue that there is a stringent need for adding a third dimension to the design-space exploration focused on tool design and optimization. This new exploration axis adds to new perspectives to the DSE problem, namely the adequacy tool-flow/architecture and the adequacy tool-flow/application. In the context of this thesis the tool-flow/application adequacy is treated as a secondary issue, while the focus is on the tool-flow/architecture adequacy. The importance of this new perspective comes mainly from the need of tool reuse (to reduce the development costs) and from the need of unbiased evaluation of different technological frameworks at the architectural level (to objectively compare different computing supports).

Amongst all emerging architectures competing for adoption as a CMOS replacement, the fabricdesigns based on silicon nanowire crossbar imposed themselves as a viable solution, principally due to their bottom-up fabrication process which offers the opportunity of achieving unprecedented integration density. However, besides their advantages, these designs come with new challenges and constraints. Among these, their bottom-up fabrication process leads to a regularity of assembly, which means the end of custom-made computational fabrics in favor of regular structures designed with respect to the application needs. Hence research activities in this area mainly focus on structures conceptually similar to today's reconfigurable PLA<sup>3</sup> and/or FPGA<sup>4</sup> architectures[165, 160]. Based on this observation, it has been assumed that the tools traditionally used in the context of reconfigurable architecture design can be easily retargeted for these new computing supports. During the last ten years, the reconfigurable architecture tool-flow improved and matured relying mainly on a common tool infrastructure implementing generic algorithms and heuristics tuned by externally defined optimization metrics. However, in the context of crossbar-based nanoscale architectures the circuit design optimization tool-flow is still developed in an ad-hoc, architecturespecific manner. This aspect is even more questionable since most of these architecture-specific tools rely extensively on generic FPGA frameworks with design specific proprietary extensions, such as VPR[9] in the context of CMOL[165] and NanoPLA[31], and Madeo[90] in the context of NASIC[115, 96]. In this context, the question is to what extent tools from reconfigurable field can be reused for automating circuit design on nanoscale crossbar fabrics, what are the limitations of

<sup>&</sup>lt;sup>3</sup>Programmable Logic Array

<sup>&</sup>lt;sup>4</sup>Field-Programmable Gate Array

such tools, and most importantly, can we provide a generic multi-fabric infrastructure for nanoscale circuit design, similar with today's generic FPGA toolkits?

In the context of nanoscale electronics, one of the principal challenges to overcome is the highrate of defects, which needs innovative defect-tolerance strategies to enable the creation of reliable computing fabrics. A large number of research work was dedicated to this topic, and different solutions were proposed, ranging from self-healing fabric architectures[115] to defect-tolerance through reconfiguration[165]. However, little or no attention was given to the integration of these defect-tolerance techniques into the circuit automation tool-flow, nor to the infrastructure needed to seamlessly integrate defect-awareness into the design-flow.

In this thesis, we address some of the questions raised in this section from the tool-flow perspective at the physical-design level. The problems raised and the solutions provided are studied in the context crossbar-based nanoscale architecture, but most of the issues are more general, transcending this architectural approach, and the solutions can sometimes be reframed in the larger context of emerging architectures.

#### 1.3 Contribution of this thesis

The results presented in this thesis rely most notably on the exploration and the analysis of the interdependence between the crossbar-based nanoarchitectures and the physical design tools, with the purpose of providing answers that would help reduce the design and exploitation costs for new technologies. The principal contributions presented in this manuscript are:

- The introduction of a *common vocabulary* for nanoscale architecture modeling at different abstraction levels. This vocabulary is based on an abstract meta-model relying on a hierarchical port-graph structure. This meta-model is used for architecture and application modeling, for the specification of different simulation models, and can be extended to address defect and fault modeling and injection.

- The design of a model-driven physical synthesis tool-flow which decouples the architectural model from the physical synthesis tools. This flow enables the parallel evolution of the architectures and tools, improves the algorithm reutilization, eases the agile development of the design-flow, and creates the necessary conditions for incremental design space exploration. Moreover, the use of the Model-Driven Development in the context of the physical design opens the toolbox offering an unprecedented flexibility and support for the evolution of the tool-flow.

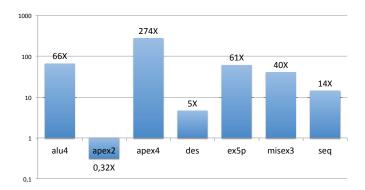

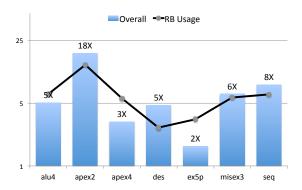

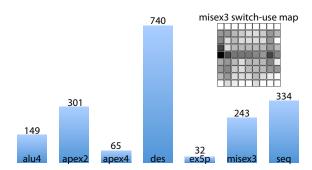

- The design of a new nanoscale architecture based on the NASIC fabric concepts along with its performance models and optimization policies. This architecture, named R2D NASIC, is compatible with the NASIC technological framework and fabrication process, and can easily be adapted according to the technological and application constraints. Through its regularity, this architecture enables arbitrary logic placement and routing. Moreover it offers the possibility of implementing max-rate pipeline designs with an average 35X higher-frequency than non-pipelined versions, paving the way to high-performance nanoscale circuits.

- The bootstrap of the design space exploration relying on tools used today in the context of reconfigurable architectures. An approach through which early baseline evaluations were performed on the R2D NASIC design. These evaluations were then used to guide the architectural and tool-flow design process.

- The creation of a *new routing algorithm* specific for R2D NASIC, for achieving max-rate pipeline designs. This algorithm balances the pipeline stages over the routing paths. Using this algorithms the performances were improved up to 77X, with 3X better performances per unit area compared to the non-optimized designs.

#### 1.4 Outline of the thesis

This section overviews the content presented in this thesis, briefly announcing the core content of each chapter.

#### Chapter 2 - Future of Integrated Circuits

The main intent of this chapter is to familiarize the reader with the main terms, concepts and challenges of the electronics industry while introducing the technological framework used in the subsequent parts of the thesis. The context is described with details which emphasize the limitations of the current technology and motivate the research for breakthrough solutions. A number of emerging technologies are briefly presented before the focus is drawn to crossbar-based design, the technological framework that represents the basis of the work presented in this thesis.

#### Chapter 3 - Bridging the Gap Between Applications and Technology

As the complexity of integrated circuits increases, their design puts more and more pressure on the automated tool-flow used. This chapter gives an overview of the main steps of circuit design automation in the context of current technology. It then presents the physical design of nanoscale circuits from the perspective of this traditional design flow, pointing out the challenges that need addressing in this new technological context.

#### Chapter 4 - Model-Driven Physical Design Flow

The model-driven software development methodology is used to implement the physical design step of the circuit design tool-flow. The targeted fabric design is described using an abstract model of a hierarchical port-graph. The tool-flow is reified and modeled using a specific object-oriented abstract model, which enables a high-degree of algorithm reuse and drives design-space exploration. Moreover, this tool-flow is backward-compatible and favors high-degree of flexibility and reuse.

#### Chapter 5 - Nanoscale Architecture Template and Associated Tools

A regular 2D nanoscale architecture template based on NASIC fabric building blocks is presented along with its evaluation metrics and optimization tools. Besides being compatible with NASIC technological and manufacturing guidelines, this architecture enables the creation of highly pipelined circuits while easing the delay estimation at the tool-flow level.

#### Chapter 6 - Conclusions & Perspectives

The main points evoked and developed in this thesis are overviewed. The principal contributions are summarized and discussed emphasizing the strengths of the presented CAD methodology. Moreover, some insights on future developments and main open research questions for the ECAD targeting nano-electronics are addressed in the perspectives section.

## 2

## The Future of Integrated Circuits

This chapter presents the technological context, which motivates the work presented in this manuscript. After briefly presenting the integrated circuits field and some of the terminology that will be reused in the following chapters, we explain the limits of the current CMOS technology and we present the state of the research on emerging technologies with a focus on the crossbar-based designs.

#### 2.1 Introduction

Since the invention of the first integrated circuit[136], in 1958, the electronics field had an unprecedented evolution getting from a few transistor integrated on a silica plate to billions in the current circuit designs. This evolution was possible mainly due to technological and fabrication breakthroughs that enabled the exponential size reduction of devices integrated on a chip. In 1965 Gordon Moore stated an empirical law which drove the industry for the last four decades. The Moore's law predicted that the number of transistors integrated in a chip will double every two years. This exponential increase in integration density enabled the reduction of the fabrication cost per chip, the design of higher frequency chips with lower power consumption per device, and the creation of smaller and smarter<sup>1</sup> end-products.

Today the feature size of the devices integrated in a chip reached the nano-metric scale. The cost of foundries continues to increase and the ability to handle fabrication process variations decreases. Moreover, at device level, the parasitic resistance and capacitance are starting to dominate the intrinsic resistance and capacitance of the devices, which imposes hard physical limits for performance improvements by reducing the feature size. As a result the experts are announcing the end of the CMOS technology evolution, or at least the end of the Moore's law as we know it - based on the integration density as a metric for evolution. In 2009 ITRS[73] reports the possible replacement of this "geometric scaling" by the "equivalent scaling". Equivalent scaling will continue evolution based on innovative devices (e.g. memristor[167]), revolutionary computing models (e.g. DNA computing[146]), creative architectures, and software evolutions.

A large number of technologies and innovative designs are nowadays under investigation and are considered as possible alternatives for the future of integrated circuits evolution. Some examples are Quantum cellular automata[100], Spin-based electronics[168, 151], Carbon nanotube[131] and Silicon Nanowire designs[17], Markov random networks[124], Neuromorphic designs[196], etc. Each

<sup>&</sup>lt;sup>1</sup>integrating more and more functional blocks

of these technologies have their advantages and challenges, and for the time being none of them is considered mature enough to replace traditional CMOS circuits.

The SiNW-based crossbars[182] are the most promising building blocks for the future integrated circuit design due to their fabrication methods, their electrical properties, their huge integration capacity and their compatibility with today's technology.

This chapter starts (Sec. 2.2) by overviewing the different integrated circuit designs and their evolution over the years. In Sec. 2.3 the limits of the current CMOS technology are presented. Sec. 2.4 presents the alternatives that are currently under investigation for replacing CMOS and continuing Moore's law. The different crossbar based fabric designs are presented in Sec. 2.5. Sec. 2.6, reviews the most important aspects described in this chapter.

#### 2.2 Integrated Circuits - Overview

Integrated circuits are without doubt one of the most amazing success stories of the last 60 years. They can be found virtually in all electronic equipment today, and have revolutionized society. Today's computers, cell phones, GPS devices, IPods, etc., fiction for our grand-parents, have become embedded in our daily lives. They are made possible by the tight integration of advanced electric circuits enabled by the technological advancements of the last century.

These circuits are made up of basic electrical components such as:

- resistors passive devices that limit the flow of current passing through and allow the control

of the amount of current allowed to pass.

- capacitors passive devices allowing to store electric charge and to release it.

- diodes passive devices that allow electric current to pass in one direction while blocking it in the opposite direction. But they can be tuned towards more complex behavior.

- transistors active devices that behave like a switch and thus are used to allow and disallow the flow of current. Moreover, they can amplify current.

The transistor is probably the most important device in today's electronics. Before its invention, at Bell Labs in 1947, the vacuum tubes were used for the same functions, but in comparison they were big, slow, consumed more power, moreover, they would burn out easily. The transistor didn't have these problems, however solutions to design complexity and imperfections of the manual assembly techniques had to be found, before starting the exponential progress that we have witnessed. In 1958 Jack Kilby and Robert Noyce solved the complexity problem by proposing what we call today integrated circuits. J. Kilby's proposition[83, 136] enabled building many transistors out of a monolithic block of semiconductor, while R. Noyce[129] made this approach practical by adding a metal layer on top, that will be patterned to create wires, thus solving the connection problems.

Based on these fundamental breakthroughs, during the last 50 years, the integrated circuit industry moved fast forward, nowadays integrating billions of transistors in a single chip. This history of evolution, driven mainly by the ability to scale down devices and build denser and denser chips, can be broken down into several generations, according to the integration level (the number of transistors on a single chip):

- Small-Scale Integration, consisting in small circuits assembly of a few (tens of) transistors.

- Medium-Scale Integration, circuits having hundreds of transistors on the same die.

- Large-Scale Integration, having thousands of devices.

- Very-Large-Scale Integration, ranging from 100 000 to, nowadays, several billion transistors.

• Ultra-Large-Scale Integration, stands for further improvements and scaling, but there are technological factors that limit the scaling of the current technology (See. Section 2.3 for details). Today several alternative scaling strategies (based on other metrics than integration density) are investigated, like system-on-chip (SoC), or three-dimensional integrated circuits (3D-IC).

The integrated circuits can be classified into three broad categories, digital, analog, and mixed-signal, according to the way the electrical signals are interpreted either as discrete signals (0,1), continuous signals, or a mix of discrete and continuous signals.

oDigital circuits are the dominating class of integrated circuits, replacing wherever possible the analog counter-parts, due to their noise tolerance, and automated design process.

#### Managing Complexity through Design Styles

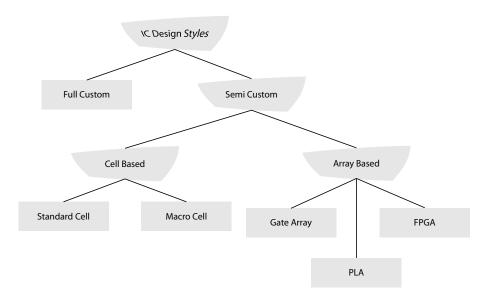

Due to the huge integration densities the physical design of an integrated circuit is an extremely complex process. In consequence the entire process was decomposed into several easier steps, thus isolating the concerns and rendering the design complexity manageable. However under the market pressure, which demand quick time-to-market and high yield, the gap between the ever increasing requirements and the reality of circuit design complexity pushed designer towards restricted IC models and design styles that reduce the complexity of physical design. The design style can be classified into two distinct categories full-custom and semi-custom. In a full-custom design style the functional blocks of the circuit can be placed arbitrarily on the wafer without overlapping them. On the other hand, in semi-custom designs, different parts of the circuit are predesigned and placed at predefined positions on the layout. Figure 2.1 presents a classification of IC design styles showing further derivations of the semi-custom style. In the following paragraphs we will briefly present the most important design styles used for IC design. For the interested reader more details can be found in [156].

Figure 2.1: A taxonomy of digital IC design styles

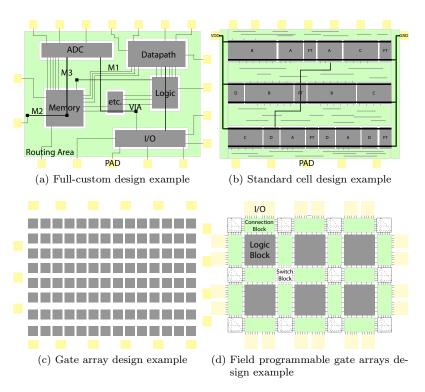

**Full-Custom Design** This is the most general form of circuit design in which the circuit is partitioned into a collection of blocks usually based on the functionality and the density of connection between devices. This process is done hierarchically producing design with several levels of hierarchy. The full-custom design style doesn't constraint the shape nor the size of the functional blocks thus providing an array of heterogenous tiles which are placed on the wafer. Figure 2.2a

shows an example of a full-custom design with a few blocks. For simplicity, only one hierarchical level is shown in this figure. The connections between blocks are realized using several metal layers (three in the figure). The circuits realized using the full-custom design style are very compact. However, this design style is used for mass produced IC, since the high costs of optimizing the layout cannot be justified for low-volume production.

Figure 2.2: Four different IC design styles

Standard Cell Design Compared to the full custom design style, the design process of standard cell is much simples. The blocks (called standard cells in this context) are constrained to have the same height and are placed in parallel rows on the layout. The circuit is partitioned into smaller blocks which are equivalent to some predefined cells. These predefined cells are designed and tested separately prior to the circuit design and they provide a collection of standard functional blocks common to most IC needs. A collection of these cells is called a cell library. According to the circuit needs (identified during the partitioning) a number of cells from the library are instantiated and placed on the layout on a regular manner (in parallel rows). The space between these rows, called a channel, is used for interconnecting the cells to create the desired circuit. If two connected cells are placed on two rows that are not adjacent to each other, the electrical connection between these two is realized using feedthrough cells which are placed in the rows. Figure 2.2b shows a simple example of standard cell design using 4 cells (A, B, C, D). Typically standard cell designs are faster to develop, however an important non-recurring design effort is invested for creating the cell library. This design style is typically preferred for the creation of high-performance application specific integrated circuits.

Gate Array Design Gate arrays appeared to simplify the standard cell design. Unlike standard cell design, the cells in a gate array are identical. Each chip is a regular array of identical gates separated by horizontal and vertical channels. The cells of a gate array can be a simple NAND gate, which is regularly replicated. The gate array wafers are pre-fabricated, and they are

named "uncommitted" as long as the routing connections are not added to the chip. Once the circuit design is known, and placed on the uncommitted array the routing wires can be added to create a customized chip implementing the desired behavior. Figure 2.2c shows schematically an "uncommitted" gate array. The gate array design style has one of the most restrictive forms of layout, which implies simpler design automation algorithms, especially in terms of routing which is conceptually simpler than in the cases of full-custom or standard cell designs.

#### 2.2.0.1 Programmable Logic Devices

A programmable logic device (PLD) is an electronic component with a regular organization, similar to the gate-array design, which enables post-manufacturing configuration to implement a specified logic functionality. The idea behind PLDs is to provide a functionally rich prefabricated chip which can be customized on demand. The user simply configures the already existing interconnect resources to suit its application needs. Two main design directions can be identified, one using a large number of simple logic gates to create the support for implementing logic functions in the sum of products canonical forms, another relying on small memory blocks (LUTs<sup>2</sup>) which can be configured to store the truth table of a logic function. This difference renders the first category more suitable for implementing large combinational logic application, while the second is more suitable for implementing sequential logic applications (i.e. large stage machines, microprocessors).

**Programmable Logic Arrays (PLA)** is one of the first programmable device relying on a set of programmable AND gate planes linked to a set of programmable OR gate planes to implement logic functions as sum of products. These first PLA devices are programmed during the fabrication process using different masks according to the desired functionality. The main advantage of this approach is the reduced fabrication cost, and the high integration density that can be achieved. However, the need for two different masks (one for the AND plane and one for the OR plane) made these devices less popular.

Programmable Array Logic (PAL) design is conceptually similar to the PLA design, however there are two important differences. The PAL devices implement logic functions using a programmable AND plane followed by a fixed OR plane, whereas the OR plane is programmable in the case of PLA. And probably the most important difference is the way these devices are programmed. If the PLAs are mask-programmed during the manufacturing process, the PAL devices rely on programmable read-only memories (PROM) to achieve one-time field-programming. The field-programming feature of these devices enables foundries to produce large amounts of virtually identical PAL devices, which will be then programmed by the customer to suit its application needs.

Generic array logic (GAL). The next evolution step of PAL devices is the introduction of generic array logic (GAL). Besides the logical properties of PALs these devices are re-programmable, which means that they can be erased and reprogrammed. The re-programmability of GALs is very useful during the prototyping stage of the design, when the eventual logic errors can be corrected by reprogramming. Moreover, since the implemented logic can be replaced after deployment the logic design can be updated or completely changed on the field.

Complex PLDs (CPLD). The main limitation of PLAs, PALs, and GALs is their small size. For bigger circuit design complex PLDs (CPLD) devices were introduced. Conceptually they are composed of a set of PALs (or GALs) integrated in on IC and interconnected by a programmable routing infrastructure that enables the creation of arbitrary connections between the PLDs.

$<sup>^2</sup>$ LUT - Look-Up Table

Field Programmable Gate Array (FPGA) designs are an alternative to ASIC design that can dramatically reduce manufacturing costs for low-volume IC circuit production. The idea behind FPGA design is to provide a functionally rich prefabricated chip which can be customized on demand. The user simply configures the already existing interconnect resources to suit its application needs. An FPGA can be seen a regular array of cells - much like a gate array - interconnected by a flexible and customizable routing architecture. The FPGA cells are more complex than standard cells, however most of the cells are identical. Figure 2.2d shows schematically the design of an island style FPGA design. The FPGA cells can be seen as memory blocks which can be configured to remember the truth table of a logic function. The given the input the cell "looks up" for the corresponding output in the stored table and passes it to the output. The big advantage of FPGAs is that there is no need user specifications to fabricate the unprogrammed FPGA. Hence, it is cost effective to produce a large volume of generic (unconfigured) FPGAs. Moreover, from the user perspective an FPGA is an ideal platform for IC prototyping especially in the context of re-configurable FPGAs which can be erased and re-configured to implement another circuit at any time during its lifetime.

#### 2.3 CMOS Technology and Its Limits

The complementary metal-oxide semiconductor (CMOS) technology was, historically, a good choice for circuit design, due to the lower power consumption achieved by leveraging the complementarity of the n and p MOSFET devices. This enabled the creation of logic circuits with virtually no power consumption during the off-state[132]. Moreover the gate-dielectric isolates the logic stages which enabled easier circuit designs (relaxing the loading effect constraint) with large fan-out for a single MOSFET.

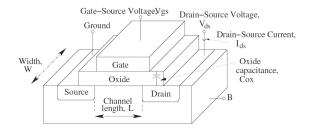

Figure 2.3: MOSFET Structure

The standard structure of a MOSFET device, presented in Fig. 2.3, comports three layers: the metal gate electrode, the gate dielectric, and the semiconductor substrate. Historically, the material used for the gate electrode was poly-silicon, for the gate dielectric silicon-oxide, and silicon for the substrate. Nowadays the metal gate electrode material was replaced by polycrystalline silicon and the silicon oxide dielectric by materials with a high dielectric constant (high-k), like Hf and Zr[17]. The source and drain electrodes are formed by doping the substrate with a material providing (n-type) or accepting electrons (p-type). The source-drain doping has to be opposite than the doping of the channel under the gate. A high voltage on a N-type MOSFET gate creates a bridge between the source and the drain, while for P-type MOSFET the channel between source and drain conducts at a low voltage on the gate.

The main parameters, characteristic of MOSFETs, are:

- oxide capacitance,  $C_{ox}$ , the capacitance between the gate and the substrate;

- gate-source voltage,  $V_{GS}$ , is the voltage between gate and source that controls the transistor switching;

- drain-source voltage,  $V_{DS}$ , the voltage between drain and source;

- threshold voltage,  $V_T$ , is the minimum voltage at which the transistors switches;

- drain-source current,  $I_{DS}$ , is the current flow when the transistor is switched on.

For the last 40 years MOSFET devices scaled based on a set of simple rules, one of which is constant-field scaling (CFS)[61]. According to CFS if all the dimensions as well as voltages of a MOSFET device are scaled with the same factor, the electric field and the current density remain constant. For logic circuits this results in doubling the integration density, while speed increases by the scale factor and the power density remains unchanged. But as feature size got smaller and smaller, different properties, overlooked by this simple scaling rule, had to be taken into account. In [61] the authors classified the challenges encountered by CMOS scaling today according to 5 categories:

- Physical challenges refer to side effects of scaling, like parasitics, off-state leakage and doping effects;

- Material challenges refer to the inability of finding the chemical compounds able to counter-act some of the physical challenges, like better insulators to reduce parasitics and conductors to improve the performances;

- Power-Termal challenges refer to the increase in power consumption and heat dissipation

per chip, which continuously increase due to the exponential increase of the integration

density;

- Technological challenges refer to inability to scale at the same pace the lithography-based fabrication processes; thus wafer diameter increased over time to maintain the productivity but the patterning steps became more and more complicated, and is expected that optic-based fabrication would not be feasible for future technology nodes;

- Economical challenges refer to the IC production costs. As the complexity of the fabricated chips increase, the testing cost start to dominate the circuit fabrication cost. Moreover, as our capability of handling the fabrication process decrease the testing becomes even more costly and complex. At the same time, the foundry cost increased exponentially. These reasons drive the industry to question the affordability of this technology from a purely economical point of view.

To overcome these challenges, much of the scientific community embraced the "equivalent scaling" idea[73], and during the last 10 years they have tried to pin down the next best technology - after CMOS. The following section (Sec. 2.4) reviews some of the most promising alternatives to CMOS.

#### 2.4 Emerging technologies

The deepening of CMOS problems at the nano-metric scale threatens the future of integrated circuits industry. Today, a large array of possible ways of scaling past Moore's law are under scrutiny. The purpose of this section is to review some of the most promising approaches to better understand the technological context that influenced the work presented in this thesis.

#### 2.4.1 Taxonomy

In [74] ITRS proposes a classification of the emerging research devices according to a taxonomy of the principal technology layers that interact for creating a fully functional system. Figure 2.4 presents these layers starting from the lowest physical level, the state variables, up to architecture level passing through materials, devices, and data representation levels.

Figure 2.4: Emerging Circuits Taxonomy.

**State Variables** refers to the physical phenomena that give the intrinsic characteristics of the device and enable computation based on a number of discrete states. The current technology makes use of the electric charge as state variable, relying on charge or voltage state of a node in CMOS logic. A number or research projects focus specifically on finding an alternative set of state variables for creating computational devices. Some examples are:

- Molecular state relies on particular molecular configurations that can be changed over time. The rotaxane molecule[22], bistable catenanes[163], and molecular quantum dot system[135] are some examples of molecules engineered as building blocks for future molecular electronics[64].

- Spin orientation exploits the intrinsic electron spin and magnetic moment. In [74], two types of spin transistors are presented: spin-FET, that operates by precession or de-phasing of polarized carriers in the channel; and spin-MOSFET, that use relative magnetization configurations to modify the output current. Moritz et al. proposed a different approach by showing that complex logic devices can be built using spin-waves[151].

Materials refers to the choice of particular chemical substances, molecules, polymers for their physical properties that support different types of devices and functional schemes. During the last years research efforts were made to better understand the advantages and limitations of other materials besides silicon (e.g. carbon, high-k materials, superconductors). Moreover with the advances in nanotechnology and molecular engineering nano-structured materials like silicon nanowires, carbon nanotubes, and graphene became some of the most promising materials for supporting the circuit scaling to few nanometer ranges.

**Devices.** From the device perspective three principal axes can be identified [74]: one focusing on scaling CMOS to its ultimate limits; the second one using new charge-based devices; and the third one striving to reinvent integrated circuits all over again by using completely new devices and physics (not charge-based). The principal pillars for supporting the ultimate CMOS scaling are devices like finFET[71], unconventional transistors, CNT FETs[29], graphene nanoribbon FETs[56], NW FETs[3], etc. Single-electron transistors (SET)[169], tunnel-effect transistors[133],

and spin transistors[168] are the principal electric charge-based devices that can potentially replace CMOS. As for the third axis, we can cite collective spin devices[18], moving domain wall logic[1], molecular devices like the ones presented in [64], and magnetic quantum cellular automata[38]

**Data Representation** represents the way information is encoded for computation. Besides the classical analog and digital data representation, there are some new approaches like patterns[196], quantum state[6], probabilistic data encoding[124].

**Architecture** level is the highest technological level proposed by this taxonomy. It spans geometrical integration (2D, 3D), physical structure (regular and heterogeneous), connectivity (GALS, fan-out, signal distribution), reliability, logic implementation and data storage, application-specific and reconfigurable designs, and computing machinery (vonNeumann, neuromorphic, quantum, etc).

#### 2.4.2 Requirements for Competitiveness

ITRS [73] proposed a number of requirements that should be meet for a new fabric to be competitive. These requirements include:

- inversion and flexibility;

- isolation between the input and the output of each device;

- logic gain, the output may have a fan-out bigger than one;

- logical completeness, ensuring that any logic function can be implemented and thus eliminating the need for additional supporting circuitry;

- self-restoring/stable for ensuring the signal quality;

- low cost manufacturing for increasing the productivity and further decreasing the cost per device ratio;

- reliability;

- performance.

Based on these requirements and the maturity of today's CMOS technology, it was stated[74] that CMOS designs are difficult to replace by any new technology especially for binary computations based on the von Neumann model. But the new charge-based devices either CMOS-like (e.g. SiNW FETs) or not appear to be the best candidates for continuing the incremental evolution of circuits. Break-through devices based on new state variables, are to be better understood for building novel architectures leveraging their features and eventually breaking the current incremental evolution process.

#### 2.4.3 Some Fabric Propositions

Quantum-dot cellular automata (QCA)[176, 100], Tour's Nanocell[177], Markov Random Network (MRN)[7, 124], and Nanowire Crossbar-based Fabrics (NCF) [60] are a few approaches for building computational structures bridging the gap between the need for powerful, energy efficient, and small circuits and the intrinsic limits of the current integrated circuits. They exploit novel state variables (QCA), random device organization (Nanocell), probabilistic data and circuits (MRN), unidimensional structures (NCF).

Figure 2.5: Left, QCA cell polarizations; Right, QCA majority gate

#### 2.4.3.1 Quantum-dot cellular automata

Quantum-dot cellular automata[176, 100], introduced in 1993 by Lent et al., and fabricated in 1997 represent a completely new approach for implementing circuits. Based on quantum interactions between electrons, it provides an alternative to current CMOS technology.

A QCA cell can be seen as a set of four charge containers or dots positioned at the corners of a square. Each cell contain two mobile electrons that can quantum-mechanically tunnel between the dots but, by construction, cannot move between cells. In Figure 2.5 (left), we show an abstract view of a QCA cell with the two possible states binary 1 at left and binary 0 at right. The state of each QCA cell is influenced by the state of the neighboring cell. So basically, if we place the cell at left in Figure 2.5 next to the cell at right, the last one will change its state to a binary 1 value. This way a set of interesting computational devices can be obtained (ex. majority gate[127] in Figure 2.5 on right).

In [128], the authors presented a FPGA-like architecture using these revolutionary devices. Some of the particularities of this approach compared to traditional FPGA are: a) instead of implicit latching of signals QCA FPGA use QCA wires' self-latching capabilities; b) the clock for QCA FPGA has four phases instead of just two in traditional circuits; c) the use of a QCA wire loop for storing state.

In 2006, a PLA architecture using QCAs was proposed [67]. This PLA fabric is reconfigurable and defect tolerant. The basic building blocks used in this approach are PLA cells made up by one AND gate, one OR gate and one select bit. The AND and OR gates are obtained by constraining a majority gate to perform the desired function. The select bit is used to indicate if the PLA cell acts as a wire or as a logic gate. The PLA logic is build up by using 2 logic planes one AND plane followed by an OR plane. These logic planes are made up of PLA cells which act as AND gates or OR gates according to the position of the two gates inside the PLA cell. The issues of configurability and fault tolerance were also addressed in the same paper. Also the nature of the clocking circuitry and structure were discussed.

However, even though the research in the area of QCA started almost 20 years ago the field is still young, and the published works are just pointing the needs for further research in order to render these technologies a veritable candidate to replace "current flow" based technologies.

#### 2.4.3.2 Nanocell

One of the first proposed computational architectures that make use of nanoelectronic devices is Tour's Nanocell[177]. This fabric is conceived to harness the random nature of nano scale devices by randomly depositing very small conductive particles of gold or platinum on a substrate and then adding molecules having NDR properties to each of these particles. Thus obtaining a random network of switching nanodevices, namely Nanocell shown in Figure 2.6. This network is then trained to perform the desired function using a genetic algorithm. The building block for computational fabrics, using Nanocell approach, are presented in [68].

The main advantage of this approach is that it has inherent fault tolerance by harnessing the random nature of nanotechnology instead of trying to create some order. However, the huge amount of computational resources needed to train a Nanocell renders this approach not scalable for creating large logic arrays.

Figure 2.6: Example of a Nanocell Tile

#### 2.4.3.3 Markov Random Network

Researchers at Brown University proposed a probabilistic design method for nanoscale circuits based on Markov Random Fields (MRF)[7, 124]. Independent from the underlaying technology and the presence of defective devices, this computational fabric relies on a graph of stochastic variables, a belief propagation algorithm, and the Gibbs energy distribution[7].

In [124], the authors have shown that CMOS circuits implemented using this methodology can be noise tolerant, feature that can be used to lower the power consumption by lowering the supply voltage.

However, in the case of the CMOS designs the number of devices needed is larger than the one required by classical CMOS logic gates for equivalent functionality. To address this issue the authors propose a carbon nanotube-based implementation, which improves the density but it challenging from a technological point of view. Besides these technological issues, another limitation of this design methodology is the lack of tools for logic and physical synthesis.

#### 2.4.3.4 Hybrid nano/CMOS Nanowire Crossbar Fabrics

Amongst the most promising emerging devices are the Si-nanowire FETs[75] "[...] because of higher on-current conduction due to their quantum nature and also because of their adoptability for high-density integration including that of 3D". A number of fabric structures, relying on these devices, are currently under study, e.g. NanoPLA, NASIC, etc. At the beginning of 2011, Nature reported the first successful fabrication of such a fabric[192]. The experiment showed the design, the manufacturing, and the use of programmable nanowire-based logic arrays as computational primitive for nano-processors. These nanowire arrays, named crossbars in literature, consist of two sets of orthogonally placed nanowires having configurable FET devices at the crosspoints.

Another very promising device is the memristor, which was showed experimentally in [167]. The memristor is a passive device with a resistance that increases or decreases according to the current flow direction, and remains unchanged when there is no current flow. Nanowire crossbars with memristors at the crosspoints are another structure that show very desirable characteristics. In [189] the authors show the experimental results of fabricating a hybrid nano/CMOS reconfigurable structure that use the memristor-crossbar for signal routing and a CMOS layer for logic implementation.

These two success stories, built on the last fifteen years of research, provided insights into the theoretical and practical aspects of semiconductor nanowires and carbon nanotubes. Simple devices and logic gates were realized experimentally in the past and paved the way to this notable success. From the architectural point of view a number of different fabric structures were proposed and are currently under investigation. The following sections of this chapter focus on the principal characteristics of these fabrics, in terms of fabrication process, defect/fault tolerance methodology, the integration with CMOS complementary circuitry, and the different logic implementation strategies. Moreover, four of the most important fabric contribution are reviewed for a comprehensive understanding of the field.

### 2.5 From crossbars to digital circuits

To continue integrated circuit evolution according to the trend imposed by Moore's law, past the CMOS technology limits, we have seen that a number of alternative technologies are under investigation. Amongst these, the crossbar-based nano-fabrics are some of the most promising candidates. They tackle the impossibility of arbitrary placement and routing of nanoscale structures by using regular arrays of crossed nanowires with functionalized cross-points. These arrays are structured, conceptually, like traditional reconfigurable architectures (FPGA / PLAs). The purpose of this section is to show the principal characteristics of these nano-fabrics for digital circuit implementation. The section starts, Sec. 2.5.1, by presenting different fabrication alternatives for building nanowire crossbars. Sec. 2.5.2 presents one of the most important issue of these structures, the high-rate of defects, along with some techniques proposed for creating reliable circuits. Sec. 2.5.3, shows different ways of implementing digital logic using these supports. Since all these propositions use CMOS circuitry for different purposes, Sec. 2.5.4 reviews the main approaches for interfacing between the nanoscale and CMOS structures. Sec. 2.5.5 briefly details four of these fabric propositions focusing on their respective differences.

#### 2.5.1 Fabrication process

For the fabrication of regular nanowire arrays, the traditional lithographic process cannot be used mainly due to the small feature size and to the need to finely control the fabrication parameters (the number of NWs, the pitch, the NW diameter). To address this problem three new fabrication methods have been proposed:

- NW growth and alignment in-situ

- NW growth with ex-situ alignment

- Patterning and Etching based on Nano-lithography

#### 2.5.1.1 NW growth and alignment in-situ

This method is used for the fabrication of NW arrays by growing aligned nanowires using chemical auto-assembly on the target substrate. Guiding techniques are used to orient the growth process. Substrate or template guiding[62, 153], electric field guiding[48], and gas flow guiding[105] are some examples of guiding methods. The growth, resulting from catalytic processes, depends strongly on the chosen catalyst which has to be compatible with the substrate and the auto-assembly temperature. Moreover, for successful NW alignment, the catalyst has to be placed as aligned dots with the same diameter and inter-dot distances.

#### 2.5.1.2 NW growth with ex-situ alignment

This method uses two independent steps: the nanowire growth, and their placement on the target substrate. Techniques like Vapor-Liquid-Solid[16] can be used for growing NW forests. Then, different techniques can be employed for their alignment and on-substrate placement, like Langmuir-Blodgett[21, 188], liquid or electric field guided alignment[190, 104], organic auto-assembly[78], or contact printing[76]. The principal challenge of this technique is the control over the NW position and orientation on the target surface and, thus the capacity of finely tuning the pitch and the NW lengths. This fabrication procedure is more flexible than the NW growth and alignment in-situ with respect to the materials used for the growth process.

#### 2.5.1.3 Patterning and Etching based on Nano-lithography

Compared to the bottom-up techniques, presented in the previous paragraphs, this fabrication process is a top-down method relying on patterning and etching, similar with the traditional lithography. The patterning step engraves the pattern on the substrate using Nano-imprint lithography

(NIL) [148], or Superlattice nanowire pattern transfer (SNAP) [182], while the etching step is similar to the standard lithographic etching process. For patterning, the NIL technique uses the mechanical deformation by pressing the masks on the substrate. The simplicity is the principal advantage of this approach, since it enables low-cost patterning compared to standard photolithography. The SNAP patterning method is compatible with standard lithographic process and enables the creation of large arrays of NW from a large palette of materials (metals, insulators, semi-conductors). The main challenges of these two techniques are the mask degradation over time and the eventual NW performance degradation due to the etching process.