# Electro-thermal Characterizations, Compact Modeling and TCAD based Device Simulations of advanced SiGe:C BiCMOS HBTs and of nanometric CMOS FET

Amit Kumar Sahoo

### ▶ To cite this version:

Amit Kumar Sahoo. Electro-thermal Characterizations, Compact Modeling and TCAD based Device Simulations of advanced SiGe:C BiCMOS HBTs and of nanometric CMOS FET. Micro and nanotechnologies/Microelectronics. Universit\'e Bordeaux 1 Sciences et Technologie, 2012. English. NNT: . tel-02457044

# HAL Id: tel-02457044 https://hal.science/tel-02457044v1

Submitted on 27 Jan 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre: 4557

# **THESE**

### PRESENTEE A

# L'UNIVERSITE BORDEAUX I

### ECOLE DOCTORALE DE SCIENCES PHYSIQUES ET DE L'INGENIEUR

### Par Amit Kumar SAHOO

POUR OBTENIR LE GRADE DE **DOCTEUR**

SPECIALITE: ELECTRONIQUE

\*\*\*\*\*\*\*\*\*

# Electro-thermal Characterizations, Compact Modeling and TCAD based Device Simulations of advanced SiGe:C BiCMOS HBTs and of nanometric CMOS FET

\*\*\*\*\*\*\*\*\*

Soutenance prévue le : 13<sup>th</sup> Juillet 2012

Après avis de :

M. Raymand QUEREProfesseur, XLIM, Université de LimogesRapporteurM. Christophe GAQUIEREProfesseur, IEMN LilleRapporteur

### Devant la Commission d'examen formée de :

| M. Thomas ZIMMER       | Professeur                        | Université Bordeaux 1 | Président             |

|------------------------|-----------------------------------|-----------------------|-----------------------|

| M. Raymond QUERE       | Professeur                        | XLIM                  | Rapporteur            |

| M. Christophe GAQUIERE | Professeur                        | IEMN                  | Rapporteur            |

| M. Nicolas KAUFFMANN   | Ingénieur recherche-développement | STMicroelectronics    | Examinateur           |

| Mme. Nathalie MALBERT  | Professeur                        | Université Bordeaux 1 | Directeur de thèse    |

| M. Sébastien FREGONESE | Chargé de recherche               | Université Bordeaux 1 | Co-directeur de thèse |

# Electro-thermal Characterizations, Compact Modeling and TCAD based Device Simulations of advanced SiGe:C BiCMOS HBTs and of nanometric CMOS FET

*H*mit Kumar Sahoo

Laboratoire IMS, CNRS - UMR 5218, Université de Bordeaux 1 Cours de la Libération - 33405 Talence Cedex, France

7o Pubali 7o my Parents Janakibala and Abhoy Narayan Sahoo

# Acknowledgment

I would like to express my honest appreciation to all the people who ever gave me help and support during my PhD study period. Particularly, I would like to thank my co-advisor Dr. Sebastien Fregonese for his guidance and valuable suggestions and always keeping his door open whenever I need help and advice. It has been always fruitful and joyful to discuss with him. I would like to thank my research advisor Prof. Nathalie Malbert for her continual instruction and encouragement. I have greatly benefited from her profound knowledge and charming personality. I would also like to warmly thank Prof. Thomas Zimmer for his continuous support and help during my Ph.D study period. Also, I would like to thank XMOD Technologies for supplying the compact model parameters and STMicroelectronics for BiCMOS9MW wafer.

I thank my committee members Prof. Raymond QUERE from XLIM, Prof. Christophe GAQUIERE from IEMN and Prof. Nicolas KAUFFMANN from STMicroelectronics for being on my thesis committee.

I would like to thank my present and former lab members, especially the Compact Modeling team members: Cyril Hainaut, Mario Weisz, Maura Magallo, Marco Santorelli, Gilles Kone, David Schong and former colleagues: Johnny Goguet, Brice Grandchamp, Montassar Najari, Mahmoud Alsa'di, Si-Yu Liao, Arkaprava Bhattacharyya, Jad Bazzi and Sudip Ghosh. Their help and support during these years was invaluable. It was fun to be part of this research group and share the time in the laboratory. Finally, I wish to thank Pubali, my parents and my brothers for their support my decision to pursue my PhD far from them, and for providing invaluable assistance and encouragement.

# **Contents**

| Ab         | ostract                                                     | 15 |

|------------|-------------------------------------------------------------|----|

| Glo        | ossary                                                      | 19 |

|            |                                                             |    |

| Ge         | eneral introduction                                         | 23 |

| Α.         | Millimeter to THz waves and its application                 | 24 |

| В.         | High frequency state of the art                             | 26 |

|            | i. MOSFET technology                                        | 27 |

|            | ii. SiGe BiCMOS technology                                  | 29 |

| <i>C</i> . | Power density and thermal phenomena                         | 33 |

| D.         | Motivation                                                  | 36 |

| E.         | Thesis organization                                         | 37 |

| F.         | Project description                                         | 38 |

| G.         | Technology under analysis                                   | 40 |

| Н.         | Reference                                                   | 42 |

|            |                                                             |    |

| Ch         | napter 1: Self-heating and device compact modeling          | 47 |

|            | 1.1 Introduction                                            | 48 |

|            | 1.1.1 Electrical representation of thermal system           | 49 |

|            | 1.1.2 Thermal modeling of electronic system                 | 50 |

|            | 1.1.3 One dimensional modeling approach                     | 51 |

|            | 1.2 Analytical model and Electro-thermal network topologies | 53 |

|            | 1.3 Frequency domain thermal impedance for two-port device  | 58 |

|            | 1.3.1 Z <sub>TH</sub> formulation from y-parameters         | 59 |

|            | 1.3.2 The generalized form of $Z_{TH}$                      | 62 |

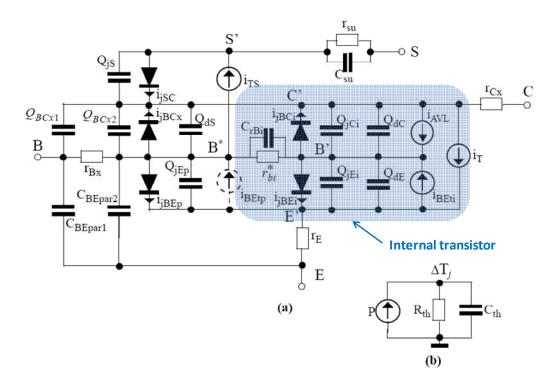

| 1.4 Compact model                                         | 63 |

|-----------------------------------------------------------|----|

| 1.4.1 High-Current Model (HiCuM)                          | 63 |

| 1.4.2 Large signal equivalent circuit                     | 65 |

| 1.4.3 Temperature dependence in HiCuM                     | 66 |

| 1.4.3.1 Temperature dependent band-gap voltage            | 66 |

| 1.4.3.2 Transfer current                                  | 67 |

| 1.4.3.3 Junction current components                       | 67 |

| 1.4.3.4 Series resistance                                 | 68 |

| 1.4.4 Self-heating in HiCuM                               | 69 |

| 1.4.5 Compact modeling                                    | 69 |

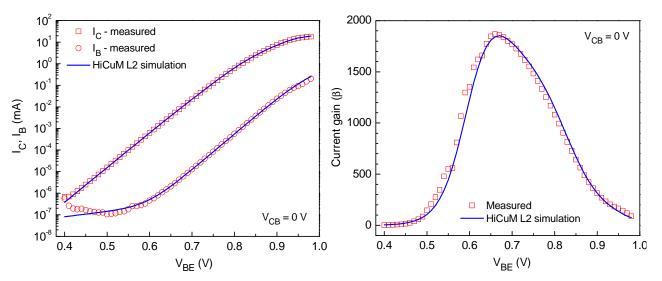

| 1.4.5.1 Gummel plot                                       | 70 |

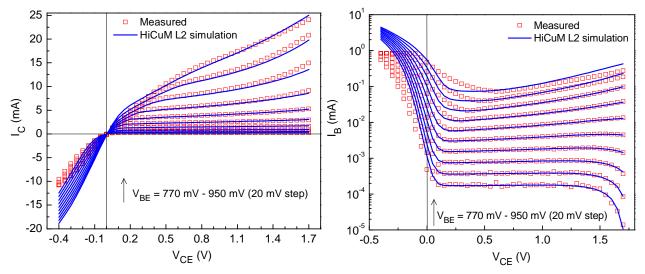

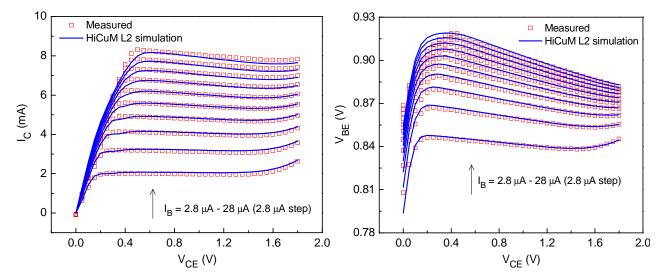

| 1.4.5.2 Output characteristic                             | 70 |

| 1.4.5.3 Dynamic characteristics                           | 71 |

| 1.5 Conclusions                                           | 72 |

| 1.6 Reference                                             | 72 |

|                                                           |    |

| Chapter 2: Characterization of SiGe:C BiCMOS HBTs         |    |

| 2.1 Introduction                                          |    |

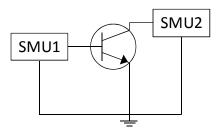

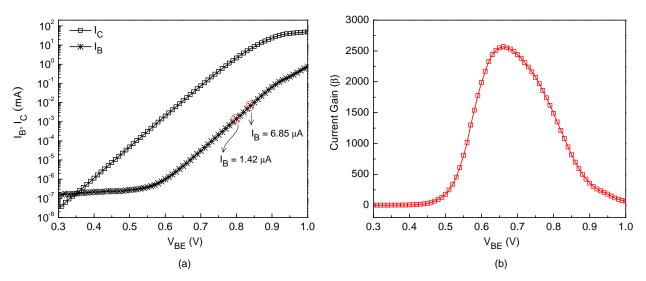

| 2.2 DC Measurements                                       | 77 |

| 2.2.1 Extraction methodology                              |    |

| 2.2.1.1 Gummel characteristic                             |    |

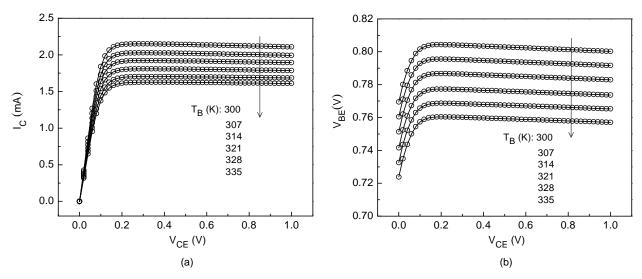

| 2.2.1.2 Output characteristics at constant I <sub>B</sub> |    |

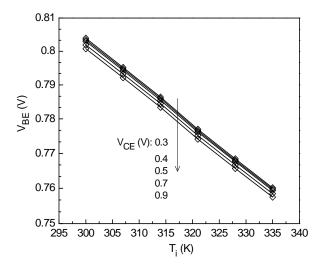

| 2.2.1.3 $V_{BE}$ as a function of ambient temperature     |    |

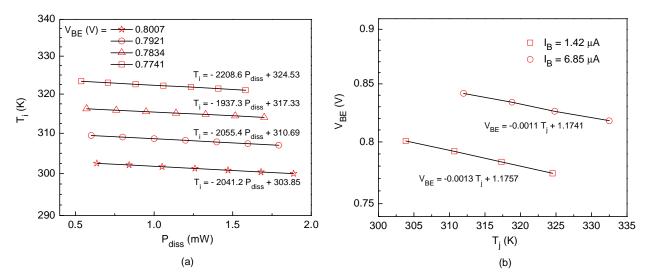

| 2.2.1.4 R <sub>TH</sub> calculation                       |    |

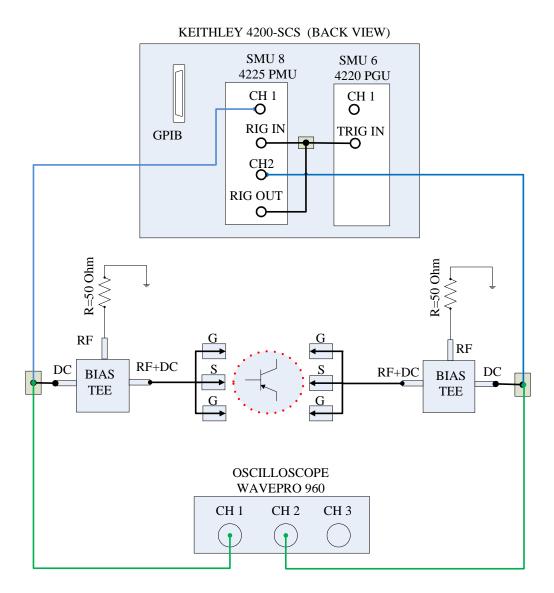

| 2.2.2 R <sub>TH</sub> vs. device geometry                 |    |

| 2.3 Pulse measurements                                    |    |

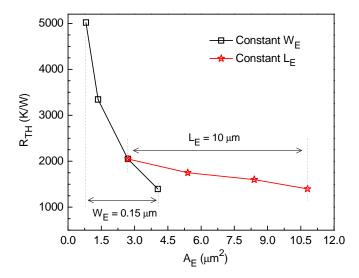

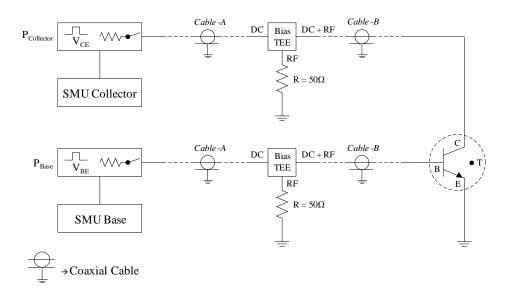

| 2.3.1 Experimental setup: KEITHLEY 4200SCS                |    |

| 2.3.1 EAPETHICIAN SCIUP. INDITITED 74003C3                |    |

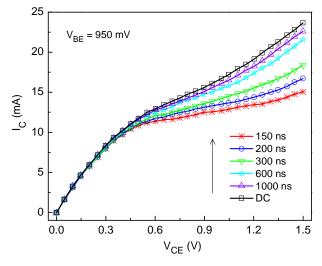

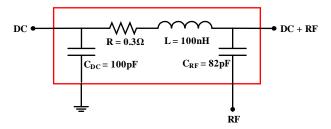

| 2.3.2         | Pulsed output and Gummel characteristic                                  | 82  |

|---------------|--------------------------------------------------------------------------|-----|

| 2.4 Tin       | ne domain characterization                                               | 83  |

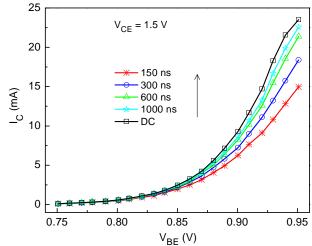

| 2.4.1         | Experimental setup: MC2 Technology APMS                                  | 83  |

| 2.4.2         | Overview of the approach                                                 | 85  |

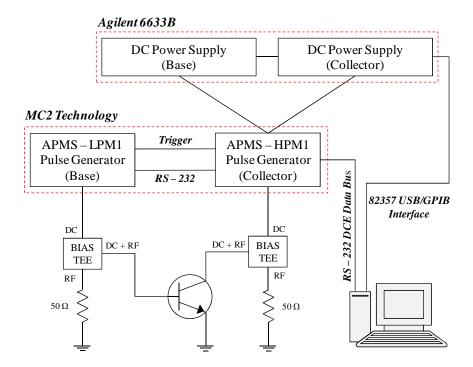

| 2.4.3         | Optimizations                                                            | 86  |

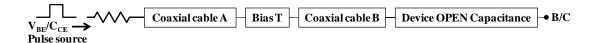

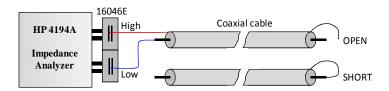

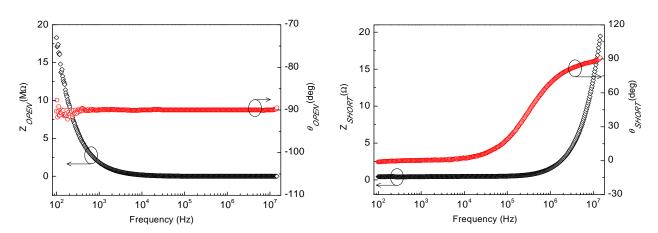

| 2.4.          | 3.1 Measurement of coaxial cable impedance                               | 86  |

| 2.4.          | 3.2 "Passive circuit" design                                             | 88  |

| 2.4.          | 3.3 Compact model simulation with "passive circuit"                      | 89  |

| 2.4.4         | Measurements comparison and analysis                                     | 90  |

| 2.5 Tro       | ansient thermal modeling                                                 | 92  |

| 2.5.1         | Influence of passive circuit                                             | 92  |

| 2.5.2         | Comparison between single pole and recursive network in time domain      | 93  |

| 2.5.3         | Transient variation of junction temperature                              | 94  |

| 2.6 Iso       | thermal data extraction                                                  | 95  |

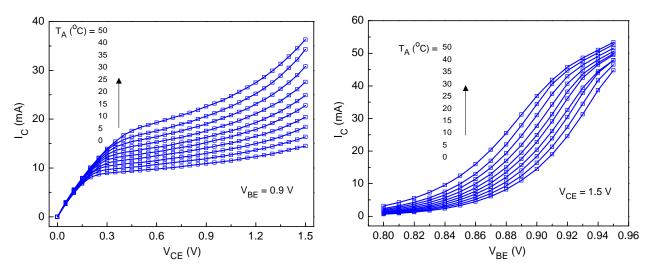

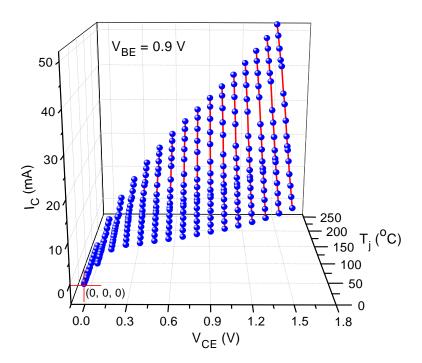

| 2.6.1         | $DC$ output and forward Gummel at different $T_A$                        | 95  |

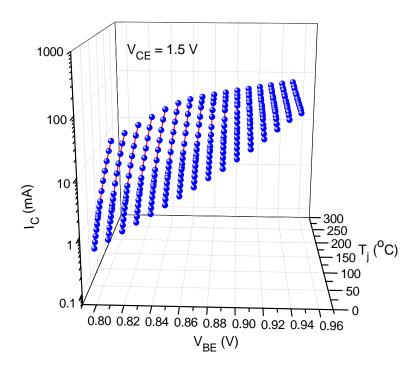

| 2.6.2         | Extraction methodology                                                   | 95  |

| 2.6.3         | Isothermal characteristics and validation                                | 98  |

| 2.6.4         | Limitations of the approach                                              | 99  |

| 2.7 Lo        | w frequency s-parameter measurements                                     | 99  |

| 2.8 Dy        | namic thermal modeling                                                   | 100 |

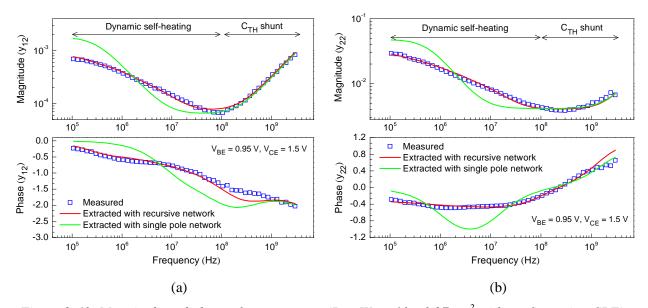

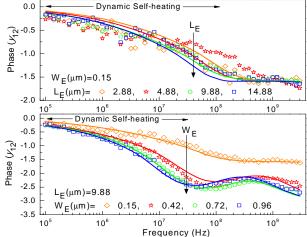

| 2.8.1         | Y-parameters and dynamic self-heating                                    | 100 |

| 2.8.2         | Comparison between single pole and recursive network in frequency domain | 102 |

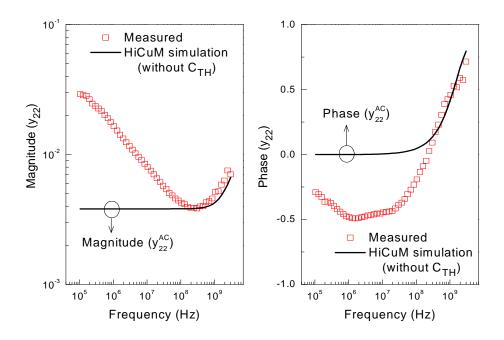

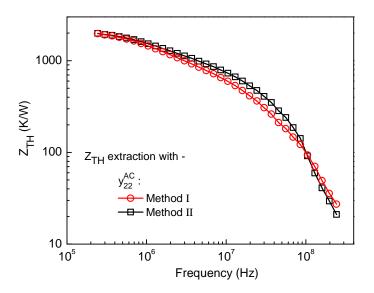

| $2.9  Z_{TH}$ | <sub>t</sub> extraction                                                  | 102 |

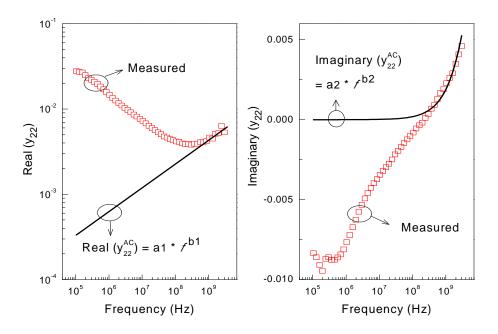

| 2.9.1         | Frequency domain slope and Maximum phase shift                           | 105 |

| 2.9.2         | Modeling and comparison among different networks                         | 106 |

| 2.9.          | 2.1 Magnitude and phase of $Z_{TH}$                                      | 106 |

| 2.9.          | 2.2 v-parameter                                                          | 107 |

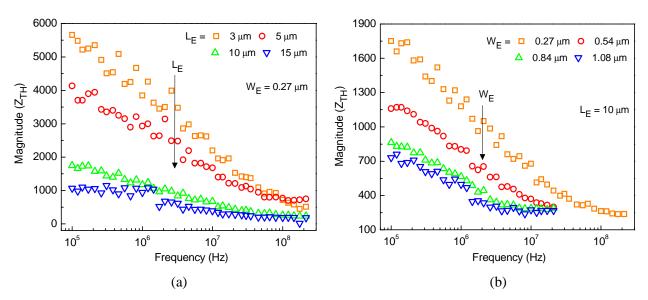

| 2.9.3 Geometry dependent y-parameter and extracted $Z_{TH}s$   |     |

|----------------------------------------------------------------|-----|

| 2.10 Conclusion                                                | 110 |

| 2.11 Reference:                                                | 110 |

| Chapter 3: Characterization of nano-metric CMOS                | 113 |

| 3.1 Introduction                                               | 114 |

| 3.2 DC measurements and R <sub>TH</sub> extraction             | 115 |

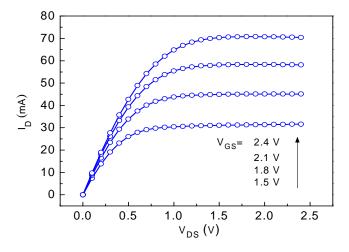

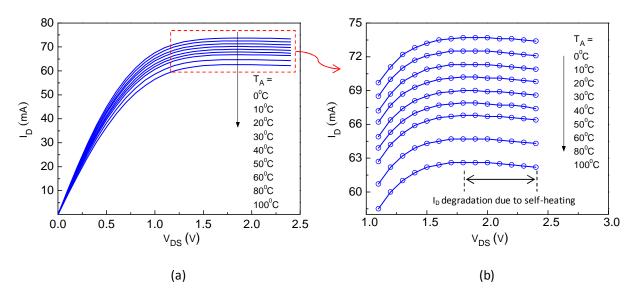

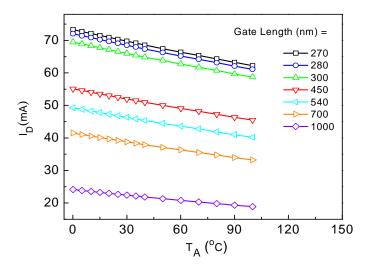

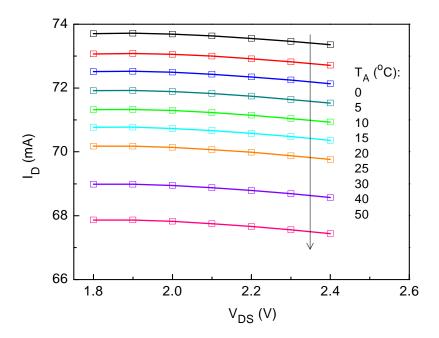

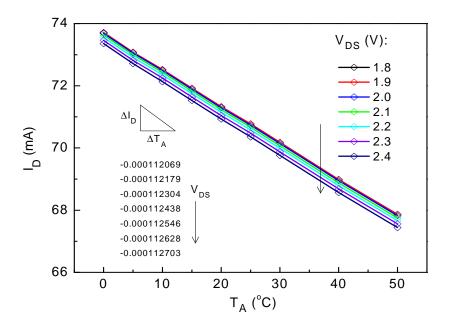

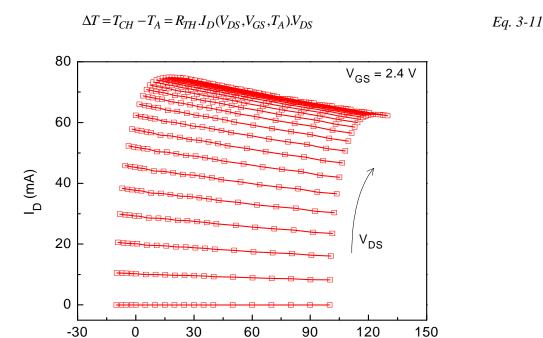

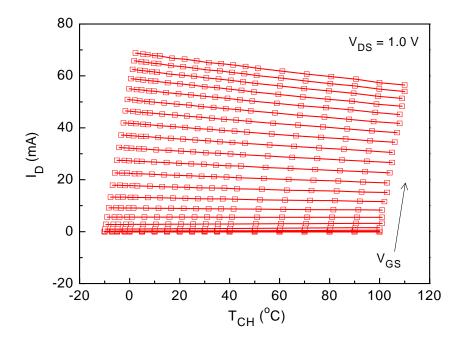

| 3.2.1 Output characteristics at different ambient temperatures | 116 |

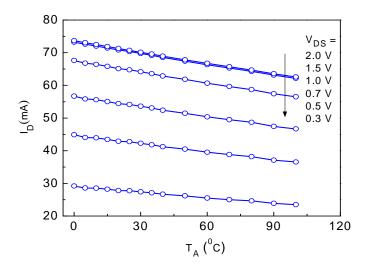

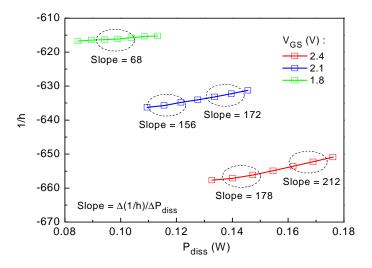

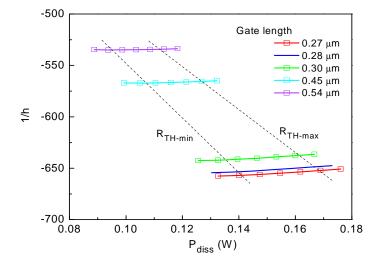

| 3.2.2 Extraction methodology                                   | 118 |

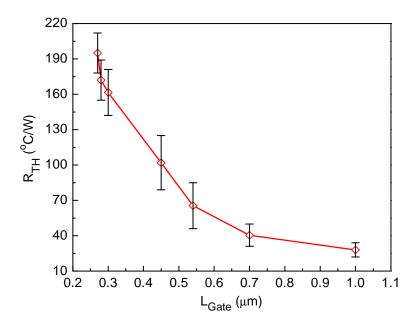

| 3.2.3 R <sub>TH</sub> with device gate length                  | 122 |

| 3.3 Isothermal data extraction                                 |     |

| 3.3.1 Extraction methodology                                   |     |

| 3.3.2 Isothermal characteristics                               |     |

| 3.4 Pulse measurements                                         | 127 |

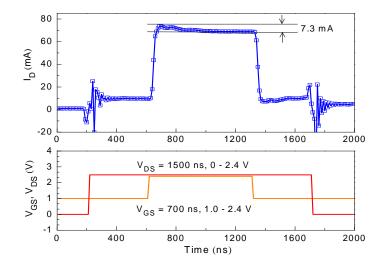

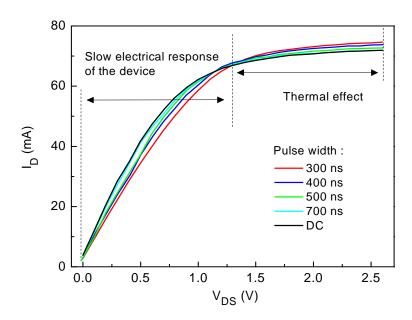

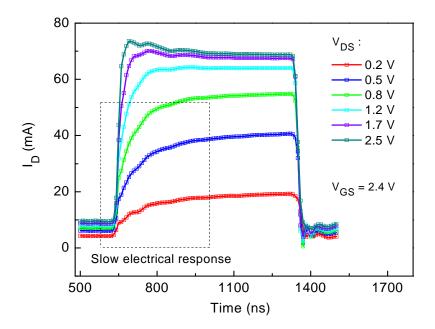

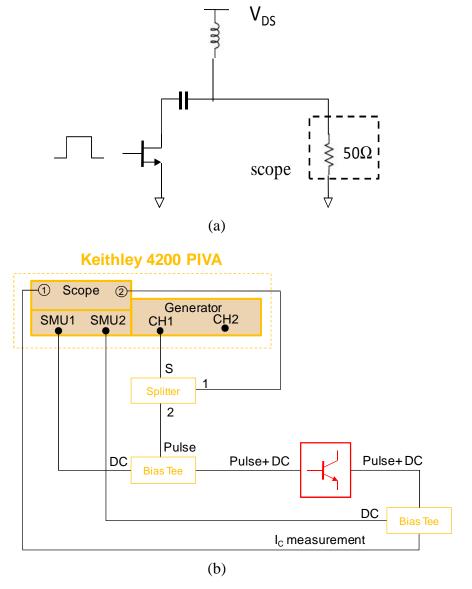

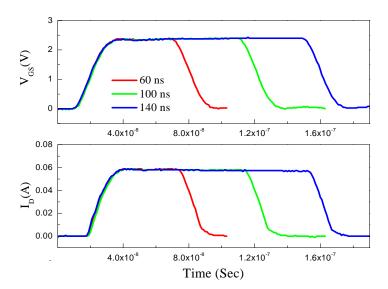

| 3.4.1 Measurements with MC2 Technology APMS                    | 127 |

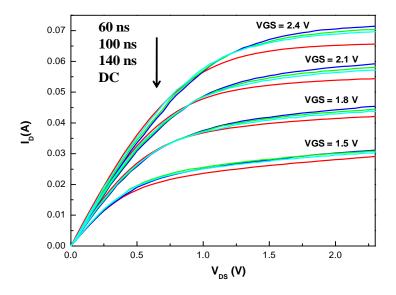

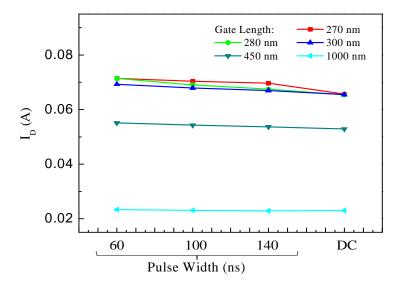

| 3.4.2 Measurements with KEITHLEY 4200SCS                       | 130 |

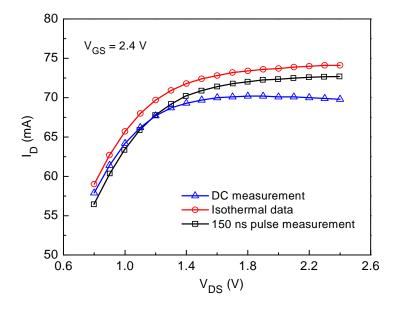

| 3.5 Isothermal data vs. pulse measurements                     | 132 |

| 3.6 DC and RF pulse measurement                                |     |

| 3.6.1 DC and RF pulse synchronization                          | 134 |

| 3.6.2 Transit frequency $f_T$ measurements                     |     |

| 3.7 Conclusion                                                 | 136 |

| 3.8 Reference:                                                 | 136 |

| Chapter 4: 3D Thermal TCAD Simulations                         | 137 |

| 4.1 Introduction                                               | 138 |

| 4.2 Thermal simulation                                         | 139 |

| 4.2.1 Thermodynamic model                                      | 139 |

| 4.2.2 Simulation methodology                                 | 140   |

|--------------------------------------------------------------|-------|

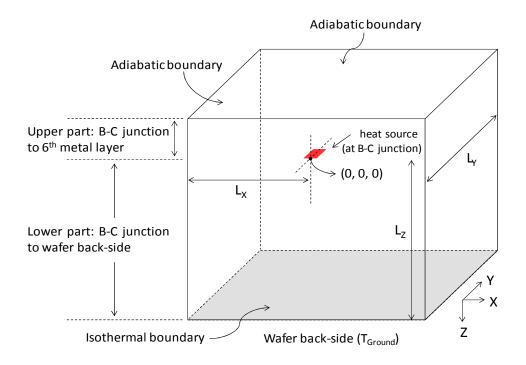

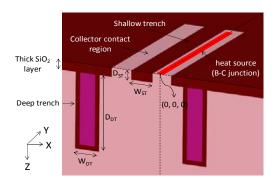

| 4.3 Device structure and material properties                 | 141   |

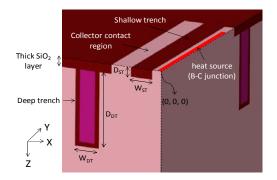

| 4.3.1 The basic structure: "Lower part"                      | 142   |

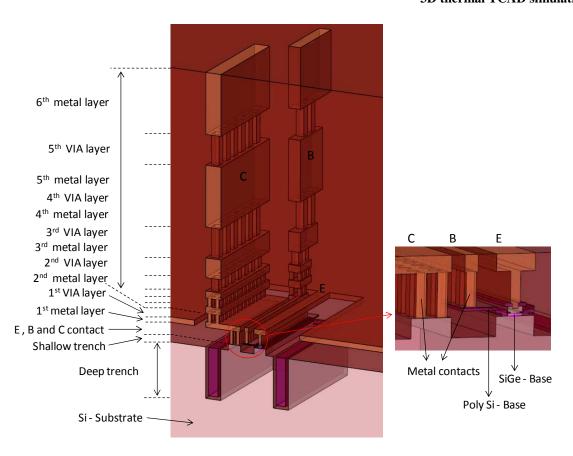

| 4.3.2 Basic structure with back-end layers: "Complete device | e"143 |

| 4.3.3 Physical parameters                                    | 144   |

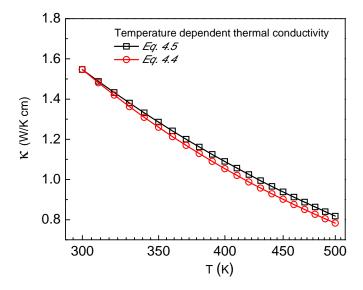

| 4.3.3.1 Thermal conductivity ( $\kappa$ )                    | 144   |

| 4.3.3.2 Lattice heat capacity (C <sub>L</sub> )              | 146   |

| 4.4 Optimizations                                            | 146   |

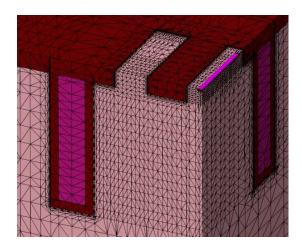

| 4.4.1 Mesh refinement and simulation time                    |       |

| 4.4.2 Simulation domain                                      |       |

| 4.4.3 Applied power density                                  | 149   |

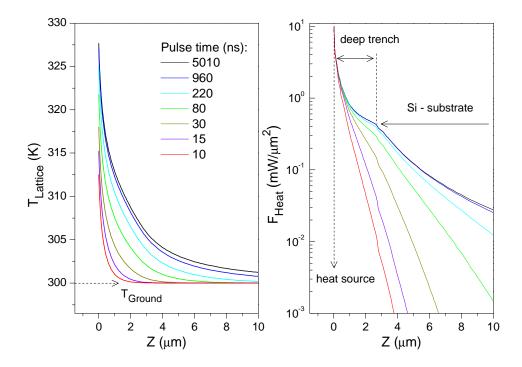

| 4.5 Transient simulations                                    |       |

| 4.5.1 Large signal transient simulation                      |       |

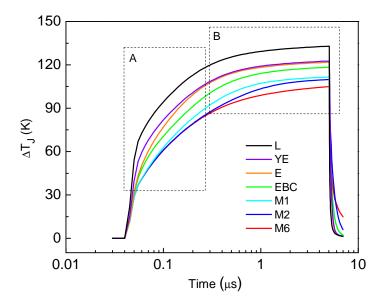

| 4.5.1.1 Transient $\Delta T_J$                               |       |

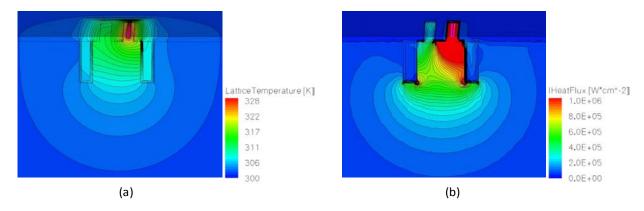

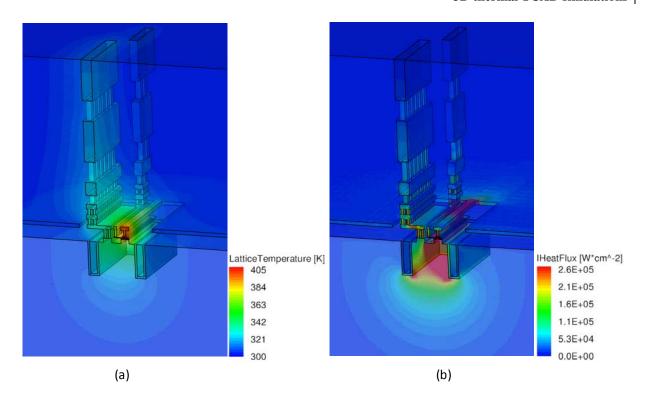

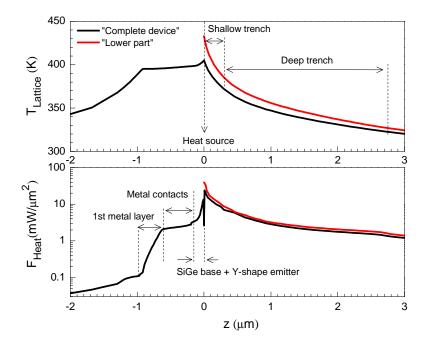

| 4.5.1.2 $T_{Lattice}$ and $F_{Heat}$ distribution            |       |

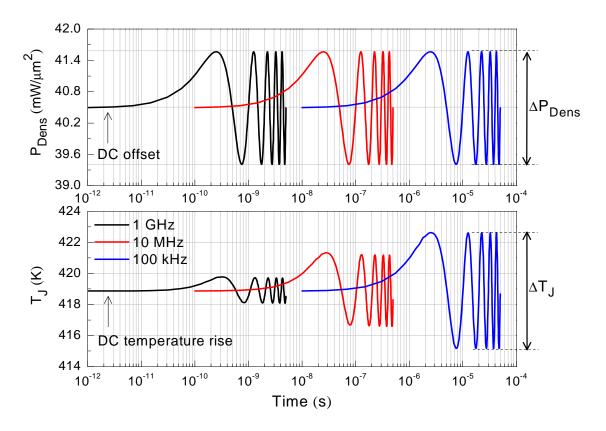

| 4.5.2 Sinusoidal transient simulation                        |       |

| 4.5.2.1 Dynamic T <sub>J</sub>                               |       |

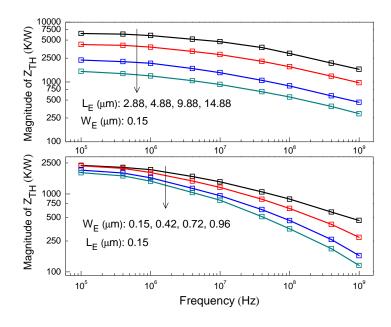

| 4.5.2.2 Thermal impedance extraction                         |       |

| 4.6 Electro-thermal modeling                                 |       |

| 4.6.1 Single pole network                                    |       |

| 4.6.2 Recursive network                                      |       |

| 4.6.3 Parameter extraction                                   |       |

| 4.7 Impact of back-end layers on thermal effect              |       |

| 4.7.1 $T_{Lattice}$ and $F_{Heat}$ distribution              |       |

| 4.7.2 Comparison of $\Delta T_J s$                           | 161   |

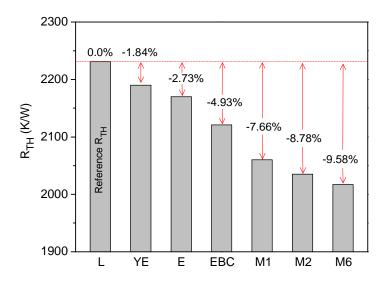

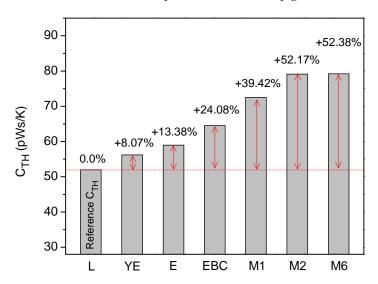

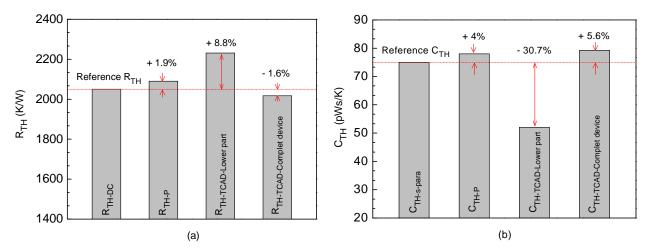

| 4.7.3 Comparison of R <sub>TH</sub> s and C <sub>TH</sub> s  | 161   |

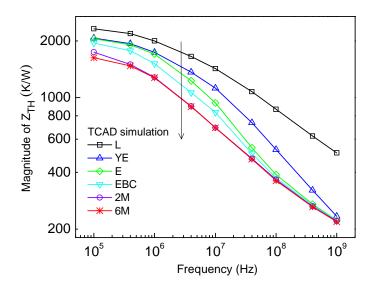

| 4.7.4 Comparison of frequency domain $Z_{THS}$               |       |

| 4.7.5 Analysis of the effect                                                            | 163 |

|-----------------------------------------------------------------------------------------|-----|

| 4.8 Conclusion                                                                          | 164 |

| 4.9 Reference                                                                           | 165 |

| Chapter 5: Results validation, scalable approach and applications                       | 167 |

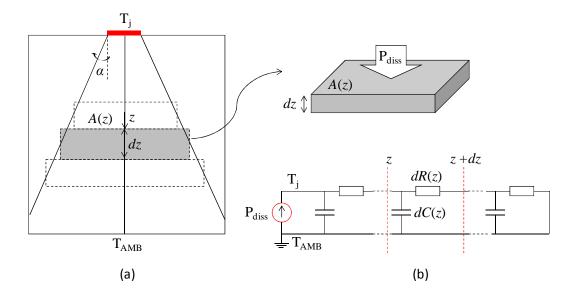

| 5.1 Results and validation: comparison between measurements and thermal TCAD simulation |     |

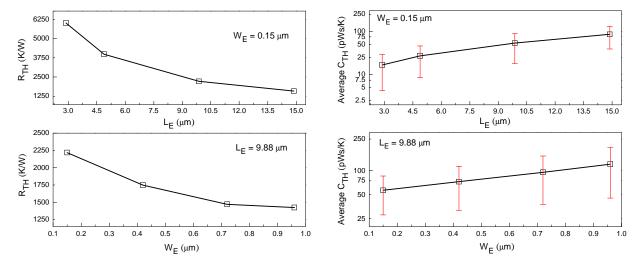

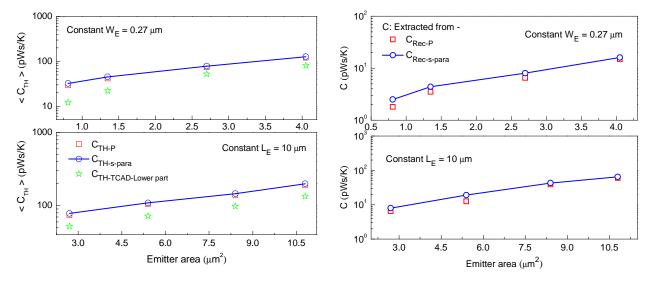

| 5.1.1 R <sub>TH</sub> s – different geometries of transistors                           | 168 |

| 5.1.2 C <sub>TH</sub> s – different geometries of transistors                           | 169 |

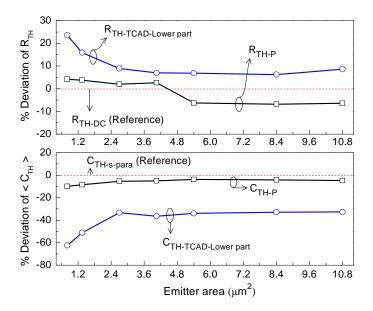

| 5.1.3 % deviation of $R_{TH}$ s and $C_{TH}$ s from reference value                     | 170 |

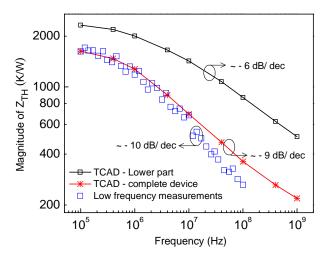

| 5.1.4 Z <sub>TH</sub> s – measurements and thermal TCAD simulations                     | 172 |

| 5.2 Introduction to scalable model                                                      | 172 |

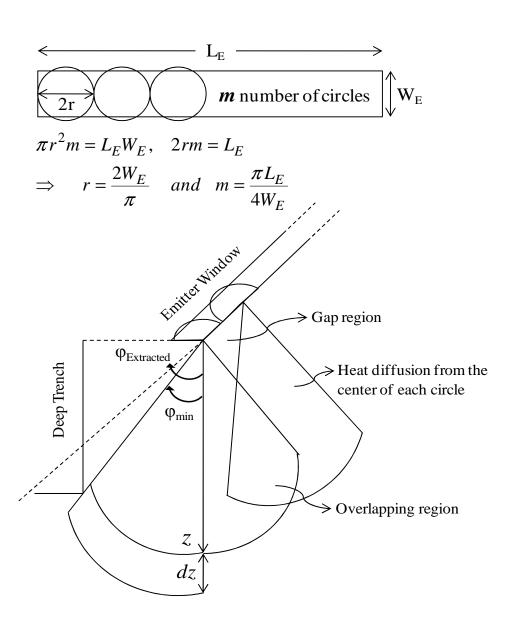

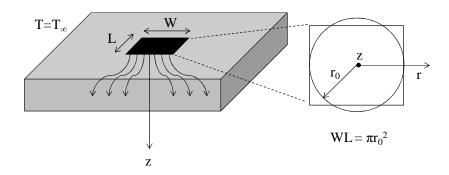

| 5.3 Theoretical analysis of thermal spreading behavior                                  | 173 |

| 5.4 Distributed Electro-thermal network                                                 | 174 |

| 5.4.1 Thermal distribution inside the device                                            | 174 |

| 5.4.2 Placement of the network cells                                                    | 175 |

| 5.5 Approximations in the heat diffusion mechanism                                      | 176 |

| 5.5.1 Spherical heat diffusion model                                                    | 176 |

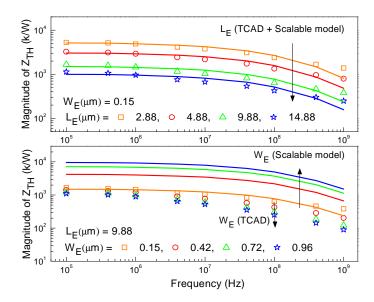

| 5.5.1.1 Verification of the model: Z <sub>TH</sub> modeling                             | 178 |

| 5.5.1.2 Limitations of the model                                                        | 179 |

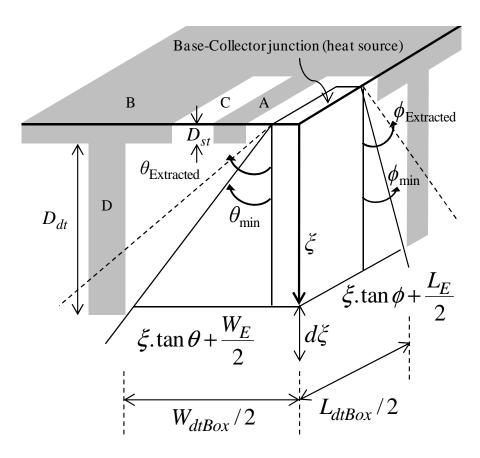

| 5.5.2 Pyramidal heat diffusion model                                                    | 179 |

| 5.5.2.1 Verification of the model with thermal TCAD simulations                         | 181 |

| 5.5.2.1.1 Numerical Z <sub>TH</sub> modeling                                            | 181 |

| 5.5.2.1.2 Numerical $\Delta T_J$ modeling                                               | 183 |

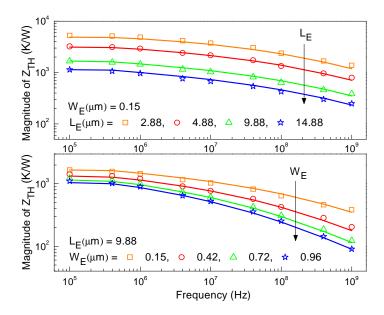

| 5.5.2.2 Verification of the model with low frequency s-parameter measurements           | 184 |

| $5.5.2.2.1$ $Z_{TH}$ modeling                                                           | 184 |

| 5.5.2.2.2 y-parameters modeling                                                         | 185 |

| 5 5 2 3 Advantage of the model                                                          | 186 |

|        | 5.5.2.4     | Convergence issues                                   | 186 |

|--------|-------------|------------------------------------------------------|-----|

|        | 5.5.2.5     | Limitations of the model                             | 187 |

| 5.6    | Applicat    | ions                                                 | 187 |

| 5.7    | Conclusi    | ion                                                  | 187 |

| 5.8    | Referenc    | :e:                                                  | 188 |

|        |             |                                                      |     |

| SUMM   | ARY OF T    | THE WORK                                             | 191 |

| Gen    | eral Conc   | lusion                                               |     |

| Pers   | spectives   |                                                      |     |

|        |             |                                                      |     |

| Appen  | ndix — A: 7 | Theoretical formulation                              | 199 |

| Appen  | dix – B: 2  | Z <sub>TH</sub> calculations from h and z parameters | 207 |

|        |             |                                                      |     |

| Public | ations      |                                                      | 213 |

# **Abstract**

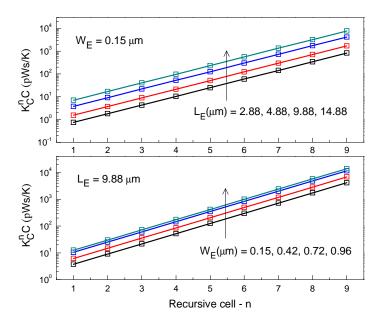

An extensive evaluation of different techniques for transient and dynamic electrothermal behavior of microwave SiGe:C BiCMOS hetero-junction bipolar transistors (HBT) and nano-scale metal-oxide-semiconductor field-effect transistors (MOSFETs) have been presented. In particular, new and simple approach to accurately characterize the transient self-heating effect, based on pulse measurements, is demonstrated. The methodology is verified by static measurements at different ambient temperatures, s-parameter measurements at low frequency region and transient thermal simulations. Three dimensional thermal TCAD simulations are performed on different geometries of the submicron SiGe:C BiCMOS HBTs with  $f_T$  and  $f_{max}$  of 230 GHz and 290 GHz, respectively. A comprehensive evaluation of device self-heating in time and frequency domain has been investigated. A generalized expression for the frequency-domain thermal impedance has been formulated and that is used to extract device thermal impedance below thermal cut-off frequency. The thermal parameters are extracted through transistor compact model simulations connecting electro-thermal network at temperature node. Theoretical works for thermal impedance modeling using different networks, developed until date, have been verified with our experimental results. We report for the first time the experimental verification of the distributed electrothermal model for thermal impedance using a nodal and recursive network. It has been shown that, the conventional single pole thermal network is not sufficient to accurately model the transient thermal spreading behavior and therefore a recursive network needs to be used. Recursive network is verified with device simulations as well as measurements and found to be in excellent agreement. Therefore, finally a scalable electro-thermal model using this recursive network is developed. The scalability has been verified through numerical simulations as well as by low frequency measurements and excellent conformity has been found in for various device geometries.

**Key words:** Hetero-junction bipolar transistors (HBTs), MOSFET, electrothermal effects, thermal resistance, thermal capacitance, thermal impedance, semiconductor device characterizations, pulse measurements, semiconductor device modeling, thermal TCAD simulation, scalable electrothermal model.

# Résumé

Ce travail de thèse présente une évaluation approfondie des différentes techniques de mesure transitoire et dynamique pour l'évaluation du comportement électro-thermique des transistors bipolaires à hétérojonctions HBT SiGe:C de la technologie BiCMOS et des transistors Métal-Oxyde-Semiconducteur à effet de champ (MOSFET) de la technologie CMOS 45nm. En particulier, je propose une nouvelle approche pour caractériser avec précision le régime transitoire d'auto-échauffement, basée sur des mesures impulsionelles. La méthodologie a été vérifiée par des mesures statiques à différentes températures ambiantes, des mesures de paramètres S à basses fréquences et des simulations thermiques transitoires. Des simulations thermiques par éléments finis (TCAD) en trois dimensions ont été réalisées sur les transistors HBTs de la technologie submicroniques SiGe: C BiCMOS. Cette technologie est caractérisée par une fréquence de transition f<sub>T</sub> de 230 GHz et une fréquence maximum d'oscillation f<sub>MAX</sub> de 290 GHz. Par ailleurs, cette étude a été réalisée sur les différentes géométries de transistor. Une évaluation complète des mécanismes d'auto-échauffement dans les domaines temporels et fréquentiels a été réalisée. Une expression généralisée de l'impédance thermique dans le domaine fréquentiel a été formulée et a été utilisé pour extraire cette impédance en deçà de la fréquence de coupure thermique. Les paramètres thermiques ont été extraits par des simulations compactes grâce au modèle compact de transistors auquel un modèle électro-thermique a été ajouté via le nœud de température. Les travaux théoriques développés à ce jour pour la modélisation d'impédance thermique ont été vérifiés avec nos résultats expérimentaux. Il a été montré que, le réseau thermique classique utilisant un pôle unique n'est pas suffisant pour modéliser avec précision le comportement thermique transitoire et donc qu'un réseau plus complexe doit être utilisé. Ainsi, nous validons expérimentalement pour la première fois, le modèle distribué électrothermique de l'impédance thermique utilisant un réseau nodal récursif. Le réseau récursif a été vérifié par des simulations TCAD, ainsi que par des mesures et celles ci se sont révélées en excellent accord. Par conséquent, un modèle électro-thermique multi-géométries basé sur le réseau récursif a été développé. Le modèle a été vérifié par des simulations numériques ainsi que par des mesures de paramètre S à basse fréquence et finalement la conformité est excellente quelque soit la géométrie des dispositifs.

**Mots-clefs :** Hétéro-transistors bipolaires (HBT), MOSFETs, effets électrothermiques, résistance thermique, capacité thermique, impédance thermique, caractérisations de semi-conducteurs, des mesures impulsionnelles, la modélisation de dispositifs semi-conducteurs, de simulation thermique TCAD, modèle électrothermique multi-gémoétries.

# Glossary

### Acronym and abbreviations:

ITRS International Technology Roadmap for Semiconductors

WiHDMI Wireless High-Definition Multimedia Interface CMOS Complementary metal—oxide—semiconductor

FET Field Effect Transistor

MOSFET Metal-Oxide Semiconductor Field Effect transistor

HBT Heterojunction Bipolar transistor

SiGe Silicon-Germanium

HEMT High electron mobility transistor WLAN Wireless local area network

TEM Transmission electron microscopy

HICUM High Current Model RF Radio Frequency

TCAD Technology Computer-Aided Design

NQS Non-quasi-static

SMU Source/monitor unit

PMU Pulse measurement units

GSG Ground – Signal – Ground

SOLT Short-Open-Load-Thru

VNA Vector network analyzer

### General notations:

$\lambda$  wavelength

$f_{\rm max}$  Maximum frequency of oscillation

$f_T$  Transit frequency  $L_G$  Gate length

$Z_{TH}$  Thermal impedance  $R_{TH}$  Thermal resistance  $C_{TH}$  Thermal capacitance  $A_E$  Emitter contactarea  $L_E$  Emitter contact length  $W_E$  Emitter contact width

Current Gain in common base configuration

Current Gain in common emitter configuration

$BV_{CB0}$  Base-collector breakdown voltage in common base configuration  $BV_{CE0}$  Base-collector breakdown voltage in common emitter configuration

$BV_{EB0}$  Emitter-base junction breakdown voltage

$C_{BC}$  Base-collector capacitance  $C_{BE}$  Base-emitter capacitance  $E_{C}$  Energy of conduction band

$E_G$  Energy gap between valance band and conduction band

$E_V$  Valance band energy  $g_m$  Transconductance

$I_B$  Base current

$I_C$  Collector current  $I_F$  Emitter current

J<sub>C</sub> Collector current density

$J_{CKirk}$  Collector current density due to the Kirk effect

k Boltzmann constant Effective mass of electron

$N_{ab}$  Doping concentration in the base

nIdeality factor of base-emitter junction $N_{dc}$ Doping concentration in collector $N_{de}$ Doping concentration in the base

$au_B$  Transit time in the base  $au_C$  Transit time in the collector

$\tau_{\scriptscriptstyle F}$  Transit time in the base-collector

$au_{F0}$  Base-collector transit time at zero current

$V_{BE}$  Applied base-emitter voltage  $V_{CB}$  Applied base-collector voltage  $V_{CBi}$  Intrinsic base-collector voltage

$V_{CE}$  Collector-emitter voltage

$v_{sat}$  Saturation velocity of electron

$egin{array}{lll} egin{array}{lll} egin{array}{lll} egin{array}{lll} egin{array}{lll} Electron thermal velocity \\ T_j & & & & & & & \\ T_{sub} & & & & & & & \\ P_{diss} & & & & & & \\ \Delta T & & & & & & \\ \end{array}$

$\lambda_{th}$  Specific heat conductance  $T_{amb}$  Ambient temperature  $\tau_{Thermal}$  Thermal time constant  $f_{Thermal}$  Thermal cut-off frequency

p Laplace variable

$T_B$  Base—plate temperatures  $L_{Cable}$  Coaxial cable inductance  $C_{Cable}$  Coaxial cable capacitance

$R_{cable}$ Coaxial cable resistance

$|Z|_{Cable}$ Coaxial cable characteristic impedance

Transient collector current  $I_C(t)$  $I_{C-ISO}$ Isothermal collector current  $Z_{trans}$ Transient state thermal impedance

$V_{GS}$ Gate-source voltage Drain-source voltage  $V_{DS}$

Drain current  $I_D$

Channel temperature  $T_{CH}$ Thermal conductivity κ Lattice heat capacity  $c_L$

Electron and hole quasi-Fermi potentials

$\phi_n$  and  $\phi_p$   $\mu_n$  and  $\mu_p$ Electron and hole nobilities

Lattice temperature  $T_{Lattice}$

Heat flux  $F_{Heat}$

# General introduction

Lower production cost and higher product complexity are key factors for the success of semiconductor and system integration companies. Volume market domination is more than ever related to low cost, high performance, and reliable products with very short development and production cycle time. Thus, a high level of innovation is mandatory if we want to succeed in this highly evolving and competitive world.

### A. Millimeter to THz waves and its application

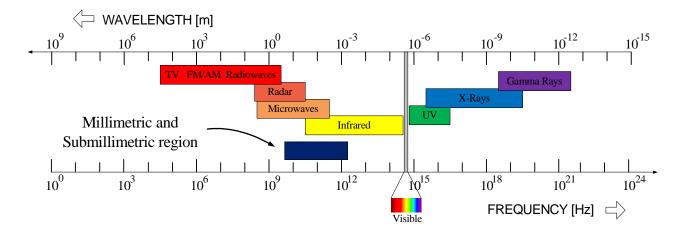

Millimeter and terahertz waves are the electro-magnetic waves like microwaves, radio waves, visible and infrared light (*Figure I*). Millimeter waves lie in the frequency region from  $30{\text -}300~\text{GHz}$  ( $\lambda = 1{\text -}10~\text{mm}$ ) and the terahertz waves, sometimes called sub-millimeter waves, lie in the region from 300 GHz to 3 THz ( $\lambda = 100~\mu\text{m}$  to 1 mm) [1]. However, in the context of wireless communication, the term Millimeter waves generally corresponds to a few bands of spectrum near 38, 60 and 94 GHz, and more recently to a band between 70 GHz and 90 GHz (also referred to as E-Band), that have been allocated for the purpose of wireless communication in the public domain [2].

Figure I: Millimeter and sub-millimeter wave range

The electromagnetic waves up to and including microwaves that have relatively low frequencies are generally unaffected by atmospheric effects. This has made them suitable for long-range radio communications such as television and radio broadcasting. In comparison, millimeter and terahertz waves suffer from attenuation caused by rain and resonant absorption in oxygen and water molecules, so they are unsuitable for long-range radio communications. However, their short wavelengths prove to be an advantage in the transmission of large amounts of data at one time. Millimeter and terahertz waves also provide high spatial resolution in imaging applications, in contrast to the low definition of microwave imaging. Moreover, in the terahertz region, it may be possible to detect molecular networks through weak inter molecule coupling, which could lead to the application of terahertz waves to protein analysis and drug discovery [1].

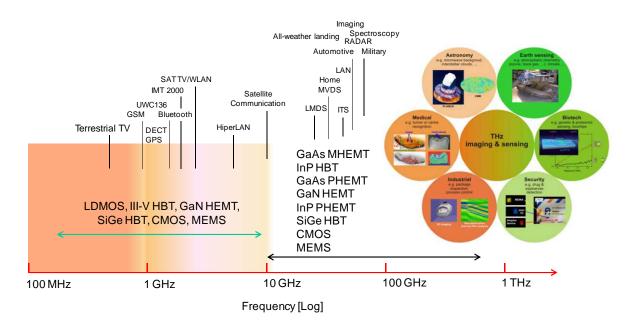

Figure II: Millimeter wave to THz frequency application; source[3], [4].

The evolution of these technologies is based on the ability of transistors to increase their performance. This is achieved by reducing the size of device and circuit which implies an increase in computing speeds. In modern integration technology, the down scaling of electronic device dimensions has been expected to be the main way to achieve better high frequency performance as seen by the International Technology Roadmap for Semiconductors (ITRS). The faster growth of RF wireless communications market requires the necessity of high performance device at low cost, because transistors fabricated on silicon offer ultra-large-scale integration capability and a high cut-off frequency. The requirement of high speed circuit performance has been addressed by miniaturization of device geometries and increased packaging densities. All these developments are opening up a wide spectrum of applications, from radar to automotive (77 GHz), wireless broad band network, WiHDMI (60 GHz) and range beyond 100 GHz [5]. This implies transistors capable of operating up to 0.5 THz. The applications being referred many of astronomy to biotechnology (biochip) in through the medical (identification of tumors or cavities) or safety (detection drugs or explosives). Over the past decades this downscaling has allowed the semiconductor industry to gain significant progress in high speed and also new circuit applications such as automotive radar, terahertz imaging, 100Gb/s data transfer etc. As seen by the technology roadmap, geometry scaling is anticipated to be the key technique to carry on this tendency.

# B. High frequency state of the art

Since the revolutionary invention of the transistor at Bell Laboratories in 1947, the progress made in the field of semiconductor technology have a constant increase in performance according to Moore' law which states that the number of transistors per chip doubles every 2 years [6]. Early 1950s, the transistors were made from germanium. However, the germanium-based transistor is not very reliable and does not work at very high temperature. Everything changed in 1954 when Texas Instruments announced the first silicon transistor. Ten years later, a silicon chip containing over 2000 transistors was fabricated. Today, the Quad Core Intel Itanium contains more than 1 billion transistors. This is an amazing and revolutionary progress of silicon technology.

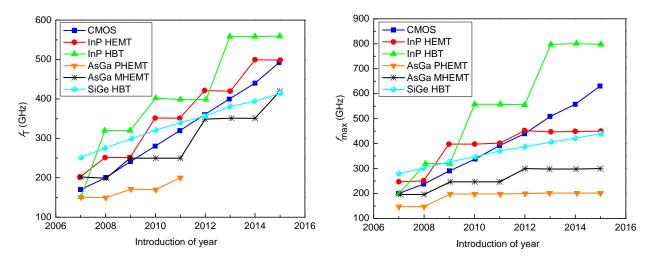

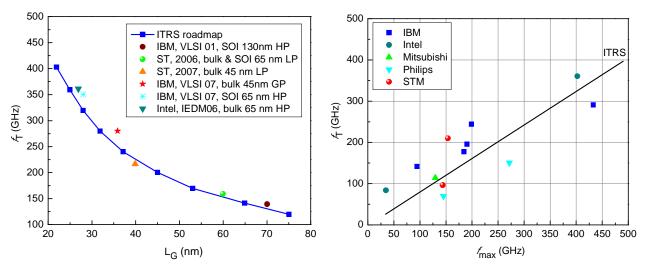

Figure III and Figure IV show the roadmap prescribed by the ITRS in terms of transit frequency ( $f_{\rm T}$ ) and maximum oscillation frequency ( $f_{\rm max}$ ) by comparing the silicon components (CMOS and SiGe HBT) and III-V (InP HEMT, InP HBT, GaAs and GaAs PHEMT and MHEMT).

Figure III: Evolution of transit frequency  $f_T$  with Figure IV: Evolution of maximum oscillation introduction of year for silicon and III-V frequency  $f_{max}$  with introduction of year for silicon technology; source [7], [8].

and III-V technology; source [7], [8].

In millimeter wave applications, the III-V technologies have dominated the silicon technologies for many years. Performances of silicon technologies are still lower than GaAs, PHEMT, InP and InP HBT HEMT. The electron mobility of silicon is lower, which limits the performance of the technology. However, advancement in silicon technology driven by high

performance digital applications offer advantages to the mm-wave designer [9]. Performance, quantified by  $f_{\rm T}$  and  $f_{\rm max}$  has dramatically increased with geometry scaling and technology enhancements in both CMOS and SiGe HBTs. Both CMOS and BiCMOS technologies have been used to demonstrate circuit functioning at frequencies in and above the K-band. Now, these silicon technologies are, by virtue of nanometer-scale design rules, able to implement staggering amounts of digital logic in a given area thereby enabling the on-chip integration of sophisticated control logic for performance tuning and/or digital signal processing [9]. Furthermore, the worldwide manufacturing capacity of silicon technologies driven by consumer applications like gaming and personal electronic appliances assures low-cost. This will certainly provide a boost for the evolution of mm-wave consumer applications. The combination of mm-scale wavelengths, low cost and the ability to integrate begs the consideration of array-based transceiver topologies being implemented on a single die or package.

Silicon HBT offer some advantages compared to CMOS devices such as lower  $1/f_{\text{noise}}$ , higher output resistance and higher voltage capability for a given speed [10]. The range of technologies on the market today offers HBTs with  $f_T > 200 \, \text{GHz}$  and sometimes  $f_{\text{max}} > 300 \, \text{GHz}$ . In 2006, the state of the art frequency performance ranged beyond 300 GHz. Indeed, Intel presented frequencies transition record of 360 GHz and 420 GHz  $f_T$  and  $f_{\text{max}}$  [11]. In 2005, IBM presented a transistor on SOI nFET with 290 and 450 GHz  $f_T$  and  $f_{\text{max}}$  [12] respectively. In 2010, IHP invented an HBT with a maximum oscillation frequency of 500 GHz under DOTFIVE project which is considered as the highest for SiGe devices till date. The follow up project DOTSEVEN is targeting the development of SiGe:C HBTs technologies with cut off frequencies  $f_{\text{max}}$  of around 700 GHz. This opens the door for terahertz (THz) applications.

Thus, the context of this thesis is part of the recent progress of millimeter range of components such as silicon MOSFETs on solid substrate ("bulk") and hetero-junction bipolar transistors (HBT) based SiGe: C.

### i. MOSFET technology

Micro and nano technologies tend towards the miniaturization of device to reach ultimate higher performances. The progress has been driven by the downscaling of the components in large-scale-integration. Since last 20 years CMOS became the technology of choice for general-

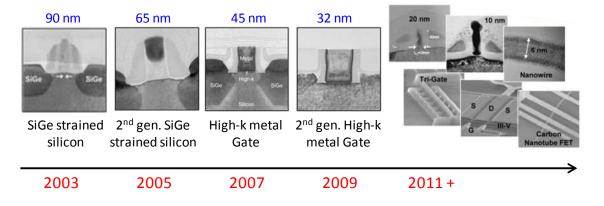

purpose integrated circuit applications. Advantages of CMOS technology are low static power consumption, simple laws of scalability, stability of operation and not only for digital circuits but also for analog and RF circuits. A large part of the success of the MOS transistor is due to the fact that it can be scaled to smaller dimensions, which results in higher performance. The ability to improve performance consistently while decreasing power consumption has made CMOS architecture the dominant technology for integrated circuits. The scaling of the CMOS transistor has been the primary factor driving improvements in microprocessor performance. Transistor delay times have decreased by more than 30% per technology generation resulting in a doubling of microprocessor performance every two years [13], [14]. In order to maintain this rapid rate of improvement, aggressive engineering of the source/drain and well regions is required. In *Figure V* Intel's commercial process technology is shown which employed 90 nm MOSFET in 2003 and recently reaches to below 32 nm dimension in 2011.

Figure V: Device scaling as projected by Intel; source [15], [16]

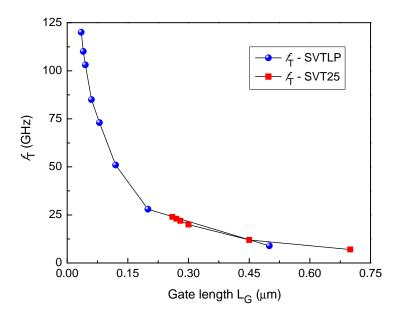

CMOS transistors follow the well-known Moore's Law of scaling, thus leading to always increasing functional integration. The physical gate length is reduced to shrink the CMOS device. For MOS device,  $f_T \propto 1/L_G$  ( $L_G$  = gate length) and as a first order approximation, is independent of the gate oxide thickness [17].  $f_T$  as high as above 350GHz are reached in the 65nm node of Intel's high power (HP) devices. Collected  $f_T$  data with  $L_G$  scaling from several major semiconductor foundries show good conformity with the ITRS road map as shown in Figure VI.

Figure VI:  $f_T$  with gate length  $L_G$  - ITRS road-map Figure VII:  $f_T$  -  $f_{max}$ : ITRS road-map and several and several foundries' performances; source [9]. foundries' performances; source [7], [8].

### ii. SiGe BiCMOS technology

High-performance silicon-germanium (SiGe) technology already addresses the demands of high frequency transceivers for millimeter wave applications [18]. The rapid technology development has made SiGe being a feasible alternative to III-V compound semiconductors for many microwave and millimeter-wave applications [19]. The development of SiGe Heterojunction bipolar transistor (HBT) has progressed rapidly in recent years. In terms of  $f_T$  and  $f_{max}$ , SiGe HBTs have advanced from 100 GHz of a few years ago to today's 300 GHz and beyond in several research laboratories as described in *Figure VIII*.

BiCMOS technology is the combination of Bipolar and CMOS technology [20], [21]. Bipolar technology provides high switching speed and good noise performance. On the other hand, CMOS technology offers less power dissipation and higher packaging density. Following both bipolar and CMOS technology, BiCMOS technology achieve improved speed over CMOS and lower power dissipation than bipolar. The introduction of Silicon-Germanium (SiGe) in the base region of silicon-based bipolar transistors offers improved overall performance at higher operating frequencies. SiGe BiCMOS technology features important advantages such as [22]:

- (i) inherently high forward current gain,

- (ii) homogeneous high integration of bipolar transistors and CMOS,

- (iii) power saving due to a higher transit frequency ( $f_T$ ) allowing a lower bias current for a given gain at a given frequency, and

- (iv) lower noise figure and high linearity.

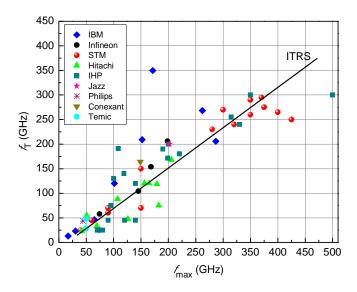

Figure VIII:  $f_{max}$  and the associated  $f_T$  data for selected SiGe HBT vendors; source [19].

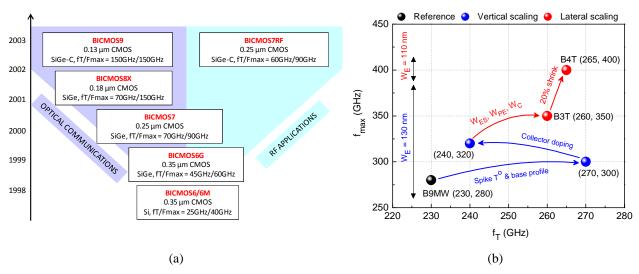

The first STMicroelectronics technology capable of addressing the mm-wave domain was BiCMOS9 [23]. The 120-nm SiGe BiCMOS9 process offers a quasi self-aligned (QSA) 160 GHz  $f_T/f_{max}$  Si/SiGeC HBT, dual  $V_T$  (high performance / low leakage) and dual gate oxide (1.2 V / 2.5 V) 120-nm CMOS devices, passives and a 6-level copper back-end. This BiCMOS9 technology was mainly developed for optical networking and wireless applications up to 40 Gb/s - 40 GHz, and is the most advanced high-speed SiGe BiCMOS technology currently in production at STMicroelectronics. However, higher device performance is required to meet the needs of circuits operating at frequencies > 50 GHz and targeting 77 GHz automotive radars, 60 GHz WLAN, 100 Gb/s optical communications or non-intrusive imaging technologies [24], [25]. A new technology of STMicroelectronics, 120-nm SiGe BiCMOS9MW [26], is dedicated to millimeter-wave applications. The SiGe BiCMOS9MW has a 230-GHz  $f_T$  / 280-GHz  $f_{max}$  HBT, which is achieved with a fully self-aligned (FSA) architecture using selective epitaxial growth of the base. The device features record low minimum noise figures: NF<sub>min</sub> of 1.2 dB at 40 GHz and 1.6 dB at 60 GHz. This BiCMOS9MW technology is mainly intended for 60-GHz WLAN, 77-

GHz automotive radars and 80-Gb/s optical communications. The main characteristics of the technology are summarized in *TABLE I*.

TABLE I

ST Microelectronics 120-nm high-speed SiGe BiCMOS technologies; source: [26]

| Technology Targets       | BiCMOS9 BiCMOS9MW                                             |         | DS9MW                                  |     |  |

|--------------------------|---------------------------------------------------------------|---------|----------------------------------------|-----|--|

| CMOS                     | $T_{OX} = 20 \text{ nm (GO1)} / T_{OX} = 50 \text{ nm (GO2)}$ |         |                                        |     |  |

| (NMOS & PMOS)            | High & Low $V_T$ (mV)                                         |         |                                        |     |  |

| N: 120nm/1.2V (GO1)      | 450                                                           | 340     | 450                                    | 340 |  |

| P: 120nm/1.2V (GO1)      | 395                                                           | 300     | 395                                    | 300 |  |

| N: 280nm/2.5V (GO2)      | 430                                                           | 140     | 430                                    | 140 |  |

| P: 280nm/2.5V (GO2)      | 485                                                           | 180     | 485                                    | 180 |  |

| Si/SiGe:C HBT            | QSA structure (W <sub>E</sub> =170 nm)                        |         | FSA structure (W <sub>E</sub> =120 nm) |     |  |

| $f_T$ (GHz)              | 16                                                            | 160 230 |                                        | 30  |  |

| $f_{max}$ (GHz)          | 160                                                           |         | 28                                     | 280 |  |

| $BV_{CEO}$ (V)           | 1.                                                            | 1.8     |                                        | .6  |  |

| BEOL (Cu)                | 6ML                                                           | + Al    | l 6ML + Al                             |     |  |

| thin / thick Cu layers   | 5 / 1                                                         |         | 3 / 3                                  |     |  |

| $\alpha @ 80GHz (dB/mm)$ | 1.2                                                           |         | 0.5                                    |     |  |

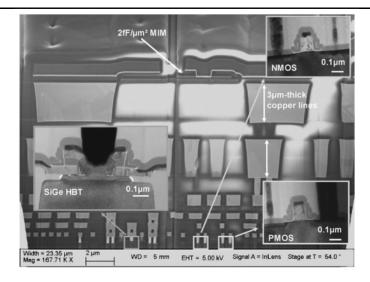

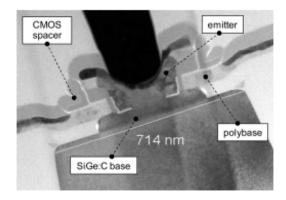

Figure IX: SEM cross-section of the technology (BiCMOS process and device features) with thick-copper back-end, MIM capacitor and TEM pictures of the HBT and MOSFETs; source: [27], [28].

STMicroelectronics developments within DOTFIVE project [29] are based on a state-of-the-art 130nm SiGe BiCMOS technology optimized for very high frequency applications [27]. As shown in *Figure IX*, this technology includes a dedicated copper metallization scheme with two 3 $\mu$ m thick levels to minimize signal attenuation at mm-wave frequencies ( $\alpha \sim 0.6$ dB/mm at 80GHz). Figure shows a cross-sectional view of the technology showing the three active devices, the MIM capacitor and the back-end interconnections.

In *Figure X*, the roadmap of ST BiCMOS process technologies is shown. *Figure X* (*b*) summarizes the various steps in the optimization of high speed SiGe HBT performances from BiCMOS9MW (230-GHz  $f_T$  / 280-GHz  $f_{max}$ ) to B3T (260-GHz  $f_T$  / 350-GHz  $f_{max}$ ) and B4T (265-GHz  $f_T$  / 400-GHz  $f_{max}$ ) [27].

Figure X: Different BICMOS process technology developed by ST microelectronics – (a) roadmap of ST BiCMOS process; source [30], (b) from BiCMOS9MW to B3T and B4T technology; source [27].

# C. Power density and thermal phenomena

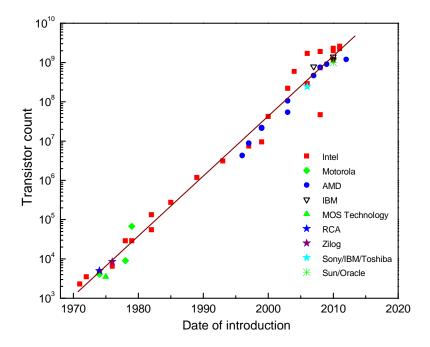

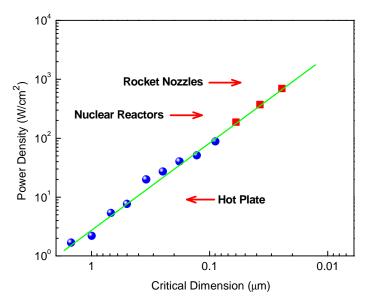

Ever increasing demand for faster microprocessors and the continuous trend to pack more transistors on a single chip (*Figure XI*) have resulted in an unprecedented level of power dissipation [16]. Moreover, power density of the transistor increases noteworthy due to the geometry shrinking. In *Figure XII*, the evolution of power density with critical device dimension of Intel's transistor is shown.

*Figure XI: Transistor count per chip with introduction of year; source [7], [16].*

The following well-known Moore's law, the improved device integration pursued in order to support high current capability, has led to a steady increase in power density [31–34]. This significantly contributes to even higher device and system operational temperature. Thermal phenomena influence the electrical functionality and performance of semiconductor devices and also adversely affect their reliability. The major thermally-induced reliability concerns for transistors are [16]:

- (i) degradation of device electrical characteristics due to heating effects,

- (ii) stresses due to different rates of thermal expansion of transistor constituents, and

(iii) failure of metallic interconnects due to diffusion or flows of atoms along a metal interconnect in the presence of a bias current, known as the electro-migration phenomenon.

Self-heating of the device reduces electron mobility and results in a poor performance of these devices.

Figure XII: Evolution of the average power with critical dimension of device; source[16], [49], [50].

In microwave applications, SiGe Heterojunction Bipolar Transistors (HBTs) play an important role due to their high linearity and ability to operate at high current densities. Advanced device performance is mainly achieved with shrinking of device dimensions and by improving the device architecture. The high performances bipolar technology requires good device isolation. Structural innovation has contributed to reduce the parasitic elements and to decrease the transit time by introducing shallow trench, deep trench and other technological process steps [35–37]. The major improvements are: (i) parasitic capacitances are reduced by introducing deep trench and shallow trench isolation. The drawback is that, due to lower thermal conductivity of  $SiO_2$  trench wall, the heat flow is confined and resulting larger thermal impedance ( $Z_{TH}$ ) [38–46]. (ii) In order to boost the transit frequency, a lot of attention is paid to a careful design of the BC junction and the EPI-collector. It permits to push the Kirk-effect to higher current densities leading to higher transit frequency  $f_T$  on the one hand, but on the other hand to lower breakdown voltages with a minimum value of above 1V for ultimately scaled

devices [47]. Finally, it shifts the operating point to higher current densities [48]. Therefore temperature rise induced by the power consumption of devices increase significantly in high power application and thus heat dissipation, the source of heat increase, becomes a major issue to confront. Both aspects for the increase of device performances result in a more pronounced self-heating effect. In a bipolar transistor self-heating occurs mainly in the base-collector depletion region, where both the current and field are high. This can produce negative output impedance, a shift in DC characteristic, as well as concerns about device stability and reliability.

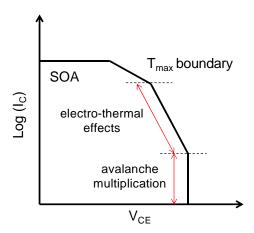

In bipolar technology, a device operating point is essential due to the thermal reliability issue. A transistor Safe Operating Area (SOA) is limited by various breakdown mechanisms [34], [51–54]. According to the *Figure XIII*, the first breakdown is caused by avalanche multiplication that is the multiplication of the carriers in the space charge region. The second breakdown is caused by electro-thermal effects and impact ionization. Following the *Figure XIII*, maximum device temperature ( $T_{max}$ ) boundary is limited by SOA. This SOA is minimized with increase of current density i.e., device down-scaling. The increase in power density leads to higher operating temperature. The temperature rise  $\Delta T$  in a bipolar device can be given by,

$$\Delta T = R_{TH} \cdot A_E \cdot J_C \cdot V_{CE}$$

Eq. 1

where,  $R_{TH}$ ,  $A_E$ ,  $J_C$  and  $V_{CE}$  are the thermal resistance, emitter area, current density and collectoremitter voltage respectively. Following the  $Eq.\ 1$ , the higher current density due to down scaling issue is the cause of device temperature increase.

Figure XIII: Transistor safe operating area due to avalanche multiplication and electro-thermal effect; source [34].

## D. Motivation

Thermal issue is one of the key factors limiting the performance and reliability of the devices and integrated circuits. Consequently, realistic thermal compact modeling is strongly mandatory in order to obtain accurate simulation results taking into account the intrinsic operating temperatures. The excessive temperature has underscored the need of thermal effect characterization in device compact models. An accurate determination of the device thermal impedance is required to specify operating temperature. Characterization of thermal phenomena is necessary for thermal stability and reliability analysis for modern bipolar circuits design. Moreover, the thermal compact model must also be valid up to the RF range. The electrical behavior is also influenced by the dynamic variations of junction temperature [55] which can have significant impact on third-order intermodulation products generated near the thermal time constant due to the nonlinearity of the device [56]. Therefore, the characterization and modeling of self-heating in electronic devices remains a major research issue associated with the advancement of technology.

It is obvious from the previous discussion that, the self-heating can cause major changes in the device operation when there are considerable temperature rise. In general the extractions of compact model parameters are usually based on steady-state measurements at a single ambient temperature. But, transistor junction (HBT) or channel (MOSFET) temperature rises due to self-heating during the measurements. The resulting steady-state measurements compose a temperature dependent characterization. Therefore, the predictive ability of the compact model could be restricted if the final operating point and thermal environment differ from the one in which the device was characterized. Also, the unphysical nature of extracted parameters can make it difficult to develop a scalable model. The absence of such a scalable model is a significant restriction in the development of analog circuits. Not only the self-heating is important to integrated circuit designers, but it is also dominant concern for the reliability engineers because device operation at high temperatures results a shorter device lifetime. The knowledge of self-heating is needed to extrapolate the statistical estimation of device lifetime.

# E. Thesis organization

The thesis is organized as follows:

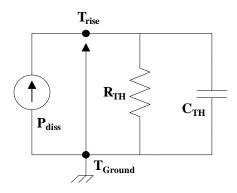

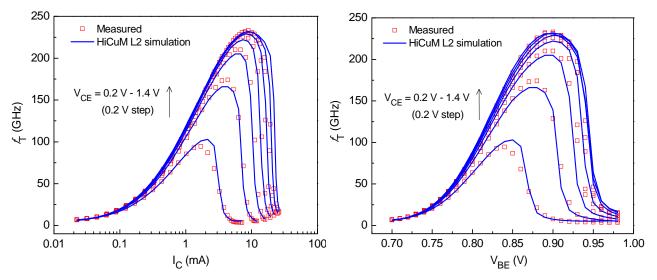

Chapter 1: Self-heating and device compact modeling - This chapter demonstrates a general overview of self-heating effect in electronic device and a short description on different analytical models, presented in literatures. Transistor compact model has been discussed in brief. The compact model has been verified by static and dynamic measurements.

Chapter 2: Characterization of SiGe:C BiCMOS HBTs - This chapter provides an extensive evaluation of self-heating in microwave SiGe:C BiCMOS HBTs through DC, pulse and low frequency s-parameter measurements. Different methodologies have been applied in order to evaluate steady state, transient and dynamic thermal behavior of the device. Thermal parameters are extracted with HiCuM L2 simulations using different electro-thermal networks at temperature node.

*Chapter 3: Characterization of nano-metric MOSFETs* - In this chapter, we present the self-heating characterization of nano-metric CMOS technology through DC measurements, pulse measurements and, DC and pulse RF measurements.

Chapter 4: 3D thermal TCAD simulations - This chapter discussed about 3D thermal simulations. TCAD simulations are performed in order to investigate the transient and the dynamic behavior of the device temperature in dependence of the device architecture and material properties. The structure of the transistors is same as the measured one, submicron SiGe:C BiCMOS HBTs.

Chapter 5: Results validations, scalable approach and applications - This chapter presents a comparison of thermal parameters extracted from different measurements and device simulations. A scalable model has been proposed for transient self-heating modeling in trench isolated Si-Ge HBTs. This model has been verified through numerical simulations as well as low frequency s-parameter measurements and found to be in excellent agreement for various device geometries.

# F. Project description

This work is the part of DOTFIVE project (BiCMOS HBT) and MIRENDELA project (45 nm CMOS).

**DOTFIVE** [4], [57]: This is an ambitious three-year (2008 to 2010) European project supported by the European Commission through the Seventh Framework Program for Research and Technological Development, focused on advanced Research, Technology, and Development activities necessary to move the SiGe-HBT into the operating frequency range of 0.5 THz (500 GHz). This high frequency performance is currently only possible with more expensive technology based on III-V semiconductors, making high integration and functionality for large volume consumer applications difficult. The new transistors developed by DOTFIVE will be used for designing circuits enabling power efficient millimeter-wave applications such as automotive radar (77 GHz) or WLAN communications systems (60 GHz -Wireless Local Area Network). In addition to these already evolving markets, DOTFIVE technology sets out to be a key enabler for silicon based millimeter-wave circuits with applications in the security, medical and scientific areas. A higher operating speed can open up new application areas at very high frequencies, or can be traded for lower power dissipation, or can help to reduce the impact of process, voltage and temperature. The project involves 15 partners (University of Naples-Italy, ST Microelectronics-France, IMEC Microelectronics-Belgium, IMS-University of Bordeaux 1-France and Bundeswehr University Munich-Germany.) from industry and academia in five countries teaming up for research and development work on silicon-based transistor architectures, device modeling, and circuit design.

MIRANDELA [58], [59]: This is a research project within the ENIAC - Technology Platform. The project aims to the MIllimetre-wave and Radio-frequency integrAtion in Nanoelectronics CMOS Platforms for MoDErn WireLess 5A Communications. Starting from core CMOS nodes, specific works will be conducted in order to offer a silicon technology platform adequate for the development of modern wireless communication applications. They can be "labeled" as 5A communications: Anything to be transferred from/to Anybody located Anywhere at Anytime using the most appropriate physical path from Any-path available between the sender and the recipient based on performance and/or economical considerations. A significant effort will be devoted to the architecture of RF and millimeter-wave functions. In addition to traditional analog

RF design, there are several new ideas that will be eventually deployed in such a technology node: millimeter-wave design in pure CMOS, RF design at very low power consumption, auto calibration of RF functions, etc. The capability of these technologies will be demonstrated through the development of mixed signal very low power RF circuits to be used for autonomous reconfiguration and communication nodes supporting for multiple RF air interface protocols.

Starting from a standard CMOS technology node (e.g. 32nm to be shrunk to 28nm), the project intend to derive a technology and design platform for the integration of analog, RF and MMW components, blocks and functions together with the digital base-band on a same chip in order to address the very promising mobile communication market as indicated by the evolution of the smart phone sales. Our view of the next generations of mobiles phone is on one hand the low cost market of emerging countries and the evolution to very sophisticated smart phone able to replace PC, TV, video recorder, video storage and much more devices all in a pocket. To address such markets we need to integrate more function on the same chip for production cost consideration for low end products that will anyway propose more communication paths (2G, Bluetooth) or for high end products where High Data Rates are mandatory for large file transfers (picture, personal of commercial video for instance).

# G. Technology under analysis

In this work, transistors with two different technologies are taken for self-heating analysis.

#### **❖** SiGe BiCMOS9MW HBT

The analyzed device is SiGe NPN HBTs. The transistors are fabricated within the ST Microelectronics with SiGe BiCMOS9MW technology, which is a quasi self-aligned trench isolated technology. The key figures of this technology are: breakdown voltage, BVCEO = 1.6 V, BVCBO = 5.5 V, transit frequency ( $f_T$ ) = 230 GHz and maximum oscillation frequency ( $f_{max}$ ) = 290 GHz. A TEM cross-section of the BiCMOS9MW HBT is shown in *Figure XIV*.

Figure XIV: TEM picture of BiCMOS9MW self-aligned SiGe HBT; source: [27].

The device (taken for characterization) specification: (i) the maximum safe operating range: collector – emitter voltage ( $V_{CE}$ ) = 1.5 V and base – emitter voltage ( $V_{BE}$ ) = 0.05 V; (ii) the dimensions of the drawn emitter window:  $L_E \times W_E (\mu m^2) = 3 \times 0.27$ , 5 x 0.27, 10 x 0.27, 15 x 0.27, 10 x 0.54, 10 x 0.84 and 10 x 1.08; and (iii) transistor configuration: CBE (1 emitter, 1 base and 1 collector) and CBEBC (1 emitter, 2 base and 2 collector).

#### **❖** CMOS 045 MOSFET

In this work, CMOS045 (SVT25 / SVTLP) RF MOS technologies are characterized. The device specification: (i) the maximum safe operating range: for SVT25 RF MOS, drain – source voltage ( $V_{DS}$ ) = 2.5 V and gate – source voltage ( $V_{GS}$ ) = 2.5 V; for SVTLP RF MOS,  $V_{DS}$  = 1.2 V and  $V_{GS}$  = 1.2 V (ii) transistor configuration: SVT25 transistors are with10 fingers (finger width = 3  $\mu$ m) with 4 MOS parallel and SVTLP transistors are with10 fingers (finger width = 2

$\mu$ m) with 6 MOS parallel. The total gate width (W<sub>G</sub>) = 120  $\mu$ m for both SVT25 and SVTLP. The transit frequency  $f_T$  with L<sub>G</sub> is given in *Figure XV*. The  $f_T$  is extracted at 10 GHz frequency (not deembeded).

Figure XV: Measured (extracted at 10 GHz frequency)  $f_T$  with gate length  $L_G$ .

# H. Reference

- [1] Naoya Kukutsu and Yuichi Kado, "Overview of Millimeter and Terahertz Wave Application Research," NTT Microsystem Integration Laboratories Atsugi-shi, 243-0198 Japan.

- [2] S. O. Iakushev, S. I. Petrov, I. A. Sukhoivanov, J. A. A. Lucio, A. Garcia Perez, and O. Ibarra-Manzano, "Omnidirectional multilayer mirrors for 60-GHz-band," in *Laser and Fiber-Optical Networks Modeling (LFNM)*, 2011 11th International Conference on, 2011, pp. 1–3.

- [3] Dr. W.Klingenstein, "Technology Roadmap for Semiconductors," Infineon Technologies AG, 2002.

- [4] O. R.-A. C. Group, "Dotfive." [Online]. Available: http://www.dotfive.eu/.

- [5] A. Cathelin, B. Martineau, N. Seller, S. Douyere, J. Gorisse, S. Pruvost, C. Raynaud, F. Gianesello, S. Montusclat, S. P. Voinigescu, A. M. Niknejad, D. Belot, and J. P. Schoellkopf, "Design for millimeter-wave applications in silicon technologies," in *Solid State Circuits Conference*, 2007. *ESSCIRC* 2007. 33rd European, 2007, pp. 464–471.

- [6] Wolfgang Arden, Michel Brillouët, Patrick Cogez, Mart Graef, Bert Huizing, and Reinhard Mahnkopf, "More-than-Moore." [Online]. Available: http://www.itrs.net/Links/2010ITRS/IRC-ITRS-MtM-v2%203.pdf.

- [7] Nicolas WALDHOFF, "Caractérisations et modélisations des technologies CMOS et BiCMOS de dernières générations jusque 220 GHz," L'UNIVERSITE DE LILLE 1 SCIENCES ET TECHNOLOGIES Ecole Doctorale Sciences Pour l'Ingénieur, 2009.

- [8] "International Technology Roadmap for Semiconductors:Reports and Ordering Information." [Online]. Available: http://www.itrs.net/reports.html.

- [9] Andreia Cathelin and John J. Pekarik, "Silicon Technologies to Address mm-Wave Solutions," in *mm-Wave Silicon Technology 60 GHz and Beyond*, 2008 Springer Science+Business Media, LLC.

- [10] Ali M. Niknejad and Hossein Hashemi (Eds.), *mm-Wave Silicon Technology* 60 GHz and Beyond. Springer Science+Business Media, LLC, 2008.

- [11] I. Post, M. Akbar, G. Curello, S. Gannavaram, W. Hafez, U. Jalan, K. Komeyii, J. Lin, N. Lindert, J. Park, J. Rizk, G. Sacks, C. Tsai, D. Yeh, P. Bai, and C.-H. Jan, "A 65nm CMOS SOC Technology Featuring Strained Silicon Transistors for RF Applications," in *Electron Devices Meeting*, 2006. *IEDM '06. International*, 2006, pp. 1–3.

- [12] S. Lee, B. Jagannathan, S. Narasimha, A. Chou, N. Zamdmer, J. Johnson, R. Williams, L. Wagner, J. Kim, J.-O. Plouchart, J. Pekarik, S. Springer, and G. Freeman, "Record RF performance of 45-nm SOI CMOS Technology," in *Electron Devices Meeting*, 2007. IEDM 2007. IEEE International, 2007, pp. 255 –258.

- [13] S. Thompson, M. Alavi, M. Hussein, P. Jacob, C. Kenyon, P. Moon, M. Prince, S. Sivakumar, S. Tyagi, and M. Bohr, "130nm Logic Technology Featuring 60nm Transistors, Low-K Dielectrics and Cu Interconnects," *Intel Technology Journal*, vol. 6, no. 2.

- [14] Scott Thompson, Paul Packan, and Mark Bohr, "MOS Scaling: Transistor Challenges for the 21st Century," *Intel Technology Journal Q3'98*.

- [15] M. Bohr and K. Mistry, "Intel's Revolutionary 22 nm Transistor Technology," May-2011.

- [16] D. Vasileska, K. Raleva, and S. Goodnick, "Modeling heating effects in nanoscale devices: the present and the future," *Journal of Computational Electronics*, vol. 7, no. 2, pp. 66–93, 2008.

- [17] A. Cathelin, B. Martineau, N. Seller, F. Gianesello, C. Raynaud, and D. Belot, "(INVITED) Deep-submicron digital CMOS potentialities for millimeter-wave applications," in *Radio Frequency Integrated Circuits Symposium*, 2008. RFIC 2008. IEEE, 2008, pp. 53–56.

- [18] V. Jain, F. Tzeng, L. Zhou, and P. Heydari, "A Single-Chip Dual-Band 22-29-GHz/77 -81-GHz BiCMOS Transceiver for Automotive Radars," *Solid-State Circuits, IEEE Journal of*, vol. 44, no. 12, pp. 3469 –3485, Dec. 2009.

- [19] Yinggang Li, Harald Jacobsson, Mingquan Bao, and Thomas Lewin, "High-frequency SiGe MMICs an Industrial Perspective (Invited)," Ericsson AB, Ericsson Research, MHSERC, SE-43184 Mölndal, Sweden.

- [20] A. R. Alvarez, BiCMOS Technology and Applications. Springer, 1993.

- [21] "BiCMOS Process Technology," *Institute for microelectronics, Faculty of Electrical Engineering and Information Technology.* [Online]. Available: http://www.iue.tuwien.ac.at/phd/puchner/node47\_app.html.

- [22] A European Commission co-funded Research Project, "SiGe BiCMOS technology," *The C3PO Project: Colourless and Coolerless Components for low Power Optical Networks.* [Online]. Available: http://www.greenc3po.eu/index.php/sige-bicmos-technology.

- [23] M. Laurens, B. Martinet, O. Kermarrec, Y. Campidelli, F. Deleglise, D. Dutarte, G. Troillard, D. Gloria, J. Bonnouvrier, R. Beerkens, V. Rousset, F. Leverd, A. Chantre, and A. Monroy, "A 150GHz f<sub>T</sub>/f<sub>max</sub> 0.13 mu;m SiGe:C BiCMOS technology," in *Bipolar/BiCMOS Circuits and Technology Meeting*, 2003. *Proceedings of the*, 2003, pp. 199 202.

- [24] B. A. Orner, M. Dahlstrom, A. Pothiawala, R. M. Rassel, Q. Liu, H. Ding, M. Khater, D. Ahlgren, A. Joseph, and J. Dunn, "A BiCMOS Technology Featuring a 300/330 GHz (fT/fmax) SiGe HBT for Millimeter Wave Applications," in *Bipolar/BiCMOS Circuits and Technology Meeting*, 2006, 2006, pp. 1–4.

- [25] H. Riicker, B. Heinemann, R. Barth, J. Bauer, D. B. K. Blum, D. Bolze, J. Drews, G. G. Fischer, A. Fox, O. Fursenko, T. Grabolla, U. Haak, W. Hoppner, D. Knoll, K. Kopke, B. Kuck, A. Mai, S. Marschmeyer, T. Morgenstern, H. H. Richter, P. Schley, D. Schmidt, K. Schulz, B. Tillack, G. Weidner, W. Winkler, D. Wolansky, H.-E. Wulf, and Y. Yamamototo, "SiGe BiCMOS Technology with 3.0 ps Gate Delay," in *Electron Devices Meeting*, 2007. IEDM 2007. IEEE International, 2007, pp. 651 –654.

- [26] P. Chevalier, B. Barbalat, M. Laurens, B. Vandelle, L. Rubaldo, B. Geynet, S. P. Voinigescu, T. O. Dickson, N. Zerounian, S. Chouteau, D. Dutartre, A. Monroy, F. Aniel, G. Dambrine, and A. Chantre, "High-Speed SiGe BiCMOS Technologies: 120-nm Status and End-of-Roadmap Challenges," 2007, pp. 18–23.

- [27] A. Chantre, P. Chevalier, T. Lacave, G. Avenier, M. Buczko, Y. Campidelli, L. Depoyan, L. Berthier, and C. Gacquière, "Pushing conventional SiGe HBT technology towards 'Dotfive' terahertz," in *Microwave Integrated Circuits Conference (EuMIC)*, 2010 European, 2010, pp. 21–24.

- [28] G. Avenier, P. Chevalier, G. Troillard, B. Vandelle, F. Brossard, L. Depoyan, M. Buczko, S. Boret, S. Montusclat, A. Margain, S. Pruvost, S. T. Nicolson, K. H. K. Yau, D. Gloria, D. Dutartre, S. P. Voinigescu, and A. Chantre, "0.13μm SiGe BiCMOS technology for mm-wave applications," in *Proceedings of the IEEE Bipolar/BiCMOS Circuits and Technology Meeting*, 2008, pp. 89–92.

- [29] "Towards 0.5 TeraHertz Silicon / Germanium Heterojunction bipolar technology," *Dotfive Project*. [Online]. Available: http://www.dotfive.eu/.

- [30] "STMicroelectronics Deep Sub-Micron Processes 0.18µ, 0.12µ, 90nm CMOS," 13-Jan-2006.

- [31] G. E. Moore, "Cramming More Components Onto Integrated Circuits," *Proceedings of the IEEE*, vol. 86, no. 1, pp. 82 –85, Jan. 1998.

- [32] G. E. Moore, "Cramming more components onto integrated circuits, Reprinted from Electronics, volume 38, number 8, April 19, 1965, pp.114 ff.," *Solid-State Circuits Newsletter, IEEE*, vol. 20, no. 3, pp. 33 –35, Sep. 2006.

- [33] E. Pop, S. Sinha, and K. E. Goodson, "Heat Generation and Transport in Nanometer-Scale Transistors," *Proceedings of the IEEE*, vol. 94, no. 8, pp. 1587 –1601, Aug. 2006.

- [34] J. P. Nowakowski, "Development of a new electro-thermal simulation tool for RF circuits," Università degli Studi di Napoli "Federico II," Napoli, Italie, 2008.

- [35] D. L. Harame, J. H. Comfort, J. D. Cressler, E. F. Crabbe, J. Y.-C. Sun, B. S. Meyerson, and T. Tice, "Si/SiGe epitaxial-base transistors. I. Materials, physics, and circuits," *IEEE Transactions on Electron Devices*, vol. 42, no. 3, pp. 455–468, Mar. 1995.

- [36] D. L. Harame, J. H. Comfort, J. D. Cressler, E. F. Crabbe, J. Y.-C. Sun, B. S. Meyerson, and T. Tice, "Si/SiGe epitaxial-base transistors. II. Process integration and analog applications," *IEEE Transactions on Electron Devices*, vol. 42, no. 3, pp. 469–482, Mar. 1995.

- [37] M. Forsberg, C. Bormander, T. Johansson, T. Ko, W. Liu, M. Vellaikal, and A. Cheshire, "Shallow and Deep Trench Isolation for use in RF-Bipolar IC:s," in *Solid-State Device Research Conference*, 2000. Proceeding of the 30th European, 2000, pp. 212–215.

- [38] D. J. Walkey, T. J. Smy, D. Marchesan, H. Tran, and M. Schröter, "A scalable thermal model for trench isolated bipolar devices," *Solid-State Electronics*, vol. 44, no. 8, pp. 1373–1379, Aug. 2000.

- [39] D. J. Walkey, T. J. Smy, C. Reimer, M. Schröter, H. Tran, and David Marchesan, "Modeling thermal resistance in trench-isolated bipolar technologies including trench heat flow," *Solid-State Electronics*, vol. 46, no. 1, pp. 7–17, Jan. 2002.

- [40] I. Marano, V. d' Alessandro, and N. Rinaldi, "Analysis of the thermal behavior of trench-isolated bipolar transistors fabricated on SOI substrates," in *International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Micro-Systems, 2008. EuroSimE 2008*, 2008, pp. 1–7.

- [41] I. Marano, V. d' Alessandro, and N. Rinaldi, "Effectively modeling the thermal behavior of trenchisolated bipolar transistors," in *International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Micro-Systems, 2008. EuroSimE 2008*, 2008, pp. 1–8.

- [42] T. Vanhoucke and G. A. . Hurkx, "A new analytical model for the thermal resistance of deep-trench bipolar transistors," *IEEE Transactions on Electron Devices*, vol. 53, no. 6, pp. 1379–1388, Jun. 2006

- [43] J.-S. Rieh, J. Johnson, S. Furkay, D. Greenberg, G. Freeman, and S. Subbanna, "Structural dependence of the thermal resistance of trench-isolated bipolar transistors," in *Bipolar/BiCMOS Circuits and Technology Meeting*, 2002. *Proceedings of the 2002*, 2002, pp. 100–103.

- [44] A. R. Reid, T. C. Kleckner, M. K. Jackson, D. Marchesan, S. J. Kovacic, and J. R. Long, "Thermal resistance in trench-isolated Si/SiGe heterojunction bipolar transistors," *IEEE Transactions on Electron Devices*, vol. 48, no. 7, pp. 1477–1479, Jul. 2001.

- [45] D. J. Walkey, T. J. Smy, D. Marchesan, Hai Tran, C. Reimer, T. C. Kleckner, M. K. Jackson, M. Schroter, and J. R. Long, "Extraction and modelling of thermal behavior in trench isolated bipolar structures," in *Bipolar/BiCMOS Circuits and Technology Meeting*, 1999. Proceedings of the 1999, 1999, pp. 97–100.

- [46] D. J. Walkey, T. J. Smy, H. Tran, D. Marchesan, and M. Schroter, "Prediction of thermal resistance in trench isolated bipolar device structures," in *Bipolar/BiCMOS Circuits and Technology Meeting*, 1998. Proceedings of the 1998, 1998, pp. 207–210.

- [47] M. Schroter, G. Wedel, B. Heinemann, C. Jungemann, J. Krause, P. Chevalier, and A. Chantre, "Physical and Electrical Performance Limits of High-Speed SiGeC HBTs—Part I: Vertical Scaling," *IEEE Transactions on Electron Devices*, vol. 58, no. 11, pp. 3687–3696, Nov. 2011.

- [48] G. Freeman, J.-S. Rieh, Z. Yang, and F. Guarin, "Reliability and performance scaling of very high speed SiGe HBTs," *Microelectronics Reliability*, vol. 44, no. 3, pp. 397–410, Mar. 2004.

- [49]"The ITRS and MOORE's Law." [Online]. Available: http://www.iue.tuwien.ac.at/phd/holzer/node11.html. [Accessed: 25-May-2012].

- [50] M. Pant, "Microprocessor Power Impacts, intel," Jun-2011.

- [51] N. Rinaldi and V. d' Alessandro, "Theory of electrothermal behavior of bipolar transistors: Part I single-finger devices," *Electron Devices, IEEE Transactions on*, vol. 52, no. 9, pp. 2009 2021, Sep. 2005.

- [52] N. Rinaldi and V. d' Alessandro, "Theory of electrothermal behavior of bipolar transistors: part II-two-finger devices," *Electron Devices, IEEE Transactions on*, vol. 52, no. 9, pp. 2022 2033, Sep. 2005.

- [53] N. Rinaldi and V. d' Alessandro, "Theory of electrothermal behavior of bipolar transistors: part III-impact ionization," *Electron Devices, IEEE Transactions on*, vol. 53, no. 7, pp. 1683 –1697, Jul. 2006.

- [54] H. A. Schafft, "Second breakdown #8212; A comprehensive review," *Proceedings of the IEEE*, vol. 55, no. 8, pp. 1272 1288, Aug. 1967.

- [55] R. T. Dennison and K. M. Walter, "Local thermal effects in high performance bipolar devices/circuits," in *Bipolar Circuits and Technology Meeting*, 1989., *Proceedings of the 1989*, 1989, pp. 164–167.

- [56] A. E. Parker and J. G. Rathmell, "Self-heating process in microwave transistors," in *URSI Commission C Applications in Radio Science Workshop*, 2004, pp. 18–20.

- [57] Mahmoud AL-SA'DI, "TCAD Based SiGe HBT Advanced Architecture Exploration," ELECTRONIQUE, L'UNIVERSITE BORDEAUX I, 351 Cours de la Libération, 33405 Talence Cedex, France., 2011.

- [58] Project MIRANDELA, "Millimetre-wave and radio-frequency integration in nanoelectronics for modern wireless." [Online]. Available: http://eniac.eu/web/downloads/projectprofiles/call2\_eniac\_mirandela.PDF.

- [59] "MIRANDELA Millimetre-wave and Radio-frequency integration in Nanoelectronics for Modern Wireless 5 A Communications." [Online]. Available: http://www.sintef.no/home/Information-and-Communication-Technology-ICT/Communication-Systems/Projects/MIRANDELA/.

Technology – state of the art – introduction to thesis General introduction

# Self-heating and device compact modeling

This chapter demonstrates a general overview of self-heating effect in electronic device and a short description on different analytical models, presented in literatures. Transistor compact model has been discussed in brief. The compact model has been verified by static and dynamic measurements.

#### 1.1 Introduction

The temperature rise in a chip is mainly due to three different mechanisms; (i) self-heating in the device because of power dissipation, (ii) thermal coupling between neighboring device and (iii) chip to package and package to ambient thermal impedance. This thesis concentrates to investigate the first effect, the thermal phenomena inside the device, as it has a major impact on analog circuits.

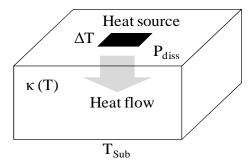

Figure 1-1: A semiconductor device with a heat source of power dissipation  $P_{diss}$ : the heat flow coupled with substrate thermal conductivity  $\kappa(T)$  results in a temperature rise of heat source  $\Delta T$ .

The self-heating is the process by which power dissipation of the device alters its temperature. Heat is generated only in a localized portion of the transistor and conduction of heat away from this region into the surroundings is limited due to several reasons and, therefore, device temperature rises. In general, this temperature rise is non uniform. The device operation is a time-average power dissipation, which results in a heat flow from the heat source to the backside of the substrate. The backside of the substrate is considered to be controlled by the external environment to a substrate temperature T<sub>sub</sub>. The heat flow to the backside of the wafer, coupled with the thermal conductivity of the semiconductor wafer on which the device is fabricated, results in a temperature rise of the device above the ambient temperature. The heat flow from the thermal source to the top of the device via the interconnect metallization is usually assumed to be negligible. In many cases it is necessary to account for the temperature dependence of the thermal conductivity and also the possibility for the power dissipation. The temperature dependent power dissipation causes electro-thermal feedback. Solution of the equations describing the non-linear system illustrated in Figure 1-1 gives the temperature distribution throughout the device under study; it is this temperature rise that is a direct result of self-heating.

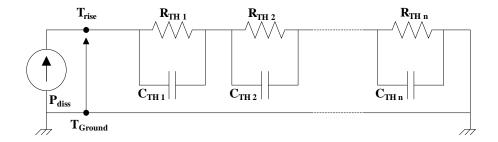

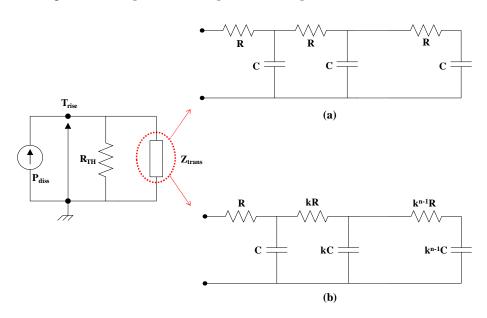

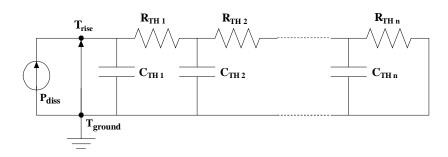

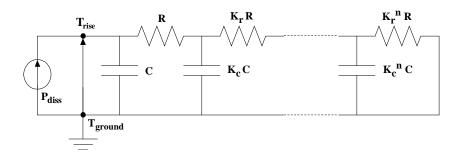

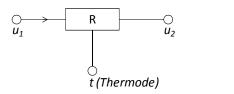

#### 1.1.1 Electrical representation of thermal system

The propagation of heat in a medium can take place in three different ways, convection, radiation and conduction. The electronic components generally have only the heat conduction. In a homogeneous isotropic material medium it is described by a parabolic partial differential equation,

$$\frac{\partial^2 T}{\partial x^2} = \frac{c\rho}{\lambda_{th}} \frac{\partial T}{\partial t}$$

Eq. 1-1

In the above equation,  $\lambda_{th}$  stands for the specific heat conductance, c for the specific thermal capacitance and the  $\rho$  for the density of the material. T describes the temperature and x the coordinates in the direction of heat propagation.

In order to investigate for an electrical analog model, the comparison with a transmission line comes contiguous [1]. The transmission line equation describes all the properties for a wave such as reflection, standing wave etc. which is expressed by a much more complex form,

$$\frac{\partial^2 U}{\partial x^2} = C'L'\frac{\partial^2 U}{\partial t^2} + \left(C'R' + G'L'\right)\frac{\partial U}{\partial t} + G'R'U$$

Eq. 1-2

Here C' is the capacitance per unit length, R' the resistance per unit length, G' the transverse conductance per unit length and L' the impedance per unit length.

It is considered that, in the field of heat conduction in solid, there is no direct comparison for electrical term of inductance, because a volume element cannot cool itself [1]. This can be described by L'=0 and G'=0. Therefore the transmission line equation is reduced to

$$\frac{\partial^2 U}{\partial x^2} = C'R' \frac{\partial U}{\partial t}$$

Eq. 1-3

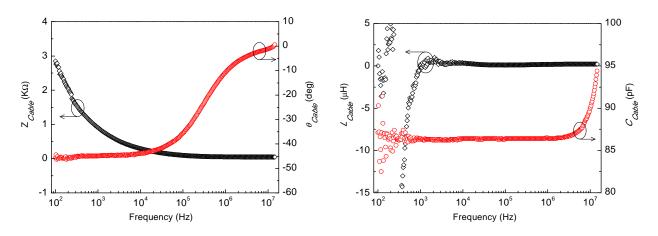

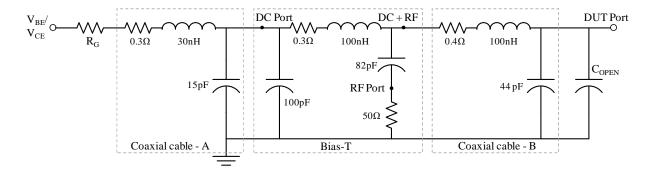

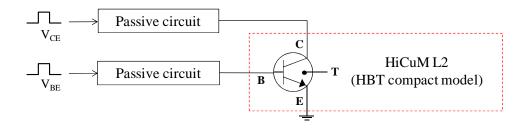

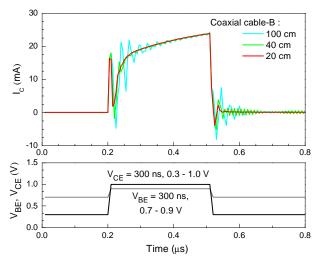

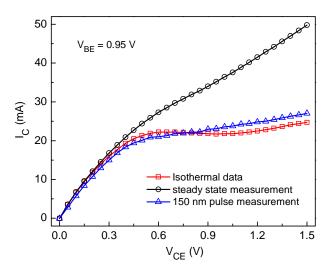

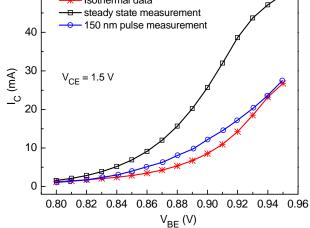

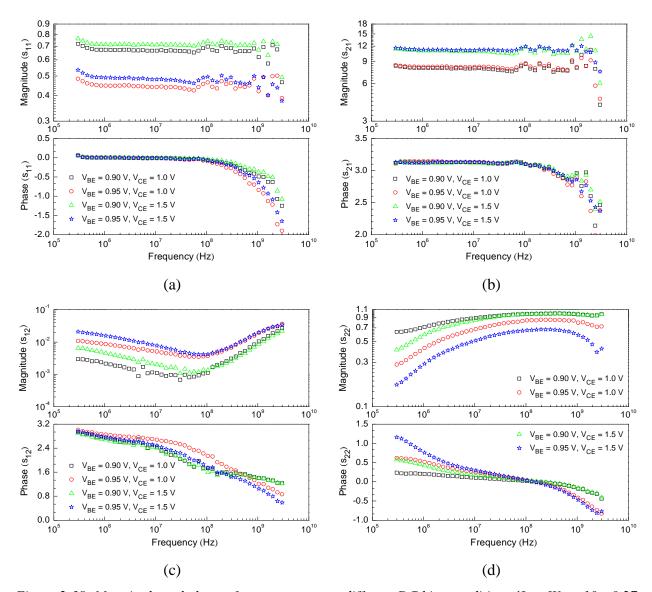

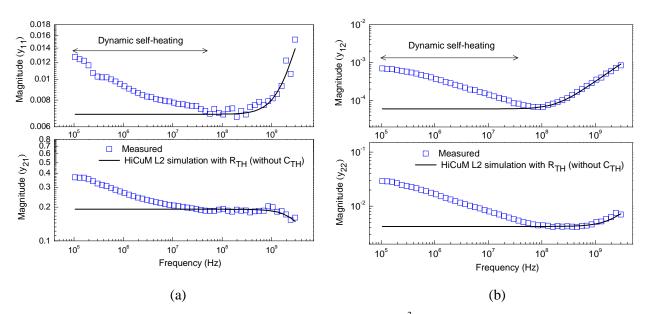

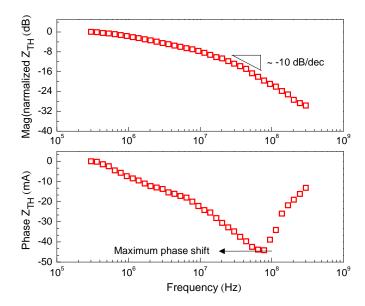

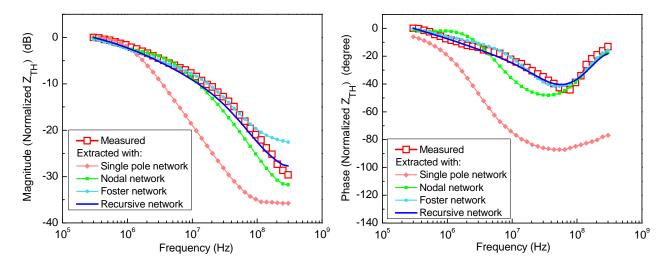

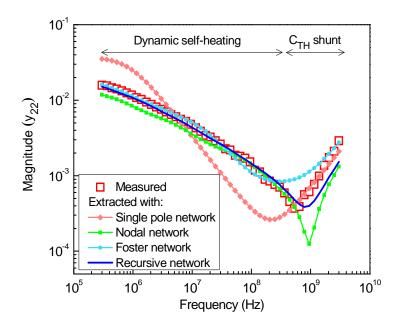

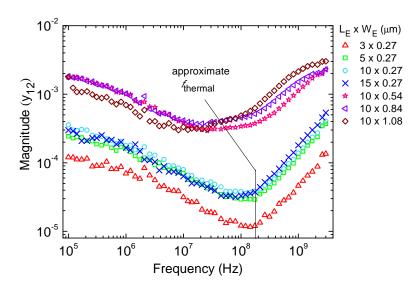

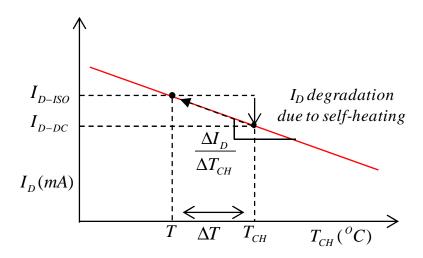

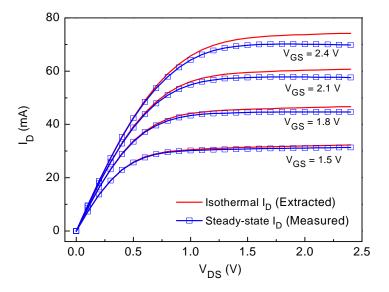

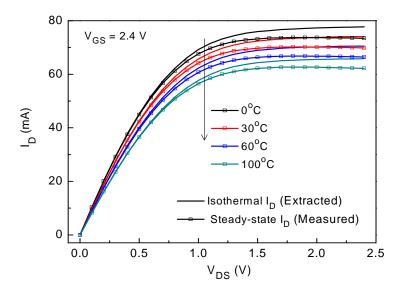

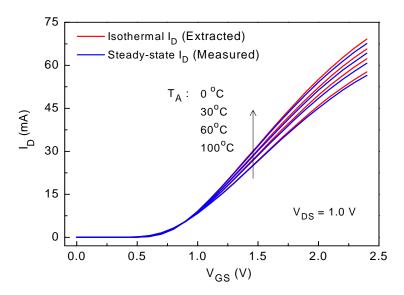

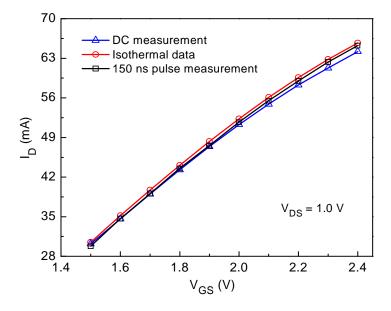

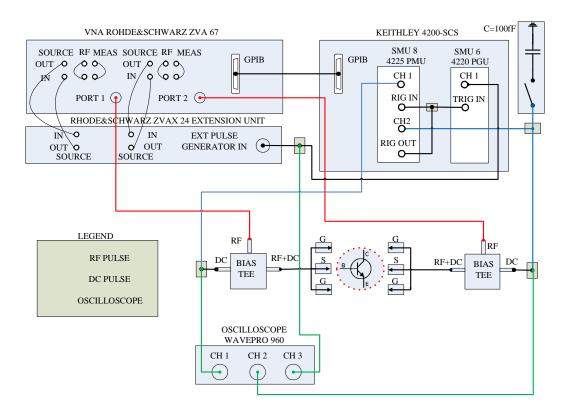

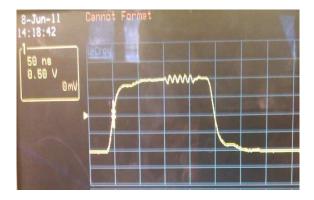

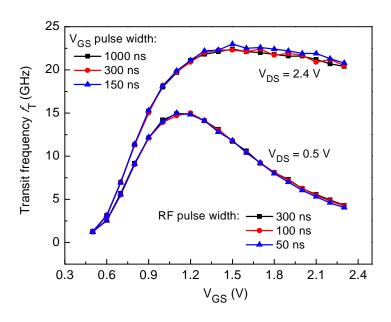

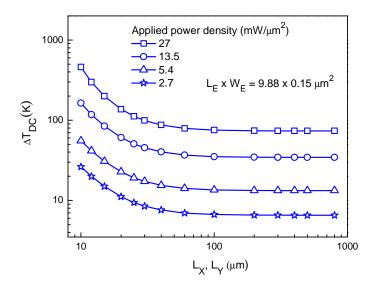

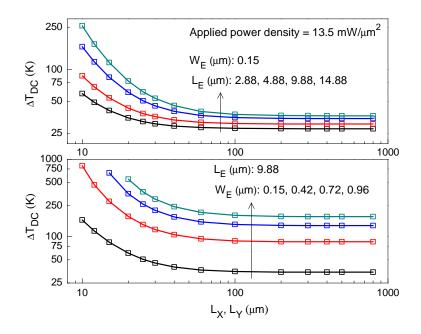

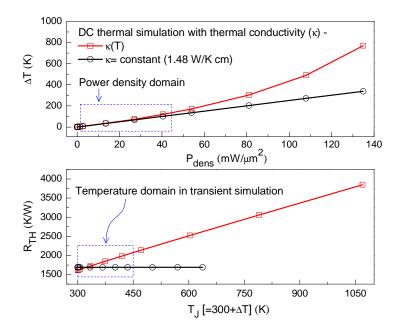

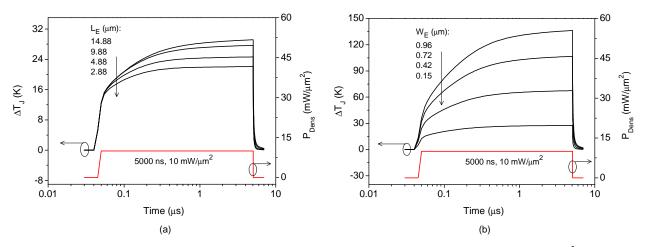

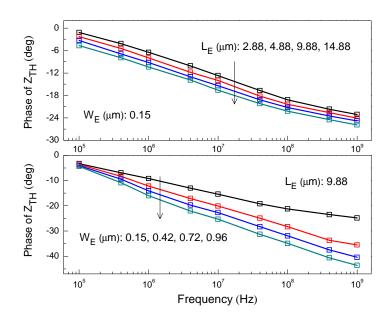

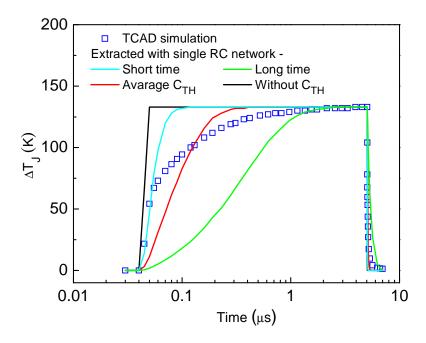

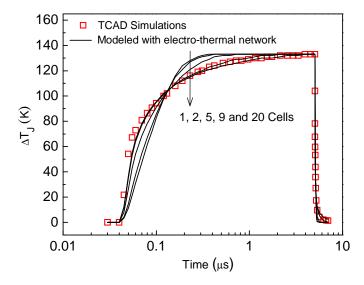

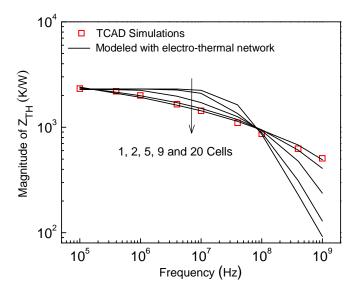

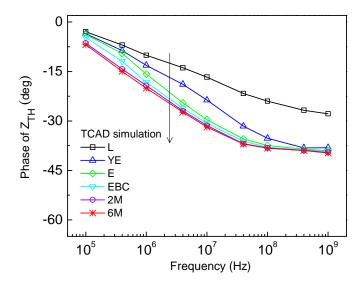

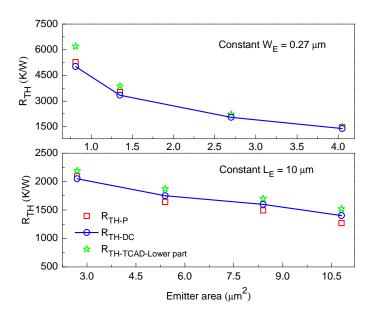

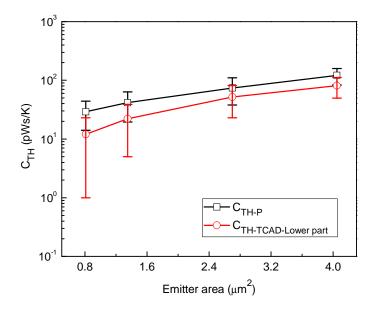

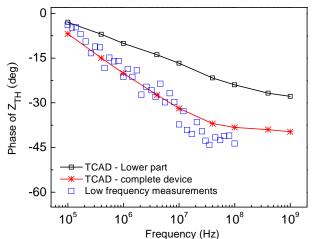

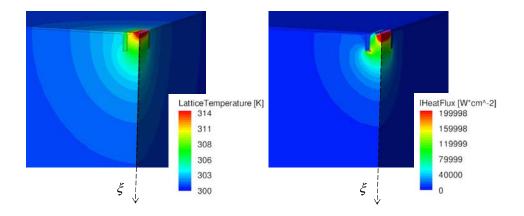

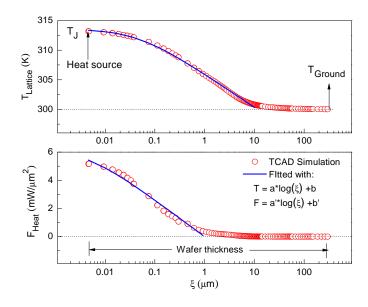

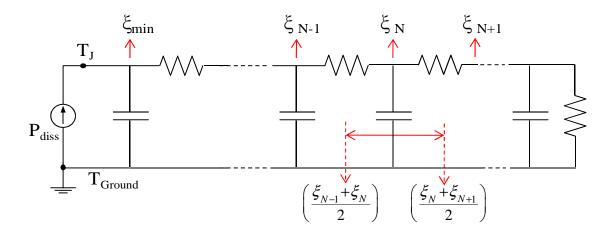

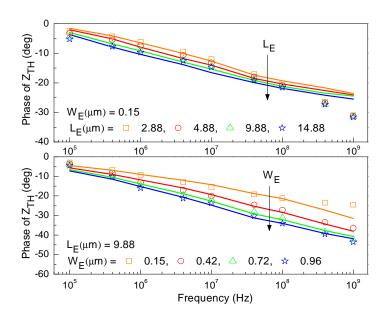

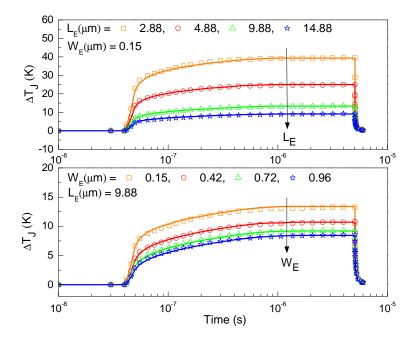

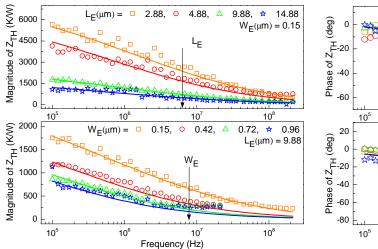

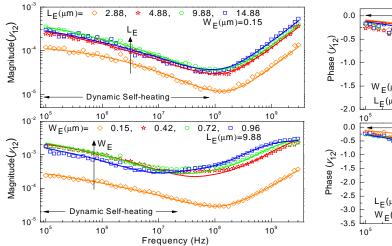

The structure of the *Eq. 1-3* is same as *Eq. 1-1*. In 1845 Kirchhoff stated that, "two different forms of energy behave identically when the basic differential equations which describe them have the same form and the initial and boundary conditions are identical".