# Static analysis of least recently used caches: complexity, optimal analysis, and applications to worst-case execution time and security

Valentin Touzeau

# ▶ To cite this version:

Valentin Touzeau. Static analysis of least recently used caches: complexity, optimal analysis, and applications to worst-case execution time and security. Programming Languages [cs.PL]. UGA - Université Grenoble Alpes, 2019. English. NNT: . tel-02454946

# HAL Id: tel-02454946 https://hal.science/tel-02454946

Submitted on 24 Jan 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

#### Valentin TOUZEAU

Thèse dirigée par **David MONNIAUX**, CNRS et codirigée par **Claire MAIZA**, MCF, Grenoble INP préparée au sein du **Laboratoire VERIMAG** dans **l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique**

Analyse statique de caches LRU : complexité, analyse optimale, et applications au calcul de pire temps d'exécution et à la sécurité

Static analysis of least recently used caches: complexity, optimal analysis, and applications to worst-case execution time and security

Thèse soutenue publiquement le **30 septembre 2019**, devant le jury composé de :

#### **Monsieur David MONNIAUX**

DR, Communauté Université Grenoble Alpes, Directeur de thèse

#### Madame Claire Maïza

Maître de Conférences, Communauté Université Grenoble Alpes, Codirecteur de thèse

#### **Monsieur Kenneth McMillan**

Directeur de Recherche, Microsoft Research, Rapporteur

## Monsieur Björn Lisper

Professeur, Mälardalen University, Rapporteur

#### **Monsieur Hugues Cassé**

Maître de Conférences, Université Paul Sabatier, Examinateur

#### Monsieur Jan Reineke

Professeur, Saarland University, Examinateur

#### **Monsieur Frédéric Pétrot**

Professeur, Communauté Université Grenoble Alpes, Examinateur

#### Monsieur Sébastien Faucou

Maître de Conférences, Université de Nantes, Examinateur

#### **Abstract**

The certification of real-time safety critical programs requires bounding their execution time. Due to the high impact of cache memories on memory access latency, modern Worst-Case Execution Time estimation tools include a cache analysis. The aim of this analysis is to statically predict if memory accesses result in a cache hit or a cache miss. This problem is undecidable in general, thus usual cache analyses perform some abstractions that lead to precision loss. One common assumption made to remove the source of undecidability is that all execution paths in the program are feasible. Making this hypothesis is reasonable because the safety of the analysis is preserved when adding spurious paths to the program model. However, classifying memory accesses as cache hits or misses is still hard in practice under this assumption, and efficient cache analysis usually involve additional approximations, again leading to precision loss. This thesis investigates the possibility of performing an optimally precise cache analysis under the common assumption that all execution paths in the program are feasible.

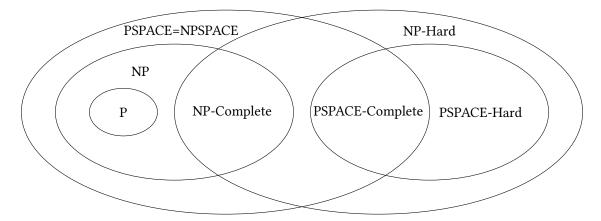

We formally define the problems of classifying accesses as hits and misses, and prove that they are NP-hard or PSPACE-hard for common replacement policies (LRU, FIFO, NMRU and PLRU). However, if these theoretical complexity results legitimate the use of additional abstraction, they do not preclude the existence of algorithms efficient in practice on industrial workloads.

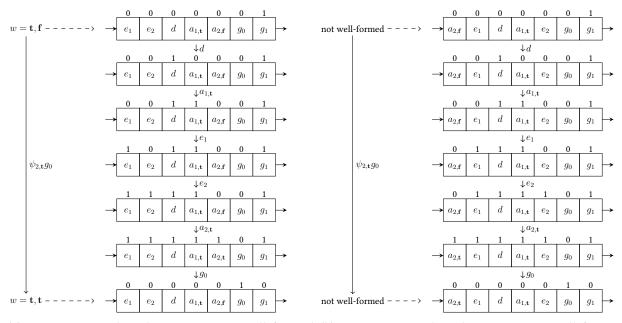

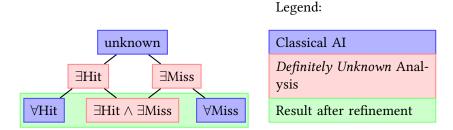

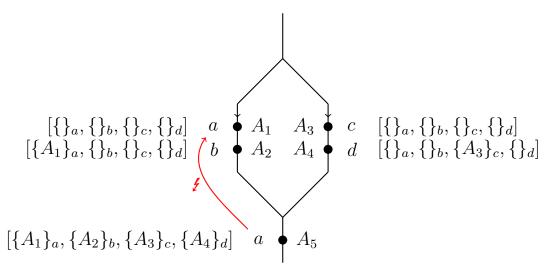

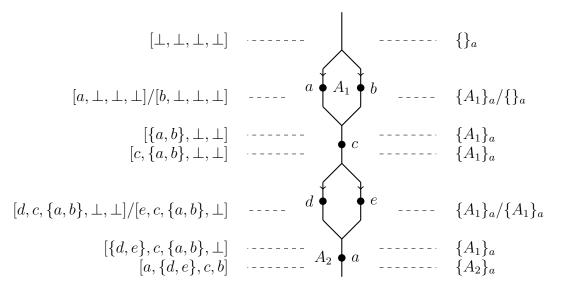

Because of the abstractions performed for efficiency reasons, cache analyses can usually classify accesses as *Unknown* in addition to *Always-Hit* (Must analysis) or *Always-Miss* (May analysis). Accesses classified as *Unknown* can lead to both a hit or a miss, depending on the program execution path followed. However, it can also be that they belong to one of the *Always-Hit* or *Always-Miss* category and that the cache analysis failed to classify them correctly because of a coarse approximation. We thus designed a new analysis for LRU instruction that is able to soundly classify some accesses into a new category, called *Definitely Unknown*, that represents accesses that can lead to both a hit or a miss. For those accesses, one knows for sure that their classification does not result from a coarse approximation but is a consequence of the program structure and cache configuration. By doing so, we also reduce the set of accesses that are candidate for a refined classification using more powerful and more costly analyses.

Our main contribution is an analysis that can perform an optimally precise analysis of LRU instruction caches. We use a method called *block focusing* that allows an analysis to scale by only analyzing one cache block at a time. We thus take advantage of the low number of candidates for refinement left by our *Definitely Unknown* analysis. This analysis produces an optimal classification of memory accesses at a reasonable cost (a few times the cost of the usual May and Must analyses).

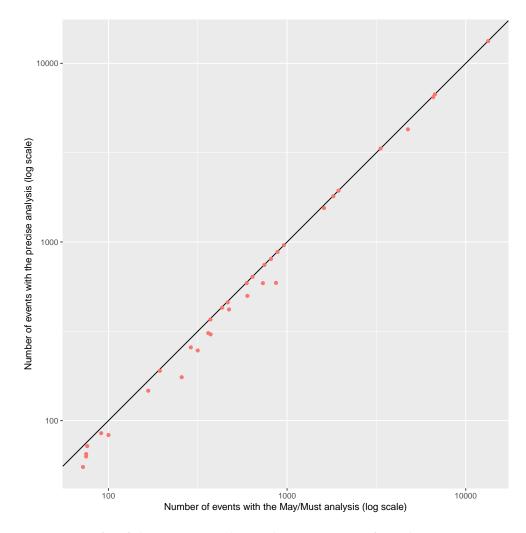

We evaluate the impact of our precise cache analysis on the pipeline analysis. Indeed, when the cache analysis is not able to classify an access as *Always-Hit* or *Always-Miss*, the pipeline analysis must consider both cases. By providing a more precise memory access classification, we thus prune the state space explored by the pipeline analysis and hence the WCET analysis time.

Aside from this application of precise cache analysis to WCET estimation, we investigate the possibility of using the *Definitely Unknown* analysis in the domain of security. Indeed, caches can be used as side-channel to extract some sensitive data from a program execution, and we propose a variation of our *Definitely Unknown* analysis to help a developer finding the source of some information leakage.

#### Résumé

Dans le cadre des systèmes critiques, la certification de programmes temps-réel nécessite de borner leur temps d'exécution. Les mémoires caches impactant fortement la latence des accès mémoires, les outils de calcul de pire temps d'exécution incluent des analyses de cache. Ces analyses visent à prédire statiquement si ces accès aboutissent à des cache-hits ou des cache-miss. Ce problème étant indécidable en général, les analyses de caches emploient des abstractions pouvant mener à des pertes de précision. Une hypothèse habituelle pour rendre le problème décidable consiste à supposer que toutes les exécutions du programme sont réalisables. Cette hypothèse est raisonnable car elle ne met pas en cause la validité de l'analyse : tous les véritables chemins d'exécutions du programme sont couverts par l'analyse. Néanmoins, la classification des accès mémoires reste difficile en pratique malgré cette hypothèse, et les analyses de cache efficaces utilisent des approximations supplémentaires. Cette thèse s'intéresse à la possibilité de réaliser des analyses de cache de précision optimale sous l'hypothèse que tous les chemins sont faisables.

Les problèmes de classification d'accès mémoires en hits et miss y sont définis formellement et nous prouvons qu'ils sont NP-difficiles, voire PSPACE-difficiles, pour les politiques de remplacement usuelles (LRU, FIFO, NMRU et PLRU). Toutefois, si ces résultats théoriques justifient l'utilisation d'abstractions supplémentaires, ils n'excluent pas l'existence d'un algorithme efficace en pratique pour des instances courantes dans l'industrie.

Les abstractions usuelles ne permettent pas, en général, de classifier tous les accès mémoires en *Always-Hit* et *Always-Miss*. Certains sont alors classifiés *Unknown* par l'analyse de cache, et peuvent aboutir à des cache-hits comme à des cache-miss selon le chemin d'exécution emprunté. Cependant, il est aussi possible qu'un accès soit classifié comme *Unknown* alors qu'il mène toujours à un hit (ou un miss), à cause d'une approximation trop grossière. Nous proposons donc une nouvelle analyse de cache d'instructions LRU, capable de classifier certains accès comme *Definitely Unknown*, une nouvelle catégorie représentant les accès pouvant mener à un hit ou à un miss. On est alors certain que la classification de ces accès est due au programme et à la configuration du cache, et pas à une approximation peu précise. Par ailleurs, cette analyse réduit le nombre d'accès candidats à une reclassification par des analyses plus précises mais plus coûteuses.

Notre principale contribution est une analyse capable de produire une classification de précision optimale. Celle-ci repose sur une méthode appelée *block focusing* qui permet le passage à l'échelle en analysant les blocs de cache un par un. Nous profitons ainsi de l'analyse *Definitely Unknown*, qui réduit le nombre de candidats à une classification plus précise. Cette analyse précise produit alors une classification optimale pour un coût raisonnable (proche du coût des analyses usuelles May et Must).

Nous étudions également l'impact de notre analyse exacte sur l'analyse de pipeline. En effet, lorsqu'une analyse de cache ne parvient pas à classifier un accès comme *Always-Hit* ou *Always-Miss*, les deux cas (hit et miss) sont envisagés par l'analyse de pipeline. En fournissant une classification plus précise des accès mémoires, nous réduisons donc la taille de l'espace d'états de pipeline exploré, et donc le temps de l'analyse.

Par ailleurs, cette thèse étudie la possibilité d'utiliser l'analyse *Definitely Unknown* dans le domaine de la sécurité. Les mémoires caches peuvent être utilisées comme canaux cachés pour extraire des informations de l'exécution d'un programme. Nous proposons une variante de l'analyse *Definitely Unknown* visant à localiser la source de certaines fuites d'information.

# **Contents**

| 1 | Intr | oductio                   | on                                              | 1  |  |  |  |  |  |  |

|---|------|---------------------------|-------------------------------------------------|----|--|--|--|--|--|--|

|   | 1.1  | Organi                    | ization of the manuscript                       | 3  |  |  |  |  |  |  |

| 2 | Con  | text                      |                                                 | 5  |  |  |  |  |  |  |

|   | 2.1  | Caches                    | 3                                               | 5  |  |  |  |  |  |  |

|   |      | 2.1.1                     | Blocks and Locality Principles                  | 6  |  |  |  |  |  |  |

|   |      | 2.1.2                     | Cache sets and associativity                    | 6  |  |  |  |  |  |  |

|   |      | 2.1.3                     | Index, Tag, Offset                              | 8  |  |  |  |  |  |  |

|   |      | 2.1.4                     | Replacement policies                            | 8  |  |  |  |  |  |  |

|   |      | 2.1.5                     | Caches and Address Translation                  | 13 |  |  |  |  |  |  |

|   |      | 2.1.6                     | Cache configuration in this thesis              | 15 |  |  |  |  |  |  |

|   | 2.2  | Static A                  | Analysis                                        | 15 |  |  |  |  |  |  |

|   |      | 2.2.1                     | Abstract Interpretation                         | 16 |  |  |  |  |  |  |

|   |      | 2.2.2                     | Model Checking                                  | 23 |  |  |  |  |  |  |

|   |      | 2.2.3                     | Cache analysis methods in this thesis           | 28 |  |  |  |  |  |  |

|   | 2.3  | State o                   | of the Art in Cache Analysis                    | 28 |  |  |  |  |  |  |

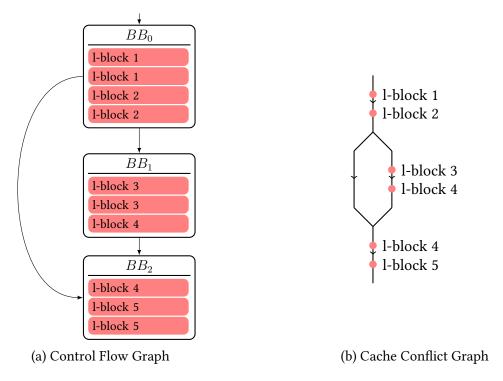

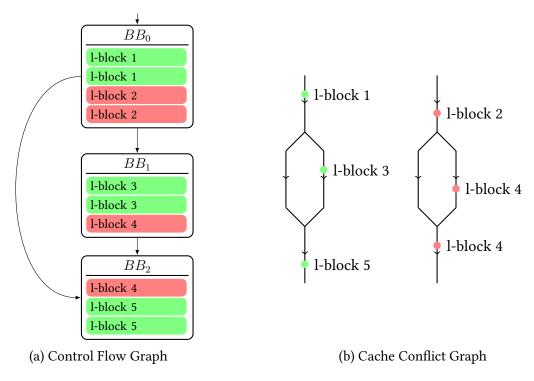

|   |      | 2.3.1                     | Cache Conflict Graph                            | 28 |  |  |  |  |  |  |

|   |      | 2.3.2                     | Analysis of LRU caches                          | 29 |  |  |  |  |  |  |

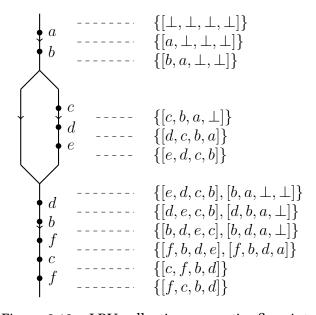

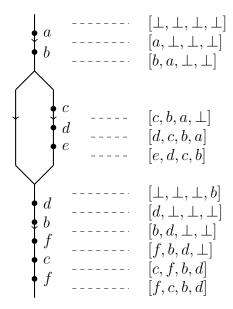

|   |      | 2.3.3                     | Ferdinand's May and Must analyses               | 32 |  |  |  |  |  |  |

|   |      | 2.3.4                     | Persistence Analysis and Loop Unrolling         | 35 |  |  |  |  |  |  |

|   |      | 2.3.5                     | Other replacement policies                      | 37 |  |  |  |  |  |  |

|   |      | 2.3.6                     | Cache analysis by Model Checking                | 37 |  |  |  |  |  |  |

| 3 | Cac  | Cache Analysis Complexity |                                                 |    |  |  |  |  |  |  |

|   | 3.1  | Backgı                    | round                                           | 39 |  |  |  |  |  |  |

|   | 3.2  | _                         |                                                 | 42 |  |  |  |  |  |  |

|   |      | 3.2.1                     | Fixed associativity                             | 44 |  |  |  |  |  |  |

|   |      | 3.2.2                     | LRU                                             | 45 |  |  |  |  |  |  |

|   |      | 3.2.3                     | FIFO                                            | 49 |  |  |  |  |  |  |

|   |      | 3.2.4                     | PLRU                                            | 56 |  |  |  |  |  |  |

|   |      | 3.2.5                     | NMRU                                            | 60 |  |  |  |  |  |  |

| 4 | Exa  | ct Cach                   | e Analysis                                      | 67 |  |  |  |  |  |  |

|   | 4.1  | Approx                    | ximating the set of Definitely Unknown Accesses | 68 |  |  |  |  |  |  |

|   |      | 4.1.1                     | ,                                               | 68 |  |  |  |  |  |  |

|   |      | 4.1.2                     | Abstract Interpretation for Definitely Unknown  | 70 |  |  |  |  |  |  |

|   |      | 4.1.3                     | Definitely Unknown Proofs                       | 74 |  |  |  |  |  |  |

|   |      | 4.1.4                     |                                                 | 79 |  |  |  |  |  |  |

|   | 4.2  | Exact Analysis of LRU Cache by Model Checking                  | 83  |

|---|------|----------------------------------------------------------------|-----|

|   |      | 4.2.1 Block Focusing                                           | 84  |

|   |      | 4.2.2 Proof of Block focusing correctness                      | 86  |

|   | 4.3  | Exact Analysis of LRU Cache by Abstract Interpretation         | 88  |

|   |      | 4.3.1 Exact Analyses as Fixed-Point Problems                   | 90  |

|   |      | 4.3.2 Data Structures and Algorithms                           | 93  |

|   | 4.4  | Experiments                                                    | 96  |

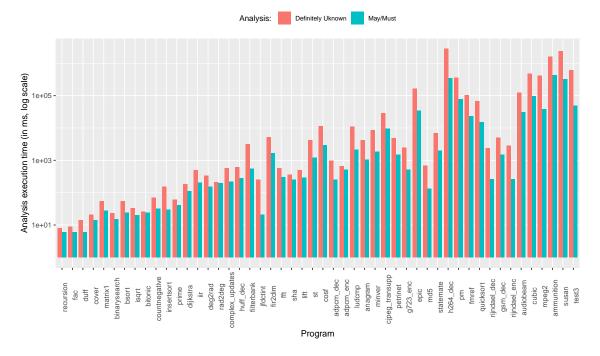

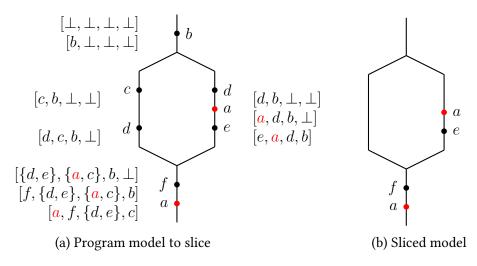

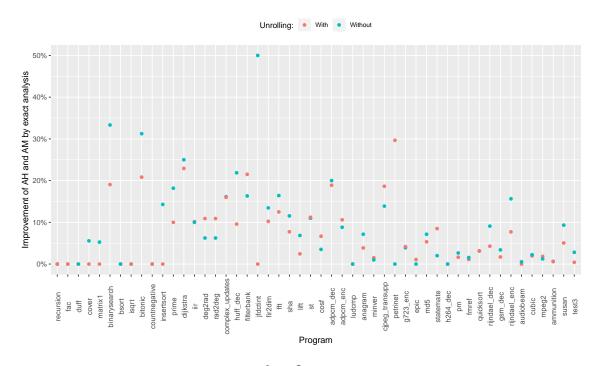

|   |      | 4.4.1 Refinement of Accesses classification by Exact Analyses  | 96  |

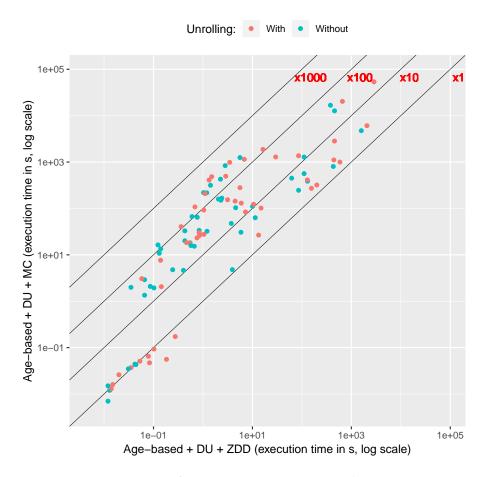

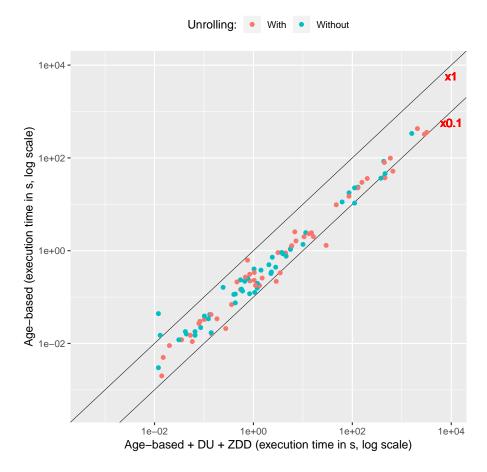

|   |      | 4.4.2 Efficiency comparison of Model Checking and ZDD approach | 97  |

|   |      | 4.4.3 May/Must and Exact analyses execution time comparison    | 97  |

| 5 | App  | cations                                                        | 99  |

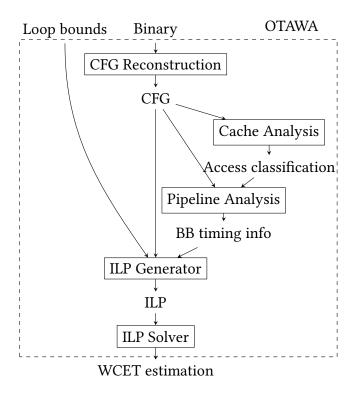

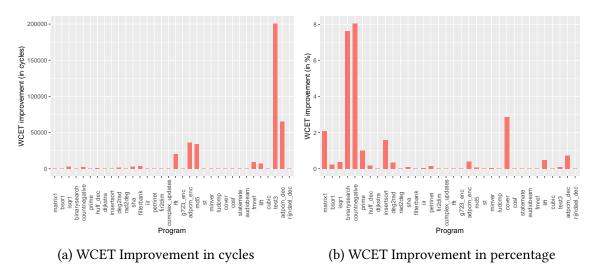

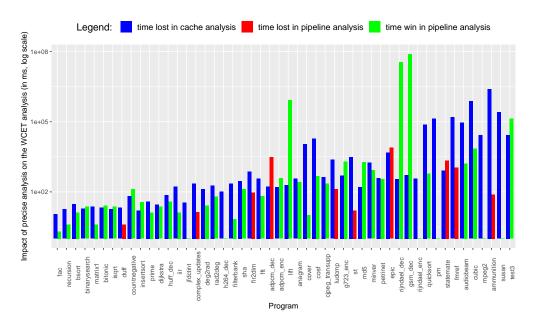

|   | 5.1  | WCET Application                                               | 99  |

|   | 5.2  |                                                                | 102 |

|   |      |                                                                | 103 |

|   |      | <del>-</del>                                                   | 104 |

|   | 5.3  | Security                                                       | 108 |

|   |      | 5.3.1 Program model and semantics                              | 109 |

|   |      |                                                                | 111 |

|   |      | 5.3.3 Analyses soundness                                       | 114 |

| 6 | Con  | lusion                                                         | 117 |

|   | 6.1  | Future Work                                                    | 119 |

|   |      | 6.1.1 Program Semantics                                        |     |

|   |      | 6.1.2 Analyzing Data Caches                                    |     |

|   |      | 6.1.3 Reducing analysis cost                                   |     |

|   |      |                                                                | 126 |

| 7 | Rési | mé en français                                                 | 138 |

# **Chapter 1**

# Introduction

Power plants, trains, airplanes, communication satellites and spacecrafts are some examples of safety-critical real-time systems. They are safety critical because any failure of such a system can lead to a human loss or huge economic cost, and they are real-time systems because they have to react fast enough to their inputs and environments to be correct. In other words, safety critical real-time systems are systems that have to respect their deadlines, and whose failures can have disastrous consequences. An example of such system is a task that periodically reads some sensors to correct the trajectory of a plane. If the period of the task is one millisecond, the task must terminate in less than one millisecond (or less if input/output jitter is constrained).

However, because of the always increasing amount of data to treat by time unit, modern processors use a wide variety of hardware optimizations that make the execution time of such systems hard to predict. In particular, the use of cache memories aims at keeping the processor busy in presence of a DRAM-based main memory, by retaining frequently used instructions and data in a fast memory close to the processing unit. Indeed, the latency of an instruction involving the CPU alone is usually several orders of magnitude lower than the main memory latency. Thus, in the presence of caches, the latency of an individual memory access may vary considerably depending on whether the access is a *cache hit*, i.e; it can be served from an on-chip cache memory, or a *cache miss*. Ensuring that a real-time program meet its deadline is thus harder in presence of caches.

In practice, static analysis approaches for bounding the worst-case execution time (WCET) of programs have to take into account whether or not accessed information is cached. The purpose of cache analyses considered in thesis is thus to statically classify every memory access at every machine-code instruction in a program into one of the following three classes:

- 1. Always Hit: each dynamic instance of the memory access results in a cache hit;

- 2. Always Miss: each dynamic instance of the memory access results in a cache miss;

- 3. there exist dynamic instances that result in a cache hit and others that result in a cache miss.

This is of course, in general, an undecidable question; so all analyses involve some form of abstraction, and may classify some accesses as "unknown". More precisely, the undecidability issue is usually tackled by making the assumption that every execution path in the program is feasible. Of course, building a program that violate this assumption (for instance, by adding some dead-code) is trivial. However, the program model (which consider all paths as feasible) covers all the actual behaviors of the real program. An analysis that correctly treat all possible executions of the model thus treats all the executions of the program.

Even under this "all path feasible" assumption the problem of memory classification seems difficult, and many cache analyses use additional abstraction. In this thesis, we thus look at the impact of this assumption on the cache analysis problem. More precisely:

- We investigate the complexity of performing an optimally precise cache analysis under this

hypothesis. If the problem is decidable under this assumption, some caches seem easier to

analyze that others. We thus investigate the difficulty of some cache analysis related problems under this hypothesis, for different cache replacement policies (that is, the algorithm

used for choosing which memory block to evict from the cache to make room for a new

block), from the complexity theory point of view.

- As mentioned above, there exist analyses that can guarantee that some accesses lead to a hit, or a miss. However, there is no analysis to our knowledge that can guarantee an access belongs to the category 3 above (i.e. no known analysis ensures the existence of paths leading to both a hit and a miss for some accesses).

- Finally, the question of the efficiency of an optimally precise cache analysis in the context of the "all path feasible" hypothesis is worth investigating. In practice, analyzed binaries are industrial program with restricted control flow, and caches have relatively low associativity. It is thus interesting to look at the practical efficiency of optimally precise cache analyses.

The goal of this thesis is to address the three points above.

#### Contributions

**Complexity of optimally precise cache analysis** While the intuition is that a cache retains the most recently accessed memory words, up to its size, reality is far more complex: what happens depends on the number of cache levels, the size of each level, the "number of ways" (also known as the associativity) of the cache and the cache replacement policy. Cache analyses depend on the cache replacement policy, and, in the literature, there is a clear preference for the LRU (Least Recently Used) policy, notably the well-known age-based abstract analysis of Ferdinand [AFMW96] and its variations. In contrast, other policies such as PLRU (pseudo-LRU), NMRU (Not Most Recently Used) and FIFO (First-In, First-Out) have a reputation for being very hard to analyze [HLTW03a] and for having poor predictability [RGBW07a]. A legitimate question is whether these problems are intrinsically difficult, or is it just that research has not so far yielded efficient analyses. Indeed, issues of static analysis of programs under different cache policies are not necessarily correlated with the practical efficiency of cache policies. Static analysis is concerned with worst-case behavior, and policies with approximately equal "average" practical performance may be very different from the analysis point of view. Even though PLRU and NMRU were designed as "cheap" (easier to implement in hardware) alternatives to LRU and have comparable practical efficiency [AMM04], they are very different from the worst-case analysis point of view. We thus explore the complexity of the memory access classification problem under different replacement policies.

**Definitely Unknown memory accesses** As mentioned above, analyses like the *May* and *Must* analyses presented in [AFMW96] rely on approximations to classify accesses as *Always-Miss*

<sup>&</sup>lt;sup>1</sup>By "average" we do not imply any probabilistic distribution, but rather an informal meaning over industrially relevant workloads, as opposed to examples concocted for exhibiting very good or very bad behavior.

or *Always-Hit*. In this setting, one does not have any information on the remaining unclassified accesses. Indeed, any access not classified can be always a hit (or miss) not detected by the analysis because of the approximation, or can both lead to a hit or a miss depending on the execution path in program. We thus introduce a new category, called *Definitely Unknown*, for distinguishing those accesses that can lead to both a hit or a miss. The distinction between *Definitely Unknown* and unclassified (*Unknown*) accesses is important because it characterizes the precision of an analysis. *Unknown* accesses can be refined into *Always-Hit*, *Always-Miss* or *Definitely Unknown* by improving the precision of the analysis. However, *Definitely Unknown* accesses are a consequence of the program and the cache analyzed, not of the analysis. These accesses have no chance to be refined into *Always-Hit* or *Always-Miss* by improving the precision of the cache analysis. We then propose an analysis that, similarly to the *May* and *Must* analyses of [AFMW96], is able to approximate the sets of *Definitely Unknown* memory accesses for *LRU* caches under the "all path feasible" assumption.

**Exact cache analysis** Once the accesses that can not be refined are filtered out, one can focus on the remaining candidates. For these few candidates, more expensive analyses can be considered. In particular, it is possible to treat them one by one and, by doing so, to design specific analysis that focus on a single block, pruning the state space to explore. In this thesis, we thus propose two approaches to remove the remaining uncertainty about memory accesses, one relying on a model checker, the other performed by abstract interpretation.

**Applications** Our last contribution is an application of the analyses design in this thesis in two different domains. First, the uncertainty about the classification of a memory access can have serious consequences on the WCET analysis. For instance, it is very important to have precise information about the cache behavior when analyzing pipelined and superscalar architectures, since pipeline analysis must consider the two cases "cache hit" and "cache miss" for any memory access that cannot be shown to be *Always-Hit* or *Always-Miss* [LS99, R<sup>+</sup>06], leading to a state explosion. Thus, imprecise cache analysis may have two adverse effects on WCET analysis. First, it may lead to an excessive overestimation of the WCET compared to the true WCET. An industrial user may suspect this when the upper bound on WCET given by the tools is far from experimental timings. This may discourage the user from using static analysis tools. In addition, imprecise cache analysis might results in excessively high WCET analysis time due to state explosion.

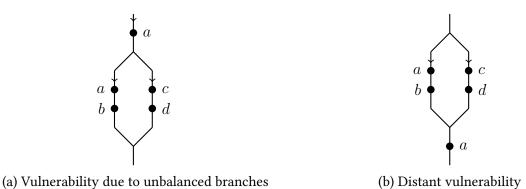

Finally, we explore some security related questions concerning caches. *Definitely Unknown* blocks might results in both hits or misses. When this variation is observable by an attacker and correlated to the variation of some secrete data, the cache might be the source of information leakage. We thus propose to use our *Definitely Unknown* analyses to detect such vulnerabilities. In addition, we propose some slight modification that allow to spot the origin of the leakage by tracking the last access to the leaking block.

# 1.1 Organization of the manuscript

Chapter 2 describes the context of this thesis. It describes how caches work, introduces some static analysis methods, and present the *May/Must* analysis of LRU caches. The problem of classifying memory accesses into *hits* and *misses* is studied from the complexity theory point of view in Chapter 3. Among other things, this chapter shows that the usual replacement policies lead to high complexity classification problems (most analyses are at least NP-hard). Chapter 4 introduces several techniques that allows to derive an optimally precise classification by abstract

interpretation and/or model checking. Two applications of cache analyses are investigated in Chapter 5. First, we study the benefit of a precise cache analysis on the WCET. Then, some aspects related to security are investigated. Finally, we discuss and conclude about the results and possible extensions of our work in Chapter 6.

# Chapter 2

# Context

# 2.1 Caches

Any computer needs memory to perform arbitrary computations, and this memory is usually available in different kinds. Registers form the most frequently used one. Located in the CPU core, they provide high speed and low latency. However, the total amount of memory available as registers is usually very low. For example, RISC-V architectures only provide 16 or 32 registers of 32 bits each, for a total of 128 bytes maximum.

Because of this very low capacity, computers rely on another kind of memory, called main memory, to perform computations. This main memory offers a much higher capacity (around 8GB for a recent personal computer), at the expense of a higher latency. Even though compilers tend to maximize the use of registers over main memory to decrease computation latency, accessing the main memory is unavoidable. In case the value of the accessed memory is needed immediately, the processor is simply stalled and waits for the data to be available to pursue the execution. However, the speed of modern processors is usually far beyond the speed of the main memory. Thus, such a simple computer only consisting in registers and main memory would spend most of its time waiting for the main memory to issue the requested data and instructions. To avoid this problem, called the Memory Wall [WM95], modern processors make heavy use of *cache memories*.

Cache memories offer a capacity/speed trade-off intermediate between registers and main memory: they are bigger but slower than registers, and smaller but faster than main memory. To speed computation up, the main idea is to store into caches information that is frequently accessed in the main memory, reducing the time needed to retrieve the information and thus the overall execution time. When the CPU issues a memory access, the information is searched in the cache. If it is found, the access is said to be a *cache hit* and the information is retrieved quickly. Otherwise, the access is a *cache miss* and the information is retrieved from the memory. When this happens, a copy of the retrieved data is stored into the cache to avoid a future cache miss. For efficiency reasons, the chunk of copied data contains several consecutive bytes, and not the accessed byte only. These chunks, called cache blocks, have the same size fixed by the hardware, and are aligned in memory according to this size.

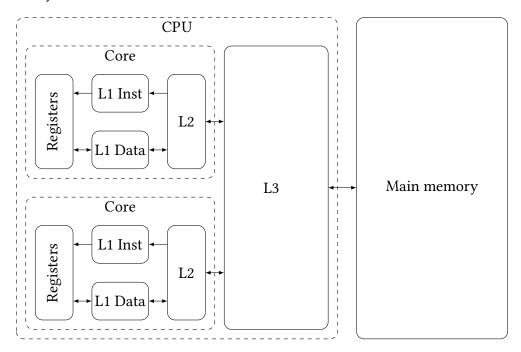

The idea of speeding up information retrieval by introducing an intermediate memory level can be repeated. Most modern CPU architectures indeed use several levels of caches, offering different capacity/speed trade-offs. The fastest level, which also offers the lowest capacity, is referred to as L1 cache, and is often split into an instruction cache and a data cache. The next cache level is referred to as L2, and is bigger but slower than L1 caches. Contrarily to L1 caches, the L2 cache usually mixes instructions and data, both data and instruction L1 caches use the L2 cache as a backing store. Finally, many architectures nowadays offer a L3 cache (or even a L4

cache [KCB<sup>+</sup>15]), that is shared between different cores. Figure 2.1 shows an example of typical cache hierarchy.

Figure 2.1 – Example of cache hierarchy (Intel Core i3 Haswell)

# 2.1.1 Blocks and Locality Principles

The efficiency of caches relies on two key principles:

- Time locality: when a word is accessed, it will be accessed again soon with high probability.

- Spatial locality: when a word is accessed, words close to it will be accessed with high probability.

On one hand, one should load into the cache large cache blocks to profit from space locality. Indeed, by loading into the cache words that are contiguous to the recently accessed word, one increases the chances that the next word accessed will already be cached. On the other hand, caches should keep words available for the processor as long as possible to benefit from time locality. The two principles are thus adversarial: the bigger the cache blocks are, the fewer can be cached, and the faster they are evicted. In practice, a typical trade-off for the size of memory blocks is 32 to 64 bytes (see Table 2.2 later in the section). The area occupied by a memory block in the cache is called a *cache line*.

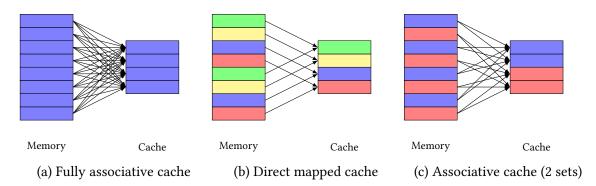

# 2.1.2 Cache sets and associativity

For efficiency reasons, a given memory block can usually only be stored in the cache at some locations and nowhere else, to reduce the time needed to retrieve it. This set of cache lines a block can be stored in is called a *cache set* and is fully determined by the block address. Generally, this cache set is given by a part of the block address (i.e. a part of the address of the first byte in the block). Thus, the cache is split into several cache sets of equal size, each of them associated to different cache blocks. The number of cache sets composing the cache is usually a power of 2 varying with the cache size [Rei09]. Two special cases can be distinguished:

- The cache contains a single cache set: the cache is said to be *fully associative*, a memory block can thus reside in any cache line.

- The cache contains as many cache sets as blocks (i.e. each cache set is composed of a single cache line): the cache is *direct mapped*, a memory block can only reside in the cache line associated to it.

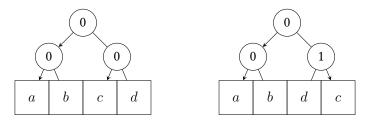

Figure 2.2 – Example of mapping from main memory to cache

Figure 2.2 illustrates different possible cache set configurations. Each rectangle represents a memory block, and its color identifies its associated cache set. Arrows designate the possible cache lines a memory block can be stored in. Figure 2.2a shows the mapping of memory to a fully associative cache, a memory block can be loaded in potentially any cache line. Figure 2.2b is an example of direct mapping, a memory block can only be stored in one cache line. Finally, Figure 2.2c is the intermediate situation: the cache is composed of a few cache sets of several cache lines each.

As shown on Figure 2.2 different cache configurations are possible for a fixed cache size and block size, each of them being uniquely defined by its number of cache sets. Alternatively, a cache configuration can be identified by the number of cache lines (also named number of ways) contained in a single cache set. This number is called the cache ways and is often denoted by ways.

For example, caches represented on Figure 2.2a, Figure 2.2b and Figure 2.2c respectively have associativity 4, 1, and 2. Table 2.1 shows how the number of sets, the cache associativity and the cache size vary for an example processor<sup>1</sup>, the Intel Core i3-3110M.

| Cache          | Size   | Number of sets | Associativity | Block size |

|----------------|--------|----------------|---------------|------------|

| L1 Data        | 32 KB  | 64             | 8             | 64         |

| L1 Instruction | 32 KB  | 64             | 8             | 64         |

| L2 Unified     | 256 KB | 512            | 8             | 64         |

| L3 Unified     | 3 MB   | 4096           | 12            | 64         |

Table 2.1 - Characteristics of Intel Core i3-3110M CPU

$<sup>^1\</sup>mathrm{Data}$  were extracted from the /sys/devices/system/cpu/cpuX/cache/indexY directory on a laptop using the mentioned CPU.

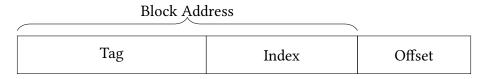

# 2.1.3 Index, Tag, Offset

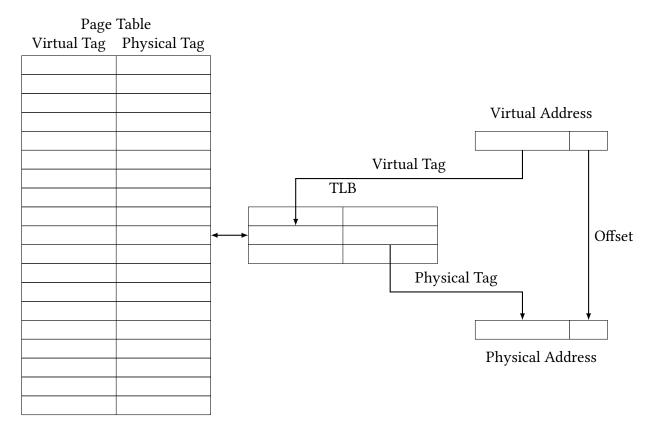

As mentioned above, the location of a given byte in the cache is determined by its address. More precisely, any address can be split into two distinct parts: i) the least significant bits, which form an offset indicating the location of the byte into the block ii) the remaining part of the address, which constitutes the block address. The block address can in turn be decomposed into a tag, and an index. The index identifies the unique cache set the block can be loaded in, whereas the tag is used to distinguish blocks mapping the same cache set. Figure 2.3 recaps the complete slicing of the address.

Figure 2.3 – Address splitting

# 2.1.4 Replacement policies

As mentioned previously, when a memory access results in a cache miss, the block accessed is issued by the main memory and a copy is loaded into the cache. The cache set where this block is stored is given by the address of the block. However, it happens that the cache set a block should be stored in is already full. In this case, one has to select a block from this cache set and evict it to make space available for the new block. Note that a block eviction can occur when the cache is not full, but a set is.

When a block must be evicted, it is selected according to a *replacement policy*. Many cache policies exist, offering different efficiency/implementation cost trade-off. Among the most widely used one can find LRU (Least Recently Used), PLRU (Pseudo-Least Recently Used), FIFO (First In First Out) and NMRU (Not Most Recently Used).

Cache sets are usually managed independently, i.e. the state of a cache set only depends on the accesses that map to this cache set. However, in some replacement policies (such as the Pseudo-Round Robin policy), an access to a cache set influences the other cache sets, thus the state to be considered is global. In this thesis, we consider only local cache set management.

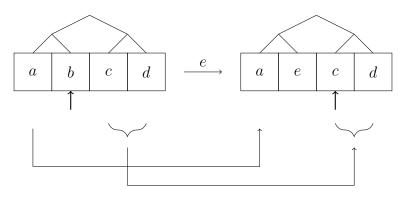

## LRU: Least Recently Used

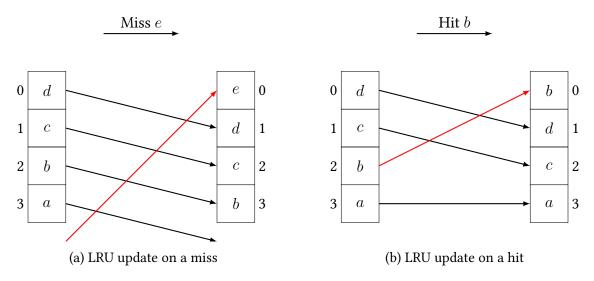

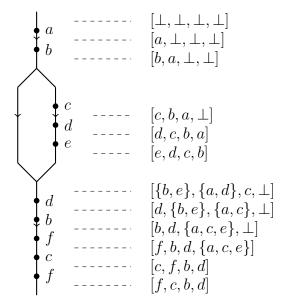

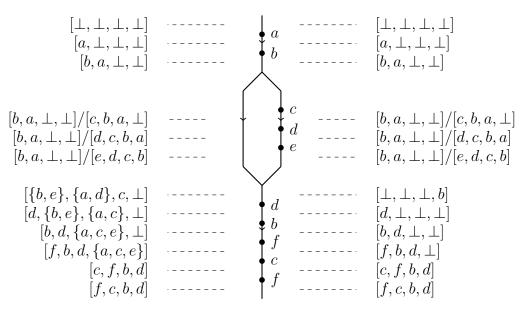

The Least Recently Used policy maintains a list of blocks ordered from the most recently used to the least recently used among each cache set. Upon a miss, the accessed block is loaded at the MRU (Most Recently Used) position and other blocks are simply shifted by one logical position. Finally, the Least Recently Used block is evicted. Figure 2.4a illustrates the update of a cache set containing blocks a, b, c and d when accessing block e.

Upon a hit, no block is evicted: the accessed block is simply moved to the MRU position, and blocks that had been more recently used (i.e. before the accessed block) are shifted by one position. This case is depicted by Figure 2.4b.

Note that hardware implementations of LRU do not actually move memory blocks from one cache line to another. Instead, the logical position of blocks is maintained separately in additional registers (see [TAMV19] for details of several possible implementations).

Because the blocks are ordered from the most recently used to the least recently used, the position of a block among a cache set is usually called its age. For example, block c on Figure 2.4a

Figure 2.4 – LRU behavior

has age 1 before the access to e, and age 2 after the access. The older a block is, the closer it is from being evicted. More precisely, a block that has just been accessed will be evicted after exactly k misses [Rei09].

#### FIFO: First-In First-Out

Figure 2.5 – FIFO behavior

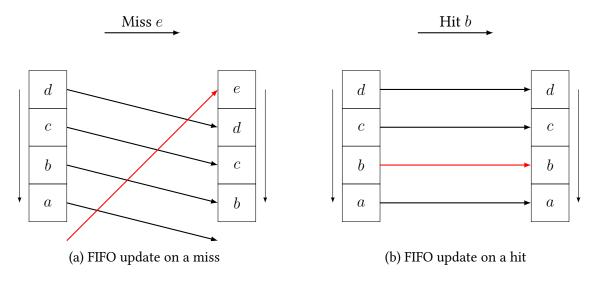

Similarly to LRU, the First-In First-Out policy works like a queue: on a miss, the accessed block is inserted at the head and the block at the tail is evicted. However, contrarily to LRU, the cache set is left unchanged in case of a hit. Figure 2.5 presents both cases. One can notice that FIFO behaves as LRU on a miss (see Figure 2.5a), and as the identity function on a hit (see Figure 2.5b). The different behavior of FIFO relatively to LRU has two main implications:

• FIFO is much simpler to implement at hardware level. A simple "pointer" going from one cache line to the next one is enough to track which block will be evicted on the next miss. Moreover, the cache update is very fast when it needs to be i.e. in case of a hit, because there is no action to perform.

• A block that has just been accessed can be evicted on the next access. This happens when an access to the last block of the queue is followed by a miss which evicts it. This behavior makes FIFO caches harder to predict. An example of this phenomenon, called "domino effect", is given in [Lun02].

## NMRU: Not Most Recently Used

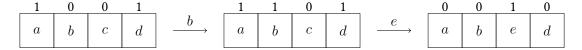

As its name suggests the Not Most Recently Used policy does not provide guarantee as strong as the LRU policy: instead of ensuring that the least recently used block is evicted, it makes sure the block evicted on a miss is not the most recently used one. To do so, one extra bit, called MRU bit, is associated to each cache line. If this bit is a 1, then the cache line might contain the most recently used block. Conversely, if the MRU bit value is 0, then the associated cache line can not contain the last block accessed.

To preserve this property, the NMRU policy works as follows:

- On a miss, the first block (from left to right) which MRU bit is 0 is replaced by the accessed block, and its MRU bit is flipped to 1.

- On a hit, the MRU bit of the accessed block is set to 1 whatever its value is.

- In both cases if the MRU-bit of the block accessed is the last one to 0, all other MRU-bits are reset to 0 (this is called a global-flip). This ensures that at any time, there is at least one cache line which MRU bit is 0.

Figure 2.6 – NMRU behavior

This behavior is illustrated by Figure 2.6. The first access is an access to block b which is cached. The MRU associated to b is then flipped to value 1. Then, an access to e is performed, and leads to a miss. The first cache line which MRU bit is 0 is the one containing c. e is thus evicted to store e and the associated MRU bit is set to 1. Finally, because this bit was the last one with value 0, all other bits are set to 0.

Note that this policy is sometimes referred as Most Recently Used, or PLRU-bit (i.e. Pseudo-Least Recently Used - *bit version*, as opposed to the *tree version* described below).

Similarly to the FIFO policy, blocks stored in an NMRU cache can be evicted quickly. After only two accesses, a block that has just been loaded can already be evicted. However, some approaches (see [GLYY14]) show that NMRU caches, although not as predictable as LRU caches, are more predictable than other replacement policies.

## PLRU: Pseudo-Least Recently Used

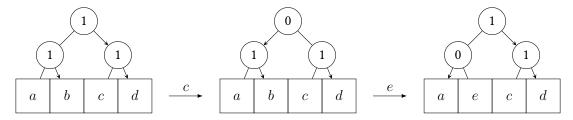

As indicated by its name the Pseudo-Least Recently Used policy approximates the LRU policy. To do so, cache lines of a set are organized into a full binary tree, in which leaves are cache lines and other nodes contain bits (called MRU-bits) indicating where is the next block to evict. More precisely, when a block must be evicted, one recursively looks at the value of a node, starting from the root. If the node contains 0, then the block to evict should be evicted from the left subtree,

otherwise (when the node contains 1) it should be evicted from the right subtree. This process is repeated until a leaf is reached, the associated cache line is then used to store the new block.

In case of a hit, the tree is explored from bottom to top. Each time a node is encountered, its MRU-bit is set to protect the accessed block from eviction. In other words, for a given node in the tree, three outcomes are possible on a hit:

- If none of the right and left subtrees contain the accessed block, the MRU-bit of the node is unchanged.

- If the accessed block is in the left subtree, then the MRU-bit of the node is set to 1.

- If the accessed block is in the right subtree, then the MRU-bit of the node is set to 0.

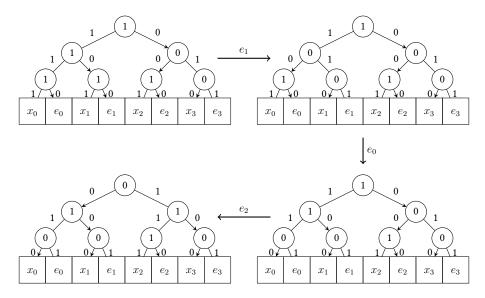

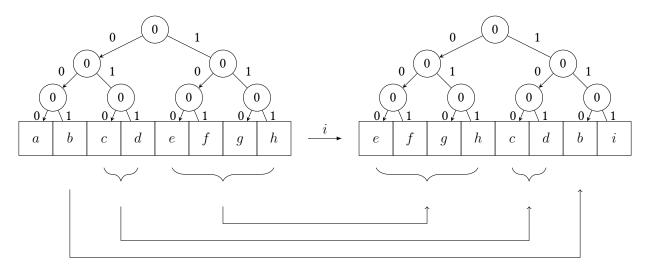

Figure 2.7 – PLRU behavior (To ease reading, we use arrows to reflect the value of nodes, i.e. when node's value is 0 the associated arrow points to left and conversely)

Figure 2.7 illustrates both hit and miss cases:

- The first memory block access is c, and it is cached. Thus, all arrows on the path from the root to the cache line containing c are flipped to point away. The second level arrow already points towards d, it is thus kept unchanged. On the other hand, the first level arrow now points to the left subtree, which does not contain c (the root bit is changed to 0).

- The next access is a miss because e is not cached. We thus find the block to evict by following the arrows. In this case, b is evicted and replaced by e. Finally, all bits on the path to e are flipped.

This policy is named PLRU because it behaves like the LRU policy in case of misses. More specifically, on a long sequence of misses, the cache lines are replaced one by one circularly, mimicking the LRU behavior, up to a permutation of cache lines. However, in the general case, only  $\log_2(k)+1$  accesses might be enough to evict a block that has been stored (see [Rei09]), whereas LRU requires k accesses. Indeed, the tree-bit of a PLRU cache has height  $\log_2(k)$ , and accessing  $\log_2(k)$  blocks can thus change the arrows direction to point to a given cache line. With one more access (a miss), the given cache line is evicted.

#### Writing policies

This thesis mainly focuses on the analysis of instruction caches. Some of the analyses described can be used to analyze data caches, but require some modification. This section describes the aspects that make data caches differ from instruction caches behavior.

In addition to the replacement policy, the behavior of a data cache is described by a write policy. Indeed, contrarily to instruction caches, which are usually read-only, data caches must handle write accesses too.

The first aspect of the write policy consists in specifying whether memory blocks are loaded (allocated) into the cache in case of write accesses. One usually distinguishes two allocation policies:

- The *write allocate* policy simply consists in loading the block into the cache (if needed, i.e., in case of a write miss) before modifying it.

- The *no-write allocate* policy does not load the block in case of a write miss. Instead, the block is modified directly in the next level cache (or main memory). Thus, this policy does not need to evict a block in case of a write miss. The drawback is that successive writes to the same block induce several slower writes at the backing store level.

The second aspect of the write policy concerns the modification of the backing store (i.e., next level cache or main memory) on a write:

- The *write-through* policy forwards the write to the backing store: on a write, the block is modified both in the cache (if loaded, according to the allocation policy) and in the next level cache. One advantage of this policy is that it greatly simplifies the coherence protocol between cache levels. However, it might suffer efficiency penalties when handling repeated writes to the same block.

- The write-back policy modifies the block in the cache, mark it as "dirty", and delays the modification of the next-level cache to the eviction time. When a block is evicted, the cache checks if it is marked dirty. If this is the case, the backing store is updated to reflect the new value of the block (i.e. the evicted block). If the block is not dirty, then the backing store and the cache are consistent and there is no need to modify the backing store.

One can thus distinguish four possible write policies:

- Write allocate, Write-through: this policy is rarely used because the need to modify the next-level cache on each write greatly reduces the advantage of allocating the block.

- Write allocate, Write-back: this policy is the most complex to implement but handles sequences of writes very efficiently. The first write to a given block might suffer a miss, but the next writes will not. Finally, the backing store is only modified once, on the block eviction.

- No-write allocate, Write-through: this policy is the dual of the previous one. It does not handle write sequences very efficiently, but the hardware implementation is simplified.

- No-write allocate, Write-back: again, this policy is rarely used. Indeed, in this configuration, write-back is only useful if the block has been loaded first on a read, because writes do not trigger cache line allocation.

This additional complexity coming from the writing policy make data cache harder to analyze. Not only these analyses must distinguish between write accesses and read accesses, but they also need to track the status of dirty bits in case of write-back caches.

## **Examples of Cache Memories**

Table 2.2 shows some examples of cache memories one can find in different processors. Note that this table only gives a rough idea of the processors behavior and hide many implementation details. In practice, cache memories are often pipelined, and interact with each other through

write-buffers and victim caches<sup>2</sup>, and are tightly coupled with prefetchers or branch predictors. Table 2.2 shows common values of associativity and cache size, but does not reflect the complete cache behavior. Note that detailled information about cache implementation are not always available. Some approaches thus try to infer the cache characteristics from a set of experiments designed do distinguish replacement policies (see [AR14])

| CPU                      | Level | Cache<br>Size | Number of ways | Block<br>Size | Number of sets | Replacement<br>Policy | Details                                      |

|--------------------------|-------|---------------|----------------|---------------|----------------|-----------------------|----------------------------------------------|

|                          | L1I   | 8K            | 2              | 32B           | 128            | LRU                   | -                                            |

| Kalray<br>MPPA           | L1D   | 8K            | 2              | 64B           | 64             | LRU                   | Write-back/<br>Write-through<br>configurable |

|                          | L1I   | 32K           | 8              | 32B           | 128            | PLRU                  | -                                            |

| MPC7450                  | L1D   | 32K           | 8              | 32B           | 128            | PLRU                  | Write-back/<br>Write-through<br>configurable |

|                          | L1I   | 32K           | 32             | 32B           | 32             | FIFO                  | -                                            |

| Intel Core<br>XScale     | L1D   | 32K           | 32             | 32B           | 32             | FIFO                  | Write-back/<br>Write-through<br>configurable |

|                          | L1I   | 32K           | 4              | 64B           | 128            | Unknown               | Write-back<br>No-write allocate              |

| Intel Core<br>i7 Nehalem | L1D   | 32K           | 8              | 64B           | 64             | Unknown               | Write-back<br>No-write allocate              |

| , remarem                | L2    | 256K          | 8              | 64B           | 512            | Unknown               | Write-back                                   |

|                          | L3    | 8M            | 16             | 64B           | 8192           | MRU                   | Write-back                                   |

Table 2.2 – Examples of processor caches

#### 2.1.5 Caches and Address Translation

The analysis of cache behavior require knowledge of the memory address accessed by the program. However, these addresses are not fully known at run-time, because of the address translation mechanism operating systems use to manage the main memory between processes. This section describes this mechanism and how it interferes with caches.

## **Virtual Memory**

To avoid memory corruption, each process running on a system has its own memory areas that no other process can access. However, the location of these areas are unknown at compilation time, and are attributed at running time by the operating system. The solution to this problem is to add an abstraction layer to dissociate the physical memory from the memory used by the program (see [HP12, Chapter 5.7] for more detailed explanations). The program then operates on virtual memory, and all manipulated addresses are translated at run time into physical addresses. This translation is usually performed by the operating system, and accelerated through hardware support.

<sup>&</sup>lt;sup>2</sup>Victim caches are caches that exclusively store blocks that are evicted from another cache.

Figure 2.8 - Virtual Address Translation

For efficiency reasons, address translation is performed by splitting virtual and physical memory into contiguous blocks called pages (a usual page size is 4 KiB). Because pages are aligned in memory, the offset designating a byte inside a page is left unchanged by translation. The remaining part of an address is called the *tag*, and is translated by inspecting the page table. This table being looked up on every memory access translation, it is often cached by a dedicated cache called Translation Lookaside Buffer. The whole translation process is described on Figure 2.8.

# Virtual and Physical Indexing and Tagging

The translation of the virtual address into the physical one must be taken into account when designing cache mechanisms, because it might impact the value of the cache tags, indexes and offsets. Here are some widely used configurations:

- Using the physical address of the blocks to cache them. This is the simplest solution: translate the address first, and then use the physical address to determine the cache set the block should be stored in. However, this solution is also very slow, because one waits until the translation process is finished to perform cache look-up.

- Using the virtual address of the block to cache it. This solution can be more efficient than the previous one because cache look-up and address translation can be performed in parallel, and address translation is bypassed in case of cache hits. However, using the virtual cache index and the tag can lead to complications, because the same virtual address can refer to two different blocks when used in two different processes. In this case, either the operating system flushes the cache on a context switch, or the cache stores an address space identifier in addition to the tag to distinguish between the two synonym blocks.

- A trade-off between these two strategies consists in using a virtual index and a physical

tag. The cache set a block is potentially cached in is then identified during the address

translation and the physical tag is available when looking up the cache set. This solution

however imposes some constraints on cache configuration because both cache offset and

index should fit into the page offset.

- Finally, more complex strategies can be considered by relying on extra hardware support or by taking advantage that some caches are read-only.

In this thesis, we do not consider the address translation mechanism and we assume that every memory access is associated with an address known at compile time. This assumption is obviously safe in the case of caches using virtual tags and indexes, because the addresses manipulated by the program and the cache are identical (the virtual addresses are used by both). In this thesis, we only consider L1 instruction caches, which usually work with indexes and offsets that both fit in the page offset. Cache offset and index are thus invariant by translation. We thus additionally assume that mapping from virtual pages to physical pages is injective for pages containing instructions.

# 2.1.6 Cache configuration in this thesis

The idea of caches, i.e., storing frequently used data in fast memories to speed computation up, is simple and natural. However, the practical implementations of hardware caches involve many efficiency/cost trade-offs, and the mechanisms used to maximize performance of modern CPU are very complex.

Thus, in order to study the possible behaviors of a program in relation to the cache, this thesis makes several simplifying assumptions. Mainly, we focus on the analysis of L1 instruction caches that use the LRU policy, for several reasons:

- Analyzing data caches requires knowledge about data addresses, which can lead to complex static analysis problem (e.g., pointer aliasing analyses), out of the scope of this thesis. We thus focus on the analysis of instruction caches, because instruction addresses are more predictable than data addresses. However, in case the addresses of data accessed are known, some approaches developed in this thesis might be used to analyze data caches, by adapting them slightly to take the writing policy into account (see Section 6.1).

- Higher level caches usually mix instructions and data, and thus suffer the same analysis difficulties as data caches. In addition, analyzing caches beyond level L1 requires to take complex cache coherence protocol into account. Finally, L3 caches are often shared, and can thus suffer from interferences from other cores. Note that a part of the complexity in analyzing higher-level caches comes from the difficulty of predicting hits and misses at lower level. Thus, a precise cache analysis at level L1 would benefit higher-level cache analyses.

- Concerning the replacement policy, we focus on LRU because, as shown in chapter 3, it already leads to high complexity problems. Other replacement policies lead to even harder classification problems (see Section 6.1).

# 2.2 Static Analysis

Static analysis consists in proving properties of a program without having to execute it, as opposed to dynamic program analysis, which ensures that the program behaves correctly on some inputs

by executing it. The main reason to perform static analysis rather than dynamic analysis is that the first can guarantee that a given property is true for all program executions, whereas the second guarantees that the property is true only on the tested inputs.

The fundamental drawback of static analysis techniques is that the vast majority of properties one would like to prove about a program are undecidable. Is is thus impossible to build to a static analyzer that decides such a property and is correct for any program on any input. One way to circumvent this problem is to allow the static analyzer to answer "unknown" when deciding if a property holds or not. In this case, running a static analysis tools leads to one of the following outcomes:

- the analyzer is able to cover all inputs of the program and check that the desired property holds. The program is then accepted.

- the analyzer is able to find at least one input value for which the program behavior is incorrect. The program is then rejected.

- the analyzer answers "unknown", it is not able to ensure the correctness of all behaviors of the program. The program might be correct, but is rejected.

This section introduces two static analysis methods that tackle the undecidability problem:

- Abstract Interpretation computes over-approximations to cover all the possible program

behaviors. If the over-approximations performed are sound, then this approach guarantees

that the desired property holds for any execution of the program. Indeed, if the property

holds for all the behaviors covered by the analysis, then it must hold for the subset of behaviors that the program can exhibit. However, if the approximation performed is too coarse, a

correct program (i.e., satisfying the property) might be rejected because spurious behaviors

are taken into account.

- Model Checking consists in checking the correctness of a finite model of the program by exhaustively exploring all its states <sup>3</sup>. Symbolic Model Checking [McM93] relies on an implicit representation of the state space. Using compact descriptions of Boolean functions, one can represent a huge state space in a reasonable model.

One can choose an abstraction of the program as a model; such an approach is thus tightly related to abstract interpretation.

These two methods offer different performance performance/precision trade-off, and are thus complementary. We thus use both of them in this thesis.

# 2.2.1 Abstract Interpretation

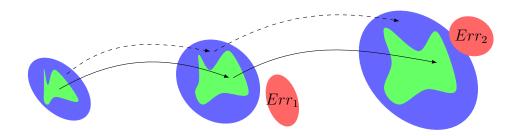

Abstract interpretation [CC77] is a framework used to ensure the soundness of over-approximations. The main idea is to characterize all possible program states using a representation that is expressive enough to prove the desired property, but allows fast computations. This is illustrated on Figure 2.9: green shapes symbolize the evolution of possible programs states step by step. The solid arrows are examples of transition from one concrete state to another one. Blue ellipses represent over-approximations of the sets of concrete states, and dashed arrows

$<sup>^{3}</sup>$ In Bounded Model Checking [CBRZ01], one truncates the program execution after k steps. The resulting model is then obviously finite but the method is unsound, as it might miss incorrect behaviors that happen after the kth step.

Figure 2.9 – Over-approximation of program states

symbolizes the transition between over-approximations. If the over-approximation does not cover any invalid state (in red on the figure), then the program is safe. In our example, this is illustrated by the error states  $Err_1$ , which are guaranteed to be unreachable because they do not intersect the blue ellipses (and thus, they do not intersect the green shape). However, it might be that the program is safe but rejected by the analyzer because of the precision loss. This phenomenon, called "false alarm", corresponds to the  $Err_2$  states on Figure 2.9. They are unreachable (they do not intersect the green shape) but the analysis can not prove it (they intersect the blue area).

## **Control Flow Graph**

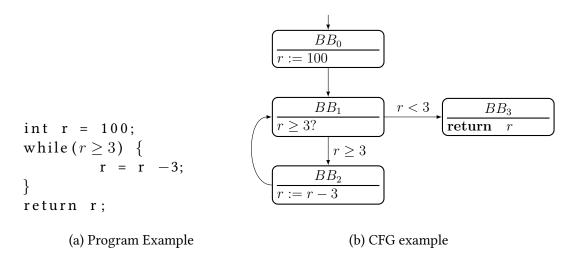

In order to formalize the notion of program execution we use the concept of Control-Flow Graph (CFG), which represents all the possible execution paths of a program. A CFG is a directed graph whose nodes, called basic blocks, symbolize sequences of instructions which flow cannot be broken: once the execution reaches the first instruction of a basic block, the whole block is executed sequentially until the end. Outgoing edges represent the flow to the next possible basic blocks that can be executed. A CFG is a data structure that represents all possible program execution paths. The program is then modeled by representing each function by its CFG.

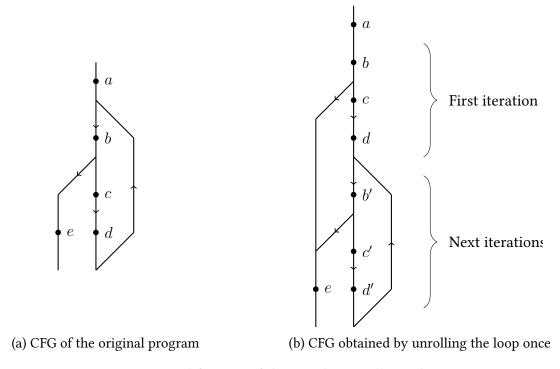

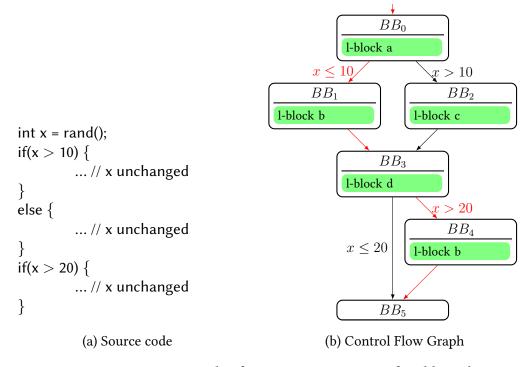

Figure 2.10 – A simple program and its associated Control-Flow Graph

Consider the program of listing 2.10a, which performs a naive Euclidean division. We will use this program as an example in this section. Figure 2.10b then represents the CFG of this program and shows how the program executes:

- The program starts at the entry node, basic block  $BB_0$ , where the value 100 is stored in variable r.

- The execution proceeds in basic block  $BB_1$ . The current value of r is compared to 3, and because it is greater, the execution flow goes to basic block  $BB_2$ .

- In  $BB_2$  r is decremented by 3, and thus takes value 97.

- $BB_1$  is executed again and the new value of r is compared to 3.

- After 33 iterations of the loop, r has value 1, and the flows finally goes to the final block  $BB_3$ .

In this thesis, the notation  $G=(V,E,v_0)$  denotes a graph where V is the set of basic blocks,  $E\subseteq V^2$  is the set of edges, and  $v_0\in V$  is the entry node, which is assumed to be unique. In our example, we have:

$$V = \{BB_0, BB_1, BB_2, BB_3\}$$

$$E = \{(BB_0, BB_1), (BB_1, BB_2), (BB_2, BB_1), (BB_1, BB_3)\}$$

$$v_0 = BB_0$$

#### **Concrete Semantics**

In the context of abstract interpretation, the behavior of a program is captured by its concrete semantics, which is given by two elements:

- a concrete domain  $D_{conc}$  which can precisely express all possible program states. A frequent choice is to use a map that associates a value to each variable of the program. In the case of our division example we have one variable r, and there is no need to use such a map. Instead, one can use the concrete domain  $D_{conc} = \mathbb{Z}$  that tracks the value of r.

- a set of transformers are introduced to model the effect of program instructions. These transformers are functions from  $D_{conc}$  to  $D_{conc}$  that, given the value at the entry of a basic block, computes the value at the end of this block. In our example, the transformers that capture the program behavior are the following:

$$\begin{array}{lll} - \ f_{BB_0} : r \mapsto 100 & - \ f_{BB_1} : r \mapsto r \\ \\ - \ f_{BB_2} : r \mapsto \begin{cases} r-3 & \text{if } r \geq 3 \\ \text{undefined} & \text{otherwise} \end{cases} & - \ f_{BB_3} : r \mapsto \begin{cases} r & \text{if } r < 3 \\ \text{undefined} & \text{otherwise} \end{cases} \end{array}$$

Basic blocks  $BB_1$  and  $BB_3$  do not modify r, whereas basic blocks  $BB_0$  and  $BB_2$  set it to 100 and decrement it by 3 respectively (if the guard is satisfied).

Given a finite path in the CFG of the program and an initial value in the concrete domain, one can apply the sequence of transformers associated to the sequence of blocks met along the path

<sup>&</sup>lt;sup>4</sup>Note that some authors call *concrete domain* what we later call the *collecting semantics domain*. Here, we use the same convention than [Rei09].

and get the concrete value describing the program state at the end of the path. In our example, given the path  $(BB_0, BB_1, BB_2, BB_1, BB_2)$ , one would obtain for a concrete initial value r:

$$(f_{BB_2} \circ f_{BB_1} \circ f_{BB_2} \circ f_{BB_1} \circ f_{BB_0})(r) = (f_{BB_2} \circ f_{BB_1} \circ f_{BB_2} \circ f_{BB_1})(100)$$

$$= (f_{BB_2} \circ f_{BB_1} \circ f_{BB_2})(100)$$

$$= (f_{BB_2} \circ f_{BB_1})(97)$$

$$= f_{BB_2}(97)$$

$$= 94$$

This value obtained at the end of basic block  $BB_2$  after two loop iterations is independent of the initial value of r, because the first instruction of the program erases this initial value and replaces it by 100.

This process can be used to define the concrete value after the execution of any path, but one is generally more interested in the set of all possible program states at a given location, whatever the execution path is, rather than a single concrete value. In our example, one could be interested in the set of values that reach basic block  $BB_2$  for instance, to check that the subtraction never results in an overflow.

This computation of all concrete values at a program location v is what the collecting semantics  $F: V \to \mathcal{P}(D_{conc})$  achieves, by aggregating the concrete values obtained for all paths ending at v.

Before giving a formal definition of the collecting semantics, we illustrate how it can be computed on our example. First, we look at the set of concrete values that can reach the entry block. At this point r is not initialized yet, and we thus assume that any integer value is reachable. Hence, we have  $F(BB_0) = \mathbb{Z}$ . Then, after the execution of  $BB_0$ , all these values are replaced by the assigned value 100. This gives the following inclusion:  $F(BB_1) \supseteq \{100\}$ . By propagating this information, one get that  $F(BB_2) \supseteq \{100\}$  because 100 satisfies the guard condition  $r \ge 3$ . We thus deduce that  $\{97\}$  is a subset of values reaching the end of  $BB_2$ , and that therefore it is a subset of  $F(BB_1)$ . This lead to the new inclusion  $F(BB_1) \supseteq \{97, 100\}$ , by combining the new reachable value with the set of reachable values previously computed. By iterating this process, one gets to the point where we know  $F(BB_1) \supseteq \{1, 4, \dots, 97, 100\}$ . To propagate this set through the edge  $(BB_1, BB_2)$ , it is intersected once again with the edge condition  $r \geq 3$ , leading to  $F(BB_2) \supseteq \{4, 7, \dots, 97, 100\}$ . We thus deduce that  $\{1, 4, \dots, 94, 97\}$  is subset of values reachable at the end of block  $BB_2$ . For the first time, this set is included in the set of values reaching  $BB_1$  previously. The process finally stabilizes, and we know that the exact set of values reaching  $BB_1$  is  $F(BB_1) = \{1, 4, \dots, 97, 100\}$ . By intersecting it with the edge guard r < 3, we then deduce that  $F(BB_3) = \{1\}$ . The final solution obtained by this iterating process is thus:

•

$$F(BB_0) = \mathbb{Z}$$

•  $F(BB_2) = \{4, 7, \dots, 97, 100\}$

•  $F(BB_1) = \{1, 4, \dots, 97, 100\}$  •  $F(BB_3) = \{1\}$

Intuitively, the values that reach the beginning of a block can be computed from the values coming from predecessors. This leads to the formal definition of the collecting semantics F, as the least fixpoint solution of the following equation:

$$\forall v \in V, F(v) = F_0(v) \bigcup_{(u,v) \in E} \{f_u(c), c \in F(u)\},$$

where

$$F_0(v) = \begin{cases} \{c_0\} & \text{if } v = v_0 \\ \{\} & \text{otherwise} \end{cases}$$

F(u) is the set of values that reach the beginning of the basic block u. Thus,  $\{f_u(c), c \in F(u)\}$  is the set of values that reach the end of u. By computing the union of all those sets over all predecessors u of v, one obtains the set of values reaching the basic block v. The term  $F_0(v)$ , where  $F_0: V \to D_{conc}$ , is added to take the entry value into account. It is always empty, except for the entry node, which is reached with initial value  $c_0$ .

The solution F of this fixpoint equation is guaranteed to exist<sup>5</sup>. However, the iterating process described above is not guaranteed to reach a fixpoint in finite time.

#### **Abstract Semantics**

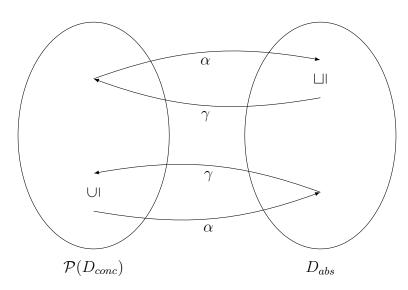

To avoid this expensive computation and/or ensure that the process finishes, one computes an approximation of the concrete collecting semantics instead of the collecting semantics itself. The main idea is that a set  $X \subseteq D_{conc}$  of concrete values will be abstracted by a single value  $\alpha(X)$ . This value  $\alpha(X)$  then represents all values in X, and possibly other additional concrete values (in blue in Figure 2.9). The function  $\alpha: \mathcal{P}(D_{conc}) \to D_{abs}$  is called an abstraction and  $D_{abs}$  is named the abstract domain.

In our example, one possible abstraction is to use an integer interval instead of a set of integers. For instance, the set  $\{97,100\}$  will be abstracted by  $\alpha(\{97,100\})=[97,100]$ . Thus,  $\alpha(\{97,100\})$  covers the set  $\{97,100\}$ , plus the extra values 98 and 99. This abstraction function  $\alpha$  is then defined by:

$$\alpha: \mathcal{P}(\mathbb{Z}) \to \mathbf{Intervals}$$

$$X \mapsto [\min X, \max X]$$

To make the usage of an abstraction meaningful,  $D_{abs}$  and  $\alpha$  are required to satisfy some properties (see [CC77]):

- D<sub>abs</sub> must be equipped with an order relation (i.e., reflexive, transitive and antisymmetric)

⊑ that makes it a complete lattice (D<sub>abs</sub>, ⊑, ⊒, ⊔, □). This relation represents the relative preciseness of abstract values: if x ⊑ y then x is more precise than y.

- $\alpha$  is monotonic:  $X \subseteq Y \Rightarrow \alpha(X) \sqsubseteq \alpha(Y)$ , i.e. it conserves the preciseness relation.

The requirement that  $D_{abs}$  should be a lattice ensures that any abstract values x and y can be joined together in one that approximates both:  $x \sqcup y$ . This is needed to compute the abstract value at the entry of a block that has many predecessors. In the Euclidean division example, after the two loop iterations the value at the beginning of basic block  $BB_1$  is built from the value [100, 100] coming from  $BB_0$ , and the value [94, 97] coming from  $BB_2$ . These two values are joined together into the single interval [94, 100]. Note that this join operation has lost precision, because it covers values that were not represented in any of the two joined intervals (namely 98 and 99). If x and

<sup>&</sup>lt;sup>5</sup>This results from Tarski's fixpoint theorem [Tar55], knowing that F is continuous and  $D_{conc}$  is a complete lattice.

y are the abstract values at the end of predecessors, then  $x \sqcup y$  is the most precise abstract value that covers all concrete values represented by x and y.

An equivalent possibility is to express the relation between concrete and abstract value by introducing a concretization function  $\gamma:D_{abs}\to \mathcal{P}(D_{conc})$  instead of the abstraction  $\alpha$ . This concretization associates to an abstract value the set of concrete values it approximates. For instance, the concretization one would use in our example is the following:

$$\gamma : \mathbf{Intervals} \to \mathcal{P}(\mathbb{Z})$$

$[a, b] \mapsto \{x \in \mathbb{Z}, a \le x \le b\}$

To ensure consistency of the definitions, the  $(\alpha, \gamma)$  pair is required to be a Galois connection [CC77], i.e. it must satisfy the following properties:

- $\forall X \in \mathcal{P}(D_{conc}), (\gamma \circ \alpha)(X) \supseteq X$

- $\forall x \in D_{abs}, (\alpha \circ \gamma)(x) \subseteq x$

Figure 2.11 – Composition of abstraction and concretization

These conditions ensure that one cannot lose safety, but only precision, by repetitively applying  $\alpha$  and  $\gamma$  to a value. By abstracting a concrete value x by  $\alpha(x)$ , we over-approximate it. If the set resulting from the concretization of  $\alpha(x)$  does not contain x, then this over-approximations is incorrect. For example, by abstracting and concretizing the set  $\{97,100\}$ , one obtains  $\gamma(\alpha(\{97,100\})) = \gamma([97,100]) = \{97,98,99,100\}$ . This value covers the input  $\{97,100\}$ , illustrating the correctness of the  $(\alpha,\gamma)$  pair. Figure 2.11 illustrates how these compositions of concretization and abstraction behave. By applying one after the other, one can only go "higher" in the lattice and lose precision. Note that when  $(\alpha,\gamma)$  is a Galois connection,  $\alpha$  uniquely defines  $\gamma$  and conversely (see [NNH99, p. 239] for a proof).

Once an abstraction is chosen, one must define the abstract transformer associated to each basic block. These abstract transformers are the abstract counterpart of the concrete transformers and express the program behavior in the abstract domain. One way to define the abstract transformers is to compose the concrete transformers with the abstraction and concretization functions. The obtained functions,  $f_v^\# = \alpha \circ f_v \circ \gamma$ , are the most precise abstract transformers that can be used, and are called the best abstract transformers. In our example, the best abstract transformers are:

•

$$f_{BB_0}^{\#}: [a,b] \mapsto [100,100]$$

•

$$f_{BB_1}^{\#}: [a,b] \mapsto [a,b]$$

•

$$f_{BB_2}^{\#}: [a,b] \mapsto \begin{cases} \emptyset & \text{if } [a,b] \cap [3,+\infty] = \emptyset \\ [a'-3,b'-3] & \text{if } [a,b] \cap [3,+\infty] = [a',b'] \end{cases}$$

$$\bullet \ f^\#_{BB_3}: [a,b] \mapsto \begin{cases} \emptyset & \text{if } [a,b] \cap [-\infty,2] = \emptyset \\ [a',b'] & \text{if } [a,b] \cap [-\infty,2] = [a',b'] \end{cases}$$

This family of transformers can be used to derive the abstract collecting semantics  $F^{\#}:V\to D_{abs}$ , which is defined similarly to the concrete collecting semantics but in the abstract domain. More formally,  $F^{\#}$  is a solution of the fixpoint equation:

$$\forall v \in V, F^{\#}(v) = F_0^{\#}(v) \bigsqcup_{(u,v) \in E} \{f_u^{\#}(F^{\#}(u))\},$$

where  $F_0^{\#} = \alpha \circ F_0$

In our case, applying the iteration process described previously for the concrete collecting semantics yield the following solution:

•

$$F^{\#}(BB_0) = [-\infty, \infty]$$

•  $F^{\#}(BB_2) = [3, 100]$

•

$$F^{\#}(BB_1) = [0, 100]$$

•  $F^{\#}(BB_3) = [0, 2]$

Note that those values completely cover the results obtained by the concrete collecting semantics.

#### **Analysis Soundness**

The main benefit of the abstract interpretation framework is the soundness proofs it automatically provides. Indeed, it is guaranteed that the fixpoint reached by the abstract collecting semantics covers all the values collected in the concrete domain:

$$\forall v \in V, F(v) \subseteq \gamma(F^{\#}(v))$$

In addition, this soundness proof can be generalized to any set of safe transformers. Let  $\widehat{(f_v^\#)}_{v\in V}$  and  $\widehat{\sqcup}$  verifying the two following safety conditions:

$$\forall v \in V, \forall x \in D_{abs}, f_v(\gamma(x)) \subseteq \gamma(\widehat{f_v^{\#}}(x))$$

$$\forall (x, y) \in D_{abs}^2, \gamma(x) \cup \gamma(y) \subseteq \gamma(x \widehat{\sqcup} y)$$

These conditions ensure that abstract transformers correctly captured their concrete counterpart. A safe over-approximations cannot become unsafe by applying the abstract transformer. This means that no concrete behavior of the program can be lost during the abstract interpretation. Note that those conditions trivially hold for the best abstract transformers and the abstract lattice join operator. When those conditions hold, any fixpoint  $\widehat{F^{\#}}$  of the following equation:

$$\forall v \in V, \widehat{F^{\#}}(v) = \widehat{F_0^{\#}}(v) \widehat{\bigsqcup}_{(u,v) \in E} \{ \widehat{f_u^{\#}}(x), x \in \widehat{F^{\#}}(u) \},$$

where  $\widehat{F_0^{\#}} \supseteq \alpha \circ F_0$

is guaranteed to satisfy the soundness property:

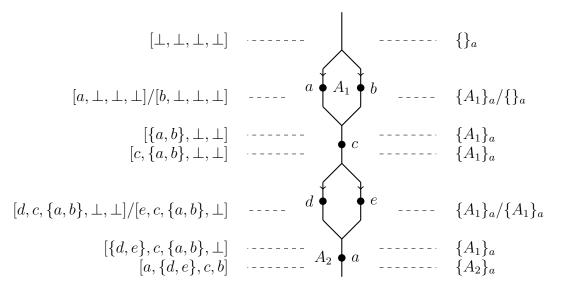

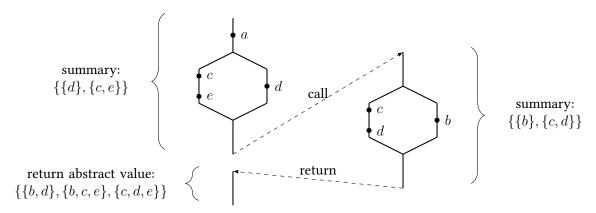

(a) Example of boolean program

$$\forall v \in V, F(v) \subseteq \gamma(\widehat{F^{\#}}(v))$$

Note that the iteration process described above (sometimes referred as chaotic iteration, or worklist algorithm) is not guaranteed to terminate in general. However, all abstract domains introduced in this thesis are finite, and thus, the process is guaranteed to terminate without additional requirements.

Many cache analyses introduced in this thesis are formalized in the abstract interpretation framework. The different concrete and abstract domains introduced then represented several aspect of the cache state/behavior.

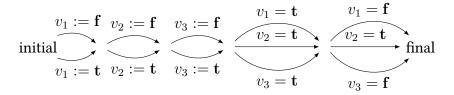

# 2.2.2 Model Checking

Model Checking [EC82] is a static analysis method that is used to ensure that some system satisfies a given property. The system is described by a set of variables and is modeled as finite state machine, and the property to check is modeled as a temporal formula over those variables. The role of the model checker is then to ensure that the finite state machine evolves safely according to the formula.

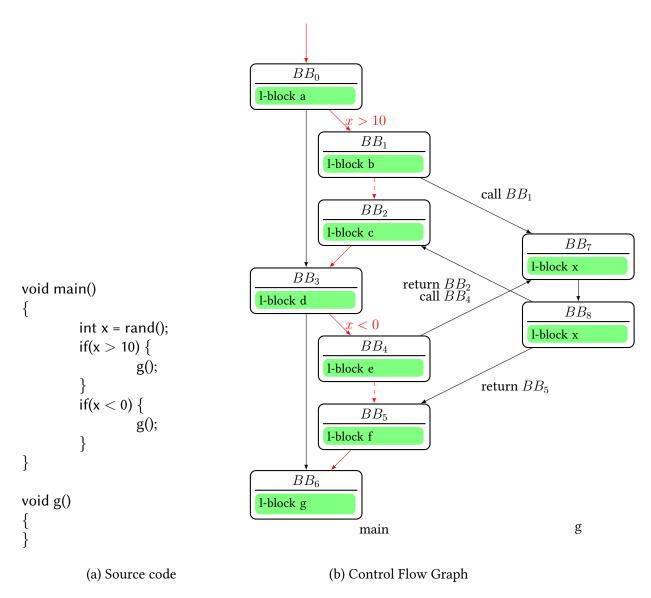

Figure 2.12 - A simple program and its associated Kripke structure

(b) Example of Finite State Machine

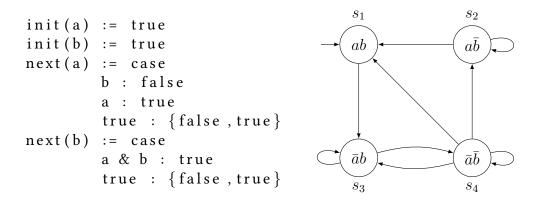

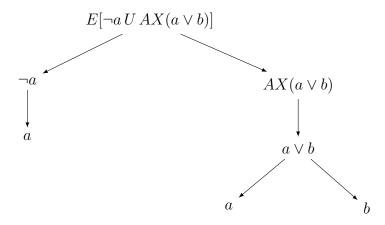

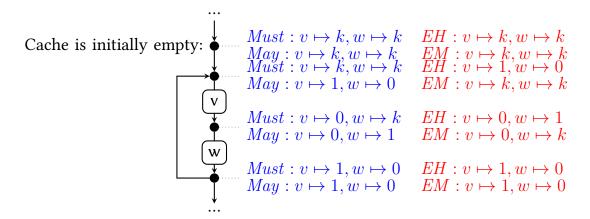

To give the intuition of how model checkers work, this section focuses on the model checking of Boolean programs (i.e. programs manipulating boolean variables only). Most modern model checkers support integer variables, sometimes relying on a Satisfiability Modulo Theory solvers, but we do not consider those complex solvers in this thesis. Consider the Boolean (non-deterministic) program of Listing 2.12a. This program is composed of two parts:

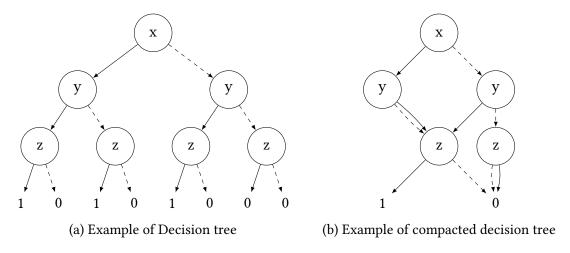

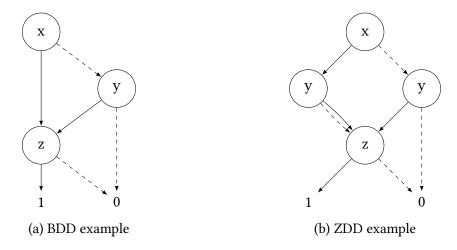

- The initialization of all variables. In our cases, both *a* and *b* are initially set to true.