## Hybridation CMOS/STT-MRAM des circuits intégrés pour la sécurité matérielle de l'internet des Objets

Mounia Kharbouche-Harrari

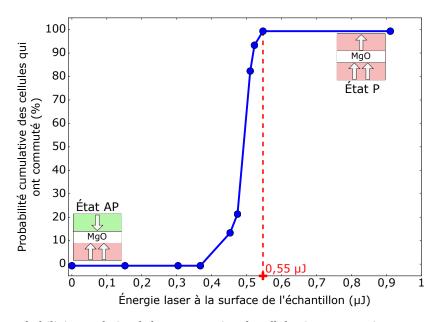

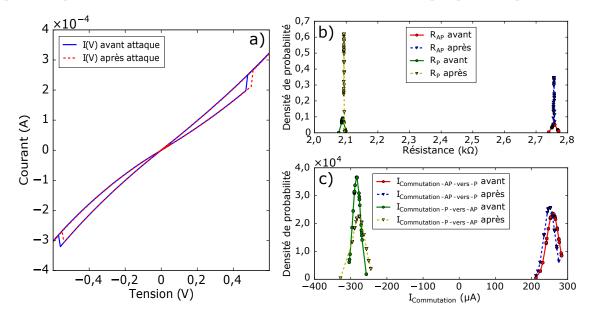

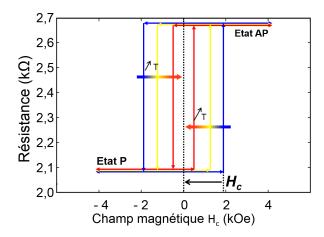

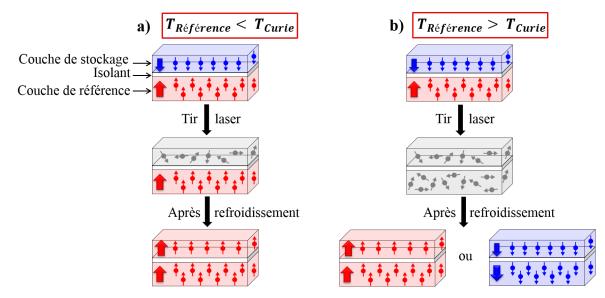

#### ▶ To cite this version:

Mounia Kharbouche-Harrari. Hybridation CMOS/STT-MRAM des circuits intégrés pour la sécurité matérielle de l'internet des Objets. Micro et nanotechnologies/Microélectronique. Université d'Aix-Marseille (AMU), 2019. Français. NNT: . tel-02422442

### HAL Id: tel-02422442 https://hal.science/tel-02422442

Submitted on 22 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# AIX-MARSEILLE UNIVERSITÉ ECOLE DOCTORALE 353

IM2NP - UMR CNRS 7334

En collaboration avec le CEA Tech et Spintec

Thèse présentée pour obtenir le grade universitaire de docteur

Discipline : Sciences pour l'Ingénieur Spécialité : Micro et Nanoélectronique

#### Mounia KHARBOUCHE-HARRARI

# Hybridation CMOS/STT-MRAM des circuits intégrés pour la sécurité matérielle de l'Internet des Objets

#### Soutenue le 09/12/2019 devant le jury composé de :

Bruno Rouzeyre Professeur des Universités, LIRMM Président Professeur des Universités, Paris Sud Jacques-Olivier Klein Rapporteur Lorena Anghel Professeur à l'INP, Grenoble Rapporteure Jean-Luc Danger Directeur d'études, Telecom ParisTech Examinateur Professeur des Universités, IM2NP Jean-Michel Portal Directeur de thèse Ingénieur de recherche CNRS, Spintec Encadrant Gregory Di Pendina Ingénieur-chercheur, CEA-Tech Romain Wacquez Encadrant Jérémy Postel-Pellerin Maître de conférences, IM2NP Encadrant Driss Aboulkassimi Ingénieur-chercheur, CEA-Tech Encadrant

Numéro national de thèse/suffixe local : 2019AIXM0621/039ED353

### Remerciements

Ces travaux de thèse ont été menés au sein de l'équipe commune CEA tech et École des Mines de Saint-Étienne 'SAS' située à Gardanne, en collaboration avec les laboratoires CNRS-SPINTEC (équipe 'Spintronics IC Design') à Grenoble et IM2NP (équipe 'Mémoires') à Marseille.

Mes premiers remerciements vont à mon encadrement de thèse, Jean-Michel, Jérémy, Gregory, Romain et Driss. Je vais regretter ces trois années qui ont été d'une extrême richesse scientifique grâce à vous et à vos différentes expertises. Nous avons pu explorer ensemble un nouveau sujet de recherche mêlant sécurité et hybridation CMOS/STT-MRAM.

Un immense merci à Lorena Anghel et Jacques-Olivier Klein pour leurs rapports et leurs conseils sur l'amélioration de la compréhension de certains points de ce manuscrit de thèse. Merci également à Bruno Rouzeyre et Jean-Luc Danger pour avoir examiné ces travaux et pour les discussions constructives que nous avons pu partager lors de la soutenance.

Je tiens évidemment à remercier toutes les personnes avec qui j'ai partagé un bureau au fil de ces trois années: Thomas, Paul, David, Raphaël, Alexis, Damien, Benjamin, Alexandre, Antoine, Meriem, Amina, Clément, Lina, Élise et Rémi. Cela a été un immense plaisir de partager avec vous au quotidien. Merci évidemment à tous les membres de l'équipe commune 'SAS' avec qui j'ai eu plaisir d'échanger et qui êtes restés à mon écoute en tout temps.

Je souhaite également remercier toutes les personnes qui ont facilité l'accomplissement de ces travaux : Anaïs, Michelle, Séverine et Bastien. Tous les membres de la plateforme Micro-PackS pour votre bonne humeur au quotidien ainsi que pour tout votre soutien lors de la mise en place du banc de test des circuits fabriqués lors du projet GREAT.

Toute l'équipe mémoire de l'IM2NP et en particulier Marc et Vincenzo qui m'ont été d'une grande aide lors de ma première année de thèse et avec qui j'ai eu un plaisir immense d'échanger. Je tiens également à remercier Guillaume, Rana, Lucian, François et Odilia de Spintec pour tout le contenu technique que nous avons partagé, pour votre sympathie et surtout votre accueil au sein de l'équipe; malgré la distance, cela n'a jamais été un frein.

Pour finir, merci à ma famille et mes amis qui m'ont beaucoup soutenu au fil de ces années; en particulier mon époux, Elias, qui m'a énormément soutenu pendant toutes les phases de la thèse, pendant les hauts et surtout les phases de stress. Encore merci à toi!

> Bien à vous. Mounia

## Table des matières

| In | trodu | uction  | général    | e                                                 | 1  |

|----|-------|---------|------------|---------------------------------------------------|----|

| 1  | Séci  | urisati | on des c   | circuits intégrés                                 | 3  |

|    | 1     | Enjeu   | ıx de la s | sécurité dans l'Internet des Objets               | 4  |

|    | 2     |         |            | gies mémoires                                     | 5  |

|    |       | 2.1     | Les tec    | chnologies mémoires traditionnelles               | 5  |

|    |       |         | 2.1.1      | Les mémoires volatiles                            | 5  |

|    |       |         | 2.1.2      | Les mémoires non-volatiles                        | 6  |

|    |       | 2.2     | Les mé     | émoires émergentes                                | 7  |

|    |       |         | 2.2.1      | Les mémoires résistives ReRAM                     | 7  |

|    |       |         | 2.2.2      | Prérequis à la MRAM                               | 9  |

|    |       |         | 2.2.3      | Les technologies MRAMs                            | 11 |

|    | 3     | Sécur   | ité des c  | circuits intégrés                                 | 18 |

|    |       | 3.1     | La cryp    | ptographie et ses enjeux                          | 19 |

|    |       |         | 3.1.1      | L'histoire de la cryptographie                    | 19 |

|    |       |         | 3.1.2      | La cryptographie asymétrique                      | 19 |

|    |       |         | 3.1.3      | La cryptographie symétrique                       | 21 |

|    |       | 3.2     | Les dif    | férentes techniques d'attaques matérielles        | 24 |

|    |       |         | 3.2.1      | Les attaques par observation                      | 24 |

|    |       |         | 3.2.2      | Les attaques par perturbation                     | 25 |

|    |       |         | 3.2.3      | Les fautes et leurs modèles                       | 28 |

|    | 4     | Sécur   |            | s la logique hybride CMOS/STT-MRAM                | 29 |

|    |       | 4.1     |            | plications "normally-off/instant-on"              | 29 |

|    |       | 4.2     | Les str    | uctures hybrides CMOS/STT-MRAM                    | 30 |

|    |       |         | 4.2.1      | Les bascules non-volatiles                        | 30 |

|    |       |         | 4.2.2      | Les bascules multi-contextes CMOS/STT-MRAM        | 30 |

|    |       | 4.3     | Les arc    | chitectures hybrides de sécurité                  | 31 |

|    |       |         | 4.3.1      | Les PUFs                                          | 31 |

|    |       |         | 4.3.2      | Les TRNGs                                         | 32 |

|    | 5     | Conc    | lusion .   |                                                   | 33 |

| 2  | Inté  | grité d | les mém    | noires STT-MRAMs                                  | 35 |

|    | 1     | Le LA   | SER        |                                                   | 36 |

|    |       | 1.1     | Princip    | pe de fonctionnement d'une source LASER           | 36 |

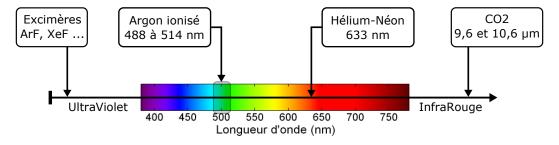

|    |       | 1.2     | Les dif    | férentes catégories de LASERs                     | 39 |

|    |       |         | 1.2.1      | Les lasers à gaz                                  | 39 |

|    |       |         | 1.2.2      | Les lasers à liquides (ou à colorants chimiques)  | 39 |

|    |       |         | 1.2.3      | Les lasers à solides                              | 39 |

|    | 2     | Inject  | tion de f  | autes par laser sur jonctions unitaires STT-MRAMs | 40 |

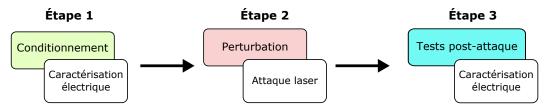

|    |       | 2.1     | Protoc     | ole expérimental                                  | 40 |

|    |       |         |            | Conditionnement initial des cellules STT-MRAMs    | 41 |

|   |     |        | 2.1.2 Le banc de caractérisation physique : Laser Nd-YAG                    | 44         |

|---|-----|--------|-----------------------------------------------------------------------------|------------|

|   |     |        | 2.1.3 Résultats expérimentaux de la caractérisation sécuritaire de STT-MRAM | s 45       |

|   |     |        | 2.1.4 Fiabilité du point mémoire STT-MRAM post-attaque                      | 47         |

|   |     | 2.2    | Discussion sur les phénomènes physiques induisant la commutation des cel-   |            |

|   |     |        | lules STT-MRAMs                                                             | 48         |

|   |     |        | 2.2.1 Commutation de la JTM au niveau circuit                               | 48         |

|   |     |        | 2.2.2 Commutation de la JTM au niveau spins                                 | 49         |

|   | 3   | Modè   | ele thermique COMSOL de l'attaque LASER                                     | 50         |

|   |     | 3.1    | Le transfert de chaleur dans les solides                                    | 50         |

|   |     | 3.2    | Proposition de contre-mesures                                               | 52         |

|   | 4   | Concl  | lusion et perspectives                                                      | 53         |

| 3 | Dét |        | 1 1 1                                                                       | 55         |

|   | 1   | Straté | égies de durcissement des circuits intégrés                                 | 56         |

|   |     | 1.1    | Protections contre les attaques par canaux cachés                           | 56         |

|   |     |        | 1.1.1 Principe de dissimulation                                             | 56         |

|   |     |        | 1.1.2 Principe de masquage                                                  | 57         |

|   |     | 1.2    | Protections contre les injections de fautes                                 | 57         |

|   |     |        | 1.2.1 Diminution de la sensibilité du circuit face aux attaques par pertur- |            |

|   |     |        |                                                                             | 57         |

|   |     |        | 1 1 1                                                                       | 58         |

|   |     | 1.3    |                                                                             | 61         |

|   |     |        | 1 1                                                                         | 61         |

|   |     |        |                                                                             | 61         |

|   | 2   |        | 1 1 1                                                                       | 62         |

|   |     | 2.1    | 1                                                                           | 63         |

|   |     |        | 1                                                                           | 63         |

|   |     |        | 1 0                                                                         | 65         |

|   |     | 2.2    | 1 ,                                                                         | 66         |

|   |     | 2.3    | 1 1                                                                         | 66         |

|   |     |        | ±                                                                           | 66         |

|   |     |        |                                                                             | 68         |

|   |     |        | 1                                                                           | 69         |

|   | 3   | Concl  | lusion et perspectives                                                      | 70         |

| 4 | Imp |        | •                                                                           | 71         |

|   | 1   | _      | 71 0 1 0                                                                    | 72         |

|   |     | 1.1    | 0 71 0 1 0                                                                  | 72         |

|   |     | 1.2    | e                                                                           | 73         |

|   | 2   |        | · ·                                                                         | 74         |

|   |     | 2.1    | •                                                                           | 75         |

|   |     |        | · · ·                                                                       | 75         |

|   |     |        | 1 ,                                                                         | 75         |

|   |     | 2.2    | 1 1 1                                                                       | 76         |

|   |     |        | 2.2.1 Flot de conception standard de l'algorithme PRESENT en technolo-      | <b>-</b> 6 |

|   |     |        |                                                                             | 76         |

|   |     |        | 1                                                                           | 79         |

|   |     |        | ı                                                                           | 80         |

|   |     | 2.3    | Flot de conception hybride CMOS/STT-MRAM de l'algorithme de cryptogra-      |            |

|   |     |        | •                                                                           | 80         |

|   |     |        |                                                                             | 81         |

|   |     |        | 2.3.2 Scénario #2 : schéma d'écriture partiellement série des NVFFs         | 82         |

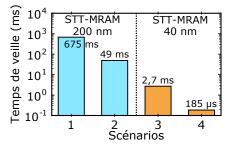

|       |          | 2.3.3     | Résumé des résultats des implémentations réalisées                 | 83  |

|-------|----------|-----------|--------------------------------------------------------------------|-----|

|       |          | 2.3.4     | Évolution des densités de courants en fonction du nœud technolo-   |     |

|       |          |           | gique de la STT-MRAM                                               | 84  |

|       | 2.4      | Estima    | ation des performances du chiffrement PRESENT pour les nœuds tech- |     |

|       |          | nologi    | ques avancés                                                       | 85  |

|       |          | 2.4.1     | Scénario #3 : technologies bulk CMOS 180 nm et STT-MRAM de dia-    |     |

|       |          |           | mètre 40 nm                                                        | 86  |

|       |          | 2.4.2     | Scénario #4 : technologies FD-SOI 28 nm et STT-MRAM de diamètre    |     |

|       |          |           | 40 nm                                                              | 87  |

|       |          | 2.4.3     | Résumé des performances des différents scénarios évalués           | 87  |

| 3     |          |           | t du chiffrement PRESENT hybride                                   | 88  |

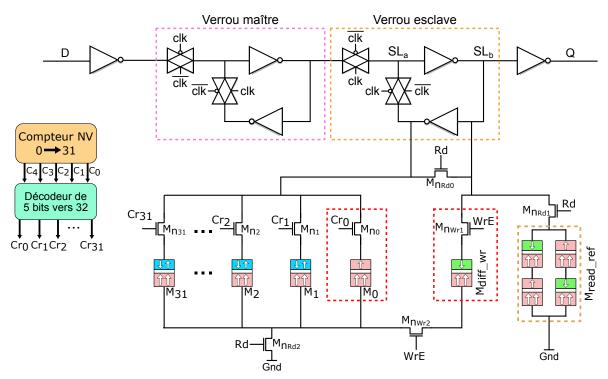

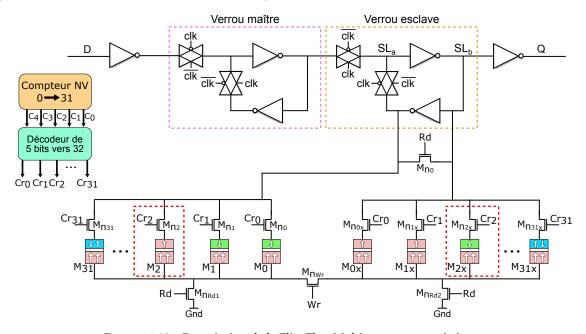

|       | 3.1      |           | es multi-contextes (MC-NVFF)                                       | 89  |

|       |          | 3.1.1     | MC-NVFF Asymétrique                                                | 89  |

|       |          | 3.1.2     | MC-NVFF Symétrique                                                 | 90  |

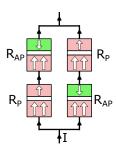

|       | 3.2      |           | dance Technologique Double : DTR                                   | 91  |

|       |          | 3.2.1     | Caractéristiques de la solution DTR                                | 91  |

|       |          | 3.2.2     | Mise en œuvre de la contre-mesure DTR                              | 92  |

|       |          | 3.2.3     | Fonctionnement de la solution DTR                                  | 93  |

|       |          | 3.2.4     | Injection de fautes                                                | 94  |

|       |          | 3.2.5     | Proposition complémentaire pour une architecture PRESENT durcie    | 96  |

| 4     |          |           | e du banc de test des circuits intégrés                            | 96  |

|       | 4.1      |           | abriquée                                                           | 96  |

|       | 4.2      |           | n boîtier                                                          | 97  |

|       | 4.3      |           | orme de test                                                       | 98  |

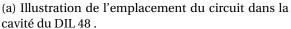

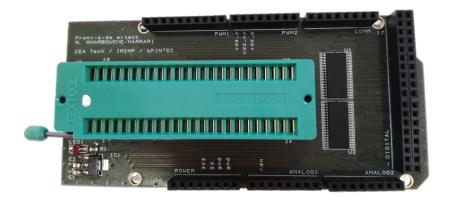

|       |          | 4.3.1     | Carte mère                                                         | 98  |

| _     |          | 4.3.2     | Carte fille                                                        | 98  |

| 5     | Cone     | clusion e | t perspectives                                                     | 100 |

| Cond  | clusions | et persp  | ectives                                                            | 103 |

| Publ  | ications | 5         |                                                                    | 104 |

| A D   | e la phy | sique au  | magnétisme                                                         | 105 |

| Liste | des acr  | onymes    |                                                                    | 107 |

| Bibli | ograph   | ie        |                                                                    | 109 |

| Résu  | mé et A  | bstract   |                                                                    | 121 |

## Introduction générale

Depuis l'avènement de l'informatique, la quantité de données échangées entre différentes entités ou objets a littéralement explosé. En effet, 2,5 Exaoctets (10<sup>18</sup>) sont créés chaque jour [1], [2]. À titre de comparaison, ce nombre correspond au nombre d'informations produites entre le début de l'humanité et l'année 2003. Ce chiffre ne cesse d'augmenter, mais la modification des usages de la société rend difficile une estimation à long terme.

Le développement rapide de l'Internet des Objets lors de cette dernière décennie n'a pas suffisamment pris en compte la sécurité des communications. En effet, bien que certains de ces objets traitent et transmettent des informations confidentielles, dont l'intégrité et l'authenticité doivent être garanties, la sécurité n'est pas une contrainte forte lors de leur développement. C'est ainsi qu'une personne *lambda* peut avoir un libre accès à des caméras de vidéosurveillances de lieux privés ou publics, à des webcams d'ordinateurs [3], aux données traitées par des bracelets connectés ou autres, en toute liberté. En effet, dans ce contexte où le nombre de fabricants d'objets connectés est important, le *time-to-market* occupe une place essentielle. Dès la fonctionnalité du composant, celui-ci est commercialisé sans études supplémentaires sur ses besoins sécuritaires.

Afin de sécuriser ces objets connectés, des algorithmes de cryptographie permettant le chiffrement des messages, peuvent être utilisés. Ces algorithmes permettent, le plus souvent, grâce à une clé confidentielle et personnelle de chiffrer des messages. Le déchiffrement ne peut être réalisé qu'en connaissant cette clé. Ainsi, deux entités peuvent communiquer en toute "sécurité". Toutefois, bien que ces chiffrements soient mathématiquement sûrs, ils sont tout de même sensibles à différents types d'attaques que nous pouvons désigner par attaques physiques. Ces méthodes visent à récupérer la clé de chiffrement utilisée par un algorithme de cryptographie, afin de pouvoir déchiffrer n'importe quel message.

Dans le cadre de cette thèse, nous ne traiterons que des attaques qui sont dites physiques car elles nécessitent l'accès au circuit. Ces attaques conduisent soit à des fuites (de courant par exemple) susceptibles d'être corrélées aux données que le circuit manipule, soit à la création d'une perturbation qui conduit à la modification des données stockées dans la mémoire, à la modification du programme en exécution, ou à l'injection d'une faute dans l'exécution d'un algorithme de chiffrement. Dans ce dernier cas, l'attaquant vise à retrouver la clé de chiffrement.

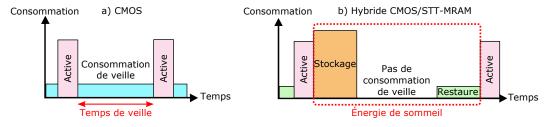

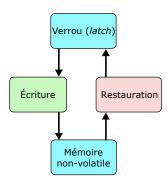

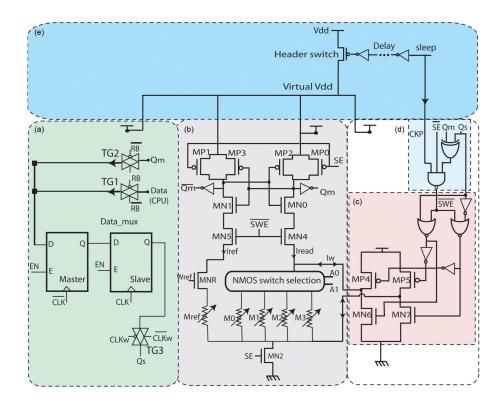

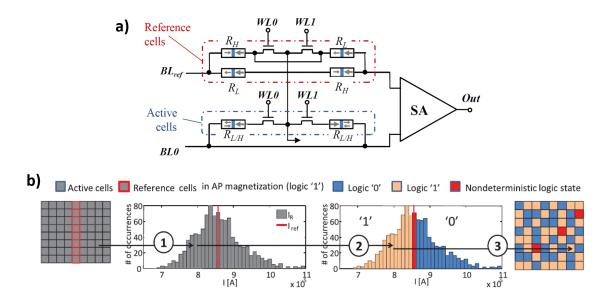

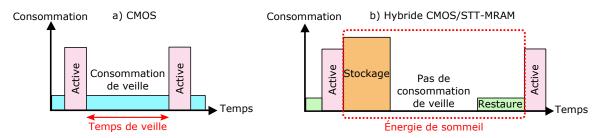

Bien avant l'aspect sécuritaire, la consommation des objets connectés a été un enjeu majeur pour leur déploiement. Pour cela, l'intégration de mémoires non-volatiles dans les circuits intégrés a démontré un avantage indéniable dans la consommation des applications normalement arrêtées ("Normally-off"). En effet, la consommation statique (ou de veille) d'un circuit qui est non-négligeable dans certains cas, est presque complètement inhibée dans le cas de l'hybridation des technologies CMOS et des mémoires non-volatiles émergentes. Les données sont au préalable stockées dans les mémoires avant la mise hors tension du circuit, ce dernier ne consommant quasiment plus d'énergie. Lorsque l'application doit reprendre son fonctionnement, les informations sont restaurées.

Dans ce contexte et dans ce travail, nous nous intéresserons à l'hybridation des algorithmes de cryptographie avec la technologie mémoire émergente STT-MRAM qui présente des propriétés

exceptionnelles pour une intégration dans les objets connectés (faible consommation, forte densité et rapidité de vitesse de fonctionnement). Pour ce faire, dans un premier temps, l'étude des éléments mémoires STT-MRAMs face aux injections de fautes par laser est réalisée afin de déterminer leur sensibilité ou robustesse face aux attaques. Ces éléments sont ensuite intégrés dans des algorithmes de cryptographie en vue du développement d'un chiffrement très faible consommation. L'algorithme de cryptographie légère "PRESENT" est privilégié. En effet, l'implémentation matérielle de cet algorithme est l'une des plus efficaces pour les objets connectés.

Afin de réduire les possibilités de manipulations frauduleuses de ces chiffrements, deux contremesures sont développées. Alors que la première désignée par DDHP (*Dual Detection of Heating and Photocurrent attacks*) se présente comme capteur d'attaques qui ne vise que la détection des perturbations ciblant les technologies CMOS et/ou STT-MRAM, sans les corriger; la seconde intitulée DTR (*Dual Technology Redundancy*) consiste au-delà de la détection, à pouvoir restituer un contexte sain dans les algorithmes de cryptographie après que ces derniers aient été ciblés par des perturbations physiques. En effet, cette seconde contre-mesure consiste à comparer deux chemins d'attaques, un chemin CMOS pur à un chemin hybride CMOS/STT-MRAM.

## Chapitre 1

## Sécurisation des circuits intégrés

If you say you understand quantum mechanics, then you don't understand quantum mechanics

#### - Richard Feynman

Presque tout objet peut être connecté à un réseau, constituant ainsi l'Internet des Objets. Ces objets connectés envahissent le marché pour répondre à différentes applications du quotidien. Ils ont des exigences accrues en terme de consommation et de surface. Toutefois, leur sécurité face aux attaques extérieures est encore peu étudiée, bien qu'elle soit un enjeu majeur de cette décennie et doit donc être garantie.

Ce premier chapitre est introduit par une description des différentes technologies mémoires existantes, traditionnelles et émergentes, dont la STT-MRAM qui est utilisée dans ces travaux. Puis, dans une seconde partie, les exigences des objets connectés en terme de sécurité sont développées. Enfin, ce chapitre est conclu par une dernière partie sur l'hybridation des technologies CMOS et STT-MRAM pour le développement d'architectures sécurisées en vue de leur intégration dans l'Internet des Objets.

#### **Sommaire**

| · · · · · · · · · · · · · · · · · · · |                                                          |  |

|---------------------------------------|----------------------------------------------------------|--|

| 1                                     | Enjeux de la sécurité dans l'Internet des Objets 4       |  |

| 2                                     | Les technologies mémoires                                |  |

|                                       | 2.1 Les technologies mémoires traditionnelles 5          |  |

|                                       | 2.2 Les mémoires émergentes                              |  |

| 3                                     | Sécurité des circuits intégrés                           |  |

|                                       | 3.1 La cryptographie et ses enjeux                       |  |

|                                       | 3.2 Les différentes techniques d'attaques matérielles 24 |  |

| 4                                     | Sécurité dans la logique hybride CMOS/STT-MRAM           |  |

|                                       | 4.1 Les applications "normally-off/instant-on" 29        |  |

|                                       | 4.2 Les structures hybrides CMOS/STT-MRAM                |  |

|                                       | 4.3 Les architectures hybrides de sécurité               |  |

| 5                                     | Conclusion                                               |  |

#### 1 Enjeux de la sécurité dans l'Internet des Objets

Lors de cette dernière décennie, les habitudes quotidiennes de la population française et à fortiori mondiale, ont été bouleversées. Les objets connectés sont devenus une réalité et ont pris une place considérable dans notre quotidien. Ces circuits se multiplient de façon exponentielle et apparaissent sous différentes formes, pour diverses applications. Les objets connectés ont été dénombrés à plus de 20 milliards, dont 7 milliards en ne considérant que les objets hors ordinateurs, tablettes et smartphones. L'estimation de la place de l'Internet des Objets dans les prochaines décennies indique qu'ils pourront atteindre plus de 70 milliards (dont 25 milliards d'objets connectés) en 2025 [4], [5]. Ceux-ci sont présents dans diverses applications grand public comme l'automobile, la domotique, la santé ou encore les applications militaires, illustrées Figure 1.1. Comme les ordinateurs, chaque objet possède sa propre adresse IP (*Internet Protocol*) permettant son identification dans un réseau informatique [6].

FIGURE 1.1 – Illustration des diverses applications de l'Internet des Objets [7].

Toutefois, lors du développement d'objets connectés communicants avec un environnement extérieur en mettant à disposition des informations sur le réseau, la caractéristique qui est encore peu prise en compte est la sécurité. En effet, ces dispositifs traitent des informations sensibles qui peuvent être publiques ou privées. Dans le second cas, la confidentialité, l'authenticité et l'intégrité des données traitées doivent être assurées à tout moment et inhiber toute attaque extérieure qui pourrait s'étendre et toucher l'ensemble du réseau d'objets connectés. Les attaques visant ces dispositifs peuvent être de deux natures différentes :

— Matérielle (ou *Hardware*) : cette catégorie d'attaques se caractérise par des attaques physiques qui peuvent soit perturber le fonctionnement physique du circuit, ces attaques sont

dites par perturbation, soit observer les émissions d'un circuit pour en déterminer les données manipulées, ces dernières sont dites par observation. Pour cela, il est nécessaire d'avoir un accès physique à l'objet. Les attaques par perturbation peuvent par exemple viser la mémoire où sont stockées les données sensibles sur le long terme (mémoire non-volatile de type Flash par exemple) ou les données en cours de traitement dans les registres ou dans les mémoires volatiles, de type mémoire statique ou – *Static Random Access Memory* – (SRAM) par exemple. Les attaques par observation ciblent les algorithmes de cryptographie afin d'en extraire la clé utilisée pour le chiffrement et donc pouvoir déchiffrer tout message crypté.

— Logicielle (ou Software): cette seconde catégorie d'attaques exploite l'utilisation de protocoles de communication dans les objets connectés, afin de réaliser des attaques à distance, via le réseau. Une instanciation non-adaptée de ces protocoles peut induire des fuites et des intrusions dans les données ou les programmes qui sont traités par les objets. Ces attaques logicielles peuvent également être induites en exploitant des portes dérobées dont l'attaquant, contrairement à l'utilisateur, a connaissance. Contrairement aux attaques matérielles, l'accès physique à l'objet n'est pas forcément nécessaire dans ce cas.

Ces problématiques de sécurité sont aujourd'hui au centre des débats. Pour cela diverses solutions peuvent être étudiées. Dans le cadre de ces travaux, nous ne traiterons que des attaques matérielles qui peuvent viser les circuits intégrés et principalement viser les éléments mémoires où sont stockées les données sensibles de l'utilisateur. Effectivement, cette thèse traitera de l'intégration de la technologie mémoire émergente *Spin-Transfer Torque MRAM* – (STT-MRAM) dans l'Internet des Objets.

Dans un premier temps, son niveau de sécurité face à des perturbations extérieures est étudié. Puis, sa capacité d'hybridation avec la technologie CMOS est analysée afin d'obtenir des solutions cryptographiques plus performantes en terme de sécurité, tout en étudiant leur impact en terme de consommation et de surface. Avant de développer ces différentes études, ce premier chapitre met en avant un état de l'art non-exhaustif des technologies mémoires et de leur sécurité en vue de leur intégration et hybridation avec des procédés CMOS.

#### 2 Les technologies mémoires

#### 2.1 Les technologies mémoires traditionnelles

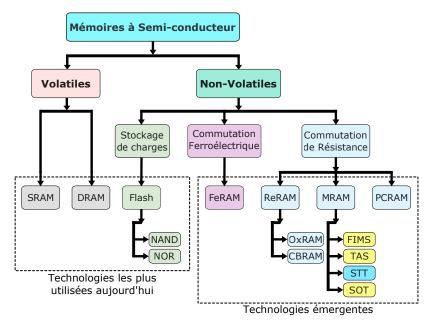

Les mémoires sont des composants essentiels de l'industrie de la microélectronique. Elles sont principalement utilisées pour le stockage de données ou de programmes. Le stockage de l'information dans ces composants, selon leur positionnement dans une architecture de calcul fait appel à différentes technologies mémoires comme représenté sur la Figure 1.2. Il existe deux familles principales de mémoires : les mémoires volatiles et mémoires non-volatiles.

#### 2.1.1 Les mémoires volatiles

Les mémoires volatiles sont des dispositifs dont la préservation des données ne dépend que de son alimentation. Dès que celles-ci ne sont plus alimentées, l'information stockée est perdue. Cette catégorie de mémoires est principalement utilisée pour implémenter la mémoire cache ou les mémoires de travail ou mémoires primaires. Les mémoires statiques ou – *Static Random Access Memories* – (SRAMs), composent les mémoires dominantes embarquées dans un microcontrôleur alors que les mémoires dynamiques ou – *Dynamic Random Access Memories* – (DRAMs), représentent la plus importante part de marché en mémoires volatiles isolées (ou *stand-alone*).

Cette catégorie de mémoires présente des avantages majeurs facilitant son utilisation et intégration dans les circuits électroniques. Dans un monde connecté où les données communiquées

sont importantes, la rapidité de fonctionnement et la densité sont des atouts majeurs, des attraits mis en avant par les SRAMs et DRAMs.

FIGURE 1.2 – Classification des différentes technologies de mémoires à semi-conducteur.

#### 2.1.2 Les mémoires non-volatiles

Dans les mémoires non-volatiles, l'information stockée est préservée même sans alimentation, comme par exemple dans le cas d'une clé USB. Tant que l'information écrite dans la mémoire n'est pas effacée ou modifiée, alors la donnée est invariable avec ou sans alimentation. Cette mémoire est principalement présente pour le stockage de masse. La Flash détient aujourd'hui la plus importante part de marché en terme de mémoires non-volatiles et notamment pour les mémoires isolées. La technologie Flash est la plus mature, elle est étudiée depuis 1984 [8]. Il existe deux types de mémoires Flash : la mémoire NOR et la mémoire NAND.

#### 2.1.2.1 La NOR:

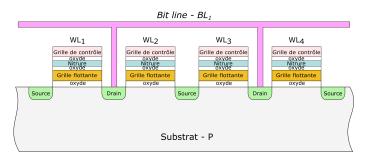

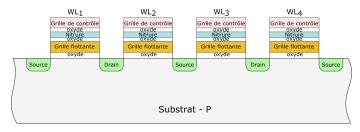

La technologie mémoire NOR est une architecture présentant une vitesse d'accès aux points mémoires importante puisque chaque point peut être adressé indépendamment des autres, ce qui est un atout pour le stockage d'instructions. En effet, chaque transistor est adressé par une *bitline* (BL) et une *wordline* (WL), comme illustré sur la Figure 1.3. Toutefois, cette caractéristique conduit également à la réduction de la densité de l'architecture. La Figure 1.3 illustre une vue en coupe et le schéma de fonctionnement d'une cellule mémoire NOR.

(b) Schéma de fonctionnement.

FIGURE 1.3 - La mémoire Flash NOR.

#### 2.1.2.2 La NAND:

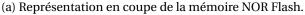

La catégorie de mémoires Flash de type NAND présente une plus forte densité que la technologie mémoire NOR. Toutefois, l'adressage d'un point mémoire précis ne peut être réalisé directement. En effet, dans une mémoire Flash de type NAND, toutes les mémoires sont connectées en série et la BL est connectée à un transistor d'accès  $TA_0$ , comme représenté sur la Figure 1.4. Ainsi, les temps d'écriture et de lecture d'une cellule particulière dans la matrice sont plus lents que pour son homologue NOR. D'autre part, afin de réaliser la lecture d'un plan mémoire, il est nécessaire d'activer toutes les WLs mises en jeu dans cette matrice. La Figure 1.4 représente une vue en coupe et le schéma de fonctionnement d'une mémoire Flash de type NAND.

- (a) Représentation en coupe de la mémoire NAND Flash.

- (b) Schéma de fonctionnement.

FIGURE 1.4 - La mémoire Flash NAND.

La Recherche et Développement (R&D) sur les mémoires non-volatiles émergentes est en perpétuelle évolution. Ces études sont réalisées afin d'atteindre une mémoire idéale dont les caractéristiques seraient les suivantes :

- Une consommation minimale déterminée par des tensions de fonctionnement de la mémoire proche des tensions utilisées pour le fonctionnement du CPU.

- Une endurance présentant au moins  $10^{15}$  cycles d'écriture/effacement répondant aux contraintes de durée de vie des produits les plus exigeants.

- Un temps de lecture/écriture de la mémoire de l'ordre de la nanoseconde, permettant ainsi de réduire le gap entre la vitesse de traitement des cœurs de calcul et l'accès aux informations mémorisées.

- Une forte densité afin de réduire la surface silicium nécessaire pour fabriquer le produit et donc pouvoir plus facilement l'intégrer dans les applications embarquées et baisser en même temps les coûts.

- La non-volatilité pour conserver les informations même en l'absence d'alimentation.

Cette mémoire idéale serait définie comme une mémoire fonctionnant à la vitesse et au niveau de tension des mémoires volatiles de type SRAMs, tout en ayant la non-volatilité des mémoires Flash.

#### 2.2 Les mémoires émergentes

Les différentes mémoires émergentes aujourd'hui étudiées se rapprochent par bien des points de la mémoire idéale, même si certains obstacles subsistent. Après la présentation de certaines de ces catégories de mémoires, il sera alors possible de comparer leurs caractéristiques, même si cela reste toujours subjectif.

#### 2.2.1 Les mémoires résistives ReRAM

Les mémoires résistives *Resistive Random Access Memories* – (ReRAMs ou RRAMs) font partie des mémoires non-volatiles émergentes des plus prometteuses, présentant divers avantages comparé à la technologie Flash. Ces mémoires sont des dispositifs qui se positionnent physiquement

dans le *Back-End of Line* – (BEoL), contrairement à la mémoire Flash qui est définie directement sur le substrat. Cette caractéristique de positionnement des mémoires résistives sur les niveaux de métallisations supérieurs permet d'augmenter la densité des plans mémoires. Cette technologie émergente est aujourd'hui la plus utilisée dans les applications embarquées [9].

#### 2.2.1.1 Oxide Random Access Memory - OxRAM:

La technologie mémoire *Oxide Random Access Memory* – (OxRAM) est une structure résistive de type Métal-Isolant-Métal qui est l'une des deux mémoires émergentes privilégiées par l'*International Technology Roadmap for Semiconductors* – (ITRS) [10] pour remplacer les Flashs. Elle combine les avantages de la mémoire Flash en terme de non-volatilité et de la mémoire SRAM en terme d'endurance et de consommation bien que son principal défaut reste la variabilité. Les deux états mémoires de Basse résistivité L<sub>RS</sub> (*Low Resistive State*) et Haute résistivité H<sub>RS</sub> (*High Resistive State*) sont induits respectivement par la création ou la destruction d'un filament conducteur d'anions d'Oxygène dans l'isolant compris entre les deux électrodes. Ce filament est créé par le passage d'un courant à travers la structure.

Nous pouvons distinguer deux catégories de mémoires OxRAMs; une version unipolaire (les commutations sont réalisées sous la même polarité mais à deux amplitudes distinctes) et bipolaire (qui est aujourd'hui celle qui est principalement étudiée).

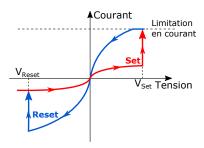

Les commutations dans une OxRAM bipolaire sont réalisées pour deux polarités inverses. La tension permettant de réaliser l'opération de Set (commutation d'un état  $H_{RS}$  vers  $L_{RS}$ ) a une polarité positive, inverse à la tension effectuant le Reset ( $L_{RS}$  vers  $H_{RS}$ ), comme illustré Figure 1.5. Cette technologie mémoire est une candidate exceptionnelle dans le remplacement des mémoires conventionnelles pour les nœuds technologiques inférieurs à 20 nm [11], [12]. Toutefois, cette technologie peut induire des niveaux de courants élevés dans la structure pouvant conduire à sa destruction. C'est pourquoi il est nécessaire d'imposer lors des phases de programmation, des courants de "compliance" ou limite maximale à ne pas dépasser, comme illustré sur la Figure 1.5.

FIGURE 1.5 – Représentation du fonctionnement électrique d'une OxRAM bipolaire [12].

#### 2.2.1.2 Conductive Bridging Random Access Memory - CBRAM:

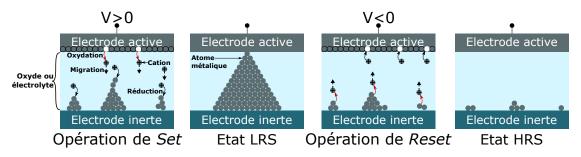

La seconde technologie mémoire résistive décrite ici est la  $Conductive\ Bridging\ Random\ Access\ Memory$  – (CBRAM). Le changement d'état de cette architecture est induite par une commutation électrochimique. En effet, cette structure est composée de trois couches de matériaux différents, une électrode active et une électrode inerte séparées par un oxyde ou une électrolyte, comme représenté sur la Figure 1.6. L'état de faible résistivité  $L_{RS}$  (respectivement de forte résistivité  $H_{RS}$ ) est alors atteint lors de la création (resp. destruction) d'un filament d'ions métalliques dans cet oxyde (comme par exemple d'Argent) [13], comme illustré Figure 1.6. Cette technologie est très attractive pour son utilisation de niveaux de tension de fonctionnement faibles.

FIGURE 1.6 – Illustration du fonctionnement interne de la mémoire CBRAM [12].

#### 2.2.2 Prérequis à la MRAM

Dans le contexte des mémoires non-volatiles émergentes, une seconde catégorie s'est illustrée par ses performances et caractéristiques intéressantes pour l'Internet des Objets, la technologie mémoire magnétique – ou *Magnetic Random Access Memory* – (MRAM), illustrée Figure 1.2. Afin d'introduire cette technologie mémoire, il est nécessaire de réaliser quelques rappels de physique et de magnétisme, principalement concernant les matériaux qui entrent en jeu dans la composition de ces structures. En effet, les MRAMs sont des technologies mémoires composées de matériaux magnétiques de diverses natures. La nature de ces matériaux est déterminée par les caractéristiques des moments magnétiques qui les composent.

#### 2.2.2.1 Le moment magnétique :

La fonction principale du magnétisme est caractérisée par le moment magnétique des électrons, qui gravitent autour du nucléon. En effet, l'électron qui tourne autour du nucléon N génère un courant en sens inverse à son déplacement. Pour une boucle de courant d'intensité I, comme représentée sur la Figure 1.7, de surface S, alors le moment magnétique  $\overrightarrow{m}$  exprimé en  $A.m^2$  est défini par l'Équation 1.1 où  $\overrightarrow{n}$  est le vecteur unitaire perpendiculaire à la surface de la boucle de courant.

$$\overrightarrow{m} = I.S.\overrightarrow{n}$$

(1.1)

FIGURE 1.7 – Représentation du moment magnétique de spin  $\overrightarrow{m}$ .

Ainsi, ce moment magnétique peut être défini comme la force résultante induite par cette boucle de courant.

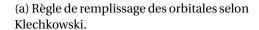

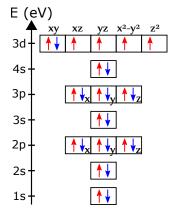

En outre, il est également défini par son moment magnétique angulaire et son moment magnétique intrinsèque ou spin. Alors que le premier est nul lorsque l'atome est immobile et sera donc négligé ici, le second quant à lui provient de la contribution des couches énergétiques nonpleines (les couches "3d" ou "4f" par exemple, comme développé en Annexe A). En effet, le moment magnétique total de l'atome correspond à la somme des moments magnétiques des électrons qui le forment. Ainsi, l'énergie des moments magnétiques de spins est non-nulle tant que les orbitales ne sont pas toutes remplies et donc tant que les moments magnétiques ne s'annulent pas.

#### 2.2.2.2 Les matériaux magnétiques :

Selon le tableau de D.I. Mendeleïev [14], la majorité des matériaux peuvent être décomposés en différentes catégories de matériaux : des matériaux ferromagnétiques, des matériaux antiferromagnétiques, des matériaux diamagnétiques et des matériaux paramagnétiques, dépendant des caractéristiques physiques des moments magnétiques intrinsèques de chaque composant.

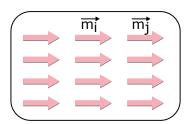

— Les matériaux ferromagnétiques sont des éléments pour lesquels tous les moments magnétiques ont la même direction (co-linéaires) et sont orientés dans le même sens de façon intrinsèque et spontanée, sans besoin d'application d'un champ magnétique extérieur [15], illustré Figure 1.8.a. Cet effet est induit par une énergie d'échange  $E_c$  qui est présente entre deux moments magnétiques directement voisins  $\overrightarrow{m_i}$  et  $\overrightarrow{m_i}$ , tel que décrit en Équation 1.2 :

$$E_c = -J \sum_{i, j} \overrightarrow{m_i} \cdot \overrightarrow{m_j}$$

(1.2)

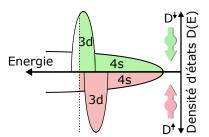

La constante de couplage d'échange J est positive afin d'assurer l'alignement des moments magnétiques. La Figure 1.8.b représente le remplissage réel de la couche "3d", où les *spinsdown* (en vert) ne sont pas suffisants pour la remplir complètement.

(a) Représentation conventionnelle de l'organisation des moments  $\overrightarrow{m}$ .

(b) Densité d'états des *spins-up* et *spins-down*, organisation réelle des moments  $\overrightarrow{m}$ .

FIGURE 1.8 - Illustration du matériau ferromagnétique.

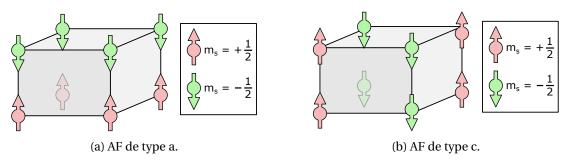

- Les matériaux antiferromagnétiques (AF) sont les composants pour lesquels tous les moments magnétiques sont co-linéaires bien que deux moments successifs ont un sens opposé (soit en x, y ou z). Ainsi, les matériaux antiferromagnétiques ont une aimantation globale nulle. Il existe un large nombre de classes de matériaux AFs, qui dépendent de l'arrangement des *spins-up* par rapport aux *spins-down* dans la matrice [15]. Pour exemple, soit les deux catégories d'antiferromagnétiques les plus représentatives : AF de type a et AF de type c, comme illustrés Figure 1.9.

- type a : Dans une structure cubique simple par exemple, les 4 coins de la face supérieure ont un spin inverse aux 4 coins de la face inférieure. Le spin est fixé selon le plan (100). Ce matériau est illustré par la Figure 1.9.a.

- type c : Dans la même structure cubique simple, ce type correspond au spins de même orientation magnétiques organisés selon la diagonale de cette structure (selon le plan (111)). Ce matériau est illustré par la Figure 1.9.b.

L'équation 1.2 représente également les matériaux antiferromagnétiques avec la seule différence que la constante de couplage d'échange J sera dans ce cas négative, imposant donc à deux moments magnétiques voisins d'être dans des sens inverses (bien qu'ils restent colinéaires).

Les matériaux ferromagnétiques et antiferromagnétiques sont liés soit à la couche "3d" soit à la couche "4f" qui sont partiellement remplies.

FIGURE 1.9 – Deux modèles de matériaux antiferromagnétiques présentant la position des moments magnétiques (positifs et négatifs) dans une structure cubique.

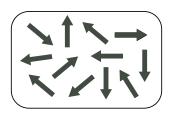

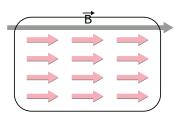

— Les matériaux paramagnétiques ont des moments magnétiques dont le sens et la direction ne sont pas intrinsèquement prédéfinis. Ils s'orientent dans toutes les directions de l'espace de façon aléatoire, comme illustrés Figure 1.10.a. Cette catégorie de matériaux magnétiques met ainsi en jeu des moments magnétiques voisins qui peuvent être considérés comme indépendants les uns des autres et qui n'interagissent pas entre eux.

(a) Organisation des moments magnétiques sans application de champ.

(b) Ordonnancement des moments magnétiques  $\overrightarrow{m}$  sous l'effet d'un champ  $\overrightarrow{B}$ .

FIGURE 1.10 – Les matériaux paramagnétiques sous différentes conditions extérieures.

Toutefois, lors de l'application d'un champ magnétique extérieur, ces moments magnétiques se polarisent et deviennent le temps de la polarisation magnétique des ferromagnétiques orientés dans le sens du champ magnétique appliqué [15], comme illustré Figure 1.10.b. D'autre part, une augmentation de la température a l'effet inverse sur ces moments et va davantage favoriser une orientation aléatoire.

— Les matériaux diamagnétiques sont des matériaux à faible susceptibilité magnétique négative. Contrairement aux matériaux paramagnétiques, les matériaux diamagnétiques, lorsqu'ils sont soumis à un champ magnétique, voient tous les électrons s'orienter dans le sens opposé au champ magnétique [15]. Ainsi, l'aimant et le matériau se repoussent.

#### 2.2.3 Les technologies MRAMs

La découverte de M. Julliere [16] à l'Institut National des Sciences Appliquées de Rennes en 1975 de la variation de la conductance d'un empilement "magnétique - isolant - magnétique" selon l'orientation des couches ferromagnétiques conduit au développement de la Magnéto-Résistance Tunnel ou – *Tunnel MagnetoResistance* – (TMR). En 1988 et 1989, les équipes d'A. Fert [17] et P. Grünberg [18] ont découvert la Magnéto-Résistance Géante ou – *Giant MagnetoResistance* – (GMR). Ils ont été récompensés en 2007 du prix Nobel de physique pour cette conquête d'une nouvelle voie dans le stockage des données et ont ouvert de nouvelles voies à la recherche. Ce fut l'avènement de la spintronique. L'électron n'est plus considéré que par sa charge comme dans l'électronique traditionnelle mais également pour sa propriété quantique : le spin, d'où le nom spintronique.

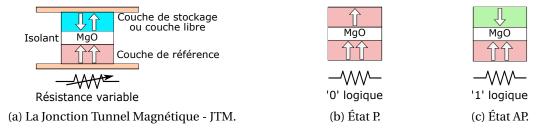

Ces découvertes conduirent au développement des mémoires MRAMs. Cette technologie est composée d'un isolant non-magnétique (ou barrière tunnel) positionné entre deux matériaux ferromagnétiques, constituant ainsi une hétérostructure magnétique appelée Jonction Tunnel Magnétique – ou *Magnetic Tunnel Junction* – (JTM) [19], illustrée sur la Figure 1.11.a.

FIGURE 1.11 – Illustration de la Jonction Tunnel Magnétique (JTM) et de ses états.

L'orientation magnétique de l'une de ces couches ferromagnétiques est fixe, elle est définie comme couche de référence. La seconde couche ferromagnétique peut changer l'orientation de son aimantation, elle est désignée par couche libre ou couche de stockage. L'orientation magnétique de la couche libre par rapport à la couche de référence permet de définir l'information stockée.

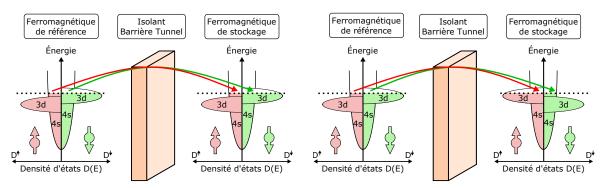

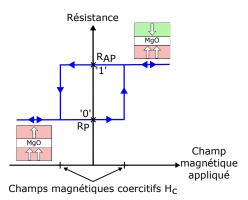

Lorsque les deux ferromagnétiques composant cette jonction ont des aimantations qui sont dans une orientation commune, alors la JTM est dans un état parallèle P (faible résistivité notée R<sub>P</sub> qui par convention correspond à un '0' logique), illustrée Figure 1.11.b. Dans ce cas, les électrons de spins majoritaires de l'une de ces couches (*spins-up*, illustrés sur la Figure 1.12.a) peuvent traverser la barrière tunnel jusqu'à la seconde couche ferromagnétique qui a ses électrons de spins majoritaires orientés dans la même aimantation magnétique.

(a) Configuration parallèle des 2 ferromagnétiques composant la structure MRAM.

(b) Configuration anti-parallèle des 2 ferromagnétiques composant la structure MRAM.

FIGURE 1.12 – Configurations possibles des deux ferromagnétiques composant la structure JTM.

Inversement, si les moments magnétiques de la couche de stockage sont co-linéaires à ceux de la couche de référence mais dans un sens opposé, alors la résistance est définie comme antiparallèle AP (forte résistivité notée R<sub>AP</sub> qui par convention correspond à un '1' logique), comme illustrée Figure 1.11.c. Dans ce cas, les électrons de spins majoritaires (*spins-up*, illustrés sur la Figure 1.12.b) qui doivent traverser l'isolant par effet tunnel sont minoritaires de l'autre côté (les *spins-down* sont majoritaires dans le second ferromagnétique). Le courant pouvant traverser la structure est faible et la résistance du point mémoire est importante.

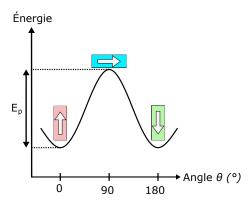

Seuls ces deux états P et AP sont possibles dans les mémoires MRAMs. Tout autre état intermédiaire de la couche de stockage nécessiterait une énergie permanente  $E_p$  pour être stabilisé, comme représenté par la couche dont l'aimantation est horizontale (pour un angle de  $90^\circ$ ) sur la Figure 1.13.a.

(a) Angle d'orientation de la couche de stockage par rapport à la référence.

(b) Évolution de la résistivité en fonction du champ magnétique.

FIGURE 1.13 – Orientation des deux couches ferromagnétiques dans une MRAM et évolution de la résistivité en fonction du champ magnétique.

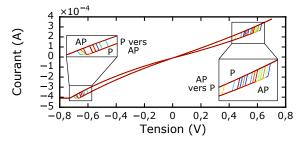

Différentes générations de cette famille de mémoires ont été proposées. La classification de ces catégories est principalement due au moyen utilisé pour commuter la structure d'un état logique à l'autre. En effet, la commutation peut être provoquée par deux mécanismes : soit un champ magnétique (représenté sur la Figure 1.13.b) soit un courant. Le champ magnétique coercitif correspond à la force minimale à fournir à la structure afin de la commuter d'une aimantation à l'autre. De plus, il peut être noté que la stabilité thermique des composants peut modifier ce champ coercitif [20]. L'accroissement de la température peut donc modifier l'aimantation de la jonction.

La TMR exprime la proportion relative de la résistivité de l'état AP par rapport à l'état P. Cette grandeur est définie par l'Équation 1.3. L'évolution de la technologie mémoire MRAM est directement corrélée à l'augmentation significative de la TMR au fil de son développement et des matériaux utilisés, permettant ainsi de distinguer plus facilement les deux états de la mémoire.

$$TMR = \frac{R_{AP} - R_P}{R_P} \tag{1.3}$$

Bien que le matériau de prédilection de la barrière tunnel ait d'abord été l'Oxyde d'Aluminium  $(Al_2O_3)$  sous sa forme amorphe, il a ensuite été remplacé par de l'Oxyde de Magnésium (MgO) dans sa forme cristalline, le rendement de TMR de ce dernier étant bien supérieur. Alors que l'Oxyde d'Aluminium induit des TMRs observées inférieures à 100 % à température ambiante [21], [22], [23], l'Oxyde de Magnésium conduit à un passage cohérent des électrons dans l'empilement [24], [25], ce qui peut atteindre une TMR supérieure à 600 % à température ambiante et plus de 1000 % à basse température [26].

Dans cette section, nous décrirons quatre technologies mémoires MRAMs : la mémoire *Field Induced Magnetic Switching-Toggle* – (FIMS-Toggle), *Thermally Assisted Switching MRAM* – (TAS-MRAM), *Spin-Transfer Torque MRAM* (STT-MRAM) et *Spin-Orbit Torque MRAM* – (SOT-MRAM).

#### 2.2.3.1 Field Induced Magnetic Switching-Toggle (FIMS-Toggle MRAM):

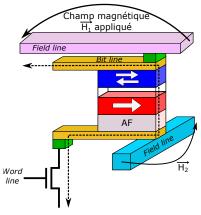

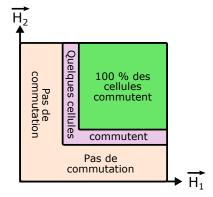

La mémoire FIMS-Toggle utilise deux champs magnétiques simultanés pour commuter la JTM, via des lignes de cuivre qui passent en dessous (*word line*) et au-dessus (*bit line*) de l'élément mémoire, comme représenté Figure 1.14.a. En effet, ces deux champs permettent de fixer la position en x et en y de la jonction à écrire, dans la matrice de jonctions. Le développement et la commercialisation par Everspin de cette technologie se base sur la théorie de L. Savtchenko *et al.* sur la commutation d'une mémoire via la génération d'un champ magnétique induit par des lignes de courant [27]. Chacune des deux énergies fournies par les deux champs magnétiques doit être

suffisante pour faire commuter toutes les cellules visées, faute de quoi seules quelques cellules pourront commuter, comme illustré Figure 1.14.b.

(a) Représentation de l'architecture d'une mémoire FIMS-Toggle.

(b) Commutation en fonction des champs  $\overrightarrow{H_1}$  et  $\overrightarrow{H_2}$ .

FIGURE 1.14 – La mémoire FIMS-Toggle.

Le principe d'écriture de la mémoire FIMS-Toggle consiste en l'inversion de l'orientation magnétique de la couche de stockage. Cette commutation est réalisée par un phénomène de nucléation et propagation correspondant à une rotation successive des moments magnétiques d'un angle de 45° [28].

Cette architecture est composée principalement d'un empilement antiferromagnétique (AF) - ferromagnétique - isolant - ferromagnétique. La couche AF a pour rôle de fixer l'aimantation de la couche de référence.

Cette méthode d'écriture souffre principalement de la précision de la sélectivité du point mémoire avec la miniaturisation, ainsi que de sa consommation relativement élevée.

#### 2.2.3.2 Thermally Assisted Switching MRAM (TAS-MRAM):

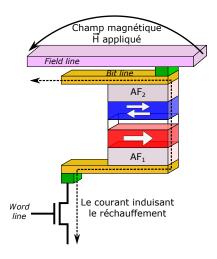

La commutation assistée par température ou *Thermally Assisted Switching MRAM* – (TASMRAM) combine un réchauffement localisé de la jonction mémoire sélectionnée et un champ magnétique unique appliqué pour modifier l'aimantation de la couche de stockage. L'une des différences majeures de cette technologie par rapport à la technologie FIMS-Toggle est la présence d'un second antiferromagnétique  $AF_2$  au-dessus de la couche de stockage, comme illustré Figure 1.15. Ainsi, la JTM est composée d'un empilement : antiferromagnétique - ferromagnétique - isolant - ferromagnétique - antiferromagnétique. Ce second antiferromagnétique va conduire à fixer l'aimantation de la couche libre tant qu'aucun échauffement n'est induit dans la structure.

Lorsque la température résultante dans l'antiferromagnétique  $AF_2$  est supérieure à sa température de Néel, celui-ci deviendra paramagnétique et n'appliquera plus de force (ou énergie d'échange) sur la couche ferromagnétique de stockage. L'écriture de la jonction est alors réalisée via l'activation de la ligne de champ (*Field line*, illustrée Figure 1.15), pendant que le matériau  $AF_2$  est paramagnétique.

Cette méthode d'écriture résout en partie les difficultés de sélectivité observés sur la technologie FIMS-Toggle mais souffre également de difficultés, certes moindres, de miniaturisation et de consommation.

FIGURE 1.15 - Schéma de la mémoire TAS-MRAM.

#### 2.2.3.3 Spin-Transfer Torque MRAM (STT-MRAM):

La difficulté majeure des technologies MRAMs dont la commutation est réalisée par champ (FIMS-Toggle et TAS-MRAM) est la génération d'un champ localisé de manière extrêmement précise sur un nœud mémoire. En effet, le rayonnement du champ peut facilement conduire à la commutation des éléments voisins proches de la cellule visée. Dans le cadre du développement de cette catégorie de mémoires non-volatiles, de nouvelles générations utilisant des mécanismes de commutation différents sont apparues, principalement la technologie STT-MRAM.

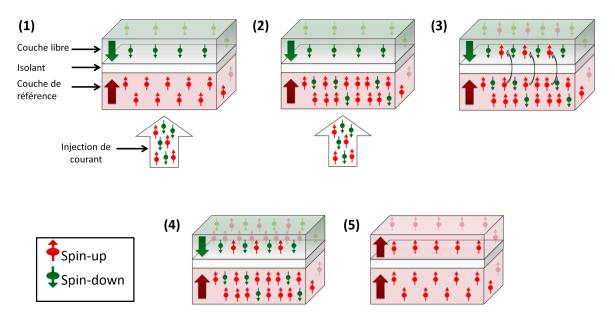

Cette technologie ne nécessite qu'un **courant de spin polarisé** pour commuter d'un état de faible résistivité vers un état de forte résistivité et inversement. Un courant initialement non-polarisé devient polarisé en spins (soit en *spins-up* majoritaires soit en *spins-down* majoritaires) grâce à l'effet des moments magnétiques de la première couche ferromagnétique de la JTM qu'il traverse. L'analogie entre une JTM et un filtre peut être réalisée. Pour exemple, les électrons de *spins-down*, traversant un matériau ferromagnétique orienté majoritairement en *spins-up*, sont filtrés. Seuls les *spins-up* réussissent à traverser cette première couche ferromagnétique de la JTM.

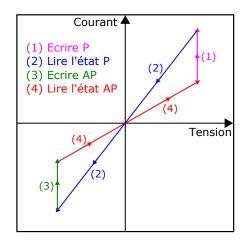

L'injection d'un courant dans la JTM soit par la couche de stockage soit par la couche de référence conduit à l'écriture de l'un des deux états de la mémoire (P ou AP). Ce mécanisme est désigné par *Transfer Torque* [29], [30].

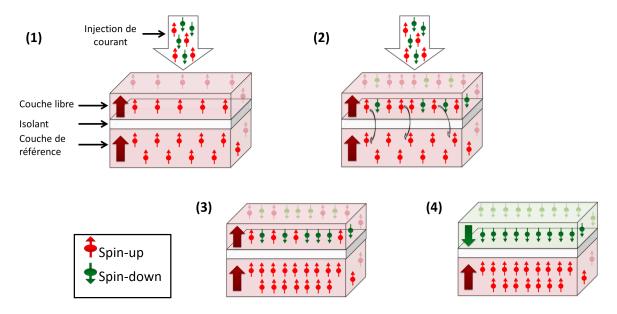

Considérons donc les deux phénomènes qui induisent la programmation des cellules STT-MRAMs:

- La commutation d'un état AP (forte résistivité) vers un état P (faible résistivité) :

Considérons une JTM initialement dans un état AP (avec par exemple les *spins-up* majoritaires dans la référence et les *spins-down* majoritaires dans la couche de stockage, comme illustré étape (1) de la Figure 1.16) :

- Le courant (non-polarisé) injecté par la couche de référence conduit à sa polarisation en *spins-up*. Les électrons de *spins-up* peuvent alors traverser la barrière tunnel, étapes (2) et (3). Les électrons de *spins-down* sont eux réfléchis par la couche de référence, étape (2) de la Figure 1.16. Toutefois, la couche de stockage étant orientée en *spins-down*, celle-ci réfléchit quelques électrons de *spins-up*, étape (4). Lorsque la densité de courant qui traverse la STT-MRAM est suffisante, les électrons de *spins-up* transmis à la couche de stockage deviennent majoritaires aux électrons de *spins-down* présents, étape (5). La couche inverse donc son aimantation. L'état de la STT-MRAM bascule de AP vers P.

Dans ce cas, la commutation est induite par la transmission des électrons majoritaires polarisés par la couche de référence.

FIGURE 1.16 - Commutation d'une cellule STT-MRAM d'un état AP vers un état P.

- La commutation d'un état Parallèle P vers un état Anti-Parallèle AP est illustrée sur la Figure 1.17 :

- Étape (1) : considérons la JTM initialement dans un état P, comme décrite Figure 1.17. Dans ce cas, les *spins-up* sont majoritaires dans les deux couches ferromagnétiques.

- Étape (2) : le courant injecté par la couche de stockage est polarisé en *spins-up* par cette couche et traverse la JTM. Les *spins-down* sont eux réfléchis dans la couche de stockage.

- Étape (3) : lorsqu'une densité de courant suffisante est atteinte, la population de *spins-up* et de *spins-down* (réfléchis) dans la couche de stockage s'inverse. Les *spins-down* deviennent majoritaires.

- Étape (4): La résistivité de la STT-MRAM bascule de l'état P vers l'état AP.

Dans ce cas, la couche de stockage joue le rôle de polariseur du courant et la commutation est induite par la réflexion des électrons minoritaires.

FIGURE 1.17 – Commutation d'une cellule STT-MRAM d'un état P vers un état AP.

#### — Lecture d'une cellule STT-MRAM :

Comme pour les technologies FIMS-Toggle et TAS-MRAM, cette structure est une architecture à deux terminaux, la lecture et l'écriture suivent le même chemin.

La lecture de l'état mémoire dans une STT-MRAM est réalisée par le passage d'un courant dans l'empilement de la JTM. Toutefois, la densité de courant doit être inférieure à la densité nécessaire pour réaliser une commutation de l'état mémoire, au risque d'écrire pendant une phase de lecture.

La STT-MRAM a été initialement développée comme une architecture à aimantation planaire. Les spins des couches ferromagnétiques étaient parallèles au plan, comme représenté Figure 1.18.a. Depuis, les architectures ont évolué en structures à aimantations perpendiculaires (p-STT-MRAM) dont les spins sont orthogonaux au plan de la JTM, comme illustré Figure 1.18.b.

(a) Schéma d'une STT-MRAM dont l'aimantation des ferromagnétiques est planaire au plan.

(b) Schéma d'une STT-MRAM dont l'aimantation des ferromagnétiques est perpendiculaire au plan.

FIGURE 1.18 – Illustration des deux architectures mémoires STT-MRAMs existantes.

Les p-STT-MRAMs sont plus efficaces en terme de consommation grâce à une plus forte anisotropie perpendiculaire et à la diminution des niveaux d'énergies nécessaires pour réaliser la commutation. L'énergie nécessaire pour commuter l'état de la cellule est exprimée par la stabilité thermique  $\Delta_T$  (sans dimension). La densité de courant d'une architecture perpendiculaire  $I_c^{perp.}$  est exprimée par l'Équation 1.4 [31].

$$I_c^{perp.} = (\frac{4e}{\hbar}) \frac{\alpha k_B T}{\eta} \Delta_T$$

(1.4)

Cette expression est définie en fonction de : e la charge élémentaire de l'électron,  $\hbar$  la constante de Planck réduite,  $\alpha$  le coefficient d'atténuation de Gilbert,  $k_{\rm B}$  la constante de Boltzmann, T la température et  $\eta$  la polarisation en spin du courant.

Cette technologie mémoire cumule différents avantages qui en font une structure de choix dans le panel des mémoires non-volatiles émergentes. En effet, sa compatibilité avec le CMOS, sa vitesse d'écriture et de lecture (de l'orde de la ns), sa densité et sa consommation réduite en font une mémoire de choix pour une utilisation dans diverses applications embarquées. C'est pourquoi, la STT-MRAM est aujourd'hui selon l'ITRS la mémoire susceptible de devenir la mémoire universelle [10], [32]. De plus, le rapport de *Yole development* de 2018 prévoit que cette technologie mémoire deviendra en 2023, la première technologie mémoire émergente embarquée [9].

#### 2.2.3.4 Spin-Orbit Torque MRAM (SOT-MRAM):

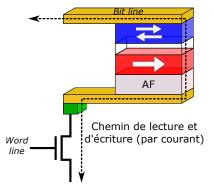

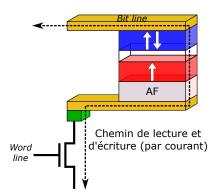

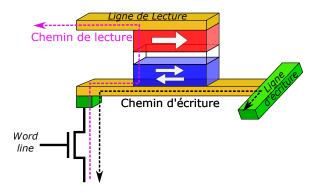

Contrairement à la mémoire STT-MRAM, la SOT-MRAM est une structure à trois terminaux [33] qui a été découverte par le laboratoire Spintec [34], [35] et [36]. Le principal avantage de cette génération de mémoires magnétiques est la séparation des chemins de lecture et d'écriture, qui se font par deux chemins distincts comme représentés sur la Figure 1.19. Cette caractéristique

limite la détérioration de l'isolant puisque seuls de faibles courants de lecture traversent cette barrière tunnel, augmentant donc leur endurance. De plus, compte tenu que le courant d'écriture ne traverse pas l'isolant, il est possible d'utiliser de forts courants pour atteindre des temps de commutation ultra-rapides jusqu'à 210 ps [37], [38].

Le fonctionnement de cette technologie mémoire a été démontré par I. M. Miron *et al.* [39], [40] puis par L. Liu *et al.* [41]. Ces travaux ont démontré la capacité de cet empilement à commuter grâce à une conduction de courant sur le niveau de métal inférieur pour inverser l'état stocké dans la couche libre, comme représenté sur la Figure 1.19. Les phénomènes mis en avant expliquant la commutation de cette couche de stockage sont l'effet *Rashba* [39] et l'effet de *Spin Hall* [42].

FIGURE 1.19 – Schéma de la technologie mémoire SOT-MRAM.

Le Tableau 1.1 conclut cette première section, en répertoriant les différentes propriétés des technologies mémoires MRAMs. Comme il peut être noté, les deux dernières générations STT-MRAM et SOT-MRAM présentent de nombreux avantages en terme de surface, consommation et vitesse de fonctionnement. Ces caractéristiques en font de bons candidats pour une intégration dans l'Internet des Objets. Dans le cadre de cette thèse, la technologie mémoire STT-MRAM est privilégiée pour sa faible surface et faible consommation.

|             | Commutation | Surface | Consommation | Vitesse | Terminaux |

|-------------|-------------|---------|--------------|---------|-----------|

| FIMS-toggle | Champ       | Forte   | Forte        | Faible  | 2         |

| TAS         | Champ       | Moyenne | Moyenne      | Faible  | 2         |

| STT         | Courant     | Faible  | Faible       | Moyenne | 2         |

| SOT         | Courant     | Moyenne | Faible       | Forte   | 3         |

TABLEAU 1.1 – Caractéristiques des différentes technologies MRAMs présentées.

### 3 Sécurité des circuits intégrés

La cryptologie ou science du secret est le domaine qui permet d'assurer la sécurité des composants en rendant indéchiffrables, hormis pour l'expéditeur et le destinataire, les données échangées. Celle-ci englobe la **cryptographie** qui vise à chiffrer des messages personnels entre deux personnes grâce à des clés spécifiques. Sans ces clés, une personne extérieure est incapable de déchiffrer le message [43]. Afin de considérer la cryptographie comme opérationnelle et fonctionnelle, il est nécessaire de s'assurer que ces quatre points sont vérifiés :

- La confidentialité : les données sont accessibles uniquement aux sujets autorisés.

- L'intégrité : les données sont modifiables uniquement par les sujets autorisés.

- L'accessibilité : l'accès à un objet ne devrait pas être refusé à une personne autorisée.

- L'authenticité : Les données auxquelles l'utilisateur à accès sont vérifiées.

#### 3.1 La cryptographie et ses enjeux

#### 3.1.1 L'histoire de la cryptographie

La cryptographie est utilisée depuis l'antiquité pour chiffrer les messages. Le chiffrement de *César* est aujourd'hui le plus connu de cette période de l'histoire. Il consiste à chiffrer un message par un décalage des lettres de l'alphabet par un certain nombre fixe [44]. Ce type d'algorithme est simple à déchiffrer en réalisant une analyse fréquentielle selon l'utilisation des lettres dans la langue française. En effet, dans un message *M*, les lettres qui apparaissent le plus souvent peuvent être considérées comme les lettres qui apparaissent le plus dans la langue française. Par la suite, un choix est réalisé parmi les différentes possibilités.

La cryptographie fait également partie des moments les plus importants qui ont marqué l'histoire. Nous pouvons ainsi citer l'exemple de la machine *Enigma* utilisée par les allemands lors de la seconde guerre mondiale pour chiffrer leurs messages contenant leurs tactiques militaires [44], illustrée sur la Figure 1.20.

FIGURE 1.20 – Photographie d'Enigma [45].

Alan Turing a alors inventé ce qui peut être considéré comme un précepteur du premier ordinateur, qui permettait de déchiffrer ces messages et de garder une longueur d'avance sur les attaques planifiées par l'ennemi. Cette invention a joué un rôle majeur dans la victoire de la seconde guerre mondiale par les alliés.

Par la suite, la nécessité de protection des communications et des données par cryptographie en développpant des algorithmes de chiffrement fut décrétée par le *National Institute of Standards and Technology* – (NIST) anciennement *National Bureau of Standards* – (NBS) en 1973 [46]. Ces derniers doivent respecter les préceptes d'A. Kerckhoffs énoncés en 1883 [47] indiquant que :

- Le système de chiffrement doit être mathématiquement sécurisé.

- La sécurité du chiffrement ne doit dépendre que de la clé de chiffrement et non du secret de la méthode utilisée.

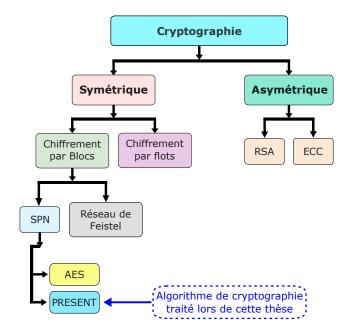

Il existe aujourd'hui un nombre important d'algorithmes de cryptographie qui peuvent être organisés en différentes catégories comme représenté sur la Figure 1.21.

#### 3.1.2 La cryptographie asymétrique

L'algorithme de Cryptographie à Clé Publique ou – *Public Key Cryptography* – (PKC) est apparu en 1976 grâce à W. Diffie et M. Hellman qui ont ouvert une nouvelle voie dans la cryptographie [48].

Les PKCs effectuent des chiffrements asymétriques. Pour cela, pour deux entités communicantes, chacune nécessite deux clés : une clé privée et une clé publique. Alors que la clé publique est transmissible sans aucune restriction, la clé privée n'est connue que de son détenteur. Le chiffrement d'un message clair en utilisant ce protocole est facilement réalisable. Toutefois, le déchiffrement ne peut pas être réalisé en inversant simplement la fonction de chiffrement. Cette fonction n'est pas bijective.

FIGURE 1.21 - Catégories des différents algorithmes de cryptographie.

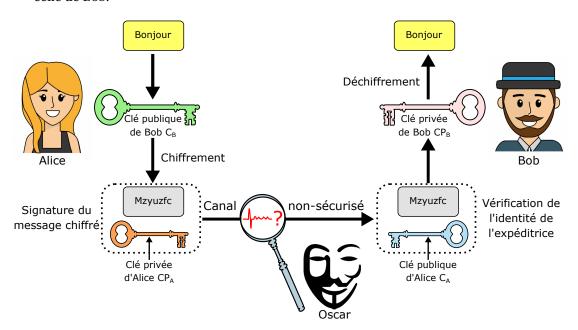

Considérons le cas où deux identités *Alice* et *Bob* souhaitent communiquer des informations sensibles sur un canal non-sécurisé. Une personne malveillante, *Oscar*, pourrait alors observer leur conversation sur ce canal. C'est pourquoi *Alice* et *Bob* chiffrent leurs messages, comme illustré sur la Figure 1.22.

Pour réaliser le chiffrement de leurs messages, chaque partie a une paire de clés :

- Une clé publique connue de tous, C<sub>A</sub> et C<sub>B</sub> respectivement pour l'entité *Alice* et *Bob*.

- Une clé privée connue uniquement par l'identité, tel que CP<sub>A</sub> la clé privée d'*Alice* et CP<sub>B</sub> celle de *Bob*.

FIGURE 1.22 - Modèle de fonctionnement d'un algorithme de cryptographie asymétrique.

Le chiffrement et déchiffrement du message secret nécessitent l'utilisation de deux de ces quatre clés. En effet, lorsque *Alice* souhaite envoyer un message secret à *Bob*, le message est chiffré par  $C_B$  alors que le déchiffrement est réalisé par *Bob* grâce à  $CP_B$ , comme illustré sur la Figure 1.22.

De plus, la clé CP<sub>A</sub> est utilisée par *Alice* pour signer son message alors que C<sub>A</sub> permet à *Bob* de confirmer l'identité de l'expéditrice.

L'un des principaux algorithmes de la cryptographie asymétrique est le chiffrement de Ri- $vest\ Shamir\ Adleman$  – (RSA), du nom de ses inventeurs, proposé en 1978 [49]. Le RSA est un

protocole se basant sur l'exponentiation modulaire où le chiffrement est réalisé par la fonction :  $C = M^e\ mod[N] \text{ tel que } C \text{ est le texte chiffré}, M \text{ le message clair}, e \text{ et et } N \text{ deux entiers}. La fonction

de déchiffrement d'autre part est réalisée par l'opération <math>M = C^d\ mod[N]$ , tel que d un entier.

Cette catégorie d'algorithmes de cryptographie est généralement plus lente que les algorithmes de cryptographie symétriques [46], [6].

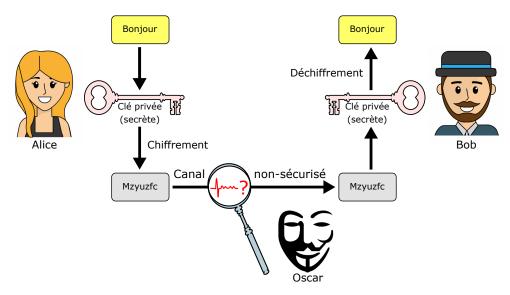

#### 3.1.3 La cryptographie symétrique

Les algorithmes de cryptographie symétriques ou à clé secrète sont des schémas d'offuscation d'un message clair, en utilisant une même clé - privée et secrète - pour le chiffrement et le déchiffrement, comme illustré Figure 1.23. Cette clé est communiquée entre les deux identités *Alice* et *Bob* par un canal sécurisé au préalable. Cette application de chiffrement et de déchiffrement est dite bijective.

FIGURE 1.23 - Modèle de fonctionnement d'un algorithme de cryptographie symétrique.

Les algorithmes à clé secrète symétriques peuvent être décomposés en deux principales catégories de techniques de chiffrement : les chiffrements par flots et les chiffrements par blocs.

#### 3.1.3.1 Les chiffrements par flots :

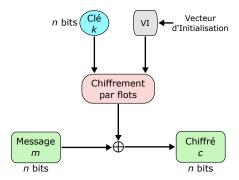

Les algorithmes de cryptographie par flots consistent à chiffrer des messages de toutes tailles [50], sans besoin de les découper au préalable [46]. Cette propriété permet de réaliser un chiffrement continu des données, sans nécessité d'attendre la transmission de tout le message. D'où, une utilisation accrue dans le domaine des télécommunications, où le transfert des données doit se faire de manière instantanée. Pour chaque message clair m de taille n ( $m_{n-1} \cdots m_0$ ) est associé une clé de taille identique n ( $k_{n-1} \cdots k_0$ ), afin de pouvoir réaliser le chiffrement bit à bit.

Les chiffrements par flots ont la particularité d'associer à chaque message un masque aléatoire, comme illustré sur la Figure 1.24. Il est nécessaire de modifier ce masque aléatoire après chaque chiffrement. Cette opération est appelée l'affectation d'un masque jetable. Ce masque est généralement généré par un générateur pseudo aléatoire. Ainsi, lors d'une première étape d'ini-

tialisation, la clé est combinée à un Vecteur d'Initialisation (*VI*) généré aléatoirement par un générateur pseudo aléatoire, comme illustré sur la Figure 1.24.

FIGURE 1.24 – Algorithme de chiffrement par flots : représentation des opérations réalisées sur un message clair m et une clé k pour obtenir le texte chiffré c, grâce à un Vecteur d'Initialisation VI.

Le résultat de ce masquage de la clé k permet le chiffrement du message m, bit à bit en utilisant majoritairement une fonction XOR, tel que développé en Équation 1.5.

$$\forall i \in [0, n], \quad c_i = m_i \oplus k_i \tag{1.5}$$

Il est possible de citer les algorithmes ChaCha [51], Mickey [52] ou encore Trivium [53] dans cette catégorie. Ces algorithmes sont recensés dans [54].

#### 3.1.3.2 Les chiffrements par blocs :

La seconde catégorie des chiffrements symétriques est la famille des chiffrements par blocs. Contrairement aux chiffrements par flots, la taille des messages m à chiffrer dépend directement de l'algorithme de cryptographie utilisé. Pour chaque algorithme, la clé et le message clair ont des tailles fixes.

En outre, les chiffrements par blocs sont réalisés en plusieurs tours d'opérations contrairement aux chiffrements par flots. Ces algorithmes se décomposent en deux sous-blocs :

#### — Réseau de Feistel :

Les réseaux de Feistel tiennent leur nom d'H. Feistel, l'inventeur de l'algorithme Lucifer qui fut le premier de ce type de chiffrements à être développé [55].

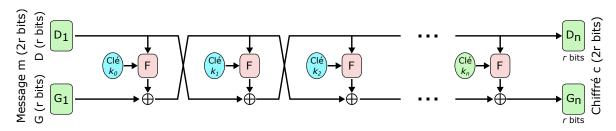

Afin de réaliser le chiffrement d'un message clair m via les réseaux de Feistel, il est nécessaire de décomposer dans un premier temps ce mot, en deux mots de tailles équivalentes. Soit le mot m de taille 2r décomposé en deux mots D et G, de G bits chacun. Considérons par exemple le premier tour de chiffrement, le mot G va être combiné à la clé alors que le mot G est transmis directement au tour suivant. Lors du second tour, le chiffrement est réalisé sur G. Ainsi, lors de chaque tour une seule moitié du message est chiffrée (alors que la seconde moitié est transmise au tour suivant). Chaque tour utilise une clé intermédiaire calculée par l'algorithme via la fonction G.

FIGURE 1.25 – Algorithme de type réseau de Feistel : représentation des différentes opérations réalisées sur un message clair m et une clé  $k_0$  pour obtenir le texte chiffré c, après (n+1) tours.

Dans cette catégorie de chiffrements, il est possible de citer : *Data Encryption Standard* – (DES) [56], triple-DES [57], Blowfish [58], SIMON et SPECK [59].

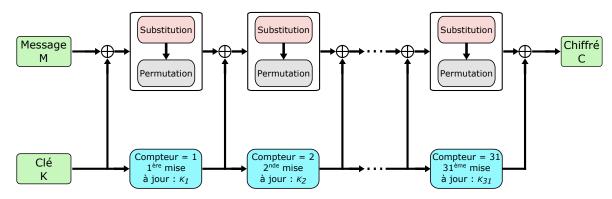

- Réseau de Substitution et de Permutation ou Substitution Permutation Network (SPN) : Ces algorithmes réalisent des opérations de substitution et de permutation à chaque tour du chiffrement. Cette technique de chiffrement se caractérise par trois opérations qui sont appliquées au message clair m afin d'obtenir le message chiffré c, comme illustré Figure 1.26.

- La première étape est l'exécution d'une fonction XOR entre la clé de chiffrement maître  $k_0$  et le message clair m.

- Le résultat de cette opération est envoyé vers une fonction de substitution. Chaque partie du message est remplacée par un mot de taille identique. Cette fonction est induite par une table de substitution pré-définie.

- La dernière étape de ce premier tour de chiffrement est la permutation. Dans un mot m, la position  $p_i$  du bit  $b_i$  est modifiée (également en suivant une table de permutation pré-définie).

La succession de ces opérations est répétée le nombre de tours nécessaires pour le chiffrement du message par l'algorithme.

FIGURE 1.26 – Algorithme de type SPN : représentation des différentes opérations réalisées sur un message clair m et une clé  $k_0$  pour obtenir le texte chiffré c, après (n+1) tours.

Le chiffrement considéré aujourd'hui comme référence est le chiffrement standard avancé ou – *Advanced Encryption Standard* – (AES) (chiffrement de Rijndael) [60], [61]. Il est comme son nom l'indique la technique de chiffrement standard utilisée depuis 2007. Cet algorithme après avoir été publié en 1998, a démontré son intérêt en matière de performances (vitesse, consommation et sécurité) face à ses concurrents.

La cryptographie symétrique et la cryptographie asymétrique sont deux techniques complémentaires de chiffrement. Alors que la première présente des avantages majeurs en termes de performance et de vitesse, permettant ainsi le chiffrement à faible coût, d'un message par deux entités ayant un accès physique à la clé secrète, la seconde est nécessaire pour par exemple la communication, au préalable, de cette clé entre ces entités de manière sécurisée. De plus, la cryptographie asymétriques est utilisée lors de la confection de protocoles d'authentification et de signature des messages.

Les algorithmes de cryptographie (symétriques et asymétriques) se sont multipliés lors cette dernière décennie par la proposition de chiffrements dont les performances conviendrait à l'Internet des Objets (surface et consommation réduites et vitesse d'exécution importante). Ce fut l'avènement de la cryptographie légère ou – *Light Weight Cryptography* – (LWC). Cette famille d'algorithmes est extrêmement étudiée et présente un nombre important d'algorithmes développés, comme pour exemple : Camellia [62], Piccolo [63], SEA [64], KLEIN [65], PRINCE [66], PRIDE [67], ou encore PRESENT [68] qui est un standard de la cryptographie légère.

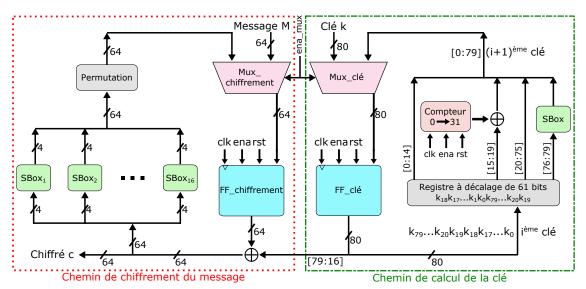

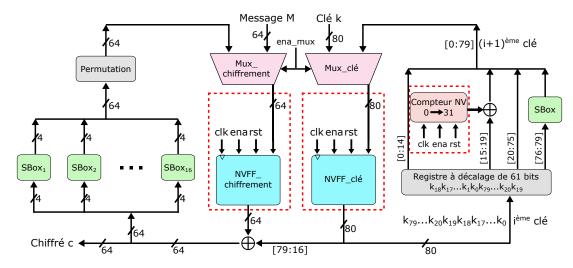

Dans le cadre des études réalisées lors de cette thèse, l'algorithme de cryptographie étudié est le chiffrement symétrique de type SPN : PRESENT [68], précédemment illustré sur la Figure 1.21.

#### 3.2 Les différentes techniques d'attaques matérielles

Les attaques visant à exploiter des résultats erronés dans un calcul, de corrompre le fonctionnement du circuit et donc de récupérer des informations secrètes sont en constante évolution. Ces attaques peuvent être de différents types, logicielles ou matérielles. Les attaques qui sont présentées dans ce chapitre sont les attaques matérielles. Ces dernières peuvent être classées en deux catégories distinctes : les attaques par observation et les attaques par perturbation.

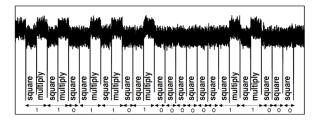

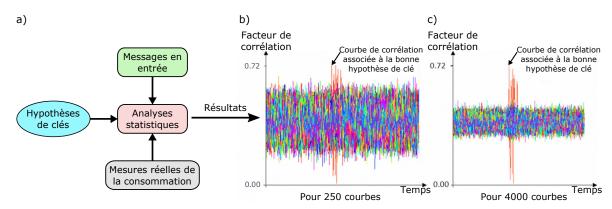

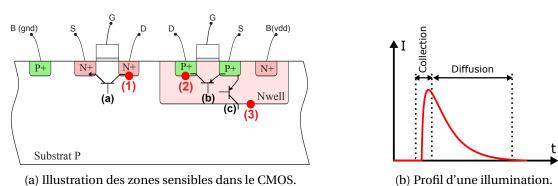

#### 3.2.1 Les attaques par observation

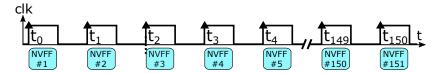

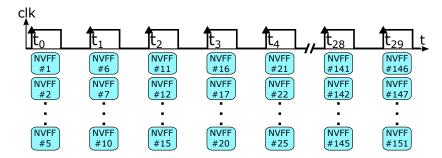

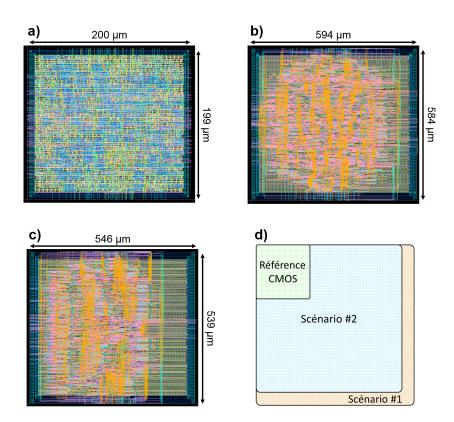

Les attaques par observation correspondent aux attaques non-invasives qui peuvent être réalisées sur des circuits, sans altérer leur fonctionnement interne ou modifier leurs caractéristiques physiques. Cette catégorie d'attaques est constituée essentiellement des attaques par canaux cachés (ou canaux auxiliaires), des attaques qui exploitent des failles matérielles pour retrouver les données secrètes. En effet, le fonctionnement d'un circuit peut conduire à des fuites exploitables par l'attaquant. Ces fuites dépendent des données manipulées par le circuit, conduisant à des émissions électromagnétiques [69], une consommation en courant [70], des temps de calculs [71] ou encore des émissions acoustiques [72] qui dépendent des données manipulées, et donc de la clé de chiffrement.