# High-level synthesis and arithmetic optimizations Yohann Uguen

#### ▶ To cite this version:

Yohann Uguen. High-level synthesis and arithmetic optimizations. Computer Arithmetic. INSA Lyon, 2019. English. NNT: . tel-02420901v1

# $\begin{array}{c} {\rm HAL~Id:~tel-02420901} \\ {\rm https://hal.science/tel-02420901v1} \end{array}$

Submitted on 20 Dec 2019 (v1), last revised 17 Jul 2020 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2019LYSEI099

## THÈSE de DOCTORAT DE L'UNIVERSITÉ DE LYON

Opérée au sein de :

(INSA de Lyon, CITI lab)

Ecole Doctorale InfoMaths EDA 512 (Informatique Mathématique)

Spécialité de doctorat : Informatique

Soutenue publiquement le 13/11/2019, par :

## Yohann Uguen

# High-level synthesis and arithmetic optimizations

Devant le jury composé de :

Frédéric Pétrot Président

Professeur des Universités, TIMA, Grenoble, France

Philippe Coussy Rapporteur

Professeur des Universités, UBS, Lorient, France

Olivier Sentieys Rapporteur

Professeur des Universités, Univ. Rennes, Inria, IRISA, Rennes

Laure Gonnord Examinatrice

Maître de conférence, Université Lyon 1, France

Martin Kumm Examinateur

Professeur des Universités, Université de Fulda, Allemagne

Florent de Dinechin Directeur de thèse

Professeur des Universités, INSA Lyon, France

## Résumé

À cause de la nature relativement jeune des outils de synthèse de haut-niveau (HLS), de nombreuses optimisations arithmétiques n'y sont pas encore implémentées. Cette thèse propose des optimisations arithmétiques se servant du contexte spécifique dans lequel les opérateurs sont instanciés. Certaines optimisations sont de simples spécialisations d'opérateurs, respectant la sémantique du C. D'autres nécéssitent de s'éloigner de cette sémantique pour améliorer le compromis précision/coût/performance. Cette proposition est démontré sur des sommes de produits de nombres flottants. La somme est réalisée dans un format en virgule-fixe défini par son contexte.

Quand trop peu d'informations sont disponibles pour définir ce format en virgule-fixe, une stratégie est de générer un accumulateur couvrant l'intégralité du format flottant. Cette thèse explore plusieurs implémentations d'un tel accumulateur. L'utilisation d'une représentation en complément à deux permet de réduire le chemin critique de la boucle d'accumulation, ainsi que la quantité de ressources utilisées.

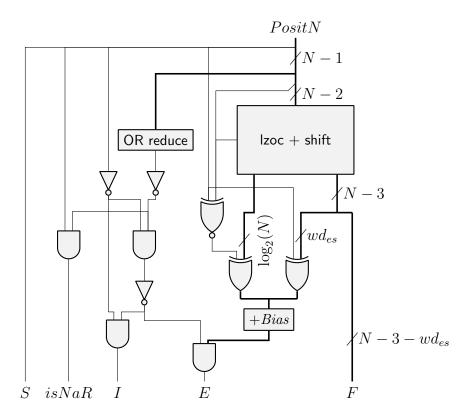

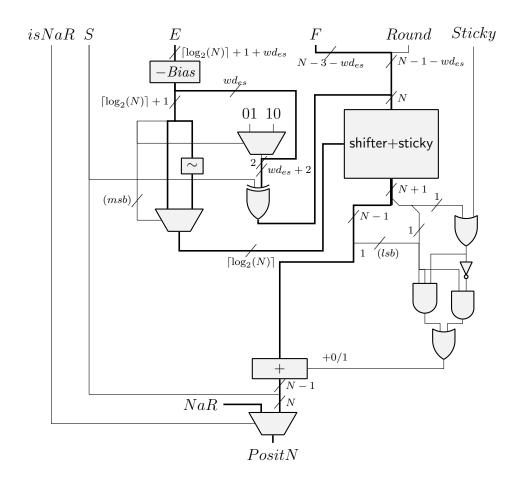

Un format alternatif aux nombres flottants, appelé posit, propose d'utiliser un encodage à précision variable. De plus, ce format est augmenté par un accumulateur exact. Pour évaluer précisément le coût matériel de ce format, cette thèse présente des architectures d'opérateurs posits, implémentés avec le même degré d'optimisation que celui de l'état de l'art des opérateurs flottants. Une analyse détaillée montre que le coût des opérateurs posits est malgré tout bien plus élevé que celui de leurs équivalents flottants.

Enfin, cette thèse présente une couche de compatibilité entre outils de HLS, permettant de viser plusieurs outils avec un seul code. Cette bibliothèque implémente un type d'entiers de taille variable, avec de plus une sémantique strictement typée, ainsi qu'un ensemble d'opérateurs ad-hoc optimisés.

## Abstract

High-level synthesis (HLS) tools offer increased productivity regarding FPGA programming. However, due to their relatively young nature, they still lack many arithmetic optimizations. This thesis proposes safe arithmetic optimizations that should always be applied. These optimizations are simple operator specializations, following the C semantic. Other require to a lift the semantic embedded in high-level input program languages, which are inherited from software programming, for an improved accuracy/cost/performance ratio. To demonstrate this claim, the sum-of-product of floating-point numbers is used as a case study. The sum is performed on a fixed-point format, which is tailored to the application, according to the context in which the operator is instantiated.

In some cases, there is not enough information about the input data to tailor the fixed-point accumulator. The fall-back strategy used in this thesis is to generate an accumulator covering the entire floating-point range. This thesis explores different strategies for implementing such a large accumulator, including new ones. The use of a 2's complement representation instead of a sign+magnitude is demonstrated to save resources and to reduce the accumulation loop delay.

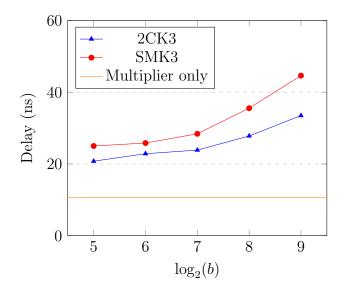

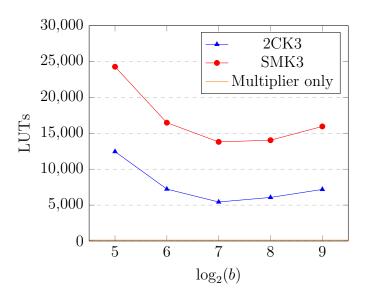

Based on a tapered precision scheme and an exact accumulator, the posit number systems claims to be a candidate to replace the IEEE floating-point format. A throughout analysis of posit operators is performed, using the same level of hardware optimization as state-of-the-art floating-point operators. Their cost remains much higher that their floating-point counterparts in terms of resource usage and performance.

Finally, this thesis presents a compatibility layer for HLS tools that allows one code to be deployed on multiple tools. This library implements a strongly typed custom size integer type along side a set of optimized custom operators.

## Contents

| 1 | Intr | troduction |                                                                 |    |

|---|------|------------|-----------------------------------------------------------------|----|

| 2 | Con  | ıtext      |                                                                 | 13 |

|   | 2.1  | Repres     | senting real numbers                                            | 13 |

|   |      | 2.1.1      | Fixed-point representation                                      | 13 |

|   |      | 2.1.2      | Floating-point representation                                   | 15 |

|   | 2.2  | Field 1    | Programmable Gate Arrays (FPGAs)                                | 20 |

|   |      | 2.2.1      | FPGAs architecture                                              | 20 |

|   |      | 2.2.2      | FPGAs programming model                                         | 23 |

| 3 | Brio | dging l    | nigh-level synthesis and application specific arithmetic        | 29 |

|   | 3.1  | Optim      | ization examples that do not change the program semantic        | 31 |

|   |      | 3.1.1      | Floating-point corner-case optimization                         | 31 |

|   |      | 3.1.2      | Integer multiplication by a constant                            | 33 |

|   |      | 3.1.3      | Integer division by small constants                             | 33 |

|   |      | 3.1.4      | Floating-point multiplications and divisions by small constants | 36 |

|   |      | 3.1.5      | Evaluation in context                                           | 37 |

|   | 3.2  | Optim      | ization examples that change the program semantic               | 38 |

|   |      | 3.2.1      | High-level synthesis (HLS) faithful to the floats               | 38 |

|   |      | 3.2.2      | Towards HLS faithful to the reals                               | 39 |

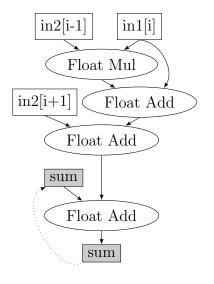

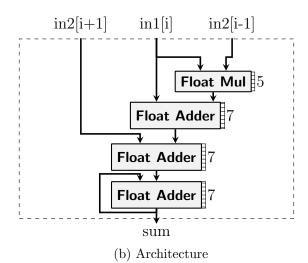

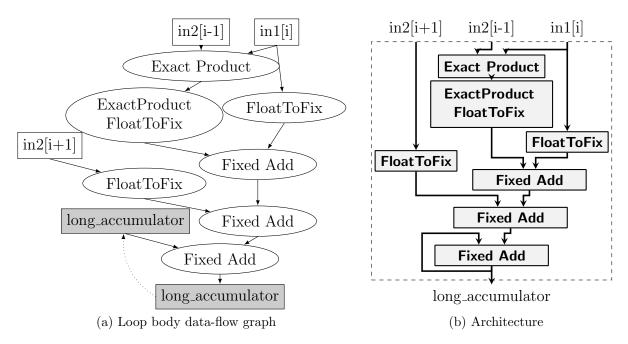

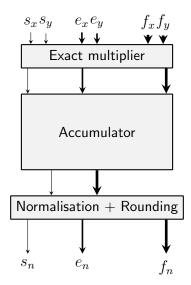

|   |      | 3.2.3      | The arithmetic side: application-specific accumulator support   | 40 |

|   |      | 3.2.4      | The compiler side: source-to-source transformation              | 43 |

|   |      | 3.2.5      | Evaluation in context                                           | 48 |

|   | 3.3  | Discus     | sion                                                            | 51 |

| 4 | Arc  | hitectı    | re exploration of exact floating-point accumulators             | 53 |

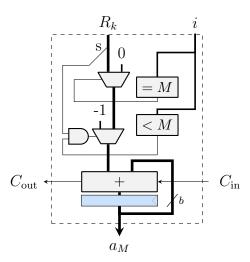

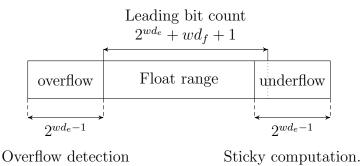

|   | 4.1  | Param      | eters of an accumulator for exact sums and sums-of-products     | 54 |

|   | 4.2  | Kulisc     | h-1: Long adder and long shift                                  | 55 |

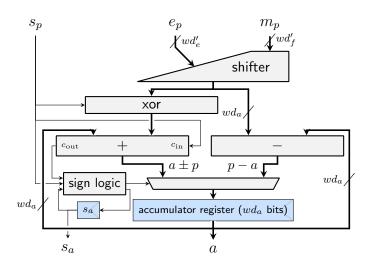

|   |      | 4.2.1      | Kulisch-1 with the accumulator in sign+magnitude                | 55 |

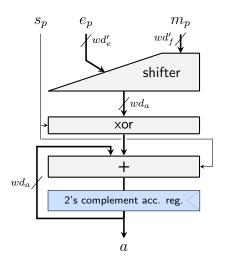

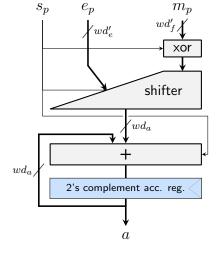

|   |      | 4.2.2      | Kulisch-1 with the accumulator in 2's complement                | 56 |

|   |      | 4.2.3      | Kulisch-1 high-radix carry-save architecture                    | 57 |

|   | 4.3  | Segme      | nting the accumulator into words                                | 58 |

|   |      | 4.3.1      | Kulisch-2: Segmented accumulator in RAM                         | 58 |

|   |      | 4.3.2      | Kulisch-3: Sub-adders with delayed carry propagation            | 59 |

|   | 4.4  | Recove     | ering the accumulator values                                    | 61 |

|   | 4.5  |            | ation of Kulisch accumulators                                   | 63 |

|   |      | 4.5.1      | Cost/frequency/latency trade-off                                | 64 |

|        |      | 4.5.2 Comparisons with plain floating-point accumulation          | 65        |  |  |  |

|--------|------|-------------------------------------------------------------------|-----------|--|--|--|

|        | 4.6  | Discussion                                                        | 66        |  |  |  |

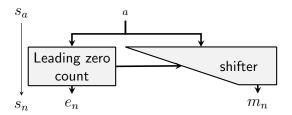

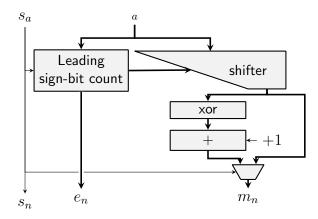

| 5      | Arc  | chitecture exploration of operators for the posit number system 6 |           |  |  |  |

|        | 5.1  |                                                                   | 68        |  |  |  |

|        |      | 1                                                                 | 68        |  |  |  |

|        |      |                                                                   | 69        |  |  |  |

|        | 5.2  |                                                                   | 70        |  |  |  |

|        |      |                                                                   | 70        |  |  |  |

|        |      |                                                                   | 71        |  |  |  |

|        |      |                                                                   | 72        |  |  |  |

|        |      | •                                                                 | 73        |  |  |  |

|        |      |                                                                   | 75        |  |  |  |

|        | 5.3  | ·                                                                 | 76        |  |  |  |

|        |      |                                                                   | 76        |  |  |  |

|        |      | • • •                                                             | 80        |  |  |  |

|        |      |                                                                   | 81        |  |  |  |

|        | 5.4  | ·                                                                 | 82        |  |  |  |

|        | 5.5  | O I                                                               | °-<br>85  |  |  |  |

|        |      |                                                                   |           |  |  |  |

| 6      | A t  | ype-safe arbitrary precision arithmetic portability layer for HLS |           |  |  |  |

|        | tool | $_{ m S}$                                                         | <b>87</b> |  |  |  |

|        | 6.1  | Background and motivation                                         | 88        |  |  |  |

|        |      | v e                                                               | 88        |  |  |  |

|        |      | 6.1.2 Type safety                                                 | 89        |  |  |  |

|        |      | 6.1.3 Core arithmetic primitives for floating-point and posits    | 90        |  |  |  |

|        |      | 6.1.4 Fused arithmetic primitives                                 | 90        |  |  |  |

|        |      | 6.1.5 Support of these primitives in HLS tools                    | 91        |  |  |  |

|        | 6.2  | Type safety for arbitrary-precision integers in HLS               | 91        |  |  |  |

|        |      | 6.2.1 Variable declaration                                        | 91        |  |  |  |

|        |      | 6.2.2 Variable assignment                                         | 91        |  |  |  |

|        |      | 6.2.3 Slicing                                                     | 92        |  |  |  |

|        |      | 6.2.4 Concatenation                                               | 92        |  |  |  |

|        |      | 6.2.5 Others                                                      | 92        |  |  |  |

|        | 6.3  | Portability to mainstream HLS tools                               | 94        |  |  |  |

|        |      | 6.3.1 Class duplication for each backend                          | 94        |  |  |  |

|        |      |                                                                   | 94        |  |  |  |

|        |      | 6.3.3 Curiously recurring template pattern (CRTP)                 | 94        |  |  |  |

|        | 6.4  | Evaluation                                                        | 95        |  |  |  |

|        | 6.5  | Discussion                                                        | 98        |  |  |  |

| 7 Conc |      | clusion and future work 99                                        |           |  |  |  |

| -      | 7.1  |                                                                   | 99        |  |  |  |

|        |      |                                                                   | 00        |  |  |  |

## Remerciements (Acknowledgements)

Cette thèse n'aurait pu être possible sans un certain nombre de personnes clés.

D'un point de vue scientifique, cette thèse s'appuie sur deux personnes: Mon directeur de thèse Florent de Dinechin pour l'arithmétique des ordinateurs et mon mentor rennais Steven Derrien pour la compilation. Je n'aurai pas pu rêver mieux que Florent de Dinechin en tant que directeur de thèse. Il a non seulement essayé de me transmettre ses connaissances mais également ses intuitions. Un puits de savoir me laissant croire que nous avions tous les deux des choses à nous apporter. Je serai à jamais reconnaissant de tout ce qu'il m'a transmis. Avant lui, Steven Derrien m'avait ouvert les portes de la recherche académique dès la licence. Sans retenue, il m'a formé à des outils modernes et confronté à des problématiques inexplorées. À mi-chemin entre la compilation et l'architecture, il a su me pousser vers un filon prometteur, filon qui a fini par déboucher sur cette thèse.

D'un point de vue personnel, j'ai toujours été aveuglément soutenu par ma mère et ma famille malgré quelques virages le long du chemin. Il semblerait que le fait d'avoir atteint une destination nous fasse relativiser l'importance de la destination originelle. Bien évidemment, le bonheur quotidien partagé avec Léonie Caprais/Bliskiye m'a offert un contexte de vie et de travail idéal. Elle a su rester ma supportrice officielle, malgré mon humour... discutable. Même lors de ses réactions bilatérales symétriques, elle a su être l'oreille attentive dont j'avais besoin. Son rôle était était essentiel et m'a permis de prendre du recul sur mon travail. Depuis mes débuts en informatique, la présence inconditionnelle de mon cher ami Thomas Lefeuvre/Trackman\_ était aussi indispensable à ma réussite. Pendant nos études comme dans les jeux vidéos, notre symbiose et notre travail d'équipe ont toujours payé. Et c'est sans compter sur son humour douteux (partagé) dans les moments difficiles (ou non). D'autres m'ont rejoint plus loin au cours de ce voyage comme Jean-Baptiste Trystram/SuperMaki\_, m'enseignant la mécanique, que ce soit les mains dans le cambouis ou face à un tableau blanc.

Plus largement, l'ensemble des personnes que je côtoie m'ont, de près ou de loin, aidé dans cette aventure. Je pense notamment à Guillaume Uguen et Fanny Marrot avec leurs week-ends "dégustation", Jonathan Tournier pour les sessions d'escalade, ainsi que Marion Trystram et Amandine Chaudier pour les soirées lyonnaises et les week-ends à la montagne. Je pense aussi aux doctorants du CITI comme Luc Forget pour ses collaborations et son esprit critique, m'ayant apporté une nouvelle façon de travailler, mais aussi à tous les autres: David Kibloff, Tristan Delizy, Gautier Berthou etc. J'ai aussi une pensée pour le reste des membres du CITI et en particulier pour Guillaume Salagnac et nos échanges enrichissants.

À l'ensemble de ces personnes, merci.

## Chapter 1

## Introduction

If you don't know how to start your introduction, you can always begin by saying: Even the Romans...

An old German teacher...

Even the Romans faced the difficulty of building a good number system. Indeed, the Roman numerals lack some computation qualities. In that matter, a good number system should find a good trade-off between:

- (1) being a compact representation,

- (2) being easy to interpret,

- (3) being easy to compute on.

The Roman numerals are a base-10 system, just like the usual base-10 Arabic numerals. In terms of (1) being a compact representation, the Roman numerals sometimes are more compact than the Arabic system (e.g M=1000). However, most of the time they are not. Indeed, the representation of one decimal digit in the Arabic system requires between zero and four characters (e.g. IX = 10 - 1 = 9, VIII = 5 + 1 + 1 + 1 = 8). This also means that (2) the interpretation of a value requires many intermediate computations. The reader is invited to parse my birth year (MCMXCII), starting by identifying the character groups that correspond to each power of ten. Since Roman numerals encode a base-10 position system, it is however (3) possible to perform additions and subtractions. The corresponding algorithm is more complex than its base-10 Arabic system counterpart. Still, there were abacuses (mechanical computing devices) for Roman numerals.

The base 10 Arabic numerals improve Roman numerals on (1), (2) and (3). This probably explains why Roman numerals are now only used for aesthetics, for example on some clock faces.

The example of Roman numerals demonstrates that representing the set of integers using textual characters is not straightforward. Representing real numbers is even more difficult, especially if one intends to automate the computation. In a physical computing device (abacus or computer), a number is represented by a discrete finite quantity of information. As the set of integers is discrete, it is relatively easy to map a finite subset of integers to such a device. However the reals are a continuous set, therefore an additional difficulty is to chose the finite discrete subset that can be represented.

The general consensus on representation of real numbers in modern computers is the IEEE-754 standard [1]. It defines floating-point formats that are followed by most central processing units (CPUs). This standard is so well established that a CPU performance is usually measured as its peak FLOP/sec (floating-point operations per second). For that matter, the performance of the floating-point units (FPUs) has been, and is still, a subject of improvement [2, 3, 4, 5, 6, 7, 8, 9].

As CPUs are general-purpose processors, they are built from a low count of fast but complex cores. Alternatively, graphics processing units (GPUs) are built from a very high count of slow and simple cores. CPUs are therefore optimized for latency of general purpose applications, while GPUs are optimized for throughput of highly parallel applications. In both cases, because of their genericity, these processors implement an instruction based mechanism. The latter requires to be able to decode and execute said instructions before storing the results.

When optimizing a specific application, performance improvements can be achieved through the use of a custom hardware accelerator. In this context, the overheads due to genericity can be mitigated. For example, there is no need for instructions and their associated mechanisms. Also, the wide variety of operators can be limited to the required ones. Those can even be replicated as many times as possible. Regarding floating-point operators, the application might not even require strict IEEE-754 compliance [10, 11].

Further optimizations can be made through operator specialization. For instance, a complete floating-point divisor/multiplier might not be required if the application only performs a division/multiplication by a constant [12, 13, 14].

Depending on the application accuracy requirements and the nature of the input data, the datapath of the circuit can be tailored so that enough but no more bits than needed are computed. Examples of such circuits range from artificial intelligence performed using ternary arithmetic [15] to digital signal processing filters [16].

All these optimizations are enabled by moving away from generic processors to application-specific accelerators.

To implement an accelerator, several technologies can be used. Application-specific integrated circuits (ASICs) offer the most performance. However, the manufacturing process of such hardware is very expensive. This cost can only be mitigated by a large production. An alternative is to use circuits that can be reconfigured after manufacturing such as field-programmable gate arrays (FPGAs). The cost of such circuits is reduced as they can be produced at a large scale. For a given application, FPGAs can offer better performance than CPUs at a fraction of the cost of an ASIC.

The highly customizable nature of FPGAs comes at the price of a more difficult programming model than the one of general purpose processors. Indeed, programming a FPGA is done through low level hardware description languages (HDLs). These are notoriously error prone and difficult to debug. However, because of the very mature nature of HDLs, many libraries and code generators provide highly optimized designs for programmers to build around.

To increase the productivity of hardware designers, new techniques try to compile classical programming languages to HDLs. Such a process is called high-level synthesis (HLS). This compilation flow is less mature than classical HDL synthesis. HLS-generated designs has long been inferior to handwritten HDL components regarding performance and resource consumption. However, HLS offered increased productivity. This is less and less true: in many situations, HLS now not only improves productivity, but also the quality of

the results. This thesis shows several contributions to this trend, all related to arithmetic computations.

First, most arithmetic optimizations in current HLS tools rely on their underlying compiler frameworks. In particular, the instruction selection of the CPU backend is used as a *better than nothing* optimization. However, the FPGA arithmetic community has long worked on better FPGA-specific optimizations. A first axis of this thesis, described in Chapter 3, is to try to fill this gap between the compiler designers community and the arithmetic community, when targeting FPGAs.

As a second axis, Chapters 4 and 5 are experiments in using HLS to explore the architecture design space for two non-standard arithmetic objects: Kulisch's exact floating-point accumulators and Gustafson's posits (an alternative to floating-point for representing real numbers). The use of C++ templates enables genericity beyond what HDL generators can offer. Furthermore, templated operators are compiled and optimized by the HLS tools in their context. In both cases, the operators libraries designed this way are the state of the art.

When performing such architecture explorations, the use of a custom-size integer library is required for tailoring the datapath. As HLS tools do not all use the same integer library, source code cannot be shared between tools. Furthermore, each FPGA vendor uses its own HLS tool, which makes the generated code suboptimal on FPGAs of a different vendor. This is problematic to compare novel designs to the state-of-the-art if not targeting the same FPGA brand. A third and last axis of this thesis, described in Chapter 6, is to build an abstraction layer on top of vendor custom-size integer libraries. Thus, it allows a programmer to only write one component for all supported tools. Furthermore, the proposed library embeds a type-safe semantic and offers several useful operators.

Beforehand, a preliminary Chapter (2) introduces the necessary notions to understand this thesis. It starts by reminding the basic formats for representing real numbers and perform arithmetic computations. It then gives the necessary an overview of FPGAs architecture and their programming model.

## Chapter 2

## Context

As this thesis is about arithmetic optimizations for high-level synthesis tools, this Chapter first introduces number representations onto which arithmetic optimizations are performed. A second part presents the hardware targeted in this work and their programming model, in particular it presents high-level synthesis tools.

#### 2.1 Representing real numbers

The efficient manipulation of real numbers in computers relies on the representation in which the data is approximated. The choice of such a representation is often not straightforward as it is tied to a accuracy/speed/ease-of-use/cost trade-off. The most widely used ways of representing real numbers is floating-point arithmetic presented in 2.1.2. There are emerging alternative formats, such as posits that will be presented in Chapter 5. Floating-point and posit operators are built out of simpler fixed-point operations. Therefore, fixed-point arithmetic is presented in 2.1.1.

#### 2.1.1 Fixed-point representation

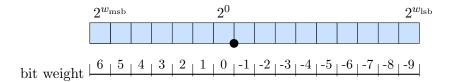

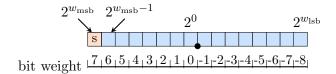

A N-bit unsigned fixed-point format is defined by the weight  $w_{\rm lsb}$  of its least significant bit (LSB) and the weight  $w_{\rm msb}$  of its most significant bit (MSB), with  $w_{\rm msb} = w_{\rm lsb} + N - 1$ . A number in such a format holds N weighted binary digits  $x_i$  and represents the rational number

$$x = \sum_{i=w_{\rm lsb}}^{w_{\rm msb}} 2^i x_i$$

An example is given in Figure 2.1. Here  $(w_{\text{msb}}, w_{\text{lsb}}) = (6, -9)$ , hence N = 16. The LSB is then the  $9^{th}$  fraction bit from the decimal point (which is actually here a binary point).

Figure 2.1: The bits of an unsigned fixed-point format, here  $(w_{\text{msb}}, w_{\text{lsb}}) = (6, -9)$ .

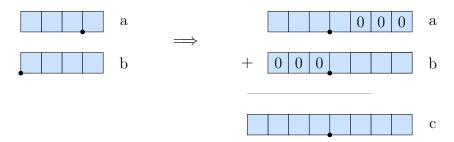

Figure 2.2: Illustration of the summation of unsigned fixed-point numbers with different formats.

Negative numbers are supported by either using a sign+magnitude or a 2's complement encoding. The sign+magnitude encoding adds a sign bit to specify the signedness of the fixed-point value. The 2's complement encoding stores negative numbers as their complement with respect to  $2^N$ . As an example, the 2's complement of the 4-bit value  $0110_b$  is  $1010_b$  as  $0110_b + 1010_b = 10000_b$ . The 2's complement encoding has the advantage that the fundamental arithmetic operations of addition and subtraction are identical to those for unsigned binary numbers, which is not the case of the sign+magnitude arithmetic. A value encoded using the 2's complement encoding can be decoded as follows:

$$x = -2^{-w_{\text{msb}}} + \sum_{i=w_{\text{lsb}}}^{w_{\text{msb}}-1} 2^{i} x_{i}$$

Fixed-point arithmetic requires carefulness if the format changes during the computation. As a general example, lets consider a and b where a uses a  $(w_{\mathrm{msb}_a}, w_{\mathrm{lsb}_a})$  fixed-point format and b a  $(w_{\mathrm{msb}_b}, w_{\mathrm{lsb}_b})$  one. Their exact sum c = a + b requires a  $(w_{\mathrm{msb}_c}, w_{\mathrm{lsb}_c})$  where  $w_{\mathrm{msb}_c} = \max(w_{\mathrm{msb}_a}, w_{\mathrm{msb}_b}) + 1$  and  $w_{\mathrm{lsb}_c} = \min(w_{\mathrm{lsb}_a}, w_{\mathrm{lsb}_b})$ . Indeed, prior to performing the operation, the numbers are first aligned according to their bit weights. Figure 2.2 illustrates this alignment where a uses a (2, -1) format and b uses a (-1, -4) format. Here a has 3 decimal bits and 1 fractional bit where b has no decimal bit and 4 fractional bits. In that case, b must be arithmetically shifted so that it aligns with a, as a holds the most significant bits before the summation can occur. Therefore, the final result c, if computed exactly, requires a (3,-4) fixed-point format.

The extra bit added to  $\max(w_{\text{msb}_a}, w_{\text{msb}_b})$  is to capture the output carry that can be produced by the addition. Indeed, once the inputs are aligned, the sum of two N-bit fixed-point values will produce the following exact answer:

$$z = x + y$$

$$= \sum_{i=w_{lsb}}^{w_{msb}} 2^{i} x_{i} + \sum_{i=w_{lsb}}^{w_{msb}} 2^{i} y_{i}$$

$$= \sum_{i=w_{lsb}}^{w_{msb}} 2^{i} (x_{i} + y_{i})$$

$$= \sum_{i=w_{lsb}}^{w_{msb}+1} 2^{i} z_{i}$$

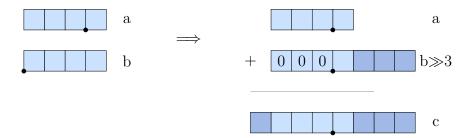

Figure 2.3: Illustration of the summation of two numbers usign different unsigned fixed-point formats using only the 4-bit integer arithmetic.

In a software context When programming a CPU, fixed-point numbers are computed using integer arithmetic. Support for fixed-point numbers is then easy and fast. However, values must use a format where N is of a standard integer size. The formats are chosen before the computation according to the manipulated values and their associated operations. However, when manipulating variables, chosing a format can be challeging as the range and the accuracy of the data might not be known beforehand. Having a software mechanism to change the format at runtime according to the current value of the variable would be very costly - it would be some form of floating point. As most programs rely on variables, fixed-point formats are difficult to use in the general case.

The programmer is in charge of handling the change of format of the variables after each operation. To illustrate this format management, let us consider 4-bit integer arithmetic. The example from Figure 2.2 can be modified to the one from Figure 2.3. The programmer must have chosen the formats of the three variables. Here, a and c uses a (2,-1) format and b uses a (-1,-4) format. The variable b must first be shifted by 3 to the right before the summation. The 3 LSBs of b are then discarded. The 4-bit addition is then performed and the extra bit of the exact sum must be discarded because it does not belong to the format of the result. All the discarded bits entail numerical errors.

For all these reasons, code written using a fixed-point representation is usually not flexible. Little code modifications might make the programmer change and debug his entire program again.

A software emulation of a larger fixed-point format can be obtained by chaining multiple standard size integers. This tedious process can be eased by using dedicated C/C++ libraries such as GMP [17]. This chaining approach reveals a performance/accuracy trade-off. Also, some previous work try to ease the fixed-point usage by inferring the correct fixed-point formats for a given application [18, 19, 20, 21, 22].

In a hardware context When designing custom hardware, the standard sizes are no longer a limitation. Each operator and datapath can be tailored. The size of the format then becomes a parameter of the architecture to control the accuracy. This still entails issues related to format conversion, operations on data formats, etc. Chapter 6 will include and in-depth discussion on these issues.

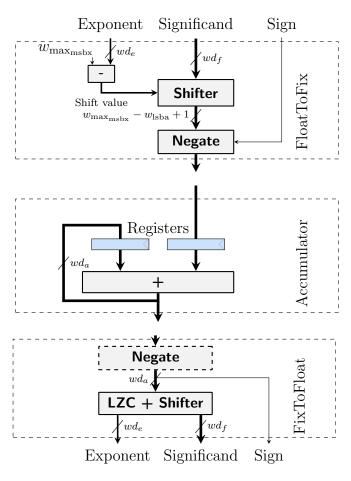

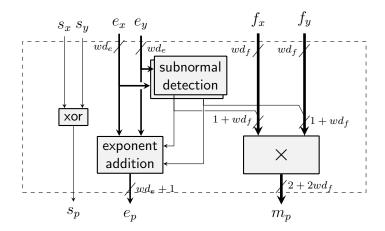

#### 2.1.2 Floating-point representation

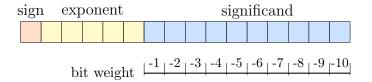

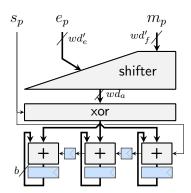

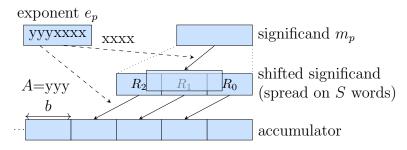

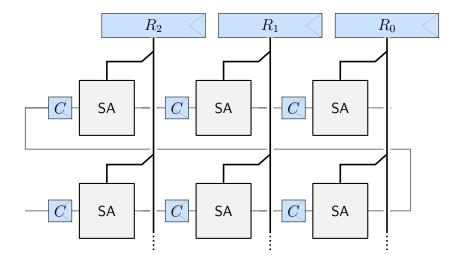

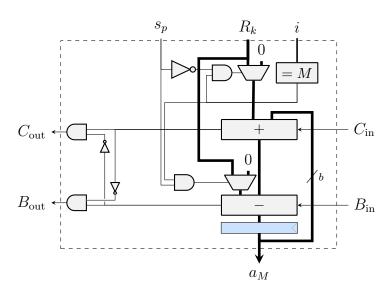

A N-bit floating-point format is defined by the size  $wd_e$  of its exponent e and the size  $wd_f$  of its signed significand f, with  $N = 1 + wd_e + wd_f$ . The extra bit is used to store the

sign s of the encoded value. Such an encoding is illustrated by Figure 2.4.

Figure 2.4: The bits of a floating-point format, here  $(wd_e, wd_f) = (5, 10)$ .

The value x of a normal floating-point number is defined [23] as:

$$x = (-1)^s \cdot 2^e \cdot 1.f$$

The notation 1. f expresses that an implicit bit is appended to the significand with a weight of 0. The exponent e must be signed so that small values may be represented as well as large values. Instead of using a 2's complement encoding, the choice here is a biased representation: the exponent bits represent an unsigned integer k, and the exponent e is e = k - bias, where  $\text{bias} = 2^{wd_e-1} - 1$ . This choice eases the comparisons as it makes the floating-point numbers to follow the natural order of their encodings (see Table 2.1 below). Hence, if  $f_i$  is the bit of f with weight i, the decoded floating-point value is:

$$x = (-1)^s \cdot 2^{k-\text{bias}} \cdot (1 + \sum_{i=-1}^{-wd_f} 2^i f_i)$$

Figure 2.5: Floating-point value example where  $(wd_e, wd_f) = (3, 5)$ .

To illustrate this decoding, Figure 2.5 shows a floating-point value on a  $(wd_e, wd_f) = (3,5)$  format. Here s = 1, k = 4 and  $f = 2^{-1} + 2^{-2} + 2^{-3} = 0.875$ . Hence, the decoded value is:

$$x = (-1)^{1} \cdot (2^{4-(2^{3-1}-1)}) \cdot 1.875$$

$$= -1 \cdot 2 \cdot 1.875$$

$$= -3.75$$

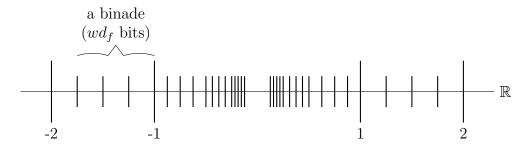

**Subnormal numbers** As the implicit bit is set to 1, values close to 0 (included) cannot be represented. To illustrate this phenomenon, Figure 2.6 represents normal floating-points  $((wd_e, wd_f) = (3, 2))$  on the real axis. The smallest positive and largest negative values that can be represented in this format are  $1.00_b \cdot 2^{-3}$  and  $-1.00_b \cdot 2^{-3}$ . This leads to a large gap centered in 0. To cope with this phenomenon, the IEEE-754 standard chooses to set the implicit bit to 0 instead of 1 when the minimum exponent is reached (0 when unbiased). The floating-point number is no longer a normal but rather a subnormal (or denormal) number. Figure 2.7 shows the subnormal numbers in red on the real axis next the the normal numbers (in black).

To illustrate the natural order on floating-point values, Table 2.1 shows the decoding of all the positive values of a  $(wd_e, wd_f) = (3,2)$  format.

Figure 2.6: Illustration of floating-point density on the real axis  $((wd_e, wd_f) = (3, 2))$

Figure 2.7: Illustration of floating-point density on the real axis  $((wd_e, wd_f) = (3, 2))$ . Normal numbers are represented in black and subnormals are represented in red. Note that there are two zeroes: +0 and -0.

Standard sizes and values The IEEE-754 standard [1] defines sizes, special values, arithmetic behaviors and rounding modes for floating-points. The three floating-point formats introduced with this standard are:

- binary32 ( $wd_e = 8, wd_f = 23$ ), formerly called single precision, which corresponds to the float type in C,

- binary64 ( $wd_e = 11, wd_f = 52$ ), formerly called double precision, which corresponds to the double type in C,

- binary128 ( $wd_e = 15, wd_f = 112$ ), formerly called quadruple precision.

Some special values are also encoded by specific combinations of the sign, exponent and significand: plus and minus infinity, positive and negative zeros and not a number (NaN). Hence each operator has special cases to handle special values arithmetic. For example, the addition of  $x + \infty$  is defined as  $\infty$  if x is finite, while  $\infty - \infty$  returns -NaN.

**Rounding** The IEEE-754 standard defines 5 rounding modes. Two rules round to the nearest value while the others rounds towards a direction. The rules that round to the nearest differ in the way they handle ties, i.e. values exactly between the two nearest floating point numbers. One is round to nearest, ties to even while the other is round to nearest, ties away from  $\theta$ . The rules that perform a directed rounding are towards  $\theta$ , towards  $\theta$  and towards  $\theta$ . The default behavior is to use the round to nearest, ties to even rounding. For a floating-point operator to be IEEE-754 compliant, it must implement these rounding modes. The output of a IEEE-754 compliant operator can then be written as:

$$fp_{op}(a,b) = rnd(op(a,b))$$

where  $fp_{op}(a, b)$  is the output of the floating-point operator, op(a, b) is the mathematical operation and rnd(...) is the rounding rule.

| Exp. | Signif. | Value                         | Comment                     |

|------|---------|-------------------------------|-----------------------------|

| 000  | 00      | 0                             | (positive) zero             |

| 000  | 01      | $0.01 \cdot 2^{1-3} = 0.0625$ | smallest positive subnormal |

| 000  | 10      | $0.10 \cdot 2^{1-3} = 0.125$  |                             |

| 000  | 11      | $0.11 \cdot 2^{1-3} = 0.1875$ | largest subnormal           |

| 001  | 00      | $1.00 \cdot 2^{1-3} = 0.25$   | smallest normal             |

| 001  | 01      | $1.01 \cdot 2^{1-3} = 0.3125$ |                             |

| 001  | 10      | $1.10 \cdot 2^{1-3} = 0.375$  |                             |

| 001  | 11      | $1.11 \cdot 2^{1-3} = 0.4375$ |                             |

| 010  | 00      | $1.00 \cdot 2^{2-3} = 0.5$    |                             |

| 010  | 01      | $1.01 \cdot 2^{2-3} = 0.625$  |                             |

| 010  | 10      | $1.10 \cdot 2^{2-3} = 0.75$   |                             |

| 010  | 11      | $1.11 \cdot 2^{2-3} = 0.875$  |                             |

| 011  | 00      | $1.00 \cdot 2^{3-3} = 1$      |                             |

| 011  | 01      | $1.01 \cdot 2^{3-3} = 1.25$   |                             |

| 011  | 10      | $1.10 \cdot 2^{3-3} = 1.5$    |                             |

| 011  | 11      | $1.11 \cdot 2^{3-3} = 1.75$   |                             |

| 100  | 00      | $1.00 \cdot 2^{4-3} = 2$      |                             |

| 100  | 01      | $1.01 \cdot 2^{4-3} = 2.5$    |                             |

| 100  | 10      | $1.10 \cdot 2^{4-3} = 3$      |                             |

| 100  | 11      | $1.11 \cdot 2^{4-3} = 3.5$    |                             |

| 101  | 00      | $1.00 \cdot 2^{5-3} = 4$      |                             |

| 101  | 01      | $1.01 \cdot 2^{5-3} = 5$      |                             |

| 101  | 10      | $1.10 \cdot 2^{5-3} = 6$      |                             |

| 101  | 11      | $1.11 \cdot 2^{5-3} = 7$      |                             |

| 110  | 00      | $1.00 \cdot 2^{6-3} = 8$      |                             |

| 110  | 01      | $1.01 \cdot 2^{6-3} = 10$     |                             |

| 110  | 10      | $1.10 \cdot 2^{6-3} = 12$     |                             |

| 110  | 11      | $1.11 \cdot 2^{6-3} = 14$     | largest normal              |

| 111  | 00      | $+\infty$                     |                             |

| 111  | 01      | NaN                           |                             |

| 111  | 10      | NaN                           | (with different payloads)   |

| 111  | 11      | NaN                           |                             |

Table 2.1: All positive values of a floating-point  $(wd_e, wd_f) = (3,2)$  format.

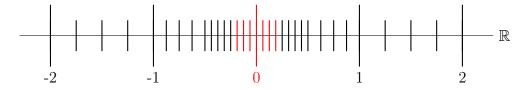

Reproducible results The rounding errors of floating-point operators implies that a sequence of operations cannot be reordered to ensure the reproducibility of the results. An illustrative example is to consider a custom floating-point format where  $wd_f = 3$  and the operation  $fp_-(fp_+(a,b),c)$  where  $a=1.101_b \cdot 2^3$ ,  $b=1.010_b \cdot 2^0$  and  $c=1.100_b \cdot 2^3$ . This sequence of operations cannot be replaced by  $fp_+(fp_-(a,c),b)$  even if the associated mathematical sequence of operations a+b-c is equivalent to a-c+b. Figure 2.8 illustrates this example.

The sum of a and b (top) is rounded so that the result fits in  $wd_f$  bits of significand.

Figure 2.8: Illustration of non-associativity of the floating-point addition ( $wd_f = 3$ ).

Hence, one bit of b is lost in the process. However, performing a different sequence of operations (bottom) can modify the rounding error.

Implementation Combining all these properties, any implementation of an IEEE-754 floating-point operation requires to: decode the inputs; detect special values; compute the arithmetic function; normalize the computed result (shift significand to have its most significant bit at 1 while modifying the exponent accordingly); round the result. These steps require either time for software implementations ([24]) or both time and resources for hardware implementations.

The subtleties of the encoding are completely hidden to the programmer and rely on the underlying more complex hardware or software implementation. Therefore it makes it easy to use.

### 2.2 Field Programmable Gate Arrays (FPGAs)

A field programmable gate array (FPGA) is a hardware component that can be configured by software in such a way that it allows to simulate complex logic functions. This Section aims at giving the reader enough information to understand the basics of FPGAs architecture, programming model and the corresponding synthesis reports. It does not provide a complete understanding of modern FPGAs and their complexity.

#### 2.2.1 FPGAs architecture

FPGAs are based on small memories (lookup tables) connected together through an interconnect network. Each vendor builds upon this concept with its own hardware structure/organization. However, the general programming model and functionalities are similar. The FPGAs vendors considered in this thesis are Xilinx and Intel (formerly Altera).

Before detailing FPGAs' architecture, it is important to differentiate two moments in their life cycle:

- configuration time: the FPGA is configured to simulate a specific function

- execution time: data is processed by the simulated function and produces the output

#### Configurable logic functions using LookUp Tables (LUTs)

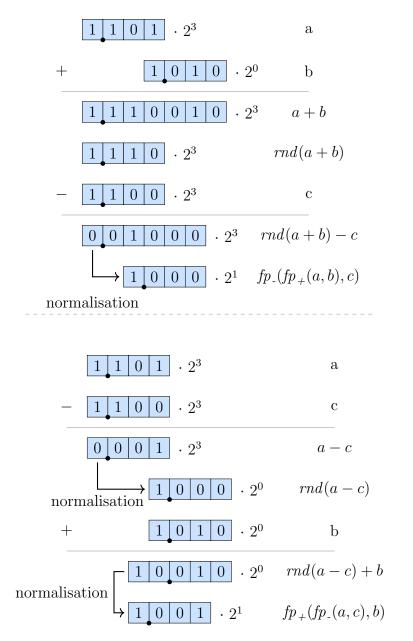

A LUT is a memory, holding a truth table, that can be configured by software. Given  $\alpha$  input bits, a LUT $\alpha$  will return a single bit from its  $2^{\alpha}$  entries. Hence, it is capable of simulating any boolean function on  $\alpha$  bits.

A simple example of a LUT is given in Figure 2.9 (left). It takes 2 bits of input (LUT2) and outputs a single bit. These 2 bits are used to select one of the configured bit (illustrated by  $\square$ ) using a multiplexer. Hence, changing the configuration bits changes the boolean function simulated.

Figure 2.9: Example of a LUT2 (left) and its integration in a simple slice with a register (right).

The configuration bits are set prior to the execution and cannot be modified during the execution. However, during the execution, the data bits are used as inputs to compute the output.

Modern FPGAs use between 4-input and 6-input LUTs. The combination of such LUTs is the basis of FPGA's architecture.

#### Slice and Adaptive Logic Modules (ALMs)

A Slice or ALM (for Xilinx and Intel FPGAs respectively) is a combination of one or more LUTs with registers. The latter are memories that can store data bits synchronously during the execution and are represented by  $\square$  in Figures. In the case of a Slice/ALM, they are used to store the output of the LUT, as illustrated by Figure 2.9 (right). An extra configuration bit  $(c_m)$  selects between the LUT output and the previously stored value. From now on, we will refer as a slice for naming both Slices and ALMs.

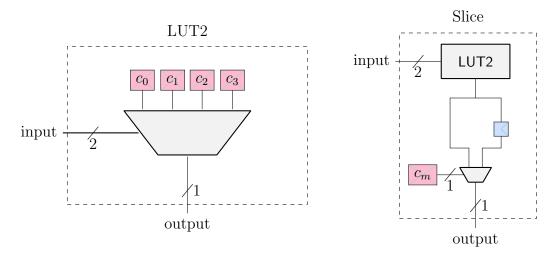

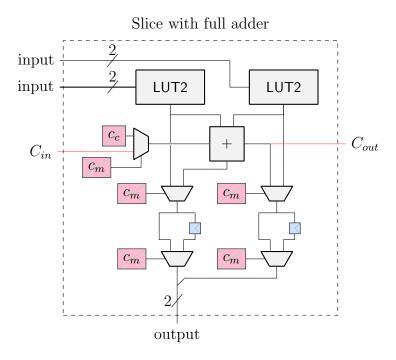

Modern slices will combine multiple LUTs and registers as well as one or more full adders. An example of such a slice is depicted in Figure 2.10. This slice takes two 2-bit input signals that address two LUT2. Two configuration bits control which signals to forward between the direct output of the LUTs and their sum. Finally, two more configuration bits select the two output bits between the delayed result and the immediate result.

A new configuration bit is added to the slice  $(c_c)$  to fill the carry input port of the full adder. However, a special input of the slice  $(C_{in})$  can be used instead of  $c_c$ . Therefore, another configuration bit is used to perform that selection. This example is still a simplistic illustration of modern FPGAs slices.

This slice example has 6 configuration bits (plus 4 in each LUT2); and 4 data bits.

Figure 2.10: Example of a slice with two LUT2, two registers and a full adder.

#### Interconnect

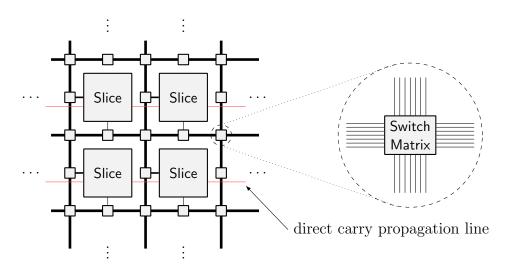

An interconnect is configured to route slices inputs and outputs, allowing to simulate more complex logic functions. Such an interaction between slices is depicted in Figure 2.11.

The interconnect is a set of wires connected to the slices in a grid manner. At each crossing point, a switch matrix decides where to route each wire. Similarly to the slice configuration bits, the switch matrix configuration is performed by software before the start of the computation. There has been a lot of research on switch matrices [25, 26, 27]. The switch matrix details are currently well hidden behind FPGA synthesis tools.

Figure 2.11: Example of slices connected through an interconnect.

A special type of connection creates a direct link between adjacent slices without going through the interconnect. This allows to perform faster operations as it removes the latency of the routing. It is depicted by the red connections from Figure 2.11. This mechanism is particularly used for carry propagation when performing additions, giving it its name: *carry chain*. However it can also be used for other functions such as wide AND or wide OR.

#### Block RAM (BRAM)

The registers inside a slice can be linked to build a larger memory. However, such a sparse distribution of data may imply longer routing delays. To cope with this, FPGAs are equipped with small block RAMs (BRAMs) connected to the interconnect. These store data in a much more dense fashion, hence allowing LUTs to be used for other purposes.

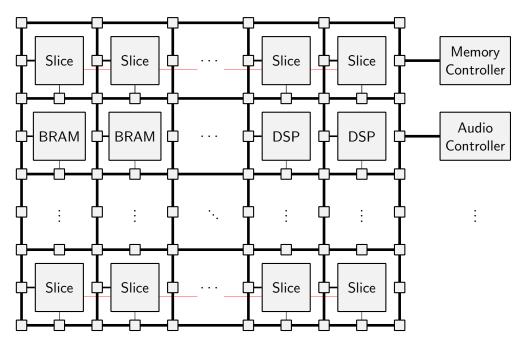

#### Digital Signal Processing (DSP) blocks

FPGAs contain dedicated hardware blocks (DSPs) for accelerating commonly used functions. For example, integer multipliers and multiply-accumulate units are available as DPS blocks on both Intel and Xilinx FPGAs. Most recent Intel FPGAs even embed DSPs with integrated single-precision floating-point multipliers [28].

Figure 2.12 illustrates a combination of the above mentioned components to make a simple FPGA. The interconnect is also connected to different controllers which allow communication with the outside world.

Figure 2.12: Example of a populated FPGA with slices, DSPs and BRAMs.

The complex task of configuring each slice and the interconnect is well hidden behind synthesis tools. Indeed, these are able to generate a bitstream (that is composed of all the configuration bits), that program the FPGA, from an input program. The methodology used by synthesis tools for generating such a configuration file is not described here. However, it is useful for the reader to know that the final step before the bitstream generation is called *place-and-route*. This step is very computationally intensive (it may last days for large FPGAs).

#### 2.2.2 FPGAs programming model

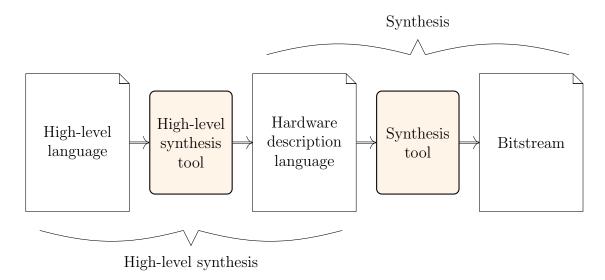

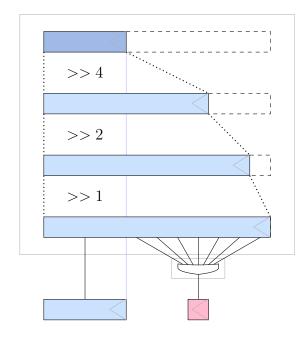

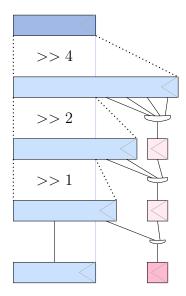

Figure 2.13 illustrates the typical flows for programming FPGAs. The synthesis (right) is the process of generating a bitstream from a low-level description of a circuit, using a hardware description language (HDL). Hand writing a component using a HDL is today the standard for creating optimized designs. Another approach is to generate a HDL program from a higher-level language. This is the process of high-level synthesis (Figure 2.13, left). Both approaches are described in the next sections.

#### Hardware Description Languages (HDLs)

The usual way of describing a circuit is to use a HDL such as VHDL or Verilog. Such languages do not follow a usual sequential semantic. Instead, they describe components connected together through wires and buses with a partially parallel semantic.

Writing a component using a HDL is considered quite tedious. First, it departs from traditional programming. Second, debugging tools give the user a view of the state of the component at given a time. This requires the programmer to inspect the state of wires, and follow where each wire is connected. In contrast, when using a high-level language debugger, the user follows a sequential program step by step where only one change occurs at the time.

Figure 2.13: Design flow for programming FPGAs.

In the entire architecture, the longest distance between two registers is called the critical path (CP). The maximum frequency at which a design can operate is therefore computed from the length of the CP. Indeed, the time between two ticks should be long enough for a every signals to exit their registers and to be stored in the next. Hence, the shorter the CP is, the higher the frequency can be. The commonly used method to increase the frequency is to cut the CP in parts by inserting registers. This delays the output of the design by as many cycles as there are registers on the CP. The frequency is then increased at the cost of a greater latency and a higher register usage. This process, called pipelining, makes debugging even more difficult as an error can now also be due to wrongly timed events.

In order to ease the debugging of HDL designs, subsets of higher-level languages can be used as domain specific languages (DSLs) to generate faithful HDL. This allows to describe and simulate a component using the higher-level language environment. Examples of open-source DSLs are MyHDL [29], for using the Python environment or Chisel [30], for the Scala environment.

A component can be distributed as an intellectual property (IP). Thus, the IP is characterized by its maximum frequency (with an impact on its latency and register cost). When integrating it into an existing design, the IP may:

- hold the CP as its maximum frequency is not high enough

- delay the result and use too much registers as the maximum frequency achievable is too high

For optimized designs, it is therefore better to write a specific IP for the clock frequency targeted by the current design. Some techniques allow for automatic retiming of circuits [31, 32, 33]. However, in our case, when designing custom arithmetic operators, not only the timing of the circuit must be customizable but also the sizes of the datapath.

HDL generators Most arithmetic operators can be customized in input and output sizes. Operators can be described as parametrized HLS, but the complexity of the code

scales poorly with the number of parameters. Therefore, most arithmetic IPs comes from HDL generators rather than from standard IP collections.

Commercial tools such as Matlab HDL coder allow users to generate portable Verilog or VHDL from Matlab functions and Simulink models. For targeting specific FPGAs, vendors provide their own tools such as Xilinx system generator or Intel DSP Builder.

One of the most notorious open-source HDL generator for arithmetic cores is FloPoCo [34]. It generates custom arithmetic IPs that can achieve user specified frequency. The main focus of FloPoCo is to generate circuits that compute functions at a user specified accuracy without computing useless bits. The IP's datapath is tailored to the application, and the pipeline depth to the required performance.

In most cases, the IP requires control signals, it will have to be connected to a finite state machine (FSM). This FSM also has to be described using a HDL. However, multiple tools allow for HDL generation from a graphical design of the FSM.

#### High-Level Synthesis (HLS)

Generating IPs and connecting them together increases productivity compared to writing everything using a HDL by hand. However, in most cases, development and debugging time is still slower than high-level programming. HLS tools [35], which is the process of transforming a high-level description to an HDL (Figure 2.13, left), tries to fill that gap in productivity. The most popular commercial tools are Xilinx Vivado HLS, Intel HLS, CatapultC where the most popular academic tools are LegUp [36], Bambu [37], GAUT [38], AUGH [39], among others [35].

Programmers are offered some high-level input languages such as C/C++, SystemC, C#, OpenCL to write a program. Compared to using a HDL, the component is described by its behavior instead of its implementation. The users benefit from these high-level languages compilers for fast simulation and debugging tools for more traditional debugging. However, only a subset of such languages can be used. For example, dynamic memory allocation, access to standard input/output streams generally can't be synthesized.

HLS tools automatically insert registers in the designs to reach the clock target, and generate the corresponding IP. Connection to specific FPGAs pins are also automated by such tools, as the target FPGA is known at compile time. The FSM required for the design is then included in the IP as derived from the program control flow. Therefore it makes it easier for one to describe complex circuits using standard high-level languages constructions.

**Specific coding style** HLS tools require a specific coding style. In fact, two functionally equivalent programs can result in designs with very different resource usage/latency. However, this specific coding style is described in some best practice guides [40, 41, 42].

A first example illustrates how to save resources on a simple code example (Figure 2.14, left). In that code snippet, the component takes four integer inputs and a selection boolean. Depending on that boolean, the component will output the product result of either a and b, or c and d. Synthesis results of this component reveal that two multiplier are generated and one multiplexer (Vivado 2018.3) as illustrated by Figure 2.14 (right). This result is suboptimal as the multipliers require more resource and a longer critical path than the multiplexers. A simple fix to that code is given in Figure 2.15 where selecting

Figure 2.14: Suboptimal resource utilisation of a HLS component written in C/C++.

Figure 2.15: Corrected C/C++ component from Figure 2.14.

the operands first and then performing the multiplication (left) produces the expected hardware (right).

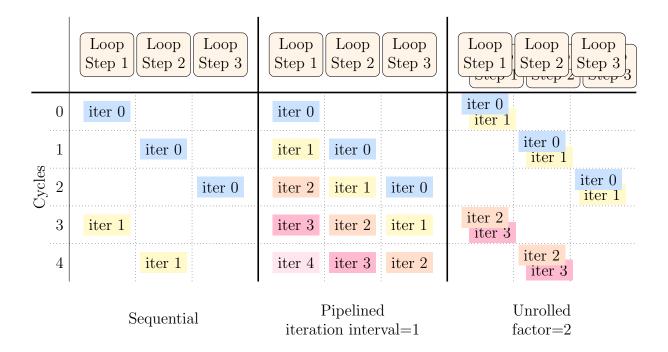

A second example illustrates how to improve the latency of a computation loop. The code snippet provided in Figure 2.16 computes the set of products from arrays a and b, storing the results in array c. If we consider that one iteration of the loop requires 3 steps/cycle at a given frequency, the resulting scheduling of such a component will be the one from Figure 2.17 (left). Indeed, iteration 0 will occupy the resources from the first step of the loop at cycle 0, then it will move to the resource of loop step 2 at cycle 1 and

```

void component(int a[SIZE], int b[SIZE], int c[SIZE]){

for(int i=0; i<SIZE; i++){

c[i] = a[i]*b[i];

}

}</pre>

```

Figure 2.16: Example of a HLS component performing a computation loop written in C/C++.

Figure 2.17: Different scheduling for the computation loop from Figure 2.16.

so on. The iteration 1 will only start when the computation of iteration 0 is over. In our case, the loop instructions are independent and this schedule can be improved (both its throughput and resource activity) by using another scheduling policy.

HLS compilers can be directed towards a specific resource allocation, loop schedule or interface by adding pragmas. These compiler directives will only be used for generating HDL and won't affect simulation. In the code example of Figure 2.16, one can specify the HLS compiler to pipeline the loop. Multiple loop iterations will interleave and share the hardware resources (as illustrated in Figure 2.17, middle). In this case, the loop iterations

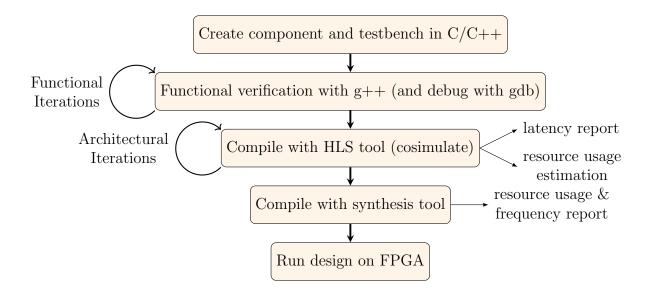

Figure 2.18: HLS design flow example using C/C++.

are all independent, hence a new iteration can be started each cycle. This start distance is called *iteration interval (II)*. Alternatively, one can choose to duplicate the resources in order to execute several instructions in parallel (shown in Figure 2.17, right); in that case unrolling by a factor 2.

The complete HLS design flow is described in Figure 2.18. The user creates a component using the high-level language and debugs it using high-level debuggers. Once the component has the expected behavior, it can be compiled by the HLS compiler. The latter will provide resource estimations and latency reports, according to which the programmer can iterate to improve his design. The generated HDL can then be verified using cosimulation before finally using synthesis tools.

#### **IPs** integration

Once an IP is ready, whether it has been written by hand, generated using HDL generators or through HLS, it needs to be connected to the outside world. Its inputs and outputs must be connected to the correct FPGA pins. However, each specific chip has different functionalities and connections. Traditional flows then require deep FPGA knowledge and hand-writing HDLs.

Recent development environment such as Intel FPGA SDK for OpenCL or Xilinx SDAccel provide a complete abstraction of the FPGA connections. Indeed, a programmer can program a FPGA only by writing in a high-level language, the tools will then manage pin connections and data-transfers.

## Chapter 3

# Bridging high-level synthesis and application specific arithmetic

This Chapter results from a joint collaboration with Steven Derrien and Victor Lezaud.

High-level synthesis tools rely heavily on compiler optimizations [43, 44, 45]. As most of these optimizations were designed for standard CPUs, it is relevant to question if they make sense in an FPGA context. It is also relevant to attempt to identify new optimizations that were not investigated previously because they make sense only in this FPGA context. This is the main objective of this Chapter, with a focus on arithmetic-related optimizations.

Consider for example the integer multiplication by a constant. Figure 3.1 implements a simple integer multiplication by 7. Figure 3.2 shows the assembly code of Figure 3.1, when compiled with gcc 7.4.0 without any particular optimization flag. We can see that the multiplication by 7 has been transformed by the compiler into a *shift and add* algorithm:  $7x = 8x - x = x \cdot 2^3 - x$  where the multiplication by  $2^3$  is a simple shift left by 3 bits (this multiplication by 8 may also be implemented by the lea instruction in a slightly less obvious way, and this is what happens, both on GCC or Clang/LLVM, when using -O2 optimization).

As a consequence, the architecture produced by HLS tools based on GCC or Clang/L-LVM will implement this algorithm. This optimization makes even more sense in HLS, since the constant shifts reduce to wires and therefore cost nothing. Indeed, the synthesis of Figure 3.1 in Vivado HLS reports 32 LUTs, the cost of one addition. Experiments with Vivado HLS (based on Clang/LLVM) and Intel HLS (based on GCC) show that for all the constant multiplications that can be implemented as an addition, these tools instantiate an adder instead of a multiplier.

Figure 3.1: C code.

Figure 3.2: Objdump of Figure 3.1 when compiled with gcc.

```

int mul2228241 ( int x ){

return x*2228241;

}

(...)

(...)

10: ... imul $0x220011, %edi, %eax

16: ... retq

(...)

```

Figure 3.3: C code.

Figure 3.4: Objdump of Figure 3.3 compiled with Clang/LLVM -O2.

```

int mul2228241 ( int x ){

int t = (x<<4) + x;

return (t<<17) + t;

}</pre>

```

Figure 3.5: C code using a shift-and-add algorithm.

Now consider the multiplication by another constant in Figure 3.3. On this example, we observe that Clang/LLVM x86 backend keeps the operation as a multiplication.

Indeed, the synthesis of this operator by Vivado HLS on a Kintex reports 2 LUTs and 2 DSPs, which are the resources needed to implement a 32-bit multiplier.

However, although the constant looks more complex, it barely is: the multiplication by 2228241 can be implemented in two additions only if one remarks that  $2228241 = 17 \cdot 2^{17} + 17$ : first compute  $t = 17x = x \cdot 2^4 + x$  (one addition), then compute  $2228241x = t \cdot 2^{17} + t$  (another addition). Still, neither Clang/LLVM nor GCC use a shift-and-add in this case. The rationale could be the following: the cost of one addition will always be lower than or equal to the cost of a multiplication, whatever the processor, so replacing one multiplication with one addition is always a win. Conversely, it may happen on some (if not most) processors that the cost of two additions and two shifts is higher than the cost of one multiplication.

Is this true in an HLS context? The best architecture for this multiplication, achieved by the C program of Figure 3.5, consists of two adders: one that computes the 32 lower bits of  $t = 17x = x \cdot 2^4 + x$  (and should cost only 28 LUTs, since the lower 4 bits are those of x); one that computes the 32 lower bits of  $t \cdot 2^{17} + t$ , and should cost 32-17=15 LUTs, for the same reason (the 17 lower bits are those of t). The total cost should be 43 LUTs.

For this program, Vivado HLS indeed reports 46 LUTs, very close to the predicted 43 (and not much higher than the cost of the multiplication by 7).

In summary, what we observe here is that the arithmetic optimization has been completely delegated to underlying compiler's x86 backends, and we have a case here for enabling further optimizations. Indeed, hardware constant multiplication has been the subject of much research [46, 47, 48, 49, 50, 51], some of which is specific to FPGAs [12, 52, 53, 14].

The broader objective of the present work is to list similar opportunities of hardware-specific arithmetic optimizations that are currently unexploited, and demonstrate their effectiveness. We classify these optimizations in two broad classes.

In Section 3.1, we discuss optimization opportunities that strictly respect the semantic of the original program. The previous multiplications by constants examples belong to this class, we also discuss divisions by constants, and we add in this Section a few floating-point

optimizations that make sense only in a hardware context. This Section should be perfectly uncontroversial: all optimizations in this class should be available in an HLS flow as soon as they improve some metric of performance. The only reason it is not yet the case is that the field of HLS is still relatively young.

The second class, discussed in Section 3.2 is more controversial and forward-looking. It includes optimizations that relax (and we argue, only for the better) the constraint of preserving the program semantics. In this Section, we assume that the programmer who used floating-point data in their programs intended to compute with real numbers, and we consider optimizations that lead to cheaper and faster, but also more accurate hardware. This approach is demonstrated in depth on examples involving floating-point summations and sums-of-products.

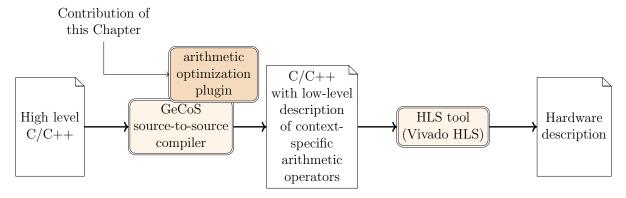

In each case, we use a compilation flow illustrated by Figure 3.6, that involves one or several source-to-source transformations using the GeCoS framework [54] to improve the generated designs. Source-to-source compilers are very convenient in an HLS context, since they can be used as optimization front-ends on top of closed-source commercial tools.

Finally, we discuss in Section 3.3 what we believe HLS tools should evolve to.

Figure 3.6: The proposed compilation flow.

# 3.1 Optimization examples that do not change the program semantic

The arithmetic optimizations that fit in this Section go well beyond the constant multiplications. In particular, there are opportunities of floating-point optimizations in FPGAs that are more subtle than operator specialization.

#### 3.1.1 Floating-point corner-case optimization

Computing systems follow the IEEE-754 standard on floating-point arithmetic, which was introduced to normalize computations across different CPUs. Based on this standard, the C standard prevents compilers from performing some floating-point optimizations. Here are some examples that can be found in the C11 standard [55]:

• x/x and 1.0 are not equivalent if x can be zero, infinite, or NaN (in which case the value of x/x is NaN).

- x y and -(y x) are not equivalent because 1.0 1.0 is +0 but -(1.0 1.0) is -0 (in the default rounding direction).

- x x and 0 are not equivalent if x is a NaN or infinite.

- $0 \times x$  and 0 are not equivalent if x is a NaN, infinite, or -0.

- x + 0 and x are not equivalent if x is -0, because (-0) + (+0), in the default rounding mode (to the nearest), yields +0, not -0.

- 0-x and -x are not equivalent if x is +0, because -(+0) yields -0, but 0-(+0) yields +0.

Of course, programmers usually don't write x/x or x+0 in their code. However, other optimization steps, such as code hoisting, or procedure specialization and cloning, may lead to such situations: their optimization is therefore relevant in the context of a global optimizing compiler [43].

Let us consider the first example (the others are similar): A compiler is not allowed to replace x/x with 1.0 unless it is able to prove that x will never be zero, infinity or NaN. This is true for HLS as well as for standard compilers. However, it could replace x/x with something like (is\_zero(x)||is\_infty(x)||is\_nan(x))?NaN:1.0;. This is, to our knowledge, not implemented. The reason is again probably that in software, the test on x becomes more expensive than the division.

However, if implemented in hardware, this test is quite cheap: it consists in detecting if the exponent bits are all zeroes (which capture the 0 case) or all ones (which captures both infinity and NaN cases). The exponent is only 8 bits for single precision and 11 bits for double-precision.

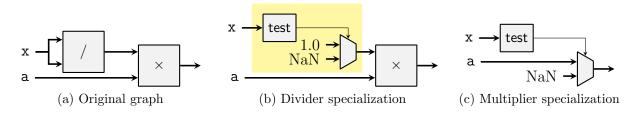

In an FPGA context, it therefore makes perfect sense to replace x/x (Figure 3.7a) with an extremely specialized divider depicted on Figure 3.7b. Furthermore, the two possible values are interesting to propagate further (1.0 because it is absorbed by multiplication, NaN because it is extremely contagious). Therefore, this optimization step enables further ones, where the multiplexer will be pushed down the computation, as illustrated by Figure 3.7c.

Figure 3.7: Optimization opportunities for floating-point x/x \* a.

Note that this figure replaces 1.0\*x by x: this is a valid floating-point optimization, in the sense that it is valid even if x is a signed zero, an infinity or a NaN.

Occurrences of x - x,  $0 \times x$ , x + 0, 0 - x can similarly be replaced with a multiplexer and very little logic, and may similarly enable further optimizations.

Since these arithmetic optimizations are expected to be triggered by optimizations (procedure specialization) and trigger further optimizations (conditional constant propagation), they need to be implemented and evaluated within an optimizing compiler.

```

(...)

0: ... movslq %edi,%rax

3: ... imul $0xfffffffff92492493,%rax,%rcx

a: ... shr $0x20,%rcx

e: ... add %ecx,%eax

10: ... mov %eax,%ecx

12: ... shr $0x1f,%ecx

15: ... sar $0x2,%eax

18: ... add %ecx,%eax

18: ... add %ecx,%eax

```

Figure 3.9: Objdump of Figure 3.8 when compiled with Clang -O2.

The source-to-source flow depicted on Figure 3.6 is ill-suited to studying such cascaded optimizations. Furthermore, the multiple conditional constant propagation that transforms Figure 3.7b into Figure 3.7c is probably not implemented yet, since it doesn't make much sense in software. This evaluation is therefore left out of the scope of the present work.

In the following, we focus on FPGA-specific semantic-preserving optimizations which will not trigger further optimizations.

#### 3.1.2 Integer multiplication by a constant

Multiplication by a constant has already been mentioned in introduction. We just refer to the rich existing literature on the subject [12, 46, 52, 47, 48, 49, 50, 53, 51, 14]. These are mostly academic works, but backend tools already embed some of it, so this optimization could be the first to arrive. An issue is that its relevance, in the big picture of a complete application, is not trivial: Replacing DSP resources with logic resources is an optimization only in a design that is more DSP-intensive than logic-intensive. Besides, as soon as a logic-based constant multiplier requires more than a handful of additions, it may entail more pressure on the routing resources as well. Discussing this trade-off in detail in the context of an application is out of scope of the present work.

#### 3.1.3 Integer division by small constants

Integer division by a constant adds one more layer of optimization opportunities: In some cases, as illustrated by Figure 3.8 and Figure 3.9, a compiler is able to transform this division into a multiplication by a (suitably rounded) reciprocal. This then triggers the previous optimization of a constant multiplier. Actually, one may observe that on this example that the constant 1/7 has the periodic pattern 1001001001001001001001001001001 (hidden in the hexadecimal pattern  $924_{16}$  in Figure 3.9). This enables a specific optimization of the shift-and-add constant multiplication algorithm [56].

Table 3.1 shows synthesis results on the two FPGA mainstream HLS flows. Intel HLS reports usage of MLABs which are the aggregation of several ALMs to emulate a larger LUT. The timing constraint was set to 100 MHz, however this factor is not important here as it does not change the structure of the generated operators. The goal here is to

Table 3.1: Synthesis results of 32-bit integer dividers with Vivado HLS for Kintex 7 (a), and Intel HLS for Arria 10 (b).

|                | (a)  | Vivado H | ILS  |      |       |     | (b) Intel H | HLS  |       |

|----------------|------|----------|------|------|-------|-----|-------------|------|-------|

| Value          | LUTs | Regs.    | DSPs | SRLs | ALMs  | FFs | RAMs        | DSPs | MLABs |

| $\overline{x}$ | 235  | 295      | 0    | 1    | 625   | 638 | 4           | 10   | 9     |

| 1              | 0    | 0        | 0    | 0    | 2     | 3   | 0           | 0    | 0     |

| 2              | 94   | 0        | 0    | 0    | 18    | 3   | 0           | 0    | 0     |

| 3              | 142  | 113      | 4    | 9    | 121   | 62  | 0           | 0    | 2     |

| 4              | 94   | 0        | 0    | 0    | 18    | 3   | 0           | 0    | 0     |

| 5              | 142  | 113      | 4    | 9    | 119.5 | 74  | 0           | 0    | 2     |

| 6              | 163  | 103      | 4    | 9    | 109.5 | 59  | 0           | 0    | 2     |

| 7              | 142  | 111      | 4    | 9    | 122   | 75  | 0           | 0    | 2     |

| 8              | 92   | 0        | 0    | 0    | 18    | 3   | 0           | 0    | 0     |

| 9              | 142  | 114      | 4    | 9    | 151.5 | 63  | 0           | 0    | 2     |

observe the optimizations performed (or not) by the tools. Here is what we can infer from this table:

- The generic divider (Value=x) is based on Xilinx on a shift-and-add algorithm, while on Intel a polynomial approach is used [57] that consumes multiplier and DSP resources.

- Both tools correctly optimize the division by a power of two, converting it into a shift.

- Division by non-power of two integers is implemented by a multiplication by the inverse on Xilinx (it consumes DSP blocks). On Intel, this multiplication is further optimized as a logic-only operation.

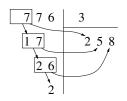

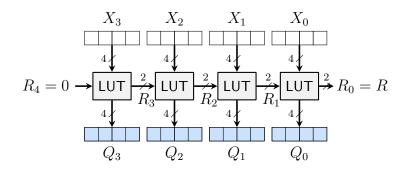

For the division of an integer by a very small constant, the best alternative is the algorithm described in [13]. It is based on the decimal paper-and-pencil algorithm illustrated in Figure 3.10. Figure 3.11 describes an unrolled architecture for a binary-friendly variant of this algorithm. There, the input X is written in hexadecimal (each 4-bit word  $X_i$  is an hexadecimal digit). The quotient bits come out in hexadecimal. The remainder of the division by 3 is always between 0 and 2, therefore fits on 2 bits. Each LUT on the Figure therefore stores the quotient  $Q_i$  (between  $0_h$  and  $F_h$ ) and the remainder  $F_i$  (between  $F_i$  and  $F_i$ ) of the division by 3 of a number  $F_i$  and  $F_i$  are a recent LUT-based FPGA, each 6-input, 6-output LUT of Figure 3.11 consumes exactly 6 FPGA LUTs: This architecture is very well suited to FPGAs.

Table 3.2 compares the performance of the division of a 64-bit integer by a small constant, when left to Vivado HLS (left part), and when first replaced by an HLS description of the architecture of Figure 3.11 by a source-to-source transformation (right part of the table). The results were obtained using Vivado HLS 2016.3 targeting a Kintex 7 (part xc7k160tfbg484-1) at 330MHz. For constants smaller than 9, all the metrics (logic resources, DSP, latency and frequency) are improved by this transformation. As the constant grows larger, the latency degrades and the resource consumption increases:

We first compute the Euclidean division of 7 by 3. This gives the first digit of the quotient, here 2, and the remainder is 1. In other words  $7 = 3 \times 2 + 1$ . The second step divides 77 by 3 by first rewriting 77 =  $70 + 7 = 3 \times 20 + 10 + 7$ : dividing 17 by 3 gives  $17 = 3 \times 5 + 2$ . The third steps rewrites 776 = 770 + 6 = 250 + 20 + 6 where  $26 = 3 \times 8 + 2$ , hence  $776 = 3 \times 258 + 2$ .

The only computation in each step is the Euclidean division by 3 of of a number between 0 and 29: it can be pre-computed for these 30 cases and stored in a LUT.

Figure 3.10: Illustrative example: division by 3 in decimal.

for the division by 9 we already have a worst latency and frequency than the default multiplication-based implementation, but still with much less resources.

Figure 3.11: Unrolled architecture for a LUT-based division by a constant with a 16-bit input and LUTs with 4 input bits.

Table 3.2: Synthesis results of 64-bit integer constant divisors using Vivado HLS for Kintex 7.

|       |      | (a) C | (b)  | [13] div             | vision in HLS |      |                         |

|-------|------|-------|------|----------------------|---------------|------|-------------------------|

| Value | LUTs | reg.  | DSPs | Cycles @ Freq        | LUTs          | reg. | Cycles @ Freq           |

| x     | 8831 | 8606  | 0    | 68@293MHz            | NA            | NA   | NA                      |

| 2     | 194  | 193   | 0    | 3@467MHz             | 0             | 0    | $1 @ 1488 \mathrm{MHz}$ |

| 3     | 931  | 966   | 16   | $23@373\mathrm{MHz}$ | 62            | 127  | 17 @ 403 MHz            |

| 4     | 191  | 190   | 0    | 3@444MHz             | 0             | 0    | $1 @ 1488 \mathrm{MHz}$ |

| 5     | 925  | 962   | 16   | 23@364MHz            | 107           | 152  | 23 @ 377 MHz            |

| 6     | 927  | 964   | 16   | $23@363\mathrm{MHz}$ | 72            | 156  | $17 @ 380 \mathrm{MHz}$ |

| 7     | 923  | 956   | 16   | $23@355\mathrm{MHz}$ | 107           | 152  | $23 @ 377 \mathrm{MHz}$ |

| 8     | 189  | 187   | 0    | 3@449MHz             | 0             | 0    | $1 @ 1488 \mathrm{MHz}$ |

| 9     | 929  | 961   | 16   | 23@356MHz            | 100           | 193  | 33 @ 351MHz             |

Table 3.3: Synthesis results of single-precision floating-point constant multipliers/dividers using Vivado HLS (Kintex 7) (a) and Intel HLS (Arria 10) (b) targeting 100 MHz.

|             |                  | (a) Vi | vado HLS | $\mathbf{S}$ |      |   |       |     | (b) Intel H | LS   |       |

|-------------|------------------|--------|----------|--------------|------|---|-------|-----|-------------|------|-------|

|             | Value            | LUTs   | Regs.    | DSPs         | SRLs | Ī | ALMs  | FFs | RAMs        | DSPs | MLABs |

|             | $\overline{x}$   | 86     | 99       | 3            | 0    |   | 43    | 36  | 0           | 1    | 2     |

|             | 1.0              | 0      | 0        | 0            | 0    |   | 2     | 3   | 0           | 0    | 0     |

| Mult        | 2.0              | 70     | 67       | 3            | 0    |   | 69.5  | 21  | 0           | 0    | 2     |

| $\boxtimes$ | 3.0              | 67     | 70       | 3            | 0    |   | 102   | 20  | 0           | 0    | 2     |

|             | 4.0              | 71     | 67       | 3            | 0    |   | 69    | 20  | 0           | 0    | 2     |

|             | 5.0              | 71     | 67       | 3            | 0    |   | 108   | 21  | 0           | 0    | 2     |

|             | $\boldsymbol{x}$ | 780    | 392      | 0            | 25   |   | 311.5 | 634 | 3           | 4    | 7     |

|             | 1.0              | 0      | 0        | 0            | 0    |   | 2     | 3   | 0           | 0    | 0     |

| Div         | 2.0              | 75     | 67       | 3            | 0    |   | 72    | 23  | 0           | 0    | 2     |

| О           | 3.0              | 740    | 250      | 0            | 25   |   | 331.5 | 500 | 3           | 4    | 9     |

|             | 4.0              | 75     | 67       | 3            | 0    |   | 71.5  | 22  | 0           | 0    | 2     |

|             | 5.0              | 739    | 250      | 0            | 25   |   | 322.5 | 504 | 3           | 4    | 9     |

Table 3.4: Synthesis results of floating-point constant divisors for single (a) and double (b) precision that implements [13] using Vivado HLS for Kintex 7.

|                |      | (a) float |                         |      | (b) double |                             |  |  |

|----------------|------|-----------|-------------------------|------|------------|-----------------------------|--|--|

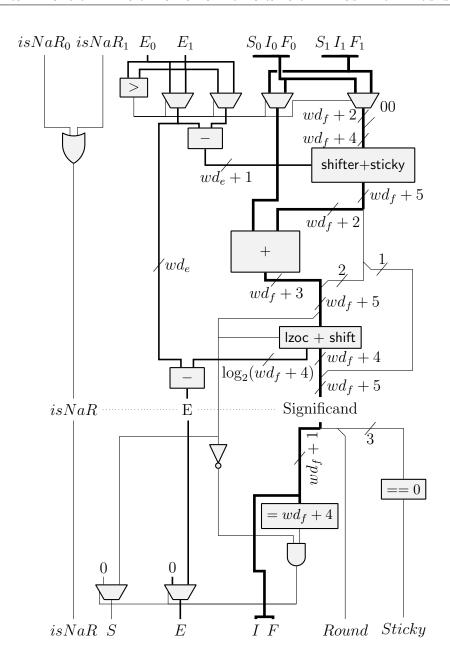

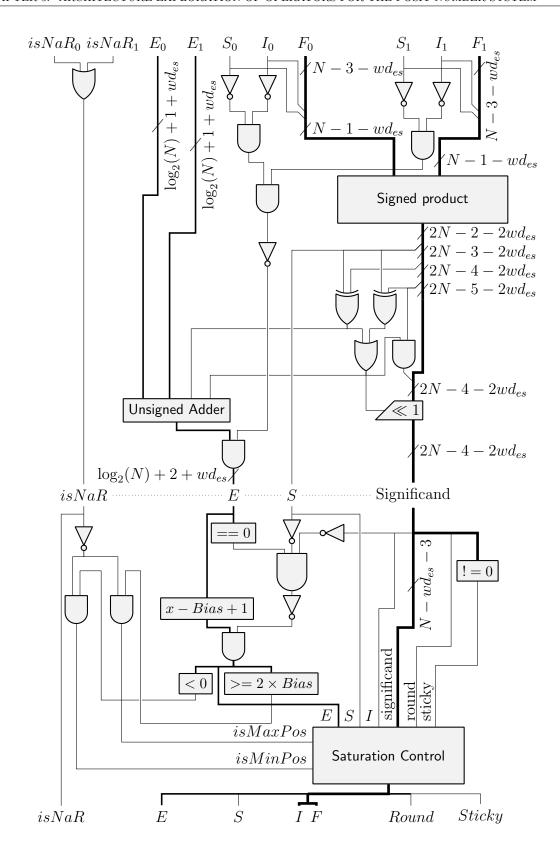

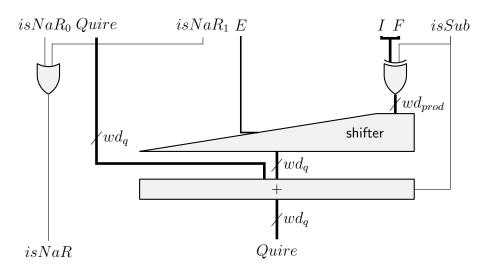

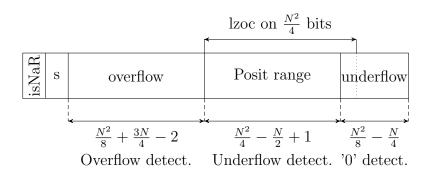

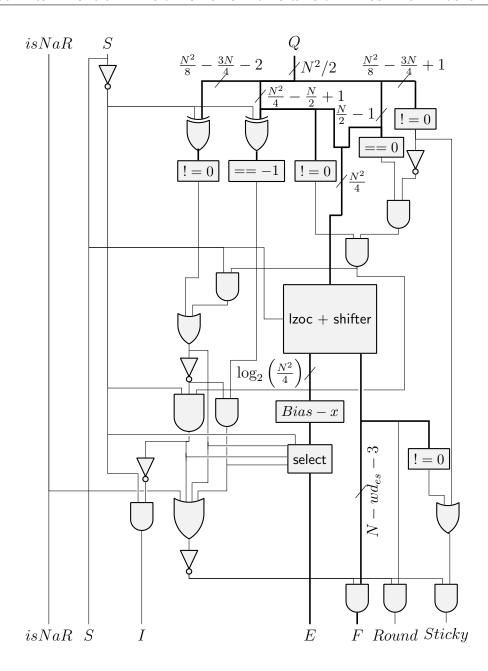

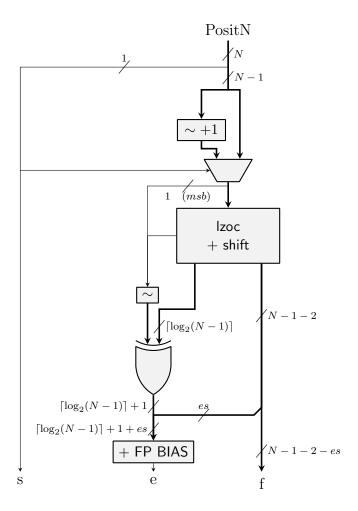

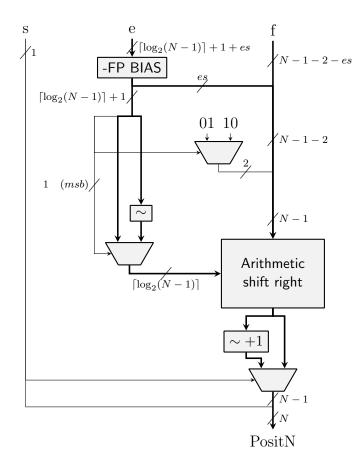

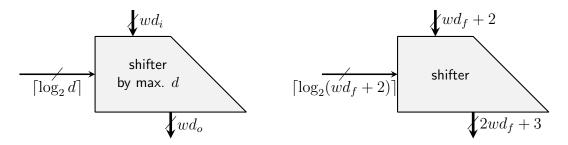

| Value          | LUTs | reg.      | Cycles @ Freq           | LUTs | reg.       | Cycles @ Freq               |  |  |