## Efficient Code Generation for Hardware Accelerators by Refining Partially Specified Implementations

Ulysse Beaugnon

## ▶ To cite this version:

Ulysse Beaugnon. Efficient Code Generation for Hardware Accelerators by Refining Partially Specified Implementations. Programming Languages [cs.PL]. Ecole Normale Superieure de Paris - ENS Paris, 2019. English. NNT: . tel-02385303v1

## HAL Id: tel-02385303 https://hal.science/tel-02385303v1

Submitted on 28 Nov 2019 (v1), last revised 26 Nov 2020 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PSL

Préparée à l'École Normale Supérieure

# Efficient Code Generation for Hardware Accelerators by Refining Partially Specified Implementation

### Soutenue par

## **Ulysse BEAUGNON**

Le 10 Juin 2019

Ecole doctorale n° 386

Sciences Mathématiques de Paris Centre

Spécialité

Informatique

## Composition du jury :

Francesco, ZAPPA NARDELLI

Directeur de Recherche, INRIA Président

Rastislav, BODIK

Professeur, University of Washington Rapporteur

Christophe, DUBACH

Professeur, University of Edinburgh Rapporteur

Anton, LOKHMOTOV

CEO, Dividiti Examinateur

Jacques, PIENAAR

Ingenieur, Google Examinateur

Albert, COHEN

Chercheur, Google & ENS Directeur

Marc, POUZET

Professeur, École Normale Supérieure Directeur

## Abstract

Software programmable hardware accelerators, such as Graphical Processing Units (GPUs), are specialized processors designed to perform specific tasks more efficiently than general purpose processors. They trade off generality against specialized data paths and massive parallelism, providing a raw processing power that is orders of magnitude higher than for contemporary multicore CPUs.

Unfortunately, finding an efficient implementation for a function on an hardware accelerator is a complex problem. It requires making careful decisions for mapping computations to the appropriate levels of parallelism and for expliciting data movements across the different memory spaces, in addition to choosing amongst to the many possible thread-local optimizations. While the set of possible optimizations is usually well known, complex interactions between them make it hard to find a global optimum.

Indeed, anticipating downstream transformations and deriving profitability information from intermediate compilation steps is a challenge. Transformations may not commute and some optimization opportunities may only become available after applying so-called "enabling" transformations. Conversely, some transformations may hinder further optimizations. As a result, the production of highly tuned implementations remains a critical challenge to achieve competitive performance.

This dissertation introduces the concept of *candidate* to formally define, represent and explore spaces of possible implementations. A candidate is a partially specified implementation with some decisions fixed while others are left open. It represents a whole set of possible implementations of the same function.

Candidates expose all potential decisions upfront and ensure they are commutative. Taking a decision always restricts the set of possible implementations. This defines a well-behaved optimization space; in particular, it allows search algorithms looking for the best implementations to make the most performance-impacting decisions first and to have a global knowledge of wich optimizations may feature in implementations. We provide a framework that automatically generate code to represents and manipulates candidates, from a declarative description of available choices and their interaction. This description is independent of the function to implement.

We instantiate our concept of candidate to generate efficient code for linear algebra functions on GPUs. This shows our approach is expressive enough to model interacting decisions with a fundamental impact on the structure of the generated code, including compositions of strip-mining, loop fusion, loop interchange, unrolling, vectorization, parallelization, and orchestration of data movements across the memory hierarchy.

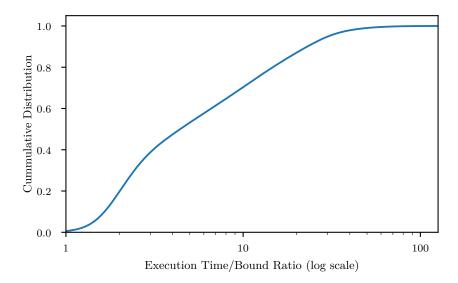

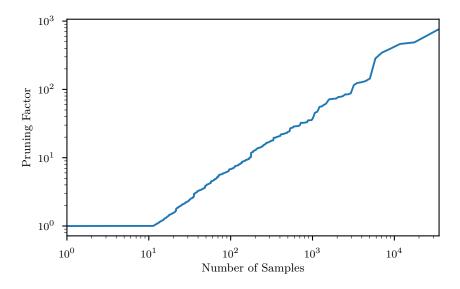

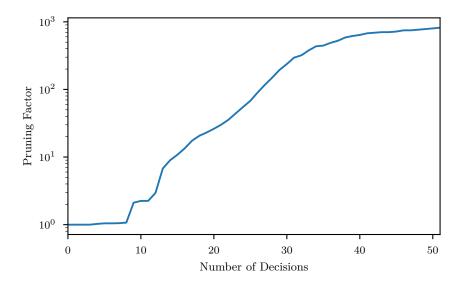

We develop a model capable of computing a lower bound for the execution time of any implementation that derives from a candidate. We show that this model provides actionable information, even after taking only a few decisions, and that it enables pruning the implementation space, reducing its size by several orders of magnitude.

We propose a simple search algorithm to illustrate our approach. It combines the lower bound performance model and actual evaluation on the hardware with statistical exploration to drive the search towards the most efficient implementations. Our experiments show that it generates code that is competitive with hand-tuned libraries for linear algebra functions on GPUs. They also demonstrate that taking the most important decisions first helps finding better implementations faster, thus showing how the concept of candidate empowers search algorithms.

## Acknowledgements

Many people helped me along the path leading to this dissertation. I am dedicating the next few paragraphs to thank them. First and foremost, I am grateful for my PhD advisors, Albert and Marc, who put their expertise to the service of my scientific and human development. In particular, I would like to honor the trust Albert put in me and the energy he gave for my ideas to succeed. And to honor Marc's thoroughness and the life he injects into the Parkas team, be it with the ski, the brioches or the rest

This dissertation would not have been possible without Jacques, who helped me develop the initial idea and create the first prototype. Thank you for your guidance during that time. I look forward to working with you once again. The role played by Basile, Nicolas and Andi was equally crucial. They poured their ideas and their technical knowledge into my prototype to turn it into something that actually works. The careful proofreading of this dissertation by Basile and Andy was also essential. Thank you for your patience and your dedication. I would also like to thank the members of my PhD jury, especially the reviewers for reading my dissertation and providing constructive feedback.

The years I spent working in the Parkas team are full of happy memories. Thank you Tim, Francesco, Paul, Adrien, Guillaume, Nath, Guillaume, Lélio, Chandan, Adila and all the others. A special mention for Tim and his legendary helpfulness.

I made my first steps into the world of compilers during an internship with Anton. Obviously, I was convinced. Thank you for your kind welcome and your guidance.

Finally, thank you Florian, Yoann, Éric, Particia for your support along these years and Anaël for all the courage you gave me.

## Contents

| 1        | Introduction                                              | g  |

|----------|-----------------------------------------------------------|----|

|          | 1.1 Hardware Accelerators                                 | Ć  |

|          |                                                           | 10 |

|          | 1.3 Our Solution: Partially Specified Implementations     |    |

|          | 1.4 Key Contributions                                     |    |

|          | 1.5 Organization                                          | 12 |

| <b>2</b> | Motivation: Partially Specified Schedules                 | 15 |

|          | 2.1 Problem Statement: Scheduling a Basic Block           | 16 |

|          | 2.2 Background: Constraint Satisfaction Problems          | 17 |

|          | 2.3 Partially Specified Schedule                          | 19 |

|          | 2.4 Optimistic Model of Partially Specified Schedules     |    |

|          | 2.5 Summary                                               | 21 |

| 3        | Representing Candidate Implementations                    | 23 |

|          | 3.1 Candidate Implementations                             |    |

|          | 3.2 Decision Space Definition                             |    |

|          | 3.3 Candidate Representation Description Language         | 27 |

|          | 3.4 Example: Instructions Scheduling Within a Basic Block | 34 |

|          | 3.5 Constraint Propagation Code Generation                | 36 |

|          | 3.6 Discussion                                            | 39 |

|          | 3.7 Summary                                               | 41 |

| 4        | Application: Linear Algebra on GPUs                       | 43 |

|          | 4.1 Background: GPUs Architecture                         |    |

|          | 4.2 Kernel Representation                                 |    |

|          | 4.3 Decisions Encoding                                    | 49 |

|          | 4.4 Code Generation                                       | 56 |

|          | 4.5 Discussion                                            | 60 |

|          | 4.6 Summary                                               | 63 |

| 5        | An Optimistic Performance Model of Candidates             | 65 |

|          | <u>-</u>                                                  |    |

|          |                                                           |    |

|          | 5.3 Instantiation of the Model for Kepler GPUs            | 80 |

|          | 5.4 Empirical Evaluation                                  | 82 |

|          | 5.5 Discussion                                            | 85 |

|          | 5.6 Summary                                               | 87 |

| 6        | Scaling the Search with the Properties of Candidates      | 89 |

| •        | 6.1 Search Algorithm                                      | 90 |

|          | 6.2 Sample Kernels                                        | 91 |

|          | 6.3 Empirical Evaluation                                  | 93 |

|          | 6.4 Discussion                                            | 95 |

|          | 6.5 Cummour                                               | 06 |

| 7            | Conclusion |                                    |     |  |

|--------------|------------|------------------------------------|-----|--|

|              | 7.1        | Principal Contributions            | 98  |  |

|              | 7.2        | Long Term Perspectives             | 100 |  |

| $\mathbf{A}$ | Pro        | ofs of the Performance Model       | 109 |  |

|              | A.1        | Notations and Basic Properties     | 109 |  |

|              | A.2        | Program Order                      | 110 |  |

|              | A.3        | Execution Graph Properties         | 114 |  |

|              | A.4        | Virtual and Concrete Paths         | 116 |  |

|              | A.5        | Abstraction of the Execution Graph | 123 |  |

## Chapter 1

## Introduction

Hardware accelerators are specialized processors that are orders of magnitude more efficient than traditional processors for some classes of computation. This dissertation address the generation of optimized code for such specialized hardware. However, starting from a high level implementation of a computationally intensive algorithm, finding the right combination of code transformations to fully exploit this computing power is a complex problem. The main limitation of existing approaches is that they make it hard to anticipate downstream transformations and to extract profitability information from early compilation steps.

The question this dissertation addresses is: Which combination of implementation decisions does lead to the fastest code, given a set of available optimizations?. The originality of our approach is that we expose the compilation process as a progressive refinement of a candidate implementation, that represents a whole set of potential implementations.

Internally, a candidate implementation (candidate for short) is a partially specified implementation, with some implementation choices fixed while others are left open. It explicitly lists all potential implementation decisions, and makes sure they commute. It thus precisely defines potential downstream transformations, which in turn allows for deriving pertinent information from candidates early in the compilation process.

In this dissretation, we first introduce and formalize the concept of candidate. We then apply it to linear algebra on Graphical Processing Units (GPUs) and show how this concept helps finding better implementations faster. We develop a performance model that extracts actionable information from candidates, even when they contain several open choices. We also develop a simple search algorithm to illustrate our claims on the benefits of candidates.

**Introduction Outline.** Section 1.1 gives some background on hardware accelerators, Sections 1.2 and 1.3 respectively lay out our motivations and the high-level ideas behind our approach, while Sections 1.4 and 1.5 detail our key contributions and the organization of this thesis.

#### 1.1 Hardware Accelerators

Software programmable hardware accelerators, such as GPUs are specialized processors designed to perform some specific tasks more efficiently than what is possible with general purpose processors. They trade generality against specialized data paths and massive parallelism, providing a raw processing power that is orders of magnitude higher than the performance of contemporary multicore CPUs. In some domains, adequately taking advantage of this power can be game-changing, allowing computations that would otherwise be too time or energy consuming. For instance, the recent success of deep learning methods can largely be attributed to the performance of GPU-accelerated libraries [1, 2].

Hardware accelerators perform small computation-intensive functions, called *kernels*. Unfortunately, writing or generating efficient code implementing a kernel is a complex problem. Hardware accelerators usually offer multiple levels of parallelism, with different trade-offs between the number of threads, the cost of communication and synchronization and the coherency of memory accesses. They also often feature domain-specific instructions and a complex memory hierarchy, with multiple caches and scratchpad memories of different sizes and properties.

Finding an efficient implementation requires making careful decisions for mapping computations to the appropriate levels of parallelism, for explicitly moving data movements across the different memory spaces and for exploiting domain-specific instructions, in addition to choosing amongst to the many possible thread-local optimizations. While the set of potential optimizations is usually well known, complex interactions between them make it hard to find the best global implementation. Applying one transformation can alter the low-level structure of the code and can change the pressure on constrained resources (e.g. the memory available or the number of threads that can execute in parallel), which in turn can render other decisions invalid or inefficient. These interactions are critical for performance; for instance, parallelizing too many loops is harmful if the threads end up doing too few computations.

Moreover, the best combination of transformations depends on the kernel to implement, the size of the input data and the targeted accelerator. Different computations and input sizes may alter the trade-offs between bottlenecks. Implementations may not even be portable across accelerators implementing the same hardware abstraction. For example, different families of GPUs have memory spaces of different sizes and properties and the code for one GPU may not run on another [3]. It is thus difficult to reuse implementations or compiler heuristics across kernels, input sizes and targets. Writing optimized implementations by hand in infeasible when considering more that a few kernels and a few input sizes. However, automatically generating efficient implementations is also not trivial, as the following section explains.

## 1.2 Challenges of Code Generation for Hardware Accelerators

The problem of picking a good combination of implementation decisions in an interaction-heavy optimization space is not specific to hardware accelerators and occurs on any architecture complex enough that exhaustive enumeration is impossible. The literature already proposes multiple approaches to represent and explore the space of potential implementations, such as SPIRAL [4] for DSP codes, LGen [5] for basic linear algebra, or LIFT [6] for more general computations expressed using combinators.

These approaches all rely on rewrite rules, transforming and incrementally lowering an intermediate representation of the program. They start from an unoptimized implementation and iteratively replace expression patterns with purportedly more efficient ones, or code closer to the target instruction set architecture (ISA) and model of parallelism. A well-defined set of rewrite rules allows for the construction of a search tree, whose nodes are implementations and edges represent the application of rewrite rules. The compiler, or an expert programmer, can then navigate through the tree looking for the best implementation using domain-specific knowledge, hand-tuned heuristics or statistical exploration. Exhaustive evaluation of all possible implementations is usually infeasible. The implementation space grows exponentially with the number of decisions. Even small functions can have billions of possible implementations and just enumerating them, without evaluation, can already be too costly for most applications.

We argue that existing approaches make it hard to anticipate possible downstream transformations and to derive profitability information from intermediate compilation steps. While the list of directly applicable transformations at intermediate steps is usually well known, further transformations may only become available after applying so-called "enabling" transformations. For example, the contraction and promotion of an array into registers may only happen after fusing the producer and consumer loops of the array. Conversely, some transformations may hinder further optimizations. For example, interchanging the nesting order of two loops may forbid loop fusion. Moreover, transformations may not commute. As a result, the production and the specialization to a given target or problem size of highly tuned kernel implementations remains a critical challenge. Consequently, programmers often have to rely on proprietary libraries provided by hardware vendors to achieve competitive performance. Libraries are only available for a limited set of functions and are usually only optimized for a few problem sizes.

## 1.3 Our Solution: Partially Specified Implementations

This dissertation addresses the problem of anticipating downstream transformations and deriving profitability information from intermediate compilation steps. It exposes the compilation process of a kernel as the progressive refinement of a candidate. A candidate is a partially specified implementation where

some implementation choices are fixed, while others are left open. It represents a whole set of implementations of the same kernel. For example, a candidate may expose loop transformation opportunities, instruction selection, data mapping alternatives and memory transfer optimizations. This representation is compact and efficient to manipulate as it does not individually list each possible implementation. The compilation process starts with all choices open and iteratively specifies them until reaching a fully specified implementation.

Driving the Search Towards Efficient Implementations. The key benefit of candidates compared to existing approaches is that they expose all potential decisions upfront and ensure that they are commutative. Making a decision always restricts the set of possible implementations. This defines a well-behaved optimization space; in particular, it allows search algorithms looking for the best implementations to make the most performance-impacting decisions first and expert programmers to manually force any decision. It also precisely defines which transformations might be present in the final implementation from intermediate compilation steps, allowing for deriving profitability information before fixing all choices.

Our approach is not tied to a particular framework to express the objective function and to drive the search. It enables solutions combining actual evaluations on the hardware, performance models, heuristics and statistical approaches. This is critical as solvers cannot encode the full complexity of the hardware.

Candidates Representation. Not all combinations of decisions are valid. Candidates define a Constraint Satisfaction Problem (CSP) to model interactions between decisions, respect the semantics of the kernel and enforce hardware limitations. Since manually writing code to enforce constraints is a hard and error-prone process, we propose a Domain Specific Language (DSL) to describe implementation choices and express constraints between them. A compiler then automatically generates code to represent and manipulate candidates from the DSL. The DSL is generic, as it is not tied to a particular program representation. It enables us to iterate on different implementation space representations faster and makes it easier for external users to use our approach for different domains of application or hardware targets.

## 1.4 Key Contributions

This dissertation introduces the concept of candidate and studies how it enables search algorithms to better implementations faster. We illustrate our ideas by applying them to implement linear algebra kernels on GPUs. This last point is a contribution in itself, as it provides a new way to generate efficient code, competitive with or outperforming hand-tuned libraries.

Candidate Implementations. We propose an approach to formally define, represent and explore spaces of possible implementations using implementation candidates. We model the interactions between decisions as a constraint satisfaction problem. Candidates explicitly list open implementation choices and make sure they are commutative. This defines a well-behaved optimization space; in particular, the search algorithms can be organized to take the most performance-impacting decisions first. We provide a compiler generator that automatically generate code to represent and manipulate candidates, starting from a high-level declarative description.

Implementation Space Exploration. We study how the candidate approach empowers implementation space exploration techniques. We show that they allow precise information to be derived from sub-spaces of implementations, even before fixing all implementation choices. In particular, we develop a performance model that computes a lower bound of the execution time of a candidate. Formally, if c is a candidate,  $x \in [X]$  are the actual implementations that derive from c, B(c) is the lower bound provided by the model and T(x) is the execution time for  $x \in [c]$  on the target accelerator, then

$$\forall x \in \llbracket c \rrbracket . B(c) \le T(x). \tag{1.1}$$

We combine this model with actual runs of implementations on the hardware in a branch-and-bound algorithm. This algorithm prunes entire regions of the implementation space at once without discarding the best implementation.

In order to illustrate our approach and show how it perform in practice, we propose a simple algorithm that searches for good implementations of a kernel. This algorithm combines the lower bound performance model and actual evaluation on the hardware with statistical exploration to drive the search towards the most efficient implementations. We show that both the commutativity of decisions and the ability to derive information from partially specified candidates are critical for guiding the exploration towards efficient implementations.

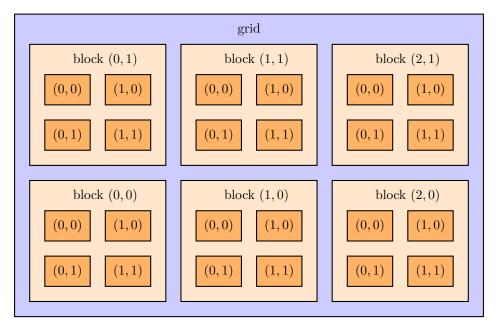

Candidates for Linear Algebra on GPUs. We instantiate our approach to optimize linear algebra kernels on GPUs. We provide a representation of candidates that exposes optimization decisions required to generate efficient code for this application domain and target hardware. We then provide and evaluate a lower bound performance model for this representation of candidates. This demonstrates that our approach is sufficiently expressive to represent complex decisions, with a fundamental impact on the structure of the generated code. This includes compositions of strip-mining, loop fusion, loop interchange, unrolling, vectorization, mapping to multiple levels parallelism, and orchestration of data movements across the memory hierarchy. We validate this work on the generation of optimized linear algebra kernels. We obtain code that is competitive with the performance of vendor-provided hand tuned libraries, and even outperforms them in some cases.

## 1.5 Organization

The rest of this thesis comprises a motivating chapter, that presents the ideas on a simple example, followed by four chapters that formalize our approach and apply it to GPUs. The last chapter presents future research directions and concludes the dissertation.

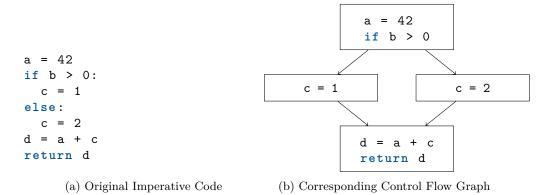

Chapter 2: Motivation: Partially Specified Schedules. The motivation chapter showcases our ideas on a simple problem: the scheduling of instructions within a basic block. It presents concrete questions and solutions that motivate following chapters. In particular, it states the problem we solve, explain how we can encode partially specified schedules and shows how we can use a performance model to prune whole classes of solutions at once when looking for the best implementation.

Chapter 3: Representing Candidate Implementations. This chapter formalizes the concept of candidate. It represents the set of potential implementations as the solutions of a constraint satisfaction problem. It then presents a language to define available implementation decisions and their interactions in a high level declarative domain specific language. Finally, it explains how to automatically generate code to represent and manipulate candidate implementations from the declarative description.

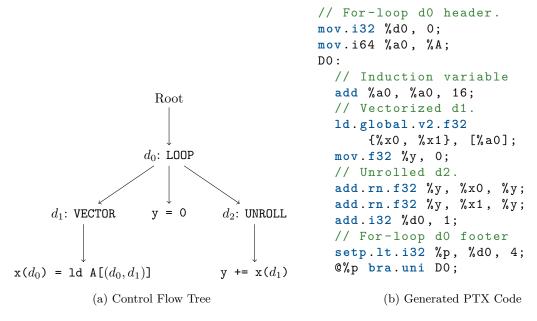

Chapter 4: Application: Linear Algebra on GPUs. This chapter instantiates the ideas of Chapter 3. It proposes an encoding of possible implementations for linear algebra kernels on GPUs. This encoding supports both thread-local and global implementation decisions, including compositions of stripmining, loop fusion, loop interchange, unrolling, vectorization, mapping to multiple levels parallelism, and orchestrating data movements across the memory hierarchy.

Chapter 5: An Optimistic Performance Model of Candidates. This chapter presents an analytical model of a lower bound for the execution time of a candidate. It then instantiates the performance model for GPUs. The model heavily relies on the nature of candidates to provide exact information early in the compilations process.

Chapter 6: Scaling the Search with the Properties of Candidates. This chapter puts together the ideas developed in Chapters 3, 4 and 5 to efficiently explore the implementation space. The goal is to discover how to specify the open choices of a candidate in order to maximize performance. We define a hybrid approach that combines the lower bound performance model with a Monte Carlo Tree Search algorithm driving the search towards the best decisions.

**Chapter 7: Conclusion.** Finally, the last chapter concludes this thesis with a summary of our work and presents our research perspectives to improve the expressiveness of our implementation spaces and develop new search algorithms.

We have implemented the ideas developed in this thesis in a framework named Temalon. This framework, written in Rust, is available under the Apache 2.0 License at the following address.

https://github.com/ulysseb/telamon.

## Chapter 2

# Motivation: Partially Specified Schedules

The goal of this dissertation is to find combinations of implementation decisions for a kernel leading to efficient code. In the general case, this involves a wide variety of decisions, interacting with each other. This chapter introduces, on a simpler problem, the questions and the ideas developed in subsequent chapters. Its goal is to hint at the solutions and the formalism we later present, to help the reader understand the general direction of the dissertation. This chapter studies the problem of scheduling instructions within a basic block, that is, a block of straight-line code with a single entry point and a single exit point. To simplify things further, we also assume a simplistic hardware target evaluating instructions in order and on which we can easily evaluate a schedule.

Even if it only serves as an example here, the problem of scheduling basic blocks is an actual problem encountered by compilers. The number of potential schedules grows exponentially with the number of instructions, making exhaustive exploration of possible schedules impossible. We propose to reason about whole classes of schedules in order to tame the size of the search space. For this, we start from a partial order that we iteratively constrain until reaching a total order. Each intermediate step is a partially specified schedule from which we can extract information to drive the search towards the best solutions.

The idea to manipulate partially specified schedules matches the concept of candidate implementations, which is central in this dissertation. The treatment of the scheduling problem follows the ideas that we develop in the subsequent chapters of this thesis. In particular, it formulates the scheduling problem as a Constraint Satisfaction Problem (CSP). This formalism is crucial to represent partially specified solutions for more complex problems. It also builds a performance model that gives a lower bound for the execution time of any implementation derived from a partially specified schedule. This model suggests that partially specified implementations allow for the development of global heuristics that extract pertinent information from intermediate compilation steps.

This chapter is in the scope of superoptimization. This technique, pioneered by H. Massalin [7], optimizes a computation by trying every potential implementation in a class of program. In our case, we consider every permutation of the initial instructions. Superoptimization typically relies on a combination of empirical tests and a theorem prover to ensure generated implementations are correct a posteriori [8, 9]. Instead, we rely on constraint propagation to avoid considering any invalid implementation in the first place. This is crucial to later consider bigger and more complex implementation spaces, outside of the scope of superoptimization, without spending too much time finding valid implementations.

Outline. Section 2.1 gives a formal definition of the scheduling problem and discusses the difficulties encountered to find the best schedule. Section 2.2 presents some background on Constraint Satisfaction Problems. Section 2.3 leverages this background to reformulate the scheduling problem. It shows how we represent and manipulate partially specified schedules to search for a good solution. Then, Section 2.4 defines a performance model that extracts accurate information for partially specified schedules and explains how we use it to safely prune the schedule space. Finally, Section 2.5 summarizes the ideas of this chapter and explains how we develop them in the rest of this dissertation.

Note that this first chapter only serves to illustrate the problems we propose to solve and the solutions we provide in subsequent chapters. It does not claim to provide a better way to schedule instructions within a basic block nor does it provide any actual evaluation as it only considers an abstract, idealistic, hardware. Subsequent chapters develop these ideas on actual hardware with more complex implementation spaces.

## 2.1 Problem Statement: Scheduling a Basic Block

The principal question this dissertation answers is: Which combination of implementation decisions lead to the fastest code, given the set of available optimizations? Here, we consider a simpler problem, where the kernel is composed of a straight-line sequence of instructions, without any loops or parallelism. We assume that the only way to act on performance is to reorder instructions. This corresponds to the problem of scheduling instructions within a basic block. We also assume a simplistic hardware, that executes instructions in parallel but issues them in order, at a maximum rate of one instruction per cycle.

#### 2.1.1 Problem Formalization

Formally, let I be a set of instructions to schedule and  $\prec$  be a partial order on I that indicates data dependencies. Let l(a) be the latency of each instruction  $a \in I$ . Any total order  $\prec$  that respects  $\prec$  is a valid schedule. From a schedule  $\prec$ , we define the time  $t(a) \in \mathbb{N}$  when an instruction  $a \in I$  starts executing as the smallest integer such that t respects the following constraints.

• Instructions are issued in order.

$$\forall a, b \in I. \ a < b \implies t(a) \le t(b) \tag{2.1}$$

• Only one instruction can be issued per cycle.

$$\forall a, b \in I. \ a \neq b \implies t(a) \neq t(b) \tag{2.2}$$

• Instructions wait on their data dependencies.

$$\forall a, b \in I. \ a \prec b \implies t(b) \ge t(a) + l(a) \tag{2.3}$$

Finally, we define the total execution time of the schedule  $T_{<}$  as

$$T_{<} = \max_{a \in I} t(a) + l(a).$$

(2.4)

For a schedule,  $T_{<}$  corresponds to the time when the last instruction of the schedule has finished executing. The goal is to find a valid schedule < that minimizes  $T_{<}$ .

### 2.1.2 Finding the Best Schedule

The simplest approach to finding an optimal schedule is to evaluate them all. However, the number of valid schedules grows exponentially with the number of instructions. The time required to enumerate valid schedules quickly makes exhaustive enumeration intractable, even if evaluating a schedule was instantaneous.

The alternatives are either to use hand-tuned heuristics to build a single schedule or to use statistical algorithms that drive the exploration of the schedule space toward the best solutions while only evaluating a fraction of valid schedules. Hand-tuned heuristics offer acceptable performance, but are unable to adapt to the subtleties of each input program. Statistical approaches are more versatile as they learn from trials and errors but still suffer from the exponential nature of the problem. The expected number of required evaluations to find a near-optimal solution grows with the size of the search space.

To generate a good schedule, we propose to start from the partial order representing data dependencies and iteratively constrain it until reaching a total order. Each intermediate step is a partially specified schedule, from which we can extract information to drive the search towards the best solutions. A partial order represents all the total orders that derive from it. The search algorithm can thus reason about whole parts of the schedule space without enumerating them. We now introduce the concept of CSP that we later use to model partially specified schedules.

## 2.2 Background: Constraint Satisfaction Problems

A Constraint Satisfaction Problem (CSP) models a system as a finite set of variables that take values in a finite universe. Constraints between variables encode their relationships. A solution of the problem is an assignment of the variables that satisfies the constraints. CSPs are widely used to model complex combinatorial problems, for examples for scheduling, planning, vehicle routing, network management and bioinformatics [10].

Finding a solution to a CSP is an NP-hard problem. In particular, the Boolean satisfiability problem (SAT) translates into a CSP. Constraint Satisfaction Systems combine heuristics and combinatorial search to find solutions to CSPs. In our specific case, finding a solution to the problem is trivial. The CSP formalism allows to easily reason about and manipulate partial orders and later fully fledged partially specified implementations.

This section follows the notations and definitions presented in the thesis of G. Tack [11]. We first give a denotational semantics of CSPs. We then explain how to enforce constraints and how to search for a solution of a CSP.

#### 2.2.1 Variables, Domains and Constraints

CSPs are defined with respect to a finite set of variables X and a finite set of values V. A solution of a CSP assigns a value to each variable. A constraint restricts the set of valid assignments. The following definition captures the concepts of assignments and constraints.

**Definition 2.1** (Assignment and Constraint). An assignment  $a: X \to V$  is a mapping from variables to values. A constraint is a set of assignments  $c \subseteq \mathcal{P}(X \to V)$ . Any assignment  $a \in c$  is a solution of c.

In practice, constraints are usually expressed as logic formulae that only involve a few variables. For  $a:X\to V,\ x\in X$  and  $v\in V$  we denote a[v/x] the assignment a' where a'(x)=v and a'(y)=a(y) for all  $y\neq x$ . We define the *significant* variables of a constraint c, vars(c), as the variables that have an impact on whether an assignment is in c.

$$vars(c) := \{ x \in X \mid \exists v \in V. \ a \in c. \ a[v/x] \notin c \}$$

$$(2.5)$$

Next, we define *domains* that indicate the set of values each variable can take.

**Definition 2.2** (Domain). A *domain* is a function  $d: X \to \mathcal{P}(V)$  that maps variables to set of values. The set of values d(x) for a particular variable  $x \in X$  is the *variable domain* of x. A domain represents a set of assignments (i.e. a constraint) defined as

$$\operatorname{con}(d) := \left\{ a \in X \to V \mid \forall x \in X. \ a(x) \in d(x) \right\}. \tag{2.6}$$

We say that an assignment  $a \in \text{con}(d)$  is *licensed* by d. We call  $\text{Dom} := X \to \mathcal{P}(V)$  the set of all domains.

While domains each represent a constraint con(d), the converse is not true. Domains are a Cartesian representation that is limited to conjunction of unary constraints, that is constraints with a single significant variable. We define a subset order on domains as the subset order on the induced constraints:

$$\forall d_1, d_2 \in \text{Dom. } d_1 \subset d_2 \iff \text{con}(d_1) \subset \text{con}(d_2). \tag{2.7}$$

When any variable domain d(x) is empty,  $con(d) = \emptyset$ . In that case, we say the domain is *failed*. We say that a domain corresponding to a single assignment or a variable domain with a single value is *fixed*.

A CSP is composed of a domain that restricts the initial values variables can take and of constraints that specify the relations between variables.

**Definition 2.3** (Constraint Satisfaction Problem). A Constraint Satisfaction Problem is a pair  $\langle d, C \rangle$  of a domain  $d \in X \to \mathcal{P}(V)$  and a set of constraints  $C \in \mathcal{P}(X \to V)$ . A solution of  $\langle d, C \rangle$  is an assignment licensed by d that respects all the constraints in C.

$$\operatorname{sol}(\langle d, C \rangle) := \{ a \in \operatorname{con}(a) \mid \forall c \in C. \ a \in c \}$$

(2.8)

## 2.2.2 Constraint Propagation and Search

The basis of a constraint satisfaction system is a search procedure that instantiates variables with values from their domain. Enforcing constraints directly from their extensional definition is infeasible, as it would require to enumerate all the assignments licensed by the domain. Instead, constraint satisfaction systems employ *propagators* that decide if an assignment is valid and prune the domain to rule out invalid assignments.

**Definition 2.4** (Propagator). A propagator is a function  $p: Dom \to Dom$  such that:

- p is contracting:  $p(d) \subseteq d$  for any domain  $d \in Dom$ , and

- p is sound: for any domain  $d \in Dom$  and assignment  $a \in d$ ,  $p(\{a\}) \subseteq p(d)$ .

We say that a propagator  $p: Dom \to Dom \ prunes$  a domain  $d \in Dom$  if p(d) is strictly included in d, that is  $p(d) \subset d$ . The propagator p induces a constraint  $c_p$  defined by the set of assignment not pruned by p.

$$c_p := \{ a \in X \to V \mid p(\{a\}) = \{a\} \}$$

(2.9)

Soundness is a weak form of monotonicity. It expresses that the pruning decisions realized by a propagator are consistent. A propagator never prunes assignments that satisfy its induced constraint. Propagators are the operational equivalent of constraints. Each propagator induces a single constraint, that is exactly realized by its pruning procedure. We now define *propagation problems* to realize CSPs using propagators.

**Definition 2.5** (Constraint Propagation Problem). A propagation problem is a pair  $\langle d, P \rangle$  of a domain  $d \in Dom$  and a set of propagators  $P \subseteq Dom \to Dom$ . The induced constraint satisfaction problem of a propagation problem  $\langle d, P \rangle$ , is the CSP  $\langle d, \{c_p \mid p \in P\} \rangle$ . The solutions of a propagation problem are the solutions of the induced CSP:

$$\operatorname{sol}(\langle d, P \rangle) := \operatorname{sol}(\langle d, \{c_p \mid p \in P\} \rangle) \tag{2.10}$$

The solutions of a propagation problem  $\langle d, P \rangle$ , are the assignments licensed by d that are not pruned by any propagator. This is obtained by just applying the definition of the induced constraints to the definition of the solution of a propagation problem.

$$\operatorname{sol}(\langle d, P \rangle) = \{ a \in \operatorname{con}(d) \mid \forall p \in P. \ p(\{a\}) \} = \{ a \} \}$$

$$(2.11)$$

In practice, the constraint satisfaction system automatically generates the propagators from the constraints definition.

The search procedure for a propagation problem  $\langle d, P \rangle$  works as follows. It starts from the initial domain and instantiates the value of a variable by restricting its domain to a single element. It then prunes the domain with propagators until reaching a fix point. The resulting domain falls into three categories:

- If each variable domain contains a single value, then the search is finished and the domain represents a single valid assignment.

- If any variable domain is empty, then the domain is failed and the search procedure backtracks.

- Otherwise, some variable domain still contains multiple values. In that case, the search procedure calls itself recursively on the pruned domain.

Running all propagators at each step of the search procedure would be too costly. Therefore, constraint satisfaction systems try to avoid running a propagator when they know it will not prune the domain. In particular, they only run a propagator if the domain of any significant variable of the induced constraint has changed.

Two propagators inducing the same constraint may prune domains differently. Definition 2.4 only requires that they enforce the induced constraints on fixed domains that represent a single assignment. Propagators may keep invalid values in other domains as long as they are sound. An optimal propagator

$p_{opt}$  inducing a constraint c only keeps the values of a domain d that appear in at least one solution of  $\langle d, \{c\} \rangle$ .

$$\forall x \in X. \ p_{opt}(d)(x) = \{ v \in d(x) \mid \exists a \in c \cap \operatorname{con}(d). \ a(x) = (v) \}$$

(2.12)

Using optimal propagators is impractical in the general case. They may require to enumerate all possible assignments. Moreover, the fix point of two optimal propagators inducing constraints  $c_1$  and  $c_2$  might be weaker than the optimal propagator for  $c_1 \cap c_2$ . Considering constraints independently instead of as a single conjunction alters propagation strength but makes it possible to generate faster propagators and reduces the number of significant variables. Constraint satisfaction systems must thus consider the trade-off between strong and fast propagators. Since propagators are exact on fixed domains, using weaker propagators does not alter correctness. Backtracking handles the cases that constraint propagation misses.

We now go back to the problem of scheduling a basic block and leverage the CSP formalism we just presented to model partially specified schedules.

## 2.3 Partially Specified Schedule

One way to specify a valid schedule is to start from the partial order representing data dependencies and to iteratively refine it by specifying the order between pairs of instruction, until the order is total. With this approach, a partial order is a partially specified schedule that represents all the total orders that derive from it. We model this problem as a CSP whose variables are the pairwise ordering between instructions.

#### 2.3.1 Formalization as a Constraint Satisfaction Problem

Formally, a valid schedule is an assignment of a function *order* that maps pairs of distinct instructions to the values *before* and *after*,

$$order: I \times I \to \{before, after\}$$

(2.13)

and that respects the following constraints.

• The order enforces data dependencies.

$$\forall a, b \in I. \ a \prec b \implies order(a, b) = before$$

(2.14)

• The order is antisymmetric.

$$\forall a, b \in I. \ order(a, b) = before \iff order(b, a) = after$$

(2.15)

• The order is transitive.

$$\forall a, b, c \in I. \ order(a, b) = before \land order(b, c) = before \implies order(a, c) = before$$

(2.16)

This specifies a constraint satisfaction problem, with *order* being an uninterpreted function that defines the CSP variables.

$$X := \{ order(a, b) \mid a, b \in I \} \quad V := \{ before, after \}$$

(2.17)

Formulae (2.15) and (2.16) respectively translate into one constraint for each pair and each triplet of instructions, while (2.14) defines the initial domain d.

$$d: X \to \mathcal{P}(\{before, after\})$$

$$order(a, b) \mapsto \begin{cases} \{before\} & \text{if } a \prec b \\ \{after\} & \text{if } b \prec a \\ \{before, after\} & \text{otherwise} \end{cases}$$

$$(2.18)$$

Following the search procedure sketched in Section 2.2.2, the search for a schedule starts from the initial domain and iteratively specifies the value of the order between pairs of instructions. In this specific case, we can generate propagators that are strong enough to prevent backtracking. After propagation, order represents a partial order.

#### 2.3.2 Schedule Search Tree

The traditional goal of CSPs is to find solutions to a problem. In our case, finding a solution is trivial. A topological sort of the instructions following data dependencies would suffice. Instead we are looking for the best solution we can obtain in a limited amount of time. Ideally, we would generate all possible schedules and return the best one. For this, we would build a binary tree where each node is a partial order and the child of a node are the possible orderings between a pair of unordered instructions. This tree corresponds to the possible instantiations of the pairwise orderings by the CSP search procedure, with variables instantiated in a fixed order.

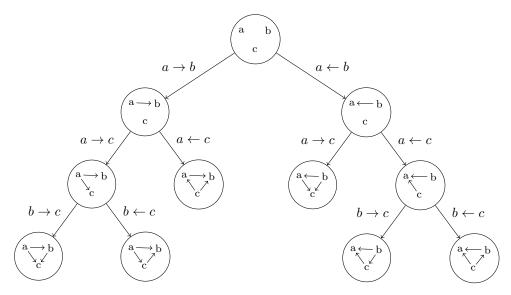

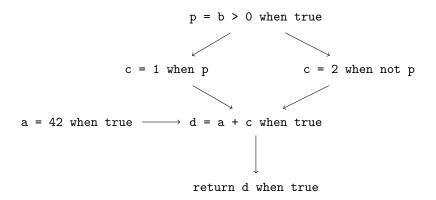

Figure 2.1: A Schedule Search Tree for Basic Blocks With Three Instructions

To build the tree, we start from the root representing the full domain. The two children of a node are the domains obtained by respectively assigning before and after to the next unspecified variable and propagating constraints. The leaves of the tree are fully specified schedules for which we can compute an execution time, while the nodes of the tree represent the set of schedules in their sub-tree. Figure 2.1 presents a schedule search tree for a basic block with three instructions (a, b and c) and no data dependencies. Each level of the tree specifies the order between two instructions, with two possible outcomes.

Building the entire tree would, of course, be infeasible when the number of instructions grows. Thus, we only build the parts of the tree in which we expect to find the best implementations. The idea is that we can reason on partially specified schedules to detect uninteresting nodes early in the search tree, thus avoiding building large parts of the tree.

## 2.4 Optimistic Model of Partially Specified Schedules

We now present a performance model of partially specified schedules to prune the search tree. The performance model gives a lower bound B(d) on the execution time of any schedule licensed by the domain  $d \in Dom$ . If S is the set of all valid schedules, then:

$$\forall s \in S. \ s \in \text{con}(d) \implies T_s \ge B(d) \tag{2.19}$$

From the point of view of the search tree, the bound obtained for an internal node is a lower bound for the execution time of all the schedules in the subtree rooted in the node.

The performance model relies on a graph that represents timestamp constraints between instructions. Given a domain d, the vertices are the set of instructions I and the edges between any two instructions  $a, b \in I$  are defined as follows.

• If a is scheduled before b, that is  $d(order(a,b)) = \{before\}$ , then E contains an edge from a to b with weight 1. This corresponds to the constraint imposed by equation (2.1)

• If b depends on a ( $a \prec b$ ), then E contains an edge from a to b with weight l(a). This corresponds to the constraint imposed by equation (2.3).

We compute B(d) as the weight of the longest path in the graph plus the latency of the last instruction. This corresponds to equation (2.4). Constraints (2.15–2.16) ensure there are no loops in the graph so the longest path weight is well-defined. When the domain is fixed, the bound is equal to the execution time. Otherwise, the graph only contains edges that appear in the graph of every schedule licensed by the domain and the longest path in the graph is a lower bound of possible execution times.

This bound allows us to prune the search tree using a branch and bound strategy. The search algorithm discards branches for which the bound B is bigger than the current best candidate. Because this model works on partially specified implementations, we can prune whole parts of the schedule space at once. We also ensure than we never prune any optimal schedules.

## 2.5 Summary

This chapter presents a solution to the problem of scheduling instructions within a basic block. For this it first formalized the problem and gave some background on CSPs. It them reformulated the problem of scheduling instructions as a CSP. Intermediate steps of the CSP resolution represent partial orders, while solution of the CSP represent fully specifed implementations of the basic block. In practice, scheduling instructions in straight-line code is only one of the many aspects of choosing an implementation for a kernel.

Chapter 3 builds on the ideas of representing sets of potential implementation using the CSP formalism. It presents a generic framework that defines a CSP for each kernel from a declarative description of implementation choices and constraints. Chapter 4 then apply this framework to represent implementation spaces of linear algebra kernels on GPUs, supporting complex transformations. It shows that while the formalism of this chapter may seem overly complex, it is critical when considering several classes of optimizations, interacting with each other.

This chapter also proposes to build a performance model to prune parts of the schedule space. Chapter 5 extends this idea to compute a lower bound for the execution time of any implementation that derives from a partially specified implementation. We show that such models can extract pertinent information early in the compilation process, greatly improving the performance of the search for efficient implementations.

## Chapter 3

## Representing Candidate Implementations

This chapter introduces and formalizes the concept of *candidates*, that are partially specified implementations, with some implementation decisions left open while others are fixed. A candidate thus represents a whole set of potential implementations of the same kernel, up to semantics-preserving implementation decisions. The compilation process starts with all choices open and iteratively specifies them until reaching a fully specified implementation.

Not all combinations of decisions are valid. Candidates define a Constraint Satisfaction Problem (CSP) to model interactions between decisions, respect the semantics of the kernel and enforce hardware limitations. Because manually writing the code to enforce constraints is a hard and error-prone process, we propose a domain specific language (DSL) to describe implementation choices and express constraints between them. This defines a *decision space* that we can instantiate on different kernel to represent candidates.

A dedicated compiler transforms a specification using this DSL into code that we then use to construct the search tree. This consists in generating a data structure that holds the list of available decisions, the code that builds this data structure from the kernel description and the code that propagates constraints on decisions. The DSL and its compiler make our approach independent of a particular encoding of transformations or a of a particular kernel representation. It enables us to easily try out different decision spaces and allows external users to define their own decision space for different application domains.

**Contributions.** This chapter focuses on the formalism and the generic framework to define candidate implementations, while Chapter 4 explains how we use our framework to build a decision space for linear algebra kernels. Specifically, this chapter makes the following contributions.

- It introduces the concept of candidate implementation.

- It presents a formalism to define candidates independently of a particular kernel.

- It presents a declarative language and an associated compiler that implements the formalism. Together, they make it easier to extend the implementation space with new decisions or to apply our approach to other domains of applications.

Outline. Section 3.1 gives a definition of candidate implementations and explains how we expose potential decisions. Section 3.2 then explains how we can specify the decisions and constraints that make up candidates independently of kernel instances. This section introduces the concept of decision space, that lists generic choices and constraints that can be instantiated on any kernel. It also introduces the concept of lowering, that allows us to lower some high-level constructs in the kernel definition when certain conditions are met. Section 3.3 defines a declarative language that defines decision spaces. Section 3.4 illustrate our approach by applying our formalism to the problem of Chapter 2. Then, Section 3.5 explains how we generate code from our domain specific language to represent and manipulate candidates. Finally, Sections 3.6 and 3.7 compares our work to existing approaches and discuss how our framework helps finding efficient implementations.

## 3.1 Candidate Implementations

We represent the problem of choosing among possible implementations of a computational kernel as a CSP. Each variable of the CSP materializes an implementation choice. The initial domain of such a variable contains one value for each possible outcome of the choice. Not all combinations of decisions are valid, hence constraints ensure decisions are coherent. An implementation is a solution of the CSP, that is, an assignment from choices to outcomes that satisfies the constraints. This section assumes that the encoding of the implementation space into a CSP  $\langle d_K, C_K \rangle$  for any kernel K is given. Sections 3.2 and 3.4 and Chapter 4 later explain how we build this encoding from a kernel-independent description.

## 3.1.1 Representation of Potential Implementations.

Following the motivating example of Chapter 2, we use domains to represent and manipulate sets of possible implementations.

**Definition 3.1** (Candidate and Implementation). A candidate is a pair (K, d), composed of a kernel K to implement and a domain d for the CSP  $\langle d_K, C_K \rangle$ . The domain d is thus a more constrained version of the initial domain  $d_K$  of the CSP:  $d \subseteq d_K$ . An implementation of (K, d) is a solution of  $\langle d, C_K \rangle$ . The implementation space  $[\![(K, d)]\!]$  of a (K, d) is the set of all solutions of  $\langle d, C_K \rangle$ .

The domain of a candidate lists possible decisions for each choice. A search algorithm enforces a decision by restricting the domain of the corresponding choice. Constraints may forbid some combinations of decisions. Following the formalism of CSPs, we use propagators that implement the constraints to prune the domains from invalid values. To maximize the information about the validity of decisions, we only consider candidates with domains on which propagators have reached a fixed point. We thus run propagators at the creation and after each modification of the domain. Even then, some invalid value may remain undetected until further choices are specified. In fact, it might be possible that a candidate does not represent any valid implementation at all if one of the variable domains only contains invalid values. CSP solvers solve this problem by backtracking.

In our case, Section 4.5.2 shows that the constraints we use are simple enough constraints to generate accurate propagators that almost never miss invalid values, and thus accurately represent possible decisions. Our search strategy, which we present in Chapter 6, already backtracks when it encounters some candidates that only lead to inefficient implementations. The impact of backtracking due to suboptimal propagators is negligible compared to the number of backtracking due to the search strategy. The definition of propagators (Section 2.2) ensures no invalid value remains in fixed domains, thus ensuring that fully specified candidates are valid.

#### 3.1.2 Interface With Search Algorithms

The objective of a search algorithm is to find an assignment of variables that satisfies the constraints and minimizes the execution time of the kernel on a particular input. Algorithms operate on the domain of variables while the kernel representation remains mostly untouched. From the point of view of a search algorithm, a candidate is thus a partially instantiated decisions vector, with the domain of each choice. The only actions the algorithm can perform are the following.

- 1. It can restrict the domain of a variable in the decision vector. This automatically triggers propagators to recursively prune incompatible values from other variable domains.

- 2. It can copy the decision vector, to branch the search and try different decisions. It does not need to copy the constraints that define the CSP, as they solely depend on the kernel instance which is unchanged by this operation.

A search algorithm typically combines these actions to build a tree whose nodes are candidates. The root is the fully unrestricted candidate  $(K, d_K)$  and each node is a strictly more constrained version of its parent. The leaves of the tree are fixed candidates, corresponding to actual implementations, for which the algorithm can generate code and measure its execution time.

#### 3.1.3 Key Benefits of Candidates

This approach based on candidates offers three advantages. First, domains define a well-behaved set of actions that search algorithms can use to generate implementations. Since it can only restrict the domain of choices, decisions commute and the set of potential decisions decreases after each action. This means that the search algorithm is aware of all potential actions upfront and can make the most performance-impacting decisions first.

Second, it allows for manipulating intermediate steps of the decision process. This is in opposition to black-box solvers, such as ILP or SMT solvers, that optimize for a single objective function. Such solvers cannot fully encode the complexity of the target architecture. On the opposite, our approach allows to mix actual evaluations on the hardware, performance models, heuristics and statistical approaches.

Finally, it allows for the definition of functions from candidates, that extract information from the domains and guide the search. For instance, a function could estimate the execution time of the best implementation that derives from a candidate, or compute a probability distribution on the decisions. Theses function reason about entire sets of candidates at once and have a global knowledge of upcoming decisions, giving them access to the potential characteristics of final implementations. A limitation is that these functions operate on the domain, which is a Cartesian over-approximation of valid assignments.

The definition of candidates we gave in this section assumes we have a CSP  $\langle d_K, C_K \rangle$  for each kernel K. The next section introduces the concept of decision space, that describes  $d_K$  and  $C_K$  independently of the kernel K.

## 3.2 Decision Space Definition

As stated in Definition 3.1, candidates are composed of two parts: a representation of the kernel and a domain. The kernel representation is mostly constant through the search, although some decisions – such as the introduction of temporary variables – can interact with the representation in a limited way. This section explains how we derive the list of decisions that must appear in the domain and the associated constraints from a kernel instance. It presents a formalism to define a generic CSP that can be instantiated for any kernel instance.

This formalism interprets the kernel representation as a set of objects that respect different properties, such as x is an instruction or x depends on y. While objects vary from one kernel to the other, the list of properties remains the same, allowing for the description of the implementation space independently from the kernel instance. Our formalism describes generic decisions and constraints that we instantiate for every tuple of objects verifying given properties. For instance, the generic CSP may induce a choice, indicating if a loop is unrolled or not, for each object x respecting the property x is a loop.

We first explain how we specify the choices and constraints independently of the kernel representation in Section 3.2.1 and then how we allow extending the implementation space with new choices and constraints when lowering high level constructs Section 3.2.2.

#### 3.2.1 Formalization of the CSP Definition

This section explains how we define the CSP  $\langle d_K, C_K \rangle$  relative to a kernel K. For that, we first formalize the concept of *kernel*. We then define *generic choices* as choices that we instantiate for each kernel and a *decision space* as a collection of generic choices and constraints. Finally, we define the CSP associated to a kernel K as the instantiation of the generic choices and constraints for K.

#### Kernel Representation

Let  $\Omega$  be a set of identifiers representing objects let  $\Pi$  be a set of identifiers called *properties* and let  $a:\Pi\to\mathbb{N}$  denote their arity. Let  $\Omega^*$  be the set of tuples of objects of any size. We define a *kernel instance* as a mapping of properties to tuples of objects.

**Definition 3.2** (Kernel Instance). A *kernel instance* is a function K mapping properties to the objects satisfying it:

$$K: \quad \Pi \to \mathcal{P}\left(\Omega^*\right) \\ p \mapsto K(p) \subseteq \Omega^{a(p)}$$

#### Generic Choices

Let  $\mathcal{D}$  be a set of *domains*, where each domain is a (distinct) set of identifiers. We define a *generic choice* as a choice in a given domain that is instantiated for all tuples of objects respecting a set of properties.

**Definition 3.3** (Generic Choice). A generic choice with arity k is a tuple  $c:((p_0,\ldots p_{k-1}),D)\in\Pi^k\times\mathcal{D}$ .

A generic choice  $c = ((p_0, \ldots, p_{k-1}), D) \in \Pi^* \times \mathcal{D}$  indicates a choice among the values of D for each tuple of distinct objects verifying properties  $(p_0, \ldots, p_{k-1})$ . For instance, the choice could be how each loop should be implemented, with k = 1,  $p_0 = is$  a loop and  $D = \{\text{regular}, \text{unrolled}, \text{parallel}\}$ . Similarly, the choice could be the pairwise ordering between pairs of instructions, with k = 2,  $p_0 = p_1 = is$  an instruction and  $D = \{\text{before}, \text{after}\}$ .

Instantiated for a kernel K, a generic choice  $c = ((p_0, \ldots, p_{k-1}), D) \in \Pi^* \times \mathcal{D}$  defines an actual choice – that is a CSP variable – for each combination of object that respect the properties. That is for each tuple of distinct objects in  $K(p_0) \times \cdots \times K(p_{k-1})$ . In our examples, that would respectively be for each loop and for each pair of distinct instructions.

#### **Decision Space**

Next we define a *decision space* in order to represent sets of possible implementations. A decision space is the combination of a set of generic choices defining the list of open decisions and a set of formulae expressing constraints on the decisions. Constraints are universally quantified over objects so that they are independent of the kernel instance, similarly to generic choices.

**Definition 3.4** (Decision Space). A *Decision space* is the pair  $\langle \mathcal{C}, F \rangle$  of a set  $\mathcal{C} \subseteq \Pi^* \times \mathcal{D}$  of generic choices, and a set of first-order formulae F called *constraint formulae*. The alphabet for the constraint formulae contains one predicate symbol with arity a(p) for each property  $p \in \Pi$ , and one function symbol with arity  $\sum_{i \leq k} a(p_i)$  for each choice  $c = ((p_0, \ldots, p_{k-1}), D) \in \mathcal{C}$ .

Note that a decision space represents the generic decisions and constraints that are independent of any kernel, while an *implementation space* represents the set of potential implementations of a kernel. An implementation space is thus a decision space instantiated for a kernel.

### CSP Associated to a Kernel

A decision space  $\langle \mathcal{C}, F \rangle$  defines a CSP for each kernel K. The initial domain is the domain that maps each variable defined by a choice  $c = ((p_0, \dots, p_{k-1}), D)$  to the full domain D. Solutions are the assignments licensed by the decision vector that respect the constraints specified by F. The definition of decision vector below captures the domains of this CSP.

**Definition 3.5** (Partially Instantiated Decision and Decision Vector). A partially instantiated decision for a choice  $c = ((p_0, \ldots, p_{k-1}), D)$  and a kernel K is a function  $\chi_c$  that assigns sets of possible values to a generic choice:

$$\chi_c: K(p_0) \times \cdots \times K(p_{k-1}) \mapsto \mathcal{P}(D)$$

.

A decision vector for a decision space  $\langle \mathcal{C}, F \rangle$  and a kernel is vector with one partially instantiated decision  $\chi_c$  for each choice  $c \in \mathcal{C}$ .

Partially instantiated decisions are partial in the sense that it restricts the possible values, but does not necessarily select one. They are the domains associated to each generic choice instantiated for a kernel while a decision vector represents the full domain. In practice, their representation stores the value of the applications of the  $\chi_c$  to each of their input.

We are now ready to define the constraint satisfaction problem  $\langle d_K, C_K \rangle$  associated to a kernel K that we mention in Definition 3.1.

**Definition 3.6** (CSP Associated to a Kernel). The CSP associated to a kernel K for the decision space  $\langle \mathcal{C}, F \rangle$  is the pair  $\langle d_K, C_K \rangle$  where:

- $d_K$  is the decision vector that maps each variable defined by the generic choice  $c = ((p_0, \dots, p_{k-1}), D) \in \mathcal{C}$  to the full domain D, and

- $C_K$  is the assignments licensed by  $d_K$  for which all constraint formulae hold when interpreting the predicate symbol for property p with K(p) and the function symbol for choice c with  $\chi_c$ .

## 3.2.2 Lowering of High-Level Constructs

This formalism allows for adding objects to the kernel representation during the search. Indeed, extending the set of objects that respects properties adds decisions and constraints without invalidating pre-existing ones. This is useful to lower high-level constructs upon reaching specific decisions. For example, this allows for inserting the appropriate load and store instructions after deciding to allocate a temporary array in memory. Lowering a construct may only add new objects or add properties to existing ones.

It is important to note that it is always possible to express directly in the initial CSP the choices and constraints that the constructs lowering introduce. Indeed, if a construct lowering triggers when a condition p is satisfied, and introduce a choice c, we can add a value ABSENT to the initial domain of c and a constraint  $\neg p \lor c =$  ABSENT so that we can expose c directly in the initial CSP. Similarly, we can add the term  $\lor \neg p$  to the constraints the lowering introduces. This ensures that our claim that all decisions can be available upfront is respected.

The reason to rely on the lowering of high-level constructs to define the decision space are:

- to avoid cluttering the decision vector with decisions that will not affect the generated code, making constraint propagation more efficient;

- and intentionally delay some decisions to focus search algorithms on more impactful choices first.

An hybrid approach is to use construct lowering but to pre-compute the transitive closure of choices that we can add to the CSP and to expose them to search heuristics only.

To lower a high-level construct, we operate in four steps.

- 1. First, the CSP solver detects the lowering condition is met. We describe such conditions using first-order logic formulae that are independent of the kernel instance, similar to the ones in F.

- 2. Then, the solver copies the kernel representation and adds objects to the sets representing properties.

- 3. Then, the solver extends the decision vector to accommodate the new variables induced by the new objects.

- 4. Finally, the solver enforces the new constraints obtained by evaluating the properties  $p \in \Pi$  to the new objects in F.

This section gave of formal definition of the concept of *decision space*, that describes the choices and constraints that make up a candidate, independently of kernels. The following section explains how we specify decision spaces in practice.

## 3.3 Candidate Representation Description Language

This section presents a domain specific language (DSL) that implements the formalism presented in Section 3.2. It declaratively defines a decision space. In particular, it specifies how to interact with the kernel and defines generic choices, constraints and lowering conditions.

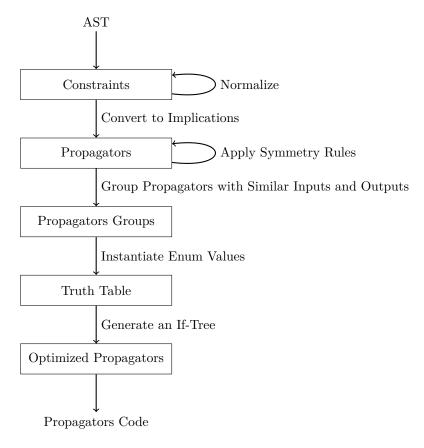

This language serves two distinct purposes. First, it precisely define the decision space in a concise way. This is essential to understand and debug the constraints. Second, it simplifies changing the encoding of the decision space. This makes it possible to try out different approaches or to build an decision space for a different domain with low effort. Indeed, we have implemented a compiler, hereafter referred to as the *DSL compiler*, that generates code to create, represent and manipulate candidates from the DSL. In particular, it outputs code to store the decision vector, compute the initial domain, propagate constraints, and perform construct lowering.

**Outline.** The specification of a decision may contain five kinds of statements, each detailed in a dedicated section:

- $\langle set \rangle$  statements that specify the properties the kernel expose, and how to access the set of objects that respect each property, defined in Section 3.3.1,

- \(\langle \choice \rangle \) statements to define generic choices, defined in Section 3.3.2,

- (constraint) statements to specify the constraints formulae, defined in Section 3.3.3,

- $\bullet$   $\langle lowering \rangle$  statements to indicate when and how to lower high-level constructs, defined in Section 3.3.4 and

- \(\langle quotient \rangle \) statements to represent classes of equivalent objects, for example fused dimensions, defined in Section 3.3.5.

#### 3.3.1 Kernel Interface Definition

Our DSL defines a decision space on top of an existing kernel representation. Following our formalism, a kernel representation exposes a set of properties  $\Pi$ , and the sets of objects that respect each property  $p \in \Pi$ . A  $\langle set \rangle$  statement defines a single property  $p \in \Pi$  and specifies how to access the corresponding set K(p) for each kernel K.

```

⟨specification⟩ ::= (⟨set⟩ | ⟨choice⟩ | require ⟨constraint⟩ | ⟨lowering⟩ | ⟨quotient⟩)*

⟨set⟩ ::= 'set' ⟨set-ident⟩ ⟨set-arg⟩? ⟨superset⟩? ':' ⟨set-disjoint⟩? (⟨entry-name⟩ '=' ⟨code-snippet⟩)*

'end'

⟨set-arg⟩ ::= '(' ⟨ident⟩ 'in' ⟨set-ident⟩ ')'

⟨superset⟩ ::= 'subsetof' ⟨set-ident⟩

⟨set-disjoint⟩ ::= 'disjoint' ':' list(⟨set-ident⟩, ',')

⟨entry-name⟩ ::= 'type' | 'id_type' | 'id_getter' | 'iterator' | 'getter' | 'from_superset' | 'var_prefix'

```

Figure 3.1: Top-Level and Set Statements Syntax

Sets Definition Syntax. Figure 3.1 presents the syntax of set definitions in Backus-Naur form. The list(A, B) operator indicates a list of As separated by Bs. A set definition includes the set name, an optional argument, an optional superset, a list of other disjoint sets and several entries that indicate how to generate code that manipulates the set. Each  $\langle entry-name \rangle$  may appear only once in a set definition. When generating code from snippets, the CSP compiler substitutes variables starting with \$. It replaces \$fun by a pointer to the kernel, \$item by a pointer to the current object and \$id by the id of the current object where it makes sense.

```

set Instructions:

type = "ir::Instruction"

iterator = "$fun.instructions()"

id_type = "ir::InstId"

id_getter = "$obj.id()"

item_getter = "$fun.instruction($id)"

var_prefix = "inst"

end

```

Listing 3.1: Instructions Set Definitions

For example, Listing 3.1 defines a property Instructions that lists the instructions of the kernel. Beside the name of the set, this definition has a list of entries that map attributes to snippets of code. The CSP compiler embed these snippets in the generated code to manipulate the set and its objects. Mandatory entries are:

type: the type of the set objects,

iterator: an expression that returns an iterator on the set,

id\_getter: an expression that returns the unique identifier of an object,

id\_type: the type of the unique identifier, and

getter: an expression that returns the object associated to a unique identifier.

Additionally, the optional var\_prefix entry specifies a prefix to use when naming a variable holding objects of the set. It makes it easier to debug the code generated by the CSP compiler.

Relations Between Sets. Listing 3.2 shows how we define relations between sets with subset and disjointedness directives. The DSL compiler uses these directives to type-check constraints and to determine when to run propagators. It automatically assumes sets with no common superset disjoint. While limited in expressiveness, these relations nicely match the concepts of type and subtype in programming languages. Listing 3.2 defines two sets Loads and Stores that correspond to the ir::LoadInst and ir::StoreInst types in the kernel representation. Both are subtypes of ir::Instruction and thus the LoadInsts and StoreInsts sets are subsets of Instructions. Subsets have an additional entry, from\_superset to test if an object of the superset is in the subset. This entry maps to an expression that returns the object downcast to the correct type if it is part of the set, using the Option Rust type.

```

set Loads subsetof Instructions:

type = "ir::LoadInst"

from_superset = "$item.as_load()"

... // Elided for the sake of brevity

end

set Stores subsetof Instructions:

disjoint: Loads

type = "ir::StoreInst"

from_superset = "$item.as_store()"

... // Elided for the sake of brevity

end

```

Listing 3.2: Subset Definition

**Parametric Sets.** Finally, our DSL supports parametric sets. Parametric sets define a set for each object respecting a property. For example, Listing 3.3 defines a set containing the arrays accessed for each load instruction. In our formalism, this translates to a property on tuples of objects: the parameters and the objects of the set.

```

set AccessedArray($inst in LoadInsts) subsetof Arrays:

... // Elided for the sake of brevity

end

```

Listing 3.3: Parametric Set Definition

Note that we specify the set parameter as a variable binding: **\$inst in LoadInsts**. This pattern occurs each time we quantify a definition for all objects in a set. The variable may appear in code snippets inside the definition. The DSL compiler replaces it with an expression pointing to the object of the currently considered set.

#### 3.3.2 Choices Definition