## Model-Driven Architecture Exploration for Fault Tolerance Improvement

Thi-Tuyen Nguyen

#### ▶ To cite this version:

Thi-Tuyen Nguyen. Model-Driven Architecture Exploration for Fault Tolerance Improvement. Electronics. UNIVERSITE DE NANTES, 2019. English. NNT: . tel-02378951

## HAL Id: tel-02378951 https://hal.science/tel-02378951

Submitted on 25 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

## L'UNIVERSITE DE NANTES

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Electronique

## Par Tien Thanh NGUYEN

## **Model-Driven Architecture Exploration for Fault Tolerance Improvement**

Thèse présentée et soutenue à Nantes, le 15 Novembre 2019 Unité de recherche : IETR UMR CNRS 6164

#### Rapporteurs avant soutenance :

Alexandre NketsaProfesseur, Université Toulouse 3Samy MeftaliMaître de conférences, HDR, Université de Lille 1

#### **Composition du Jury :**

| Président :<br>Examinateurs :         | Alexandre Nketsa<br>Florence Maraninchi<br>Samy Meftali<br>Olivier Pasquier | Professeur, Université Toulouse 3<br>Professeur, INP Grenoble<br>Maître de conférences, HDR, Université de Lille 1<br>Maître de conférences, Université de Nantes |

|---------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Invité :                              | Anthony Mouraud                                                             | Chef de projets, CEA Tech Nantes                                                                                                                                  |

| Dir. de thèse :<br>Co-dir. de thèse : | Sébastien Pillement<br>Mathieu Thévenin                                     | Professeur, Université de Nantes<br>Chercheur, CEA - Paris Saclay                                                                                                 |

# Projet de thèse :

Cette thèse est principalement préparée au sein du laboratoire IETR (Institut d'Électronique et de Télécommunications de Rennes), UMR CNRS 6164 à l'Ecole polytechnique de l'université de Nantes, avec des séjours réguliers aux CEA Tech à Nantes et au CEA Saclay.

La thèse est financée par un projet HOLISTAR de ressourcement CEA Tech en région Pays de la Loire.

### Acknowledgments

I would like to start my thesis to talk about what is important in my 3-year journey. It was not a long time but it was enough for me to discover not only knowledge but also a process of hearing and identifying myself. It was also a journey that I met and worked with new people in France, a beautiful land far from Vietnam where I was born.

First, I would like to thank my advisors, Mathieu THÉVENIN, Researcher at CEA Paris Saclay, and Sébastien PILLEMENT, Professor at Université de Nantes. They gave me dedicated instructions that played a key role in my research process. Mathieu has given me good advice for one year I worked at CEA. And Sébastien, whose clear insights into the direction of the job, has challenged me with his full-of-ideas questions for two years at Polytech Nantes.

Next, I would like to thank my co-advisors, Anthony MOURAUD, Project Manager at CEA Tech Nantes, and Olivier PASQUIER, Lecturer at Université de Nantes. The interesting debates with Anthony showed me meaningful ideas when I was working at CEA Tech Nantes. Meanwhile, Olivier's caution kept me on track in my works at IETR Polytech. They helped me lead my work further and more fully.

I want to express my sincere gratitude to all the members of the jury. I begin by thanking Mr. Alexandre NKETSA, Professor at Université Toulouse 3, and Mr. Samy MEFTALI, Lecturer, HDR, Université de Lille 1, for having accepted the responsibility of rapporteur. I express my gratitude to MM. Florence MARANINCHI, Professor at INP Grenoble, to have participated in the jury of my thesis.

Special thanks to the secretaries, Sandrine CHARLIER at IETR Polytech Nantes and Nathalie FEIGUEL at LCAE/DM2I CEA for taking care of all my administrative issues with their ultimate goodness.

I also want to express my gratitude to my friends, brothers, colleagues that I can hardly name them all. They are an integral part of my life.

And last but not least, I want to send my love to my family, my father Trong Hoang NGUYEN, my mother Thi Ngan HOANG, my brother and sister-in-law Duc Canh NGUYEN and Thi Thao DO, and my nephew Hoang Duong NGUYEN. They all are my motivation, my love, and my spiritual support even though they stay thousands of kilometers away from me.

Finally, I would like to conclude this section with a verse in the poem "Cáo tật thị chúng" of Zen Master Man Giac (1052-1096), a famous Zen Master in Vietnamese history:

"Mạc vị xuân tàn hoa lạc tận

Đình tiền tạc dạ nhất chi mai."

("Do not say that the spring is over, all the flowers fall off

Last night in the front yard there was a branch of apricot blossom.")

Thank you all,

Tien Thanh NGUYEN

# Contents

| Li | st of | f figures                                               | 9         |

|----|-------|---------------------------------------------------------|-----------|

| Li | st of | f tables                                                | 11        |

| A  | crony | yms                                                     | 15        |

| R  | ésum  | né                                                      | 17        |

| 1  | Inti  | roduction                                               | <b>21</b> |

|    | 1.1   | Embedded system                                         | 22        |

|    | 1.2   | Fault model                                             | 25        |

|    | 1.3   | Tolerance strategies                                    | 27        |

|    |       | 1.3.1 Spatial redundancy                                | 27        |

|    |       | 1.3.2 Temporal redundancy                               | 28        |

|    |       | 1.3.3 Check-pointing                                    | 28        |

|    |       | 1.3.4 Error correction code                             | 29        |

|    | 1.4   | Problem statement and contributions                     | 30        |

| 2  | Lite  | erature reviews                                         | <b>31</b> |

|    | 2.1   | Model driven engineering                                | 32        |

|    |       | 2.1.1 Model-Based Testing                               | 33        |

|    |       | 2.1.2 Model-driven development                          | 33        |

|    | 2.2   | Static and dynamic exploration                          | 39        |

|    |       | 2.2.1 Design-time exploration                           | 40        |

|    |       | 2.2.2 Run-time exploration                              | 43        |

|    |       | 2.2.3 Fault-tolerance and reliability-based exploration | 45        |

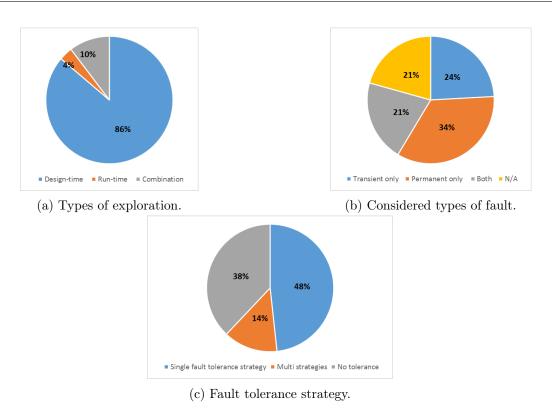

|    |       | 2.2.4 Analysis                                          | 48        |

|    | 2.3   | Summary                                                 | 52        |

| 3  | Fau   | ılt-tolerant platform meta-model                        | 53        |

|    | 3.1   | Platform meta-model                                     | 54        |

|    |       | 3.1.1 Proposed meta-model                               | 54        |

|    |       | 3.1.2 Fault tolerance in the meta-model                 | 58        |

|    | 3.2   | Supporting tool                                         | 64        |

|    | 3.3   | Summary                                                 | 67        |

#### CONTENTS

| 4            | Des        | sign space exploration                      | 69  |

|--------------|------------|---------------------------------------------|-----|

|              | 4.1        | Design space                                | 70  |

|              |            | 4.1.1 Initialization                        | 71  |

|              |            | 4.1.2 Mapping process                       | 73  |

|              |            | 4.1.3 Solution evaluation                   | 86  |

|              | 4.2        | Optimization process                        | 95  |

|              |            | 4.2.1 Objective function                    | 95  |

|              |            | 4.2.2 Search strategies                     | 96  |

|              | 4.3        | Summary                                     | 97  |

| 5            | Exp        | perimental evaluation                       | 99  |

|              | $5.1^{-1}$ | Case-study description                      | 100 |

|              |            | 5.1.1 Sobel filter                          | 100 |

|              |            | 5.1.2 Harris detector                       | 102 |

|              | 5.2        | DSE results                                 | 104 |

|              |            | 5.2.1 Sobel filter                          | 104 |

|              |            | 5.2.2 Harris detector                       | 109 |

|              | 5.3        | Summary                                     | 117 |

| 6            | Cor        | nclusions and perspectives                  | 19  |

|              | 6.1        | Conclusions                                 | 120 |

|              | 6.2        | Perspectives                                | 121 |

| Bi           | blio       | graphy                                      | 122 |

| P۱           | ıblic      | cations                                     | 133 |

| $\mathbf{A}$ | ppen       | ndices                                      | 135 |

| A            | Coo        | de implementation                           | 137 |

|              |            |                                             | 137 |

|              | A.2        | Harris conner dectector code implementation | 138 |

|              | A.3        |                                             | 141 |

# List of Figures

| 1.1  | An example of target application with 4 functions and their properties                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Overview of a heterogeneous Multi-Processor System-on-Chip (MPSoC)                                                                                                                         |

| 1.3  | Abstraction levels of design space exploration [4]. $\ldots \ldots \ldots$ |

| 1.4  | Relation between fault, error and failure                                                                                                                                                  |

| 1.5  | A transient fault appears and disappears on a Processing Element (PE) component 20                                                                                                         |

| 1.6  | An instance of spatial redundancy: Triple Modular Redundancy (TMR) (Triple Modular                                                                                                         |

|      | Redundancy)                                                                                                                                                                                |

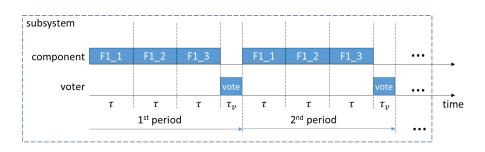

| 1.7  | An instance of temporal redundancy: Triple Re-execution Redundancy (TReR) (Triple                                                                                                          |

|      | Re-execution Redundancy)                                                                                                                                                                   |

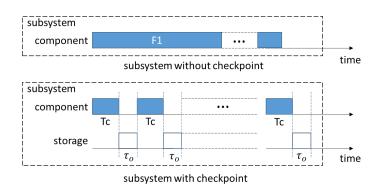

| 1.8  | Subsystem without/with checkpoint                                                                                                                                                          |

| 1.9  | Memory with correction code                                                                                                                                                                |

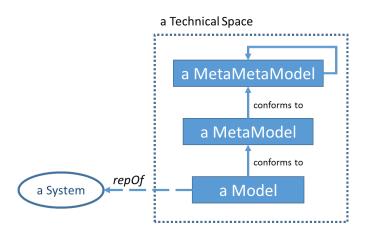

| 2.1  | System, models and technical space [26]                                                                                                                                                    |

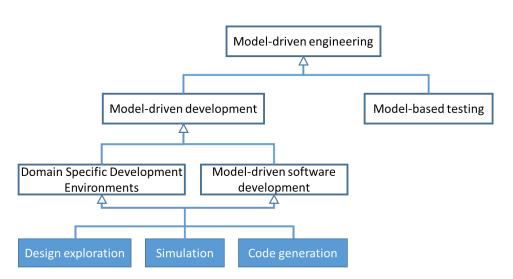

| 2.2  | Model Driven Engineering (MDE) classification                                                                                                                                              |

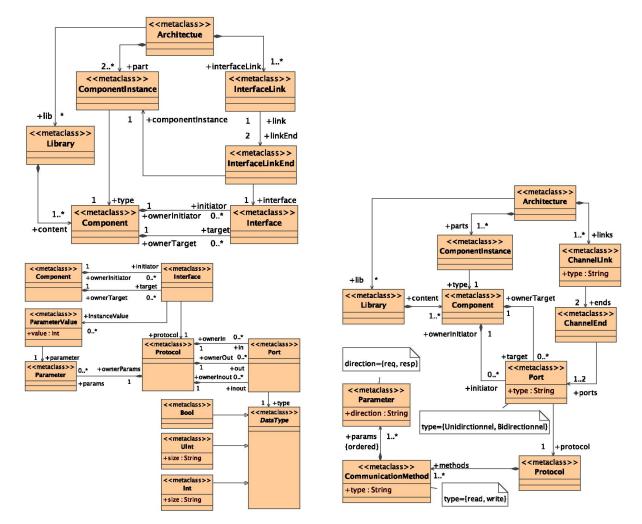

| 2.3  | Hardware architecture meta-model proposed by Graphical Array Specification for Par-                                                                                                        |

|      | allel and Distributed Computing (GASPARD) [34] describes the hardware architecture                                                                                                         |

|      | at a) the clock cycle level and b) the timed programmer's view level                                                                                                                       |

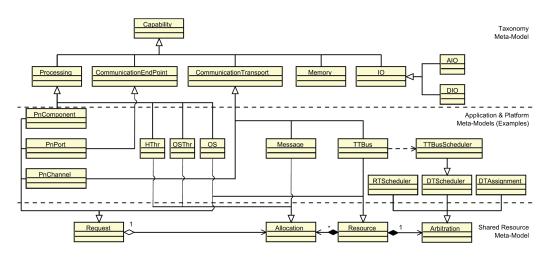

| 2.4  | Application and platform meta-model for the heterogeneous multiprocessor architectures                                                                                                     |

|      | with time-triggered execution paradigm [38]                                                                                                                                                |

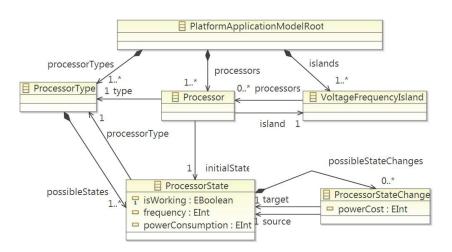

| 2.5  | Platform Application Model (PAM) metamodel [40]                                                                                                                                            |

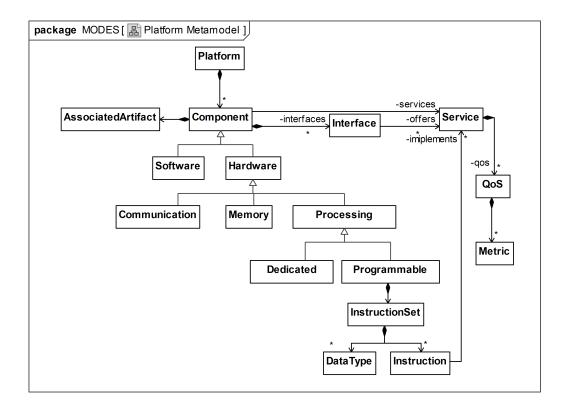

| 2.6  | Meta-model proposed by ModES [41]                                                                                                                                                          |

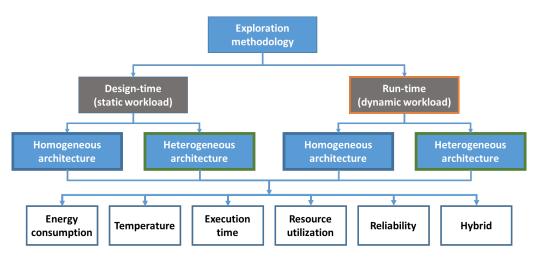

| 2.7  | Classification of exploration methodology                                                                                                                                                  |

| 2.8  | Design-time exploration chart                                                                                                                                                              |

| 2.9  | Run-time exploration flow.    43                                                                                                                                                           |

| 2.10 | Review the reliability-aware Design Space Exploration (DSE) studies                                                                                                                        |

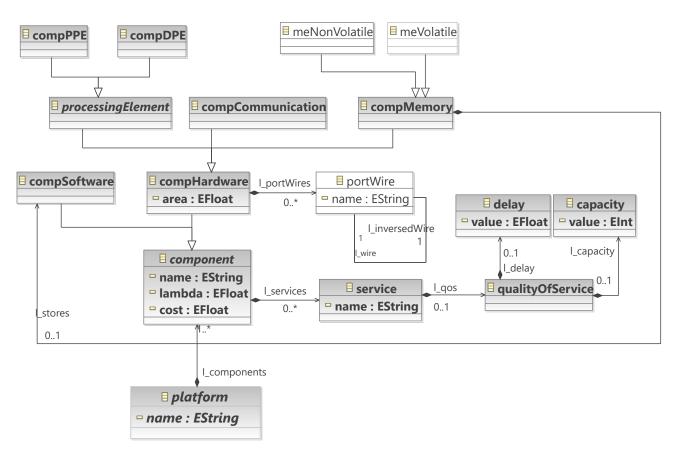

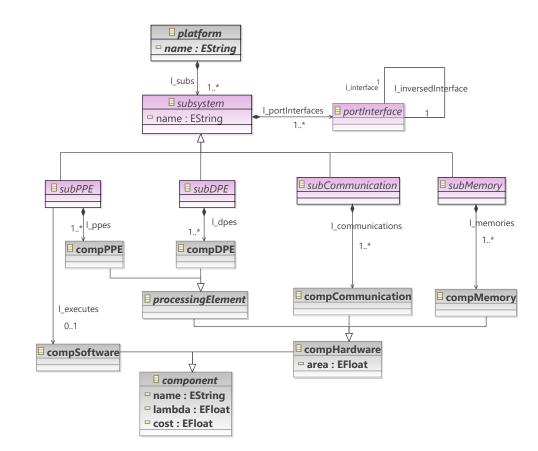

| 3.1  | architectural part related to the component. Gray elements refer to the Model-driven                                                                                                       |

|      | Embedded System (ModES) platform meta-model [41]. White elements are defined in                                                                                                            |

|      | this thesis. $\ldots \ldots \ldots$                                        |

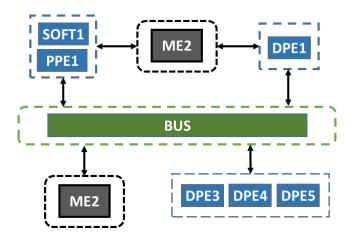

| 3.2  | an example of an MPSoC platform                                                                                                                                                            |

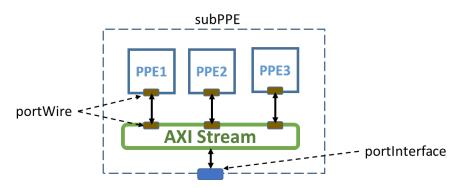

| 3.3  | proposed meta-model of subsystem. Gray and bold elements refer to Figure 3.1. Violet<br>and italic elements represents the subsystem level                                                 |

| 3.4  | an example: a <i>compCommunication</i> in a <i>subPPE</i>                                                                                                                                  |

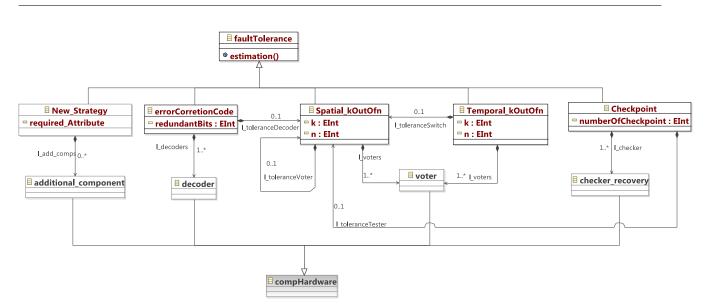

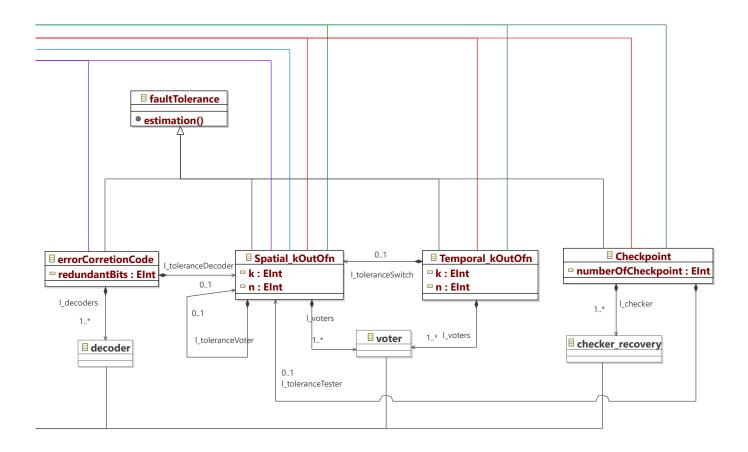

| 3.5  | fault tolerance strategies on the proposed platform meta-model                                                                                                                             |

|      |                                                                                                                                                                                            |

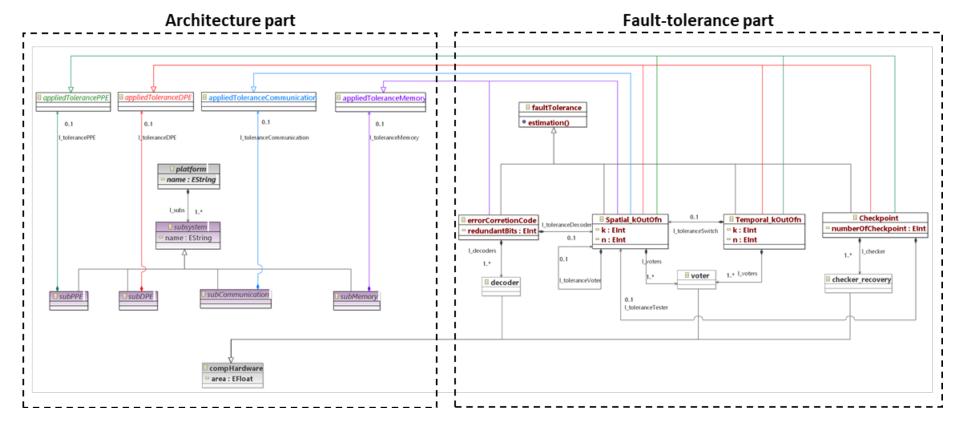

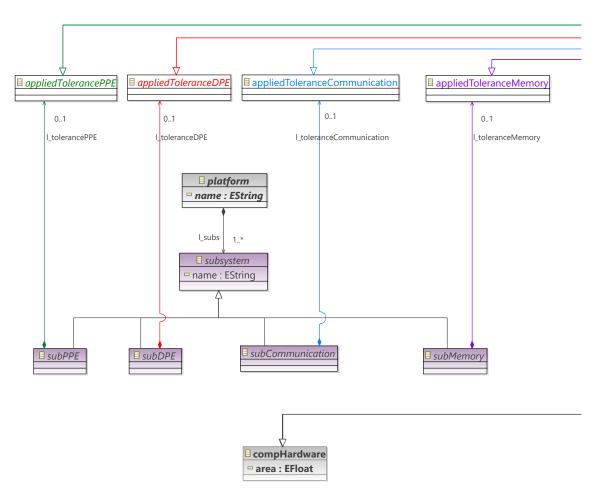

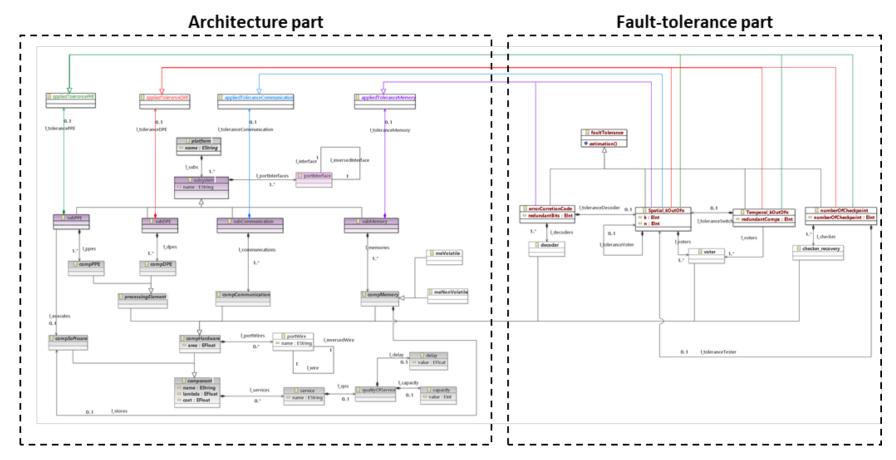

| 3.6   | relation between the simplified architectural part and the fault tolerance part of the                 |          |

|-------|--------------------------------------------------------------------------------------------------------|----------|

|       | proposed platform meta-model. The left part (Architectural part) refers to Figure 3.8.                 |          |

|       | The right part (Fault-tolerance part) refers to Figure 3.7.                                            | 60       |

| 3.7   | fault tolerance part of the proposed platform meta-model                                               | 61       |

| 3.8   | the simplified architectural part related to the fault tolerant. The <i>platform</i> , <i>subDPE</i> , |          |

|       | subPPE, subCommunication, subMemory and compHardware elements refer to Fig-                            |          |

|       | ure 3.3.                                                                                               | 62       |

| 3.9   | overall view of the platform meta-model. The left part (Architectural part) refers to                  |          |

|       | Figure 3.1, 3.3 and 3.8. The right part (Fault-tolerance part) refers to Figure 3.5                    | 63       |

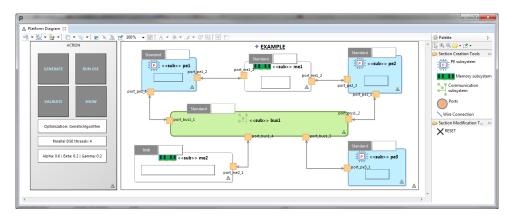

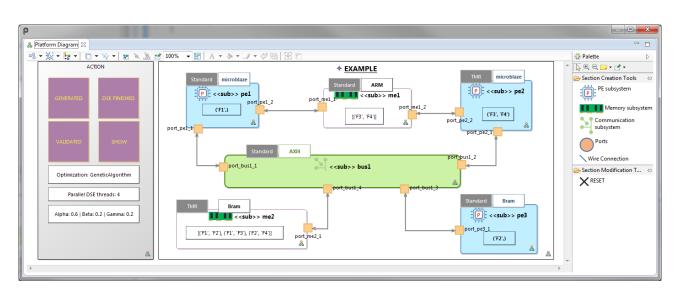

|       | illustration of the workbench for the modeling of a 6-subsystem platform.                              | 64       |

| 3.11  | four big buttons in the left have changed from the gray to pink, meaning the DSE                       |          |

|       | process is complete and the result has been found. The best solution is found shown in                 | 05       |

| 9 10  | the workbench.                                                                                         | 65       |

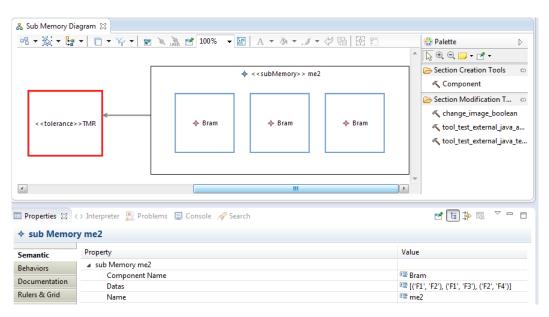

| 3.12  | workbench inside a subsystem diagram; the centre is the Subsystem Diagram; the palette                 |          |

|       | on the right is composed of the tools that allow to modify, customize the subsystem, the               | 66       |

| 9 1 9 | box in the bottom shows parameters of the Subsystem.                                                   | 66       |

| 3.13  | table generated automatically in terms of fault tolerance and cost of the platform ac-                 | 66       |

|       | cording to the best solution found in a DSE process                                                    | 00       |

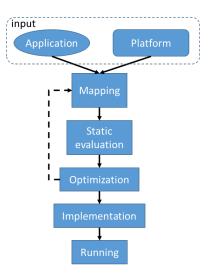

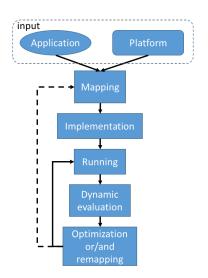

| 4.1   | proposed design solution generator flow.                                                               | 70       |

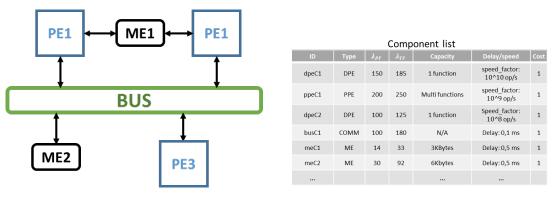

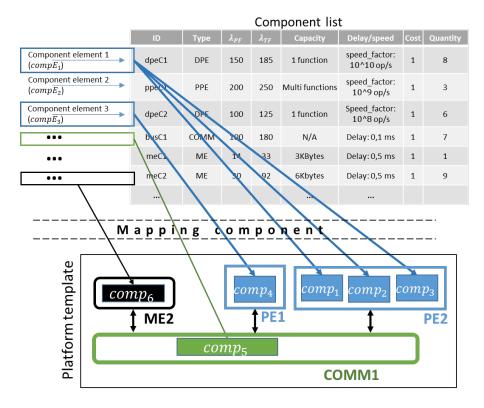

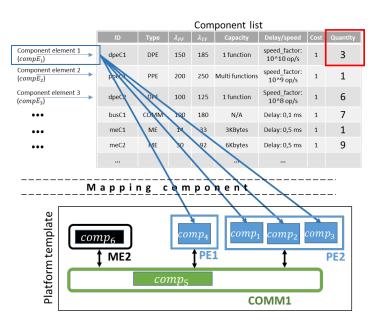

| 4.2   | a platform template and a component list prepared before a DSE process                                 | 73       |

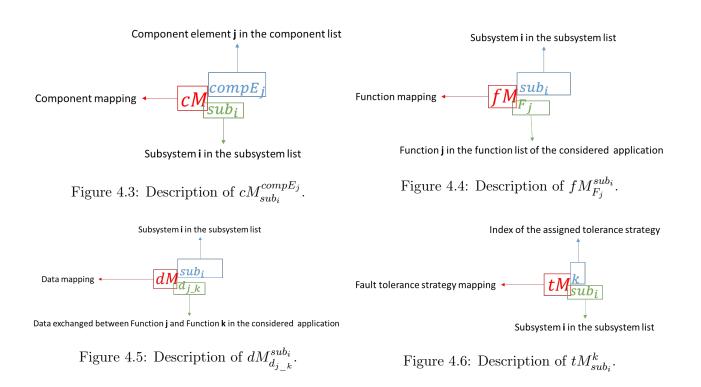

| 4.3   | Description of $cM_{sub_i}^{compE_j}$ .                                                                | 75       |

| 4.4   | Description of $fM_{F_j}^{sub_i}$ .                                                                    | 75       |

|       | Description of $j M_{F_j}$ .                                                                           |          |

| 4.5   | Description of $dM_{d_{j_k}}^{sub_i}$ .                                                                | 75       |

| 4.6   | Description of $tM_{sub_i}^{k}$ .                                                                      | 75       |

| 4.7   | Illustration of component list, platform template, and component mapping.                              | 76       |

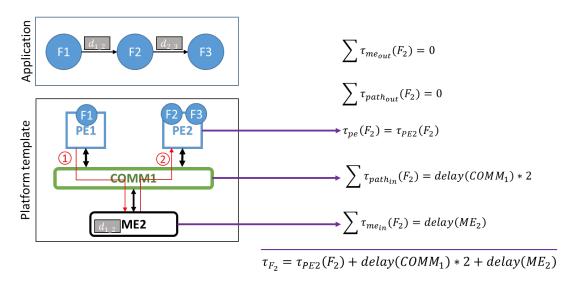

| 4.8   | Application graph, platform, and function mapping.                                                     | 79       |

| 4.9   | An example of the component mapping does not respect Constraint 4.3.                                   | 84       |

| 4.10  | Connection between two functions.                                                                      | 87       |

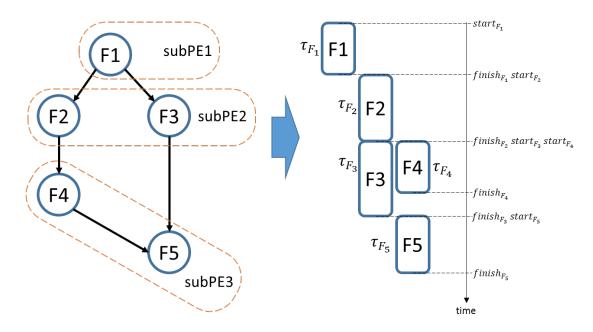

|       | An example of function mapping and scheduling                                                          | 88       |

|       | A transient fault appears and disappears on a PE component                                             | 89<br>90 |

|       | Multi functions are mapped on the same PE subsystem with TMR                                           | 90<br>92 |

| 4.14  | wuld functions are mapped on the same i is subsystem with i ftert                                      | 92       |

| 5.1   | the Directed Acyclic Graph (DAG) of the Sobel-filter application                                       | 100      |

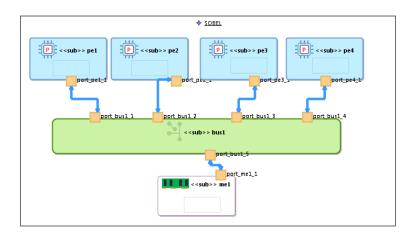

| 5.2   | platform template for the case study-1 is composed of 6 subsystems: 4 subPEs (in blue),                |          |

|       | 1 subCommunication (in green), and 1 subMemory (in white)                                              | 101      |

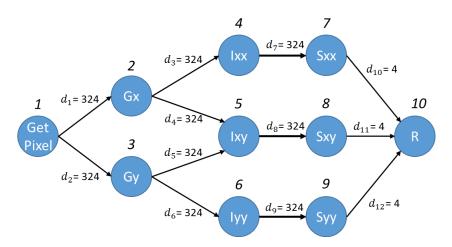

| 5.3   | the DAG of the 10-function application in the case study-3.                                            | 102      |

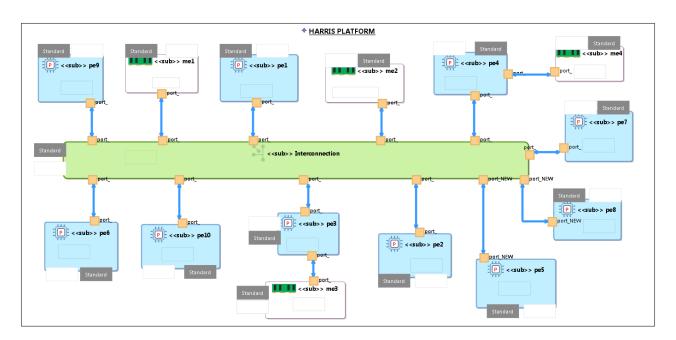

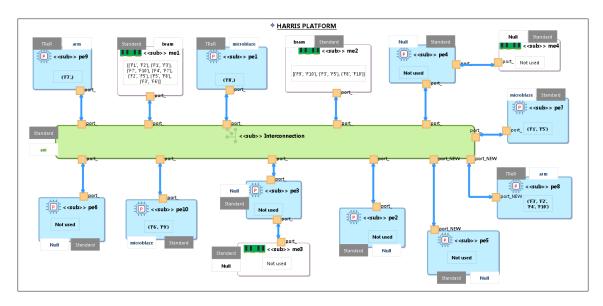

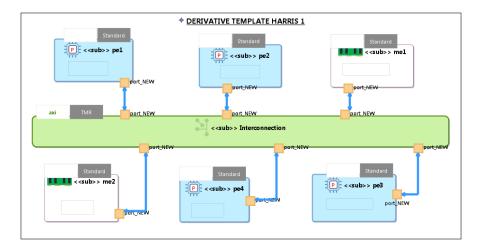

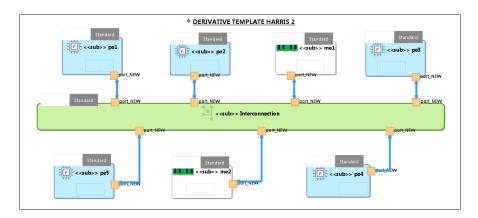

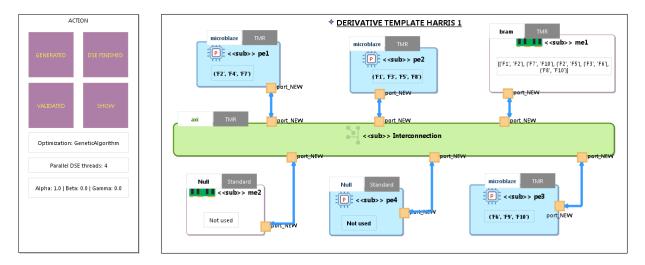

| 5.4   | platform template in the case study-2 is composed of 15 subsystems                                     | 103      |

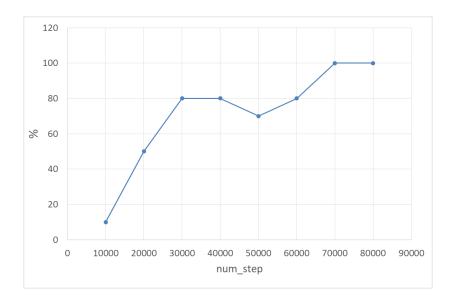

| 5.5   | Impact of the number of steps on the probability to find the best solution                             | 106      |

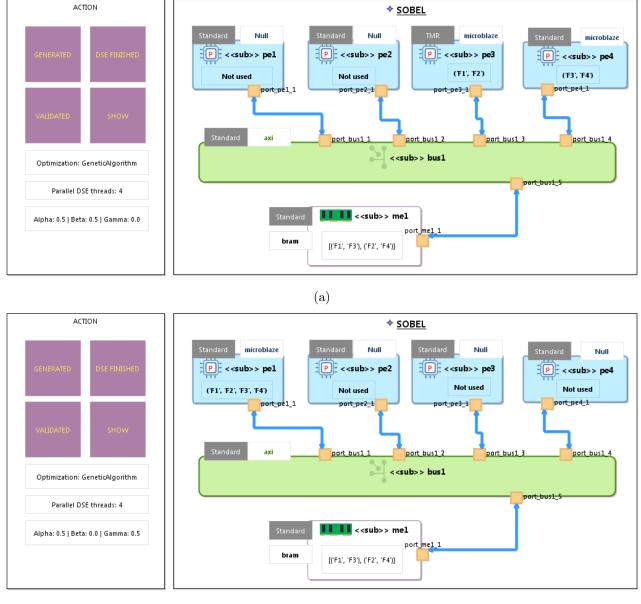

| 5.6   | result found and shown on the DSE tool by all three search strategies (a) with $\{\alpha = 0.5,$       |          |

|       | $\beta = 0.5, \gamma = 0.0$ }. (b) with { $\alpha = 0.5, \beta = 0.0, \gamma = 0.5$ }.                 | 107      |

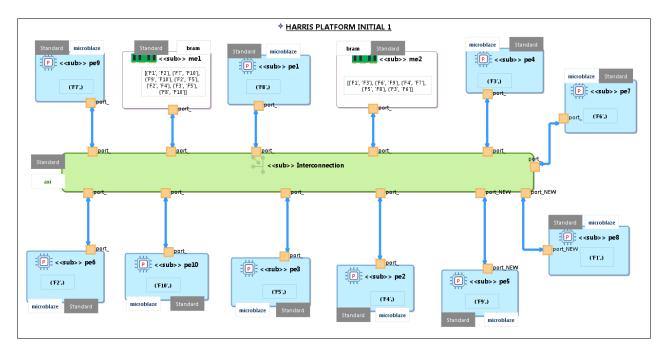

| 5.7   | initial solution in which each PE subsystem only performs one function, "INITIAL 1",                   | 110      |

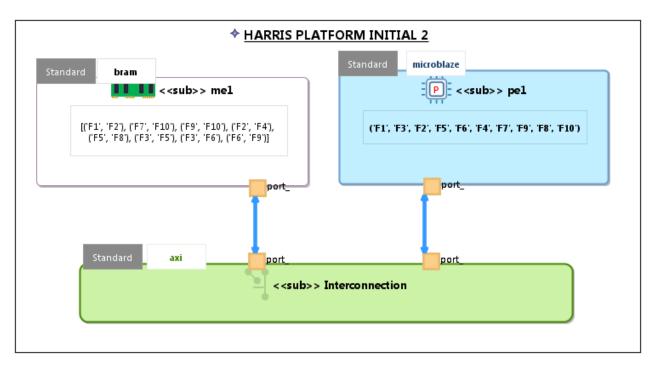

| 5.8   | initial solution in which all functions are mapped into a single processor, "INITIAL 2",               | 111      |

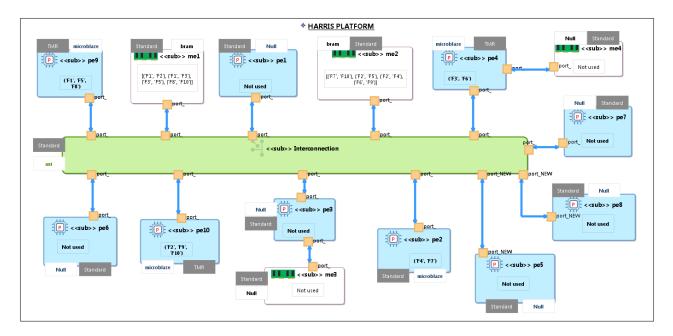

| 5.9   | good platform found with { $\alpha = 1.0, \beta = 0.0, \gamma = 0.0$ } by Simulated-Annealing (SA),    | 112      |

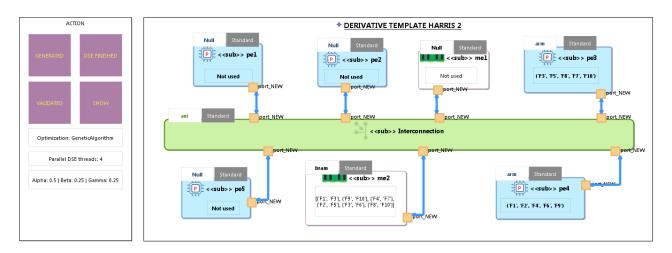

| 5.10  | good platform found with { $\alpha = 0.5, \beta = 0.25, \gamma = 0.25$ } by SA.                        | 113      |

| 5.11 platform template used in the DSE process with { $\alpha = 1.0, \beta = 0.0, \gamma = 0.0$ } by Genetic  |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| Algorithm (GA).                                                                                               | 113 |

| 5.12 platform template used in the DSE process with { $\alpha = 0.5, \beta = 0.25, \gamma = 0.25$ } by GA.    | 114 |

| 5.13 result found and shown on the DSE tool with $\{\alpha = 1.0, \beta = 0.0, \gamma = 0.0\}, \ldots \ldots$ | 114 |

| 5.14 result found and shown on the DSE tool with $\{\alpha = 0.5, \beta = 0.25, \gamma = 0.25\}, \ldots$      | 115 |

# List of Tables

| 1.1                                       | Targets for the probabilistic metric for random hardware failure [9]                                           | 25                                        |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| $2.1 \\ 2.2 \\ 2.3$                       | MDE studies for embedded system development                                                                    | 39<br>42                                  |

| 2.4                                       | tecture                                                                                                        | $\frac{44}{50}$                           |

| 3.1                                       | quality of service and properties specializations.                                                             | 55                                        |

| 4.1                                       | Description and notation of parameters and variables used in ILP formulation                                   | 74                                        |

| 4.2                                       | List of equations to calculate the execution time for each subsystem type depending fault tolerance strategy.  | 87                                        |

| 4.3                                       | List of equations used to calculate the cost of fault tolerance strategies of a subsystem $C_{\text{sub}_i}$ . | 94                                        |

| 5.1                                       | **                                                                                                             | 100                                       |

| 5.2                                       |                                                                                                                | 101                                       |

| 5.3                                       |                                                                                                                | 102                                       |

| 5.4                                       |                                                                                                                | 103                                       |

| $\begin{array}{c} 5.5 \\ 5.6 \end{array}$ |                                                                                                                | $\begin{array}{c} 104 \\ 105 \end{array}$ |

| 5.0<br>5.7                                |                                                                                                                | 105<br>105                                |

| 5.8                                       |                                                                                                                | 105                                       |

| 5.9                                       |                                                                                                                | 108                                       |

| 5.10                                      |                                                                                                                | 100                                       |

| 5.11                                      |                                                                                                                | 109                                       |

|                                           |                                                                                                                | 110                                       |

|                                           | reliability, execution time and cost of solutions found by DSE process with $\{\alpha = 1.0, \dots, \alpha\}$  |                                           |

|                                           |                                                                                                                | 115                                       |

| 5.14                                      | reliability, execution time and cost of solutions found by DSE process with $\{\alpha = 0.5, \dots, \alpha\}$  |                                           |

|                                           | $\beta = 0.25, \gamma = 0.25$ }                                                                                | 116                                       |

| 5.15                                      | improvement of the solution found by DSE process compared to the "naive" initial                               |                                           |

|                                           |                                                                                                                | 116                                       |

| 5.16                                      | improvement of the solution found by DSE process compared to the initial solutions                             |                                           |

|                                           | with $\{\alpha = 0.5, \beta = 0.25, \gamma = 0.25\}$ .                                                         | 116                                       |

# Acronyms

ACG Application Characteristic Graph. ADAG Annotated Directed Acyclic Graph. ASIC Application-Specific Integrated Circuit. **ASIL** Automotive Safety Integrity Level. CABA Cycle-Accurate Bit-Accurate. **CIM** Computational Independent Modes. COMM Communication. CS Comprehensive Search. DAG Directed Acyclic Graph. **DP** Dynamic Programming. **DPE** Dedicated PE. **DSDE** Domain Specific Development Engineering. **DSE** Design Space Exploration. **DVFS** Dynamic Voltage/Frequency Scaling. **EA** Evolutionary Algorithm. FIFO First In, First Out. FIT Failure In Time. FPGA Field Programmable Gate Array. GA Genetic Algorithm.

# GASPARD Graphical Array Specification for Parallel and Distributed Computing.GDSE Gradient-based Design Space Exploration.

GPP General Purpose Processor. GPPs General Purpose Processors. GUI Graphical User Interface. ILP Integer Linear Programming. **IP** Intellectual Property. **IP-cores** Intellectual Property cores. **ISPs** Instruction Set Processors. LUT Look-Up Table. **MBT** Model-Based Testing. MDA Model Driven Architecture. MDD Model-Driven Development. **MDE** Model Driven Engineering. MDSD Model-Driven Software Development. ME Memory. ModES Model-driven Embedded System. MOF Meta-Object Facility. MOST Multi-Objective System Tune.  $\mathbf{MPSoC} \hspace{0.1in} \text{Multi-Processor System-on-Chip.}$ MPSoCs Multi-Processor System-on-Chips. MTTF Mean Time To Failure. NoC Network on Chip. NSGA-II Non-dominated Sorting Genetic Algorithm-II. OCL Object Constraint Language. **OMG** Object Management Group. **PAM** Platform Application Model. **PE** Processing Element.

${\bf PEs}\,$  Processing Elements.

**PIM** Platform Independent Model. **PPE** Programmable PE. **PSM** Platform Specific Model. **RTL** Register Transfer Level. **SA** Simulated-Annealing. **SDF** Synchronous Dataflow. SDFG Synchronous Data-Flow Graph. **SER** Soft Error Rate. **SEUs** Single-Event Upsets. SIL Safety Integrity Level. SOFT Software. SUS System Under Study. SUT System Under Test. **TMR** Triple Modular Redundancy. **TPV** Timed Programmer's View. **TReR** Triple Re-execution Redundancy. **UML** Unified Modeling Language. wcet worst-case execution time. XMI XML Model Interchange.

**XML** Extensible Markup Language.

Acronyms

A cronyms

# Résumé

Dans le processus de conception d'un système MPSoC hétérogène (MPSoC : Multi Processor System on Chip), un large espace de solutions de conception émerge de différentes solutions alternatives. La fiabilité est la probabilité qu'un système ou un composant remplisse les fonctions requises sans défaillance dans les conditions spécifiées pendant une période donnée. Par conséquent, la fiabilité est devenue l'une des propriétés les plus importantes des systèmes embarqués. Outre les efforts visant à améliorer la fiabilité du matériel, il est nécessaire d'utiliser des stratégies de tolérance aux fautes afin de réduire l'impact des fautes au niveau du système. La tolérance aux fautes est la capacité d'une unité fonctionnelle à continuer à exécuter une fonction requise en présence de fautes ou d'erreurs. Il existe plusieurs stratégies de tolérance aux fautes développées dans la littérature comme redondance triple modulaire, checkpoiting, code de correction d'erreur. Par conséquent, les concepteurs ont besoin d'une méthodologie qui intègre l'évaluation de la fiabilité dans le processus d'exploration de l'espace de conception (DSE: Design Space Exploration). Notre objectif est d'établir un cadre permettant de trouver la meilleure solution pour une application donnée dans des contraintes de tolérance aux fautes. Cet objectif s'inscrit dans le contexte de la prise en compte de l'impact des stratégies de tolérance aux fautes (permanentes et transitoires) sur la fiabilité et le temps d'exécution du système et le coût de la plate-forme. De plus, le mapping des composants, le mapping des données et le mapping des fonctions sont des aspects importants qui affectent la fiabilité du système. Nos contributions et travaux en cours peuvent être résumés par les points suivants:

1) Nouveau méta-modèle intégrant la tolérance aux fautes pour les systèmes embarqués. Le métamodèle est au cœur de la méthode d'ingénierie dirigée par les modèles. Ceci propose de couvrir la tolérance de fautes; sert de pont entre les différents outils, entre les différents langages de programmation et les différentes étapes de conception, permettant ainsi aux concepteurs de disposer d'une vue cohérente et unifiée d'une plateforme MPSoC. Avec des modèles, les concepteurs peuvent configurer l'exploration en fonction de leur propre niveau d'expertise, tout en faisant abstraction de la complexité et des spécificités de l'architecture cible. Cela favorise la portabilité et la réutilisation des conceptions en fournissant des modèles tout en résumant les détails de bas niveau du système considéré.

2) La nouvelle méthode DSE comprend la génération, l'évaluation et l'optimisation d'espaces de conception de la tolérance aux fautes. Dans la spécification utilisateur, les dimensions explorées incluent le choix du matériel, le mapping des tâches, le mapping des données et le choix de la stratégie de tolérance aux fautes. Une nouvelle solution est générée et évaluée en matière de temps d'exécution, de coût et de niveau de fiabilité. Ensuite, un processus d'optimisation explore la meilleure solution parmi les espaces de conception.

3) Evaluation de la plate-forme MPSoC hétérogène sous l'impact des fautes transitoires et permanentes. Cette évaluation est une partie très importante de la DSE pour aider les concepteurs à choisir la stratégie de tolérance aux fautes appropriée en ce qui concerne un compromis avec les exigences de l'application. 4) Un nouvel outil avec une interface utilisateur graphique permet de modéliser et d'exécuter le processus DSE. Il simplifie le processus en interagissant avec l'utilisateur via l'interface graphique et en automatisant le processus d'exploration de l'espace de conception.

L'ingénierie dirigée par les modèles (MDE: Model Driven Engineering) peut fournir des moyens efficaces pour résoudre les besoins de la DSE. Un modèle représente une abstraction d'un système ainsi que des éléments de ce système d'un point de vue de la conception. Les mécanismes de construction de modèles valides sont spécifiés dans des méta-modèles. De nombreux travaux ont fourni des méta-modèles pour les structures et le comportement des plates-formes MPSoC. Cependant, ces méta-modèles sont conçus pour des objectifs spécifiques tels que les architectures avec paradigme d'exécution déclenché par le temps, l'estimation des performances ou la génération de codes pour la simulation ou à un niveau d'abstraction bas, ce qui les rend difficiles à réutiliser. Dans tous les cas, les méta-modèles présentés dans la littérature ne sont pas développés pour l'évaluation de la fiabilité. En outre, dans l'exploration de l'espace de conception, il y a de nombreux efforts de recherche qui combinent le mapping des composants, des fonctions ou des données avec l'évaluation de la fiabilité. Cependant, ces travaux considèrent souvent ces objectifs individuellement ou sont conçus pour des architectures spécifiques (processeurs homogènes ou uniquement).

Il existe de nombreuses études DSE basées sur la fiabilité. L'objectif commun est d'améliorer la fiabilité d'une plate-forme face aux exigences d'une application multifonction. Différentes approches à différents niveaux du système ont été étudiées. Ces études utilisent des modèles d'application et de plate-forme en tant qu'entrée de leur processus DSE, puis fournissent une solution optimale avec la cartographie. Plusieurs stratégies de tolérance aux fautes sont utilisées, telles que la réplication de ressources, la réplication de tâches, le point de contrôle, la réexécution. Différentes stratégies de recherche ont été utilisées (Recuit Simulé, Algorithme Génétique). Cependant, il reste des points dans le processus d'exploration qui n'ont pas été examinés ou considérés séparément, telles que l'impact des deux types de faute, l'impact de différents types de composants et l'impact de la tâche ou de la fonction et la cartographie des données sur la fiabilité globale.

Nous avons développé un nouveau méta-modèle de plateforme intégrant la tolérance aux fautes. Le méta-modèle est construit en utilisant la syntaxe UML. Un niveau de représentation intermédiaire est créé appelé "sous-système". Par le biais des "sous-systèmes", les parties de tolérance aux fautes sont connectées à la partie architecturale dans le méta-modèle. Dans la partie architecturale, une plateforme MPSoC hétérogène est composée de composants (matériels et logiciels) configurés pour fournir un ensemble de services (mémorisation, exécution, etc.). Un composant peut être une mémoire, un composant d'interconnexion ou un processeur. La plate-forme peut contenir plus d'un type de processeur ou d'unité de traitement (terme: hétérogène). La partie de la tolérance aux fautes déclare des stratégies de tolérance aux fautes comme la redondance de temps, la redondance de composants. Un sous-système est composé d'un type de composant matériel et éventuellement de plusieurs versions de composants logiciels. La description des sous-systèmes prend en charge la modélisation de la redondance utilisée dans les stratégies de tolérance. Sur une plate-forme, si des composants individuels sont observés séparément, il sera difficile d'évaluer la fiabilité d'une fonction et, par conséquent, il est difficile d'évaluer la fiabilité d'une plate-forme pour une application. En attendant, l'utilisation du concept de sous-système n'affecte pas l'unité de la plate-forme entière. Ainsi, le "sous-système" constitue non seulement le niveau intermédiaire entre le niveau de la plate-forme et celui des composants, mais également un pont entre un modèle de plate-forme et un modèle d'application. Évaluer une plate-forme sans tenir compte d'une application n'est pas utile, mais si le modèle de plate-forme et le modèle d'application sont trop étroitement liés, la capacité de réutilisation et l'extensibilité de la plate-forme ne sont que considérablement limitées dans la cadre de l'application. Le niveau de sous-système garantit à la fois la liaison du modèle de plate-forme avec le modèle d'application, mais également une indépendance par rapport au modèle de plate-forme, notamment en termes d'évaluation de la fiabilité.

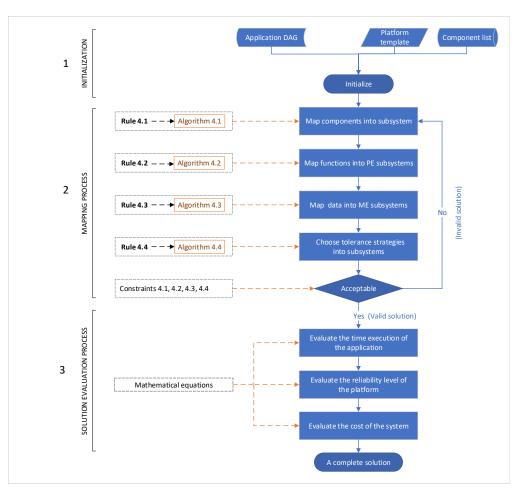

Les trois parties principales du flux DSE sont composées des processus d'initialisation, de mapping et d'évaluation de la solution. L'initialisation est l'étape de préparation d'un processus DSE. À cette étape, une application considérée, une plate-forme et les composants disponibles sont initialisés avec leurs paramètres. Les méta-modèles de plate-forme sont la base du processus DSE.

À partir des modèles d'entrée, un processus de mapping est effectué pour trouver une solution de mapping. Le problème peut être transformé en un problème de programmation linéaire entier. Le mapping comprend un ensemble de règles, des contraintes pour allouer des ressources et pour mapper les fonctions requises, des données sur les ressources. Une règle est un guide pour définir la relation entre les éléments (application, plate-forme) dans un système MPSoC, qui est stricte et impossible à modifier dans un cadre DSE spécifique. Une contrainte est une limitation pour une ou plusieurs fonctionnalités (quantité ou qualité) d'un système MPSoC qui peut être modifiée ou définie par les concepteurs dans un cadre DSE spécifique. Dans la deuxième étape (processus de mapping), il y a quatre règles: mapping de composant, mapping de fonction, mapping de données, choix des stratégies de la tolérance aux fautes. Ces règles sont implémentées sous forme d'algorithmes permettant de créer une conception dans la forme la plus élémentaire sans aucune contrainte. Ensuite, la conception est vérifiée sous contraintes. Les contraintes sont moins obligatoires que les règles et peuvent être modifiées et remplacées en fonction des objectifs des concepteurs, tels que la limitation des ressources, de la technologie et du temps. Dans nos travaux, il existe quatre contraintes: limitation de la capacité (de l'élément de traitement), limitation de la taille des données, limitation de la quantité et limitation du chemin de connexion entre les composants d'une plate-forme. S'il répond aux contraintes (solution valable), la solution passe à la troisième partie (processus d'évaluation de la solution); sinon (une solution non valide), nous devons revenir en arrière pour créer un autre design.

Ensuite, il est possible de passer par une série d'évaluations. Le processus d'évaluation permet aux concepteurs d'examiner la solution de manière quantitative, ce qui constitue la base du choix de la meilleure solution lors des prochaines étapes de la DSE. Il y a trois évaluations en matière de temps d'exécution, de fiabilité et de coût. Avec l'évaluation du temps d'exécution d'une application, tout d'abord, le temps d'exécution de chaque fonction est estimé. Ensuite, une stratégie de planification est appliquée à l'application et enfin, le temps d'exécution de l'application donnée est estimé. La fiabilité d'un système pendant une exécution est la probabilité qu'aucune défaillance ne survienne sur le résultat du système pendant toute la durée.

L'évaluation de la fiabilité est réalisée à partir d'un modèle de fautes permanentes et transitoires. Une faute est un événement qui cause un défaut dans le composant, tel qu'un bogue logiciel, un blocage, un circuit cassé. Une erreur fait référence à une différence entre la sortie réelle et la sortie attendue lorsqu'une opération requise est exécutée. Une défaillance apparaît lorsqu'un système ou un sous-système ne parvient pas à exécuter une fonction requise conformément à ses spécifications. Il y a deux catégories de la faute dérivées de ses conséquences pour des composants: permanente et transitoire. Les fautes permanentes découlent d'une destruction matérielle telle que le vieillissement, des circuits électroniques cassés ou bloqués. Une faute permanente reste active jusqu'à ce qu'une intervention de correction soit effectuée. Les fautes transitoires peuvent être causées par une seule particule ionisante frappant un nœud sensible ou une interconnexion d'un circuit. Contrairement aux fautes permanentes, une faute transitoire ne reste active que pendant une courte duration et disparaît à la prochaine duration de fonctionnement. Taux de défaillance (FIT : Failure In Time) est l'inverse du temps moyen de fonctionnement avant une défaillance. Cette valeur représente la possibilité d'une faute entraînant une défaillance lors de l'opération d'un composant. Ces paramètres reflètent les expériences existantes des processus d'injection, de simulation, de prévision des défauts et d'expérimentation sur les composants utilisés. Avec le taux de défaillance, nous avons utilisé des distributions de probabilité pour modéliser l'impact des fautes permanentes et transitoires sur le système. Dans cette thèse, deux stratégies de tolérance aux fautes sont considérées: Redondance Triple Modulaire (TMR), Redondance Triple Ré-exécutions (TReR). Sur la base du modèle de probabilité des fautes, nous proposons des équations mathématiques pour évaluer la fiabilité de chaque sous-système, puis la fiabilité globale d'une plate-forme.

Le coût d'une plate-forme est le coût total de tous les composants actifs utilisés dans cette plateforme. L'évaluation des coûts vise à assurer l'équilibre entre les ressources matérielles et les objectifs de performance et de fiabilité lors de la conception d'un système. Chaque composant a une valeur de coût.

Il y a trois critères de performance d'une solution de mapping: temps d'exécution, niveau de fiabilité et coût. L'objectif est de maximiser le niveau de fiabilité (maximum = 1), de minimiser les coûts et de minimiser le temps d'exécution. Fondamentalement, avec l'optimisation d'un problème multi-objectifs, une formule est configurée pour comparer deux solutions basées sur la méthode de métriques pondérée. Une fonction mathématique objectif est proposée et elle permet d'évaluer simultanément trois sous-objectifs d'une solution de mapping. La stratégie la plus classique de l'optimisation est la recherche exhaustive (CS: Comprehensive Search). Trois stratégies de recherche telles que la recherche complète, le recuit simulé et l'algorithme génétique consistent à trouver la meilleure solution parmi l'espace de conception possible. Nous allons calculer à partir de la première solution jusqu'à la solution finale, sans manquer aucune solution possible dans l'espace de conception. Le recuit simulé est un algorithme d'optimisation basé sur la simulation d'un processus de refroidissement du métal, du verre ou du cristal. L'algorithme génétique est basé sur le paradigme néo-darwinien de simulation de l'évolution naturelle des systèmes biologiques.

Deux cas d'étude sont présentés, le filtre Sobel et le détecteur de coin Harris. Le filtre Sobel est une application simple et très répandue qui permet de détecter les contours des images. De plus, le détecteur de coin Harris est utilisé dans le traitement d'image pour extraire les coins d'une image, qui s'appuie sur le filtre Sobel. Le détecteur de coin Harris contient plus de fonctions que le filtre Sobel et est appliqué pour augmenter la complexité des études de cas pour notre framework. Les résultats expérimentaux ont montré que le cadre DSE permet une exploration efficace d'un grand espace de conception et des résultats proches ou équivalents d'une approche de la recherche complète. De plus, la fiabilité des solutions trouvées est supérieure à celle des solutions construites sans notre Framework.

Les modèles construits par notre framework sont basés sur le méta-modèle proposé. L'outil est construit sur l'environnement Sirius avec l'espace de travail appelé PolarSys, qui est un projet Eclipse. Il simplifie le processus en interagissant avec l'utilisateur via l'interface graphique et en automatisant le processus d'exploration de l'espace de conception.

# Chapter 1

# Introduction

## Contents

| 1.1 Em  | bedded system                    |  |

|---------|----------------------------------|--|

| 1.2 Fau | lt model                         |  |

| 1.3 Tol | erance strategies                |  |

| 1.3.1   | Spatial redundancy               |  |

| 1.3.2   | Temporal redundancy              |  |

| 1.3.3   | Check-pointing                   |  |

| 1.3.4   | Error correction code            |  |

| 1.4 Pro | blem statement and contributions |  |

#### 1.1 Embedded system

Nowadays, embedded systems become a integral part of most domains such as vehicle, airplane, industrial machines. An embedded system is composed of two parts: an embedded application and a platform. **Embedded applications** can take many forms as signal processing, distributed control system, etc. An application is composed of multi functions/tasks. The complexity of an application is increasing with different requirements such as performance, power consumption, cost, and reliability. Any application need to be executed on hardware and software components. This set of components is called a platform.

#### Embedded applications

The DAG is very widely used in the DSE literature to describe an application with functions or tasks. It describes effectively the characteristics of applications and is easy to use for modeling, mapping objectives as well as programming [1]. Therefore, we introduce the following concept to describe an application (Definition 1.1) used in this thesis:

**Definition 1.1.** An application G is represented by a DAG G = (V, E, D), where: each node in  $V = \{F_1, F_2, ..., F_k | k \in \mathbb{N}\}$  represents a function of G; E is the set of directed arcs that represent precedence constraints and connect the functions with each other as well as indicate their data dependencies;  $D = \{d_{1,2}, d_{1,3}, ..., d_{j,k} | j, k \in \mathbb{N}\}$  specifies the amount of communicated data associated to each link.  $d_{j,k}$  represents the data block which is sent from  $F_j$  to  $F_k$ . These functions have to be executed in a given order to produce desired outputs from the input functions to the output ones. An input function is a function where no arc goes in and an output function is a function where no arc goes out. A **period** is an execution duration from the earliest start time of input functions to the latest ending time of output functions that gives expected results in the output functions. An application can be executed iteratively through many periods.

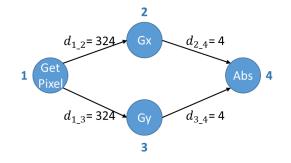

Figure 1.1 illustrates an example of an application with four functions and only four data blocks between these functions. In this application, there is one input function  $(F_1)$  and one output function  $(F_4)$ . The pre-defined size corresponds to a number of operations of each function. The number of operations is obtained from the algorithm of the application. An operation can be an addition (+), a subtraction (-), a multiplication  $(\times)$ , a division  $(\div)$ , or an assignment (=). Besides, the data size is also predefined in the 2 rightmost columns. The data is the variables shared between 2 functions.

| $d_{1,3}$ F3 $d_{3,4}$ |          |                          |           |               |

|------------------------|----------|--------------------------|-----------|---------------|

| (F1) (F2) $d_{2,4}$    | Function | <b>size</b> (operations) | Data      | size (MBytes) |

|                        | $F_1$    | $80 \times 10^3$         | $d_{1 2}$ | 2             |

|                        | $F_2$    | $250 \times 10^3$        | $d_1_3$   | 1             |

|                        | $F_3$    | $32 \times 10^3$         | $d_{2_4}$ | 3             |

|                        | $F_4$    | $192 \times 10^3$        | $d_{3_5}$ | 1             |

Figure 1.1: An example of target application with 4 functions and their properties.

#### Heterogeneous MPSoC platforms

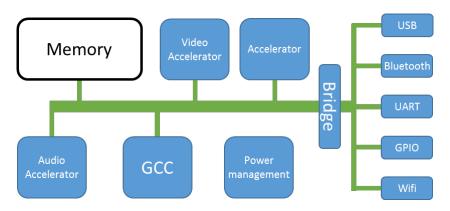

A heterogeneous/homogeneous MPSoC (Multi-Processor System-on-Chip) is a system in which all components as processing units, memories, buses are put on a same chip. The term "homogeneous" means that all processing elements are identical and interconnected through a dedicated communication infrastructure. Meanwhile, the term "heterogeneous" means that there are different types of processing elements, such as general purpose processors, digital processors, accelerators, that are interconnected through a communication infrastructure as shown on Figure 1.2. The homogeneous architectures are commonly used for certain architectures such as servers, desktop computers, video game consoles. The heterogeneous Multi-Processor System-on-Chips (MPSoCs) are used for embedded systems as they use heterogeneity for optimisation purpose [2, 3].

Increasing the complexity of applications and platforms makes many potential solutions appearing, especially for **heterogeneous** systems, because the different properties of components can make more difficult to designers to choose an optimal solution. In that context, exploration of the design space and optimization of design solutions are practical needs.

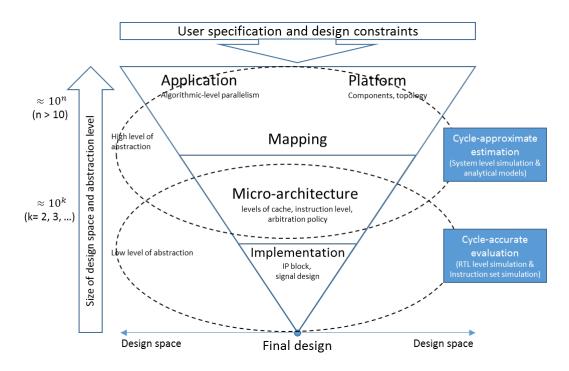

The exploration process evaluates design points in a design space and gives a set of best solutions in terms of execution time of an application, reliability of a platform, cost of a system, energy under design constraints. At different levels of abstraction, the exploration strategies corresponds to different accuracy levels (Figure 1.3). An accuracy approach is often used at a low level and the system-level architecture features are fully defined. At this level, designers can use precise simulators (instruction, Register Transfer Level (RTL) levels) or implement prototypes to accurately evaluate a solution. The exact approach is suitable for exhaustive exploration when a several design points are already characterized. However, design spaces are often large (>  $10^{10}$  design points - a point represents a design solution) and the exhaustive exploration is impossible. Moreover, the exploration in low level also takes a lot of time to evaluate a solution. If there has not been an optimal process and evaluation on the whole design space before, it is likely that designers are wasting time evaluating solutions that are not good.

Meanwhile, the higher the abstraction level (cycle-approximate estimation) is, more design solutions can be explored, and more design alternatives can be chosen to satisfy design constraints or achieve a better performance. The higher abstraction level often takes place at the system level. The DSE (Design Space Exploration) focuses on the the application and platform models. If the application model is given and fixed, the exploration process is mainly on the platform building process and mapping process. The platform building defines the resource allocation, the interconnection, etc. The

Figure 1.2: Overview of a heterogeneous MPSoC.

#### 1.1. EMBEDDED SYSTEM

Figure 1.3: Abstraction levels of design space exploration [4].

mapping process defines the function/task allocation. After these processes, designers can find several solutions and they can bring them into the next design steps at a lower abstraction level to evaluate them pore accurately. Definitions 1.2, 1.3, 1.4 describe concepts of an MPSoC platform.

**Definition 1.2.** A heterogeneous MPSoC platform is composed of (hardware and software) components configured to provide a set of services (memorization, execution, etc.). The platform contains more than one type of processor or processing unit (term: *heterogeneous*). The connections between components form the platform topology.

**Definition 1.3.** A hardware component can be:

- a PE (Processing Element) that can be hardwired (such as an IP, an Application-Specific Integrated Circuit (ASIC)), thus called a Dedicated PE (DPE) (no software can be executed on it) or a general purpose processor (it can execute software as a hard-core or a soft-core), called a Programmable PE (PPE). PE components are used to execute functions of a given application;

- a Memory (ME) component used to store data and source codes;

- a Communication (COMM) component used to transfer data, signals between others hardware components.

Each component provides at least one service to implement requirements of a given function. A service is a component-specific capability. A service is represented by metrics such as delay, cost, computing capacity and will be discussed in more details in the next Section.

**Definition 1.4.** A Software (SOFT) component is a software implementation of a function. Its source code is stored in a memory and a SOFT component runs on top of a PPE [5].

| ASIL | Random hardware failure rate values |

|------|-------------------------------------|

| D    | $< 10^{-8}$ per hour                |

| С    | $< 10^{-7}$ per hour                |

| В    | $< 10^{-7}$ per hour                |

| Α    | $< 10^{-6}$ per hour                |

Table 1.1: Targets for the probabilistic metric for random hardware failure [9].

#### Reliability and system safety

In the process of exploration, a special concern can be the fault tolerance to ensure system safety. Fault tolerance of a system can be assessed through its reliability level in the range from 0% to 100%. Higher is better. The analysis of the predictive reliability of the electronic components is studied and standardized in FIDES [6] and MIL-HDBK-217 [7].

However, the comprehensive evaluation of reliability of an embedded system requires the oversight of all behaviors of the system such as the time to perform functions/tasks, the time of receiving/sending data, the interconnection time, etc. Besides, many designers want to use fault-tolerance strategies in their design. Assessing reliability needs them to consider the impact of these strategies on the system performance and cost. And, the DSE process also need to explore solutions with different fault-tolerance strategies.

Reliability and the safety are not the same, but the probabilistic risk for a random failure has created a relationship between these two aspects [8]. For example, Table 1.1 shows the failure rate used in the quantitative safety assessment in the safety standard ISO26262. ISO26262 is a safety standard released in November 2011 to measure and document the safety level of automotive electronic systems [9]. A designer can use this standard to build their system as a constraint. Each safety goal is given as Automotive Safety Integrity Level (ASIL) that determines what ISO 26262 safety requirements that apply to the goal.

The evaluation and optimization of reliability of a heterogeneous MPSoC also need to be relevant in relation to other needs of the system such as processing time, system construction costs, energy etc.

Thus, in this whole context, designer will have to solve the problems for embedded systems such as: modeling the heterogeneous MPSoC architecture, exploring mapping solutions, exploring fault-tolerant strategies, evaluating system and eventually finding optimal solutions.

### 1.2 Fault model

In order to tolerate faults, we need to understand the object that we need to resist: that is the fault consequence, fault kind, and fault model.

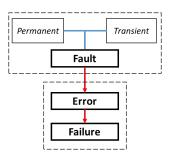

A **fault** is an event that causes a defect within the component such as a software bug, a bit stuck, a broken circuit, etc. An **error** refers to a difference between the actual output and the expected output when a required operation is executed. A **failure** appears when a system or a subsystem fails to perform a required function according to its specification. The relation between fault, error, and failure is depicted in Figure 1.4. A fault may lead to an error, and an error might cause a failure in the whole system or a subsystem, or a component [10] [11]. A goal of safety-critical systems is that errors should not lead to any failure. More generally, designers expect that the system should not have a fault that results in failure.

A fault can be divided into two categories derived from its consequences for components: permanent and transient. Permanent faults are derived from a hardware destruction such as aging, broken

Figure 1.4: Relation between fault, error and failure.

electronic circuits, stuck-at-bit [10]. A permanent fault remains active until there is an intervention for correction. Transient faults can be caused by a single ionizing particle striking a sensitive node or an interconnection of a circuit [10]. Unlike permanent faults, a transient fault only remains active in a short period and disappears on the next operating period. For example in Figure 1.5, a transient fault appears in the execution duration of  $F_2$  but it disappears in the execution duration of  $F_3$ . As consequences of faults, the effects of errors and failures on the component are also either temporary or permanent.

The failure rate is often expressed in Failure In Time (FIT), which is the number of failures that can be expected in one  $10^9$  device-hours of operation. This value represents the possibility of a fault causing a failure during the operation of a component. The failure-rate evaluation of transient and permanent faults in every single component is not trivial. These parameters reflect the existing experiences from complex and time-consuming processes of injection, simulation, prediction of faults, and experiment on components [12, 13, 14, 15, 16]. This work uses the failure rates as the inputs of the design exploration in order to evaluate the reliability of components. The reliability is the probability that the component or system will not cause a failure for a specified time under specific conditions.

**Permanent fault** There are four main wear-out effects for integrated circuit components: electromigration, time-dependent dielectric breakdown, stress migration, and thermal cycling [17]. For this work, electromigration related wear-out failures are assumed, however, any other effects can be included either standalone or using sum-of-failure-rate model for any combination of the above failure effects. We use a Weibull distribution to describe the wear-out effects, Equation 1.1 gives the evaluation of the probability that permanent faults cannot cause any failure on the component during the interval between 0 and the time moment  $\tau$ , where alpha(T) is the scale parameter, that is a function of temperature depending to the wear-out failure model,  $\beta$  is the slope parameter shown to be nearly independent of temperature [18].

$$R_{\rm PF}(\tau) = e^{-\left(\frac{\tau}{\alpha(T)}\right)^{\beta}} \tag{1.1}$$

Figure 1.5: A transient fault appears and disappears on a PE component.

To model the useful life of the product, we choose  $\beta = 1$  as in [19]. So, in that case, Equation 1.1 becomes Equation 1.2:

$$R_{\rm PF}(\tau) = e^{-\frac{\tau}{\alpha(T)}} \tag{1.2}$$

We have Equation 1.3, where  $\lambda_{\text{comp}_{PF}} = \frac{1}{\alpha(T)} = \frac{1}{MTTF}$  is the failure rate of the component caused by permanent faults, MTTF is Mean Time To Failure, as following:

$$R_{\rm PF}(\tau) = e^{-\lambda_{\rm comp}_{TF}.\tau} \tag{1.3}$$

For example, 1 component has a lifetime of 10 years, so it means that the average time for a permanent error to appear is 10 years (MTTF = 10 years). So,  $\lambda_{\text{comp}_{PF}} = \frac{1}{\alpha(T)} = \frac{1}{MTTF} = \frac{1}{10 \times 365 \times 24}$  failure/hour  $= \frac{10^9}{10 \times 365 \times 24}$  failure/(10<sup>9</sup> hours) = 11415 FIT.

**Transient fault** Assuming the failure from transient faults arrival on a component follows Poisson distribution [20], Equation 1.4 gives the evaluation of the probability that transient faults cannot cause any failure on the component during the interval between 0 and the time moment  $\tau$ , where  $\lambda_{\text{comp}_{TF}}$  is the failure rate of the component caused by transient faults.

$$R_{\rm TF}(\tau) = e^{-\lambda_{\rm comp}_{TF} \cdot \tau} \tag{1.4}$$

Given that the events of the permanent faults and the transient faults are independent, we have the reliability of a component during the interval between 0 and the time moment  $\tau$  as Equation 1.5, where  $R_{\rm PF}(\tau)$  and  $R_{\rm TF}(\tau)$  is the reliability considering the permanent fault and the transient fault, respectively.

$$R_{\rm comp}(\tau) = R_{\rm PF}(\tau) \times R_{\rm TF}(\tau) \tag{1.5}$$

#### **1.3** Tolerance strategies

There are several fault-tolerance strategies developed in the literature [10]. Herein, we describe the strategies that are popular and effective strategies.

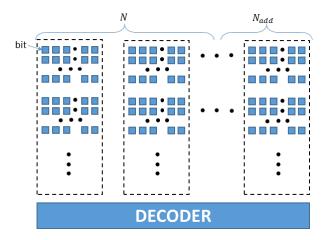

#### 1.3.1 Spatial redundancy

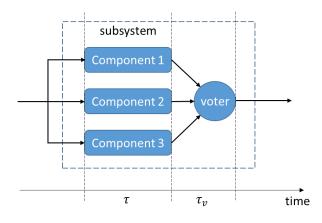

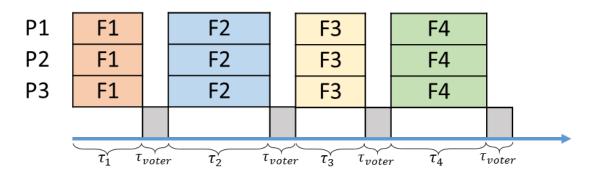

The k-out-of-n (also known as N-modular redundancy) is one of the most popular strategies of the passive redundancy [10]. The passive redundancy strategies have no need to detect faults but mask them. With the spatial redundancy, designers use multiple hardware components in the same subsystem. The components are multiplied to perform the same computation in parallel. The majority voting is used to determine the correct output from these components, except for N < 3.

Figure 1.6 gives the concept of a popular instance of the spatial k-out-of-n with k = 2 and n = 3. In the TMR subsystem, if one of the components fails, the voter masks the fault by comparing the outputs among the faulty module and the remaining two fault-free modules. In addition to the time that the component implements the function  $(\tau)$ , the system has to take into account the time that the voter handles the outputs  $(\tau_v)$ . Depending on the purpose, the redundant components can be processors, memories, buses, network connections, etc. This strategy can mask both permanent and transient faults. However, it requires high overheads in terms of area, price, energy, etc.

Figure 1.6: An instance of spatial redundancy: TMR (Triple Modular Redundancy).

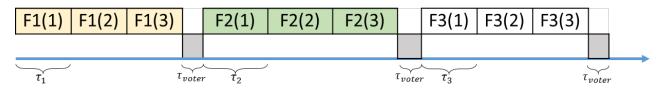

#### 1.3.2 Temporal redundancy

If the size, weight, power consumption and cost of a system is a big constraint, designers can use extra time rather than extra hardware to tolerate faults. The temporal redundancy includes the repetition of the computation between two or more times and compares the results with the previous computations [10]. This repetition is usually performed on only one hardware component.

The Figure 1.7 describes the TReR strategy as an instance of the temporal redundancy. The execution time in this concept is 3 times longer than the no-redundancy. It assumes that the function  $F_1$  is mapped to the subsystem, at each computing cycle, this subsystem executes  $F_1$  three times. If a permanent fault occurs and causes an error on this component, all the computations on this component are faulty and the resultant output is wrong. Therefore, this strategy can not mask permanent faults. However, if a transient fault occurs in one of three occurs and disappears in the remaining two times, this strategy can produce the correct output. A TReR subsystem can mask only one transient fault among 3 executions. The temporal redundancy is suitable for processors.

#### 1.3.3 Check-pointing

The check-pointing technique is a recovery mechanism that is based on check-points and restart mechanisms [10, 21]. Most software faults are design faults that resemble hardware intermittent faults: they appear in a period and disappear, then appear again. Hence, simply restarting the subsystem is usually sufficient to successfully complete its execution, it also masks transient faults or software bugs.

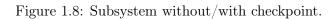

Figure 1.9: Memory with correction code.

The Figure 1.8 describes the concept of this strategy. In a normal period, the subsystem that is composed of a component executes a mapped function without checkpoints during  $\tau$  - the total execution time of the mapped function on the subsystem. If designers apply the strategy with Ncheckpoints, checkpoints are created between N points during the execution.  $T_c$  is the execution time of the function in each check-point,  $T_c = \frac{\tau}{N+1}$ . At each checkpoint, the subsystem saves the current state.  $\tau_o$  is the time for checkpoint capture and storage. If a fault is detected, the subsystem returns to the last checkpoint state and resumes the execution. The time for recovery from a checkpoint is  $\tau_r$ . Fault-detection checks need to be embedded in the code and executed before the checkpoints are saved. This strategy is usually applied to processors by the ability to save theirs states, and rebooting can be easily done through programming in the code.

#### 1.3.4 Error correction code

The code correction is a famous technique to tolerate faults for the memory [22]. The main idea is that some redundant bits are used to detect whether errors in the bits are stored in the memory and/or correct the errors.

Figure 1.9 shows a typical model of a memory with correction code. A data word stored in the memory owns initially N bits. Depending on the error correction requirements (capacity), there are

$N_{add}$  encode bits to be added to data words. A single error can appear in any bit on  $N + N_{add}$  bits. In order to correct at least one error in a data word, the number of additional bits must satisfy the inequality  $N + N_{add} + 1 < 2^{N_{add}}$ .

#### 1.4 Problem statement and contributions

In this thesis, we present a framework that explores the design space of embedded systems that incorporates fault-tolerance strategies. The main contributions are:

- 1. New meta-model integrating the fault tolerance for embedded systems. The meta-model is the core of the Model-Driven Engineering method. This proposes to cover the fault tolerance; serves as a bridge between the different tools, between different programming languages, and different design stages, allowing designers to have a unified and coherent view of an MPSoC platform. With the model, designers can configure the exploration according to their own level of expertise, while also abstracting the complex and the specifics of the target architecture. This favors design portability and reuse by providing models while abstracting low-level details of the considered system.

- 2. New DSE method is composed of fault-tolerance design space generation, evaluation and optimization. From the user specification, explored dimensions include hardware choice, task mapping, data mapping, and fault-tolerance-strategy choice. A new solution is generated and evaluated in terms of execution time, cost and, reliability level. Then, an optimization process will explore the best solution among the design space.

- 3. Evaluation of heterogeneous MPSoC platform under the impact of transient and permanent faults. This evaluation is a very important part of the DSE to help designers choosing the appropriate strategy fault tolerance in regard to a compromise with the requirements of the application.

- 4. New tool with a graphical user interface allows to model and run the DSE process. It simplifies the process by interacting with the user through the graphical interface and automating the process of exploring design space.

The remains of this manuscript is as follows:

- Chapter 2 gives an overview of the state-of-the-art, classification of existing approaches of Model-Driven Engineering and Design Space Exploration;

- Chapter 3 introduces the meta-model of the MPSoC platform integrating the fault-tolerance and the modeling tool with graphical user interface;

- Chapter 4 introduces our DSE algorithms;

- Chapter 5 presents the evaluation and validation of the method through the use of three casestudies;

- Chapter 6 concludes this thesis by summarizing its contributions and providing perspectives and future work.

## Chapter 2

# Literature reviews

Abstract: In the previous chapter, we introduce the context of MPSoCs. Design space exploration must meet the needs for fault tolerance of embedded applications. In addition, modeling of high-level system components helps reuse existing modules and can reveal many potential solutions. Therefore, in this chapter, we present the works that are related to the same context. In order to clarify the high-level model-based designs, we review existing MDE (Model Driven Engineering) studies for the MPSoCs as well as platform meta-models in the first Section. Next, we will have a deeper look into different approaches of the DSE (Design Space Exploration). It should be noted that in this section we will devote most of the time to analyzing the DSE studies related to the use of fault tolerance or the reliability-awareness.

#### Contents

| <b>2.1</b> | Mod   | lel driven engineering                            |

|------------|-------|---------------------------------------------------|

|            | 2.1.1 | Model-Based Testing                               |

|            | 2.1.2 | Model-driven development                          |

| <b>2.2</b> | Stat  | ic and dynamic exploration                        |

|            | 2.2.1 | Design-time exploration                           |

|            | 2.2.2 | Run-time exploration                              |

|            | 2.2.3 | Fault-tolerance and reliability-based exploration |

|            | 2.2.4 | Analysis                                          |

| 2.3        | Sum   | mary                                              |

#### 2.1 Model driven engineering

MDE (Model-Driven Engineering) addresses the application and platform complexity and expresses domain concepts effectively to alleviate this complexity.

A model is a structure that represents a design artifact as a relation schema, an interface definition, a domain specific language (such as Extensible Markup Language (XML), Unified Modeling Language (UML)) or a hypermedia document) [23]. In [24], George E. P. Box wrote: "All models are wrong but some are useful". A model is not the considered entity and does not carry all characteristics of an entity. Designers just choose which properties of an entity are important and put them into their models to reduce the complexity of the interest entities (herein such as application, platform, and components). Each model has to conform to a meta-model. A meta-model describes the various types of model elements and how they are connected, arranged and constrained.

Figure 2.1 describes the relationship between the systems, models and technical space. A technical space [25] is an environment with associated concepts, tools, required skills based on some algebraic structures (tree, graphs, categories, etc.). Each technical space is based on a meta-meta-model and a set of meta-models. Several companies and organizations (Object Management Group (OMG), IBM, and Microsoft) are proposing several environments to support MDE.

For instance, OMG proposed Model Driven Architecture (MDA) as one of vision of MDE with a set of OMG standards like Meta-Object Facility (MOF), XML Model Interchange (XMI), Object Constraint Language (OCL), UML, etc [27]. In OMG MDA, the MOF and the collections of standard meta-models and UML profiles play the role of a technical space.

A meta-model is the core of an MDE methodology. As such, there are many supports for the model/meta-model building. The demand is to have a mechanism for the construction of valid models *i.e.* the meta-model needs to be defined in a suitable way and abstraction level to be easily reused, maintained and operated.

Figure 2.2 describes the classification of MDE. We classify according to the general purpose of applying MDE according to literature studies [27, 28, 29]. However, this classification is not really clear due to the overlap between the classes. But this classification makes it easier to see the MDE application in the literature.

Accordingly, MDE is classified into two main categories: Model-Based Testing (MBT) and Model-

Figure 2.1: System, models and technical space [26].

Figure 2.2: MDE classification.

Driven Development (MDD). In MDD, two classes were identified. One is called Model-Driven Software Development (MDSD) and the other is Domain Specific Development Engineering (DSDE). After that, the MDE methodologies can serve different purposes such as design exploration, simulation, code generation.

#### 2.1.1 Model-Based Testing

MBT (Model-Based Testing) is a technique for automatic generation of test cases using models [30]. MBT is defined as the automation of the design of black-box tests. Testing models are used to represent the considered domain for the test input data, the desired behavior, testing strategies, and the testing environment of the System Under Test (SUT). A testing model is usually an abstract, partial representation of the desired behavior of the SUT. These models capture some of the requirements. Then model-based testing tools are used to automatically generate test-cases from that model. Test cases are functional tests and might then be mapped into executable tests that can communicate directly with the SUT by the specific testing tools and frameworks.

As such, we can see that MBT is an interesting area of MDE but not in the goal we are aiming at in the context of this thesis. Therefore, we will not continue to discuss this issue.

#### 2.1.2 Model-driven development