# Management of Dynamic Reconfiguration in a Wireless Digital Communication Context

Mohamad-Al-Fadl Rihani

#### ▶ To cite this version:

Mohamad-Al-Fadl Rihani. Management of Dynamic Reconfiguration in a Wireless Digital Communication Context. Computers and Society [cs.CY]. INSA de Rennes, 2018. English. NNT: 2018ISAR0030. tel-02079257v2

# $\begin{array}{c} {\rm HAL~Id:~tel-02079257} \\ {\rm https://hal.science/tel-02079257v2} \end{array}$

Submitted on 14 May 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

# L'INSTITUT NATIONAL DES SCIENCES APPLIQUEES RENNES

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N°601

Mathématiques et Sciences et Technologies de l'Information et de la Communication

Spécialité: Télécommunications

Par

## « Mohamad-Al-Fadl Rihani »

« Management of Dynamic Reconfiguration in a Wireless Digital Communication Context»

Thèse présentée et soutenue à « INSA Rennes », le « 18 Decembre 2018 »

Unité de recherche : IETR Thèse N° : 18ISAR 38 / D18 - 38

#### Rapporteurs avant soutenance:

**EI-Bay BOURENNANE** Professeur, Université de Bourgogne, Dijon

Olivier ROMAIN Professeur, ENSEA, Université de Cergy-Pontoise

#### **Composition du Jury:**

**Président:** Bertrand GRANADO Professeur, UPMC, Paris

Rapporteur1: El-Bay BOURENNANE Professeur, Université de Bourgogne, Dijon

Rapporteur2: Olivier ROMAIN Professeur, ENSEA, Université de Cergy-Pontoise

#### **Ali CHEHAB**

Professeur, Université Américaine, AUB, Liban

**Mohamad MROUE**

Professeur Associé, Université Libanaise, Faculté de Génie, Liban

Jean-Christophe PREVOTET

Maître de Conférence, INSA, Rennes

Yasser MOHANNA

Professeur, Université Libanaise, Faculté des Sciences, Liban

Co-directeur de thèse

**Fabienne NOUVEL**

Maître de Conférence, HDR, INSA, Rennes

Directrice de thèse

#### Intitulé de la thèse :

# Management of Dynamic Reconfiguration in a Wireless Digital Communication Context

**Mohamad-Al-Fadl RIHANI**

#### En partenariat avec :

Document protégé par les droits d'auteur

# Acknowledgments

First, I would like to thank God, whom blessed and gave me the strength to be what I am today.

I wish to express my sincere gratitude to the persons who helped to make my PhD year's a valuable experience and a pleasing journey that I will never forget.

I am truly grateful to my thesis supervisors, Dr. Fabeinne Nouvel, and Dr. Jean-Christophe Prevotet at INSA Rennes, and for Prof. Yasser Mohanna, and Dr. Mohamad Mroue at the Lebanese University at Beirut for all their help and guidance throughout my PhD.

I would like also to thank the Lebanese University and Metro-pole Rennes for providing finical aid during the PhD.

It is also my pleasure to express my sincere thanks to the committee members, Prof. Bertrand GRANADO, Prof. EL-BAY BOURENNANE, Prof. Olivier ROMAIN and Prof. Ali CHEHAB, for reading and evaluating my manuscript.

Besides, I would like to thank the staff members in IETR, for providing a friendly working environment and facilities to complete this thesis. I also wish to express my gratitude to the officials and other staff members who rendered their help during the period of my thesis work.

My thanks also go to all my colleagues and friends at IETR, who encouraged and helped me during my stay at Rennes.

My sincere feelings of gratitude to my family, my parents, my brothers, and my sisters for their support and valuable prayers.

Finally, I thank my beloved wife, Zahraa, for her love, patience, and encouragement throughout my life.

# Abstract

Today, wireless devices generally feature multiple radio access technologies (LTE, WiFi, WiMax, ...) to handle a rich variety of standards or technologies. These devices should be intelligent and autonomous enough in order to either reach a given level of performance or automatically select the best available wireless technology according to standards availability. On the hardware side, System on Chip (SoC) devices integrate processors and FPGA logic fabrics on the same chip with fast inter-connection. This allows designing Software/Hardware systems and implementing new techniques and methodologies that greatly improve the performance of communication systems. In these devices, Dynamic Partial Reconfiguration (DPR) constitutes a well-known technique for reconfiguring only a specific area within the FPGA while other parts continue to operate independently. To evaluate when it is advantageous to perform DPR, adaptive techniques have been proposed. They consist in reconfiguring parts of the system automatically according to specific parameters. In this thesis, an intelligent wireless communication system aiming at implementing an adaptive OFDM based transmitter and performing a vertical handover in heterogeneous networks is presented. An unified physical layer for WiFi-WiMax networks is also proposed. An intelligent Vertical Handover Algorithm (VHA) based on Neural Networks (NN) was proposed to select best available wireless standard in heterogeneous network. The system was implemented and tested on a ZedBoard which features a Xilinx Zynq-7000-SoC. The performance of the system is described and simulation results are presented in order to validate the proposed architecture. Real time power measurements have been applied to compute the overhead power for the PR operation. In addition demonstrations have been performed to test and validate the implemented system.

# Résumé de la Thèse

Un système de communication sans fil est défini comme la transmission et la réception de signaux par des systèmes électromagnétiques. Il a été initialement utilisé vers 1890 en télégraphie sans fil. De nos jours, les systèmes de communication sans fil sont partout.

Le canal sans fil constitue un canal de communication des plus difficiles. Comme le canal sans fil est considéré comme variant dans le temps, il semble intéressant de disposer d'un système sans fil reconfigurable au noeud d'extrémité, comprenant certains modules de la chaîne de communication pouvant être reconfigurés pour optimiser l'utilisation de la capacité de canal disponible. Aujourd'hui encore, les utilisateurs font face à une très grande diversité de réseaux et de protocoles de communication généralement très complexes et hétérogènes. Dans ce contexte, il semble évident que nous pourrions bénéficier de l'utilisation de systèmes sans fil reconfigurables. Les questions qui sont ouvertes : comment et quand les radios reconfigurables devraient-elles être reconfigurées? Comment décider quelle standard est le plus adapté et décider dde l'utiliser pour la communication?

Afin de décider quand et quoi reconfigurer dans la chaîne de communication, des techniques adaptatives ont été proposées pour permettre d'appliquer des modifications en temps réel aux couches PHY et/ou MAC d'un système sans fil. Des algorithmes "d'hand-over" vertical (VHA) ont été proposés pour permettre de sélectionner le meilleur système de communication sans fil disponible sur le noeud final. Par ailleurs, les algorithmes d'apprentissage automatique sont une des techniques prometteuses utilisées dans ces VHA pour fournir plus d'intelligence au dispositif de noeud final. Lorsqu'une décision est prise, le système devra exécuter et reconfigurer la chaîne de communication. Parmi les solutions matérielles, les réseaux FPGA (Field Programmable Gate Arrays) constituent des circuits efficaces pour mettre en oeuvre de tels systèmes reconfigurables. Ces dispositifs sont maintenant suffisamment mûrs pour implémenter des systèmes très complexes avec un haut niveau de performance. La reconfiguration partielle (PR) est l'une des fonc-

vi Résumé de la Thèse

tionnalités intéressantes qui ont été ajoutées par les fournisseurs de FPGA pour assurer encore plus de flexibilité. La PR fournit la possibilité de reconfigurer un module spécifique sur le FPGA pendant l'exécution, sans perturber le fonctionnement des autres blocs statiques.

Une autre caractéristique intéressante dans les récents dispositifs basés sur les FPGA est la présence de coeurs de processeurs embarqués qui sont implémentés avec la structure FPGA matérielle, dans la même puce (SoC). Les périphériques SoC sont appropriés pour la conception de systèmes logiciels et matériels (SW/HW). Il est important de comprendre et d'étudier les mécanismes d'application de la PR sur la plateforme ARM-FPGA dans le contexte d'un système sans fil reconfigurable. Quelles sont les exigences et les besoins pour créer un système sans fil reconfigurable sur les parties logicielles et matérielles? Comment ces parties interagissent-elles entre elles et comment la reconfiguration est-elle gérée? En outre, il est intéressant d'effectuer des mesures en temps réel pour la consommation d'énergie dans la partie PR. La gestion de la reconfiguration est étudié sur un système de communication utilisant la modulation OFDM (multiplexage par répartition de fréquence orthogonal). En tant qu'étude de cas, le passage d'une norme WIFI à WIMAX en utilisant la reconfiguration dynamique est analysé et mis en oeuvre.

Cette thèse a pour objectifs de répondre aux questions de l'intérêt, de la mise en ouevre de la technique PR dans le contexte de systèmes de communication sans fil sur une plateforme ARM-FPGA.

# 1. Concepts et état de l'art

#### 1.1 Communications sans fil

Au cours des dernières décennies, les communications sans fil sont devenues un facteur important dans notre vie quotidienne. En raison de l'essor d'Internet, les utilisateurs finaux souhaitent toujours être connectés à l'intérieur et à l'extérieur, en mobilité ou non.

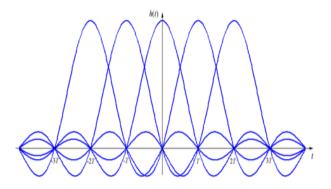

Les canaux sans fil sont considérés comme des canaux les plus difficiles pour la transmission de données. Les signaux sans fil sont généralement affectés par de multiples facteurs liés à l'existence d'obstacles, de bâtiments et de la mobilité de l'utilisateur. Les chercheurs ont proposé plusieurs techniques de modulation et de multiplexage pour maximiser la capacité du canal. Parmi les différentes, celle du multiplexage par répartition de fréquences orthogonale (OFDM). Lancé

Résumé de la Thèse vii

dans les années 1950, l'OFDM est une technique de multiplexage très répandue permettant une transmission de données à haut débit sur des supports filaire ou sans fil [Cha66]. L'OFDM offre de bonnes performances contre les interférences multi-trajets sur de grandes distances.

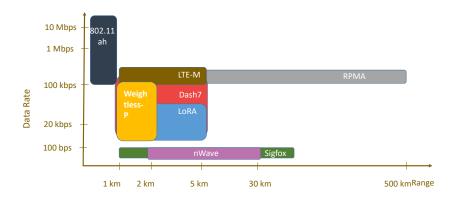

Les systèmes de communication sans fil ont beaucoup évolué en termes de mobilité, de couverture et de débit. Un grand nombre de normes avec des spécifications différentes, à la fois dans les couches PHY (bande passante, débit et codage de modulation) et MAC, sont prposées pour répondre aux différentes exigences techniques et donner accès à de nouveaux services. Les architectures les plus connues des réseaux sans fil sont les réseaux locaux sans fil (WLAN), les réseaux sans fil métropolitains (WMAN), les réseaux cellulaires et les réseaux Internet des objets (IoT). Nous pouvons par ailleurs remarquer l'existence de plusieurs normes sans fil. Cela contribuera à former des réseaux hétérogènes. Les noeuds source et destination devront savoir comment sélectionner le meilleur standard sans fil disponible en fonction des préférences requises.

### 1.2 Techniques adaptatives et radio reconfigurable

L'augmentation des performances des systèmes de communication sans fil a toujours été l'un des premiers objectifs des concepteurs. En raison des caractéristiques des canaux sans fil (perte de chemin, évanouissement, ombrage ...), de la multiplicité des normes, des attributions de fréquences et des caractéristiques de mobilité offertes par les dispositifs sans fil, l'environnement d'exploitation devient de plus en plus complexe à appréhender.

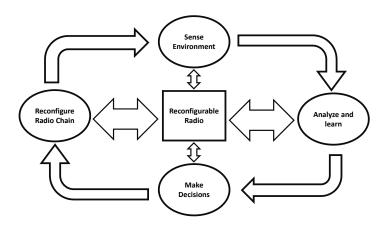

Dans ce contexte, les chercheurs ont proposé des mécanismes adaptatifs pour permettre aux systèmes sans fil d'adapter les formes d'onde en fonction des propriétés du canal. De tels systèmes analysent, apprennent et décident de se reconfigurer dynamiquement. Divers paramètres de bas niveau tels que la puissance du signal reçu (RSSI), le rapport signal / bruit (SNR), le taux d'erreur binaire (BER) ont été utilisés pour garantir l'adaptabilité. D'autres paramètres de haut niveau, tels que l'utilisation des ressources, la QoS et la consommation d'énergie, ont également été étudiés pour décider et adapter de manière appropriée le système à l'environnement en temps réel. L'un des principaux avantages des techniques adaptatives consiste à maximiser la capacité du canal tout en minimisant les coûts ( exemple la consommation d'énergie).

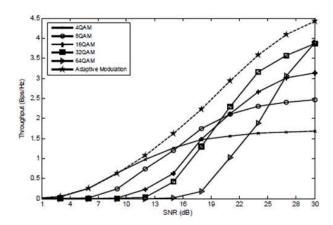

La modulation adaptative est l'une des techniques de transmission qui a été proposée pour établir le meilleur schéma de constellation en fonction des conditions

viii Résumé de la Thèse

de canal [FS], [KH00] et [MN15]. L'encodage de canal adaptatif et le taux de codage sont d'autres techniques adaptatives proposées pour sélectionner le meilleur encodeur ou le meilleur débit en fonction de l'état du canal tel que présenté dans [SPA10], [LTG04] et [DF03]. D'autres algorithmes et méthodologies ont également été proposés pour traiter l'adaptation selon la bande passante. Par exemple, dans les systèmes OFDM, les blocs de mappeur de FFT et de sous-porteuse peuvent être adaptés en fonction des paramètres fournis par le dispositif et par le réseau tels que présentés dans [ZKS07] et [FBF16]. Dans [ZEA05] et [LWN09], les auteurs montrent qu'il est important d'adapter la taille de la FFT par rapport à la consommation d'énergie. Les résultats présentés dans ces deux documents décrivent comment la consommation d'énergie augmente à mesure que la taille de la FFT augmente.

L'application de techniques adaptatives sur les communications sans fil nécessite la mise en oeuvre d'un algorithme qui détecte l'environnement et reconfigure en conséquence des blocs spécifiques dans la couche PHY pendant l'exécution, par exemple le codeur, le modulateur et les blocs IFFT.

### 1.3 Transfert vertical dans les réseaux hétérogènes

Les algorithmes "d'hand-over" vertical (VHA) ont été développés par les chercheurs pour décider quel standard sans fil dans les réseaux hétérogènes est le meilleur pour la communication. Les VHA étudient plusieurs paramètres liés au canal sans fil, au réseau, à l'application utilisateur et aux périphériques pour prendre une telle décision. Selon les valeurs des paramètres, le VHA sélectionne la meilleure norme sans fil disponible et décide de passer d'un standard sans fil à un autre si nécessaire.

Dans le contexte du "hand-over" vertical dans des réseaux hétérogènes, plusieurs travaux peuvent être mentionnés. Dans [KJU<sup>+</sup>15], les auteurs ont proposé un algorithme composé de deux étapes. Dans la première étape, le transfert est déclenché en fonction du débit demandé par l'utilisateur. Avant de débuterr le transfert, le système évalue la vitesse du noeud. Si la vitesse est supérieure à un certain seuil prédéfini qui ne permet pas de bénéficier efficacement du passage à un autre système, le transfert est annulé et considéré comme inutile. Sinon, si la vitesse est appropriée, les réseaux disponibles sont comparés en fonction de cinq paramètres : la bande passante, la gigue, le retard, le coût et l'erreur binaire. Ensuite, le meilleur standard est sélectionné et le changement de standard est effectué si nécessaire.

Résumé de la Thèse ix

Les VHA proposés les plus prometteurs sont ceux basés sur les techniques d'apprentissage automatique. Ils peuvent être catégorisés comme des systèmes basés sur l'intelligence définie dans [ABG14] avec les autres VHA basés sur la logique floue. Les VHA détectent généralement les standards sans fil disponibles et prennent une décision basée sur les valeurs actuelles de certains paramètres. D'un autre côté, les VHA basés sur des techniques d'apprentissage automatique auront la capacité d'étudier et d'apprendre des étapes précédentes pour prendre une décision efficace.

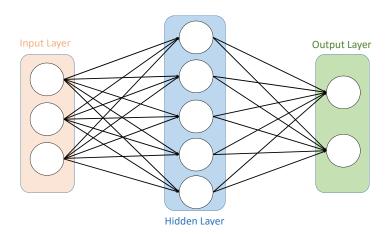

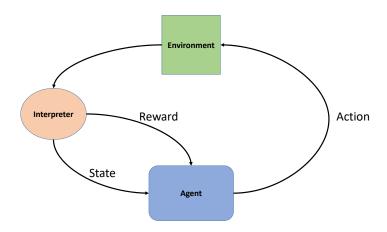

Les réseaux de neurones (NN) sont des systèmes informatiques inspirés des réseaux de neurones biologiques qui constituent le cerveau. De tels systèmes d'apprentissage sont considérés comme un algorithme d'apprentissage automatique supervisé. le réseau de neurones apprend à partir d'un ensemble de données pour générer des sorties. L'apprentissage par renforcement est un domaine d'apprentissage automatique qui concerne la façon dont les agents doivent agir dans un environnement afin de maximiser le résultat. Il est similaire à la programmation dynamique, dans laquelle les résultats sont enregistrés après chaque action et la fonction est reconfigurée pour maximiser le résultat. Les VHA basés sur des algorithmes d'apprentissage automatique ont fourni de bonnes performances et ont la capacité d'apprendre des anciens enregistrements pour créer des fonctions de prédiction.

L'une des principales étapes du "hand-over" vertical est l'étape d'exécution. Après avoir décidé de passer d'un standard sans fil à un autre, au niveau du noeud d'extrémité, la communication doit être commutée de la couche MAC / PHY actuelle à la couche MAC / PHY cible. Certaines études considèrent dès lors la création d'une chaîne reconfigurable unifiée pour plusieurs normes sans fil.

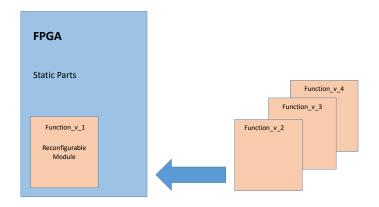

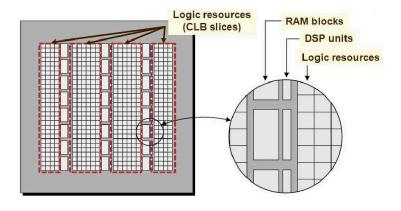

# 1.4 Plates-formes reconfigurables flexibles pour les systèmes de communication

Contrairement à un ASIC, un FPGA est un circuit intégré conçu pour être configuré par un concepteur. Les dispositifs FPGA contiennent un ensemble de blocs logiques programmables et une hiérarchie d'interconnexions reconfigurables qui permettent aux blocs d'être interconnectés entre eux. La reconfiguration partielle est une fonctionnalité intéressante qui a été rendue disponible dans certaines familles de FPGA. Il offre la possibilité de reconfigurer un sous-ensemble de blocs logiques dans le FPGA sans altérer le fonctionnement des autres blocs implantés.

Au cours de la dernière décennie, la recherche sur la conception de micropro-

x Résumé de la Thèse

cesseurs intégrés et d'architectures hybrides FPGA est devenue un sujet d'intrêt. L'idée consiste à combiner les dispositifs FPGA traditionnels et les microprocesseurs avec des périphériques associés afin de construire un système complet sur puce programmable (SoPC). A titre d'exemple, le Zynq 7000 proposé par Xilinx est un composant SoC dont l'architecture est constituée d'un processeur ARM Cortex A9 dual-core et d'un FPGA Artix-7 ou Kintex-7 [CEES14].

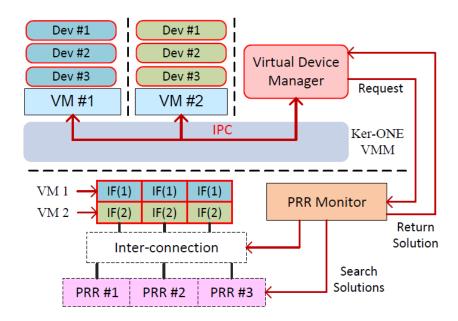

Les systèmes d'exploitation pour les systèmes numériques embarqués sont généralement conçus pour être efficaces en ressources et en énergie. Le concept de base de micro-noyau a été proposé dans [Han70] comme un noyau réduit avec des mécanismes d'ordonnancement fondamentaux. Les micro-noyaux s'exécutent sur la partie processeur (PS) et peuvent utiliser des blocs sur FPGA en tant qu'accélérateurs matériels. L'un de ces micro-noyaux proposés est Ker-ONE [XPN15]. Ker-ONE est très simple, il ne fournit que des fonctions fondamentales telles que l'ordonnancement circulaire, la communication interprocessus et la gestion de la mémoire.

# 1.5 Application de la reconfiguration partielle dans le contexte de radios reconfigurables

En raison de ses propriétés intéressantes, il semble très intéressant de bénéficier de la technique de reconfiguration partielle dans le contexte des radios reconfigurables, car elle permet de reconfigurer les modules matériels lors de l'exécution. De nombreux travaux proposés pour les systèmes de communication sans fil reconfigurables et la radio cognitive ont déjà mis à profit la technique de reconfiguration partielle dans les FPGA.

# 2. Plate-forme ARM-FPGA pour systèmes de communication sans fil adaptatifs automatisés utilisant une technique de reconfiguration partielle

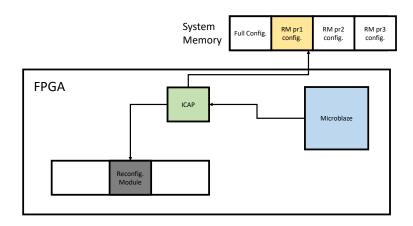

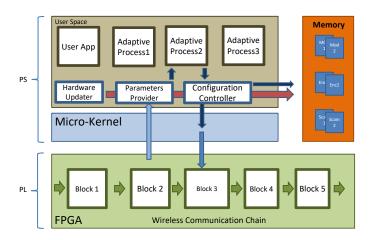

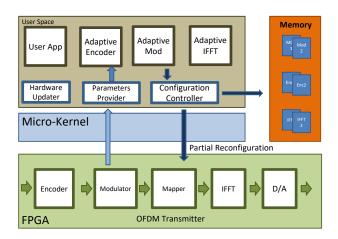

Dans cette section, nous présentons une plate-forme logicielle / matérielle pour les systèmes de communication sans fil adaptatifs automatisés. Le système proposé bénéficie de la technique de reconfiguration partielle disponible dans le dispositif FPGA. Les fonctions de bande de base du système sans fil sont implémentées dans la structure FPGA, tandis que la reconfiguration des différents blocs fonctionnels

Résumé de la Thèse xi

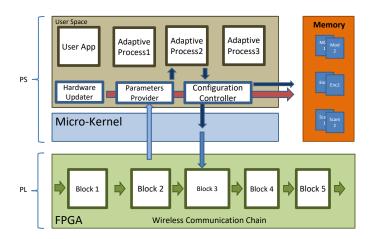

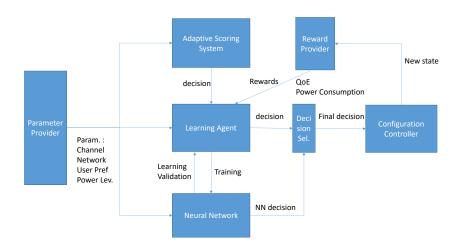

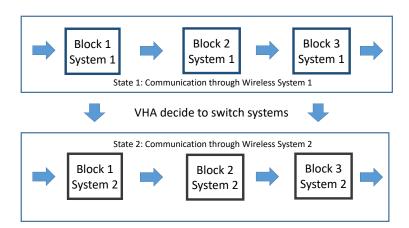

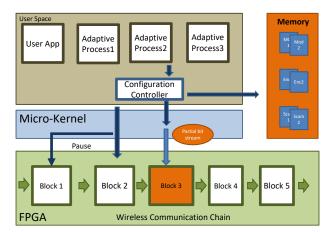

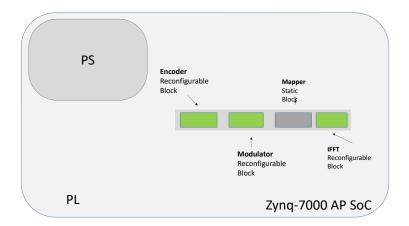

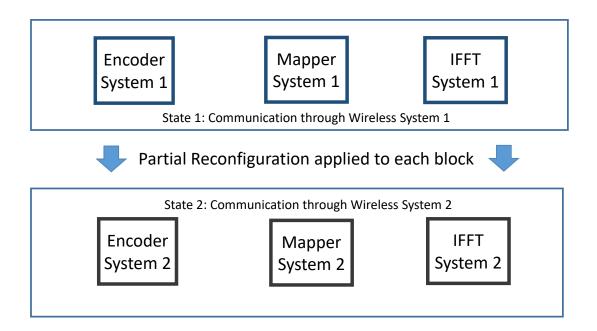

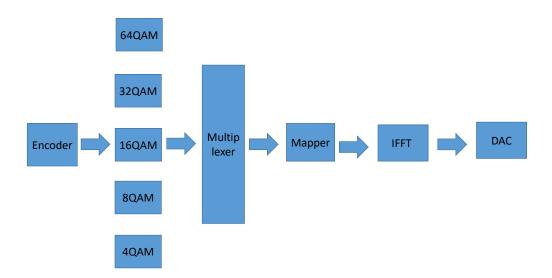

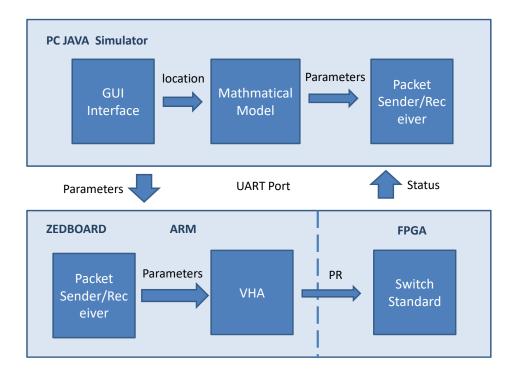

FIGURE 1 – Blocs de conception générale du système

est gérée par des processus s'exécutant sur le processeur ARM. Les processus sont basés sur des algorithmes adaptatifs. Leur rôle est de prendre des décisions et de gérer le processus de reconfiguration des modules concernés.

## 2.1 Conception générale du système

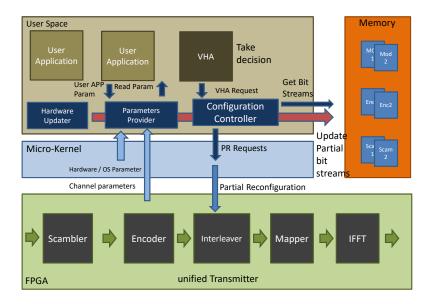

Le système SoC proposé peut être divisé en deux parties : la première partie est exécutée sur le processeur ARM, tandis que la seconde partie est exécutée dans le FPGA. La conception générale du système est présentée dans la FIGURE 1.

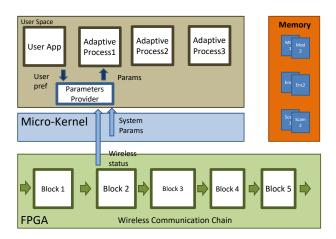

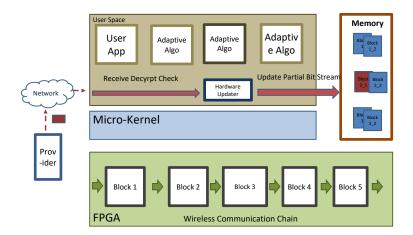

Les modules proposés sur l'ARM sont les suivants : le Contrôleur de configuration, le fournisseur de paramètres et le module de mise à jour matérielle. Tous ces modules fonctionnent comme des tâches dans l'espace utilisateur du micro-noyau Ker-One. Le contrôleur de configuration doit appliquer et contrôler la PR sur le PL et contrôler le flux de données pendant l'opération de reconfiguration partielle. Le fournisseur de paramètres fournit aux processus adaptatifs les paramètres nécessaires à la prise de décision. Le processus de mise à jour matérielle ajoute ou met à jour les nouvelles versions des modules reconfigurables.

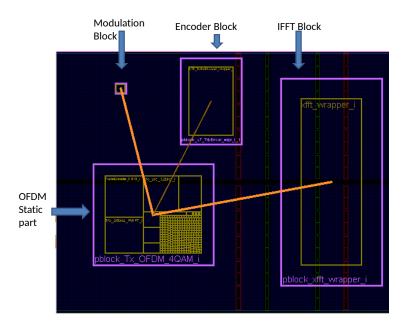

Sur la partie PL, une chaîne de communication reconfigurable (niveau PHY) est implémentée en utilisant la conception reconfigurable dynamique. Ainsi, la chaîne de communication sans fil est divisée en parties statiques et reconfigurables

xii Résumé de la Thèse

dynamiquement. Les modules reconfigurables sont reconfigurés pendant l'exécution lorsque le processus adaptatif le décide.

## 2.2 Émetteur OFDM adaptatif automatique

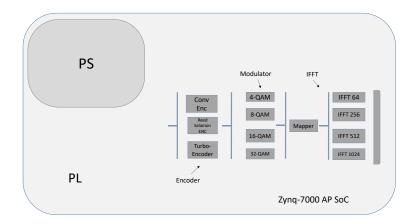

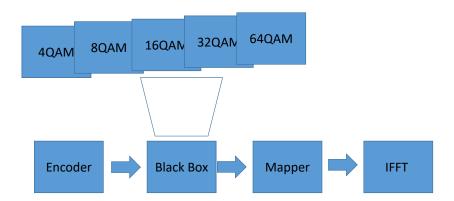

Pour étudier l'impact de l'application de la reconfiguration partielle dans le contexte des radios reconfigurables, nous avons implémenté un transmetteur OFDM auto-adaptatif.

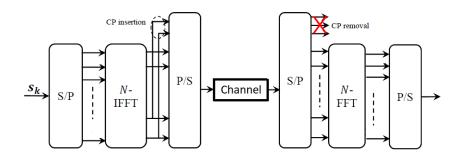

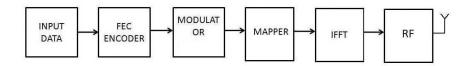

L'émetteur OFDM générique est composé d'un codeur, d'un modulateur, d'un mappeur et d'une IFFT. Sur la base de l'outil Xilinx Vivado, plusieurs bitstreams partiels ont été générés pour ces modules.

Dans la conception PR, les différentes versions des blocs reconfigurables seront stockées en mémoire et chargées à la demande. Si le mécanisme de reconfiguration partielle n'est pas mis en oeuvre, il convient alors d'implanter toutes les versions possibles de chacun des blocs. Ceux-ci seront alors rendus actifs selon la demande (choix des paramètres du standard) et le flux de données y est alors appliqué. Ce type d'implantation est qualifié d'implantation parallèle. En utilisant la PR, il est certain que les ressources utilisées sur le FPGA diminuent, au fur et à mesure que le nombre de blocs implémentés diminuent.

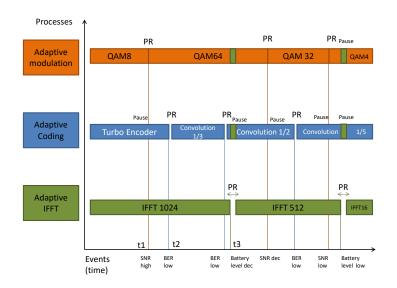

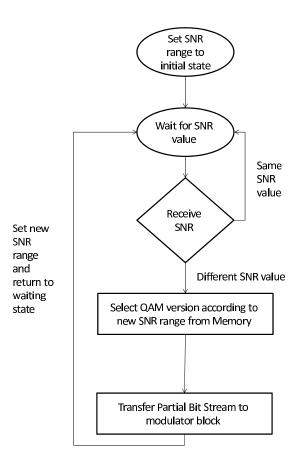

L'outil Xilinx SDK a été utilisé pour implémenter trois processus adaptatifs s'exécutant sur le processeur ARM. Les processus sont implémentés en code C et s'exécutent parallèlement au micro-noyau Ker-One. Dans notre scénario, nous appliquerons trois processus adaptatifs. Le premier processus concerne la modulation adaptative qui décide de reconfigurer le module modulateur. Le second processus est le codage adaptatif qui contrôle le module codeur et le reconfigure selon les conditions de canal. Le troisième processus adaptatif est le processus IFFT adaptatif qui reconfigure le module IFFT.

## 2.3 Résultats expérimentaux

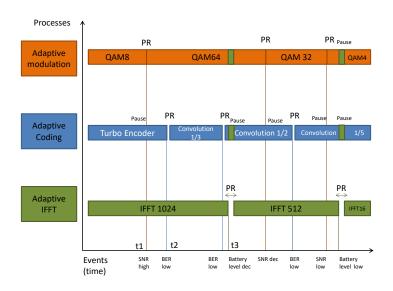

Cette section présente les résultats obtenus à partir du scénario d'émetteur OFDM adaptatif. Les résultats analysent le temps nécessaire pour reconfigurer les modules dynamiques, la taille des bitstreams partiels, la consommation d'énergie et les ressources réservées par chaque version de modules. Enfin, un diagramme de Gantt illustre le comportement du système en fonction des variations des paramètres liés aux demandes de reconfiguration.

Comme décrit précédemmen, nous considérons trois modules de la chaîne OFDM

Résumé de la Thèse xiii

reconfigurables : le modulateur, l'encodeur et l'IFFT. Les résultats présentés dans TABLE 1 incluent la taille des bitstreams partiels et le temps requis pour reconfigurer chaque module respectivement.

| Module     | Taille partielle de Bitstream | Temps de reconfiguration |

|------------|-------------------------------|--------------------------|

| IFFT       | 188 KB                        | 1.48 ms                  |

| Encoder    | 106 KB                        | $0.834~\mathrm{ms}$      |

| Modulation | 30 KB                         | $0.236~\mathrm{ms}$      |

Table 1 – Taille partielle de Bitstream et temps de reconfiguration

Comme indiqué dans la TABLE 1, le temps nécessaire pour transférer un flux de données vers le matériel à l'aide de l'interface PCAP du SoC dépend de la taille du bistream.

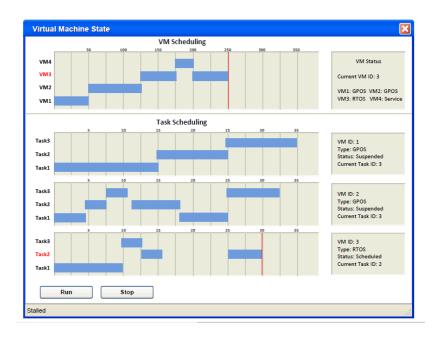

En outre, il est important d'analyser les processus en cours à travers un diagramme de Gantt tel que représenté dans la FIGURE 2. Comme le montre cette figure, trois processus adaptatifs fonctionnent en parallèle sur la partie PS, ils analysent leurs propres paramètres et détectent finalement tout changement. Si nécessaire, la reconfiguration partielle est appliquée sur le bloc approprié afin d'adapter le système au nouvel environnement.

On peut remarquer que le temps nécessaire pour reconfigurer le module IFFT est plus long que celui des modules de codage et de modulation. Cela est dû à la différence dans la taille des bistreams partiels. Pendant la reconfiguration partielle, les modules précédents dans la chaîne sont "suspendus" comme indiqué dans la FIGURE 2. Le temps de suspension dépend de la taille des bistreams partiels transférés. Comme illustré, la suspension d'exécution n'affecte que les modules précédents le bloc reconfiguré.

Avec la reconfiguration partielle, la consommation d'énergie du FPGA et les ressources réservées sont réduites. En alternative à cette technique, toutes les versions des différents modules peuvent être implémentées dans le FPGA, avec des multiplexeurs supplémentaires pour sélectionner le module souhaité. Cela nécessite généralement beaucoup plus de ressources sur le FPGA. En conséquence, la consommation d'énergie statique et dynamique de la puce serait relativement plus élevée vis à vis d'un système basé sur la PR.

La TABLE 2 indique la quantité de ressources utilisées lors de l'application de la technique PR par rapport au cas où la PR n'est pas adoptée. On peut voir qu'il y a environ un rapport de 4 entre les deux cas. De plus, dans le cas de la PR, le gain de ressources permet d'utiliser les parties restantes du FPGA pour implémenter

xiv Résumé de la Thèse

FIGURE 2 – Processus adaptatifs reconfigurant l'émetteur OFDM pendant l'exécution en fonction des valeurs des paramètres

Table 2 – Comparaison de l'utilisation des ressources matérielles

| Ressources                     | LUTs  | REGs   | DSPs |

|--------------------------------|-------|--------|------|

| avec reconfiguration partielle | 2578  | 4129   | 12   |

| sans reconfiguration partielle | 10320 | 16938  | 57   |

| Disponible sur ZYNQ            | 53200 | 106460 | 220  |

des unités de traitement supplémentaires. Le pourcentage des LUT, REG et DSP utilisés sur le SoC est respectivement de 19,3%, 15,9% et 25,9%, lorsque tous les blocs sont implémentés en parallèle. Lors de l'utilisation de la technique PR, le pourcentage de ressources utilisées est respectivement de 4,8%, 3,8% et 5,4%.

# 3. Couche PHY unifiée reconfigurable pour les systèmes sans fil utilisant la reconfiguration partielle - VHA

Dans cette section, le principe de la reconfiguration partielle appliquée à différents standards est étudié. Deux architectures d'implémentation différentes et Résumé de la Thèse xv

reconfigurables sur PL sont comparées. Une chaîne sans fil reconfigurable unifiée pour Wifi-WiMax est testée en tant qu'étude de cas pour évaluer les résultats expérimentaux.

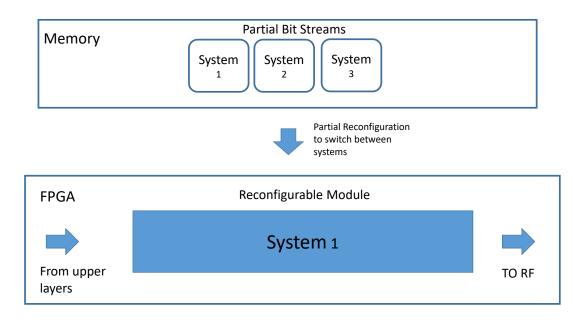

# 3.1 Plate-forme ARM-FPGA pour la commutation entre plusieurs systèmes sans fil

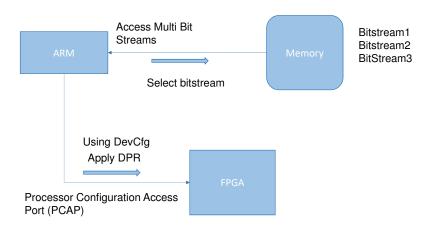

Le système étudié est divisé en deux parties : logiciel et matériel. Dans la partie logicielle, les processus s'exécutent sur le processeur ARM pour contrôler et gérer la configuration de la chaîne sans fil implémentée sur le matériel. Dans la partie matérielle, les systèmes sans fil reconfigurables sont implémentés et conçus pour être partiellement reconfigurés pendant leur exécution.

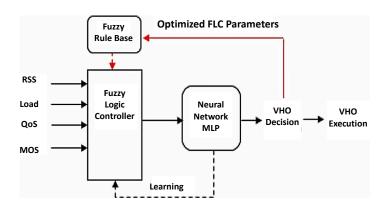

La partie logicielle du système s'exécute dans l'espace utilisateur du micronoyau léger dédié à la reconfiguration partielle. Le rôle du VHA est de lire les paramètres des systèmes de communication disponibles, d'apprendre et de décider s'il faut passer à un autre système ou continuer à fonctionner avec le système actuel.

Le flux de données de la partie logicielle peut être résumé comme suit : Le fournisseur de paramètres fournit au VHA les paramètres pertinents des différentes couches d'u standard. Le VHA analyse les valeurs des paramètres et prend une décision concernant un hand-over possible. En conséquence, une demande de hand-over est envoyée par le VHA au contrôleur de configuration. Le contrôleur de configuration gère le transfert des bitstreams vers les modules reconfigurables du FPGA à travers l'interface PCAP.

La partie matérielle du système implante les couches physiques des systèmes de communication mis en place sur le FPGA. En utilisant la reconfiguration partielle, nous visons à mettre en oeuvre une seule chaîne reconfigurable unifiée pour différentes normes sans fil. Le système de communication est supposé fonctionner en parallèle avec d'autres accélérateurs matériels sur le FPGA. Lorsque la reconfiguration partielle est appliquée, les autres accélérateurs ne sont pas impactés.

# 3.2 Architectures reconfigurables proposées

Dans la partie PL, une seule couche physique reconfigurable pour plusieurs systèmes sans fil est implémentée.

Dans la première architecture, toute la chaîne de communication est considérée comme un module reconfigurable. Dans ce cas, chaque standard sans fil ne possède

xvi Résumé de la Thèse

qu'un seul bistream partiel. Lorsque le système décide de passer à un autre système sans fil, le bistream partiel souhaité est transféré et remplace l'existant. Cette architecture reconfigurable est dénommée une architecture de bloc reconfigurable (ORBA).

La deuxième architecture divise le système de communication en plusieurs blocs reconfigurables. Dans ce cas, pour chaque bloc reconfigurable dans la chaîne, n bistreams partiels sont stockés en mémoire, où n est le nombre de normes sans fil considérées. Si chaque chaîne est divisée en m blocs reconfigurables, alors (m \* n) bistreams sont nécessaires. Cette architecture reconfigurable est appelée architecture à blocs reconfigurables multiples (MRBA).

Les deux schémas sont comparés pour définir les avantages et les inconvénients de chaque architecture.

## 3.3 Étude de cas: Chaîne reconfigurable unifiée WiFi-WiMax

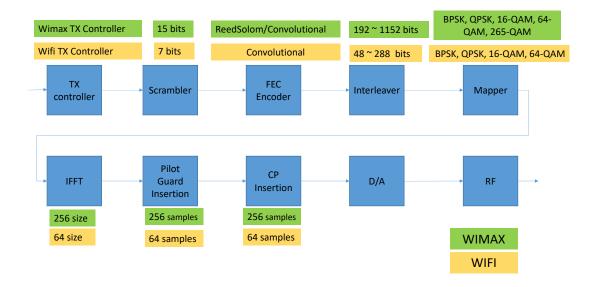

Tout d'abord, la couche physique pour chaque norme est présentée, puis nous expliquons la chaîne unifiée.

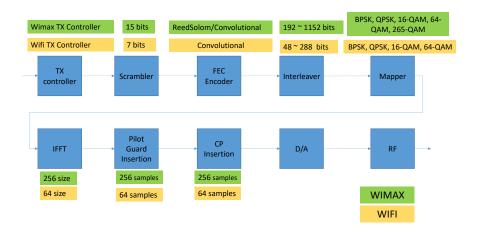

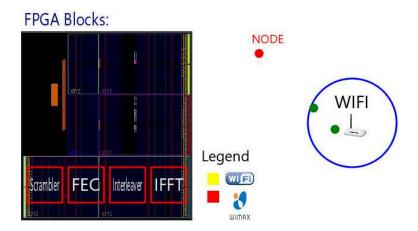

IEEE définit la couche PHY et les spécifications des couches MAC pour WIFI et WIMAX. La couche physique de ces deux normes est basée sur le schéma de modulation OFDM. Les modules principaux sont : Brouilleur/Désembrouilleur, Codeur/Décodeur de Correction d'Erreur Directe (FEC), Interleaver/De-Interleaver, Mapper/De-Mapper, Insertion/Retrait de Pilot Guard, IFFT/FFT et Insertion/Suppression de Préfixe Cyclique. Les différences dans les architectures des émetteurs sont illustrées dans la FIGURE 3. Comme indiqué dans la FIGURE 3, les architectures de couche physique des deux standards sont assez similaires avec peu de différences dans la fonctionnalité de certains modules. Par exemple, WIMAX utilise un FEC Reed-Solomon avec un encodeur de convolution tandis que WIFI utilise uniquement l'encodeur de convolution. Les différences dans le récepteur sont similaires à celles de l'émetteur. Sur cette base, il semble approprié d'appliquer la PR avec la méthode MRBA.

L'application de la PR dans la conception du système à l'aide de MRBA nécessite de diviser le système en deux parties, statique et dynamique. La partie statique est constituée de blocs partagés utilisés dans les deux normes. Pendant le processus de commutation entre les normes, cette partie du système reste inchangée. La partie dynamique est composée de modules qui peuvent être reconfigurés si nécessaire. Plusieurs versions de ces modules reconfigurables sont stockées en mémoire.

Résumé de la Thèse xvii

FIGURE 3 – Liste des modules reconfigurables pendant VHA

## 3.4 Résultats expérimentaux

Les résultats expérimentaux pour la chaîne unifiée de Wifi et WiMax sont donnés en terme de temps de reconfiguration, de ressources sur FPGA, et de consommation sur puce.

Les outils d'estimation de puissance et Vivado ont été utilisés pour estimer la consommation d'énergie et les ressources réservées des différentes versions des modules reconfigurables. Comme indiqué dans la TABLE 3, l'application de la reconfiguration partielle permet de réduire la consommation d'énergie et les ressources utilisées sur le FPGA. Pour l'émetteur, les résultats montrent que les ressources

Table 3 – Comparaison de l'utilisation des ressources matérielles

|                                     | LUTs  | REGs   | DSPs |

|-------------------------------------|-------|--------|------|

| chaîne unifiée pour les deux normes | 2229  | 3376   | 9    |

| les deux normes mises en oeuvre     | 3967  | 6027   | 15   |

| Disponible sur ZYNQ                 | 53200 | 106460 | 220  |

utilisées sont réduites d'environ un facteur de 1,7, lorsque la chaîne unifiée partiellement reconfigurable est utilisée. Le pourcentage de ressources utilisées lorsque les deux normes sont implémentées est respectivement de 6,9%, 5,6% et 6,81% pour xviii Résumé de la Thèse

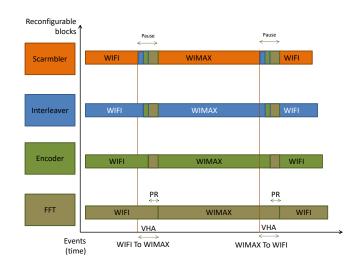

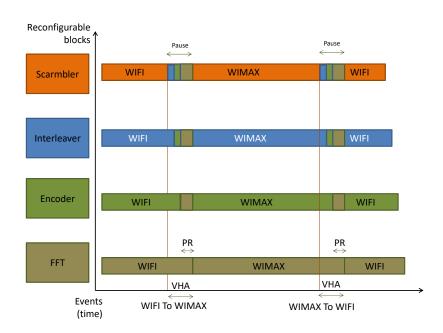

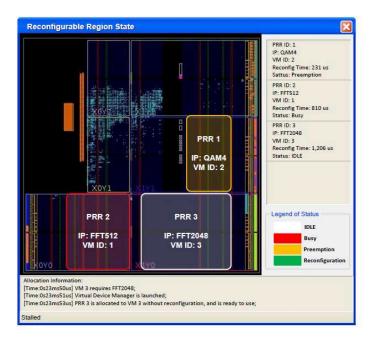

FIGURE 4 – Etat des modules reconfigurables pendant le VHA

les LUT, les REG et les DSP. En revanche, le pourcentage est de 4,18%, 3,17% et 4,09%. lorsqu'une chaîne unifiée est utilisée pour les deux normes.

Dans la FIGURE 4, un diagramme de Gantt illustre un scénario qui montre l'état des modules reconfigurables implémentés sur FPGA lors de l'application du VHA. Le graphique est établi en fonction des temps de reconfiguration mesurés et reflète la manière dont la chaîne unifiée passe d'un standard à l'autre. Comme le montre la figure, les modules sont reconfigurés séquentiellement dans un ordre lié à leur position dans la chaîne. Le temps nécessaire pour passer d'un standard à un autre est la somme des temps de reconfiguration requis par chaque module.

Comme indiqué, lorsqu'un module est reconfiguré, le flux de données est mis en pause jusqu'à ce que les modules suivants soient également reconfigurés. Comme mentionné précédemment, le temps nécessaire pour reconfigurer un bloc est lié à sa taille. Ceci est illustré dans la FIGURE 4 dans laquelle le temps nécessaire pour reconfigurer le bloc IFFT est supérieur à celui requis par les autres. Le passage de WIFI à WIMAX est réalisé lorsque le dernier module (par exemple IFFT) est reconfiguré avec succès. Enfin, les données sont transférées via la norme WIMAX jusqu'à ce qu'une autre VHA se produise.

Résumé de la Thèse xix

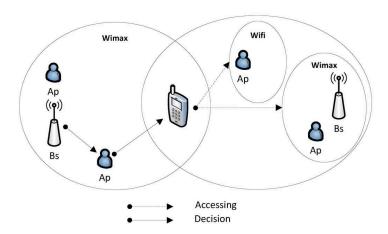

# 4. VHA intelligent pour les réseaux sans fil utilisant les réseaux neuronaux et l'apprentissage par renforcement

Dans les réseaux hétérogènes, les utilisateurs mobiles peuvent détecter de multiples normes sans fil telles que l'accès sans fil haut débit mobile (3G, 3.5G et 4G) et les technologies WLAN. Dans cette section, nous présenterons l'application du VHA pour les réseaux hétérogènes dans lesquels le WiFi et le WiMax sont présents. Ce VHA est considéré comme l'agent de décision dans la plateforme ARM-FPGA proposée.

# 4.1 VHA pour WIFI et WiMax basé sur le poids des paramètres

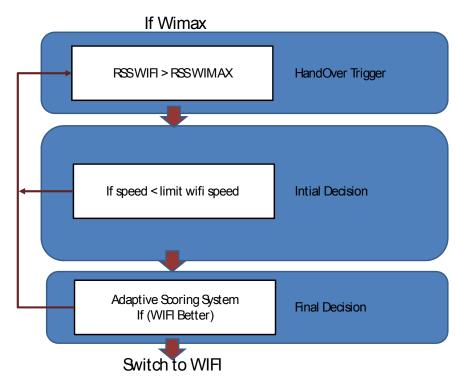

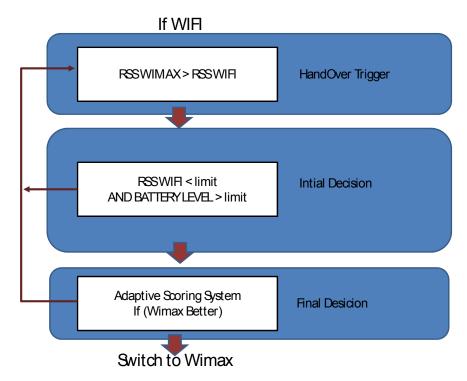

Le VHA proposé pour un réseau WIMAX-WIFI se déroule en trois étapes : un déclencheur de transfert/hand-over, une décision initiale, et une décision finale. L'algorithme identifie deux contextes d'exécution. Dans le premier contexte, le système sans fil communique via le standard WIMAX, alors que dans le second cas, le système fonctionne initialement avec WIFI.

Le déclenchement est initié dès que le processus de transfert détecte une valeur RSS\_WIFI supérieure au RSS\_WIMAX. L'état de décision initiale est utilisée pour prendre des décisions rapides et détecter de faux transferts. un faux transfert est détecté si la vitesse du mobile est supérieure à un seuil WIFI\_max\_speed\_limit. Si la décision initiale est validée, le système passe à l'étape de décision finale. Dans cette dernière étape, un système de notation adaptatif lit plusieurs paramètres pour décider quel standard est le meilleur selon les préférences de l'utilisateur. L'ajout de l'adaptabilité au système de notation améliore l'efficacité du système.

# 4.2 VHA proposé basé sur l'apprentissage automatique

Il est intéressant d'utiliser les techniques de ML (Machine learning) pour rendre le VHA plus intelligent. L'apprentissage automatique fait référence à la science consistant à faire en sorte que les ordinateurs agissent sans être explicitement programmés. Les Neural Networks (NN) sont l'une des techniques ML intéressantes. De tels systèmes d'apprentissage sont considérés comme un algorithme d'apprentissage automatique supervisé. Les systèmes NN apprennent à partir d'un ensemble

de données pour générer des sorties, des décisions, des classes.

L'apprentissage par renforcement est un domaine d'apprentissage automatique qui traite de la manière dont les agents logiciels doivent agir dans un environnement afin de maximiser la récompense. Il est similaire à la programmation dynamique, où les récompenses sont enregistrées après chaque action et la fonction du système est reconfigurée pour maximiser la récompense.

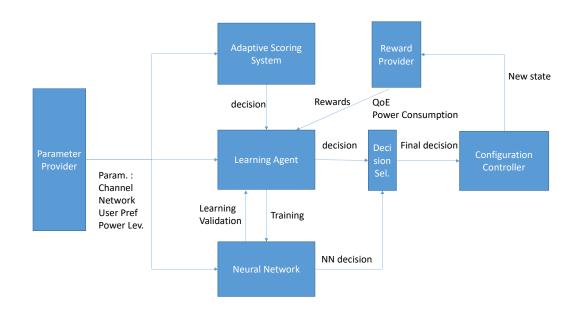

Dans ce travail, nous proposons un système qui combine à la fois des algorithmes d'apprentissage automatique supervisés et non supervisés pour passer d'une norme à l'autre. Ce mécanisme qui est implémenté dans le système est basé sur une amélioration du processus de notation adaptative proposé précédemment. L'idée principale est de bénéficier du travail précédent dans une première étape. Cette étape consiste à collecter des enregistrements et des récompenses/retours du système de notation adaptatif précédent. Les décisions prises sont ensuite classées en fonction des récompenses obtenues. Dans un deuxième temps, seules celles qui génèrent de bonnes récompenses sont considérées et elles formeront un nouvel ensemble de données. Les enregistrements collectés et les récompenses acceptables ou bonnes correspondantes seront utilisés pour l'apprentissage du réseau de neurones NN.

Après la collecte d'un grand ensemble de données, le réseau de neurones NN est considéré comme suffisamment "formé" et stable pour prendre une bonne décision. Ainsi, il peut être adopté pour prendre les décisions. Le système peut répéter la procédure d'apprentissage du NN après la mise à jour de l'ensemble de données afin d'optimiser cette opération et d'améliorer son comportement. Le système proposé est constitué des blocs représentés sur la FIGURE 5.

## 4.3 Résultats expérimentaux

Pour prouver le concept, une simulation a été réalisée sur la base d'un scénario WiFi-WiMax utilisant un simulateur Java. Basé sur le système de notation adaptative et un système de récompense/retour simple, un simulateur Java a été mis en place pour générer les données requises (Paramètres d'entrée - Décisions - Récompenses/Retours - et Décisions d'apprentissage). Le simulateur génère aléatoirement les paramètres d'entrée : RSS, Charge réseau, Préférences utilisateur, Niveau de puissance et Statut. Ensuite, les décisions et récompenses associées pour la puissance et la QoS peuvent être sélectionnées selon une décision simple et un moteur de récompenses. Le moteur fonctionne en fonction des paramètres d'entrée et des décisions précédentes.

Résumé de la Thèse xxi

FIGURE 5 – Conception proposée de VHA

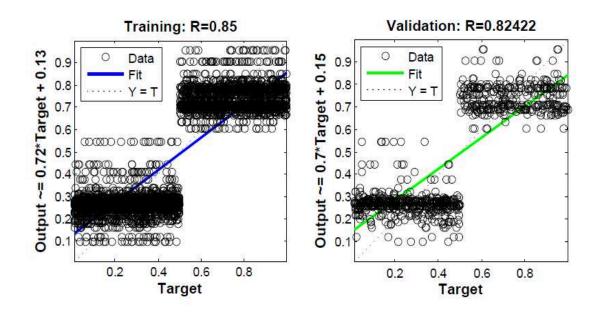

Comme nous l'avons déjà expliqué, l'agent d'apprentissage doit savoir quand il faut que le NN apprenne. Il a également pour tâche de valider le NN chaque fois qu'il y a suffisamment d'enregistrements étiquetés. Il est important de savoir quel est le meilleur nombre d'enregistrements étiquetés nécessaires pour obtenir de bons résultats.

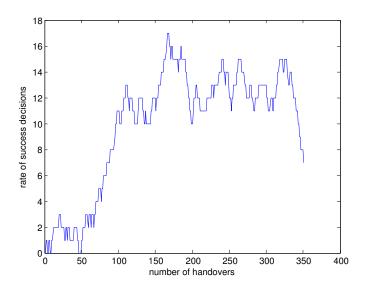

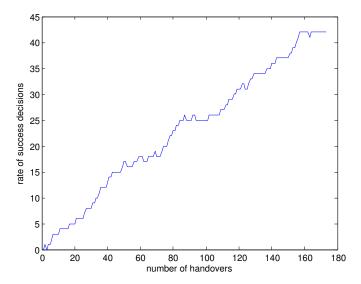

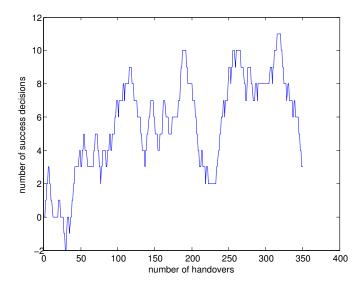

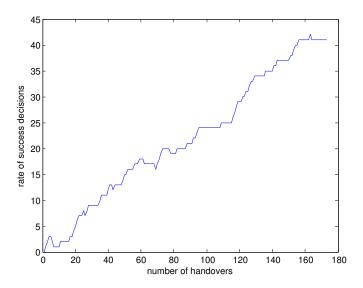

Le taux de décisions réussies conduit à en ajouter une pour une bonne décision et en soustraire une pour une mauvaise décision. Les résultats prennent en compte le retour de la consommation d'énergie pour décider si les décisions obtenues sont bonnes ou mauvaises. Il est à souligner que la formation du NN avec les enregistrements marqués qui représentent les enregistrements avec seulement de bonnes récompenses donne de meilleurs résultats. Le même scénario a été appliqué en prenant en considération la récompense QoS comme récompense principale pour décider de la qualité de la décision prise.

xxii Résumé de la Thèse

# 5. Implémentation et mesures de puissance en temps réel

Dans cette section, nous présentons la implémentation du PR sur les outils Vivado pour la technique de modulation adaptative dans une chaîne OFDM. Ensuite, nous présentons les résultats de consommation d'énergie sur le SoC. À la fin de ce chapitre, deux démonstrations sont présentées. La première concerne le déroulement des processus du micro-kernel Ker-One et de la PR. La deuxième démonstration concerne la commutation entre le WiFi et le WiMax en utilisant la technique PR.

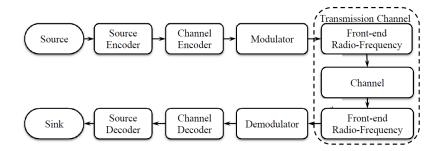

# 5.1 Implémentation et analyse de puissance pour un transmetteur OFDM reconfigurable automatisé et adapté

La chaîne générique de l'émetteur SISO OFDM est formée par différentes entités. Ces entités sont implémentées en utilisant VHDL. Certaines de ces entités sont créées à l'aide du générateur IP Xilinx. Ils sont connectés par mappage de port pour former la chaîne complète. Le code VHDL du transmetteur SISO OFDM a été implémenté à l'aide de la suite de conception Xilinx ISE et testé avec le simulateur Modelsim. Les résultats générés par le simulateur Modelsim ont été comparés à ceux obtenus avec Matlab pour garantir et valider la fonctionnalité de l'ensemble du système.

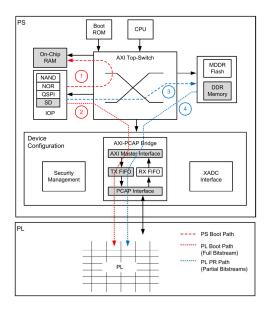

Le flux de conception Xilinx pour la reconfiguration partielle est utilisé pour mettre en oeuvre le concept de reconfiguration sur la chaîne de comumnication après avoir testé les différents blocs de code VHDL. Pour mettre en oeuvre la technique de modulation adaptative, le concept PR a été appliqué sur le bloc de modulation. Dans ce cas, les blocs Encoder, Mappeur, Bloc IFFT, Scaler et FIFO constituent les parties statiques du système. En utilisant Xilinx ISE ou Vivado Tools, le bloc de modulation a été resynthétisé sous forme de boîte noire. Une boîte noire est une implémentation d'une entité avec une définition de ports mais sans architecture. Le système a été rendu auto-intelligent en appliquant le concept DPR (Dynamic PR) sur la partie PL du Soc. Pendant la phase de démarrage, le système envoie le bistream principal au FPGA, puis configure le PS. Il charge également les bistreams partiels en mémoire permettant au PS d'y accéder lors de l'exécution de la reconfiguration.

La puissance consommée par la puce FPGA est la somme des consommations

Résumé de la Thèse xxiii

d'énergie statique et dynamique. La puissance statique est principalement due au courant de fuite des transistor. Cela se produit même lorsque le transistor est "off" logiquement. La puissance dynamique est la somme de la consommation d'énergie transitoire et de la consommation d'énergie de la charge capacitive. Dans notre cas, nous utiliserons Xpower Analyzer, un analyseur de phase de conception, pour estimer les consommations électriques statiques et dynamiques. Les résultats montrent un taux de réduction de 1,6% de la puissance totale sur la puce et un taux de réduction de la puissance dynamique de 18,7%.

# 5.2 Analyse dynamique et partielle de la consommation d'énergie lors de la reconfiguration des mesures d'exécution pour les appareils SoC Zynq

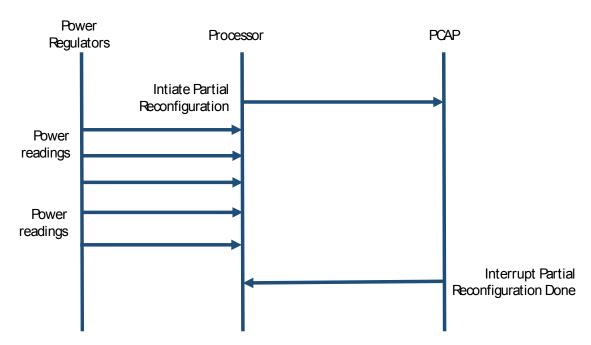

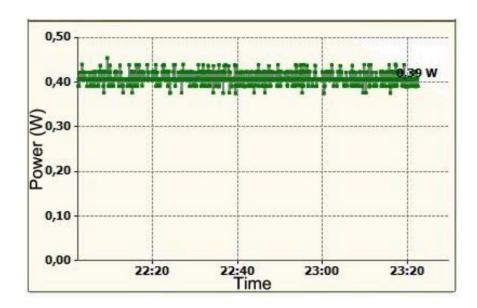

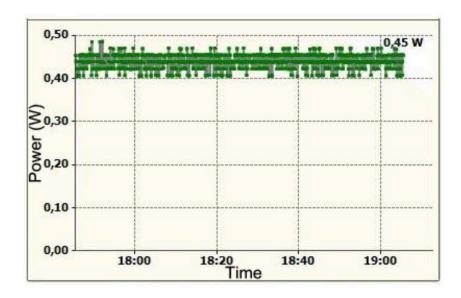

Il est intéressant dans notre travail de calculer la consommation d'énergie pour l'opération de reconfiguration partielle dynamique à la fois sur le PS et le PL.

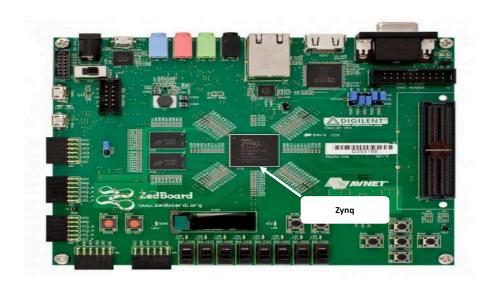

Dans cette étude, les cartes d'évaluation ZC70 ZYNQ et ZC702 ZYNQ ont été utilisées. La carte ZC706 possède un SoC AP-SoC ZYNQ 7000-XC7Z045, alors que la carte ZC702 est équipée d'une carte SoC AP ZYNQ 7000-XC7Z020 CLG484. Le SoC ZYNQ 7000-XC7Z045 fournit plus de ressources que le ZYNQ 7000-XC7Z020. Dans les deux dispositifs ZYNQ, les parties PS et PL sont intégrées avec des interfaces d'interconnexion AMBA AXI à bande passante élevée.

Les deux contrôleurs de consommation sont accessibles via l'interface I2C en utilisant le protocole de commandes PMBus [pmb]. Nous avons utilisé l'outil TI pour obtenir une vue d'ensemble de la consommation d'énergie sur PL et le PS lors d'une reconfiguration partielle. De plus, nous exécutons notre code implémenté sur le processeur pour contrôler les données à envoyer, et pour lire ces données uniquement pendant le processus de reconfiguration partielle.

La puissance consommée par le FPGA est mesurée sur deux SoC ZYNQ de taille différente. L'objectif est d'évaluer l'impact de la taille de la partie logique sur la consommation d'énergie pendant la reconfiguration partielle.

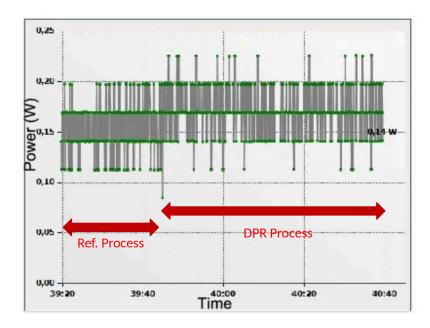

Pour la partie PS, le processus DPR est comparé à un processus de référence dans lequel la reconfiguration partielle n'est pas appliquée. Par conséquent, le pilote DevCfg avec l'interface PCAP n'est pas utilisé. Ce processus de référence consiste à exécuter une boucle while infinie et vide. Le processus DPR est un code C exécuté sur le processeur et a accès au pilote DevCfg pour appliquer des transferts de bits partiels consécutifs au PL. Dans ce cas, l'interface PCAP est engagée dans le

processus PR et le processeur ARM envoie des requêtes répétitives pour effectuer la reconfiguration partielle sur le bloc concerné. La puissance consommée par le VCCPINT est mesurée à l'aide de l'outil TI GUI.

La puissance consommée par le processus de référence est légèrement supérieure à celle obtenue pour le processus DPR. Ce résultat montre qu'il n'y a pas d'augmentation de la consommation d'énergie pour le processus de reconfiguration partielle sur le processeur. De plus, nous avons mesuré la puissance consommée par le régulateur VCCPAUX pendant la DPR et le processus de référence. Les résultats montrent qu'il y a une légère puissance supplémentaire consommée pendant le processus DPR. Les valeurs moyennes pour les mesures de puissance présentées dans les figures précédentes sont résumées dans TABLE 4.

| Power Reg | with DPR            | No DPR              |

|-----------|---------------------|---------------------|

| VCCINT    | 274,8 mW            | 274.4  mW           |

| VCCPINT   | 40.2  mW            | 41.8 mW             |

| VCCPAUX   | $170.3~\mathrm{mW}$ | $157.7~\mathrm{mW}$ |

Table 4 – Puissance moyenne pour PS et PL dans deux cas

#### 5.3 Démonstrations

Dans cette section nous présenterons deux démonstrations, la première démonstration illustre le fonctionnement du micro-noyau Ker-ONE utilisé pour le contrôle de la reconfiguration. La deuxième démonstration décrit l'application du VHA entre le WiFi et le WiMax basée sur une reconfiguration partielle.

La première démonstration est exécutée sur la plateforme Xilinx Zynq-7000 SoC, avec le processeur ARM Cortex-A9 dual-core et le FPGA reconfigurable. Plusieurs algorithmes de communication sont implémentés dans le FPGA. Ils sont considérés comme des accélérateurs matériels vis à vis des applications s'exécutant sur l'ARM, par exemple la FFT. Au dessus de Ker-ONE, plusieurs OS( ucos-II) s'exécutent simultanément en mode machines virtuelles (OS invités) avec des priorités différentes. La démonstration montre comment Ker-One traite les requêtes des machines virtuelles selon leur priorité et les demandes de reconfiguration sur le FPGA.

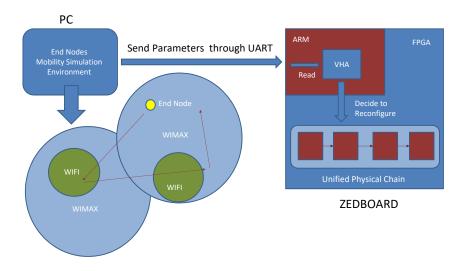

Dans la seconde démonstration, nous proposons un système implémentant le VHA pour les standards WIFI-WiMAx sur la même plateforme utilisant la technique PR. Le VHA fonctionne sur l'ARM. La chaîne reconfigurable unifiée qui

Résumé de la Thèse xxv

implémente les couches PHY des deux normes sans fil est implémentée dans la partie PL du SoC. La démonstration est constituée en deux parties. La première partie consiste en une application en code C fonctionnant sur le processeur ARM avec la chaîne de communication sans fil implémentée sur le FPGA. La deuxième partie est un code JAVA exécuté sur le PC pour simuler les paramètres de prise de décision et gérer l'interface graphique. Le simulateur sur le PC et l'application sur ARM communique via l'UART. Le simulateur collecte les valeurs de paramètres générées à partir de modèles mathématiques et les transmet dans un paquet à l'application sur l'ARM en temps réel. L'application sur l'ARM extrait les valeurs et applique le VHA pour sélectionner le meilleur standard. Si le VHA décide de passer d'un standard à un autre, il demandera au contrôleur de reconfiguration de reconfigurer la chaîne unifiée. Sur la ZedBoard, l'application transmet le nouveau statut des modules reconfigurables au simulateur. Cette transmission est également illustrée dans l'interface graphique (voir FIGURE 6).

La démonstration illustre ainsi l'effet de la mobilité d'un utilisateur, la décision prise par le VHA et l'état des blocs reconfigurables sur le FPGA.

FIGURE 6 – Capture d'écran du simulateur illustrant l'état des blocs reconfigurables, le noeud mobile et la décision VHA

# 6. Conclusion et perspectives

Au cours de la dernière décennie, les systèmes de communication sans fil ont beaucoup évolué en termes de mobilité, de couverture et de débit. Un grand nombre de normes avec des spécifications différentes, à la fois dans la PHY (bande passante, débit, et techniques de codage de modulation) et MAC couches, ont été fournis pour répondre aux différentes exigences techniques et donner accès à de nouveaux services.

La reconfiguration matérielle des systèmes de communication sans fil est la solution la plus intéressante pour mettre en oeuvre des techniques adaptatives et VHA. Dans ce cas, certaines fonctions du système peuvent être modifiées pendant l'exécution, tandis que d'autres continuent à fonctionner sans interruption. Les FPGA constituent les circuits idéaux pour implémenter de tels systèmes reconfigurables. De tels dispositifs sont maintenant suffisamment mûrs pour implémenter des systèmes très complexes avec un haut niveau de performance. PR est l'une des fonctionnalités intéressantes qui ont été ajoutées par les fournisseurs de FPGA pour assurer encore plus de flexibilité.

Une autre caractéristique intéressante dans les récents dispositifs FPGA est la présence de coeurs de processeurs embarqués qui sont implémentés avec la structure FPGA matérielle, dans la même puce. Par exemple, les appareils SoC Zynq de Xilinx sont équipés d'un processeur ARM Cortex-A9 à double coeur (PS) ainsi que d'un PL dans un seul appareil. Comparés à leurs homologues de processeurs soft core, ces processeurs offrent beaucoup plus de puissance et de rapidité de calcul. Les appareils SoC sont appropriés pour la conception de systèmes logiciels et matériels communs. L'existence de tels systèmes dans les terminaux permet de concevoir des objets de communication intelligents haute performance.

Dans cette thèse, nous présentons une plate-forme ARM-FPGA pour les systèmes de communication sans fil reconfigurables qui bénéficie de la technique de reconfiguration partielle. Le système proposé a été testé pour la chaîne OFDM auto-adaptative. Il a également été utilisé pour basculer entre les réseaux WiFi et WiMax basés sur l'apprentissage automatique VHA. Des mesures de puissance et des démonstrations en temps réel ont été effectuées pour extraire les résultats expérimentaux et tester le système proposé.

Pour le travail à venir, il est intéressant d'avoir un vrai test pour une communication sans fil entre deux ou plusieurs cartes basées sur SoC avec l'application de PR pour reconfigurer les blocs dans la chaîne sans fil. Il sera également intéressant d'appliquer un test réel pour une commutation entre deux standards sans

Table of Contents xxvii

fil sur deux cartes ARM-FPGA en utilisant une technique de reconfiguration partielle. Il sera également intéressant de proposer une architecture combinée entre PR et conception parallèle pour optimiser la meilleure puissance et le temps de reconfiguration pour les systèmes sans fil reconfigurables.

# TABLE OF CONTENTS

| A                | ckno   | wledgn  | nents                     |                                                                      |    | i    |

|------------------|--------|---------|---------------------------|----------------------------------------------------------------------|----|------|

| $\mathbf{A}$     | bstra  | ct      |                           |                                                                      |    | iii  |

| $\mathbf{T}_{i}$ | able ( | of Con  | $	ext{tents}$             |                                                                      | XX | cvii |

| $\mathbf{A}$     | bbre   | viation | ıs                        |                                                                      | ХX | ΧXV  |

| In               | trod   | uction  |                           |                                                                      |    | 1    |

| 1                | Co     | NCEPT   | S AND R                   | RELATED WORKS                                                        |    | 7    |

|                  | 1.1    | Introd  | onumber luction onumber . |                                                                      |    | 7    |

|                  | 1.2    | Wirele  | ess Comm                  | ${\it nunications}  \dots  \dots  \dots  \dots  \dots  \dots  \dots$ |    | 8    |

|                  |        | 1.2.1   | Wireless                  | s Channels                                                           |    | 8    |

|                  |        | 1.2.2   | OFDM                      |                                                                      |    | 9    |

|                  |        | 1.2.3   | Wireless                  | s Communication Standards                                            |    | 10   |

|                  |        |         | 1.2.3.1                   | Wireless Local Area Networks                                         |    | 10   |

|                  |        |         | 1.2.3.2                   | Wireless Metropolitan Area Networks                                  |    | 12   |

|                  |        |         | 1.2.3.3                   | Cellular Networks                                                    |    | 12   |

|                  |        |         | 1.2.3.4                   | Internet of Things Networks                                          |    | 12   |

|                  | 1.3    | Adapt   | ive Techn                 | niques and Reconfigurable Radio                                      |    | 13   |

|                  | 1.4    | Vertic  | al Hando                  | ver in Heterogeneous Networks                                        |    | 16   |

|                  |        | 1.4.1   | Vertical                  | Handover Algorithms                                                  |    | 16   |

|                  |        | 1.4.2   | VHAs B                    | Based on Machine Learning                                            |    | 19   |

|                  |        |         | 1.4.2.1                   | Machine Learning                                                     |    | 19   |

|                  |        |         | 1.4.2.2                   | Neural Networks                                                      |    | 20   |

|                  |        |         | 1.4.2.3                   | Reinforcement Learning                                               |    | 20   |

|                  |        |         | 1.4.2.4                   | Applying the Machine Learning Technique in the                       |    |      |

|                  |        |         |                           | VHA context                                                          |    | 21   |

|                  |        |         |                           |                                                                      |    |      |

|   |                        | 1.4.3 Unified Reconfigurable Communication Chain for Multiple Wireless Standards |

|---|------------------------|----------------------------------------------------------------------------------|

|   | 1.5                    | Flexible Reconfigurable Platforms for Communications Systems 2                   |

|   |                        | 1.5.1 Field Programmable Gate Array                                              |

|   |                        | 1.5.2 Dynamic Partial Reconfiguration (DPR)                                      |

|   |                        | 1.5.3 ARM-FPGA Platform                                                          |

|   |                        | 1.5.4 Embedded Operating Systems in SoC Devices                                  |

|   | 1.6                    | Applying Partial Reconfiguration in Context of Reconfigurable Radios 3           |

|   | 1.7                    | Summary                                                                          |

| 2 | $\mathbf{A}\mathbf{R}$ | M-FPGA Based Platform for Automated Adaptive Wi-                                 |

|   | REL                    | ESS COMMUNICATION SYSTEMS USING PARTIAL RECONFIGU-                               |

|   | RAT                    | TION TECHNIQUE 3                                                                 |

|   | 2.1                    | Introduction                                                                     |

|   | 2.2                    | General System Design                                                            |

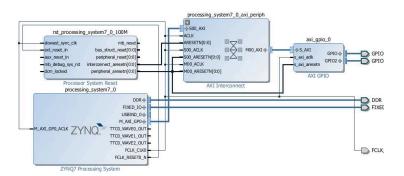

|   |                        | 2.2.1 Overview for ARM-FPGA platform                                             |

|   |                        | 2.2.2 Xilinx Vivado Tools                                                        |

|   |                        | 2.2.3 Processing System Modules- PS part                                         |

|   |                        | 2.2.3.1 Micro-Kernel                                                             |

|   |                        | 2.2.3.2 Configuration Controller                                                 |

|   |                        | 2.2.3.3 Parameters Provider                                                      |

|   |                        | 2.2.3.4 Hardware Updater                                                         |

|   | 2.3                    | Auto Adaptive OFDM transmitter                                                   |

|   |                        | 2.3.1 Reconfigurable Hardware                                                    |

|   |                        | 2.3.2 Adaptive processes                                                         |

|   | 2.4                    | Experimental Results                                                             |

|   | 2.5                    | Summary                                                                          |

| 3 |                        | ECONFIGURABLE UNIFIED PHY FOR MULTI WIRELESS SYS-                                |

|   |                        | IS USING PARTIAL RECONFIGURATION 5                                               |

|   | 3.1                    | Introduction                                                                     |

|   | 3.2                    | ARM-FPGA Platform for Switching between Multi Wireless Sys-                      |

|   |                        | tems                                                                             |

|   |                        | 3.2.1 Software Part                                                              |

|   |                        | 3.2.2 Hardware Part                                                              |

|   | 3.3                    | Proposed Reconfigurable Architectures                                            |

|   | 3.4                    | Case Study: WiFi-WiMax Unified Reconfigurable chain                              |

|   |     | 3.4.1 IEEE 802.11 WiFi                                           | 64         |

|---|-----|------------------------------------------------------------------|------------|

|   |     | 3.4.2 IEEE 802.16 WiMax                                          | 64         |

|   |     |                                                                  | 64         |

|   | 3.5 |                                                                  | 66         |

|   |     | 3.5.1 Performance Evaluation for MRBA and ORBA                   | 66         |

|   |     | 3.5.2 Experimental Results for the Unified Chain for WiFi-WiMax  | 68         |

|   | 3.6 |                                                                  | 71         |

| 4 | Int | ELLIGENT VHA FOR WIRELESS NETWORKS USING NEURAL                  |            |

|   | NE  | TWORKS AND REINFORCEMENT LEARNING                                | <b>7</b> 3 |

|   | 4.1 | Introduction                                                     | 73         |

|   | 4.2 | Heterogeneous Networks and Vertical Handover                     | 73         |

|   | 4.3 | VHA for WiFi and WiMax Heterogeneous Network                     | 74         |

|   |     | 4.3.1 Vertical Handover Algorithm based on Adaptive Scoring Sys- |            |

|   |     | $\mathrm{tem}$                                                   | 75         |

|   | 4.4 | Proposed VHA based on Machine Learning                           | 80         |

|   |     | 4.4.1 Proposed System Design                                     | 80         |

|   |     | 4.4.1.1 Parameters Provider                                      | 80         |

|   |     | 4.4.1.2 The Neural Network                                       | 81         |

|   |     | 4.4.1.3 Adaptive Scoring System                                  | 82         |

|   |     | 4.4.1.4 Learning Agent                                           | 82         |

|   |     | 4.4.1.5 Reward Provider                                          | 83         |

|   |     | 4.4.1.6 Decision Selector                                        | 83         |

|   |     | 4.4.1.7 The Configuration Controller                             | 84         |

|   |     | 4.4.2 NN based VHA Vs. standard VHA                              | 84         |

|   | 4.5 | Experimental Results                                             | 85         |

|   | 4.6 | Summary                                                          | 91         |

| 5 | IMF | LEMENTATION AND REAL TIME POWER MEASUREMENTS                     | 93         |

|   | 5.1 | Introduction                                                     | 93         |

|   | 5.2 | Implementation and Power Analysis for Automated Adapted Re-      |            |

|   |     | configurable OFDM Transmitter                                    | 93         |

|   |     | 5.2.1 Implementation of the OFDM Transmitter on FPGA             | 94         |

|   |     | 5.2.2 Applying Partial Reconfiguration on OFDM Transmitter       | 95         |

|   |     | 5.2.3 Automated Adapted Reconfigurable OFDM Transmitter          | 97         |

|   |     | 5.2.4 On Chip Power Results                                      | 98         |

|              | 5.3   |        | Time Measurements and Analysis of Dynamic and PR Power       |    |

|--------------|-------|--------|--------------------------------------------------------------|----|

|              |       |        | mption for Zynq SoC Devices                                  |    |

|              |       | 5.3.1  | BackGround and Related Work                                  |    |

|              |       | 5.3.2  | Experimental Setup                                           |    |

|              |       | 5.3.3  | Experimental Results                                         |    |

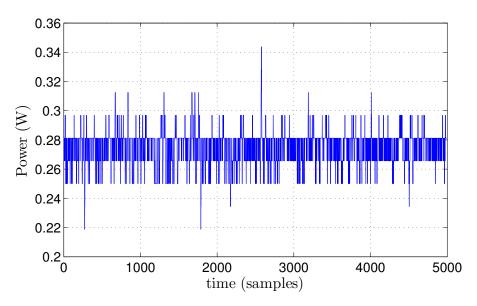

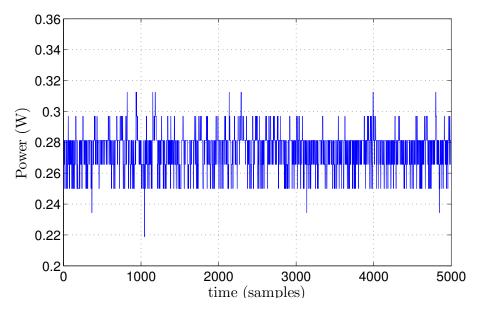

|              |       |        | 5.3.3.1 PL Power Measurements                                |    |

|              | - ,   | a      | 5.3.3.2 PS Power Measurements                                |    |

|              | 5.4   | Summ   | ary                                                          | 10 |

| 6            | Con   |        | n and Perspectives                                           |    |

|              | 6.1   |        | ary                                                          |    |

|              | 6.2   | Perspe | ectives and Future Works                                     | 14 |

| $\mathbf{A}$ | ppen  | dix A  | DEMONSTRATIONS 11                                            | 15 |

|              | A.1   | Introd | uction                                                       | 15 |

|              |       | A.1.1  | Ker-ONE : Embedded Virtualization Approach with Dyna-        |    |

|              |       |        | mic Reconfigurable Accelerators Management                   | 15 |

|              |       |        | A.1.1.1 Demonstrations Description                           | 17 |

|              |       | A.1.2  | WiFi-WiMax Vertical Handover on an ARM-FPGA Plat-            |    |

|              |       |        | form with Partial Reconfiguration                            | 19 |

|              |       |        | A.1.2.1 WiFi-WiMax Handover on ARM-FPGA Platform             | 10 |

|              |       |        | with PR Technique                                            |    |

|              |       |        | A.1.2.2 Demonstration Description                            |    |

|              |       |        | A.1.2.3 VHA on ZedBoard with Partial Reconfiguration 1       |    |

|              |       |        | A.1.2.4 End-Node Mobility Simulator on the PC                |    |

|              |       |        | A.1.2.5 Connection between the ZedBoard and the Simulator 1: | 21 |

| A            | ppen  | dix B  | EVALUATION BOARDS 12                                         | 23 |

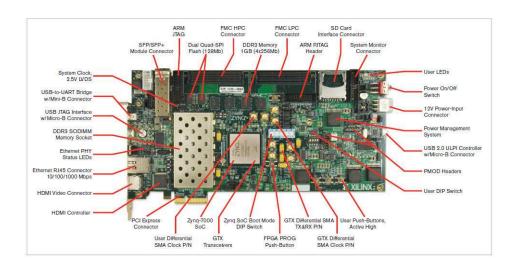

|              | B.1   | ZedBo  |                                                              |    |

|              |       | B.1.1  | FEATURES                                                     |    |

|              |       | B.1.2  | TARGET APPLICATIONS                                          |    |

|              | B.2   | ZYNÇ   | 2-7000 SOC ZC706 Evaluation Kit                              |    |

|              |       | B.2.1  | Key Features and Benefits                                    |    |

|              | B.3   | ZYNÇ   | 2-7000 SOC ZC702 Evaluation Kit                              |    |

|              |       | B.3.1  | Key Features and Benefits                                    | 26 |

| Τ.i          | st of | Figure | PS 15                                                        | 29 |

| 133 |

|-----|

| 133 |

|     |

# **ABBREVIATIONS**

MAC: Media Access Control Multi-RAT: Multiple Radio Access Technologies

VHA: Vertical Handover Algorithm

QoS: Quality Of Service

FPGA: Field Programmable Gate Array

$\mathbf{PR}: \mathbf{P}$ artial  $\mathbf{R}$ econfigurable

PS: Processing System

$\mathbf{PL}: \mathbf{Programmable} \ \mathbf{Logic}$

OFDM: Orthogonal Frequency Division Multiplexing

NN: Neural Network

IFFT: Inverse Fast Fourier TransformWLAN: Wireless Local Area Network

WMAN: Wireless Metropolitan Area Networks

IoT : Internet Of Things

Wi-Fi : Wireless Fidelity

**GSM**: Global System for Mobile Communications

LTE: Long Term Evolution

RSSI: Received Signal Strength Indicator

SNR: Signal-to-Noise Ratio

BER : Bit Error Rate NN :Neural Network

ASIC: Application-Specific Integrated Circuit

DSP: Digital Signal Processor

**DPR**: Dynamic Partial Reconfiguration

RM: Reconfigurable Module

HDL: Hardware Description Language

SoC: System on Chip

MC-CDMA: Multi Carrier Code Division Multiple Access

PSK: Phase Shift Modulation

xxxvi Abbreviations

**QAM**: Quadrature Amplitude Modulation

SDR: Software Defined Radio

ICAP : Internal Configuration Access Port PCAP : Processor Configuration Access Port

IP: Intellectual Property

DMA: Direct-Memory Access

OS: Operating System

GPIO : General-Purpose Input OutputAXI : Advanced EXtensible InterfaceGIC : Generic Interrupt Controller

SRAM: Static Random Access Memory

VHDL: Very high speed integrated circuit Hardware Description Language

# INTRODUCTION

## Context

Wireless communication was defined as the transmission and reception of signals by electromagnetic systems. It was initially used around 1890 in wireless telegraphy. In the 90's it was used mainly for the voice telecommunication which was known as cellular network. Today, researchers keep working on achieving best wireless communication performance in terms of data rate, coverage, and mobility.

In the last decade, wireless communication systems have greatly evolved in terms of mobility, covered range, and throughput. A lot of standards with different specifications, both in the physical layer (PHY) (bandwidth, throughput, and modulation encoding techniques) and media access control (MAC) layer, have been provided to meet different technical requirements and give access to new services. Nowadays, wireless communications systems are everywhere, in our homes, offices, metros, urban, and in space. Furthermore these systems are now used for machine to machine communication in an Internet of Things (IOT) to go beyond the standard Internet.

The wireless channel is one of the most challenging communication channels. Due to the characteristics of this channel, the existence of obstacles in the signal path, and the mobility of the end-nodes, the form of the transmitted signal will not be the same at the receiver side. Since the wireless channel is considered unstable, the wireless system at the end-node may be reconfigurable and some modules in the wireless communication chain could be reconfigured to optimize the usage of the available channel capacity. Also today, users are facing a huge diversity of communication networks and protocols that are generally very complex and heterogeneous. This is especially true for mobile devices that have to deal with multiple radio access technologies (Multi-RAT) during their mobility.

Nowadays the requirements of the applications used at the end-node consist in using the best available wireless standard. Throughput, delay, and other quality

of service parameters are variable due to the mobility of the user. This is effected by the characteristics of the wireless channel used by the wireless standard and the variable number of connected users to the wireless network. To achieve best performance, the end device should switch to the best available wireless standard.

In this context, it seems obvious that one could benefit from using reconfigurable wireless systems. The open questions are how and when reconfigurable radios should be reconfigured? Which parts of the wireless communication chain have to be reconfigured during runtime? What is the overhead of real time reconfiguration? Is it possible to have one reconfigurable chain for multiple wireless standards? How to decide which is the best standard and how to switch the communication through it?

In order to decide when and what to reconfigure in the communication chain, adaptive techniques were proposed to enable applying modifications in real-time to both PHY or MAC layers of a wireless system. Using these techniques, modifications are performed according to specific conditions and to the state of the communication channel within the overall network. This allows achieving the best performance by adapting and reconfiguring the communication system in real-time without interruption. The operation of switching between radio access technologies is denoted as vertical handover. Vertical Handover Algorithms (VHA) have been proposed to enable selecting the best available wireless communication system at the end-node. Based on multiple parameters coming from different layers, many simple and complex VHAs have been proposed to achieve better Quality of Service (QoS) or most power efficient communications. Machine learning algorithms are one of the promising techniques used in such VHAs to provide intelligence to the end-node device.

When a decision is made, the system needs to execute and reconfigure the communication chain. This reconfiguration step can be applied to software as proposed in Software Defined Radio (SDR). On the other hand, hardware reconfiguration of wireless communication systems seems also a promising solution for implementing adaptive techniques and systems dealing with multiple wireless standards. In this case, some system functions may be modified during runtime, while other functions continue to run without any interruption. Field Programmable Gate Arrays (FPGA)s constitute efficient circuits to implement such reconfigurable systems. Such devices are now sufficiently mature to implement very complex systems with a high level of performance. Partial Reconfiguration (PR) is one of the interesting features that has been added by FPGAs' vendors to ensure even more flexibility. PR provides the ability to reconfigure a specific modules on the FPGA during

Introduction 3

runtime. Furthermore, partial reconfiguration decreases the time needed to reconfigure parts of the circuit, and reduces its power consumption by considering only partial bit-streams instead of complete ones.

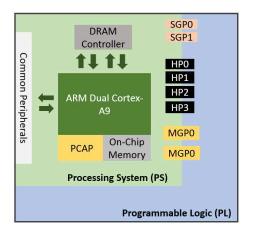

Another interesting feature in recent FPGA devices is the presence of embedded hard processor cores that are implemented with the hardware FPGA fabric, in the same chip. For example, the ZYNQ SoC devices from Xilinx feature a dual-core ARM Cortex-A9 based Processing System (PS) as well as a Programmable Logic (PL) within a single device. Compared to their soft core processors counterparts, these processors offer much more computing power and speed. SoC devices are appropriate for designing joined software and hardware (SW/HW) systems. The existence of such systems in the end-devices allows designing high performance smart communication systems.

In this context, it has become very interesting to consider a multi-standards device, capable of implementing several MAC/PHY layers within the same chip. In general, this is performed by implementing several radio access technologies, in parallel, within the same chip. This solution is obviously very costly and not satisfactory in terms of hardware resources usage. Moreover, only few protocols can be handled in this case.

It is important to understand and study the mechanisms of applying PR on ARM-FPGA platform in the context of reconfigurable wireless system. What are the requirements and needs for creating a reconfigurable wireless system on both software and hardware parts? How do these parts interact with each other and how the reconfiguration is managed? For that, PS modules have been proposed to control the PR operation on PL in context of wireless communication systems. It is also important to understand what should be taken into consideration in the hardware design when applying partial reconfiguration. In addition, some measurements should be done to extract specific parameters in order to evaluate the performance of the system. These parameters include the reconfiguration time, on-chip power consumption and reserved hardware resources. Also, it was interesting to perform real time measurements for PR power consumption.

To study the proposed system and in order to achieve measurements, a reconfigurable Orthogonal Frequency Division Multiplexing (OFDM) transmitter, which is considered as one of the most modulation schemes in current standards, has been implemented. Adaptive and PR techniques have been applied to reconfigure the implemented chain. As a case study, switching between WiFi-WiMax standards using PR has been considered and implemented and an unified chain for both standards was implemented. In addition, VHA based on adaptive scoring system

4 Introduction

for both standards was proposed. It was very interesting to benefit from machine learning algorithms such as Neural Network (NN) to improve the decision of the proposed VHA and make it more intelligent.

This thesis proposes to answer the questions by benefiting from the PR technique in the context of reconfigurable wireless communication systems on ARM-FPGA platform. In our research, we propose a general architecture for such type of systems. Our approach has been implemented and tested in specific scenarios. We have also run extensive experiments on our system to evaluate the resources, time, and power consumption of the proposed approach.

# Manuscript organization