# Efficient Virtualization of NUMA Architectures

Gauthier Voron

### ▶ To cite this version:

Gauthier Voron. Efficient Virtualization of NUMA Architectures. Operating Systems [cs.OS]. Sorbonne Université, Faculté des Sciences et Ingénierie, 2018. English. NNT: . tel-01947560v1

# $\begin{array}{c} {\rm HAL~Id:~tel\text{-}01947560} \\ {\rm https://hal.science/tel\text{-}01947560v1} \end{array}$

Submitted on 7 Dec 2018 (v1), last revised 22 May 2019 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# ÉCOLE DOCTORALE EDITE DE PARIS (ED130)

Informatique, Télécommunication et Électronique

### THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

SPÉCIALITÉ: INGÉNIERIE / SYSTÈMES INFORMATIQUES

Présentée par : Gauthier Voron

POUR OBTENIR LE GRADE DE :

DOCTEUR DE SORBONNE UNIVERSITÉ

SUJET DE LA THÈSE:

VIRTUALISATION EFFICACE D'ARCHITECTURES NUMA

SOUTENUE LE : 8 MARS 2018

DEVANT LE JURY COMPOSÉ DE :

Rapporteurs: R. Guerraoui Professeur, École Polytechnique Fédérale de Lausanne

L. RÉVEILLÈRE Professeur, Université de Bordeaux Examinateurs : V. QUÉMA Professeur, Université Grenoble INP

E. ENCRENAZ Maître de conférences, Sorbonne Université

P. SENS Professeur, Sorbonne Université G. THOMAS Professeur, Télécom SudParis

# REMERCIEMENTS

Lors d'un cours de master, Gaël Thomas soutint que la pièce la plus importante d'un laboratoire était la salle café. À l'époque, je mis cette digression sur le compte de l'addiction notable de mon professeur pour la caféine. Je me rend compte aujourd'hui à quel point l'échange et la communication, en salle café ou ailleurs, sont importants, car la recherche est avant tout un effort collectif. Il est donc naturel de remercier ici tous ceux qui ont contribué, directement ou pas, à ces années de recherche, pour l'aide, le soutien ou le café qu'ils m'ont apporté.

Je tiens tout d'abord à remercier mes directeurs de thèse, **Gaël Thomas** pour son encardement suffisamment strict pour me permettre de progresser et suffisamment souple pour me laisser maître de ma thèse, ainsi que **Pierre Sens** qui a su observer mes travaux avec assez de recul pour m'apporter les conseils et le bon sens qui manque parfois cruellement aux doctorants trop concentrés sur leur tâche. Leur soutien et leurs encouragements m'ont aidé à surmonter de nombreuses déconvenues. Nos conversations furent pour moi une source de satisfaction et d'enrichissement, tant sur un plan scientifique et technique que sur un plan humain.

Merci ensuite à **Vivien Quéma** sans qui le sujet même de cette thèse aurait été bien différent. Sa capacité à identifier les pistes de recherche prometteuses fut la bienvenue à de nombreuses reprises. Merci également aux membres de mon jury et notamment aux deux rapporteurs de ce travail, **Rachid Guerraoui** et **Laurent Réveillère** qui ont accepté de prendre du temps sur leurs propres recherches pour relire et évaluer ce manuscrit.

Je souhaite également remercier tous les membres du LIP6, en particulier **Julien Sopena** pour son enthousiasme à pousser les idées les plus improbables jusqu'à leurs limites. Le dévouement dont il fait preuve en tant qu'enseignant a largement contribué à mon intérêt pour ce domaine de recherche, d'abord en tant qu'étudiant puis comme enseignant. Merci à **Marc Shapiro** pour ses judicieux conseils en matière d'exposé, ils me furent d'une aide précieuse quand vint l'heure de présenter mes travaux à la communauté scientifique. Merci à **Yann Thierry-Mieg** dont les questions aussi simples qu'incessantes me forcèrent à prendre le recul nécessaire vis-à-vis de mes recherches.

Viennent ensuite les autres membres des différentes équipes Delys, Move et Whisper du LIP6 et de l'équipe HP2 de Télécom SudParis avec lesquels j'ai eu la chance de travailler. Ainsi je tiens à remercier **Hakan Metin**, d'abord ingénieur puis doctorant mais toujours spécialiste des usines à gaz et **Damien Carver**, grand amateur de *checksum* et convaincu

qu'il vaut parfois mieux être un problème qu'une solution. Un grand merci à **Alexis Lescouet**, le seul doctorant avec qui j'ai pu échanger sur l'absurde comportement du bit EFER [SVME]. Merci également à **Ilyas Toumlilt** qui a compris l'intérêt du +2; au Stéphanois **Francis Laniel** qui connaît la beauté du Perl; à **Maxime Bittan** qui mieux que personne sait marier vidéos et PDF ainsi qu'à **Lyes Hamidouche** et à **Florent Coriat** nos spécialistes réseau. Merci aussi à Maxime Lorrillere, Antoine Blin, Florian David, Rudyar Cortés, Redha Gouicem, Cedric Courtaud et Lucas Serrano avec qui j'ai partagé maintes conversations passionantes.

Le travail du doctorant ne s'arrête pas aux portes du laboratoire et pour cette raison je tiens bien sûr à remercier ma famille et mes amis. Vous avez célébré avec moi les petites victoires qui parsèment la recherche et m'avez aidé à aller de l'avant quand je baissai les bras. Merci à la **Team Njut**: Geoffroy Blesbois, Alexis Barbier, Lou Laurent et François Rollot. Vous avez trouvé la patience de supporter mes élucubrations *geeks* sans queue ni tête en sachant qu'une oreille attentive et une bonne bière m'aideraient sûrement à y voir plus clair.

Finalement je tiens à remercier **toute ma famille** pour ses encouragements constants durant toute cette thèse et depuis bien avant cela. Grâce à votre soutien inconditionnel, j'ai pu étudier ce domaine qui me passionne et m'investir dans cette tâche de longue haleine. Ce travail que j'achève après plus de trois ans, c'est en grande partie à vous que je le dois.

À tous, merci infiniment!

# RÉSUMÉ

Alors que le surcoût de la virtualisation reste marginal sur des machines peu puissantes, la situation change radicalement quand le nombre de cœur disponible augmente. Il existe aujourd'hui des machines de plusieurs dizaines de cœurs dans les *data centers* dédiés au *cloud computing*, un modèle de gestion de ressources qui utilise largement la virtualisation. Ces machines reposent sur une architecture Non Uniform Memory Access (NUMA) pour laquelle le placement des tâches sur les cœurs ainsi que celui des données en mémoire est déterminant pour les performances.

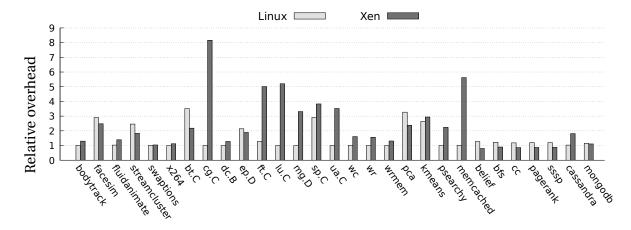

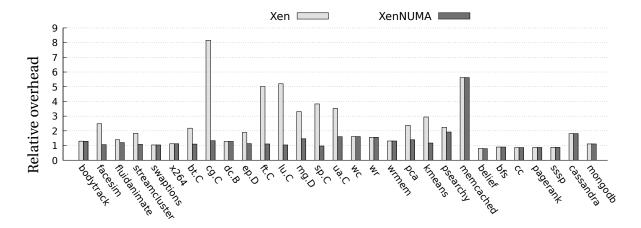

Cette thèse montre d'une part comment la virtualisation affecte le comportement des applications en les empêchant notamment d'utiliser un placement efficace de leurs données en mémoire. Cette étude montre que les erreurs de placement ainsi provoquées engendrent une dégradation des performances allant jusqu'à 700%.

D'autre part, cette thèse propose une méthode qui permet la virtualisation efficace d'architectures NUMA par la mise en œuvre dans l'hyperviseur Xen de politiques génériques de placement mémoire. Une évaluation sur un ensemble de 29 applications exécutées sur une machine NUMA de 48 cœurs montre que ces politiques multiplient les performances de 9 de ces applications par 2 ou plus et diminuent le surcoût de la virtualisation à moins de 50% pour 23 d'entre elles.

# **ABSTRACT**

While virtualization only introduces a negligible overhead on machines with few cores, this is not the case when the number of cores increases. We can find such computers with tens of cores in todays data centers dedicated to the cloud computing, a resource management model which relies on virtualization. These large multicore machines have a complex architecture, called Non Uniform Memory Access (NUMA). Achieving high performance on a NUMA architecture requires to wisely place application threads on the appropriate cores and application data in the appropriate memory bank.

In this thesis, we show how virtualization techniques modify the applications behavior by preventing them to efficiently place their data in memory. We show that the data misplacement leads to a serious performance degradation, up to 700%.

Additionally, we suggest a method which allows the Xen hypervisor to efficiently virtualize NUMA architectures by implementing a set of generic memory placement policies. With an evaluation over a set of 29 applications on a 48-cores machine, we show that the NUMA policies can multiply the performance of 9 applications by more than 2 and decrease the virtualization overhead below 50% for 23 of them.

# **CONTENTS**

| Co | nten  | ts                                      | X  |

|----|-------|-----------------------------------------|----|

| 1  | Intro | oduction                                | 1  |

| 2  | State | e of the Art                            | 7  |

|    | 2.1   | Multicore architectures                 | 8  |

|    |       | Architecture details                    | 9  |

|    |       | Related challenges                      | 13 |

|    | 2.2   | Non Uniform Memory Access architectures | 20 |

|    |       | Architecture details                    | 21 |

|    |       | Linux NUMA policies                     | 26 |

|    |       | Related challenges                      | 27 |

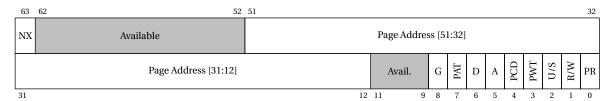

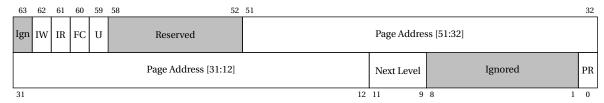

|    | 2.3   | System virtualization                   | 34 |

|    |       | Technical details                       | 35 |

|    |       | Architecture details                    | 38 |

|    |       | Related challenges                      | 41 |

|    | 2.4   | Software settings                       | 47 |

|    | 2.5   | Conclusion                              | 48 |

| 3  | The   | Well-Known Bottlenecks                  | 49 |

|    | 3.1   | The Virtualized I/O Overhead            | 49 |

|    |       | Hardware Emulation                      | 49 |

|    |       | The I/O Memory Management Unit          | 50 |

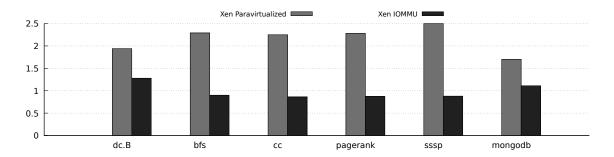

|    |       | Evaluation of IOMMU                     | 53 |

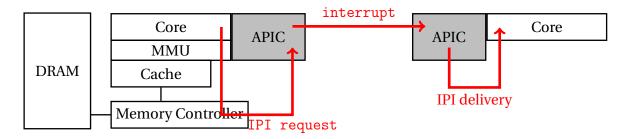

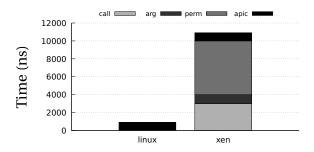

|    | 3.2   | The virtualized IPI overhead            | 54 |

|    |       | Usage of the IPI                        | 54 |

|    |       | Implementations of IPI                  | 55 |

|    |       | The libactive library                   | 57 |

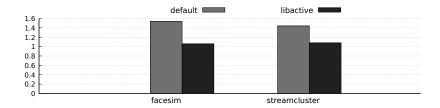

|    |       | Evaluation of vIPI                      | 58 |

|    | 3.3   | The Xen load balancer                   | 59 |

|    |       | Completely Fair Scheduler               | 60 |

|    |       | Credit Scheduler                        | 60 |

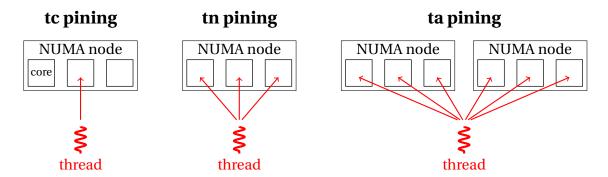

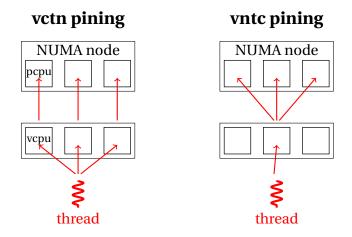

|    |       | The libpin                              | 60 |

|    |       | Evaluation of pining scheme             | 62 |

*CONTENTS* xi

|    | 3.4   | Conclusion                              | 64         |

|----|-------|-----------------------------------------|------------|

| 4  | The   | NUMA Bottleneck                         | 65         |

|    | 4.1   | NUMA policies under study               | 65         |

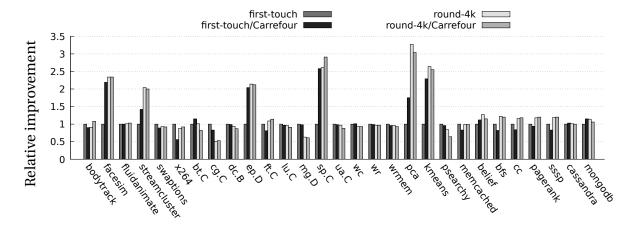

|    |       | Comparison of NUMA policies effects     | 66         |

|    |       | The NUMA policy selection metric        | 66         |

|    | 4.2   | Current hypervisor NUMA management      | 69         |

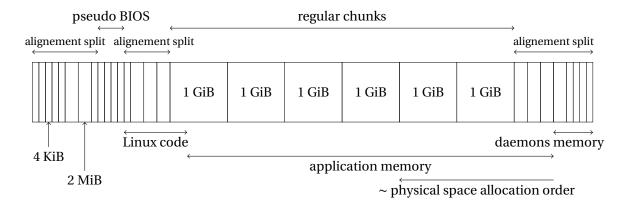

|    |       | The default round-1G policy             | 69         |

|    |       | Huge pages and splinterring             | 70         |

|    |       | Evaluation of the default policy        | 71         |

|    | 4.3   | Conclusion                              | 72         |

| 5  | Virt  | ualization of NUMA Architectures        | <b>7</b> 3 |

|    | 5.1   | Improved hypervisor NUMA management     | 74         |

|    |       | The Xen implementation of round-4K      | 75         |

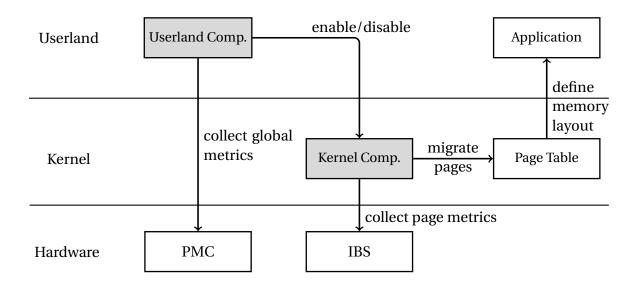

|    |       | The Xen implementation of Carrefour     | 75         |

|    |       | Limitations of PEBS with virtualization | 79         |

|    |       | The Xen implementation of first-touch   | 79         |

|    |       | Limitations of first-touch with IOMMU   | 82         |

|    |       | The Xen NUMA policy selection interface | 82         |

|    | 5.2   | Evaluation                              | 83         |

|    |       | Evaluation of vNUMA on a single machine | 83         |

|    |       | Evaluation of vNUMA on several machines | 87         |

|    | 5.3   | Conclusion                              | 88         |

| 6  | Con   | clusion                                 | 91         |

|    | 6.1   | Future works                            | 92         |

|    | 6.2   | Perspectives                            | 93         |

| Bi | bliog | raphy                                   | 95         |

CHAPTER

# INTRODUCTION

In 1965, Gordon E. Moore publishes a short paper, named "Cramming More Components onto Integrated Circuits" [50], containing one of the best-known conjectures in computer science: "The number of components per integrated circuit will double every 18 months". Until the early 2000s, this conjecture nonetheless was verified, but also had the effect, as a fortunate consequence, to rise up the clocks frequency. In these years, simply waiting for the next generation hardware was sufficient to increase the software performance. However, physical constraints, such as thermal dissipation difficulties, prevent CPU manufacturers to keep increasing the clock frequency. Thus, until this year (2018), the Moore conjecture is still verified since the number of transistors in a chip actually keeps doubling. The manufacturers then use these additional components to provide more than a computing unit per chip, naming them *cores*<sup>1</sup>. As a result, it is common nowadays to have a dozen cores in a single personal computer.

While the increasing number of cores in a chip makes it able to execute more instructions in a given time, these instructions have to be executed in parallel. This constraint drastically changes the conditions for software to gain performance on new hardware. A programmer now needs to design its algorithms to be parallelizable so when the number of core increases, the amount of instruction executed in parallel increases too. Parallelizing a program is, however, a difficult task as it generally implies to add synchronization mechanisms for the different cores to coordinate with each other.

Furthermore, increasing the number of core worsens an already existing problem. As each core needs to access the memory, either to fetch instructions or to manipulate data, adding more cores puts more pressure on the memory system. This issue was already known before the 2000s as the memory system clock was not as fast as the cpu clock, and then unable

<sup>&</sup>lt;sup>1</sup>In this document, we use terms *CPU* and *core* interchangeably as they both designate some circuitry able to execute a sequence of instructions.

to satisfy every CPU request. The hardware designers used to add fast memory caches to absorb the cost of the memory accesses. With more than a dozen cores, however, even this cache mechanism is not sufficient to contain the memory load and the memory system saturates. This gap between the cores needing more information to work and a memory system unable to scale up to serve the cores requests led to a major modification in the computer's architecture. As the processor has been redesigned to contain multiple cores when it became impossible to improve a single processing unit performance, the memory system now contains multiple memory banks and controllers as it became impossible to speed up a single memory unit. Because of this distributed aspect of the memory, the access time to data is not uniform anymore and depends on where it is placed on the computer. This architecture is thence called Non-Uniform Memory Access (NUMA) architecture. As a result, the performance of a process is today constrained by the parallelization of its algorithms but also by a good dispatch of its data.

In parallel to the evolution of hardware architecture, the hardware usage also changes with the rise of cloud computing. Indeed, as the hardware becomes more powerful, it executes more complex tasks more quickly. Nevertheless, this hardware power and complexity are nothing but a waste of processing power if there is no consuming task to execute. As this waste of electricity also means a proportional waste of money, a common practice is to share the same hardware between multiple users to maximize the computer usage. This way of using computers is not particularly new, the UNIX operating system already was multiuser. Nowadays, however, this tendency is so widespread that tens of completely unrelated users can share the same hardware somewhere in a data center owned by a cloud provider. As the users generally have different needs, such as what operating system they want to use, the cloud providers usually emulate several virtual machines on their powerful hardware and rent them to users. With this technology, called virtualization, the same hardware can be shared between several users where each of them has the illusion to control its own computer with the freedom to configure it to suit its needs.

The virtualization technology and the NUMA architecture both evolved independently to tackle different issues: reduce hardware usage cost for the first, produce more powerful hardware for the second. Nonetheless, nowadays, the hardware used in the cloud data centers uses NUMA architectures and thus, the virtual machines are executed atop such hardware. The virtualization software has, however, not been designed for NUMA architectures. Because of this poor integration, the applications executed inside a virtual machine running atop of a NUMA architecture may have low performance. As the combined use of NUMA architectures and virtualization is relatively recent, because of the cloud computing emergence, only a few works [56, 44] address this performance issue.

My PhD thesis addresses the challenge of efficiently virtualizing a NUMA architecture in a cloud infrastructure. In detail, my research is twofold. On the first side, my research has the goal of measuring how virtualization behaves on a NUMA architecture, and how and why a NUMA architecture changes the performance of virtualized applications. On the other side, my PhD thesis proposes new techniques to efficiently use NUMA architectures when the hardware is virtualized. The contributions of this research are:

- A systematic performance analysis of a large set of applications from different benchmarks suites on a large NUMA virtualized system.

- For each already known performance bottleneck due to virtualization, the implementation of a solution showing that the overhead is not affected by the NUMA architecture.

- An evaluation of the already known NUMA memory management algorithms in operating systems and the proposition of a metric to choose which algorithm provides the best performance.

- The adaptation of the main NUMA memory management algorithms in operating systems to a virtualized system, an implementation of them on the Xen hypervisor and an evaluation of this implementation with a representative set of 29 applications.

Each contribution is explained in the following chapters of this document. These contributions, as well as the experimental evaluations lead to the following conclusions:

- With a single virtual machine spanning 48 cores, our systematic performance analysis shows that, in the set of applications we choose, the overhead is mainly caused by the I/O virtualization, the inter-processor interrupts (IPI) virtualization, and a bad NUMA memory management by the hypervisor.

- While the I/O and IPI virtualization causes important performance losses, the existing approaches to solve these issues give good results, even on a 8 nodes NUMA hardware. Additionally, a third supposed bottleneck, the thread and virtual CPU load balancing only causes marginal performance losses on a NUMA architecture.

- The metric we propose allows the user to choose the best NUMA memory management algorithm by executing the application once. This algorithm is nonetheless the best one for a native system but is also the best option in most cases for a virtualized system.

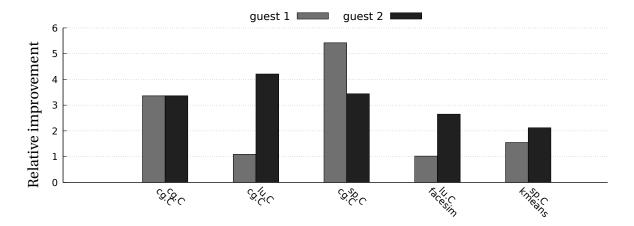

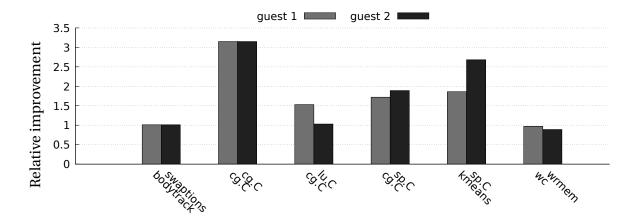

- The adaptation and evaluation of the main NUMA memory management algorithms in operating systems to virtualized systems show that the current Xen hypervisor NUMA management is highly inefficient. More precisely, with a single virtual machine spanning 48 cores, using an efficient NUMA policy divides the completion time of 9 applications by more than 2, with an observed maximum improvement of 6 times. With consolidated workloads of multiple virtual machines, among the 11 tested configurations, using an efficient NUMA policy reduces the completion time of at least one virtual machine by more than 2 in 9 cases.

The remaining of this document is organized in 5 chapters. Chapter 2 describes the state of the art for NUMA architectures and system virtualization, Chapter 3 focuses on the already known virtualization bottlenecks, Chapter 4 focuses on the NUMA architecture effects on

performance for both native and virtualized systems, Chapter 5 describes our solution to implement a NUMA management in the Xen hypervisor as well as an evaluation of this solution and Chapter 6 concludes the thesis. More precisely:

### State of the Art

Chapter 2 describes the existing work related to NUMA architectures and system virtualization with the aim to show that on one side, achieving good performance on a NUMA architecture requires explicit communication and resource management, while on the other side, the virtualization, by design, hides hardware and software aspects, thus preventing explicit approaches. Prior to focusing on NUMA architecture details, the first part describes the general multicore architecture and the main mechanisms for several cores to synchronize. This part also presents some previous works that aim to improve multicore performance and shows that a way to achieve that is to not use the synchronization mechanisms provided by the hardware and instead make the synchronization explicit in the software. The second part describes some key characteristics of the NUMA architecture as well as some well-known NUMA memory management policies. This part also describes related works that aim to improve performance by exploiting the knowledge of the NUMA topology. The last part briefly presents the different virtualization techniques and gives additional details about the techniques we focus on in this research, especially about memory management. This part also presents some previous works addressing the issues caused by virtualization.

### The Well-Known Bottlenecks

Chapter 3 evaluates three possible performance bottlenecks for virtualized applications. The first bottleneck is the I/O virtualization which is described at an architectural level in the first part. We show that we can remove this bottleneck by using a dedicated part of the hardware implemented in modern computers. In the second part, we describe how this hardware part works and interacts with the memory management circuitry. In the third part, we evaluate the effects of this hardware part on the applications performance. The second bottleneck is the inter-processor interrupts virtualization. We first describe how the IPI mechanism is implemented in a native system, then in a virtualized one and show what causes the overhead. We then describe a solution to remove the vIPI overhead, based on previous works. We finally evaluate the performance of applications when using this solution. The third supposed bottleneck is the load balancer. A first part describes how the hypervisor and guest operating system load balancers work. A second part describes a tool we use to evaluate the impact of the load balancer on application performance by constraining the decisions it can take. A third part evaluates the impact of the load balancer decisions on the applications performance.

### The NUMA Bottlenecks

Chapter 4 focuses on the impact of the NUMA architecture on application performance in both native and virtualized systems. A first part evaluates the importance of the NUMA memory management on application performance on a native system. This is done by comparing the effects of the NUMA memory management algorithms described in Chapter 2 on application execution times. This part also describes the NUMA policy selection

metric and evaluates its efficiency. A second part describes the NUMA memory management algorithm used in the Xen hypervisor. We also describe what effects this algorithm has on the memory accesses of the virtual machine. This algorithm is then evaluated by comparing the applications performance executed in Xen and in a native system.

### **Virtualization of NUMA Architectures**

Chapter 5 describes how we implement an efficient NUMA management in the hypervisor. In the first part, we show how we adapt each of the NUMA memory management algorithms described in Chapter 2 to a virtualized configuration. We also outline the limitations we encountered while adapting these NUMA policies and how a cloud user could use them through a policy selection interface. Then, the second part evaluates the performance gains of the applications when using these NUMA memory management algorithms in a virtualized system. We evaluate both single virtual machine configurations and consolidated virtual machine configurations.

### Conclusion

Chapter 6 concludes the thesis with a summary of the lessons learnt about the virtualization of NUMA architectures. The thesis shows that combining the system virtualization technology with the NUMA architecture raises resource management issues. When the architecture becomes complex, like with NUMA hardware, the software layer that manages the hardware resources has to know the hardware details so it can use it efficiently. The system virtualization technology isolates the guest operating system from the hardware, preventing it from taking efficient decisions. We show that we can overcome this issue by shifting the NUMA management from the guest operating system to the hypervisor. Additionally we show, with an implementation in the Xen hypervisor and with an evaluation over a large set of applications, that existing NUMA management techniques are as effective in the hypervisor as in an operating system. Moreover, we show that a hypervisor that uses the appropriate NUMA policies executes NUMA virtual machines with no overhead. This chapter also discusses future work and perspective. The future work that we propose focuses on three axes: (i) increase the performance of already implemented NUMA policies, (ii) implement additional NUMA policies and (iii) compare our approach to address the virtual NUMA management to other possible approaches. In the perspective part, we look at this thesis from a larger point of view and discuss the implications of this work and of the lessons we learnt.

# CHAPTER CHAPTER

# STATE OF THE ART

My PhD thesis addresses the challenge of efficiently virtualizing a NUMA architecture. This chapter presents the existing works in both NUMA architecture and system virtualization fields with the following goals:

- Describe the concepts related to NUMA architectures and explain how to reach good

performance on this hardware. Specifically, this chapter shows that the more the end

user program knows about the NUMA topology and the hardware details, the more it

can use the machine efficiently.

- Describe the concepts related to system virtualization and especially to the virtualization of memory. In particular, this chapter shows that, by design, nowadays virtualization isolates the virtualized system from the hardware and hides the topology details.

Achieving good performance on a NUMA hardware requires an explicit access to the hardware information that, precisely, the system virtualization hides to the guest system. This contradiction makes the efficient virtualization of NUMA architectures a challenging task.

As an introduction to NUMA architectures, this chapter presents the general multicore architectures. Indeed, the NUMA architecture is a special kind of multicore architecture. It is then necessary to understand how an application can be efficient on a multicore hardware. The first part of this chapter thus focus on the specificities of multicore architectures and how a poor awareness of these characteristics can lead to scalability issues. This first part also presents existing works that address these performance issues.

Interestingly, this chapter shows that, as for NUMA architectures, the more an application knows about the multicore hardware details, the more it can scale. Moreover, the third

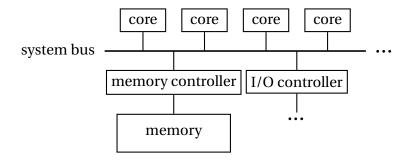

Figure 21: The architectural view of an multicore architecture

part of this chapter, dedicated to system virtualization, shows that existing works related to multicore virtualization address issues caused by the opacity enforced by the virtualization. This opacity prevents the virtualized software to use the hardware details to scale. The parallel we can make between multicore and NUMA virtualization tends to show that the virtualization opacity causes issues that require important research efforts.

### 2.1 Multicore architectures

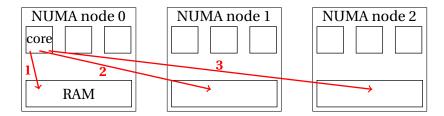

As stated in Chapter 1, in order to use an increasing number of transistors, modern processors are built from several computation units called *cores*, each executing a different instruction sequence. In this section, we focus on multicores without considering the NUMA architectures. We consider thus a small multicore, in which the cores, the devices and the memory are all connected to a single bus. Figure 21 illustrates this architecture. This (relatively simplified) architecture is currently used in desktops, laptops and smartphones when the processor provides several cores.

On this architecture, the main performance concern for a program is to efficiently exploit all the available cores. To this end, a common method is to split the program algorithm in smaller and independent tasks. Each of these tasks are executed on different cores. It is, however, necessary to collect the results of these tasks and to merge them in order to obtain the final result. Moreover, it may be impossible to split an algorithm into completely independant tasks. Instead, some computations can only be decomposed in mostly independant tasks that must occasionally synchronize. Since these synchronization steps may limit the scalability of applications, we study them in this section.

This section first presents the synchronization mechanisms provided by modern multicore architectures, namely the MOESI cache coherency protocol, and the inter-processor interrupts. For each of these mechanisms, this section describes its purpose, how it works and what performance issue it can cause when used without caution. Some existing works focusing on the performance improvement on multicore architecture are then presented with a specific emphasis on how the described solutions use, or avoid using, the implicit multicore synchronization mechanisms.

### Architecture details

The hardware provides several synchronization mechanisms, but two of them are especially important in the context of my study. The first mechanism is the MOESI cache coherency protocol that allows all the cores of a system to have the same view of the memory, even if the main memory data is outdated with respect to some core local cache. This first mechanism is implicit since the program has no explicit control on this coherency, except to not work on the same data from different cores. The second mechanism is the inter-processor interrupt: the way for cores to asynchronously notify other cores that an event occurred. As opposite to the MOESI protocol, the inter-processor interrupt is an explicit mechanism since the communication aspect, as a synchronization mechanism is ultimately a form of communication, is explicit.

### The MOESI protocol

As a processor consumes instructions much faster than the memory can serve data<sup>1</sup>, chip manufacturers include a cache hierarchy between the processing unit and the memory controller. When the processor modifies the data, it stores them in the cache and data are eventually, at an unpredictable time, committed to memory. During the time the modified data are in the cache but not yet committed to the main memory, the main memory stores an outdated state of the data. On a monocore architecture, this is not an issue since the only accessing core asks the cache controller for the data before to ask memory. The unique core of the system is thus sure to fetch the most up-to-date state of the data. On a multicore architecture, each core has its own cache hierarchy, at least for the first levels of cache. Each of these caches is able to store modified states of data and commit them to the main memory, possibly in a different order than the writes occurred. This breaks the sequential consistency property of the memory.

To overcome the resulting consistency issues, the hardware implements a cache coherency protocol. When a cache controller is asked for a data item, it ensures that the state it has of this data item is the most up to date state known by any cache controller in the system. To do so, modern cache controllers implement a distributed reader-writer lock algorithm. Several versions of this algorithm exist, but they all follow these two principles:

- Several cache controllers can hold the same data item in parallel as lon as none of them try to modify the data item. When asked by a core to read a data item, a cache controller thus probes the other cache controllers for the sought data item. The other controllers can share it without breaking the sequential consistency.

- Only a single cache controller can modify a data item at a given time. When asked by

a core to modify a data item, a cache controller must ensure that none of the other

controllers hold the data item. To this end, this cache controller sends invalidation

requests to the other controllers for the modified data item. The other controllers can

later probe for this data item and fetch the modified state.

<sup>&</sup>lt;sup>1</sup>On today hardware, a single core can consume data 100 times faster than the main memory can serve it.

|                 | Not last writter | Last writter |

|-----------------|------------------|--------------|

| Exclusive owner | Exclusive        | Modified     |

| Sharing owner   | Shared           | Owned        |

| Not owner       | Invalid          |              |

Table 21: MOESI States

A cache controller conforming to these principles ensures that it always provides the most recent version of a data known in the memory system. By doing so, the cache controllers ensure the memory is sequentially consistent.

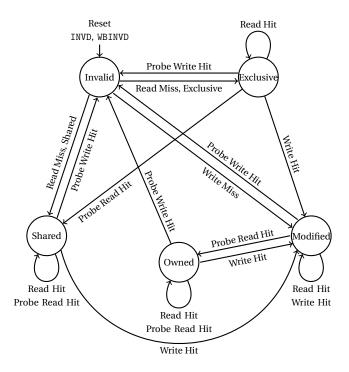

In addition to preserve the memory sequential consistency, the cache controllers try to minimize the number of communications. Indeed, accessing to the cache is a frequent operation for a core. Hence, broadcasting to every cache controller of the system each time a core asks for a data item would be inefficient and not scalable. A common way to provide a reader-writer lock semantic with a low number of required communcation is the MOESI procotol. This protocol defines a set of possible states a data item can have. The state of a data item is relative to a cache controller. Different cache controllers in the system may thus associate different states to the same data item. The state of a data indicates to the cache controller if the data can be read or written, or if the cache controller must communicate with the other controllers first. The MOESI protocol defines five states. One of them, the Modified state represents the read-write acquisition of the lock. Three other ones, the Exclusive, Shared and Owned states represent the read-only acquisition of the lock. The last one is the Invalid state that represents the not acquired lock.

From a communication point of view, the Invalid state indicates that the data item is not present in the local cache and that it is necessary to probe all the other caches, then if none of them holds the latest state of the data item, fetch it from main memory. The four remaining states indicates (i) if the local cache holds the unique copy of the data item outside of the main memory and (ii) if the local cache is the last one that has modified the data item. The first indication is useful to avoid communications: if the local cache is the only one to work on a data item, there is no need to probe the other caches when reading or writing the data item. The indication of what is the last modifier of a data item is used to know if the data item must be committed from the local cache to the main memory if the cache is flushed. Table 21 presents the MOESI states and what they indicate.

Excepted if a data is Invalid, a cache controller can always read it without changing its state. Reading a data with an Invalid state leads the cache controller to probe the other caches. If one other cache contains the data, it is fetched with the Shared state, otherwise it is read from the main memory and has the Exclusive state. Since the local cache does not modify the data, both the Exclusive and the Shared state indicate the local cache is not the last writer. Modifying a data from any state puts it in the Modified state, which effectively indicates the local cache is the last modifier. The Modified state also indicates the local cache is the exclusive owner. Indeed, when a cache modifies a data, the other copies become outdated and are invalidated by a probe. The probes are not sent if the data was in the

Figure 22: MOESI State Transitions

Exclusive state since no copy could exist in this case. If a cache owns a data in the Exclusive state and another cache probes to read this data, it goes in the Shared state. If a cache owns a data in the Modified state and another cache probes to read this data, it goes in the Owned state. The Owned state indicates that the data is shared between several caches but the last writer on this data is local cache. The local cache is then responsible to commit the data to main memory if the cache is flushed. Beside this, there is no difference with the Shared state. Figure 22 summarizes the transitions between the MOESI states.

By conforming to the MOESI protocol, the cache controllers hide the complexity of hardware to the cores. Whereas the memory system is composed of the main memory and of several caches, the cache controllers expose a flat topology to the cores. While this simplifies the task of programmers, ignoring the communications a memory access can cause may lead to produce highly inefficient applications. These are typical examples of hidden communication inefficiencies.

- False sharing: If two or more variables are packed in a small address range, they may

be considered by the cache controllers as a single data. If these variables are modified

by different cores, the data keeps moving from a cache to another, causing a lot of

costly communications.

- Migration cost: It is frequent that several tasks update successively the same data structure. If different cores execute these tasks, even one by one, the data has to

migrate from one cache to another, again causing costly communications.

Ticket lock: A simple implementation of a spinlock is the ticket lock where several

cores spin reading the same variable. This variable is updated at each lock release. If

the lock is highly contended, each release causes an invalidation for all the waiters,

which then broadcast probe requests. If the lock is frequently released, it causes a

massive amount of useless communications.

The downside of the cache coherency protocol is that, by hiding the communcation caused by memory accesses, it generates a high number of messages on the system bus and makes the cores spend a lot of time stalled, waiting for cache controllers answers. As presented in Section 2.2, this phenomenon worsens on a NUMA architecture where the number of cores is higher and even the main memory is distributed. The issues related to the MOESI protocol is also a good example of the performance overhead an application may encounter if it does not take the hardware details into account, which is the case for virtualized software as we explain in Section 2.3.

### **Inter-processor interrupts**

The MOESI protocol and the cache coherency mechanisms in general allow the core to communicate by exchanging data. Synchronization, however, requires that a core signals an event to one or many other cores. This can be done by using only memory, as for the spinlocks. This method, however, has two drawbacks. First, a waiting core has to spin on a memory location and to continuously pull a possible update issued by the signaling core. This constant pulling causes a waste of CPU cycles and, despite the modern processors energy saving instructions, a waste of energy. Then, since a processor can only pull with this method, it is impossible for a core to asynchronously notify another core of an unexpected event.

In order to provide a push notification mechanism, modern processors provide the notion of interrupt. Conceptually, an interrupt is a message emitted by a device and received by one or several cores. When the core receives the message, it reacts by executing some code defined by the system prior to the reception. When the core has executed this code, it continues its previous execution. This mechanism can be used by I/O devices to signal that an I/O operation occured, for instance, a disk controller has finished transfering a disk sector into main memory. Additionally, on modern hardware, a core can stop fetching new instructions and halt. Once halted, a core only consumes a very low amount of energy. The reception of an interrupt wakes a core up and allows it to fetch instructions again.

A special kind of interrupt is the inter-processor interrupt (IPI). A core can issue an IPI to notify another core that some system defined event should be handled. To indicate precisely the nature of the event, it is common for the sending core to store information in a well known memory location that the receiving core can read upon receiving the interrupt. In addition, the sending core sometimes needs to be sure the target core has handled the event before to continue its execution. In this case the sending core can use a pull method, as spinning on an acknowledgement memory location.

On the architecture we use, the IPI mechanism goes through a special device called the Advanced Programmable Interrupt Controller (APIC). There is one APIC per core, included in the processor chip. Sending an IPI is thus an extremely fast operation since it does not require to acquire the system bus or any circuitry shared by the other cores. For security reasons, however, it is common for the operating system to restrict the APIC usage to the kernel only.

The inter-processor interrupts are thus an explicit communication mechanism. As opposite to the cache coherency mechanism, the system programmer is fully aware of every transmitted message. However, since the access to the APIC, and thus the ability to send IPI, is restricted to the kernel code, application programmers cannot use this mechanism explicitely. Additionally, the kernel programmers assume that sending an IPI is a fast, almost instantaneous, operation and then use it in critical path code, such as synchronization primitives provided to applications. Section 3.2 shows that sending an IPI can be a slow operation in a virtualized system and explains how this incorrect assumption reduces the application performance.

### **Synthesis**

In this part, we show that modern multicore hardware provides several mechanisms for the different cores to communicate and synchronize. Some of these mechanisms, like the cache coherency MOESI protocol, are implicit: they hide hardware complexity to the end programmer by presenting a simple hardware with more convenient properties, like sequential consistency. Some of these mechanisms, like the IPI, are explicit: they allow the programmer to deal with the hardware complexity and to exploit it. These two kinds of mechanisms have a cost. The only difference is that the programmer is most likely to have this cost in mind when dealing with explicit mechanisms than with implicit ones.

## **Related challenges**

In the previous section, we describe several communication mechanisms provided by multicore architectures. The study of these mechanisms is an introduction to the specificities of the NUMA architectures. In this section, we present works focusing on how to exploit or deliberately avoid exploiting these communication mechanisms in order to improve performance. These works only address inter-core communication issues. Especially, this section does not present works addressing cache pollution issues or other multithread related issues, as these are not specific to multicore architectures.

Table 22 enumerates the works we present. For each of them, we present the issue they address and the approach they use. We can classify the addressed issues in two categories: (i) contention issues where too many cores access the same resource at the same time, which cause access serialization, (ii) hardware related issues where there is no contention but a naive usage of the hardware leads to hidden expensive operations. We can also characterize the used approach by looking the amount of inter-core communication it induces:

| Solution           | Issue                         | Approach             | Exposure |  |

|--------------------|-------------------------------|----------------------|----------|--|

| Remix              | Hardware MOESI awareness Hide |                      | Hidden   |  |

| Scalloc            | Contention                    | MOESI awareness      | Hidden   |  |

| Scanoc             | Contention                    | + Private data space | Hilluten |  |

| Sloppy Counter     | Hardware                      | Private data space   | Hidden   |  |

| Sloppy Counter     | Haluwale                      | + Lazy merging       |          |  |

| The Multikernel    | Hardware                      | Private data space   | Explicit |  |

| The Factored OS    | Hardware                      | Share nothing        | Explicit |  |

| The Scalable       | Contention                    | No communication     | Explicit |  |

| Commutativity Rule | Contention                    | No communication     | Explicit |  |

Table 22: Works related to multicore architectures

**MOESI awareness** These approaches use the hardware efficiently, making sure to not generate unnecessary communications between the cache controllers. They consider worst-case scenarios where a lot of cache invalidation occurs but could be avoided, for instance, with a different memory layout. Except for these specific worst cases, the application still relies on cache coherency.

Private data space The different cores only work on their own data located in a memory zone they access exclusively. By avoiding to share data, the cores avoid to synchronize by cache coherency messages. The software can however use the memory as an explicit communication channel between cores. Several data spaces can be merged on demand. Communicating by memory is efficient but requires that a cache coherency protocol is implemented by hardware. Additionally, communicating by memory is not well suited for asynchronous notifications.

**Share nothing** The cores cannot share memory. The cores then do not exchange cache coherency messages. The cores can, however, communicate by explicit channels, like IPI or I/O. Such approaches do not require a cache coherency protocol to be implemented by hardware. It is then appropriate to be used in large scale systems with hundreds of cores and even in distributed systems.

**No communication** The system is designed so there is no need for the cores to communicate. This approach is the most scalable but also the most compelling. Indeed, using this approach may require to change the design of the application at a high level.

In addition to the *Issue* and *Approach* criteria, Table 22 indicates in the last column if the presented work hides the hardware details to the end user application or if it exposes them.

### Remix

In a multicore system, several cores sharing data need to synchronize. This synchronization causes inter-core communication and often worsens the application performance. By contrast, if each core works on its own data, there is no need to communicate. In modern processors, the cache controllers work on data item of fixed size, called cache line. If two

or more variables are packed in an address range smaller than a cache line size, they are considered by the cache controllers as a single data. Two or more cores can thus work on unrelated variables but still force cache controllers to communicate. This problem is called *false sharing*.

In optimized native applications, experimented programmers can ensure there is no false sharing by choosing wisely the memory layout of their variables. In a managed runtime environment, like a Java Virtual Machine, the memory layout is chosen by the environment. It is then difficult for the programmer to fix false sharing issues.

Eizenberg et al. [32] address this problem by modifying the JVM. At runtime, the JVM uses hardware sampling counters to detect where false sharing occurs. The sampling counters capture, for each core, which memory addresses are set in the Modified state. If two or more addresses are set in the Modified state by different cores in the same cache line, the JVM considers the cache line is falsely shared.

Once the JVM has detected which cache line is falsely shared, it repairs it. The JVM first identifies the objects containing the problematic cache lines. Then, the JVM stops the mutator threads and for each problematic object, modifies the memory layout of all the objects of the same class. Technically, the JVM adds padding between the fields accessed by several cores to place them on different cache lines. The JVM finally resumes the mutator threads.

This work thus addresses a hardware related issue: the inability of the cache controllers to manage data smaller than a cache line size. The approach is to change the memory layout to match the implicit memory partitioning made by the cache controller. This solution, however, is invisible to the end user application.

### **Scalloc**

The false sharing is a special case of data sharing. When several cores access the same variable to modify it, it is called *true sharing* or simply *sharing*. Usually, the application protects this shared data with locks. These locks force to serialize the accesses, thus nullifying the performance gain of the multicore chip.

Memory allocators are typical programs that try to avoid sharing situations [4, 11, 57]. We call a memory allocator a library that provides the malloc() and free() primitives. This library is a bridge between the mmap() system call that allocates memory at a memory page granularity and the application which allocates memory at various granularities, from the byte to several megabytes. Memory allocators usually implement several buffers larger than a memory page that can be fragmented into smaller regions. The memory allocator returns these regions, called objects, to the application on a malloc(). There are different fragmentation size, or class size, for these buffers, so the allocator can allocate for several granularities. When the application releases an object, it is tagged free in its buffer and is added to the free list of the buffer.

In a multicore context, several cores may concurrently allocate objects of the same size. A naive solution would be to protect the size class buffers with locks. This solution would

result in a sharing situation, causing poor allocation performance. Instead, memory allocators usually maintain one size class buffer per application thread. These buffers are called Thread Local Allocation Buffers (TLAB). With this design, the threads do not share any buffer and allocating an object requires no lock.

However, using TLAB causes 2 issues. First, if a thread releases all the objects of a TLAB, the memory allocator should make this TLAB available to the other threads. Indeed, a memory allocator should avoid wasting memory space. Transferring a TLAB from a thread to another one is a form of sharing. Second, a thread can allocate an object, and another thread can release it. This means that using TLAB does not prevent several threads to share buffers.

Aigner et al. solve these issues with Scalloc [3]. First, Scalloc implements a buffer backend where the threads put empty TLAB. This backend is an array of lock-free stacks, with as many stacks as there are cores. Each application thread is associated to one of these stacks. The stacks are evenly associated to the threads. Each application thread releases and allocates TLAB from its associated stack. This design ensures that TLAB are shared between a relatively small number of threads. If its associated stack is free, a thread allocates a new TLAB from a larger zone called the arena. The arena is shared between all the threads but is rarely used.

When a thread releases an object it has allocated previously, it puts it in the free list of its TLAB. The thread can pop an object from this free list on a later allocation. But when a thread releases an object that another thread has allocated, using the free list of the allocating TLAB would mean to share this free list. Since the free list may be frequently used by the thread owner of the TLAB, sharing this list could cause a serialization overhead. A scalloc TLAB uses 2 free lists. The first one is the local free list, used only by the owner thread. The second one is the remote free list. If a thread releases an object from a TLAB not owned by the thread, the object goes to the remote free list of the TLAB. The remote free list is thus shared between the threads not owning the TLAB. Since releasing an object allocated by another thread is an uncommon operation, this does not affect the performance. When the owner thread allocates an object, it tries to pop one from the local free list. When the local list is empty, it looks the size of the remote free list. Only if this free list is full enough, it moves the content of this remote free list to the local one. Otherwise, the allocating thread fetches a new TLAB from the backend.

Scalloc addresses a contention problem: how to handle a large amount of threads allocating and releasing objects concurrently. The general solution is to use TLAB, which are private allocation spaces and avoid communication between threads, and thus, between cores. When it is necessary to communicate, Scalloc makes sure to reduce the amount of implied cores and that communication happens as rarely as possible. However, as an allocator, Scalloc only expose the malloc() and free() primitives without exposing the hardware details to the application.

### **Sloppy Counter**

Memory allocators such Scalloc solve the issue of shared data structures by using several private thread local structures instead. This kind of per thread or per core replication avoids the cores to communicate and thus, improves performance.

However, some data structures are intended to be shared between cores to allow them to communicate. This is the case for the reference counter. This kind of counter is often used for reference-counted garbage collection of various resources. While a core uses a resource, it keeps a reference on this resource. Keeping a reference means that before using the resource, the core increments the associated reference couter. When the core stops to use the resource, it releases the reference by decrementing the counter. When the counter drops to zero, the resource is garbage collected. The reference counter is hence a communication protocol between the cores.

Usually, a reference counter is implemented with atomic operations. Atomic operations are special instructions provided by the processor making a read then a, possibly conditional, write on a cache line while keeping the cache line locked. Because the processor keeps the cache line locked, it prevents other cores to access it between the read and the write. However, atomic operations are implemented atop cache coherent caches. Many cores updating the same reference counter concurrently thus generate a high amount of cache coherency messages. These communication decrease the application performance.

Boyd-Wickizer et al. [14] propose a scalable implementation of the reference counter called the Sloppy Counter. The sloppy counter is composed of a global counter and one local counter per core. In this structure, the local counter acts as a cache for the global counter. When a core takes a reference, it tries to acquire one in its local counter. If the local counter is non-zero, the core decrements it and no communication occured. If the local counter is zero, the core then increments the global counter. To release a reference, a core only increments its local counter and, once again, no communication occurs. Because references are released in the local counter, this one rarely reaches zero. Accessing the global counter is thus an uncommon operation.

The global counter and the local ones are then merged only when the system decides to perform a garbage collection. The merge operation simply consists to subtract the local counters to the global one. The result is the new value of the global counter while all the local counters are reset to zero. If the global counter is zero, then the resource is garbage collected.

The sloppy counter thus avoids unnecessary cache coherency communications between cores. To this end, it is structured with one shared space accessed rarely: the global counter, and one private space per core, accessed frequently: the local counters. The sloppy counter is an implementation of an existing mechanism, the reference counter, and hence does not expose any additional hardware details.

### The Multikernel

The previous approaches systematically hide the multicore aspect of the hardware. Indeed, Remix [32] silently modifies the classes memory layout, Scalloc [3] only provides the malloc() and free() primitives and the sloppy counter [14] provides put() and get() primitives.

In the problem addressed by Remix, the false sharing, the JVM is the cause: it prevents the programmer to choose an efficient memory layout, which would avoid to create false sharing. The solution is thus implemented in the JVM. There is no reason to inform the user application about the JVM decisions.

By contrast, in the problems addressed by Scalloc and the sloppy counter, the cause is the user application. The congestion occurs because too many threadd access the same resource pool or because too many cores modifies the same counter. Both Scalloc and the sloppy counter solve the problem by duplicating the implied data structures. However, the threads or cores ultimately need to communicate. Because of that, Scalloc sometimes share TLAB between threads and the sloppy counter merges its local and global parts on a garbage collection.

Hiding the multicore nature of the hardware is convenient because it makes the new solutions compatible with existing software. Nontheless, while the system hides the multicore details of the hardware to the application, this application will, at some point, require expensive communication between cores, decreasing its performance. The following works expose the hardware to the user application.

Several works [13, 40, 52] address the multicore scalability problem by redesigning operating systems. The Multikernel [9] is representative of these works. The general idea is to consider each core as a separated computer with its own operating system. Each of these operating system has its own data structures and work only on them. This is typically the case for the scheduler structures.

For other operating system functions that need a global state, like process memory management, each operating system has its own replicate of the global state. The cores keep the replicated states consistent with explicit synchronization based on message passing. The message passing is implemented with some dedicated memory zones used as a channel to transfer cache-line-sized messages point-to-point between single writer and reader cores.

The Multikernel thus avoid unnecessary communication between cores, whether cache coherency messages or inter processor interrupts. To this end, each operating system in the Multikernel only works on its own private space and perform explicit communication when needed.

### The Factored Operating System

The previously presented works make communication explicit by avoiding to use shared memory. Instead they maintain private state that can be synchronized with message passing. This message passing is implemented with cache coherency.

Wentzlaff et al. [69] argue that implementing a cache coherency protocol may not even be possible in a computer with thousands of cores. Indeed, even if the software rarely use cache coherency, a local cache controller with a cache line in an Invalid state still needs to probe other cache controllers if the core requires the cache line. Thus, the cache controllers still exchange messages, even if the cores only use private data structures.

The Factored Operating System (FOS) is an operating system designed to execute in a computer without a global cache coherency. The FOS is based on an idea similar to the Multikernel [9]: execute an autonomous part of the system on each core. Unlike the Multikernel, the FOS does not maintain any global state. Instead, each core works as a server that perform one task: either execute application threads, one at a time, or execute a kernel service. Additionally, each core maintains a name cache. The name cache is a routing table that indicate what core to contact for a given service to execute. The cores communicate with message passing that is architecture dependent.

### The Scalable Commutativity Rule

The works presented in this section address the communication effects on performance. The first work, namely Remix [32], remove the useless cache coherency messages. Indeed false sharing messages do not actually maintain coherency because the cores work on distinct variables. The next works, namely Scalloc [3] and the sloppy counter [14], reduce the amount of exchanged message by batching them. The cores make most of the updates on private data and commit these changes to a global state when required. The two last works, namely the Multikernel [9] and the FOS [69], reduce the amount of required messages. Because they are designed like distributed systems, they maintain private states, one per core that rarely or never have to be synchronized.

All of these presented works however require that the cores synchronize between each others at some point. Clements et al. describe a general method to design a software which does not require that the core synchronize. To be so, a software must provides an interface that follows the Scalable Commutativity Rule [22]. This rules states that, given a set S of operation executed concurrently, the result of an operation o executed after S must not depends on the ordering of operations inside S. If a software interface follows that rule, then it exists an implementation of this interface that can executes the operations concurrently with no need of synchronization.

By using this rule, a programmer can design a system which does not require any expensive communication. This actually solves contention issues by making the multicore aspect of the underlying hardware part of the software conception.

### Conclusion

Previous works brings different solutions to address the problem of system efficiency and scalability in a multicore context. However, they are all built atop of at least one of these two general concept: (i) synchronization necessarily induces serialization, thus a system can be scalable only if its data is shared as little as possible between the cores, (ii) hardware

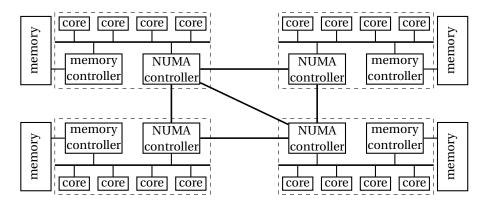

Figure 23: The architectural view of a NUMA architecture

coherency makes programmation easier but is expensive, an efficient system should make every inter-core communication explicit and avoid to rely on hardware coherency.

As a consequence, we can assume that (i) to bring the best performance, nontheless the software must avoid inter core sharing, but also the hardware must do. Especially, we describe in Section 2.2 that with a large number of core, hardware components, like memory, must be partitioned in private subcomponents instead of shared.

Also, we can assume that (ii) to bring the best performance, all the sofware layers must be aware of the communication mechanisms their actions imply and use them explicitely. We describe in Section 2.3 that the virtualization layer makes it difficult.

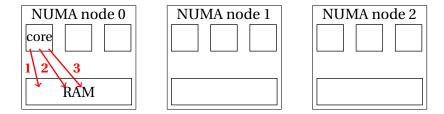

# 2.2 Non Uniform Memory Access architectures

As we show in Section 2.1, cores synchronizations cause the serialization of operations and hence, poor performance. We show that a good software design reduces the number of core synchronizations on shared data, which improve application performance. However, in a simple multicore architecture, as illustrated in Figure 21, the cores still share hardware components. Indeed, each core accesses the memory through a single memory controller and a single system bus. Thus, even if each core accesses to its own private data space, all the cores still share the same memory controller. Since this controller serves the core requests sequentially, it causes the serialization of operations.

The local memory caches of the cores serve a large part of the memory requests. When there is no more than about ten cores in the machine, the number of memory requests sent to the memory controller is then too low to cause a serialization. By contrast, in a machine with several tens of cores, the cache mechanism is not sufficient anymore. It then becomes necessary that several cores can access the memory concurrently. In a *Non Uniform Memory Access* (NUMA) architecture, the available cores and memory banks are partitioned in several nodes, with each node having a separated bus and dedicated memory controllers. All the nodes are bound together with an internal network called the *interconnect*. This ar-

chitecture is illustrated in Figure 23. Using several nodes and thus several buses spreads the memory load across the nodes.

This section first presents how the cores communicate in a NUMA architecture. In particular, we describe the HT Assist cache coherency protocol: an extension of the MOESI protocol for NUMA architectures. We also describe the NUMA hardware that we use for our evaluations. We then explain how Linux handle the distributed aspect of the memory. To this end, we present two NUMA memory management policies provided by the Linux kernel. These explanations help to understand what aspects of a NUMA hardware impact the application performance. Finally, we present some existing works that focus on how to use the NUMA architecture specificities to bring good applications performance.

### Architecture details

In a NUMA architecture, there are several memory controllers that can serve requests concurrently. Each of these controller serves the requests to its associated memory banks. A *cache coherent NUMA* (ccNUMA) architecture presents these memory banks as a single address space to the software: the first gigabytes stand for the memory banks of the first node, the following gigabytes for the next node and so on. Thanks to this unified address space, legacy applications can execute on ccNUMA computers. In the remainder of this thesis, we focus exclusively on ccNUMA architecture. We thus simply use the term NUMA instead of ccNUMA.

As suggested by the architecture name, the memory access time, in a NUMA architecture, varies depending on the memory bank a core access to. Intuitively, we can assume that a core access a memory bank of this node faster than a memory bank of a remote node. In Chapter 4, we explain that several other factors may impact the memory access time. As a result, accessing to the unified memory address space without considering the underlying memory banks located in different nodes may lead to poor application performance.

In this part, we describe how a NUMA hardware exposes a unified address space out of several memory banks accessed through independent memory controllers. We also give some key characteristics of the hardware we use for our evaluations.

### **HT Assist protocol**

As we explain in Section 2.1, in a modern multicore, the cores access to the memory through a cache hierarchy. A cache coherency protocol maintains sequential consistency for the memory accesses. A usual way to achieve this consistency is to implement a reader-writer lock for each cache line. This lock ensures that at any given time, either one cache contains the cache line and can modify it or many caches contain a read-only copy of the cache line. When the core requires a cache line, the cache controller acquires the lock of this cache line in the appropriate mode.

To acquire a lock in a simple multicore architecture, the cache controller broadcasts messages, called probes, to the other cache controllers. This approach works well with a small

number of cores. In a NUMA architecture with tens of cores, the broadcast approach would saturate the communication links. Thus, using the MOESI cache coherency protocol would be inefficient.

The AMD implementations of the NUMA architecture [23] do not apply the MOESI protocol to all the cores of a machine. Instead, only the cores of the same NUMA node synchronize between each others with the MOESI protocol. Since the number of cores in a single NUMA node is low, using the legacy MOESI broadcast inside a node does not saturate communication links.

Using the MOESI protocol inside each NUMA node is however not sufficient to ensure a sequential consistency over the whole machine. Specifically, the nodes still have to synchronize in two cases:

**Read case** If a core reads a cache line, the cache controller has to acquire the lock in readonly mode. If no other core in the local node owns the lock, then another core in a remote node may own the lock in the read-write mode.

**Write case** If a core writes a cache line, the cache controller has to acquire the lock in readwrite mode. If no other core in the local node already owns the lock in read-write mode, then other cores in a remote node may own the lock.

For these two cases, the nodes must synchronize to ensure they respect the reader-writer lock invariants.

The NUMA node synchronization has the form of another reader-writer lock, this time at the node granularity. The invariant of this lock is that at any time, either several NUMA nodes can own the lock in read-only mode or at most one NUMA node can own the lock in read-write mode. The synchronization for the **Read case** thus translates into a read-only lock acquisition. Similarly, the synchronization for the **Write case** translates into a read-write lock acquisition. We can notice that the node grained lock and the core grained locks are tied together by two logical relations. If a core owns the core grained lock in read-write mode, then the node of this core owns the node grained lock in read-write mode. Also, if a core owns the core grained lock in read-only mode, then the node of this core owns the node grained lock.

The AMD implementation of the reader-writer lock between the NUMA nodes is called HT Assist. In this implementation, each cache line has an associated NUMA node called the *home node*. The home node stores, for each of its associated cache line, a corresponding state. There are 4 possible states. These states have the same name that the MOESI protocol states, however, they have slightly different meanings. The state Exclusive/Modified represents a lock in read-wite mode. The states Owned and Shared represent a lock in read-only mode. The state Invalid represents a lock not acquired<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>The AMD documentation [23] actually defines a fifth state called Shared-1. However, it seems that this state is not used, whether in the protocol description or in the experimental evaluation.

|            | No owner | One owner          | Many owners |

|------------|----------|--------------------|-------------|

| Clean copy | Invalid  |                    | Shared      |

| Dirty copy |          | Exclusive/Modified | Owned       |

Table 23: HT Assist States

|            | Invalid | Shared    | Owned       | Exclusive/Modified |

|------------|---------|-----------|-------------|--------------------|

| Read-only  | -       | -         | probe owner | probe owner        |

| Read-write | -       | broadcast | broadcast   | probe owner        |

| Eviction   | -       | broadcast | broadcast   | probe owner        |

Table 24: HT Assist probing policy of the home node

The HT Assist protocol thus implements a reader-writer lock between the nodes for each cache line. Additionally, the HT Assist protocol tries to minimize the number of messages that the NUMA nodes exchange. From this perspective, the reader-writer lock state indicates if no, one or many nodes have a copy of the cache line. Furthermore, the HT Assist states also indicate if the cache line is clean or dirty, and thus if it can be fetched from main memory. This indication matters because the home node, which stores the state of its associated cache lines, is also the node where the cache line has its original main memory copy. Fetching a cache line from main memory then means that the home node does not have to probe any other NUMA nodes and can respond to the acquiring node. Table 23 shows, for each state, how many nodes can have a copy of the cache line and if the copy is clean or dirty. For the states storing a dirty copy of the cache line, the home node also stores the id of the NUMA node to probe to fetch the data, called the *owner node*.

To acquire the lock of a cache line, a NUMA node first computes the id of its home node, basing on the cache line address. The acquiring node then probes the home node indicating if it requires a read-only or a read-write lock. Based on the required lock mode and on the cache line state, the home node decides what probe messages it sends.

If the acquiring node requires a read-only lock and the cache line is clean, so Invalid or Shared state, the home node serves the cache line from its main memory and updates the cache line state to Shared. If the cache line is dirty, so Owned or Exclusive/Modified, the home node probes the *owner node* and updates the cache line state to Owned. The owner node sends its cache line copy to the acquiring node. Additionally, if the node was in the Exclusive/Modified state, it ensures that its cores update their MOESI state from Exclusive to Shared and from Modified to Owned.

If the acquiring node requires a read-write lock and many NUMA nodes may own a copy of the cache line, so Shared or Owned states, the home node broadcasts an invalidation probe for this cache line. If the cache line is in the Exclusive/Modified state, the home node only sends an invalidation probe to the owner node. In both cases, the home node updates the cache line state to Exclusive/Modified and sets the acquiring node as the owner node. Table 24 summarizes the probes that the home node sends for each combination of

required modes and cache line states.

Because the home node of a cache line always knows its associated state, it sends probes only if the cache line cannot be served from main memory. Additionally, the home node only sends directed probes when possible, as opposed to broadcast probe. However, the home node can only store a limited number of cache line states. These states are stored along with the owner node of a cache line in the last level cache of the node. This storage area is called the *cache directory*.

When a cache line is loaded from the main memory for the first time, the home node creates a new corresponding entry in the cache directory. If the cache directory is already full, an older entry is evicted. The HT Assist protocol however requires that any cache line that has a copy in any cache also has an entry in the cache directory. A cache entry eviction thus implies that the corresponding cache line is invalidated from all the caches.

The home node uses the state of the evicted cache line to decide to which node it sends invalidation messages. If the cache line may be owned by many NUMA nodes, so Shared or Owned states, the home node broadcasts invalidation probes. Instead, if the cache line is in the Exclusive/Modified state, the home node only sends an invalidation probe to the owner node. Table 24 summarizes the probes that the home node sends on a cache line eviction depending on the cache line state.

Using both the node grained lock for the whole NUMA machine and a core grained lock in each NUMA node guarantees that at most one core in the machine modifies a cache line at a time. Using these locks also guarantees that the cores always read the freshest state of a cache line, which is a way to provide sequential consistency. By this mean, the HT Assist protocol ensures the memory accesses from all the cores are sequentially consistent, only using a low number of internode messages.

#### **Synthesis**

In Section 2.1, we show that understanding the MOESI protocol helps to design software that use the hardware more efficiently. In the same way, a software understanding the HT Assist protocol is more likely to avoid performance killer patterns:

- Transferring a cache line between two NUMA nodes. This happens if two cores of

different nodes modify the same cache line. The performance loss is even larger than

in MOESI cache line sharing since a HT Assist read-write acquisition may involve up

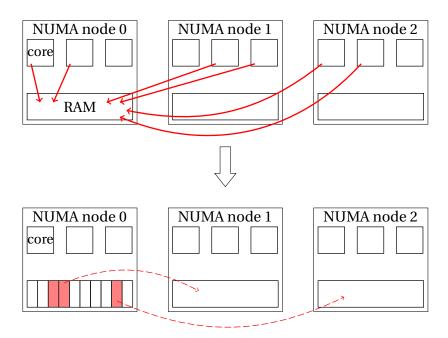

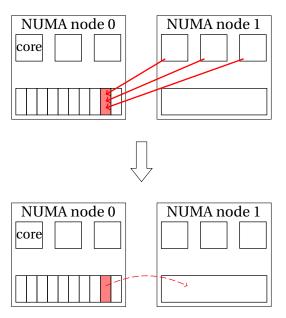

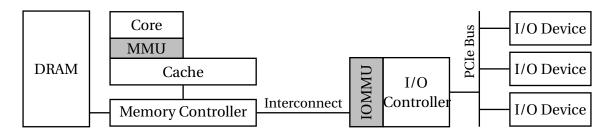

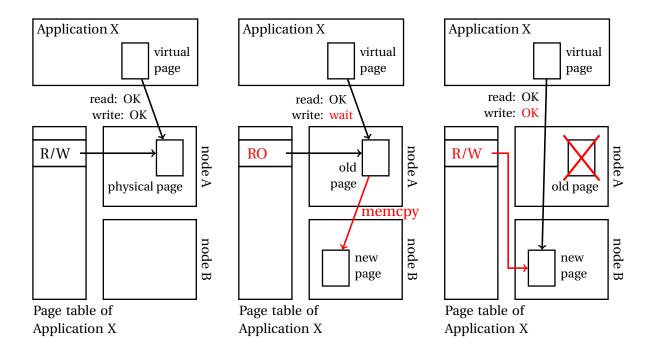

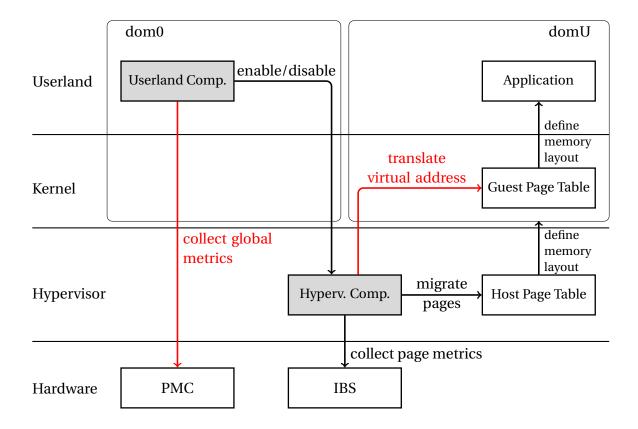

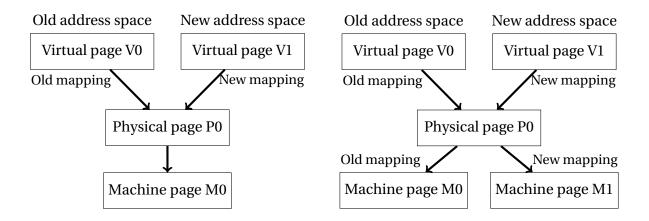

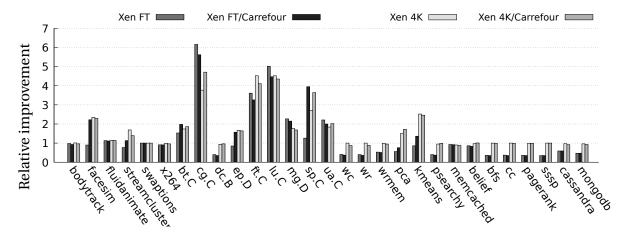

to three NUMA nodes. Also the internode messages go through the interconnect,