# Modelling and control of modular multilevel converters dedicated to HVDC Grids

M Ahmed Zama

#### ▶ To cite this version:

M Ahmed Zama. Modelling and control of modular multilevel converters dedicated to HVDC Grids. Electric power. Université Grenoble Alpes, 2017. English. NNT: 2017GREAT125. tel-01915488v2

# HAL Id: tel-01915488 https://hal.science/tel-01915488v2

Submitted on 25 Jul 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

#### **DOCTEUR DE LA**

#### COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : **Génie Electrique** Arrêté ministériel : 25 mai 2016

Présentée par

#### M. Ahmed ZAMA

Thèse dirigée par **Seddik BACHA** et codirigée par **Abdelkrim BENCHAIB** et **David FREY**

Préparée au sein du Laboratoire de Génie Electrique de Grenoble (G2Elab)

dans l'École Doctorale d'Electronique, Electrotechnique, Automatique et Traitement du Signal (EEATS)

# Modélisation et Commande des Convertisseurs Modulaires Multiniveaux (MMCs) Destinés aux Réseaux HVDC

Thèse soutenue publiquement le **13 Octobre 2017** devant le jury composé de :

#### **Madame Manuela SECHILARIU**

Maitre de conférences, UGA / SuperGrid Institute

Professeur, Université de Technologie de Compiègne Président **Monsieur Mauro CARPITA** Professeur, Université d'Yverdon-les Bains Rapporteur **Monsieur Maurice FADEL** Professeur, Institut National Polytechnique de Toulouse Rapporteur Monsieur Kamal AL HADDAD Professeur, Ecole de Technologie Supérieure de Montréal Examinateur Monsieur Sebastien SILVANT R&D Manager, SuperGrid Institute/ GE Grid Solutions Examinateur Monsieur Seddik BACHA Professeur, UGA / SuperGrid Institute Directeur Monsieur Abdelkrim BENCHAIB Docteur-HDR, R&D Manager, SuperGrid Institute/ GE Grid Solutions Co-Encadrant Monsieur David FREY

Co-Encadrant

#### DISSERTATION

In partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY OF COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Department: Electrical Engineering

# Modeling and Control of Modular Multilevel Converters (MMCs) for HVDC applications

#### **Presented by:**

Mr. Ahmed ZAMA

#### **Supervised by:**

Pr. Seddik BACHA (UGA / SuperGrid Institute)

Dr. Abdelkrim BENCHAIB (GE Grid Solutions / SuperGrid Institute)

Dr. David FREY (UGA / SuperGrid Institute)

# **Dédicace**

A vous mes chers parents, mon frère Mehdi et mes deux sœurs Amira et Sana,

A mes deux beaux-frères Fouad, Hamza et toute la famille ZAMA et Loucif,

A la personne avec qui je souhaite fêter mes cent ans,

Je dédie ce modeste travail

# Remerciements

Une thèse de doctorat est un long voyage, un long parcours, une longue et belle aventure qui nécessite un moral d'acier et un bon environnement humain et matériel. Je mets à profit cette partie pour exprimer mes plus sincères remerciements à tous ceux qui m'ont aidé à vaincre les difficultés rencontrées que sont les moments de doutes, les incertitudes et les divers blocages. Je salue chapeau bas toutes ces personnes qui ont contribué à réaliser mon rêve d'enfance : celui d'obtenir le grade de DOCTEUR.

Je tiens tout d'abord à remercier Messieurs les professeurs Maurice FADEL et Mauro CARPITA pour l'intérêt qu'ils ont accordé à mon travail en ayant accepté de rapporter sur mon manuscrit. Je remercie également, avec la même gratitude, Madame la professeure Manuela SECHILARIU pour avoir accepté de présider mon jury de thèse et enfin Monsieur le professeur Kamal AL HADDAD pour m'avoir fait l'insigne honneur d'être de ce jury d'évaluation en tant qu'examinateur et ce, malgré des emplois du temps très chargés. C'est pour moi un honneur et une fierté d'avoir pu rassembler ses quatre éminentes personnalités au sein de mon jury de thèse.

Je tiens à exprimer mes profonds remerciements à toi Seddik. Professeur BACHA, j'ai beaucoup apprécié le fait de travailler sous ta direction. Je n'oublierai jamais notre première rencontre dans ton bureau où l'on a beaucoup échangé sur mon projet professionnel. Ce jour-là constitue un tournant dans ma vie. Merci de la confiance que tu m'as accordé et d'avoir misé sur mes capacités pour réaliser cette thèse. Je ne te remercierai jamais assez pour ta disponibilité, ton accompagnement, tes conseils, sans oublier ton côté humain et paternel. Tu es une des personnes qui ont marqué ma vie, Milles merci à toi!!

Ce travail n'aurait pas été assez complet sans la collaboration et l'expertise de mes deux superviseurs Abdelkrim BENCHAIB et David FREY.

Abdelkrim, je te remercie pour ton support et les conseils que tu m'as donné durant toute cette aventure. Tu étais toujours là pour moi, notamment durant les moments les plus difficiles de la thèse et grâce à toi j'ai pu transformer cette thèse « scientifique » en une précieuse expérience professionnelle dans l'industrie en tant qu'Ingénieur/Chercheur. Je te remercie pour tous les échanges fructueux, qu'on avait eus, que ce soit dans le cadre du travail ou autour d'un café,

sur les différents sujets de la vie. Tes futurs doctorants seront gâtés d'avoir un manageur exemplaire comme toi.

David, j'étais très chanceux de t'avoir eu comme encadrant. Contrairement à Abdelkrim et Seddik, tu étais le seul à t'engager dans cette aventure sans avoir la moindre idée sur mon profil. Ce fait a constitué pour moi une motivation perpétuelle pour être à la hauteur de la confiance que tu m'as accordée dès le départ. Merci pour ton support et l'apport de ton expertise en électronique de puissance et à sa mise en œuvre, c'est un vrai plaisir de travailler avec toi.

Je ne manquerai pas non plus de remercier Sébastien SILVANT qui a rejoint l'équipe d'encadrement en cours de route. Merci pour le support que tu as apporté à ma thèse, tes remarques et tes orientations ont toujours été des motivations pour moi. Je n'oublie pas une mention spéciale à Eric COURBON pour ses compétences informatiques et sa totale disponibilité.

Je souhaite remercier aussi chaleureusement le directeur du programme P1 de Supergrid Institute, Bruno LUSCAN, qui nous a fait confiance, qui était toujours au courant de nos progressions et qui nous a soutenu tout le long du déroulement de ce travail. Je n'oublierai pas non plus les deux autres responsables de sous programmes que sont Serge POULLAIN et Alberto BERTINATO pour leurs contributions d'une façon ou d'une autre à la bonne réussite de cette thèse.

J'ajouterai ici un mot spécial à Luis COSTA, ancien responsable du sous-programme P1.4 et mon tuteur durant mon stage de fin d'étude. Merci pour la confiance et la patience dont tu as fait preuve durant le stage et surtout pour le sujet de thèse que tu m'as proposé. Saches bien que c'est une fierté pour moi d'avoir eu l'opportunité de travailler avec toi et j'espère que ce travail sera à la hauteur de tes attentes. Un mot aussi pour Xavier GUILLAUD qui m'a co-encadré lors du stage et qui m'a mis le pied à l'étrier dans le domaine des convertisseurs multi modulaires. Merci aussi pour m'avoir accueilli dans son laboratoire durant une semaine au début de la thèse.

Mes remerciements vont aussi à la direction générale de SuperGrid Institute et à sa tête Hubert de la GRANDIERE pour m'avoir donné l'opportunité de travailler dans cet environnement unique de recherche et développement.

Au tour de mes chers collègues du programme P1 que je remercie chaleureusement. Merci aux pionniers du P1 (Kosei, William, Deiynaba, Swann et Janailson) et félicitations pour vos nouveaux grades de DOCTEUR mérités. Une pensée aussi aux futurs docteurs (Amjad, Miguel, Juan-carlos, Guilherme, Raga et Nicolas), je vous souhaite le meilleur dans vos recherches ainsi que du courage et de la persévérance pour la rédaction de vos manuscrits de thèse. Je n'oublie pas Luc-André, Boussaad, Séllé, Manuel, Leo, Theihotua et tous les stagiaires, alternants et ingénieurs qui ont eu à travailler au P1. Merci à vous tous pour les remarques et les conseils que vous m'aviez apporté au cours des follow-ups. Merci pour la bonne ambiance créée dans les bureaux et les bons moments passés ensemble que soit autour des cafés avec des croissants le matin ou le soir à star-ferry pour un afterwork.

Je tiens à remercier également tous mes amis qui m'ont aidé de près ou de loin à arriver jusqu'à ce stade: mes amis d'enfance (Yahia, Toufik, les deux Yakoub...), ceux de l'ENP Alger (Ayoub, Youcef, Mouhamed, Merouan, Arezki, Tarek...), mes amis en France (Amin, Djamel, Bilal, Chawki, Nassim...). Pour tous ceux que je n'ai pas pu citer ici (la section remerciement étant limitée et la liste est longue...), sachez que je n'oubliai jamais vos contributions.

Je laisse maintenant un mot pour mon ami Zaki GUICHICHE, tu es le frère que la vie m'a donné. Merci pour les voyages qu'on a organisé, les restos qu'on a fait et tous les moments de partage que ce soit à Grenoble ou à Lyon. Je te demande une seul chose : comme tu le sais les aiguilles tournent, sois courageux et patient, tous ces moment difficiles vont être récompensés tôt au tard.

Merci à tous les gens qui ont fait le déplacement à Grenoble, le jour de ma soutenance, pour y assister et m'apporter leurs soutiens.

Pour finir, rien de tout cela n'aurait été possible sans l'appui de mes parents. Je vous remercie pour tous les sacrifices humains et financiers que vous avez faits afin que je puisse arriver à ce stade. Je vous remercie pour votre soutien qui, malgré la distance, a toujours été là pour moi lorsque j'en avais le plus besoin.

# **Content**

| Dédicace                                                  | V      |

|-----------------------------------------------------------|--------|

| Remerciements                                             | VII    |

| Content                                                   | XI     |

| Table of Figures                                          | XIX    |

| Abstract                                                  | XXIX   |

| Résumé                                                    | XXXI   |

| List of Publications                                      | XXXIII |

| General Introduction                                      | 1      |

| Thesis context                                            | 3      |

| Main objectives and thesis methodology                    | 4      |

| Thesis outline                                            | 5      |

| CHAPTER I HVDC Technology and Architectures               | 7      |

| 1. Introduction                                           | 9      |

| 2. Needs for HVDC                                         | 9      |

| 3. High voltage direct current                            | 10     |

| 3.1. Concept                                              | 10     |

| 3.2. Configurations                                       | 11     |

| 3.2.1. Asymmetric monopolar scheme                        | 11     |

| 3.2.2. Symmetric monopolar scheme                         | 12     |

| 3.2.3. Bipolar scheme                                     | 12     |

| 4. Converter technologies for HVDC application            | 13     |

| 4.1. Line-Commuted Converters (Current Source Converters) | 14     |

| 4.2. Self-Commuted Converters (Voltage Source Converters) | 17     |

| 4.3. Comparison between VSC and LCC                       | 19     |

| 4.3.1 Advantages of LCC compared to VSC                   | 19     |

| 4.3.2. Advantages of VSC compared to LCC                                          |

|-----------------------------------------------------------------------------------|

| 5. Modular Multilevel Converter (MMC)                                             |

| 5.1. Topology and principle                                                       |

| 5.2. SM Topologies                                                                |

| 5.3. MMC Topologies                                                               |

| 6. Conclusion                                                                     |

| CHAPTER II Modular Multilevel Converter Modeling31                                |

| 1. Introduction                                                                   |

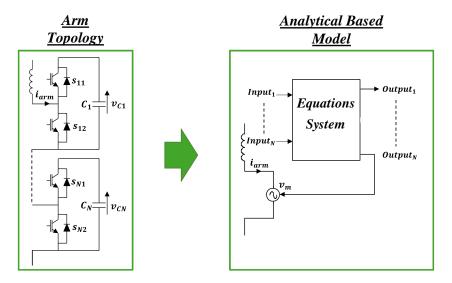

| 2. Model categories                                                               |

| 3. MMC modeling levels (state of the art)                                         |

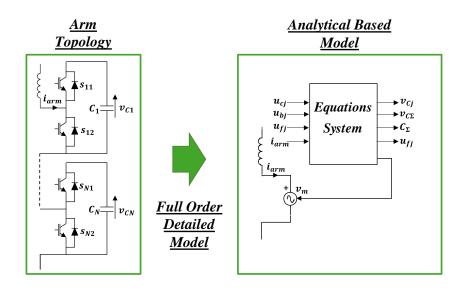

| 3.1. Full order detailed model (DM)                                               |

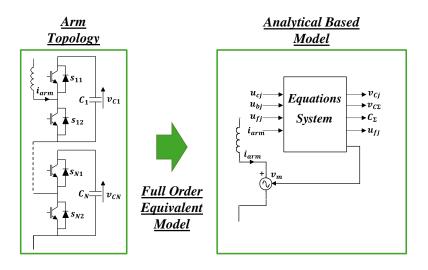

| 3.2. Full order equivalent model (EM)                                             |

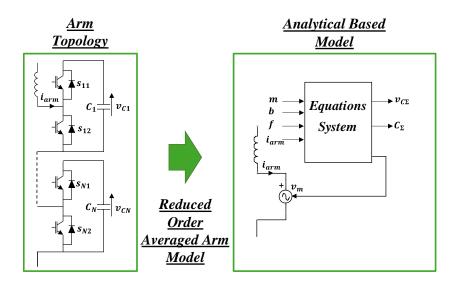

| 3.3. Reduced order averaged arm model (AVM)                                       |

| 3.4. MMC models including blocked state                                           |

| 4. Scientific contributions                                                       |

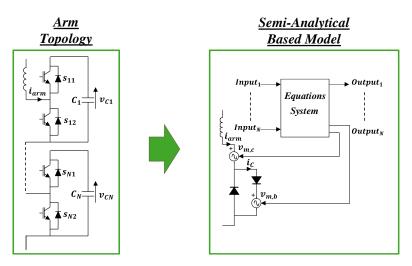

| 4.1. Semi-analytical modeling technique                                           |

| 4.1.1. Full order detailed model based on semi-analytical modeling technique 54   |

| 4.1.2. Full order equivalent model based on semi-analytical modeling technique 57 |

| 4.1.3. Reduced order averaged arm model based on semi-analytical modeling         |

| technique59                                                                       |

| 4.2. Analytical modeling technique                                                |

| 4.2.1. Full order detailed model based on analytical modeling technique           |

| 4.2.2. Full order equivalent model based on analytical modeling technique 64      |

| 4.2.3. Reduced order averaged arm model based on analytical modeling technique66  |

| 5. Validation of proposed models                                                  |

| 5.1. Controlled state tests                                                       |

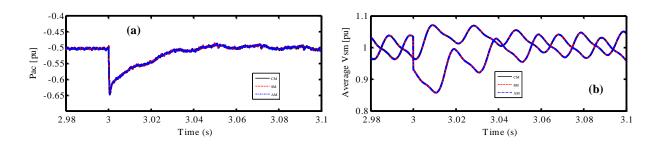

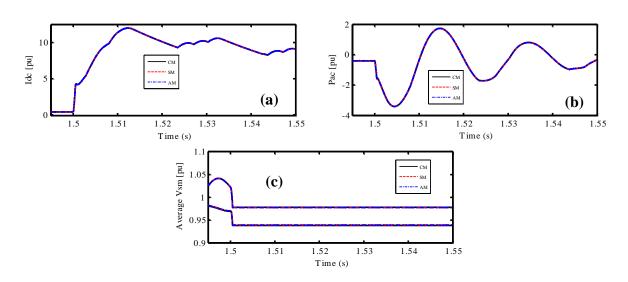

| 5.1.1 Step change in DC power reference 68                                        |

| 5.1.2.      | Step change in stored energy reference | 69 |

|-------------|----------------------------------------|----|

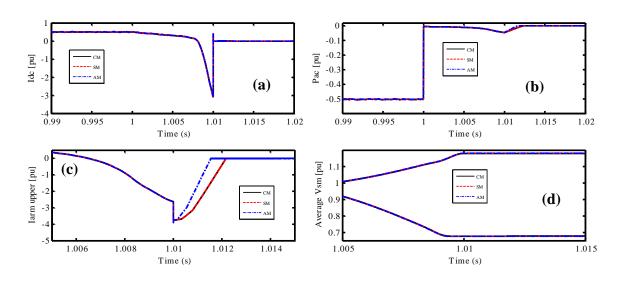

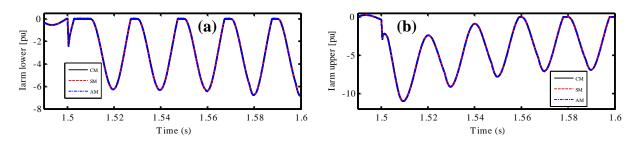

| 5.2. Blo    | ocked state tests                      | 69 |

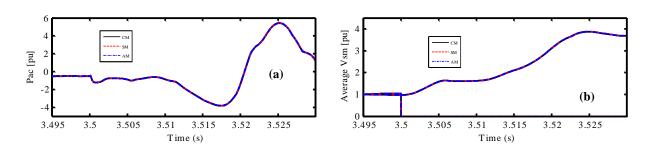

| 5.2.1.      | Three phase AC fault                   | 69 |

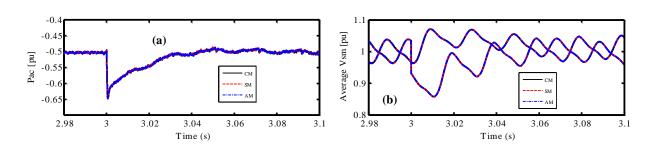

| 5.2.2.      | Pole to pole DC fault                  | 71 |

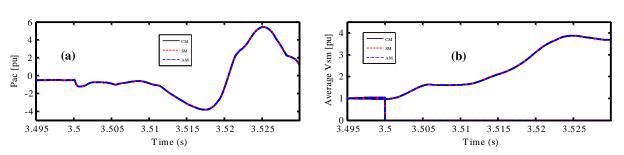

| 5.3. Fau    | ulted state tests                      | 73 |

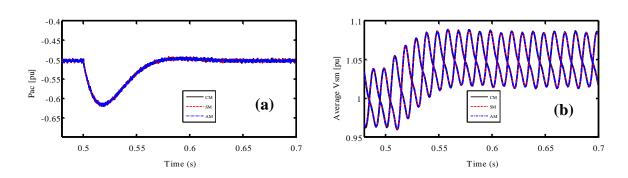

| 5.3.1.      | Loss of 10% SMs for one arm            | 73 |

| 5.3.2.      | Loss of one arm                        | 73 |

| 5.4. Sin    | nulation performances                  | 74 |

| 6. Conclus  | sion                                   | 74 |

| CHAPTER III | Modular Multilevel Converter Control   | 77 |

| 1. Introduc | ction                                  | 79 |

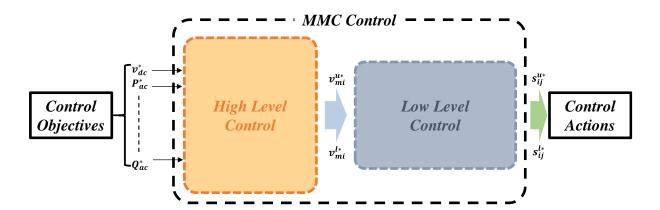

| 2. MMC C    | Control principle                      | 79 |

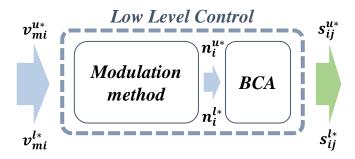

| 3. Low lev  | vel control                            | 80 |

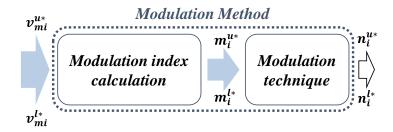

| 3.1. Mo     | odulation technique                    | 80 |

| 3.1.1.      | Modulation index calculation           | 81 |

| 3.1.2.      | Modulation techniques                  | 82 |

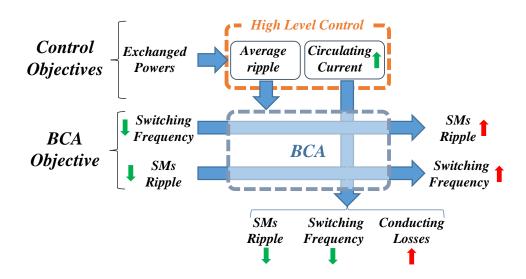

| 3.2. Bal    | lancing Control Algorithm (BCA)        | 84 |

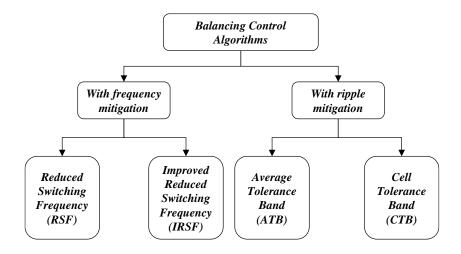

| 3.3. Cla    | assification of different BCAs         | 85 |

| 3.3.1.      | BCAs with frequency mitigation         | 87 |

| 3.3.2.      | BCAs with ripple mitigation            | 88 |

| 3.4. Co     | mparison                               | 90 |

| 3.4.1.      | Basic BCA                              | 90 |

| 3.4.2.      | Reduced Switching Frequency            | 92 |

| 3.4.3.      | Improved Reduced Switching Frequency   | 93 |

| 3.4.4.      | Average Tolerance Band (Sorts)         | 93 |

| 4. High le  | vel control                            | 95 |

| / 1 Sto     | ta space equations for MMC             | 05 |

| 4.1.1. AC power equation                                                   | 97            |

|----------------------------------------------------------------------------|---------------|

| 4.1.2. DC power equation                                                   | 98            |

| 4.1.3. Energy global equation                                              | 99            |

| 4.1.4. Energy balancing equations                                          | 100           |

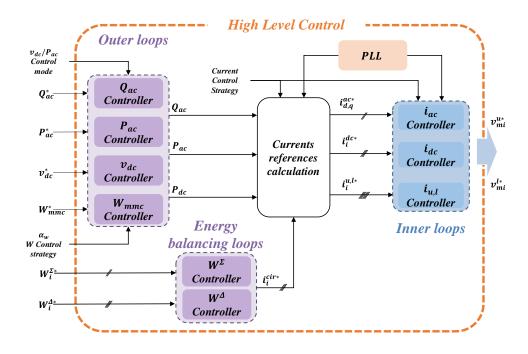

| 4.2. High level control structure                                          | 104           |

| 4.2.1. Multivariable control                                               | 104           |

| 4.2.2. Cascaded control                                                    | 105           |

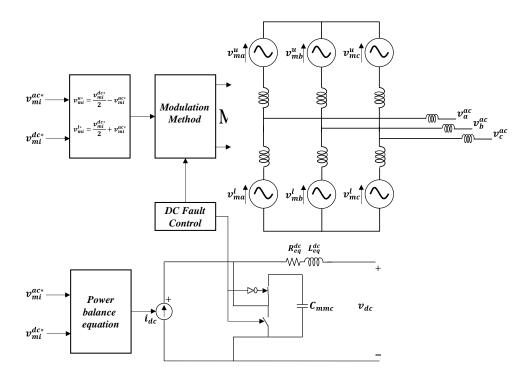

| 5. Considered control structure for thesis contributions                   | 109           |

| 5.1. Low level control                                                     | 110           |

| 5.2. High level control                                                    | 110           |

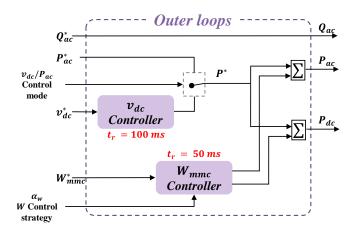

| 5.2.1. Outer loops                                                         | 111           |

| 5.2.2. Energy balancing loops                                              | 112           |

| 5.2.3. Current references calculation                                      | 113           |

| 6. Conclusion                                                              | 115           |

| CHAPTER IV Contributions to MMC control                                    | 117           |

| 1. Introduction                                                            | 119           |

| 2. A contribution to low level control: Improved Averaged Tolerance Band ( | (IATB) method |

| 119                                                                        |               |

| 2.1. Introduction                                                          | 119           |

| 2.2. Improved ATB algorithm                                                | 120           |

| 2.3. Simulation and validation                                             | 122           |

| 3. Contributions to high level control: high dynamics MMC control          | 124           |

| 3.1. Introduction                                                          | 124           |

| 3.2. Variable structure MMC control: sliding mode control                  | 124           |

| 3.2.1. Sliding mode control for MMC                                        | 125           |

| 3.2.2. Validation                                                          | 130           |

| 3 2 3 Improved sliding mode control                                        | 135           |

| 3.2.4. Stability analysis                                       | 137   |

|-----------------------------------------------------------------|-------|

| 3.2.5. Validation                                               | 139   |

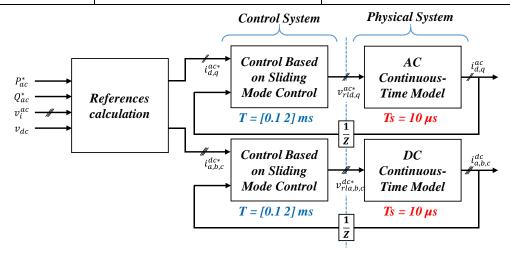

| 3.3. Discrete-time MMC control                                  | 143   |

| 3.3.1. Exact discrete-time MMC modeling                         | 143   |

| 3.3.2. Discrete-time MMC control based on pole placement method | od149 |

| 3.3.3. Discrete-time MMC control based on sliding mode control  | 154   |

| 3.3.4. Control laws validation                                  | 161   |

| 3.4. Offline validation of proposed controllers                 | 165   |

| 3.4.1. Control in normal operation                              | 165   |

| 3.4.2. Control against external events                          | 170   |

| 4. Conclusion                                                   | 173   |

| CHAPTER V Real-Time (HIL and RCP) Validations                   | 175   |

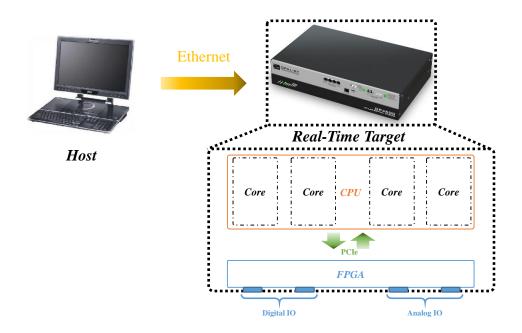

| 1. Introduction                                                 | 177   |

| 2. Real-Time simulation                                         | 177   |

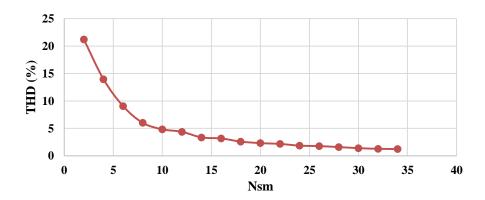

| 3. Small scale MMC sizing                                       | 178   |

| 3.1. Number of SMs                                              | 178   |

| 3.2. SM capacitor                                               | 179   |

| 3.3. Arm inductance                                             | 180   |

| 4. Hardware in the loop (HIL) validation                        | 181   |

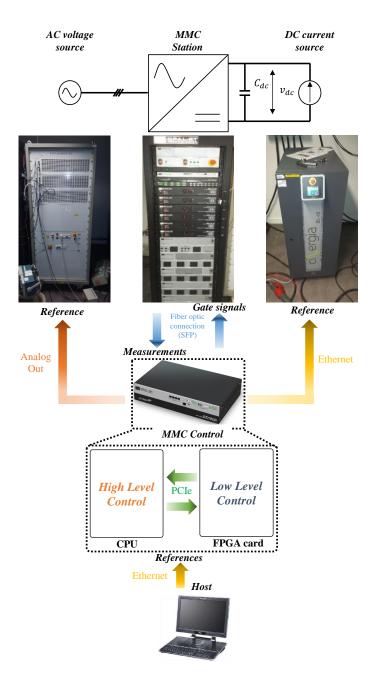

| 4.1. HIL setup (configuration)                                  | 181   |

| 4.1.1. Model implementation                                     | 183   |

| 4.1.2. Control implementation                                   | 183   |

| 4.1.3. HIL communication                                        | 184   |

| 4.2. HIL validation                                             | 184   |

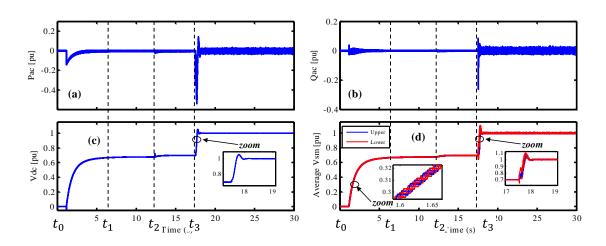

| 4.2.1. Start-up sequence                                        | 184   |

| 4.2.2. High dynamics test                                       | 186   |

| 5. Rapid Control prototyping (RCP) validation                   | 187   |

| 5      | .1.   | Mo    | ck-up description                       | 187 |

|--------|-------|-------|-----------------------------------------|-----|

| 5      | .2.   | Tes   | t bench structure                       | 188 |

| 5      | .3.   | Exp   | perimental tests validation             | 189 |

|        | 5.3   | .1.   | Start-up sequence                       | 189 |

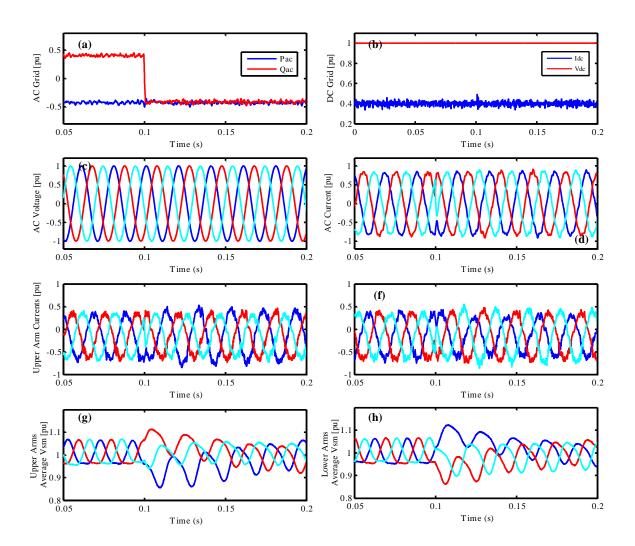

|        | 5.3   | .2.   | High dynamics test                      | 190 |

|        | 5.3   | .3.   | Energy step                             | 191 |

|        | 5.3   | .4.   | Symmetric AC dip                        | 192 |

|        | 5.3   | .5.   | Asymmetric AC dip                       | 193 |

| 6.     | Con   | clus  | ion                                     | 194 |

| Concl  | usior | ns an | d Perspectives                          | 197 |

| Refere | ences | S     |                                         | 203 |

| Résun  | né Et | endı  | ı en Français                           | 217 |

| APPE   | ENDI  | CES   |                                         | 227 |

| 1.     | App   | endi  | ix A: Validation of proposed MMC models | 229 |

| 1      | .1.   | Val   | idation of proposed equivalent models   | 229 |

|        | 1.1   | .1.   | Controlled state tests                  | 229 |

|        | 1.1   | .2.   | Blocked state tests                     | 230 |

|        | 1.1   | .3.   | Faulted state tests                     | 231 |

| 1      | .2.   | Val   | idation of proposed averaged models     | 232 |

|        | 1.2   | .1.   | Controlled state tests                  | 232 |

|        | 1.2   | .2.   | Blocked state tests                     | 233 |

|        | 1.2   | .3.   | Faulted state tests                     | 234 |

| 2.     | App   | endi  | ix B: MMC controllers tuning            | 237 |

| 2      | .1.   | DC    | voltage controller                      | 237 |

| 2      | .2.   | Ene   | ergy global controller                  | 239 |

| 2      | .3.   | Ene   | ergy leg (sum) controller               | 240 |

| 2      | 4     | Ene   | ergy difference controller              | 242 |

|   | 2.5.  | Phase locked loop                                                        | 243 |

|---|-------|--------------------------------------------------------------------------|-----|

| 3 | . Арр | pendix C: High dynamics MMC control based on MMC arm current controllers | 245 |

|   | 3.1.  | Introduction                                                             | 245 |

|   | 3.2.  | Exact discrete-time MMC modeling                                         | 246 |

|   | 3.3.  | Discrete-time controllers based on pole placement method                 | 247 |

|   | 3.4.  | Offline validation                                                       | 247 |

|   | 3.4   | -1. High dynamics test                                                   | 247 |

|   | 3.4   | -2. Symmetric ac voltage dip                                             | 250 |

|   | 3.4   | -3. Asymmetric ac voltage din                                            | 251 |

# **Table of Figures**

| Figure I-1: HVDC system concept                                                      | 10     |

|--------------------------------------------------------------------------------------|--------|

| Figure I-2: Back-to-back scheme.                                                     | 10     |

| Figure I-3: Asymmetric monopolar scheme without metallic return.                     | 11     |

| Figure I-4: Asymmetric monopolar scheme with metallic return.                        | 11     |

| Figure I-5: Symmetric monopolar scheme.                                              | 12     |

| Figure I-6: Bipolar scheme without metallic return.                                  | 13     |

| Figure I-7: Bipolar scheme with metallic return.                                     | 13     |

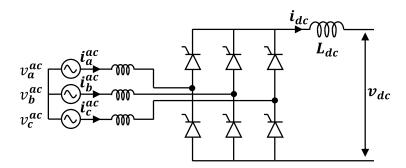

| Figure I-8: Three phase Line-Commuted Converter (LCC).                               | 14     |

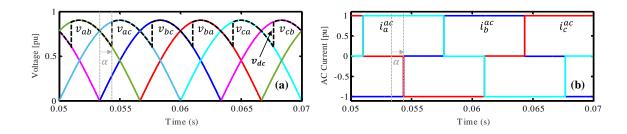

| Figure I-9: (a) DC voltage waveform, (b) AC current waveform with LCC                | 15     |

| Figure I-10: LCC-HVDC station                                                        | 15     |

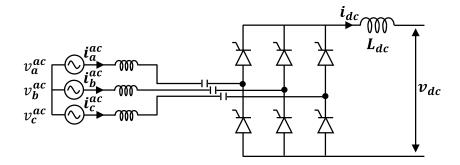

| Figure I-11: Three phase Capacitor-Commutated Converter (CCC)                        | 16     |

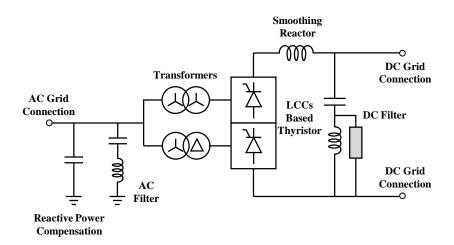

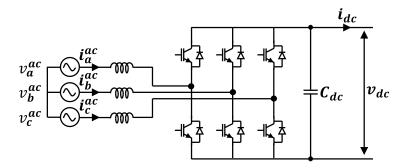

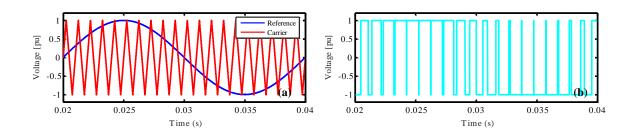

| Figure I-12: Three-phase 2-level Voltage Souce Converter (VSC)                       | 17     |

| Figure I-13: (a) Requested AC voltage, (b) generated AC voltage with VSC             | 17     |

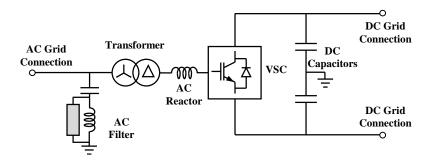

| Figure I-14: VSC-HVDC station                                                        | 19     |

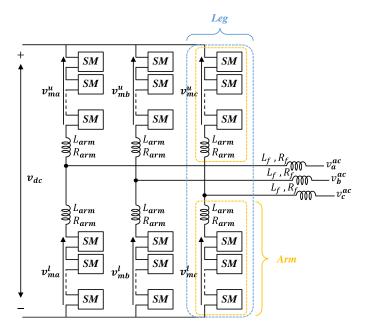

| Figure I-15: Three-phase Modular Multilevel Converter (MMC).                         | 22     |

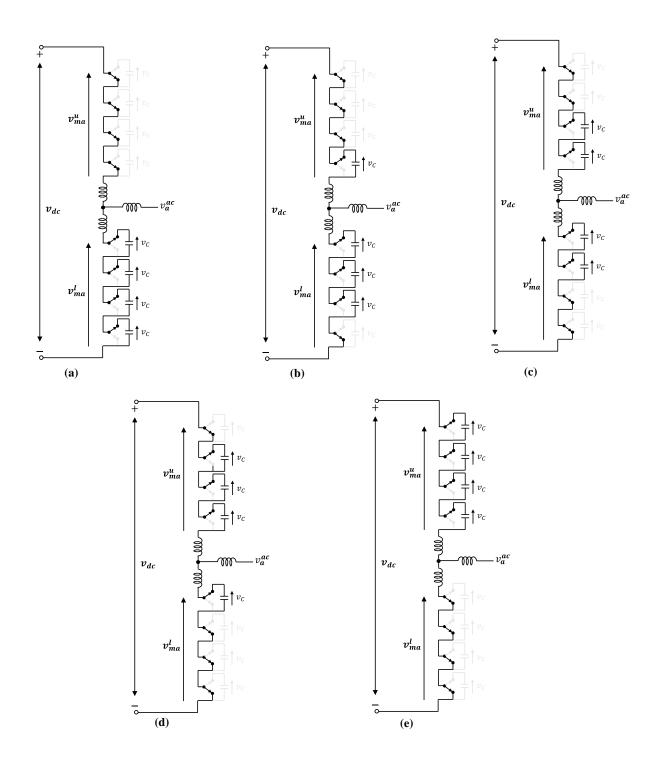

| Figure I-16: Operation principle of 5-level MMC.                                     | 23     |

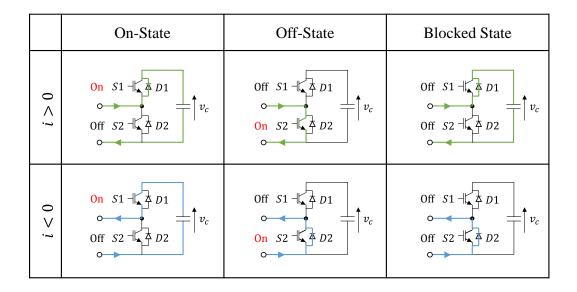

| Figure I-17: Different states for Half-Bridge SM.                                    | 24     |

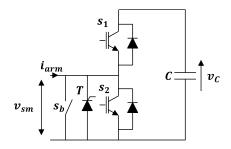

| Figure I-18: Half-Bridge SM including protecting Thyristor and mechanical switch     | 24     |

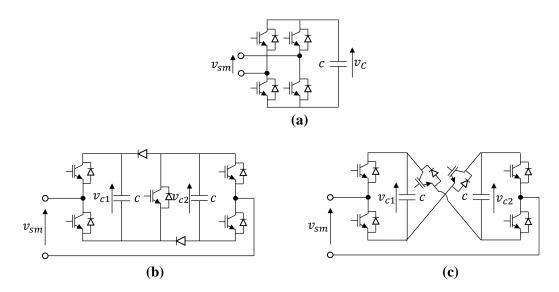

| Figure I-19: Comparison of features of various SM topologies: (a) Full-Bridge, (b) C | lamp-  |

| Double, (c) Cross-Connected.                                                         | 25     |

| Figure I-20: Hybrid modular multilevel converter (FB+HB) SMs [30].                   | 26     |

| Figure I-21: New hybrid modular multilevel converter (2-level+FB SMs) [32]           | 27     |

| Figure I-22: Alternative Arm Converter (AAC) [34]                                    | 28     |

| Figure I-23: Series bridge converter (SBC) [35]                                      | 28     |

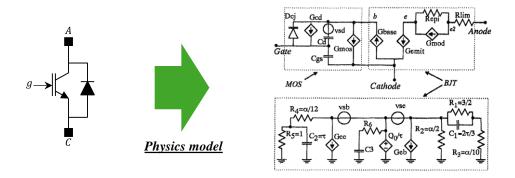

| Figure II-1: Physics based model for IGBT [40].                                      | 37     |

| Figure II-2: Detailed based models for IGBT: (a) non-linear diodes model, (b) resist | tances |

| equivalent model                                                                     | 37     |

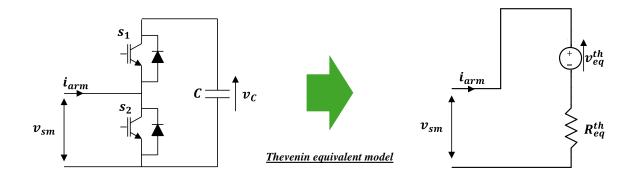

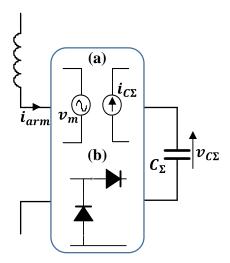

| Figure II-3: Equivalent Thevenin model for one SM                                    | 38     |

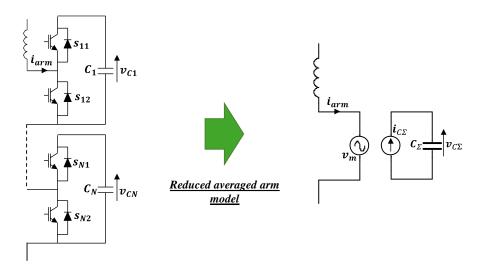

| Figure II-4: Reduced averaged arm model                                              | 39     |

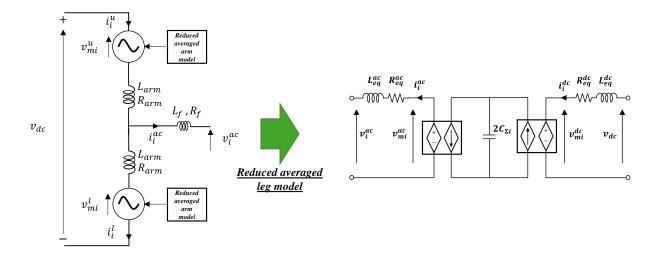

| Figure II-5: Reduced averaged leg model.                                             | 40     |

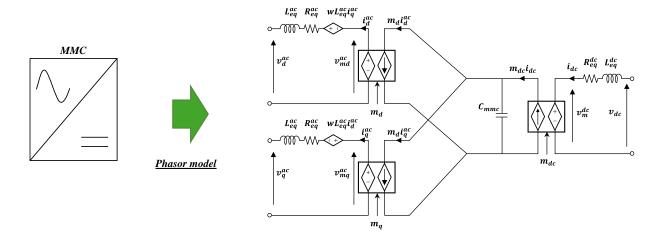

| Figure II-6: Phasor MMC model                                                        | 40     |

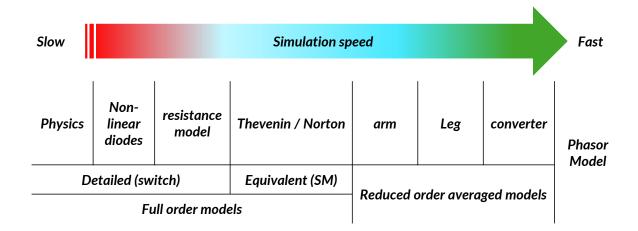

| Figure II-7: Summary of different model types for MMC                                            |

|--------------------------------------------------------------------------------------------------|

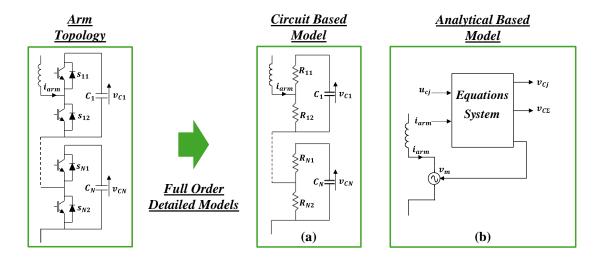

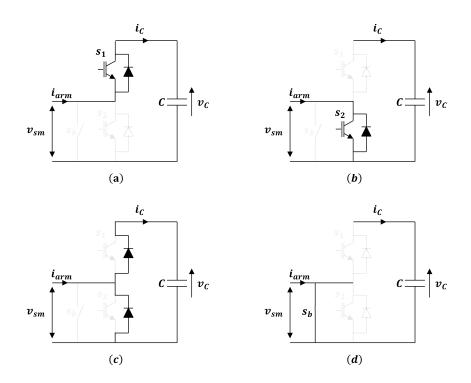

| Figure II-8: Full order detailed models: (a) circuit based model, (b) analytical based model. 42 |

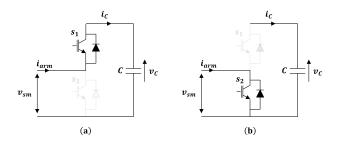

| Figure II-9: SM configurations for controlled states                                             |

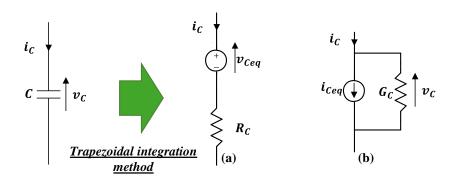

| Figure II-10: Capacitor equivalent circuit: (a) resistive, (b) conductance                       |

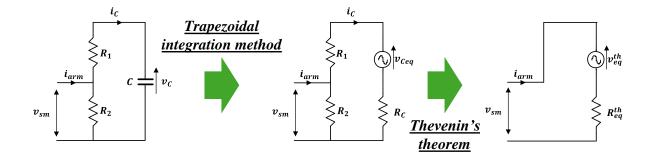

| Figure II-11: From detailed to equivalent model                                                  |

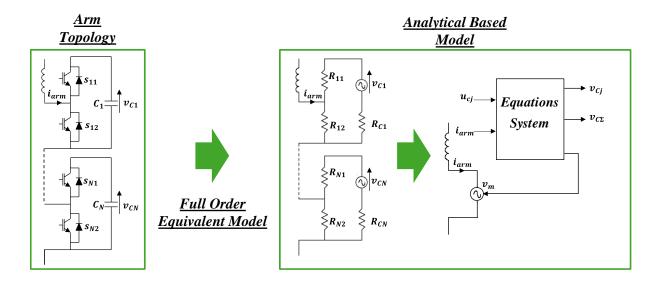

| Figure II-12: Full order equivalent model. 47                                                    |

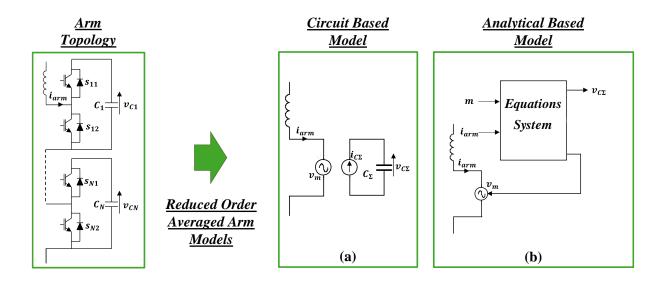

| Figure II-13: Reduced order averaged arm models: (a) circuit based model, (b) analytical based   |

| model                                                                                            |

| Figure II-14: Reduced order averaged model including blocking capability50                       |

| Figure II-15: Reduced order averaged arm model: (a) controlled state, (b) blocked state 51       |

| Figure II-16: SM Configurations including blocked and fault states                               |

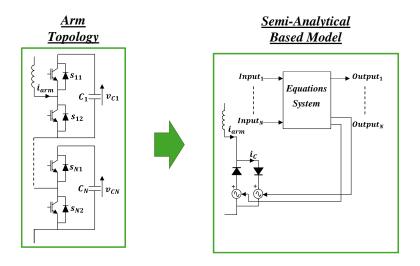

| Figure II-17: Semi-analytical model proposed in [61]                                             |

| Figure II-18: Semi-analytical model proposed in [64]                                             |

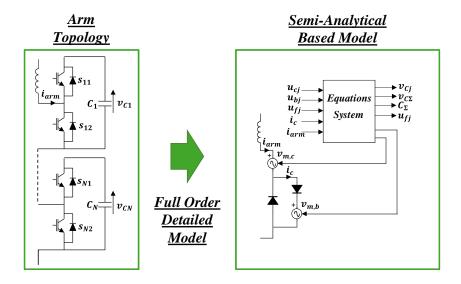

| Figure II-19: Full order detailed model based on semi-analytical modeling technique 57           |

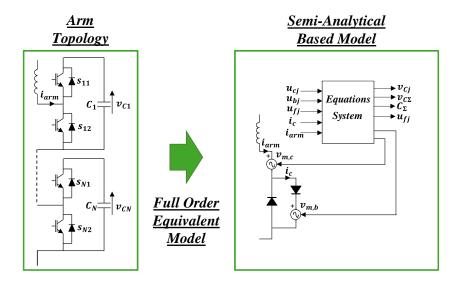

| Figure II-20: Full order equivalent model based on semi-analytical modeling technique 59         |

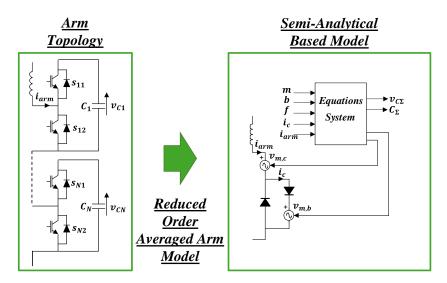

| Figure II-21: Reduced order averaged arm model based on semi-analytical modeling technique.      |

| 60                                                                                               |

| Figure II-22: Proposed analytical model. 61                                                      |

| Figure II-23: Full order detailed model based on analytical modeling technique                   |

| Figure II-24: Full order equivalent model based on analytical modeling technique                 |

| Figure II-25: Reduced order averaged arm model based on analytical modeling technique $67$       |

| Figure II-26: Simulation circuit for models validation                                           |

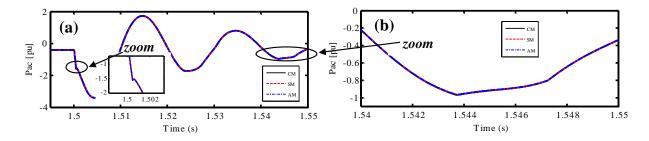

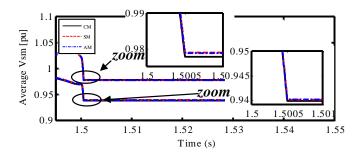

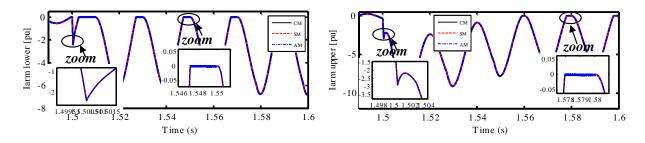

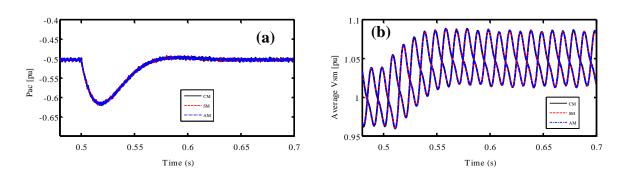

| Figure II-27: Dynamics response of detailed models for a DC power step change: (a) active        |

| power, (b) DC current, (c) average SM voltages for upper and lower arms for phase a 69           |

| Figure II-28: Dynamics response of detailed models for a stored energy step change: (a) active   |

| power and (b) average SMs voltages for upper and lower arms for phase a                          |

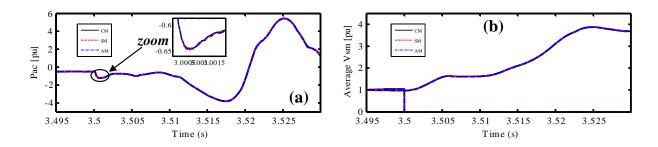

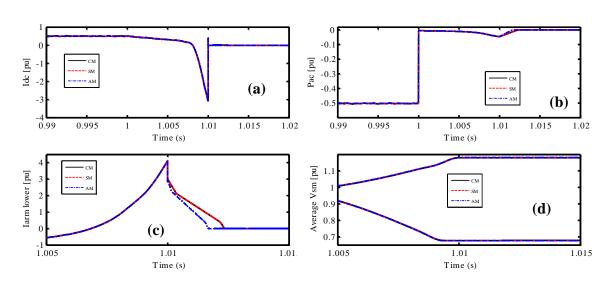

| Figure II-29: Active power dynamics of detailed models for a three phase AC fault70              |

| Figure II-30: Arm currents (phase a) dynamics of detailed models for a three phase AC fault.     |

| 70                                                                                               |

| Figure II-31: DC current dynamics of detailed models for a three phase AC fault71                |

| Figure II-32: Models dynamics of the detailed model for a three phase AC fault: average SMs      |

| voltages for upper and lower arm of phase a                                                      |

| Figure II-33: DC current dynamics of detailed models for a pole-to-pole DC fault72               |

| Figure II-34: Active power dynamics of detailed models for a pole-to-pole DC fault                                    | 72              |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|

| Figure II-35: Average SMs voltages for upper and lower arms dynamics of detailed mod                                  | lels for        |

| a pole-to-pole DC fault                                                                                               | 72              |

| Figure II-36: Arm currents dynamics of detailed models for a pole-to-pole DC fault (ph                                | ase a).         |

|                                                                                                                       | 72              |

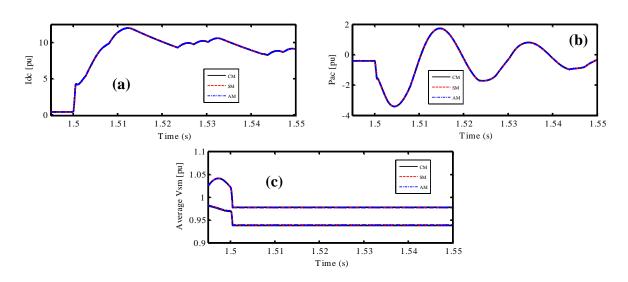

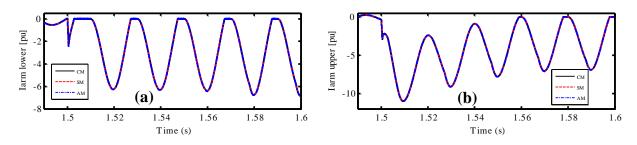

| Figure II-37: Dynamics response of detailed models for a loss of 10% SMs in one ar                                    | m: (a)          |

| active power, (b) average SM voltages for upper and lower arms for phase a                                            | 73              |

| Figure II-38: Dynamics response of detailed models for a loss of one arm: (a) active pow                              | /er, (b)        |

| average SM voltages for upper and lower arms for phase a.                                                             | 74              |

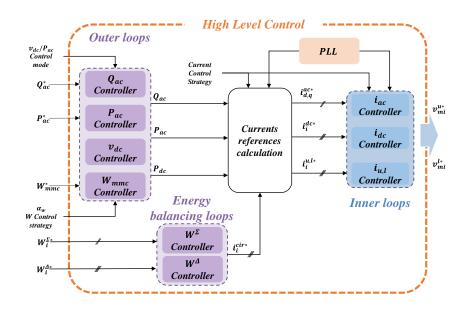

| Figure III-1: General scheme of MMC control.                                                                          | 79              |

| Figure III-2: Architecture of low level control.                                                                      | 80              |

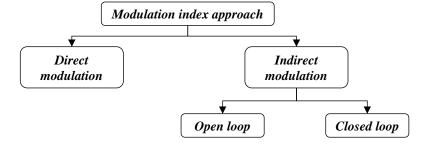

| Figure III-3: Modulation method diagram.                                                                              | 80              |

| Figure III-4: Modulation index classification.                                                                        | 81              |

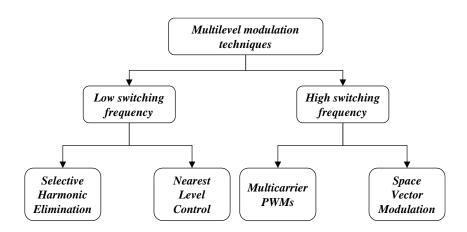

| Figure III-5: Multilevel modulation classification.                                                                   | 82              |

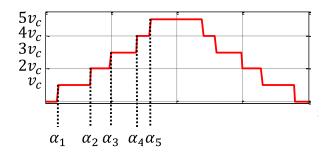

| Figure III-6: Modulated arm voltage using SHE modulation technique                                                    | 83              |

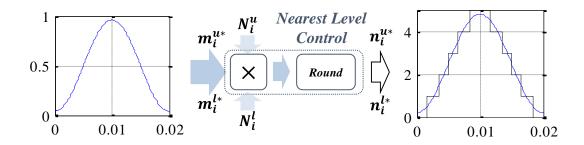

| Figure III-7: Nearest level modulation scheme.                                                                        | 84              |

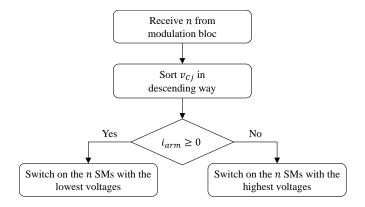

| Figure III-8: Basic BCA flowchart                                                                                     | 85              |

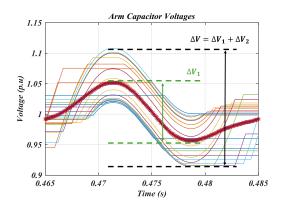

| Figure III-9: Voltage ripple $\Delta V = \Delta V 1 + \Delta V 2$ , average ripple $\Delta V 1$ and voltage tolerance | e Δ <i>V</i> 2. |

|                                                                                                                       | 85              |

| Figure III-10: Criteria and choices of balancing control algorithms.                                                  | 86              |

| Figure III-11: Balancing control algorithms classification.                                                           | 87              |

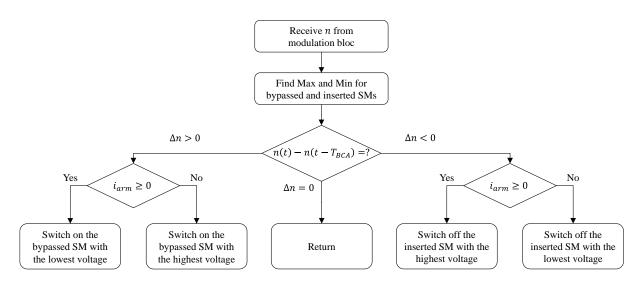

| Figure III-12: Reduced switching frequency algorithm flowchart                                                        | 87              |

| Figure III-13: Improved reduced switching frequency algorithm flowchart                                               | 88              |

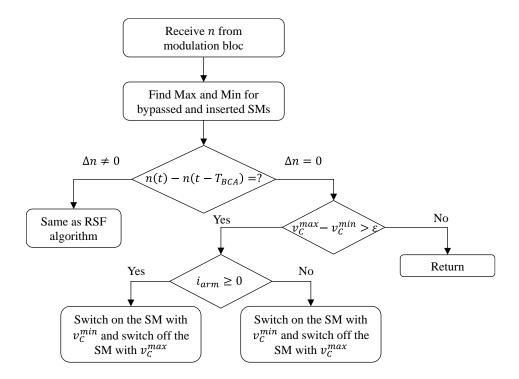

| Figure III-14: Average tolerance band algorithm flowchart.                                                            | 89              |

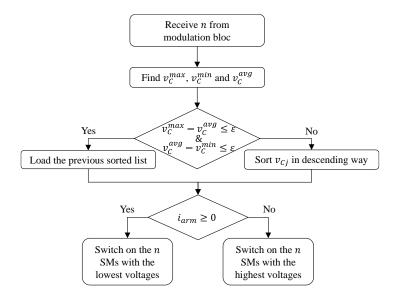

| Figure III-15: Cell tolerance band algorithm flowchart.                                                               | 90              |

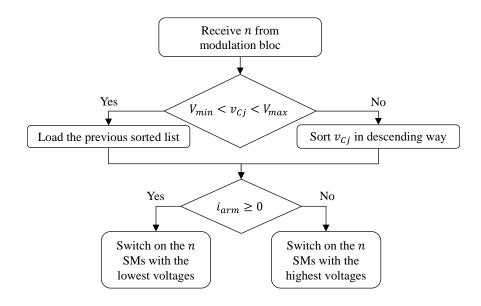

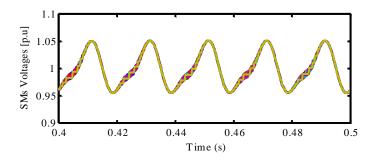

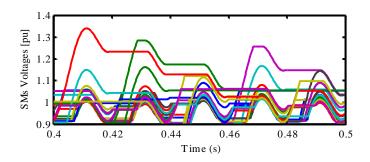

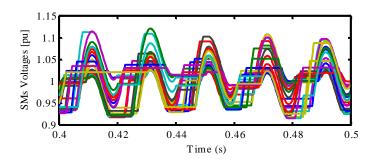

| Figure III-16: SM voltages using Basic BCA with 1 pu transferred power                                                | 91              |

| Figure III-17: (a) Switching frequency, (b) voltage ripple variations regarding transferred                           | power           |

| level using Basic BCA.                                                                                                | 92              |

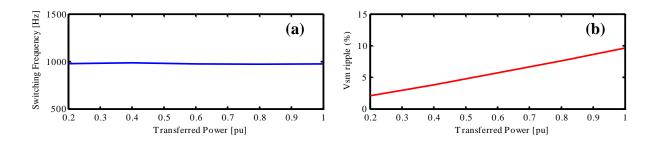

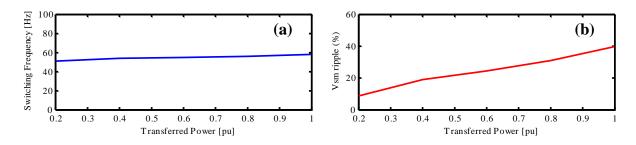

| Figure III-18: SM voltages using RSF-algorithm with 1 pu transferred power                                            | 92              |

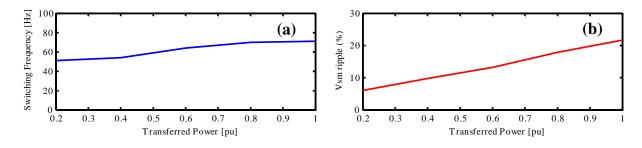

| Figure III-19: (a) Switching frequency, (b) voltage ripple variations regarding transferred                           | power           |

| level using RSF-algorithm.                                                                                            | 92              |

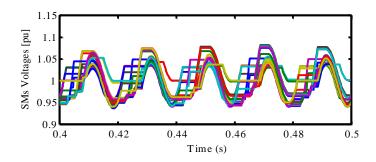

| Figure III-20: SM voltages using IRSF algorithm with 1 pu transferred power                                           | 93              |

| Figure III-21: (a) Switching frequency, (b) voltage ripple variations regarding transferred power |

|---------------------------------------------------------------------------------------------------|

| level using IRSF algorithm. 93                                                                    |

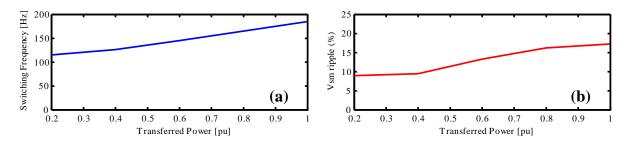

| Figure III-22: SM voltages using ATB algorithm with 1 pu transferred power94                      |

| Figure III-23: (a) Switching frequency, (b) voltage ripple variations regarding transferred power |

| level using ATB algorithm. 94                                                                     |

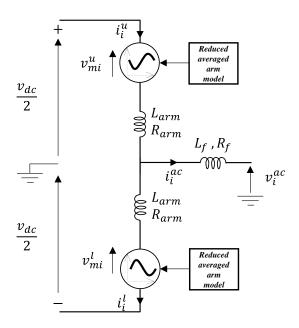

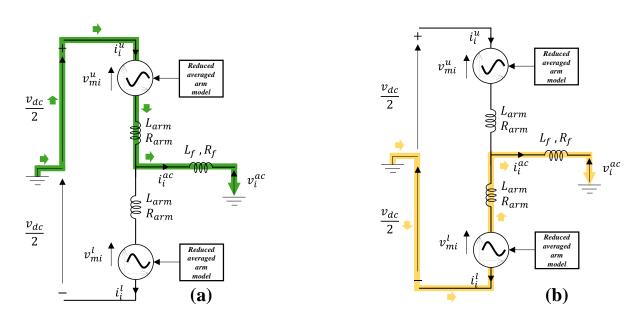

| Figure III-24: Simplified circuit for one MMC leg                                                 |

| Figure III-25: Upper and lower voltage loops                                                      |

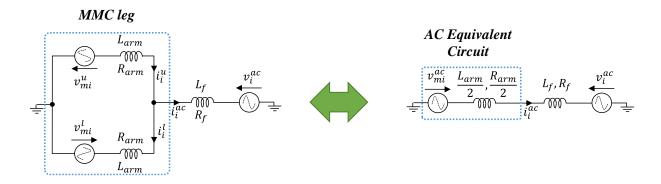

| Figure III-26: MMC equivalent circuit from AC standpoint                                          |

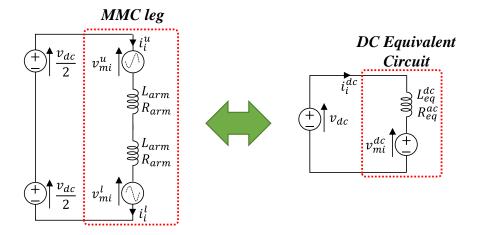

| Figure III-27: MMC equivalent circuit from DC standpoint                                          |

| Figure III-28: Power exchange inside the MMC.                                                     |

| Figure III-29: Distribution of stored energy in the MMC                                           |

| Figure III-30: Multivariable control diagram for MMC                                              |

| Figure III-31: Cascaded control principle                                                         |

| Figure III-32: Cascaded control scheme for MMC.                                                   |

| Figure III-33: Non-energy based control diagram                                                   |

| Figure III-34: Direct modulation indexes calculation                                              |

| Figure III-35: Non energy based control diagram including CCSC                                    |

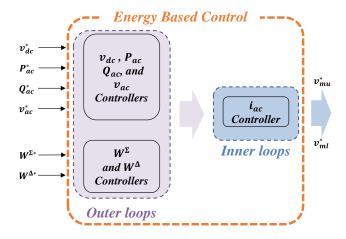

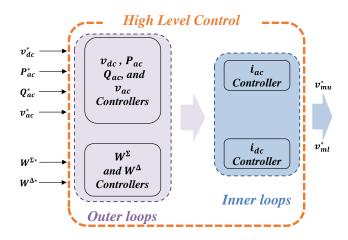

| Figure III-36: Energy based control diagram (first version)                                       |

| Figure III-37: Energy based control diagram (second version)                                      |

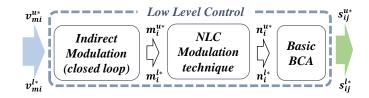

| Figure III-38: Schematic diagram for the considered low level control for thesis contributions    |

| 110                                                                                               |

| Figure III-39: Schematic diagram for the considered high level control for thesis contributions   |

| 110                                                                                               |

| Figure III-40: Zoom on outer loops configuration.                                                 |

| Figure III-41: Zoom on energy balancing loops configuration                                       |

| Figure IV-1: SM voltages variation using ATB algorithm                                            |

| Figure IV-2: (a) Switching frequency, (b) voltage ripple variations regarding transferred power   |

| and tolerance band parameter                                                                      |

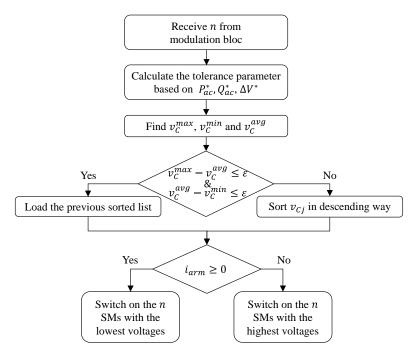

| Figure IV-3: Proposed improved average tolerance band method diagram                              |

| Figure IV-4: Proposed improved average tolerance band algorithm flowchart                         |

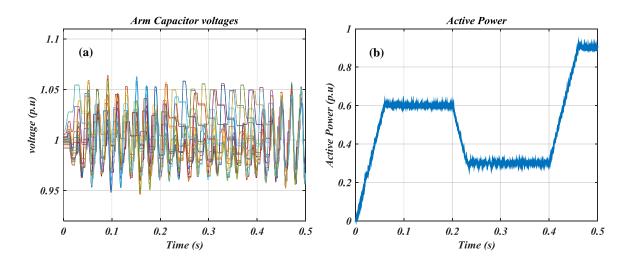

| Figure IV-5: Simulation results: (a) SM voltage for one arm, (b) active power                     |

| Figure IV-6: A zoom on SM voltages.                                                               |

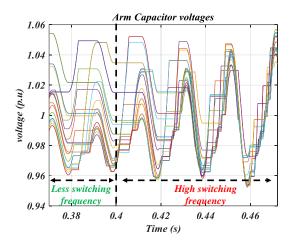

| Figure IV-7: Simulation circuit for sliding mode control validation                               |

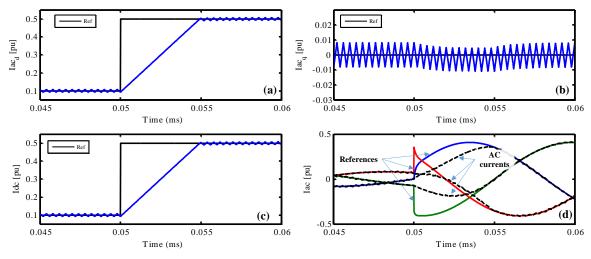

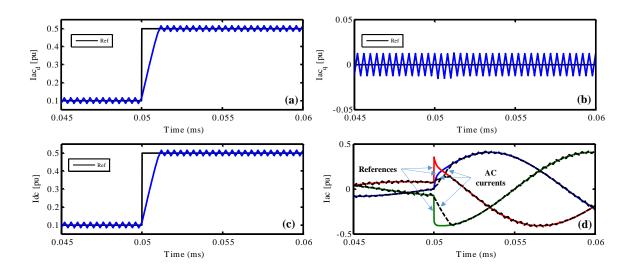

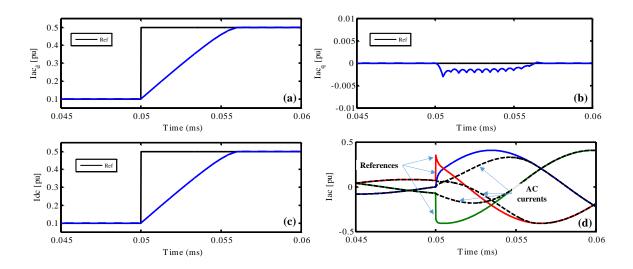

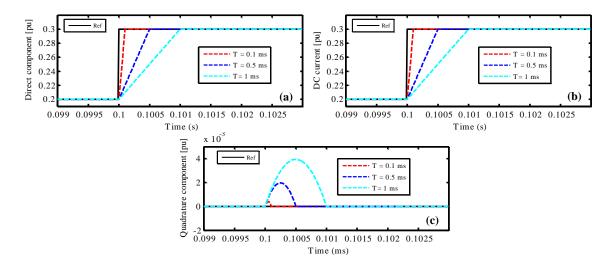

| Figure IV-8: Simulation results for active power reference change ( $kiac=kidc=10000$ ): (a)             |

|----------------------------------------------------------------------------------------------------------|

| direct component for AC currents, (b) quadrature component for AC currents, (c) DC current,              |

| (d) three phase AC currents                                                                              |

| Figure IV-9: Simulation results for reactive power reference change ( $kiac=kidc=10000$ ): (a)           |

| direct component for AC currents, (b) quadrature component for AC currents, (c) DC current,              |

| (d) three phase AC currents                                                                              |

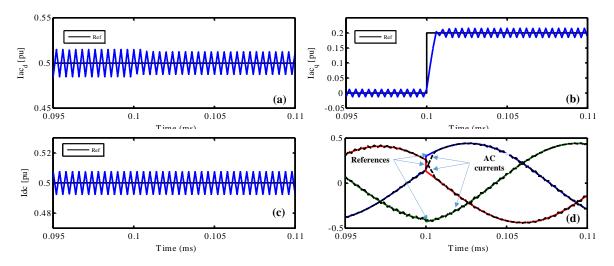

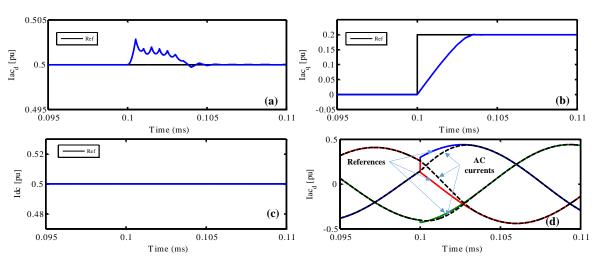

| Figure IV-10: Simulation results for active power reference change ( $kiac=kidc=10000$ , $\sigma=50$ ):  |

| (a) direct component for AC currents, (b) quadrature component for AC currents, (c) DC                   |

| current, (d) three phase AC currents                                                                     |

| Figure IV-11: Simulation results for reactive power reference change                                     |

| $(kiac=kidc=10000, \sigma=50)$ : (a) direct component for AC currents, (b) quadrature component          |

| for AC currents, (c) DC current, (d) three phase AC currents                                             |

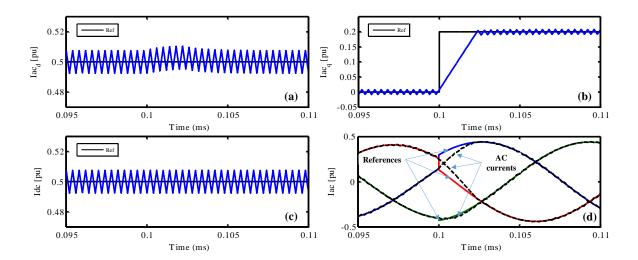

| Figure IV-12: Simulation results for active power reference change ( $kiac=kidc=30000$ , $\sigma=50$ ):  |

| (a) direct component for AC currents, (b) quadrature component for AC currents, (c) DC                   |

| current, (d) three phase AC currents                                                                     |

| Figure IV-13: Simulation results for reactive power reference change (kiac=kidc=30000,                   |

| $\sigma$ =50): (a) direct component for AC currents, (b) quadrature component for AC currents, (c)       |

| DC current, (d) three phase AC currents.                                                                 |

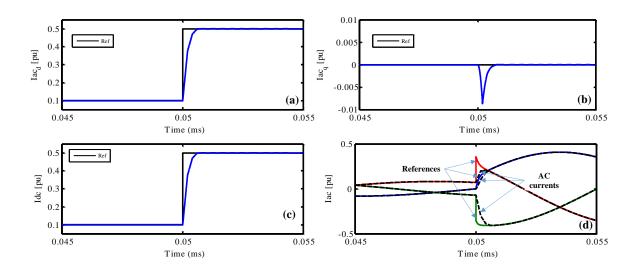

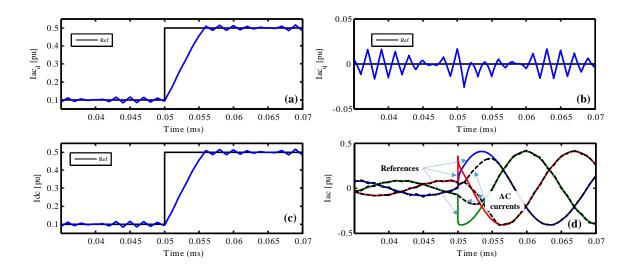

| Figure IV-14: Simulation results for active power reference change (kiac=kidc=10000,                     |

| $\sigma$ =50, $kpac$ = $kpdc$ =3200): (a) direct component for AC currents, (b) quadrature component for |

| AC currents, (c) DC current, (d) three phase AC currents                                                 |

| Figure IV-15: Simulation results for reactive power reference change (kiac=kidc=10000,                   |

| $\sigma$ =50, $kpac$ = $kpdc$ =3200): (a) direct component for AC currents, (b) quadrature component for |

| AC currents, (c) DC current, (d) three phase AC currents                                                 |

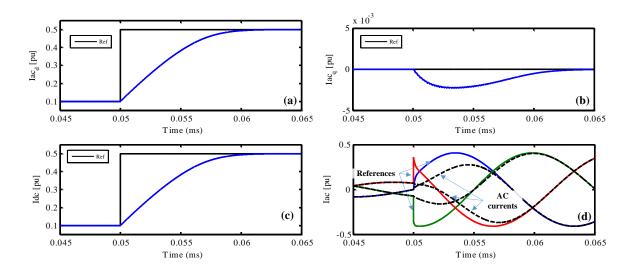

| Figure IV-16: Simulation results for active power reference change with T=0.5 ms                         |

| ( $kiac=kidc=10000$ , $\sigma=50$ , $kpac=kpdc=3200$ ): (a) direct component for AC currents, (b)        |

| quadrature component for AC currents, (c) DC current, (d) three phase AC currents 140                    |

| Figure IV-17: Simulation results for reactive power reference change with T=0.5 ms                       |

| ( $kiac=kidc=10000$ , $\sigma=50$ , $kpac=kpdc=3200$ ): (a) direct component for AC currents, (b)        |

| quadrature component for AC currents, (c) DC current, (d) three phase AC currents 140                    |

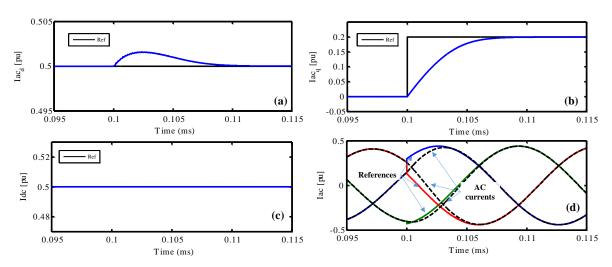

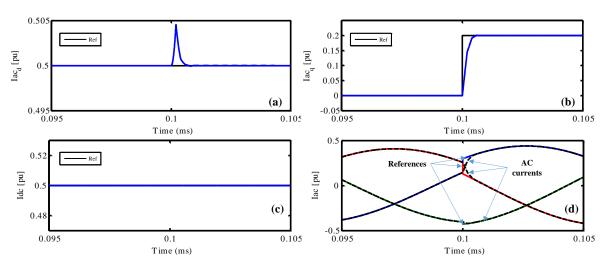

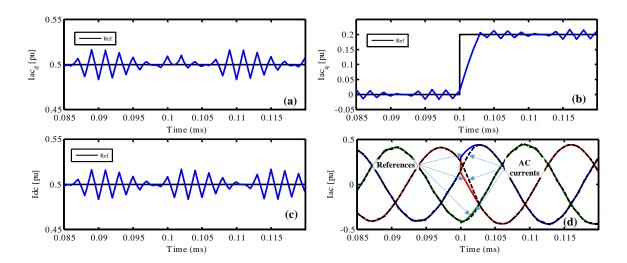

| Figure IV-18: Simulation results for active power reference change with T=1 ms                           |

| ( $kiac=kidc=10000$ , $\sigma=50$ , $kpac=kpdc=3200$ ): (a) direct component for AC currents, (b)        |

| quadrature component for AC currents (c) DC current (d) three phase AC currents 1/11                     |

| Figure IV-19: Simulation results for reactive power reference change with T=1 ms                             |

|--------------------------------------------------------------------------------------------------------------|

| ( $kiac=kidc=10000$ , $\sigma=50$ , $kpac=kpdc=3200$ ): (a) direct component for AC currents, (b)            |

| quadrature component for AC currents, (c) DC current, (d) three phase AC currents 142                        |

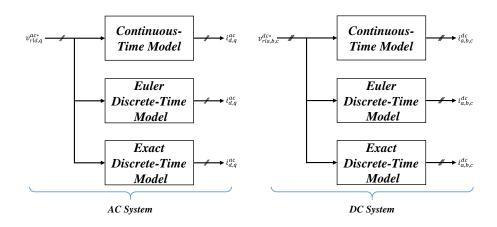

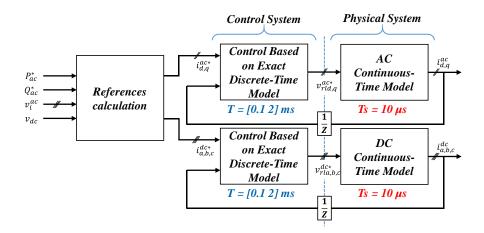

| Figure IV-20: Simulation circuit for discrete-time models validation                                         |

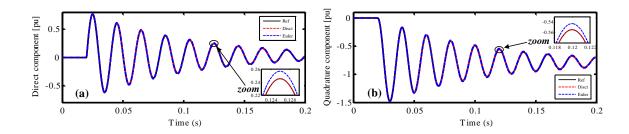

| Figure IV-21: AC discrete-time models dynamics with 10 $\mu s$ : (a) $idac$ , (b) $iqac$ variations. 147     |

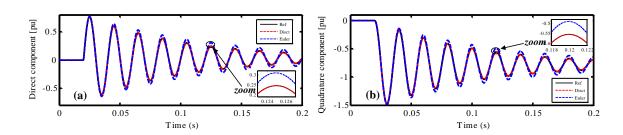

| Figure IV-22: AC discrete-time models dynamics with 50 $\mu s$ : (a) $idac$ , (b) $iqac$ variations. 147     |

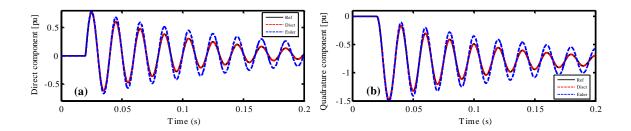

| Figure IV-23: AC discrete-time models dynamics with 100 $\mu s$ : (a) $idac$ , (b) $iqac$ variations.        |

|                                                                                                              |

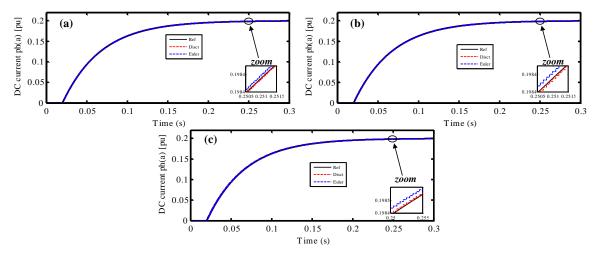

| Figure IV-24: DC discrete-time models dynamics: $iadc$ variation with (a) 10 $\mu$ s, (b) 50 $\mu$ s and     |

| (c) 100 µs                                                                                                   |

| Figure IV-25: Simulation circuit for discrete-time controller validation                                     |

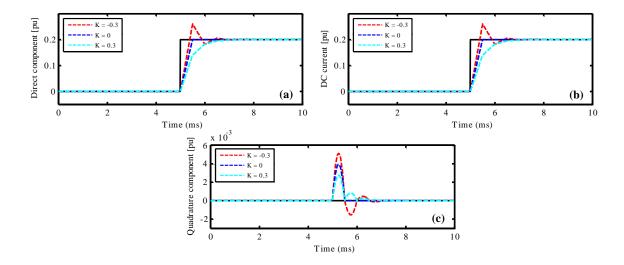

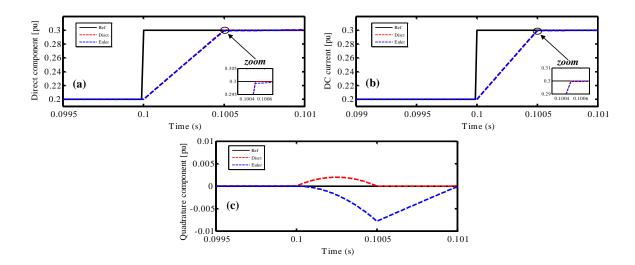

| Figure IV-26: Proposed controllers dynamics with different gain values: (a) direct component                 |

| for AC currents, (B) DC current, (c) quadrature component for AC currents162                                 |

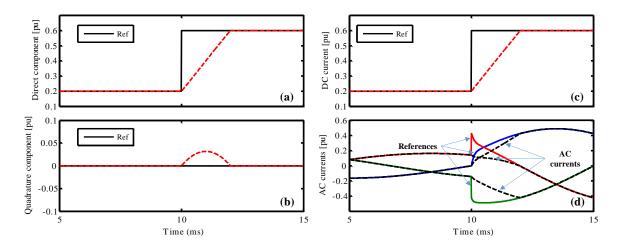

| Figure IV-27: Proposed controllers dynamics with 2 ms sampling period: (a) direct component                  |

| for AC currents, (b) quadrature component for AC currents, (c) DC current, (d) three phase AC $$             |

| currents. 162                                                                                                |

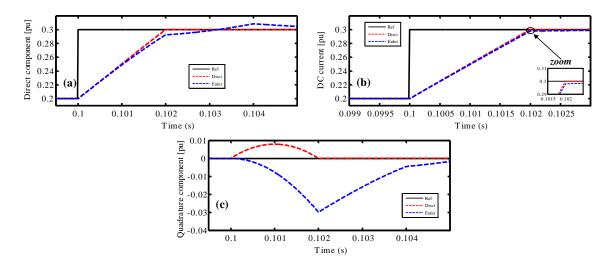

| Figure IV-28: Proposed controllers dynamics with different sampling periods: (a) direct                      |

| component for AC currents, (b) DC current, (c) quadrature component for AC currents 163                      |

| Figure IV-29: Discrete-time controllers performances with 0.5 ms sampling period: (a) direct                 |

| component for AC currents, (b) DC current, (c) quadrature component for AC currents 164                      |

| Figure IV-30: Discrete-time controllers performances with 2 ms sampling period: (a) direct                   |

| component for AC currents, (b) DC current, (c) quadrature component for AC currents 164                      |

| Figure IV-31: Simulation circuit for offline control validation                                              |

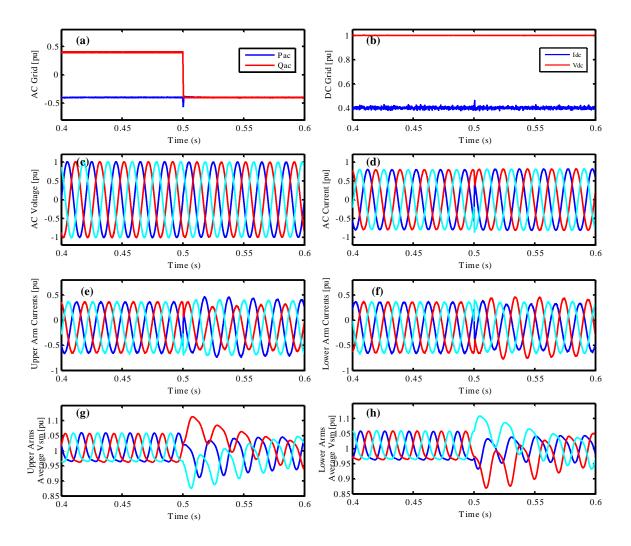

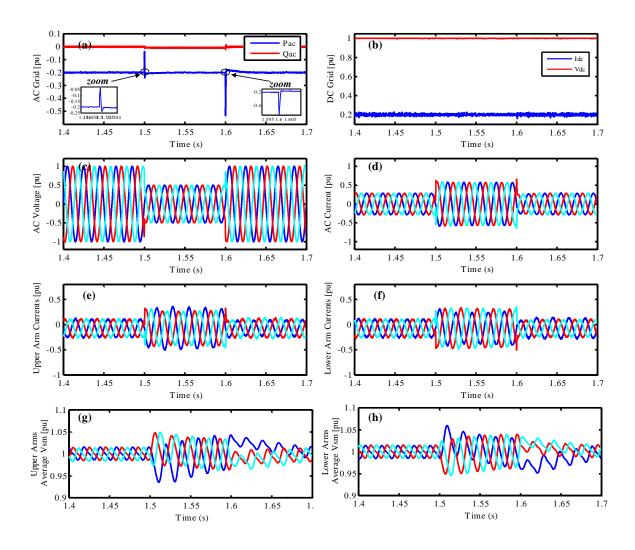

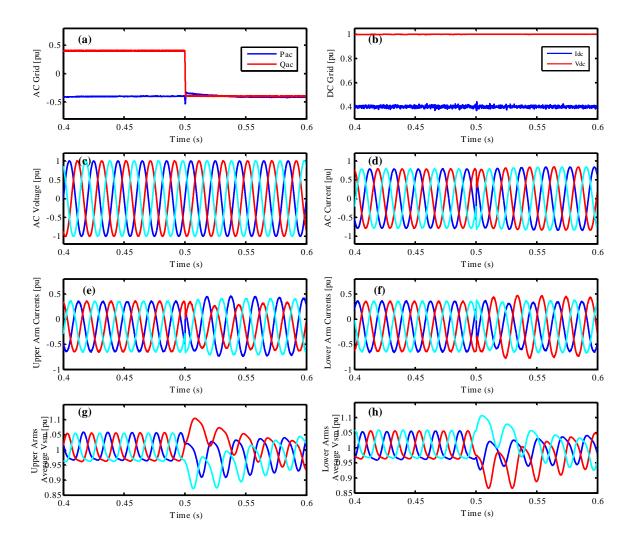

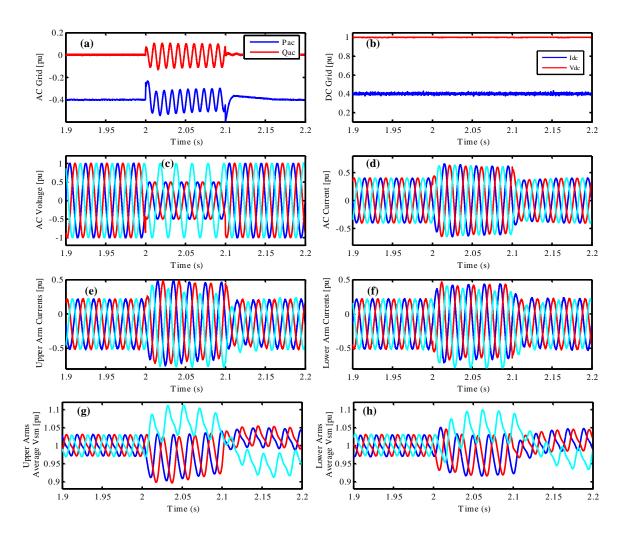

| Figure IV-32: Simulation results with 0.2 ms sampling period: (a) active and reactive power,                 |

| (b) DC current with DC voltage, (c) AC voltages, (d) AC currents, (e) upper arm currents, (f)                |

| $lower\ arm\ currents, (g)\ average\ SM\ voltages\ for\ upper\ arms, (h)\ average\ SM\ voltages\ for\ lower$ |

| arms                                                                                                         |

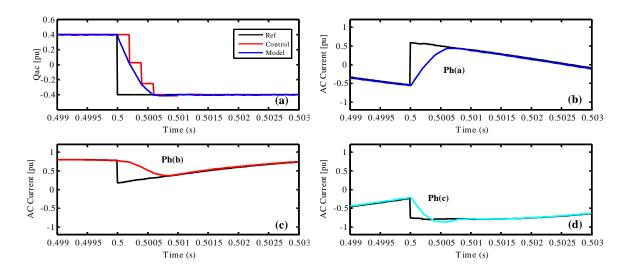

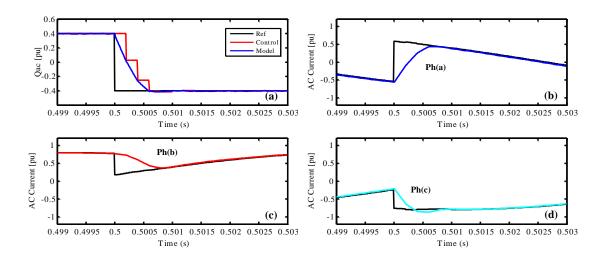

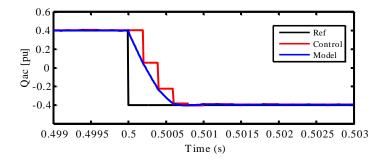

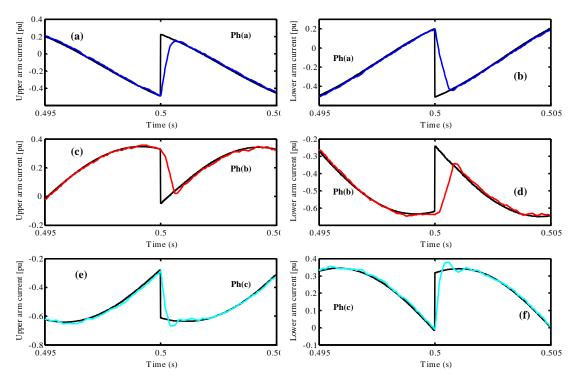

| Figure IV-33 Zoom on simulation results with 0.2 ms sampling period: (a) reactive power, (b)                 |

| AC current phase (a), (b) AC current phase (b), (b) AC current phase (c)                                     |

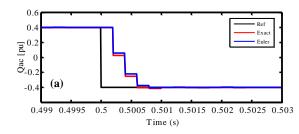

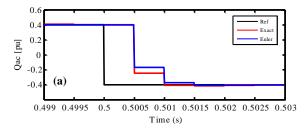

| Figure IV-34: Reactive power for different controllers with 0.2 ms sampling period: (a)                      |

| measurement, (b) seen by control                                                                             |

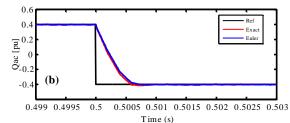

| Figure IV-35: Reactive power for different controllers with 0.5 ms sampling period: (a)                      |

| measurement, (b) seen by control                                                                             |

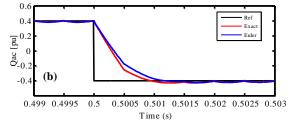

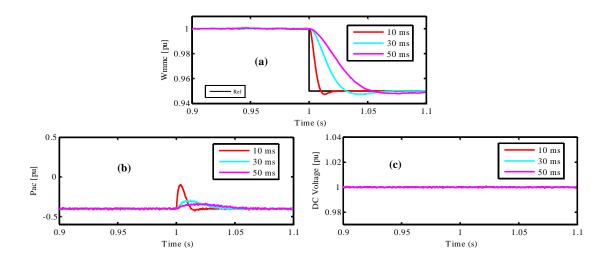

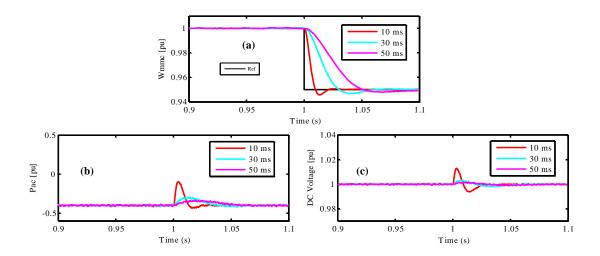

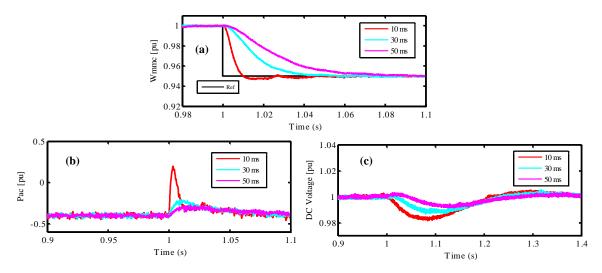

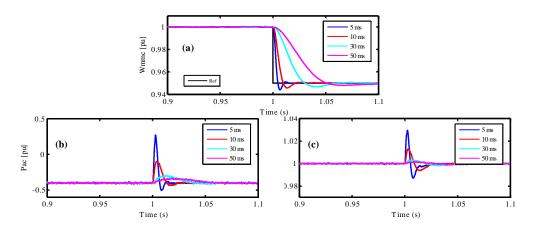

| Figure IV-36: Simulation results with different energy loop time response $\alpha W = 0$ : (a) MMC |

|----------------------------------------------------------------------------------------------------|

| energy, (b) active power, (c) DC voltage                                                           |

| Figure IV-37: Simulation results with different energy loop time response $\alpha W=1$ : (a) MMC   |

| energy, (b) Active power, (c) DC voltage                                                           |

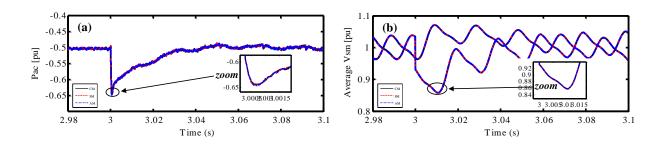

| Figure IV-38: Simulation results for symmetrical AC voltage dip with 0.2 ms sampling period:       |

| (a) active and reactive power, (b) DC current with DC voltage, (c) AC voltages, (d) AC currents,   |

| (e) upper arm currents, (f) lower arm currents, (g) average SM voltages for upper arms, (h)        |

| average SM voltages for lower arms                                                                 |

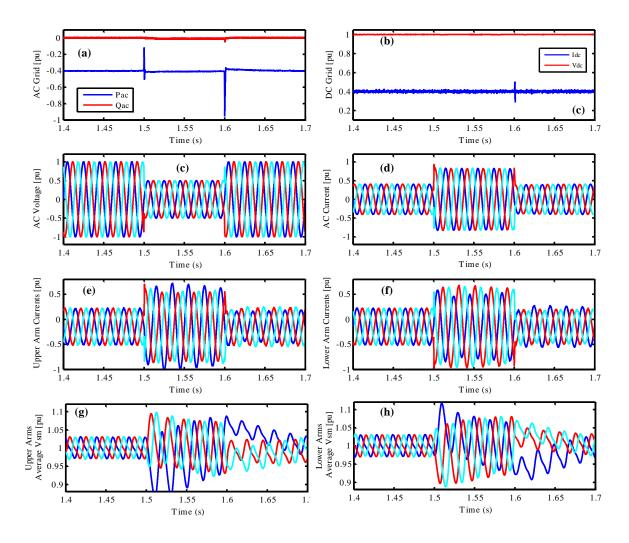

| Figure IV-39: Simulation results for Asymmetrical AC voltage dip with 0.2 ms sampling              |

| period: (a) Active and reactive power, (b) DC current with DC voltage, (c) AC voltages, (d) AC     |

| currents, (e) Upper arm currents, (f) lower arm currents, (g) Average SM voltages for upper        |

| arms, (h) Average SM voltages for lower arms                                                       |

| Figure V-1: The variation of voltage THD regarding the number of SMs                               |

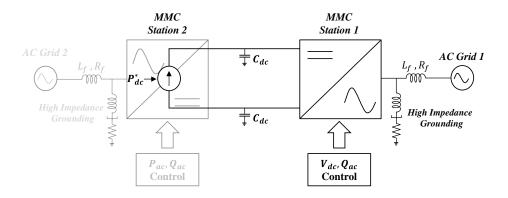

| Figure V-2: Hardware in the loop simulation circuit                                                |

| Figure V-3: Zoom on the HIL configuration                                                          |

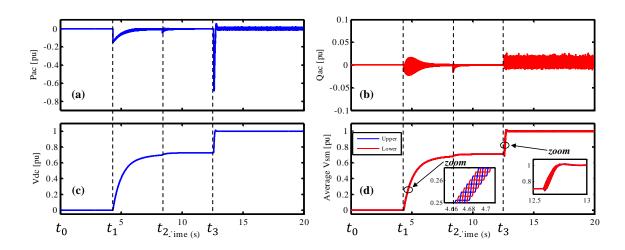

| Figure V-4: HIL results for start-up sequence: (a) active power, (b) reactive power, (c) DC grid   |

| voltage, (d) average SM voltages for leg (a).                                                      |

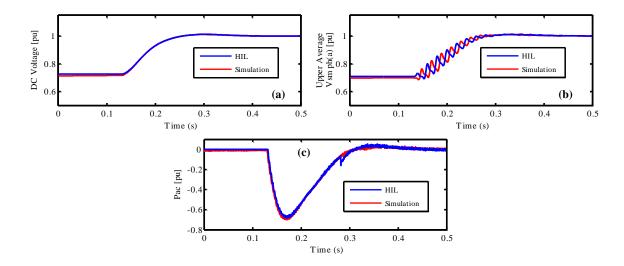

| Figure V-5: Comparison between offline and HIL simulation results for control activation           |

| during the start-up process: (a) DC grid voltage, (b) upper arm average SM voltage for leg (a),    |

| (c) active power. 185                                                                              |

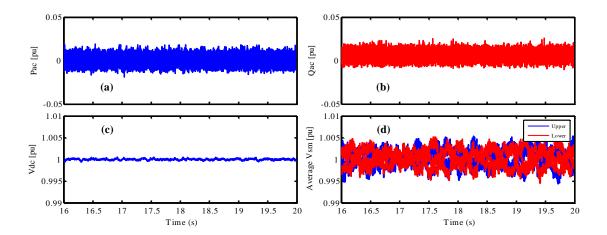

| Figure V-6: Zoom on HIL results for start-up sequence: (a) Active power, (b) reactive power,       |

| (c) DC grid voltage, (d) average SM voltages for leg (a)                                           |

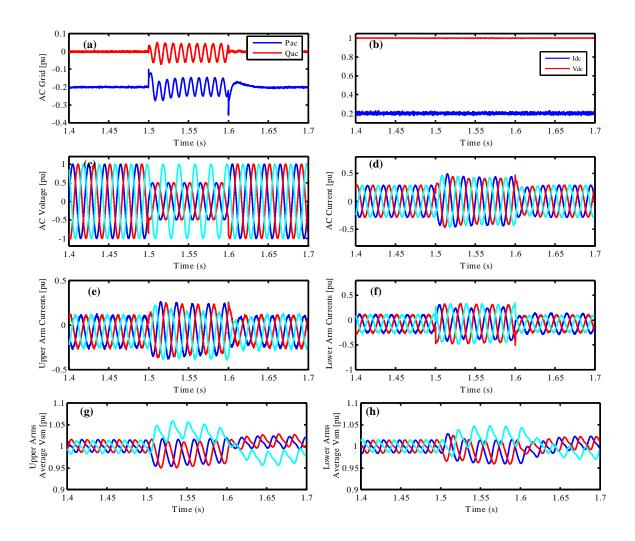

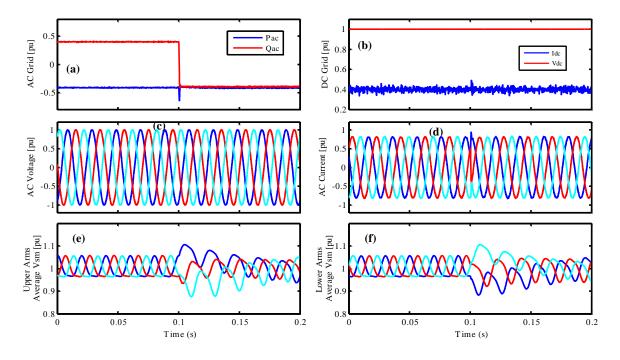

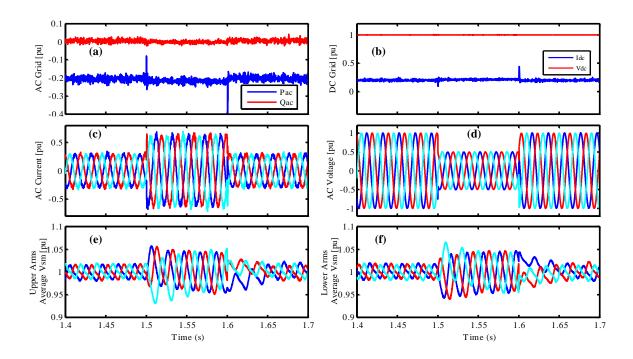

| Figure V-7: HIL simulation results for reactive power step change: (a) active and reactive         |

| powers, (b) DC voltage with DC current, (c) AC voltage, (d) AC current, (e) upper average SM       |

| voltages, (f) lower average SM voltages                                                            |

| Figure V-8: Small scale MMC station                                                                |

| Figure V-9: Experimental test bench setup                                                          |

| Figure V-10: Experimental results for start-up sequence: (a) Active power, (b) reactive power,     |

| (c) DC grid voltage, (d) average SM voltages for leg (a)                                           |

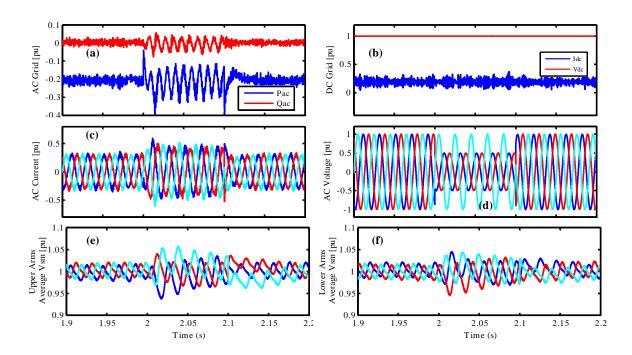

| Figure V-11: Experimental results for reactive power step change: (a) active and reactive          |

| powers, (b) DC voltage with DC current, (c) AC voltage, (d) AC current, (e) upper arm currents,    |

| (f) lower arm currents, (g) upper average SM voltages, (h) lower average SM voltages, 190          |

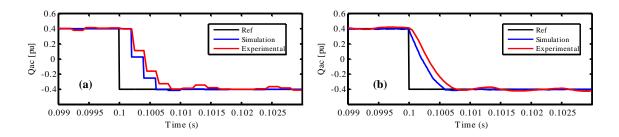

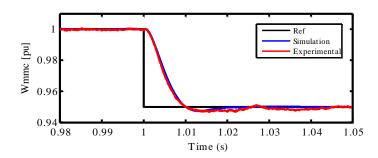

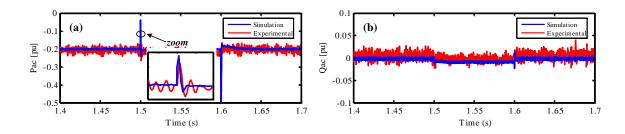

| Figure V-12: Comparison between simulation and experimental results for reactive power step            |

|--------------------------------------------------------------------------------------------------------|

| change: (a) seen by control, (b) measurements                                                          |

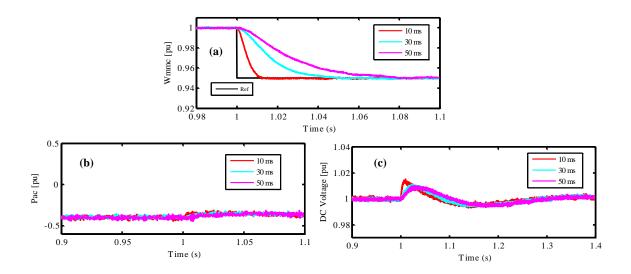

| Figure V-13: Experimental results for energy step change with AC control strategy $\alpha W = 0$ : (a) |

| MMC energy, (b) active power, (c) DC voltage                                                           |

| Figure V-14: Experimental results for energy step change with DC control strategy $\alpha W = 1$ : (a) |

| MMC energy, (b) active power, (c) DC voltage                                                           |

| Figure V-15: Comparison between simulation and experimental results for energy step change             |

| with AC control strategy ( $\alpha w = 0$ )                                                            |

| Figure V-16: Experimental results for symmetric AC voltage dip (50%): (a) active and reactive          |

| powers, (b) DC voltage with DC current, (c) AC current, (d) AC voltage, (e) upper average SM           |

| voltages, (f) lower average SM voltages                                                                |

| Figure V-17: Comparison between simulation and experimental results for symmetric AC                   |

| voltage dip (50%): (a) Active power, (b) reactive power                                                |

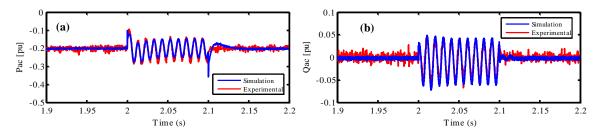

| Figure V-18: Experimental results for asymmetric AC voltage dip (50%): (a) active and reactive         |

| powers, (b) DC voltage with DC current, (c) AC current, (d) AC voltage, (e) upper average SM           |

| voltages, (f) lower average SM voltages                                                                |

| Figure V-19: Experimental results for symmetric AC voltage dip (50%): (a) active and reactive          |

| powers, (b) DC voltage with DC current, (c) AC current, (d) AC voltage, (e) upper average SM           |

| voltages, (f) lower average SM voltages                                                                |

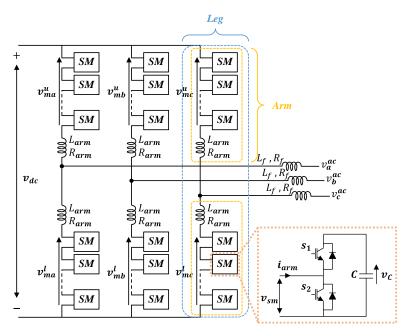

| Figure-1: La structure du convertisseur MMC étudiée dans la thèse                                      |

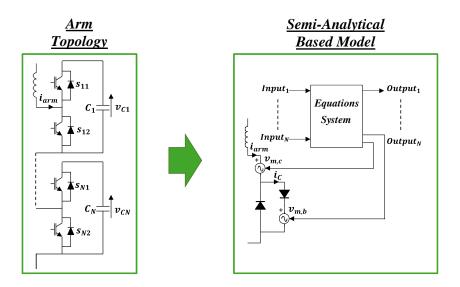

| Figure-2: Le modèle semi-analytique proposé pour un bras du MMC                                        |

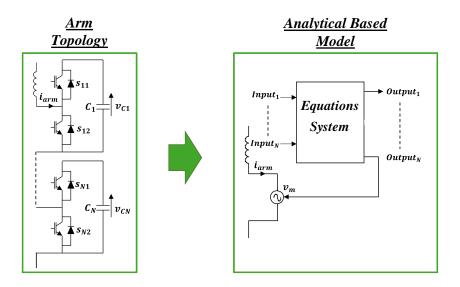

| Figure-3: Le modèle analytique proposé pour un bras du MMC                                             |

| Figure-4: Schéma de contrôle retenu pour l'étage supérieur                                             |

| Figure-5: Schéma de contrôle retenu pour l'étage inférieur                                             |

| Figure-6: Résultats de simulation pour un échelon sur la puissance réactive avec une période           |

| d'échantillonnage de 0,2 ms: (a) puissance réactive, (b) courant alternatif dans la phase (a), (c)     |

| courant alternatif dans la phase (b), (d) courant alternatif dans la phase (c)                         |

| Figure-7: Résultats de simulation pour un échelon sur l'énergie interne du MMC: (a) énergie            |

| stockée dans le MMC, (b) la variation de la puissance active, (c) la variation de la tension du        |

| bus DC                                                                                                 |

| Figure-8: Comparaison entre les résultats de simulation et les résultats expérimentaux pour un   |

|--------------------------------------------------------------------------------------------------|

| échelon sur l'énergie interne du MMC.                                                            |

| Figure-9: Comparaison entre les résultats de simulation et les résultats expérimentaux pour un   |

| creux symétrique de tension AC (50%): (a) la variation de la puissance active, (b) la variation  |

| de la puissance réactive.                                                                        |

| Figure-10: Comparaison entre les résultats de simulation et les résultats expérimentaux pour un  |

| creux asymétrique de tension AC (50%): (a) la variation de la puissance active, (b) la variation |

| de la puissance réactive                                                                         |

### **Abstract**

Common understanding today is that the challenges to develop the SuperGrid are huge at many levels (e.g.: political, societal, economical, financial, scientific, technical...). It is also commonly accepted that the SuperGrid will require novel technologies (breakers, cables, converters...) and operating principles (e.g.: transition from a more passive essentially AC-based power system to a more active AC/DC-based one). This thesis deals with the development of a key actor for SuperGrid technology, that is, AC/DC converters.

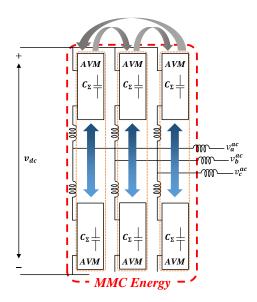

Recently, the Modular Multilevel Converter (MMC) has gained more and more importance for different applications, particularly for High Voltage Direct Current (HVDC). This topology, firstly proposed by Lesnicar and Marquardt in 2003, has many advantages compared to other Voltage Source Converter (VSC) topologies. As the name suggests, the topology is modular and easily scalable in terms of voltage levels: excellent AC output voltage and DC voltage can be easily increased by adding new cells. Moreover, thanks to the redundant cells, the MMC can also manage its internal degraded modes which are important technical and economic issues.

The development of a complex structure such as the MMC, requires a detailed analysis of its state variables and a depth understanding of its behavior when integrated. This necessitates developments of accurate models (detailed and/or simplified) and performant control systems. In 2014, when this work has started, many studies from academia as well as industry involving modeling and control of Modular Multilevel Converter have been carried out. In this thesis, these two aspects have been reviewed, analyzed and improved by proposing new models based on several implementation methods, in addition to develop innovative control algorithms in order to fulfill industrial requests by allowing fast MMC dynamics. Real time simulation as well as experimental tests have been carried out to validate our findings.

### Résumé

La compréhension commune aujourd'hui est que les défis pour développer le réseau SuperGrid sont énormes et à plusieurs niveaux (p. Ex.: Politique, sociale, économique, financier, scientifique, technique ...). Il est également admis que le réseau SuperGrid nécessitera de nouvelles technologies (disjoncteurs, câbles, convertisseurs ...) et de nouveaux principes de fonctionnement (p. Ex.: transition d'un système d'alimentation passif essentiellement à base d'un réseau alternative (AC) à un système plus actif à base d'un réseau hybride alternative/continue (AC/DC)). Cette thèse porte sur la modélisation et le contrôle d'un élément clé pour les réseaux SuperGrid qui est le convertisseur AC / DC.

Récemment, et pour beaucoup d'application telle que le transport d'électricité en courant continu à très haute tension (HVDC), le Convertisseur Modulaire Multiniveau (MMC) semble devenir un élément incontournable. Cette topologie, proposée par Lesnicar et Marquardt en 2003, présente de nombreux avantages par rapport aux autres topologies de convertisseur à source de tension (VSC). Comme son nom l'indique, cette topologie est modulaire et facilement évolutive en termes de niveaux de tension: une excellente qualité de tension alternative en sortie et une tension continue qui peut être augmentée facilement en ajoutant des cellules en série. De plus, grâce aux cellules redondantes, le MMC peut également gérer ses modes dégradés internes qui peuvent donner lieu à des problèmes (techniques et économiques) importants.

Le développement d'une structure complexe telle que le MMC nécessite une analyse détaillée de ses variables d'état et une compréhension approfondie de son comportement avant son intégration. Cela nécessite des développements de modèles précis (détaillés et/ou simplifiés) et des systèmes de contrôle performants. En 2014, lorsque ce travail a débuté, une analyse de l'état de l'art des recherches et études menées par des chercheurs universitaires et industriels impliquant la modélisation et le contrôle-commande des MMC a été réalisée. Dans cette thèse, ces deux aspects principaux ont été revus, analysés et améliorés. D'abord en proposant de nouveaux modèles et méthodes de mise en œuvre, ensuite en développant des algorithmes innovants pour répondre aux demandes industrielles permettant une dynamique rapide pour le MMC. Des simulations en temps réel ainsi que des tests expérimentaux ont été réalisés pour valider ces résultats obtenus.

## **List of Publications**

The publications resulting from this thesis are listed below:

#### **Patents**

- A. Zama, S. Bacha, A. Benchaib, D. Frey, and S. Silvant, "Procédé de simulation d'un convertisseur modulaire multiniveaux y compris dans l'état bloqué." Applied for a patent, 01/07/2016.

- **A. Zama**, A. Benchaib, S. Bacha, D. Frey, and S. Silvant, "Procédé de contrôle d'un convertisseur modulaire multi-niveaux" **Applied for a patent, 01/08/2016.**

- A. Zama, M. Romero, A. Benchaib, and B. Luscan: "Dispositif de contrôle d'un terminal pour le rétablissement de la puissance dans une installation", Applied for a patent, 20 Avril 2017.

### Journal papers

- A. Zama, S. Bacha, A. Benchaib, D. Frey, and S. Silvant, "A novel modular multilevel converter modeling technique based on semi-analytical models for HVDC application".

Journal of Electrical Systems, 12(4), (2016).

- A. Zama, A. Benchaib, S. Bacha, D. Frey, and S. Silvant, "High Dynamics Control for MMC Based on Exact Discrete-Time Model with Experimental Validation". IEEE Transactions on Power Delivery, (2017).

- A. Zama, A. Benchaib, S. Bacha, D. Frey, and S. Silvant, "Advanced Currents Control Based on Discrete-Time Sliding Mode Control for Modular Multilevel Converter: Experimental Results". Submitted for IEEE Transactions on Industrial Electronics.

## **Conferences papers**

Ahmed Zama, "A Review of Modular Multi-Level Converter (MMC) Modeling for HVDC Application." In Journée des jeunes chercheurs en génie électrique, Cherbourg, France. June 2015.

- A. Zama, S. Bacha, A. Benchaib, D. Frey, and S. Silvant, "A Novel Modular Multilevel Converter Modelling Technique Based on Semi-Analytical Models." In international Conference on Renewable Energy: Generation and Applications (2016).

- A. Zama, D. Frey, A. Benchaib, S. Bacha, B. Luscan, and S. Silvant, "Optimisation des Pertes par Commutation dans un Convertisseur Modulaire Multiniveaux (MMC)." In Symposium de Genie Electrique (SGE 2016). ), June. 2016, conference location: Grenoble.

- A. Zama, S. Ait Mansour, D. Frey, A. Benchaib, S. Bacha and B. Luscan, "A

Comparative Assessment of Different Balancing Control Algorithms for Modular

Multilevel Converter (MMC)", In press, the 18th European Conference on Power

Electronics and Applications (EPE 2016), Sept. 2016, conference location: Karlsruhe.

- A. Zama, A. Benchaib, S. Bacha, D. Frey, and S. Silvant, "Advanced MMC Current Controllers With Experimental Validations Using OP1200 Test Bench". 9ème Conférence Internationale sur la Simulation Temps Réel par OPAL-RT Delivery (RT'17), Sept 2017, conference location: Montréal.

#### Thesis context

Nowadays, energy systems are facing many requirements and challenges which need a paradigm-shift. Political and public willingness to increase energy independency, reduce greenhouse gas emissions and increase exchange capabilities require urgent actions in order to meet such ambitious targets. To do so, it is highly expected that the integration of large amount of renewable energy systems will play a crucial role for future power systems. In addition, in order to increase the robustness of the actual systems and create a large electric network, the interconnection of different countries and continents can be considered as a good solution. In order to achieve a good power distribution, we cannot rely only on Kirchhoff laws. The insertion of power electronic devices associated to new control concept and the increase of the submarine links capacities will enhance the management of the energy fluxes. It is therefore necessary to look for an optimum transmission solution (economical, technical, financial...) to meet all these needs.

High Voltage Direct Current (HVDC) based on Voltage Source Converter (VSC) technology has broadly appeared as a good solution to answer this question. Several HVDC projects have been developed or currently planned around the world: Trans Bay Cable, (USA), INELFE (France-Spain), Rio Madeira (Brazil), Nanao multi-terminal VSC-HVDC (China)...This will lead to the development of meshed grids including Multi terminal DC grid (MTDC) which opens an opportunity for hybrid AC/DC transmission systems. For this purpose, new operation philosophies as well as sophisticated equipments to operate such new transmission systems are more and more required. Considerable research are carried out today to meet these needs such as:

- Define new DC grid code.

- Investigate the interaction between AC and DC grids.

- Develop new equipment: cables, breakers, power converters, surge-arresters...

One of the key actors for HVDC technology development is the AC/DC converter. Various VSC topologies, including two-level, three-level and floating capacitor converters have been proposed in the literature. For further improvements of power quality and reliability, the Modular Multilevel Converter (MMC) has been gathering considerable attention since its

invention. Thanks to its scalability, performance and efficiency, this topology is considered as the most promising solution for AC/DC converter for HVDC applications.

This thesis deals with the development of models and associated controls of MMCs. The large number of switching elements and state variables inside of the MMC introduce modelling challenges especially when implemented in electromagnetic transient (EMT) programs for simulation purpose. Moreover, the control system for this structure is a bit different than other VSC topologies, since the storage management is not the same, which necessitates a special attention. More specifically, this thesis investigates these two aspects in order to well understand these challenges and propose new solutions.

The first contribution of this thesis is the development of new models (full order and reduced order), based on different implementation techniques. The obtained models allow to reduce the switching elements leading to facilitate their implementation in EMT programs and, hence, accelerate the simulations. The second contribution is to propose new control algorithms for current controllers. Two methods have been used to derive their control laws which allow to obtain the fastest response time.

# Main objectives and thesis methodology

The focus of this thesis covers the modeling and control of MMC, its main objectives are:

- Investigate the existing MMC model types (detailed, equivalent and averaged).

- Propose new implementation techniques including analytical equations for existing models to reduce computational time.

- Identify the effect of Balancing Control Algorithm (BCA) regarding MMC operation as well as its dimensioning criteria.

- Propose new advanced control algorithms for current loops when the cascaded control approach is used.

- Integrate the sampling period of hardware control in the control algorithm of current loops to go further in term of response time.

• Explore the possibility of accelerating the outer layer such as the energy loop.

The obtained results in this thesis are mainly derived from theoretical analysis of the considered converter topology (MMC based on Half-Bridge Sub-Modules). This is achieved by, first, deriving different analytical expressions for several model types. After that, the simplified models are used to perform theoretical analysis of MMC operation which leads to propose new control algorithms. The obtained results, in term of modeling and control, are then validated either by offline/Real-time simulations or by experimental tests.

#### Thesis outline

This thesis is organized as follows:

**Chapter 1:** This chapter introduces the HVDC grid technology and its principle. First, the HVDC configurations are presented with their associated advantages and drawbacks. After that, the main AC/DC converter technologies which are Line-Commuted Converter (LCC) and Voltage Source Converter (VSC) are presented and compared. Finally, the advantage of MMC compared to other VSC topologies are shown in order to understand the motivation behind the focus of the thesis.

**Chapter 2:** This chapter deals with the modeling of MMC. In order to well understand this research axis, the problematic related to its dynamics modeling is addressed. After a state of the art based on recent bibliography references, three dynamic models are chosen to address thesis contributions in the field of MMC modeling which are: detailed, equivalent and averaged models. For the considered models, new implementation methods are developed, explained and validated.

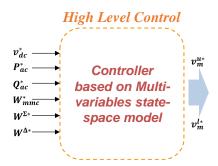

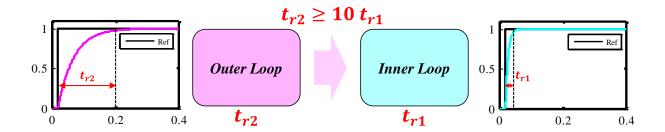

**Chapter 3 and chapter 4:** These two chapters cover the problematic related to the control of MMC. Chapter 3 introduces the MMC control principle and its two main layers. These latter are explained and reviewed based on recent bibliography publications with the conclusion that the energy based control allows to obtain a better control of all MMC variables. The cascaded structure which is based on time scales assumption allows to handle the control objective in a decoupling manner. Such decoupling necessitates slow response time for outer loops (control objectives) in order to maintain the time ratio between the layers. Chapter 4 proposes high

dynamics controllers for inner loops in order to accelerate the response time of outer ones. Based on exact discretization of MMC state-space models, two control methods have been used to derive current control laws which are: pole placement method and discrete-time sliding mode control. Offline simulations have demonstrated that the proposed controls present many advantages in terms of performances on one hand and allow to accelerate the outer loops such as energy loop (5 ms) on the other hand.

**Chapter 5:** The aim of this chapter is to validate the previous results on real time simulation test bench. Before going to Rapid Control Prototyping (RCP) test, Hardware in the Loop (HIL) validation is used to anticipate some constrains such as measurements delay and noises. Small scale MMC has been sized in order to have the same dynamics as a real MMC which will be used for the RCP test. The experimental results show a good correlation with simulation ones.

# CHAPTER I HVDC Technology and Architectures

#### 1. Introduction

This chapter provides a brief introduction to HVDC transmission system followed by the chronological evolution of various AC/DC converter employed for such application. This permits to better understand the advantages carried with the Modular Multilevel Converter and the motivations behind the research works involving this topology. An overview of development trends regarding MMC topologies ends this chapter.

#### 2. Needs for HVDC

Since the 19th century, the HVAC (High Voltage Alternating current) has been the dominant solution for transmitting electrical power over long distances; transferring power from generating stations to electrical substations. However, due to technological and stability constraints, the maximum transfer capability is limited. This is especially the case when the series and shunt compensations cannot be incorporated in the transmission system (e.g. submarine cables) [1].

With technological innovations, notably in power electronics, HVDC technology has emerged as a promising solution for such application. Compared to the HVAC solution, the HVDC allows to overcome several constraints related to the old solution [2, 3, 4]:

- Reduce the investment cost when the distance becomes higher than a specific one, socalled "break-even distance": around 600 km for overhead lines and 50 km for submarine ones.

- No distance limitation regarding stability matter.

- Integration of renewable energy located far from consumption (e.g. wind farm energy).

- Great power transfer capability per conductor.

- Power factor is always unity: line does not require reactive compensation.

- Reduce line losses: skin effect is absent in DC technology.

- Asynchronous interconnection can be achieved which is not possible using HVAC.

- Low short circuit current.

- Less radio interference with nearby communication lines.

- Ground return can be used in some cases.

# 3. High voltage direct current

# 3.1. Concept

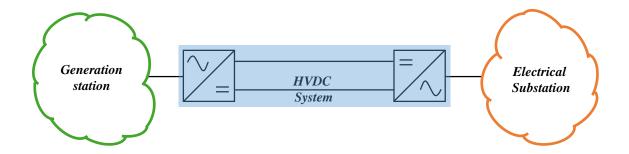

The HVDC system allows to transmit power in DC form. This is achieved through power converters which are able to convert electrical energy from AC to DC or vice versa.

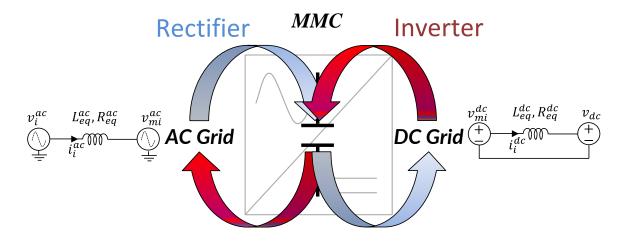

Figure I-1: HVDC system concept.

The vast majority of HVDC transmission system consists of three basic parts:

- 1) Converter station in rectifier mode to convert the power for AC to DC form.

- 2) Transmission line, it can be achieved using overhead lines or cables.

- 3) Converter station in inverter mode to convert the power for DC to AC form.

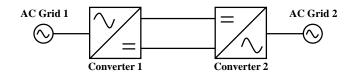

The power direction can be inversed using the associated control of converter stations. When the two converters are located in the same stations, the HVDC link is often called "Back-to-Back" configuration, see Figure I-2.

Figure I-2: Back-to-back scheme.

It is the simplest possible configuration and allows to connect two independent neighboring systems with different and incompatible electrical parameters (voltage, frequency, short-circuit power level). It can be also used to stabilize weak AC links in some cases.

#### 3.2. Configurations

Depending on the nature of projects and stations location, a number of different HVDC configurations can be employed [5, 6]. Independently from the converter technology (see section 4), a short description of these configurations is presented below with their associated advantages and drawbacks. In the following, a point-to-point scheme is used to illustrate their schematic diagram but all of which can be extended to a Multi-Terminal DC (MTDC) grid.

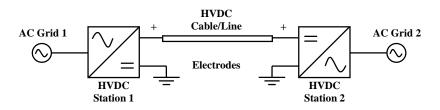

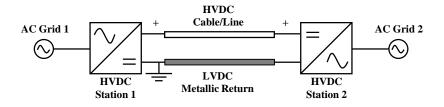

#### 3.2.1. Asymmetric monopolar scheme

The scheme of asymmetric monopolar is illustrated in Figure I-3, it includes two converter stations, single pole line (cable/line), and two grounded electrodes (one for each station). This configuration is the simplest and the advantageous one from a cost perspective. Another advantage is the possibility of expansion to a bipolar if necessary (to increase power rating). However, in many cases, the fact that the current return flows through the ground requires permission and can raise environmental concerns.

Figure I-3: Asymmetric monopolar scheme without metallic return.

Figure I-4: Asymmetric monopolar scheme with metallic return.

To overcome this issue, another scheme is proposed which includes in addition to the previous scheme a small metallic return (see Figure I-4). The latter, which does not require high-voltage

insulation, is used to return the current and consequently no ground current is obtained. Many of HVDC transmissions with submarine connections use such configuration system.

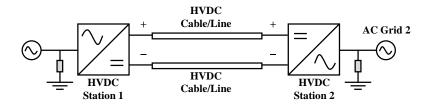

#### **3.2.2.** Symmetric monopolar scheme

A symmetric monopolar configuration is shown in Figure I-5. It can be considered as an alternative monopole scheme that avoid a continuous ground current. The earth reference can be provided by a high impedance reactor on the AC side and in some cases by capacitor's midpoint for the DC grid. Due to its symmetry, this is the only topology where the AC transformer is not subjected to DC voltage stresses, which simplifies its design. However, it has higher cost since it requires two fully insulated conductors. In addition, it extension to bipolar scheme requires lot of modifications.

Figure I-5: Symmetric monopolar scheme.

A major drawback concerns all monopolar HVDC configurations is the lack of power in case of DC faults. Since there is no redundancy stations, the transferred power can be missed for a given period which vary depending to the used DC protection strategy.

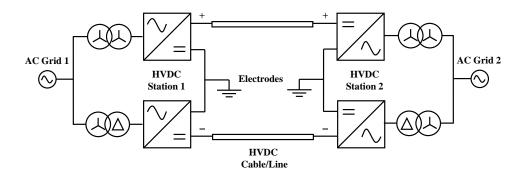

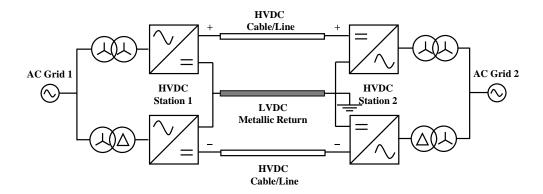

#### 3.2.3. Bipolar scheme

The bipolar configuration, shown in Figure I-6, can be seen as two monopolar configurations connected in parallel. Compared to the monopolar scheme, this configuration has higher cost since at least two stations at each terminal are needed and a transformer with two secondary windings or two different transformers groups (Yg- $\Delta$  and Yg-Y) are necessary to connect the two stations to AC grid [7].

Figure I-6: Bipolar scheme without metallic return.

The main advantage of the bipolar configuration is its redundancy, one pole can be overloaded (if the dimensioning allows it) to compensate the lack of power when the other one is out of service for whatever reason (e.g. maintenance periods). In balanced operation, small/no current flows in the ground event without metallic return scheme. When the latter is employed (see Figure I-7), the bipolar scheme ensures that no current is flowing through the ground whatever the operation conditions are.

Figure I-7: Bipolar scheme with metallic return.

# 4. Converter technologies for HVDC application

After presenting the different schemes of HVDC transmission, it is necessary to review the converter topologies that have been or can be used for such application. There are basically two configuration types of power converters which are: Line-Commuted Converter (LCC) known also as Current Source Converters (CSC) and Self-Commuted Converter (SCC) known also as Voltage Source Converters (VSC). The principles of both technologies with their advantages and drawbacks are presented below.

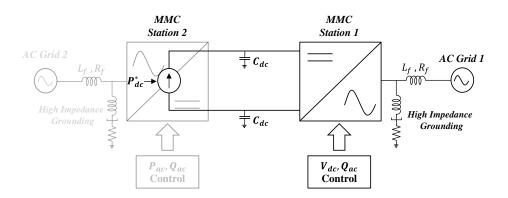

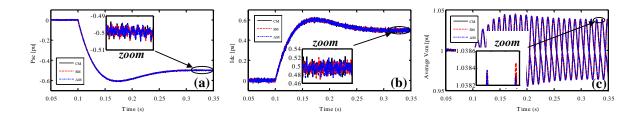

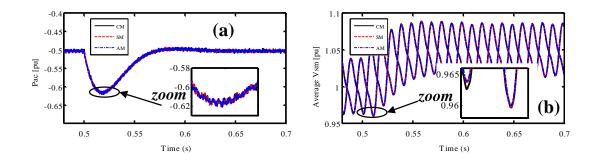

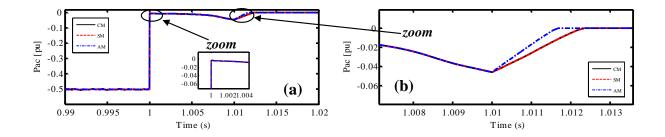

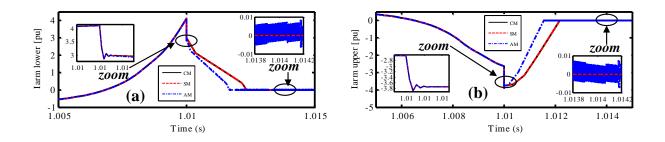

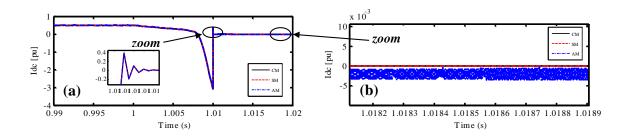

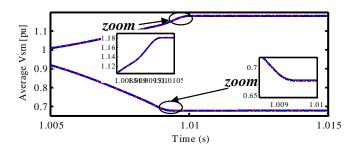

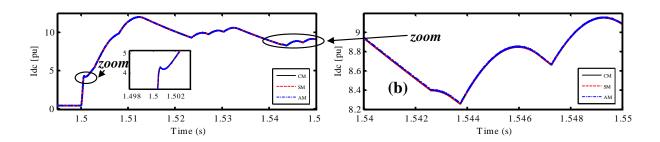

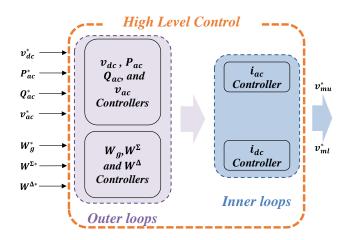

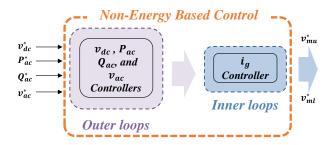

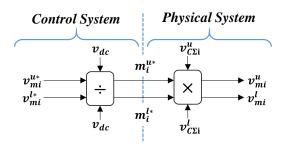

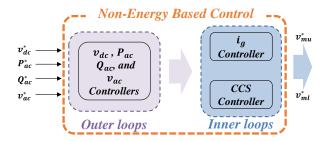

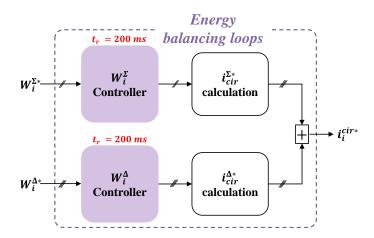

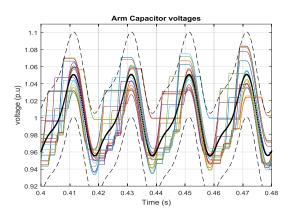

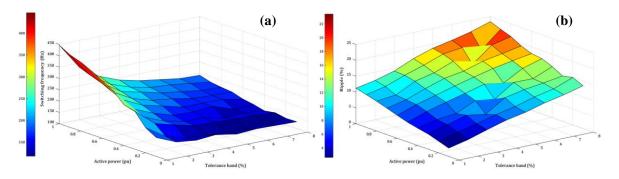

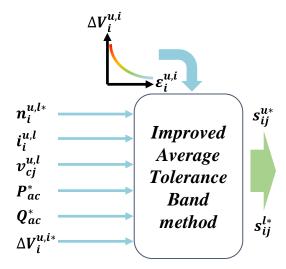

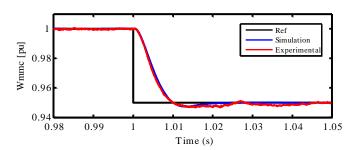

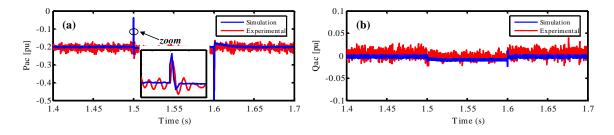

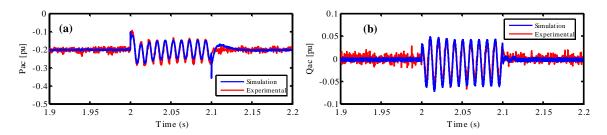

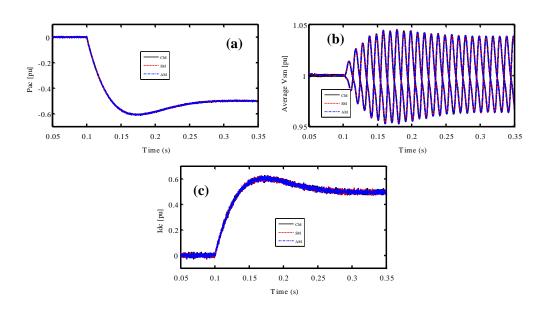

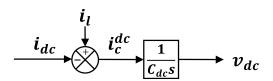

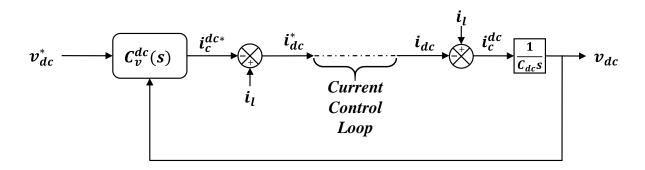

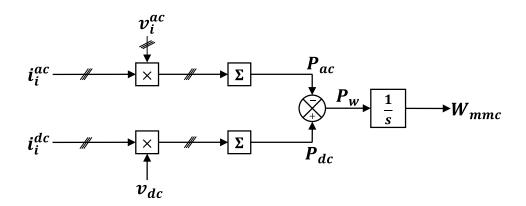

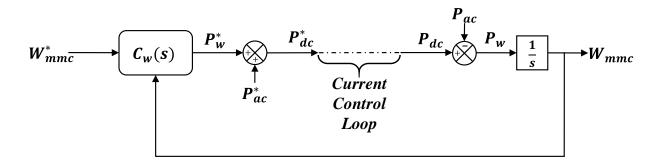

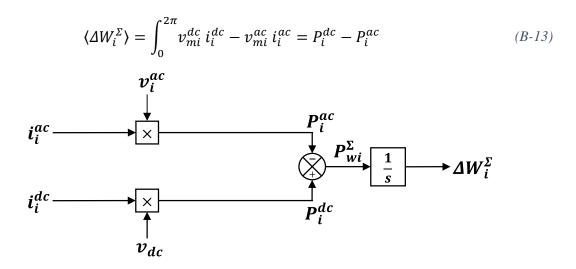

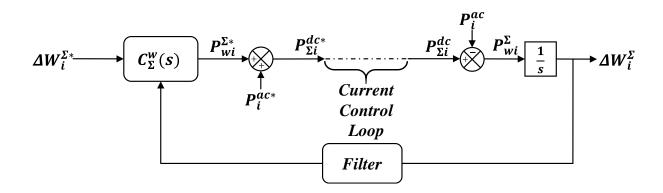

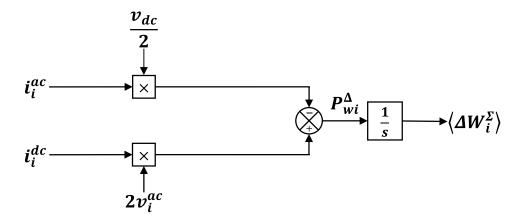

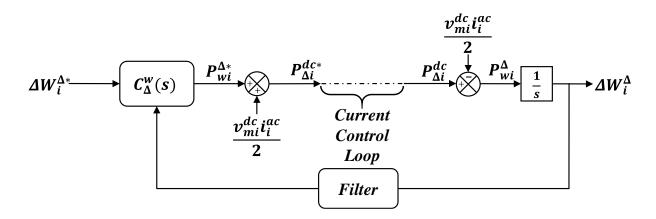

# **4.1. Line-Commuted Converters (Current Source Converters)**