# Exploration Architecturale au Niveau Comportemental - Application aux FPGAs

Sébastien Bilavarn

#### ▶ To cite this version:

Sébastien Bilavarn. Exploration Architecturale au Niveau Comportemental - Application aux FP-GAs. Architectures Matérielles [cs.AR]. Université de Bretagne Sud (Lorient Vannes), 2002. Français. NNT: . tel-01886615

# $\begin{array}{c} {\rm HAL~Id:~tel\text{-}01886615} \\ {\rm https://hal.science/tel\text{-}01886615v1} \end{array}$

Submitted on 3 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o d'ordre$ :

### **THÈSE**

présentée devant

L'Université De Bretagne Sud

pour obtenir le grade de

DOCTEUR DE L'Université De Bretagne Sud

Mention:

ÉLECTRONIQUE ET INFORMATIQUE INDUSTRIELLE

École Doctorale Pluridisciplinaire

Composante Universitaire:

UFR SCIENCES

ET

SCIENCES DE L'INGÉNIEUR

par

Sébastien BILAVARN

### Exploration Architecturale au Niveau Comportemental - Application aux FPGAs

soutenue le 28 Février 2002 devant la commission d'examen composée de :

| M.: J. L. Philippe LESTER Directeur d | le thèse |

|---------------------------------------|----------|

| M.: M. Auguin I3S Rapporteur          | rs       |

| M.: D. Lavenier IRISA                 |          |

| M.: M. Corazza ENSSAT Examinated      | urs      |

| M.: T. Collette CEA                   |          |

M.: G. Gogniat LESTER

M. : J. P. Diguet LESTER Invité

Laboratoire d'Électronique des Systèmes TEmps Réel

### Remerciements

Ce travail a été effectué au sein du groupe Adéquation Application Système (AAS) du Laboratoire d'Électronique des Systèmes TEmps Réel (LES-TER), à Lorient. Je souhaiterais donc tout d'abord remercier M. E. Martin de m'avoir accueilli dans son laboratoire et M. J. L. Philippe, mon directeur de thèse, pour l'opportunité de thèse qui m'a été proposée il y a trois ans. Je le remercie aussi pour son soutien et ses conseils au cours de ces trois années de recherche.

Je tiens ensuite à remercier tous les membres du groupe AAS, les enseignants chercheurs, les thésards ainsi que les stagiaires avec qui j'ai été amené à travailler, parmi lesquels J. P. Diguet, Y. le Moullec, F. Bertrand, D. Heller, L. Bossuet, . . . .

Je souhaiterais remercier tout particulièrement Guy Gogniat, avec qui j'ai beaucoup apprécié travailler, pour son encadrement, ses conseils et encouragements.

Je remercie Messieurs M. Auguin, et D. Lavenier, pour avoir accepté d'être rapporteurs de ce travail ainsi que le président et les membres du jury.

Enfin, je remercie tous les membres du LESTER et leur souhaite à chacun beaucoup de réussite dans leurs projets.

Ce travail est dédié à la mémoire de ma mère.

# Table des matières

| 1 | Inti | oduct  | ion                                                 | 1  |

|---|------|--------|-----------------------------------------------------|----|

| 2 | Mé   | thodol | ogies de conception                                 | 7  |

|   | 2.1  | La con | nception conjointe logiciel / matériel              | 8  |

|   |      | 2.1.1  | Problématique du codesign                           | 8  |

|   |      | 2.1.2  | Limites des approches classiques                    | 9  |

|   | 2.2  | Codes  | sign: l'approche du LESTER                          | 10 |

|   |      | 2.2.1  | Principe de l'approche                              | 10 |

|   |      | 2.2.2  | Spécification : le modèle SPF - HCDFG               | 12 |

|   |      | 2.2.3  | L'Estimation Système                                | 15 |

|   |      | 2.2.4  | L'Estimation Architecturale                         | 18 |

|   | 2.3  | État c | de l'art dans le domaine des estimations            | 20 |

|   |      | 2.3.1  | État de l'art des estimations au niveau système     | 20 |

|   |      | 2.3.2  | État de l'art des estimations au niveau RTL         | 21 |

|   |      | 2.3.3  | État de l'art des estimations spécifiques aux FPGAs | 26 |

|   | 2.4  | Comp   | osants cibles : les FPGAs                           | 29 |

|   |      | 2.4.1  | La famille Virtex (Xilinx)                          | 30 |

|   |      | 2.4.2  | La famille Apex (Altera)                            |    |

|   |      | 2.4.3  | Bilan des architectures                             |    |

|   | 2.5  | Concl  | usion                                               | 35 |

| 3 | L'E  | xplora | tion Architecturale                                 | 37 |

|   | 3.1  | Appro  | oche de la méthode                                  | 38 |

|   |      | 3.1.1  | Introduction                                        | 38 |

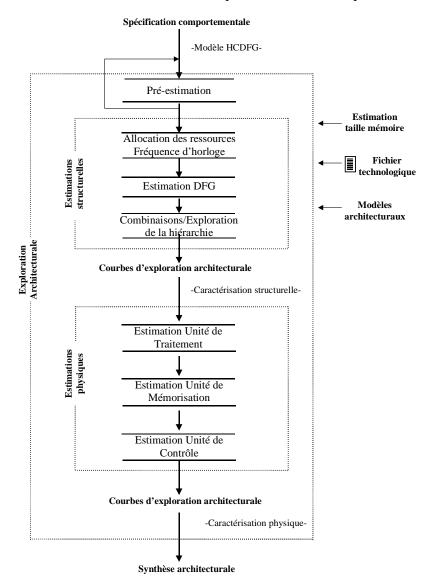

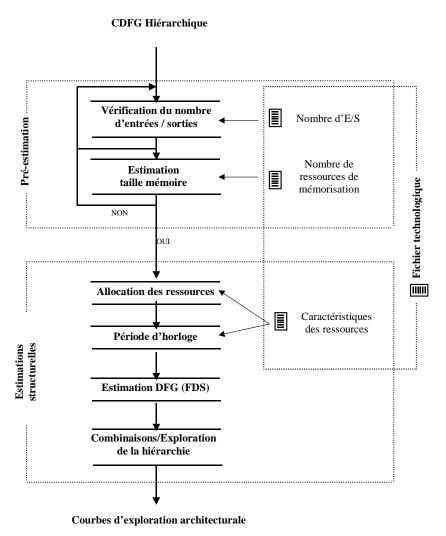

|   |      | 3.1.2  | Le flot d'estimation                                | 39 |

|   | 3.2  | La spe | écification d'entrée : mode d'utilisation           | 42 |

|   | 3.3 | Les co  | ourbes d'exploration architecturale                | $_{1}$     |

|---|-----|---------|----------------------------------------------------|------------|

|   |     | 3.3.1   | Introduction                                       | $_{1}$     |

|   |     | 3.3.2   | Caractérisation structurelle                       | 16         |

|   |     | 3.3.3   | Caractérisation physique                           | 18         |

|   | 3.4 | Les m   | odèles architecturaux pour l'estimation            | 49         |

|   |     | 3.4.1   | Unité de traitement                                | 19         |

|   |     | 3.4.2   | Unité de mémorisation                              | <u>.</u>   |

|   |     | 3.4.3   | Unité de contrôle                                  | 5.         |

|   | 3.5 | Concl   | usion                                              | ر<br>آ     |

| 4 | Les | Estim   | ations au Niveau Structurel                        | 5          |

|   | 4.1 | Introd  | $egin{array}{cccccccccccccccccccccccccccccccccccc$ | 5(         |

|   | 4.2 | Pré-es  | timation                                           | <b>5</b> ′ |

|   |     | 4.2.1   | Choix d'un composant d'implantation                | 5′         |

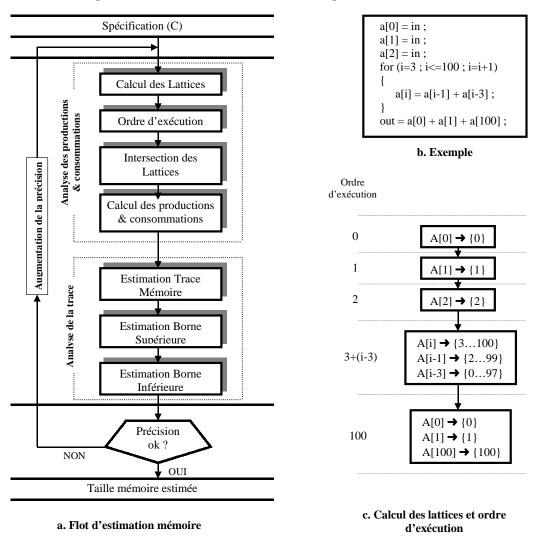

|   |     | 4.2.2   | Estimation de la taille mémoire                    | 58         |

|   | 4.3 | Explo   | ${f ration}$ à l'étape de sélection / allocation   | 3:         |

|   |     | 4.3.1   | Allocation des ressources                          | 3;         |

|   |     | 4.3.2   | Détermination de la fréquence d'horloge            | 3;         |

|   | 4.4 | Estim   | ation des DFGs                                     | ; 6        |

|   | 4.5 | Les di  | fférents types de combinaison                      | 36         |

|   |     | 4.5.1   | Structures conditionnelles                         | 7          |

|   |     | 4.5.2   | Structures itératives                              | 7:         |

|   |     | 4.5.3   | Exécution séquentielle de deux graphes             | 79         |

|   |     | 4.5.4   | Exécution concurrente de deux graphes              | 3          |

|   | 4.6 | Carac   | térisation structurelle globale                    | 3:         |

|   |     | 4.6.1   | Exploration de la hiérarchie                       | 3:         |

|   |     | 4.6.2   | Cas des dépendances d'exécution                    | 3          |

|   |     | 4.6.3   | Analyse de la réutilisation                        | 3(         |

|   | 4.7 | Concl   | usion                                              | 38         |

| 5 | Les | Estim   | ations au Niveau Physique                          | 39         |

|   | 5.1 | Le fich | nier technologique                                 | )(         |

|   |     | 5.1.1   | La bibliothèque de ressources                      | )(         |

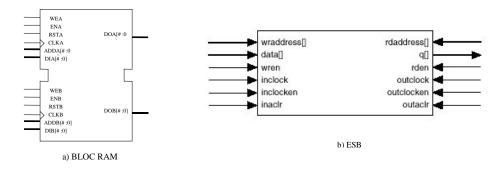

|   |     | 5.1.2   | Caractérisation des mémoires                       | ),         |

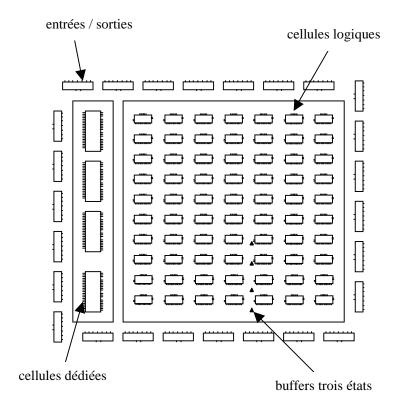

|   |     | 5 1 3   | Caractérisation de l'architecture du composant     | 3.5        |

|   | 5.2 | La projection technologique |                                                     |  |

|---|-----|-----------------------------|-----------------------------------------------------|--|

|   |     | 5.2.1                       | Unité de mémorisation                               |  |

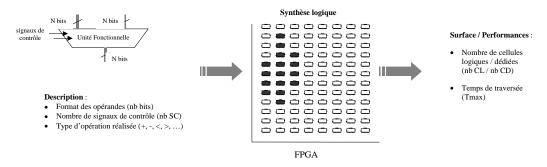

|   |     | 5.2.2                       | Unité de traitement                                 |  |

|   |     | 5.2.3                       | Unité de contrôle                                   |  |

|   |     | 5.2.4                       | Caractérisation physique globale                    |  |

|   | 5.3 | Concl                       | usion                                               |  |

| 6 | App | plicatio                    | ons 109                                             |  |

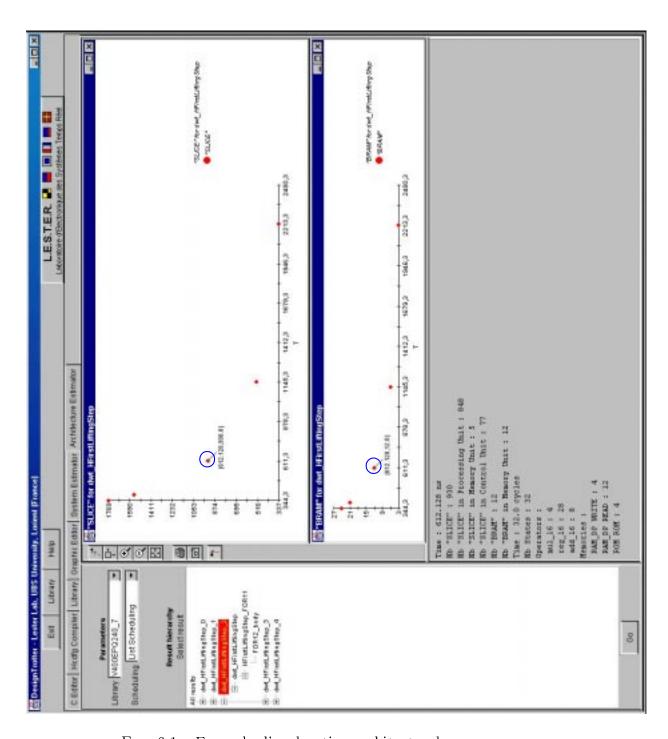

|   | 6.1 | Préser                      | ntation de l'outil d'exploration architecturale 110 |  |

|   | 6.2 | Résult                      | ats d'estimation vs synthèse : Introduction         |  |

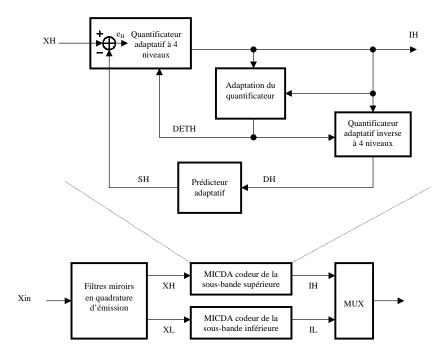

|   | 6.3 | $\operatorname{codag}$      | e de la parole : G722                               |  |

|   |     | 6.3.1                       | Présentation de la norme G722                       |  |

|   |     | 6.3.2                       | Synthèse du prédicteur                              |  |

|   |     | 6.3.3                       | Conclusion                                          |  |

|   | 6.4 |                             |                                                     |  |

|   |     | 6.4.1                       | Présentation de la transformée en ondelettes 120    |  |

|   |     | 6.4.2                       | Synthèse de la transformée en ondelettes            |  |

|   |     | 6.4.3                       | Conclusion                                          |  |

|   | 6.5 | Concl                       | usions générales sur les résultats                  |  |

| 7 | Cor | nclusio                     | ns et perspectives 131                              |  |

# Table des figures

| 1.1  | Flot de Codesign                                               | 3   |

|------|----------------------------------------------------------------|-----|

| 2.1  | Les différentes solutions d'intégration d'un système           | 9   |

| 2.2  | Flot de conception : "Design Trotter"                          | . 1 |

| 2.3  | Le modèle SPF                                                  | .3  |

| 2.4  | Exemple de profil de coût global                               | .6  |

| 2.5  | Allocation de composants                                       | 8.  |

| 2.6  | Modélisation mémoire sous forme de polyèdre                    | 25  |

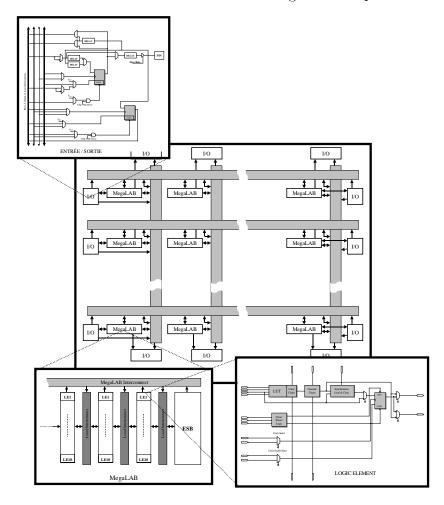

| 2.7  | Architecture Virtex                                            | 31  |

| 2.8  | Architecture Apex                                              | 3   |

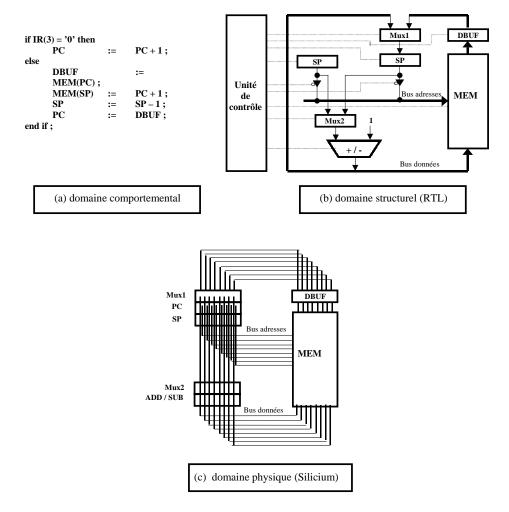

| 3.1  | Trois domaines de description : (a) comportemental, (b) struc- |     |

|      | turel, (c) physique $\ldots 3$                                 | 8   |

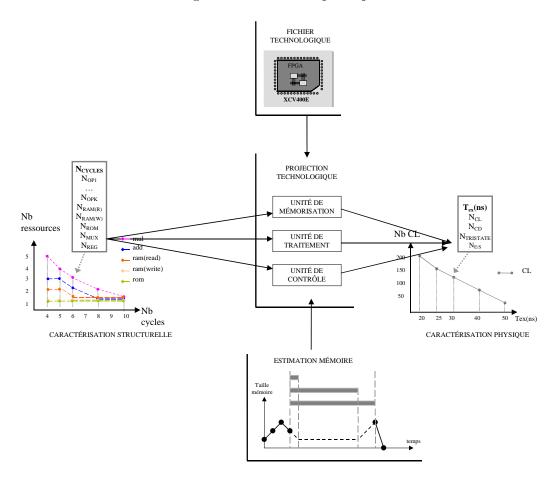

| 3.2  | Flot d'Exploration Architecturale 4                            | 0   |

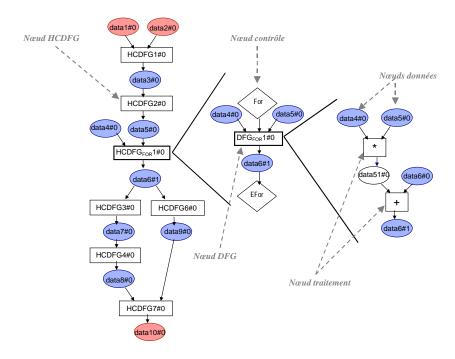

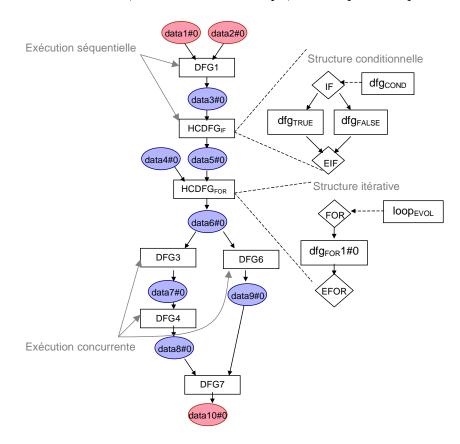

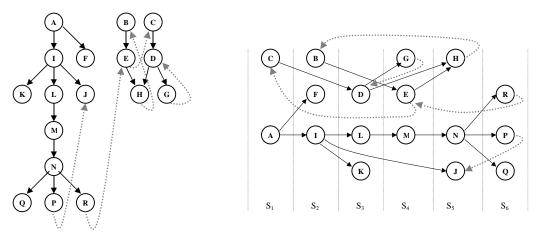

| 3.3  | Modèle de graphe HCDFG                                         | 13  |

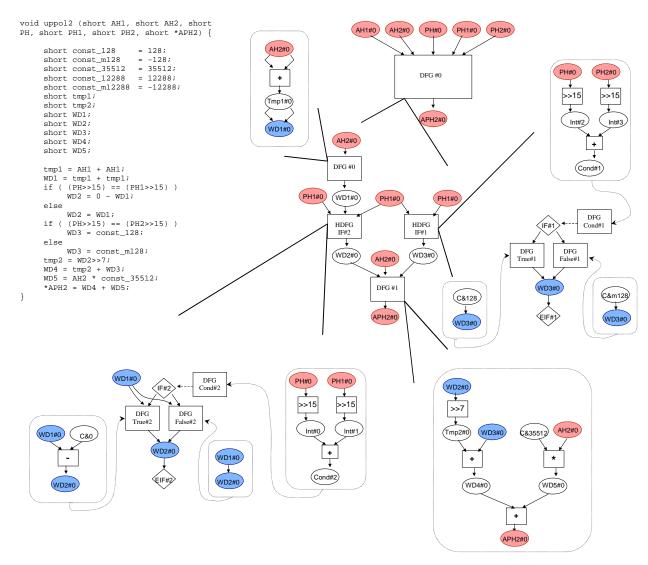

| 3.4  | Exemple de traduction du C vers HCDFG 4                        | 4   |

| 3.5  | Surface de la DCT en fonction du temps de calcul 4             | 15  |

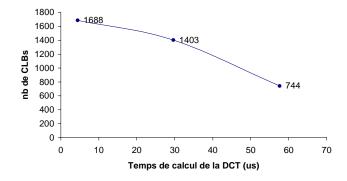

| 3.6  | Courbes d'exploration architecturale                           | 6   |

| 3.7  | Exemple de caractérisation structurelle (dwt) 4                | 17  |

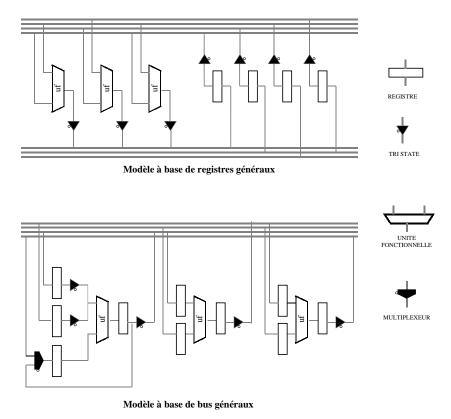

| 3.8  | Modèles architecturaux pour l'UT                               | 60  |

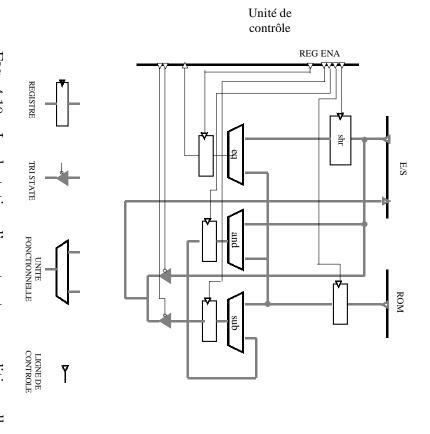

| 3.9  | Modèle d'Architecture pour l'Unité de Traitement 5             | 51  |

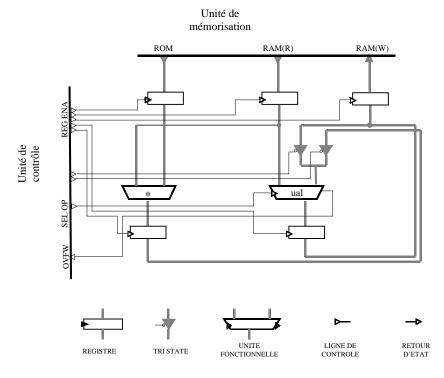

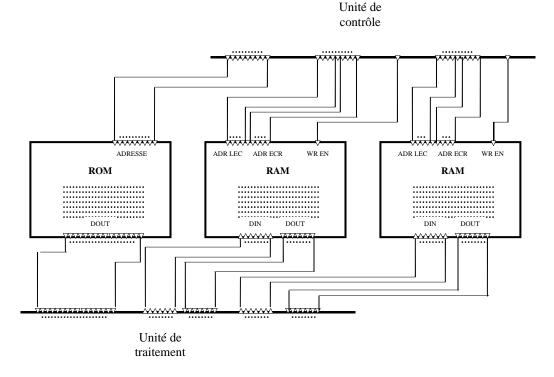

| 3.10 | Modèle d'Architecture pour l'Unité de Mémorisation 5           | 52  |

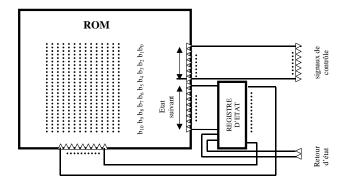

| 3.11 | Modèle d'Architecture pour l'Unité de Contrôle                 | 53  |

| 4.1  | Flot d'estimations structurelles                               | 66  |

| 4.2  | Estimation mémoire : principe et exemple                       | 69  |

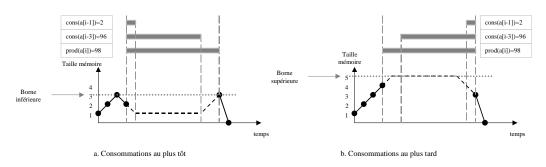

| 4.3  | Estimation des bornes supérieure et inférieure 6               | 1   |

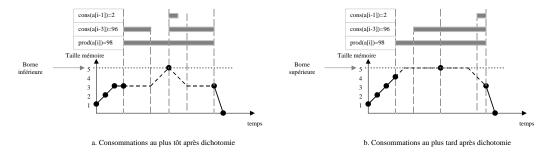

| 4.4  | Amélioration de la précision : méthode dichotomique 6          | :2  |

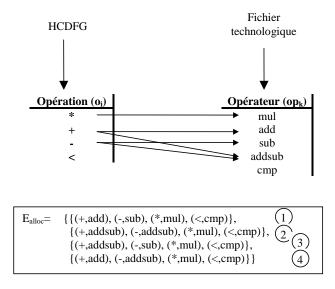

| 4.5  | Les ensembles d'allocation opération - opérateur possibles 6       | 33 |

|------|--------------------------------------------------------------------|----|

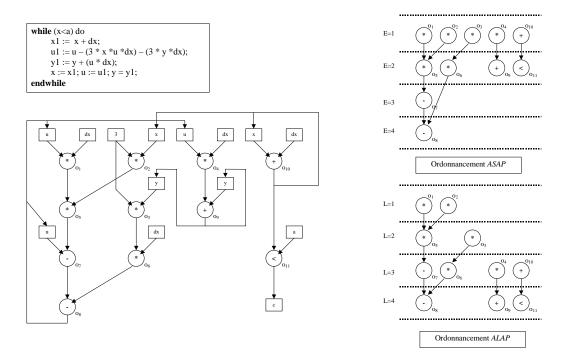

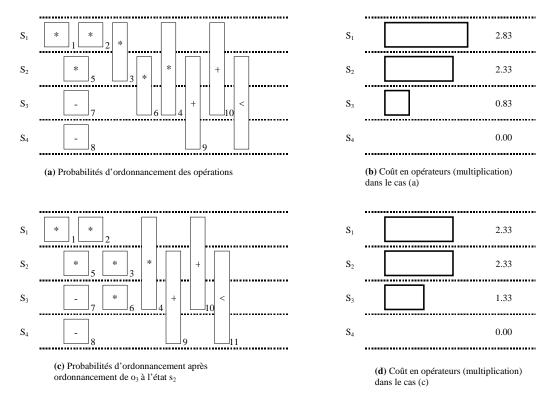

| 4.6  | Ordonnancements $ASAP$ et $ALAP$                                   | 35 |

| 4.7  | Exemple d'application de la technique FDS                          | 3E |

| 4.8  | Les quatre types de combinaison hiérarchique                       | 70 |

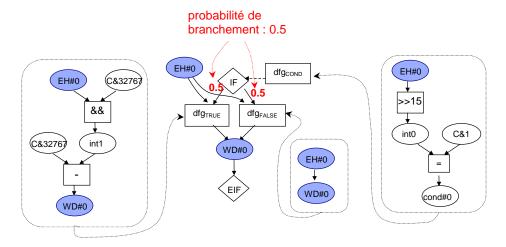

| 4.9  | Graphe de spécification d'une structure conditionnelle             | 71 |

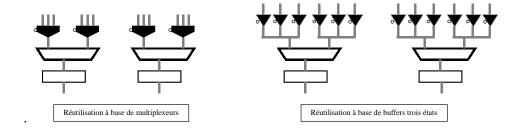

| 4.10 | Implantation d'une structure conditionnelle                        | 73 |

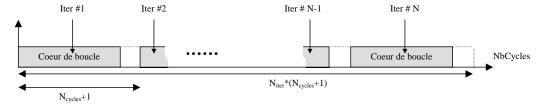

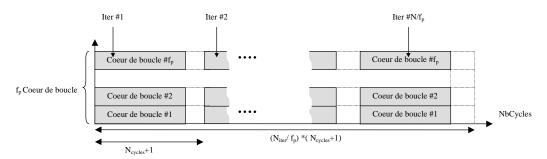

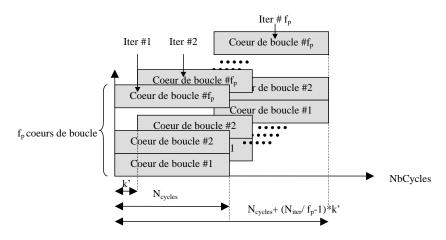

| 4.11 | Ordonnancement des boucles : séquentiel                            | 74 |

| 4.12 | Ordonnancement des boucles : déroulage                             | 75 |

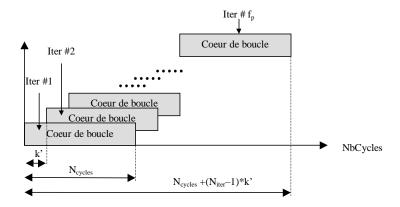

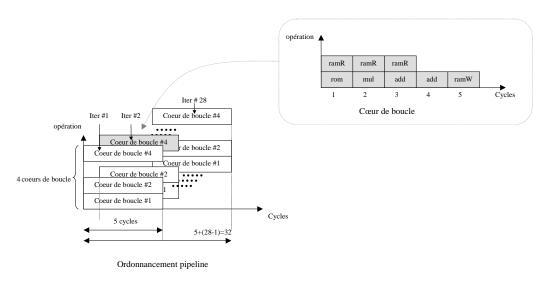

| 4.13 | Ordonnancement des boucles : recouvrement (pipeline)               | 76 |

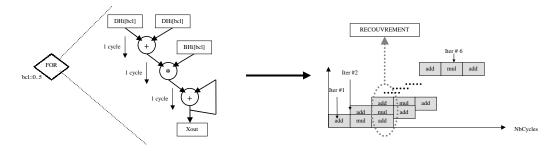

| 4.14 | Exemple de recouvrement                                            | 77 |

| 4.15 | Ordonnancement des boucles : déroulage et recouvrement             | 78 |

| 4.16 | Exemple de dépendances inter-itérations                            | 79 |

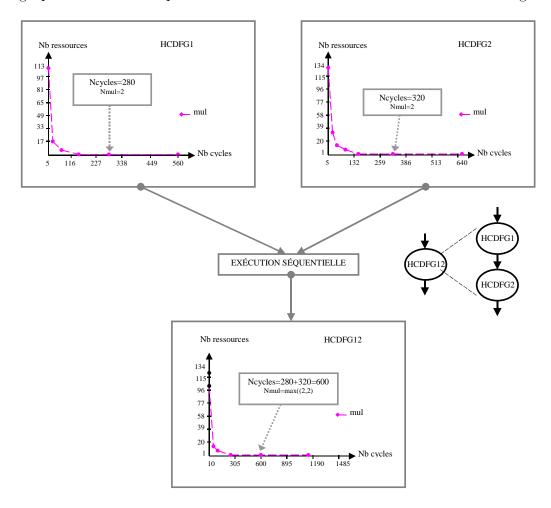

| 4.17 | Estimation de l'exécution séquentielle de deux graphes 8           | 30 |

| 4.18 | Estimation de l'exécution concurrente de deux graphes 8            | 32 |

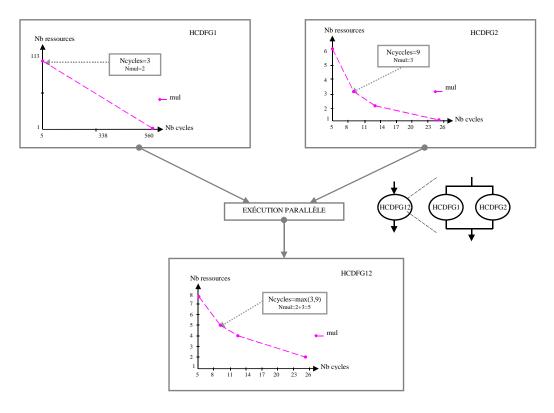

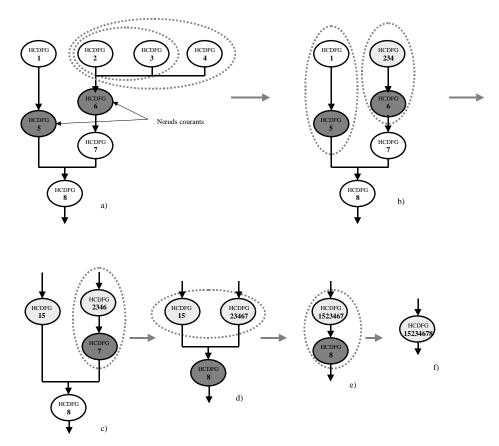

| 4.19 | Combinaison des résultats                                          | 35 |

| 4.20 | Réutilisation des unités fonctionnelles                            | 87 |

| 5.1  | Principe de caractérisation des opérateurs                         | 91 |

| 5.2  | Mémoires dédiées : Virtex vs. Apex                                 | 95 |

| 5.3  | Caractérisation de l'architecture du composant                     | 96 |

| 5.4  | Principe de la projection technologique                            | )( |

| 6.1  | Exemple d'exploration architecturale                               | 11 |

| 6.2  | Ordonnancement pour l'exemple de la figure 6.1                     | 12 |

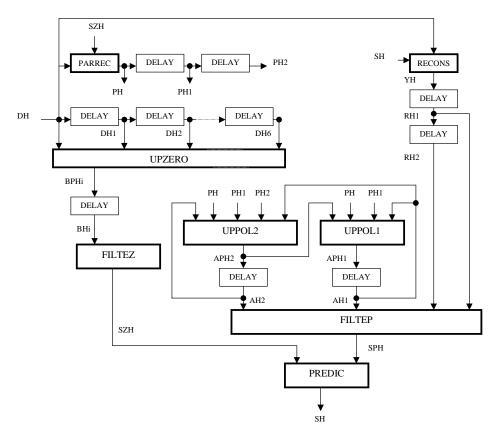

| 6.3  | Schéma de principe du codeur SB-MICDA                              | 14 |

| 6.4  | Prédicteur adaptatif de la sous-bande supérieure                   | 15 |

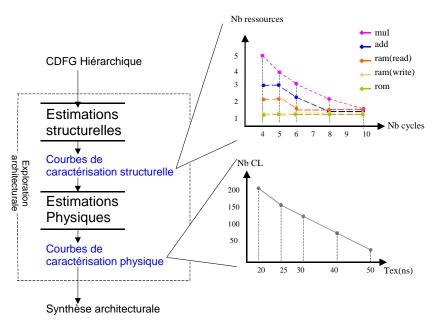

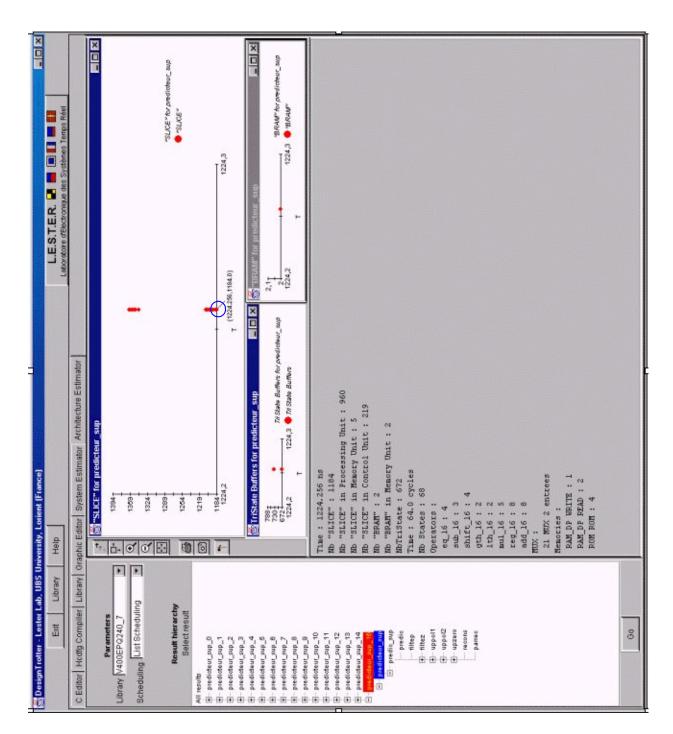

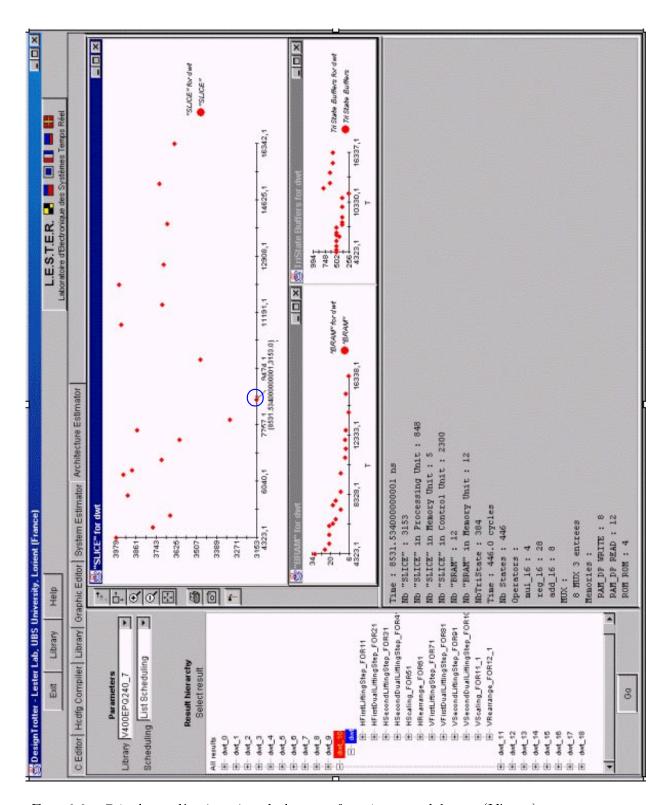

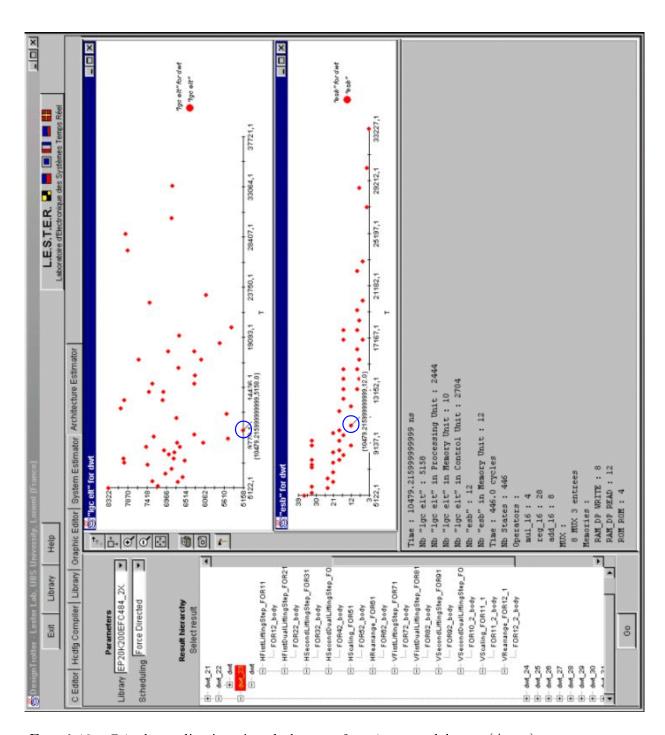

| 6.5  | Résultats d'estimation du prédicteur (Virtex)                      | 17 |

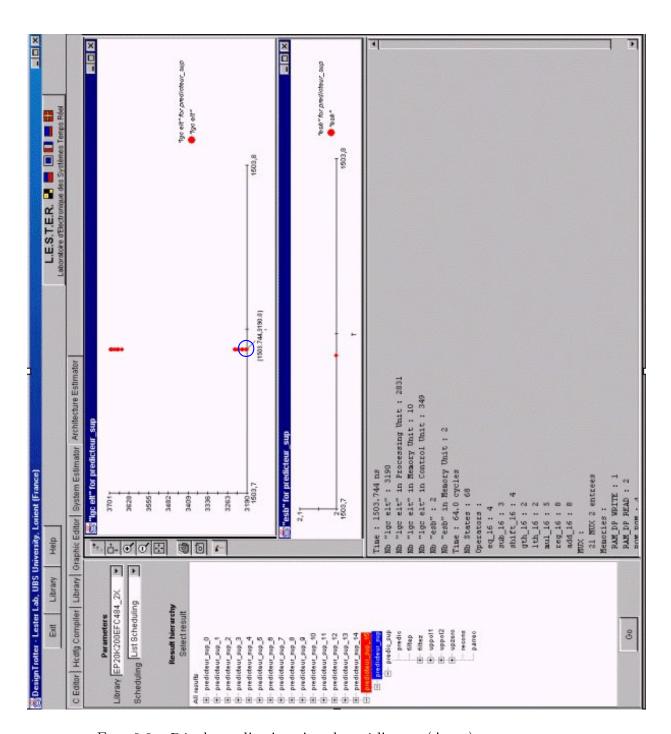

| 6.6  | Résultats d'estimation du prédicteur (Apex)                        | 18 |

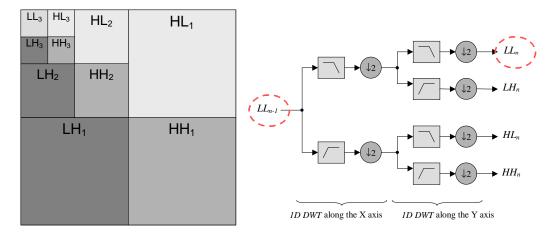

| 6.7  | Décomposition d'une image par la transformée en ondelettes         |    |

|      | sur 3 niveaux                                                      | 21 |

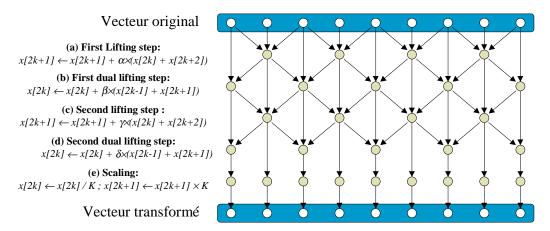

| 6.8  | Décomposition de l'image par l'utilisation du Lifting Scheme . 12  | 22 |

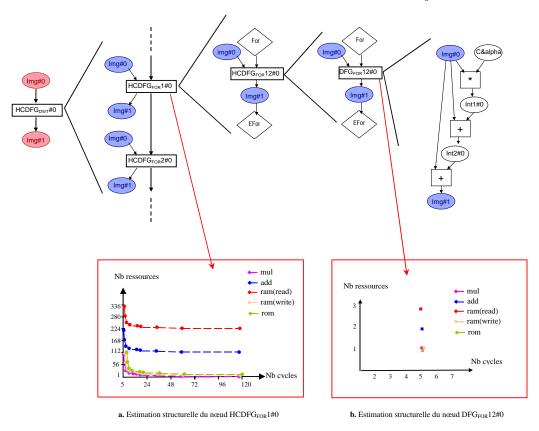

| 6.9  | Résultats d'estimation de la transformée en ondelettes (Virtex) 12 | 24 |

| 6.10 | Résultats d'estimation de la transformée en ondelettes (Apex) 12   | 25 |

# Liste des tableaux

| 2.1 | Différentes techniques pour l'estimation au niveau comporte- |            |

|-----|--------------------------------------------------------------|------------|

|     | mental                                                       | 24         |

| 2.2 | Caractéristiques Apex et Virtex                              | 35         |

| 4.1 | Calcul des productions et des consommations                  | 60         |

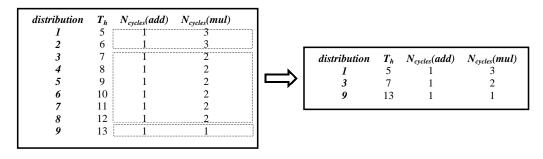

| 4.2 | Détermination d'un ensemble de périodes d'horloge 6          | <b>j</b> 4 |

| 4.3 | Exemple d'estimation d'une structure conditionnelle          | 72         |

| 5.1 | Caractérisation des opérateurs de base                       | )2         |

| 5.2 | Exemple de caractérisation des ressources                    | )3         |

| 5.3 | Caractérisation des mutiplexeurs (opérandes 8 bits) 9        | )4         |

| 5.4 | Performances des mémoires dédiées                            | )6         |

| 5.5 | Performances des mémoires distribuées                        | 7          |

| 5.6 | Exemple de caractérisation des mémoires                      | 8(         |

| 5.7 | Exemple de caractérisation d'une architecture                | 99         |

| 6.1 | Prédicteur : Estimation vs Synthèse                          | 9          |

| 6.2 | Prédicteur : Écarts                                          | 9          |

| 6.3 | Transformée en ondelettes : Estimation vs Synthèse 12        | 26         |

| 6.4 | Transformée en ondelettes : Écarts                           | 27         |

# Chapitre 1

# Introduction

#### MOTIVATION

La conception des systèmes électroniques n'a cessé d'évoluer vers l'intégration d'applications plus complexes pour des temps de conception plus courts. Cette progression a été rendue possible grâce aux spectaculaires avancées effectuées dans le domaine technologique, mais est ralentie par le fort décalage avec les environnements et outils de conception permettant de les exploiter. Afin de réduire ce gap technologie/outil, les méthodologies de conception se sont naturellement orientées vers des niveaux d'abstraction supérieurs, où fonctionalités et compromis sont plus faciles à discerner. Aujourd'hui, l'évolution des applications vers des systèmes à la fois plus performants et plus complexes conduit à l'élaboration de dispositifs hétérogènes, c'est à dire constitués d'unités de nature différente (i.e. logicielle, matérielle). Parmi les unités logicielles, on peut distinguer deux grandes classes de circuits numériques : les processeurs d'usage général (GPP) et les processeurs à usage spécifique (ASIP, DSP). Les processeurs d'usage général peuvent être programmés pour exécuter n'importe quelle classe d'application, alors que les processeurs à usage spécifique sont dédiés à une classe d'application (e.g. traitement d'image, traitement du signal, cryptographie) où directement à une application précise (e.g. console de jeux). Un certain nombre d'applications numériques peuvent être réalisées de façon uniquement logicielle, solution intéressante par la flexibilité qu'elle apporte due à la possibilité de reprogrammation. La motivation principale de l'utilisation de processeurs dédiés réside elle dans le respect des contraintes de performances ou dans la confidentialité de la solution implémentée. Toutefois, bien que ces solutions

2

uniquement logicielles soient préférables, un grand nombre d'applications, notamment dans le domaine des télécommunications et du multimédia, impliquent une architecture hétérogène logicielle / matérielle. Dans ce cas, de nouvelles méthodologies de conception qualifiées de conception conjointe logiciel/matériel (codesign) sont nécessaires. L'approche codesign consiste alors à définir l'ensemble des sous tâches d'une application à intégrer et à effectuer leur répartition sur des cibles logicielles ou matérielles. L'intérêt majeur de cette méthodologie réside dans la recherche d'une adéquation application / architecture satisfaisant les nombreuses contraintes de conception telles que le coût, les performances, la surface, la consommation, les temps de conception et de développement (Time To Market), l'évolutivité, ... La conception efficace de ces systèmes hétérogènes nécessite une approche globale dans laquelle les parties matérielles et logicielles sont conçues en parallèle et de façon interactive.

Un autre facteur important dans l'évolution des systèmes modernes est l'apparition de nouvelles architectures exploitant la synergie entre le matériel et le logiciel, basées sur la programmation de circuits matériels tels que les composants FPGAs (Field Programmable Gate Array). Ces composants sont actuellement principalement utilisés pour l'accélération de calculs spécifiques ou pour faire du prototypage d'ASIC (Application Specific Integrated Circuit). Leur introduction comme unité de calcul alternative et la flexibilité dont ils font preuve introduit une nouvelle dimension au problème de la conception, en élargissant un peu plus l'ensemble des choix d'intégration possibles. De plus, les récentes évolutions des différentes familles autorisent aujourd'hui l'intégration de systèmes de plus en plus complexes avec des contraintes de performances de plus en plus fortes. En effet, de nombreux fondeurs proposent aujourd'hui des puces électroniques intégrant sur un même substrat un ou plusieurs coeurs de processeurs et une matrice programmable (ex : Excalibur d'Altera). Par ailleurs, tout un champ technologique émerge actuellement dans le domaine de la reconfiguration dynamique (run time reconfiguration). Ces nouveaux circuits permettront de modifier, en cours d'exécution, partiellement ou complètement la configuration (donc la fonctionnalité) du circuit. Aussi, l'utilisation des composants programmables ne se limite plus à une étape dans un cycle de conception (prototypage) mais constitue véritablement une finalité d'implantation. Il est donc nécessaire

d'étendre ou de repenser les approches de conception actuelles afin de les adapter aux possibilités offertes par les technologies matérielles programmable.

#### **OBJECTIFS**

L'évaluation des performances d'une application sur une technologie de ce type est un problème peu étudié à ce jour, l'essentiel des travaux porte sur l'optimisation des architectures (dimensionnement des ressources de routage par exemple). En effet, jusqu'à présent les chercheurs ont principalement porté leurs efforts sur l'amélioration des architectures programmables et des outils de synthèse / placement / routage associés afin de les rendre plus performantes et ainsi constituer une réelle alternative aux ASICs. Aujourd'hui, l'intérêt des technologies programmables n'est plus à démontrer et plusieurs projets de recherche visant à imaginer des méthodes de conception conjointe spécifiques à ce domaine sont actuellement en cours. L'objectif du travail

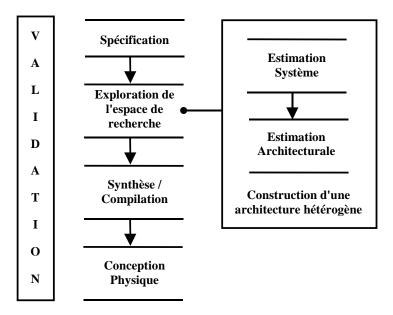

Fig. 1.1 – Flot de Codesign

présenté dans ce mémoire consiste à proposer des techniques et les outils associés permettant l'évaluation rapide de plusieurs compromis performances / occupation pour des applications candidates à une implantatation sur des architectures programmables. L'estimation de la surface et du temps d'exécution à partir d'une description comportementale telle qu'elle est abordée

ici s'intègre dans un flot de conception de systèmes hétérogènes mixtes (codesign), et se situe plus particulièrement à l'étape d'exploration de l'espace de recherche (figure 1.1). Le but de cette exploration est d'évaluer un grand nombre de solutions d'intégration afin de sélectionner la ou les meilleures. L'approche développée au laboratoire LESTER consiste à étudier le partitionnement (répartition des fonctions de l'application sur les ressources logicielles et matérielles) en partie dès la phase de spécification (estimation système), c'est à dire sans aucune notion d'architecture. Les estimations au niveau comportemental (aussi appelées estimation architecturale) qui font l'objet de ce mémoire, permettent ensuite de valider le choix des solutions d'implantation (actuellement en terme de surface et de temps d'exécution) pour les fonctions issues de l'analyse système en effectuant une estimation rapide de la faisabilité et des performances sur un composant candidat. La conjonction des estimations système et architecturale permet ainsi la définition d'une architecture mieux adaptée aux besoins de l'application.

#### CONTRIBUTION

Le travail exposé ici porte sur l'estimation en temps et en surface de fonctions candidates à une implantation matérielle, plus précisément sur des composants programmables. L'estimateur peut donc être vu comme un outil permettant de vérifier la faisabilité de l'intégration d'un système sur un FPGA, à partir d'une spécification comportementale issue d'un code de haut niveau. Ce travail est original en plusieurs points: Tout d'abord, peu d'études sont menées dans le domaine, en partie pour les raisons précédemment citées, à savoir l'intérêt nouveau des chercheurs pour la définition de méthodes de conception conjointe appliquées aux technologies matérielles programmables. A notre connaissance, seules trois études visant à définir des méthodes d'estimation qui tiennent compte de l'application à intégrer ont été publiées (ce point sera reprit en détail dans l'état de l'art). De plus, ces études ne prennent pas en compte les structures de contrôle intervenant dans les applications complexes, ce qui limite leur utilisation à l'estimation de chemins de données. Dans l'approche présentée ici, la spécification supporte différentes structures de contrôle telles que les boucles et les structures conditionnelles. Ainsi, l'estimation d'applications complexes (incluant par exemple de la hiérarchie, des données multidimentionnelles) peut être effectuée.

La méthode développée intègre l'estimation des unités de traitement, de

mémorisation et de contrôle, ce qui constitue un point original dans la mesure où il existe très peu d'approches s'intéressant à ces trois aspects simultannément. Ce point est nécessaire pour obtenir une estimation globale d'une application sur une architecture matérielle programmable. La validation de la méthode s'est donc portée sur des systèmes représentatifs de deux classes d'applications (orientées vers du traitement, du contrôle ou de la mémorisation de données) : codage audiofréquence et traitement d'image. Enfin, bien que l'étude présentée dans ce mémoire vise essentiellement les composants programmables, elle constitue un point de départ intéressant dans le cadre de l'élaboration d'une technique d'estimation matérielle qui puisse aussi s'appliquer aux ASICs. Un point également fondamental est la définition d'une méthode d'estimation qui soit au maximum indépendante d'une technologie donnée, afin de rendre son utilisation la plus large possible. Aussi, dans le cadre de cette thèse, nous nous sommes efforcé de rendre l'approche la plus générique possible.

Le rapport précision / complexité est une caractéristique importante pour un estimateur puiqu'elle conditionne l'exploration d'un vaste espace de recherche (exploration du parallélisme, pour plusieurs fréquences d'horloge, plusieurs allocations) et l'évaluation de plusieurs composants cibles en un temps raisonnable. D'autre part, étant données les récentes avancées dans le domaine de la synthèse de haut niveau et le degré de maturité atteint par les outils de synthèse architecturale, la méthode d'exploration développée ne se justifie que si elle apporte une amélioration significative du cycle de conception. Aussi, lors de la définition des techniques d'estimation, la complexité des algorithmes a été un critère important. Nous verrons dans la dernière partie de ce mémoire au travers des exemples choisis pour la validation que l'exploration et la synthèse architecturale ne s'opposent pas. Au contraire, leur complémentarité laisse entrevoir les perspectives d'une méthodologie de conception prometteuse.

#### Plan du mémoire

Le plan de cette étude est le suivant : Dans le chapitre 2, après une présentation du codesign et de sa problématique, une introduction de l'approche effectuée au laboratoire est réalisé afin de présenter le contexte dans lequel s'inscrit la méthode d'estimation. Un bilan des nombreuses techniques d'estimations classées par niveau d'abstraction est ensuite présenté afin de bien

6

dégager l'utilisation potentielle des différents algorithmes. Puis, les composants ayant servi à valider les travaux, à savoir la famille Virtex de Xilinx et Apex d'Altera sont abordés. Cette présentation permet au lecteur non familier avec ces technologies d'avoir une vision synthétique des deux familles les plus largement utilisées. Le chapitre 3 introduit les hypothèses à prendre en compte pour garantir la pertinence des résultats et propose la définition d'un flot d'estimation. Celui-ci est composé de deux parties, les estimations au niveau structurel (RTL ou architectural) où sont définies un certain nombre de solutions architecturales, et les estimations au niveau physique (layout) qui permettent d'évaluer la surface et les performances de ces solutions. Ces étapes sont détaillées dans les deux chapitres suivants. Le chapitre 6 présente les résultats de cette méthode sur deux applications représentatives dans le domaine de la vidéo et de l'audio. Enfin, le dernier chapitre conclut ce mémoire et évoque les différentes perspectives possibles par rapport au travail mené et aux résultats obtenus.

# Chapitre 2

# Méthodologies de conception

Les techniques et les capacités d'intégration des circuits électroniques n'ont cessé de s'accroître au cours de ces dernières années. L'intégration de systèmes toujours plus complexes nécessite la définition de nouvelles méthodes de travail afin d'exploiter pleinement les évolutions technologiques. C'est dans ce cadre que s'inscrivent les travaux présentés dans ce mémoire.

Dans ce chapitre, nous effectuons tout d'abord une brève présentation du domaine de la conception des systèmes mixtes logiciels / matériels, afin d'introduire et de positionner l'approche développée au laboratoire. Cette dernière est basée sur l'utilisation d'estimateurs très tôt dans le flot de conception (avant l'étape de partitionnement), ce qui constitue un point original. En effet, deux étapes interviennent successivement : l'estimation "Système" et l'estimation "Architecturale". Ces deux étapes sont complémentaires et consistent en un raffinement progressif des estimations. Aussi, la deuxième partie de ce chapitre est consacrée aux estimateurs afin de donner au lecteur une vision claire des méthodes d'estimation existantes et de positionner le travail présenté dans ce mémoire, à savoir une méthode d'estimation architecturale. Enfin, la technique proposée visant principalement les composants programmables, une présentation des deux architectures les plus représentatives du domaine est effectuée.

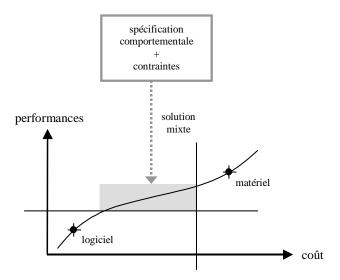

### 2.1 La conception conjointe logiciel / matériel

### 2.1.1 Problématique du codesign

Le problème de la conception conjointe logiciel / matériel provient de la nécessité de trouver une répartition équilibrée des fonctions d'une application sur les composants d'un système numérique dans le but d'aboutir à une architecture aux performances maximales sous contraintes de coût et de consommation d'énergie. L'évolution des technologies au cours de ces dernières années permet aujourd'hui l'intégration d'applications très complexes au sein d'une même puce (on parle de SOC, System On Chip). L'avènement des systèmes portables ou embarqués (téléphonie mobile, multimédia, communications sans fil ...) imposent des contraintes de plus en plus fortes car leur conception fait appel à des domaines variés tels que l'électronique analogique, numérique, les hyper fréquences, ... Si on se limite au seul domaine du numérique, les solutions d'intégration sont déjà multiples. La plus économique consiste à utiliser des processeurs. Qu'ils soient d'usage généraux ou spécifiques (DSP, Digital Signal Processor), leur emploi constitue généralement la solution la plus rapide en terme de temps de développement puisqu'elle consiste en la réalisation d'un programme, mais c'est aussi la moins intéressante en terme de performances. À l'opposé, la solution matérielle consiste à développer un circuit intégré entièrement dédié à l'application, ce qui permet toutes sortes d'optimisations que ce soit en performances, surface ou consommation d'énergie. Par rapport à une intégration logicielle, cette solution est plus chère en temps et en coût car la définition de l'architecture d'un circuit intégré est généralement beaucoup plus longue que l'écriture d'un programme, et qu'il faut en plus rajouter les délais de fonderie et de test. Ainsi, la solution intermédiaire qui consiste à combiner les avantages de ces deux approches est un challenge intéressant car elle permet l'élaboration d'architectures mieux adaptées aux contraintes de conceptions (figure 2.1). Typiquement, les parties évolutives et peu critiques sur le plan des performances sont placées sur un ou plusieurs processeurs alors que les fonctionalités coûteuses en temps et en consommation d'énergie sont elles candidates à une intégration matérielle. Les considérations d'ordre économique peuvent aussi entrer en compte en favorisant par exemple une architecture logicielle pour une mise à disposition rapide sur le marché (*Time To Market*). Le problème revient donc à choisir les composants logiciels / matériels ainsi que leur nombre (allocation), et trouver la répartition des fonctionalités du système sur ces composants (partitionnement).

Fig. 2.1 – Les différentes solutions d'intégration d'un système

Il est clair aujourd'hui que les outils de CAO sont indispensables pour une conception sûre de ces systèmes électroniques tout en réduisant les coûts et les temps de conception. Cela explique l'intérêt grandissant des industriels et du monde de la recherche dans le domaine de la conception conjointe (codesign) depuis les premiers travaux sur l'analyse et la synthèse assistée par ordinateur de systèmes mixtes à l'université de Stanford en 1990 [34].

### 2.1.2 Limites des approches classiques

Un rapide survol de quelques outils et méthodes [34][35][36] révèle deux grandes constatations. Premièrement, beaucoup d'entre eux trouvent leur limites dans une classe d'application et ceci à cause du modèle d'architecture et du modèle de spécification. D'autre part, toutes ces techniques reposent sur le principe de partitionnement, qui consiste à segmenter la spécification dans le but de réaliser l'intégration du système sur plusieurs composants. C'est lui qui constitue le coeur du processus de la conception conjointe. Les

fonctions composant le système sont réparties sur les différentes unités du modèle d'architecture et la qualité de ce partitionnement, qu'il soit manuel ou automatique, est évalué au moyen d'une fonction de coût, d'estimateurs ou directement par la vérification des performances après intégration du système. La qualité de l'intégration repose donc essentiellement sur celle du partitionnement et finalement, les propriétés intrinsèques de l'application n'ont pas une influence directe sur la topologie de l'architecture. L'approche originale développée au LESTER cherche au contraire à guider la construction de l'architecture en fonction des propriétés intrinsèques de l'application. L'architecture est élaborée de façon pragmatique en précisant progressivement les hypothèses architecturales à mesure que l'on progresse dans l'analyse du système.

Peu d'approches font intervenir les estimations avant l'étape de partitionnement. Or l'emploi d'estimateurs peut se faire dès les phases de spécification et permettre ainsi de guider les choix de conception d'une architecture hétérogène pour une meilleure adéquation avec l'application. L'architecture peut être élaborée par un raffinement progressif de l'analyse de la spécification au moyen d'estimations opérant à différents niveaux d'abstraction. Il n'y a alors plus de modèle d'architecture prédéfini, ni de notion de partitionnement tel qu'elle a été précédemment définie, ce qui simplifie à priori le processus de conception. La réduction de complexité résultant de l'emploi d'estimateurs peut alors permettre l'exploration d'un espace de recherche plus important.

## 2.2 Codesign: l'approche du LESTER

### 2.2.1 Principe de l'approche

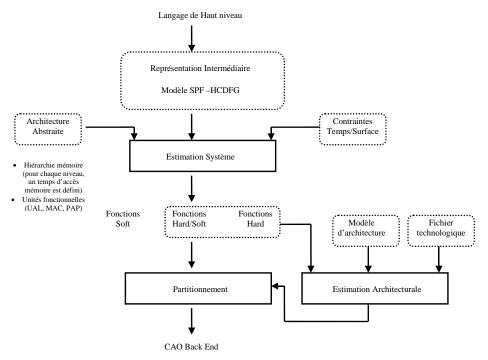

L'idée consiste à commencer la conception d'une architecture ad hoc dès les phases de spécification et de conception préliminaire des applications. L'intérêt de se situer à un tel niveau d'abstraction reside dans le fait que c'est à ce stade de la conception que les choix effectués ont le plus d'impact sur les performances finales du système. On peut distinguer deux points essentiels dans ce flot (figure 2.2) : l'estimation "Système" et l'estimation "Architecturale".

Les estimations au niveau système permettent de caractériser un ensemble

de fonctions et de les classer par ordre de criticité. La criticité traduit le poids du choix d'implantation d'une fonction sur les performances finales de l'ensemble des fonctions. Les estimations sont décorrélées de toute hypothèse architecturale, c'est à dire que seule la spécification comportementale est prise en compte pour cette analyse. Le coût et les performances de chaque

Fig. 2.2 – Flot de conception : "Design Trotter"

fonction sont ainsi estimés en tenant compte des intéractions avec les fonctions plus critiques et déjà estimées. La dernière étape de l'estimation système consiste en une projection de chacune des fonctions de l'application sur une cible modélisée afin de définir d'une part les fonctions candidates à une implantation logicielle, d'autre part les fonctions préssenties pour une implantation matérielle et enfin celles pour qui le choix ne peut être fait à ce niveau d'abstraction et nécessite par conséquent d'être traitées par les étapes "aval". Ainsi, le concepteur dispose dès l'étape de partitionnement d'une décomposition logicielle / matérielle à partir de laquelle il peut affiner la solution finale.

L'estimation architecturale intervient afin d'évaluer les performances des fonctions candidates à une implantation matérielle et celles pour qui le choix n'est pas encore établi. L'étape d'estimation architecturale a donc pour rôle de déterminer une solution d'implantation pour toutes les fonctions pouvant être implantées sur une cible matérielle, en l'occurrence, ici un FPGA. À partir de ces informations plus précises, l'étape de partitionnement effectue les choix définitifs d'implantation et définit les fonctions associées aux unités logicielles, celles relevant des unités matérielles ainsi que les supports de communication de l'architecture finale.

L'originalité de cette approche par rapport aux autres outils de codesign tient dans la stratégie qui permet une construction incrémentale de l'architecture et une exploration de l'espace de recherche à partir d'un très haut niveau d'abstraction.

### 2.2.2 Spécification : le modèle SPF - HCDFG

La description comportementale de l'application est saisie dans un langage de haut niveau et est ensuite traduite dans un modèle de représentation intermédiaire : le modèle SPF [29]. C'est sur ce modèle que les différents outils travaillent.

Le principal objectif de ce modèle est la spécification de systèmes numériques à un haut niveau d'abstraction pour permettre l'exploration de l'espace de recherche. Il permet la prise en compte de toutes les informations telles que les opérations, le contrôle, les opérandes multi-dimensionnels nécessaires à l'estimation des unités de traitement, contrôle, mémoire et au partitionnement de l'application sur une architecture hétérogène. Le modèle SPF est basé sur cinq concepts de base qui sont la concurrence, la hiérarchie, les communications, la synchronisation et le temps. La concurrence permet d'exprimer les calculs et accès aux données en parallèle. La hiérarchie permet de gérer la complexité due à l'importance du traitement et du contrôle des applications modernes. La communication traduit les échanges de données et de contrôle entre différentes tâches (process). La synchronisation est nécessaire pour modéliser les dépendances d'exécution entre processus concurrents et le temps lui, sert à spécifier les contraintes temporelles.

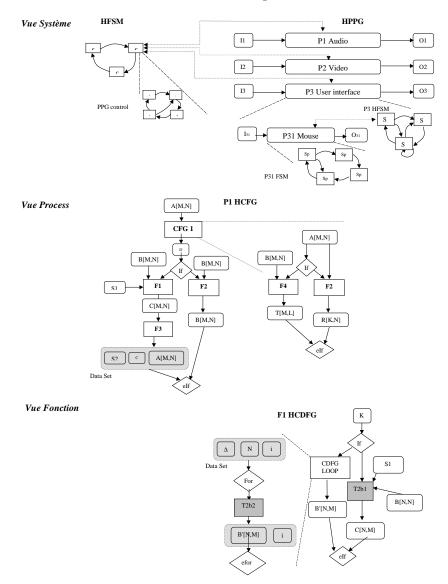

SPF est un modèle graphique basé sur trois vues (figure 2.3) : Système, Process et Fonction. Ces vues sont hiérarchiques et on passe à la vue suivante quand la granularité de la vue courante ne permet plus de décomposition.

La vue système correspond au plus haut niveau de spécification possible. Elle permet la capture des différentes configurations du système à concevoir

Fig. 2.3 – Le modèle SPF

(set top box par exemple), en montrant tous les différents processus à déclencher pour fonctionner dans une configuration, et la structure de contrôle nécessaire à leur mise en route. Elle utilise un modèle à états finis où un flot de données est associé à chaque état. La hiérarchie permet de modéliser les sous-états du système. La vue process permet de décrire chaque processus

du système. C'est un graphe hiérarchique de fonctions (autocorrélation ou filtrage par exemple) liées par des structures de contrôle et qui échangent des données. Ces données peuvent être scalaires ou multi-dimensionnelles. Dans ce dernier cas, les modes d'adressage sont explicitement représentés afin de permettre l'estimation mémoire. Le plus petit noeud de traitement dans cette vue correspond à une fonction. Le modèle utilisé dans la vue process est un graphe flot de contrôle hiérarchique (HCFG). Aucun traitement n'y apparait explicitement : ils sont encapsulés dans les fonctions. La vue fonction décrit chaque fonction associée aux processus à l'aide d'opérations élémentaires ou de graphes hiérarchiques d'opérations élémentaires. Les structures de contrôle et les échanges de données sont aussi présents dans cette vue. Le modèle utilisé à ce niveau est donc un graphe flot de contrôle et de données hiérarchique (HCDFG). Signalons ici que la méthode d'estimation architecturale présentée travaille uniquement à ce niveau (l'estimation architecturale vise à estimer une fonction sur une cible matérielle).

La figure 2.3 montre un exemple de spécification utilisant le modèle SPF. La vue système est composée de trois processus dont la décomposition hiérarchique correspond à d'autres machines à états finis (P3 User interface) ou à des sous-process (P1 Audio). La vue process permet la représentation de ces derniers sous forme de graphe flot de contrôle hiérarchique (P1 HCFG associé au processus P1 Audio par exemple). Puis la vue fonction décrit les traitements associés aux sous-fonctions par un modèle flot de contrôle et de données, comme l'illustre la sous fonction F1.

La représentation graphique du modèle permet le passage entre les différentes vues et leur hiérarchie. Le concepteur peut ainsi facilement accéder à tous les niveaux de la description du système. Grâce à ce modèle, on peut représenter un large spectre d'applications orientées contrôle ou traitement. Il permet la spécification et la représentation de systèmes hétérogènes dans le but d'effectuer les étapes d'estimation, de partitionnement et est adapté à l'approche codesign. Le concepteur doit d'abord décrire les vues système et process car ces étapes reposent esentiellement sur son analyse du système à concevoir et font largement appel à son expérience de concepteur. Le modèle HCDFG correspondant à la vue fonction est obtenue à l'aide d'un parser sur la spécification en entrée, actuellement décrite en langage C.

Après avoir présenté le flot de conception développé au LESTER, ainsi

que le modèle de spécification des applications, nous présentons une vision synthétique des méthodes mises en oeuvre dans les étapes d'estimation système et architecturale. Ceci permettra de positionner plus clairement les travaux développés au LESTER par rapport à l'ensemble des techniques d'estimation existant à ce jour, techniques dont la présentation fait l'objet de la section 2.3.2.

### 2.2.3 L'Estimation Système

Il ne s'agit pas dans cette partie d'expliquer les techniques mises en oeuvre durant l'estimation système (ceci sort du cadre de ce mémoire), mais plutôt de donner au lecteur une vision globale de l'approche afin de bien comprendre la philosophie du flot développé au LESTER.

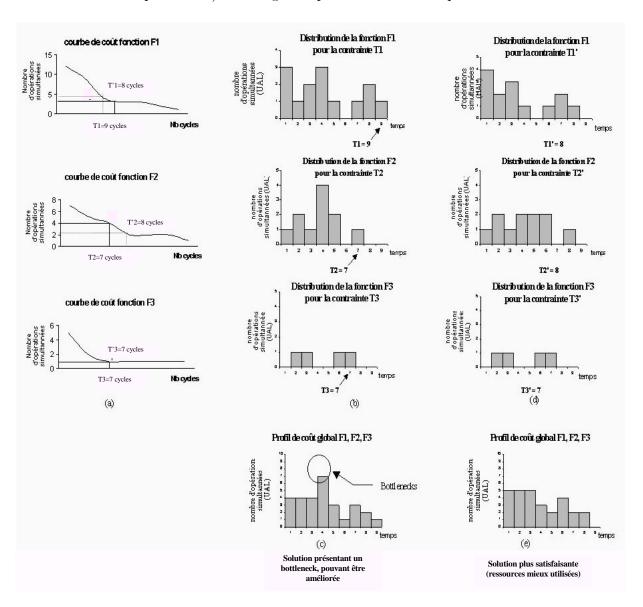

La méthodologie de l'estimation système repose sur quatre points originaux [37]. Premièrement, une caractérisation macroscopique de l'ensemble de l'application est réalisée afin de déterminer l'orientation des différentes fonctions en terme de traitement, contrôle ou mémoire (TCM par la suite). Le second point est le niveau d'abstraction élevé qui permet d'obtenir des valeurs d'estimation indépendantes de tout modèle architectural. Troisièmement, le coût est caractérisé pour différentes contraintes du nombre de cycles alloués à une fonction, ce qui conduit à exploiter plus ou moins le parallélisme intrinsèque de la fonction (figure 2.4). Ainsi, chaque fonction est caractérisée sous la forme d'une courbe (coût vs nombre de cycles), ce qui permet d'explorer un plus grand nombre de solutions architecturales et par conséquent, de retenir une solution en meilleure adéquation avec l'application. Le quatrième point porte sur l'inter-dépendance de l'estimation : le traitement d'une fonction prend en compte les interactions possibles avec le reste de l'application dans le but d'une optimisation efficace.

Le flot d'estimation système s'articule principalement autour des points suivants :

La caractérisation macroscopique : elle permet d'extraire la nature de l'application spécifiée. Dans un premier temps, un comptage du nombre d'opérations de traitement, de contrôle et de mémorisation (TCM par la suite) est effectué pour chaque fonction séparément. Cette caractérisation fournit un critère de sélection d'un ensemble de "fonctions critiques" de l'application (fonctions les plus coûteuses d'un point de vue des métriques TCM). Ceci signifie qu'on ne considère que les fonc-

Fig. 2.4 – Exemple de profil de coût global

tions qui ont le plus d'impact sur l'architecture finale.

La co-estimation intra-fonction : étant donné un ensemble de fonctions critiques, le but est de calculer pour chaque fonction la courbe de coût du nombre d'opérations simultanées pour plusieurs contraintes de

temps exprimées en nombre de cycles (figure 2.4.a.).

- L'ordre d'analyse des fonctions critiques : à partir de la classification issue du calcul des métriques TCM, un raffinement est effectué en tenant compte de la nature des liens et des potentiels d'optimisation (partage de ressources, ou minimisation d'accès à la mémoire, . . . ) existant entre les fonctions.

- La co-estimation inter-fonction : comme pour la co-estimation intrafonction, des courbes de coût sont calculées pour chaque fonction et tiennent compte du partage de ressources et de données avec les fonctions précédemment estimées, donc plus critiques.

- Le profil de coût global : il traduit le coût de l'ensemble des fonctions critiques à chaque cycle, c'est à dire le nombre de ressources utilisées simultanément du premier au dernier cycle d'exécution (qui correspond à la contrainte de temps). Ces profils permettent de repérer les goulots d'étranglement qui correspondent à de fortes discontinuités dans la répartion des opérations (figure 2.4.c.). En redistribuant le parallélisme des fonctions concernées, on "lisse" les courbes de façon à obtenir une répartition plus homogène et donc un coût moins important (figure 2.4.e.).

- les transformations algorithmiques : une fonction primitive pouvant être décrite par plusieurs algorithmes (FFT par exemple), le concepteur peut modifier ses choix d'algorithmes pour améliorer l'adéquation.

Il résulte de cette analyse système un ensemble d'informations intéressantes pour l'aide à la conception d'une architecture ad hoc. Elle fournit à l'étape de partitionnement un graphe sur lequel sont annotées un certain nombre de contraintes à respecter concernant le parallélisme (degré de déroulage des boucles par exemple). Elle fournit de plus un ensemble de contraintes séquentielles exprimées sous la forme de dépendances d'optimisation (réutilisation, optimisation des accès mémoire) et une étape de pré-ordonnancement (ordonnancement simplifié utilisé pour le calcul des profils de coût). Ces informations permettent de réduire l'exploration de l'espace de recherche pendant le partitionnement. Les estimations architecturales interviennent alors pour fournir des valeurs d'estimation précises sur le coût et les performances attendus du placement des diverses fonctions sur des composants cibles.

Il existe différents degrés de couplage entre l'estimation système et l'es-

timation architecturale. Ces derniers conduisent à des compromis entre l'exploitation du parallélisme, la précision des résultats obtenus et le temps de calcul machine. Dans le cadre de ce mémoire, nous limitons la présentation à un couplage faible : l'estimation système fournit à l'estimation architecturale une liste de fonctions potentiellement candidates à une réalisation matérielle. L'ensemble des caractéristiques résultant de l'estimation système ne sont donc pas prises en compte, car comme nous le verrons dans les chapitres suivants, l'estimation architecturale effectue de nouveau un ordonnancement afin de mettre en évidence le parallélisme potentiel. Le choix de présenter uniquement ce lien entre les deux étapes d'estimation provient de la volonté de proposer une méthode d'estimation qui s'inscrive dans le flot de conception développé au LESTER, mais qui puisse également fonctionner de façon autonome.

#### 2.2.4 L'Estimation Architecturale

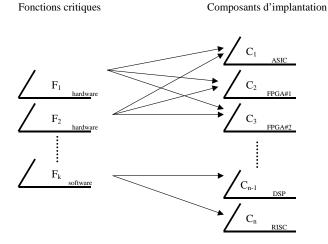

L'architecture d'un système hétérogène est composée d'unités de nature différente sur lesquelles s'exécutent les diverses fonctionnalités du système. L'exploration de l'espace de recherche doit permettre de tester rapidement la

Fig. 2.5 – Allocation de composants

faisabilité et les performances de ces fonctions sur plusieurs types de technologies (ASICs, FPGAs, DSPs, ...) afin de sélectionner la meilleure solution d'implantation. La figure 2.5 montre un exemple de fonctions critiques et de

composants candidats pour l'intégration. Le choix des composants est guidé par les métriques de caractérisation macroscopique établies à l'étape des estimations système (par exemple, une fonction effectuant du calcul intensif pourra être candidate à une implantation matérielle). L'estimation architecturale permet ensuite d'évaluer le coût de l'intégration de chaque fonction sur plusieurs composants, de façon à ne garder que le plus satisfaisant. Le travail présenté ici ne s'intéresse qu'à l'estimation pour une implantation matérielle, plus particulièrement les FPGAs. La méthode doit donc pouvoir s'appliquer à toutes les familles de composants de ce type et constitue en outre un point de départ à partir duquel une technique d'estimation globale prenant en compte l'estimation des ASICs peut être développée.

L'estimation d'une fonction décrite au niveau comportemental par un graphe flot de données et de contrôle hiérarchique (*HCDFG*) sur un composant FPGA a pour but de vérifier la faisabilté de l'intégration, d'évaluer le coût en surface (taux d'occupation) et les performances en vitesse d'exécution. Une exploration basée sur l'analyse du parallélisme, l'influence de l'allocation de ressources et de la période d'horloge, ainsi que la prise en compte de la logique de contrôle et de l'unité de mémorisation est effectuée afin de caractériser le coût de manière complète et réaliste. Les objectifs suivants ont été fixés :

- proposer une méthode globale (prise en compte des aspects traitement, contrôle, mémoire).

- proposer une méthode qui exploite le parallélisme potentiel en caractérisant les fonctions selon une courbe surface vs vitesse d'exécution.

- proposer une méthode de complexité faible afin de pouvoir évaluer plusieurs composants.

- proposer une méthode qui puisse facilement s'étendre à d'autres composants et qui ne soit pas spécifique à une seule famille.

- proposer une méthode qui s'inscrive dans le flot de conception du LES-TER, mais qui puisse aussi fonctionner de façon indépendante.

- proposer une méthode qui prenne en entrée une application intégrant de la hiérarchie, du parallélisme et des structures de contrôle.

Comme nous le verrons dans la suite du mémoire, ces objectifs ont été atteints. L'approche devait également inclure l'estimation de la puissance et une prise en compte fine du routage des composants FPGA. Malheureusement, ces travaux n'ont pu être finalisés.

Afin de définir les méthodes mises en oeuvre, un état de l'art approfondi a été effectué. Il existe en effet un grand nombre de méthodes d'estimation dans la littérature, mais aucune à notre connaissance ne réunit toutes les conditions nécessaires pour une exploration rapide à partir d'un modèle de spécification complexe autorisant la hiérarchie et les structures de contrôle. Cependant, les techniques développées dans la littérature constituent une base riche à partir de laquelle une méthode globale peut être développée. La suite de ce chapitre présente ces différentes méthodes.

## 2.3 État de l'art dans le domaine des estimations

Les estimations jouent un rôle essentiel dans le processus de conception puisqu'ils permettent de renseigner le concepteur et de le guider dans ses différents choix. Un très grand nombre de méthodes d'estimation sont décrites dans la littérature, diversité qui s'explique par la complexité du processus de conception où les estimateurs sont nécessaires à tous les niveaux : de la spécification jusqu'au plan de masse, ceci pour chaque type d'unité composant l'architecture (unités de traitement, contrôle, mémoire, communication) pour plusieurs types de contraintes (temps, surface, consommation, ...) et de technologies (ASIC, FPGAs ...). Nous proposons donc de passer en revue différentes méthodes d'estimation à partir d'une description comportementale classées par le niveau d'abstraction auquel elles s'appliquent (système ou RTL), ainsi que celles plus spécifiques aux FPGAs (niveau logique).

### 2.3.1 État de l'art des estimations au niveau système

Les avancées dans le domaine technologique permettent aujourd'hui l'intégration d'un grand nombre de fonctions au sein d'un même système. Les contraintes de conception imposent des temps de développement plus courts et donc réduisent le temps disponible pour la recherche de la meilleure adéquation application - système. L'estimation système est donc nécessaire pour guider le concepteur dans ses différents choix à l'étape d'exploration de l'espace de recherche. Le niveau système consitue le niveau d'abstraction le plus élevé. L'analyse au niveau système d'une description comportementale permet de définir un certain nombre de caractéristiques qui renseignent le concepteur sur les propriétés du système indépendamment de toute notion d'architecture ou d'implantation physique (découpage en sous-fonctions, degré de granularité, . . . ).

Vahid propose dans son approche [38], le calcul de métriques de proximité pour le partitionnement au niveau fonctionnel. Ces métriques sont définies au niveau système et permettent l'évaluation du rapprochement de deux sous parties de la spécification, en terme de calcul ou de communication. Elles sont utilisées dans des fonctions de coût basées sur des pondérations empiriques qui dépendent de l'application. Des métriques similaires sont utilisées, à un niveau de granularité plus faible, pendant la phase de regroupement d'opérations logiques [39], arithmétiques [40] et instructions [41]. Sur le plan architectural, un grand nombre de métriques sont définies dans [42] et [43] pour la communication entre opérateurs arithmétiques. Dans le cas du partitionnement sur une architecture cible donnée, des estimations sont utilisées par les fonctions de coût de l'algorithme de partitionnement [44] [45]. Le principe consiste à évaluer les conséquences en termes de surface et performances avant de modifier éventuellement les choix d'implantation. Dans [45], le but est de définir dynamiquement la granularité de l'application.

Ces estimations ont pour but de guider la conception en proposant un certain nombre de métriques à partir desquels des choix sont effectués. Plus ces métriques interviennent tôt dans le flot de conception, plus elles sont indépendantes de l'implémentation et permettent d'apprécier globalement, et non plus localement, le réel potentiel d'optimisation.

### 2.3.2 État de l'art des estimations au niveau RTL

Le niveau RTL correspond au niveau d'abstraction permettant de décrire une architecture. Les méthodes d'estimation opérant à ce niveau ont pour but d'évaluer le nombre de composants (les multiplieurs, les registres, les mémoires, ...) sous des contraintes telles que le temps d'exécution, la surface. Un grand nombre de méthodes ont été développées au cours de la recherche sur la synthèse architecturale (synthèse de haut niveau) pendant ces vingt dernières années. Beaucoup de travaux concernent l'estimation de

l'unité de traitement qui représente souvent la partie la plus coûteuse pour les algorithmes de traitement du signal. On note aussi l'apparition d'un grand nombre d'études sur les aspects mémorisation avec l'avênement des applications de type vidéo numérique.

Le coût d'une architecture dédiée au traitement du signal dépend principalement de l'unité de traitement et de l'unité de mémorisation. La réalisation de l'unité de traitement constitue souvent la première étape. Aussi, un grand nombre de ces techniques vise l'estimation du coût de l'unité de traitement, sous contrainte de temps réel. Le problème consiste à évaluer les besoins en terme d'unités fonctionnelles à partir de la description comportementale d'un algorithme. Le compromis temps / coût peut être formalisé de plusieurs façons.

Dans [6], les auteurs (Rabaey et Potkonjak) le caractérisent au moyen de bornes supérieures et inférieures. Le principe du calcul de la borne supérieure consiste à chercher entre t=0 et t=T (T étant la contrainte de temps) l'instant où le parallélisme est à son maximum ce qui se produit lorsque la superposition d'opérations appartenant à un même type est maximale. Il s'agit d'une limite surestimée reflétant le pire cas. La limite inférieure est obtenue en moyennant le temps nécessaire à l'exécution des  $n_i$  opérations de type i dans le graphe ( $n_i * \Delta_i$ , où  $\Delta_i$  représente le délai de l'opérateur réalisant l'opération i) par la contrainte de temps T. Cette valeur n'est exacte que dans le cas où le taux d'utilisation de la ressource i est de 100%. L'étude est ensuite étendue en cherchant à inclure le problème des dépendances de données.

Sharma et Jain [5] ont élaboré une méthode permettant d'obtenir la borne inférieure du nombre d'opérateurs en tenant aussi compte des dépendances entre noeuds du graphe. Le principe repose sur l'analyse de l'activité des opérations du graphe dans un intervalle  $[\delta_1, \delta_2]$  compris dans [0, T] où T est la contrainte de temps. Ainsi, chacune des opérations susceptibles d'intervenir dans cet intervalle de temps est ordonnancée à sa date au plus tôt (ASAP) si elle minimise la durée d'activité entre  $\delta_1$  et  $\delta_2$  et à sa date au plus tard (ALAP) dans le cas inverse. Le nombre d'opérations obtenu est ensuite divisé par la longueur de l'intervalle considéré pour donner une valeur moyenne. Celle-ci traduit une équirépartition temporelle des opérations, donc un parallélisme minimal. La valeur maximale obtenue sur l'ensemble des intervalles

possibles fournit finalement la borne minimale du nombre d'opérateurs. Les auteurs estiment l'erreur moyenne à 5% pour une complexité en  $O(NC^2)$ .

Les méthodes probabilistes [2] (Diguet) permettent des estimations de complexité beaucoup plus réduite, de l'ordre de O(N) selon le type d'estimation probabiliste. Comme dans les méthodes précédentes, les dépendances de données sont considérées au travers du calcul des dates ASAP et ALAP, et l'étude se fait indépendamment pour chaque opérateur. La méthode repose sur le principe suivant : une opération peut être exécutée aléatoirement (la loi est choisie uniforme) entre sa date ASAP et sa date ALAP. Pour chaque type d'opérateur, on cumule les probabilités d'exécution des opérations à chaque cycle. La somme maximale trouvée, arrondie à l'entier supérieur est le nombre d'opérateurs requis. Contrairement aux méthodes précédentes, les estimations probabilistes ne fournissent ni une borne inférieure, ni une borne supérieure. La réduction de la complexité permet en outre de caractériser le coût de manière dite "dynamique", c'est à dire sous forme de courbes en fonction d'une contrainte de temps variable.

Les méthodes présentées ci-dessus ne s'appliquent que dans le cas de spécifications qui ne comportent pas de structures de contrôle. En général, une description comportementale comporte aussi des structures conditionnelles et itératives, une méthode d'estimation réaliste doit donc en tenir compte.

Dans la méthode [3] (Narayan et Gajski), les auteurs s'intéressent à l'estimation temps / surface d'une application décrite dans un modèle de description qui accepte les structures de contrôle, ainsi que la spécification hiérarchique et l'exécution concurrente (SpecChart). Le principe repose sur l'emploi de probabilités pour pondérer les temps d'exécution de chaque branche d'une structure conditionnelle. Ces probabilités peuvent être définies par l'utilisateur, issues d'une analyse type "vecteurs de test" (profiling) ou tout simplement suivre une loi uniforme (équirépartition des probabilités en fonction du nombre de branches). Outre la prise en compte de l'aspect contrôle de la spécification, la méthode propose une technique d'évaluation de la surface de l'unité de contrôle basée sur l'estimation du nombre de pas de contrôle et de signaux nécessaires pour le séquencement des unités de traitement et de mémorisation. Des extensions aux cas des mémoires multi-ports, au traitement du pipeline et au calcul d'autres métriques de performances sont présentés par les mêmes auteurs dans [4].

Les techniques décrites ci-dessus sont basées sur des modèles simples de façon à obtenir des valeurs d'estimation rapide, ceci bien sûr au détriment de la précision. Une autre approche pour obtenir des valeurs d'estimations consiste à utiliser directement une technique d'ordonnancement. Par rapport à un algorithme d'estimation, une heuristique d'ordonnancement garantit la faisaibilité de la solution trouvée. Toutefois, l'augmentation de complexité qui en résulte est importante (typiquement  $O(N^2)$  [4]) et l'emploi d'une technique de ce type pour l'évaluation d'un grand nombre de solutions d'implantation (exploration de l'espace de recherche) peut rapidement s'avérer impossible. Une évaluation de la complexité des techniques d'ordonnancement pour les graphe flot de contrôle a été proposée dans [33]. Le tableau 2.1 présente

| Référence                     | Complexité    | Commentaire                               |  |

|-------------------------------|---------------|-------------------------------------------|--|

| Rabaey & Potkonjak [6]        | $\leq O(N^2)$ | Bornes supérieure et inférieure           |  |

|                               |               | à partir d'un DFG                         |  |

| Sharma & Jain [5]             | $O(NC^2)$     | Borne inférieure à partir                 |  |

|                               |               | d'un DFG                                  |  |

| Probabiliste [2]              | O(N)          | Caractérisation du coût en fonction d'une |  |

|                               |               | contrainte de temps variable              |  |

| Formulation ILP               | O(N + cC)     | Borne inférieure du nombre de pas de      |  |

| Rim & Jain [7]                |               | contrôle                                  |  |

| Narayan & Gajski              | _             | Prise en compte du contrôle et de la      |  |

|                               |               | de la hiérarchie (Specharts)              |  |

| List Scheduling [8]           | O(NC)         | Technique d'ordonnancement d'un           |  |

|                               |               | DFG                                       |  |

| Force Directed Scheduling [9] | $O(N^2C)$     | Technique d'ordonnancement d'un           |  |

| _                             |               | DFG                                       |  |

| Path Based Scheduling [33]    | Exponentielle | Technique d'ordonnancement prenant        |  |

|                               |               | en compte le contrôle                     |  |

TAB. 2.1 – Différentes techniques pour l'estimation au niveau comportemental

plusieurs techniques d'estimation et d'ordonnancement, ainsi que leurs complexités respectives. N représente le nombre de noeuds du graphe et C le nombre de pas de contrôle.

Dans les applications embarquées, une grande partie de la consommation d'énergie est due au stockage et au transfert des données. En outre, les mémoires ont souvent un coût important en consommation et en surface. Certains travaux se sont donc orientés vers une méthodologie de conception qui s'appuie d'abord sur l'optimisation de l'architecture mémoire, plutôt que sur celle de l'unité de traitement (travaux effectués à l'IMEC [23]). Cette approche s'applique particulièrement aux applications à forte dominance pour le traitement de données comme dans le domaine du multimédia ou de la télécommunication. Les premiers travaux relatifs à l'estimation mémoire se situent au niveau scalaire, car les applications ciblées (dans le cadre de la synthèse de haut niveau) ne contiennent qu'un nombre limité de signaux. Les variables scalaires décrites dans une spécification au niveau RTL peuvent être assignées à un nombre de registre minimum au moyen de techniques telles que l'algorithme "left-edge" [10], la formulation ILP [24], la coloration de graphe [25] ou le clique partitionning [26].

Ces techniques sont difficilement utilisables dans les applications qui traitent d'un grand nombre de signaux multi-dimensionnels. Les données struc-

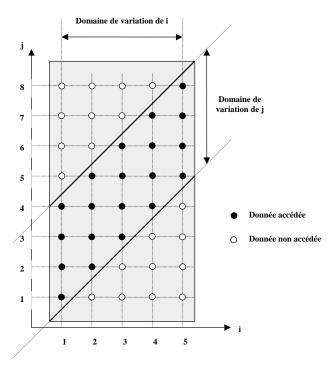

Fig. 2.6 – Modélisation mémoire sous forme de polyèdre

turées telles que les vecteurs et les matrices sont très utilisées et les traitements effectués sur ces types de données ont conduit au développement de nombreuses techniques. Lorsque l'on manipule des structures de données de type tableau, les traitements sont généralement décrits par des boucles imbriquées dont les indices sont bornés par deux fonctions affines. Une approche répandue pour l'estimation mémoire d'applications qui traitent de signaux multi-dimensionnels repose sur la modélisation sous forme de polyèdre et a été introduite dans [27]. Sur la figure 2.6 sont représentés les points du tableau qui sont accédés dans l'exemple suivant :

$$do i := 1...5$$

$do j := i...i + 3$

$f(x(i, j));$

La mémoire nécessaire pour mémoriser le tableau x est la "boîte rectangulaire" contenant l'ensemble des éléments de x. Dans notre exemple, elle est de taille 5\*8, c'est à dire qu'il faut une mémoire de 40 points, alors que le nombre d'emplacements réellement utilisés est égale à 20. Cette valeur définit le volume du polyèdre. Le taux d'utilisation de la mémoire est de 50% dans ce cas. De nombreux travaux se basent sur cette représentation pour développer d'autres techniques telles que les transformations (pour trouver un compromis entre la taille mémoire et la complexité de la fonction d'adressage par exemple), ou pour étudier le problème d'allocation mémoire, assignation signal mémoire, ordonnancement des opérations, ... [23].

# 2.3.3 État de l'art des estimations spécifiques aux FP-GAs

Les facteurs essentiels de performances pour les FPGAs sont la qualité des outils de CAO, la qualité du composant et les qualités électriques de l'architecture. La majorité des travaux relatifs aux FPGAS portent sur l'optimisation des architectures et des outils de placement / routage [13]. La prise en compte de l'application pour l'estimation du coût relève du problème de l'utilisateur et est un problème peu étudié à notre connaissance. Aujourd'hui, la complexité des systèmes électroniques est telle qu'elle nécessite l'utilisation d'architectures hétérogènes, composées d'unités de nature différente, ce qui rend la conception de ces systèmes difficile. Il est donc important de pouvoir proposer très tôt à l'utilisateur un certain nombre de métriques de performances (typiquement temps, surface, consommation) mais cette fois en tenant compte de l'application que l'on doit y intégrer. Il existe peu de

méthodes à notre connaissance qui traitent du problème d'estimation sous cet angle.

Xu et Kurdahi proposent une technique visant l'estimation en temps et surface des FPGAs de type SRAM, et proposent une application à la famille XC4000 de Xilinx [14][15][16]. La technique repose sur un modèle du processus de mapping et prend en compte les effets dus au routage. Elle consiste à prédire l'utilisation des LUTs, la construction des CLBs ainsi que le placement et la forme du plan de masse. À partir d'une netlist d'entrée au niveau logique, un regroupement des portes qui tient compte de la structure interne des LUTs est effectué (cette approche se situe après une étape de synthèse de haut niveau). Il résulte de cette étape une netlist au niveau LUT. Ces LUTs sont ensuite regroupées dans les CLBs en fonction des configurations possibles (F, G, H). La netlist de CLBs obtenue est ensuite analysée de manière à prédire la topologie du plan de masse. Le coût des interconnexions est pris en considération en ajustant la topologie de telle sorte qu'elle tienne compte des ressources de routage du composant. Ensuite, un modèle temporel permet de calculer les performances en analysant les délais dus aux CLBs, aux lignes d'interconnexions et aux points d'interconnexions. Cette méthode présente un compromis précision complexité intéressant (6.1% d'erreur moyenne pour une complexité de l'ordre de O(n), mais elle est aussi très dépendante du composant cible, la famille XC4000 de Xilinx.

Une autre approche développée à l'Institut Fédéral de Technologie Suisse [17] permet l'estimation des paramètres temps et surface à partir d'un haut niveau d'abstraction. Cette technique cible des applications de type régulières où domine le traitement de données. Le principe repose sur la séparation de l'aspect spécification comportementale de l'influence des spécificités architecturales du FPGA. La phase spécification est réalisée sous la forme d'un graphe flot de données ramené à un ensemble d'opérations élémentaires (+, \*, mux, opérations logiques et LUT). Une phase de caractérisation algorithmique est alors effectuée, elle consiste à définir les paramètres suivants : nombre d'entrées / sorties, nombre d'opérations élémentaires, nombre de registres (hors registres pipeline), facteur de parallélisme, et nombre d'itérations. Le composant lui, est caractérisé à l'aide d'un modèle spécifiant les caractéristiques de chaque type d'opération élémentaire. Une combinaison linéaire des paramètres de caractérisation algorithmique et des paramètres de caractérisation

du composant permet ensuite de calculer les performances du système. Les auteurs proposent en outre une exploration de l'espace de recherche basée sur l'utilisation du pipeline permettant ainsi de diminuer la longueur du chemin critique. Les applications révèlent une bonne précision de la méthode mais aussi quelques limites de l'aveu même des auteurs : les effets du routage introduisent une erreur importante et le contrôle n'est pas pris en compte. Ceci limite l'utilisation de l'estimateur au cas d'applications régulières constituées essentiellement d'interconnexions courtes (les deux applications test proposées dans [17]sont le filtre FIR et le calcul de ressemblance de blocs 16x16 pour l'estimation de mouvement). Cette étude est menée sur un composant de la famille XC4000E de chez Xilinx.

Il existe une autre approche [18] [19] (Miller, Owyang, Kliman) basée sur une bibliothèque de benchmarks. Ceux-ci constituent une sorte de base de données de circuits dont les caractéristiques de surface et de performances ont été mesurées sur une grande variété de FPGAs. Lorsque l'on souhaite évaluer une certaine application, celle-ci est partitionnée en sous-parties dont chacune est remplacée par le circuit benchmark le plus ressemblant. Connaissant les caractéristiques de ces circuits, il est alors possible d'en déduire des valeurs d'estimation pour l'ensemble de l'application. Cette approche est fortement limitée par le fait qu'elle dépend énormément de cette base de données qui doit être régulièrement mise à jour en fonction des évolutions à la fois des composants et des applications.

Ces trois méthodes sont les seules à notre connaissance qui s'intéressent à l'estimation d'une application sur une technologie FPGA. Les principales limitations qui en ressortent concernent les composants ciblés (XC4000 pour les deux premières) et les spécifications d'entrée, inconvénients qui sont en grande partie liés au domaine d'application de ces estimateurs. En ce qui nous concerne, il faut pouvoir traiter le cas des spécifications complexes (incluant les structures de contrôle) et l'approche doit aussi s'appliquer à plusieurs types de composants. C'est la raison pour laquelle cette étude a été validée sur deux composants représentatifs des technologies modernes employées par les deux plus importants constructeurs : Xilinx et Altera. Nous proposons maintenant une présentation des architectures de ces deux composants illustrant deux types d'architecture : la structure ilôt de calcul (Virtex) et la structure hiérarchique (Apex), pour reprendre la terminologie employée dans

[20].

# 2.4 Composants cibles: les FPGAs

Les circuits logiques programmables les plus anciens sont les PAL (Programmable Array Logic) et sont apparus sur le marché au début des années 70. La première génération de ces composants permettait uniquement la réalisation de fonctions combinatoires. Puis sont apparus les PALs à registres permettant la réalisation de systèmes synchrones. Ce type de composant de faible densité est aujourd'hui communément désigné sous l'appellation PLD (Programmable Logic Device). Face à l'augmentation croissante de la complexité des systèmes électroniques, les composants ont évolué vers l'intégration de plusieurs architectures de type PAL au sein d'un même boîtier. Ces nouveaux composants ont donc naturellement été baptisés CPLD (Complex PLD). Leur architecture peut être vue comme une multipication de modules type PAL associés à une matrice d'interconnexion programmable.

Parallèlement à l'apparition des PALs, l'augmentation de la complexité des systèmes a eu pour effet la généralisation de l'usage des composants à application spécifiques, à savoir les ASICs (Application Specific Integrated Circuits). Ces composants apportent une réponse satisfaisante aux problèmes d'intégration mais leur forte densité en limite toutefois l'application à des domaines de grande diffusion ou exigeant une grande confidentialité.

Apparus au milieu des années 80, les FPGAs correspondent à ce que l'on pourrait considérer comme la voie intermédiare entre l'approche générique (PAL, CPLD) et spécifique (ASIC). Ils autorisent à la fois de grandes capacités d'intégration et la définition de fonctions par l'utilisateur.

Les FPGAs ont connu d'importantes évolutions architecturales au cours de ces dernières années. Ces évolutions résultent essentiellement de l'augmentation des capacités d'intégration qui permettent aux différents contructeurs de proposer des composants à la fois gros et performants. Les caractéristiques essentielles de ces nouvelles familles sont d'intégrer dans leurs architectures des modules visant à augmenter les performances comme par exemple de la mémoire, des entrées / sorties rapides, asservissement d'horloge . . . Une autre innovation importante dans le domaine des composants programmables repose sur la reconfiguration partielle ou totale du composant de manière dyna-

mique. Cet aspect ne sera pas traité dans nos travaux et nous nous limiterons dans cet état de l'art à l'étude des composants qui constituent le fer de lance des deux plus importants fournisseurs de composants classiques actuellement, la famille Virtex de Xilinx et Apex de chez Altera.

## 2.4.1 La famille Virtex (Xilinx)

L'architecture générale des FPGAs de chez Xilinx est basée sur une matrice carrée de cellules configurables pouvant être connectées entre elles par un réseau d'interconnexions [21]. La liaison vers l'extérieur se fait par des blocs d'entrées / sorties configurables en niveau logique, en impédance et en direction. La première génération XC2000 date de 1985 et Xilinx en est maintenant à sa septième génération de composants FPGA. La tendance des dernières générations est de cibler certains crénaux porteurs du marché, comme la solution "bas coût" ou à l'opposé la solution "haute performance". Ainsi, la panoplie présentée par le fabricant montre sa volonté de couvrir tous les segments du marché.

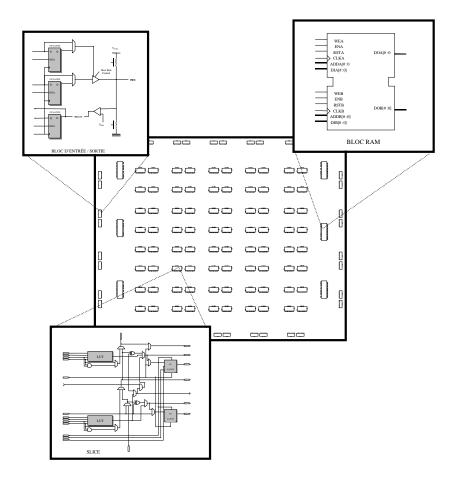

La dernière génération de composants baptisée Virtex vise les très fortes capacités (4 millions de portes) et les hautes vitesses (> 100 MHz). La technologie employée est une technologie CMOS  $0.18\mu m$  avec 6 niveaux de métallisation (2001). Dérivée de la famille des XC4000, les évolutions concernent le routage, les entrées / sorties et l'intégration des mémoires (figure 2.7). L'architecture du composant est basée sur une matrice carrée de "blocs logiques" dénommés CLBs (Configurable Logic Blocks) utilisés pour l'intégration de fonctions logiques combinatoires et synchrones. Chacun de ces blocs est constitué de quatre sous éléments regroupés par paires appelés slices. Ils comportent deux LUTs à 4 entrées permettant chacune la réalisation de fonctions logiques à 1, 2, 3 ou 4 entrées, de mémoires ou de registres à décalages. Ils disposent de plus d'un registre par générateur de fonction permettant ainsi la synchronisation de la sortie. Il est donc possible de réaliser un certain nombre de fonctions par slice : 2 fonctions logiques jusqu'à quatre entrées, 2 additionneurs 1 bit, 1 additionneur 2 bits, 2 registres à décalage 16 bits.

Chaque générateur de fonction peut être configuré en bloc mémoire RAM / ROM synchrone 16x1-bit, dite mémoire distribuée. Il est alors possible d'utiliser un CLB pour réaliser des mémoires simple port (16x8-bit, 32x4-bit,

64x2-bit, 128x1-bit) ou double port (16x4-bit, 32x2-bit, 64x1-bit). Les mémoires distribuées conviennent bien pour l'utilisation de petites mémoires. Pour des besoins plus importants, on trouve d'autres ressources de mémorisation, les blocs RAM, disposés en périphérie de la matrice de CLB. Ce sont des modules de mémoire RAM synchrone double port de 4096 bits configurables en mots de 1, 2, 4, 8 ou 16 bits. Chaque bloc est composé de deux