# Reducing hardware TCB in favor of certifiable virtual machine monitor.

François Serman

# ▶ To cite this version:

François Serman. Reducing hardware TCB in favor of certifiable virtual machine monitor.. Mobile Computing. Université Lille 1 - Sciences et Technologies, 2016. English. NNT: . tel-01757867

# HAL Id: tel-01757867 https://hal.science/tel-01757867

Submitted on 4 Apr 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Reducing hardware TCB in favor of certifiable virtual machine monitor

**Defended by François Serman**

francois@serman.me

December 8th, 2016

**Reviewed by:**

**Pr. Issa Traoré** University of Victoria **Pr. Gael Thomas** Telecom SudParis

Examined by:

Pr. Isabelle Ryl INRIA Paris

Pr. Gilles Grimaud CRIStAL Dr. Dominique Bolignano Prove&Run SAS

Dr. Michael Hauspie CRIStAL

# Résumé en Français

Cette thèse a pour objet la conception d'un hyperviseur logiciel sécurisé, à vocation de certification. Les plus hauts niveaux de certification requièrent l'usage de méthodes formelles, qui permettent de démontrer la validité d'un produit par rapport à une spécification à l'aide de la logique mathématique. Le matériel prouvé n'existant pas, les mécanismes d'hypervision sont ici implémentés de façon logicielle. Cela contribue à réduire la base de confiance, et donc la quantité de modélisation et de preuve à produire. En outre, cela rend possible la virtualisation de systèmes sur des plateformes qui ne sont pas dotées de ces instructions de virtualisation.

Les principaux challenges sont d'une part, l'analyse du jeu d'instruction qui, malgré l'existence de documentation, comporte des ambiguïtés et des particularités dépendantes de l'implémentation, voire même, des comportements non définis. D'autre part, d'identifier les intensions d'un système invité étant donné un flot d'instructions discret afin de rester en interposition avec le matériel sous-jacent. Pour ce faire, le code machine de l'invité est analysé et les instructions menaçant l'intégrité ou la confidentialité du système sont remplacées par des trapes logicielles, permettant d'analyser le contexte afin de décider de laisser s'exécuter l'instruction ou non.

En reposant sur l'existence d'un processeur et d'un système de gestion de mémoire prouvés, seul du code privilégié est susceptible d'outrepasser les droits d'accès configurés par l'hyperviseur. Il n'est donc pas nécessaire d'hyperviser le code non privilégié. Les micro-noyau, généralement choisis pour leur légèreté, ont donc un second avantage une fois hypervisés : ils réduisent au minimum le surcoût de l'hypervision certifiée.

Le document s'articule autour d'un état de l'art sur les différents systèmes de virtualisa-

tion d'une part, et sur les processus de certification d'autre part. Ensuite, la problématique est détaillée. La contribution principale est ensuite présentée, une proposition de design d'hyperviseur est discutée, et ses performances sont analysées. La conclusion résume ensuite les principaux points, et ouvre sur des perspectives d'optimisation.

# Summary

This thesis presents the design of a secured, software based hypervisor for certification purposes. The highest levels of certification require formal methods, which demonstrate the correctness of a product with regard to its specification using mathematical logic. Proven hardware is not available off-the-shelf. In order to reduce the Trusted Computing Base (TCB) and hence, the amount of specification and proofs to produce, virtualization mechanism are software-made. In addition, this enables virtualization on platforms which do not have virtualization-enabled hardware.

The challenge for achieving this goal is twofold. On one hand, despite an existing documentation, the instruction set to be analysed has tedious corner cases, implementation-dependant behaviour or even worse, undefined behaviour. On the other hand to infer the system behaviors has to be infered given a discrete instruction flow, in order to remain interposed between the guest and the underlying hardware. For achieving this, the guest's machine code is analysed, and sensitive instructions (which threaten confidentiality or integrity) are replaced by traps, which enable arbitration given the actual guest context.

Relying on hypothetically proven processor and memory management unit, only privileged code may bypass the configuration setup by the hypervisor and access the hardware. Thus, analysing unprivileged code is worthless in this case. Micro-kernel design which tends to offload most of the code in userspace, are suitable here. Using that paradigm reduces the overhead induced by certified virtualization.

This document begins with a state-of-the-art on virtualization systems, and certification processes. It is followed the detailed problem statement. Afterward the main contribution is presented. Its design is discussed and its performances evaluated. Finally, the conclusion gives a summary of this work, and future work is suggested.

# Abstract

In computer science, virtualization has been used for decades. At the beginning, it was achieved by operating systems which shared a single machine on multiple processes. Each of those were given a "virtual adress space" of arbitrary size as if it was actually available and dedicated to them. Nowadays when we speak about virtualization, we think about running multiple instances of operating systems on a single machine. This is exactly the same principle as above. In the 90s, this job was mainly achieved using complex pieces of software. After 2000, Intel and AMD included new instructions on their CPU to ease the process of virtualization. Today, this trending topic is also rising on portable devices, such as smartphones. The last ARM processors (ARM v8) now include virtualization mechanisms. But most of the ARM processor in the wild are ARMv7; thus hardware virtualization may not be available.

We present our work on hypervisors for ARM processors. Our aim was to produce the simplest hypervisor possible, in order to formalize its security properties. Thus, we decide not to rely on hardware features:

- Those features are done with microcode, whereas the core instruction set is wired logic. Because of its nature, microcode is more error prone: it is more complex, implies machine states, which makes it harder to verify than boolean functions.

- From a formal proof point of view, we would like to be able to specify the minimum requirements for a processor to actually satisfy our requirements.

- We want to address some processors (armv7 or micro-controllers) where those instructions are not available.

It seems important to unify all those specifications and requirements of the hardware to

improve reusability of this work in each layer: hardware specification, code production (in the compiler's backend) and in the hypervisor design itself.

The first part is a state of the art of virtualization on both x86 and ARM. Certified systems are also aborded. Then, the context of the thesis is presented. Afterwards, two parts of this thesis are presented: first an hypervisor for embedded system that does not rely on hardware virtualization features, and an intensive anlysis on the ARM instructionset analysis. Finally, future work is presented in the conclusion of the document.

Remerciements

—BEGIN PGP SIGNED MESSAGE— Hash: SHA512

Ma vie mon oeuvre Copyright (C) 2016 François SERMAN

This program is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 2 of the License, or (at your option) any later version.

This program is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with this program; if not, write to the Free Software Foundation, Inc., 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301, USA.

N'étant plus à une contradiction près, j'ai décidé de rédiger ces remerciements en français.

Je tiens tout d'abord à remercier la société Prove&Run, et particulièrement Dominique Bolignano, sans qui rien de cette aventure n'aurait été possible. Ensuite, merci à mes rapporteurs Issa Traoré et Gaël Thomas. Je remercie également mes encadrants Gilles Grimaud et Michael Hauspie pour leur suivi et leurs conseils ces dernières années, y compris avant la thèse.

Merci également à vous, lecteurs/lectrices et relectrices/relecteur : Mickey, Asli, Véronique

et Kate. Une mention spéciale à Oana Andreescu, pour sa première relecture rapide, et approfondie. Mon document n'aurait pas atteint ce stade de maturité sans ta relecture. Je t'en remercie sincèrement!

J'adresse également mes plus profonds remerciements à mes collègues Lillois, qui m'ont supporté autant d'années, avec une mention spéciale à mes co-bureaux. Merci également à mes collègues parisiens, particulièrement Vincent, Olivier (mon guide spirituel du standard C), Patrice pour une conversation qui m'a servi de déclic, et à Denis pour sa contribution régulière chez Schwartz.

De façon plus personnelle, je souhaite remercier Damien Riquet pour sa bonne humeur, et ses blagues drôles (il dit qu'il voit pas le rapport). Je voudrais également remercier Pierre Graux, mon seul et unique stagiaire, qui a eu le double plaisir de travailler sur l'hyperviseur, et dans emacs. Merci à Vincent Bénony pour sa contribution au code, que j'intitulerai version 3. Ne reste plus qu'à implémenter une plateforme x86 pour fructifier ce design. Merci également pour la licence d'utilisation pour Hopper<sup>1</sup>.

Enfin, je voudrais remercier ici mes amis pour leurs moqueries, et donc leur soutien. Et pour terminer, merci à ma famille, présente ou absente. Sur un malentendu, on va peut-être quand même réussir à en faire quelque chose.

Si j'ai oublié quelqu'un, merci d'adresser une pull-request.

Ps: the game.

—BEGIN PGP SIGNATURE— Version: GnuPG v2

iQIcBAEBCgAGBQJX3CxIAAoJED4y673idXxPMeUP/iA0l8crfHbfrOgEpPmLi42m M0mecVIBB0xN72xKkJ79hWaqgpc51wZWbA63fhL9iGuIVMb/uSZpS58VOKVWMwFlvXZsfuwI0IzBa1MVsG6QWWyqFX78IYqMqfC2+fG6ziY34+quCxCadenJkvYkb4TvtGgRSxoPjEWRoNdqS4p/i5r5qlKVmKOo0xXu1uM1h3gYL/eht4d3g/sA2lJS2nhLmxg0NmpVz7nJWbxj7zfBCc9wmzZYTSRMDx+6i6YQH2Zec4S2RkRrdjKtF9mFC5jbCPPM2QVb3G5eJm/sB7LtRBtUeJGA5jyynuJAwmD/Pv5lYj30VAOt82Ax/BYXrNuVjkFDRFtGqru2DQGft3O3uPeA01u85a8UZpXZnnFwVugXAgY3Inv4ln2Ytt65+UhCRIsd9TGG5La3tXvB5xuEVSPGVtRvV7s/PaZ0NivV1kERMTKasTpNFbspV/bHfG8A1vvG1PWvjYmr/VUjEtAk0eyu9FUzPkjQdRkMyoLpQRfzD2ovS/oQfStvi1pZ98FM7vZNvL70rFTzoYA8QLk355Tk0pWyyU3UffBZIFe8fjlmWFy/z/D2f6tDe45iKyGtUZ2NBOWKX5X7R7HSUfe0q1Lh7XMNzAPJPwlP8Y9EQyTPJ91Wh3Cf/J8/2IJzxnBbUS7mQdiLhnoiiORniq8W

=4CTb

—END PGP SIGNATURE—

<sup>&</sup>lt;sup>1</sup>https://www.hopperapp.com

# Table of contents

| 1        | Intr | oducti   | ion                                     | 15 |

|----------|------|----------|-----------------------------------------|----|

|          | 1.1  | Conte    | xt                                      | 16 |

|          | 1.2  | Claim    |                                         | 16 |

|          | 1.3  | Docur    | nent structure                          | 17 |

|          |      |          |                                         |    |

| <b>2</b> | Stat | te of tl | he art                                  | 19 |

|          | 2.1  | Lexico   | on                                      | 20 |

|          |      | 2.1.1    | Virtualization or abstraction?          | 20 |

|          |      | 2.1.2    | Example of virtual systems in computing | 21 |

|          |      | 2.1.3    | Example of abstractions in computing    | 22 |

|          | 2.2  | System   | n virtualization mechanisms             | 27 |

|          |      | 2.2.1    | Prologue                                | 27 |

|          |      | 2.2.2    | Software approach                       | 31 |

|          |      | 2.2.3    | Hardware approach                       | 37 |

|   |     | 2.2.4                                     | Hybrid approaches                                                                   | 40 |  |

|---|-----|-------------------------------------------|-------------------------------------------------------------------------------------|----|--|

|   |     | 2.2.5                                     | Summary                                                                             | 42 |  |

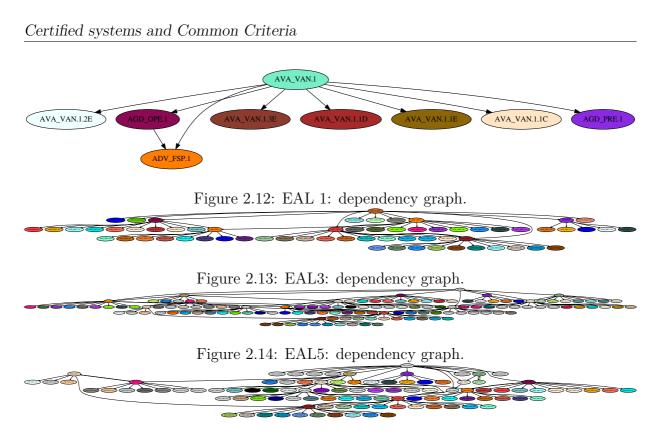

|   | 2.3 | 2.3 Certified systems and Common Criteria |                                                                                     |    |  |

|   |     | 2.3.1                                     | Landscape                                                                           | 43 |  |

|   |     | 2.3.2                                     | Common Criteria                                                                     | 44 |  |

| 3 | Pro | blem s                                    | tatement                                                                            | 55 |  |

|   | 3.1 | Hyper                                     | visors and security                                                                 | 56 |  |

|   |     | 3.1.1                                     | Introduction                                                                        | 56 |  |

|   |     | 3.1.2                                     | How does virtualization instructions enable security? $\ldots$                      | 56 |  |

|   |     | 3.1.3                                     | How do formal methods provide additional security? $\ldots$                         | 58 |  |

|   |     | 3.1.4                                     | Existing hypervisors with security focus                                            | 58 |  |

|   | 3.2 | Softwa                                    | re security and certified products                                                  | 59 |  |

|   |     | 3.2.1                                     | A market requirement                                                                | 59 |  |

|   |     | 3.2.2                                     | Certified products                                                                  | 60 |  |

|   | 3.3 | Certifi                                   | cation's impact on design                                                           | 61 |  |

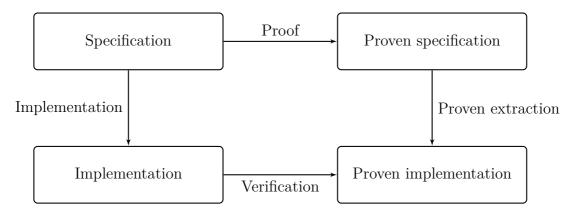

|   |     | 3.3.1                                     | How to gain confidence in software?                                                 | 62 |  |

|   |     | 3.3.2                                     | Issues with end to end proof                                                        | 66 |  |

|   | 3.4 | A new                                     | architecture for embedded hypervisors $\ldots \ldots \ldots \ldots \ldots \ldots$   | 68 |  |

|   |     | 3.4.1                                     | What is to be formalized?                                                           | 68 |  |

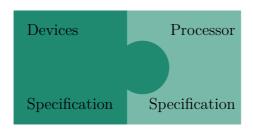

|   |     | 3.4.2                                     | Factorizing formalization: confound ISA and hardware specification                  | 70 |  |

|   |     | 3.4.3                                     | Factorizing the interpreter by executing code directly on the CPU $% \mathcal{A}$ . | 71 |  |

|   | 3.5 | Discus                                    | sion $\ldots$                                                                       | 73 |  |

|   |     |                                           |                                                                                     |    |  |

# 4 Contribution

$\mathbf{5}$

| 4.1                                | Prototype                                          |                                                                                                 |    |  |  |  |

|------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|----|--|--|--|

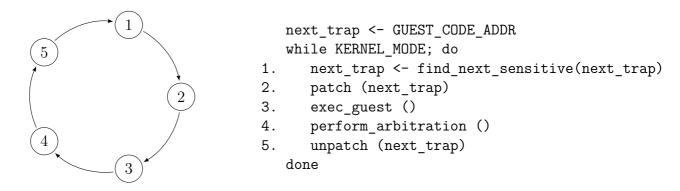

|                                    | 4.1.1                                              | Foreword: general design of the VMM                                                             | 76 |  |  |  |

|                                    | 4.1.2                                              | Design                                                                                          | 76 |  |  |  |

|                                    | 4.1.3                                              | Analysing guest code                                                                            | 77 |  |  |  |

|                                    | 4.1.4                                              | Interrupt handling                                                                              | 81 |  |  |  |

|                                    | 4.1.5                                              | Tracking privileges changes                                                                     | 82 |  |  |  |

|                                    | 4.1.6                                              | Metrics                                                                                         | 83 |  |  |  |

| 4.2                                | Perfor                                             | mance overview                                                                                  | 86 |  |  |  |

|                                    | 4.2.1                                              | Benchmarks                                                                                      | 86 |  |  |  |

|                                    | 4.2.2                                              | Evaluation                                                                                      | 86 |  |  |  |

|                                    | 4.2.3                                              | Results                                                                                         | 86 |  |  |  |

|                                    | 4.2.4                                              | Analysis                                                                                        | 88 |  |  |  |

| 4.3                                | 4.3 Hypervising cost – Micro benchmarks overview   |                                                                                                 |    |  |  |  |

|                                    | 4.3.1                                              | Benchmarks                                                                                      | 90 |  |  |  |

|                                    | 4.3.2                                              | Results                                                                                         | 90 |  |  |  |

|                                    | 4.3.3                                              | Discussion                                                                                      | 90 |  |  |  |

| 4.4                                | Concl                                              | usion $\ldots$ | 92 |  |  |  |

|                                    |                                                    |                                                                                                 |    |  |  |  |

| In depth implementation details 93 |                                                    |                                                                                                 |    |  |  |  |

| 5.1                                | Gener                                              | al concepts about the ARM architecture and instruction set $\ldots$                             | 94 |  |  |  |

|                                    | 5.1.1                                              | The ARM architecture overview                                                                   | 94 |  |  |  |

|                                    | 5.1.2 The ARM instruction set families             |                                                                                                 |    |  |  |  |

|                                    | 5.1.3 The ARM instruction set encoding             |                                                                                                 |    |  |  |  |

| 5.2                                | Analyser's implementation: the instruction scanner |                                                                                                 |    |  |  |  |

|                                  |     | 5.2.1                     | Instruction behaviors                                                                                  | 100 |  |

|----------------------------------|-----|---------------------------|--------------------------------------------------------------------------------------------------------|-----|--|

|                                  |     | 5.2.2                     | Instruction matching                                                                                   | 100 |  |

| 5.3 Arbitration's implementation |     |                           |                                                                                                        | 104 |  |

|                                  |     | 5.3.1                     | Trap to the hypervisor: the callback mechanism $\ldots \ldots \ldots \ldots$                           | 104 |  |

|                                  |     | 5.3.2                     | Tracking indirect branches                                                                             | 106 |  |

|                                  |     | 5.3.3                     | Condition validation                                                                                   | 106 |  |

|                                  |     | 5.3.4                     | Conditional blocks                                                                                     | 106 |  |

|                                  |     | 5.3.5                     | Summary                                                                                                | 107 |  |

|                                  | 5.4 | ple on a simple guest     | 107                                                                                                    |     |  |

|                                  |     | 5.4.1                     | description                                                                                            | 107 |  |

|                                  | 5.5 | Summ                      | ary                                                                                                    | 107 |  |

| 6                                | Con | onclusion and future work |                                                                                                        |     |  |

|                                  | 6.1 | Synthe                    | esis                                                                                                   | 112 |  |

|                                  | 6.2 | Future                    | e work                                                                                                 | 113 |  |

|                                  |     | 6.2.1                     | Increasing the hypervisor performances                                                                 | 113 |  |

|                                  |     | 6.2.2                     | Reducing the context-switch cost                                                                       | 113 |  |

|                                  |     | 6.2.3                     | Expectations and for<br>eseeable issues with a formal verification $% \left( {{{\bf{x}}_{i}}} \right)$ | 114 |  |

|                                  |     | 6.2.4                     | Security assessment                                                                                    | 116 |  |

|                                  | 6.3 | Person                    | al feedback                                                                                            | 118 |  |

# chapter 1

# Introduction

If you know the system well enough, you can do things that aren't supposed to be possible

Linus Torvalds

# 1.1 Context

My thesis was funded by Prove&Run SAS. This company was created in 2009 by Dominique Bolignano. It aims to increase security using formally proven solutions. Prove&Run has developed a toolchain to edit and prove computer programs written in Smart, their modeling language. Smart is a strongly typed, functional language. After writing Smart source-code, Prove&Run's toolchain will generate C code, which can be compiled using traditional tools such as GCC. This language was successfully used to write a specialized and secured operating system for embedded devices. It is now used to create a Trusted Execution Environement (TEE), and a hypervisor.

The academic side of my thesis was done in Lille, in 2XS team. 2XS is a member of CRIStAL, the research center in computer sciences, signal processing, and automation of the University of Lille. 2XS stands for eXtra Small, eXtra Safe. This team was created after a fork from POPS, a larger team which was involved in sensor networks and system design. 2XS has been involved in system design, while FUN has kept the WSN part. In 2XS, several axis are studied, but they often involve two parties, and thus co-design.

Between hardware and system first. Because of the embedded systems constraints, developers have to know exactly on which target their code is supposed to run. A second axis of that part, is the energy consumption. One of the short-term goals is to be able to produce an energy consumption cartography of individual blocks of code, and to make this information actually usable by a developer.

Between OS developers and Proof developers. A new topic is arising in 2XS: producing formal proofs on systems. A subset of the team is currently writing a mesovisor, which provides isolation between partitions. This mesovisor can be used to make a hypervisor, to run several systems in one single machine. After a proof of concept in C and a Haskell model, it was decided to write proofs directly in Coq, and to extract Coq into C language, in order to make it actually run.

For three years, I've been in 2XS 4 days a week, and one day at Prove&Run. During the fourth year, I have been at 2XS 2 days a week for six months.

# 1.2 Claim

This thesis presents a novel design to implement a hypervisor for ARM processors, suitable for the highest levels of certifications. Such levels require both a model of the product, and an implementation. Moreover, a formal proof of correctness between the model and the implementation is also required. Because no proofs on the hardware are available, we claim that the hardware mechanisms should be limited to the minimum. In particular, virtualization extensions are black boxes, which cannot be verified. This thesis presents a proof of concept of a minimal hypervisor that limits the hardware requirements to the minimum. Only the ARM core-instruction set is used, and the CP15 co-processor for the MMU<sup>1</sup>. We believe that this simple design can ease the evaluation of such a product. With a proper guest, this hypervisor can achieve less than 20% overhead.

# **1.3** Document structure

Here is the outline of the document: First comes the state of the art. This chapter covers theoretical background of virtualization and existing solutions. Then comes a presentation of the common-criteria, an internationally recognized consortium, which evaluates the security of IT products. In the second part comes the problem statement. A tour will be made on the landscape of certified products, and their issues. Afterward I will insist on the importance of keeping a connection between each layers in the stack: hardware, compiler and sofware. The third part is an in-depth description of the hypervisor. This section also presents the results on several benchmarks, and comment those results. Finally a conclusion will sumarize the document, and perspectives will be given, mainly on how to optimize performances. I will finish with a personal feedback on those four years.

$<sup>^1\</sup>mathrm{Because}$  a MMU has been successfully evaluated at the highest evaluation level, we decided that we could rely on such features

# chapter 2

# State of the art

The problem with engineers is that they tend to cheat in order to get results. The problem with mathematicians is that they tend to work on toy problems in order to get results. The problem with program verifiers is that they tend to cheat at toy problems in order to get results.

science jokes, ver 6.7 mar 1, 1995

http://lithops.as.arizona.edu/~jill/humor.text

## Contents

| <b>2.1</b> | Lexicon                               | <b>20</b> |

|------------|---------------------------------------|-----------|

| 2.2        | System virtualization mechanisms      | <b>27</b> |

| <b>2.3</b> | Certified systems and Common Criteria | 43        |

# 2.1 Lexicon

Because of trending topics on cloud computing, virtualization, hypervisors and so on, we will provide some definitions here. We begin with real life comparisons to give an intuition on two key concepts: virtualization and abstraction. Afterwards, we will illustrate these two concepts with computing-related examples.

# 2.1.1 Virtualization or abstraction?

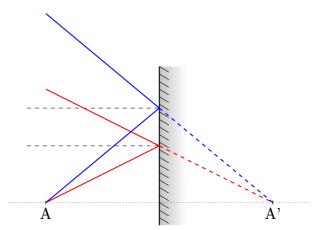

In optics, a virtual image refers to an image of an actual object which appears to be located at the point of apparent divergence. In practice, the rays never converge, which is why a virtual image cannot be projected on screen (see Fig 2.1). A virtual object is a representation of an actual object that could exist, but does not.

Figure 2.1: A is a source sending light through a mirror. All the rays seem to come from A', the virtual image of A. Thus, it seems that A is located behind the mirror, when in fact it is in front of it.

In real life, talking about television is an abstraction. Everybody (almost) has an object called television, which can represent slightly different objects. It is a screen with speakers that displays animated pictures and sounds. When talking about a television, we refer to it has its function, not what it is. For instance, no information is given on its size, resolution, display technology etc...

**Definition 1** (Virtualization). Virtualizing an object consists of creating a virtual version of that object. A virtual object does not physically exist as such, but is made by software to appear to do so.

**Definition 2** (Abstraction). Abstraction comes from the latin verb "abstrahere" which means "draw away". An abstraction considers something as a general quality or characteristic, apart from concrete realities, specific objects, or actual instances.

# 2.1.2 Example of virtual systems in computing

Computer science makes a heavy use of abstractions, and virtualization. The limit of those concepts is sometimes fuzzy, but it often corresponds to links between different layers. The following sections illustrate those concepts applied to computer hardware, and more specifically memory and microprocessor.

#### 2.1.2.1 Virtual memory

A common usage for virtualization in computing is **virtual memory**. Tanenbaum [1] provides an overview of virtual memory. The basic idea behind virtual memory is that combined size of program, data and stack may exceed the amount of physical memory available. The operating system keeps the parts of the program that are currently in use in the main memory, and the rest on disk. This mechanism is called swapping.

Virtual memory also allows multiprogramming, that is multiple processes running at once. Of course, if only one CPU is available, only one process will run at a time. The scheduler will implement time sharing on the CPU, to make users feel like several processes run concurrently.

Another issue tackled by virtual memory is relocation. When compiling a program, no information are provided to the linker regarding usable addresses. Additionally, programs shoud run on any system without memory restriction (size or available address space). To achieve that, virtual addresses are used. Processes manipulate virtual addresses, which are not the actual addresses where data is physically stored. The latter are called physical addresses. The operating system ensures that the memory management system is configured accordingly so that virtual addresses are mapped on the physical addresses associated to the running process. Each process is free to use any virtual address, as long as there is no conflict in physical addresses<sup>1</sup>. The physical address conflict or swapping (in case of memory exhaustion) is handled by the operating system.

#### 2.1.2.2 Virtual CPU

Another example is **virtual CPU**. There are several CPU emulators: BOCHS [2] or QEMU [3], Valgrind [4], EM86 [5]. I will focus only on QEMU and BOCHS, which are the most spread emulators.

According to BOCHS' description, "BOCHS is a highly portable open source IA-32 (x86) PC emulator written in C++, that runs on most popular platforms. It includes emulation of the Intel x86 CPU, common I/O devices, and a custom BIOS." Basically, the code mainly consists of a large decoding-loop which models the fetch-decode-execute actions of

<sup>&</sup>lt;sup>1</sup>This can be a way to implement efficient shared memory though.

the CPU [6].

"QEMU is a FAST! processor emulator using a portable dynamic translator." [7] . It uses dynamic translation to native code for reasonable speed. When it first encounters a piece of code, QEMUconverts it to the host instruction set. Usually dynamic translators are very complicated and highly CPU dependent. QEMUuses some tricks which make it relatively easily portable and simple while achieving good performances [8].

Despite the obvious design differences (BOCHS beeing static based and QEMU dynamic), they both are an exact replica of the emulated CPU. That is, emulated code cannot make the difference between native on-cpu execution and an emulated one.

#### 2.1.2.3 The processes case

Another example is **processes** [9]. Processes are fundamental for multiprogramming systems (also known as multitask) [10]. They are the objects manipulated by the scheduler to implement context-switching. A process is an instance of a computer program being executed. It contains an image of the associated program, and a state of the underlying hardware:

- virtual interrupts (signals);

- virtual memory;

- virtual CPU (general purpose and status registers);

- hardware access through software interruptions.

Accessing hardware through interruptions characterizes it in term of features, not as a specified piece of hardware. For instance, performing a *write* syscall makes no difference whether the data will be written on a mechanical hard drive or on a USB flash drive. This turns the process into an abstraction of the hardware rather than a virtualized representation.

**Remark.** virtual addresses can also be seen as an abstraction. On x86, PAE paging translates 32-bit linear addresses to 52-bit physical addresses [11].

# 2.1.3 Example of abstractions in computing

We have seen that the limit between abstraction and virtualization can be thin. In this section, we will illustrate the use of abstractions in well known areas of computing.

## 2.1.3.1 TCP/IP

We use TCP over IP on a daily basis for many different usages like browsing internet, sending emails, synchronize agendas etc... TCP is a reliable transport protocol, built on top of IP, the network layer in the OSI stack (ISO/IEC 7498-1). It provides an end-to-end service to applications running on end hosts. If you send a message over TCP, it will eventually be delivered without being altered. IP on the other hand, provides an unreliable datagram service and must be implemented by all systems addressable on the Internet. TCP deals with problems such as packet loss, duplication, and reordering that are not detected nor corrected by the IP layer. It provides a reliable flow of data between two hosts. It is concerned with things such as dividing the data passed to it from the application into appropriately sized chunks for the network layer below, acknowledging received packets, and setting timeouts to ensure that the other end acknowledges packets that are sent, and because this reliable flow of data is provided by the transport layer, the application layer can ignore all these details [12].

TCP is what computer scientists like to call an abstraction: a simplification of something much more complicated that is going on under the covers [13]. It lets the user communicate with remote or local nodes without handling complex problems such as packets fragmentation, retransmission, reordering etc... Hence, TCP provides an abstraction for a reliable communication channel.

#### 2.1.3.2 Operating systems

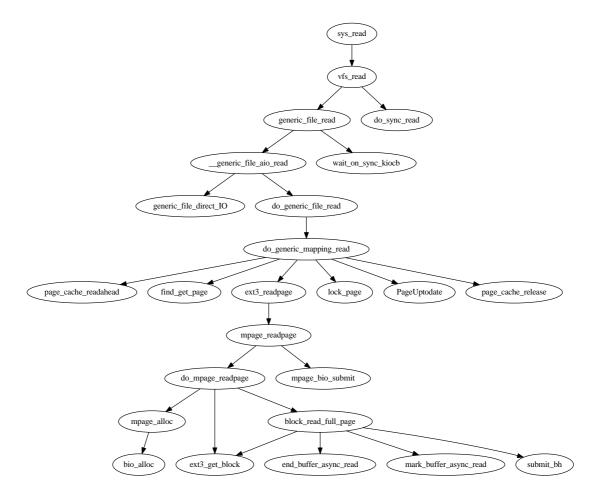

Operating systems can be depicted by two unrelated functions. Namely, extending the machine and managing resources [1]. The latter is not relevant for us now, since it only ensures (fair if possible) sharing of resources among different processes. The former, on the other hand is precisely an abstraction as defined by Def. 2. Fig. 2.2 illustrates a command run in an operating system. It looks very simple and straightforward. In fact, the operating system executes many operations to perform this simple task, as shown in Fig 2.3.

### Code

```

$ cat /etc/passwd

root:x:0:0:root:/root:/bin/bash

```

• • •

Figure 2.2: Reading the /etc/passwd file from command line

In this shell session, the user asks the system to display the content of the file /etc/passwd. The filename itself is an abstraction which exposes complex file layouts under a conveniant,

human-readable file hierarchy. The user can browse this hierarchy using a path from the root item to the file separating each node from another with a delimiter. In fact, most filesystems address files using *inode numbers*. When typing this command, several operations happen: the current shell will fork to create a new child process, then exec to replace the current (child) shell process by cat, with the parameter /etc/passwd. Cat will then open (2) /etc/passwd, read (2) its content, and write (2) it back on its standard output, and finally close (2) the file. That abstraction is provided by processes, as claimed in 2.1.2.3 (p 22). The operating system's abstraction is hidden behind the read implementation. For this example, we assume that /etc/passwd is actually stored on disk (and not on an NFS share for instance). As shown in Figure 2.3, there are quite many functions called by sys\_read. The kernel provides an abstraction of the underlying filsystem (so that read can work on every filesystem). The common part is handled by the VFS layer. Afterwards, the VFS deals with memory pages, and constructs bio which are gathered in requests. Later on, those requests are submitted to the disk. Disk specificities (cache size, buffer size, mechanical or flash-based) are handled by lower level code.

Figure 2.3: Call trace of sys\_read inside the linux kernel.

#### 2.1.3.3 Java Virtual Machine

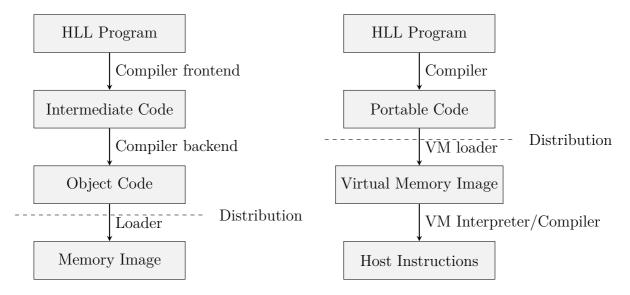

Java is a popular programming language which uses an extra layer in form of JVM (Java Virtual Machine), which makes it platform independent. The developer writes .java code compiled to .class files, which will be executed on top of the JVM. The JVM performs the translation from byte-code to the host machine's language on the fly [14]. Because it runs on different platforms (from PDA to servers), Sun Microsystems has promoted Java with the famous slogan: "Write Once, Run Anywhere" [15]. Figure 2.4 depicts the differences between traditional platform dependent executable, and High-Level Language VM (HLL)  $\hat{a}$  la java [16].

Figure 2.4: On the left, a conventional system where platform-dependent object code is distributed; on the right side a HLL VM environment where portable intermediate code is executed by a platform-dependent virtual machine.

According to [17], the Java Virtual Machine is called "virtual" because it is an abstract computer defined by a specification [18]. The Java Virtual Machine is an abstract computing machine. Like a real computing machine, it has an instruction set and manipulates various memory areas at run time. In particular, it defines data types (which may not exist on the underlying hardware) and instructions involving higher level objects, such as *invokespecial*. Thus, besides its name, JVM is rather an abstraction.

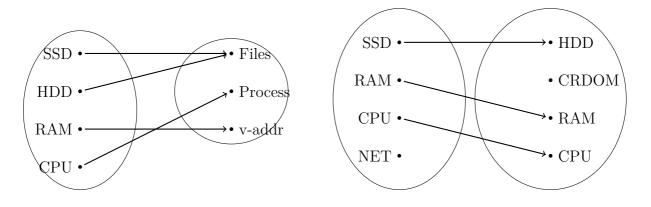

## 2.1.3.4 Conclusion

Mathematical functions can be surjective (every element of the codomain is mapped to by at least one element of the domain), injective (every element of the codomain is mapped to by at most one element of the domain) or bijective (every element of the codomain is mapped to by exactly one element of the domain). With regard to these definitions, the abstraction function would be surjective: the abstraction is a subset of the actual hardware. In the contrary, the virtualization function would be injective: virtualized domain is a superset of the hardware.

# 2.2 System virtualization mechanisms

Because cloud solutions are so widely spread, we use virtualization every day : either using software as a service (SAAS) such as Gmail, Dropbox or Netflix, or using the platform as a service (PAAS) like Amazon EC2 or Microsoft Azure. Cloud computing is just a marketing word which refers to on-demand delivery of IT resources and applications via the Internet with pay-as-you-go pricing<sup>2</sup>. However, virtualization is not a new concept in computing. In 1973, Robert P. Goldberg and Gerald J. Popek published the first articles on virtualization, which are still used to classify virtualization solutions.

In this chapter, we present an overview of virtualization, and its fundamental concepts. Both Intel and ARM will be described to have a concrete application of theoretical concepts. Afterward, we present the common criteria as a target for a security evaluation.

# 2.2.1 Prologue

## 2.2.1.1 General definitions

Nowadays, virtualization is a key concept in computer science, and let us build large and complex systems. In particular, Virtual Machine Monitor uses virtualization to present the illusion of several virtual machines (VMs), each running a separate operating system instance. An Hypervisor (or Virtual Machine Monitor) is a piece of software or hardware that creates and runs virtual machines. Hypervisors are traditionally classified into two categories after Goldberg's thesis [19]:

- **Type 1:** Type 1 hypervisors run directly on the host's hardware. To provide security (with regard to Confidentiality / Integrity / Availability), they must control all accesses on the hardware. This tedious task is usually performed by commodity kernel. *e.g.*: Xen [20], Hyper-V [21], ESX Server [22].

- **Type 2:** Type 2 are the most widely used hypervisors. They rely on an existing operating system (Host OS) and only need to implement virtualization mechanism. In particular, all the hardware initialization, sharing and arbitration are already performed by the Host OS. *e.g.*: KVM [23], Qemu [8], Bhyve [24], VirtualBox [25].

In their now famous paper "Formal Requirements for Virtualizable Third Generation Architectures" [26], Popek and Goldberg have presented requirements and definitions for

<sup>&</sup>lt;sup>2</sup>Courtesy to Amazon (https://aws.amazon.com/what-is-cloud-computing/)

|         |          |         | U       |          |         |

|---------|----------|---------|---------|----------|---------|

| Guest 1 | Guest 2  | Guest 3 |         |          |         |

|         | OS       |         | Guest 1 | Guest 2  | Guest 3 |

|         | VMM      |         | OS      |          | VMM     |

|         | Hardware |         |         | Hardware |         |

System virtualization mechanisms

Figure 2.5: Type 1 (left) hypervisors are bare-metal software. They have a direct access to the hardware. In contrast, Type 2 (right) rely on an existing operating system.

efficient virtualization. First of all, they define a machine model defined by a processor, a memory, an instruction set, and general purpose registers. The state of such a machine can be represented by the following:

$S = \langle E, M, P, R \rangle$

where:

**E** is an executable storage ; a conventional word addressed memory of fixed size. **M** is the CPU mode (Supervisor and User).

**P** is the program counter which acts as an index into E.

${\bf R}\,$  is a set of registers.

The ISA is classified into 3 groups:

#### **Privileged instructions:**

they can only run in supervisor mode. In user mode, they trap.

Control sensitive instructions:

they attempt to change the configuration of resources in the system.

## Behavior sensitive instructions:

their results depend on the configuration of resources.

A trap can be seen as an uncatchable error thrown by the hardware. This restores control to the hypervisor, which can analyse the origin of the trap. Traps can occur when a privileged instruction is executed in user mode, or when an invalid memory access is performed.

The hypervisor should exibit three essential characteristics. First, the VMM provides an environment for programs which is essentially identical to the original machine; secondly, programs, that run in this environment, show at worst only minor decreases in speed; and last, the VMM is in complete control of system resources. **Property 1** (Equivalence/Fidelity). Any program K executing performs in a manner indistinguishable from the case when the VMM did not exist and K had whatever freedom of access to privileged instructions that the programmer had intended.

This means that the virtualization layer should be invisible to the guest. The guest's behaviour should be the same as if it had been run on the original machine directly, with the possible exception of differences caused by the availability of system resources and differences caused by timing dependencies.

**Property 2** (Efficiency). A statistically dominant subset of the virtual processor's instructions has to be executed directly by the real processor, with no software intervention by the VMM.

In particular, all innocuous instructions are executed by the hardware directly, and do not trap.

**Property 3** (Resource control). It must be impossible for that arbitrary program to affect the system resources. The VMM is said to have complete control of these resources if (1) it is not possible for a program running under it in the created environment to access any resource not explicitly allocated to it, and (2) it is possible under certain circumstances for the VMM to regain control of resources already allocated.

With these concepts defined, Popek and Goldberk have stated a theorem that provides a sufficient condition to guarantee the virtualizability of an instruction set.

**Theorem 1.** A virtual machine monitor may be constructed if the set of sensitive instructions for that computer is a subset of the set of privileged instructions (sic).

This theorem states that each instruction that could affect the correct functioning of the VMM (sensitive instructions) always traps and passes control to the VMM. It is the basis of the trap-and-emulate virtualization principle, which lets every innocuous instruction run natively, and whenever a sensitive instruction arrives, the VMM traps, and emulates that instruction instead of executing it on the hardware.

#### 2.2.1.2 x86 virtualizability

According to [27], there are seventeen instructions in x86 that are sensitive but not privileged.

- SGDT, SIDT, SLDT (a GP is raised in 64bits if CR4.UMIP = 1 and CPL > 0)

- SMSW leaks PE / MP / EM / TS / ET / NE flags in bits 0-5 from CR0

- PUSHF and POPF (reverse each other's operation) PUSHF pushes lower 16 bits from the EFLAGS onto the stack and decrements the stack pointer by 2. EFLAGS contains flags that control the operating mode and state of the processor such as TF (Trap, to debug) / IF (Interrupt enable) / DF (Direction of string instructions) / and so on. Note that if an instruction is executed without enough privilege, no exception is generated, but EFLAGS are not changed either.

- LAR, LSL, VERR, VERW. LAR loads access rights from a segment descriptor into a GPR. LSL instruction loads the unscrambled segment limit from the segment descriptor into a GPR. VERR and VERW verify whether or not a code or data segment is readable or writable from the current privilege level.

- POP / PUSH (A process that thinks it is running in CPL 0 pushes the CS register to the stack. It then examines the contents of the CS register on the stack to check its CPL. Upon finding that its CPL is not 0, the process may halt.)

- CALL, JMP, INT n, RET/IRET/IRETD. Task switches and far calls to different privilege levels cause problems because they involve the CPL, DPL and RPL. A task uses a different stack for every privilege level. Therefore, when a far call is made to another privilege level, the processor switches to a stack corresponding to the new privilege level of the called procedure. Since VM normally operates at user level (CPL 3), these checks will not work correctly when a VMOS tries to access call gates or task gates at CPL 0.

- STR (This instruction prevents virtualization because it allows a task to examine its requested privilege level (RPL). This is a problem because a VM does not execute at the highest CPL or RPL (RPL = 0), but at RPL = 3. However, most operating systems assume that they are operating at the highest privilege level and that they can access any segment descriptor. Therefore, if a VM, running at a CPL and RPL of 3, uses STR to store the contents of the task register and then examines the information, it will find that it is not running at the expected privilege level.)

- MOVE (CS and SS both contain CPL in bits 0 and 1, thus a task could store the cs or ss in GPR and could examine the content of that register to find that it is not operating at the expected privileged level.

# Remark

In 64 bits:

- a GP is raised in 64 bits if CR4.UMIP = 1 and CPL > 0 when performing SGDT SIDT SLDT

- \*GDT entries are in virtual memory. Thus, MMU may be configured to raise faults on illegal access.

Consequently x86 is not virtualizable in the sense of Goldberg and Popek.

#### 2.2.1.3 ARM virtualizability

In this section, we do not consider the ARM virtualization extensions brought by ARMv8. This topic will be discussed in section 2.2.3.2 (p 38).

The ARM instruction set is not virtualizable. Indeed, several instructions are control or configuration sensitive, but not privileged. For instance, the following instruction (Fig. 2.6) will read the CPSR. This instruction is behaviour sensitive, but will not trap in user mode.

| Code                                                      |

|-----------------------------------------------------------|

| mrs r0, cpsr                                              |

| Figure 2.6: Reading CPSR into R0 in user mode won't trap. |

In [28, 29, 30], the authors reference 60 instructions which break Popek and Goldbergs requirements.

- instructions accessing coprocessor's registers (reading or writing);

- instructions modifying the processor mode;

- instructions modifying the processor state (CPSR);

- instructions modifying the program counter.

Sometimes, those instructions are both control-sensitive and configuration-sensitive. This shows that ARM instruction set is not virtualizable.

# 2.2.2 Software approach

We have seen that both ARM and x86 instruction-set are not virtualizable out of the box. To address this issue, developers have created software which is able to analyse programs, and detect problematic instructions. Several approaches are possible, each of them having advantages and disavantages. In this section, we describe classical solutions to address software virtualization.

## 2.2.2.1 Software interpretation

A software interpreter is a program that reads an instruction of the source architecture one at a time, performing each operation in turn on a software-maintained version of that architecture state. Figure 2.7 depicts a pseudo code of a minimal CPU emulator. Basically, a program is stored in Memory. A program counter PC is used to track the progression. For each instruction (OpCode), the emulator will perform an operation to emulate the expected behaviour. This snippet also takes a countdown before interrupt events. Such events can arise between each instructions.

First generation interpreters would simply interpret each source instruction as needed. These tend to exhibit poor performance due to the interpretation overhead.

The second generation interpreters dynamically translate source instructions into target instructions one at a time, caching the translations for later use.

The third generation interpreters, improved upon the performance of second generation, dynamically translate entire blocks of source instruction at a time [31].

### 2.2.2.2 Static recompilation

A binary recompiler is a software system that takes executable binaries as input, analyzes their structure, applies transformations and optimizations, and outputs new optimized executable binaries. Translated code reproduces faithfully the calling standard, implicit state, instruction side effects, branching flow, and other artifacts of the old machine. Translators can be classified as follows [32]:

- **Bounded translation systems:** all the instructions of the old program must exist at translation time and must be found and translated to new instructions.

- **Open-ended translation systems:** part of codes may be discovered, created or modified at execution time.

Sometimes binary translation is not just simply replacing op-codes and adjusting the order of the operands. Some factors must be considered when doing binary translation [33]:

#### Distinguish code and data

In assembly program, one can insert arbitrary data. In order to disassemble effectively, we have to be able to detect whether byte chunks represent code or data. Figure 2.8 depicts a real-life sample which fools the decompiler. The latter makes no difference between code and data, which leads to decode andeq and undefined instructions instead of plain data. [34] proposes an algorithm to tackle this issue:

- 1. taint each byte as data chunks

- 2. replace the data taint with code taint for each known reference (Interrupt table for instance)

- 3. calculate the address referenced for each previously untainted entry

- 4. mark that entry as data

- 5. based on the instruction, mark recursively other locations as instructions: BL (absolute) + function return jump target and next addr as instruction

(mind the SP alteration)

**B** (absolute) jump target as instruction

Indirect branch do nothing

Otherwise (not modifying control flow) mark the next address as an instruction

- **Branching** The number of instructions in the target might differ from the one in the source binary. This means that the location of the routines in the translated code could be at different addresses than the original code. Because of this, it will likely be necessary to adjust the target address of some branch instructions. This is fairly easy for statically determined branches, but it can become tedious for dynamically determined branches. In the latter case, the target of the branch cannot generally be determined at translation time.

- **Pipelining** Pipelining creates data dependencies. Code produced for the target machine must not violate these constraints even though the order or the number of instructions may be changed. This also causes issues when branches destinations are PC relative, or for any instruction breaking the sequential execution of the code.

- **Self modifying code** Self-modifying code is usually specific to the machine for which the program was targeted. This makes it difficult to write a binary translator which can handle it. Finding self-modifying code section is also difficult.

#### 2.2.2.3 Dynamic recompilation

The alternative to static recompilation is dynamic recompilation. Dynamic recompilation is theoretically slower than static recompilation for two main reasons:

- 1. translation must be performed at runtime. Translation must be as fast as possible.

- 2. Because of the previous reason, only a limited time can be used for optimization.

Dynamic recompilation has advantages over the static approach. In particular, it can emulate all the code in a given machine. It works like an interpreter emulating the code, and only decodes instructions that are actually executed. This helps to handle indirect jumps but also self-modifying code. Fig. 2.9 presents an implementation for dynamic recompilation:

- for efficiency, a cache is built indexed by addresses;

- for each instruction, the cache is consulted: if it misses, the cache is filed with a program supposed to emulate the current instruction;

- this program is executed.

# 2.2.2.4 Summary

This section gave an overview of the software technique available to perform software virtualization. We have described interpreters, static recompilers and dynamic recompilers.

The following table summarizes the advantages and disavantages of each approach:

- interpreters are platform independent and can faithfully reproduce the behavior of self-modifying programs, or programs branching to data, or using relative branches (such as jmp r4 ).

- Static recompilation provides good performances but may not be feasible.

- Dynamic recompilation is a trade-off between interpreters and static translators.

The next section will describe hardware facilities to write efficient hypervisors.

| Criterion              | Interpreter           | Static recompilation   | Dynamic recompilation |

|------------------------|-----------------------|------------------------|-----------------------|

| Required computation   | high                  | negligible (offcard)   | high                  |

| Overhead at runtime    | $\operatorname{high}$ | limited                | high                  |

| Repetitive executions  | high                  | good                   | good (cache)          |

| Platform independence  | good                  | requires a new backend | limited               |

| Possible optimizations | few                   | highly optimizable     | slightly optimizable  |

Table 2.1: Summary of technique and performances applied to software analysis.

```

Code

Counter=InterruptPeriod;

PC=InitialPC;

void emulate(instr_t opcode)

{

switch(opcode)

{

case OpCode1:

handleOpCode1(opcode);

break;

case OpCode2:

. . .

}

}

. . .

for(;;)

{

OpCode=Memory[PC++];

Counter-=Cycles[OpCode];

emulate(OpCode);

if(Counter<=0)</pre>

{

/* Check for interrupts and do other */

/* cyclic tasks here

*/

. . .

Counter+=InterruptPeriod;

if(ExitRequired) break;

}

}

```

Figure 2.7: Minimal CPU emulator : http://fms.komkon.org/EMUL8/HOWTO.html

| Code                                                                                                                                                                                 |          |                                                                    |                                 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------|---------------------------------|--|--|--|--|

| 00018280 <user_task>:</user_task>                                                                                                                                                    |          |                                                                    |                                 |  |  |  |  |

| 18280:                                                                                                                                                                               | e59f301c | ldr                                                                | r3, [pc, #28] ; 182a4           |  |  |  |  |

| 18284:                                                                                                                                                                               | e59f201c | ldr                                                                | r2, [pc, #28] ; 182a8           |  |  |  |  |

| 18288:                                                                                                                                                                               | e5832000 | str                                                                | r2, [r3]                        |  |  |  |  |

| 1828c:                                                                                                                                                                               | ef000000 | svc                                                                | 0x0000000                       |  |  |  |  |

| 18290:                                                                                                                                                                               | e59f2014 | ldr                                                                | r2, [pc, #20] ; 182ac           |  |  |  |  |

| 18294:                                                                                                                                                                               | e5832000 | str                                                                | r2, [r3]                        |  |  |  |  |

| 18298:                                                                                                                                                                               | ef000000 | svc                                                                | 0x00000000                      |  |  |  |  |

| 1829c:                                                                                                                                                                               | ef000003 | svc                                                                | 0x0000003                       |  |  |  |  |

| 182a0:                                                                                                                                                                               | e12fff1e | bx                                                                 | lr                              |  |  |  |  |

| 182a4:                                                                                                                                                                               | 000183b0 | ; <unde< th=""><th>EFINED&gt; instruction: 0x000183b0</th></unde<> | EFINED> instruction: 0x000183b0 |  |  |  |  |

| 182a8:                                                                                                                                                                               | 00018340 | andeq                                                              | r8, r1, r0, asr #6              |  |  |  |  |

| 182ac:                                                                                                                                                                               | 00018360 | andeq                                                              | r8, r1, r0, ror #6              |  |  |  |  |

| Figure 2.8: A real-life code sample: "instructions" located at 0x182a4 0x182a8 0x182ac are <i>not</i> actual instructions, but data used for (resp.) ldr at 0x18280 0x18284 0x18290. |          |                                                                    |                                 |  |  |  |  |

```

Code

```

```

while (!end)

{

translatedCode = ReadTranslationCache(PC);

if (translatedCode == NULL)

translatedCode = translate(PC)

(*translatedCode)();

}

```

Figure 2.9: Pure dynamic binary translation algorithm

#### 2.2.3 Hardware approach

To help writing efficient hypervisors, hardware designers have extended their architectures to make them "virtualization aware". In this section, we consider x86\_64 and ARMv7 with virtualization extensions [35].

#### 2.2.3.1 x86 architecture

Intel and AMD implement the same features, but are called differently. Basically, the required features are the following:

- **Provide a "hypervisor" privilege level:** Before hardware virtualization support, guest operating systems were launched deprivileged, which means having a privilege level greater than 0, so that the most privileged instructions were not executable by the guest. As we have described, some instructions were not properly handled by the hardware. Although they are mutually incompatible, both Intel VT-x (codenamed "Vanderpool") and AMD-V (codenamed "Pacifica") create a new "Ring -1" so that a guest operating system can run Ring 0 operations natively without affecting other guests or the host OS.

- Hardware Page Table Virtualization: provides a hardware assist to memory virtualization, which includes the partitioning and allocation of physical memory among VMs. Memory virtualization causes VMs to see a contiguous address space, which is not actually contiguous within the underlying physical memory. The guest OS stores the mapping between virtual and physical memory addresses in page tables.

Because the guest OSs do not have native direct access to physical system memory, the VMM must perform another level of memory virtualization in order to accommodate multiple VMs simultaneously. That is, mapping must be performed within the VMM, between the physical memory and the page tables in the guest OSs. In order to accelerate this additional layer of memory virtualization, both Intel and AMD have announced technologies to provide a hardware assist. Intel's is called Extended Page Tables (EPT), and AMD's is called Nested Page Tables (NPT). These two technologies are very similar at the conceptual level.

Interrupt Virtualization: the IA-32 architecture provides a mechanism for masking external interrupts, preventing their delivery when the OS is not ready for them. A VMM will likely manage external interrupts and deny the guest operating system the ability to control interrupt masking. This will lead to frequent mask/unmask interrupts. Moreover, intercepting every guest attempt could significantly affect system performance. Even though, challenge remains when a VMM has a "virtual interrupt" to deliver to a guest. Intel VT-d Posted-Interrupts and AMD Advanced Virtual Interrupt Controller (AVIC) provide an effective hardware mechanism which causes no overhead for interrupt handling.

#### 2.2.3.2 The ARM architecture

The ARM architecture exists in multiple revision. The latest revision is version 8. Fig. 2.10 illustrates the privileges layers of this new architecture. The architecture is separated in three profiles (where v8 stands for version 8):

the ARMv8-A "Application profile": suitable for high performance markets; the ARMv8-R "Real-time profile": suitable for embedded applications;

the ARMv8-M "Microcontroller profile": suitable for embedded and IoT applications.

These architectures are used by different processors; for example the Cortex-A7 processor implements the ARMv7-A architecture, and the Cortex-A35 provides a full ARMv8-A support. The different within a CPU families are features, such as frequency, or number of cores.

| EL0 | App1                               | Truste | ed App1        |      |  |  |  |

|-----|------------------------------------|--------|----------------|------|--|--|--|

| EL1 | Guest Operat                       | Secu   | red OS         |      |  |  |  |

| EL2 | Virtual Machine Monitor Trust Zone |        |                |      |  |  |  |

| EL3 |                                    | (      | TrustZone) Mon | itor |  |  |  |

Figure 2.10: The ARM architecture's privileges levels with virtualization and trust zone features.

ARM processors may include TrustZone, a hardware facility which provides a dedicated execution context for a secure operating system (secure OS) next to a normal operating system. The instruction Secure Monitor Call (SMC) bridges the secure and normal modes. TrustZone enables protection of memory and peripherals. Applications running in secured world can access non-secure world, whereas the opposite is impossible. It offers a secure and easy-to-implement trusted computing solution for device manufacturers.

ARM processors may also include virtualization features. These features provide a new processor mode, and several features to improve performances [36, 37]:

**CPU virtualization:** a new processor mode (*HYP* mode) was introduced, dedicated for a VMM. Hence, this mode is more privileged than the kernel mode. To reduce the virtualization overhead, the ARM architecture allows traps to be configured in order to trap directly into a VM's kernel mode instead of going through Hyp mode.

- Memory virtualization: ARM provides a hardware support for virtualization. A guest now manages Intermediate Physical Addresses (IPA, also known as guest physical addresses) which need to be translated into physical addresses (PA, or host physical addresses) by the hypervisor. TLB tags are also implemented: the TLB is now associated with a *VMID* so that TLB operations can be performed per VM instead of globally. With this new facility, shadow page table is no longer required.

- Interrupts virtualization: the ARM architecture defines a GIC (Generic Interrupt Controller), which routes interrupts from devices to CPUs. CPUs use the GIC in return, to get the source of an interrupt. The GIC is separated in two parts: the distributor, and the CPU interfaces. Interrupts can be configured to trap in Hyp or kernel mode. The VMM can generate *virtual interrupts* to a guest, which will be handled transparently, as if the interrupt came from a genuine device. A trade-of must be found between trapping all the interrupts to kernel (high speed, not applicable in virtualized environment) or to the VMM (expensive solution, but the VMM retains control).

#### 2.2.3.3 Discussion

Both ARM and x86 architecture have evolved to provide virtualization extensions to make it easier to write efficient virtual machine monitors. Despite some implementation specificities (such as guest context saving to be done by the hypervisor in ARM, whereas it is done in hardware on x86), the features are equivalent:

- a new processor mode was created. On ARM, this is a dedicated CPU execution mode, whereas on x86 it is a root/non-root mode.

- A new layer of memory virtualization was added, which lets the VMM operate an additional layer of translation. This makes shadow page-tables useless.

- Interrupts are virtualized. The VMM can inject interrupts which are handled by the guest the same way as hardware interrupts. Without this feature, the VMM must guess the interrupt entry-points, and branch at that address in the guest context.

Both architectures still require IOMMU to isolate devices (which operate on physical memory), and protect against DMA. This feature is called SMMU (System MMU) on the ARM architecture.

Currently, almost all the hypervisors rely on those hardware mechanisms. In particular, kvm and Xen do use these features on ARM and x86 architectures.

#### 2.2.4 Hybrid approaches

Hybrid approaches can be considered when virtualization extensions are not available, or to improve performances (avoiding trap to the VMM and back). KVM [30] used to patch the Linux kernel (automatically) to replace sensitive instructions, and encode their operand. SWI instruction was used to trap back to the hypervisor. But because SWI only has 24 bits for its operand (which is not enough to encode all the parameters), a trick was used: coprocessors zero through seven are not defined by the ARM architecture, but trap regardless of their operands. That way, 24 additional bits could be used to encode additional parameters. Nowaday, KVM uses hardware virtualization features.

#### 2.2.4.1 Paravirtualization

"Para-" is of greek origin that means "beside", "with" or "alongside". Paravirtualization (also known as OS assisted virtualization) refers to a cooperation between the guest OS and the hypervisor to improve performance and efficiency [38]. Cooperation does not mean that the guest has to be trusted, but only that it is aware not to run on baremetal but on top of an hypervisor. This technique consists of modifying the guest source to remove non-virtualizable instructions and replace them with "hypercalls" which will delegate the privileged tasks to the hypervisor. Paravirtualization does not require any changes to the ABI (Application Binary Interface). Hence, no modification is required for guest applications.

The Xen project [39] is an example of a hypervisor which relies on paravirtualization to virtualize processor and memory using a modified kernel, and a custom protocol to virtualize I/O. The latter uses a ring buffer located in the shared memory to communicate between virtual machines. It was successfully ported on both x86 [20] and on ARM [40]. Basically, Xen must expose 3 interfaces:

- **Memory management:** the guest OS will use hypercalls to manage virtual memory and TLB caches.

- **CPU:** the guest OS will run in a lower privilege level than Xen, register exception handlers to Xen, implement an event system in place of interrupts, and manage a "real" and "virtual" time.

- **Device I/O:** guest OS will use asynchronous I/O rings to transfer data toward disk or network devices.

Paravirtualization reduces the virtualization overhead because no traps back and forth to the hypervisor are required since those calls are made explicit. Its major drawback is that it cannot be used with unmodified guests. Nevertheless, paravirtualization can also be used for subsystems, such as device drivers like VirtIO [41]. VirtIO is an alternative to Xen paravirtualized drivers. There are currently three drivers built on top of an efficient zero-copy ring buffer: a block driver, a network driver and a pci driver.

Porting an operating system on top of a paravirtualization engine:

- **Improves security:** Because guests are deprivileged, they cannot perform critical tasks directly. Even if an unprivileged guest gets corrupted, the risk will be limited [42];

- Eases writing of operating system: Exposing a high(er) level of abstraction of the machine reduces the need of low level language (formerly required for low-level operations). There exists several unikernels targeting Xen [43]: MirageOS, HalVM, ErlangOnXen, Osv, GUK ...

- Still requires modification on guests: Today the total number of lines required to port Linux on Xen is about three thousands lines of code. This is estimated to be less than two percent of the x86 code base.

- **Removes the need of hardware extensions:** At the early days of the porting of KVM for ARM, no hardware virtualization was supported. *Lightweight* paravirtualization was introduced: it is a script-based method to automatically modify the source code of the guest operating system kernel to issue calls to KVM instead of issuing sensitive instructions [30]. It is architecture specific, but operating system independent. As mentionned in 2.2.3.2 (p 38), this has been abandoned in favour of hardware mechanisms.

#### 2.2.4.2 Trap and emulate

Trap-and-emulate was introduced by VMWare in [44] to subvert x86 virtualization issues. Suzuki and Oikawa [29] have presented their implementation on an ARMv6 CPU. Trap and emulate is somehow related to dynamic recompilation (see 2.2.2.3 (p 33)), for which the source instruction set is the same as the targeted one. Hence, only sensitive instructions must be replaced by traps to the hypervisor, which will emulate the effect of those specific instructions.

#### 2.2.4.3 Other implementations

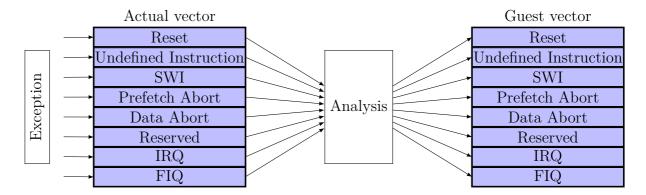

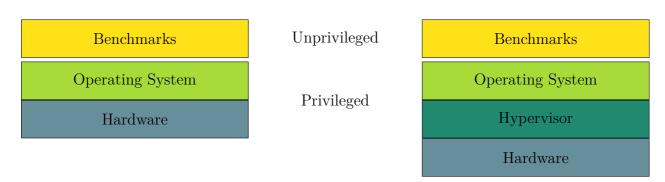

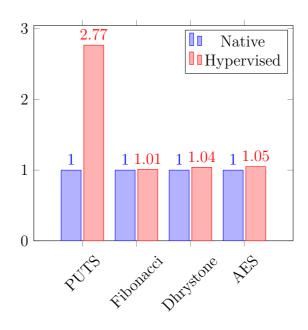

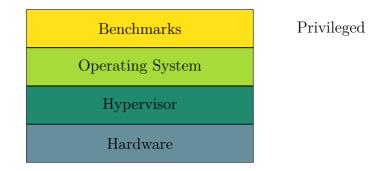

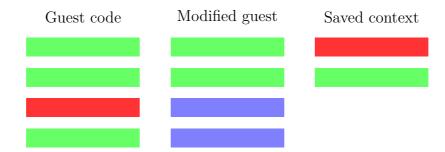

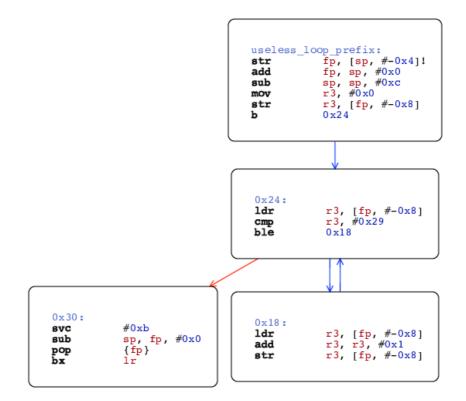

There are some other trends that have not been covered here, that I think worth to present.