# Caractérisation et modélisation compacte de mémoires émergentes

Marc Bocquet

#### ▶ To cite this version:

Marc Bocquet. Caractérisation et modélisation compacte de mémoires émergentes. Micro et nanotechnologies/Microélectronique. Aix Marseille Université, 2017. tel-01737675

### HAL Id: tel-01737675 https://hal.science/tel-01737675v1

Submitted on 19 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# AIX-MARSEILLE UNIVERSITÉ IM2NP

Préparée et soutenue publiquement pour obtenir l'habilitation à diriger des recherches

### Marc BOCQUET

# Caractérisation et modélisation compacte de mémoires émergentes

### Soutenue le 23/06/2017 devant le jury composé de :

| Pr. Christophe Muller<br>Dr. Gérard Ghibaudo | CNRS Délégation Alpes<br>IMEP-LAHC | Présidant<br>Rapporteur |

|----------------------------------------------|------------------------------------|-------------------------|

| Pr. Ian O'Connor                             | INL                                | Rapporteur              |

| Pr. Cristell O'Maneux                        | IMS                                | Rapporteur              |

| M. Marc Belleville                           | CEA-LETI                           | Examinateur             |

| Cr. Damien Querlioz                          | C2N                                | Examinateur             |

Pr. Jean-Michel Portal IM2NP

M. Jean-Michel MIRABEL STMicroelectronics Invité

Pour aller où on ne sait pas, il faut prendre des chemins qu'on ne connait pas. Sagesse des Indes.

# Table des matières

| Pr | éamb | oule                                                                     | 1  |

|----|------|--------------------------------------------------------------------------|----|

| 1  | Intr | oduction et positionnement des travaux de recherche                      | 3  |

|    | 1.1  | Positionnement des mémoires non-volatiles                                | 5  |

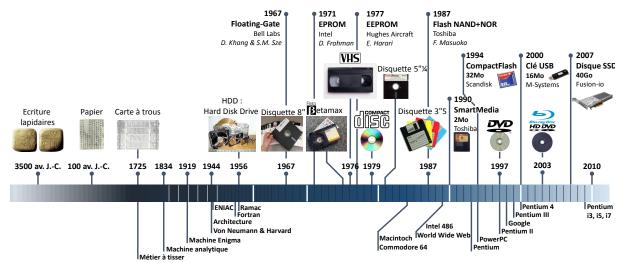

|    |      | 1.1.1 Histoire de hiérarchie : des peintures rupestres aux datacenters . | 6  |

|    | 1.2  | Les limitations des mémoires Flash                                       | 11 |

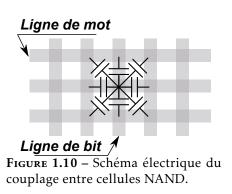

|    |      | 1.2.1 Couplages électrostatiques                                         | 12 |

|    |      | 1.2.2 Nombre d'électrons pour coder un état :                            | 13 |

|    |      | 1.2.3 Hautes tensions                                                    | 14 |

|    | 1.3  | Vers une nouvelle ère                                                    | 15 |

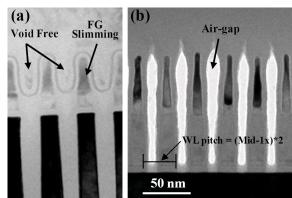

|    |      | 1.3.1 Une Flash more than Moore                                          | 15 |

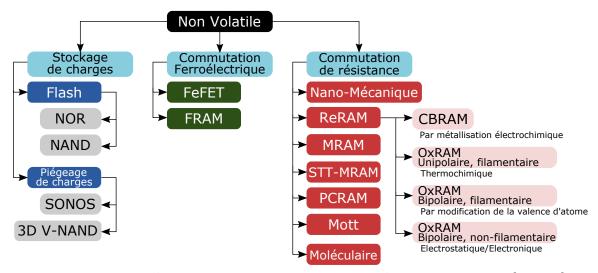

|    |      | 1.3.2 Mémoires émergentes                                                | 16 |

|    |      | 1.3.3 Conclusion                                                         | 20 |

|    | 1.4  | Positionnement des activités de recherche                                | 22 |

| 2  | Cara | actérisation de mémoires résistives OxRRAM                               | 25 |

|    | 2.1  | Contexte et positionnement                                               | 27 |

|    | 2.2  | Propriétés fondamentales des OxRRAM à base de HfO <sub>2</sub>           | 30 |

|    | 2.3  | Analyse en température — Endurance, Rétention                            | 33 |

|    |      | 2.3.1 Comportement électrique et performances                            | 33 |

|    |      | 2.3.2 Impact de l'état LRS sur la rétention                              | 36 |

|    |      | 2.3.3 Impact de l'état LRS sur l'opération de Reset                      | 39 |

|    | 2.4  | Analyse Sécuritaire - Attaque LASER                                      | 42 |

|    |      | 2.4.1 Contexte de l'étude                                                | 42 |

|    |      | 2.4.2 Attaque de cellules 1R                                             | 42 |

|    |      | 2.4.3 Éléments de compréhension                                          | 43 |

|    | 2.5  | Conclusions et perspectives                                              | 45 |

| 3  | Mod  | lélisation des mémoires résistives                                       | 47 |

|    | 3.1  | Contexte et positionnement                                               | 49 |

|    | 3.2  | Modélisation des mémoires OxRRAM unipolaires à base de NiO               | 50 |

|    |      | 3.2.1 Description du modèle                                              | 51 |

|    |      | 3.2.2 Validation du modèle                                               | 53 |

|    |      | 3.2.3 Conclusion                                                         | 55 |

|    | 3.3  | Modèle compact des dispositifs OxRRAM bipolaires                         | 56 |

|      |       | 3.3.1<br>3.3.2<br>3.3.3 | Détail du modèle compact mis en œuvre                        | 62  |

|------|-------|-------------------------|--------------------------------------------------------------|-----|

| 3    | 3.4   | Conclu                  | isions et perspectives                                       |     |

| 4 I  | Matı  | rice FeI                | RAM à base de technologie C-OTFT                             | 71  |

| 4    | 4.1   | Contex                  | xte                                                          | 73  |

|      |       | 4.1.1                   | Positionnement et objectifs                                  | 73  |

|      |       | 4.1.2                   | Filière C-OTFT: Complementary Organic Thin Film Transistors. |     |

|      |       | 4.1.3                   | Mémoire ferroélectrique : FeRAM                              |     |

| 2    | 4.2   | Caract                  | érisation et modélisation des cellules FeRAM                 |     |

|      |       | 4.2.1                   |                                                              |     |

|      |       | 4.2.2                   | Modélisation compacte                                        |     |

|      |       | 4.2.3                   |                                                              |     |

| 2    | 4.3   | Archite                 | ecture mémoire                                               |     |

|      |       | 4.3.1                   |                                                              |     |

|      |       | 4.3.2                   |                                                              |     |

|      |       | 4.3.3                   |                                                              |     |

| 4    | 4.4   | Conclu                  | isions et perspectives                                       |     |

| Con  | clus  | sions ge                | énérales et projet de recherche                              | 97  |

| Bibl | liogı | aphie                   |                                                              | 101 |

| Inde | ex    |                         |                                                              | 122 |

# Table des figures

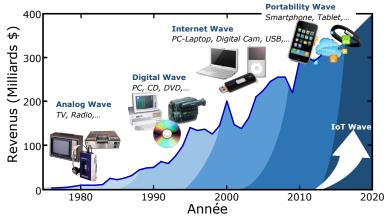

| 1.1  | Marché des semi-conducteurs (source : Semico Research Corporation)                                    | 5  |

|------|-------------------------------------------------------------------------------------------------------|----|

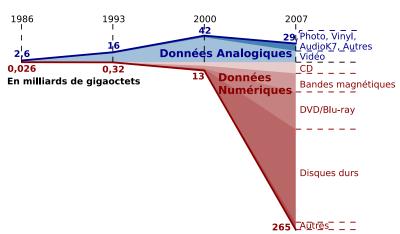

| 1.2  | Évolution de la quantité mondiale de données stockées                                                 | 5  |

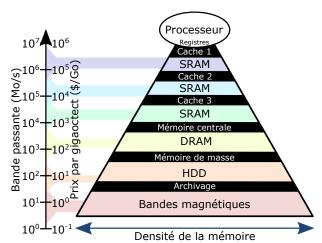

| 1.3  | Hiérarchie mémoires                                                                                   | 6  |

| 1.4  | Quelques repères historiques des moyens de stockages numériques                                       | 8  |

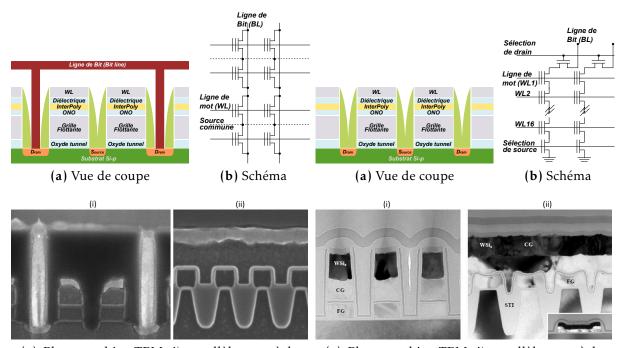

| 1.5  | Architecture NOR                                                                                      | 9  |

| 1.6  | Architecture NAND                                                                                     | 9  |

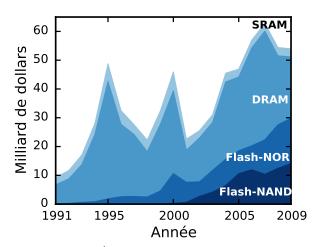

| 1.7  | Évolution des revenus du marché des mémoires                                                          | 10 |

| 1.8  | Évolution du prix du gigaoctet des mémoires NAND Flash et HDD                                         | 10 |

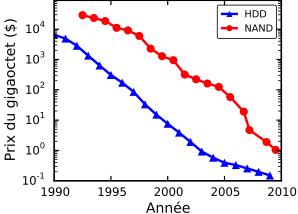

| 1.9  | Évolution de la hiérarchie mémoire                                                                    | 11 |

| 1.10 | Schéma électrique du couplage entre cellules NAND                                                     | 13 |

| 1.11 | Mise en œuvre de la technique "Air-gap"                                                               | 13 |

| 1.12 | Classification des principales technologies mémoires non-volatiles [ITRS13]                           | 16 |

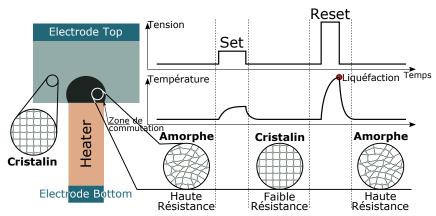

| 1.13 | Schéma simplifié de l'empilement PCRAM                                                                | 17 |

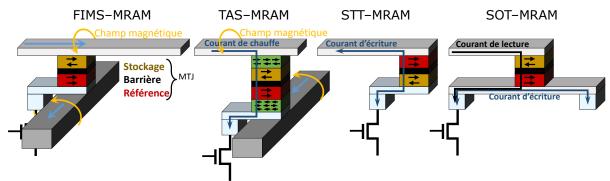

| 1.14 | Schéma structurel des différentes générations de mémoires MRAM                                        | 18 |

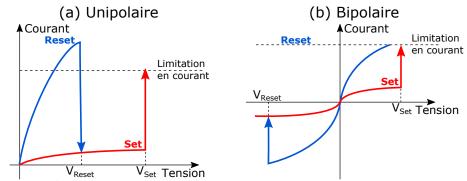

| 1.15 | Commutation unipolaire et bipolaire des mémoires ReRAM                                                | 19 |

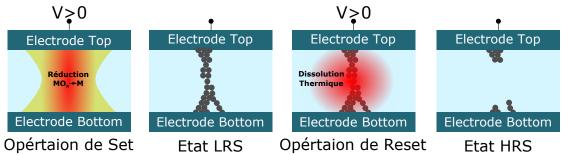

| 1.16 | Mécanismes de Set et de Reset dans une OxRRAM unipolaire de type TCM.                                 | 19 |

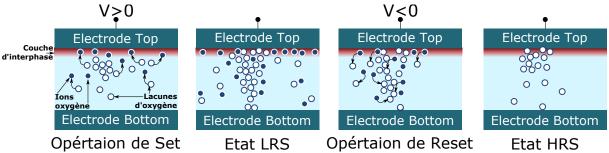

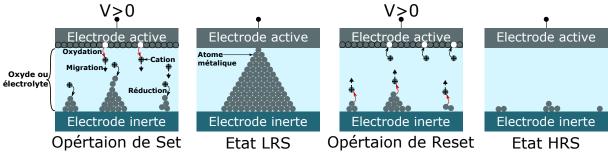

| 1.17 | Mécanismes de Set et de Reset dans une OxRRAM bipolaire de type VCM.                                  | 20 |

| 1.18 | Opérations de Set et de Reset dans un empilement CBRAM                                                | 20 |

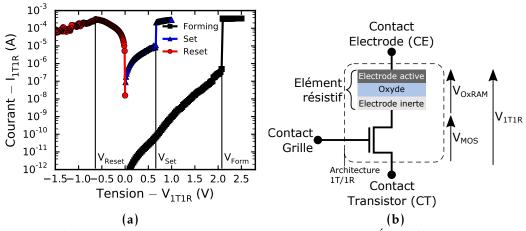

| 2.1  | Caractéristiques $I(V)$ et schéma d'une d'une architecture "1T1R"                                     | 30 |

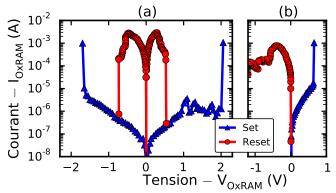

| 2.2  | I(V) d'empilements (a) Non-polaire (Pt/HfO <sub>2</sub> /Pt) et Bipolaire (Ti/HfO <sub>2</sub> /TiN)  |    |

| 2.3  |                                                                                                       | 31 |

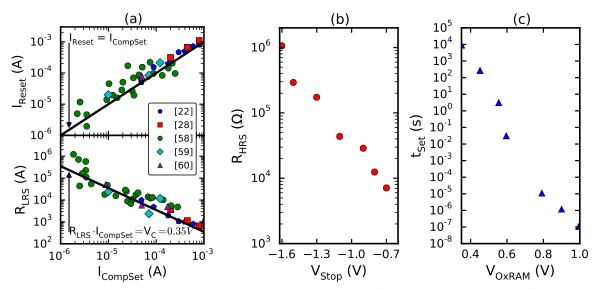

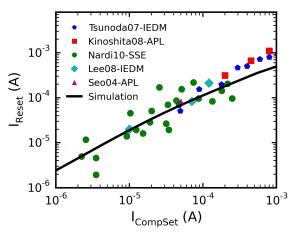

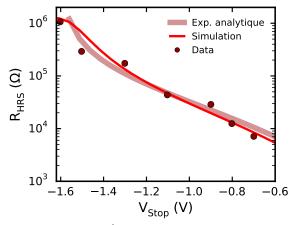

| 2.4  | Évolution de $I_{Reset}$ en fonction de $I_{CompSet}$ ; de $R_{HRS}$ en fonction de $V_{StopReset}$ ; |    |

|      | 1                                                                                                     | 32 |

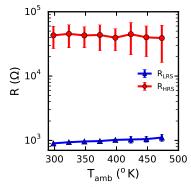

| 2.5  | Évolution en températures des résistances LRS et HRS programmées à                                    |    |

|      |                                                                                                       | 34 |

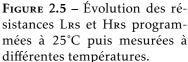

| 2.6  | Évolution avec température des tensions de commutation, de $R_{LRS}$ et de                            |    |

|      |                                                                                                       | 34 |

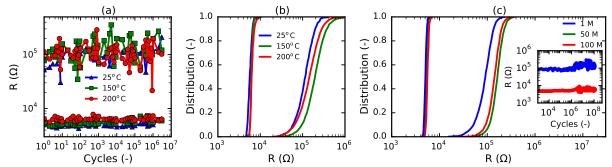

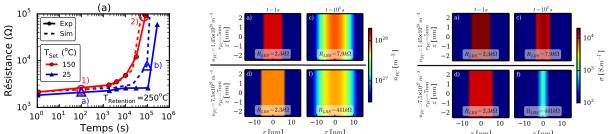

| 2.7  | Caractéristique d'endurance à 25°C, 150°C et 200°                                                     | 35 |

| 2.8  |                                                                                                       | 36 |

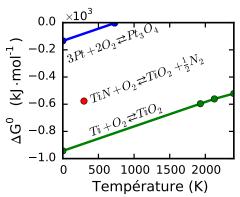

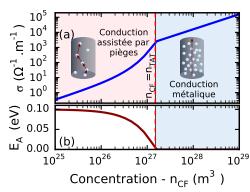

| 2.9  | $sigma$ et $R_{LRS}$ calculées en fonction de la concentration en lacunes d'oxy-                      |    |

|      | gène                                                                                                  | 38 |

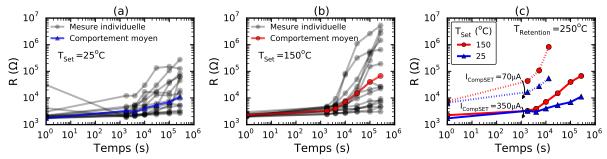

| 2.10 | Rétention expérimental et simulé en fonction de la température de Set .                               | 38 |

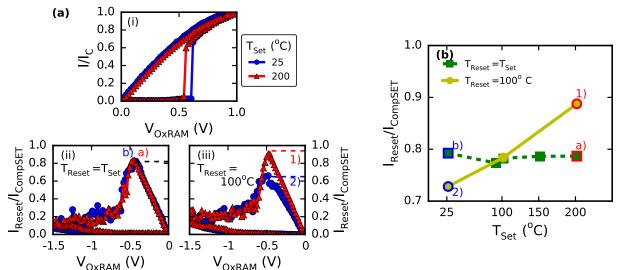

| 2.11 | Impact de la température du Set sur l'opération de Reset                                              | 39 |

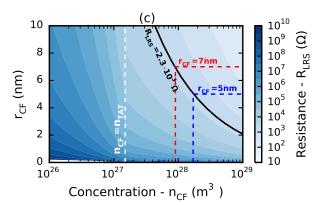

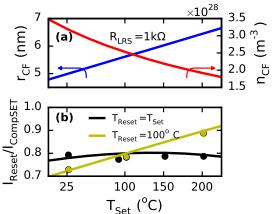

| 2.12 | a) $R_{CF}$ et $n_{CF}$ utilisées en simulation et b) Ratio $I_{Reset}/I_{CompSET}$ simulé .          | 40 |

| 2.13       | Simulation du Reset pour des filaments ayant caractéristiques microsco-                                                                      |           |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|            | piques différentes                                                                                                                           | 40        |

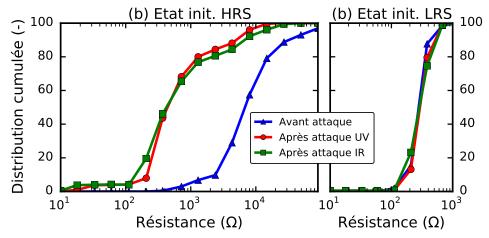

|            | Distribution cumulée des valeurs de résistances avant et après attaque .                                                                     | 43        |

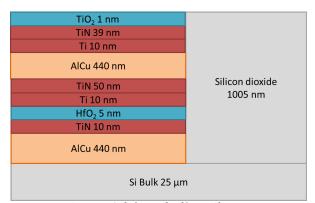

| 2.15       | Schéma de l'empilement complet utilisé dans la simulation des attaques LASER                                                                 | 44        |

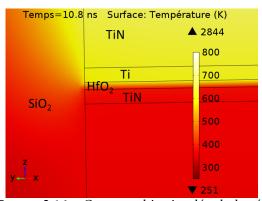

| 2.16       | Cartographie simulée de la répartition de la température après 0.8 ns suivant l'attaque LASER                                                | 44        |

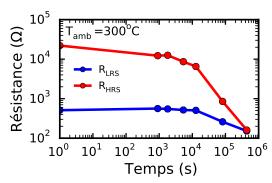

| 2.17       | Rétention à 300°C des dispositifs de l'étude des attaques LASER                                                                              | 45        |

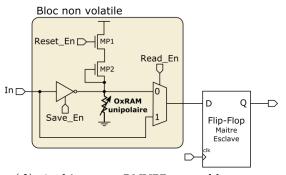

| 3.1        | Schéma de la structure utilisé dans le modèle d'OxRRAM unipolaire                                                                            | 51        |

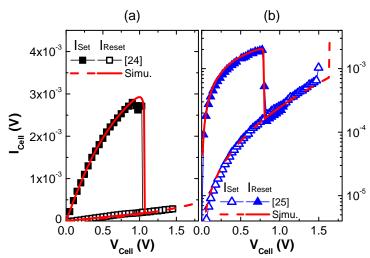

| 3.2        | Caractéristiques $I(V)$ expérimentales et simulées de cellules OxRRAM unipolaires                                                            | 54        |

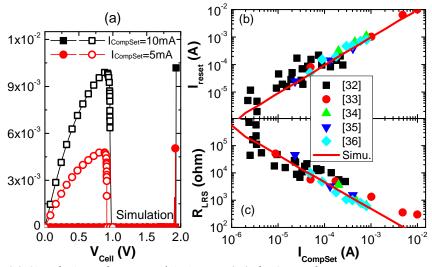

| 3.3        | Caractéristiques $I(V)$ simulées pour $I_{CompSet} = 5 \text{mA}$ et $10 \text{mA}$                                                          | 54        |

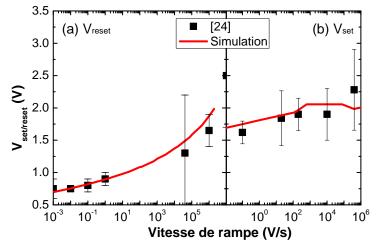

| 3.4        | Évolution des tensions de commutation en fonction de la vitesse de la                                                                        |           |

|            | rampe                                                                                                                                        | 55        |

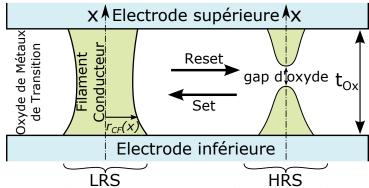

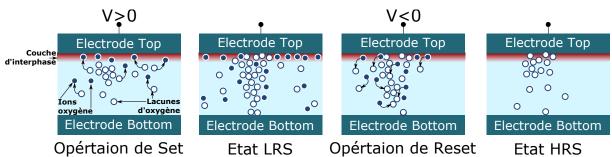

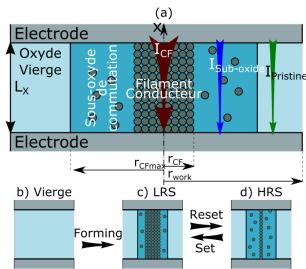

| 3.5        | Description schématique des mécanismes de fonctionnement de la tech-                                                                         |           |

|            | nologie OxRRAM – VCM : Valency Change Memory                                                                                                 | 57        |

| 3.6        | Schéma des différentes régions considérées dans le modèle compact d'OxR-                                                                     |           |

|            | RAM bipolaire                                                                                                                                | 58        |

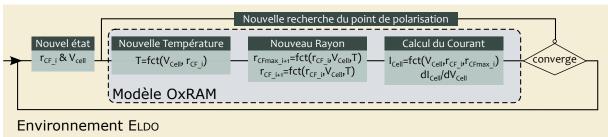

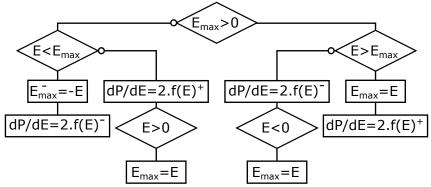

| 3.7        | Organigramme du programme employé dans l'implémentation numé-                                                                                | <b>(3</b> |

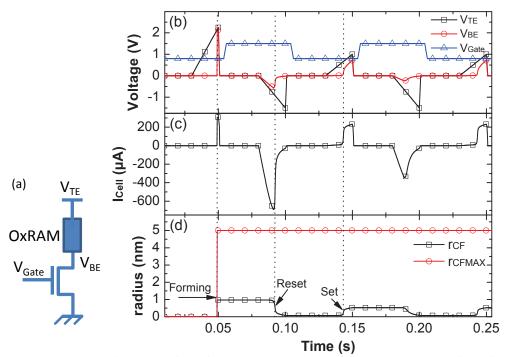

| 2.0        | rique sous ELDO                                                                                                                              | 62<br>63  |

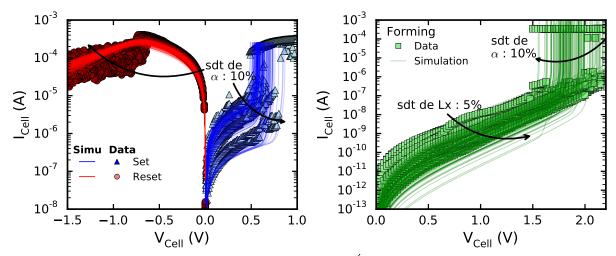

| 3.8<br>3.9 | Chronogrammes obtenu par simulation d'une OxRRAM bipolaire 1T1R . Caractéristiques $I(V)$ expérimentales et simulées d'une structure mémoire | 63        |

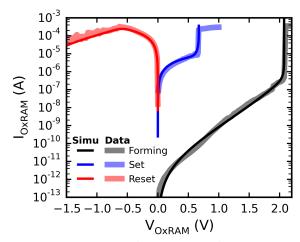

| 3.9        | à base de $HfO_2$                                                                                                                            | 64        |

| 3.10       | Evolution de $I_{Reset}$ en fonction de $I_{CompSet}$ obtenu en simulation                                                                   | 64        |

|            | Évolution de $R_{HRS}$ en fonction de $V_{StopReset}$                                                                                        | 65        |

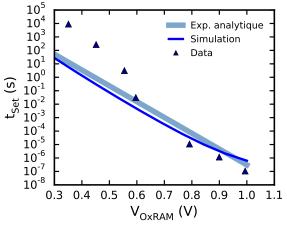

|            | Temps de commutation de l'opération de Set en fonction de la tension                                                                         | 00        |

|            | appliquée                                                                                                                                    | 65        |

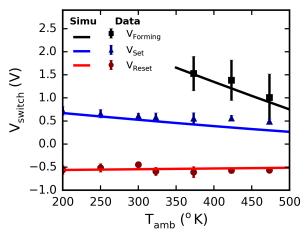

| 3.13       | Confrontation des résultats de simulation avec les données expérimen-                                                                        |           |

|            | tales des tensions de commutation en fonction de la température                                                                              | 66        |

| 3.14       | Caractéristiques $I(V)$ expérimentales et simulées de l'Électroforming, du                                                                   |           |

|            | Set et du Reset reflétant la variabilité dispositif à dispositif                                                                             | 67        |

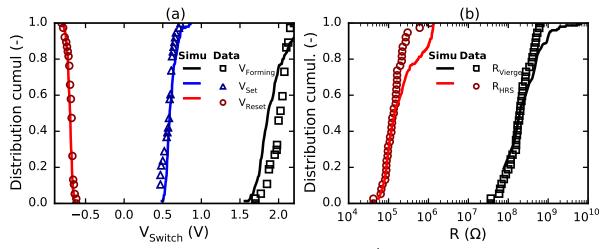

| 3.15       | Distributions cumulées des tensions de commutation et des résistances                                                                        | <b>.</b>  |

| 2 16       | de $R_{HRS}$ et de $R_{Pristine}$                                                                                                            | 68        |

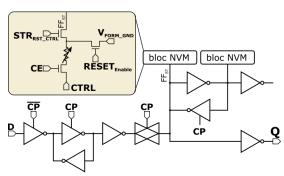

| 3.10       | Exemples d'applications réalisés à partir des modèles compacts OxRRAM                                                                        | 69        |

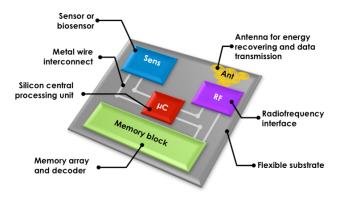

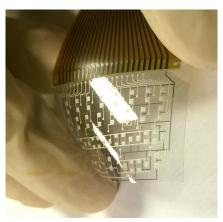

| 4.1        | Système RFID                                                                                                                                 | 73        |

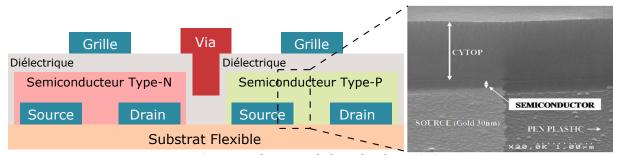

| 4.2        | Vue de coupe de la technologie C-OTFT                                                                                                        | 75        |

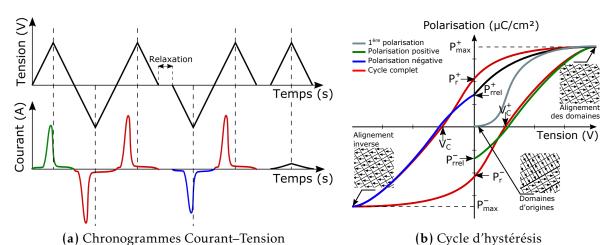

| 4.3        | Chronogrammes de mesure et Cycle d'hystérésis typique d'une mémoire FeRAM avec les grandeurs le caractérisant                                | 77        |

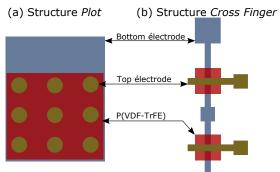

| 4.4        | Schéma des dispositifs de type <i>Plot</i> et des dispositifs de type <i>Cross Finger</i>                                                    | 79        |

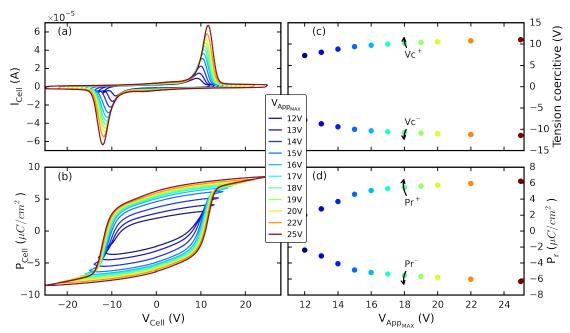

| 4.5        | Caractéristique électrique d'un condensateur $Au/P(VDF-TrFE)/Au$                                                                             | 79        |

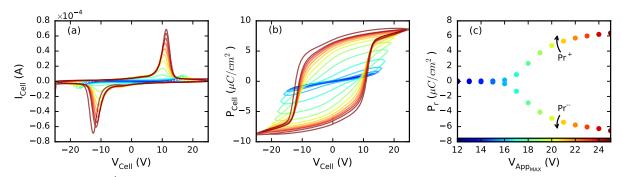

| 4.6        | Caractéristique électrique d'un condensateur $Au/P(VDF-TrFE)/Au$ lors des premiers cycles de réveil                                          | 80        |

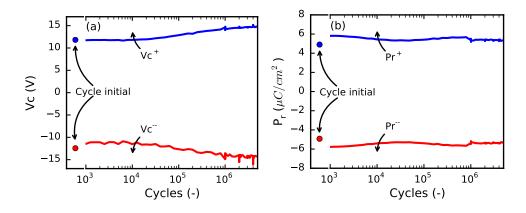

| 4.7        | Caractéristique de la fatigue d'une cellule FeRAM $Au/P(VDF-TrFE)/Au$ .                                                                      | 80        |

|            |                                                                                                                                              |           |

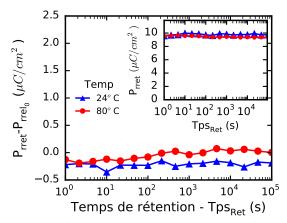

| 4 R  | Caractéristique de la rétention d'un empilement $Au/P(VDF-TrFE)/PEDOT:Particular de la rétention d'un empilement Au/P(VDF-TrFE)/PEDOT:Particular d'un empilement empilement en la rétention d'un empilement en la réten$ | SS_ A a  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.0  | à 24°C et 80°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81       |

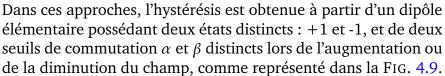

| 4.9  | Opérateur hystérésis élémentaire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82       |

|      | Logigramme simplifié                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83       |

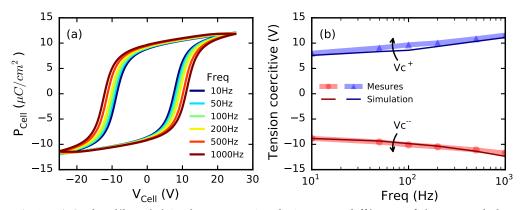

|      | Confrontation entre simulations et mesures du cycle d'hystérésis et des                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|      | courants dans un empilement $Au/P(VDF-TrFE)/PEDOT:PSS-Ag$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83       |

| 4.12 | Cycles d'hystérésis obtenus en simulation pour différentes fréquences de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|      | la tension appliquée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84       |

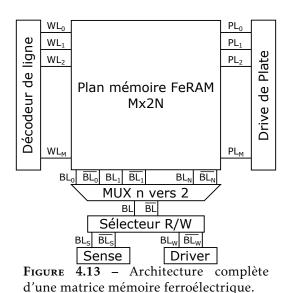

| 4.13 | Architecture complète d'une matrice mémoire ferroélectrique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85       |

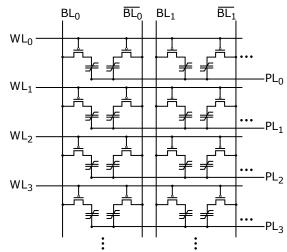

| 4.14 | Plan mémoire FeRAM de type 2T2C : 2 transistors et 2 condensateurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 85       |

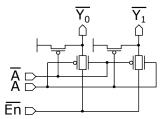

|      | Schéma de l'unité élémentaire de décodage 1 vers 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88       |

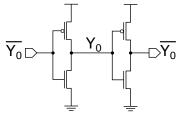

|      | Schéma de l'étage de sortie à double inversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88       |

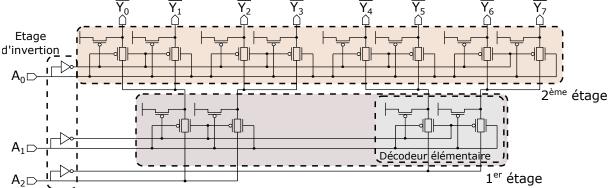

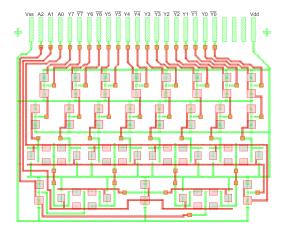

|      | Schéma électrique complet du décodeur 3 vers 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88       |

|      | Décodeur 3 vers 8 avec étage de sortie double inversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89       |

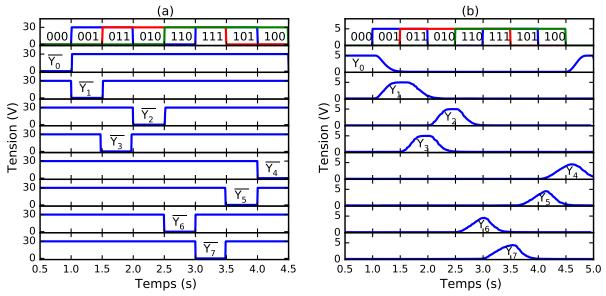

|      | Chronogrammes des signaux de sortie du décodeur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90       |

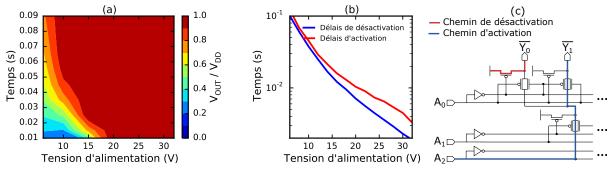

|      | Ratio $V_{OUT}/V_{DD}$ et délais d'activation et de désactivation du décodeur .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90       |

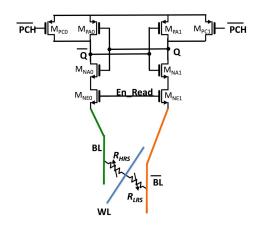

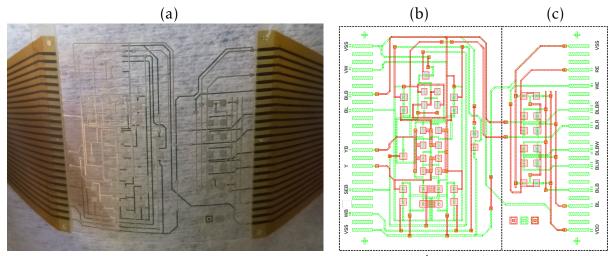

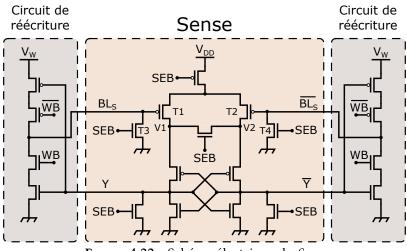

|      | Sense et sélecteur de Lecture/Écriture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91       |

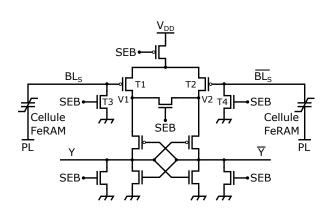

|      | Schéma électrique du Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91       |

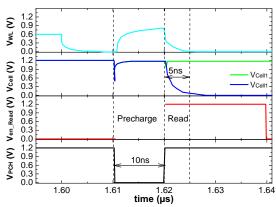

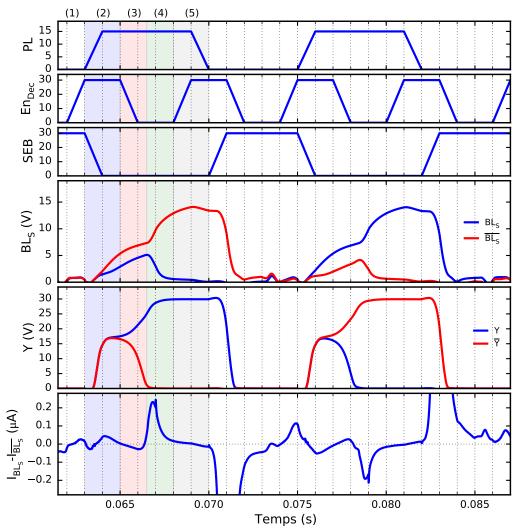

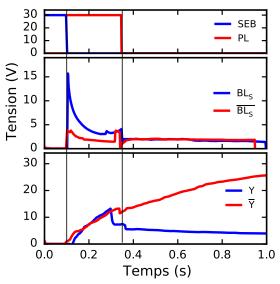

|      | Chronogrammes du Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 92       |

| 4.24 | Schéma de test du <i>Sense</i> relié à deux cellules mémoires FeRAM simulant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.4      |

| 4.25 | les conditions standards de lecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94<br>94 |

| 4.25 | Chronogrammes de test du Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| ict  | e des tableaux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 15 L | e des tableaux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

# L

| 1.1        | Tableau comparatif des performances des mémoires résistives | 21       |

|------------|-------------------------------------------------------------|----------|

|            | Paramètres physiques utilisés dans le modèle de diffusion   |          |

|            | Paramètres du modèle OxRRAM unipolaire                      |          |

| 4.2<br>4.3 | Paramètres utilisés dans le modèle compact FeRAM            | 86<br>87 |

## Préambule

Ce manuscrit présente quelques-unes de mes activités de recherche sur la période 2010 à 2017 dans le cadre de la préparation à l'Habilitation à Diriger des Recherches.