THÈSE

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

# Présentée et soutenue le 08/12/2017 par : Roberta RUFFILLI

Modes de fatigue des métallisations à base d'aluminium dans les composants MOSFET de puissance

Fatigue mechanisms in Al-based metallizations in power MOSFETs

#### JURY

MAURO CIAPPA JOSEF LUTZ MARIE-LAURE LOCATELLI MICHAEL NELHIEBEL STÉPHANE LEFEBVRE MOUNIRA BERKANI MARC LEGROS ETH, Zurich TU, Chemnitz Laboratoire LAPLACE, Toulouse K.A.I - Infineon, Villach SATIE - ENS, Cachan SATIE - ENS, Cachan CEMES - CNRS, Toulouse Rapporteur Rapporteur Membre du Jury Membre du Jury Directrice de Thèse Directeur de Thèse

#### École doctorale et spécialité :

SDM : Physique de la matière - CO090

Unité de Recherche :

Centre d'Élaboration de Matériaux et d'Études Structurales (CEMES-CNRS, UPR 8011)

# ABSTRACT

This thesis, a collaboration between CEMES-CNRS, Satie laboratory (ENS Cachan) and NXP Semiconductors is motivated by the comprehension of the failure mechanisms of low voltage power MOSFET devices produced for applications in the automotive industry.

A limiting factor for the long-term reliability of power modules is the electrothermal and/or thermo-mechanical aging of the metallic parts of the source: Al metallization and bonding wires. At the temperature reached during the on-off operating cycles (few hundred degrees), the difference in the coefficient of thermal expansion between the metallization and the oxide and semiconductor parts induces an inevitable plastic deformation in the metal, which is the softest material in the complex MOSFET architecture.

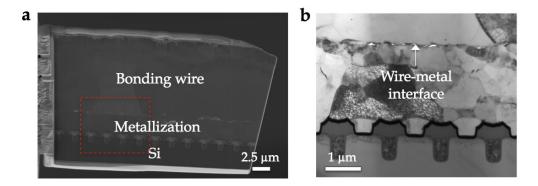

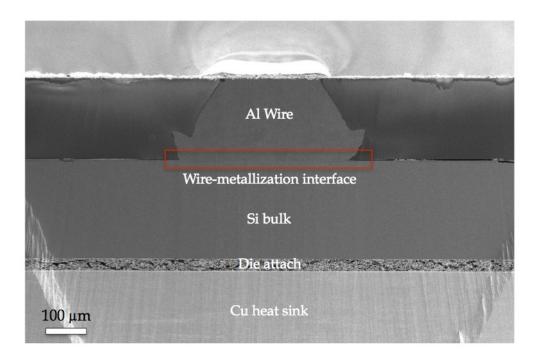

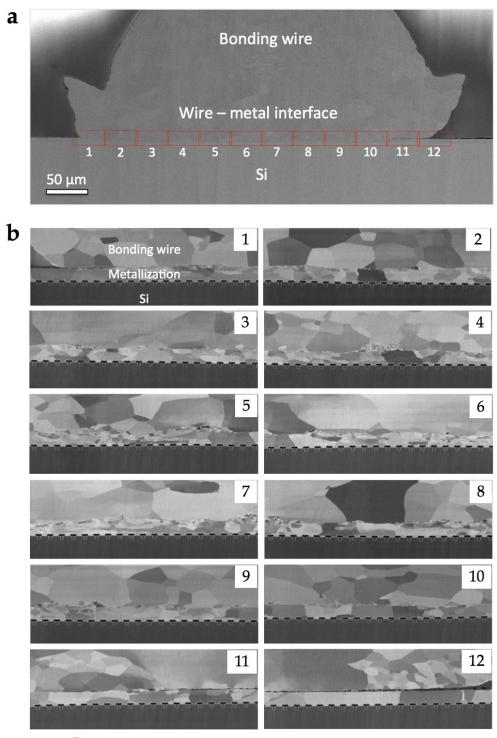

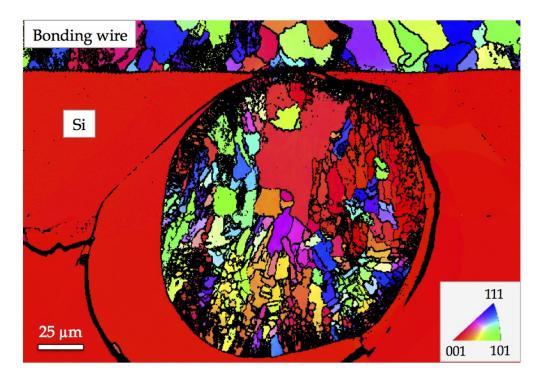

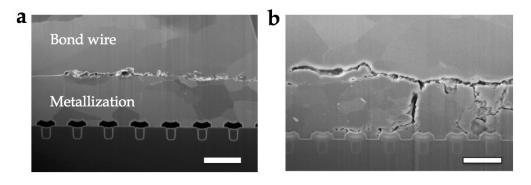

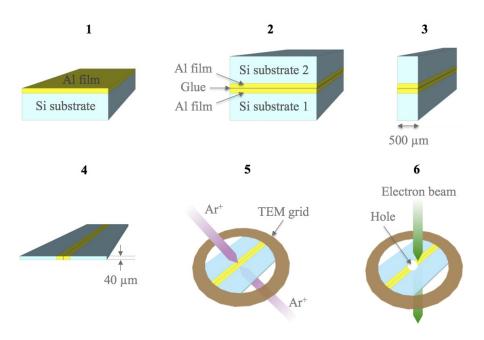

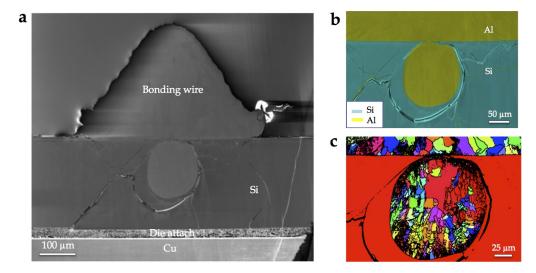

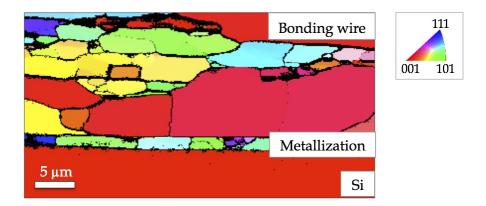

We have characterized the metal microstructure before and after accelerated electro-thermal aging tests, by using specific techniques from the field of the physical metallurgy: electron and ion microscopy, grain orientation and chemical composition mapping. For the first time the source metallization has been characterized both away and under the bonding connections, which are one hundred times thicker than the metallization layer. The latter is a critical location for the reliability assessment because the ultrasonic bonding process may weaken the initial metallization microstructure by adding an important plastic deformation prior to aging. This is, however, poorly stated in the literature because of the difficulty to access the metallization under the wires without damaging their bonding, which is known to be particularly weak in case of aged modules.

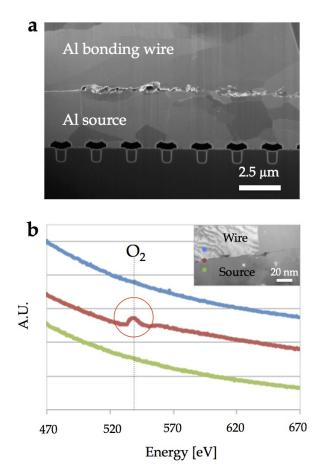

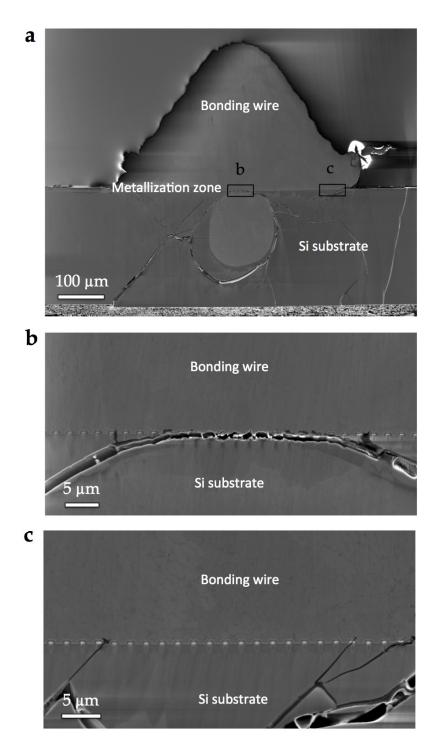

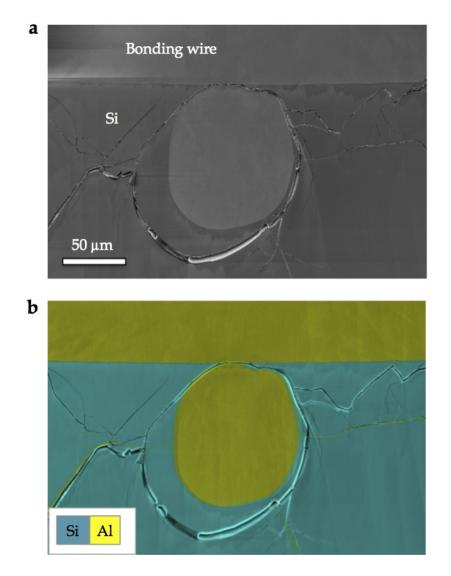

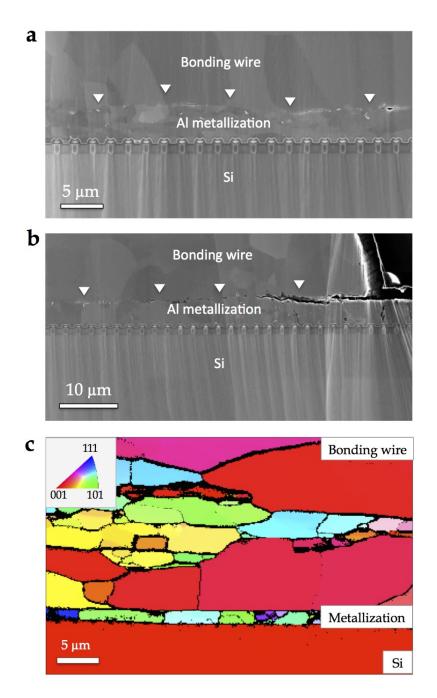

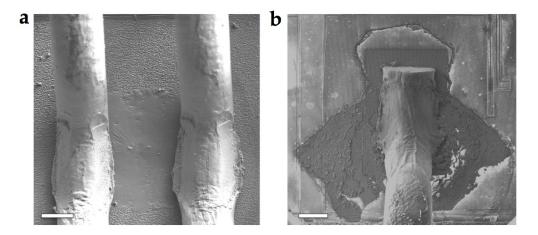

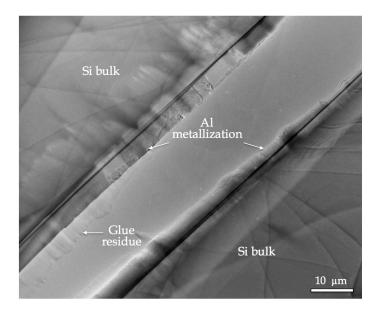

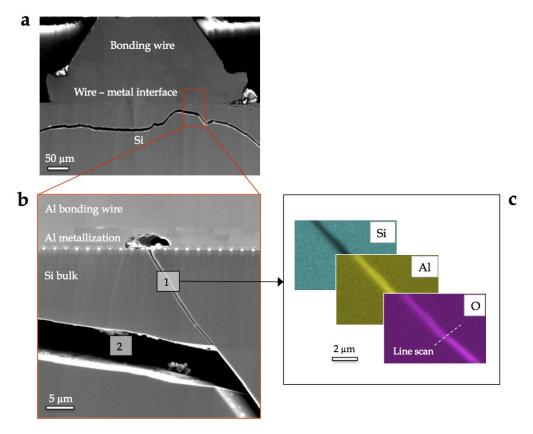

In order to investigate the wire-metallization interface, we have set up original sample preparations, based on ion polishing, that allowed us to disclose the metallization under the bonding wires without introducing preparation artifacts in the microstructure. The bonding process induces a severe and nonuniform plastic deformation in the metallization under the wires without recreating a good electrical contact: small cavities and native oxide residues, have been systematically observed at the Al/Al interface, in all the analyzed modules, before and after aging.

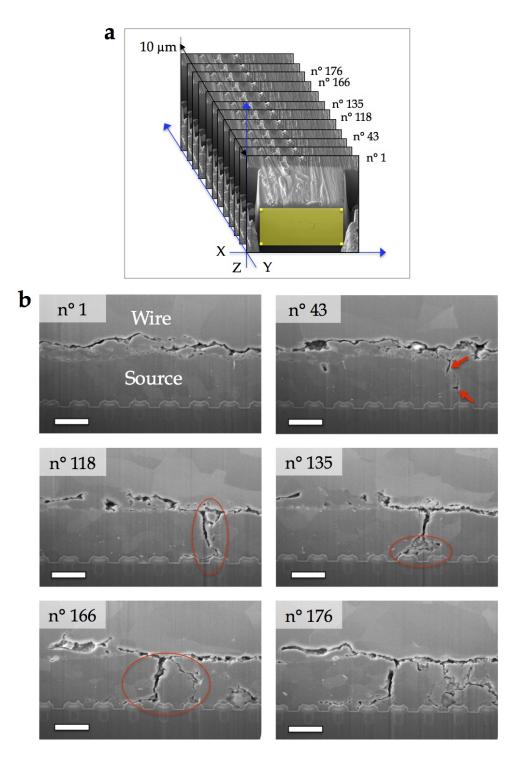

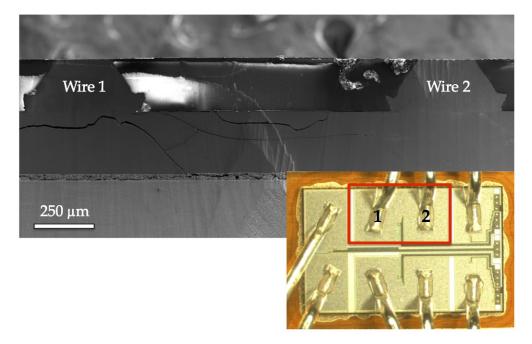

The main mechanism behind the device failure is the generation and propagation of fatigue cracks in the aluminum metallization, associated to a local Al oxidation that prevents these crack from closing. Away and under the wire bonds, they run perpendicularly from the surface down to the silicon substrate following the grain boundaries, due to an enhanced intergranular diffusion of aluminum atoms. In the bonding area, the phenomenon of parallel cracking is favored by the initial imperfections in the wire-metallization bonding. Ion tomography experiments have shown that these cracks are confined to the wiremetal interface and do not propagate in the wire despite its lower strength (pure Al, larger grain structure). Crack propagation along the Al/Al interface can cause a contact reduction between the wire and the source metallization and eventually its failure. Such discontinuities in the metal can explain the local increase in the device resistance and temperature that accelerates the aging process until failure.

This study settled new, dedicated techniques and quantification methods to assess the aging of the metal parts of MOSFET devices. The full characterization of the intrinsically defective interface generated by the bonding process and the metallization degradation during electro-thermal aging indicated paths to possible improvements of current technologies and potential developments of new processes.

# RESUMÉ

Cette thèse, effectuée en collaboration entre le CEMES-CNRS, le laboratoire Satie (ENS Cachan) et NXP Semiconductors est motivée par la compréhension des mécanismes de défaillance des dispositifs MOSFET pour les applications dans l'industrie automobile.

Un facteur limitant de la fiabilité à long terme des modules de puissance basse tension est le vieillissement électrothermique et/ou thermo-mécanique des parties métalliques de la source: métallisation en aluminium (ou alliage) et fils de connexion. A cause de la différence de coefficient de dilatation thermique entre la métallisation les oxydes et le substrat semi-conducteur, la température atteinte pendant les cycles de fonctionnement (quelques centaines de degrés), induit une déformation plastique inévitable dans le métal, qui est le matériau le plus mou dans l'architecture complexe du MOSFET.

Nous avons caractérisé la microstructure métallique avant et après les tests de vieillissement électrothermique accélérés, en utilisant des techniques spécifiques du domaine de la métallurgie physique: microscopie électronique et ionique, cartographie d'orientation de grains et de la composition chimique. Pour la première fois, la métallisation de la source a été caractérisée sous les fils de connexion, qui sont cent fois plus épais que la métallisation. Cet emplacement est critique pour la fiabilité du composant, car le processus de soudure par ultrasons induit une déformation plastique importante qui peut affaiblir la métallisation initiale avant le vieillissement. Ceci est peu étudié dans la littérature en raison de la difficulté à accéder à la métallisation sous les fils sans altérer leur interface, souvent endommagée et fragilisée dans les modules vieillis.

Nous avons mis en place des méthodes de préparation d'échantillon, basées sur le polissage ionique, pour étudier cette interface, sans introduire d'artefacts de préparation. Le processus de soudure à froid induit une déformation plastique sévère et non uniforme dans la métallisation sous les fils sans parvenir à recréer un bon contact électrique: de petites cavités et des résidus d'oxyde natif, ont été systématiquement observés à l'interface Al / Al, dans tous les modules analysés, avant et après vieillissement.

Le mécanisme principal de défaillance des modules est la génération et la propagation de fissures de fatigue dans l'aluminium, associée à une oxydation locale qui empêche la fermeture de ces fissures. Sous et en dehors des fils de connexion, ces fissures traversent la métallisation perpendiculairement à la surface jusqu'au substrat en silicium en suivant les joints de grains. Cette fissur-

ation est due à la diffusion intergranulaire accélérée des atomes d'aluminium. Dans la zone de soudure, le phénomène de fissuration parallèle à l'interface est favorisé par les imperfections initiales (cavités, oxyde). Les expériences de tomographie ionique ont montré que ces fissures sont confinées à l'interface fil-métal et ne se propagent pas dans le fil malgré sa plus faible résistance mécanique (Al pur, structure à grains plus grands). La propagation de la fissure le long de l'interface Al/Al peut provoquer une diminution du contact entre le fil et la métallisation de la source et éventuellement son décollement. Les fissures dans le métal source peuvent expliquer l'augmentation locale de la résistance et de la température du module qui accélère le processus de vieil-lissement jusqu'à l'échec.

Cette étude a établi de nouvelles techniques dédiées et des méthodes de quantification pour évaluer le vieillissement des parties métalliques des modules MOSFET. La caractérisation complète de l'interface soudée, intrinsèquement défectueuse et la dégradation de la métallisation pendant le vieillissement électrothermique ouvrent la voie à l'amélioration possible les technologies actuelles et au développement potentiel de nouveaux procédés. I had the chance to do my phd at the CEMES laboratory and NXP Semiconductors thanks to an e-mail sent by Andrea Falqui, the head of the laboratory where I worked in Italy, to the former director of the CEMES, Alain Claverie. I have to thank Andrea to have supported my desire to progress, and Alain Claverie to put me in contact with my PhD supervisor, Marc Legros.

When I moved to Toulouse for the first time I only knew all the things I was leaving in Italy, I was scared of my first job experience abroad, I did not speak French...and I had never eaten duck in my life! Despite these (huge!) cultural gaps, it took me really a short time to find my routine in the lab...and day after day with my grains of aluminum, FIB and TEM sessions, time flew and gave me good experiences, satisfaction and new friends. And I have many people to thank for this.

First of all my supervisor, Marc Legros. It is rare to meet a person so kind, fun, respectful and competent at the same time. Despite his booked agenda, he has always found the time for me, for our experiments, for answering my questions...And for encouraging me during my peaks of stress and lack of self-confidence (sorry for this!). It has been fundamental to me his support when I thought that my little pause in the middle of my PhD could prevent me from doing a good job. He taught me many things, while letting me be independent, and I am really grateful for this. I will miss him a lot.

Thanks also to Philippe Dupuy, my co-supervisor at NXP. I have peppered him with questions during these years, in person, by sms, telephone calls...He was always available to answer, and he helped me to build my network at NXP. In this regard, I would like to thank also Yann Weber, Thomas Mazeaud and Marine de Reviers for the useful discussions. And thanks to Thomas Zirilli for the help during my first ANADEF workshop and for welcoming me in his laboratory with all his staff: Céline, Thomas, Mathias, Patrick...

I also had the chance to collaborate with the SATIE laboratory in Cachan, under the supervision of Mounira Berkani: I would like to thank her, Stéphane Lefebvre and Gilles Rostaing for welcoming me during my stays there and explaining me in a simple way the secrets of electronics and aging tests!...And for the possibility to spend four beautiful days at the University of Naples, hosted by Michele Riccio.

The cross-polisher preparations of Claudie Josse at the Raimond Castaing Center helped me to save a lot of time (sorry FIB!) during the last months of my PhD. Thank you, Claudie, for these preparations and the useful advice. A lot of people supported me during my everyday life in the laboratory, professionally and humanly. I will mention only few of them, but I have really appreciate the kindness and the smiles of all the CEMES people: when I walked through the lab with my big belly, everybody seemed to support me as supporters of a football team during a match!

Thanks to Robin, Cécile (my *copine de grossesse*), Sébastien, Florent, and Philippe Salles for the precise training courses I have received and the constant support during my experiments. Thanks to all the PPM group. In particular to Alain for the access to the laboratory during the weekends and to Joel, who helped me with the bureaucracy with the École Doctorale. Fréd, thank you for our coffee breaks speaking about the illnesses of our children! Jean-Philippe, thank you for cleaning the coffee machine every day...! And Lise, thank you for your constant self-confidence training.

During these years, I have had also difficult days and sometimes it seemed me impossible to get to the end of my PhD. In these moments, my "PhD mates" have supported me and I have never felt alone. They are really precious to me and I am proud to say that I have found good friends. I think to Thomas and Zofia, my first *collègues de bureau*, Chloé, Victor, Paul, Aurelie, Lionel, who had the patience to listen to my first French sentences without laughing (too much) and helped me integrating in the lab. And to all my new friends with whom I shared my choices, joy and troubles: Winnie and Soumaya, thank your for your compliments, the daydreams about our future lives and to remind me when I had to go pick up Marta! And my *chers garçons*: Alessandro, Arthur, Nico (thank you for waiting for me at lunch!), Élie, Max and David. Melvyn, Ségolèn, Mia, Guillaume, I am sad we have spent such a short time together.

It has been a pleasure to go to work and learn something new every day. I am really grateful for these years and I will miss them.

And to conclude, thanks to Andrea and Marta for their support and patience, especially during the preparation of the dissertation. We did a great team-work in the last years: my efforts are for you, I hope you are proud of me.

# CONTENTS

| 1 | INT                               | RODUC                                          | TION                                                  | 1  |  |  |  |

|---|-----------------------------------|------------------------------------------------|-------------------------------------------------------|----|--|--|--|

| 2 | POW                               | ER ELE                                         | ECTRONICS FOR THE AUTOMOTIVE INDUSTRY, FAILURE        |    |  |  |  |

|   | моі                               | DE                                             |                                                       | 5  |  |  |  |

|   | 2.1                               | Power                                          | electronics technology evolution                      | 7  |  |  |  |

|   |                                   | 2.1.1                                          | Bipolar transistor                                    | 7  |  |  |  |

|   |                                   | 2.1.2                                          | Thyristor                                             |    |  |  |  |

|   |                                   | 2.1.3                                          | MOSFET transistor                                     | 12 |  |  |  |

|   |                                   | 2.1.4                                          | IGBT transistor                                       | 14 |  |  |  |

|   |                                   | 2.1.5                                          | Recent solutions: trench technology                   | 14 |  |  |  |

|   |                                   |                                                | 2.1.5.1 Vertical MOSFET                               | 15 |  |  |  |

|   |                                   |                                                | 2.1.5.2 Trench MOSFET                                 | 16 |  |  |  |

|   | 2.2                               | Smart                                          | Power MOSFET for the automotive industry              | 18 |  |  |  |

|   |                                   | 2.2.1                                          | Stress conditions in power electronics for automotive | 20 |  |  |  |

|   |                                   |                                                | 2.2.1.1 Thermal stress                                | 20 |  |  |  |

|   |                                   |                                                | 2.2.1.2 Electromagnetic stress                        | 21 |  |  |  |

|   |                                   |                                                | 2.2.1.3 Mechanical and chemical stress                | 21 |  |  |  |

|   |                                   | 2.2.2                                          | Failure modes in power MOSFETs                        | 21 |  |  |  |

|   |                                   |                                                | 2.2.2.1 Die/substrate solder joints fatigue           | 24 |  |  |  |

|   |                                   |                                                | 2.2.2.2 Failure modes in the active zone              | 25 |  |  |  |

|   |                                   | 2.2.3                                          | Thermosensitive aging indicators                      | 29 |  |  |  |

|   |                                   |                                                | 2.2.3.1 $R_{DS(on)}$                                  | 29 |  |  |  |

|   |                                   | 2.2.4                                          | Devices under test: 45V and 65V LFET1T technology     | 31 |  |  |  |

|   | 2.3                               | Reliability assessment of LFET1T power devices |                                                       |    |  |  |  |

|   |                                   | 2.3.1                                          | Test NXP                                              | 39 |  |  |  |

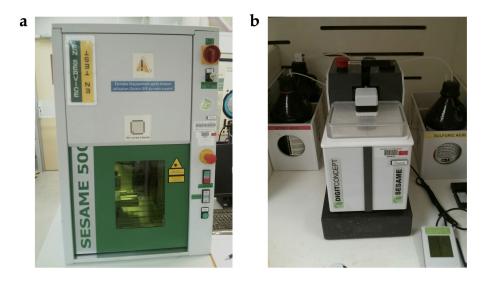

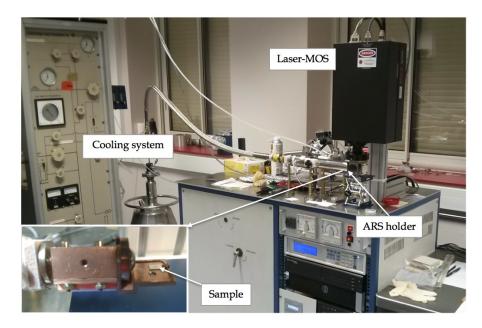

|   |                                   |                                                | 2.3.1.1 Electro-thermal test bench                    | 39 |  |  |  |

|   |                                   |                                                | 2.3.1.2 Electro-thermal test conditions               | 39 |  |  |  |

|   |                                   | 2.3.2                                          | Test Satie Laboratory                                 | 43 |  |  |  |

|   |                                   |                                                | 2.3.2.1 Electro-thermal test bench                    | 43 |  |  |  |

|   |                                   |                                                | 2.3.2.2 Electro-thermal test conditions               | 45 |  |  |  |

|   |                                   |                                                | 2.3.2.3 Supplementary characterizations               | 45 |  |  |  |

| 3 | MIC                               | ROSTR                                          | UCTURAL CHARACTERIZATION                              | 51 |  |  |  |

|   | 3.1                               | Packag                                         | ge decapsulation                                      | 52 |  |  |  |

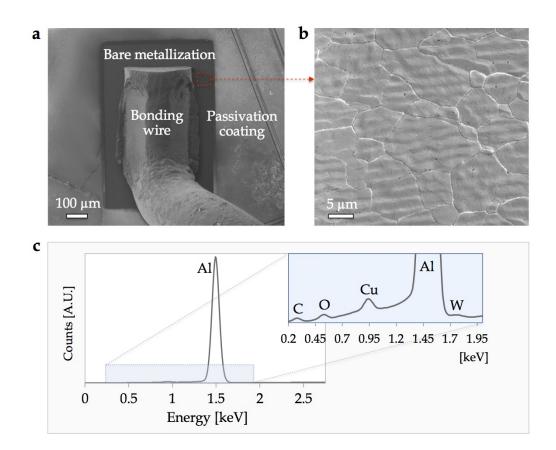

|   | 3.2                               | Surface analysis                               |                                                       |    |  |  |  |

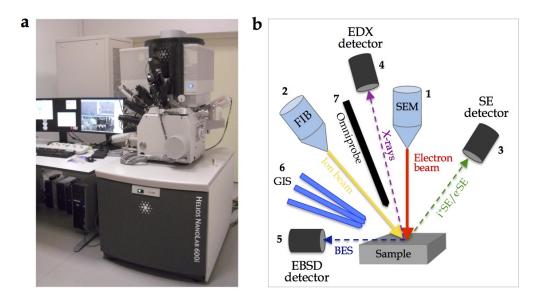

|   | -                                 | 3.2.1                                          | Scanning Electron Microscopy and Energy Dispersive X- |    |  |  |  |

|   |                                   |                                                | Ray Spectroscopy                                      | 54 |  |  |  |

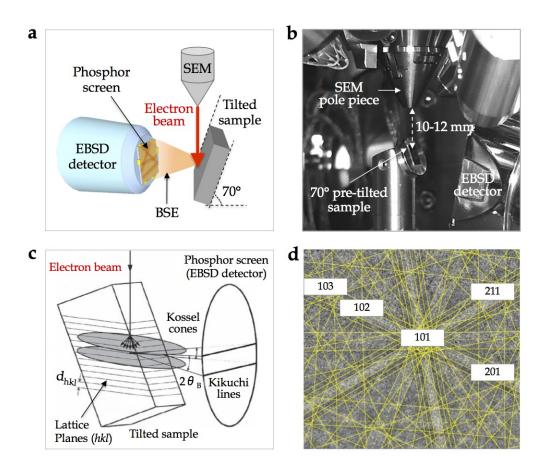

|   |                                   | 3.2.2                                          | Electron Backscattered Diffraction                    | 55 |  |  |  |

|   | 3.3 Bulk cross-sectional analysis |                                                |                                                       |    |  |  |  |

## X CONTENTS

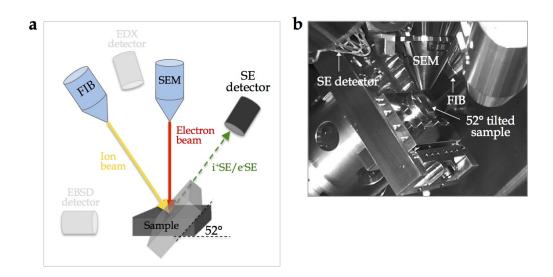

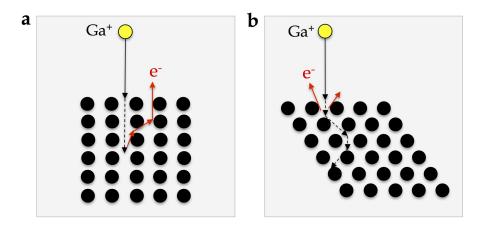

|   |     | 3.3.1   | Focused    | ion beam milling and microscopy                   | 60       |

|---|-----|---------|------------|---------------------------------------------------|----------|

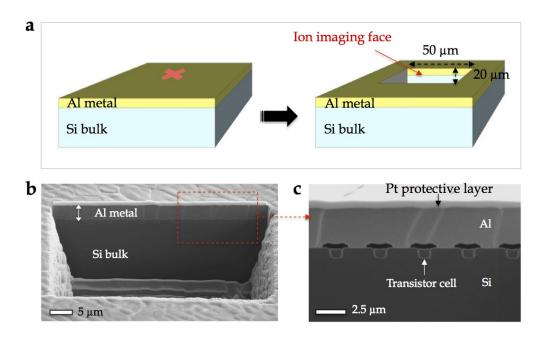

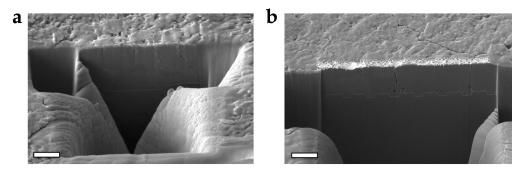

|   |     |         | 3.3.1.1    | Naked metal cross-section                         | 61       |

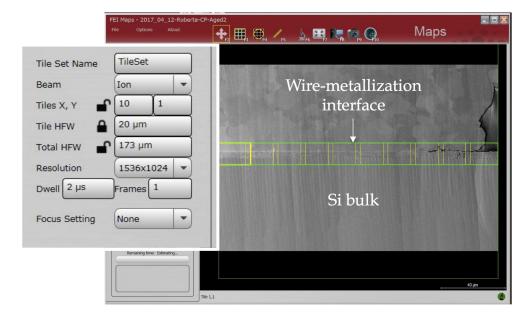

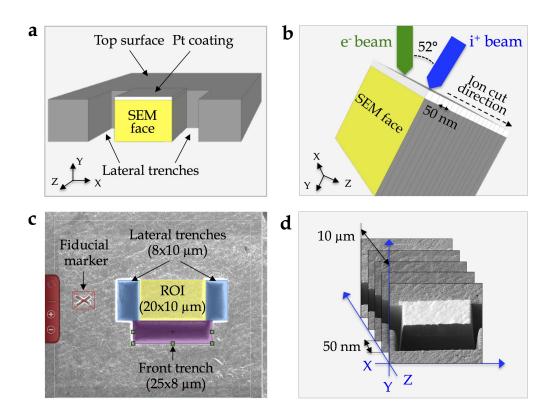

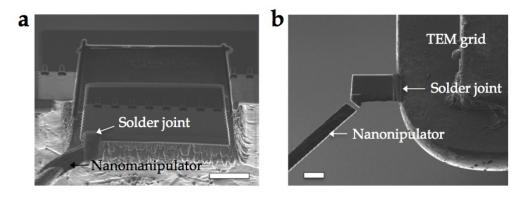

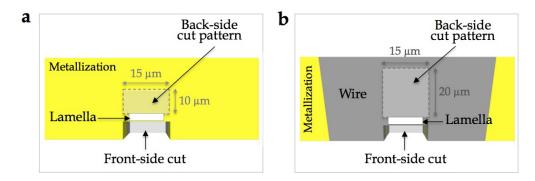

|   |     |         | 3.3.1.2    | Wire-metallization interface preliminary prepa-   |          |

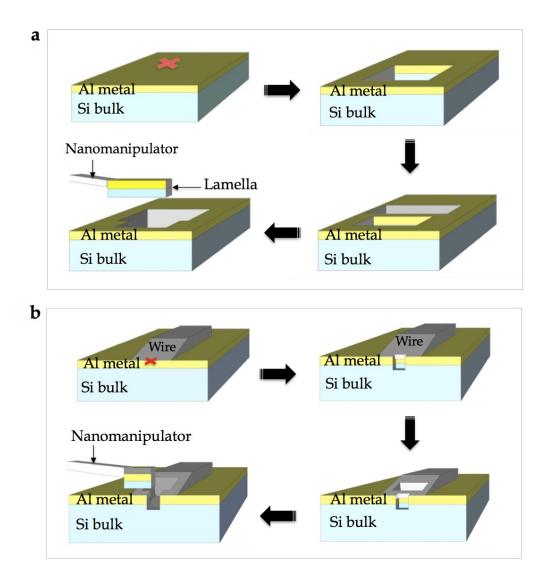

|   |     |         |            | ration                                            | 63       |

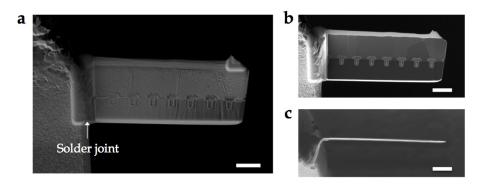

|   |     |         | 3.3.1.3    | Metal under the bonding wire cross-section        | 65       |

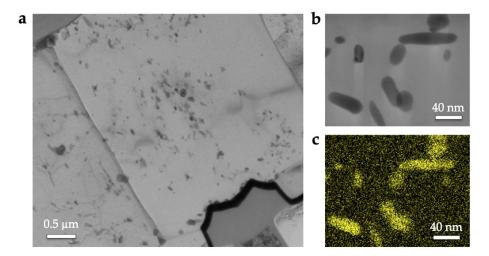

|   |     | 3.3.2   | Cross-po   | blisher milling and ion imaging                   | 67       |

|   |     |         | 3.3.2.1    | Preliminary sample preparation                    |          |

|   |     |         | 3.3.2.2    | SEM, SIM and EDX analysis                         | 69       |

|   |     | 3.3.3   | Focused    | ion beam tomography                               |          |

|   | 3.4 | Finer o | cross-sect | ional analysis                                    | 74       |

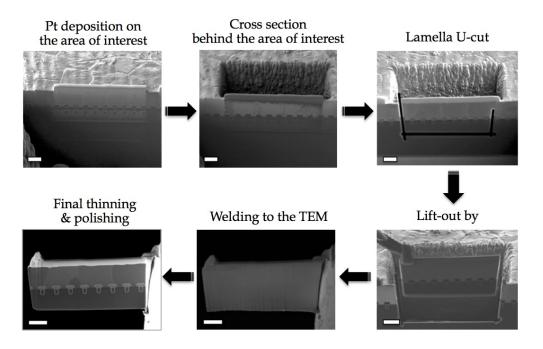

|   |     | 3.4.1   | TEM lan    | nella preparation by FIB                          | 76       |

|   |     |         | 3.4.1.1    | Why we used the FIB                               |          |

|   |     |         | 3.4.1.2    | Sample preparation protocol                       |          |

|   |     |         | 3.4.1.3    | Lamella preparation at the wire-metal interface . |          |

|   |     | 3.4.2   | TEM tec    | hniques                                           |          |

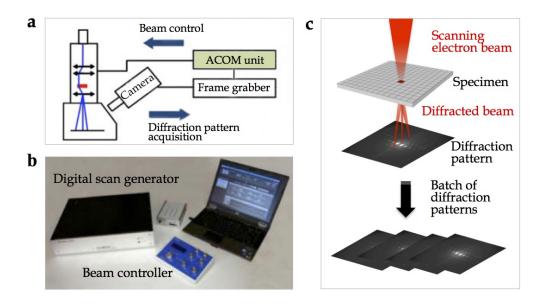

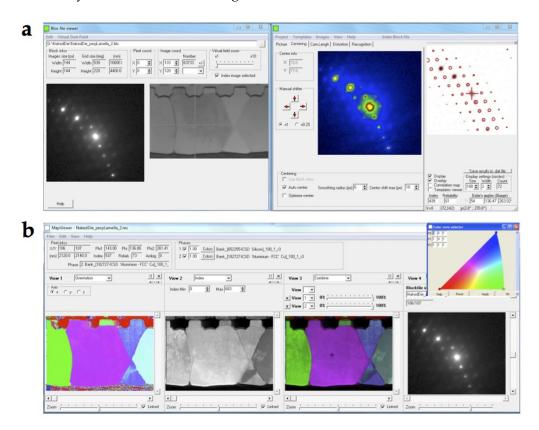

|   |     |         | 3.4.2.1    | Automated Crystal Orientation Mapping             |          |

|   |     |         | 3.4.2.2    | Chemical Analysis: EDX and EELS                   | -        |

|   |     |         | 3.4.2.3    | In situ heating experiment                        | 88       |

| 4 | RES | ULTS    | 5. 5       | 0                                                 | 89       |

| • | 4.1 | Aging   | of SPDoe   | 6 components                                      |          |

|   | •   | 4.1.1   |            | phical study                                      |          |

|   |     | •       | 4.1.1.1    | As-is metallization microstructure                |          |

|   |     |         | 4.1.1.2    | Aged metallization microstructure                 |          |

|   |     | 4.1.2   | •          | ctional study                                     |          |

|   |     | •       | 4.1.2.1    | Naked metallization                               |          |

|   |     |         | 4.1.2.2    | Metallization under the bonding wire              |          |

|   |     | 4.1.3   | •          | ture cycles: TEM heating in situ experiments      |          |

|   | 4.2 |         | -          | r7 components                                     |          |

|   | •   | 4.2.1   | -          | netallization cross-sectional study               |          |

|   |     |         |            | Cracks propagation statistics                     |          |

|   |     |         | 4.2.1.2    | Cracks propagation under the passivation layer .  |          |

|   |     | 4.2.2   | Metalliz   | ation under the bonding wire                      |          |

|   |     | •       |            | Wire-metallization interface                      |          |

|   |     |         | •          | Plastic deformation due to the bonding process    |          |

|   |     |         | •          | - Statistics                                      | 125      |

|   |     | 4.2.3   | In depth   | investigation of the whole wire-metallization in- |          |

|   |     | 1 2     | -          | y Cross Polisher preparation                      | 130      |

|   |     |         | 4.2.3.1    | Plastic deformation of the initial metallization  |          |

|   |     |         |            | under the bonding wire                            | 133      |

|   |     |         | 4.2.3.2    | Crack propagation in the metal and semicon-       | 55       |

|   |     |         |            | ductor of the aged modules                        | 136      |

|   |     |         |            |                                                   | <u> </u> |

| 5 | DISC       | CUSSION 14                                                                |             |  |  |

|---|------------|---------------------------------------------------------------------------|-------------|--|--|

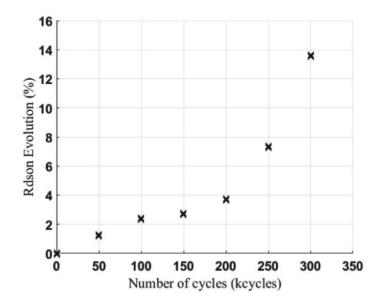

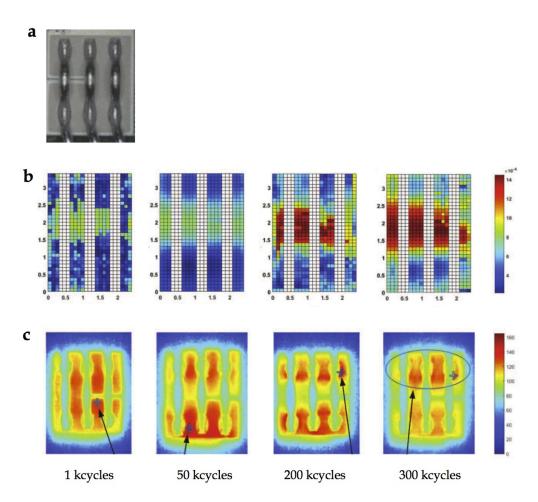

|   | 5.1        | 5.1 $R_{ds(on)}$ evolution during electro-thermal aging                   |             |  |  |

|   |            | 5.1.1 Potential and temperature mapping                                   | 148         |  |  |

|   | 5.2        | Source metallization reconstruction and crack propagation                 | 152         |  |  |

|   |            | 5.2.1 Possible deformation mechanisms                                     | 155         |  |  |

|   |            | 5.2.2 Plasticity by dislocation propagation                               |             |  |  |

|   |            | 5.2.3 Plasticity by atom diffusion                                        |             |  |  |

|   |            | 5.2.4 Plasticity by electromigration                                      |             |  |  |

|   |            | 5.2.5 Fatigue crack propagation: SPDo6 vs To7D17                          | 162         |  |  |

|   |            | 5.2.6 Passivation and temperature effect on crack propagation.            | 164         |  |  |

|   | 5.3        | Weakening of the bonding connections                                      | 167         |  |  |

|   |            | 5.3.1 Initial wire-metallization interface                                |             |  |  |

|   |            | 5.3.2 Initial Plastic deformation                                         | 171         |  |  |

|   |            | 5.3.3 Aging in the metallization under the bonding wires                  |             |  |  |

|   |            | 5.3.4 Crack propagation during electro-thermal aging                      | 173         |  |  |

| 6 | CON        | ICLUSION AND PERSPECTIVES                                                 | 177         |  |  |

|   |            |                                                                           | -           |  |  |

| Ι | AP         |                                                                           | 183         |  |  |

| Α | CON        | IVENTIONAL CROSS-SECTION TEM SAMPLE PREPARATION                           | 185         |  |  |

| В | CUR        | EVATURE EXPERIMENT                                                        | 189         |  |  |

| П | RÉ         | SUMÉ ÉTENDU                                                               | 195         |  |  |

| C |            | DES DE FATIGUE DES MÉTALLISATION À BASE D'ALUMINIUM :                     |             |  |  |

| C | C.1        | introduction et objectifs                                                 |             |  |  |

| , |            | Technologie LFET <sub>1</sub> T et vieillissement accéléré des composants |             |  |  |

|   | 0.2        | C.2.1 Technologie LFET1T                                                  |             |  |  |

|   |            | C.2.2 Tests de vieillisssement accéléré                                   |             |  |  |

|   | с.3        | Techniques expérimentales de characterization microstructurelle           | 199         |  |  |

|   | 0.5        | de la métallisation                                                       | 200         |  |  |

|   | C.4        | Etude du vieillissement de la metallisation et des fils de connextion     |             |  |  |

|   | 0.4        | C.4.1 Métallisation nue (hors zone de bonding)                            | <u> </u>    |  |  |

|   |            | C.4.2 Interface métallisation / fils                                      | -           |  |  |

|   | C.5        | Fissuration dans le semiconducteur                                        |             |  |  |

|   | с.5<br>с.б | Conclusions et perspectives                                               |             |  |  |

|   | 0.0        |                                                                           | <b>_</b> 10 |  |  |

|   |            |                                                                           |             |  |  |

# BIBLIOGRAPHY

219

# KEYWORDS

- Low voltage power MOSFETs

- Failure analysis

- Accelerated electro-thermal aging test

- Plastic deformation

- Fatigue mechanisms

- Wire-metallization interface

- Metallization microstructure aging

- Electron microscopy

- Ion microscopy

- Grain structure mapping

# INTRODUCTION

Over the last few decades, the automotive industry has started to progressively replace electro-mechanical components by purely electronic devices or miniaturized electro-mechanical systems based on Si-technologies. This paradigm shift has initially involved support electronic systems (e.g. ABS, power-assisted steering, speed limiter, air conditioning, etc.). However, the constant technology evolution and miniaturization have rapidly broadened the field of application of electronics in automotive, involving the main vehicle functions (e.g. propulsion, lighting, brakes, engine, fan control, battery management etc.) and increasingly replacing the conventional mechanical and hydraulic loads.

Nowadays, the power electronic sector is the strongest growth market in automotive. Semiconductor-based power switches are rapidly replacing conventional electromechanical relays in most of the main vehicles functions as well as in comfort, safety and communication applications. An additional growing segment is represented by the market for alternative propulsion technologies, in line with the new regulations for road transport aimed at the reduction of greenhouse gas emission level (30% lower by 2030 in the EU). This trend is seen nowadays with more and more focus on electric vehicle concepts, pure (EV) and hybrid (i.e. micro-, mild-, full-, plug-in-hybrid), until the most recent projects of autonomous cars.

The rise in electronic technology in automotive inevitably creates new demands in terms of low costs, operation under extreme environmental conditions (temperature, humidity, vibration, etc.), greater system power density, increasing miniaturization, etc. Moreover, high levels of reliability are of course required to guarantee the safety of products and people over extended periods of time. This requires an in-depth knowledge of the possible evolutions of the electronic components as a function of operating time and failure mechanisms. Failure analysis and reliability studies are, then, key steps in the manufacture industry, in order to develop devices that are 100% reliable during their lifetime. This life-time is one of the parameters required by car manufactures, among others, defined by the Automotive Electronic Council (Qualifications documents, e.g. AEC-Q100, AEC-Q200, etc...).

This work is motivated by the comprehension of the failure mechanisms occurring in power electronic switches produced by NXP Semiconductors company for the automotive industry. During their normal life, these components undergo high power levels over a long time, leading to gradual reduction of

#### 2 INTRODUCTION

their performance. Here, we present a method to assess the device electrothermal aging, focusing on a specific study case: power switches, based on the MOSFET (Metal Oxide Semiconductor) technology, used for the automobile lightning system. This application is particularly aggressive for MOSFET components because it involves repetitive on/off cycles associated with high electrical pulses and large temperature excursions, leading to a progressive alteration of the device's initial performances. In particular, its initial resistance in the "ON" state increases over time, which in turn, increases its operating temperature. Our objective is to investigate the phenomena behind the degradation of the microstructure of the critical parts of these devices that have been identified as the metallic ones, probably because of their susceptibility to plastic deformation. This would allow us to determine physical models that can explain the main failure mechanisms to be correlated with the progressive worsening of the whole device electrical performances. To do this, we have settled new dedicated techniques and quantification methods to assess the aging of the metal parts of MOSFET devices.

In the first chapter, we present the state of the art of power electronics technologies. Then, we focus on low-voltage MOSFET power devices used in car applications and we present the LFET1T components, the e-switches from NXP Semiconductors under investigation. We also go through the main reliability issues associated to this kind of devices. They are related to the complex structure of the power component, which integrates different materials at different scale. We explain why, the source metallization and bonding wires are the parts of the LFET1T technology where failure is the most prone to happen in the most recent technologies. Finally we present the electro-thermal aging tests that we have used to accelerate the device degradation and failure.

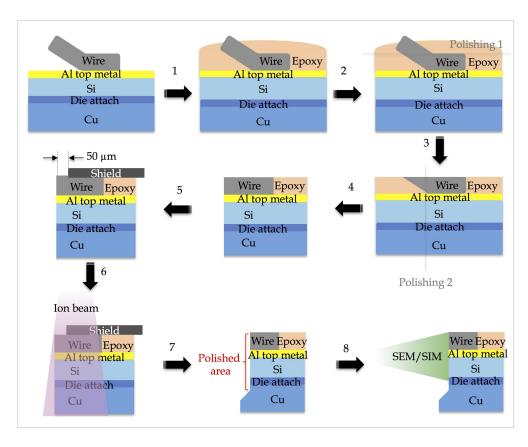

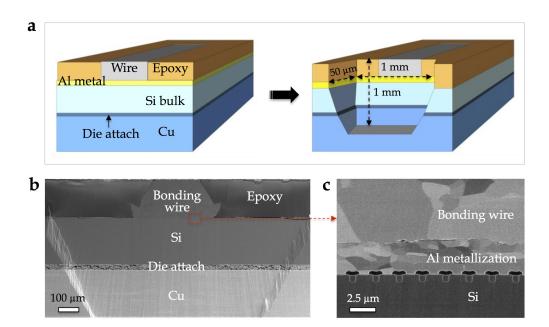

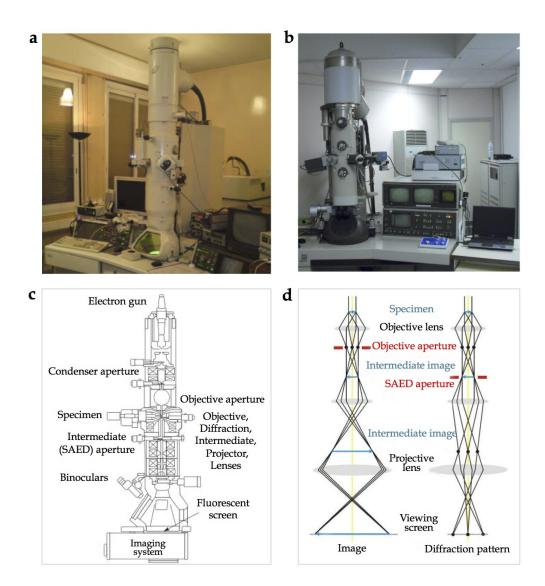

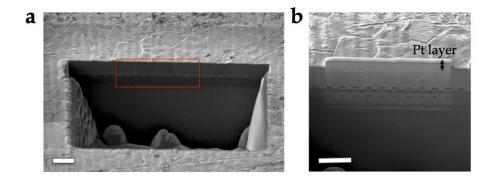

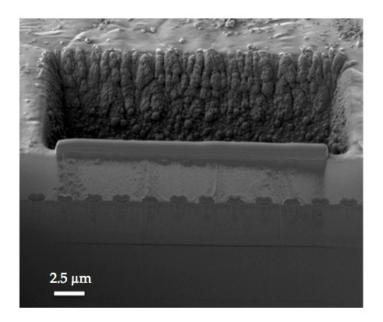

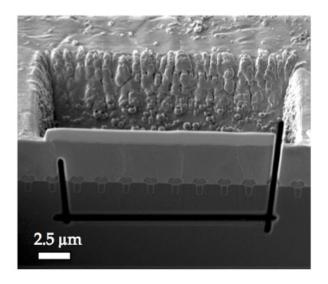

The second chapter details the specific physical metallurgy techniques that we set up in order to characterize the microstructure of the source metallization during aging at two main locations: away and under the bonding connections. These techniques consist essentially in electron and ion microscopy, and grain structure mapping. Because of the complexity and fragility of the device structure, dedicated sample preparations are also needed and described. We try to point out the choices that have motivated the established experimental protocol and the contribution of each technique to the comprehension of the degradation mechanisms.

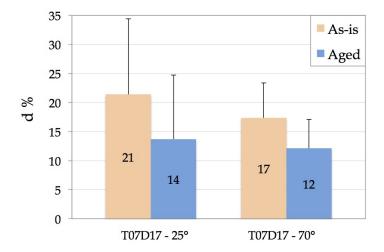

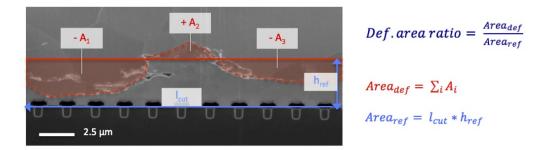

In the third chapter we introduce the results of the microstructural characterization of the metallic parts of LFET1Ts for 12V and 24V battery applications. We compare the metal microstructure away and under the bonding wires, and we follow its evolution during aging. The contacted metallization is a critical location because the bonding process induces plastic deformation prior to aging. We show that the main mechanism behind the metallization degradation is the generation and propagation of intergranular fatigue cracks in both locations. Then, we describe and use original quantification methods that allow us, for the first time, to assess the initial plastic deformation induced by the bonding process and the crack propagation during aging.

These results are discussed in detail in chapter 4. We try to highlight the universal degradation mechanisms behind the electro-thermal aging of the metal and show that many parameters can influence the potential evolution of its microstructure, such as the composition of metallization and wire, the grain size, the interface created between the two metals. At the beginning of the chapter we also show the link between the on-state resistance of the device and the increasing in temperature of the power modules during aging.

Final considerations and possible perspectives of our study conclude this dissertation.

# 2

# POWER ELECTRONICS FOR THE AUTOMOTIVE INDUSTRY, FAILURE MODES AND RELIABILITY ISSUE

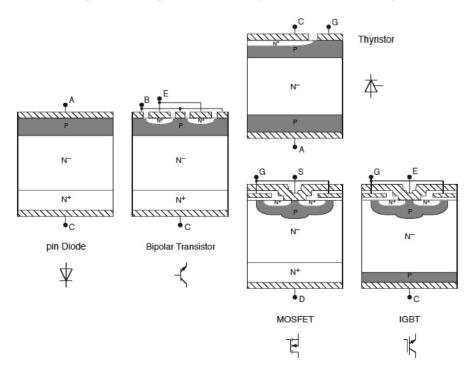

At present, power electronics is the most advanced electrical energy conversion technology that attains both high flexibility and efficiency. As an engineering field, power electronics came into existence about 60 years ago, with the development and the market introduction of the so-called silicon controlled rectifier, known today as the thyristor [Oweo7] [Holo1] [Lut11]. The structures of today's most important power semiconductor devices are shown in Fig. 1. Details on each power component will be given in the following section 2.1.

Figure 1: Basic structures of common power semiconductor devices [Lut11].

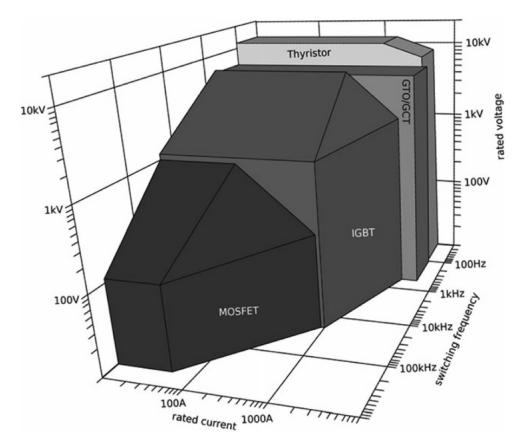

Fig. 2 illustrates the practical application range of each type of silicon device in classical switching power converters. Note that for these applications the operation ranges are within a hyperboloid. This suggests that the product of switching power (product of maximum voltage and current) and switching frequency that can be attained per device in practical conversion systems using silicon devices appears to be fairly constant. This frequency-power product is a good performance indicator for how well the designer was able to maximize utilization of the power semiconductors and to improve the power density of the converter [Lut11]. For high power applications (>  $10^3$  kW), a GTO (gate turn-off) thyristor would be the first choice. However, they will be limited by a low switching frequency. On the other hand, for lower power applications, different possibilities could be taken into account depending on the switching frequency: bipolar transistor for low frequencies (< 10 kHz), the IGBT for medium frequencies (10-100 kHz) and MOSFET for high frequencies (> 100 kHz).

Figure 2: Operating range of silicon power semiconductor devices [Lut11].

In our study, we focus on smart power devices used as switches in automotive applications that require low power and high switching frequency. Thus, we will see that they are based on MOSFET technology, in particular vertical MOSFET controlled by a "smart" circuit that have sensor and protection functions [San99] [Turo3].

The devices under test will be described in section 2.2, together with the main reliability issues intrinsic to the structure and application field of the

devices. On the base of the failure analysis conducted on previous technologies developed by NXP [Mar10] [Mar14] [Kh007b] [Kh005], the weakest parts of the power device complex architecture have been identified as the metallic ones. In this work we will focus, thus, on the failure mechanisms involving the source electrode metallization and the relative bonding connections.

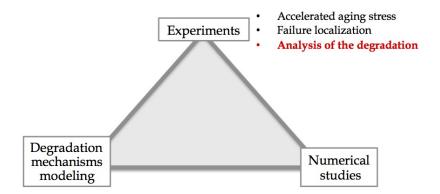

Our method to understand the physical mechanisms behind the device failure is described in section 2.3 and consists in putting the devices under accelerated electro-thermal aging and follow the degradation of the metal microstructure during aging. In this section we will focus on the description of the test protocols, whereas the physical metallurgy approach, used to study the metallization degradation mechanism and constituting the main part of this work, will be detailed in the next chapter.

#### 2.1 POWER ELECTRONICS TECHNOLOGY EVOLUTION

This part provides an insight into the main basic structures of power semiconductor device. It has the purpose to summarize the evolution of the semiconductor electronics since the bipolar transistor until the more recent technologies, in terms of structure and operational mode.

#### 2.1.1 Bipolar transistor

The bipolar transistor, or Bipolar Junction Transistor (BJT), was invented in 1948 at the Bell Laboratories by John Bardeen and Walter Brattain under the direction of William Shockley [Sho52]. The basic function of a BJT is to amplify current and they are then used in integrated circuits as amplifiers or switches.

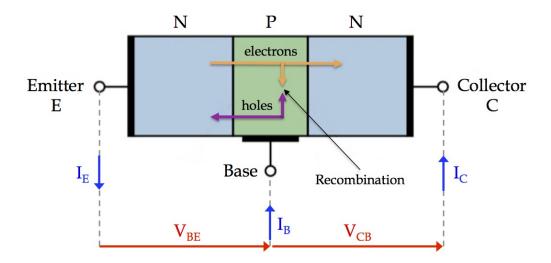

A bipolar transistor consists of a three-layer sandwich of doped semiconductor materials, either NPN or PNP, separated by two PN junctions. The N areas contain an excess of electrons, whereas the P area an excess of holes (or a lack of electrons). The principle of operation of the two transistor types, PNP and NPN, is exactly the same the only difference being in their biasing and the polarity of the power supply for each type. A BJT has three terminals connected to the three doped regions: emitter, collector and base. In a NPN transistor, represented in Fig. 3, the base terminal is connected to the central P-type region, whereas in the PNP type to the central N-type one. The electrical parameters of a BJT are the  $I_E$ ,  $I_C$  and  $I_B$  that are respectively the emitter, collector and base voltage respectively.

If a tension  $V_{BE}$  is applied to the transistor, an electron current flows from the emitter to the base because of the difference of potential between the two electrodes. These electrons can diffuse until the collector, by applying a reverse

tension between the collector and the base (V<sub>CB</sub>). In this configuration, a current flows from the emitter to the collector by applying a tension at the base (common base configuration). At this point, if V<sub>CE</sub> is lower than a threshold (V<sub>CE lin</sub>), then an important electron-hole recombination takes place at the base and the I<sub>C</sub> current gain is low (saturation region). On the other hand, if the V<sub>CE</sub> is higher enough (V<sub>CE</sub> > V<sub>CE lin</sub>), then majority of the electrons are collected at the collector terminal. The transistor operates in the linear region and the current I<sub>C</sub> is independent from the applied tension V<sub>CB</sub>.

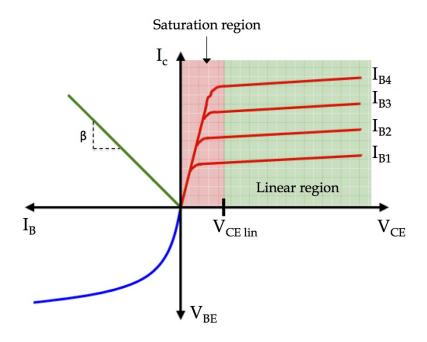

Fig. 4 shows the qualitative characteristic curves of a BJT. The plot summarize the three regions of operation: the saturation, the cutoff, the active (each family of curves is drawn for increasing  $I_B$  values):

- 1. Cutoff region: the base-emitter junction is reverse biased, then no current flows in the device.

- 2. Saturation region ( $V_{CE} < V_{CE lin}$ ): the base-emitter and collector-base junctions are forward biased, with  $V_{CE} < V_{BE}$ . I<sub>C</sub> reaches a maximum value which is independent from  $V_{CE}$ .

- 3. Linear region ( $V_{CE} > V_{CE \text{ lin}}$ ): the base-emitter junction is forward biased, while the collector-base junctions is reverse biased, with  $V_{BE} < V_{CE} < V_{CC}$ . I<sub>C</sub> is proportional to I<sub>B</sub>, I<sub>C</sub> =  $\beta$ I<sub>B</sub>. The transistor can be considered as a current amplifier with gain  $\beta$ .

Figure 3: Bipolar transistor general structure.

Figure 4: Electrical characteristic curves of a NPN bipolar junction transistor. The blue curve corresponds to  $V_{BE} = f(I_B)$ . The red curves correspond to  $I_C = f(V_{CE})$  at increasing  $I_B$  values. The red area ( $V_{CE} < V_{CE lin}$ ) indicates the saturation region whereas the green one ( $V_{CE} > V_{CE lin}$ ) the linear region. The green curve corresponds to  $I_C = f(I_B)$ .  $\beta$  is the curve slope, that is the device gain.

#### 2.1.2 Thyristor

Silicon controlled rectifier or thyristor is a family of semiconductor devices introduced by W. Shockley in 1950 [Sho51] and later developed by Ebers [Ebe52] [Mol56] [Mue58] as an evolution of the bipolar transistor.

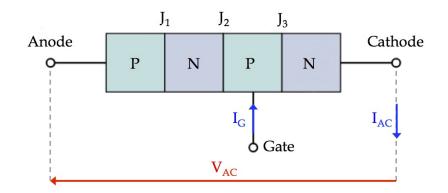

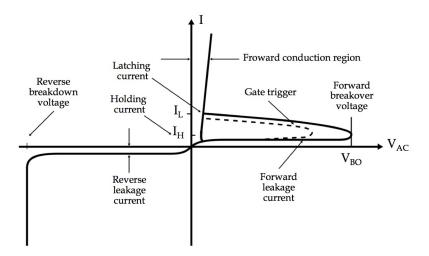

Thyristor is basically a four layered pn junction device, with two p and two n portions and three p-n junctions  $J_1$ ,  $J_2$ ,  $J_3$  (Fig. 5). It has three terminals, the anode and the cathode across the four layers, and the gate attached to the p-type layer near the cathode. As represented in Fig. 6, the thyristor operates in three different modes:

- Reverse blocking mode: the device is reverse-biased and behaves as a blocking diode.

- Forward blocking mode: voltage between anode and cathode (V<sub>AC</sub>) is applied in the direction that would cause the diode to break down, but the thyristor is not triggered into conduction.

- Forward conducting mode: the thyristor has been triggered into conduction (V<sub>AC</sub>>V<sub>BO</sub> or I<sub>G</sub>>0) and will remain conducting until the forward current drops below a threshold value (I<sub>AC</sub>< I<sub>H</sub>) known as the "holding current".

When the anode is at a positive potential  $V_{AC}$  with respect to the cathode with no voltage applied at the gate, junctions J1 and J3 are forward biased, while junction J<sub>2</sub> is reverse biased. As J<sub>2</sub> is reverse biased, no conduction takes place (Off state). Now if  $V_{AC}$  is increased beyond the breakdown voltage  $V_{BO}$  of the thyristor, avalanche breakdown of J<sub>2</sub> takes place and the thyristor starts conducting (On state). If a positive potential  $V_G$  is applied at the gate terminal with respect to the cathode, the breakdown of the junction J<sub>2</sub> occurs at a lower value of  $V_{AC}$ . This means that the value of  $V_G$  trigger the switching frequency of the thyristor. Once avalanche breakdown has occurred, the thyristor continues to conduct, independently from the gate voltage  $V_G$ , until the potential  $V_{AC}$  is removed or the current through the device (I<sub>AC</sub>) becomes less than the holding current specified by the manufacturer (I<sub>H</sub>).

Figure 5: Thyristor general structure. Without the application of any voltage, it has three diffusion regions. If we apply a positive voltage at the anode with respect to the cathode, the junctions  $J_1$  and  $J_2$  become forward biased while  $J_2$ is reverse biased. In this state, if a positive signal is applied at the gate terminal,  $J_2$  turns to forward biased state and current starts to flow. On removal of gate signal, the current continues to flow as charge is drifted from anode to cathode.

Figure 6: Thyristor static characteristic curve. The thyristor works under three modes: forward conducting mode, forward blocking mode and reverse blocking mode. The minimum anode current that causes the device to stay at forward conduction mode as it switch from forward blocking mode is called the latching current. If the SCR is already conducting and the anode current is reduced from forward conducting mode to forward blocking mode, the minimum value of anode current to remain at the forward conducting mode is known as the holding current.

#### 2.1.3 MOSFET transistor

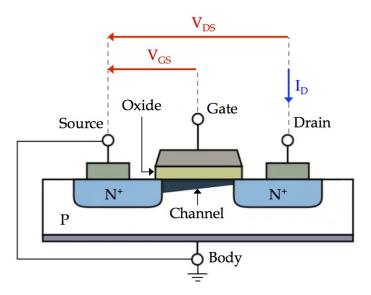

A MOSFET transistor (Metal Oxide Semiconductor Field Effect Transistor) is a semiconductor-base device widely used as switch or signal amplifier in electronic integrated circuits, with applications at high frequencies. The basic principle of the field effect transistor was first patented by Julius Edgar Lilienfeld in 1930 [Lil26], but it's only about thirty years after that Martin Atalla [Sho51] and Dawon Kahng [Sho51] from the Bell Laboratories developed the first MOSFET examples.

The main feature of the MOSFET transistors is the use of an electrical field to control the conductivity of a thin channel inside the semiconductor material. They distinguish operationally and structurally from the bipolar junction transistors since they involve single-carrier-type operation. Two different types of MOSFET exist, depending on the type of charge carriers flowing through the channel: holes in pMOSFETs and electrons in nMOSFETs. These, in turn, can work in depletion or enhancement mode, according to the polarisation of the device. In the following we will consider an n-type enhancement MOSFET as example to describe the transistor operational mode.

A MOSFET transistor consists in four electrodes, represented in Fig. 7: source (S), drain (D), gate (G) and the body (B). It is composed primarily by a large block, the body, of p-type silicon. Into the body, two regions of heavily doped n-type silicon are created to form the source and the drain. Gate is the controlling terminal and it is isolated from the rest of the transistor by an oxide layer sitting between the gate and the channel. This prevents current from flowing into/out of the gate, resulting in a high input impedances  $(10^{12} - 10^{14}\Omega)$  and a low power consumption, which make the MOSFET the fastest component during switching operations.

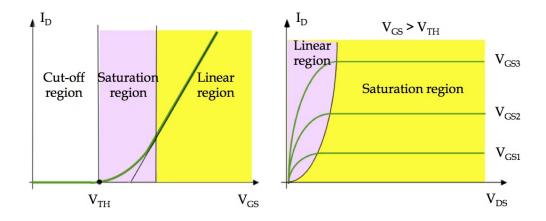

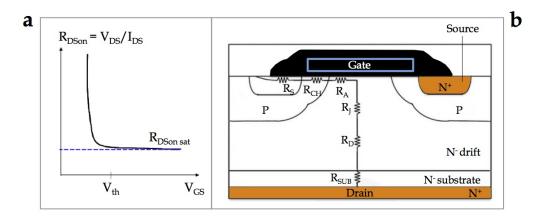

The transistor operation modes are represented in Fig. 8a and 8b, which describe respectively the  $I_D$ - $V_{GS}$  and  $I_D$ - $V_{DS}$  characteristic curves. By applying a potential difference between the gate and the body, the conductive characteristics of the channel region can be changed to allow current flow. If a small positive voltage is applied between gate and body ( $V_{GB}$ ), the positive potential at the gate repels part of the charges creating a region with a small negative charge known as depletion region. As  $V_{GB}$  is increased, the depletion region grows. When  $V_{GB}$  is increased beyond some threshold voltage (typically a few V) an inversion layer of electrons is formed near the gate. This provides a conductive channel between drain and source which allows current to flow between source and drain and voltage drop across the two terminals. The body is generally internally connected to the source. This means that the gate to base voltage  $V_{GB}$  is the same as the gate to source voltage  $V_{GS}$  and to create the inversion layer  $V_{GS}$  needs to be above the threshold voltage ( $V_{th}$ ). If  $V_{GS}$

is less than V<sub>th</sub>, no inversion layer is present and so no current can flow between source and drain and the transistor is said to be cut-off. When  $\ensuremath{V_{\text{GS}}}$  is greater or equal to  $V_{th}$ , the transistor is conductive. At this point, if  $V_{DS} > 0$ , the positive charge of the drain pulls electron away from the channel to be more distributed around the drain, where the inversion layer is smaller and the depletion region is larger than near the source. In this region, where  $V_{GS} > V_{th}$ and  $V_{DS} < (V_{GS} - V_{th})$ , the transistor is in the linear (or ohmic) region. It behaves as a voltage controlled resistor, where V<sub>GS</sub> controls the resistance. The current I<sub>D</sub> does not depend on V<sub>DS</sub>. As V<sub>D</sub> is increased, the depletion region near the drain continues to get larger and the inversion layer near the drain continues to shrink. At some point, the inversion layer entirely disappears and the drain is said to be pinched-off. Current still flows between source and drain and the potential difference is so large between the two terminals that electrons are able to push through the pinched-off area that contains few carriers. However, further increases in V<sub>D</sub> results in minimal further increases in current, as the additional potential overcome the increased pinched-off region. The transistor is said to be in the saturation region.

Figure 7: General structure of a nMOSFET. Under a positive V<sub>GS</sub>, the charge carriers flow through the channel between source and drain.

Figure 8: n-type MOSFET characteristics (a)  $I_d = f(V_{DS})$  and (b)  $Id = f(V_{GS})$

#### 2.1.4 IGBT transistor

Insulated Gate Bipolar Transistor (IGBT) is the functional integration of power MOSFET and BJT devices in monolithic form. IGBT was developed in the 1980s by B.W. Scharf and J.D. Plummer to provide a superior alternative to bipolar power transistors [Rus83] [Bal84]. It combines the gate-drive characteristics of MOSFETs (high input impedance and application at high frequency) with the high-current and low-saturation-voltage capability of bipolar transistors (low on state power loss), to achieve the optimal device characteristics. The structure of an IGBT is very similar to a vertical MOSFET (see next section) with the difference that the block connected to the drain terminal is a N<sup>+</sup>-type substrate in the vertical MOSFET, whereas in an IGBT it is P<sup>+</sup>-substrate (Fig. 9). For this reason the IGBT is often described as an N-channel power MOSFET on top of a p+ type substrate. IGBTs operate in a similar way to MOSFETs. An inversion layer is formed in the  $P^+$  area by applying a tension at the gate. However, if the potential of the collector is increased, the flow of electrons draws positive charges from the p-type substrate into the drift region, significantly increasing the conductivity of the channel region and dramatically reducing the voltage of the IGBT. This property gives the IGBTs a higher current density and capability compared to similarly gate-driven MOSFETs, resulting in low on-state power loss. Thus, IGBTs are specially designed to turn on and off rapidly in highcurrent applications.

#### 2.1.5 Recent solutions: trench technology

In the last years, power semiconductor electronics have rapidly evolved in order meet the requirements of new applications involving smaller and smaller

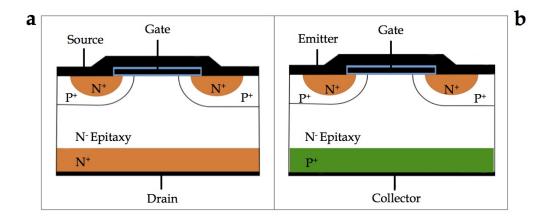

Figure 9: Comparison between (a) a vertical MOSFET and (b) an IGBT. The main difference consists in a n-type substrate in the vertical MOSFET and a p-type substrate in the IGBT (respectively in orange and green).

technology sizes and higher and higher current densities [Bayo8] [Isho4a] [Koro9]. The vertical trench technology is the most common configuration that we can find in the market nowadays, for both MOSFETs and IGBTs used in low power and high current densities application. In the following, a brief description of these components is provided, focusing, as example, on a MOSFET device, which is at the base of the technology under investigation in this work.

#### 2.1.5.1 Vertical MOSFET

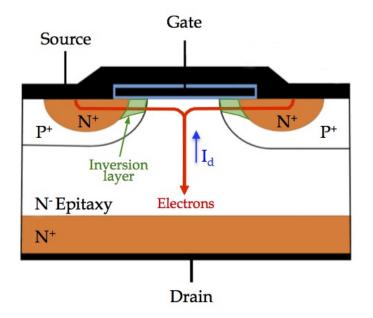

As suggested by the name, vertical MOSFETs (or VDMOS, Vertical Diffused MOS) differ from the lateral MOSFETs (Fig. 7) for their vertical structure (Fig. 10): the source electrode is placed over the drain, resulting in a current mainly vertical when the transistor is in the on-state [Mor96]. More precisely, the source is connected to a highly doped N<sup>+</sup> region that is confined insight a P region under the gate. The vertical channel is then formed between the latter and the N<sup>-</sup> region below, connected to the drain electrode by a N<sup>+</sup> layer. The working principle and electrical characteristic curves of a VDMOS are exactly the same of a planar MOSFET (Section 2.1.3):

- If the gate to source voltage (V<sub>GS</sub>) is lower than a threshold value (V<sub>th</sub>), a depletion layer is formed in the P area. The channel is isolated and the transistor is cut-off.

- When V<sub>GS</sub> is greater than V<sub>th</sub>, the carrier inversion layer is formed in the channel and the transistor is in the on state: an electron current, linearly proportional to the tension applied at the gate, flows from the source to the drain.

Thanks to its vertical structure, the main advantage of a VDMOS device consists in the possibility of a high integration of many small symmetrical cells connected in parallel to the same source metallization, at surface, and drain layer, which is directly connected to the device substrate. It is, then, the gate width that determines the number of cells which can be integrated in a single VDMOS device. Moreover, contrary to a planar structure, in which the current and breakdown voltage ratings are both functions of the channel dimensions, in a vertical structure, the voltage rating of the transistor is a function of the doping and thickness of the N<sup>+</sup> epitaxial layer, while the current rating is a function of the channel width. This makes it possible for the VDMOS to sustain both high blocking voltage and high current within a compact piece of silicon. For these reasons, vertical power MOSFETs are typically employed in applications that involve high power densities in single device packages of power modules.

Figure 10: Schema of a VDMOS.

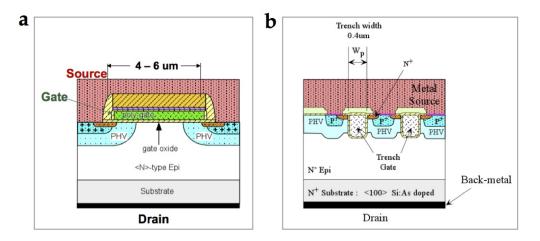

#### 2.1.5.2 Trench MOSFET

Different kinds of VDMOS exist depending on their structure: planar MOS, V-groove MOS (VMOS), trench MOS (UMOS), etc.

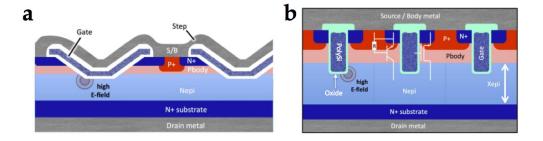

In a trench MOSFET, also called UMOS, the gate electrode is buried in a trench etched in the silicon. The comparison between a vertical v-groove structure (VMOS) and a trench structure is depicted in Fig. 11.

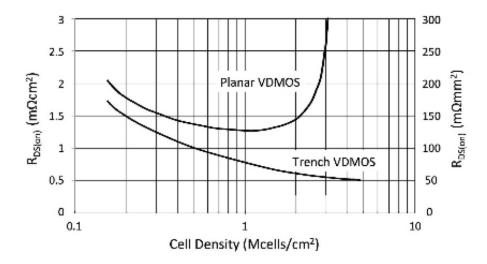

The fabrication process of a trench MOSFET is shortly described by Williams et al. [Wil17]. As shown in Fig. 11b after forming the VDMOS source and body regions, an etched trench of narrow width (e.g., 0.8 to 1.5 µm across) is oxidized to form a gate oxide lining the trench and subsequently filled with phosphorus in situ doped polysilicon. A polysilicon CVD deposition completely fills the trench, overflowing the etched trench onto the silicon surface. Except for a small masked area needed for gate contact, the polysilicon is then "etched back" so that the top surface of the polysilicon gate is recessed, but still overlapping the N<sup>+</sup> source. Subsequent thermal oxidation caps and seals the recessed polysilicon with a protective layer of oxide. A contact mask then selectively exposes the transistor's surface gate and its numerous cellular source/body regions to an oxide etch (while protecting the oxide above the trench). After contact etch, metal deposition and photolithographic patterning are performed interconnecting a series of separate and distinct trench VDMOS cells into a single three-terminal trench power MOSFET. Except for the polysilicon gate contact, the resulting die surface is nearly planar, so that problematic step coverage issues of the v-groove structure (Fig. 11a) are completely eliminated. The resulting cell pitch was half that of any other vertical device, improving channel-resistance, epitaxial current uniformity, and total R<sub>DS(on)</sub>. As represented in the graph of Fig. 12, increasing cell density of a trench MOS-FET decreases the devices R<sub>DS(on)</sub> hyperbolically. In contrast, planar VDMOS or VMOS exhibit a U-shaped dependence, declining in R<sub>DS(on)</sub> with increasing density before reaching a minimum, then rising rapidly at higher densities as a result of a decrease in channel packing density and poor current uniformity in the epitaxial layer [Wil17].

Figure 11: Cross section of (a) a v-groove VDMOS (or VMOS) and (b) of a trench gate vertical MOSFET (or trench VDMOS) [Wil17].

Figure 12: Impact of cell density on R<sub>DS(on)</sub>. Planar VDMOS exhibits a minimum while trench VDMOS benefits from scaling [Wil17].

## 2.2 SMART POWER MOSFET FOR THE AUTOMOTIVE INDUSTRY: RELIABIL-ITY ISSUE AND DESCRIPTION OF THE DEVICES UNDER TEST

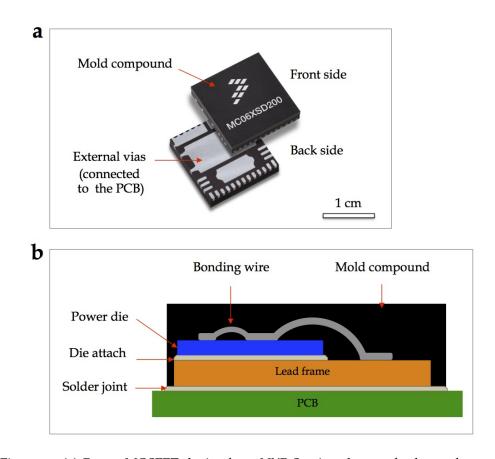

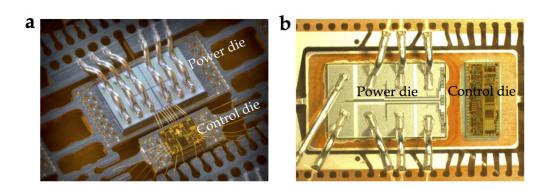

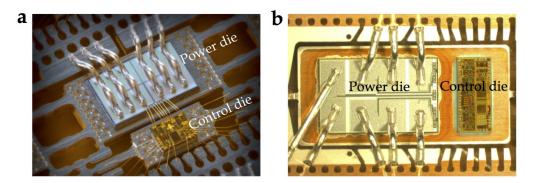

In this work we focus on low voltage MOSFET-based smart power devices used as lightning switches in car and truck applications. Fig. 13a shows an example of e-switch smart power MOSFET from NXP Semiconductors.

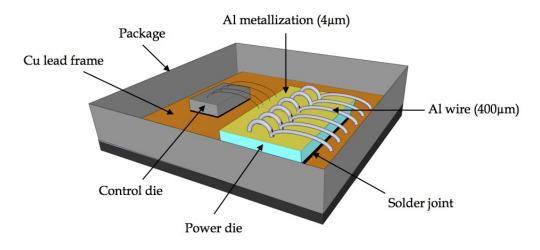

Fig. 13b represents the main parts composing the layered structure of a power device for standard low voltage applications:

- Power die. It is theMOSFET active area of the device, consisting mainly in the Si block coated by the source top metallization layer, generally made out of Al or Cu. In the "smart" power modules, the power die is connected to a control die (soldered on the same lead frame) with sensor and protection functionalities.

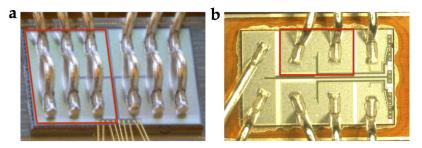

- Internal bonding connections. They allow a low-resistance current flow through the power die. Al or Cu bonding wires (Fig. 14a) are ones of the most common solution used at the moment. Several wire bondings, which a standard diameter that varies from few tens of micrometers to a maximum of 500µm, are connected in parallel in order to support and distribute high currents. Ribbon (Fig. 14b), clips and ball-bonding (Fig. 14c) are other examples of bonding internal connections that we can find in the commercial power devices.

- Lead frame. It serves primarily to support the chip mechanically during the assembly of plastic packages and to connect the chip electrically with

Figure 13: (a) Power MOSFET device from NXP Semiconductors for low voltage applications. (b) Schematic representation of the cross-section of the power MOSFET. The lead frame, made out of Cu, serves as heat sink and is directly soldered on the PCB. The bonding wires are cold welded on the Al top metallization by ultrasonic process. The device is encapsulated in a plastic mold compound.

Figure 14: Examples of internal bonding connections in a low voltage power module. (a) Cu bonding wires, (b) Al ribbons, (c) ball-bonding [San17].

the printed circuit board (PCB). It has also the function of a heatsink as it is made of a thick Cu plate.

- Solder joints. They allow the electrical and thermal contact between power die and lead frame and between lead frame and PCB. The most common alloys used nowadays are lead-free and are made out of tin, silver and copper (Sn-Ag-Cu). Many studies are focusing on these replacement solder materials [Lee17] and will be addressed later in section 2.2.2.1.

- Mold compound. It is the most widely used polymer-composite packaging material for encapsulating low voltage power devices [Proo3]. The main function of the epoxy-based package is to provide environmental and mechanical protection for the devices. It must deliver a balanced combination of properties in the areas of mechanical strength and toughness, chemical resistance, electric insulating performance, thermal conductivity and moisture stability in the range of -65 to 200 °C. In order to control thermal conductivity, internal stress characteristics and reliability performances, filler particles (commonly made out of silica or alumina) are integrated in the epoxy resin [Ham89].

#### 2.2.1 Stress conditions in power electronics for automotive

Power electronics for automotive must comply with standard qualification requirements described in the AEC-Q100 documents, developed by the Automotive Electronics Council (AEC) component technical committee. These documents contain detailed qualification requirements for integrated circuit and include failure mechanisms based stress test methods. Components meeting these specifications are suitable for use in the harsh automotive environment.

The basic standard lifetime requirements for passengers vehicles today are:

- Lifetime: 15 years

- Operation time: 10.000 hours

- Mileage: 300.000 km

In the following, we provide a short description of the main stresses at which power electronics for automotive are subject during their normal operational mode.

#### 2.2.1.1 Thermal stress

During their on-off operating cycles, power components undergo passive and active thermal cycles. They are subject to extremely diverse external climate

conditions. At the same time, when the vehicle is on, the motor compartment warms up to 130°C [Kaso1] [Bouo8]. This results in passive thermal cycles from - 40°C to 130°C [Sch10]. On the other hand, active thermal cycles correspond to the temperature increase due to Joule heating and thermal dissipation. The combination of these two stresses can severely influence the power electronics reliability, especially when the external temperature is high. In automotive applications, power devices are designed to tolerate a maximum operating temperature of 175°. When this value is reached, the integrated control circuit turns the device off as protection. The thermal amplitude in a single on-off cycle is not critical for the materials composing the device layered structure. However, the iteration of these thermal cycles induces important stresses in the electronics components during their life-time due to the difference in the coefficients of thermal expansion (CTE). These stresses can locally induce plastic deformation in the softest parts (solders, metallization, bonding wire, mold compounds) and cracks in the most fragile parts (oxides and silicon). This problem of CTE difference will be further addressed in "Source metallization" section (2.2.2.2).

#### 2.2.1.2 Electromagnetic stress

The electromagnetic interferences (due to high tension power lines, mobile phones, radio waves, etc.) and the vehicle system itself can cause a transient electrical noise that can interfere with the electrical components in the vehicle. Ignition and lighting system, electromechanical actuators, starters, alternators, etc. are the source of potential electromagnetic noise. The manufacturer must comply with electromagnetic compatibility and emission regulations [Mar11].

#### 2.2.1.3 Mechanical and chemical stress

Mechanical stress arises from the deformations and vibrations of the engine system. The parts that are the most sensitive to this stress are the solder joints and the bonding connections.

In addition, the devices are affected by environmental conditions as moisture, fog, saline atmosphere, etc. that can cause corrosion in the device components. The plastic packaging play an important role to protect the power device from the aggressive environmental factors.

#### 2.2.2 Failure modes in power MOSFETs

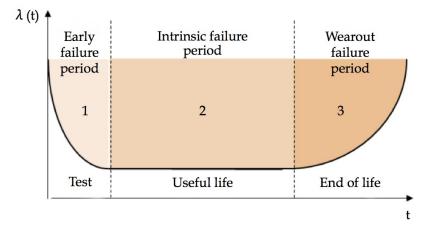

Reliability is defined as the ability of an item to perform a required function under stated conditions for a certain period of time, which is often measured by probability of failure, by frequency of failure, or in terms of availability [Ele12] [Wan13]. Power device failure or degradation can be caused by external factors, such as moisture, temperature, vibrations, mechanical shock, etc. (see previous section 2.2.1), or internal factors, such as, for instance, the normal usage of the component or repetitive high current cycles, associated to thermal cycles (due to the Joule effect), that result in fatigue degradation of the main parts composing the device. These kinds of degradation or failure correspond then to the final part of the typical failure rate profile ("bathtub" curve - Fig. 15) as a function of the device life-time. The failure rate in this stage increases with the usage duration and the device aging and this defines the life-time of the device.

Figure 15: Bathtub curve of failure rate.

Considering our specific application field, power switches driving the vehicle light system are located far from the engine system. Thus, the mechanical stress and the thermal variations generated by the engine system, can be neglected. The main stress they undergone is the electro-thermal one. In fact, during their life, the components undergo several short-circuits and avalanche [Ber10] events, inducing thermo-mechanical effects, added to the normal thermal excursions due of the environment in which they operate. These repetitive electro-thermal stresses produce degradation effects at the interfaces between the different materials composing the device structure, because of the difference in their physical properties (table 1), and in particular in the coefficients of thermal expansion (CTE).

Fig. 16 shows a schema of a smart power device with the main critical parts during electro-thermal aging: the solder joint and the metallic parts (source electrode metallization and bonding wires). In the following the associated failure mechanisms are described. In this work, we will focus on the failure mechanisms of the metallic parts.

| J I I                                                 | 1             | <b>J</b>        |                        |                                     |

|-------------------------------------------------------|---------------|-----------------|------------------------|-------------------------------------|

| Function                                              | Semiconductor | Conductor       |                        | Solder                              |

| Material                                              | Si            | Al              | Cu                     | PbSn <sub>5</sub> Ag <sub>2.5</sub> |

| CTE [10 <sup>-6</sup> /K]                             | 4.15          | 23.1            | 16.5                   | 21                                  |

| Young modulus [GPa]                                   | 131           | 70              | 120                    | 10                                  |

| Poisson ratio                                         | 0.27          | 0.35            | 0.34                   | 0.4                                 |

| El. cond. $[\Omega^{-1}m^{-1}]$ (doping dependent)    | $10^{-3}$     | $37.7 * 10^{6}$ | 59.6 * 10 <sup>6</sup> | 6.67 * 10 <sup>6</sup>              |

| Thermal cond. $[Wm^{-1}K^{-1}]$                       | 148           | 237             | 385                    | 50                                  |

| Thermal capacity [Jkg <sup>-1</sup> K <sup>-1</sup> ] | 752           | 897             | 385                    | 150                                 |

Table 1: Physical properties of the main representative materials at 25°Cl [Pie11].

Figure 16: Schematic representation of a LFET1T-like smart MOSFET power device. The critical points subject to electro-thermal stress are: die/leadframe solder joint, Al source metallization, bonding wires.

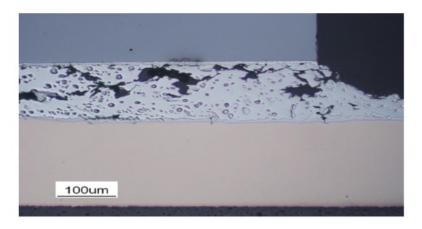

#### 2.2.2.1 Die/substrate solder joints fatigue

The solder joint between the Si substrate of the power die and the Cu lead frame ensures their thermal, electrical and mechanical contact. At increasing temperature, the power die heating is transferred through this connection to the lead frame where it is dissipated. Since 2006, after the restriction of the use of hazardous substances in electronic equipments, the lead-based soldering process has been replaced by high temperature (> 270 °C) process and Pb-free solders, consisting essentially in Sn-Ag-Cu alloy, are more and more used from the electronics manufacturers. The low elastic limit of these materials induces deformation in the solder layer even at low stress. In addition, the CTE mismatch between Si and Cu can strain the solder joint connection, and over the component lifetime can contribute to mechanical solder joint fatigue failure [Leeoo]. Two phenomena can then occur during the electro-thermal aging of the device: cavities multiplication and delamination starting from the edges of the solder towards the center (Fig. 17). Both of them limit the current flow in the solder layer, increasing the R<sub>DS(on)</sub> of the device. It has been demonstrated that the less is the solder thickness the more fragile is the solder [Hayo2] [You15] [Guéo2]. However, an increase in the thickness results in a increase in the thermal resistance of the solder layer, because of the low thermal conductivity of the materials constituting the solder. A trade-off between thermal conductivity and mechanical strength is then required in phase of design of the solder interface.

Figure 17: Delamination of a lead-free solder joint between the die Si substrate and the Cu lead frame [Bouo8].

#### 2.2.2.2 Failure modes in the active zone

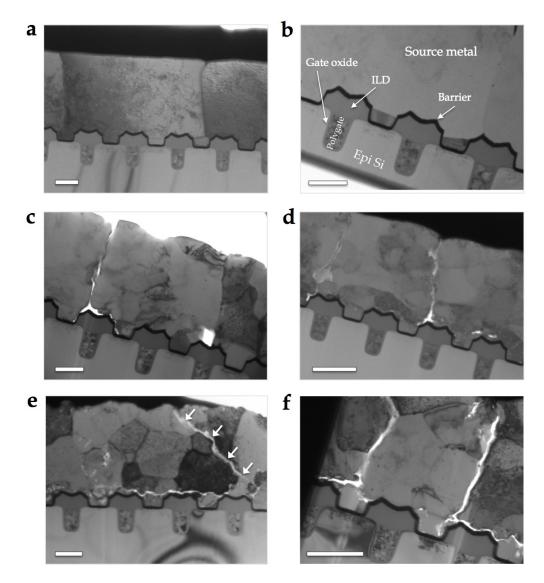

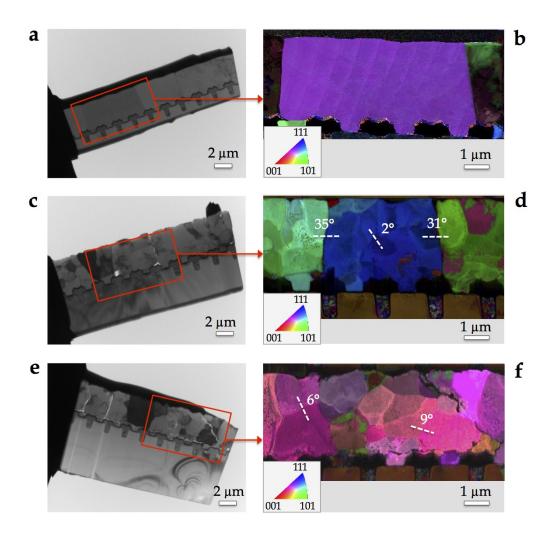

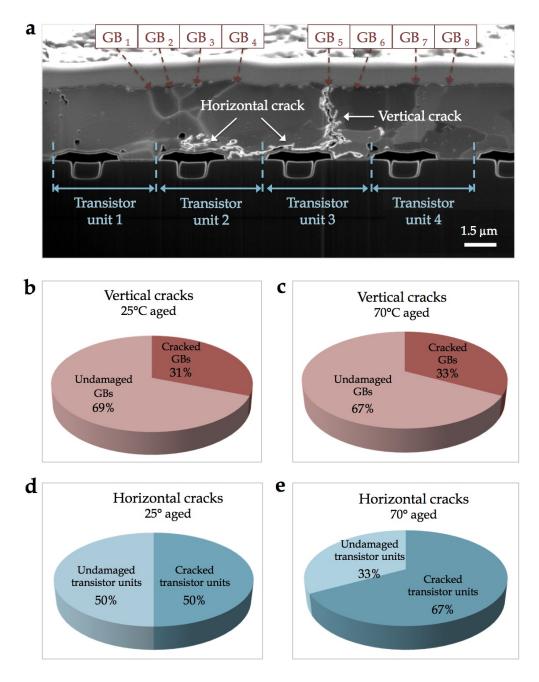

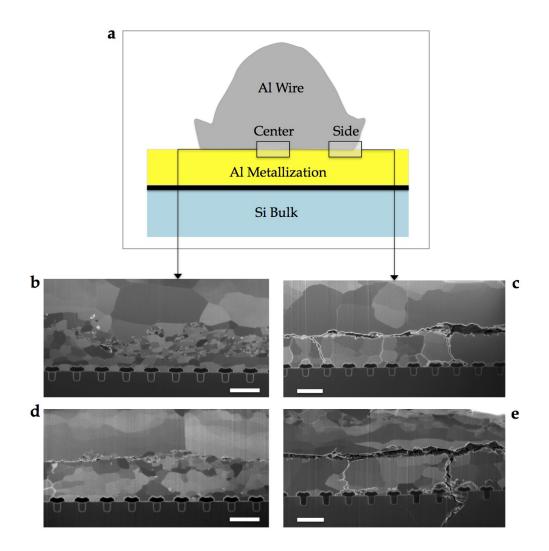

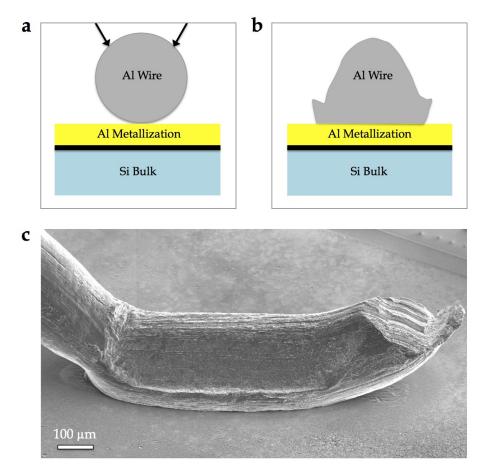

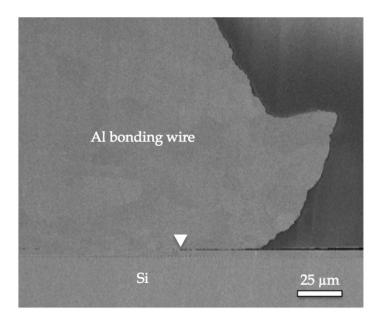

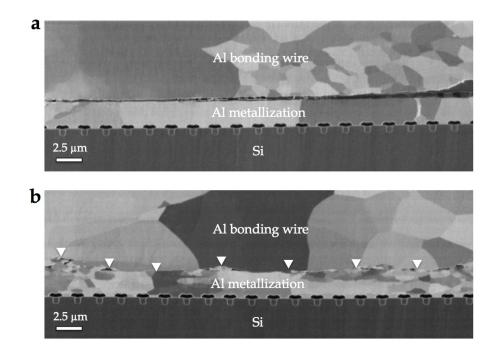

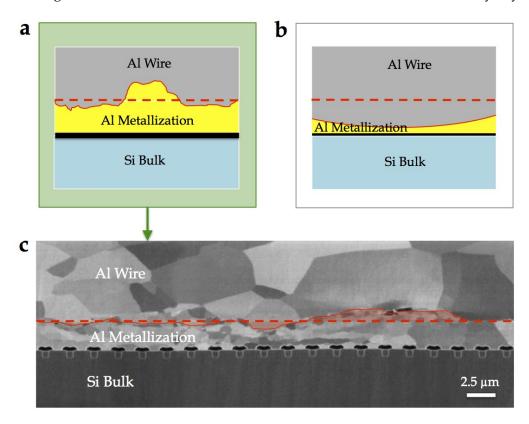

The active zone of the power device corresponds to the MOSFET die and the bonding wires connected to the source metallization. In this area, the electrothermal cycles induce mechanical stress in the softest parts of the complex layered structure that, by nature, consists in the interconnection of different materials (metal-oxide-semiconductor) and constitutes the MOSFET device. They are the Al source metallization and bonding wires, which have higher coefficient of thermal expansion respect to the oxide and the Si (table 1).

#### Source metallization

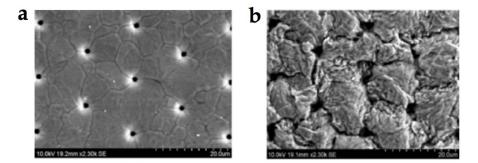

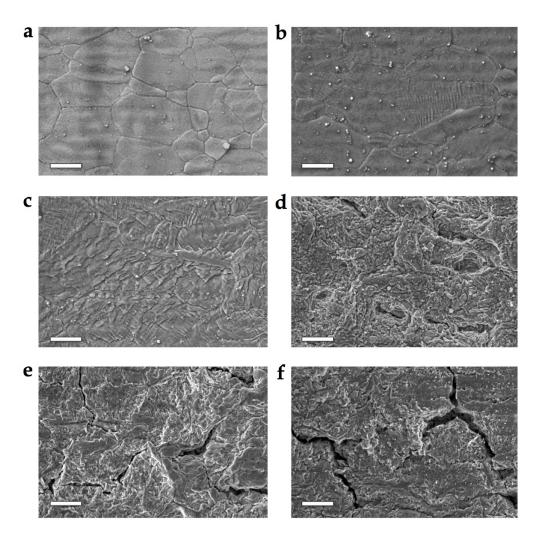

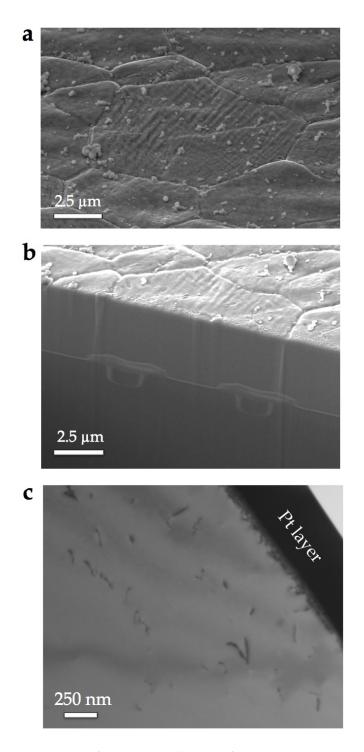

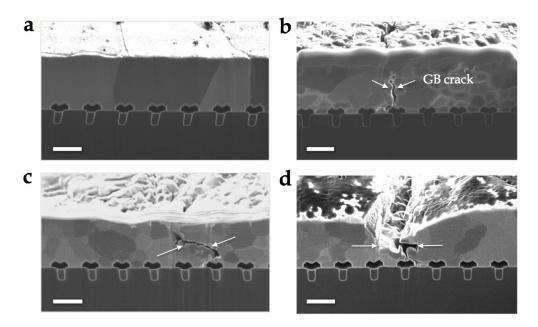

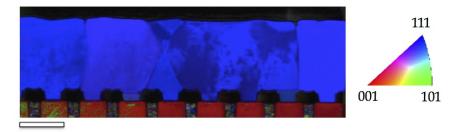

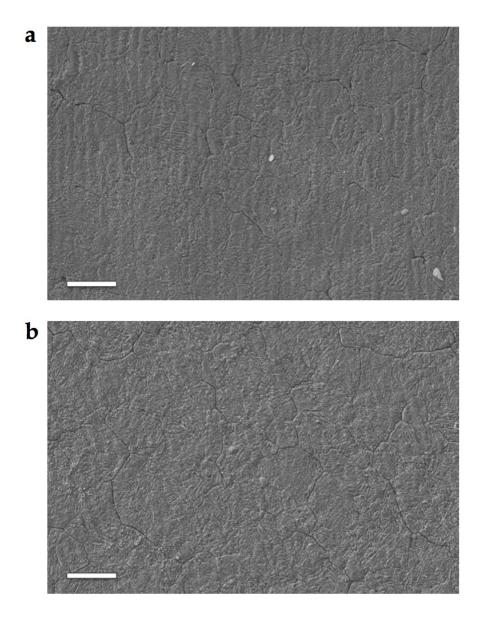

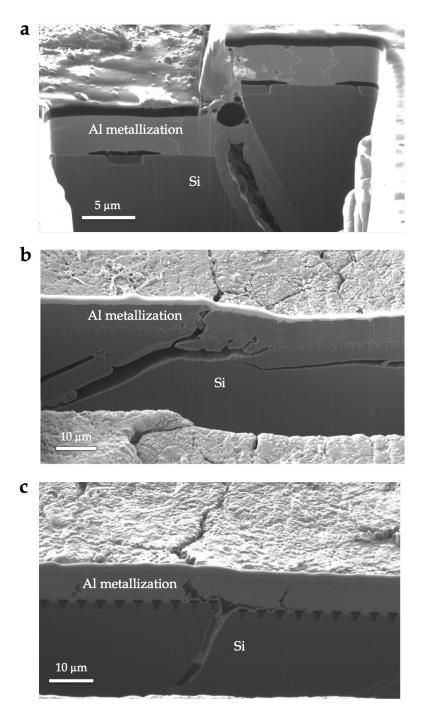

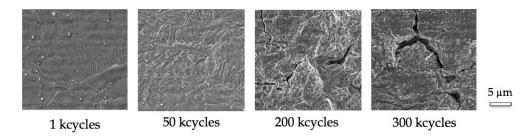

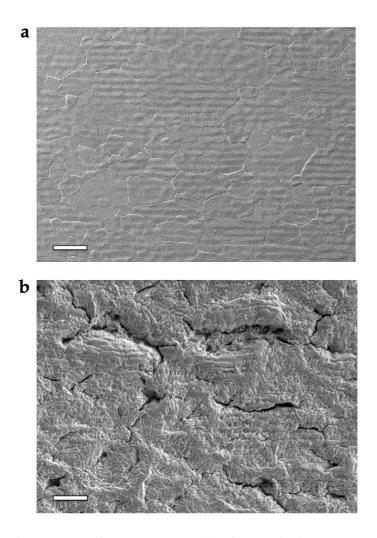

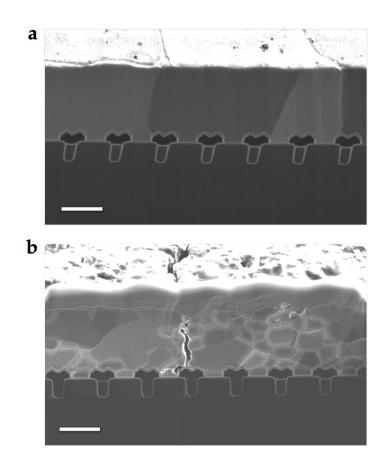

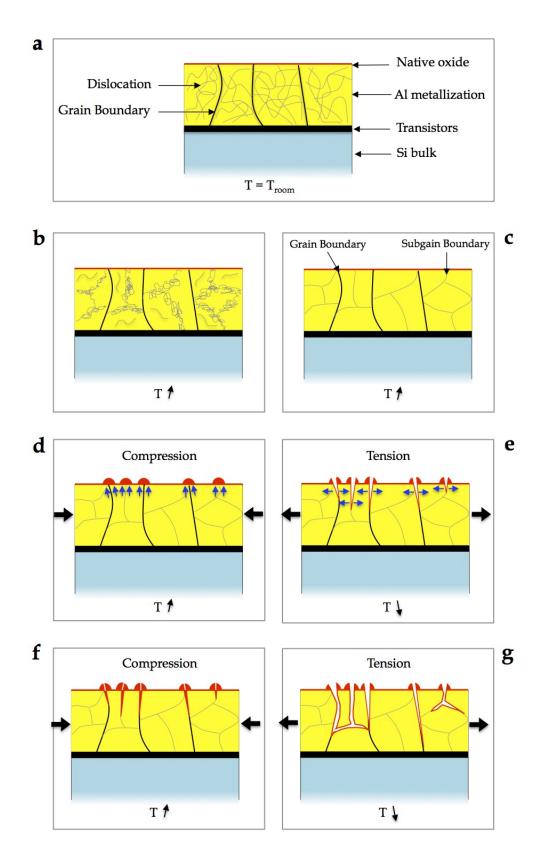

Reconstruction of the aluminum metallization is an effect observed since the early times of microelectronics [San69] [Phi71]. During thermal cycling of IGBT and MOSFET devices, periodical compressive and tensile stresses are introduced in the thin metalization film by the different CTEs of the aluminum and of the silicon chip, due to the large thermo-mechanical mismatch between both materials and due to the stiffness of the silicon substrate [Ciao2]. The thermomechanical stresses in the Al results in the gradual change in its granular structure. Fig. 18 shows the comparison between the Al metallization surface in a power MOSFET before and after electro-thermal cycles. The aged metal is characterized by an higher roughness and cracks along the grain boundaries.

Figure 18: Electro-thermal ageing of the source electrode metallization in a smart power MOSFET. Scanning electron micrograph of the (a) fresh metallization and (b) at failure [Pie11].

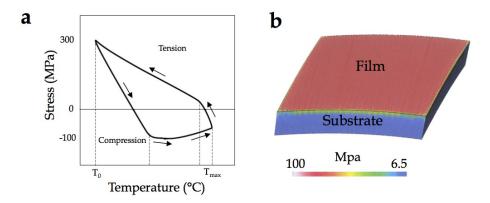

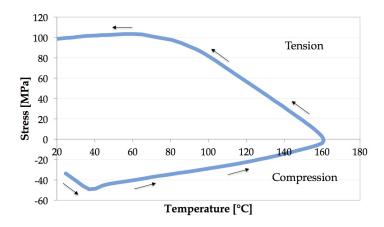

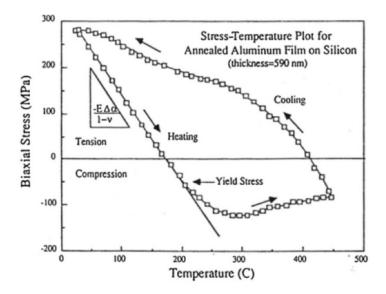

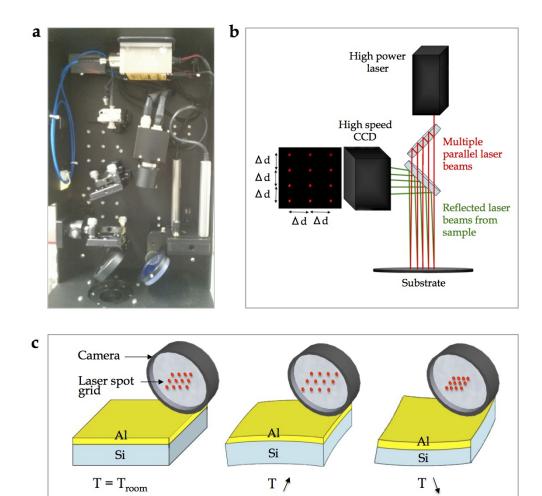

To assess the stress seen in interconnects during operation, Flinn and coworkers [Fli87] considered the simplest approximation of a chip: a metal layer deposited on a silicon substrate. They measured the stress arising during thermal cycles due to the mismatch between both materials using a laser reflectometer set up and the approximation of the Stoney equation [Stoo9] [Fre99] [Jano9].

$$\sigma_{\rm f} = \frac{\mathsf{E}_{\rm s} \mathsf{t}_{\rm s}^2}{6(1-\nu)\mathsf{t}_{\rm f}\mathsf{R}} \tag{1}$$

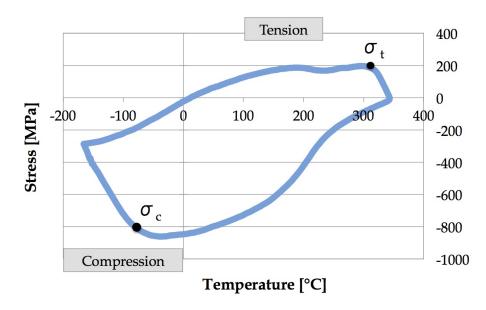

In this equation, only the thicknesses of both film and substrate ( $t_f$  and  $t_s$ ) are needed, along with the substrate Young's modulus and Poisson's ratio ( $E_s$  and v). The film stress  $\sigma_f$  is then directly deduced from the radius of curvature R measured by the laser. Because the substrate is more rigid and does not plastically deform at room temperature, most of the plasticity is expected to occur in the metallic film. In their first paper, the metallization was an Al-1%Si thin film and the cycles were performed from room temperature to 400 °C at a rate of about 20°C/min. During the process, the Al layer would go from slightly tensile to compressive stresses (max 100 MPa) during heating, before deforming plastically in tension during the cooling, up to a stress of 300 MPa (Fig. 19).

Figure 19: (a) Typical stress-temperature cycle for a 1- $\mu$ m-thick poly-crystalline Al film on oxidized Si substrate (T<sub>max</sub> ~ 450°C). (b) Finite element simulation showing the Von Mises stresses generated by a temperature change of 50 °C in a 1 cm x 2cm x 0.5 mm specimen (typical size used in wafer curvature) [Lego9].

Several publications followed (a nice and recent review can be found in Wiederhirn's thesis [Wieo7] and established that the film strength <sup>1</sup> increased as the inverse of the film thickness. This increase in film thickness was then rationalized in term of threading dislocation movements by Nix in 1989 [Nix98],

<sup>1</sup> During thermal cycles, metallic thin films experience two yield stresses, at the end of the elastic compression stage (heating) and in tension during cooling. The maximum stress is usually reached at the end of the cooling and is considered as the "film's strength"- see [Lego6]

from an initial calculation of image forces in thin films by Matthews and Blakeslee [Mat74] [Mat75]. Later on, this model was questioned [Mue98] [Leg09] because the amorphous layer between the Si substrate and the metal film (usually Si oxide), acted as a dislocation sink. This later effect may however reflect an artifact of TEM observation because Si oxide seems to soften significantly under electron beam [Zhe10]. In any case, the reversible motion of threading dislocations (Nix's model) cannot explain the strong and non-crystallographic roughening of Al films on Si, observed in power mosfets ([Pie11] or plain thin Al films on substrates [Tur92] [Leg05] [Ka003].

Another approach consisted in applying the Frost and Ashby deformation mechanisms maps [Fro82] to the stress/temperature cycles. These maps and equation were established for bulk materials and link a given plastic strain rate  $\dot{\epsilon}$  to a given stress and temperature. By comparing the predicted stress/temperature cycles using these maps and the experimentally established one (by laser curvature), Bostrom [Boso1] showed that a large discrepancy existed between both approaches, underlying the fact that thin films on substrate deformed in a specific way.

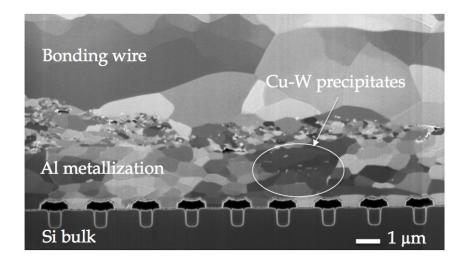

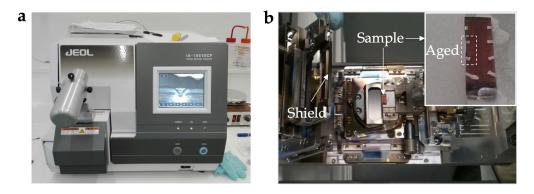

Recently, a qualitative model adapted to the bamboo-microstructure of thin film was developed to explain how the plastic deformation proceeded by atomic self diffusion of Al atoms along the grain boundaries (GBs) [Mar14]. These GBs, acting as fast diffusion paths would gradually open during tension (cooling phase). During heating, the Al atoms are expelled to the surface through the same GBs, as predicted by the model from Gao [Gao99], and contribute to its roughening. The irreversibility of the process is due to the native oxidation of cracks surfaces that will prevent crack healing during compression.

## **Bonding wires**

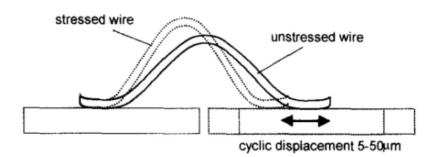

Reliability of bonding connections in power modules, and in particular of wire bonds soldered on the source electrode metallization by cold-bonding process, is an important issue for the reliability of power systems because of extending operation temperatures (due to the Joule effect in the wire itself and to the power dissipation in the Si substrate) which induce high levels of thermomechanical stress in the bonding area [Ciao2] [Glao4] [Dupo7]. Ramminger et al. [Ramoo] described and modeled this cyclic stress as wire flexure by thermal expansion or wire deformation under mechanical shock loading if the bond surfaces are able to move relatively to each other (Fig. 20).

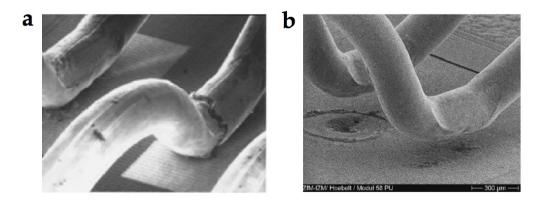

As consequence of this stress, mainly two kinds of failures of wire bonds have been reported in the literature:

1. Heel crack failure (Fig. 21a), originating from bending caused by thermal expansion or by mechanical deformation of the wire [Meh99] [Ciao2].

- Figure 20: Bonding wire subjected to cyclic mechanical stress applied by lateral displacement of one bonding area relatively to the other in Ramminger et al. experiments [Ramoo].

- 2. Bond wire lift-off (Fig. 21b), resulting from material fatigue at the chip metallization. This is caused by shear forces which result from the different coefficients of thermal expansion on the interface [Ber98] [Ciao2].

These degradation modes have been mainly observed in components that undergo active cycles and rarely under extreme conditions (avalanche or shortcircuit). In the latter case, the metallization is the location most prone to degradation, but even in the cases of faster bonding failure, metallization reconstruction is always observed [Sme11].

The failure mechanisms at the bonding connections are generally studied combining experimental test and simulation. Ramminger has demonstrated, by a finite element model based on stress experiments, that the number of cycles to heel crack failure is strongly dependent on the loop geometry [Ramoo]. He has also considered that cracks in the bonding wires and at the wire-metallization interface do not propagate towards the metallization because of its higher yield strength [Ram98]. The layout of the bonding connection also play a role in the reliability of power device. According to Ishiko et al., the reliability of IGBT components can be improved by optimizing the wire position configuration by thermo-electric simulation in order to make the temperature distribution of the devices more uniform [Isho6].

In parallel to the studies in simulation, the microstructure of the bonding wires has been inspected in order to investigate the influence of the grain structure evolution on the crack growth and the device life-time. Yamada et al. [Yamo7] showed that the crack growth increases with the number of thermal cycles (from -40 °C to 200 °C), resulting in a reduction of the residual bonding length of Al wires that seems to be independent by the limited recrystallization of the wire grains at high temperature.

Figure 21: Examples of bond failures in power components: (a) heel crack failure [Ciao2] and (b) wire lift-off [Den17].

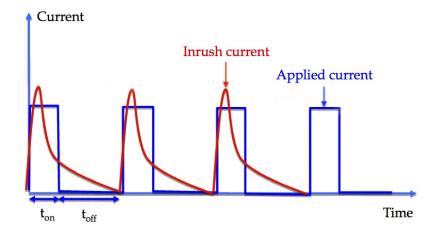

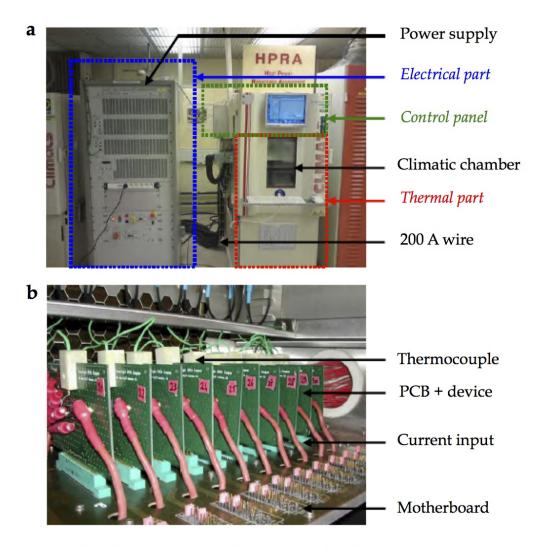

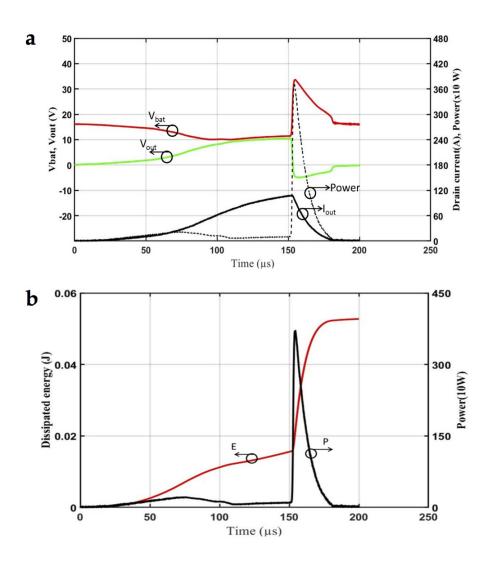

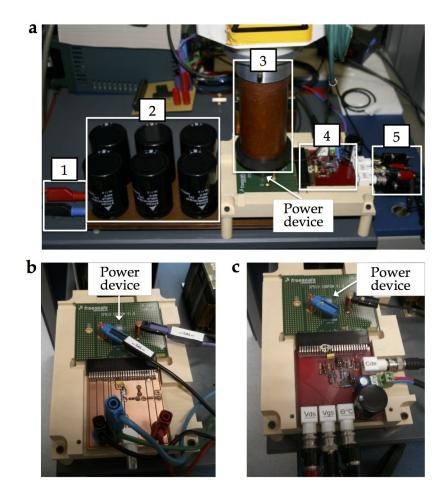

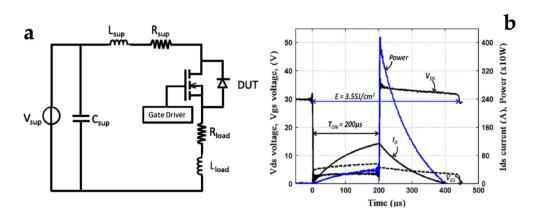

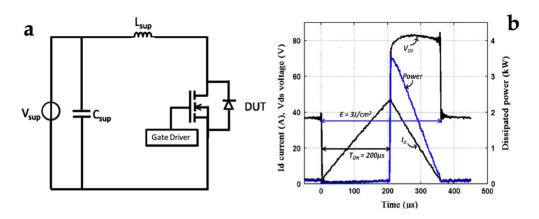

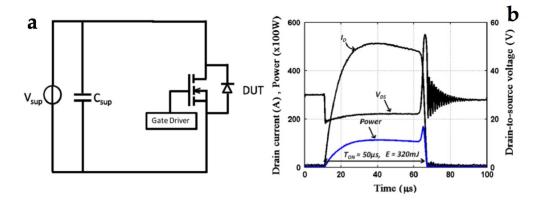

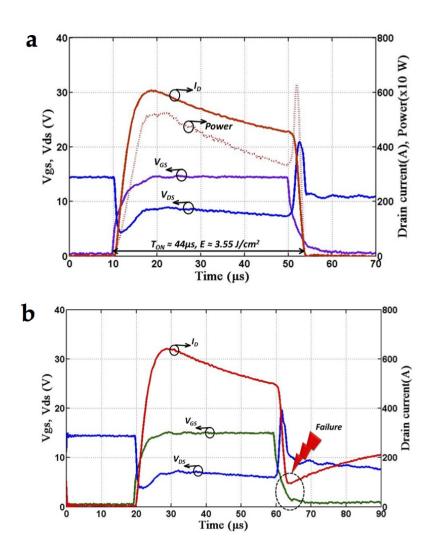

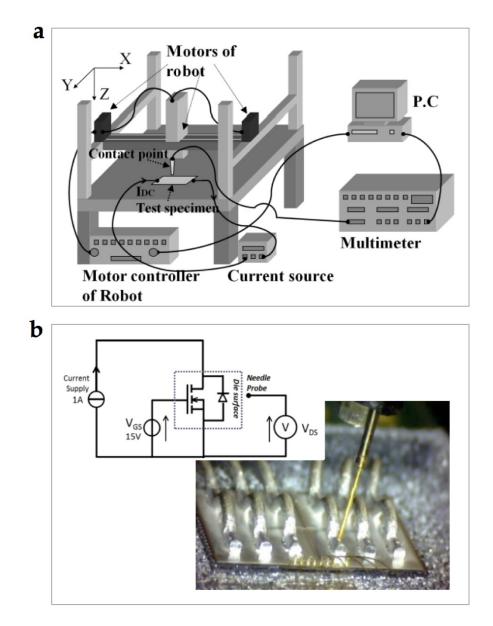

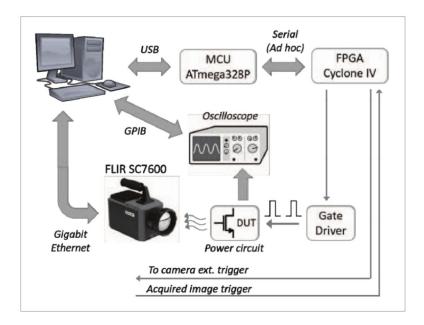

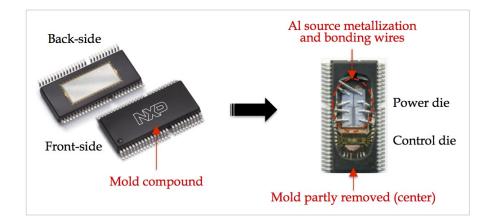

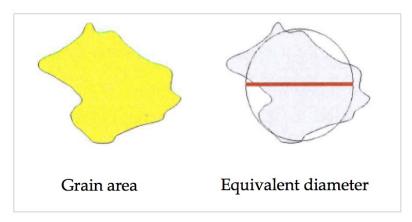

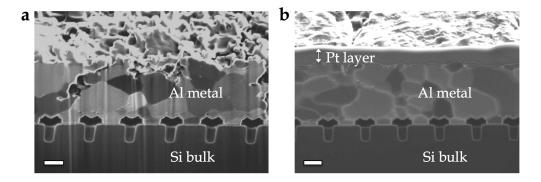

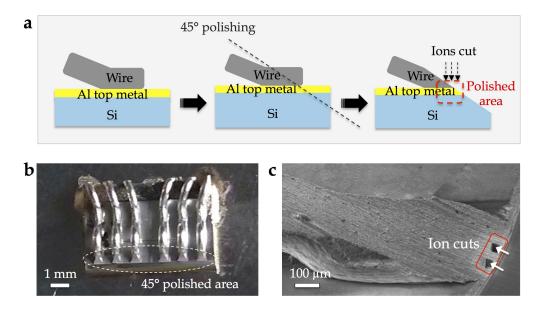

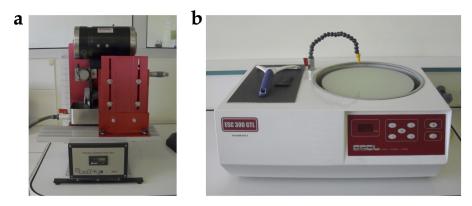

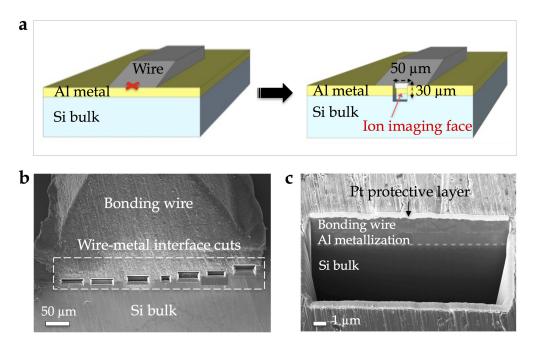

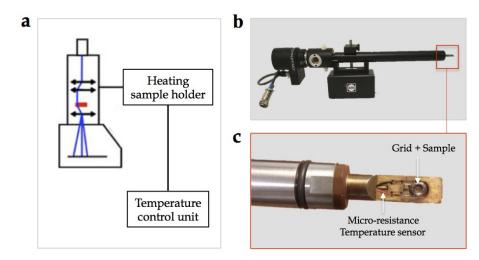

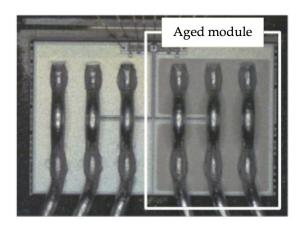

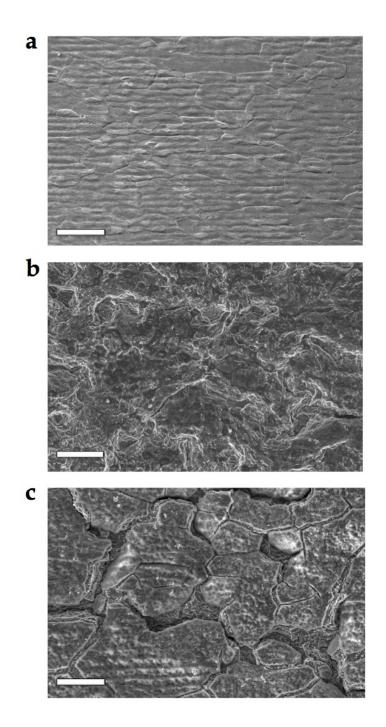

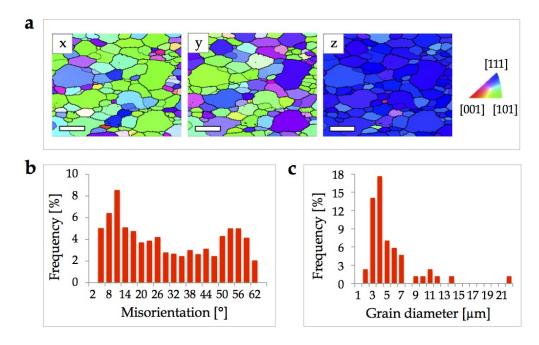

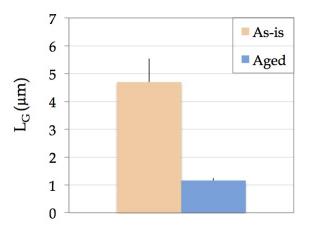

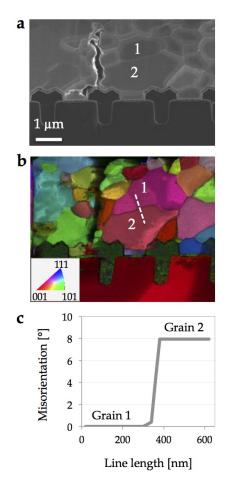

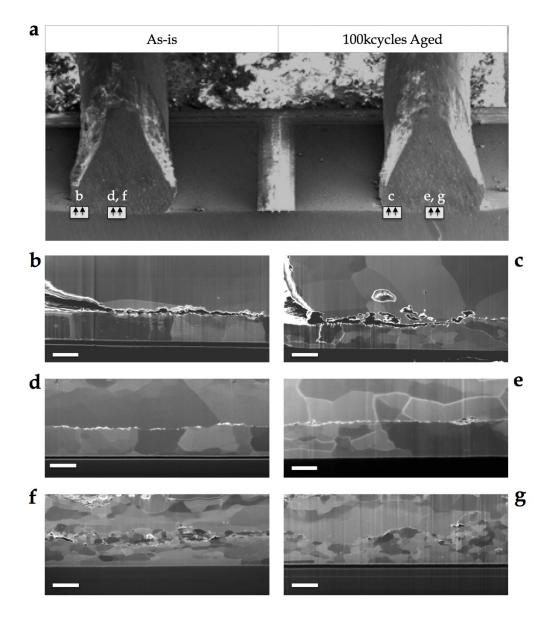

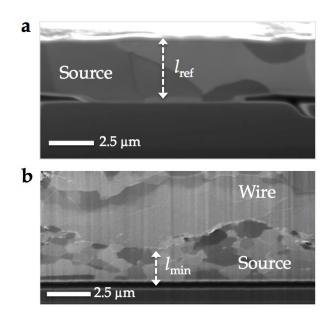

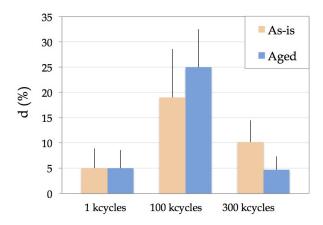

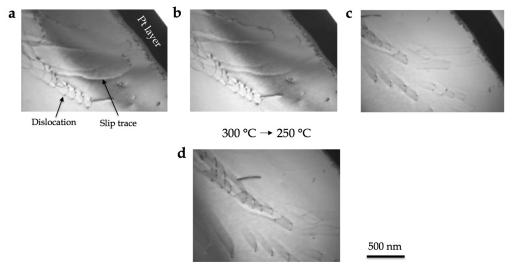

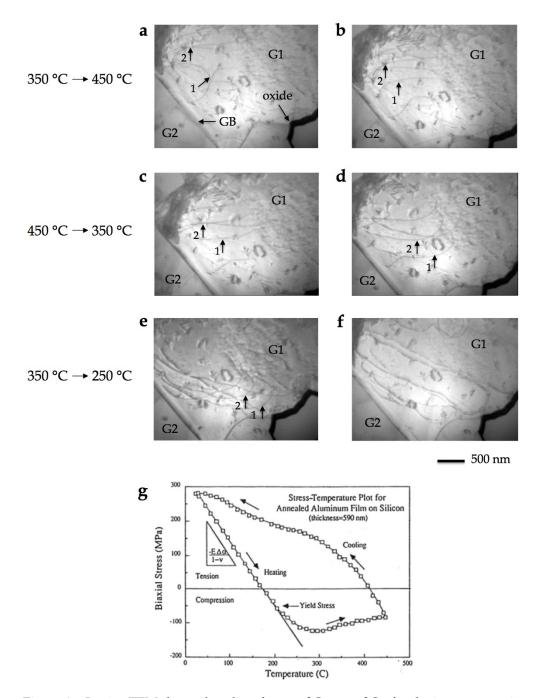

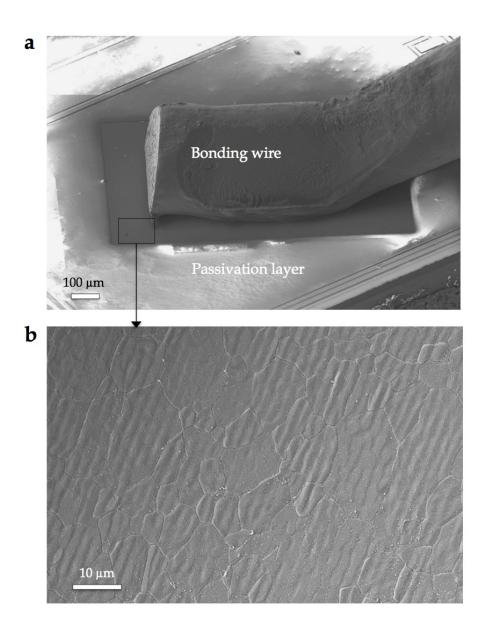

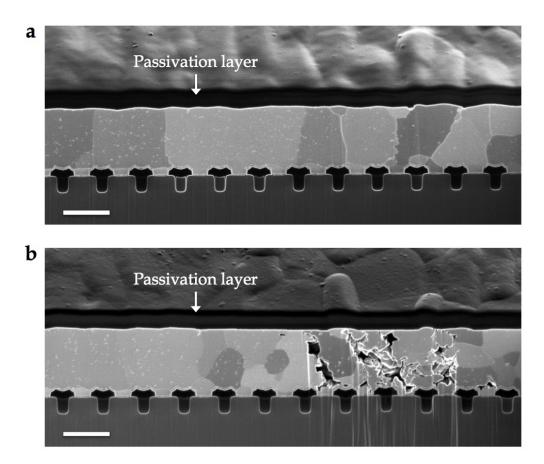

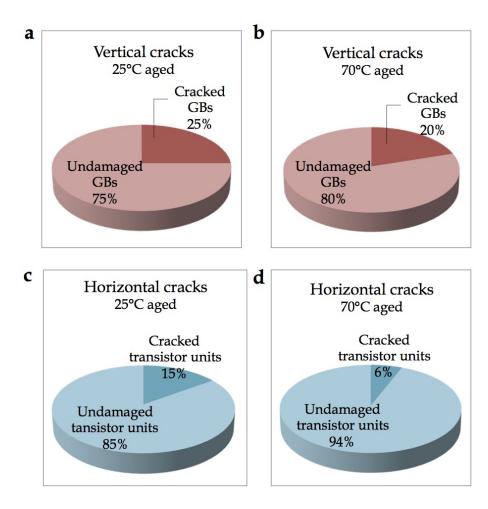

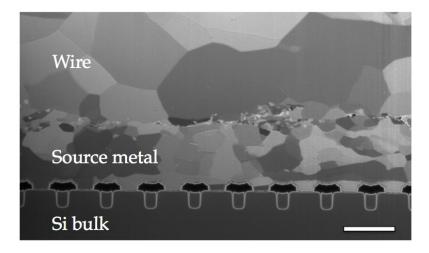

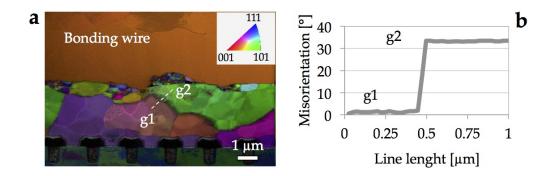

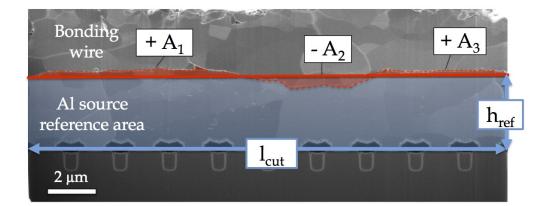

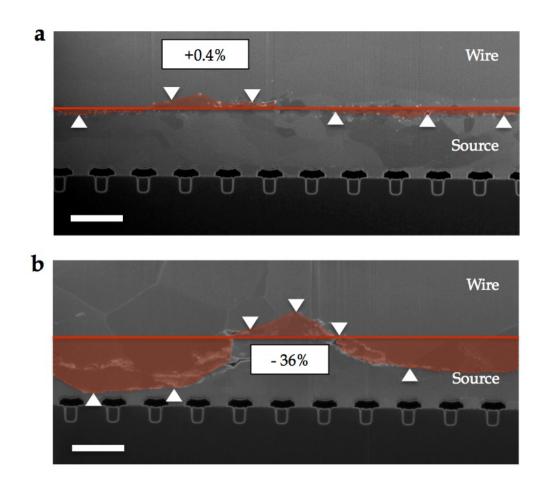

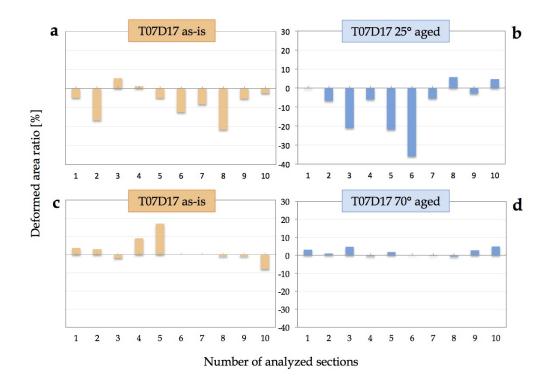

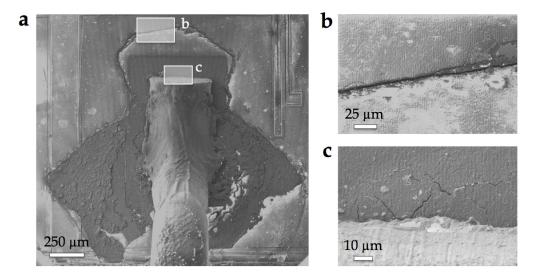

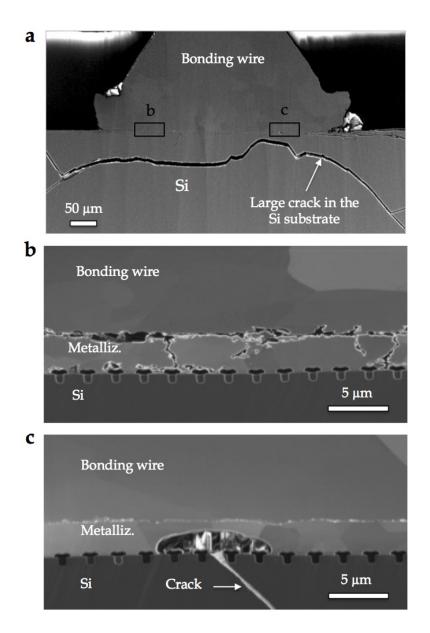

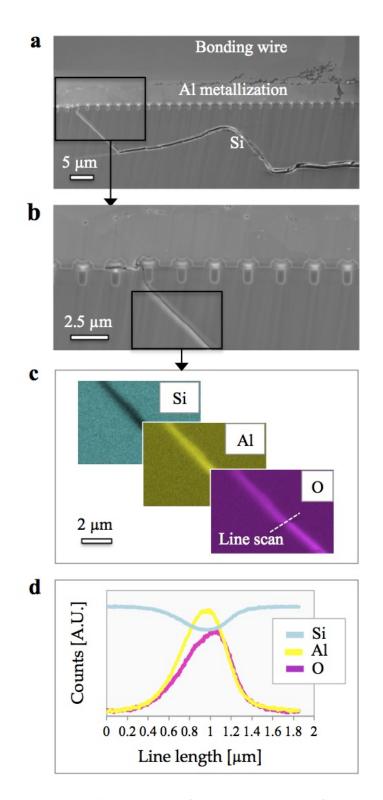

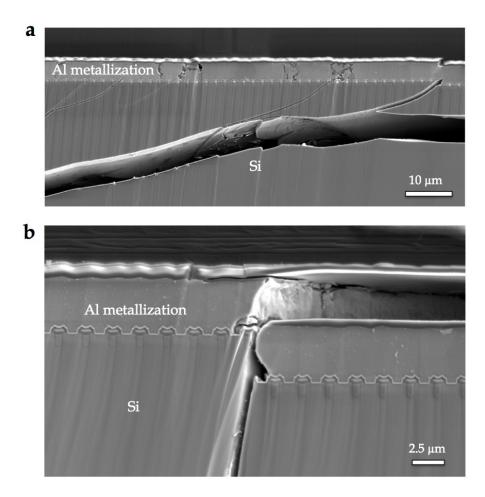

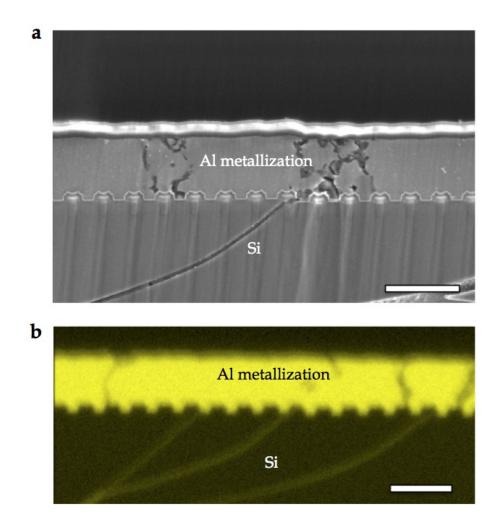

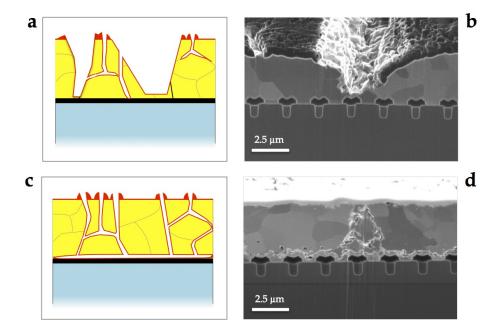

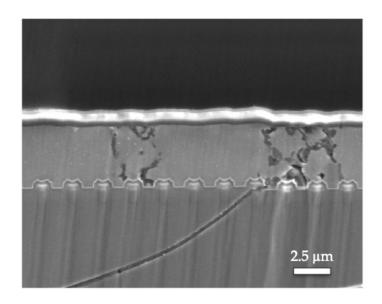

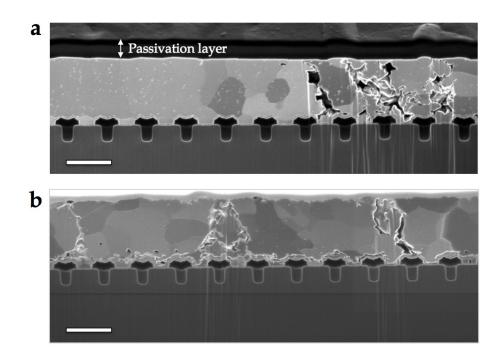

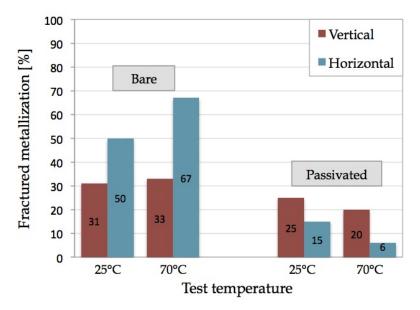

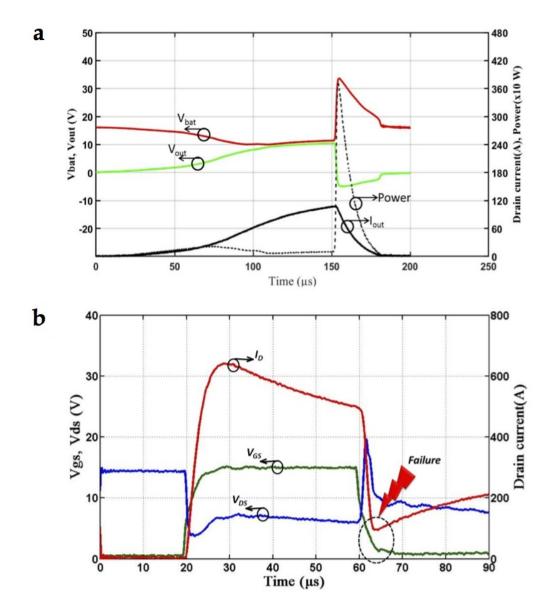

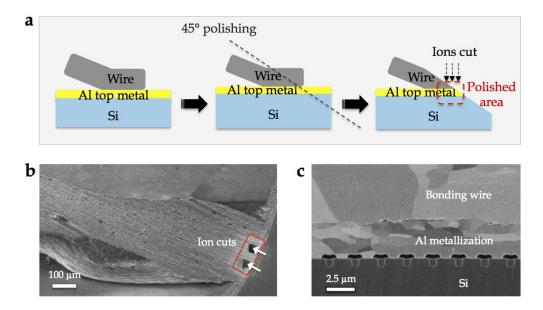

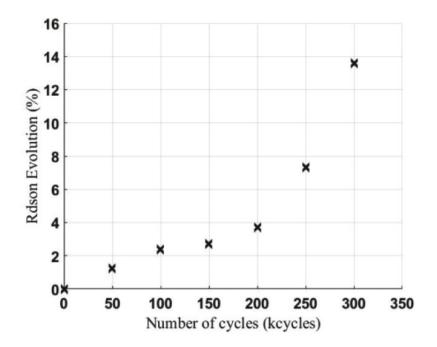

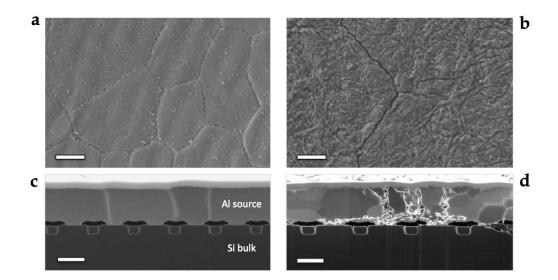

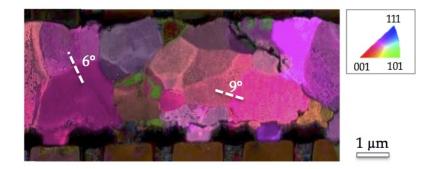

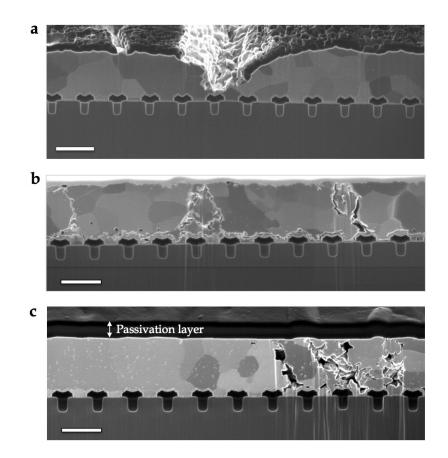

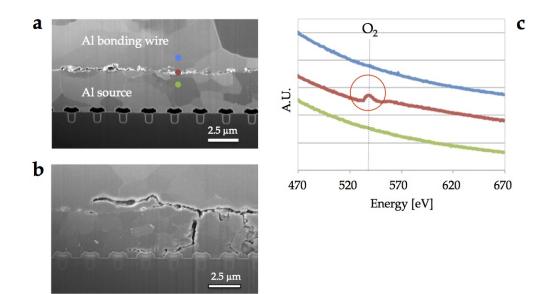

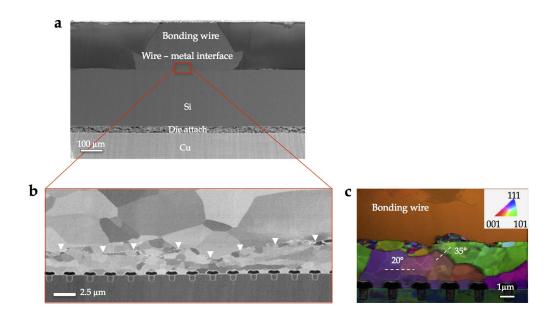

## 2.2.3 Thermosensitive aging indicators