## Unconventional Computing Using Memristive Nanodevices: From Digital Computing to Brain-like Neuromorphic Accelerator

Mahyar Shahsavari

### ▶ To cite this version:

Mahyar Shahsavari. Unconventional Computing Using Memristive Nanodevices: From Digital Computing to Brain-like Neuromorphic Accelerator. Neural and Evolutionary Computing [cs.NE]. Université de Lille, Sciences et Technologies 2016. English. NNT: . tel-01451613

## HAL Id: tel-01451613 https://hal.science/tel-01451613v1

Submitted on 1 Mar 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Mahyar SHAHSAVARI Lille University of Science and Technology

**Doctoral Thesis**

## Unconventional Computing Using Memristive Nanodevices: From Digital Computing to Brain-like Neuromorphic Accelerator

**Supervisor: Pierre BOULET**

Thèse en vue de l'obtention du titre de

Docteur en

### INFORMATIQUE

### **DE L'UNIVERSITÉ DE LILLE**

École Doctorale des Sciences Pour l'Ingénieur de Lille - Nord De France

14-Dec-2016

### Jury:

Hélène Paugam-MoisyProfessor of University of the French West Indies (Université des Antilles), France (Rapporteur)Michel PaindavoineProfessor of University of Burgundy (Université de Bourgogne), France (Rapporteur)Virginie HoelProfessor of Lille University of Science and Technology, France(Président)Said HamdiouiProfessor of Delft University of Technology, The NetherlandsPierre BouletProfessor of Lille University of Science and Technology, France

# Acknowledgment

Firstly, I would like to express my sincere gratitude to my advisor Prof. Pierre Boulet for all kind of supports during my PhD. I never forget his supports specially during the last step of my PhD that I was very busy due to teaching duties. Pierre was really punctual and during three years of different meetings and discussions, he was always available on time and as a record he never canceled any meeting. I learned a lot form you Pierre, specially the way of writing, communicating and presenting. you were an ideal supervisor for me.

Secondly, I am grateful of my co-supervisor Dr Philippe Devienne. As I did not knew any French at the beginning of my study, it was not that easy to settle down and with Philippe supports the life was more comfortable and enjoyable for me and my family here in Lille. I have never forgotten our joyful time in concert and playing violin with ELV music group, your delicious foods and cakes, visiting London, Vienna, Kermanshah and Tehran all nice moments we spended with Philippe. With Philippe support we started a scientific collaboration with Razy University at my hometown city Kermanshah. We got the Gundishapour grants for two years collaboration between Lille 1 and Razy Universities In addition to signing a MoU for long term collaboration between two universities all thanks to Philippe efforts.

I would like to acknowledge and thanks to my thesis committee: Prof. Hélène Paugam-Moisy, Prof. Michel Paindavoine, Prof. Said Hamdioui and the president of the jury, Prof. Virginie Hoel for their insightful comments and encouragement, and reviewing my thesis.

My sincere thanks also goes to CRIStAL lab and Émeraude team colleagues, prof. Giuseppe Lipari, Dr Richard Olejnik, Dr Clément Ballabriga and specially to Dr Julien Forget. I will never forget Forget supports specially for the first time teaching at Polytech Lille. I appreciate my Émeraude team friends Antoine Bertout, Khalil Ibrahim Hamzaoui, Houssam Zahaf, Pierre Falez and Yassine sidlakhdar for nice discussions, coffee drinking and playing football together. I would like to thanks to our colleague Dr Fabien Alibart in IEMN lab for his technical consultancy during my research particularly during developing new synapse. I gratefully acknowledge my previous friends and colleagues in TUDelft in The Neterlands, my lovely and kind friends Faisal Nadeem, Arash Ostadzadeh, Mahmood Ahmadi that shared with me valuable knowledge and information. Thanks again to Prof. Said Hamdioui that we started working on memristor together in CE group at TUDelft.

Special thanks go to my Iranian friends in Lille Farzan, Hamid, Hamidreza, Ehsan, Babak, and Sina thanks for bing there for me. Eric and Leopoled, my lovely officemates and friends, I never forget your kindnesses in our calm office in M3 building. I am grateful of my Iranian friends and colleagues at Razi University, Prof. Mohsen Hayati Dr Mahmood Ahmadi, Dr Arash Ahmadi and one of my best friend Mazdak Fatahi that we started working on neural network research for his Master thesis. We have done many skype meetings that both of us learned a lot during those scientific discussions. Actually the last chapter of my thesis is related to his master thesis topic. I appreciate my father in law Prof. Mohammad Mehdi Khodaei for his guidance during my research as well as supporting us for starting collaboration between Razi and Lille 1 universities. I really Dr Mahmood Ahmadi, and Mazdak Fatahi for their supports and being kindly present specially during the time our French professors and colleagues

visited Kermanshah and Razi university. Without Mahmood helps and supports this collaboration was not feasible.

I am very grateful of my close family in Iran, my kind father, my lovely mother and two supportive brothers Mehdi and Mahziar and my little nephews Abolfazl and Ali who always prayed for me and encouraged me continuously not only during my PhD but also in whole my life.

Last, but not the least, I would like to express my appreciation to my better-half Hanieh, actually Dr Hanieh Khodaei. She was a kind wife, the best friend that we shared whole the beautiful, sad and even stressful moments of our PhD together. Thanks for all those understanding and supports. The best gift during my PhD was from my Almighty, Hana was my best gift, thanks God. Sorry Hana that I consisted part of the time that I should have played with you to my thesis and research.

Be yari Parvardegar Yekta Mahyar Shahsavari, December 2016

# Abstract

By 2020, there will be 50 to 100 billion devices connected to the Internet. Two domains of hot research to address these high demands of data processing are the Internet of Things (IoT) and Big Data. The demands of these new applications are increasing faster than the development of new hardware particularly because of the slowdown of Moore's law. The main reason of the ineffectiveness of the processing speed is the memory wall or Von Neumann bottleneck which is comming from speed differences between the processor and the memory. Therefore, a new fast and power-efficient hardware architecture is needed to respond to those huge demands of data processing.

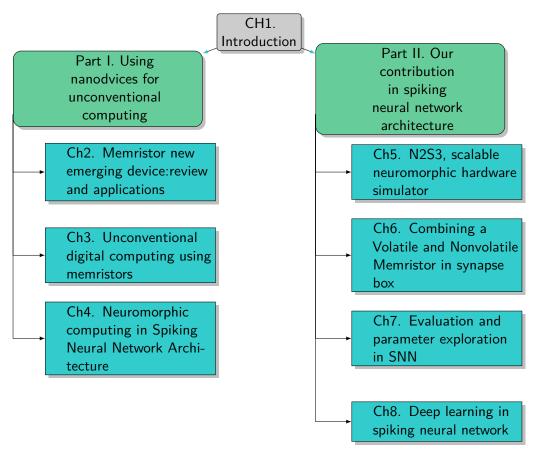

In this thesis, we introduce novel high performance architectures for next generation computing using emerging nanotechnologies such as memristors. We have studied unconventional computing methods both in the digital and the analog domains. However, the main focus and contribution is in Spiking Neural Network (SNN) or neuromorphic analog computing. In the first part of this dissertation, we review the memristive devices proposed in the literature and study their applicability in a hardware crossbar digital architecture. At the end of part I, we review the Neuromorphic and SNN architecture. The second part of the thesis contains the main contribution which is the development of a Neural Network Scalable Spiking Simulator (N2S3) suitable for the hardware implementation of neuromorphic computation, the introduction of a novel synapse box which aims at better learning in SNN platforms, a parameter exploration to improve performance of memristor-based SNN, and finally a study of the application of deep learning in SNN.

# Résumé

On estime que le nombre d'objets connectés à l'Internet atteindra 50 à 100 milliards en 2020. La recherche s'organise en deux champs principaux pour répondre à ce défi : l'internet des objets et les grandes masses de données. La demande en puissance de calcul augmente plus vite que le développement de nouvelles architectures matérielles en particulier à cause du ralentissement de la loi de Moore. La raison principale en est est le mur de la mémoire, autrement appelé le goulet d'étranglement de Von Neumann, qui vient des différences de vitesse croissantes entre le processeur et la mémoire. En conséquence, il y a besoin d'une nouvelle architecture matérielle rapide et économe en énergie pour répondre aux besoins énormes de puissance de calcul.

Dans cette thèse, nous proposons de nouvelles architectures pour les processeurs de prochaine génération utilisant des nanotechnologies émergentes telles que les memristors. Nous étudions des méthodes de calcul non conventionnelles aussi bien numériques qu'analogiques. Notre contribution principale concerne les réseaux de neurones à impulsion (RNI) ou architectures neuromorphiques. Dans la première partie de la thèse, nous passons en revue les memristors existants, étudions leur utilisation dans une architecture numérique à base de crossbars, puis introduisons les architectures neuromorphiques. La deuxième partie contient la contribution principale : le développement d'une simulateur d'architectures neuromorphiques (N2S3), l'introduction d'un nouveau type de synapse pour améliorer l'apprentissage, une exploration des paramètres en vue d'améliorer les RNI, et enfin une étude de la faisabilité des réseaux profonds dans les RNI.

# Contents

| Co  | nten    | ts                                                                                      | 1  |

|-----|---------|-----------------------------------------------------------------------------------------|----|

| Lis | st of F | igures                                                                                  | 3  |

| Lis | st of T | ables                                                                                   | 7  |

| 1   | Intr    | oduction                                                                                | 9  |

| -   | 1.1     | Introduction                                                                            | 9  |

|     | 1.2     | Part I:Motivation, state-of-the-art and application of using emerging nanodevices for   | -  |

|     |         | unconventional computing                                                                | 10 |

|     | 1.3     | Part II:Our contribution in spiking neural network architecture: Simulator, New synapse |    |

|     |         | box, Parameter exploration and Spiking deep learning                                    | 11 |

|     | 1.4     | Manuscript outline                                                                      | 13 |

| I   |         | ivation, state-of-the-art and application of using emerging nanodevices for             |    |

|     | unc     | onventional computing                                                                   | 15 |

| 2   | Men     | nristor nanodevice for unconventional computing: review and applications                | 17 |

|     | 2.1     | Introduction                                                                            | 17 |

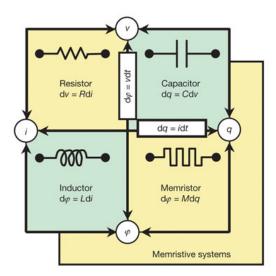

|     | 2.2     | Memristor device overview and properties                                                | 18 |

|     |         | 2.2.1 Memristor a missing electrical passive element                                    | 18 |

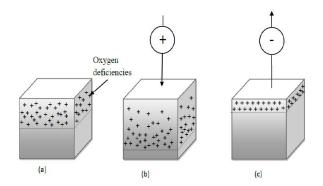

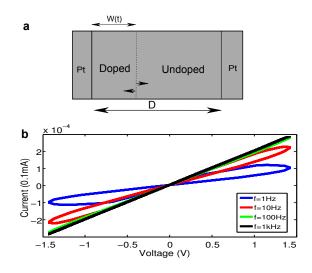

|     |         | 2.2.2 Memristive device functionality                                                   | 19 |

|     |         | 2.2.3 Electrical model                                                                  | 20 |

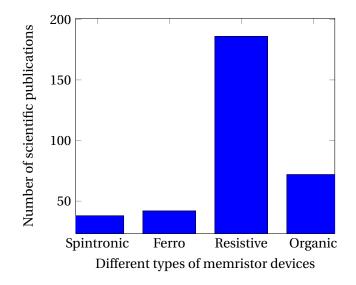

|     | 2.3     | Memristor classification based on different materials and applications                  | 21 |

|     |         | 2.3.1 Resistive Memristor                                                               | 22 |

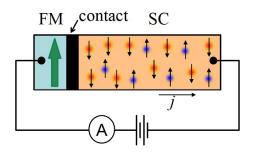

|     |         | 2.3.2 Spintronic Memristor                                                              | 22 |

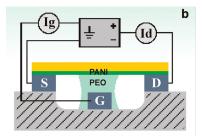

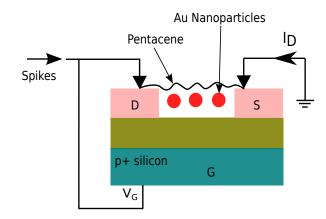

|     |         | 2.3.3 Organic (Polymeric) Memristor                                                     | 23 |

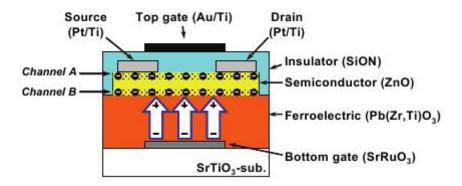

|     |         | 2.3.4 Ferroelectric Memristor                                                           | 25 |

|     |         | 2.3.5 Evaluation of Memristor with different materials                                  | 25 |

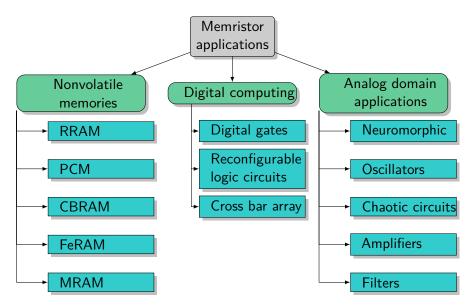

|     | 2.4     | Potential applications of memristors                                                    | 27 |

|     |         | 2.4.1 Memristor-based nonvolatile memory                                                | 27 |

|     |         | 2.4.2 Digital computing                                                                 | 27 |

|     |         | 2.4.3 Analog domain applications                                                        | 28 |

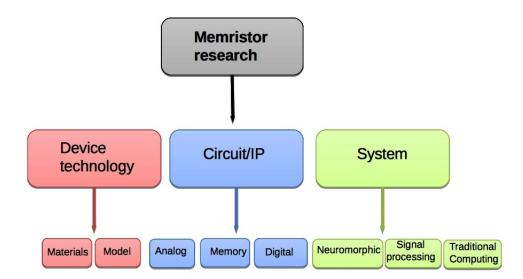

|     | 2.5     | Streams of research                                                                     | 28 |

|     | 2.6     | Conclusions and summary                                                                 | 29 |

| 3   | Unc     | onventional digital computing approach: memristive nanodevice platform                  | 31 |

|     | 3.1     | Introduction                                                                            | 31 |

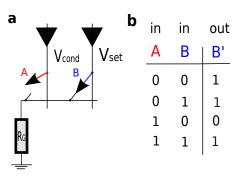

|    | 3.2                                                                                                        | Stateful implication logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

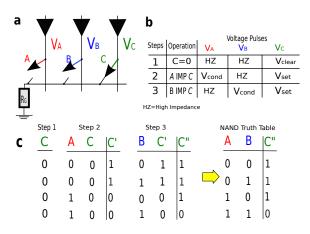

|    |                                                                                                            | 3.2.1 Functionally complete Boolean operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

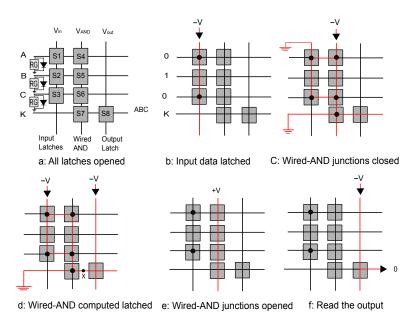

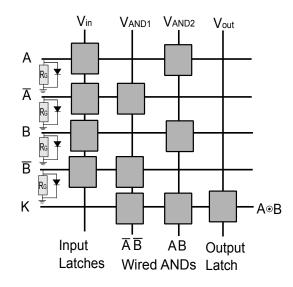

|    | 3.3                                                                                                        | Crossbar architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

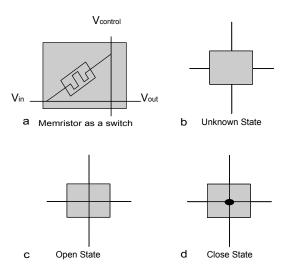

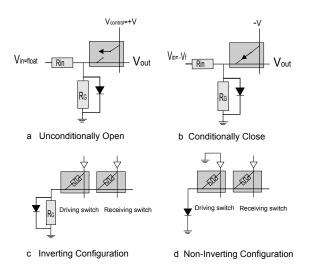

|    |                                                                                                            | 3.3.1 Memristive switches in crossbar architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    |                                                                                                            | 3.3.2 Configurable crossbar array logic gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 3.4                                                                                                        | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 3.5                                                                                                        | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 0.0                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

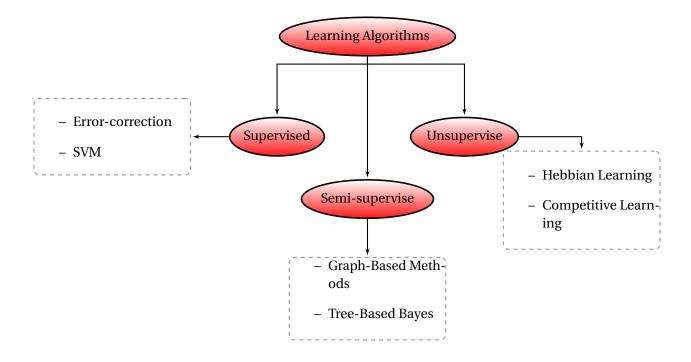

| 4  | Neu                                                                                                        | romorphic computing in Spiking Neural Network architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 4.1                                                                                                        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 4.2                                                                                                        | Spiking Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

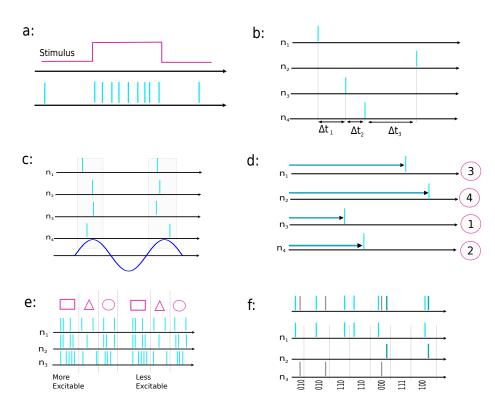

|    | 1.2                                                                                                        | 4.2.1 Spike information coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

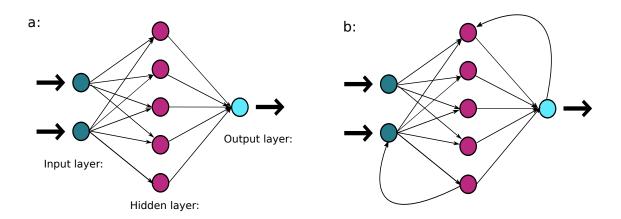

|    |                                                                                                            | 4.2.1       Opike information county         4.2.2       Network topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 1 2                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43<br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

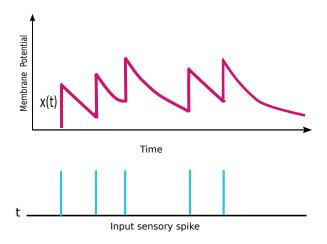

|    | 4.3                                                                                                        | Spiking neuron model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

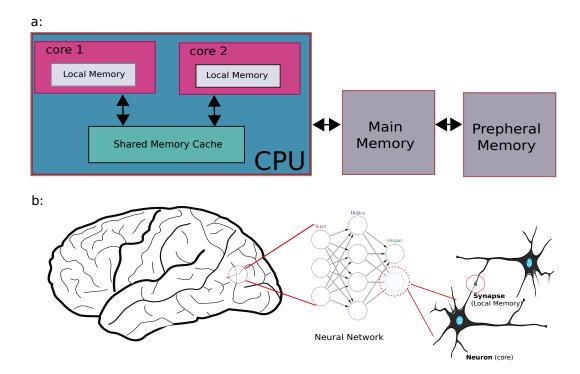

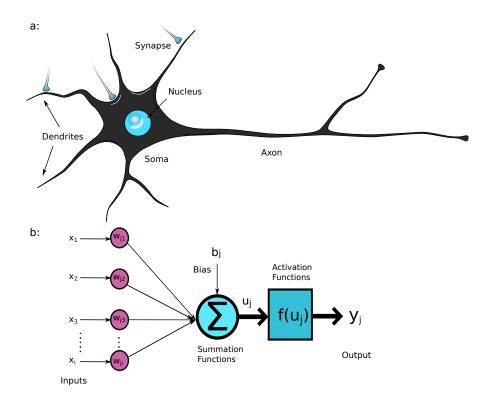

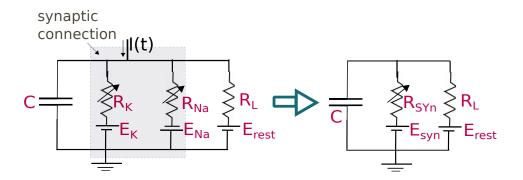

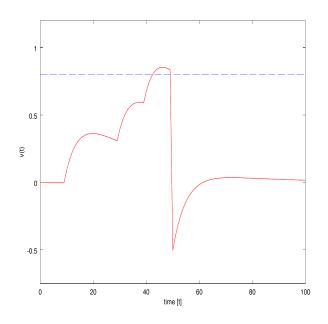

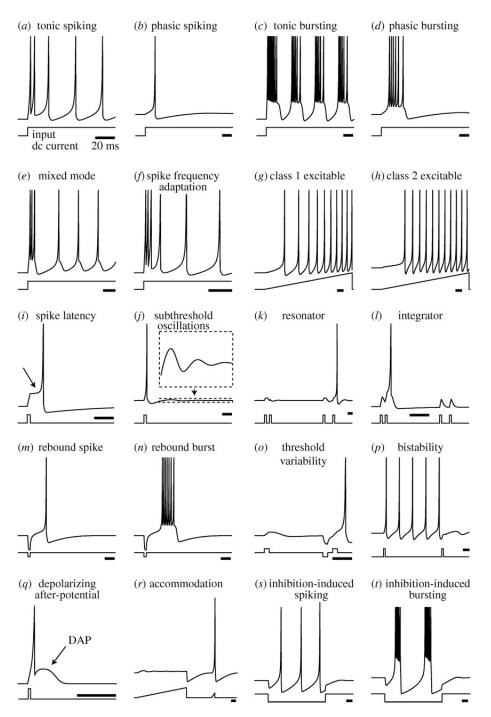

|    |                                                                                                            | 4.3.1 Biological, artificial and spiking neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

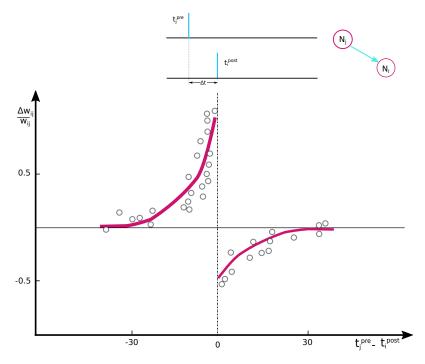

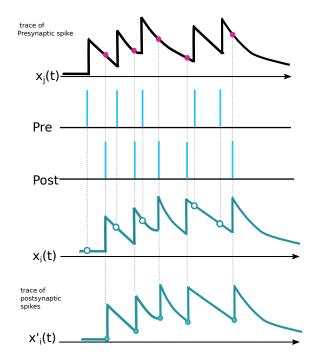

|    | 4.4                                                                                                        | Synapse and learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

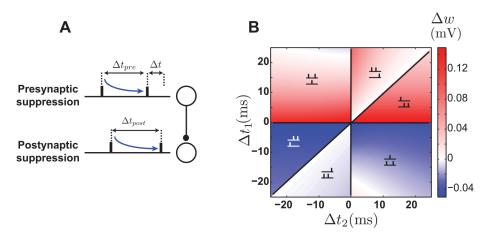

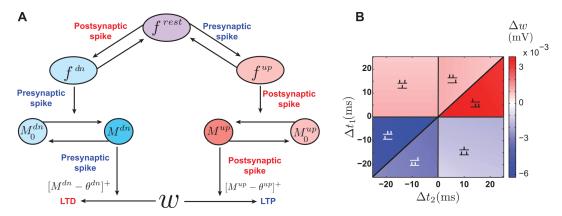

|    |                                                                                                            | 4.4.1 Synaptic learning and plasticity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

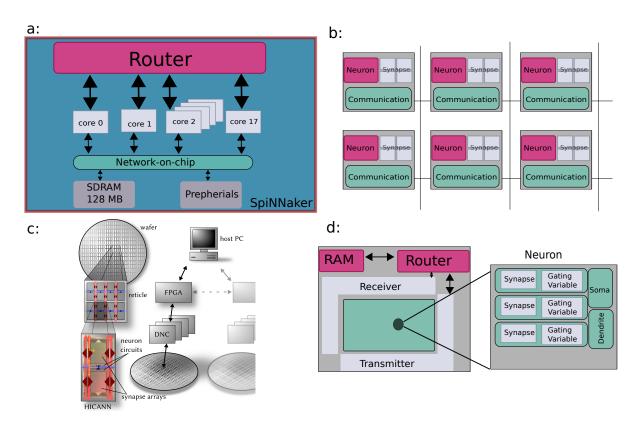

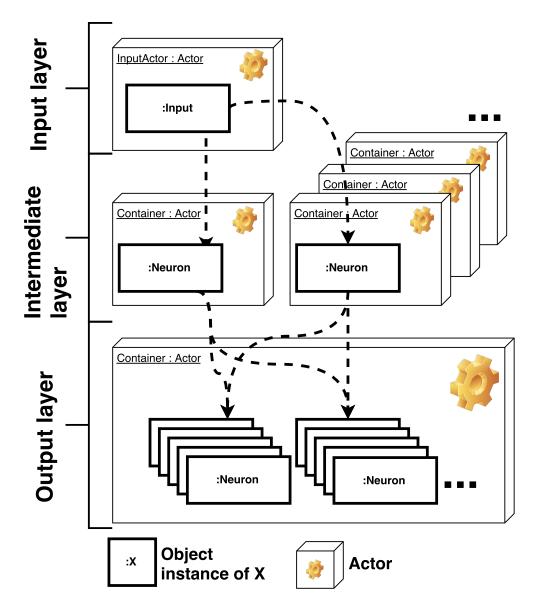

|    | 4.5                                                                                                        | Hardware spiking neural network systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    | 4.6                                                                                                        | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

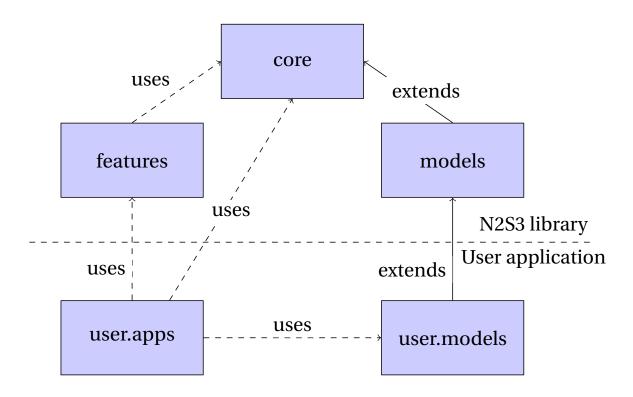

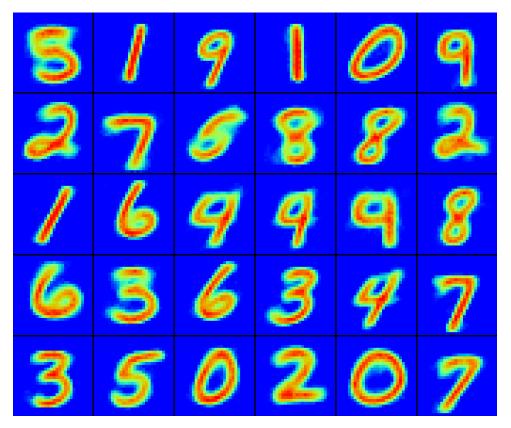

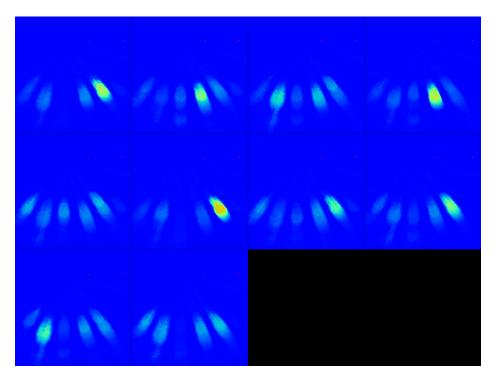

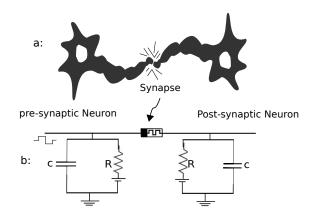

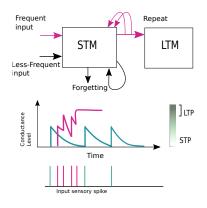

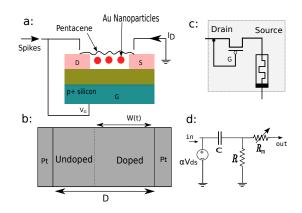

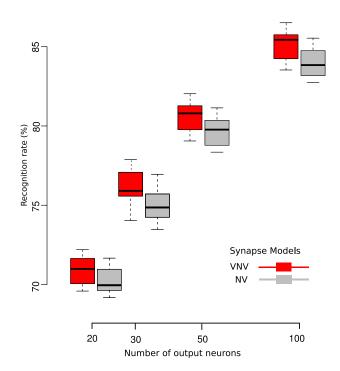

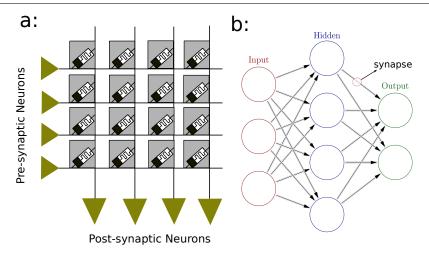

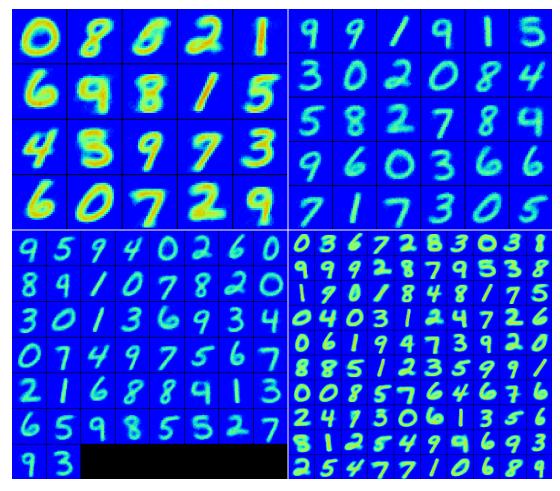

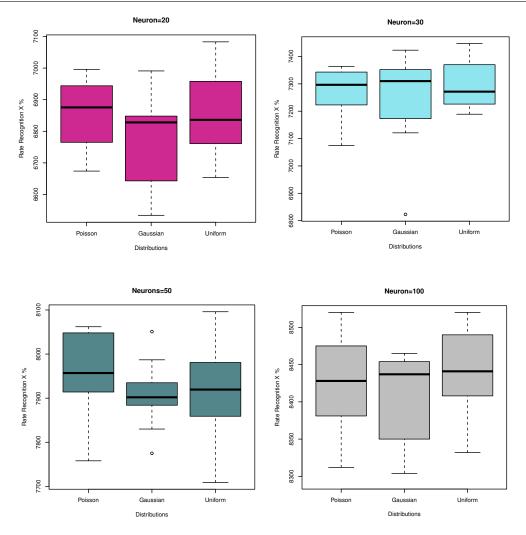

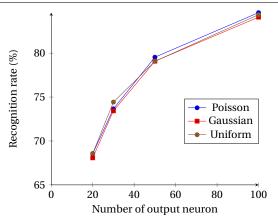

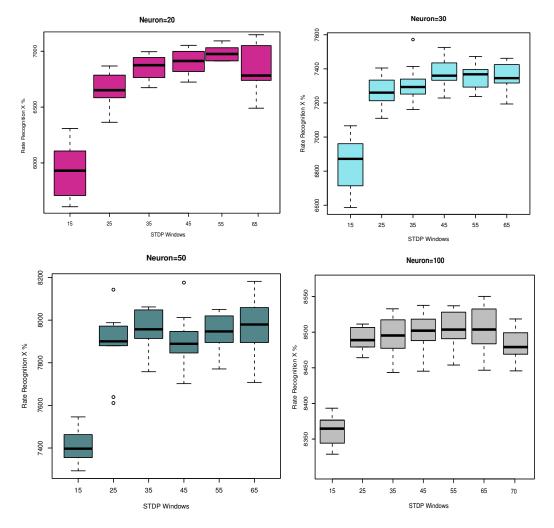

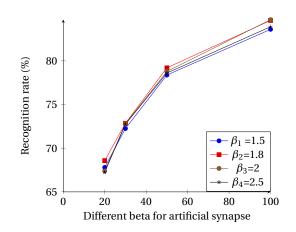

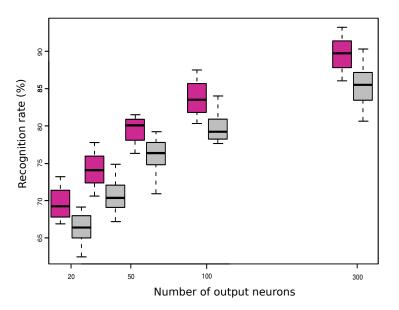

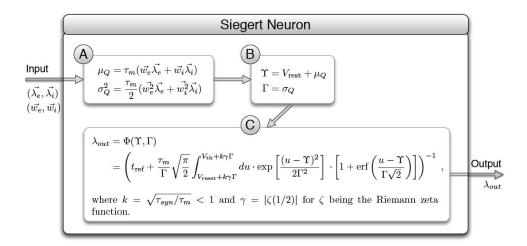

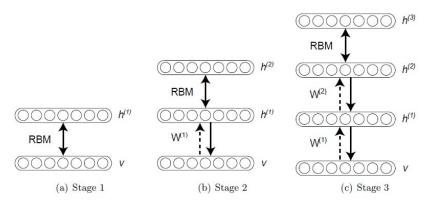

|    | 4.7                                                                                                        | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |