## Towards More Scalable Mutual Exclusion for Multicore Architectures

Jean-Pierre Lozi

#### ▶ To cite this version:

Jean-Pierre Lozi. Towards More Scalable Mutual Exclusion for Multicore Architectures. Operating Systems [cs.OS]. Université Pierre et Marie Curie (Paris 6), 2014. English. NNT: . tel-01303075v1

## HAL Id: tel-01303075 https://hal.science/tel-01303075v1

Submitted on 13 Dec 2020 (v1), last revised 23 Sep 2014 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

PhD Thesis, Université Pierre et Marie Curie Whisper team, LIP6/INRIA

**Subject:** Computer Science **Option:** Distributed Systems

Presented by: Jean-Pierre Lozi

### Towards More Scalable Mutual Exclusion for Multicore Architectures

Vers des mécanismes d'exclusion mutuelle plus efficaces pour les architectures multi-cœur

Presented on 16/07/14 in front of the following jury:

| M. Luc Bouganim                 | INRIA Paris-Rocquencourt                 | Paris, France       | Examiner |

|---------------------------------|------------------------------------------|---------------------|----------|

| M. Tim Harris                   | Oracle Labs                              | Cambridge, UK       | Examiner |

| M. Maurice Herlihy              | Brown University                         | Providence, RI, USA | Examiner |

| M. Gilles Muller                | Univ. Pierre et Marie Curie (LIP6/INRIA) | Paris, France       | Advisor  |

| M. Vivien Quéma                 | INP / ENSIMAG (LIG)                      | Grenoble, France    | Reviewer |

| M. Wolfgang Schröder-Preikschat | Friedrich-Alexander-Universität          | Erlangen, Germany   | Reviewer |

| M. Gaël Thomas                  | Univ. Pierre et Marie Curie (LIP6/INRIA) | Paris, France       | Advisor  |

## Abstract

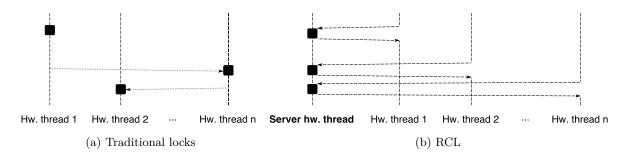

The scalability of multithreaded applications on current multicore systems is hampered by the performance of lock algorithms, due to the costs of access contention and cache misses. The main contribution presented in this thesis is a new lock algorithm, Remote Core Locking (RCL), that aims to improve the performance of critical sections in legacy applications on multicore architectures. The idea of RCL is to replace lock acquisitions by optimized remote procedure calls to a dedicated hardware thread, which is referred to as the *server*. RCL limits the performance collapse observed with other lock algorithms when many threads try to acquire a lock concurrently and removes the need to transfer lock-protected shared data to the hardware thread acquiring the lock because such data can typically remain in the server's cache.

Other contributions presented in this thesis include a profiler that identifies the locks that are the bottlenecks in multithreaded applications and that can thus benefit from RCL, and a reengineering tool developed with Julia Lawall that transforms POSIX locks into RCL locks. Eighteen applications were used to evaluate RCL: the nine applications of the SPLASH-2 benchmark suite, the seven applications of the Phoenix 2 benchmark suite, Memcached, and Berkeley DB with a TPC-C client. Eight of these applications are unable to scale because of locks and benefit from RCL on an x86 machine with four AMD Opteron processors and 48 hardware threads. Using RCL locks, performance is improved by up to 2.5 times with respect to POSIX locks on Memcached, and up to 11.6 times with respect to Berkeley DB with the TPC-C client. On an SPARC machine with two Sun Ultrasparc T2+ processors and 128 hardware threads, three applications benefit from RCL. In particular, performance is improved by up to 1.3 times with respect to POSIX locks on Memcached, and up to 7.9 times with respect to Berkeley DB with the TPC-C client.

**Keywords.** Multicore, synchronization, lock, combining, RPC, locality, busy-waiting, memory contention, profiling, reengineering.

# Acknowledgments

I would like to thank my advisors Gilles Muller and Gaël Thomas, as well as Julia Lawall for their help, support and reactivity during all of my PhD. Working with them has been a pleasure and a very positive experience. I would also like to thank the rest of the Regal and Whisper teams. In particular, I would like to thank other PhD students from room 25-26/231 without whom Paris would not have been such an enjoyable experience during my PhD years.

A big thanks Michael Scott for having kindly let me use the Niagara2-128 machine at the University of Rochester for more than a year, as well as Oracle, from which the machine was a gift. I would also like to thank James Roche for having been so quick to reboot it when needed.

A special thanks to Alexandra Fedorova from Simon Fraser University for her insight without which publishing a paper to USENIX ATC [71] would have been impossible, and to Vivien Quéma and Wolfgang Schröder-Preikschat for their constructive comments that helped improve this thesis.

Finally, finishing this PhD would not have been possible without the incredible support I received from my family during the past four years.

# Preface

This thesis presents the main research that I conducted in the Whisper (formerly Regal) team at Laboratoire d'Informatique de Paris 6 (LIP6), to pursue a PhD in Computer Science from the doctoral school "École Doctorale Informatique, Télécommunications et Électronique" (EDITE) in Paris. My PhD advisors were Gilles Muller and Gaël Thomas (LIP6/INRIA).

**Research presented in this thesis.** The main focus of the research presented in this thesis was the design of better techniques to ensure mutual exclusion on multicore architectures. My main contribution, presented in Chapter 4, is the design of a new lock algorithm, named Remote Core Locking (RCL), that dedicates one or several hardware threads for the serial execution of critical sections. This work led to the following publications, at a French conference and an international one:

- Le Remote Core Lock (RCL) : une nouvelle technique de verrouillage pour les architectures multi-cœur. Jean-Pierre Lozi. 8<sup>ème</sup> Conférence Française en Systemes d'Exploitation (CFSE '8). Saint-Malo, France, 2011. Best Paper award. [69]

- Remote Core Locking: Migrating Critical-section Execution to Improve the *Performance of Multithreaded Applications*. Jean-Pierre Lozi, Florian David, Gaël Thomas, Julia Lawall and Gilles Muller. In Proceedings of the 2012 USENIX Conference on Annual Technical Conference (USENIX ATC '12). Boston, USA, 2012. [71]

An INRIA research report [72] was also produced. Finally, my work was presented at many occasions. In particular, I presented a poster at EuroSys 2011 in Salzburg, Austria, and participated to the Work in Progress (WiP) session at SOSP'11 in Cascais, Portugal.

**Other research.** As a member of the Whisper team, I was also involved in other projects. In particular, I worked on EHCtor/Hector, a tool that makes it possible to detect resource-release omission faults in kernel and application code: I helped analyze the reports generated by the tool, and I devised techniques to exploit some of the bugs it found. This research has led to the two following publications:

- EHCtor: Detecting Resource-Release Omission Faults in Error-Handling Code for Systems Software. Suman Saha and Jean-Pierre Lozi. 9<sup>ème</sup> Conférence Française en Systemes d'Exploitation (CFSE '9). Grenoble, 2013. [94]

- Hector: Detecting Resource-Release Omission Faults in Error-Handling Code for Systems Software. Suman Saha, Jean-Pierre Lozi, Gaël Thomas, Julia Lawall, and Gilles Muller. In Proceedings of the 43<sup>rd</sup> Annual IEEE/IFIP International Conference on Dependable Systems and Networks (DSN '13). Budapest, 2013. Best Paper award. [95]

In the context of that work, I submitted a bug report to the PHP developers [105, 70] that describes a possible exploit for a memory leak that was found with Hector. I wrote a bug fix that was accepted by the PHP team and is part of the codebase since PHP 5.4.5.

Since my work on EHCtor/Hector was only secondary to my main research, it is not described further in this thesis: the reader is invited to refer to the aforementioned papers for more information.

# Contents

| 1        | Intr | Introduction                           |                |  |  |  |  |  |  |  |

|----------|------|----------------------------------------|----------------|--|--|--|--|--|--|--|

| <b>2</b> | Mul  | ticore architectures                   | 7              |  |  |  |  |  |  |  |

|          | 2.1  | Overview                               | $\overline{7}$ |  |  |  |  |  |  |  |

|          | 2.2  | Hardware threads                       | 8              |  |  |  |  |  |  |  |

|          | 2.3  | Communication between hardware threads | 9              |  |  |  |  |  |  |  |

|          |      | 2.3.1 CPU caches                       | 10             |  |  |  |  |  |  |  |

|          |      | 2.3.1.1 Overview                       | 10             |  |  |  |  |  |  |  |

|          |      | 2.3.1.2 Cache-coherent architectures   | 11             |  |  |  |  |  |  |  |

|          |      | 2.3.1.2.a Cache-coherence protocol     | 12             |  |  |  |  |  |  |  |

|          |      |                                        | 13             |  |  |  |  |  |  |  |

|          |      |                                        | 15             |  |  |  |  |  |  |  |

|          |      |                                        | 15             |  |  |  |  |  |  |  |

|          |      | 2.3.2 NUMA architectures               | 15             |  |  |  |  |  |  |  |

|          | 2.4  |                                        | 17             |  |  |  |  |  |  |  |

|          | 2.5  | 9                                      | 18             |  |  |  |  |  |  |  |

|          |      | 2.5.1 Magnycours-48                    | 18             |  |  |  |  |  |  |  |

|          |      |                                        | 19             |  |  |  |  |  |  |  |

|          |      |                                        | 19             |  |  |  |  |  |  |  |

|          |      |                                        | 20             |  |  |  |  |  |  |  |

|          |      | 2.5.3.2 Contention overhead            | 20             |  |  |  |  |  |  |  |

|          |      |                                        | 22             |  |  |  |  |  |  |  |

|          |      |                                        | 23             |  |  |  |  |  |  |  |

|          | 2.6  | U U                                    | 24             |  |  |  |  |  |  |  |

|          | _    |                                        |                |  |  |  |  |  |  |  |

| 3        |      | 0                                      | 25             |  |  |  |  |  |  |  |

|          | 3.1  |                                        | 26             |  |  |  |  |  |  |  |

|          | 3.2  | 1                                      | 27             |  |  |  |  |  |  |  |

|          | 3.3  | -                                      | 28             |  |  |  |  |  |  |  |

|          | 3.4  |                                        | 29             |  |  |  |  |  |  |  |

|          | 3.5  | 1                                      | 31             |  |  |  |  |  |  |  |

|          | 3.6  |                                        | 32             |  |  |  |  |  |  |  |

|          | 3.7  | 8                                      | 35             |  |  |  |  |  |  |  |

|          | 3.8  | U U                                    | 37             |  |  |  |  |  |  |  |

|          | 3.9  | 1 0                                    | 40             |  |  |  |  |  |  |  |

|          | 3.10 | Other lock algorithms                  | 42             |  |  |  |  |  |  |  |

|    | 3.11                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                            |

|----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

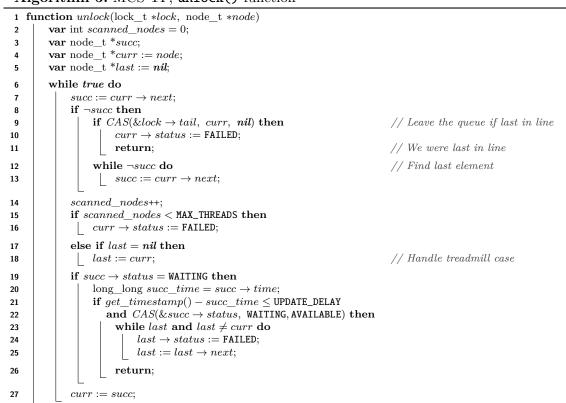

| 4  | Con<br>4.1<br>4.2<br>4.3 | tribution       44         Remote Core Lock       44         4.1.1       Core algorithm       44         4.1.2       Implementation of the RCL Runtime       44         4.1.2.1       Ensuring liveness and responsiveness       44         4.1.2.2       Algorithm details       56         4.1.3       Comparison with other locks       56         4.2.1       Profiler       57         4.2.2       Reengineering legacy applications       56         4.2.2       Reengineering legacy applications       57         50       Conclusion       57 | 567702447                    |

| 5  | Eva<br>5.1<br>5.2<br>5.3 | Iuation6Liblock6Microbenchmark6Applications65.3.1Profiling65.3.2Performance overview75.3.3Performance of SPLASH-2 and Phoenix applications75.3.4Performance of Memcached75.3.5Performance of Berkeley DB with TpccOverBkDb75.3.5.1Experimental setup75.3.5.2Performance analysis85.3.5.3Yielding the processor in busy-wait loops8                                                                                                                                                                                                                     | 1377047992                   |

|    | 5.4                      | 5.3.5.3 Yielding the processor in busy-wait loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |

| 6  | Con                      | clusion 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                            |

| A  | A.1<br>A.2<br>A.3        | Ach summary of the thesis9Introduction9Contribution9A.2.1 Algorithme de RCL9A.2.2 Outils10Évaluation10Á.3.1 Microbenchmark10A.3.2 Applications10Conclusion10                                                                                                                                                                                                                                                                                                                                                                                           | $5 \\ 9 \\ 9 \\ 1 \\ 1 \\ 3$ |

| Li | st of                    | Illustrations       119         Figures       111         Algorithms       12         Listings       12                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>1                       |

|    |                          | Listings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                            |

# Chapter 1 Introduction

Until the early 2000's, the performance of Central Processing Units (CPUs) had been steadily improving for decades thanks to rising hardware clock frequencies. However, due to physical limitations, CPU manufacturers have now found it impossible to keep increasing clock frequencies and instead focus on embedding several execution units in the same CPU. These execution units are referred to as *cores*, and technologies such as Simultaneous Hyper-Threading (SMT) replicate some parts of these cores in order to make them run several *hardware threads* simultaneously. The number of hardware threads in consumer CPUs keeps increasing for all computing devices, from servers to mobile phones. It is not uncommon nowadays for multiprocessor servers to include dozens of hardware threads.

The main downside of manufacturers increasing the number of hardware threads in CPUs instead of increasing their frequency is that applications do not see their performance automatically improve as newer and faster CPUs are released. Harvesting the performance of modern multicore architectures is difficult because most programs cannot be fully parallelized, and Amdahl's Law [4] shows that as the number of hardware threads increases, the critical path, i.e., portions of the application's source code that cannot be parallelized, ends up being the limiting factor. This is why, in order to use multicore architectures efficiently, it is important to focus on shortening the critical path. In most legacy applications, a large part of the critical path consists of *critical sections*, i.e., sections of code that are to be run in mutual exclusion.<sup>1</sup> Critical sections are usually protected by *locks*, i.e., synchronization mechanisms that make it possible for several threads to ensure mutual exclusion for the execution of sections of code that access the same resources.

In order to fully exploit the processing power of recent multicore machines, legacy applications must be optimized to exploit parallelism efficiently, which can be extremely complex and requires a lot of work: while making legacy applications scale up to a few hardware threads is relatively simple with naïve, coarse-grained parallelization, getting them to scale on newer multicore architectures with dozens of hardware threads remains a challenge. Since a large number of very complex applications has been developed over the previous decades without taking these architectures into account, rewriting large parts of the legacy codebase in order to harvest the performance of modern multicore architectures is a very costly task that will take several years.

One way of getting legacy applications to scale on multicore architectures is to shorten the critical path by reducing the size of critical sections, i.e., to use *fine-grained locking* [6, 55]:

<sup>&</sup>lt;sup>1</sup>The critical path can also contain other parts such as program initialization and finalization as well as transitions between loop-parallel program sections. These parts are identified as *data management housekeeping* and *problem irregularities* by Amdahl [4].

while this approach is generally regarded as being very efficient, it can be extremely complex for programmers. There is no general technique that makes it possible to reduce the size of critical sections, instead, developers must use different approaches for each one of them, thereby increasing the complexity of the concurrent logic of the application and increasing the probability of introducing hard-to-find concurrency bugs. It is also possible to avoid the use of critical sections in some cases and to rely on atomic instructions for synchronization instead, by using *lock-free* algorithms and data structures [56, 77, 52, 40, 62, 63]. While this approach can be very efficient in some cases and efficient lock-free algorithms have been proposed for most standard data structures such as stacks, queues, and skiplists, it is not possible to replace any set of critical sections with an efficient lock-free algorithm. Finally, using *transactional memory*, either implemented in software or hardware, has been proposed as an alternative to locks [61, 54, 98, 53, 45]. While transactional memory can be easier to use than locks, it is currently not widely used due to limited hardware support and weak performance of software implementations. Moreover, with transactional memory, critical sections cannot perform any operation that cannot be undone, including most I/O.

Other solutions have been proposed to harvest the performance of multicore architectures. Some approaches simply focus on improving the implementation of one specific mechanism on multicore architectures, like Remote Procedure Calls (RPC) [10, 11, 42], but these techniques are too limited to make it possible to harvest the processing power of multicore machines by legacy applications in the general case. Some specific improvements to parts of the operating system such as the scheduler have been proposed for multicore architectures [64], but they do not remove the need to modify applications. Whole new operating systems designs have also been proposed, such as Opal [22], Corey [13], Multikernel [9], and Helios [78], but legacy operating systems have become so complex and feature-rich that switching to completely new operating systems now would come at a major redevelopment cost and legacy applications would need to be completely rewritten. Some tools have been proposed to help with the redesign of applications on multicore architectures, such as profilers [87, 65], which can be useful to detect bottlenecks. Profilers do not aim to fix these bottlenecks however, other techniques have to be used once the causes of the lack of scalability have been identified.

Another way to improve the performance of multithreaded applications on multicore architectures is to improve the way locks are implemented. The main advantage of this approach is that it does not require a complete redesign of applications. Over the last twenty years, a number of studies [2, 8, 12, 49, 51, 59, 75, 96, 100, 102] have attempted to optimize the performance of locks on multicore architectures, either by reducing access contention or by improving cache locality. Access contention occurs when many threads simultaneously try to enter critical sections that are protected by the same lock, thereby saturating the memory bus with messages from the underlying cache-coherence protocol in order to reach an agreement as to which thread should obtain the lock first. The lack of cache locality becomes a problem when a critical section accesses shared data that has recently been written by another hardware thread, resulting in cache misses, which greatly increase the critical section's execution time. Addressing access contention and cache locality together remains a challenge. These issues imply that some applications that work well on a small number of hardware threads do not scale to the number of hardware threads found in today's multicore architectures.

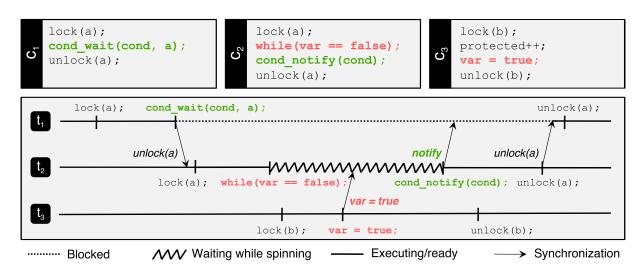

Recently, several approaches have been proposed to execute a succession of critical sections on a single *server* (or *combiner*) hardware thread to improve cache locality [51, 102, 39]. Such approaches also incorporate a fast transfer of control from other *client* hardware threads to the server, to reduce access contention. Suleman et al. [102] propose a hardware-based solution, evaluated in simulation, that introduces new instructions to perform the transfer of control, and uses a hardware thread from a special fast core to execute critical sections. Software-only algorithms in which the server is an ordinary client thread and the role of server is handed off between clients periodically have also been proposed [82, 51, 39]. These algorithms are referred to as *combining locks*. Combining locks are faster than traditional locks, but they sometimes incur an overhead for the management of the server role and the list of threads, and they are vulnerable to preemption. Furthermore, neither Suleman et al.'s algorithm nor combining locks propose a mechanism to handle condition variables, which makes them unable to support many widely used applications.

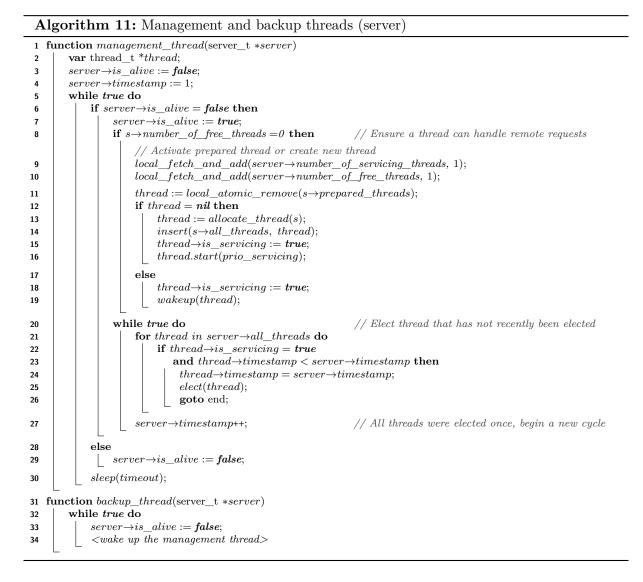

The objective of the research presented in this thesis is to focus on decreasing the time spent by applications in critical sections in such a way that avoids redesigning whole applications, by focusing on reducing the time to enter critical sections and improving their memory access locality. The main contribution presented in this thesis is a new locking technique, Remote Core Locking (RCL), that aims to improve the performance of legacy multithreaded applications on multicore hardware by executing critical sections that are protected by highly contended locks on one or several dedicated server hardware threads. In particular, RCL targets legacy server applications that run on modern multicore servers. It is entirely implemented in software and supports x86 and SPARC multicore architectures. At the basis of RCL is the observation that most applications do not scale to the number of hardware threads found in modern multicore architectures, and thus it is possible to *dedicate* the hardware threads that do not contribute to improving the performance of the application to serving critical sections. It is therefore not necessary to burden the application threads with the role of server, as done in combining locks. The design of RCL addresses both access contention and locality. Contention is solved by a fast transfer of control to a server, using a dedicated cache line for each client to achieve busy-wait synchronization with the server hardware thread. Locality is improved because shared data is likely to remain in the server hardware thread's cache, allowing the server to access such data without incurring cache misses. In this, RCL is similar to combining locks, but it has a lower overall overhead, it resists better to preemption because the dedicated server thread always makes progress, and it proposes a mechanism to handle condition variables, which makes it directly usable in real-world applications. RCL is well-suited to improve the performance of a legacy application in which contended locks are an obstacle to performance, since using RCL enables improving resistance to contention and locality without requiring a deep understanding of the source code. On the other hand, modifying locking schemes to use fine-grained locking, lock-free algorithms or transactional memory is time-consuming, requires an overhaul of the source code, and does not improve locality.

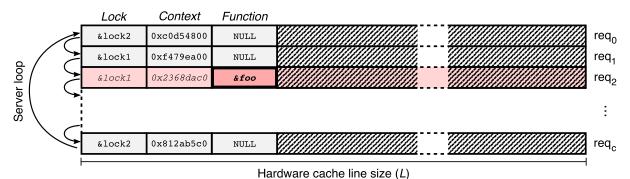

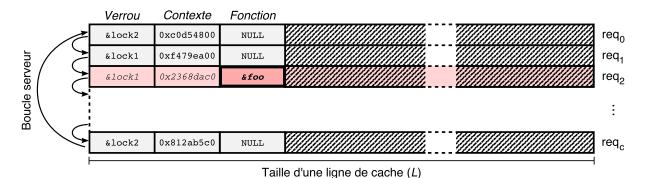

Other contributions presented in this thesis include a methodology along with a set of tools to facilitate the use of RCL in legacy applications. Because RCL serializes critical sections associated with locks managed by the same server hardware thread, transforming all locks into RCLs on a smaller number of servers induces *false serialization*: some servers serialize the execution of critical sections that are protected by different locks and therefore do not need to be executed in mutual exclusion. In some cases, false serialization can introduce a significant overhead. Therefore, the programmer must first decide which lock(s) should be transformed into RCLs and which server(s) handle which lock(s). A profiler was written for this purpose. It is designed to identify which locks are frequently used by the application, to measure how much time is spent on locking, and to measure how good the data locality of critical sections is. Based on this information, a set of simple heuristics are proposed to help the programmer decide which locks must be transformed into RCLs. An automatic reengineering tool for C programs was

designed with the help of Julia Lawall in order to transform the code of critical sections so that it can be executed as a remote procedure call on the server hardware thread: the code within a critical section must be extracted as a function. The argument passed to that function will be its *context* object, i.e., an object that contains copies of all variables referenced or updated by the critical section that are declared in the function containing the critical section code. RCL takes the form of a runtime for Linux and Solaris that is compatible with POSIX threads, and that supports a mixture of RCL and POSIX locks in a single application.

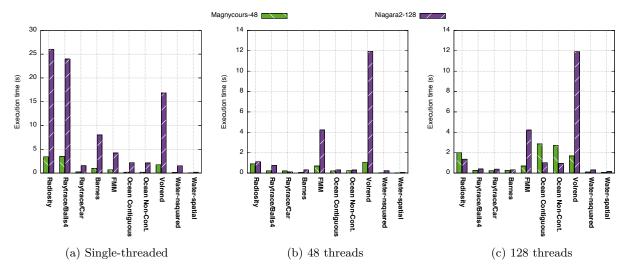

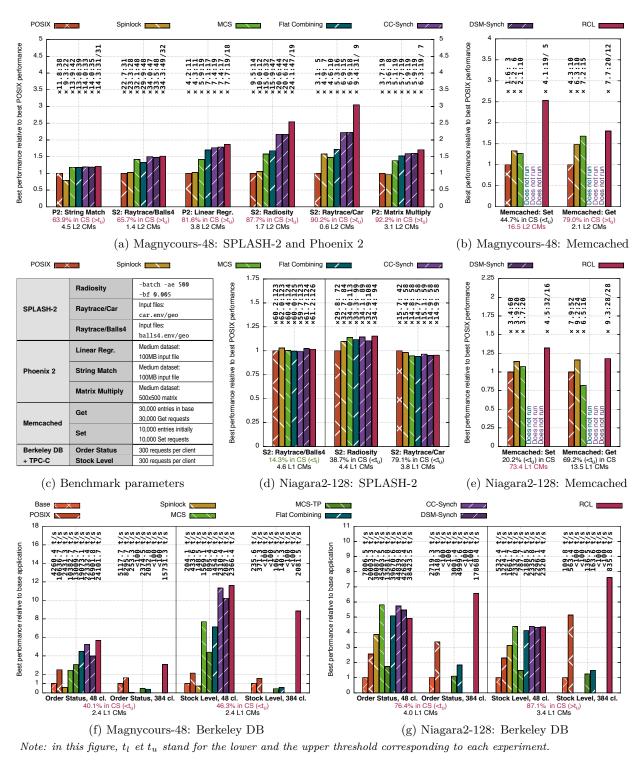

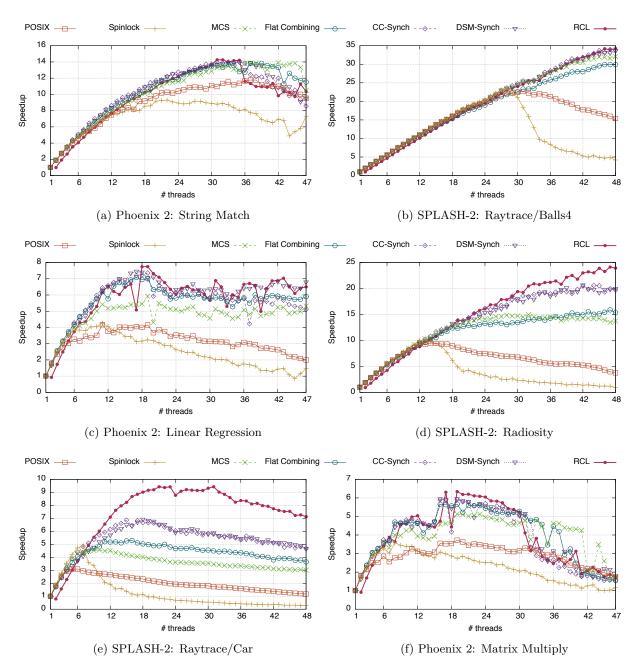

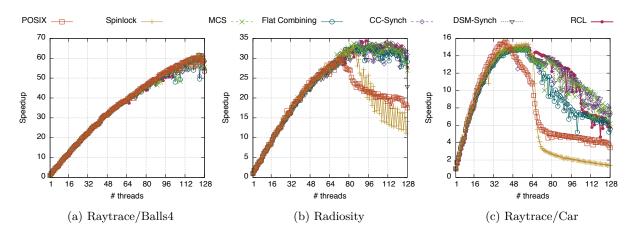

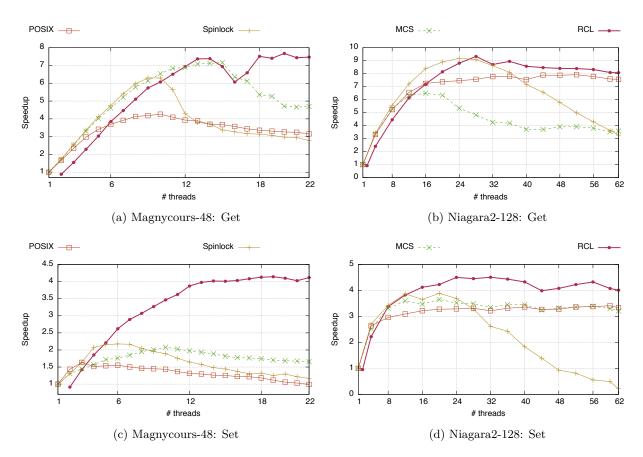

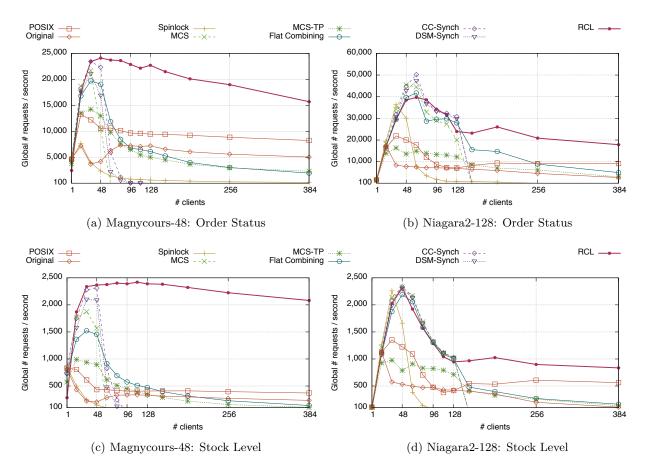

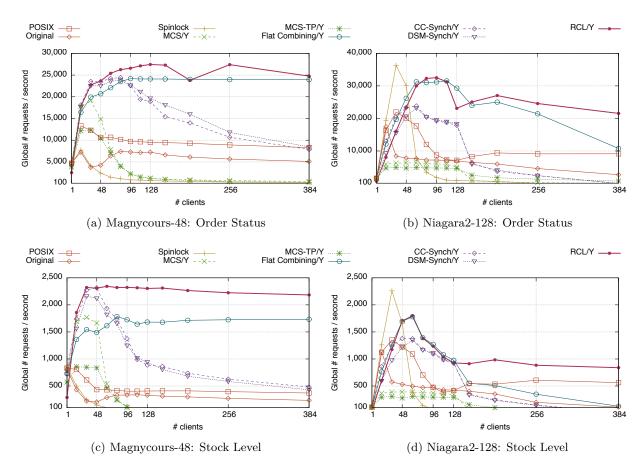

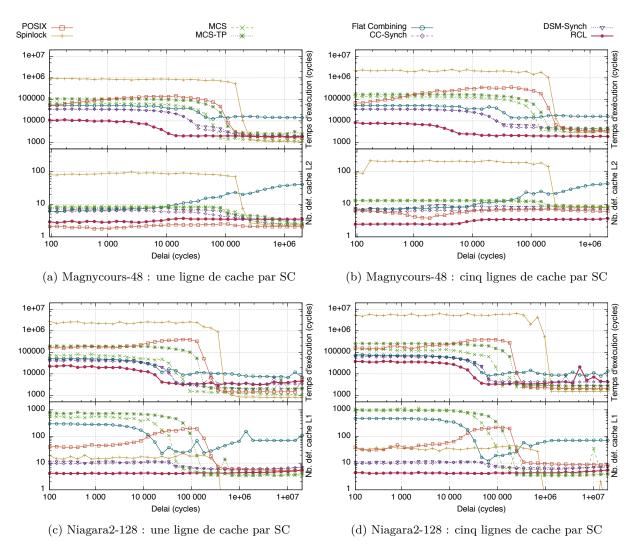

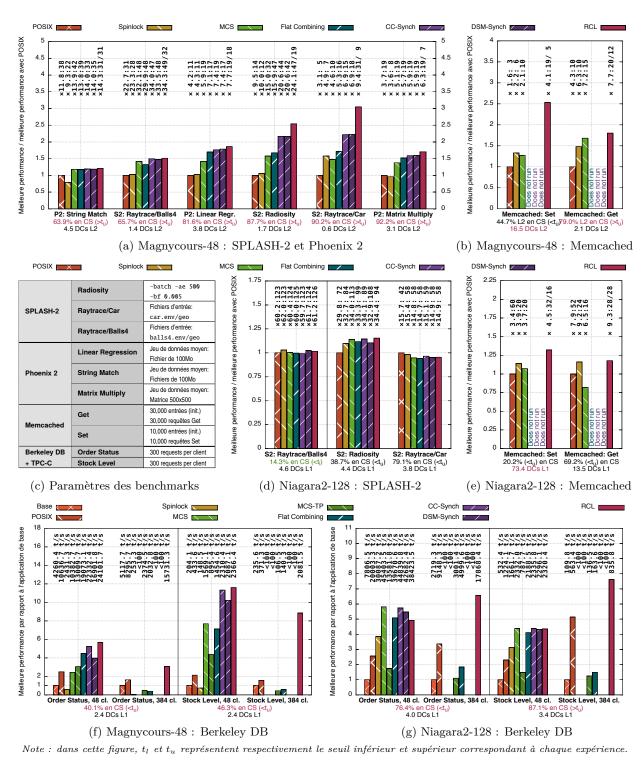

The performance of RCL is compared to other locks with a custom microbenchmark which measures the execution time of critical sections that access a varying number of shared memory locations. Furthermore, based on the results of the profiler, three benchmarks from the SPLASH-2 [107, 99, 110] suite, three benchmarks in the Phoenix 2 [101, 103, 112, 92] suite, Memcached [26, 41], and Berkeley DB [80, 79] with a TPC-C benchmark developed at Simon Fraser University were identified as applications that could benefit from RCL. In each of these applications, RCL is compared against a basic spinlock, the standard POSIX lock, MCS [75], and Flat Combining [51]. RCL is also compared with CC-Synch and DSM-Synch [39], two state-of-the-art algorithms that were designed concurrently with RCL, and therefore were not included in the evaluation of the RCL paper that was published at USENIX ATC [71]. Comparisons are made for a same number of hardware threads, which means that there are fewer application threads in the RCL case, since one or more hardware threads are dedicated to RCL servers.

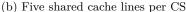

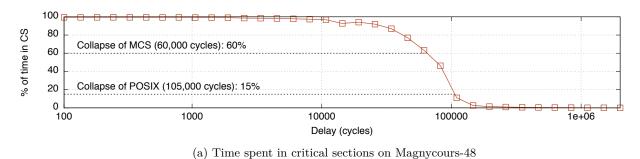

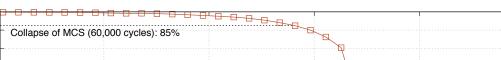

RCL is evaluated on two machines: (i) Magnycours-48, an x86 machine with four AMD Opteron CPUs and 48 hardware threads running Linux 3.9.7, and (ii) Niagara2-128, a SPARC machine with two Ultrasparc T2 CPUs and 128 hardware threads running Solaris 10. Key highlights of the results are:

- On a custom microbenchmark, under high contention, RCL is faster than all other evaluated approaches: on Magnycours-48 (resp. Niagara2-128), RCL is 3.2 (resp. 1.8) times faster than the second best approach, CC-Synch, and 5.0 (resp. 7.2) times faster than the POSIX lock.

- On other benchmarks, contexts are small, and thus the need to pass a context to the server has only a marginal performance impact.

- On most benchmarks, only one lock is frequently used and therefore only one RCL server is needed. The only exception is Berkeley DB with the TPC-C client, which requires two or three RCL servers to reach optimal performance by reducing false serialization.

- On Magnycours-48 (resp. Niagara2-128), RCL improves the performance of five (resp. one) application(s) from the SPLASH-2 and Phoenix 2 benchmark suites more than all other evaluated locks.

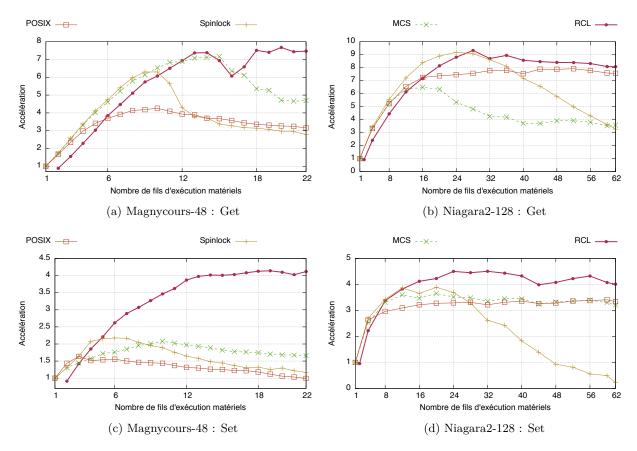

- For Memcached with Set requests, on Magnycours-48 (resp. Niagara2-128), RCL yields a speedup of 2.5 (resp. 1.3) times over the POSIX lock, 1.9 (resp. 1.2) times over the basic spinlock and 2.0 (resp. 1.2) times over MCS. The number of cache misses in critical sections is divided by 2.9 (resp. 2.3) by RCL, which shows that it can greatly improves locality. Combining locks were not evaluated in this experiment because they do not implement condition variables, which are used by Memcached.

- For Berkeley DB with the TPC-C client, when using Stock Level transactions, on Magnycours-48 (resp. Niagara2-128) RCL yields a speedup of up to 11.6 (resp. 7.6) times over the original Berkeley DB locks for 48 (resp. 384) simultaneous clients. RCL resists better than

other locks when the number of simultaneous clients increases. In particular, RCL performs much better than other locks when the application uses more client threads than there are available hardware threads on the machine, even when other locks are modified to yield the processor in their busy-wait loops.

**Organization of the document.** The thesis is structured as follows:

- Chapter 2 focuses on multicore architectures. It presents the general design of these architectures and describes the most common bottlenecks they suffer from. The two machines used in the evaluations are also described in that chapter.

- Chapter 3 presents the evolution of lock algorithms. Detailed algorithms of all locks that are used in the evaluation in Chapter 5 are presented in that chapter, as a reference.

- Chapter 4 presents the main contributions of the research work presented in this thesis, namely, RCL and its implementation, the profiler that makes it possible to identify which applications and locks can benefit from RCL, and the reengineering tool that automatically transforms applications so that they can be used with RCL.

- Chapter 5 presents an evaluation of RCL's performance. First, a microbenchmark is used to obtain a first estimate of the performance of RCL as well as that of some of the locks presented in Chapter 3. Then, the profiler designed to help decide when using RCL would be beneficial for an application is presented. Finally, using the results of the microbenchmark combined with the results of the profiler presented in Chapter 4, a set of applications that are likely to benefit from RCL is identified, and RCL as well as other locks are evaluated with the applications from that set.

- Finally, Chapter 6 concludes the thesis and considers future research directions.

## Chapter 2

## Multicore architectures

This chapter presents multicore architectures and their bottlenecks. Section 2.1 quickly presents the various components of a multicore architecture. Section 2.2 presents hardware threads, i.e., the minimal execution units of multicore machines. Section 2.3 describes how hardware threads communicate with each other through the CPU caches and the RAM. Section 2.4 presents heterogeneous multicore architectures, i.e., architectures that use various cores with different characteristics. Section 2.5 presents the machines used in the evaluation. Finally, Section 2.6 concludes the chapter.

#### 2.1 Overview

Historically, most CPUs contained a single processing core, with a single hardware thread, and manufacturers mainly improved the performance of CPUs by increasing their clock speed, which went from a few megahertz in the early 1980's to several gigahertz twenty years later. However, in the early 2000's, increasing the CPU clock speed became increasingly difficult due to power dissipation, which makes CPUs with high clock speeds consume too much energy and overheat. Manufacturers instead switched to bundling several processing cores into CPUs in order to keep increasing overall processing performance, even though exploiting the computing power of multicore architectures requires parallelizing applications efficiently, whereas clock speed increases automatically improved the performance of all software.

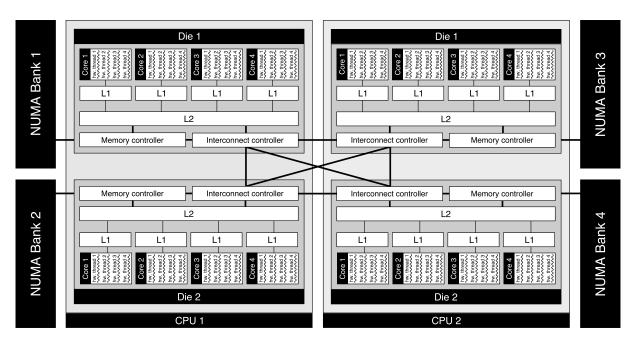

A typical, current, consumer multicore machine is shown in Figure 2.1. It can have one or several *Central Processing Units* (*CPUs*, two in the figure). Each CPU can have one or several *dies* (four in the figure), and each die contains one or several *cores* (16 in the figure). Some machines only run one hardware thread per core, while others use hardware multithreading to run several hardware threads in parallel (64 in the figure). Communication between hardware threads by low-level CPU caches (L1 or L2, L1 in the figure). Communication between cores is typically ensured by high-level CPU caches (L2 or L3, L2 in the figure). Communication between dies and/or CPUs is ensured by a data bus. Nowadays, buses are most frequently implemented in the form of a point-to-point interconnect. In Figure 2.1, all dies are directly connected to each other, but that is not always the case: sometimes, several hops are needed for the communication between two dies. All dies are connected to the Random Access Memory (RAM) via their memory controller. In Uniform Memory Access (UMA) architectures, accessing the memory from any of the dies comes at the same cost (latency and speed). The

#### CHAPTER 2. MULTICORE ARCHITECTURES

Figure 2.1: Example of a multicore architecture

architecture presented in Figure 2.1 uses Non-Uniform Memory Access, because the memory is split in different memory banks, and dies access local memory banks faster than remote memory banks.

Moreover, the machine presented in Figure 2.1 is *cache-coherent*, which means that all of its memory is directly addressable, and the underlying cache-coherence mechanism, implemented in hardware, transparently fetches data in the right memory bank or CPU cache to bring it to the hardware thread that requests it. Some new architectures are now *non-cache-coherent*, which means that each core or CPU can only access its own local memory, and explicit messages must be used by the software layer to transfer data from one core to the other. However, non-cache-coherent architectures are not very commonly used yet. Section 2.3.1 focuses on cache-coherent vs. non-cache-coherent architectures in more detail.

#### 2.2 Hardware threads

Until the early 2000's, most consumer CPUs were only able to run a single software thread at any given time, i.e., they only provided a *single hardware thread*. Multitasking was handled by schedulers, which used time-sharing to enable several software threads to use the CPU concurrently. The first technique that was commonly used to introduce parallelism in CPUs was *instruction pipelines*: each instruction is broken up into a number of steps, and different steps from consecutive instructions are executed in parallel [93]. With the introduction of multicore CPUs, the parallelism provided by the multiple cores was combined with the parallelism provided by the instruction pipeline, in order to improve performance.

In many multicore architectures, several software threads can be running at a given time if they are placed on different cores. Moreover, in order to increase parallelism even more, some CPU manufacturers do not only bundle several CPU cores into a single CPU, they also replicate some parts of the cores in order to make each one of them execute several software threads simultaneously: from the point of view of the developer, each core provides *multiple hardware threads* that are completely independent execution units, and one software thread can be running on each of these hardware threads at any given time [106]. In practice, however, two hardware threads running concurrently on the same core may slow down each other more than if they were running on different cores, because they share resources such as, for instance, their Arithmetic and Logic Unit (ALU). The idea of hardware multithreading is to increase parallelism at a lower cost than by adding more cores, because some components that are not usually bottlenecks can be shared by several hardware threads.

Each hardware thread must have access to the following components, some of which possibly being shared: (i) A set of registers that store the data that is currently being used by the hardware thread (generally not shared), (ii) an arithmetic and logic unit, often completed with a Floating Point Unit (FPU) for operations on floating point numbers, (iii) a Transaction Lookaside Buffer (TLB), which is a cache that is used to accelerate the translation of virtual memory addresses into physical addresses, and (iv) elements that are located outside CPU cores and sometimes shared by several cores, as shown in Figure 2.1, such as data and instruction CPU caches, or memory/interconnect controllers. Hardware multithreading can be implemented using three techniques: coarse-grained multithreading, fine-grained multithreading, and simultaneous multithreading.

**Coarse-grained multithreading.** Also called *block multithreading* or *cooperative multithread-ing*, coarse-grained multithreading lets a thread run until it is blocked by an event that causes a long enough stall, such as a cache miss or a page fault. The thread will not be scheduled again until the data or signal it was waiting for has arrived. Each hardware thread must have its own set of data and control registers, so that the CPU can switch between hardware threads in a single CPU cycle.

**Fine-grained multithreading.** Also called *interleaved multithreading*, with fine-grained multithreading, the CPU starts executing an instruction from a different hardware thread at each cycle, in a round-robin fashion. Since instructions from several threads are executed in parallel in the pipeline, each stage in the pipeline must track which thread's instruction it is processing. Moreover, since more threads are executed in parallel than with coarse-grained multithreading, shared resources such as the TLB and CPU caches must be larger so that they do not become bottlenecks.

Simultaneous multithreading (SMT). It is the most advanced implementation of hardware multithreading, and it is designed for superscalar CPUs. In a traditional superscalar CPU with one hardware thread, several instructions are issued from a single thread at each CPU cycle. With SMT, CPUs issue several instructions from multiple threads at each CPU cycle. This requires to track which thread's instruction is being processed for each thread at each stage of the pipeline. However, SMT has the advantage to use issue slots better than traditional superscalar processors, because single threads only have a limited amount of instruction-level parallelism, whereas multiple threads are typically independent from each other. SMT is used in some Intel (HyperThreading) and Sun/Oracle CPUs. In particular, SMT is used by the UltraSPARC T2+, the CPU used by Niagara2-128, one of the machines described in Section 2.5.2 and used in the evaluation in Chapter 5.

#### 2.3 Communication between hardware threads

This section describes the means by which hardware threads communicate with each other. Section 2.3.1 describes CPU caches and how they are used for communicating between hardware threads. It also presents cache-coherent and non-cache-coherent architectures. Section 2.3.2 focuses on NUMA architectures.

#### 2.3.1 CPU caches

An overview of CPU caches is given in Section 2.3.1.1. Cache-coherent and non-cache-coherent architectures are described in Sections 2.3.1.2 and 2.3.1.3, respectively.

#### 2.3.1.1 Overview

CPU caches (simply referred to as "caches" henceforth) are fast components that store small amounts of data closer to CPU cores in order to speed up memory access. The data stored in caches can either be duplicates of data stored in the RAM and that is expected to be used soon by a hardware thread, or values that have been recently computed and that will be flushed back to the RAM later. As shown in Figure 2.1, caches are usually organized in a *hierarchy*, with typically two to three levels (L1, L2 and L3 caches). The farther caches are from CPU cores, the larger and slower they are. The unit of addressable data in a cache is a *cache line*, which means that each time data is transfered to a cache, the minimum of data that can be transfered is the size of the cache line for that cache (a typical cache line size in current architectures could be 64 or 128 bytes). When a hardware thread tries to read or write data that is not available in its lowest level cache, a *cache miss* is triggered, and the cache line is fetched from higher level caches or from the RAM. Caches can either store instructions, data, or both.

**Replacement policy.** In the case of a cache miss, the cache may have to evict one of the cache lines to make room for the newly fetched cache line. There are many possible policies to determine which cache line should be evicted from the cache. For instance, the *Least Recently Used (LRU)* or the *Least Frequently Used (LFU)* cache line can be evicted.

Write policy. When data is written into a cache line that is present in the cache (*write hit*), it must be flushed into the main memory. There are two main approaches:

- With a *write-through* policy, a write to the cache causes a write to the main memory.

- With a *write-back* policy, writes to the main memory are delayed: cache lines that have been written over in the cache are marked *dirty*, and dirty cache lines are written to the main memory when they are evicted from the cache (following the replacement policy).

If a hardware thread needs to write data to a cache line that is not present into the cache (*write miss*), two main approaches are possible:

- With a *no-write-allocate* policy, the cache line is not loaded into the cache, instead, the data is directly written into the main memory.

- With a *write-allocate* policy, the cache line is loaded into the cache, then overwritten into the cache with the new data (*write hit*).

Any pair of write-hit and write-miss policies is functional, but typically, most caches use either write-through combined with no-write-allocate, or write-back combined with write-allocate. However, many different types of caches exist that use variations of the policies listed above. Moreover, write policies are more complicated on cache-coherent architectures, because the same cache line may be stored in the caches of several cores, and some caches may not hold the most recent version of the data. This issue is discussed in more detail in Section 2.3.1.2.

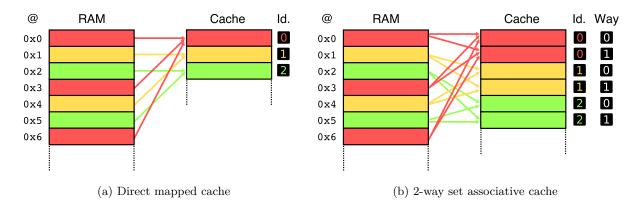

Figure 2.2: CPU cache associativity

Associativity. When a cache line is inserted into the cache, the replacement policy determines which cache line is evicted and will be replaced with the new cache line. If the replacement policy may evict any cache line, regardless of the address it maps to (by picking the *least recently used* cache line, for instance), the cache is said to be *fully associative*, as illustrated in Figure 2.2a. If, on the contrary, a memory location may only be mapped to one location in the cache, determined by its address, the cache is said to be *direct mapped*. Typically, the replacement policy can pick a location in the cache among a set of n cache lines, the cache is said to be n-way associative. Figure 2.2b illustrates the behavior of a n-way set associative cache for n = 2: each element in memory can be stored in two different locations in the cache. Increasing n decreases the number of cache misses, because if multiple memory locations that map to the same address in the cache are used in a short time period, several of them will be able to fit in the cache. On the other hand, n entries in the cache must be checked in order to determine whether a cache line is present in the cache, therefore, increasing n induces a overhead. In n-way set associative caches, a popular replacement policy is *Pseudo-LRU (PLRU)*: if a cache line must be inserted into a set s, the least recently used element of s is evicted.

**Prefetching data.** In order to reduce the number of cache misses, CPUs try to predict which data will be used in the near future and load it in cache before it is accessed. Modern CPUs include a data prefetching unit that performs this job. The data prefetching unit performs well when an application has regular access patterns (stride accesses such as scanning an array, or following pointers in linked-list traversals). Even though a lot of memory access patterns are too complex to be recognized by the data prefetching unit, they rarely hinder performance [60]. Modern processors also prefetch instructions, which can be a complex task due to branches in programs: the instruction prefetch is sometimes part of a complex branch prediction algorithm.

#### 2.3.1.2 Cache-coherent architectures

On multicore architectures, each core has its own local caches. If different caches hold different versions of the same data, two hardware threads may not have the same view of the global memory, and it may be hard for hardware threads to ensure that the data they are reading is up-to-date. To prevent this, most CPUs nowadays are *cache-coherent*, which means that even though cores have their own local caches with possibly different versions of the same data, a *cache-coherence protocol* is implemented in the hardware in order to make sure that different hardware threads have a consistent view of the global memory.

An architecture is said to be cache-coherent if the following conditions are met [86]:

- If a hardware thread t writes then reads from a location l, with no writes from other hardware threads at the same location between the write and the read operation, then t must read the value it wrote at the location l.

- A read from a hardware thread  $t_1$  to a location l that was previously written by  $t_2$  must return the value that  $t_2$  wrote at that location if enough time passed between the read and the write operation, and if no other hardware thread wrote data at l between the read and the write operation.

- Writes to the same location are serialized, i.e., two writes to the same location by any two hardware threads are seen in the same order by all hardware threads.

Section 2.3.1.2.a describes *cache-coherence protocols* that ensure that all hardware threads have a consistent view of the global memory. Section 2.3.1.2.b presents instructions that facilitate synchronization between hardware threads. Finally, Section 2.3.1.2.c gives a quick overview of common bottlenecks on cache-coherent architectures.

#### 2.3.1.2.a Cache-coherence protocol

In cache-coherent architectures, hardware threads typically rely on the cache-coherence protocol for communication: when a hardware thread  $t_1$  needs to send a value to a hardware thread  $t_2$ , it writes the value at a known memory address, and  $t_2$  reads it later, possibly busy-waiting for the value at that address to be modified by  $t_1$ . Most cache-coherence protocols that are used in current multicore machines are based on the MESI protocol [85]. The name MESI comes from the four possible *states* it defines for cache lines: Modified, Exclusive, Shared and Invalid. These states can be described thus:

- Modified. The data in the cache line has been modified locally (i.e., it is *dirty*), and *only* resides in this cache. The copy in the main memory is is not up to date, therefore, if the cache line is evicted or changes its state, its data must be flushed to the main memory.

- Exclusive. The data in the cache line is unmodified (i.e., it is *clean*), and it does not reside in any other cache.

- Shared. The data in the cache line is clean but other copies may reside in other caches.

- **Invalid.** The cache line does not contain valid data. This typically happens when a shared cache line was modified in one of the caches: other copies of the data got *invalidated* by the cache-coherence protocol.

While the MESI protocol is functional, its performance is not optimal on architectures with a large number of cores because of its communication overhead. In particular, the MESI protocol may send many high-latency messages that contain redundant data: if a cache requests data that resides in many different caches (Shared state), all caches may send the same data to the requesting cache, which results in wasted bandwidth. Another drawback of the MESI protocol is that the only way for data from a Modified cache line to be accessed by remote hardware threads is to flush that data to the main memory and fetch it again, when fast cache-to-cache communications should be sufficient. Improved versions of the MESI protocol, with more states, have been implemented to solve these issues. Two widely-used variants are the MESIF protocol and the MOESI protocol.

**MESIF protocol.** The MESIF protocol has been used by Intel CPUs since the Nehalem architecture. It adds a Forwarded state to the MESI protocol and modifies its Shared state. The Forwarded (F) state is a variant of the Shared state that expresses the fact that the cache should act as the designated responder for that cache line. At most one cache holds a copy of data in the Forwarded state. If a cache requests data that exists in various caches, and if one of the caches holds a copy of the data that is in the Forwarded state, only that cache will send the data: no redundant messages are sent. If no version of the data is in the Forwarded state, the data will be fetched from the main memory, which may induce a overhead. This can happen if a cache line that was in the Forwarded state was evicted. To avoid this issue, the most recent requester of the data is automatically assigned the Forwarded state, which decreases the risk of Forwarded cache lines getting evicted.

**MOESI protocol.** The MOESI protocol is used by AMD and Sun/Oracle CPUs. It adds an Owned state and modifies the Shared state of the MESI protocol. The Owned (O) state expresses the fact that the cache holds one of the copies of a cache line (as with the Shared state) and has the exclusive right to modify it. All modifications to that cache line must be broadcast to all other caches that own it (in the Shared state): this allows for direct core-to-core communication without going through the main memory. An Owned cache line may change its state to Modified after invalidating all shared copies, and it may change its state to Shared after flushing the data to memory. The semantics of the Shared state in the MOESI protocol are modified: unlike with the MESI protocol, a Shared cache line may hold invalid data if an Owned cache line holds the correct, most recent version of the data. The Owned cache line is responsible for eventually flushing its data to the main memory. If no Owned cache line holds the data, the Shared cache line holds data that is ensured to be valid. Shared cache lines may change their state to Exclusive or Modified after invalidated all other shared copies.

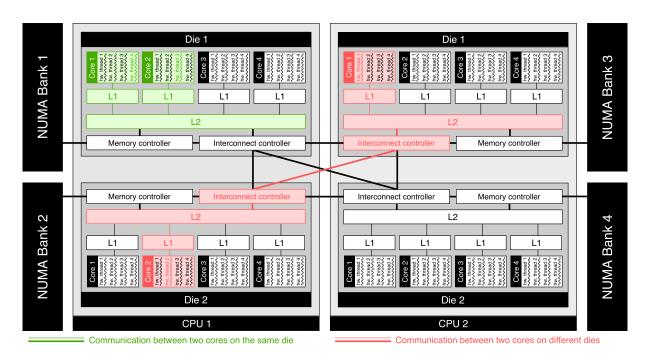

As shown in Figure 2.3, with the MOESI protocol, when two hardware threads from the same die communicate together, all they need to use is their local cache and the minimum subset of caches that they share. When hardware threads from different dies or CPUs communicate, the data must go through the interconnect, but no access to the main memory is needed.

#### 2.3.1.2.b Instructions used for synchronization

While, on cache-coherent architectures, reading and writing data to shared memory locations is sufficient for basic communication between hardware threads, specific instructions are sometimes needed for more complex synchronization schemes. First, because CPUs automatically reorder independent instructions, some specific instructions can be used to ensure system-wide ordering constraints between read and write operations of different hardware threads: these instructions are known as *memory barriers*. Second, it is sometimes useful to execute several operations in a way that appears atomic to other hardware threads. This can be done thanks to *atomic instructions*.

**Memory barriers.** Modern CPUs use *out-of-order* execution, i.e., they may reorder instructions to improve performance: instructions that can be instantly executed are sometimes executed before earlier instructions that would cause a stall waiting for their input data. While out-of-order execution is completely transparent in architectures that provide a single hardware thread, it can cause unpredictable behavior in architectures that provide several hardware threads: the reordering of instructions is designed to be transparent for the hardware thread that executes them, but other hardware threads see the side effects of these instructions in the real order

#### CHAPTER 2. MULTICORE ARCHITECTURES

Figure 2.3: Communication between hardware threads with the MOESI protocol

in which they are executed. Memory barriers, also known as memory fences, make it possible to enforce an ordering constraint on memory operations issued before and after the barrier instruction. Most modern architectures (including x86) do not ensure that stores may not be reordered after loads to different addresses. To prevent this, a *store fence* can be issued between the store and load instructions. Atomic instructions also act as memory barriers: all pending load and store operations must be executed before the atomic instruction.<sup>1</sup>

Atomic instructions. The instruction set of current CPUs often includes a set of atomic instructions. These instructions combine several operations whose execution appears to be *atomic* to hardware threads, i.e., no other instruction from any hardware thread can modify the shared data they operate on during their execution. Atomic instructions make it possible for programs to modify shared data without having to acquire locks. Common atomic instructions include: (i) *test-and-set*, which reads (and returns) the value  $v_1$  at a given address and replaces it with a new value  $v_2$  if  $v_1$  is non-zero<sup>2</sup>, (ii) *fetch-and-store*, which reads (and returns) the value  $v_1$  at a given memory address and replaces it with a new value  $v_2$ , (iii) *fetch-and-add*, which fetches a value  $v_1$  at a given address, adds a value  $v_2$  to  $v_1$  and stores the result at  $v_1$ 's address, (iv) *atomic swap*, or *atomic exchange*, which swaps the values at two given addresses in memory, and (v) *Compare-And-Swap (CAS)*, which compares the value  $v_1$  at a memory address to a value  $v_2$  and, in case of equality, writes a value  $v_3$  at  $v_1$ 's address. A whole class of algorithms, named *lock-free algorithms*, rely exclusively on atomic instructions instead of locks for synchronization [56, 77, 52, 40, 62, 63].

$<sup>^{1}</sup>$ On x86 architectures, atomic instructions only force the execution of pending memory instructions if the LOCK prefix is used. The LOCK prefix also ensures that during the execution of the atomic instruction, the hardware thread has exclusive ownership of the cache line on which a read-modify-write operation is performed.

<sup>&</sup>lt;sup>2</sup>Several definitions of test-and-set exist. According to some authors, test-and-set behaves exactly like the fetch-and-store instruction described in the same paragraph.

#### 2.3.1.2.c Bottlenecks

The cache-coherence protocol can often be a source of bottlenecks. It is important for developers to ensure good *cache locality* in multithreaded applications, i.e., to try to keep data in local caches as much as possible in order to avoid the overhead caused by cache misses. A common cache bottleneck is the presence of *false sharing*: two hardware threads may frequently access independent variables that are located in the same cache line, which results in the cache line needlessly "ping-ponging" between the caches, thereby causing unnecessary cache misses. Profilers such as DProf [87] are designed to locate cache locality bottlenecks. Sheriff [68] specifically detects false sharing and protects applications from it by adaptively isolating shared updates from different threads into separate physical addresses. Corey [13], an operating system for manycore architectures, proposes several techniques that aim to improve cache locality. In particular, it makes it possible for applications to dedicate cores for handling specific kernel functions or data. The research work presented in this thesis, RCL, tackles the specific issue of improving cache locality inside critical sections by executing them all on the same hardware thread.

#### 2.3.1.3 Non-cache-coherent architectures

As seen in the previous section, the cache-coherence protocol incurs an overhead, and this overhead may get worse as the number of cores increases. To prevent this, some manufacturers have designed *non-cache-coherent architectures*, in which each core owns part of the global memory, and hardware threads must use *message-passing* in order to request data from other cores. Non-cache-coherent CPUs include Intel's Single Chip Cloud Computer (SCC) and to some extent, Tilera's TILE-Gx CPUs. In both the SCC and the TILE-Gx CPUs, cores are organized in a grid. Writing code for non-cache-coherent architectures can be very complex since cores cannot simply read and write from known memory addresses to communicate, and must rely on custom message-based protocols instead. Moreover, operating systems and applications have to be rewritten for these architectures. Fortunately, non-cache-coherent multicore architectures have many common points with distributed systems, and research on distributed operating systems has been ongoing for decades [66, 91, 104]. This led to the design of some research operating systems for non-cache-coherent architectures such as Corey [13] and Barrelfish [9] that solely rely on message-passing. Similarly, some software components such as garbage collectors [114] have been written for non-cache-coherent architectures. However, it will take a lot of time for operating systems and other software components to become as feature-rich as currently-used legacy software that has been developed for decades on cache-coherent architectures. Moreover, it has been shown [14] that legacy operating systems such as Linux can be made to scale on current cache-coherent multicore architectures with dozens of cores.

#### 2.3.2 NUMA architectures

The main memory (RAM) can be organized in two ways on multicore architectures: UMA or NUMA. Uniform Memory Access (UMA) architectures use a very simple design: all CPUs address all of their memory requests to a single memory controller that is itself connected to the RAM. With this design, accessing any part of the RAM has the same cost (in latency and bandwidth) from any hardware thread. The main issue with UMA machines is that the unique memory controller can be a bottleneck on multicore architectures, especially as the number of hardware threads increases. Non-Uniform Memory Access (NUMA) architectures, on the other hand, use several memory controllers: cores are grouped into NUMA nodes, each of which is

#### CHAPTER 2. MULTICORE ARCHITECTURES

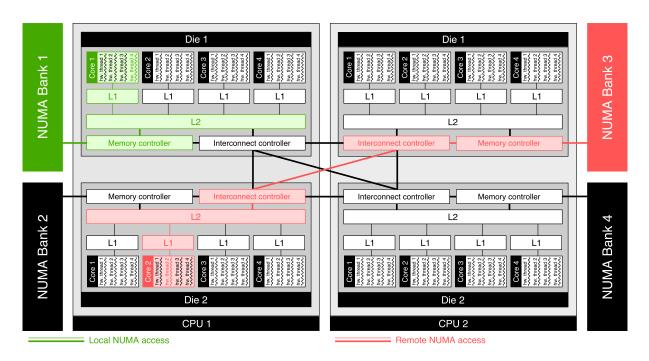

Figure 2.4: Local and remote NUMA accesses

connected to a *NUMA bank* that contains part of the main memory. The hardware handles mapping memory addresses to the right NUMA nodes: typically, the range of memory addresses is split into as many contiguous chunks as there are nodes, and addresses from chunk n are all mapped to the  $n^{\text{th}}$  NUMA bank. If a hardware thread needs to access a memory address that is located in a remote NUMA bank, then requests have to be sent on the interconnect to the node that owns that NUMA bank, possibly with several hops if there is no direct interconnect link between the two nodes. This indirection increases latency: local accesses are faster than remote accesses. Moreover, the interconnect links may decrease bandwidth if they are saturated, and if a lot of memory accesses from various nodes access the same NUMA bank, the memory controller of that NUMA bank can become a bottleneck, as is the case with UMA architectures.

In Figure 2.4, each die is a NUMA node that is connected to its local NUMA bank. An example of local NUMA access is shown in green: when a hardware thread reads data from memory, that data is copied into its L2 and L1 cache from which it can access it. When a hardware thread needs to access remote data, however, it must request it to the die whose NUMA bank holds the data. In the figure, any two dies have a direct interconnect link that connect them, therefore, one hop is sufficient. This is not always the case: requests sometimes have to be forwarded across several nodes in more complex multicore architectures, which comes at an increased latency cost.

Since remote accesses in NUMA architectures are costly, developers must be careful to write programs that avoid them: lack of NUMA locality can hinder the scalability of key software components such as garbage collectors [44]. Similarly to how developers can use profilers such as DProf [87] in order to detect remote cache or RAM accesses and improve cache locality, specific profilers such as MemProf [65] have been designed to help developers detect remote NUMA accesses and avoid them when possible. Some tools such as Carrefour [27] make it possible to automatically improve NUMA locality system-wide, by gathering statistics (such as those provided by hardware performance counters [18]), and deciding when to migrate, interleave or replicate memory pages.

**Hyper-Transport Assist.** In some NUMA architectures, when a hardware thread  $t_1$  in NUMA node  $n_1$  needs to access data from a cache line that is stored in the remote caches of a hardware thread  $t_2$  in NUMA node  $n_2$ , with the data being allocated in the RAM of node  $n_3$ ,  $t_1$  broadcasts a read or a write request to all caches because it does not know which cache owns the cache line. Since this scenario is fairly common, the resulting requests increase the load on caches and interconnect links, which may lead to non-negligible overhead. To prevent this, AMD Opteron CPUs use an optimization known as HyperTransport Assist [24] (a.k.a. HT Assist). With HT Assist, part of the highest level cache of die<sup>3</sup>  $d_3$ , whose memory controller handles node  $n_3$ , holds a *cache directory* (or *probe filter*) that contains information about the location of the cache lines that hold data from that node  $(n_3)$ . Thanks to the cache directory,  $t_1$  simply sends its request to  $d_3$  instead of broadcasting it. The cache directory of  $d_3$  indicates that the data is stored into  $t_2$ 's caches, therefore,  $d_3$  sends a message to  $t_2$ 's die, which replies with the requested cache line to  $d_3$ , and  $d_3$  forwards the cache line to  $t_1$ 's die. Therefore,  $d_3$  is used as a proxy and all communication is point-to-point, which is more efficient than broadcasting requests to all caches in the hope that one of them will respond with the cache line.

**Interleaved memory.** Current NUMA-capable systems usually make it possible to use *inter-leaved memory* instead of NUMA. With interleaved memory, memory addresses are allocated to each bank in turn. Consequently, contiguous reads and write access each bank in turn, which can improve memory throughput because less time is wasted waiting for memory banks to become ready for memory operations. Moreover, with interleaved memory, when hardware threads access a chunk of contiguous memory, the load is naturally balanced among memory controllers. NUMA usually offers better results than interleaved memory for applications that were designed with memory locality in mind, and should be more scalable in future architectures with many cores and memory banks.

#### 2.4 Hetereogeneous architectures

While most current multicore architectures provide a set of identical cores, architectures that provide cores with various characteristics (different processing speeds, cores specialized for specific tasks) have been proposed: IBM's Cell processor, for instance, features one general-purpose CPU core and eight coprocessors organized in a ring. Even on common consumer architectures where all cores provided by CPUs tend to be identical, small, specialized cores provided by the Graphics Processing Unit (GPU) can be used for computations.

Exploiting the performance of heterogeneous multicore architectures is even more challenging than with homogeneous multicore architectures due to their increased complexity. Some schedulers that try to predict which threads could be executed more efficiently on faster cores have been proposed [64]. Other works propose to dedicate faster cores to specific tasks such as executing critical sections [102]. Finally, whole new operating systems such as Helios [78] have been proposed, with the claim that current operating systems are not able to scale on future heterogeneous architectures with a large number of cores.

<sup>&</sup>lt;sup>3</sup>Or CPU, if the architecture uses one memory controller per CPU instead of per die.

#### 2.5 Machines used in the evaluation

This section describes the two machines used in the evaluation in Chapter 5. Section 2.5.1 describes Magnycours-48, a machine with 48 hardware threads that uses AMD Opteron processors. This machine is still available on the market, it is currently sold by Dell as a general-purpose server. Section 2.5.2 describes Niagara2-128, a machine that uses Sun UltraSPARC T2+ CPUs and offers more hardware threads (128) even though it is older: the UltraSPARC T2+, released in 2008, was replaced with the SPARC T3 in 2010. Finally, Section 2.5.3 discusses and compares the performance of the two machines using benchmarks.

#### 2.5.1 Magnycours-48

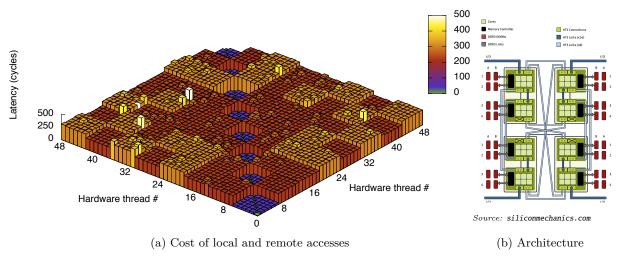

Magnycours-48 is an x86 machine with four AMD Opteron 6172 CPUs (the Opteron 6100 series is codenamed "Magny-cours", hence the name of the machine). The CPUs' clock speed is 2.100GHz. Each of the CPUs has twelve cores split across two dies: Magnycours-48 features 48 cores in total. Since Opterons do not use hardware multithreading, Magnycours-48 also provides 48 hardware threads. Each core has a local L1 and L2 cache, while the L3 cache is shared among all six cores on the die. Each core has two dedicated 2-way set associative 128KB L1 caches, one for instructions and one for data, for a total of 256KB of L1 cache memory. Each core also has a 16-way set associative 512KB cache that contains both instructions and data. The six cores on each die share a 96-way set associative 6MB L3 cache. All caches have a 64KB cache line size. Each die is a NUMA node, therefore, Magnycours-48 has eight NUMA banks. Each bank handles 32GB of 1.333GHz U/RDDR3 memory, for a total of 256GB quad-channel main memory. The interconnect links between the six dies do not form a complete graph: each die is only connected to the other die on the same CPU and to three remote dies. Therefore, the diameter of the interconnect graph is two: inter-core communications (fetching cache lines from remote caches, or NUMA accesses, for instance) require at most two hops. The structure of the interconnect graph can be seen in Figure 2.5b, along with the rest the architecture of Magnycours-48. The interconnect uses HyperTransport 3.0 links with a theoretical peak bandwidth of 25.6GB/s at 6.4GT/s (GigaTransfers per second).

Boyd-Wickizer et al. use a set of tools in their paper about Corey [13] to measure various metrics about their hardware. In particular, they provide an application named Memal that loads cache lines in the L1, L2 or L3 cache of a specific core  $c_1$ , and accesses them remotely with a remote core  $c_2$ , in order to measure the cost of cache misses. Many cache lines are accessed and the benchmark returns the average access time. Running Memal for every pair of cores on Magnycours-48 gives the results shown in Figure 2.5a when cache lines are initially loaded in the L1 cache. Local L1 accesses cost around 3 cycles (in green), and accessing data from a core on the same die costs around 38 cycles (in purple). There are two distinct costs for remote cache accesses, which is due to the non-complete interconnect graph described in the previous paragraph: accessing to data on a remote die that is directly connected to the local die (i.e., it is one hop away) costs around 220 cycles (in red), while accessing data from a die that is two hops away costs around 300 cycles (in yellow). The spikes in the graph are caused by the fact that these results are not averaged, therefore, any random interference during a run (context switches, for instance) can lead to erroneous longer access times. The reason why the results were not averaged is that given the large number of data points, running the experiment once already takes a long time. Running Memal for L2 and L3 caches does not alter remote access times, which shows that fetching a cache line from a remote CPU cache or from the NUMA bank of

Figure 2.5: Cache latencies and architecture of Magnycours-48

that CPU incurs the same cost. The local access times for L2 and L3 cache misses are around 15 and 30 cycles, respectively.

**Software environment.** Magnycours-48 runs Ubuntu 11.10 (Oneiric Ocelot) with a 3.9.7 Linux kernel, glibc 2.13, libnuma 2.0.5, and gcc 4.6.1.

#### 2.5.2 Niagara2-128

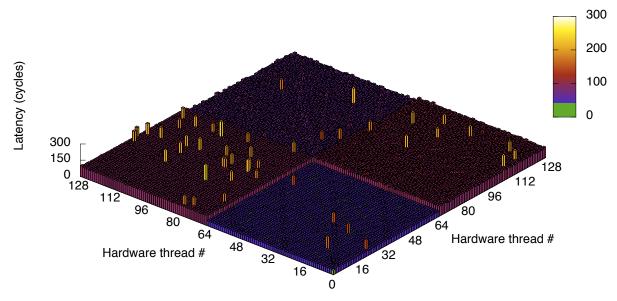

Niagara2-128 is a SPARC machine with two Sun UltraSPARC T2+ CPUs (codenamed Niagara 2). Each CPU has a clock frequency of 1.165GHz and comes with eight cores on a single die. Each core runs eight hardware threads thanks to simultaneous multithreading. Each core has a 16KB 8-way set associative instruction cache and a 8KB 4-way set associative data cache. L1 cache lines are 16 bytes wide. The L2 cache is shared among all cores in a CPU. It is a 4MB 16-way associative cache, with 64-byte cache lines. The 32GB dual-channel FB-DIMM main memory is interleaved (NUMA is disabled). The two CPUs are connected with an interconnect whose theoretical peak bandwidth is 63 GB/s (42 GB/s read and 21 GB/s write).

The results of running Memal on Niagara2-128<sup>4</sup> for all hardware thread pairs with data in the L1 cache are shown in Figure 2.6. Local L1 accesses cost around 42 cycles (in green), and local L2 accesses have similar latency (not shown in the figure). Interestingly, even though accessing data on a remote core on the same CPU through the L2 cache costs around 46 cycles (in purple) for the first CPU, it costs 60 cycles for the second CPU. We have not been able to find the source of this discrepancy. Accessing data that is located on a remote CPU costs about 90 cycles (in pink). Again, the yellow spikes on the graph are artifacts that would be removed by averaging the results over several runs.

Software environment. Niagara2-128 runs Solaris 10 (SunOS 5.10) with gcc 4.7.1.

#### 2.5.3 Performance comparison

This section discusses and compares the performance of Magnycours-48 and Niagara2-128. Section 2.5.3.1 compares the cache access latencies of the two machines. Section 2.5.3.2 uses a

<sup>&</sup>lt;sup>4</sup>Memal had to be ported to Solaris to run on Niagara2-128.

Figure 2.6: Cost of local and remote accesses on Niagara2-128

custom benchmark to measure the overhead of write-access contention on a shared cache line. Section 2.5.3.3 uses a benchmark suite to compare the sequential and the parallel performance of the two machines. Finally, Section 2.5.3.4 summarizes the results.

#### 2.5.3.1 Cache access latencies

Memal was used in Sections 2.5.1 and 2.5.2 to measure the cache access latencies of Magnycours-48 and Niagara2-128, respectively. These results are summarized in Figure 2.7a, with latencies converted from cycles (c) to nanoseconds (ns) in order to allow for easier comparison between the two machines. On Niagara2-128, hardware threads access data from the local core up to 25.8 times slower than on Magnycours-48, and they access data from a different core on the local die up to 2.9 times slower than on Magnycours-48. However, Niagara2-128 can almost be twice as fast as Magnycours-48 when it comes to accessing data that is located on a remote die thanks to its faster interconnect and the fact that its two CPUs are directly connected (at most one hop is needed).

In summary, Magnycours-48 is slower when it comes to uncontended inter-die communication, but Niagara2 has slower uncontended communication inside its dies. Since Magnycours-48 has eight dies with six hardware threads on each instead of only two dies with sixty-four hardware threads on each for Niagara2-128, Magnycours-48 uses more inter-die communication, which is its weak point, and Niagara2-128 uses more communication that is local to its dies, which is also its weak point. To conclude, it is difficult to determine which of the two machines has the best performance when it comes to cache access latencies.

#### 2.5.3.2 Contention overhead

A custom benchmark was written to assess the overhead of contention on regular and atomic instructions on Magnycours-48 and Niagara2-128. This benchmark runs a *monitored thread* that executes an instruction 1,000,000 times on a shared variable, and the execution time of every 1,000<sup>th</sup> instruction is measured: not all instructions are monitored in order to prevent the performance measurements from causing too much overhead. The measurements are then

|               | Local core access |                  |           |                          | Local die access |            |   | Remote die access |                       |              |        |                    |

|---------------|-------------------|------------------|-----------|--------------------------|------------------|------------|---|-------------------|-----------------------|--------------|--------|--------------------|

| Magnycours-48 | L1:<br>L2:<br>L3: | 3c<br>15c<br>30c | <br> <br> | 1.4ns<br>7.1ns<br>14.3ns |                  | 38c        | / | 18.1ns            | One hop:<br>Two hops: | 220c<br>300c | /<br>/ | 104.1ns<br>142.9ns |

| Niagara2-128  | L1 / L2:          | 42c              | /         | 36.1ns                   | CPU 1:<br>CPU 2: | 46c<br>60c | / | 39.5ns<br>52.5ns  |                       | 90c          | /      | 77.3ns             |

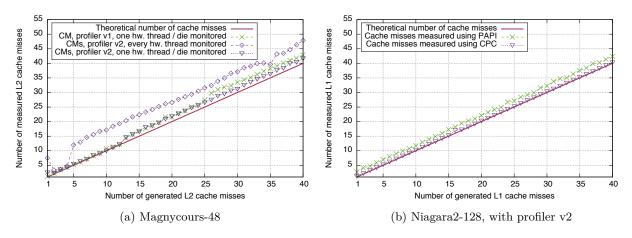

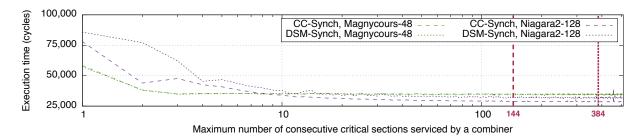

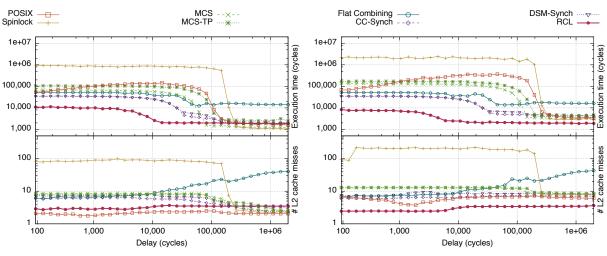

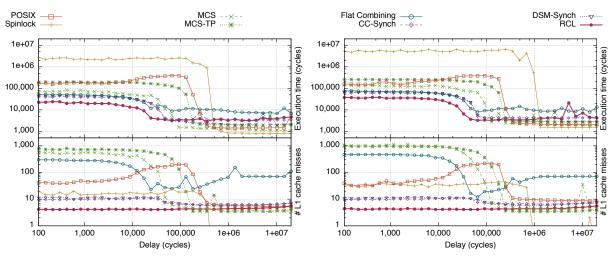

|                  | 1 thread | 2 threads    | 24 threads     | 48 threads         | 64 threads           | 128 threads        |                      |  |