#### GPU-ENHANCED POWER FLOW ANALYSIS

#### Manuel Marin

#### ▶ To cite this version:

Manuel Marin. GPU-ENHANCED POWER FLOW ANALYSIS. Distributed, Parallel, and Cluster Computing [cs.DC]. Université de Perpignan Via Domita, 2015. English. NNT: . tel-01299182

### HAL Id: tel-01299182 https://hal.science/tel-01299182

Submitted on 7 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESIS To obtain the degree of Doctor of Philosophy

#### From

#### UNIVERSITÉ DE PERPIGNAN VIA DOMITIA and UNIVERSITY COLLEGE DUBLIN

Prepared at

École Doctorale Énergie et Environnement and School of Electrical and Electronic Engineering In the research units DALI-LIRMM and ERC

Field: Computer Science and Electrical Engineering

Presented by Manuel Marin

# GPU-ENHANCED POWER FLOW ANALYSIS

Defended on December 11th, 2015, before the jury composed of

MCF HDR Dr David Defour Université de Perpignan Adviser Dr Federico Milano Associate Professor University College Dublin Adviser Dr Didier Elbaz CR HDR LAAS-CNRS Reviewer Dr Angelo Brambilla Politecnico Milano Reviewer Professor Dr Raphaēl Couturier Professor IUT Belfort-Montbéliard Examiner Senior Lecturer Dr Terence O'Donnell University College Dublin Examiner

#### Abstract

This thesis addresses the utilization of Graphics Processing Units (GPUs) to improve the Power Flow (PF) analysis of modern power systems. GPUs are powerful vector co-processors that have been very useful in the acceleration of several computational intensive applications. PF analysis is the steady-state analysis of AC power networks and is widely used for several tasks involved in system operation and planning. Currently, GPUs are challenged by applications exhibiting an irregular computational pattern, as is the case of most known methods to solve the PF analysis. At the same time, the PF analysis needs to be improved in order to cope with new requirements of efficiency and accuracy coming from the Smart Grid concept. The relevance of GPU-enhanced PF analysis is twofold. On one hand, it expands the application domain of GPUs to a new class of problems. On the other hand, it consistently increases the computational capacity available for power system operation and design. What specific features of GPUs can be used to enhance crucial aspects of PF analysis? What algorithms or models for PF analysis are best suited to the massively parallel architecture of GPUs? The present work attempts to answer such questions in two complementary ways: (i) by developing novel GPU programming strategies for available PF algorithms, and (ii) by proposing novel PF analysis methods that can exploit the numerous features present in GPU architectures. The proposed methods are implemented using state-of-the-art programming frameworks and paradigms, and tested over state-of-the-art GPU and CPU architectures. Results are discussed and compared with existing solutions from the literature of the field, leading to relevant conclusions and guidelines for future research. Specific contributions to GPU computing include: (i) a comparison of two programming paradigms, namely regularity and load-balancing, for implementing the so-called treefix operations; (ii) a study of the impact of the representation format over performance and accuracy, for fuzzy interval algebraic operations; and (iii) the utilization of architecture-specific design, as a novel strategy to improve performance scalability of scientific applications. Contributions to PF analysis include: (i) design and evaluation of a novel method for the uncertainty assessment, based on the fuzzy interval approach; and (ii) the development of an intrinsically parallel method to solve the PF analysis, which is not affected by the Amdahl's law.

#### Acknowledgments

I would like to express my most sincere gratitude to my advisers, David and Federico, for their continuous guidance and support. I learned a lot from them during these years, about research and life, and I am sure I will continue to do so in the future.

My thanks also go to my fellow labmates in DALI and ERC, for all the stimulating discussions and exchanges, lunches and dinners. I am very much looking forward to the next time we cross paths.

Last but not least, I would like to thank my family and friends, who were always there to give me their support and to ask me to explain my thesis, once again. For this and more I could never be grateful enough.

# Contents

| 1 Introduction |      |                                                    |  |

|----------------|------|----------------------------------------------------|--|

|                | 1.1  | Overview                                           |  |

|                | 1.2  | Context                                            |  |

|                |      | 1.2.1 Graphics Processing Units                    |  |

|                |      | 1.2.2 PF analysis                                  |  |

|                | 1.3  | Problem statement                                  |  |

|                | 1.4  | Methodology                                        |  |

|                | 1.5  | Summary of contributions                           |  |

|                | 1.6  | List of publications                               |  |

|                | Refe | rences                                             |  |

| 2              | Gra  | phics Processing Units 19                          |  |

|                | 2.1  | Introduction                                       |  |

|                | 2.2  | Hardware architecture                              |  |

|                |      | 2.2.1 Execution model                              |  |

|                |      | 2.2.2 Memory hierarchy                             |  |

|                |      | 2.2.3 Programming frameworks                       |  |

|                | 2.3  | Performance considerations                         |  |

|                |      | 2.3.1 Regularity                                   |  |

|                |      | 2.3.2 Latency hiding                               |  |

|                |      | 2.3.3 Throughput                                   |  |

|                | 2.4  | Conclusions                                        |  |

|                | Refe | erences                                            |  |

|                |      |                                                    |  |

| 3              |      | cuit and Power Flow analysis 32                    |  |

|                | 3.1  | Introduction                                       |  |

|                | 3.2  | Classic circuit analysis                           |  |

|                | 0.0  | 3.2.1 Alternating current circuits in steady-state |  |

|                | 3.3  | PF analysis                                        |  |

|                |      | 3.3.1 Conventional solution methods                |  |

|                |      | 3.3.2 Uncertainty assessment                       |  |

|                | 3.4  | Conclusions                                        |  |

|                | Refe | prences                                            |  |

| 4              | Tre  | efix operations on the GPU 53                      |  |

|                | 4.1  | Introduction                                       |  |

|                | 4.2  | Treefix operations                                 |  |

|                |      | 4.2.1 Vectorial approach                           |  |

|                |      | 4.2.2 Parallel approach                            |  |

|                | 43   | GPU implementation 60                              |  |

Contents 2

|   |      | 4.3.1   | Vectorial approach                       |

|---|------|---------|------------------------------------------|

|   |      | 4.3.2   | Parallel approach 61                     |

|   | 4.4  | Tests   | and results                              |

|   |      | 4.4.1   | Performance                              |

|   |      | 4.4.2   | Accuracy                                 |

|   |      | 4.4.3   | Case study                               |

|   | 4.5  | Concl   | usions                                   |

|   | Refe | erences |                                          |

| 5 | Fuz  | zy arit | chmetic on the GPU 75                    |

|   | 5.1  | Introd  | luction                                  |

|   | 5.2  | Mathe   | ematical background                      |

|   |      | 5.2.1   | Interval arithmetic                      |

|   |      | 5.2.2   | Fuzzy interval arithmetic                |

|   | 5.3  | Propo   | sed fuzzy arithmetic implementation      |

|   |      | 5.3.1   | Midpoint-radius format                   |

|   |      | 5.3.2   | Midpoint-increment format                |

|   |      | 5.3.3   | Error analysis                           |

|   | 5.4  | Imple   | mentation on the GPU                     |

|   |      | 5.4.1   | Tests and results                        |

|   | 5.5  | Propo   | sed method for fuzzy PF analysis         |

|   |      | 5.5.1   | Method description                       |

|   |      | 5.5.2   | Case study                               |

|   | 5.6  | Concl   | usions                                   |

|   | Refe | erences |                                          |

| 6 | Asy  | nchro   | nous Power Flow analysis 108             |

|   | 6.1  | Introd  | luction                                  |

|   | 6.2  | Fixed-  | -point iterations on a parallel computer |

|   |      | 6.2.1   | Synchronous iterations                   |

|   |      | 6.2.2   | Asynchronous iterations                  |

|   |      | 6.2.3   | Partially asynchronous iterations        |

|   | 6.3  | _       | sed method for AC circuit analysis       |

|   |      | 6.3.1   | Network model                            |

|   |      | 6.3.2   | Component and node models                |

|   |      | 6.3.3   | Convergence study                        |

|   | 6.4  | Exten   | sion of the method to PF analysis        |

|   |      | 6.4.1   | Network model                            |

|   |      | 6.4.2   | Component and node model                 |

|   | 6.5  | -       | mentation and evaluation                 |

|   |      | 6.5.1   | Implementation                           |

|   |      | 6.5.2   | Evaluation                               |

|   | 6.6  |         | usions                                   |

|   | Refe | erences | 127                                      |

Contents 3

| 7            | Conclusions |                                     |     |  |  |

|--------------|-------------|-------------------------------------|-----|--|--|

|              | 7.1         | Overview                            | 129 |  |  |

|              | 7.2         | Empirical findings                  | 131 |  |  |

|              |             | 7.2.1 Treefix operations on the GPU |     |  |  |

|              |             | 7.2.2 Fuzzy arithmetic on the GPU   |     |  |  |

|              |             | 7.2.3 Asynchronous PF analysis      |     |  |  |

|              | 7.3         | Theoretical implications            |     |  |  |

|              | 1.0         | 7.3.1 For GPU computing             |     |  |  |

|              |             | 7.3.2 For Power System Analysis     |     |  |  |

|              | 7.4         | Limitations of the study            |     |  |  |

|              | 7.5         | Recommendations for future research |     |  |  |

|              | 7.6         | Final remarks                       |     |  |  |

|              | 7.0         | r mai remarks                       | 101 |  |  |

| $\mathbf{A}$ | Mat         | chematical reminders 1              | .38 |  |  |

|              | A.1         | Definitions                         | 138 |  |  |

|              | A.2         | Theorems                            |     |  |  |

|              | Refe        | rences                              |     |  |  |

|              | 10010       |                                     |     |  |  |

| В            | Pro         | of of theorems and propositions 1   | 42  |  |  |

|              | Refe        | rences                              | 148 |  |  |

| Re           | efere       | nces 1                              | 49  |  |  |

# Nomenclature

```

Complex numbers

The imaginary unit.

\dot{j}

A phasor.

\mathbb{X}

x^*

The complex conjugate of x.

|x|

The magnitude of x.

The real part of x.

Re(x)

Im(x)

The imaginary part of x.

Linear algebra

\boldsymbol{x}

A vector.

\boldsymbol{A}

A matrix.

The Jacobian matrix of f.

J_f

The diagonal matrix that has x as diagonal.

Diag(\boldsymbol{x})

The norm of \boldsymbol{x}.

\| oldsymbol{x} \|

Floating-point arithmetic

The rounding attribute towards \infty.

\triangle

The rounding attribute towards -\infty.

\nabla

The rounding attribute towards the nearest.

The relative rounding error (i.e., the machine epsilon).

The smallest representable (denormalized) floating-point positive num-

\eta

Interval analysis

An interval.

[x]

[\tilde{x}]

A fuzzy interval.

\underline{x}

The lower bound of [x].

\overline{x}

The upper bound of [x].

\check{x}

The midpoint of [x]; alternatively, the kernel of [\tilde{x}].

The radius of [x].

\rho_x

\mu(x)

A membership function.

The ith \alpha-cut of [\tilde{x}].

[x_i]

The radius of [x_i].

\rho_{x,i}

\delta_{x,i}

The radius increment associated to [x_i].

Probability theory

X

A random variable.

Pr(A)

The probability of event A.

F_X

The distribution function of X.

f_X

The density function of X.

E(X)

The expected value of X.

f_X \otimes f_Y

The convolution product of f_X and f_Y.

```

Nomenclature 5

#### Asynchronous power flow method

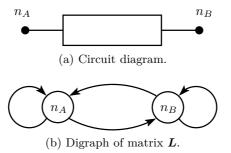

| $n_h$                   | The node $h$ .                                   |

|-------------------------|--------------------------------------------------|

| $c_{hm}$                | The component situated between $n_h$ and $n_m$ . |

| $\mathcal{N}$           | The set of circuit nodes.                        |

| $\mathcal C$            | The set of circuit components.                   |

| $\mathcal{I}_h$         | The set of influencers of $n_h$ .                |

| $\mathbb{V}_h$          | The voltage at $n_h$ .                           |

| $\mathbb{u}_{hm}$       | The voltage at $n_h$ according to $c_{hm}$ .     |

| $\dot{\mathbb{I}}_{hm}$ | The current flowing from $n_m$ to $n_h$ .        |

| $\Delta \mathtt{i}_h$   | The current mismatch at $n_h$ .                  |

| $z_{hm}$                | The impedance of $c_{hm}$ .                      |

| $\hat{\mathbb{V}}_{hm}$ | The voltage source of $c_{hm}$ .                 |

| $w_{hm}$                | The weight within $n_h$ of $c_{hm}$ .            |

| $\$_{hm}$               | The power flowing from $n_m$ to $n_h$ .          |

| $\Delta \mathbf{s}_h$   | The power mismatch at $n_h$ .                    |

| ${\mathbb S}_{L,h}$     | The power injected by loads to $n_h$ .           |

| 7                       |                                                  |

# Abbreviations

GPU Graphics Processing Unit.CPU Central Processing Unit.

HPC High Performance Computing.SIMT Single Instruction Multiple Thread.

TLP Thread-Level Parallelism.

ILP Instruction-Level Parallelism.

SM Streaming Multiprocessor.

API Application Program Interface.

**PF** Power Flow.

**NR** Newton-Raphson.

BFS Backward-Forward Sweep.AC Alternating Current.

**FDPF** Fast Decoupled Power Flow.

14

16

# Introduction

#### Contents 7 1.1 Overview 1.2 Context 8 8 1.2.2 10 11 1.4 12**13**

#### 1.1 Overview

1.6

In the last decade, Graphics Processing Units (GPUs) have gained popularity in accelerating calculations thanks to massive parallelism. Originally intended to optimize graphics rendering, they have quite naturally extended their domain of application to the most diverse fields [Pharr 2005, Nguyen 2007]. To date, several computing intensive applications have been ported to GPUs, dramatically changing the landscape of high performance computing (HPC) [Keckler 2011]. At the same time, Power Flow (PF) analysis has consolidated as a most relevant tool in power systems management and planning, as the shift towards the Smart-Grid concept takes place [Amin 2005]. By providing a snapshot of the network, PF analysis allows for several security-related tasks (e.g., the reliability assessment) to be efficiently performed [Milano 2010]. Several software packages are available that implement the different methods for PF analysis proposed in the literature [Simulator 2005, Milano 2013, Simulink 1993].

GPUs are challenged by several applications, e.g., applications that do not exhibit a regular computational pattern [Collange 2010]. This is precisely the case of most algorithms for PF analysis (e.g., the Newton-Raphson (NR) method and the Backward-Forward Sweep (BFS) [Milano 2010, Kersting 2012]). At the same time, PF analysis software need to be enhanced in order to satisfy new requirements of efficiency and accuracy [Momoh 2009, Fang 2012]. The interest of GPU-based PF analysis is twofold. On one hand, it expands the application domain of GPUs to a

1.2. Context

new class of problems, opening the possibility for similar tools to benefit from the same computing power. On the other hand, it consistently increases the computational capacity available for power system operation and design.

In the present work, the above problem is addressed in two ways. First, by taking existing algorithms for PF analysis and exploring the possibilities and issues of a GPU-based implementation. Second, by developing novel methods for PF analysis specifically designed to run on such architectures. The proposed methods are implemented using state-of-the-art programming frameworks and paradigms, and tested over recent GPU and CPU architectures. The results are discussed and compared with existing solutions from the literature of the field, leading to relevant conclusions and guidelines for future research.

The remainder of this chapter is organized as follows. Section 1.2 provides a preliminary discussion of GPUs and PF analysis. Section 1.3 exposes the main problem addressed in this thesis and its significance. The method of the investigation is stated in Section 1.4. Finally, Section 1.5 outlines the main contributions of the present research.

#### 1.2 Context

This section introduces the state-of-the-art of GPUs and PF analysis at the time of writing this thesis. The discussion is thoroughly expanded in Chapters 2 and 3.

#### 1.2.1 Graphics Processing Units

The development of GPUs started during the 1990s, largely motivated by the multimedia industry and the necessity of rendering graphics quickly at an affordable cost [Owens 2008, Nickolls 2010]. GPUs were originally conceived as powerful vector co-processors, capable of computing the information for thousands of pixels at a time. For this purpose, several (somewhat rudimentary) computing cores were disposed together in a configuration allowing for data-parallelism to be exploited. The Single Instruction Multiple Thread (SIMT) execution model was adopted, and a specific memory hierarchy was implemented in order to satisfy the particular needs of graphics developers. Two main manufacturers captured a large portion of the market: Nvidia and ATI. From then on, several generations of GPUs have been released, embedding more and more computing cores, as well as larger memory spaces and newer features. Various supercomputers and calculation clusters around the world adopted GPUs as part of their environment, and GPUs consolidated as a key element for high performance computing.

At the beginning, GPUs were devoted to graphics rendering. The architectural design was dictated by the specification of the programming language, e.g., DirectX and OpenGL. Programming for general applications was only possible through cleverly and carefully manipulating graphics primitives from those dedicated languages. The situation drastically changed when, by the middle of the

1.2. Context

past decade, general purpose GPU programming frameworks made their appearance. For the first time, developers were able to exploit the potential of GPUs on any application that would fit the GPU architectural model. Two of these frameworks have gained popularity: CUDA, developed by Nvidia, and OpenCL, by the Khronos Group [Cuda 2012, Stone 2010]. Thanks to these frameworks, the growth of GPU applications has been exponential. Many GPU applications nowadays achieve speed-ups of several orders of magnitudes over their serial CPU versions [Che 2008, Volkov 2008].

Before the raise of GPU technology, the performance of serial programs was automatically enhanced through increasing the frequency of CPU cores. No major effort was required from the developers: a program simply runs faster on a faster machine. However, by the end of the 1990's, the development of CPUs started hitting several walls. The first of them was the "power wall": since the power consumed by the processor grows exponentially with the frequency, it became increasingly difficult to cool high performance CPU cards. The second was the "memory wall": CPUs were evolving much faster than memories, and memory access latency prevented most applications to achieve peak CPU performance. The third was the "instruction-level parallelism (ILP) wall": the instruction pipeline, used by CPUs to enhance performance, was under-utilized by programs having insufficient independent instructions to execute in parallel [Asanovic 2006].

Interestingly, the stall of CPUs coincided with GPUs reaching their maturity in terms of architecture and programming. The computing power of GPUs was seen as an opportunity to keep increasing performance through the use of parallel programming. However, this time software developers were bound to play an important part, as programs designed for CPUs had to be re-written in order to run on GPUs. Developers faced a double challenge: (i) discovering the parallelism inherent in their application; and (ii) exposing that parallelism to the GPU in a special, novel programming language (such as CUDA and OpenCL).

The above did not prevent GPUs from disrupting into the world of HPC. A novel research field named General Purpose GPU programming (GPGPU) would emerge to accompany and confirm the success of GPUs [Du 2012]. GPGPU is concerned with the following question: how to write parallel code in order to extract the maximum benefit of various GPU architectural features? GPGPU has revealed several guidelines to answer such a question: guidelines to hide latency, to maximize utilization of floating-point units and to access memory more efficiently [Harris 2012]. Applications exhibiting a regular computation pattern and data structure proved to fit best the SIMT paradigm. Several examples of such successful experiences can be found in the recent literature on HPC. Currently, the challenge is to move from such "embarrassingly parallel" applications to a wider variety of tools, including, for instance, computations over graphs and sparse matrix operations.

1.2. Context 10

#### 1.2.2 PF analysis

PF analysis is the steady-state analysis of Alternating Current (AC) power systems. Given the specification of all electrical components in the network, the PF analysis determines the system operating point and is a tool for analysts and stakeholders to make better decisions and improve system security [Milano 2010].

PF analysis has been at the core of power system analysis since the 1950s. System operators have used it to anticipate and prevent the effects of critical contingencies, but also to optimize performance under a series of economical and political constraints. System planners have used it to compare expansion scenarios and select the ones that fit the best [Machowski 1997]. New applications continue to be added to the list, as the system evolves into newer and more complex configurations. Recently, the introduction of massive renewable energy generation, smart metering and load demand response is challenging system operators and planners, as part of the shift into the so-called Smart Grid concept [Momoh 2009]. The PF analysis appears to be a crucial tool in accompanying and consolidating this crucial process.

The standard PF formulation specifies loads in terms of real and reactive power consumptions; generators in terms of real power injections and rated voltages; and transmission lines in terms of susceptances and impedances. Since the power flowing through an impedance is a function of the product of voltage and current, solving the PF problem implies dealing with a highly-coupled, often ill-conditioned system of non-linear equations. In the past, a linearized model based on direct current (DC) was used to find an approximate solution. Nonetheless, this method can lead to an accuracy loss of up to 50% and is not considered in this work. On the other hand, Newton-based methods have proven to be fairly efficient and soon became the industry standard. Gauss-based methods have also been investigated, although their relevance is nowadays more academical than practical. In addition, the BFS method is largely used for the analysis of radial distribution networks.

For PF analysis to be applied to power system operation, certain standards of efficiency and accuracy need to be fulfilled. Due to computational constraints, the above did not happen until the late 1960s [Stott 1974]. At that point, key improvements in the digital processor allowed a variant of the Newton method, namely the Fast Decoupled Power Flow (FDPF), to be appropriately suited for industry. The FDPF is based on a fixed slope to move from one approximation to the next, instead of factorizing the system Jacobian matrix at each iteration. With time, numerous improvements in sparse matrix factorization made the full NR method increasingly efficient, and now several software packages implement it as the basic general purpose approach [Milano 2013].

To date, most attempts to improve performance of PF analysis have consisted in accelerating certain routines involved in the Newton method. Different libraries for sparse matrix factorization have been tried out, e.g. SuperLU, UMFPACK, KLU, among others [Li 2005, Davis 2004, Davis 2010]. Simultaneously, various forms of non-deterministic PF analysis have been proposed to provide accurate results in scenarios of high uncertainty [Alvarado 1992]. As power systems become more

heterogeneous, the sources of uncertainty increase, and the numerical quality of PF solutions needs to be reassessed. A possible approach consists in providing results in terms of intervals or distributions, which allows the analysis of several possible scenarios at once. Currently, the trend is to combine all these improvements (and others to come) into a comprehensive PF analysis tool, for the enhancement of modern and future power systems [Vaccaro 2013].

#### 1.3 Problem statement

The SIMT execution model adopted by GPUs allows the same instruction to be executed over different data by a large number of parallel threads. GPU programming is achieved through *kernel* functions, which contain the instructions to be executed by every thread within a multidimensional array. At the architectural level, threads are scheduled for execution by batches (of 32 or 64, depending on the manufacturer). All threads in the batch execute the same instruction, and memory accesses are served with full lines of cache to an entire batch. For an application to sufficiently exploit this model, all threads in a batch should follow the same execution path. Also, they should access data in the same line of cache. This means that applications exhibiting a regular computation pattern automatically achieve better performance.

The NR method for PF analysis computes successively better approximations of the zero of a non-linear function describing the system. The method moves from one point to the next one by following the tangent to the function at the current point, which is done by factorizing the system Jacobian matrix. To the date, most matrix factorization algorithms rely on some sort of reordering followed by block factorization and backward substitution. The process as a whole is characterized by strong data dependencies, making the application of the SIMT execution model extremely difficult. The underlying data structure, in turn, is highly irregular, as the power network is typically a sparse meshed graph. This makes GPU memory model difficult to exploit.

In synthesis, neither the SIMT execution model nor the GPU memory model can be properly exploited by the NR algorithm for PF analysis. However, GPUs exhibit many other features that can become a leverage for either performance or accuracy. Similarly, PF analysis can be performed by other methods, either available or newly developed. This thesis is confronted with the question of how to efficiently use GPUs to improve PF analysis in a general way. This means understanding GPU architecture in deep detail, such that novel programming guidelines can be proposed. It also means rediscovering PF analysis from the point of view of parallel computing. What specific features of GPUs can be used to enhance crucial aspects of PF analysis? What algorithms or models for PF analysis are best suited to massively parallel computing architectures? These questions have not been sufficiently explored.

The problem stated above spans two independent areas of knowledge. Accord-

ingly, its significance is twofold. On one hand, there is the enormous benefit of expanding the applicability of GPUs to new areas. PF analysis is exactly the kind of applications that the current trend in GPU computing is trying to assess. That is to say, applications with no evident data parallelism in their work-flow, exhibiting an irregular computation pattern, with a scattered data structure, and so on. Being able to adopt PF analysis as one of GPU applications certainly opens the door for others to follow.

On the other hand, enhancing PF analysis is crucial in the current worldwide scenario of power systems. The shift towards the Smart Grid means novel technologies being introduced to the network and new services to be provided. The ability to analyze large, complex and heterogeneous networks efficiently and accurately is key for the success of that process. The above is particularly true as PF analysis is at the core of many other relevant analysis over power systems. From this point of view, any improvement either in the time of response, the numerical quality of the results or the comprehensiveness of the solution, can have a big impact on the way the whole system is conceived and dealt with.

#### 1.4 Methodology

The very nature of the problem, i.e., how to efficiently use GPUs to enhance various aspects of PF analysis, allows it to be addressed in two complementary ways. The first consists in developing novel GPU programming strategies for available PF algorithms. The second is to propose novel PF analysis methods that can exploit the numerous features present in GPU architectures.

Each aspect of the methodology requires a deep understanding of both GPU computing and PF analysis. Accordingly, the first part of the thesis, comprising Chapters 2 and 3, is devoted to investigate the state-of-the-art in these two fields. The peculiarities of GPUs are discussed in Chapter 2. Several details of the execution model, memory hierarchy and programming frameworks are exposed. As features are described, several guidelines and strategies for GPU programming are discussed.

PF analysis is studied in Chapter 3, starting from the fundamentals of circuit theory and AC circuit analysis. After stating the PF problem, relevant solution methods are described. The above includes deterministic and non-deterministic methods, the latter oriented to deal with uncertainty. It also includes methods for fully meshed networks, i.e., with arbitrary topology, and methods for radial networks. As methods are described, relevant implementation issues are discussed.

The second part of the thesis, comprising Chapters 4, 5 ad 6, is focused on developing the field. Based on the understanding of the state-of-the-art, several research directions are proposed. These are obtained by combining one crucial aspect of each subject, i.e., GPU computing and PF analysis, which results in a particular viewpoint. The viewpoint originates a novel technique, or improves an existing technique in an original way. The proposed technique is first studied and

validated from a theoretical point of view. Then, the technique is implemented and tested using state-of-the-art programming methods and computing architectures. The results are discussed and compared with results obtained using other methods from existing literature. The assessment of the proposed methods is carried out considering real-world problems. Based on the above, guidelines for further research are finally proposed. In particular, Chapter 4 studies different ways of implementing the so-called treefix operations on GPUs, for the analysis of radial power networks. Chapter 5 proposes a novel GPU fuzzy interval arithmetic implementation, and its application to uncertainty modelling in PF analysis. Chapter 6 proposes a novel fixed-point method for PF analysis which is intrinsically parallel, and discusses its implementation using asynchronous iterations on the GPU.

#### 1.5 Summary of contributions

The present work intends to bring the following main contributions. To GPU programming:

- Comparison of programming paradigms. The analysis of different treefix approaches in Chapter 4 brings an answer to the problem of regularity versus load-balancing on GPUs for this kind of problem. Which approach is better for GPU programming? On one hand, regularity exploits better the SIMT execution model, but may introduce extra operations and data transfer. On the other hand, load-balancing keeps the number of operations to a minimum, but it may generate a computational pattern unsuited to SIMT.

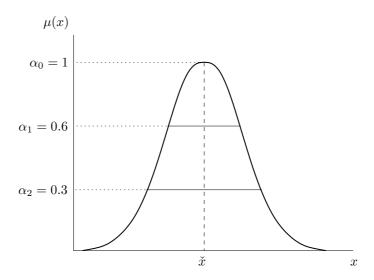

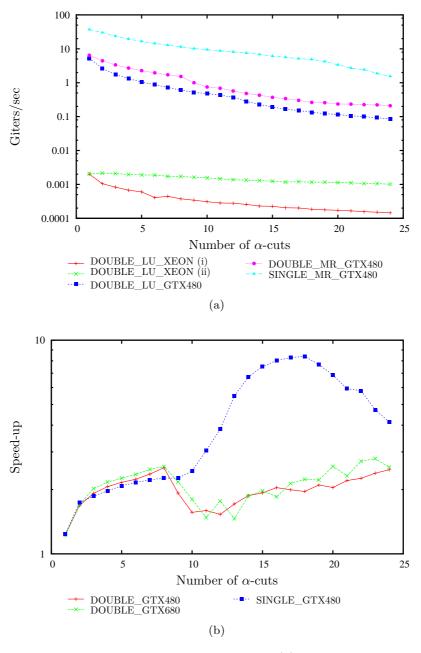

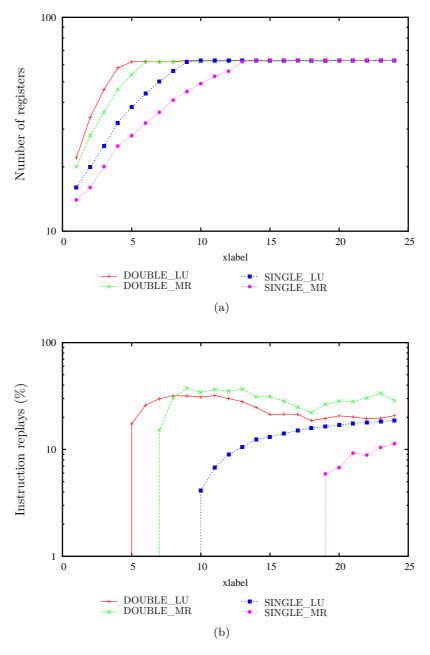

- Impact of the representation format. Chapter 5 provides a comparison of different interval representation formats for fuzzy algebra. Is it possible to improve performance or accuracy of fuzzy applications by using a specific representation format? Certain peculiarities of the membership function can be exploited by the midpoint-radius format, however, most available fuzzy algebra implementations overlook that fact, relying exclusively on lower-upper.

- Architecture-specific design. GPU computing is a relatively recent technology. Therefore, most existing GPU-based approaches for numerical analysis and simulation rely on parallelizing already available techniques. What about using our knowledge of the GPU to design new methods, specifically suited for the implementation on such massively parallel architectures? The asynchronous PF method proposed in Chapter 6 is one of the first attempts to achieve that goal.

#### To PF analysis:

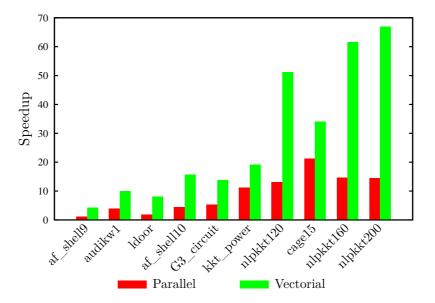

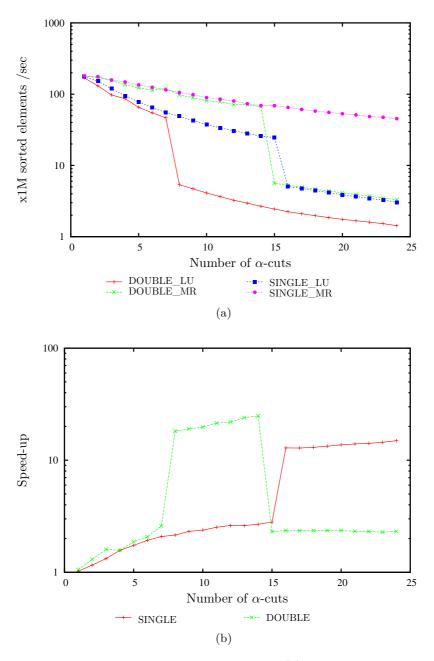

• Acceleration of radial network analysis. Chapter 4 proposes a novel vectorial implementation of the BFS algorithm, based on the study of treefix operations. How much faster can this solution be, compared to the traditional

approach based on sequential tree traversals? Experimental results show that a speedup of 2 to 9 can be achieved, depending on several implementation features

- Uncertainty assessment. Chapter 5 proposes a novel method for the uncertainty assessment in PF analysis. Current interval approaches are affected by the dependency problem, which causes a critical loss of accuracy in the final results. Is it possible to overcome that issue? In the proposed method, the above is achieved by using an optimization problem to compute the radius of the solution. The proposed method provides an accuracy similar to that of the Monte Carlo approach, with a much lower computational complexity.

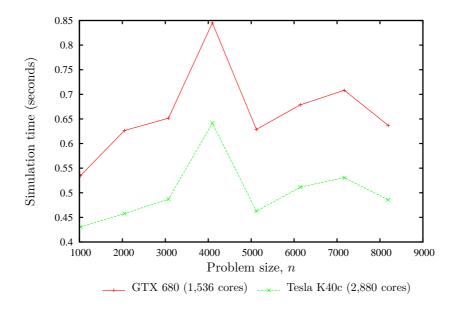

- Intrinsically parallel PF analysis. Chapter 6 proposes a novel fixed-point method for PF analysis, which is intrinsically parallel. How advantageous this approach can be, compared to parallelizing existing serial approaches? Two features of the proposed method are particularly interesting: (i) performance does not depend as much on the problem size, as it does in traditional PF approaches; and (ii) performance is able to scale with the number of computing cores, automatically benefiting from improvements in the computer architecture.

#### 1.6 List of publications

The present work has originated the following publications. In peer-reviewed international conferences:

- D. Defour and M. Marin. Regularity Versus Load-balancing on GPU for Treefix Computations. Procedia Computer Science, 2013 International Conference on Computational Science, vol. 18, pp. 309 318, 2013.

- D. Defour and M. Marin. FuzzyGPU: A Fuzzy Arithmetic Library for GPU. Parallel, Distributed and Network-Based Processing (PDP), 2014 22nd Euromicro International Conference on, pp. 624–631, 2014.

- M. Marin, D. Defour and F. Milano. Power flow analysis under uncertainty using symmetric fuzzy arithmetic. IEEE PES General Meeting, Conference & Exposition, pp. 1–5, 2014.

#### In national journals:

- D. Defour and M. Marin. Simulation temps réel de réseaux électriques à l'aide des architectures multicœurs. UPVD Magazine Hors-Série recherche, no. 3, pp. 42-44, 2014.

- D. Defour and M. Marin. Optimiser la représentation des flottants. HPC Magazine France, vol. 4, pp. 65-70, 2013.

Under review:

• M. Marin., D. Defour and F. Milano An efficient representation format for fuzzy intervals based on symmetric membership function. Submitted to ACM Transactions on Mathematical Software.

#### References

[Alvarado 1992] F. Alvarado, Y. Hu and R. Adapa. *Uncertainty in power system modeling and computation*. Systems, Man and Cybernetics, 1992., IEEE International Conference on, pp. 754–760. IEEE, 1992. (Cited on pages 10 and 48.)

- [Amin 2005] S. M. Amin and B. F. Wollenberg. *Toward a smart grid: power delivery for the 21st century*. Power and Energy Magazine, IEEE, vol. 3, no. 5, pp. 34–41, 2005. (Cited on page 7.)

- [Asanovic 2006] K. Asanovic, R. Bodik, B. C. Catanzaro, J. J. Gebis, P. Husbands, K. Keutzer, D. A. Patterson, W. L. Plishker, J. Shalf, S. W. Williams et al. The landscape of parallel computing research: A view from berkeley. Technical report, Technical Report UCB/EECS-2006-183, EECS Department, University of California, Berkeley, 2006. (Cited on page 9.)

- [Che 2008] S. Che, M. Boyer, J. Meng, D. Tarjan, J. W. Sheaffer and K. Skadron. A performance study of general-purpose applications on graphics processors using CUDA. Journal of parallel and distributed computing, vol. 68, no. 10, pp. 1370–1380, 2008. (Cited on pages 9 and 19.)

- [Collange 2010] S. Collange. Design challenges of GPGPU architectures: specialized arithmetic units and exploitation of regularity. PhD thesis, Université de Perpignan, 2010. (Cited on pages 7 and 26.)

- [Cuda 2012] C. Cuda. *Programming guide*. NVIDIA Corporation, July, 2012. (Cited on pages 9, 24, 25, 27, 88 and 92.)

- [Davis 2004] T. A. Davis. Algorithm 832: UMFPACK V4. 3—an unsymmetric-pattern multifrontal method. ACM Transactions on Mathematical Software, vol. 30, no. 2, pp. 196–199, 2004. (Cited on page 10.)

- [Davis 2010] T. A. Davis and E. Palamadai Natarajan. *Algorithm 907: KLU, A Direct Sparse Solver for Circuit Simulation Problems*. ACM Transacctions on Mathematical Software, vol. 37, no. 3, pp. 36:1–36:17, 2010. (Cited on pages 10 and 124.)

- [Du 2012] P. Du, R. Weber, P. Luszczek, S. Tomov, G. Peterson and J. Dongarra. From CUDA to OpenCL: Towards a performance-portable solution for multiplatform GPU programming. Parallel Computing, vol. 38, no. 8, pp. 391–407, 2012. (Cited on page 9.)

- [Fang 2012] X. Fang, S. Misra, G. Xue and D. Yang. Smart Grid The New and Improved Power Grid: A Survey. IEEE Communications Surveys Tutorials, vol. 14, no. 4, pp. 944–980, 2012. (Cited on page 7.)

[Harris 2012] M. Harris. *GPGPU. org.* General Purpose Computation on Graphics Hardware, 2012. (Cited on page 9.)

- [Keckler 2011] S. Keckler, W. Dally, B. Khailany, M. Garland and D. Glasco. *GPUs and the Future of Parallel Computing*. IEEE Micro, vol. 31, no. 5, pp. 7–17, 2011. (Cited on page 7.)

- [Kersting 2012] W. H. Kersting. Distribution system modeling and analysis. CRC Press, 2012. (Cited on pages 7 and 37.)

- [Li 2005] X. S. Li. An overview of SuperLU: Algorithms, implementation, and user interface. ACM Transactions on Mathematical Software, vol. 31, no. 3, pp. 302–325, 2005. (Cited on page 10.)

- [Machowski 1997] J. Machowski, J. Bialek and J. Bumby. Power system dynamics and stability. Wiley, 1997. (Cited on pages 10 and 36.)

- [Milano 2010] F. Milano. Power system modelling and scripting. Springer Science & Business Media, 2010. (Cited on pages 7, 10, 37, 120 and 124.)

- [Milano 2013] F. Milano. A Python-based software tool for power system analysis. IEEE Power and Energy Society General Meeting, pp. 1–5, 2013. (Cited on pages 7, 10, 68, 98, 122 and 124.)

- [Momoh 2009] J. Momoh et al. Smart grid design for efficient and flexible power networks operation and control. IEEE Power Systems Conference and Exposition, 2009, pp. 1–8, 2009. (Cited on pages 7 and 10.)

- [Nguyen 2007] H. Nguyen. Gpu gems 3. Addison-Wesley Professional, 2007. (Cited on page 7.)

- [Nickolls 2010] J. Nickolls and W. Dally. *The GPU Computing Era.* Micro, IEEE, vol. 30, no. 2, pp. 56–69, 2010. (Cited on page 8.)

- [Owens 2008] J. D. Owens, M. Houston, D. Luebke, S. Green, J. E. Stone and J. C. Phillips. *GPU computing*. Proceedings of the IEEE, vol. 96, no. 5, pp. 879–899, 2008. (Cited on pages 8 and 19.)

- [Pharr 2005] M. Pharr and R. Fernando. Gpu gems 2: programming techniques for high-performance graphics and general-purpose computation. Addison-Wesley Professional, 2005. (Cited on page 7.)

- [Simulator 2005] P. Simulator. *Version 10.0 SCOPF*. PVQV, PowerWorld Corporation, Champaign, IL, vol. 61820, 2005. (Cited on page 7.)

- [Simulink 1993] M. Simulink and M. Natick. *The Mathworks*, 1993. (Cited on page 7.)

[Stone 2010] J. E. Stone, D. Gohara and G. Shi. *OpenCL: A parallel programming standard for heterogeneous computing systems*. Computing in science & engineering, vol. 12, no. 1-3, pp. 66–73, 2010. (Cited on pages 9 and 24.)

- [Stott 1974] B. Stott. Review of load-flow calculation methods. Proceedings of the IEEE, vol. 62, no. 7, pp. 916–929, 1974. (Cited on pages 10 and 32.)

- [Vaccaro 2013] A. Vaccaro, C. A. Cañizares and K. Bhattacharya. A range arithmetic-based optimization model for Power Flow analysis under interval uncertainty. IEEE Transactions on Power Systems, vol. 28, no. 2, pp. 1179–1186, 2013. (Cited on pages 11, 46, 49, 95, 96 and 98.)

- [Volkov 2008] V. Volkov and J. W. Demmel. *Benchmarking GPUs to tune dense linear algebra*. IEEE International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 1–11, 2008. (Cited on pages 9 and 27.)

# **Graphics Processing Units**

| Contents |        |                         |

|----------|--------|-------------------------|

| 2.1      | Intr   | oduction                |

| 2.2      | Har    | dware architecture      |

|          | 2.2.1  | Execution model         |

|          | 2.2.2  | Memory hierarchy        |

|          | 2.2.3  | Programming frameworks  |

| 2.3      | Perf   | formance considerations |

|          | 2.3.1  | Regularity              |

|          | 2.3.2  | Latency hiding          |

|          | 2.3.3  | Throughput              |

| 2.4      | Con    | clusions                |

| Ref      | erence | es                      |

#### 2.1 Introduction

This chapter describes several features of Graphics Processing Units (GPUs), focusing on architectural aspects. It does not aim to be an exhaustive review but rather provide the basis for the discussion that will follow in Chapters 4, 5 and 6.

GPUs have gained popularity lately thanks to their high computational power, attractive cost, programmability and availability. Applications ported to GPUs can achieve a substantial speed-up over their single-core versions, and this performance gain is able to scale with the number of cores [Owens 2008, Che 2008]. Writing an application for the GPU, however, requires understanding the architectural model. Specifically, programmers need to expose the data parallelism of their applications by using some dedicated programming language. In addition, they may need to tune their implementations in order to achieve maximum efficiency [Ryoo 2008]. This chapter presents the most relevant features of GPU architecture, and discusses how these features can be exploited in order to achieve maximum performance.

The remainder of the chapter is organized as follows. Section 2.2 introduces the GPU, detailing the hardware architecture, execution model, memory hierarchy and main programming frameworks. In Section 2.3, three relevant factors for GPU performance are discussed: regularity, latency hiding and instruction throughput. These factors are presented along with several strategies to leverage performance of

GPU applications. Finally, Section 2.4 draws conclusions and outlines GPU issues discussed in following chapters.

#### 2.2 Hardware architecture

GPUs are powerful co-processors designed to exploit data parallelism. This section presents an overview of key aspects of GPU architecture, focusing particularly on Nvidia architectures.

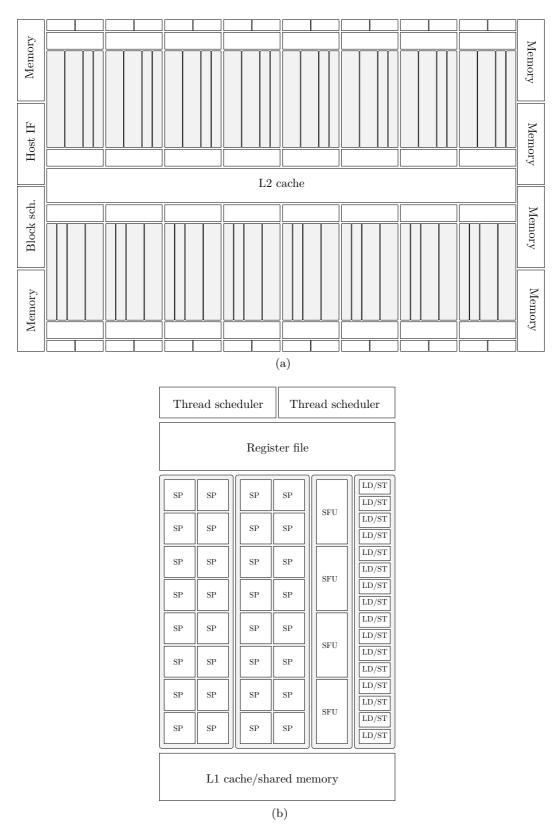

Modern GPU architectures embed hundreds to thousands of computing cores, along with several memories, caches, and dedicated units. These elements are organized into so-called Streaming Multiprocessors (SM). Figure 2.1 presents a schematic of the Nvidia Fermi GPU architecture [Glaskowsky 2009]. The entire board is shown in Fig. 2.1(a), and Fig. 2.1(b) shows an individual SM.

At high level, the host interface communicates the GPU with the 'host' processor, which launches the task (typically, a CPU). In this context, the GPU is called the 'device'. GPU global memory allows both processors to exchange data. The thread-block scheduler distributes blocks of threads to different SMs for their execution. Additionally, the L2 cache allows data caching for redundant global memory accesses made by SMs.

At SM level, the thread scheduler and dispatch units distribute threads to the different execution units. The latter include scalar processors (SP), special function units (SFU) and load/store units. SPs execute integer and floating-point arithmetic instructions, whereas SFUs accelerate in hardware the execution of transcendental instructions such as sine, cosine, square root and interpolation. Load/store units calculate source and destination addresses.

The SM register file provides registers for threads execution. The L1 cache allows additional data caching for global memory accesses made by different threads. Finally, shared memory allows different threads to explicitly share data.

#### 2.2.1 Execution model

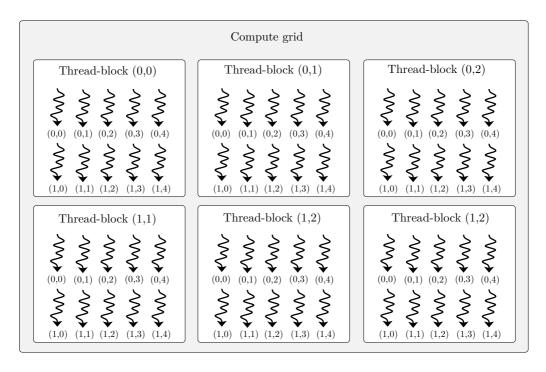

GPUs rely on a Single Instruction Multiple Thread (SIMT) execution model, where a *kernel* program is launched over a grid of thread-blocks. The above is illustrated in Fig. 2.2. Grid and blocks can be up to three-dimensional. Each block has a unique identifier within the grid, and each thread has a unique identifier within its block. These two can be used together to compute a unique global identifier for each thread.

The thread-block scheduler distributes blocks of threads to the different SMs. Each block is executed on a single SM, however, each SM can have multiple blocks running concurrently. The number of blocks that can run on a given SM depends on the resources of the SMs compared to the requirements of each block. Within the SM, threads are scheduled by batches of a fixed size to the different execution units. In Nvidia architectures, 32 threads are scheduled together and called a warp.

Figure 2.1: Nvidia Fermi architecture: (a) Graphics processing unit. (b) Streaming multiprocessor.

Figure 2.2: Grid of thread-blocks.

In the rest of the chapter, the term warp is used to refer to a batch of threads simultaneously executed.

For illustration purposes, consider the Nvidia Fermi architecture, where each SM has two thread schedulers and dispatch units and the execution units are organized in four sets: two sets of 16 SPs each, one set of 4 SFUs, and one set of 16 load/store units (see Fig 2.1(b)). At every instruction issue time, each scheduler selects a warp and issues one instruction from that warp to consume any two of the four sets of execution units listed above. For example, one instruction can consume both sets of 16 SPs, or one set of 16 SPs and the set of 4 SFUs, or any combination alike.

All the execution units are fully pipelined, which allows the GPU to exploit Instruction-Level Parallelism (ILP) within a single thread. This adds up to the data parallelism that is already exploited by the SIMT execution model.

In the presence of a branch, execution paths that are only taken by some of the threads in a warp are also executed by the others. Typically, all divergent paths are executed by the entire warp serially (unless all the threads happen to follow the exact same path). This generates unnecessary computation and should be avoided if possible. One solution is to sort the data so that divergent paths are taken preferable by different warps. Another is to use function templates and generate separate kernels for each execution path. For details on the latter, see [Harris 2007].

#### 2.2.2 Memory hierarchy

GPU memory is organized in three main areas: registers, shared memory and global memory. The first two can be found inside any individual SM, i.e., on-chip. The third is located outside the SM, i.e., off-chip. These areas are distinguished in Fig. 2.1. According to their distance to the execution units, these memories are accessed at different speeds: registers and shared memory have a low latency access (few cycles), whereas global memory has a relatively high latency access (hundreds of cycles). In general, registers have a higher bandwidth than shared memory, and shared memory has a higher bandwidth than global memory. For example, in the Fermi architecture, these are 8 TB/s for registers, 1.6 TB/s for shared memory, and 192 GB/s for global memory.

Registers. Registers are allocated to each thread as needed, with a maximum depending on the architecture (e.g., 63 registers per thread in modern Nvidia architectures). The number of registers per thread decreases as the number of threads in flight increases. When a thread needs more registers than the ones available, registers are spilled onto off-chip "local" memory. Such register spilling should be avoided if possible, e.g., by adjusting the number of blocks and number of threads per block.

Shared memory. Shared memory can be used by the programmer to explicitly share data among threads from the same block, thus enabling cooperation. It can be seen as a scratchpad, or programmable cache. Shared memory is organized in banks. These can be accessed simultaneously by all the threads within a warp, as long as each thread accesses a different bank. If two or more threads try accessing the same bank, then several memory transactions are serially issued. Such concurrent access, also known as bank conflict, must be prevented in order to achieve maximum performance. Sometimes programmers add padding to the data in shared memory in order to avoid these conflicts for a given memory access pattern.

Global memory. Global memory allows host and device processors to exchange data. Typically, input data is copied from host to device prior to the kernel execution, and results are copied from device to host afterwards. Global memory is accessed by segments of a fixed size (e.g., 32, 64, or 128 bytes). When threads in a warp access data in the same segment, all the accesses are *coalesced* into a unique memory transaction. Otherwise, several transactions are issued, degrading performance. A coalesced access can be achieved, for example, by having consecutive threads accessing consecutive cells in memory.

In addition to these main memory areas, modern GPUs may provide several types of cache, e.g., L1 cache, L2 cache, constant memory and texture memory. For details about these caches, see [Glaskowsky 2009].

#### 2.2.3 Programming frameworks

General purpose GPU programming is achieved by using a specific framework, with an Application Program Interface (API) defined for that framework. CUDA and OpenCL are the most commonly used.

These frameworks define a layer of abstraction, so that the same program can be compiled for different GPU architectures without changing the code. In this way, the parallelism in the application automatically scales with the number of computing resources in the architecture. The programmer is just responsible for exposing the parallelism by writing a kernel program. The kernel may involve tasks to be executed *independently* in parallel by blocks of threads, and smaller sub-tasks, to be executed *cooperatively* in parallel by threads within a block. The programmer specifies the number of blocks and number of threads per block. However, the specific way in which these blocks and threads are executed on the GPU is entirely up to the hardware, and the programmer does not have control over it.

The CUDA and OpenCL API extend standard programming languages such as C and C++. This allows for heterogeneous programming, where sections of host code are interleaved with sections of device code. Device code is written in kernel functions, which contain the instructions to be executed by a single thread. Typically, this involves retrieving of identifiers for that thread, data transfers between global and shared memory, several arithmetic operations, and synchronization instructions. Host code typically involves setting up of GPU devices, declaration of variables in host and device memory, data transfers between host and device, and kernel calls.

Despite the fact that both CUDA and OpenCL provide a very similar functionality, there are still relevant differences between them. Some of these differences and particular features are outlined below. For an extensive description of the CUDA and OpenCL frameworks, see [Cuda 2012, Stone 2010].

**CUDA.** Compute Unified Device Architecture (CUDA) is a parallel computing platform and API developed by Nvidia exclusively for their own manufactured GPUs. The API consists of a set of C language extensions and a runtime library.

CUDA programs are compiled with *nvcc*. Compilation is usually performed offline, by targeting a specific device or range of devices. The latter is specified by a *compute capability*, which indicates relevant features common to several GPU devices, usually attached to the generation (e.g., number of SMs, number of execution units, size of the register file, size of the L1 and L2 caches). Offline compilation is divided in three steps. First, device code is separated from host code and compiled into assembly and/or binary code by nvcc. The assembly code is tailored for a specific compute capability, whereas the binary code is already tailored for a specific device. Second, host code is modified by introducing function calls to the CUDA run-time library, needed to load and launch the kernels compiled in the precedent step. Third, the resulting host code is compiled into object code by the host compiler.

When an application loads assembly code to be executed on a specific device, the driver automatically checks if there is a previously compiled binary for that device. If not, it generates the binary at run-time, using nvcc, and caches a copy for future runs. This is called *just-in-time* compilation, and allows applications to immediately take advantage of driver upgrades. It is also a way for an application to run on devices that may not have been existed at the moment the application was originally compiled.

**OpenCL.** Open Computing Language (OpenCL) is an open standard for heterogeneous programming maintained by the Khronos group. Unlike CUDA, OpenCL is designed to run across heterogeneous *platforms* with devices from several manufacturers. This includes CPUs and GPUs, but also other processors such as Digital Signal Processors (DSPs) and Field-Programmable Gate Arrays (FPGAs). The Khronos group specifies the OpenCL API to be implemented by the chip manufacturers. The API is organized into a platform layer API and a run-time API. Compliant implementations are available from Apple, Intel, AMD and Nvidia, among others.

In OpenCL, device code is usually compiled at run-time. This is intended to ensure portability of applications among several compute platforms. As a consequence, it is up to the programmer to explicitly use the run-time API in host code in order to facilitate the compilation of device code (a process which is performed automatically in CUDA). Typically, this means calling a function to create a program object with source code from a text buffer, and another function to build that program into a binary. Then, kernel objects can be created from the program just built, and queued to launch onto a selected device.

The OpenCL run-time API also provides a function to create program objects directly from binary code, instead of using source code. This is particularly useful for applications that are designed to run several times on the same device and platform, as it can reduce the execution time. However, it is up to the programmer to purposely store a copy of the generated binary into disk, as binaries normally have the lifetime of an individual execution. Of course, this strategy is not optimal for portability [van der Sanden 2011].

#### 2.3 Performance considerations

In order to improve performance of GPU applications, programmers may follow several guidelines. These guidelines revolve around optimizing instruction and memory usage. In order to know which strategies will be more impactful for a particular kernel, the first step is to determine the bottleneck of that kernel. There are three major bottlenecks that a kernel can encounter: instruction throughput, memory throughput and latencies [Cuda 2012].

The bottlenecks can be determined by using the CUDA profiler, which is provided by Nvidia with every modern CUDA distribution. For each kernel, the profiler

calculates the ratio of arithmetic instructions to data transfers. Then, by comparing this figure with the ideal ratio of the device, one can determine whether the kernel is compute-bound, memory-bound or latency-bound. Another way is to modify the kernel by alternatively removing all arithmetic instructions and memory instructions, and compare the performance of the modified kernels with the original one.

The remainder of the section discusses three relevant factors for GPU performance: regularity, latency hiding and throughput. The discussion introduces several strategies for enhancing performance of GPU applications.

#### 2.3.1 Regularity

In parallel computing, regularity means similarity of behaviour between threads. Regularity usually determines how well an application fits into the SIMT execution model. Therefore, it becomes one of the main aspects to consider for GPU programming [Collarge 2010].

For certain computations, e.g., matrix-matrix multiplication, a parallel algorithm naturally exhibits a regular computation pattern. In some cases, the regular algorithm is also work-efficient, i.e., it performs the minimal amount of operations needed to compute the result. Whereas in other cases, additional operations have to be introduced in order to provide regularity. On the other hand, applications may use *load-balancing* whenever a regular computation pattern is hard to find. Load-balancing means equally distributing parallel tasks among available threads in execution time. This is the case, for example, of certain sparse matrix computations and graph computations where the work-flow is data-driven or even topology-driven [Nasre 2013].

Regularity can take several forms. The most basic is *instruction regularity*, where different threads execute the same instruction simultaneously. On GPUs, this is implied in the SIMT execution model and the concept of warp. Additionally, applications may also implement *control regularity* and *memory regularity*, explained below.

Control regularity means having different threads follow the same execution path. On GPUs, this implies minimizing divergence among threads in a warp caused by branching. As mentioned in Section 2.2.1, when threads in a warp take divergent paths, all these paths are executed serially by the entire warp. In such case, the instruction throughput is divided by the number of divergent paths. In CUDA, whenever a branch is likely to generate many divergent paths with a limited number of instructions each, nvcc is allowed to use branch predication. With branch predication, only instructions in the path taken by each thread are actually executed. Instructions from other paths are scheduled but not executed. This allows the SM to save resources, although it does not prevent serialization of paths.

Memory regularity means using a memory access pattern that minimizes the number of memory transactions. On GPUs, this comes down to avoid uncoalesced accesses to global memory, as well as bank conflicts in shared memory accesses.

As seen in Section 2.2.2, when threads in a warp read or write data in different segments of global memory, the accesses are split into several transactions. In this case, the throughput is divided by the ratio of the size of the transaction to the size of the accessed word. For example, if a 4-byte word is accessed through a 32-byte memory transaction, then the throughput is divided by 8. Accordingly, the more scattered are the addresses, the more the throughput is reduced. As also seen in Section 2.2.2, when threads in a warp access the same shared memory bank, again, several memory transactions are issued. In this case, the throughput is divided by the number of bank conflicts.

#### 2.3.2 Latency hiding

Instruction latency is the number of cycles that a warp takes in executing a given instruction. In other words, it is the period between the instruction issue time and the completion time. On SIMT architectures, latency can be hidden by interlacing execution of independent instructions. Latency hiding is one of the main sources of GPU performance, as it allows the different execution units to remain busy most of the time [Cuda 2012].

Instruction latency is typically caused by data dependence. Thus, it depends on the memory access latency. For example, assume that an instruction needs to read a variable which is written by the previous instruction (Read After Write dependence). If this variable resides in a register, then the latency is relatively low (tens of cycles, the time of accessing the register file). Whereas if the variable resides in off-chip global memory, then the latency is much higher (hundreds of cycles).

In order to hide latency, a SM interlaces the instructions from other warps. However, the SM needs to find enough independent instructions to execute during the latency period. To determine the number of instructions needed to saturate the SM, one has to multiply latency by throughput. For example, if an instruction has a latency of 20 cycles, and the SM can issue two instructions per cycle, then at least 40 warps are needed to completely hide that 20 cycles of latency.

The CUDA programming guide recommends maximizing the occupancy, i.e., the number of warps in the flight, in order to hide latency and maximize utilization. However, latency can also be hidden by means of instruction-level parallelism (ILP). Indeed, as mentioned in Section 2.2.1, GPUs are able to exploit ILP in addition to data-parallelism, thanks to the instruction pipeline available in every execution unit. Following this, Volkov has demonstrated that kernels can use ILP to achieve better performance at lower occupancy [Volkov 2008].

In addition, using ILP means doing more work per thread, and thus fewer threads are required. In this way, the block size can be reduced and the number of registers per thread can be increased. Reducing the block size allows more blocks to fit into each SM. Therefore, arithmetic instructions can be overlapped with global memory accesses more efficiently. In turn, increasing the number of registers per thread allows data to be transferred at a higher bandwidth. Therefore,

2.4. Conclusions 28

memory-bound kernels can perform faster. These ideas are developed in more detail in [Volkov 2010].

#### 2.3.3 Throughput

Throughput is the number of operations performed per cycle. Latency hiding, discussed in the previous section, is a way to increase throughput at SM level. However, throughput can also be increased at instruction level.

Arithmetic throughput can be increased by using a lower precision either for integer or floating-point computations. For example, consider a numerical algorithm that computes a series of approximations to a certain variable and stops when the error is below a certain threshold. Assume that the error is decreasing geometrically, i.e., every new approximation is at least one order of magnitude more accurate than the precedent. For the first few approximations, when the error is still very large, the computations can be performed using a low precision (e.g., single). Then, only when the error approaches the threshold, the algorithm can switch to a higher precision in order to deliver the final result (e.g., double). This kind of methods are known as mixed precision methods [Clark 2010].

CUDA provides a set of intrinsic functions for fast mathematical computation, including division, trigonometrical functions, logarithm and exponentiation, among others. These map to fewer native instructions than their standard counterparts, resulting in faster, although less accurate computation. They can be called explicitly in device code, at the points where the programmer is willing to trade accuracy for performance.

In addition, memory throughput can be increased by avoiding memory accesses with high latency. In particular, data transfers between host and device can be reduced by running more tasks on the device, even serial ones. For example, consider a loop in host code that launches a kernel and reads back the results in order to evaluate an end condition. This requires transferring data from device to host at every iteration, whereas if the condition is evaluated on device code, then all those memory transfers are avoided.

Finally, global memory accesses from within SMs can be reduced by using shared memory. For example, assume that the previous loop can be split into several loops working on non-overlapping subsets of the data. These loops can be assigned to independent thread-blocks and performed asynchronously on shared memory. In this way, the blocks transfer their results to global memory only when the end condition is reached, instead of doing it at every iteration.

#### 2.4 Conclusions

This chapter presents a review of GPUs and general purpose GPU programming. The hardware architecture is first described, detailing the SIMT execution model, the GPU memory hierarchy and the main frameworks for GPU computing. Next,

2.4. Conclusions 29

three relevant factors for GPU performance are analyzed: regularity, latency hiding and throughput.

Following chapters resume some of the issues presented above, applied to specific problems issued from Power Flow (PF) analysis. Chapter 4 addresses the problem of regularity versus load-balancing for the implementation of the so-called *treefix* operations. Which approach is better for GPU programming? On one hand, regularity exploits better the SIMT execution model, but may introduce extra operations and data transfer. On the other hand, load-balancing keeps the number of operations to a minimum, but it may generate a computational pattern unsuited to SIMT.

Chapter 5 provides a comparison of different interval representation formats for fuzzy algebra. Is it possible to improve performance or accuracy of fuzzy interval applications by using a specific representation format? Certain peculiarities of the membership function can be exploited by the midpoint-radius format, however, most available fuzzy algebra implementations overlook that fact, relying exclusively on lower-upper.

GPU computing is a relatively recent technology. Therefore, most existing GPU-based approaches for PF analysis and simulation rely on parallelizing already available techniques. What about using our knowledge of the GPU to design new methods, specifically suited for the implementation on such massively parallel architectures? The asynchronous PF method proposed in Chapter 6 is one of the first attempts to achieve that goal.

#### References

[Che 2008] S. Che, M. Boyer, J. Meng, D. Tarjan, J. W. Sheaffer and K. Skadron. A performance study of general-purpose applications on graphics processors using CUDA. Journal of parallel and distributed computing, vol. 68, no. 10, pp. 1370–1380, 2008. (Cited on pages 9 and 19.)

- [Clark 2010] M. A. Clark, R. Babich, K. Barros, R. C. Brower and C. Rebbi. Solving Lattice QCD systems of equations using mixed precision solvers on GPUs. Computer Physics Communications, vol. 181, no. 9, pp. 1517–1528, 2010. (Cited on page 28.)

- [Collange 2010] S. Collange. Design challenges of GPGPU architectures: specialized arithmetic units and exploitation of regularity. PhD thesis, Université de Perpignan, 2010. (Cited on pages 7 and 26.)

- [Cuda 2012] C. Cuda. *Programming guide*. NVIDIA Corporation, July, 2012. (Cited on pages 9, 24, 25, 27, 88 and 92.)

- [Glaskowsky 2009] P. N. Glaskowsky. NVIDIA's Fermi: the first complete GPU computing architecture. White paper, 2009. (Cited on pages 20, 23 and 61.)

- [Harris 2007] M. Harris et al. Optimizing parallel reduction in CUDA. NVIDIA Developer Technology, vol. 2, no. 4, 2007. (Cited on page 22.)

- [Nasre 2013] R. Nasre, M. Burtscher and K. Pingali. *Data-driven versus topology-driven irregular computations on gpus.* IEEE 27th International Symposium on Parallel & Distributed Processing (IPDPS), pp. 463–474, 2013. (Cited on page 26.)

- [Owens 2008] J. D. Owens, M. Houston, D. Luebke, S. Green, J. E. Stone and J. C. Phillips. *GPU computing*. Proceedings of the IEEE, vol. 96, no. 5, pp. 879–899, 2008. (Cited on pages 8 and 19.)

- [Ryoo 2008] S. Ryoo, C. I. Rodrigues, S. S. Stone, S. S. Baghsorkhi, S.-Z. Ueng, J. A. Stratton and W.-m. W. Hwu. Program optimization space pruning for a multithreaded gpu. Proceedings of the 6th annual IEEE/ACM international symposium on Code generation and optimization, pp. 195–204, 2008. (Cited on page 19.)

- [Stone 2010] J. E. Stone, D. Gohara and G. Shi. *OpenCL: A parallel programming standard for heterogeneous computing systems.* Computing in science & engineering, vol. 12, no. 1-3, pp. 66–73, 2010. (Cited on pages 9 and 24.)

- [van der Sanden 2011] J. van der Sanden. Evaluating the Performance and Portability of OpenCL. Master's thesis, Faculty of Electrical Engineering Eindhoven University of Technology, 2011. (Cited on page 25.)

[Volkov 2008] V. Volkov and J. W. Demmel. *Benchmarking GPUs to tune dense linear algebra*. IEEE International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 1–11, 2008. (Cited on pages 9 and 27.)

[Volkov 2010] V. Volkov. Better performance at lower occupancy. Proceedings of the GPU Technology Conference, vol. 10, 2010. (Cited on page 28.)

# Circuit and Power Flow analysis

#### Contents 3.1 Introduction 3233 Alternating current circuits in steady-state . . . . . . . . . . . . 33 36 37 3.3.2 44 49 50

# 3.1 Introduction

This chapter outlines different models and methods for Power Flow (PF) analysis. It does not aim to be an exhaustive survey but rather an introduction to the main aspects of PF analysis that will be addressed in Chapters 4, 5 and 6.

PF analysis can be seen as a special case of circuit analysis, where the component behaviour is defined in terms of power injections. Using a power injection model leads to a set of nonlinear equations. As a consequence, the solution is commonly approached by using numerical methods. The Newton-Raphson (NR) method is considered the standard [Stott 1974].

This chapter also considers uncertainty in PF analysis, which is caused by the complex and heterogeneous nature of the power systems. Uncertainty is typically modelled using probabilistic and interval analysis, and a number of solution methods have been proposed. The problem acquires special relevance in the context of the smart-grid functionality, with the changes experimented by power systems worldwide in recent years [Wan 1993].

The remainder of the chapter is organized as follows. Section 3.2 presents the fundamentals of circuit analysis, including Alternating Current circuits in steady-state. Section 3.3 focuses on PF analysis. Conventional solution methods are classified based on network topology. Relevant approaches to deal with uncertainty are also discussed in Section 3.3. Finally, Section 3.4 draws conclusions and outlines the developments presented in Chapters 4, 5 and 6.

# 3.2 Classic circuit analysis

PF analysis finds its roots in circuit analysis. This consists in determining node voltages and branch currents in an electrical circuit given the description of the circuit components (sources, resistors, etc.) [Nilsson 2009].

The circuit is typically assumed to be a *lumped parameter system*, where electrical effects happen simultaneously throughout all components. This assumption is valid if the signal wavelengths are much larger than the circuit itself, and in particular if voltage and current are time-invariant. In this situation Kirchhoff's laws can be applied [Nilsson 2009]. *Kirchhoff's current law* establishes that the (signed) sum of currents injected to any node in the circuit is equal to zero. *Kirchhoff's voltage law* establishes that the voltage drop across any closed loop in the circuit is equal to zero. It is important to note that these laws are only valid when

**Kirchhoff's current law.** Let  $i_1, i_2, \ldots, i_n$  be the current intensities on n branches merging into a node in an electrical circuit. Then,

$$\sum_{k=1}^{n} i_k = 0. (3.1)$$

**Kirchhoff's voltage law.** Let  $v_1, v_2, \ldots, v_n$  be the voltage drops across n branches that form a closed loop within an electrical circuit. Then,

$$\sum_{k=1}^{n} v_k = 0. (3.2)$$

Kirchhoff's current law leads to the so-called *node method*. One node in the circuit is selected as *ground*, or reference node. All other voltages are measured with respect to ground. Then, Kirchhoff's current law is applied on every nonground node in the circuit, and the resulting equation system is solved. Of course, the above needs to be completed with the particular equations that describe circuit components and relate voltage and current within the components themselves.

#### 3.2.1 Alternating current circuits in steady-state

Let's consider the following two assumptions that characterize Alternating Current (AC) circuits in steady-state operation:

- i) All sources are sinusoidal waveforms of the same frequency (AC assumption).

- ii) The sources have been active long enough for all transients to fade away (steady-state assumption).

If these assumptions hold and all components are linear, then all voltages and currents in the circuit are sinusoidal waveforms of the same frequency as the sources [Nilsson 2009]. Typically, they are represented as *phasors*. For example,

consider the sinusoidal waveform,  $v(t) = v \cos(\omega t + \theta)$ . This is written as the real part of a complex exponential, as follows.

$$v(t) = \operatorname{Re}\left(ve^{j(\omega t + \theta)}\right) = \operatorname{Re}\left(ve^{j\omega t}e^{j\theta}\right).$$

(3.3)

Since  $\omega$  is fixed, v(t) is simply noted as the phasor  $v = ve^{j\theta} = v(\cos\theta + j\sin\theta)$ , or, in angle notation,  $v = v \angle \theta$ .

Additionally, the concept of *impedance* is introduced to model the behaviour of electrical components under the AC regime.

**Definition 3.2.1** (Impedance). Let v be the phasor voltage across an electrical component, and i, the phasor current through it, in an AC steady state operation regime. Then, the complex ratio,

$$z = \frac{\mathbb{V}}{\mathbf{i}},\tag{3.4}$$

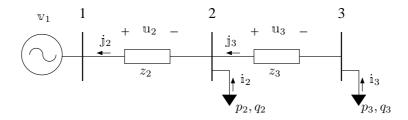

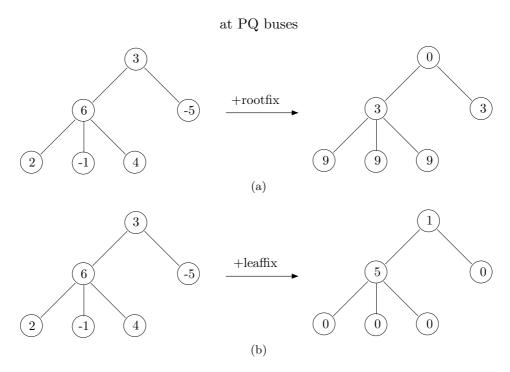

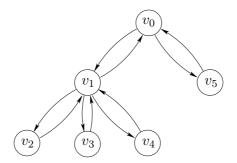

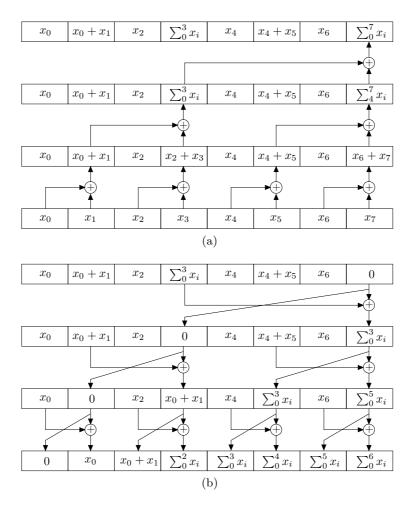

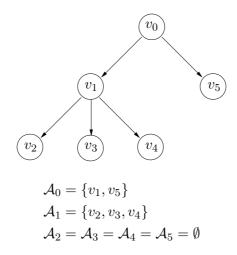

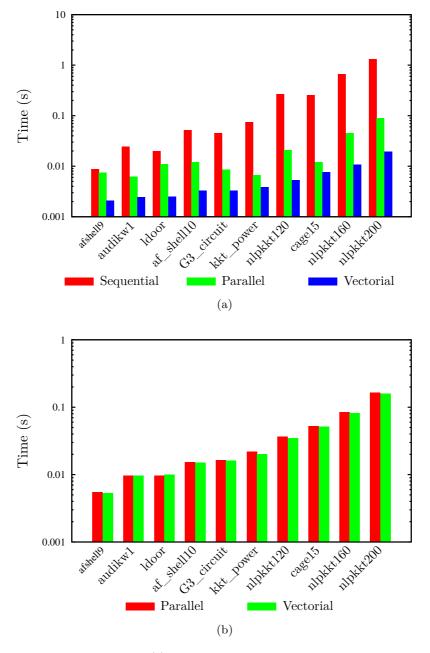

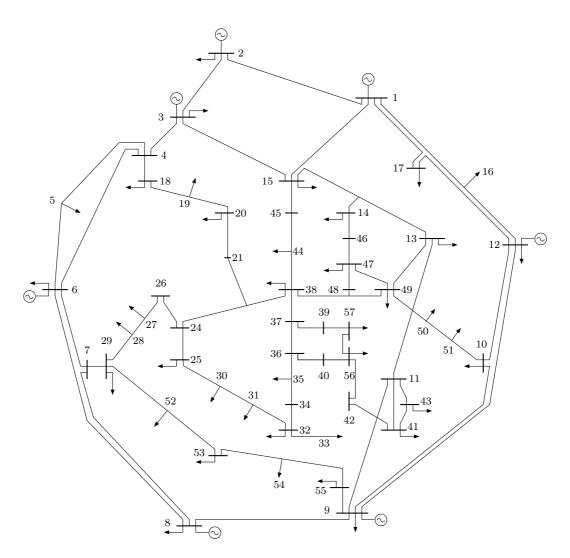

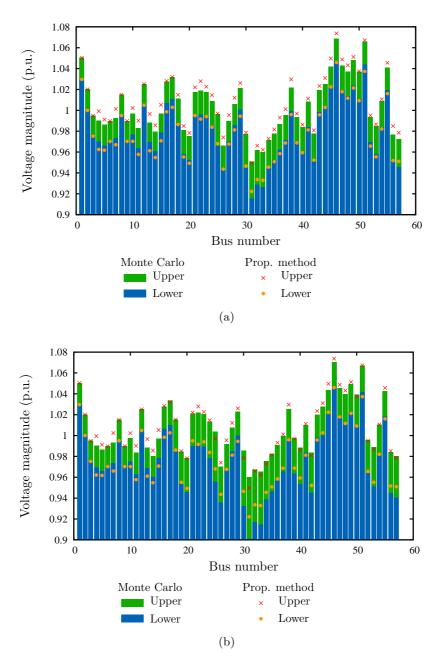

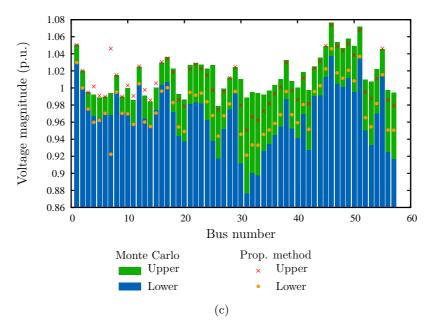

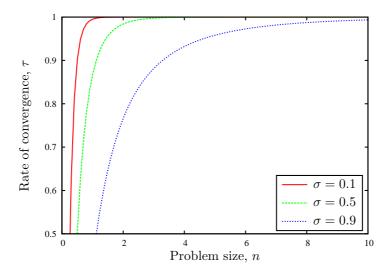

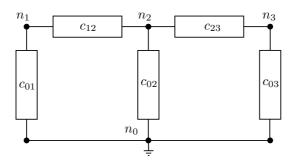

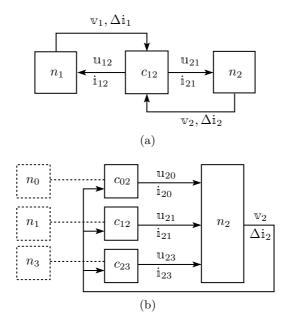

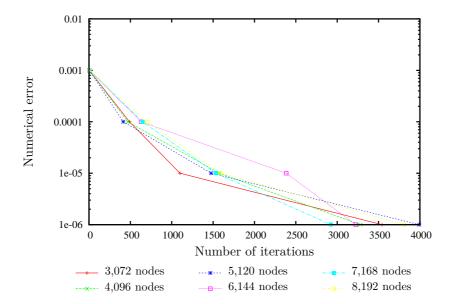

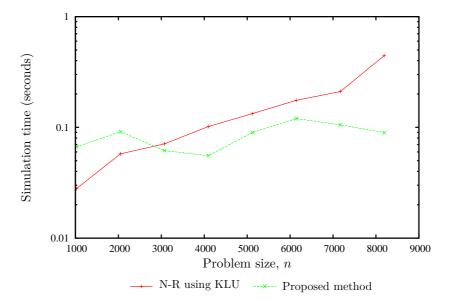

is the impedance of the component.