# High Performance Traffic Monitoring for Network Security and Management

Tristan Groleat

#### ▶ To cite this version:

Tristan Groleat. High Performance Traffic Monitoring for Network Security and Management. Human-Computer Interaction [cs.HC]. Télécom Bretagne; Université de Bretagne Occidentale, 2014. English. NNT: . tel-01217510

# $\begin{array}{c} {\rm HAL~Id:~tel\text{-}01217510} \\ {\rm https://hal.science/tel\text{-}01217510v1} \end{array}$

Submitted on 19 Oct 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**Nº d'ordre :** 2014telb0316

## Sous le sceau de l'Université européenne de Bretagne

# Télécom Bretagne

En accréditation conjointe avec l'école Doctorale Sicma

# High performance traffic monitoring for network security and management

#### Thèse de Doctorat

Mention: STIC

Présentée par **Tristan Groléat**

Départements : Informatique, électronique Laboratoires : IRISA REOP, LabSTICC CACS

Directrice de thèse : Sandrine Vaton

Encadrant : Matthieu Arzel

Soutenue le 18 mars 2014

#### Jury:

M. Guy Gogniat, Professeur, Université de Bretagne Sud (Président)

M. Philippe Owezarski, Chargé de Recherches, LAAS/CNRS (Rapporteur)

M. Dario Rossi, Professeur, Télécom ParisTech (Rapporteur)

Mme Sandrine Vaton, Professeur, Télécom Bretagne (Directrice de thèse)

M. Matthieu Arzel, Maître de Conférences, Télécom Bretagne (Encadrant)

Mme Isabelle Chrisment, Professeur, Télécom Nancy

M. Stefano Giordano, Professeur, University of Pisa

M. Ludovic Noirie, Chercheur Senior, Alcatel Lucent

# Remerciements

Je remercie d'abord Sandrine Vaton, ma directrice de thèse, qui a été très présente tout au long de ces trois ans et trois mois de thèse. Elle m'a conseillé, m'a fait profiter de son expertise sur les algorithmes de surveillance réseau, et m'a aidé à valoriser les résultats obtenus. Je remercie aussi Matthieu Arzel qui m'a encadré, et m'a fait profiter de son expertise en électronique numérique. Je remercie Sandrine et Matthieu pour le temps qu'ils ont passé à relire et commenter chacun de mes articles, chacune de mes présentations, ainsi que ce manuscrit. Mais je les remercie surtout pour m'avoir permis de découvrir la possibilité de lier la surveillance de trafic et l'électronique, en proposant un projet de détection d'attaques alors que j'étais encore élève ingénieur à Télécom Bretagne. Ils m'ont ensuite soutenu quand j'ai souhaité prolonger ce travail par une thèse, en m'aidant à transformer une simple idée en véritable sujet de thèse, et en trouvant des financements grâce à PRACOM et au projet européen DEMONS.

En parallèle de la recherche, Télécom Bretagne m'a aussi donné la possibilité de participer aux enseignements, ce qui fut très enrichissant. Je remercie Sylvie Kerouédan, qui a supervisé ma mission d'enseignement. Elle a aussi créé durant ma thèse le Téléfab, le FabLab de Télécom Bretagne, lieu permettant à tous d'échanger et de créer des objets de tous types simplement à partir d'une idée, ce qui m'a permis de faire de nombreuses rencontres et découvertes, en tant qu'étudiant et en tant qu'encadrant.

Merci à Olivier Emery, Hicham Bougdal, Sébastien Martinez, Alban Bourge, Yannick Le Balch et Manuel Aranaz Padron pour avoir fait avancer mon sujet de thèse durant un stage ou projet.

Je remercie aussi toutes les personnes à Télécom Bretagne qui ont facilité mon travail de thèse, et particulièrement Patrick Adde qui a fait le lien avec PRACOM, et Armelle Lannuzel et Catherine Blondé, qui ont du gérer mon inscription dans deux départements à la fois. Merci à Bernard L'hostis qui a du souvent me trouver des PCs, de la RAM ou des écrans.

Je remercie toutes les personnes au département électronique qui ont rendu le travail quotidien très agréable, et en particulier Benoît Larras, Pierre-Henri Horrein, Kévin Burgi, Gérald Le Mestre, Jean-Noël Bazin, Valentin Mena Morales, Charbel Abdel Nour et Michel Jezequel.

Je remercie enfin ma famille et mes proches qui m'ont toujours soutenu, même à distance.

# Contents

| A Abstract   |      |                                                          |  |  |  |  |  |  |  |  |

|--------------|------|----------------------------------------------------------|--|--|--|--|--|--|--|--|

| $\mathbf{B}$ | Rés  | umé                                                      |  |  |  |  |  |  |  |  |

|              | B.1  | Introduction                                             |  |  |  |  |  |  |  |  |

|              | B.2  | Choisir une plateforme de développement                  |  |  |  |  |  |  |  |  |

|              | B.3  | Surveillance logicielle pour la sécurité                 |  |  |  |  |  |  |  |  |

|              | B.4  | Surveillance matérielle pour la classification de trafic |  |  |  |  |  |  |  |  |

|              | B.5  | Plateforme de test avec accélération matérielle          |  |  |  |  |  |  |  |  |

|              | B.6  | Conclusion                                               |  |  |  |  |  |  |  |  |

| 1            | Intr | Introduction                                             |  |  |  |  |  |  |  |  |

| _            | 1.1  | Context                                                  |  |  |  |  |  |  |  |  |

|              | 1.2  | Objectives                                               |  |  |  |  |  |  |  |  |

|              | 1.3  | Traffic monitoring                                       |  |  |  |  |  |  |  |  |

|              |      | 1.3.1 Topology                                           |  |  |  |  |  |  |  |  |

|              |      | 1.3.2 Time constraints                                   |  |  |  |  |  |  |  |  |

|              |      | 1.3.3 Traffic features                                   |  |  |  |  |  |  |  |  |

|              |      | 1.3.4 Detection technique                                |  |  |  |  |  |  |  |  |

|              |      | 1.3.5 Calibration                                        |  |  |  |  |  |  |  |  |

|              | 1.4  | Acceleration challenges                                  |  |  |  |  |  |  |  |  |

|              |      | 1.4.1 Large data storage                                 |  |  |  |  |  |  |  |  |

|              |      | 1.4.2 Test conditions                                    |  |  |  |  |  |  |  |  |

|              | 1.5  | Thesis structure                                         |  |  |  |  |  |  |  |  |

|              |      |                                                          |  |  |  |  |  |  |  |  |

| 2            | Cho  | Choosing a development platform                          |  |  |  |  |  |  |  |  |

|              | 2.1  | Criteria                                                 |  |  |  |  |  |  |  |  |

|              |      | 2.1.1 Supported data rate                                |  |  |  |  |  |  |  |  |

|              |      | 2.1.2 Computation power                                  |  |  |  |  |  |  |  |  |

|              |      | 2.1.3 Flexibility                                        |  |  |  |  |  |  |  |  |

|              |      | 2.1.4 Reliability                                        |  |  |  |  |  |  |  |  |

|              |      | 2.1.5 Security                                           |  |  |  |  |  |  |  |  |

|              |      | 2.1.6 Platform openness                                  |  |  |  |  |  |  |  |  |

|              |      | 2.1.7 Development time                                   |  |  |  |  |  |  |  |  |

|              |      | 2.1.8 Update simplicity                                  |  |  |  |  |  |  |  |  |

|              |      | 2.1.9 Future scalability                                 |  |  |  |  |  |  |  |  |

|              |      | 2.1.10 Hardware cost                                     |  |  |  |  |  |  |  |  |

|              | 2.2  | Commodity hardware                                       |  |  |  |  |  |  |  |  |

|   |                                                         | 2.2.1  | Handling traffic                               |  |  |  |  |  |  |  |

|---|---------------------------------------------------------|--------|------------------------------------------------|--|--|--|--|--|--|--|

|   |                                                         | 2.2.2  | CPU computation                                |  |  |  |  |  |  |  |

|   |                                                         | 2.2.3  | GPU computation                                |  |  |  |  |  |  |  |

|   | 2.3                                                     | Netwo  | ork processors                                 |  |  |  |  |  |  |  |

|   |                                                         | 2.3.1  | Principles                                     |  |  |  |  |  |  |  |

|   |                                                         | 2.3.2  | Development platforms                          |  |  |  |  |  |  |  |

|   |                                                         | 2.3.3  | Use cases                                      |  |  |  |  |  |  |  |

|   | 2.4                                                     | FPGA   | <b>AS</b>                                      |  |  |  |  |  |  |  |

|   |                                                         | 2.4.1  | Composition of an FPGA                         |  |  |  |  |  |  |  |

|   |                                                         | 2.4.2  | Boards for traffic monitoring                  |  |  |  |  |  |  |  |

|   |                                                         | 2.4.3  | Development principles                         |  |  |  |  |  |  |  |

|   | 2.5                                                     | Conclu | usion                                          |  |  |  |  |  |  |  |

| 3 | Software monitoring applied to security                 |        |                                                |  |  |  |  |  |  |  |

|   | 3.1                                                     |        | of the art on DDoS detection implementation 53 |  |  |  |  |  |  |  |

|   |                                                         | 3.1.1  | Monitoring platforms                           |  |  |  |  |  |  |  |

|   |                                                         | 3.1.2  | DDoS attacks                                   |  |  |  |  |  |  |  |

|   |                                                         | 3.1.3  | DDoS detection algorithms                      |  |  |  |  |  |  |  |

|   | 3.2                                                     | Flexib | de anomaly detection                           |  |  |  |  |  |  |  |

|   |                                                         | 3.2.1  | Problem statement                              |  |  |  |  |  |  |  |

|   |                                                         | 3.2.2  | Algorithm for DDoS detection                   |  |  |  |  |  |  |  |

|   | 3.3                                                     | A flex | ible framework: BlockMon                       |  |  |  |  |  |  |  |

|   |                                                         | 3.3.1  | Principles                                     |  |  |  |  |  |  |  |

|   |                                                         | 3.3.2  | Performance mechanisms                         |  |  |  |  |  |  |  |

|   |                                                         | 3.3.3  | Base blocks and compositions                   |  |  |  |  |  |  |  |

|   | 3.4                                                     | Imple  | menting DDoS detection in BlockMon             |  |  |  |  |  |  |  |

|   |                                                         | 3.4.1  | Algorithm libraries                            |  |  |  |  |  |  |  |

|   |                                                         | 3.4.2  | Single-node detector implementation            |  |  |  |  |  |  |  |

|   |                                                         | 3.4.3  | Alternative compositions                       |  |  |  |  |  |  |  |

|   | 3.5                                                     | Result | 58                                             |  |  |  |  |  |  |  |

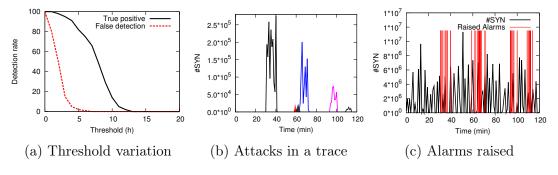

|   |                                                         | 3.5.1  | Accuracy                                       |  |  |  |  |  |  |  |

|   |                                                         | 3.5.2  | Performance                                    |  |  |  |  |  |  |  |

|   |                                                         | 3.5.3  | Going further                                  |  |  |  |  |  |  |  |

|   | 3.6                                                     | Conclu | usion                                          |  |  |  |  |  |  |  |

| 4 | Hardware monitoring applied to traffic classification 8 |        |                                                |  |  |  |  |  |  |  |

|   | 4.1                                                     | State  | of the art on traffic classification           |  |  |  |  |  |  |  |

|   |                                                         | 4.1.1  | Port-based classification                      |  |  |  |  |  |  |  |

|   |                                                         | 4.1.2  | Deep Packet Inspection (DPI)                   |  |  |  |  |  |  |  |

|   |                                                         | 4.1.3  | Statistical classification                     |  |  |  |  |  |  |  |

|   |                                                         | 4.1.4  | Behavioral classification                      |  |  |  |  |  |  |  |

|   | 4.2                                                     | Using  | SVM for traffic classification                 |  |  |  |  |  |  |  |

|   |                                                         | 4.2.1  | Proposed solution                              |  |  |  |  |  |  |  |

|   |                                                         | 4.2.2  | Background on Support Vector Machine (SVM) 93  |  |  |  |  |  |  |  |

|   |                                                         | 4.2.3  | Accuracy of the SVM algorithm                  |  |  |  |  |  |  |  |

|   | 4.3                                                     | SVM    | classification implementation                  |  |  |  |  |  |  |  |

|   |                                                         |        | Requirements 96                                |  |  |  |  |  |  |  |

|          |                                        | 4.3.2      | The SVM classification algorithm                      | 99  |  |  |  |  |  |  |  |

|----------|----------------------------------------|------------|-------------------------------------------------------|-----|--|--|--|--|--|--|--|

|          |                                        | 4.3.3      | Parallelism                                           | 99  |  |  |  |  |  |  |  |

|          | 4.4                                    | Adapt      | cation to hardware                                    | 100 |  |  |  |  |  |  |  |

|          |                                        | 4.4.1      | Architecture                                          | 100 |  |  |  |  |  |  |  |

|          |                                        | 4.4.2      | Flow reconstruction                                   | 102 |  |  |  |  |  |  |  |

|          |                                        | 4.4.3      | The RBF kernel                                        | 108 |  |  |  |  |  |  |  |

|          |                                        | 4.4.4      | The CORDIC algorithm                                  | 111 |  |  |  |  |  |  |  |

|          |                                        | 4.4.5      | Comparing the two kernels                             | 115 |  |  |  |  |  |  |  |

|          | 4.5                                    | Perfor     | mance of the hardware-accelerated traffic classifier  | 116 |  |  |  |  |  |  |  |

|          |                                        | 4.5.1      | Synthesis results                                     | 116 |  |  |  |  |  |  |  |

|          |                                        | 4.5.2      | Implementation validation                             | 120 |  |  |  |  |  |  |  |

|          | 4.6                                    | Concl      | usion                                                 | 123 |  |  |  |  |  |  |  |

| 5        | Hardware-accelerated test platform 125 |            |                                                       |     |  |  |  |  |  |  |  |

|          | 5.1                                    | State      | of the art on traffic generation                      | 126 |  |  |  |  |  |  |  |

|          |                                        | 5.1.1      | Traffic models                                        | 126 |  |  |  |  |  |  |  |

|          |                                        | 5.1.2      | Commercial generators                                 | 128 |  |  |  |  |  |  |  |

|          |                                        | 5.1.3      | Software-based generators                             | 128 |  |  |  |  |  |  |  |

|          |                                        | 5.1.4      | Hardware-accelerated generators                       | 130 |  |  |  |  |  |  |  |

|          | 5.2                                    | An op      | en-source FPGA traffic generator                      | 130 |  |  |  |  |  |  |  |

|          |                                        | 5.2.1      | Requirements                                          | 130 |  |  |  |  |  |  |  |

|          |                                        | 5.2.2      | Technical constraints                                 | 132 |  |  |  |  |  |  |  |

|          |                                        | 5.2.3      | Global specifications                                 | 132 |  |  |  |  |  |  |  |

|          | 5.3                                    | Softwa     | are architecture                                      | 134 |  |  |  |  |  |  |  |

|          |                                        | 5.3.1      | The configuration interface                           | 135 |  |  |  |  |  |  |  |

|          |                                        | 5.3.2      | The configuration format                              | 136 |  |  |  |  |  |  |  |

|          |                                        | 5.3.3      | The control tool                                      | 138 |  |  |  |  |  |  |  |

|          | 5.4                                    | Hardw      | vare architecture                                     | 138 |  |  |  |  |  |  |  |

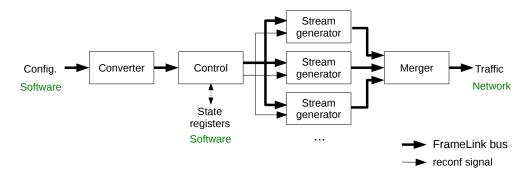

|          |                                        | 5.4.1      | Main components                                       | 139 |  |  |  |  |  |  |  |

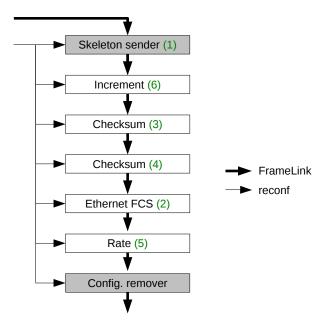

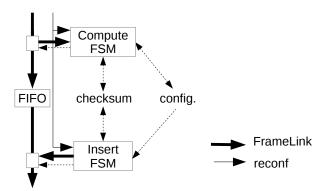

|          |                                        | 5.4.2      | Inside the stream generator                           | 141 |  |  |  |  |  |  |  |

|          | 5.5                                    | Gener      | ator use cases                                        | 145 |  |  |  |  |  |  |  |

|          |                                        | 5.5.1      | Design of a new modifier                              | 145 |  |  |  |  |  |  |  |

|          |                                        | 5.5.2      | Synthesis on the FPGA                                 | 148 |  |  |  |  |  |  |  |

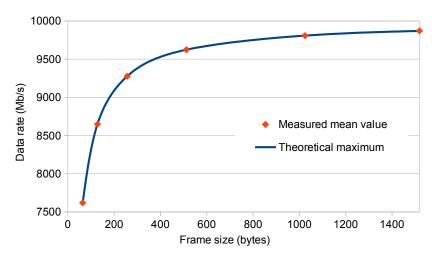

|          |                                        | 5.5.3      | Performance of the traffic generator                  | 149 |  |  |  |  |  |  |  |

|          | 5.6                                    | Concl      | usion                                                 | 152 |  |  |  |  |  |  |  |

| 6        | Cor                                    | Conclusion |                                                       |     |  |  |  |  |  |  |  |

|          | 6.1                                    | Main       | contributions                                         | 155 |  |  |  |  |  |  |  |

|          |                                        | 6.1.1      | Development platform                                  | 155 |  |  |  |  |  |  |  |

|          |                                        | 6.1.2      | Software monitoring applied to security               | 157 |  |  |  |  |  |  |  |

|          |                                        | 6.1.3      | Hardware monitoring applied to traffic classification | 158 |  |  |  |  |  |  |  |

|          |                                        | 6.1.4      | Hardware-accelerated test platform                    | 159 |  |  |  |  |  |  |  |

|          | 6.2                                    | Accele     | eration solutions comparison                          | 161 |  |  |  |  |  |  |  |

|          | 6.3                                    | Perspe     | ectives                                               | 163 |  |  |  |  |  |  |  |

| Glossary |                                        |            |                                                       |     |  |  |  |  |  |  |  |

Bibliography 171

# Chapter A

# Abstract

Traffic monitoring is a mandatory task for network managers, be it small company networks or national Internet providers' networks. It is the only way to know what is happening on a network. It can be very basic and consist in simply measuring the data rate of the traffic on a link, or it can be more sophisticated, like an application to detect attacks on protected servers and raise alarms.

Use cases for traffic monitoring are very diverse. They can be separated into categories. An important category is security: a large number of attacks are transmitted using the networks of Internet providers everyday. These attacks are dangerous, and some of them can saturate network resources and degrade the quality of service offered by the network. So network managers are very interested in detecting these attacks to try and mitigate them. Another important category is traffic engineering. It is important for all network managers to get as much data as possible about what happens on their network. Data can be used simply for statistics, or it can be used in real time by automated systems: knowing what the traffic is made of is a good way to make better real time network management decisions.

As Internet keeps gaining importance in our societies, the exchanged data amounts increase every year. To support these increases, network operators install new links with very high data rates. Customers can now get a connection of 1 Gb/s by optical fiber, so aggregation links of tens of gigabits per second are common. This is why traffic monitoring applications now have to support high data rates to be deployable on real networks.

To implement traffic monitoring applications that support high data rates, we first analyze four existing development platforms: powerful computers with high-speed network interfaces, powerful computers with high-speed network interfaces and a fast graphic card to accelerate processing, network processors and Field-Programmable Gate Arrays (FPGAs). Network processors are like normal processors, but with an optimized access to network interfaces and hardware-accelerated features useful for traffic processing. FPGAs are chips that are configurable at a very low level. They offer massive parallelism, a very low-level access to network interfaces, and a perfect control of timing.

Normal computers are the most flexible and cheapest option, but they struggle handling received packets at high data rates. Graphic cards can accelerate highly parallel computations but cannot help for low level packets processing. Network processors are good at packet processing and can offer good performance, but they are specialized for some specific use cases, different for each model. FPGAs support high data rates and can accelerate processing using parallelization, but the development time is long and the resulting application is difficult to make flexible.

Due to these differences, no platform is the absolute best, it depends on the use case. This is why we study three different use cases. All require the support of high data rates but the main goals are different. The first use case is in the domain of security and focuses on flexibility. It allows to explore the possibilities to support high data rates in software when implementing light algorithms, while keeping the great flexibility of software development. In contrast, the second use case in the domain of traffic engineering requires the implementation of heavy algorithms in a fully real-time environment. This is a reason to explore the possibilities offered by FPGAs to accelerate complex processing. It shows how parallelism and low-level control can help manage high data rates. The last use case combines the requirements of the two previous ones. It is a traffic generator with strong real-time needs, but for which flexibility is essential too. The chosen solution is a trade-off using an FPGA in collaboration with a processor to configure it.

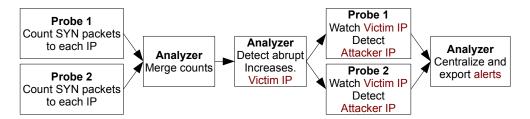

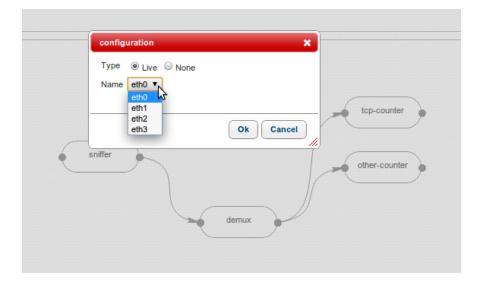

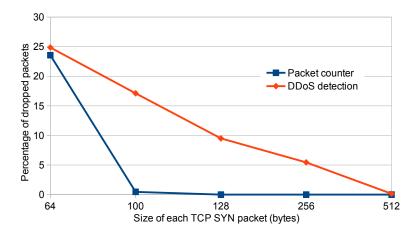

The first use case in the security domain was done in the framework of a European project called DEcentralized, cooperative, and privacy-preserving MONitoring for trustworthines (DEMONS). We participated to the development of a flexible and scalable network monitoring framework for normal computers. It is a pure software development. We developed an application to test the framework: a detector of a certain kind of network attacks called Transmission Control Protocol (TCP) SYN flooding. We used an algorithm for counting packets called Count Min Sketch (CMS) and an algorithm for detecting abrupt changes in time series called CUmulative SUM control chart (CUSUM). The advantage of software development is that it is very flexible: the detector can be made distributed simply by changing the configuration using a Graphical User Interface (GUI). We show that thanks to the efficient framework, the application is able to support realistic 10 Gb/s traffic, but it struggles in stress conditions when receiving very small packets. We then give ideas about the possibility to build an hybrid architecture, with an FPGA managing the packets and sending aggregated data to the computer. The goal is to keep the flexibility of software while supporting higher data rates easily.

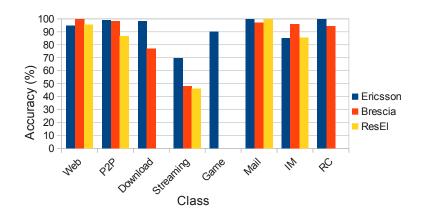

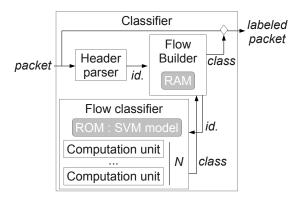

After showing the limits of pure software development, we turn to pure hardware development on FPGA with the use case of traffic classification. It consists in associating each packet transiting on a link to the category of application that generated it: for instance a web browsing application, a video streaming application, or a gaming application. We use a well-known classification algorithm called Support Vector Machine (SVM). It works with a learning phase and a classification phase. The classification phase is implemented using an optimized, massively parallel architecture on the FPGA. We show that a unique FPGA could handle the computation phase of the classification of a realistic trace at a rate up

to 473 Gb/s if adapted interfaces were available. To let the application work, we also need a way to group received packets into flows of similar packets, supporting at least one million simultaneous flows. We develop a new algorithm to do that and implement it on the FPGA. An actual implementation on an existing board supports the link rate (10 Gb/s) without problems. The main drawback of the implementation is the flexibility: changing parameters of the algorithm forces to reconfigure the FPGA, which takes time.

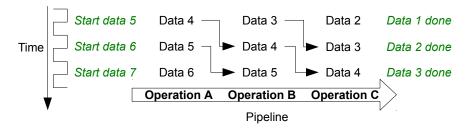

To test the attack detector or the traffic classifier, a traffic generator is needed. As test implementations support 10 Gb/s, the same rate has to be supported by the traffic generator. And to get reliable results, the generator should be able to generate traffic accurately at any rate up to 10 Gb/s, even when sending small packets, which are the most challenging to handle. As commercial traffic generators are expensive and not very flexible, we build our own open-source flexible and extensible traffic generator supporting a data rate up to 20 Gb/s. To build a reliable generator, we decide to implement it on an FPGA. But for this application, flexibility is required. All parameters of the generated traffic must be easy to configure: data rate, packet size, inter-packet delay, packet headers and data. So we design a very flexible modular architecture for the traffic generator. Each module can be configured without FPGA reconfiguration, and the creation of new modules modifying the generated traffic is made as easy as possible. A GUI is built to make the configuration simple. We show that the traffic generator can support up to 20 Gb/s easily, and that it respects the configured data rate with a very good accuracy.

Many high-performance tools built for our test implementations can be reused for other traffic monitoring applications: counting packets using CMS (software), detecting changes in time series using CUSUM (software), classifying data using SVM (hardware), grouping packets into flow using a custom algorithm (hardware), generating traffic in a flexible and scalable way (hardware). These different experiments on commodity hardware and on FPGA also allow us to draw conclusions on the best platform to use depending on the use case.

# Chapitre B

# Résumé

#### B.1 Introduction

La surveillance de trafic est une activité indispensable pour tous les gestionnaires de réseaux, que ce soit des réseaux de petites entreprises ou de fournisseurs nationaux d'accès à internet. C'est le seul moyen pour savoir ce qui se passe sur le réseau. L'objectif peut être très simple, comme la mesure du débit d'un lien, ou plus sophistiqué, comme la détection d'attaques contre des machines protégées.

Un aspect important de la surveillance de trafic est la sécurité. Les réseaux sont des outils pour différents comportements illégitimes : propagation de virus, envoi de courriers non sollicités, recherche de machines vulnérables, prise de contrôle de machines sans autorisation, envoi de grandes quantités de données pour surcharger un serveur, ou interception de données sensibles. La plupart de ces comportements produit du trafic spécifique qui peut être identifié par des outils de surveillance de trafic. Mais faire la différence entre un trafic légitime et illégitime n'est pas évident, surtout si les attaquants tentent de faire passer leur trafic pour du trafic normal. Récemment, de nombreuses attaques de grande envergure ont eu lieu, comme par exemple une tentative de faire tomber l'infrastructure du NASDAQ [Rya13]. Chaque machine peut être protégée contre les attaques par des mises à jour régulières pour colmater les failles découvertes, et par l'utilisation d'un antivirus et d'un pare-feu. Mais les opérateurs ont également leur rôle à jouer. En effet, ils ont une vision globale du réseau, et ils sont les seuls à avoir la possibilité de stopper une attaque à sa source. Actuellement, les opérateurs laissent leurs clients se défendre, mais les plus grosses attaques peuvent mettre à mal leur réseau. Ils ont donc intérêt à offrir des services de protection avancés à leurs clients. Pour cela, ils doivent disposer d'outils de surveillance en temps réel de leur réseau.

Un autre aspect important de la surveillance de trafic est son utilisation pour l'ingénierie de trafic. L'objectif est de mieux connaître le trafic pour mieux le transporter. Un application importante pour cela est la classification de trafic. Le trafic sur Internet est fait d'une agrégation de paquets représentant des bouts d'information. Chaque paquet contient une en-tête qui indique où envoyer le paquet et d'où il vient, mais pas quelle application l'a généré ou quel type de trafic il transporte. La classification de trafic consiste à associer un paquet à

l'application qui l'a généré. De cette manière, un paquet généré par Skype peut être traité différemment d'un paquet généré par Firefox par exemple. En effet, les besoins en termes de délai d'une communication vocale et de la consultation d'une page web sont très différents. La classification de trafic peut aussi être utile pour filtrer un type de trafic à surveiller particulièrement.

Bien que les applications de surveillance de trafic puissent être très différentes, elles font toutes face à une difficulté commune : la montée en débit. CISCO prévoit que le trafic global sur Internet va tripler entre 2012 et 2017 [Cis13]. La surveillance de trafic doit donc se faire à très haut débit. Les liens de plusieurs dizaines de Gb/s deviennent fréquents chez les opérateurs. Ces débits rendent très difficile l'utilisation d'ordinateurs puissants du commerce pour surveiller le trafic, mais différentes plateformes plus adaptées existent. Des cartes réseau capables de gérer 2x10 Gb/s sont vendues par Intel. Pour la partie calculatoire, des cartes graphiques permettent d'accélérer les traitements. Pour des débits plus élevés, il existe des processeurs spécialisés pour les applications réseau. À encore plus bas niveau, les Field-Programmable Gate Arrays (FPGAs) sont des puces qui peuvent être configurées pour se comporter n'importe quel circuit numérique. Ces puces permettent un parallélisme massif et un accès direct aux interfaces réseau.

L'objectif de cette thèse est d'évaluer différents moyens d'accélérer des applications de surveillance de trafic. Une littérature abondante existe sur la détection d'anomalies et la classification de trafic. La précision des algorithmes étudiés est souvent mesurée avec soin, mais la possibilité de les réaliser de manière efficace est moins souvent analysée. C'est pourquoi nous allons d'abord étudier différentes plateformes de développement offrant des possibilités d'accélération logicielle ou matérielle. Nous allons ensuite réaliser une première application dans le domaine de la sécurité en utilisant l'accélération logicielle. Puis nous réaliserons un classificateur de trafic utilisant l'accélération matérielle. Enfin, nous trouverons un compromis entre logiciel et matériel pour réaliser un générateur de trafic flexible, fiable et rapide.

# B.2 Choisir une plateforme de développement

Il existe plusieurs plateformes de développement adaptées aux applications réseau. Selon les besoins, le meilleur choix de plateforme peut être différent. Nous avons étudié trois plateformes. La première et la moins coûteuse est simplement un ordinateur du commerce puissant, avec une carte réseau capable de supporter des débits d'au moins 10 Gb/s. Un processeur graphique peut être ajouté à l'ordinateur pour permettre des calculs massivement parallèles. La seconde est un processeur réseau. C'est un processeur classique avec un accès direct à des interfaces réseau, et un jeu d'instructions qui permet de réaliser simplement certaines fonctions communes pour le traitement de trafic. La troisième est la plus bas niveau : les FPGAs. Ces puces peuvent être programmées pour réaliser n'importe quel circuit électronique. Elles permettent un accès direct à des interfaces réseau, et un traitement complètement parallélisé. Les avantages et inconvénients de chaque plateforme sont résumés en anglais dans les tableaux 2.1 et 2.2

Si le besoin le plus crucial pour l'application est la flexibilité, l'utilisation d'un

ordinateur du commerce semble être la meilleure solution car le développement et les mises à jour sont plus simples. Selon les besoins de parallélisme de calcul, l'utilisation d'un processeur graphique peut être nécessaire ou pas. Mais la vitesse de communication entre l'interface réseau et le processeur est très vite bloquante, même pour supporter seulement 10 Gb/s.

C'est pourquoi si l'objectif principal est d'obtenir le meilleur débit possible et la plus grande puissance de calcul, le choix se portera plutôt sur les processeurs réseau et les FPGAs. Les processeurs réseau sont très efficaces pour les tâches communes dans le domaine des réseaux (calcul de checksums...) et peuvent s'avérer peu coûteux s'ils sont vendus par centaines de milliers. En revanche, les FPGAs sont plus versatiles et le code développé est plus facile à porter vers d'autres plateformes. Si plus de puissance de calcul est requises et si le produit doit être vendu par centaines de milliers, les Application-Specific Integrated Circuits (ASICs) sont une option intéressante. Il s'agit de puces spécialement réalisées pour une tâche particulière. Le code développé sur FPGA peut être utilisé comme base pour concevoir un ASIC.

Dans les prochaines sections, trois applications vont être développées. Une sur un ordinateur du commerce, et les deux autres sur FPGA. Les résultats permettront de clarifier certains aspects de ces plateformes. En particulier :

- la comparaison de la puissance de calcul disponible sur processeur et sur FPGA, ainsi que la façon d'utiliser au mieux la puissance disponible;

- la simplicité de mise à jour permise par les processeurs et les moyens d'obtenir cette simplicité sur FPGA aussi;

- le temps de développement sur chaque plateforme, et les méthodes pour réduire ce temps pour les FPGAs;

- les perspectives de futur passage à l'échelle permises par chaque plateforme.

## B.3 Surveillance logicielle pour la sécurité

La façon la plus simple de réaliser une application de surveillance de trafic est de faire du développement logiciel sur un ordinateur du commerce. C'est la solution que nous avons étudié dans le cadre du projet européen DEcentralized, cooperative, and privacy-preserving MONitoring for trustworthinesS (DEMONS). L'un des objectifs de ce projet est de fournir une plateforme flexible de surveillance de trafic à haut débit. Notre rôle dans DEMONS est d'aider au développement et de tester cette plateforme appelée BlockMon. Pour cela, nous réalisons une application de détection d'un certain type d'attaques appelé Distributed Denial of Service (DDoS) qui consiste à envoyer depuis de nombreux ordinateurs beaucoup de trafic à un serveur pour l'empêcher de fonctionner normalement.

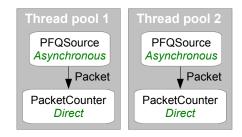

Le code développé pour BlockMon est en C++. Le fonctionnement de BlockMon est optimisé pour éviter autant que possible les opérations chronophages comme la copie des données en mémoire. BlockMon intègre une pile réseau optimisée appelée PFQ. Cette pile remplace la pile réseau standard de Linux et

est compatible avec la technologie Receive Side Scaling (RSS) d'Intel qui permet de séparer le trafic réseau reçu dans plusieurs files qui peuvent être traitées par des cœurs logiciels différents. BlockMon permet aussi de gérer très finement l'organisation du parallélisme grâce à la notion de groupes de processus réservés à l'exécution de certains blocs de code.

Grâce à sa structure en blocs configurables, BlockMon est très flexible et peut être configuré facilement grâce à une interface graphique. Sans aucun développement supplémentaire, une application développée correctement peut fonctionner avec une sonde unique ou avec des sondes multiples distribuées dans le réseau. Il est aussi possible d'utiliser plus ou moins de cœurs pour une application donnée, et de régler les paramètres de fonctionnement de l'application.

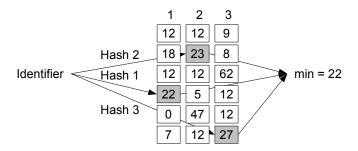

Le développement de l'application de détection de DDoS est simplifié par les blocs de base fournis par BlockMon. Nous avons développé deux algorithmes de base comme des librairies : Count Min Sketch (CMS) pour compter les paquets reçus avec une utilisation mémoire efficace, et CUmulative SUM control chart (CUSUM) pour détecter des changements brusques dans les nombres de paquets reçus. L'application elle-même est divisée en blocs pour exploiter la flexibilité offerte par BlockMon. Tous les blocs et librairies peuvent être réutilisés pour d'autres applications. Les librairies sont les plus simples à réutiliser car elles sont très génériques.

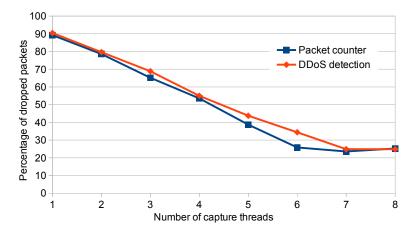

Pour tester le débit maximum supporté par notre application, nous avons utilisé un générateur de trafic pour envoyer un trafic difficile à notre détecteur. Le détecteur était installé sur une machine puissante avec une interface réseau à 10 Gb/s. Les résultats montrent l'intérêt de BlockMon et de son mécanisme de gestion du parallélisme : presque tous les paquets sont perdus en utilisant un seul cœur, mais moins d'un quart des paquets sont perdus avec sept cœurs. Ces résultats sont pour du trafic de test. Pour du trafic réaliste, avec des paquets plus longs, les 10 Gb/s peuvent être supportés par notre détecteur sans perdre de paquets.

Le développement logiciel est relativement simple et rapide. La flexibilité de BlockMon serait difficile à offrir avec des développements matériels, et l'exemple du détecteur de DDoS montre qu'il est possible de supporter 10 Gb/s en logiciel. Cependant, une machine très puissante est nécessaire, et les test avec le trafic le plus difficile à gérer montre que nous atteignons les limites de cette plateforme. En outre, une configuration très fine de la machine est nécessaire pour obtenir ces résultats.

Il serait intéressant de mélanger des fonctions bénéficiant d'accélération matérielle et des fonctions logicielles. Une société appelée Invea-Tech a déjà développé un block BlockMon permettant de communiquer avec un FPGA. Il serait donc possible par exemple d'utiliser une version matérielle de l'algorithme CMS, et d'exécuter seulement l'algorithme CUSUM en logiciel, car les contraintes temps-réel sont moins grandes pour CUSUM qui ne traite pas directement les paquets mais des données agrégées.

# B.4 Surveillance matérielle pour la classification de trafic

Nous avons vu les possibilités et les limites des approches purement logicielles. Maintenant nous allons nous intéresser à une approche purement matérielle sur FPGA. Pour tester les capacités de calcul des FPGAs, nous nous intéressons à une application plus lourde en calcul que la détection de DDoS: la classification de trafic en fonction du type d'application (web, jeu, partage de fichiers...). Pour que l'algorithme soit capable de classifier aussi le trafic chiffré, nous utilisons des paramètres très simples pour classifier les paquets. Le trafic est divisé en flots, qui sont des ensembles de paquets ayant les mêmes adresses et ports source et destination. Un flot est caractérisé par la taille des paquets 3, 4 et 5. Un algorithme de classification par apprentissage supervisé nommé Support Vector Machine (SVM) est utilisé pour associer les tailles de paquets à un type d'application. Pour la réalisation, nous utilisons des cartes de gestion de trafic intégrant des FPGAs comme la NetFPGA 10G.

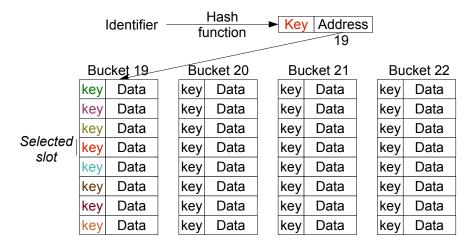

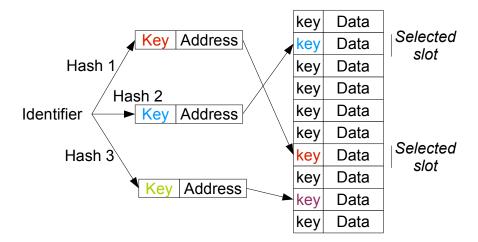

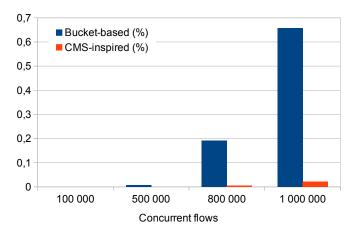

Nous avons d'abord construit un algorithme simple et efficace de stockage de flots inspiré de l'algorithme CMS. Il supporte avec quasiment aucune perte le stockage d'un million de flots simultanés, et garantit des temps de recherche et d'insertion constants. Il utilise aussi assez peu de ressources sur le FPGA.

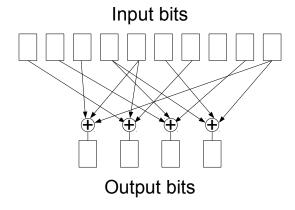

Le processus de classification de flot basé sur SVM est réalisé de manière complètement parallèle grâce à un pipeline capable de commencer le calcul sur un nouveau vecteur du modèle SVM à chaque coup d'horloge. Pour accélérer ce processus, plusieurs unités de calcul peuvent fonctionner en parallèle, divisant le temps requis pour classifier un flot.

Le noyau est une fonction importante de l'algorithme SVM. Nous en avons testé deux. Le classique RBF, et une version plus adaptée à une plateforme matérielle que nous avons nommée CORDIC. Les deux noyaux offrent la même précision, mais le CORDIC supporte des fréquences de fonctionnement plus élevées et utilise moins de place sur le FPGA, ce qui permet de mettre plus d'unités de calcul en parallèle. Le modèle SVM obtenu avec le noyau CORDIC est plus simple et plus rapide à gérer que le modèle obtenu avec RBF, ce qui apporte une amélioration inattendue du temps de traitement.

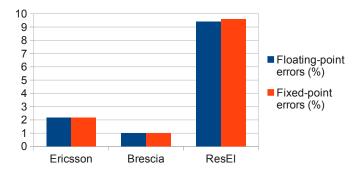

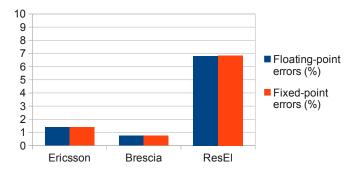

Grâce à ces optimisations, la classification de flots peut être faite à 320 075 flots par seconde pour un modèle SVM avec 8 007 vecteurs, ce qui permettrait une classification de la trace la plus réaliste que nous avons testée, Brescia, à 473 Gb/s. Pour augmenter la vitesse supportée par le classificateur, différents paramètres devraient être changés :

- utiliser des interfaces réseau à plus haut débit;

- utiliser un meilleur FPGA pour permettre de paralléliser SVM encore plus;

- utiliser une plus grosse mémoire externe pour supporter plus de flots simultanés sans augmenter le risque de perte.

Une autre amélioration possible de la version actuelle serait de la rendre plus

flexible en stockant le modèle SVM dans des RAMs plutôt que des ROMs, pour éviter d'avoir à refaire une synthèse pour changer le modèle.

Le mécanisme de stockage de flots peut être réutilisé pour toute application réseau basée sur les flots. Le code de SVM sur FPGA est générique et peut être utilisé pour d'autres problèmes de classification.

Cette réalisation sur FPGA d'un algorithme de surveillance de trafic rend les avantages et inconvénients de cette plateforme visibles :

- le développement est long et complexe. Des problèmes comme la quantification des variables doivent être pris en compte. D'autres problèmes triviaux en logiciel, comme le stockage des flots, doivent être gérés manuellement à cause des ressources limitées.

- La flexibilité n'est pas automatique. Par exemple de nouveaux développements seraient nécessaires pour changer dynamiquement le modèle SVM.

- L'accélération est très conséquente, surtout pour des algorithmes comme SVM qui peuvent être massivement parallèles.

- Il est facile de garantir un traitement en temps réel car chaque délai est connu et aucune autre tâche ne peut interférer avec le traitement en cours.

# B.5 Plateforme de test avec accélération matérielle

Nous avons vu deux approches de surveillance du trafic. Une purement logicielle et une purement matérielle. Dans chaque cas, nous avons développé des prototypes fonctionnant à 10 Gb/s. Pour les tester, nous avons eu besoin d'un générateur de trafic. Nous avons utilisé un générateur commercial, mais nous souhaitons maintenant créer notre propre générateur, plus flexible et meilleur marché. Nous voulons un générateur qui supporte au moins 10 Gb/s sans aucun paquet perdu, même avec le trafic le plus dur à gérer. C'est pourquoi nous le développons sur FPGA. Mais nous voulons aussi une grande flexibilité, d'où l'utilisation d'une approche hybride logicielle et matérielle.

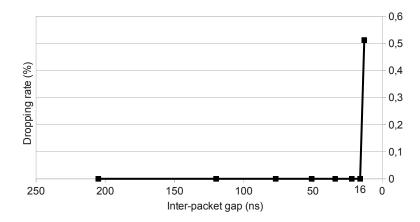

Le générateur de trafic est open-source. Il utilise le FPGA d'une carte Combo pour saturer deux interfaces à 10 Gb/s facilement, même avec les plus petits paquets permis par le protocole Ethernet. L'architecture modulaire du générateur lui permet d'être flexible à tous les niveaux.

La façon la plus simple de personnaliser le trafic généré est d'utiliser l'interface graphique de configuration. Quelques clics suffisent pour spécifier le trafic sous la forme de flux de paquets qui partagent certaines caractéristiques. Chaque flux peut atteindre 10 Gb/s. L'utilisation de plusieurs flux concurrents permet de générer un trafic diversifié, ou d'envoyer du trafic sur plusieurs interfaces.

Contrairement aux générateurs de trafic commerciaux, si l'interface graphique n'offre pas les bonnes options pour générer le trafic voulu, l'utilisateur peut développer ses propres fonctions. Le générateur est fait pour simplifier l'ajout de nouveaux modules appelés modificateurs. Le développement d'un modificateur

nécessite de connaître le VHDL et un peu de Python, mais cela reste aussi simple que possible. Tous les modificateurs existants sont documentés et peuvent être utilisés comme exemples.

Bien que le générateur fonctionne pour le moment avec la carte Combo d'Invea-Tech, cette carte est très similaire au NetFPGA 10G, bien connu des chercheurs. La plateforme NetCOPE utilisée par le générateur est compatible avec le NetFPGA 10G, donc porter le générateur vers NetFPGA devrait être assez simple. Nous souhaitons le faire dés que possible.

Actuellement, le générateur de trafic est fait pour générer du trafic à haut débit pour des tests de charge. Il n'est pas adapté pour générer du trafic réaliste. Mais cela pourrait changer simplement en développant de nouveaux modificateurs contrôlant les tailles et délais inter-paquets selon l'un des nombreux modèles de trafic disponibles dans la littérature.

Comme le générateur de trafic est un projet open-source, son code est disponible en ligne [Gro13]. Si certains lecteurs sont intéressés par le développement de nouveaux modificateurs ou veulent aider à porter le générateur vers NetFPGA, ou s'ils ont des idées pour améliorer le projet, qu'ils n'hésitent pas à s'impliquer.

L'architecture du générateur de trafic est un bon exemple de l'utilisation des avantages des FPGAs sans perdre la flexibilité pour l'utilisateur. Les FPGAs apportent des avantages clairs pour le contrôle du temps réel. Le développement bas niveau permet de contrôler les temps inter-paquets bien plus facilement qu'en logiciel. Le support du débit maximum se fait naturellement grâce au parallélisme du FPGA. Une fois que l'architecture est conçue correctement, le support du débit maximum est garanti.

Mais le développement sur FPGA est long et complexe, il devrait donc être évité autant que possible. Faire communiquer le FPGA avec l'ordinateur pour recevoir les données de configuration est une bonne manière de garder une partie du traitement en logiciel. Du point de vue de l'utilisateur, bien que le FPGA soit un outil bas niveau, il peut être caché derrière une interface graphique simple et utilisable par tous. Quand le développement sur FPGA est nécessaire malgré tout, il peut être simplifié en définissant clairement l'architecture dans laquelle les nouveaux blocs doivent être intégrés, et en fournissant des exemples.

### B.6 Conclusion

Cette thèse propose différentes méthodes pour accélérer la surveillance de trafic pour supporter de très hauts débits. La meilleure solution dépend de l'application et de ses besoins les plus importants. L'accélération doit être prise en compte à la fois au niveau algorithmique et au niveau du développement pour obtenir les meilleurs résultats. Nous avons vu qu'une bonne manière d'obtenir à la fois les avantages du matériel (haut niveau de parallélisme, contrôle du temps réel) et du logiciel (facilité de développement, flexibilité) est de concevoir des architectures mixtes. La partie traitant directement les paquets est gérée par le matériel, et la partie qui ne traite que des données accumulées est gérée par le logiciel.

De nombreux outils haute performance développés pour nos prototypes peuvent être réutilisés dans d'autres applications : le comptage de paquets utilisant l'algorithme CMS (logiciel), la détection de changements dans des séries temporelles utilisant l'algorithme CUSUM (logiciel), la classification de données utilisant l'algorithme d'apprentissage SVM (matériel), le groupement de paquets en flots utilisant un algorithme inspiré de CMS (matériel), la génération de trafic de manière flexible et efficace (matériel).

Ces développements permettent de déduire quelques règles utiles pour choisir une plateforme de développement pour un application de traitement de trafic :

- Le débit maximal supporté est le point faible des implémentations logicielles. Un débit de 10 Gb/s peut être un problème dans le pire cas, même pour une application simple.

- Le développement sur FPGA est un processus long et complexe, ce qui rend le développement logiciel plus attrayant.

- Cependant supporter des débits élevés en logiciel nécessite un développement précis et de très nombreux réglages de la plateforme, qui peuvent ralentir fortement le développement logiciel.

- Les architectures hybrides logicielles et matérielles peuvent être très efficaces, à condition de faire attention au débit de communication avec le processeur.

La possibilité d'intégrer un FPGA et un processeur sur la même puce, ou au moins sur la même carte, permettrait une communication plus facile entre les deux et des possibilités d'interactions plus grandes.

Les besoins en surveillance de trafic semblent se multiplier actuellement car les gouvernements souhaitent de plus en plus contrôler ce que les gens font sur Internet. Un Internet sans contrôle ne pourrait pas fonctionner, mais la surveillance doit prendre en compte le respect de la vie privée des utilisateurs. En effet, malgré l'utilisation de systèmes de chiffrement, il est techniquement possible d'apprendre énormément de choses sur les personnes utilisant le réseau grâce à des systèmes de surveillance en temps réel tels que ceux présentés ici.

# Chapter 1

# Introduction

## 1.1 Context

Traffic monitoring is a mandatory task for network managers, be it small company networks or national Internet providers' networks. It is the only way to know what is happening on a network. It can be very basic and consist in simply measuring the data rate of the traffic on a link, or it can be more sophisticated, like an application to detect attacks on protected servers and raise alarms.

Use cases for traffic monitoring are diverse and can be separated into different categories. An important category is security. Networks can be used for all kinds of malicious behaviours: for example propagating viruses through malicious websites or emails, sending unsolicited emails, scanning the network to find vulnerable machines, taking remotely control of machines without authorization, sending a large amount of traffic to a machine to overload it, or intercepting traffic to access to sensitive data. Most of these behaviours produce specific traffic that may be identified using traffic monitoring tools. The challenge is that legitimate traffic can take many forms, making it difficult to differentiate the malicious traffic. And attackers do all they can to make the malicious traffic look legitimate, so attacks and monitoring tools have to become more and more elaborate.

Many attacks have made the news lately, like an attempt to take the NAS-DAQ infrastructure down [Rya13]. These attacks are often successful and outline the need to have monitoring tools that can detect attacks early and make it possible to mitigate them efficiently. Attackers use multiple techniques to create successful attacks. First they hide their identity. To do that, they never conduct attacks directly. They take control of machines that are not protected properly, and use them to conduct the attacks. They also often hide the origin of the traffic by indicating fake source addresses. Techniques used to take control of machines usually take advantage of flaws in legitimate applications and protocols. So security has to be applied at multiple levels. The first thing to do is to fix flaws as soon as they are discovered. Antivirus software can also be used to protect individual machines by detecting applications with unusual behaviours. Firewalls can restrict incoming and outgoing traffic to try to prevent attackers from accessing to sensitive machines. At the network level, providers can stop traffic with fake source addresses only if it comes directly from their own customers. As

many providers do not apply such a strategy, fake source addresses cannot be fully avoided. But network providers can also apply more advanced algorithms to monitor the traffic and detect specific traffic if it behaves like an attack. They can then stop the traffic early, making the attack fail. This kind of protection is not really offered by providers yet, but solutions exist in the literature.

Another category of traffic monitoring applications is used for traffic engineering. It mostly consists in getting information about the traffic transiting in the network or the state of the network. An important application is traffic classification, which is able to associate traffic to the application that generated it. On the Internet, traffic is made of an aggregation of packets, each packet represents a piece of data. Each packet has a header giving some information like an address for the sender and the receiver of the packet. The address of the receiver is used to route the packet in the network. But there is no standard way for a packet to indicate information like the application that generated it, or the kind of data it contains. The role of traffic classification information is to use the packet data and header to guess the application or the category of applications that generated the packet. For example a packet has been generated by Skype and contains voice data. Another packet has been generated by Firefox and contains web data. A packet could also be generated by Firefox but contain video streaming data, when browsing YouTube for instance.

Traffic classification can be useful to network managers in different ways. It can be used to prioritize some traffic. For example packets that contain videoconference data must be delivered fast, so as to make the conversation fluid. Packets that contain web data can be delayed if necessary, because it will only delay the display of the page of some milliseconds. Another use of traffic classification is lawful interception: governments are more and more interested in forcing network operators to log some specific traffic, like Skype calls for example. Some use cases make traffic classification more challenging than others. For example, if it is used to prioritize traffic, some users may try to make all their traffic resemble important traffic, so malicious behaviour should be taken into account.

Be it for security or for traffic engineering, the need for automatic accurate monitoring tools is rising. This is partly due to a current trend in network management called software-defined networking. It consists in decoupling the control and data planes of a network. Traffic is managed by manipulating abstractions that are not directly related to the physical network. The goal is to make networks more flexible: creating new services or adapting to new constraints becomes just a matter of software configuration. To work, this approach requires flexible and accurate network monitoring tools to be able to know what is happening on the network and to check the impact of global configuration changes.

Although traffic monitoring applications can be diverse, they face common challenges. The most important is due to the evolution of the Internet. CISCO forecasts [Cis13] that between 2012 and 2017, the global Internet traffic will increase threefold. It will reach one zettabytes per year in 2015. This means that network operators have to cope with always higher data rates. To do that, they deploy links supporting higher data rates. Traffic monitoring applications are not deployed directly on very high-speed links like transatlantic cables that can have

a speed of multiple terabits per second. But aggregation links of 10 Gb/s or more are common, as operators now easily offer 1 Gb/s to their customers with optical fiber.

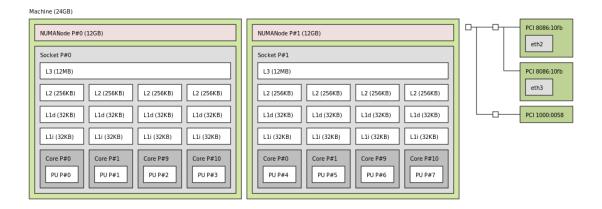

Supporting links of 10 Gb/s or more is difficult because it forces to process millions of packets per second. Current commercial computers are not offered with 10 Gb/s Network Interface Cards (NICs), but even if they were, they would not be able to process that many packets. This is why high performance developments are necessary. Different platforms are available for high-speed traffic processing. The most common is commodity hardware: powerful commercial computers can be used, fine-tuning software and using specialized NICs to make them support higher data rates. Graphics Processing Units (GPUs), which are originally designed for gaming, can also be added to perform highly parallel computations. But other platforms exist that provide more specialized hardware acceleration. Some special processors, called Network Processing Units (NPUs), have an architecture designed to handle high-speed traffic. At a lower level, Field-Programmable Gate Arrays (FPGAs) are chips that can be configured to behave like any digital electronic circuit. They provide massive parallelism and a very low-level access to network interfaces. Each platform has its own advantages and drawbacks in terms of performance, development time, cost and flexibility.

# 1.2 Objectives

The subject of this thesis is to evaluate different ways to accelerate traffic monitoring applications. A large body of literature exists in the domains of security and traffic engineering to tackle classical problems like anomaly detection or traffic classification. The accuracy of the proposed algorithms is usually well studied, but less work exists about the way an algorithm can be implemented to support high data rates.

To accelerate traffic monitoring applications, we will test different development platforms that provide software or hardware acceleration and see how they are adapted to traffic monitoring. We will implement applications for security and traffic engineering on different platforms, trying to take advantage of all features of the chosen platform, and to avoid the drawbacks specific to the platform.

The first application in the domain of security will use pure software, leveraging the flexibility inherent to software development, so that lightweight security algorithms can be used in many different contexts. It will allow to check the performance computers can provide using optimized software. The second application in the domain of traffic engineering will use an FPGA to accelerate an algorithm making heavy computations, so as to meet strong real-time requirements. It will show that hardware acceleration can bring huge speed improvements to traffic monitoring, at the cost of some other criteria like development time and flexibility. The last application, a traffic generator, will be a trade-off between flexibility and performance, using an FPGA to meet real-time requirements, as well as software to provide a simple configuration tool.

These different use cases will showcase all the aspects that should be taken into account when building a high-speed network processing application, like the performance, the development time, the cost or the flexibility. We will not test NPUs or GPUs because they require some very specific developments, and the advantages they bring (parallelism, accelerated functions, specialized architectures) can also been obtained on an FPGA. So FPGAs are a good choice to explore all possible acceleration techniques.

But to accelerate an application, it is not enough to work on an efficient implementation of a pre-defined algorithm. We will see that some algorithms are more adapted than others to support high data rates, because they are easier to parallelize or because they use less memory than others. We will also see that tweaking some algorithms can widely improve their scalability without necessarily hindering their accuracy.

Finally, we will be able to give advices on the development platform that should be chosen depending on the application, and we will provide some efficient implementations of useful traffic monitoring applications. Many developments will be reusable for other applications too, either as libraries for specific tasks, or as fully functional products.

## 1.3 Traffic monitoring

Before starting to implement traffic monitoring applications, it is important to choose the right algorithm. To do this, we will list some important features of these algorithms, focusing on the ones that impact strongly the implementation. Similar algorithms will result in the same implementation challenges.

We will discuss the **topology** of the application, that is to say the place in the network where the probe or probes are located. The **time constraints** on the algorithm are important too: some processing has to be done fast, while other things can be delayed. The **traffic features** used define the way received packets will be treated. The **detection technique** then defines how gathered data will be processed. Some applications also require a **calibration**, which is usually a separate implementation from the core of the application.

## 1.3.1 Topology

The first thing to differentiate traffic monitoring applications is the way they are located on the network. The simplest alternative is to have only one standalone probe on a link. The advantage is that it is easy to setup. It requires only one machine and it is easy to install for a network operator.

But many traffic monitoring applications are distributed. They are made of different probes on different links on the network. This way, the application has a more global view of the activity on the network. Often collectors are added to the probes. They are machines that do not monitor the traffic directly but centralize reports from the probes. They can also analyze and store data. Distributed applications are more costly to setup. and the communication protocol must be well designed to avoid exchanging too much control data when monitoring traffic at high data rates.

Distributed applications are usually deployed on one network, with all probes belonging to the same operator. But it is also possible to create inter-domain traffic monitoring applications, with probes on networks from different operators. This is interesting because the application has an even more global view of the network. The main difficulty is that operators are usually reluctant to share data with potential competitors. But it is possible to let operators share some aggregated data with operators if they are part of the same coalition.

The chosen topology fully changes the contraints on the implementation. Standalone applications may have to cope with very high data rates, and they have to take care of the whole processing. So they need a lot of processing power. Distributed applications can use multiple machines for the processing. Each probe may receive less traffic as it is distributed on multiple probes. But communication delays between the machines can be long, and the amount of data sent should be limited to avoid overloading the network. Inter-domain applications often have stronger security requirements as data is transmitted through less trusted networks.

#### 1.3.2 Time constraints

Time constraints are the requirements for the application to finish a certain processing within a guaranteed delay. Depending on the application, time constraints can be very different. For example an application monitoring the data rate on a link may log it only every minute. The delay is not a problem. But an application that detects attacks must raise an alert fast so that the network administrator acts as fast as possible. And it is even worse for an application, which directly acts on the transiting traffic. For instance, a traffic classification application can tag packets on a link with a label depending on the kind of data transported. To do that, the application has to process packets very fast. If it is slow, it will delay all packets on the link, degrading the quality of the communication.

Time constraints must be taken into account when implementing an algorithm. Some development platforms are more adapted than others to real-time applications. Most applications are made of different parts that must meet different time constraints. For example, the part directly receiving packets must work in real-time, but another part gathering data and storing it periodically in a database can be slow.

#### 1.3.3 Traffic features

Traffic monitoring applications can be divided into two categories: active measurement applications and passive measurement applications. For active measurements, applications send some traffic and then observe how it is managed by the network. This synthetic traffic can be observed by a different probe somewhere else on the network, or an answer from another machine can be observed directly by the same probe. Examples of passive measurements can be a delay for packets to be sent from one probe to another, or a delay for a machine to answer to a request from the probe. The absence of answer can also be informative.

For passive measurements, applications extract data from different features of the traffic. Some simply use data in packet headers, like the size of packets. Others use the whole data of the packet. Many applications base their analysis on flows. The structure of packets is specified by encapsulated protocols. The lowest level protocol is usually Ethernet, it allows machines to communicate when they are directly connected. Then the usual protocol is Internet Protocol (IP), it allows machines to communicate, even if they are not directly connected. The IP header contains the source and destination IP addresses, unique identifiers of the sender and the target. Then two transport protocols are very common: Transmission Control Protocol (TCP) and User Datagram Protocol (UDP). They both are made to help applications communicate with each other. To differentiate applications on the same machine, they define source and destination ports. An unidirectional flow is a set of packets with the same source and destination IP address, the same transport protocol (UDP or TCP) and the same source and destination port. Some applications are based on bidirectional flows, that is to say that packets with inverted sources and destinations belong to the same flow. But most traffic monitoring applications are based on unidirectional flows because there is no guarantee on a network link to see the two directions of a flow: packets can be sent using one path on the network, and come back using another path.

Some applications are based on other features. For example they can analyze only Domain Name Service (DNS) requests, that is to say packets sent by users to ask for the IP address corresponding to a domain name. It is an easy way to list the servers to which each user connects. It is also possible to analyze only Border Gateway Protocol (BGP) packets. They are used by routers to communicate data about the IP addresses they know how to reach. Analyzing these packets can help have a clear view of the current network routing.

Higher-level approaches exist, like behavioural analysis: communications on the network are studied to determine who communicates with whom and how. A graph is then built and the communication pattern of each machine can help identify the role of the machine.

The traffic features used impact the implementation because some are easier to extract than others. A passive probe extracting only some headers from packets is easy to implement. Active probes measuring delays need an accurate way to measure time, which is not available on all platforms. Flow-level features force the probe to group packets of the same flow, storing data about each flow in a memory. Constraints on the memory are strong: it has to be big enough to store all flows, and the read and write speeds have to be fast enough to process received packets in real time.

## 1.3.4 Detection technique

All traffic monitoring applications use an algorithm to translate traffic features into information. This is what we call the detection technique, although the word detection may not be adapted to all applications.

Many applications use signatures: signatures of the applications for traffic classification, or signature of an attack for security. A signature is a set of features.

For example it can be a sequence of bits that has to be found at a certain location in a packet. If some traffic corresponds to this set of features, it corresponds to the signature. This technique is widely used for traffic classification because applications tend to generate always the same kind of traffic.

Learning techniques are also often used for classification. They consist in building a model for each type of traffic to detect. The model is built by observing traffic for which the category is known. When new traffic arrives, computations are made to check to which model it belongs the most.

Anomaly detection is another technique, widely used for security. It requires a knowledge of the normal traffic. When some abnormal features are detected, an alarm is raised because it is a potential attack. The advantage is that attacks that never happened before can be detected this way.

Some detection techniques can be very simple to implement: tree-based classification is usually implemented by a simple succession of conditions. Other techniques can require complex computations from the traffic features, making the implementation more complicated, and the resulting application slower. Some techniques are also more adapted to take advantage of hardware acceleration than others, so the choice is crucial.

#### 1.3.5 Calibration

Most traffic monitoring applications require a calibration to be functional. The calibration process depends on the detection technique. It is how signatures or models are created. For learning techniques to build their models, three methods exist:

- Supervised algorithms need a "ground truth", an example of traffic with data already attached. For example in the security domain, attacks should be identified in the trace. For traffic classification, the generating application should be identified.

- Semi-supervised algorithms need a ground truth too, but it can contain unknown traffic. The algorithm will guess to which category the unknown traffic should belong, and include it in its learning.

- Unsupervised algorithms require no ground truth, which makes them very easy to deploy. Often their output is less detailed than supervised algorithms.

For techniques based on signatures or anomalies, a ground truth is often necessary too. The calibration is often more manual than for learning algorithms. An expert can extract signatures from a ground truth, using its own knowledge of the traffic. An expert is also often required to define rules specifying the behaviour of normal traffic, so as to be able to detect anomalies.

The calibration does not directly impact the implementation because it is usually done offline with no timing constraints. But it deeply impacts the ease of deployment of the solution. An algorithm which requires no ground truth is simple to deploy and will probably work the same way on any network, while

an adapted ground truth will have to be found for each deployment for other algorithms. But using a ground truth is a way to extract more accurate data about the traffic.

## 1.4 Acceleration challenges

We have seen that traffic monitoring applications have common features. This is why one is often faced with the same challenges when accelerating a traffic monitoring application to support high data rates. We already talked about high-level challenges like the need to receive data at high speed, the need to make fast computations and the need for flexible applications. But some less obvious challenges are limiting factors found in most high-speed monitoring implementations. We will now present two of these challenges, which are not obvious but will be found multiple times in next chapters. The solutions provided in next chapters can often be reused for other traffic monitoring applications.

#### 1.4.1 Large data storage

Traffic monitoring implies handling huge amounts of data. For example, dumping all traffic on a 10 Gb/s link during one minute requires 75 GB of disk space. The challenge becomes even bigger if data has to be stored in a way that is simple to reuse afterwards. A simple task like counting the number of packets sent to each IP address seen by a network probe requires to maintain one counter (an integer of 32 bits for example) for each destination IP address. If Internet Protocol version 4 (IPv4) is used,  $2^{32} = 4.3 \times 10^9$  addresses exist. So using a simple memory with the IP address used as memory address would require  $2^{32} \times 32 = 1.4 \times 10^{11}$  bits, that is to say 17 GB of memory. This is even worse if we want to count packets with the same source and destination IP addresses, we would need  $7.3 \times 10^7$  TB of memory.

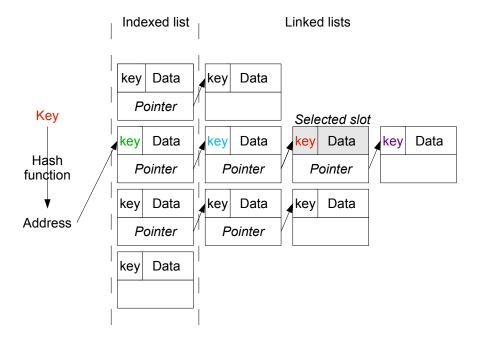

The realistic and classical solution in computer science is to use hash tables [SDTL05]. These storage structures are able to store elements in memory indexed by a key (the IP address in our example). The space they require in memory is the size of stored data plus the size of the key for each element. The key is stored alongside the pieces of data it indexes for future references. So for example if one million IP addresses are seen, a bit more than  $1000000 \times (32+32)$ bits will be required to store the counters. The first 32 bits are for the IP address and the others are for the counter itself. Hash tables provide very low mean delays for accessing or updating data from the key. The only problem is that to make sure that a new element is always stored somewhere, access and update delays can sometimes become very long, as long as the time needed to browse the whole list in the worst case. This is a blocking problem for real-time monitoring applications that must guarantee that they are able to support a certain data rate at all times. Another drawback is that the memory used can expand over time to make space for new data to store, when new IP addresses are discovered. Depending on the application, having no guaranteed maximum memory requirements can be a problem.

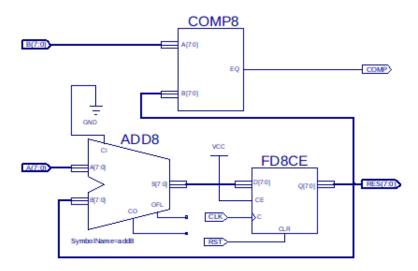

This is why data storage often is a challenge for network monitoring applications. This is especially true when available memory is constrained, as we will see it is the case on some hardware-accelerated network monitoring platforms. This challenge will arise when trying to count packets by IP address for an attack detector in Section 3.2.2. It will also arise when trying to keep data about flows for a traffic classifier in Section 4.4.2.

#### 1.4.2 Test conditions

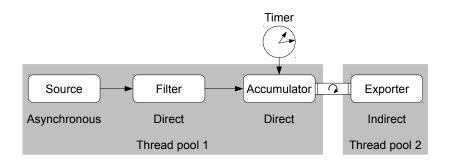

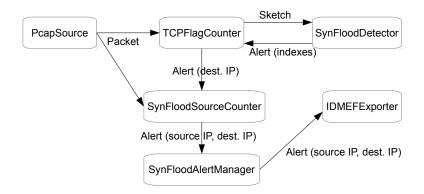

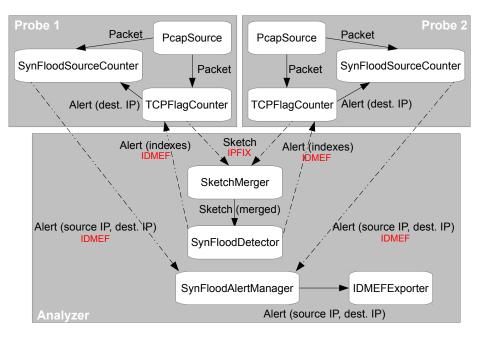

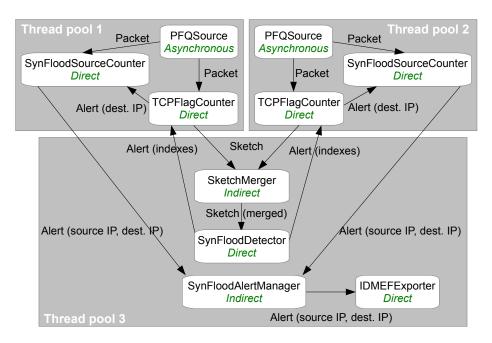

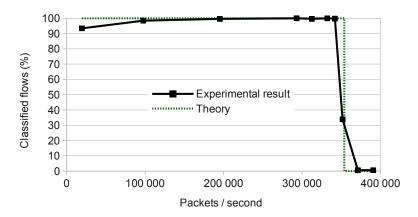

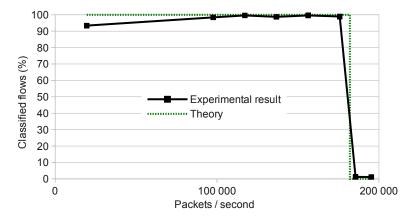

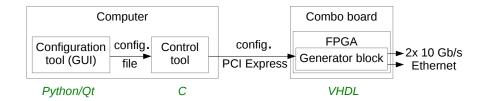

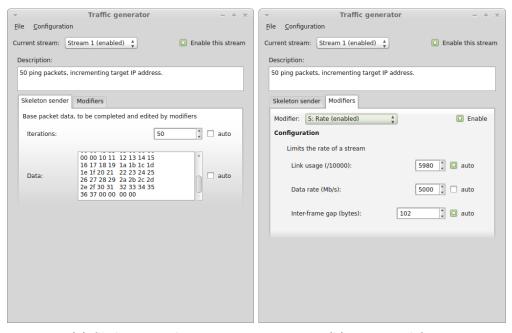

Once implemented, traffic monitoring applications have to be tested to validate their performance in terms of accuracy and in terms of supported data rate.