# Runtime mapping of dynamic dataflow applications on heterogeneous multiprocessor platforms

Dinh Thanh Ngo

## ► To cite this version:

Dinh Thanh Ngo. Runtime mapping of dynamic dataflow applications on heterogeneous multiprocessor platforms. Image Processing [eess.IV]. Université de Bretagne Sud, 2015. English. NNT: 2015LORIS371. tel-01167316v2

# HAL Id: tel-01167316 https://hal.science/tel-01167316v2

Submitted on 6 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE / UNIVERSITÉ DE BRETAGNE SUD

sous le sceau de l'Université Européenne de Bretagne

Pour obtenir le titre de DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE SUD Mention : ST/C École Doctorale SICMA <sup>présentée par</sup> Thanh Dinh NGO

Préparée à l'Unité Mixte de Recherche n° 6285 Lab-STICC Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance

UFR Sciences et Sciences de l'Ingénieur

Runtime mapping of dynamic dataflow applications on heterogeneous multiprocessor platforms Thèse soutenue le 19 Juin 2015, devant la commission d'examen composée de :

Pr. Jean-François NEZAN

Pr. Sébastien PILLEMENT Professeur, Université de Nantes, IETR Lab / Rapporteur

Dr. Samy MEFTALI

Maître de Conférences, HDR, Université des Sciences et Technologies de Lille / Rapporteur

Professeur, Institut National des Sciences Appliquées de Rennes / Examinateur **Pr. Emmanuel CASSEAU** Professeur, Université de Rennes 1, Lannion / Examinateur

DR. Jean-Philippe DIGUET Directeur de thèse / Directeur de recherche CNRS

Dr. Kevin MARTIN Co-directeur de thèse / Maître de conférences

#### Résumé

La complexité et le nombre toujours plus grandissant des applications, notamment les standards vidéo, nécessite d'étudier des méthodes et outils pour leur déploiement sur des architectures elles aussi toujours plus complexes. En effet, afin d'atteindre les performances requises en matière de temps d'exécution ou consommation énergétique, les architectures modernes proposent des éléments de calculs hétérogènes, où chacun est spécialisé pour une fonction précise. Cette thèse s'appuie sur le modèle flot de données pour la spécification de l'application. Ce modèle permet d'exposer explicitement le parallélisme spatial et temporel de l'application à travers un réseau d'acteurs interconnectés par des canaux de type FIFO. Les acteurs, en charge du calcul, peuvent exhiber un comportement statique ou dynamique. Les derniers standards vidéo contraignent à s'appuyer sur les modèles dynamiques pour obtenir une spécification fonctionnelle. Les besoins de calcul sont alors dépendants des données à traiter. Le déploiement d'une application dynamique ne peut donc se faire à l'aide des approches statiques existantes dans la littérature. L'objectif de cette thèse est de proposer des algorithmes efficaces permettant de déployer à la volée une application flot de données dynamique sur une architecture multiprocesseurs hétérogène. La première contribution est un algorithme qui permet de trouver rapidement une solution de déploiement de l'application. La deuxième contribution est un algorithme basé sur les mouvements pour adapter en cours d'exécution le déploiement, en réponse aux aspects dynamiques de l'application.

#### Abstract

Modern multimedia applications are subject to an increasing complexity with widespread standards. This has led to the interest in dataflow approach that offers a powerful perspective on parallel computations at high level. In the meantime, the emergence of massively parallel architectures has revealed the trend towards heterogeneous Multi-Processor System-on-Chips (MPSoCs) to offer a better performance and energy tradeoff than their homogeneous counterparts. However, this also imposes challenges to the mapping of multimedia applications on such complex architectures.

This thesis presents an adaptive methodology for mapping dataflow applications on heterogeneous MPSoCs. This thesis focuses on video decoders specified in RVC-CAL language, a dedicated dataflow language for video applications. Existing static approaches cannot capture all behaviors in dynamic dataflow applications. Thus, this requires to adapt the mapping according to the input data. The algorithm offers some adaptive parameters combined with our analytical communication model to improve a performance while considering load balancing. We evaluate our algorithms on a set of randomly generated benchmarks and real video decoders like MPEG4-SP and HEVC. Experimental results reveal that our mapping methodology is fast enough (in milliseconds) and the runtime remapping significantly improves the initial mapping. In the remapping process, we take the migration cost into account because the reconfiguration time also contributes to the overall performance.

n d'ordre : 00000000 **Université de Bretagne Sud** Centre de Recherche Christiaan Huygens - Rue de Saint-Maudé - 56100 Lorient, FRANCE Tél : + 33(0)2 97 87 45 62 Fax : + 33(0)2 97 87 45 27

Runtime mapping of dynamic dataflow applications on heterogeneous multiprocessor platforms Thanh Dinh Ngo 2015

# Contents

| 1        | Intr            | oductio  | n 1                                                                                                         |

|----------|-----------------|----------|-------------------------------------------------------------------------------------------------------------|

|          | 1.1             | Evolutio | on and trends in parallel systems                                                                           |

|          |                 | 1.1.1    | In General Purpose Domain                                                                                   |

|          |                 | 1.1.2    | In Embedded Domain                                                                                          |

|          |                 | 1.1.3    | Embedded parallel platforms    4                                                                            |

|          |                 |          | 1.1.3.1 Homogeneous versus heterogeneous platform 4                                                         |

|          |                 |          | 1.1.3.2 Memory architectures in MPSoCs 6                                                                    |

|          |                 | 1.1.4    | Embedded system design                                                                                      |

|          | 1.2             |          | w approach                                                                                                  |

|          |                 |          | Dataflow models of computation                                                                              |

|          |                 |          | 1.2.1.1 Kahn process networks                                                                               |

|          |                 |          | 1.2.1.2 Dataflow process networks                                                                           |

|          |                 |          | 1.2.1.3 Synchronous dataflow                                                                                |

|          |                 |          | 1.2.1.4 Cyclo-static dataflow                                                                               |

|          |                 |          | 1.2.1.5 Quasi-static dataflow                                                                               |

|          |                 | 1.2.2    | Taxonomy of Dataflow models of Computation 14                                                               |

|          |                 |          | Existing tools used in this thesis                                                                          |

|          |                 |          | 1.2.3.1 Open RVC-CAL Compiler: Orcc                                                                         |

|          |                 |          | 1.2.3.2 SDF For Free: $SDF^3$                                                                               |

|          |                 |          | 1.2.3.3 System-Level Architecture Model: S-LAM 16                                                           |

|          |                 | 1.2.4    | Case studies - RVC-CAL applications                                                                         |

|          | 1.3             |          | g problem                                                                                                   |

|          |                 |          | Problem definition                                                                                          |

|          |                 |          | Challenges in mapping problem                                                                               |

|          | 1.4             |          | ntributions $\ldots \ldots 20$ |

|          | 1.5             |          |                                                                                                             |

|          |                 |          |                                                                                                             |

| <b>2</b> | Maj             | pping M  | lethodologies of Dataflow Applications on Parallel Ar-                                                      |

|          | $\mathbf{chit}$ | ectures  | 23                                                                                                          |

|          | 2.1             |          | w Programming Models                                                                                        |

|          |                 | 2.1.1    | Embedded dataflow models                                                                                    |

|          |                 |          | 2.1.1.1 Static dataflow models                                                                              |

|          |                 |          | 2.1.1.2 Dynamic dataflow models                                                                             |

|          |                 | 2.1.2    | Dataflow tools for RVC                                                                                      |

|          |                 |          | 2.1.2.1 OpenDF                                                                                              |

|          |                 |          | 2.1.2.2 Orcc                                                                                                |

|          | 2.2             | Embedo   | led parallel architectures                                                                                  |

|          | 2.3             |          | g Methodologies                                                                                             |

|          |                 |          | Static mapping                                                                                              |

|   |     | 2.3.2<br>2.3.3 |             | tic mapping to dynamic mapping                   | 31<br>32<br>32<br>34<br>37 |

|---|-----|----------------|-------------|--------------------------------------------------|----------------------------|

|   | 2.4 | Conclu         | usion       |                                                  | 37                         |

| 3 | Con | nmuni          | cation M    | odel Based Embedded Mapping                      | 41                         |

|   | 3.1 |                | em definiti |                                                  | 42                         |

|   |     | 3.1.1          | Applicat    | ion model                                        | 42                         |

|   |     | 3.1.2          |             | ture model                                       | 43                         |

|   |     | 3.1.3          |             | nication model                                   | 43                         |

|   | 3.2 | Heuris         |             | ng algorithm                                     | 45                         |

|   |     | 3.2.1          |             | on metrics                                       | 45                         |

|   |     | 3.2.2          |             | Algorithm                                        | 47                         |

|   |     |                | 3.2.2.1     | Initialization phase                             | 47                         |

|   |     |                | 3.2.2.2     | Computation phase                                | 47                         |

|   |     |                | 3.2.2.3     | Communication phase                              | 49                         |

|   | 3.3 | Exper          | imental re  | sults                                            | 50                         |

|   |     | 3.3.1          | Simulatio   | on on Cadence virtual system platform - VSP      | 50                         |

|   |     | 3.3.2          |             | - Graph partitioning for heterogeneous multipro- |                            |

|   |     |                | cessor ar   | chitectures                                      | 51                         |

|   |     | 3.3.3          | Results v   | with SDF benchmarks                              | 51                         |

|   |     | 3.3.4          | Results v   | with real video applications                     | 52                         |

|   |     |                | 3.3.4.1     | The need of run-time mapping                     | 55                         |

|   |     |                | 3.3.4.2     | MPEG4-SP and HEVC decoder                        | 56                         |

|   | 3.4 | Conclu         | usion       |                                                  | 57                         |

| 4 | Mo  | ve Bas         | ed Algor    | ithm                                             | 59                         |

|   |     |                | em definiti |                                                  | 60                         |

|   |     | 4.1.1          | Applicat    | ion model                                        | 60                         |

|   |     | 4.1.2          |             | ture model                                       | 61                         |

|   |     | 4.1.3          |             | nication model                                   | 62                         |

|   | 4.2 | Move           |             | pping algorithm                                  | 63                         |

|   |     | 4.2.1          | -           | ers and evaluation metrics                       | 63                         |

|   |     | 4.2.2          |             | essing - PP                                      | 65                         |

|   |     | 4.2.3          |             | mapping initialization - RMI                     | 66                         |

|   |     |                | 4.2.3.1     | Algorithm principle                              | 66                         |

|   |     |                | 4.2.3.2     | Computation phase                                | 68                         |

|   |     |                | 4.2.3.3     | Communication phase                              | 68                         |

|   |     |                |             | -                                                |                            |

|          |       | 4.2.4  | Runtime remapping - RR                               | 69 |

|----------|-------|--------|------------------------------------------------------|----|

|          |       |        | 4.2.4.1 Finding the possible moves                   | 69 |

|          |       |        | 4.2.4.2 Trade-off between migration cost and perfor- |    |

|          |       |        | mance improvement                                    | 70 |

|          |       | 4.2.5  | Runtime scenario based simulation - RSS              | 72 |

|          | 4.3   | Experi | mental results                                       | 73 |

|          |       | 4.3.1  | Setup environment                                    | 73 |

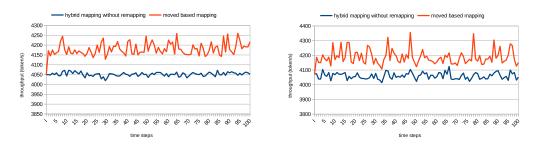

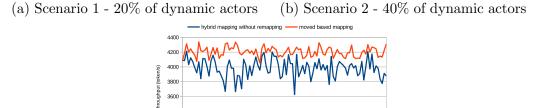

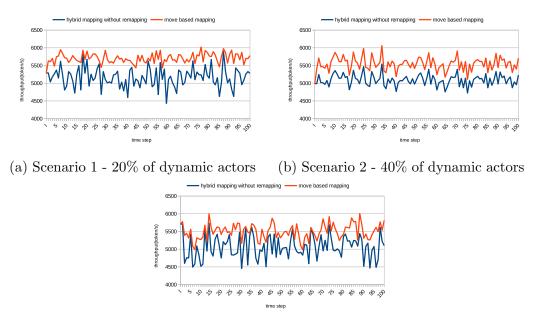

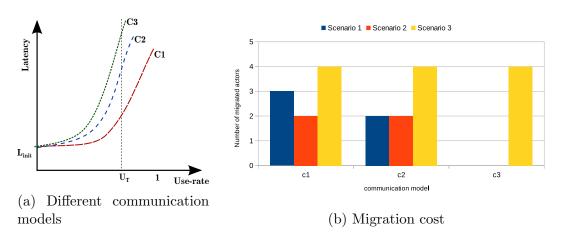

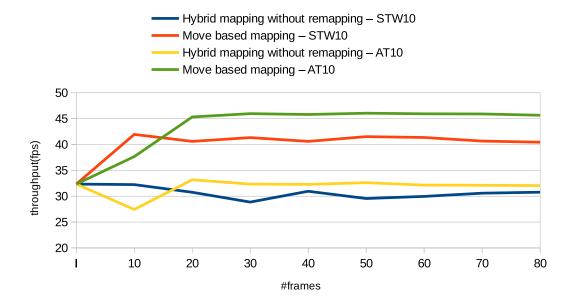

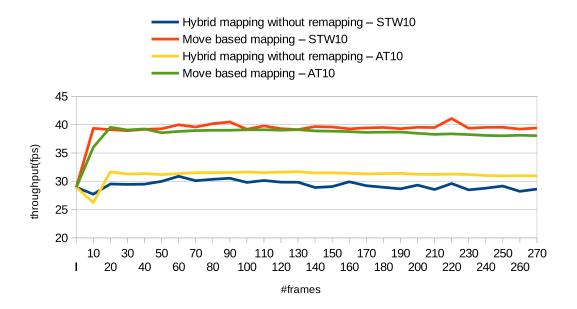

|          |       | 4.3.2  | The need of runtime remapping                        | 74 |

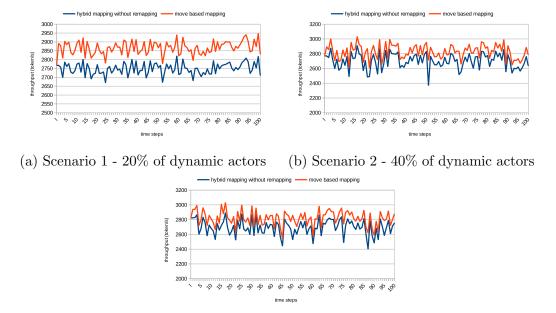

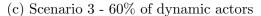

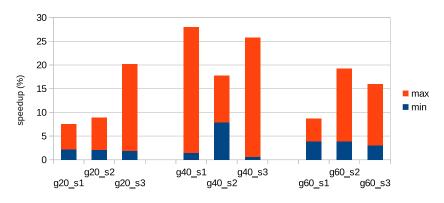

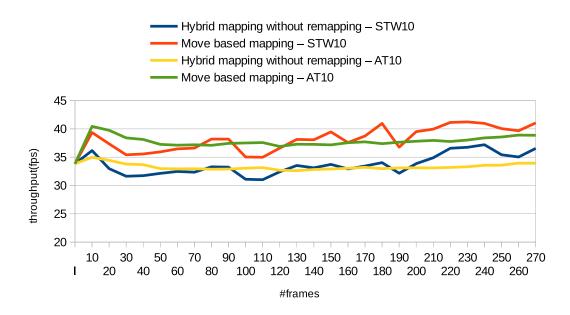

|          |       | 4.3.3  | Generated application graphs                         | 75 |

|          |       | 4.3.4  | Impact of migration cost at runtime                  | 79 |

|          |       | 4.3.5  | Real application graphs                              | 79 |

|          | 4.4   | Conclu | nsion                                                | 83 |

| <b>5</b> | Con   | clusio | 1                                                    | 85 |

|          | 5.1   | Conclu | nsion                                                | 85 |

|          | 5.2   | Perspe | ectives                                              | 87 |

|          |       | 5.2.1  | Short term                                           | 87 |

|          |       | 5.2.2  | Long term                                            | 88 |

| Bi       | bliog | graphy |                                                      | 88 |

\_\_\_\_\_

# Introduction

In modern embedded systems, the complexity of systems is rapidly increasing in hardware as well as software by the way of exploring parallelism and power saving. Indeed, embedded devices evolve towards heterogeneous Multi-Processor System-on-Chips (MPSoCs) that include more and more functional heterogeneous components on a single chip to satisfy the high performance and energy efficiency requirement of the embedded market. In the meantime the embedded software keeps growing exponentially to solve more difficult technical problems. The emergence of massively parallel architecture, along with the necessity of new parallel programming models, has revived the interest on dataflow models thanks to its ability to express parallelism. In consequence, the need to develop innovative methodologies and tools for mapping application specification onto such architecture platforms is also growing in current and upcoming embedded systems. As a design point of view, this process is necessary to bridge the gap between hardware efficiency and software flexibility while respecting time-to-market.

# 1.1 Evolution and trends in parallel systems

### 1.1.1 In General Purpose Domain

In desktop computing and high performance computing (HPC), researches are characterized by the assumption of homogeneous architectures and the goal of reducing the application makespan that is the total length of the schedule of an application. Current parallel programs typically depend on multi-threading, in which the application is expressed as a set of parallel tasks. Programming models are classified according to the way tasks or processes interact, as shared memory (e.g., Pthreads [1] or OpenMP [2]) and distributed memory (e.g., Message Passing Interface MPI [3]).

Pthreads, or Portable Operating System Interface (POSIX) Threads, are built on the top of sequential languages like C by providing libraries. Although Pthreads has its place in specialized situations, and in the hands of expert programmers, the unstructured nature of Pthreads constructs makes difficult the development of correct and maintainable programs [4]. In OpenMP, the use of threads is highly structured compared with Pthreads. The characteristics of OpenMP allow for a high abstraction level, making it well suited for developing HPC applications in shared memory systems.

As opposed to Pthreads and OpenMP, MPI was designed for distributed memory architectures. Over the last two decades, MPI has become the dominant HPC standard approach.

Since the trend in architecture design moved toward to heterogeneous architectures, programming models were developed to apply for heterogeneous architectures. In this area, two well-known programming models are Open Computing Language (OpenCL) [5] and Nvidia's Compute Unified Device Architecture (CUDA) [6].

In summary, all of the above mentioned programming models won in specific general purpose parallel domain. However, they are difficult to use in deeply embedded systems because of multi-thread safeness and runtime overhead when implementing them on modern embedded architectures.

#### 1.1.2 In Embedded Domain

Today, embedded systems are everywhere and much more widespread than other computing systems with billions sold every year [7]. As can be seen in Table 1.1, Gartner predicts that the traditional PC market will follow the downward trend but sales of mobile phones are expected to reach 2 billion units in 2015. Gartner also estimates that smartphone sales will represent 88 percent of global mobile phone sales by 2018, up from 66 percent in 2014.

Table 1.1: Worldwide device shipments by segment (thousands of units)-Source: Gartner 6-2014 [8]

| Device type                               | 2013            | 2014            | 2015            |

|-------------------------------------------|-----------------|-----------------|-----------------|

| Traditional PCs (Desk-Based and Notebook) | $296,\!131$     | 276,221         | $261,\!657$     |

| Ultramobiles, Premium                     | $21,\!517$      | $32,\!251$      | 55,032          |

| PC Market Total                           | 317,648         | 308,472         | 316,689         |

| Tablets                                   | 206,807         | $256,\!308$     | 320,964         |

| Mobile Phones                             | $1,\!806,\!964$ | $1,\!862,\!766$ | $1,\!946,\!456$ |

| Other Ultramobiles (Hybrid and Clamshell) | 2,981           | $5,\!381$       | $7,\!645$       |

| Total                                     | $2,\!334,\!400$ | $2,\!432,\!927$ | 2,591,753       |

Recent reports have shown a significant drop in sales of desktop computers

while they are significantly increasing in smartphones, tablets and other embedded devices. The increasing usage of embedded systems also brings major challenges for designers. These challenges are quantifiable goals in embedded systems: real-time performance, restricted resources, power dissipation and market cost. Especially in multimedia embedded system, these systems process streams of data, data being e.g. audio, all kinds of sensing data, videos and graphics.

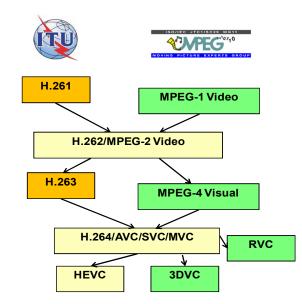

High-performance multimedia applications, such as video codecs, are becoming increasingly dynamic and complex. Fig. 1.1 illustrates the evolution of video compression standards in the past 20 years. The latest generation video codec is High-Efficiency Video Coding (HEVC), which can support 8K Ultra High Definition video, with a picture size up to 8192x4320 pixels.

Figure 1.1: Evolution of video compression standards [9]

In the meantime, because of the attractive use of dataflow programming for the development of complex signal processing systems, various dataflow model of computations (MoCs) have been proposed and studied by academia and industries. The key characteristic of MoC is that it offers a powerful perspective on parallel computations at high level. In consequence, dataflow is gaining renewed popularity. Both academia and industry use dataflow as a programming paradigm, not only for performance analysis but also for design optimization. They can be classified in terms of static models, e.g. Synchronous Dataflow (SDF), Boolean Dataflow (BDF), Cyclo-Static Dataflow (CSDF) ..., and dynamic models, e.g. Scenario Aware Dataflow (SADF), Kahn Process Networks (KPN), Dataflow Process Networks (DPN).

At the target architecture level, heterogeneous Multi-Processor System on

Chip (MPSoC) architectures are becoming emerging platforms for developing modern multimedia embedded systems because they are capable of providing better performance and energy trade-offs than their homogeneous counterparts.

However, they also bring some challenges concerning the mapping of multimedia applications on such a complex system. This requires to develop efficient mapping methodologies that can handle the increasing complexity both in applications and architectures. Moreover, it also requires highly flexible and re-usable design processes to deal with an exponential evolution in multimedia embedded systems.

#### 1.1.3 Embedded parallel platforms

#### 1.1.3.1 Homogeneous versus heterogeneous platform

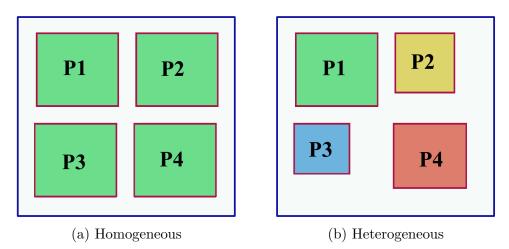

MPSoCs are becoming a popular solution for multimedia embedded systems thanks to the advantages in parallelism and flexibility. MPSoCs can be divided into two categories: homogeneous and heterogeneous MPSoCs.

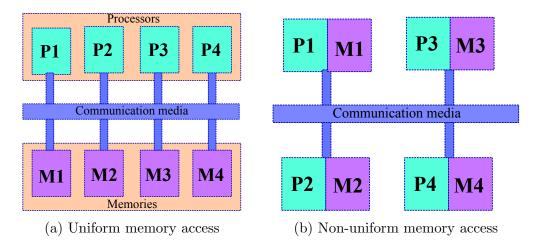

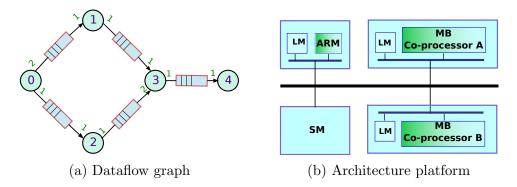

Figure 1.2: Multiprocessor architecture platform

- Homogeneous platforms are composed of the same processor type, e.g. Fig. 1.2a.

- Heterogeneous platforms are composed of different types of processors, e.g. Fig. 1.2b.

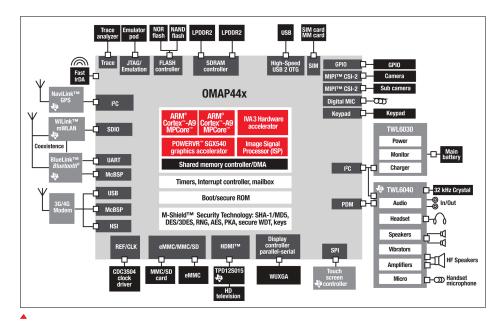

As an example of heterogeneous platform, Fig. 1.3 shows the overall structure of the OMAP 4 platform. This architecture was designed to drive smartphones, tablets and other multimedia-rich mobile devices.

Figure 1.3: A OMAP44x system diagram

An important question that arises when designing an embedded system is whether a homogeneous or heterogeneous MPSoC should be used. Amdahl's law [10] is used to find the maximum expected improvement to an overall system when only part of the system is improved. The modern version of Amdahl's law states that if you enhance a fraction f of a computation by a speedup S, the overall speedup is:

$$Speedup_{enhanced}(f,S) = \frac{1}{(1-f) + \frac{f}{S}}$$

(1.1)

To complement this law in the multicore era, the authors in [11] offer a corollary of a simple model of multicore hardware resources. For homogeneous multiprocessors with n resources, suppose we can use the resources of r base-cores (BCs) to build one bigger core/processor, which gives a performance (relative to 1 base-core) of perf(r). If a resources for n base cores BCs are available on a chip, and all BCs are replaced with n/r bigger cores, the overall speedup is:

$$Speedup_{homo}(f,n,S) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f.r}{perf(r).n}}$$

(1.2)

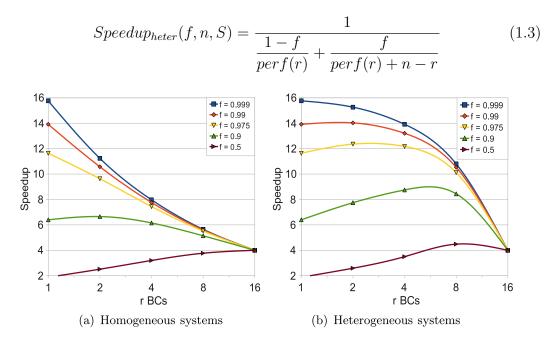

For heterogeneous multiprocessors, there are more possibilities to redistribute the resources on a chip. If only r BCs are available with 1 bigger core, the overall speedup is:

Figure 1.4: Comparison of speedup obtained by combining r smaller cores into a bigger core in homogeneous and heterogeneous systems [11, 12]

Figure 1.4 shows the speedup obtained for both homogeneous and heterogeneous systems, for different fractions of parallelizable software. This figure assumes  $perf(f) = \sqrt{r}$ . The x-axis shows the number of base cores that are combined into one larger core. In total there are resources for 16 BCs. The end-point for the x-axis is when all available resources are replaced with one big core. As can be seen, the corresponding speedup when using a heterogeneous system is much greater than homogeneous system. We also obtained similar performance speedups for other bigger chips, i.e. larger than 16 BCs. This demonstrates that a heterogeneous platform can offer better speedup than a homogeneous platform.

#### 1.1.3.2 Memory architectures in MPSoCs

The memory architecture of multi-core platforms impacts directly the programming of processors. Therefore, the programming of shared memory platforms and distributed memory platforms is usually very different.

Shared memory architectures are usually classified based upon memory access times [13], as follow:

• Uniform Memory Access (UMA): In this architecture, all the processors share the physical memory uniformly, as shown in Fig. 1.5a, which means that all the processors have an equal access and access times to memory.

• Non-Uniform Memory Access (NUMA): All processors do not have equal access time to all memories. In other words, the memory access time varies with the memory location relative to the processor. Fig. 1.5b shows an example of NUMA architecture. In NUMA, when a processor accesses a remote memory, memory local to another processor or memory shared between processors, the access time is slower than it does from its own local memory.

Figure 1.5: Shared memory architectures

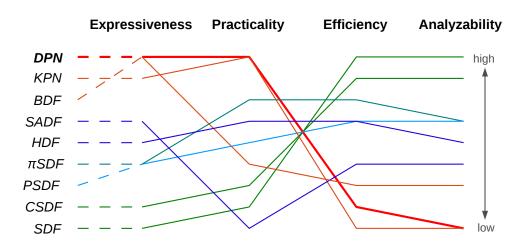

Distributed memory systems, Fig. 1.6, require a communication network to connect inter-processor memory. Each processor has its own local memory and operates independently. When a processor needs to access to data from another processor, it is usually the task of a programmer to define how and when data is communicated by means of message passing techniques.

#### 1.1.4 Embedded system design

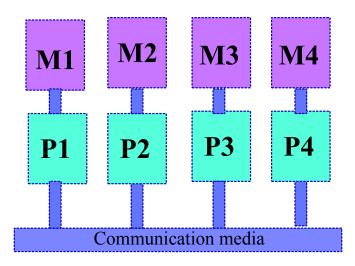

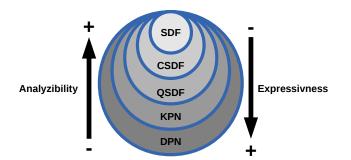

As previously mentioned in Subsection 1.1.2, dataflow MoCs are widely used in multimedia domain. In order to select one of such dataflow models, a designer should take into account the trade-off among different criteria. Fig. 1.7 shows the comparison of different dataflow MoCs based on several criteria such as expressiveness, practicality, efficiency and analyzability. Acording to [14], DPN is the most suitable model for modern multimedia applications, which become increasingly complex and dynamic.

Traditional design methodology focused a single application approach, which means that an application is mapped on a set of architectures. Usually, the designers must rewrite their source code not only to optimize performance but also to

Figure 1.6: Distributed memory architecture

Figure 1.7: Comparison of dataflow MoCs, extending the classification system introduced by Stuijk et al. [15], which shows that DPN is the most suitable model for a practical programming language [14]

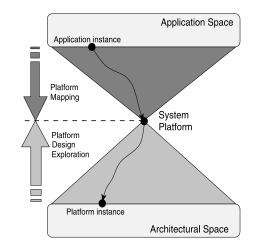

adapt these descriptions to an appropriate architecture platform. In other words, the monolithic approach of the reference software required complete rewrites of the code for new standards and failed to take advantage of the overlap in functionality. To improve the re-use and time-to-market, platform-based design methodology [16, 17] is being employed. The platform-based design methodology, as illustrated in Fig. 1.8, no longer maps a single application to an architecture that is optimal for this single application. Instead, it maps an application onto a hardware/software platform that can also be used for different applications from the same application space. The platform is defined as a family of architectures so that the application designer considers it as a common/generic platform, an essential feature to achieve re-usability.

Figure 1.8: Platform-based design approach [16, 17, 12]

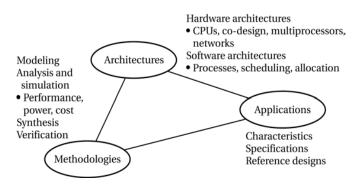

At a design point of view, the designers of embedded systems should take into account three aspects of the field: architectures, applications and methodologies as presented in Fig. 1.9.

An embedded system designer has to consider hardware as well as software design and how to tradeoff between the two. On one hand, the designer exploits all architecture components including processor architecture, memory organization, interconnection network and so on. On the other hand, the software architectures determine how we can take advantage of parallelism to improve performances. Moreover, the designer have to deeply understand about characteristics of their applications to optimize the design. The methodologies consist of modeling, analysis, simulation, synthesis and verification, which play an important role for successful embedded system design.

To handle the raising complexity in multimedia embedded system, models have been used to provide high-level of abstractions. Analysis and simulation tools are necessary to evaluate the efficiency and the design cost. Synthesis tools

Figure 1.9: Aspects of embedded design [7]

are responsible to transform high-level specifications into optimized implementations. During the embedded design process, verification is required to ensure that the system is reliability.

# 1.2 Dataflow approach

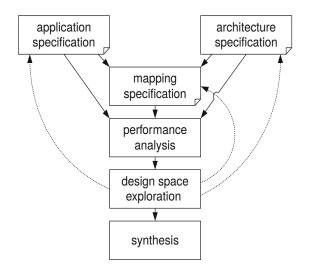

Our methodology relies on the Y-chart approach for multimedia embedded system design which is first proposed by Kienhuis et al. [18]. It is a systematic design flow for design space exploration (DSE).

Figure 1.10: Y-chart approach for designing MPSoC [18, 19]

The key idea underlying this approach is to explicitly separate the specifications as shown in Fig. 1.10. This allows to use modular system-level specifications to facilitate rapid system modifications concerning the application, architecture and mapping.

#### **1.2.1** Dataflow models of computation

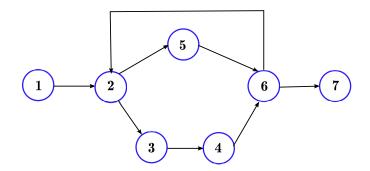

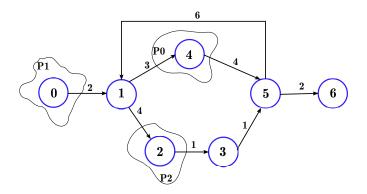

Current trends in multimedia applications use dataflow model of computations (MoCs) to define the behaviors of a program described as a dataflow graph.

Figure 1.11: Dataflow graph with 7 actors and 8 FIFO channels

A dataflow graph is a directed graph as shown in Fig. 1.11 whose vertices are actors and edges are unidirectional FIFO channels with unbounded capacity, connected between ports of actors. Fig. 1.12 illustrates a network of actors which can interact by exchanging data (called tokens) through channels. Each actor has its input and output ports. During a process (also referred as firing an action), the actor consumes input tokens, produces output tokens and changes its internal state.

Figure 1.12: A network of actors [20]

Various dataflow MoCs were studied due to their attraction in signal processing domain.

#### 1.2.1.1 Kahn process networks

Kahn process network (KPN) [21] is represented as a graph G=(V,E) such as V is a set of vertices that are called processes and E is a set of unidirectional

edges representing unbounded communication channels based on First In First Out (FIFO) principles.

In KPN, writing to the FIFO channels are non-blocking, i.e. a write returns immediately while reading to the FIFO channels are blocking. This means that when a process attempts to read data from an empty input FIFO channel, it must wait until the buffer has enough tokens to satisfy the read.

Each FIFO channel can carry an infinite sequence denoted  $X=[x_1, x_2, \ldots]$ , where each  $x_i$  is an atomic data object called a token. If the sequence X is a prefix odering of sequence Y, we can express as  $X \sqsubseteq Y$ , e.g. Given  $X=[x_1, x_2]$ and  $Y=[x_1, x_2, x_3]$  so we have  $X \sqsubseteq Y$ . The empty sequence is denoted  $\bot$ , and is obviously a prefix of any other sequence.  $S^p$  is the set of p-tuples of sequences on the p FIFO channels. This means that  $X=[x_1, x_2, \ldots, x_p] \in S^p$  represents the sequence consumed/produced by a process. The length of a sequence is given by |X|. When an actor is fired, its firing function F that consumes sequences of tokens on p input ports and produces sequences of tokens on q output ports defined as:

$$F: S^p \to S^q \tag{1.4}$$

#### 1.2.1.2 Dataflow process networks

Dataflow process network (DPN) model [22] is closely related to KPN model. DPN allows to model any algorithm even non-deterministic ones. In this model, an application is represented as a directed graph G=(V,E) where V is a set of vertices that is called actors and E is a set of edges that represent FIFO channels. DPN adds expressiveness to the KPN model by allowing actors to test an input port either absence or presence of data. This avoids process suspension and resumption incurred in most implementations of KPN. Thus scheduling a DPN does not require context-switching nor concurrent processes. In DPN model, an actor executes (or fires) when at least one of its firing rules is satisfied. In case several firing rules are satisfied at the same time, a single one is chosen based on priority and its corresponding firing function is executed. Each firing rules:

$$R = [R_1, R_2, \dots, R_N]$$

(1.5)

A firing rule  $R_i$  is a finite sequence of patterns, one for each of the p input ports of the actor:

$$R_i = [R_{i,1}, R_{i,2}, \dots, R_{i,p}] \in S^p$$

(1.6)

A pattern  $R_{i,j}$  is a (finite) sequence. A firing rule i is satisfied if and only if  $R_{i,j} \subseteq X_j$ , where  $X_j$  is the sequence of unconsumed tokens at input j. For some

firing rules,  $R_{i,j}$  might be empty lists,  $R_{i,j} = \perp$ . In other words, any available sequence at input j is acceptable. Let symbol '\*' denote a token wildcard, the sequence [\*] is a prefix of any sequence with at least one token.

#### 1.2.1.3 Synchronous dataflow

Synchronous Dataflow (SDF) model is a static dataflow model, in which an actor produces or consumes a fixed number of tokens per firing. SDF graphs can be scheduled at compile-time with bounded memory.

It may have a single firing rule, which is valid for any sequence  $S^p$  of a certain size on its inputs [23]. In case an actor has several firing rules, an actor is SDF if all its firing rules have the same consumption. In particular, any two firing rules  $R_a$  and  $R_b$  of an SDF actor must satisfy:

$$|R_a| = |R_b| \tag{1.7}$$

All the firing functions of an SDF actor must also produce a fixed number of tokens on the output ports:

$$|f(s_a)| = |f(s_b)| \qquad \forall s_a \in S^p, \forall s_b \in S^p \qquad (1.8)$$

#### 1.2.1.4 Cyclo-static dataflow

The cycle-static dataflow (CSDF) [24] extends SDF actors by allowing the number of tokens produced and consumed to vary in a periodic fashion. This variation is modeled with a state in the actor, which returns to its initial value after a defined number of firings. CSDF model has all characteristics of SDF model.

#### 1.2.1.5 Quasi-static dataflow

Dataflow modeling is the question of striking the right balance between expressive power and analyzability: On the one hand, synchronous and cyclo-static dataflow limit the algorithms to be modeled as graphs with fixed production and consumption rates for their predictability and their strong properties that allow powerful optimizations to be applied. On the other hand, dynamic dataflow offers a large expressiveness, until Turing-completeness, able to describe complex algorithms with variable and data-dependent communication rate that makes their analyze and optimization ultimately harder.

Quasi-static dataflow differs from dynamic dataflow in that there are techniques that statically schedule as many operations as possible so that only datadependent operations are scheduled at runtime [25]. An alternative to model quasi-static dataflow is the Parameterized Dataflow (PSDF) [26]. In order to select one of such dataflow models, the designers need to take into account a tradeoff between expressiveness and analyzability.

#### **1.2.2** Taxonomy of Dataflow models of Computation

Dataflow MoCs are defined as subsets of the more general DPN model. Fig. 1.13 shows the taxonomy of dataflow models of computation.

SDF was first introduced by Lee and Messerschmitt in 1987 [23]. It is the least expressive DPN model but easier to analyze.

CSDF [24] extends SDF actors by allowing the number of tokens, both producer and consumer, to vary cyclically. Most of the studies in dataflow domain use static dataflow models because they are more analytical and predictable at compile-time. As a tradeoff between expressiveness and predictability, the definition of Quasi-static dataflow model QSDF was introduced [25]. Parameterized dataflow [26] is a higher-level approach to model quasi-static behavior by the extension of existing dataflow model using parameters modifiable at runtime.

KPN was proposed by Kahn in 1974 [21] as a general perpose scheme for parallel programming. DPN [22], also known as Dynamic dataflow model (DDF), is closely related to KPN. DPN is more expressive than KPN.

Figure 1.13: Dataflow Models of Computation [27]

With the increasing complex multimedia applications, the analyzabilityexpressiveness tradeoff moved towards more expressive models. In a practical point of view, DPN is well suited to model modern multimedia applications [27], by offering Turing completeness while also keeping an intuitive description.

#### **1.2.3** Existing tools used in this thesis

#### 1.2.3.1 Open RVC-CAL Compiler: Orcc

The rapid evolution in video codec standards increases the need to develop an innovating framework to overcome the lack of interoperability between the several video codecs in the market. The Moving Picture Experts Group (MPEG) has introduced the Reconfigurable Video Coding framework (RVC) [28, 29], which offers reconfiguration, reusability and platform independent dataflow models. An RVC codec is described by using a domain-specific language, called CAL Actor Language (CAL) [30]. One of ubiquitous tools based on RVC-CAL framework is Orcc [31, 32].

Orcc [31, 33, 32] is an open-source toolkit dedicated to develop RVC-CAL applications. Orcc is a complete Eclipse based Integrated Development Environment, which aims at providing a compiler infrastructure to allow software/hard-ware code to be generated from dataflow descriptions. The compiler is able to translate RVC-CAL applications into an equivalent description not only software but also hardware languages for various platforms (FPGA, DSP,GPP, etc). In consequence, there are numerous back-ends in Orcc that target different languages (C, C++, LLVM, VHDL, Verilog etc.).

Currently, Orcc is supported to generate source code with the following backends:

- The C back-end produces an application described in portable ANSI C (Windows, Linux, Mac) like Pthreads with multi-core ability. The C backend can be considered as the main backend of Orcc. In fact, this backend is used by the most part of the developers for the development of new application.

- The Java back-end generates class-based Java code that has the advantage of being used seamlessly within the Eclipse environment.

- The Jade back-end [34] produces LLVM assembly code targeted to be used by the JIT Adaptive Decoder Engine (Jade), which provides reconfigurability for software that runs as fast as the code generated by the C back-end.

- The TTA backend implements a full co-design to design a multi-softcore platform based on the Transport-Trigger Architecture and generates the software code executed on the processors using the TTA-based Co-design Environment (TCE) [35].

- The Verilog back-end generates Verilog description using the OpenForge tools.

- The Promela back-end generates Promela code that can be used with the SPIN model-checker to analyze properties of RVC-CAL applications.

Other back-ends are still developing to deal with a wide rage of modern platforms in the market. Moreover, some advanced analysis tools have developed to offer predictable behaviors for dynamic dataflow applications. For example, Orcc has a dynamic analysis tool for actor classification [36, 27] to detect predictable behavior within a network. Orcc also offers a profiling tool to gather some useful profile information such as computation workload and communication workload of an application.

#### **1.2.3.2** SDF For Free: $SDF^3$

$SDF^3$  is an open source tool [37] for generating random SDF graphs. It also offers many SDF analysis and transformation techniques as well as a function to visualize SDF graphs. The tool supports to generate different SDF graph benchmarks used in this thesis.

#### 1.2.3.3 System-Level Architecture Model: S-LAM

S-LAM [38] is developed as a part of a prototyping tool called PREESM for Parallel and Real-time Embedded Executives scheduling Method. S-LAM provides a simple description of modern architecture platforms at high level of abstraction. Its description is a topology graph defining the data exchanges in modern platform such as heterogeneous architecture.

#### **1.2.4** Case studies - RVC-CAL applications

Orcc provides a complete environment for users to exploit and develop current and future video decoders by using dynamic dataflow programming. We use the existing RVC-CAL applications such as MPEG4 Part 2 and MPEG High Efficiency Video Coding (HEVC) which are implemented in Orcc to study all dynamic behaviors of these complex dataflow applications.

MPEG4 Part 2 standard, also known as MPEG4 visual, was developed by the Moving Picture Experts Group (MPEG), a working group of the International Organization for Standardization (ISO). It was standardized in 1999 by the joint ISO/ITU (the International Telecommunication Union). It provides a highly flexible toolkit of coding techniques and resources. There is a set of coding tools, organised into 'profiles', recommended groupings of tools suitable for certain applications. Classes of profiles comprise 'simple' profiles (coding of rectangular video frames), object-based profiles (coding of arbitrary-shaped visual objects), still texture profiles (coding of still images or 'texture'), scalable profiles (coding at multiple resolutions or quality levels) and studio profiles (coding for high-quality studio applications).

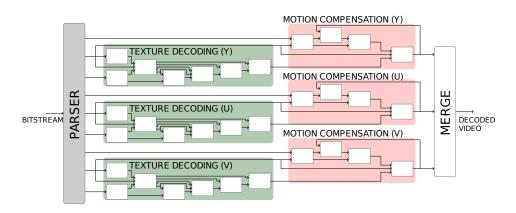

Fig. 1.14 shows RVC-based description of the MPEG4 Part 2 SP decoder. The structure of the application graph can be partitioned into three parts, each one corresponding to a dedicated processing: parsing, residual decoding and motion

Figure 1.14: MPEG4 part 2 SP decoder [39]

compensation. To increase the parallelism exposed within the decoder, the parser can separate the processing of each image components in three parallel paths (Y, U and V). At the end of the processing, the image components are then merged back.

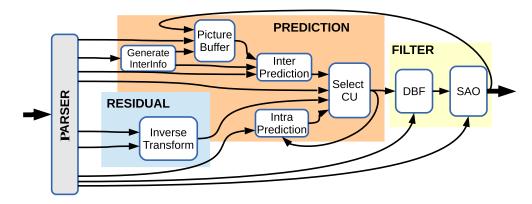

MPEGH Part 2, also known as MPEG HEVC/ H.265, is the newest video coding standard, developed conjointly by ISO/ITU. HEVC is improving the data compression rate, as well as the image quality, in order to handle modern video constraints such as the high image resolution 4K (3840 x 2160) and 8K (7680 x 4320). Another key feature of this new video coding standard is its capability for parallel processing that offers scalable performance on the trendy parallel architectures [14, 40]. The first version of the standard was completed, approved, and published in 2013. The second version was completed and approved in 2014 and published in early 2015. An implementation of the HEVC decoder using the RVC framework is presented in Fig. 1.15.

Figure 1.15: MPEG-H part 2 SP decoder [35]

Table 1.2 summarizes the properties of each description of these well-known

decoders. Their properties are the profile of the decoder, the parallelization of the decoding for each component, the number of actors and FIFO channels. The RVC-based video decoders are described with an average granularity (at block level), contrary to the traditional coarse-grain dataflow (at frame level). This finegrain streaming approach induces a high potential in pipeline parallelism and the use of small communication channels, usually between 512 and 8192 rooms [14].

| Standard      | Profile        | Version  | YUV | #Actors | #FIFOs |

|---------------|----------------|----------|-----|---------|--------|

|               | Simple Profile | RVC      | yes | 41      | 143    |

|               |                | Xilinx   | no  | 34      | 86     |

| MPEG-4 Part 2 |                | Ericsson | yes | 42      | 105    |

|               |                | EPFL     | no  | 13      | 29     |

|               |                | Irisa    | yes | 41      | 104    |

| MPEG HEVC     | Main           | RVC      | no  | 34      | 109    |

|               | Still Picture  | RVC      | no  | 31      | 74     |

Table 1.2: Statistics about the RVC-CAL description of several MPEG video decoders [14]

## 1.3 Mapping problem

#### **1.3.1** Problem definition

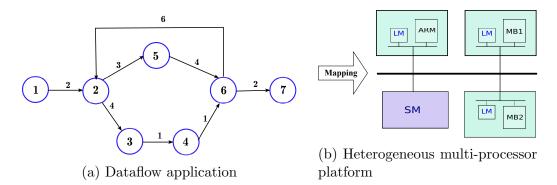

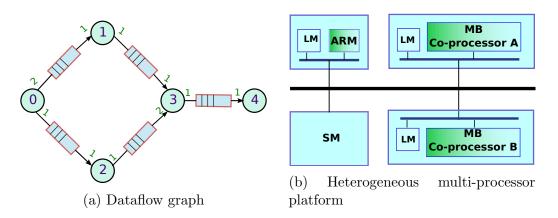

MPEG RVC defines RVC-CAL applications as dynamic dataflow applications, which are based on DPN model. An application is represented as a directed graph DPN = (V, E), where the vertex set V is a set of actors  $\mathbb{A} = [i_1, i_2, \dots, i_n]$ and the edge set E is a set of FIFO channels  $\mathbb{F} = [f_1, f_2, \dots, f_k]$ . Each FIFO channel carries a sequence of tokens  $\mathbb{X} = [x_1, x_2, \dots]$ , where each  $x_i$  is called a token. In the application, the actors may be compliant with different models of computation (MoC) and so consume and produce a fixed or variable number of tokens, additionally the execution time can be more or less variable. Fig. 1.16a shows a simple dataflow application with 7 actors and 8 FIFO channels.

A heterogeneous MPSoc is composed of different processor types  $\mathbb{P} = [P_1, P_2, \ldots, P_m]$ , storage elements and interconnect. Each processor has its local memory (LM) and communicates with other processors through several buses and shared memories (SM). In our project, we target the Zynq platform. This architecture includes two ARM processors and multiple Microblaze processors, which have different hardware accelerators and frequencies as well. Thus, we

model the target platform as  $MPSoC = (\mathbb{P}, \mathbb{CM})$ , where  $\mathbb{CM}$  is defined as a set of communication models, which are available in the platform.

Fig. 1.16b gives an example of a simple architecture platform with one ARM processor (that can run the mapping algorithm), two Microblaze (MB) with one hardware accelerator and all processors communicate through one bus and one shared memory (SM).

Figure 1.16: Dataflow application mapping on heterogeneous multi-processor platform

In this context, given a dynamic dataflow application, e.g. Fig. 1.16a, which is based on different MoCs, we assume that profiling mechanisms are available on the target platform so that we can measure at runtime the number of tokens produced and consumed by each actor as well as the execution time of actors. We then aim to map the dataflow actors onto various computation and communication resources, e.g. Fig. 1.16b, with the objective to optimize the application throughput. Finding a high-quality mapping solution for such a dynamic dataflow application on heterogeneous platform is an NP complete problem. This is why we consider the dataflow application at high-level description and propose a heuristic approach in order to produce an efficient solution in few milliseconds.

The application mapping problem has been addressed as one of the most urgent problem to be solved for implementing embedded systems [41, 42, 43].

#### 1.3.2 Challenges in mapping problem

As mentioned in the previous section, the complexity of modern multimedia systems are increasing both in applications, e.g. video codecs, and parallel architectures, e.g. heterogeneous platforms. This brings more challenges for mapping such a complex system. Therefore, it is difficult and time consuming to find an optimal solution that satisfies all performance and power constraints. Moreover, mapping problem is known as NP-hard problem [44]. This is why many studies employ heuristics based on the application domain knowledge to find a nearly optimal solution. In regard to application model, static models are restricted in the kinds of applications they can express. This also means that static mapping approaches are not suitable because they can not handle the behaviors of dynamic applications. As a result, the trend moves towards runtime/dynamic mapping techniques. Runtime mapping methodologies face the challenge to map tasks/actors of a application on MPSoC platform without advance knowledge about a dynamic changing in workload and actor migration in the platform at design time. Furthermore, runtime mapping may have some following requirements:

- A fast solution in order not to degrade the overall system performance.

- Ability to capture runtime varying workloads in the systems and runtime changing environments.

- Mapping a new task/actor into the system, which needs some information concerning available resources.

- A flexible approach, which has some adaptive parameters to deal with a wide range of applications at runtime.

- Ability to do a remapping of application, when a current mapping is not sufficiently optimal.

# **1.4 Our Contributions**

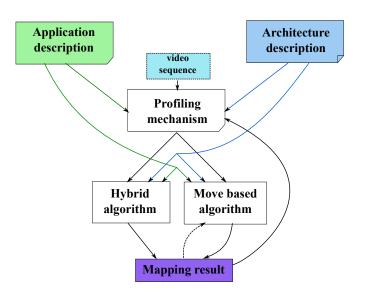

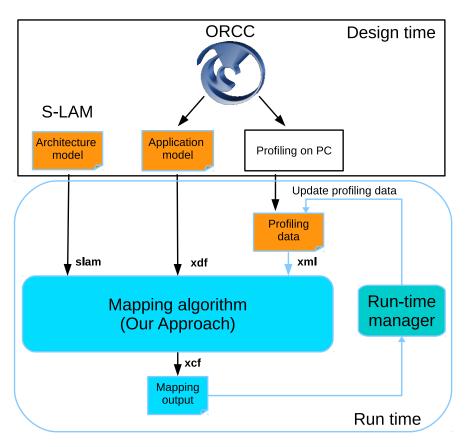

This thesis aims at providing an adaptive mapping method for dynamic dataflow applications on heterogeneous multiprocessor platform at runtime. In order to explore all issues and opportunities related to dynamic dataflow applications, we consider several video decoders which are already specified as Dataflow Process Network (DPN) in RVC-CAL framework. In this context, the objective is to maximize a system throughput when mapping RVC-CAL applications on any heterogeneous multiprocessor platform. Since DPN model is used to express dynamic behaviors of an RVC-CAL application, the mapping method can not longer be static. Thus, it requires a runtime mechanism to handle behaviors of a dynamic application. The mapping algorithm has to be fast enough to produce a decision of mapping at runtime. It should have some adaptive parameters to improve a performance and it may be able to do a remapping when a current mapping is not sufficiently optimal at online. Since the reconfiguration time also contributes to the overall performance, we should take a migration cost into account. Indeed, different mappings may incur different migration costs [45].

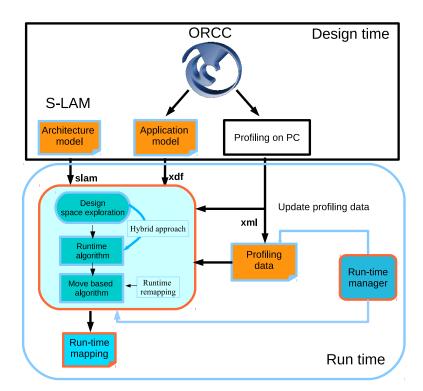

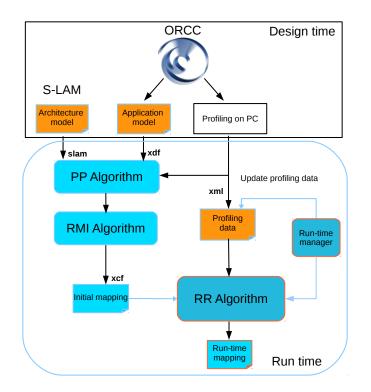

This thesis makes the following contributions as illustrated in Fig. 1.17:

- We present a novel hybrid algorithm, which takes the advantages both at design time and runtime, for mapping a dataflow application on heterogeneous multiprocessor platforms. As many studies, we also take load balancing into account. At design space exploration, we rely on the Y-chart co-design approach to make our mapping algorithm independent from application model and architecture model. By using this approach, we consider the co-design flow based on higher-level of abstractions that are necessary to deal with the growing complexity of embedded systems. Additionally, we do not need to find all mapping solutions at DSE as a reference solution for using at runtime. Instead, we propose a processing budget according to a dataflow application. This method help us to save exploration time as well as a memory for storing all mapping solutions at design time. We propose an analytical communication model for estimating the delay (latency) of the data on the communication media at runtime. This communication model is flexible since it can apply either NoC or Bus based architecture. The advantages of our algorithm are adaptability, predictability and a fast solution at runtime. This work has been published in DASIP 2014 conference [46].

- Further, we exploit dynamic behaviors of dataflow applications to demonstrate the need of doing the runtime remapping as well as illustrate the impact of migrated actor at remapping phase. We then introduce a Move Based Algorithm, namely MBA, which is compliant with Bus and NoC models takes both computation cost and communication cost while allowing remapping dataflow actors at runtime onto heterogeneous MPSoC. MBA supports the adaptivity at runtime and also takes migration cost when doing the remapping actor.

- Our mapping method can apply for mapping a dynamic dataflow application which is based on RVC-CAL framework onto any heterogeneous multiprocessor platform. This work has been submitted for review to Journal of Signal Processing Systems - Springer.

- We conduct the experiments with our runtime scenario based simulation for both randomly generated dataflow graphs and MPEG4-SP applications.

# 1.5 Outline

The remainder of this thesis is organized as follows.

• Chapter 2 reveals not only the interest in dataflow programming models but also the emergence of MPSoC platforms. We provides a wide survey

Figure 1.17: Overview of our design flow based on Y-chart approach

and classification of mapping methodologies in the literature and shows the emerging trends for multimedia embedded systems.

- Chapter 3 presents an analytical communication model. We propose a novel hybrid algorithm for mapping dataflow actors on heterogeneous MPSoC. This algorithm follows a greedy fashion to produce a fast mapping solution at runtime.

- Chapter 4 extends our approach in Chapter 3 with MBA algorithm to offer the runtime remapping.

- Chapter 5 concludes the thesis and also gives some perspectives.

2

# Mapping Methodologies of Dataflow Applications on Parallel Architectures

In this chapter, variety of dataflow programming models are first discussed in Section 2.1. As target architectures for these dataflow applications, we then introduce embedded parallel architectures in Section 2.2. In this consideration, plenty of researchers have addressed application mapping problem as one of the most urgent problem to be solved.

Since this thesis proposes a novel method for mapping dataflow actors on heterogeneous platforms, the remaining section focuses on classification of the mapping methodologies in the literature and also highlights the emerging trends in the mapping methods.

# 2.1 Dataflow Programming Models

As a rapid evolution in multimedia applications as well as architecture platforms, graphical programming models became quite popular, since they provide to algorithm designers a natural way of specifying an application. Commercial examples include MATLAB Simulink [47], National Instruments LabVIEW [48] as well as Synopsys Signal Processing Work system (SPW) [49] and System Studio [50]. Dataflow semantics are a common underpinning of most graphical programming models.

#### 2.1.1 Embedded dataflow models

Dataflow models, as introduced in Subsection 1.2.1, have achieved a dominant position in performance analysis as well as design optimization of multimedia embedded systems. Dataflow MoCs can be split into two categories: one is static models and the other one is dynamic models.

#### 2.1.1.1 Static dataflow models

There are numerous dataflow MoCs, which are known as static models. This kind of model assumes that actors have a fixed token production and consumption on each firing.

SDF is also known as Weighted Marked Graphs in Petri Net literature. Schedulability and memory consumption of SDF applications can be known at compile-time [51]. Pioneering works on SDF graphs were published by Lee et al. in [23]. Prof. Edward Lee is famous with the Ptolemy project [52]. This project studies modeling, simulation, and design of concurrent, real time, embedded systems. In this project, different kinds of dataflow models have been developed and exploited. A free tool set for generating and analyzing SDF, CSDF and socalled Scenario-Aware Dataflow (SADF) are available in the  $SDF^3$  project [37]. Diverse studies in the literature investigate SDF model in the field of multimedia applications such as [53, 54, 55, 56, 57, 58]. In [59], authors present a method for throughput analysis of SDF applications. Their approach is based on explicit state-space exploration and avoids the translation to Homogeneous SDF (HSDF) application. HSDF model is a special case of SDF model in which all token production and consumption rates are 1. In [60], authors address the problem of mapping HSDF applications on multiprocessor platform with the objective of maximizing application throughput by using Sat-based techniques. The authors in [54] propose a method to compute throughput of an SDF applications in which the execution time of actors can be parameters. To explore the parallelism with heterogeneous architectures, authors in [57] present a methodology for improving the system throughput by using SDF transformations. Many researchers [56, 60, 61, 58] consider their applications as SDF or HSDF model. This kind of models is also known as static model, which is easier to analyze and predict at design-time. Researchers in [55, 62] provide a complete approach to solve the allocation and scheduling of SDF applications on MPSoCs.

CSDF model extends SDF with the notion of state. With CSDF model, authors in [63] present a practical and accurate throughput analysis since their method can give tight estimates on the minimum throughput. A comparison between SDF and CSDF model were explored in [64]. The need for a tradeoff between expressiveness and predictability has brought the definition of so-called "quasi-static" dataflow model [26, 65, 66].

As static dataflow models are restricted in the kinds of applications they can express, these models can not express the dynamic behaviors of modern video applications. This leads to many studies of MoCs that can express the dynamic behaviors of modern multimedia applications.

#### 2.1.1.2 Dynamic dataflow models

In contrast to static model, dynamic dataflow models are able to capture the behaviors of dynamic applications. In dynamic dataflow domain, it is impossible to know production and consumption behavior of actors at compile time since each actor has a set of firing rules and can be fired if one of them is satisfied.

SADF [67] extends SDF with scenarios, which represent different modes of operation based on resource requirements. This makes it possible to capture a dynamic behavior of application to save resources. SADF improves SDF in terms of expressiveness to express dynamism. Different scenarios may differ in their execution time and communication rates. However, all scenarios are generated by a probability of occurrence and each scenario can be modeled with SDF model. Authors in [15] surveys SADF and compares different dataflow MoCs according to their expressiveness, expressiveness, analyzability and implementation efficiency.

KPN is another MoC that can be used to express behaviors of dynamic application. However, KPN requires a complex run-time mechanism that leads to a large implementation overhead [15]. Lee et al. were pioneers in a theory of dataflow process network (DPN) [22]. DPN is a special case of KPN but it can be used to model the most general form of dataflow MoCs. Therefore, recent researches employ KPN, DPN models as in [68, 69, 70, 15, 71].

Hence, with embedded multimedia becoming more complex, the trade-off between analyzability and expressiveness moved towards more expressive models.

#### 2.1.2 Dataflow tools for RVC

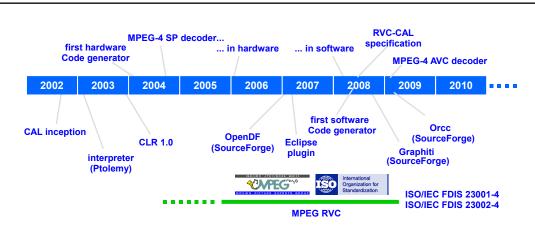

The initial work for introducing the MPEG Reconfigurable Video Coding (RVC) framework [29] started in 2004. Both academia and industries have developed a set of tools supporting RVC framework. The key characteristics of MPEG RVC are flexibility, re-usability and platform independent dataflow models. In this innovative framework, the MPEG RVC working group has adopted CAL (the Cal Actor Language) [30] as part of their standardization efforts as shown in Fig. 2.1. CAL actor language was developed at University of California at Berkeley in 2001. This language was born from Ptolemy II project [52] to modeling complex signal processing systems dedicated to software and hardware code synthesis.

#### 2.1.2.1 OpenDF

The Open Dataflow Environment (OpenDF) [72] is a dataflow toolset. OpenDF framework is composed of editing the CAL actor, some analysis tools and multi-target compiler. The compiler in OpenDF supports three back-ends to generate code for different target platforms. The first one is a back-end for generation of

26 Mapping Methodologies of Dataflow Applications on Parallel Architectures

Figure 2.1: Pictorial representation of CAL language and tools development and the timeline of the steps of MPEG RVC standardization [39]

HDL (VHDL/Verilog) [73], and the second back-end generates C code for integration with the SystemC tool chain [74]. The last one is dedicated to embedded platforms based on ARM processor [75]. As mentioned in [33], OpenDF has some technical limitations and is no longer maintained. This leads to the birth of Open RVC-CAL Compiler (Orcc) project in 2009.

#### 2.1.2.2 Orcc

As mentioned in Subsection 1.2.3, Orcc is a complete framework, which has been developed by Orcc team and widely used by academic and industrial researches. Indeed, Orcc composes of rich eclipse-based editors, integrated simulators and multi-target development tools [32]. Many synthesis tools for hardware and software co-design have been developed by Orcc communities [33, 76, 77, 78, 79, 80].

# 2.2 Embedded parallel architectures

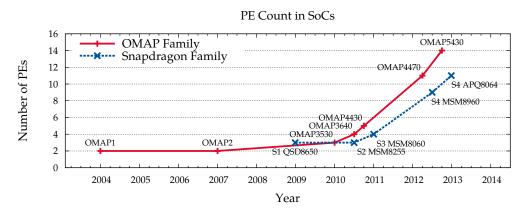

Early works ignored data communication and focused on scheduling [56, 60]. The authors target homogeneous MPSoCs with the objective of maximizing system throughput. Fig. 2.2 shows typical examples of how hardware evolution today with OMAP and Snapdragon platform families. The solid curve presents the development of OMAP family from Texas Instruments (TI) [82]. The OMAP5430, which includes ARM Cortex-A15 MPCore (with 4 cores each), two ARM Cortex-M4, a graphic processor (PowerVR), a C64x DSP, an Image Video Audio accelerator (IVA) and an image signal processor, contains 14 processing elements (PEs). We can observe the similar trend with Snapdragon family from Qualcomm [83], the dash curve in Fig. 2.2.

Figure 2.2: SoC Trends: Processing elements in TI OMAP Processors and Qualcomm Snapdragon Processors [81]

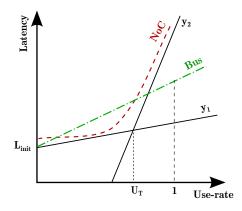

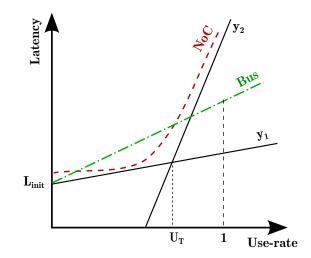

As the current trend towards to a heterogeneous platform for high performance and energy efficiency, heterogeneous architectures with many different communication standards including hardware support are available. *Therefore, the role of communication during application synthesis can no longer be ignored.* Indeed, the latency increases with the number of processors connected to it [84]. In [70, 71], communication is modeled by annotating latencies on the edges of the application graph. Other authors treat communication mapping in the context of single inter-processor communication (IPC) [58] which does not correspond to the situation in today's MPSoCs. In [58], additional actors, namely send and receive, are bound on the buses in addition to original computation actors that are bound on processors. The approach relies on an ILP formulation. Our goal is to embed the application to be typically executed by an ARM processor and there is not yet any ILP solver for this kind of embedded processor.

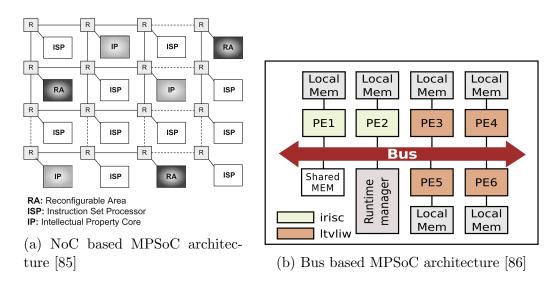

For such a complex platform, we need to estimate the delay for data to be transmitted that increases with the traffic. This is typically observed in NoC [87], where the latency increases with the injection rate. For the sake of clarity, we will use the term latency to denote the time taken by one data to travel on the bus. In [88], the authors investigate the performance of mapping algorithms in NoC based heterogeneous MPSoCs with the objective of NoC congestion minimization. They employ the Minimum Maximum Channel Load (MM), the Minimum Average Channel Load (MA) and the Best Neighbor (BN) to reduce the occupancy of the NoC channels and also the execution time of the heuristics. Thereafter, the authors in [85] present a number of communication-aware runtime task mapping heuristics on NoC based MPSoCs. They extend MPSoC architecture used in [88] to support more than one task for each processing node. Their NoC based MPSoC architecture, as shown in Fig. 2.3a, contains a set of different nodes such as Instruction Set Processor (ISP), Reconfigurable Area (RA) and Intellec-

Figure 2.3: Example of NoC and Bus based MPSoC architecture

tual Property Core (IP). They interact via a communication network with 2D mesh topology. The communication network uses wormhole packet switching, handshake control flow, input buffer and deterministic XY routing algorithm. Recently, many works consider NoC as a communication scheme [89, 61, 68, 90]. Their communication models are limited to NoC and very basic since they are a number of hops, which do not correspond to flexibility communication media in heterogeneous MPSoCs.

In [86], authors propose communication primitives, which can capture the variety of IPC software interfaces in today's MPSoCs. They target the Densely Connected Platform (DCP) in Fig. 2.3b in which PEs can communicate by various means like TI's Keystone [91]. The PEs irisc and ltvliw are in-house cycle accurate models developed with Synopsys Processor Designer [92]. The bus in the DCP is a transaction accurate model of an AMBA AHB bus. For the bus and the memories, models from the Synopsys IP library [93] are used. The runtime manager in Figure 2.3b controls the execution of processes on the different PEs. However, this kind of model only applies for bus based architectures with and without pipelined communication.

# 2.3 Mapping Methodologies

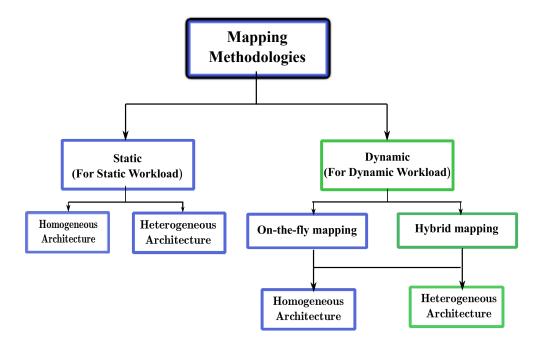

The application mapping problem, which has been identified as one of the most urgent problem to be solved for implementing embedded systems [41, 42, 43], is a NP-hard problem [44]. There are different criteria to classify the mapping methodologies such as optimization goal, target architecture, workload, etc. Fig.

2.4 shows a taxonomy of mapping methodologies based on workload scenarios. In general, there are two kinds of workload, either static or dynamic. For static workload, the mapping method can perform optimization at design time. However, for dynamic workload, the variations in terms of workload occur at runtime. This leads to classify as static and dynamic/runtime methodologies respectively. Both methodologies target either homogeneous or heterogeneous multiprocessor architectures. The type of platform can be fixed platform or generic platform. When the mapping methodology considers a fixed platform, this means that the mapping method depends on a specific platform. In case the mapping methodology applies for generic platform, it can work with a wide range of platform platform. Examples of generic heterogeneous architectures are the Texas Instruments OMAP platforms [82] or Zynq platforms [94], which contain a mixture of dedicated programmable cores, various hardware accelerators, different kinds of interconnects and memory architectures.

Figure 2.4: A Taxonomy of Mapping Methodologies, Extending the Classification in the Survey Introduced by [43]

#### 2.3.1 Static mapping

Static mapping strategies are an off-line mapping which has global view of the system at design time. These methods can explore more thoroughly system information to achieve optimal mapping solutions. They are suitable for static

| Ref. | MoC                   | Platform   | Optimization Goal        |

|------|-----------------------|------------|--------------------------|

| [56] | SDF                   | Fixed-HO   | Memory, Throughput       |

| [60] | HSDF                  | Fixed-HO   | Throughput               |

| [54] | SDF                   | N/A        | Throughput               |

| [63] | $\operatorname{CSDF}$ | Fixed-HE   | Accurate Throughput      |

| [62] | SDF                   | Fixed-HE   | Throughput               |

| [57] | SDF                   | Generic-HE | Throughput               |

| [55] | SDF                   | Fixed-HO   | Solving time, Throughput |

| [59] | SDF                   | N/A        | Throughput               |

| [95] | N/A                   | Fixed-HO   | Execution time           |

| [96] | N/A                   | Fixed-HO   | Execution time           |

| [53] | SDF                   | Fixed-HE   | Resource allocation      |

| [97] | SDF                   | Fixed-HO   | Efficient synthesis      |

|      |                       |            |                          |

Table 2.1: Classification of static mapping methodologies

workload applications and fixed platforms as well. Most of the mapping methodologies reported in the literature are static mapping techniques [98]. Table 2.1 reveals different static approaches for static applications, based on different static models such as SDF, CSDF, in different manners and optimization goals as well. The methodologies target homogeneous (HO.) or heterogeneous (HE.) multi-core platforms. There are numerous optimization goals, e.g. throughput, execution time, solving time, resource allocation, energy consumption ..., from different studies in the state of the arts [43]. As throughput is one of the most important metrics in the domain of multimedia to evaluate the system performance, authors in [59] present a method for throughput analysis of SDF graphs. In [53], authors propose a resource allocation for SDF graphs, which benefits from throughput analysis in [59]. By using cyclo static dataflow model (CSDF), authors [63] give a tight estimate on the minimum throughput for an application mapped on a multiprocessor system.

Various strategies have been reported to solve the static mapping problem. For example, Genetic Algorithm (GA) is used in [57], Simulated Annealing (SA) in [95], branch-and-bound and SAT solving in [60] and Integer Linear Programming (ILP) in [96]. Authors in [57] use GA algorithm to maximizing throughput of SDF application on a heterogeneous platform. The results indicate that their approach outperforms than other techniques such as Flextream [99] with replication heuristic and optimal ILP mapping. The disadvantages of this method are high computational cost and a large buffer sizes for an application implementation. With SA algorithm in [95], authors solve the task mapping problem based on simultaneous optimization of execution time and memory consumption. Their SA algorithm starts with an initial solution in which all task graph nodes are mapped to a single processing element and then iterates through various mapping candidates to find a better solution. Authors in [96] propose an ILP formulation for task mapping and scheduling problem to reduce system execution time. These approaches provide efficient and optimal mapping solutions that can be used as reference but they take a lot of time for searching solution of large scale problems such as applications with large number of tasks mapped on a platform with a lot of processors. Some approaches improve computational cost by other search based mapping strategies. Authors in [60] address the mapping problem of HSDF graph onto a multiprocessor platform with the objective of maximizing system throughput. They combine both branch-and-bound and SAT-solving to explore the design space of all possible actor-to-processor mappings. Their integrated approach reduces the solving time compared with Logic Based Benders Decomposition approach [100] significantly. In [55], authors propose a complete algorithm based on Constraint Programming to solve the allocation and scheduling problem of SDF graph onto a multi-core platform. Their objective is minimum throughput requirement while reducing the solving time of the algorithm.

Broadly, static approaches have interesting results in terms of performance. Moreover, they show lack of flexibility: all the parameters of the dataflow application need to be known and fixed at design time. If the applications or platforms change, then re-computation is necessary. Further, they are unable to handle dynamic behaviors of dynamic dataflow applications. Even if these mapping methodologies are not suitable for runtime varying workloads, they can be considered as a reference solution or initial mapping at runtime.

#### 2.3.2 From static mapping to dynamic mapping

Authors in [101] present an iterative probabilistic analysis to accurately predict the performance of multi-application mapped on a multiprocessor platform. They measure that the runtime complexity of their algorithm is only 300  $\mu$ s with ten applications on a 500 MHz processor. Nonetheless, they consider SDF graph applications in context of multi-application, the dynamic behavior is only the variation of execution time of applications. In [102, 15], the authors express the dynamic behavior of an application by describing several static scenarios. Consequently, the programmer has to predict all possible scenarios and describe them in a static way. Schor et al. [68] present a whole scenario-based design flow for mapping streaming application modeled by KPN onto on-chip many-core system. In [58], authors address multi-objective mapping problem of SDF graphs onto heterogeneous multiprocessor platforms based on a combination of an evolutionary algorithm with an ILP. They obtain up to 12x runtime efficiency compared to the global ILP without compromising throughput optimality. However, the runtime complexity of their algorithm significantly increases with the number of actors in a SDF graph application. Our goal is to embed the application to be typically executed by an ARM processor and there is not yet any ILP solver for this kind of embedded processor.

Authors in [61] propose a method, as shown in Fig. 2.6 for efficient mapping of throughput constrained applications on MPSoC platforms. Their method outperforms the time required (in milliseconds) to map throughput constrained multimedia applications on a 4x4 MPSoC platform. In application model, they still consider multimedia applications as SDF model.

These approaches employ static dataflow model like SDF to exploit the dynamic behaviors of the system. In other words, they do not use the dynamic models to explore the dynamic behaviors of a system directly.

#### 2.3.3 Dynamic mapping

In contrast to the static mapping, dynamic mapping is an online mapping method. Hence, it can handle dynamic behaviors of workloads at runtime. With dynamic dataflow applications, we can not know dynamic behaviors such as computation time, communication time of each task and runtime changing environments at design time. In dynamic mapping, the time taken to map each task is important since it contributes to overall application execution time. Some evolution algorithms (GA, SA ...) and ILP methods are not acceptable for runtime mapping in embedded systems since they have high computational costs with large scale problems as mentioned above. Therefore, some heuristic methods like greedy fashion are used to trade-off between efficient mapping and mapping overhead.

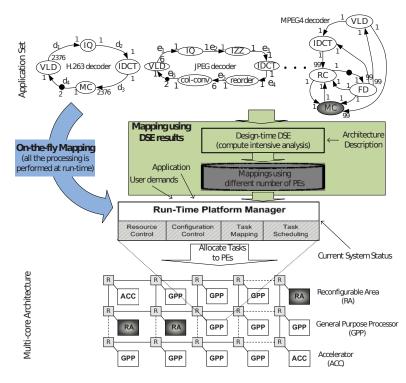

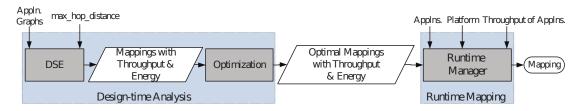

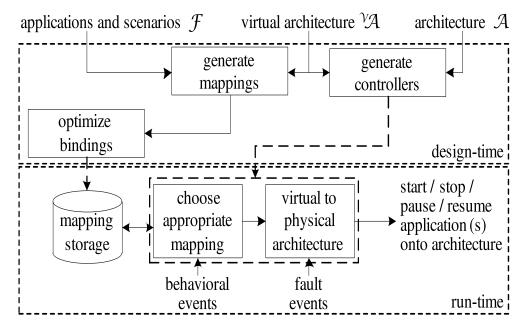

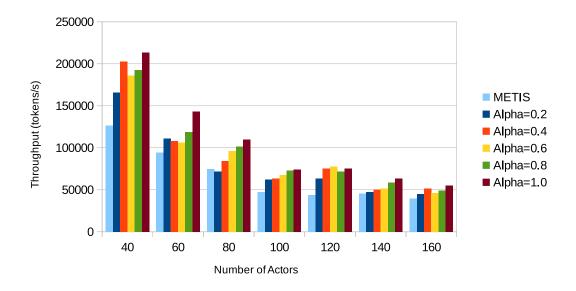

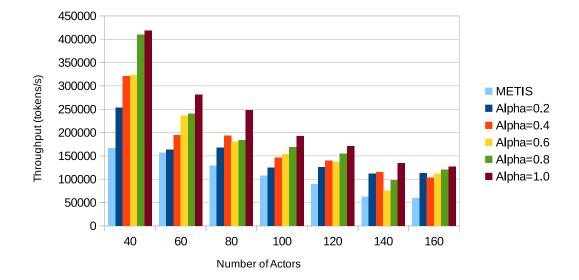

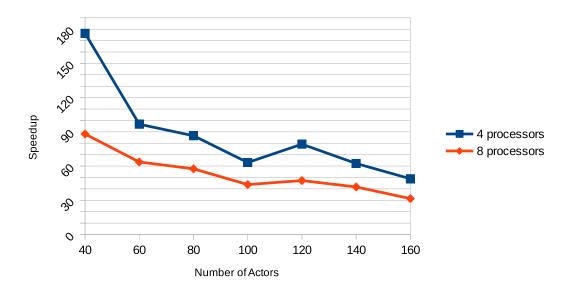

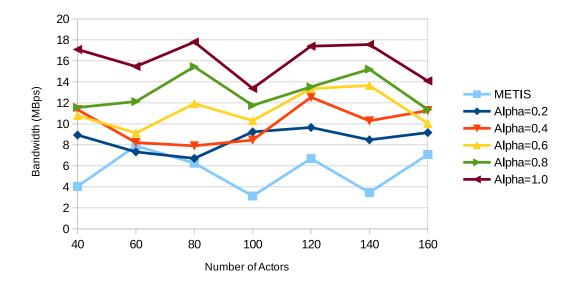

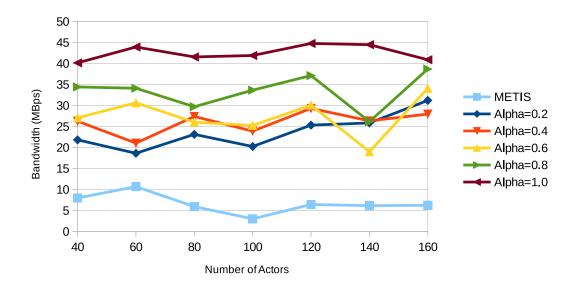

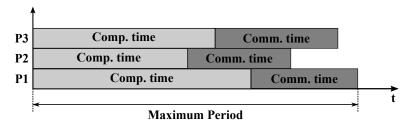

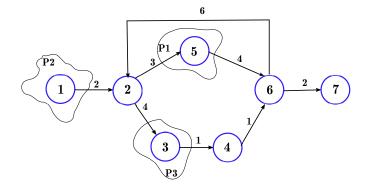

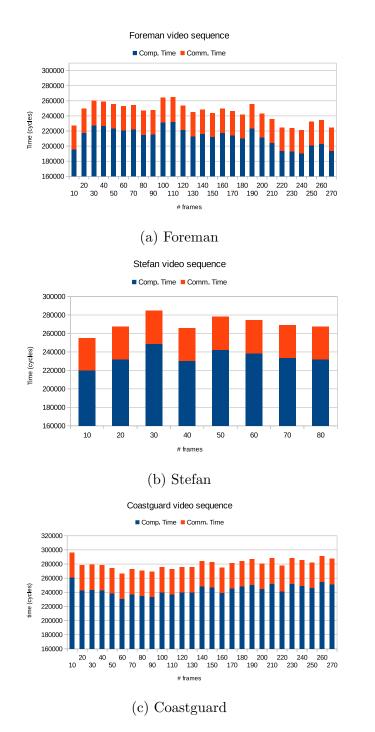

The dynamic mapping methodologies reported in the literature can be divided into three kinds of approaches, namely on-the-fly, hybrid and hybrid with runtime remapping (Hybrid+R).