### Efficient design and programming of Multiple Processors System on Chip architectures

Romain Brillu

### ▶ To cite this version:

Romain Brillu. Efficient design and programming of Multiple Processors System on Chip architectures. Engineering Sciences [physics]. UNIVERSITE DE NANTES, 2014. English. NNT: . tel-01104791

### HAL Id: tel-01104791 https://hal.science/tel-01104791

Submitted on 19 Jan 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse de Doctorat

### Romain BRILLU

Mémoire présenté en vue de l'obtention du grade de Docteur de l'Université de Nantes Sous le label de l'Université Nantes Angers Le Mans

Discipline: Electronique

Spécialité : Systèmes Embarqués Laboratoire: IETR UMR 6164

Soutenue le 12 novembre 2014

École doctorale Sciences et Technologies de l'Information et Mathématiques (STIM)

Efficient design and programming of Multiple Processors System on Chip architectures

#### **JURY**

Président M. Alain DARTE, CNRS Research Director, Laboratoire de l'Informatique du Parallélisme, Lyon

Rapporteur M. Frédéric PÉTROT, Professor, École Nationale Supérieure d'Informatique et de Mathématiques Appliquées de Grenoble Rapporteur M. Gilles SASSATELLI, CNRS Research Director, Laboratoire d'Informatique de Robotique et de Microélectronique de Montpellier

Examinateur M. Jürgen TEICH, Professor, Friedrich-Alexander-Universität Erlangen-Nürnberg, Deutschland

Directeur de Thèse M. Sébastien PILLEMENT, Professor, École polytechnique de l'université de Nantes

Co-Directeur M. Fabrice LEMONNIER, Research Engineer/HDR, Thales Research & Technology, Palaiseau

**Encadrant** M. Philippe MILLET, Research Engineer, Thales Research & Technology, Palaiseau

### Remerciements

Ah les remerciements, dernière étape dans la rédaction de cette thèse qui peut paraître simple mais qui n'en est rien, bien au contraire car résumer en quelques lignes tout ce que vous m'avez apporté au cours de ces trois années est difficile et le plus dur pour moi reste l'impair d'oublier quelqu'un. Si tel est le cas que ces personnes me pardonnent.

Je souhaite avant tout remercier l'ensemble des membres de mon jury, Monsieur Alain Darte pour avoir accepté d'en être le président, Messieurs Frédéric Pétrot et Gilles Sassatelli pour avoir accepté d'en être les rapporteurs et Monsieur Jürgen Teich pour avoir accepté d'en être l'examinateur.

Ensuite comment ne pas citer mon directeur de thèse Sébastien Pillement sans qui cette thèse n'aurait pas été à son terme. Merci pour le soutien, la confiance apportée et pour m'avoir aidé à développer et à formaliser mes idées afin que je puisse mener à bien cette thèse. Comme tu me l'a si bien dit au début de cette aventure "La recherche est avant tout un échange" et ce fût un véritable plaisir d'échanger avec toi tout au long de ces trois années aussi bien professionnellement que personnellement.

Je remercie également mon co-directeur de thèse Fabrice Lemonnier pour m'avoir permis de faire cette thèse et m'avoir accordé une grande confiance et liberté dans le développement et la réalisation de cette dernière.

Un clin d'oeil à Frédéric Falzon pour notre collaboration et à mon encadrant Philippe Millet pour les conseils apportés au cours de ce doctorat.

Merci au Spearou, Michel, Rémi, Paul et Teodora pour leur sympathie, la patience, le temps qu'ils m'ont accordés et pour avoir été présents pour moi dès que j'avais un problème ou des questions.

Ces remerciements ne seraient pas complets si je ne remercie pas ici Christophe pour l'ensemble des connaissances qu'il m'a transmises, le temps et la confiance qu'il m'a accordé et pour la patience qu'il a eu mon égard. Sache que venir à Thales sans nos échanges forts poétiques que ce soit dans les transports ou au bureau n'avaient plus la même saveur.

Au rayon des poètes comment ne pas penser à Lionel pour sa gentillesse, sa disponibilité, sa bonne humeur et son sens inné de la dédramatisation. Merci pour l'aide que tu a pu m'apporter aux différentes étapes de cette thèse et pour les moments partagés.

Je remercie aussi Hai le Zidane vietnamien pour cette année commune passée à Lannion, pour ces parties de baby-foot engagées (Mais tu es quand même particulièrement mauvais) et pour tous les fou rires que nous avons eu. Au plaisir de te revoir dans la magnifique capitale de la Bretagne qu'est Rennes. Cette dernière phrase est particulièrement destinée aux Nantais, je préfère préciser au cas où ils n'auraient pas compris ce qui n'aurait rien d'étonnant.

Vu qu'on parle des Nantais je remercie l'ensemble des membres de l'IETR Nantes. J'ouvre néanmoins ici un aparté destiné aux Nantais récalcitrant à voir la vérité en face (Ils se reconnaîtront) pour leur signaler que le R de IETR signifie Rennes. Ce qui démontre ce qui ne devrait plus être à démontrer la supériorité manifeste de la capitale Bretonne sur sa voisine Française et leur incohérence à vivement critiquer cette magnifique ville et ses clubs sportifs.

Maintenant que ce point à été clarifié je remercie particulièrement au sein de l'IETR la team café pour l'ensemble des bons moments partagés et des conseils plus ou moins pertinents distillés si et là. Distinction particulière à Loïc et Yann pour leurs recettes culinaires. En effet la recette du gâteau cramé sur le dessus et pas cuit au centre et la recette du gâteau cuit que sur les extrémités m'étaient inconnu avant leur rencontre.

Je remercie aussi tous les membres de la team billard pour m'avoir permis de croire que j'étais bon à ce jeu. Merci particulier à Guillaume pour cette victoire écrasante que nous avons connu au tournoi.

Merci à la team football pour l'ensemble des matchs disputés même si cela m'a valu quelques courbatures et une blessure à une cuisse. Les matchs Chine contre le reste du monde vont me manquer.

Je remercie aussi le Justin Bieber indien Chagun pour ces trois années de thèse partagées. Merci pour ta zenitude (qui peut quand même être stressante par moment), ta bonne humeur et ta joie de vivre. Je te remercie moins pour m'avoir arraché quelques larmes en me faisant découvrir la cuisine indienne.

Un grand merci a Joëlle et Sandrine pour leur bonne humeur et disponibilité, vous m'avez simplifié la vie et permis de me concentrer pleinement sur mes travaux.

Afin de n'oublier personne je remercie Philippe Bonnot, Olivier Sentieys, Jean-François Diouris et l'ensemble de leurs équipes pour m'avoir accueilli au sein du laboratoire des systèmes embarqués de Thales Research & Technology, du laboratoire de l'IRISA de Lannion et du laboratoire de l'IETR de Nantes.

En tant que fervent supporter du plus grand club de l'ouest je ne peux que remercier le Stade Rennais FC pour la sublime défaite infligée aux Nantais le dimanche 23 février 2014 qui m'a apporté courage et inspiration dans la phase de rédaction. J'ai une attention particulière pour Ola, Anders et Paul-Georges et leurs trois magnifiques buts plantés en ce beau dimanche après-midi.

Comme le dit si bien le dicton il faut garder les meilleurs pour la fin et donc ma famille pour avoir été toujours derrière moi.

Merci à ma mamie Marie pour s'etre occupé de moi lors de mes jeunes années.

Je remercie challeureusement ma mamie Émile pour avoir veillé sur moi depuis que je suis tout petit et pour m'avoir soutenue jusqu'au bout dans cette thèse alors que ta santé ne te le permettait pas. Je te confirme aussi que j'avais bien besoin d'un doctorat pour faire les fameux "roulé boulé".

Merci à ma filleule et nièce Gaëlla pour avoir su me détendre et me faire rire que ce soit par des tours en LEGO, des dessins, des sorties en vélo, des balades aux parc ou des chants.

Merci à mes soeurs Hélène et Élise pour m'avoir permis chacune à leur manière d'en être là aujourd'hui, pour tous les souvenirs et moments partagées et pour avoir toujours été à mes cotés que ce soit dans les bons ou les mauvais moments.

Un grand merci à ma femme Aurélie pour avoir faire preuve d'une grande patience à mon égard, su me soutenir dans les moments difficiles, m'avoir remonté le moral, fait rire et avoir fait en sorte que je garde le sourire tout au long de cette thèse.

J'adresse une très grande reconnaissance et un très grand merci a mes parents Michel et Paulette. Énumérer la liste de tout ce vous avez fait pour moi en quelques lignes est impossible donc merci pour tout. Si j'en suis là aujourd'hui c'est avant tout grâce à vous et ce doctorat est aussi le votre.

Pour finir je remercie avec émotion "le grand" à qui j'avais promis avant qu'il nous quitte de mener à bien ce doctorat et dont la mémoire m'a permis de surmonter bien des difficultés aux cours de ces trois années.

# **Contents**

| Ré | ésumé | en français                                       | i  |

|----|-------|---------------------------------------------------|----|

|    |       | Contexte et motivations                           | i  |

| 1  | Intr  | oduction                                          | 1  |

|    | 1.1   | Context and motivations                           | 2  |

|    |       | 1.1.1 Problem statement                           | 2  |

|    |       | 1.1.2 Contributions                               | 9  |

|    | 1.2   | Manuscript organization                           | 10 |

| 2  | State | e of the art                                      | 11 |

|    | 2.1   | Introduction                                      | 12 |

|    | 2.2   | MPSoC architectures                               | 12 |

|    |       | <b>2.2.1</b> Introduction                         | 12 |

|    |       | 2.2.2 Single task processor                       | 13 |

|    |       | 2.2.2.1 Symmetric multiprocessors                 | 13 |

|    |       | 2.2.2.2 Asymmetric multiprocessors                | 18 |

|    |       | 2.2.3 Multiple tasks processor                    | 21 |

|    |       | 2.2.4 Summary                                     | 23 |

|    | 2.3   | Design space exploration tool flow                | 25 |

|    |       | 2.3.1 Introduction                                | 25 |

|    |       | 2.3.2 System level framework                      | 26 |

|    |       | 2.3.3 Micro-architectural framework               | 30 |

|    |       | 2.3.4 HLS framework                               | 33 |

|    |       | 2.3.5 Summary                                     | 35 |

|    | 2.4   | Summary                                           | 36 |

| 3  | Pars  | simonious architecture solution space exploration | 37 |

|    | 3.1   | Introduction                                      | 38 |

|    | 3.2   | Definitions                                       | 38 |

|    |       | 3.2.1 Application model                           | 38 |

|    |       | 3.2.2 Task model                                  | 39 |

|    |       | 3.2.3 Architecture model                          | 40 |

|    |       | 3.2.4 Nomenclature                                | 41 |

|    | 3.3   | DSE methodology                                   | 12 |

|    |       | •                                                 | 12 |

|    |       | 3.3.2 Methodology description                     | 14 |

|    |       |                                                   | 14 |

10 CONTENTS

|      |        | 3.3.2.2           | Code parallelization                            | 45 |

|------|--------|-------------------|-------------------------------------------------|----|

|      |        | 3.3.2.3           | Profiler                                        | 46 |

|      |        | 3.3.2.4           | Parsimonious representation                     | 46 |

|      |        | 3.3.2.5           | PARSE                                           | 47 |

|      |        | 3.3.2.6           | SystemC simulation                              | 49 |

|      |        | 3.3.2.7           | Binary and HDL code generation                  | 49 |

| 3.4  | Manni  |                   | ation                                           | 50 |

| 3.4  | 3.4.1  | <u> </u>          | tion                                            | 50 |

|      | 3.4.2  |                   | rch                                             | 51 |

|      | 3.4.2  | 3.4.2.1           | Presentation                                    | 51 |

|      |        | 3.4.2.1           |                                                 | 52 |

|      |        |                   | Neighborhood generation                         |    |

|      |        | 3.4.2.3           | Diversification operator                        | 53 |

|      |        | 3.4.2.4           | Metrics                                         | 53 |

|      |        | 3.4.2.5           | Analytic performance                            | 55 |

|      |        | 3.4.2.6           | Cost function                                   | 56 |

|      | 3.4.3  | •                 | ental results                                   | 57 |

|      |        | 3.4.3.1           | Experimentations parameters                     | 58 |

|      | 3.4.4  | Results           |                                                 | 59 |

|      |        | 3.4.4.1           | Communication cost                              | 59 |

|      |        | 3.4.4.2           | Exploration runtime                             | 63 |

| 3.5  | Data p | lacement e        | exploration                                     | 64 |

|      | 3.5.1  | Introduct         | tion                                            | 64 |

|      | 3.5.2  | Genetic a         | algorithm with fusion operator                  | 65 |

|      |        | 3.5.2.1           | Presentation                                    | 65 |

|      |        | 3.5.2.2           | Chromosome encoding                             | 66 |

|      |        | 3.5.2.3           | Fusion operator                                 | 67 |

|      | 3.5.3  |                   | entation                                        | 68 |

|      | 3.3.3  | 3.5.3.1           | Experimentations parameters                     | 69 |

|      | 3.5.4  | Results           |                                                 | 70 |

|      | 3.3.4  | 3.5.4.1           | Memory and communication cost                   | 70 |

|      |        | 3.5.4.2           | Fusion operator cost                            | 71 |

|      |        | 3.5.4.2           | *                                               | 72 |

| 26   | TCDC   | -3.3.4.3<br>-GAFO | Exploration runtime                             | 73 |

| 3.6  | 10110  | 0.11              |                                                 |    |

|      | 3.6.1  |                   | entation                                        | 73 |

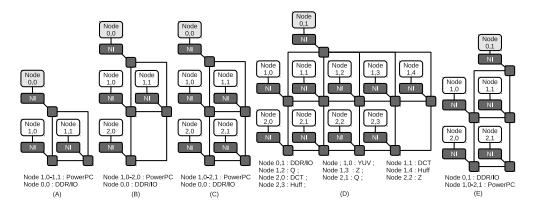

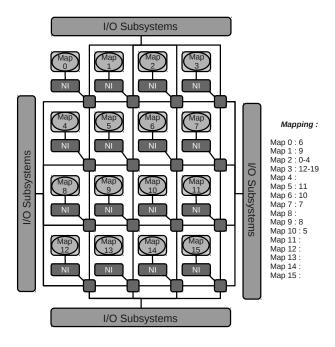

|      |        | 3.6.1.1           | Architecture models                             | 73 |

|      |        | 3.6.1.2           | Algorithm Parameters settings                   | 75 |

|      | 3.6.2  |                   |                                                 | 75 |

|      |        | 3.6.2.1           | Memory and communication cost                   | 75 |

|      |        | 3.6.2.2           | Exploration runtime                             | 76 |

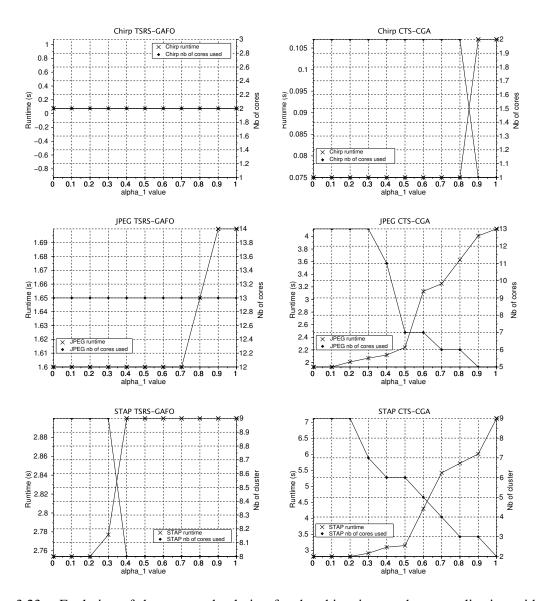

|      |        | 3.6.2.3           | Influence of the $\alpha$ parameters            | 77 |

| 3.7  | Summ   | ary               |                                                 | 79 |

|      |        |                   |                                                 |    |

| Glol |        |                   | is architecture but locally heterogeneous cores | 81 |

| 4.1  | Introd | uction            |                                                 | 82 |

| 4.2  | FlexTi | les               |                                                 | 82 |

|      | 4.2.1  | FlexTiles         | s Platform                                      | 83 |

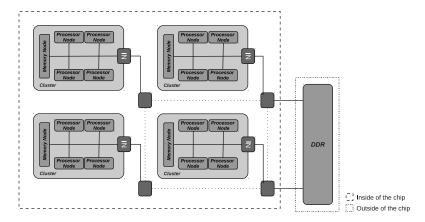

|      | 422    | MPSoC 1           |                                                 | 84 |

4

CONTENTS 11

|    |       | 4.2.3    | Reconfigurable layer                                     | 4 |

|----|-------|----------|----------------------------------------------------------|---|

|    |       | 4.2.4    | NoC                                                      | 5 |

|    |       | 4.2.5    | Programming model                                        | 5 |

|    |       | 4.2.6    | Software tools                                           | 6 |

|    | 4.3   | Accele   | rator interface                                          | 7 |

|    |       | 4.3.1    | Introduction                                             | 7 |

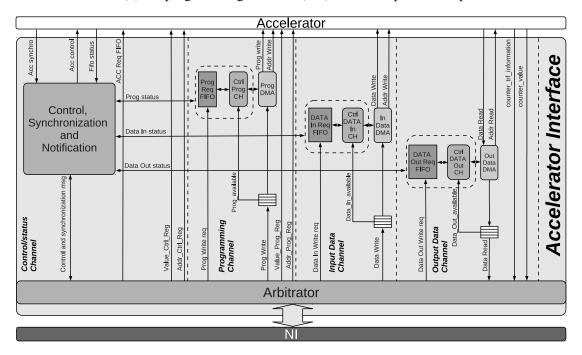

|    |       | 4.3.2    | Architecture                                             | 8 |

|    |       |          | 4.3.2.1 Arbitrator                                       | 8 |

|    |       |          | 4.3.2.2 Control/Status channel                           | 9 |

|    |       |          | 4.3.2.3 Programming channel                              | 9 |

|    |       |          | 4.3.2.4 Data Input and Output channel                    | 0 |

|    |       | 4.3.3    | Command interface                                        | 0 |

|    |       | 4.3.4    | Synchronization scheme and execution patterns            | 1 |

|    |       | 4.3.5    | Experimentation and results                              | 3 |

|    |       |          | 4.3.5.1 FlexTiles Board                                  | 3 |

|    |       |          | 4.3.5.2 Application                                      | 3 |

|    |       |          | 4.3.5.3 FlexTiles platform Implementation                | 4 |

|    |       |          | 4.3.5.4 Impact of the accelerator interface              | 5 |

|    |       |          | 4.3.5.5 Mapping test                                     |   |

|    | 4.4   | Cluster  | based architecture a memory abstraction                  |   |

|    |       | 4.4.1    | Introduction                                             |   |

|    |       | 4.4.2    | System description                                       |   |

|    |       |          | 4.4.2.1 Architecture presentation                        |   |

|    |       |          | 4.4.2.2 Cluster Architecture                             | 0 |

|    |       | 4.4.3    | Memory node                                              |   |

|    |       |          | 4.4.3.1 Partition Table                                  |   |

|    |       |          | 4.4.3.2 Address Generation Uuit                          |   |

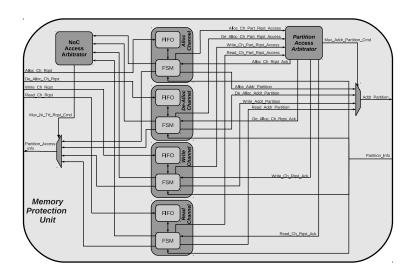

|    |       |          | 4.4.3.3 Memory Protection Unit                           |   |

|    |       | 4.4.4    | Operating Principle                                      |   |

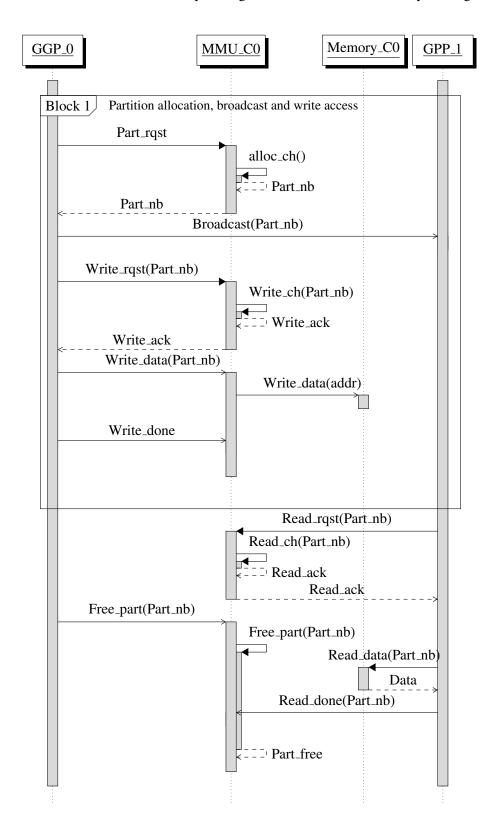

|    |       |          | 4.4.4.1 Intra cluster communication                      |   |

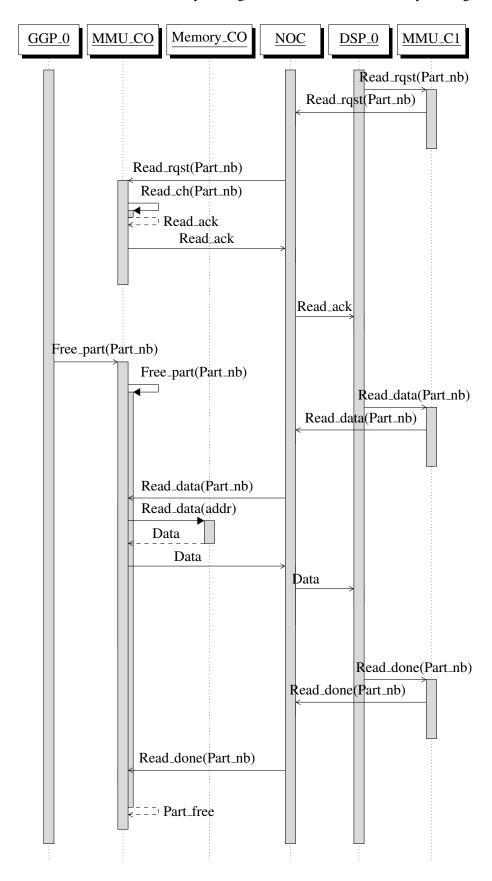

|    |       | 4.4.5    | Inter cluster communication                              |   |

|    |       | 4.4.6    | Experimentation and results                              |   |

|    |       |          | 4.4.6.1 Simulation environment                           |   |

|    |       |          | 4.4.6.2 Application                                      |   |

|    |       |          | 4.4.6.3 Influence of the data placement and task mapping |   |

|    |       | 4.4.7    | Hardware Implementation                                  |   |

|    | 4.5   |          | ary                                                      |   |

|    |       |          |                                                          |   |

| 5  | Con   | clusions | and perspectives 11'                                     | 7 |

|    | 5.1   | Conclu   | sions                                                    | 8 |

|    | 5.2   |          | ctives                                                   |   |

|    |       | 5.2.1    | Mid-term perspectives                                    | 1 |

|    |       | 5.2.2    | Long-term perspectives                                   | 2 |

| Pe | rsona | l Public | ration 12                                                | 5 |

|    |       |          |                                                          |   |

| Ab | brevi | ations   | 12                                                       | 7 |

12 CONTENTS

| A | Ann        | ex A             |                                                                        | 131       |

|---|------------|------------------|------------------------------------------------------------------------|-----------|

|   | <b>A.1</b> | Methodology      | implementation                                                         | <br>. 132 |

|   |            | A.1.1 Librar     | ary of architecture                                                    | <br>. 132 |

|   |            | A.1.2 Code       | parallelization                                                        | <br>. 132 |

|   |            | A.1.3 Profile    | ler                                                                    | <br>. 132 |

|   |            | A.1.4 System     | emC simulation and Binary code generation                              | <br>. 132 |

|   |            | A.1.4.           | 4.1 HDL code generation                                                | <br>. 133 |

|   | A.2        |                  | of the Tabu search Parameters                                          |           |

|   |            | A.2.1 Justific   | fication of the tabu search memory size and of the number of iteration | <br>. 134 |

|   |            | A.2.2 Justific   | fication of the tabu search diversification operator level             | <br>. 135 |

|   | A.3        | Application be   | penchmarks                                                             | <br>. 136 |

|   | A.4        |                  | architecture model                                                     |           |

|   | A.5        | Justification of | of the Genetic algorithm parameters                                    | <br>. 138 |

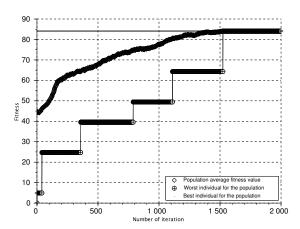

|   |            | A.5.1 Justific   | fication of the population size                                        | <br>. 138 |

|   |            |                  | fication of the number of generation                                   |           |

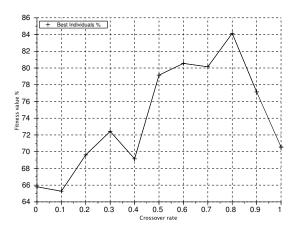

|   |            | A.5.3 Justific   | fication of the crossover rate                                         | <br>. 139 |

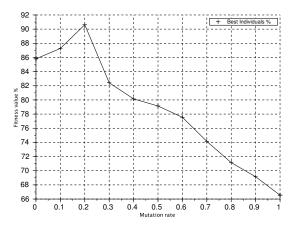

|   |            | A.5.4 Justific   | fication of the mutation rate                                          | <br>. 140 |

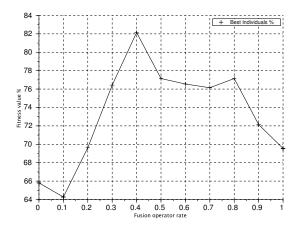

|   |            | A.5.5 Justific   | fication of the FO rate                                                | <br>. 140 |

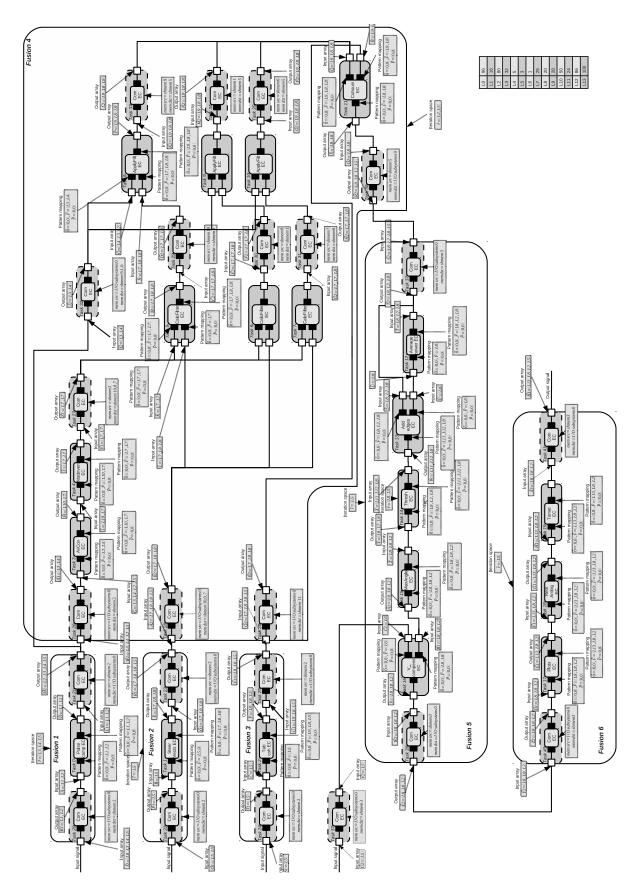

|   | A.6        | Application ta   | ask graph                                                              | <br>. 142 |

|   | A.7        |                  | ent representation                                                     |           |

|   |            | A.7.1 Examp      | nple of data placement obtained for the chirp application              | <br>. 144 |

|   |            |                  | nple of data placement obtained for the jpeg application               |           |

|   |            | A.7.3 Examp      | nple of data placement obtained for the stap application               | <br>. 146 |

|   | A.8        |                  | )                                                                      |           |

|   |            | A.8.1 Chirp      | )                                                                      | <br>. 148 |

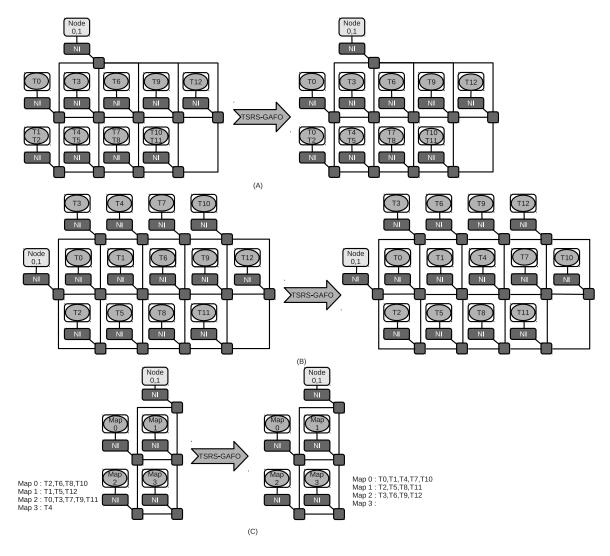

|   |            | A.8.1.           | I.1 Mapping                                                            | <br>. 148 |

|   |            | A.8.1.           | 1.2 Data placement                                                     | <br>. 148 |

|   |            | A.8.2 Jpeg .     |                                                                        | <br>. 148 |

|   |            | A.8.2.           | 2.1 Mapping                                                            | <br>. 148 |

|   |            | A.8.2.           | 2.2 Data placement                                                     | <br>. 149 |

|   |            | A.8.3 Stap.      |                                                                        | <br>. 151 |

|   |            | A.8.3.           | 3.1 Mapping                                                            | <br>. 151 |

|   |            | A.8.3.           | 3.2 Data placement                                                     | <br>. 151 |

| _ |            | _                |                                                                        |           |

| В | Ann        |                  |                                                                        | 153       |

|   | B.1        |                  | interface                                                              |           |

|   |            |                  | cle registration plate detection synchronization scheme and execution  |           |

|   | D 2        |                  |                                                                        |           |

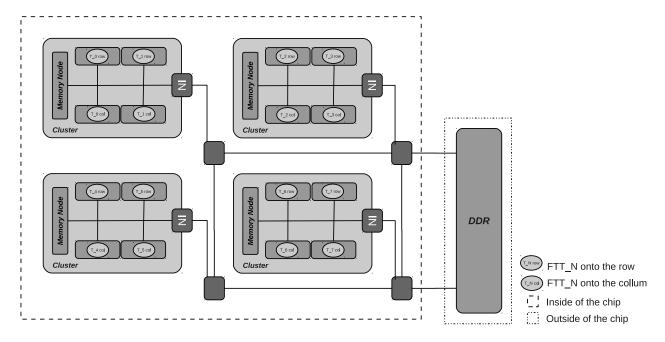

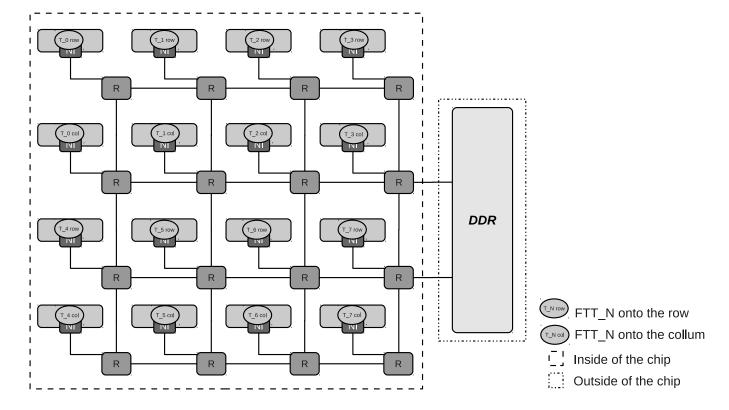

|   | B.2        |                  | d architecture a memory abstraction                                    |           |

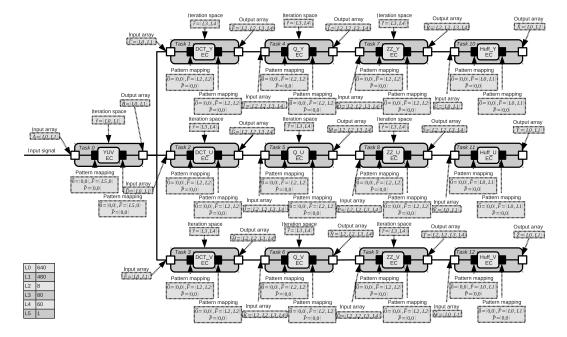

|   |            |                  | FT application mapping                                                 |           |

|   |            |                  | ter based architecture mapping                                         |           |

|   |            |                  | architecture mapping                                                   |           |

|   |            |                  | ops architecture mapping                                               |           |

|   |            |                  | ix multiplication application mapping                                  |           |

|   |            |                  | ter based architecture mapping                                         |           |

|   |            |                  | architecture mapping                                                   |           |

|   |            | B.2.8 Ter@d      | ops architecture mapping                                               | <br>. 104 |

| CONTENTS |                                                | 13  |

|----------|------------------------------------------------|-----|

| B.2.9    | Cluster based architecture inefficient mapping | 165 |

# **List of Figures**

| 1.1  | application domains [107]                                                                    | 2  |

|------|----------------------------------------------------------------------------------------------|----|

| 1.2  | Typical MPSoC architecture based on several GPP connected through an interconnect            |    |

|      | (Bus or Noc based) along with a DDR memory and all the peripherals needed for a              |    |

|      | connection with the outside environment. These MPSoC is homogeneous and can target           |    |

|      | several kinds of computation                                                                 | 3  |

| 1.3  | Evolution of the memory performance in regards of the processor performance [111]            | 4  |

| 1.4  | Point to point interconnection network                                                       | 5  |

| 1.5  | Bus interconnection network                                                                  | 6  |

| 1.6  | Representation of a NoC                                                                      | 6  |

| 1.7  | Typical heterogeneous MPSoC architecture                                                     | 8  |

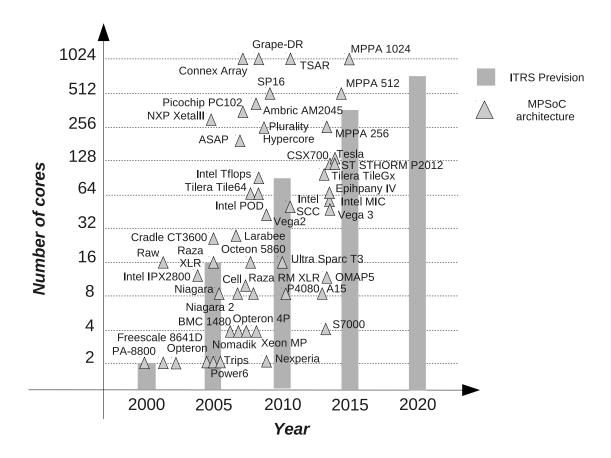

| 2.1  | Non-exhaustive list of the evolution of the multiple cores architectures in regards of their |    |

|      | number of cores and their year of production [107]                                           | 12 |

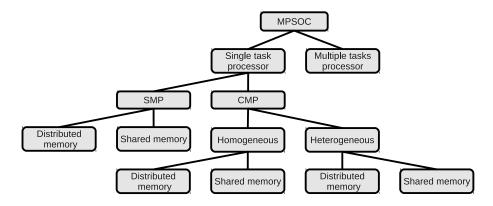

| 2.2  | Classification of the MPSoC architectures [74]                                               | 13 |

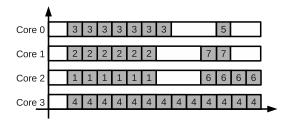

| 2.3  | Example of task mapping on a SMP MPSoC                                                       | 14 |

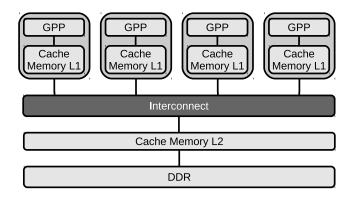

| 2.4  | Representation of a MPSoC architecture with a shared L2 cache                                | 15 |

| 2.5  | The clustered TSAR architecture using shared memory                                          | 16 |

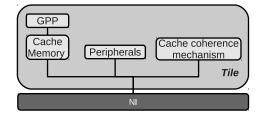

| 2.6  | Architecture of a TileGX tile organized around a GPP, a cache memory, a cache coher-         |    |

|      | ence mechanism, peripherals for synchronization and data transfers and a NI for network      |    |

|      | connection                                                                                   | 17 |

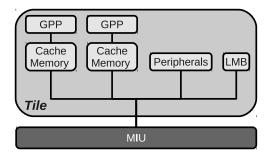

| 2.7  | Architecture of a SCC tile organized around two GPP along with their cache memory,           |    |

|      | peripherals for synchronization and data transfers, a LMB and a MIU                          | 17 |

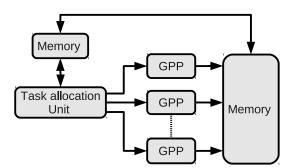

| 2.8  | Logical representation of a asymmetric architecture                                          | 18 |

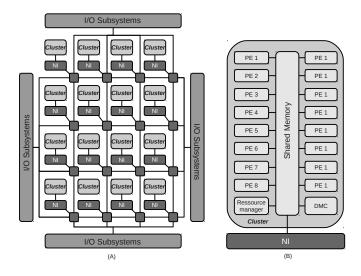

| 2.9  | (A) Overview of the MPPA 256 architecture. (B) Architecture of a MPPA cluster                | 19 |

| 2.10 | The SCMP architecture                                                                        | 19 |

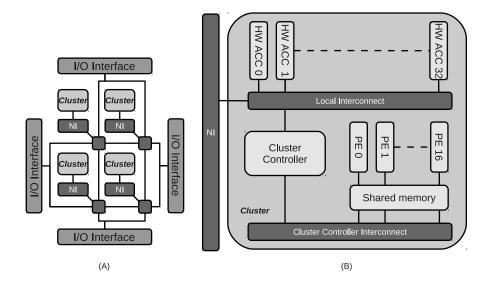

| 2.11 | (A) Representation of the STHORM architecture. (B) Architecture of a STHORM cluster.         | 21 |

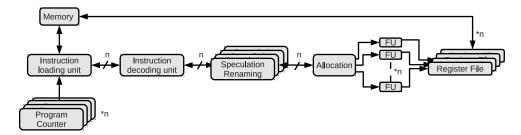

|      | Logical representation of a CMT architecture                                                 | 21 |

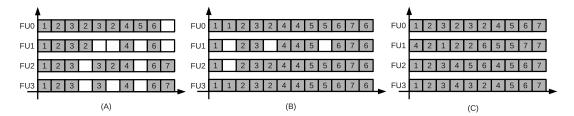

| 2.13 | (A) Example of an interleaved execution, (B) Example of a blocked execution, (C) Ex-         |    |

|      | ample of a simultaneous multithreaded execution                                              | 22 |

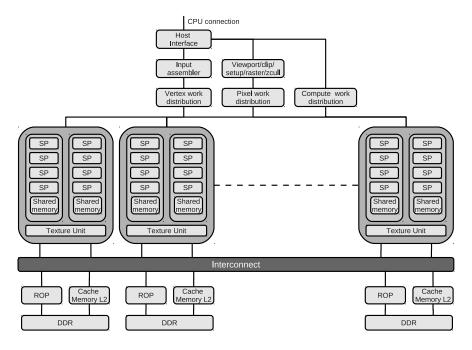

|      | Nvidia Tesla architecture                                                                    | 23 |

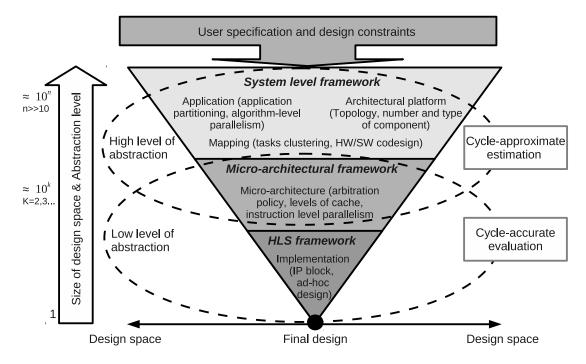

|      | Classification for DSE approach [125]                                                        | 25 |

|      | Possibilities provided by SpearDE tool                                                       | 28 |

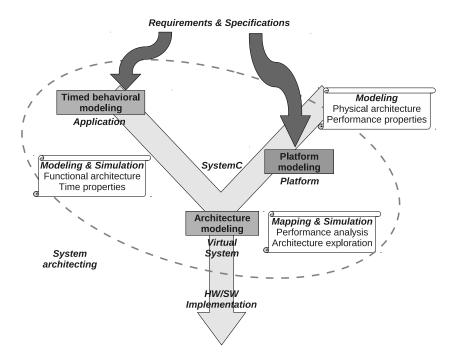

|      | Overview of Cofluent studio tool [6]                                                         | 29 |

|      | Overview of Space codesign tool [23]                                                         | 30 |

|      | Qemu-SystemC framework                                                                       | 31 |

| 2.20 | Overview of the OVP platform                                                                 | 33 |

16 LIST OF FIGURES

| 2.21 | HLS and traditional design process [184]                                                      | 34         |

|------|-----------------------------------------------------------------------------------------------|------------|

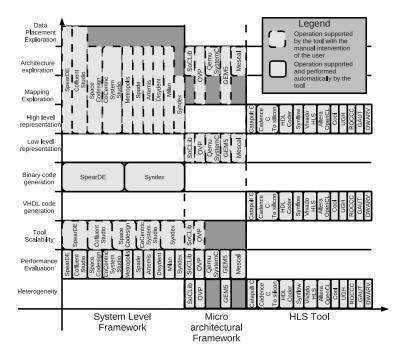

| 2.22 | Representation of the needs fullfiled by each tool presented during the state of the art      | 35         |

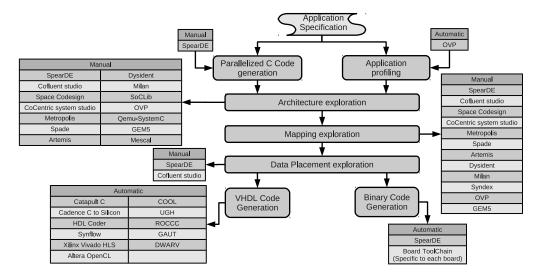

| 2.23 | Representation of an ideal flow where each state of the art tools is positioned               | 36         |

|      |                                                                                               |            |

| 3.1  | (A) Application represented as an oriented graph, (B) Task specification represented with     |            |

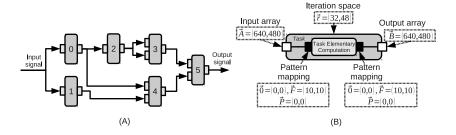

|      | the Array-OL formalism                                                                        | 38         |

| 3.2  | Example based on the task representation given Figure 3.1.B of how the input/output           | 20         |

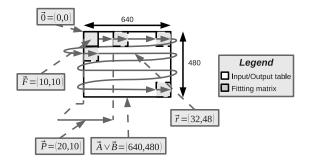

|      | array are read/write                                                                          | 39         |

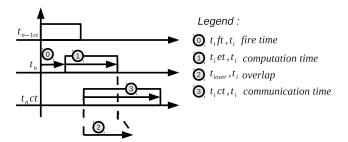

| 3.3  | Example of task execution time evaluation                                                     | 40         |

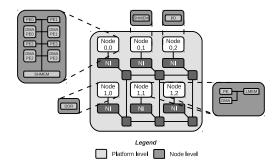

| 3.4  | Architecture model generated by PARSE                                                         | 40         |

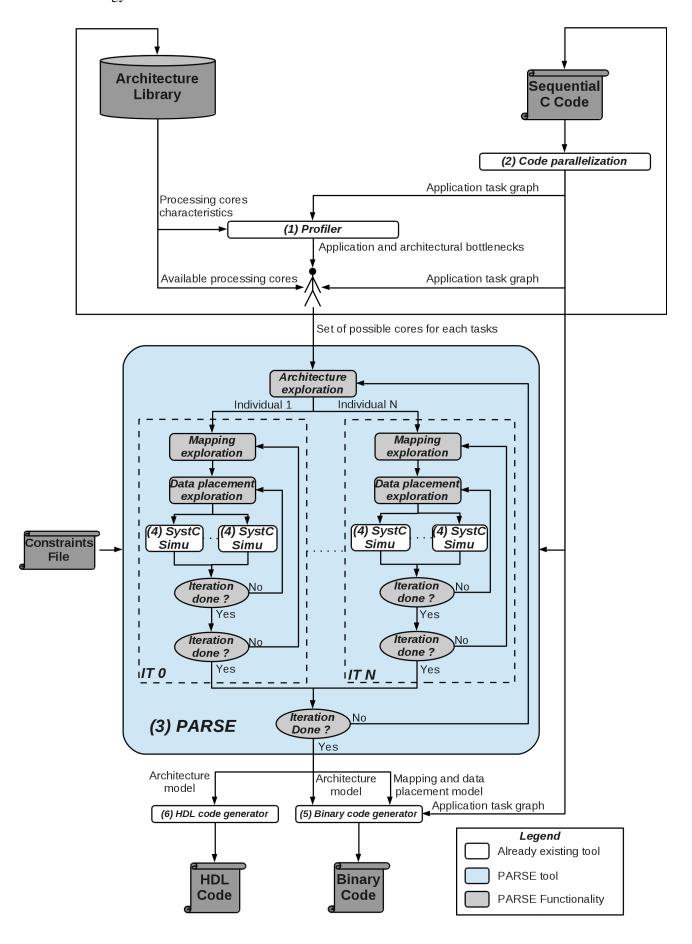

| 3.5  | Design space exploration methodology                                                          | 43         |

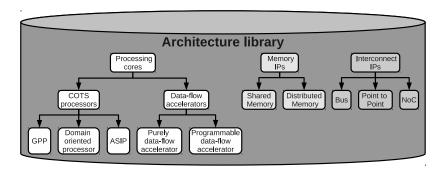

| 3.6  | Architecture library representation                                                           | 44         |

| 3.7  | Example of the operation done by the code parallelization tool, which from a sequential       |            |

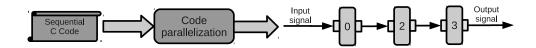

|      | C code produce a task graph                                                                   | 45         |

| 3.8  | Conversion of an architecture to a chromosome. Within this architecture the three nodes       |            |

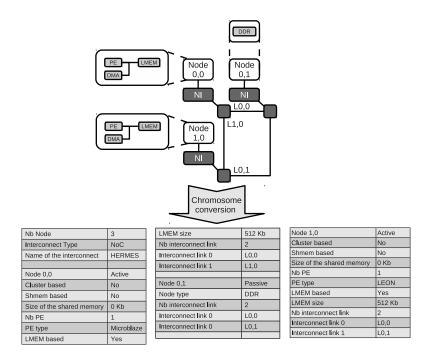

|      | are connected to a NoC. The NoC is the HERMES NoC [154]. Two nodes are active                 |            |

|      | and constructed around the microblaze and LEON processors, while the third node gives         |            |

|      | access to a DDR memory                                                                        | 48         |

| 3.9  | Representation of how the AI connect the IPs onto the interconnect                            | 49         |

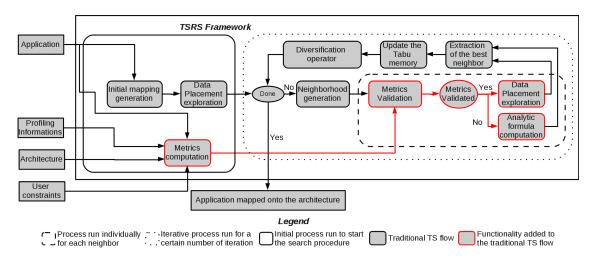

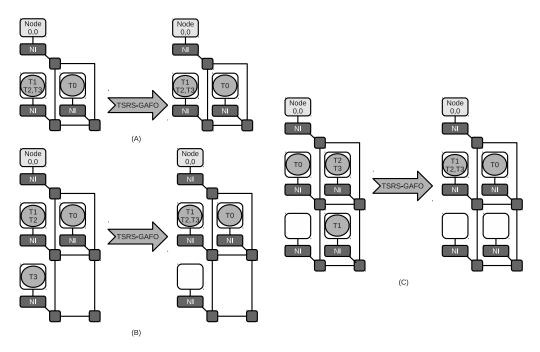

|      | TSRS framework used to explore the application mapping solution space                         | 52         |

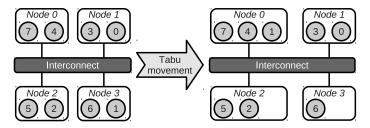

| 3.11 | Example of Tabu movement used to generate the neighborhood. One task is moved at a            |            |

|      | time. Here the task 1 is moved from the $node_3$ to the $node_0$                              | 53         |

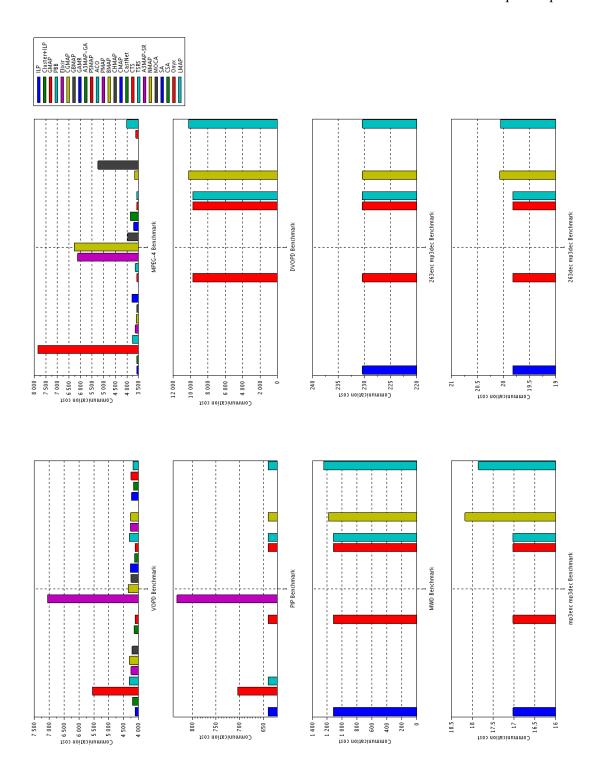

| 3.12 | Communication cost for the ILP [197], Cluster + ILP [198], GMAP [114, 115, 116], PBB          |            |

|      | [175], Elixir [174], CGMAP [175], GBMAP [193], GAMR [96], A3MAP-GA [122],                     |            |

|      | PSMAP [175], ACO [209], PMAP [131], BMAP [179], CHMAP [192], CMAP [68],                       |            |

|      | CastNet [199],A3MAP-SR [122], NMAP [175], MOCA [186], SA [145], CSA [145],                    |            |

|      | Onyx [123], LMAP [176], CTS and TSRS mapping algorithms on the tested benchmarks              | 60         |

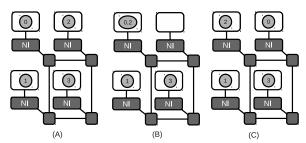

| 3.13 | Limit of the TSRS on the VOPD benchmark. From the initial solution (A), the task 2 is         |            |

|      | moved on the same node as the task 0 because all the solution are penalized and this is       |            |

|      | the most efficient penalized solution (B), the next solution (C) is then to move the task 0   |            |

|      | to the free node since this is the only solution which is not penalized or Tabu               | 61         |

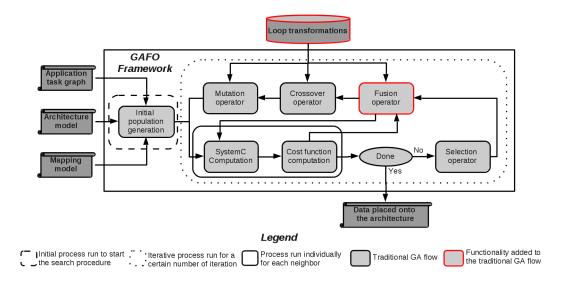

|      | GAFO framework used to explore the application data placement solution space                  | 65         |

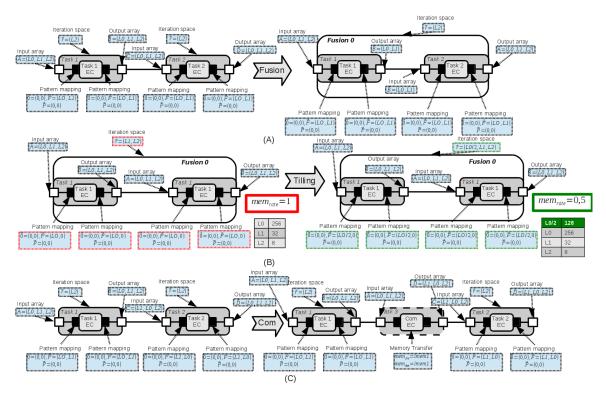

| 3.15 | Loop transformations that can be applied to the application model. (A) Task fusion to         |            |

|      | merge tasks into the same fusion, (B) Tilling change add a level of depth to a loop nest,     |            |

|      | (C) The creation of a communication for data reorganization or data transfer                  | 66         |

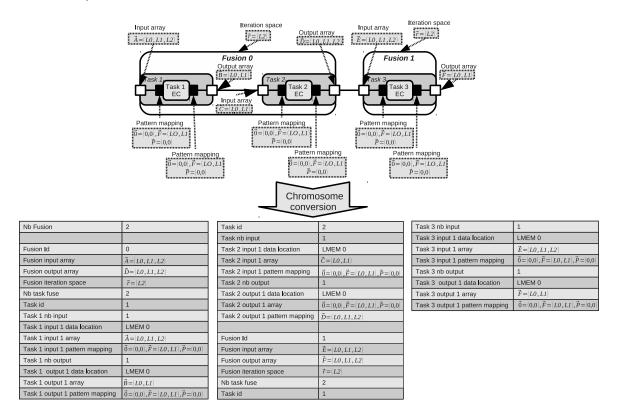

| 3.16 | Conversion of a data placement to a chromosome, within this chromosome two tasks are          |            |

|      | merged within the same iteration space and one task is allocated into its own iteration       | <b>6</b> 7 |

| 0.15 | space                                                                                         | 67         |

|      | Operating principle of the fusion operator                                                    | 68         |

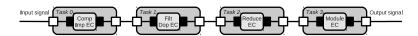

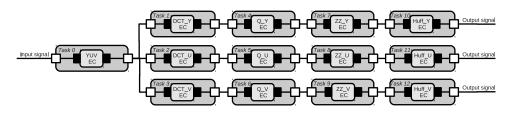

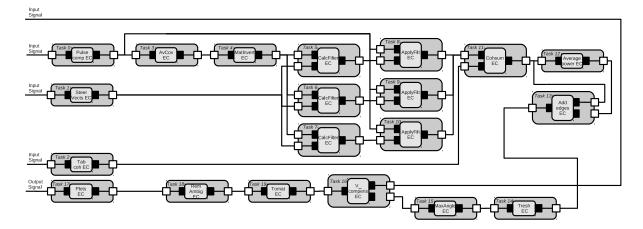

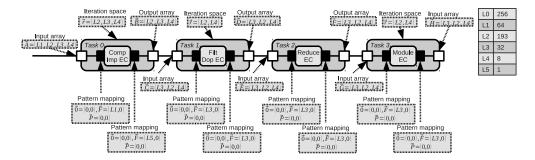

|      | Chirp application task graph.                                                                 | 68         |

|      | Jpeg application task graph                                                                   | 68         |

|      | Stap application task graph                                                                   | 69         |

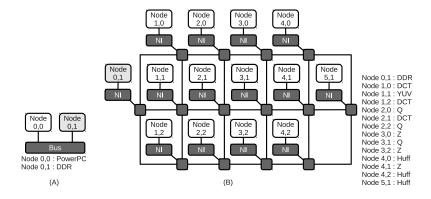

|      | Architecture models used for the chirp and jpeg application                                   | 69         |

|      | Architecture models used for the TSRS-GAFO experimentation                                    | 73         |

| 3.23 | Evolution of the proposed solution for the chirp, jpeg and stap application with the $\alpha$ |            |

|      | parameters                                                                                    | 78         |

LIST OF FIGURES 17

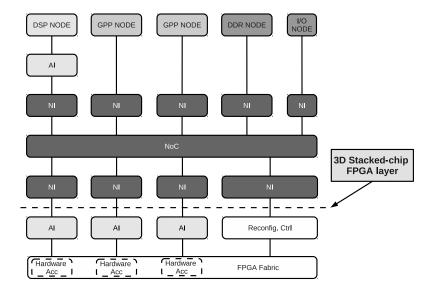

| 4.1        | the FPGA layer. GPP and DSP are mapped onto the MPSoC layer while the hardware accelerator are mapped onto the FPGA layer. All the resources are connected through a NoC, the accelerators (DSP and hardware accelerators) connection onto the NoC being | 83   |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

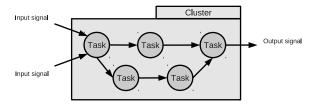

| 4.2        | abstracted by the means of the AI                                                                                                                                                                                                                        | 85   |

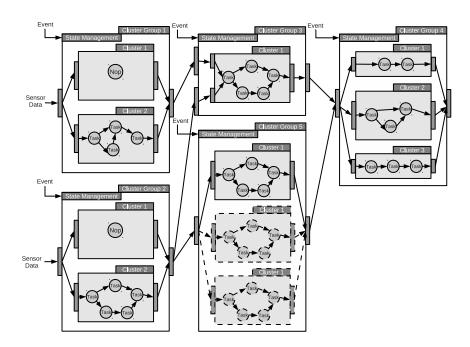

| 4.3        | Management in FlexTiles: Cluster groups can behave differently depending on their dynamicity level                                                                                                                                                       | 86   |

| 4.4        | Accelerator Interface global view.                                                                                                                                                                                                                       | 88   |

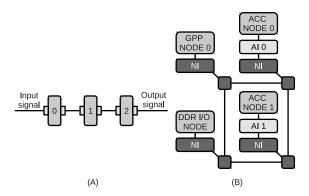

| 4.5        | (A) Application model, (B) Architecture model of the proof of concept example                                                                                                                                                                            | 91   |

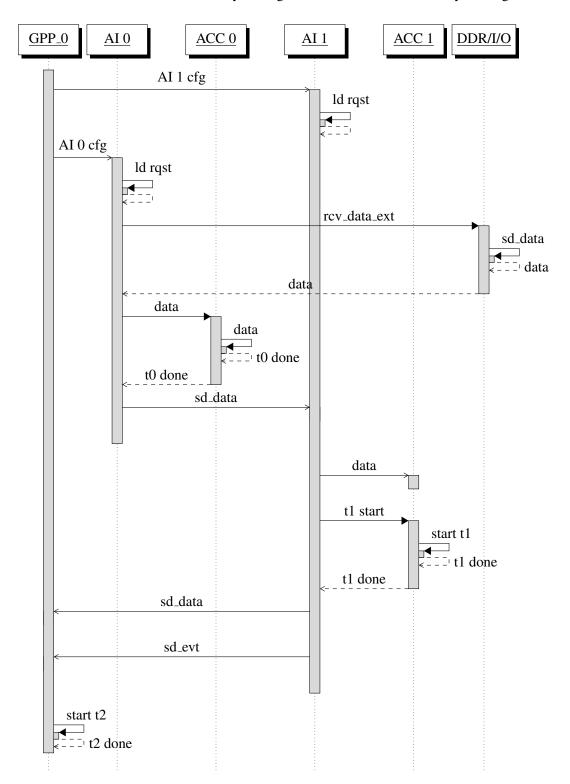

| 4.6        | Synchronization scheme and execution patterns                                                                                                                                                                                                            | 92   |

| 4.7        | FlexTiles board.                                                                                                                                                                                                                                         | 93   |

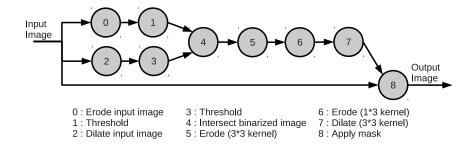

| 4.8        | Vehicle registration plate, application tasks graph                                                                                                                                                                                                      |      |

| 4.9        | Vehicle registration plate input and output images                                                                                                                                                                                                       | 94   |

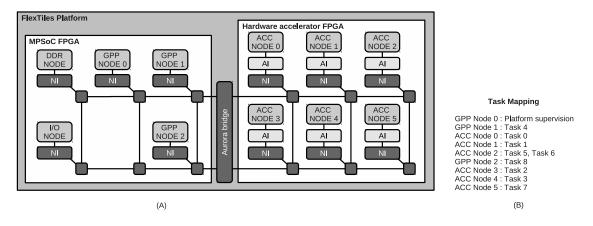

| 4.10       |                                                                                                                                                                                                                                                          | 94   |

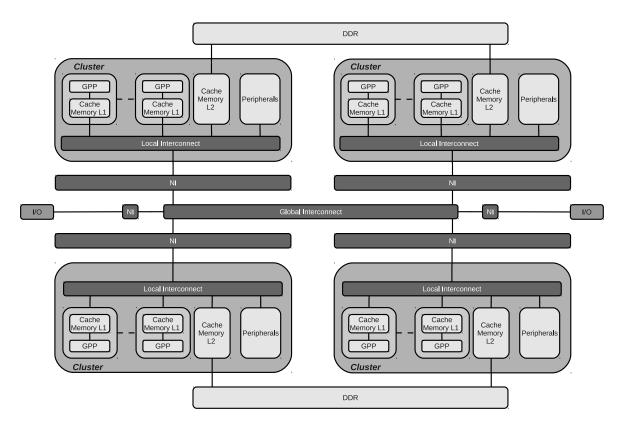

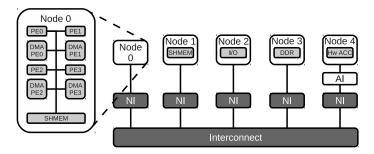

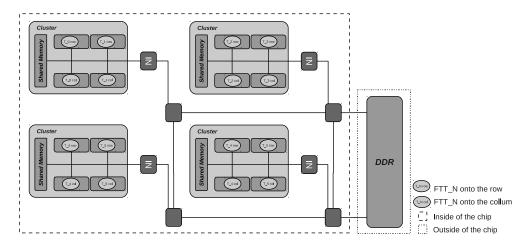

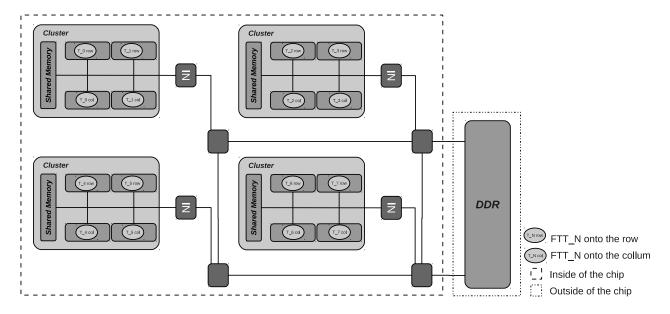

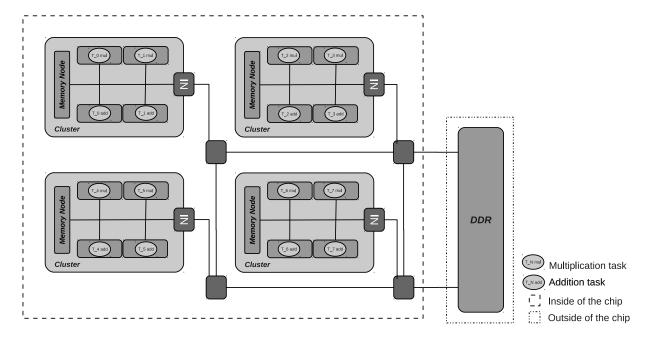

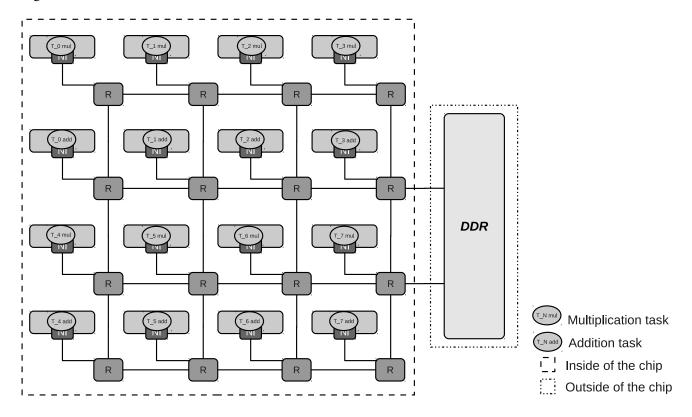

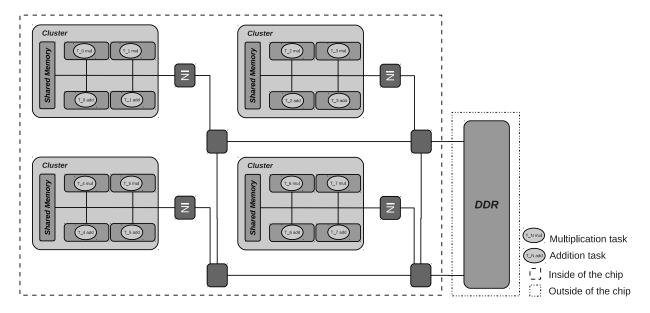

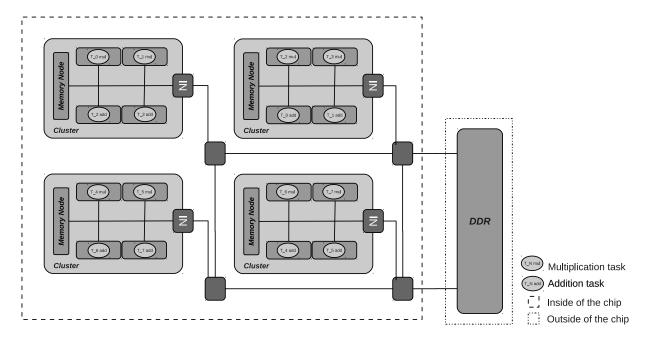

| 4.11       | Proposed architecture where clusters are implemented to favor local data transfer thereby increasing the overall system performance                                                                                                                      | 100  |

| 4.12       | Cluster architecture, each cluster is composed of a set of processor nodes along with a memory node. A processor node being composed of all the elements necessary to communicate and synchronize with the rest of the platform.                         |      |

| 4.13       | Memory node composed of a partition table, an address generation unit (AGU) and a memory protection unit (MPU)                                                                                                                                           |      |

| 4.14       | Structure of a line into the partition table                                                                                                                                                                                                             | 102  |

| 4.15       | Architecture of the address generation unit                                                                                                                                                                                                              | 102  |

|            | Architecture of the memory protection unit                                                                                                                                                                                                               | 103  |

| 4.17       | Example where two GPP within the same cluster are communicating through a partition of the memory node.                                                                                                                                                  | 104  |

| 4.18       | Example where a GPP and a DSP located into remote clusters are communicating through a memory node                                                                                                                                                       | 106  |

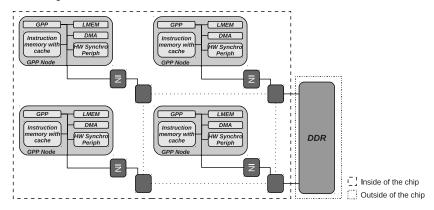

| 4.19       | OVP model of cluster based architecture implementing an on-chip MP protocol                                                                                                                                                                              |      |

|            | Ter@ops architecture                                                                                                                                                                                                                                     |      |

| 4.21       | Flat architecture model used to compare the benefits brings by the cluster based architecture.                                                                                                                                                           | 108  |

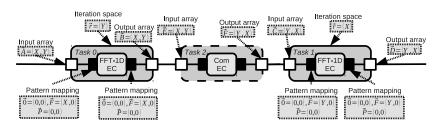

| 4 22       | 2D-FFT application task graph                                                                                                                                                                                                                            |      |

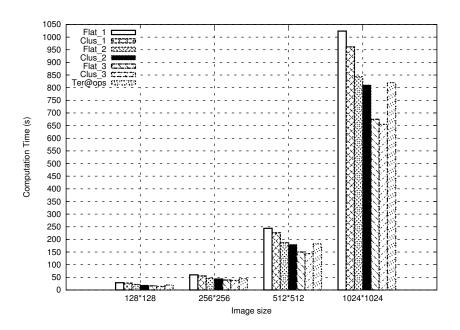

|            | Execution times needed to realize a 2D FFT on 32 images                                                                                                                                                                                                  |      |

|            | Matrix multiplication application task graph                                                                                                                                                                                                             |      |

|            | Execution times needed to realize 32 matrix multiplications                                                                                                                                                                                              |      |

|            | Influence of the task mapping and data placement onto the benefit bring by the cluster based approach.                                                                                                                                                   |      |

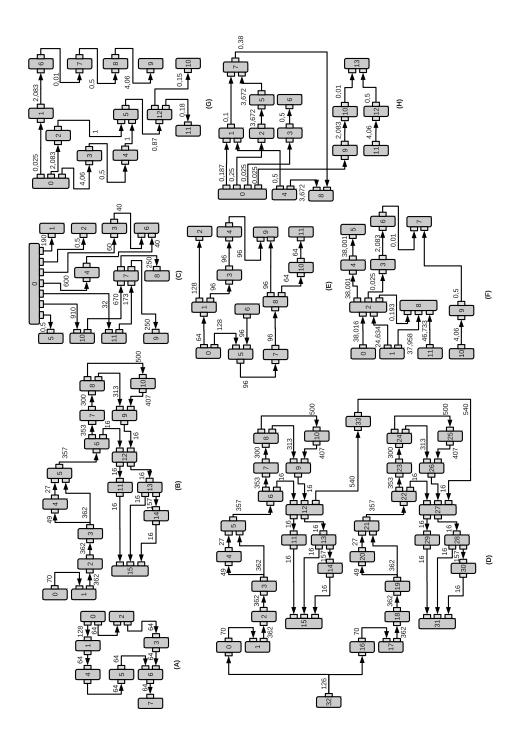

| A.1<br>A.2 | Evolution of the best solution with the diversification operator level for the stap application (A) PIP, (B) VOPD, (C) MPEG-4, (D) DVOPD, (E) MWD, (F) mp3enc mp3dec, (G)                                                                                | .135 |

|            | 263enc mp3dec, (H) 263dec mp3dec                                                                                                                                                                                                                         | 136  |

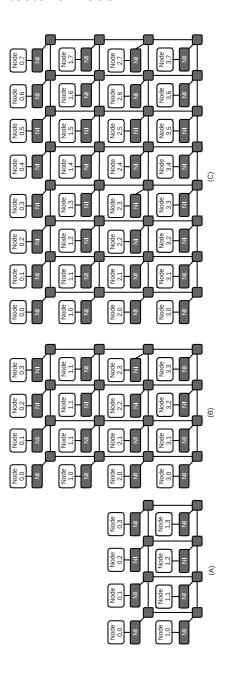

| A.3        | (A) PIP architecture model, (B) VOPD, MPEG-4, MWD, 263enc mp3dec, mp3enc mp3dec, 263dec mp3 dec architecture model, (C) DVOPD architecture model                                                                                                         |      |

| A.4        | Convergence of a population composed of 2000 individuals                                                                                                                                                                                                 |      |

|            | Impact of the crossover rate                                                                                                                                                                                                                             |      |

18 LIST OF FIGURES

| A.6          | Impact of the mutation rate                                                           | 140 |

|--------------|---------------------------------------------------------------------------------------|-----|

| A.7          | Impact of the fusion operator rate                                                    | 140 |

| A.8          | Chirp application task graph with loops details                                       | 142 |

| A.9          | Jpeg application task graph with loops details                                        | 142 |

| <b>A.</b> 10 | Stap application task graph with loops details                                        | 143 |

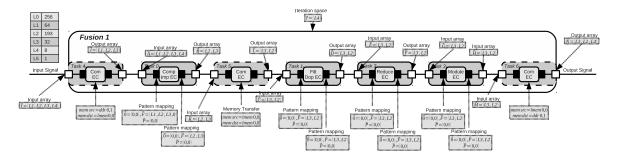

| <b>A.</b> 11 | Chirp data placement obtained following the exploration done with the GAFO            | 144 |

| A.12         | Jpeg input mapping used by the GAFO                                                   | 144 |

| A.13         | Jpeg data placement obtained following the exploration done with the GAFO             | 145 |

| A.14         | Stap input mapping used for the GAFO                                                  | 146 |

| A.15         | Stap data placement obtained following the exploration done with the GAFO             | 147 |

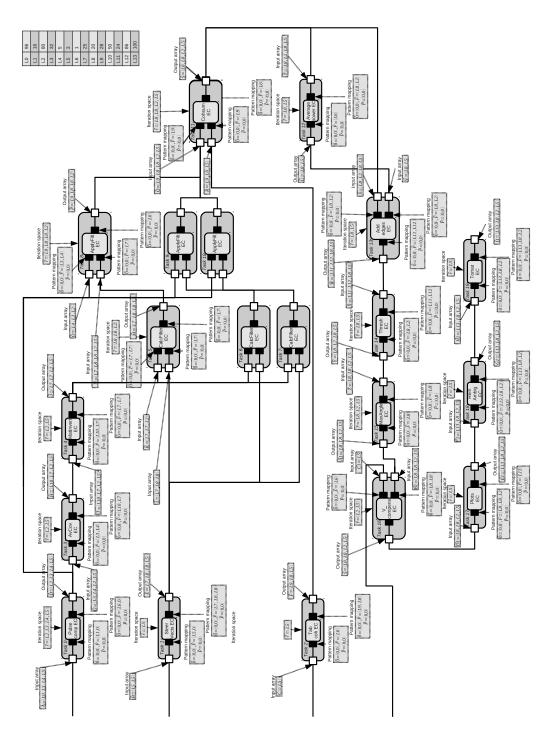

| A.16         | Initial and Final mapping obtained for the chirp application by the TSRS-GAFO for the |     |

|              | three test case architectures                                                         | 148 |

| A.17         | Initial and Final mapping obtained for the chirp application by the TSRS-GAFO for the |     |

|              | three test case architectures                                                         | 149 |

| A.18         | Jpeg data placement obtained following the exploration done with the TSRS-GAFO for    |     |

|              | the mapping shown Figure A.17 A and C                                                 | 150 |

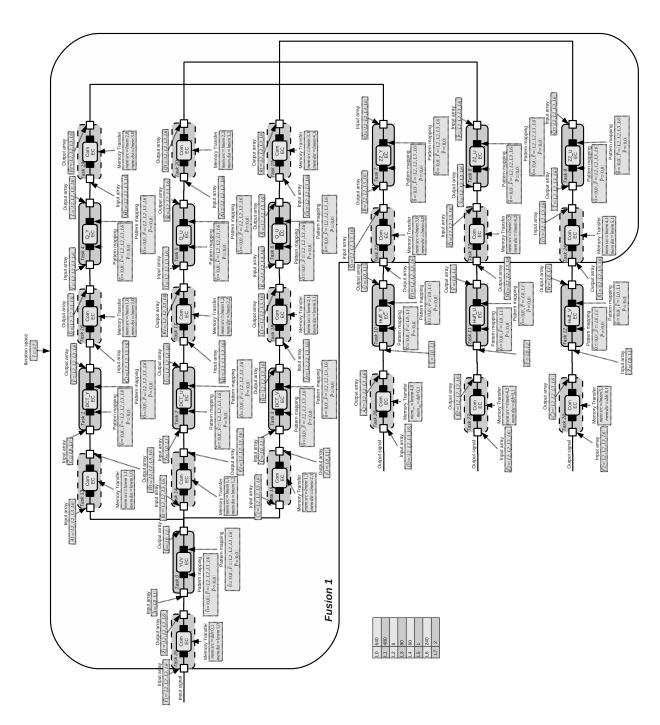

| A.19         | Initial and Final mapping obtained for the stap application by the TSRS-GAFO          | 151 |

| A.20         | Stap data placement obtained following the exploration done with the TSRS-GAFO for    |     |

|              | the mapping shown Figure A.19                                                         | 152 |

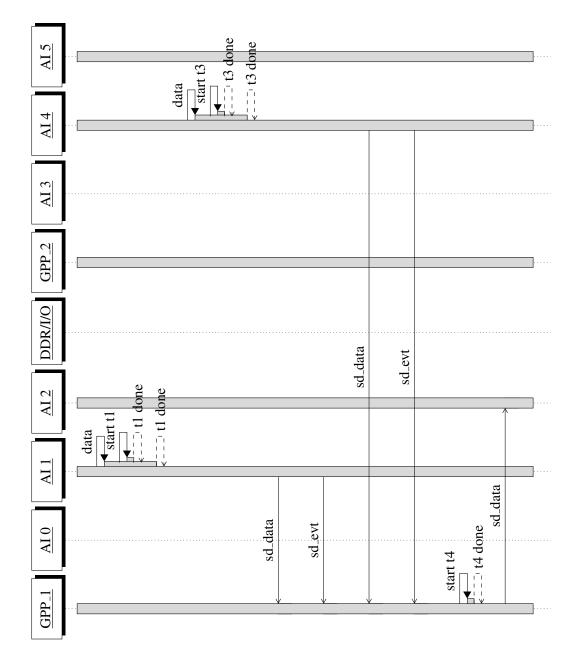

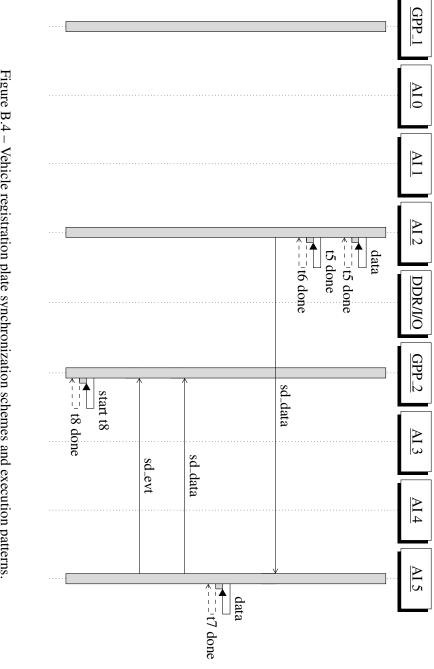

| B.1          | Vehicle registration plate synchronization schemes and execution patterns             | 155 |

| B.2          | Vehicle registration plate synchronization schemes and execution patterns.            |     |

| B.3          | Vehicle registration plate synchronization schemes and execution patterns.            |     |

| B.4          | Vehicle registration plate synchronization schemes and execution patterns             |     |

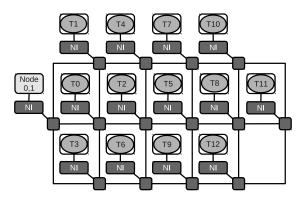

| B.5          | 2D-FFT application mapping on the clus_2 architecture                                 |     |

| B.6          | 2D-FFT application mapping on the Flat_2 architecture                                 |     |

| B.7          | 2D-FFT application mapping on the Ter@ops architecture                                |     |

| B.8          | Matrix multiplication application mapping on the clus_2 architecture                  |     |

| B.9          | Matrix multiplication application mapping on the Flat_2 architecture                  |     |

|              | Matrix multiplication application mapping on the Ter@ops architecture                 |     |

|              | Inefficient matrix multiplication application mapping on the clus_2 architecture      |     |

|              |                                                                                       |     |

# **List of Tables**

| 1.1  | Influence of the MPSoC architectures characteristics parameters                                                                                                                                                                                                 | 7   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Summary of the MPSoC architectures capabilities. In this table the MPSoC are evaluated following their capacities to ease the mapping and the data placement along with their ability to be scalable and target several applications with a reduce power budget | 24  |

| 3.1  | Variable names nomenclature                                                                                                                                                                                                                                     | 41  |

| 3.2  | Exploration runtime of the three test applications.                                                                                                                                                                                                             | 46  |

| 3.3  | Tabu search parameters settings                                                                                                                                                                                                                                 | 59  |

| 3.4  | Exploration runtime of TS on the seven tested benchmarks                                                                                                                                                                                                        | 62  |

| 3.5  | Genetic algorithm parameters settings                                                                                                                                                                                                                           | 70  |

| 3.6  | Application execution time for different memory configuration, along with the percentage of the application execution time used for the computation and for the communica-                                                                                      | , 0 |

|      | tion.                                                                                                                                                                                                                                                           | 71  |

| 3.7  | Performance benefit bring by the FO                                                                                                                                                                                                                             | 71  |

| 3.8  | Exploration runtime of the three test applications                                                                                                                                                                                                              | 72  |

| 3.9  | Profiling of the chirp application onto the PowerPC. Task numbering refer to figure 3.18.                                                                                                                                                                       | 74  |

| 3.10 | Profiling of the jpeg application onto the PowerPC. Task numbering refer to figure 3.19                                                                                                                                                                         | 74  |

|      | Profiling of the stap application onto the MPPA. Task numbering refer to figure 3.20                                                                                                                                                                            | 74  |

|      | Summary of the architectures used for these tests                                                                                                                                                                                                               | 74  |

|      | Execution time constraints set for all the application and architecture models                                                                                                                                                                                  | 75  |

|      | Parameters settings for the TSRS and CTS                                                                                                                                                                                                                        | 75  |

| 3.15 | Application execution time for different architecture model, along with the percentage of the application execution time used for the computation and for the communication                                                                                     | 76  |

| 3.16 | Exploration run-time.                                                                                                                                                                                                                                           | 77  |

| 4.1  | List of specific commands used to program the AI                                                                                                                                                                                                                | 90  |

| 4.2  | Area occupancy of one Accelerator Interface                                                                                                                                                                                                                     | 95  |

| 4.3  | AI area consumption (Occupied slices) as relative ratio between components                                                                                                                                                                                      | 96  |

| 4.4  | Latency of each elementary operation supported by the AI                                                                                                                                                                                                        | 96  |

| 4.5  | Mapping experimental Results                                                                                                                                                                                                                                    | 97  |

| 4.6  | List of evaluated architectures. The number of cores varies from 8 to 32. While the amount of memory present on the chip and the memory bandwidth stay constant                                                                                                 | 108 |

| 4.7  | Speedup of the cluster based architecture over the flat architecture and the Ter@ops on                                                                                                                                                                         |     |

|      | the FFT application                                                                                                                                                                                                                                             |     |

| 4.8  | Task overlap for the FFT application                                                                                                                                                                                                                            | 111 |

20 LIST OF TABLES

| 4.9         | Speedup of the cluster based architecture over the flat architecture and the Ter@ops    |

|-------------|-----------------------------------------------------------------------------------------|

|             | architecture on the matrix multiplication application                                   |

| 4.10        | Task overlap for a matrix multiplication application                                    |

| 4.11        | MMU resources consumption                                                               |

| <b>A.</b> 1 | Evolution of the best solution with the memory size and the number of iteration for the |

|             | stap application                                                                        |

| A.2         | Error rate on the stap application for different population size                        |

### Résumé en français

#### **Contexte et motivations**

#### **Problématiques**

Les applications embarquées incorporent de plus en plus de fonctionnalités impliquant différents types de traitements à réaliser. L'impact majeur de cette demande est l'évolution croissante des systèmes embarqués que cela soit en termes de performances et de capacité mémoire.

De plus, aujourd'hui les applications deviennent de plus en plus dynamiques. Les temps d'exécution sont alors dépendants de paramètres non prédictibles au moment de la définition de l'application. La détermination du temps d'exécution de l'application devient dès lors impossible, et seule une borne supérieure pour le temps d'exécution peut être définie.

L'évolution des systèmes embarqués entraîne donc des problèmes au niveau de la conception et de la programmation. Ces systèmes doivent en effet trouver un compromis entre leurs capacités (puissance de calcul, dynamicité) et les contraintes du domaine d'application (silicium, consommation).

La problématique, liée à la puissance de calcul, fut la première à être adressée. Dans le cas de processeur monolithique, les principales approches consistent à augmenter la fréquence de fonctionnement du cœur de calcul ou à augmenter la capacité mémoire pour limiter le nombre de cycles inutilisés du processeur. Cependant ces techniques, bien qu'efficaces, augmentent dans le même temps la surface du cœur de calcul le de petits cœurs permet d'atteindre la puissance de calcul d'un seul cœur monolithique tout en réduisant la consommation énergétique et la surface consommée.

Grâce à cette évolution, les architectures MPSoC apparaissent actuellement comme les principaux promoteurs de la révolution industrielle des semi-conducteurs [212]. Ces plates-formes contiennent plusieurs processeurs, généralement hétérogènes, des éléments de traitement avec des fonctionnalités spécifiques reflétant la nécessité du domaine d'application prévu, une hiérarchie mémoire et des composants d'entrées/sorties. Tous ces éléments étant liés les uns aux autres par une interconnexion sur puce (de plus en plus souvent un réseau sur puce ou "NoC").

Grâce à leurs évolutivités, leurs hautes performances, leurs capacités de parallélisme à un très haut niveau d'intégration et leur enveloppe énergétique restreinte ces architectures deviennent de plus en plus populaires. Elles répondent aux besoins de performances des applications multimédia, des architectures de télécommunication, de la sécurité du réseau et de nombreux autres domaines d'application. L'industrie est elle aussi consciente de la nécessité d'utiliser des architectures "MPSoC" dans le but d'augmenter le rapport performance - énergie des systèmes embarqués où les contraintes de consomma-

ii Résumé en français

tion sont plus élevées [138].

Cependant, la conception d'une architecture "MPSoC" faible consommation et supportant les performances requises, n'est pas aisée. Cet équilibre dépend en effet de nombreux paramètres tels que le nombre de cœurs de calcul, l'enveloppe énergétique globale, le type de réseau d'interconnexion, l'architecture de la hiérarchie mémoire, le déploiement de l'application sur le système. En outre, le coût de fabrication de ce type de plateforme est conséquent (surtout dans les technologies modernes) et implique la vérification de manière précise de chaque choix architectural et applicatif.

Le problème de la consommation d'énergie dans les architectures MPSoC vient du fait que l'enveloppe énergétique n'a pas suivi la même évolution que le nombre de cœurs [50]. Les solutions, afin de réduire la consommation d'énergie, ont été pleinement étudiées [86], l'une des principales approches afin de réduire la consommation étant le "voltage scaling".

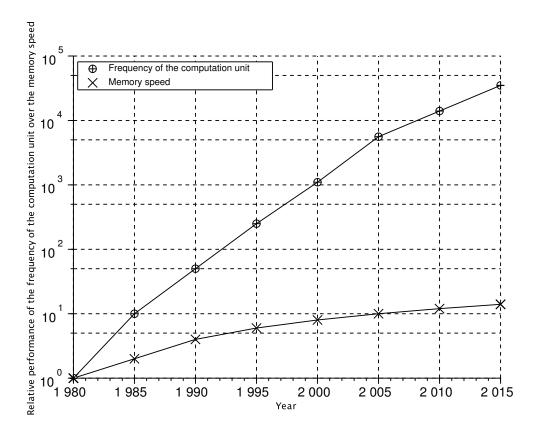

Les accès mémoires sont aussi un des facteurs critiques de la performance des architectures MPSoC [189], les gains en terme de puissance de calcul outrepassent fortement ceux de la mémoire. En effet, si la puissance de calcul double tous les deux ans, celui de la mémoire double tous les six ans [111, 149]. En conséquence, les accès à la mémoire génère des délais important pour lire ou écrire les données vis-à-vis des temps de calcul.

Dans les architectures MPSoC actuelles, les deux architectures principalement utilisés sont les modèles à mémoire partagée et à mémoire distribuée. Cependant, le choix entre ces deux modèles est complexe car il dépend à la fois de l'application, du réseau d'interconnexion et de la puissance de calcul des cœurs.

Le choix d'un réseau d'interconnexion est un autre point crucial au moment de la définition d'une architecture MPSoC. En effet, le choix d'une topologie est dépendant du nombre de cœurs qui doivent être connectés sur le réseau mais aussi des caractéristiques de l'application. Dans le domaine des systèmes embarqués, trois principales familles pour les réseaux d'interconnexions existent: (1) Les connections point à point, (2) les bus et (3) les NoC.

Une fois, l'architecture MPSoC déterminée, la difficulté réside dans le fait de tirer pleinement parti de cette dernière. À cette fin, le placement d'applications sur des architectures MPSoC à été fortement étudié dans la littérature [175]. En fonction du moment ou sont assignées les tâches sur les coeurs de calcul, les techniques de placement de tâches sont statiques ou dynamiques.

Dans le cas de placement de tâche dynamique, l'assignement et l'ordonnancement des tâches sur les processeurs sont réalisés durant l'exécution de l'application. Le placement de tâche dynamique essaye donc de toujours trouver les goulots d'étranglement de la performance et de répartir la charge de calcul sur l'ensemble des processeurs.

Dans le cas de placement de tâche statique, le placement des tâches sur les cœurs de calcul est réalisé hors-ligne, avant l'exécution de l'application sur l'architecture. Pour une application donnée et une infrastructure de communication déterminée, les algorithmes essayent de trouver le meilleur placement de tâches au moment de la conception de l'architecture.

Finalement, un des derniers défis lors de la conception d'une architecture MPSoC est le placement des données. Le placement des données est en effet un point clé afin d'être en mesure d'atteindre des hautes performances de calcul et d'avoir une utilisation efficace des ressources matérielles. Comme le placement des données est à la fois dépendant du réseau d'interconnexion, de la taille et de la bande passante des mémoires ainsi que de l'efficacité du processeur, le placement des données à un impact

fort sur le placement des tâches et sur les choix architecturaux. Un placement de données idéal est un placement de données ou le temps de traitement des données est supérieur où au moins égal au temps de transfert des données.

Comme nous pouvons le voir, les architectures MPSoC soulèvent des défis importants que ce soit au niveau de la conception ou de la programmation. De plus, étant donné que ces paramètres (Nombre de cœurs, hiérarchie et taille mémoire, réseau d'interconnexion, placement des tâches et des données) s'influencent mutuellement l'exploration de l'espace de conception des architectures MPSoC devient difficile.

En effet choisir le nombre de cœurs d'une architecture MPSoC doit être fait au regard du parallélisme de l'application mais aussi vis-à-vis de la bande passante de la mémoire et du réseau d'interconnexion. Cependant, le parallélisme pouvant être atteint par l'application est décidé en fonction du placement des tâches et des données, des tailles mémoires et des caractéristiques inhérentes de l'application.

Il apparaît clairement que la modification de l'application ou de l'un des paramètres caractéristiques de l'architecture entraîne la réévaluation complète de la solution. Ce qui dans les premières phases de développements d'une architecture MPSoC est prohibitif et consommateur en terme de temps.

De plus, ces défis de conception deviennent de plus en plus vrai avec l'émergence des architectures MPSoC hétérogène. En effet, ces architectures ne se contentent plus de répliquer plusieurs fois le même cœur de calcul mais incluent des fonctionnalités spécifiques ("Intellectual Property" (IP)) dédiées à un domaine d'application particulier, car elles présentent un meilleur niveau de performance et une meilleure efficacité énergétique [138].

Cette hétérogénéité en dépit des bénéfices apportés augmente la difficulté de concevoir et programmer les architectures MPSoC. En effet, l'architecte doit: (1) Choisir entre plusieurs types de cœurs de calcul, (2) Décider s'il est plus bénéfique de placer des tâches sur des GPP ou des accélérateurs matériels.

La construction de l'architecture est aussi complètement différente étant donnée que l'hétérogénéité de chaque composant doit être abstrait au niveau du réseau d'interconnexion. Ce qui implique de définir entre chaque cœur de calcul et le réseau d'interconnexion un "wrapper" particulier. Le "wrapper" devant être redéfini chaque fois que le réseau d'interconnexion est changé.

En outre, la programmation des architectures MPSoC hétérogènes est difficile étant donné que la manière de programmer un accélérateur matériel ou un processeur généraliste (GPP) est différent. L'utilisateur doit prendre pleinement parti de ces différences afin d'utiliser au maximum ces architectures. Ainsi, les temps de développement évoluent de manière exponentielle ainsi que les temps de mise sur le marché.

Tous ces défis durant la conception des architectures MPSoC mettent en lumière le besoin d'une méthodologie d'exploration d'espace de conception aidant l'utilisateur à définir et à programmer ces architectures. Il devient alors nécessaire de définir un outil d'exploration d'espace de conception (DSE) facilitant l'interaction entre l'application et l'architecture pour réduire efficacement le nombre de solutions s'offrant à l'utilisateur et les temps de mise sur le marché.

De plus comme les architectures MPSoC deviennent de plus en plus hétérogènes, il est nécessaire de développer des modules matériels permettant de faciliter la construction et la programmation des architectures MPSoC hétérogènes.

iv Résumé en français

#### **Contributions**

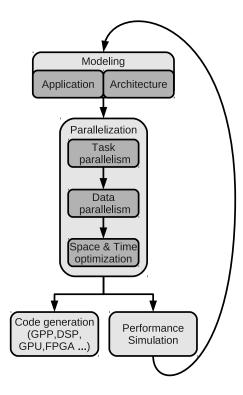

Dans le cadre de cette thèse, notre contribution est la définition d'une méthodologie d'exploration d'espace de conception. Cette méthodologie DSE a pour but de définir à la fois une architecture matérielle et son code binaire exécutable à partir de trois entrées: (1) le code C séquentiel d'une application, (2) une librairie d'architectures, (3) un fichier de contraintes.

Les principales caractéristiques de notre méthodologie DSE est la considération de manière conjointe de toutes les contraintes relatives à la définition d'une architecture matérielle grâce à une collaboration avec l'utilisateur. La méthodologie DSE proposée est en effet capable de: (1) générer une architecture composée de plusieurs cœurs de calcul, (2) définir un placement des tâches et des données ainsi que l'ordonancement associées à partir des contraintes utilisateurs.

Étant donné que ces paramètres s'influencent mutuellement, un outil nommé "Parsimonious ARchitecture Space Exploration" (PARSE) est proposé afin de parcourir l'espace de solution. PARSE est construit autour de mécanismes récursifs permettant depuis des simulations d'adapter l'architecture, le placement des tâches et des données, ceci dans le but d'atteindre le meilleur compromis à la fois pour l'architecture et pour l'application. Pour ce faire la méthodologie de PARSE est semi-automatisée.

En effet, étant donné la taille de l'espace de solution, l'utilisateur aide PARSE en retirant de l'espace de solution l'ensemble des cœurs ne répondant pas aux besoins applicatifs.

PARSE, à partir des choix de l'utilisateur, génère un ensemble d'architectures candidates, accompagnées d'un placemement des tâches et des données. Chaque solution potentielle est évaluée par le biais d'un simulateur SystemC afin de converger de manière efficace vers le meilleur compromis à la fois pour l'application et l'architecture. Cette exploration de l'espace de solution s'effectue de manière automatisée grâce à des algorithmes évolutionnaires. Une fois le meilleur compromis identifié le code VHDL de l'architecture et le code binaire exécutable associés sont générés.

Parce que PARSE à la capacité de générer des architectures matérielles, notre seconde contribution est la définition de deux modules matériels. Le premier module matériel défini une unité de management mémoire (MMU) servant à abstraire la hiérarchie mémoire aux sein d'architectures organisées autour de clusters.

La définition de cette MMU permet de faciliter la programmation des architectures MPSoC et d'optimiser le temps d'exécution de l'application, en réduisant les goulots d'étranglement, en maintenant la localité des données et en limitant les transferts de données à travers la plateforme. Pour ce faire, l'architecture proposée est basée sur des clusters où les processeurs sont regroupés et connectés au travers d'une mémoire partagée. La cohérence de la mémoire étant assurée par le biais d'une MMU matériel.

Le second module matériel défini dans le cadre de cette thèse est l'"accelerator interface" (AI) qui est une interface générique utilisée pour connecter différents types de cœurs de calcul (GPP, DSP <sup>1</sup> ou accélérateurs matériels) sur un réseau d'interconnexion.

L'AI permet de connecter de manière efficace différents types d'accélérateurs et de processeurs sur un même réseau d'interconnexion sans tenir compte de leurs spécificités ou caractéristiques. L'AI propose une apprroche "plug and play", grâce à la définition d'un modèle d'exécution unifié et d'une architecture générique qui permet de ne pas tenir compte du cœur de calcul adressé et de ses spécificités.

<sup>1.</sup> digital signal processor

De plus, toujours dans le but de tirer pleinement parti de la puissance de calcul induite par les architectures MPSoC, l'AI est autonome une fois initialisé, ce qui permet de réaliser de manière concurrente des traitements en parallèle.

Le reste de ce document présente en chapitre 1 le contexte et les motivations derrières cette thèse. Le chapitre 2 présente l'état de l'art des différentes architectures MPSoC et des outils d'exploration d'espace de conception. Le chapitre 3 quant à lui décrit la méthodologie d'exploration d'espace de conception proposé permettant d'explorer de manière conjointe les aspects architecturaux et applicatifs. Le chapitre 4 présente les contributions apportées au niveau matériels. Pour finir le chapitre 5 dressent les conclusion et les perspectives de cette thèse.

1

### Introduction

**Abstract:** This introductory chapter first presents the context and the motivations behind this thesis. Finally the manuscript organization is given at the end of the chapter.

### **Contents**

| 1.1 | <b>Context and motivations</b> | <br> |   | <br> |   |       |       | <br> |   |       | <br> | <br> |   |       | <br> |  |   |       | <br>2  |  |

|-----|--------------------------------|------|---|------|---|-------|-------|------|---|-------|------|------|---|-------|------|--|---|-------|--------|--|

| 1.2 | Manuscript organization        | <br> | • | <br> | • | <br>• | <br>• | <br> | • | <br>• | <br> | <br> | • | <br>• | •    |  | • | <br>• | <br>10 |  |

2 Introduction

### 1.1 Context and motivations

#### 1.1.1 Problem statement

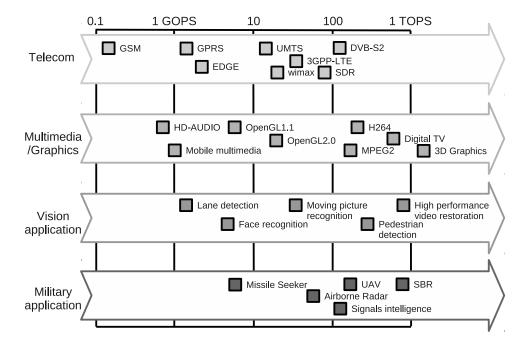

The embedded applications come up with more and more functionalities inducing various kinds of computations to realize. The major impact of these new application needs is the steadily evolution of the embedded systems performances in terms of computing power and memory capacity. The Figure 1.1 [107] shows the computing power needs depending on the application for various application domains.

Figure 1.1 – The graph shows the computational requirements of different application grouped by application domains [107].

For example in the telecom domain the application computing power needs to increase to get around 100 giga operation per second (GOPS) for the video broadcasting applications. The same trend is also observed for the multimedia applications, due to the image size and to the algorithm complexity increase. For example the 3D graphics applications require more than 1 tera operation per second (TOPS). The same evolution of the computing power affects all the embedded applications domains whether for the vision applications or the military applications.

Moreover today an embedded system has to handle several kinds of applications at the same time on the same chip. For example a mobile is no longer just used as a phone, but also used to read mails, go on internet, watch movies or play video games. These demands impose the embedded systems to run several applications which come from several applications domains.

Furthermore the applications become more and more dynamic. Indeed the application executions time is dependent of not predictable parameters at the time the program is written. It is then not possible to predict the execution time of an application and it is usually only possible to determine an upper bound for the processing time. This dynamicity is more and more present in the graphic domain where

Context and motivations 3

the algorithms adapt their computation to the data to be processed, as DVS <sup>1</sup> for 3D video games [106] for example. This application dynamicity implies that no optimal scheduling solution can be found off-line, and so the system control as to also be dynamic in order to enable an on-line optimization.

The embedded system evolution leads to a problem at the conception level. Indeed these systems have to find a trade-off between their capacity (computing power, dynamicity) and the embedded system constraints (silicium, consumption). The computing power is one of the major issues.

In order to increase the computing power of a single core architecture the solution is to improve its operation frequency or to raise the size of the memory in order to limit the idle cycle of the processor. These techniques increase, at the same time, the silicium area and the processor power consumption, which then decrease the energy efficiency [50].

Since energy efficiency is a key aspect of an embedded system, the solution is then to use a multi or a manycore architecture. Indeed as stated by [50] it is easier to integrate several little core specialized or not, whose energy and area efficiency are optimized. This allows to reach a computing power equal to the one of a single processor within a reduced power and area budget.

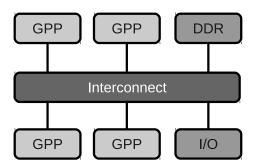

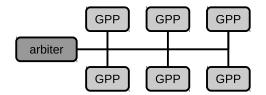

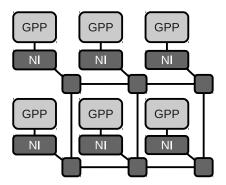

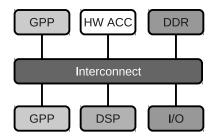

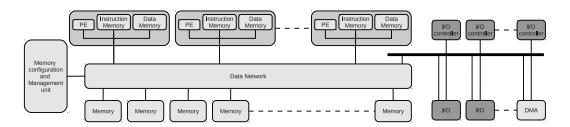

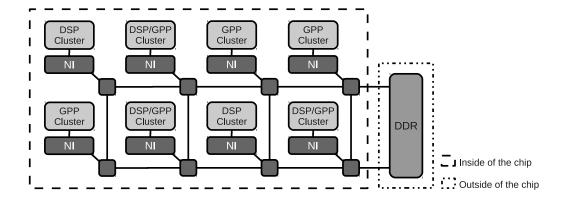

Following this trends, the multiple processors system on chip (MPSoC) architectures (Figure 1.2) appears as a major promoter of the industrial revolution of semiconductors as advised by the international technology road-map for semi-conductors (ITRS) [212]. This relies on the integration on the same chip of several complex functionalities. These platforms contain multiple processors, a memory hierarchy, and I/Os components. All these elements linked to each other by the means of an interconnect infrastructure becoming more and more often a network on chip (NoC).

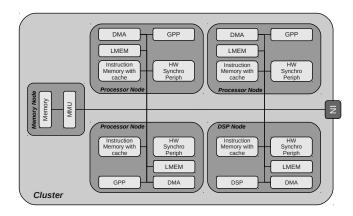

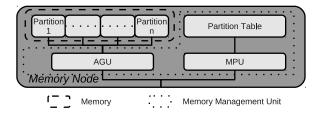

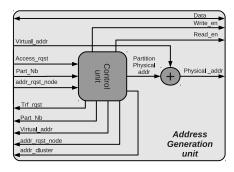

Figure 1.2 – Typical MPSoC architecture based on several GPP connected through an interconnect (Bus or Noc based) along with a DDR memory and all the peripherals needed for a connection with the outside environment. These MPSoC is homogeneous and can target several kinds of computation.

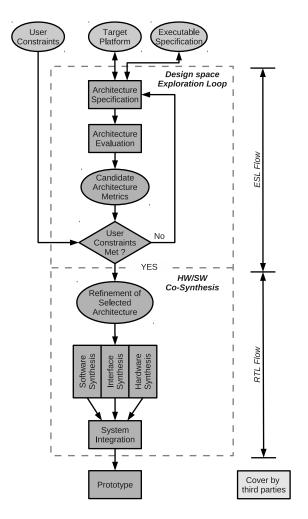

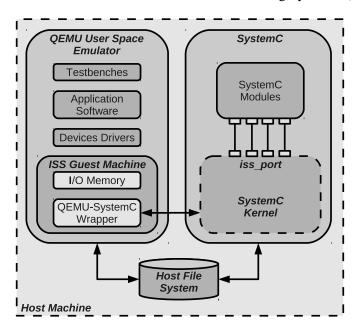

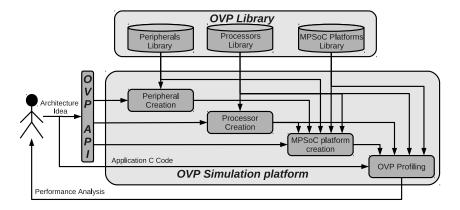

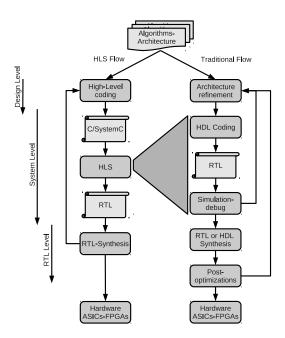

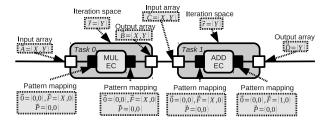

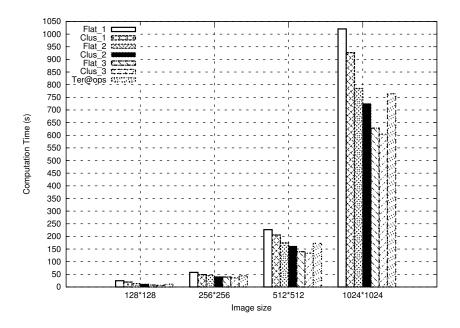

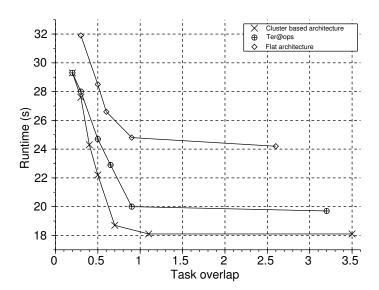

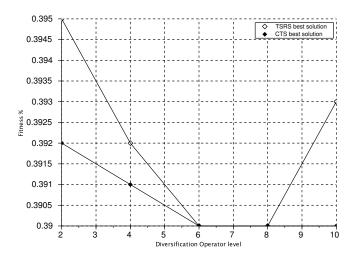

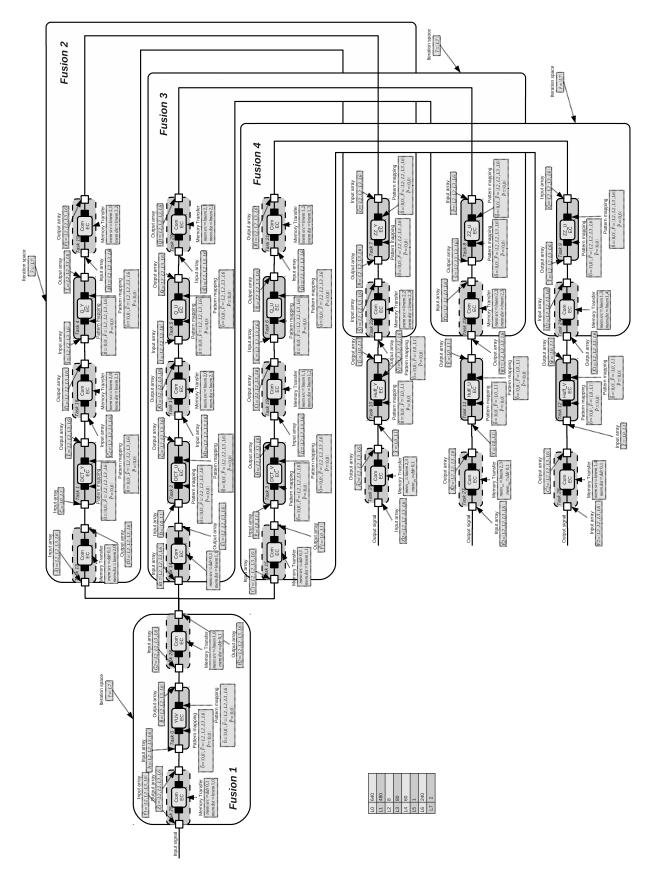

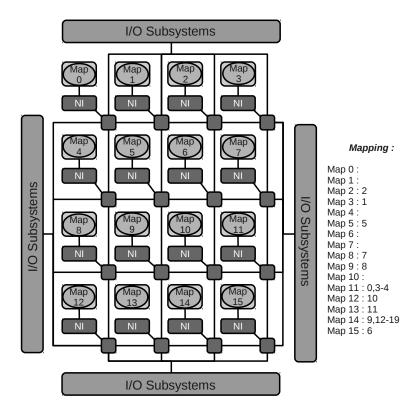

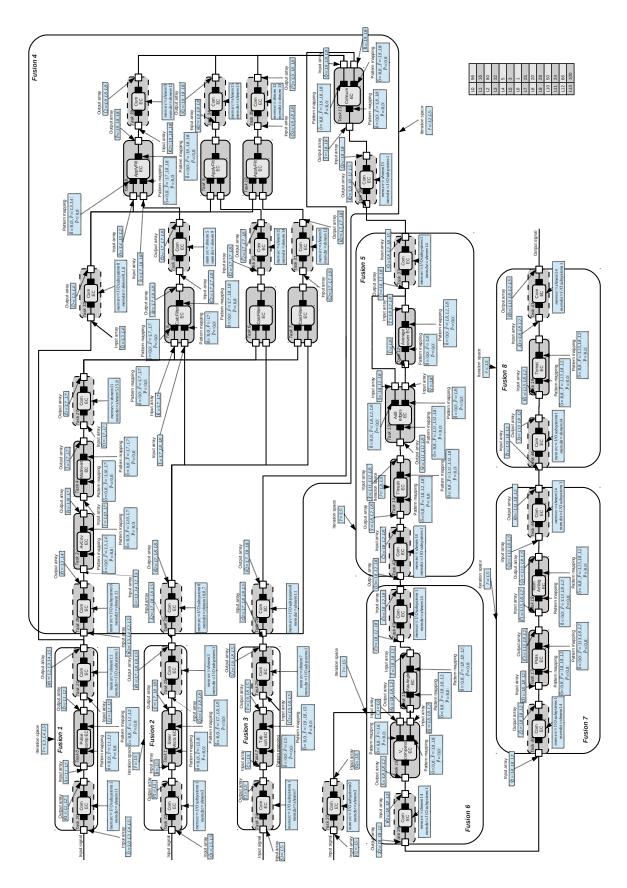

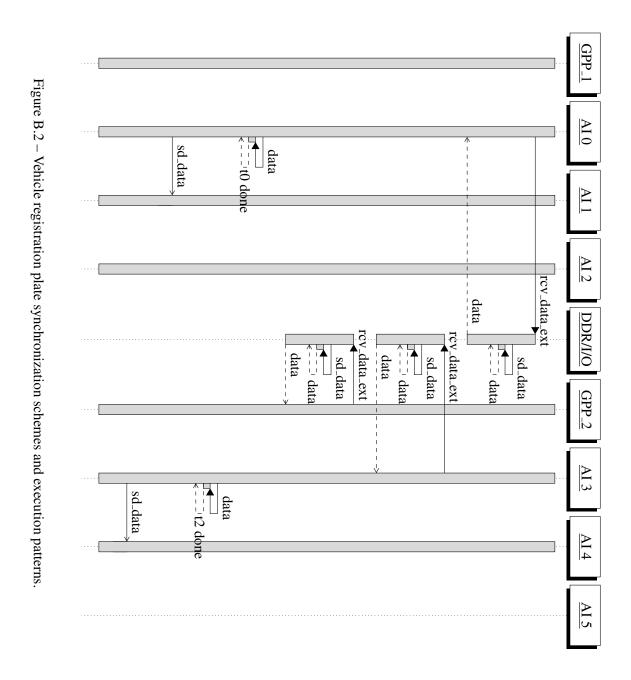

Due to their performance, MPSoC gain popularity, and are now present in various domains of applications. Industry is aware of the need of using multi-core and shortly manycore chips to raise the performance/power ratio especially in embedded systems when power consumption is one of the main constraints [138].